#### UNIVERSITY OF SHERBROOKE

Faculty of Engineering

Department of Electrical and Computer Engineering

## Titre En Français:

# Conception et Fabrication de FinFET GaN Verticaux de Puissance Normalement Bloqués

## Title in English:

# Design and Fabrication of Normally-off Vertical GaN Power FinFET

Doctoral thesis

Specialization: Electrical engineering

#### Nedal Al Taradeh

# **Jury Members:**

| Hassan MAHER        | Professeur, Université de Sherbrooke           | (Director)      |

|---------------------|------------------------------------------------|-----------------|

| Ali SOLTANI         | Professeur, Université de Sherbrooke           | (Co-Supervisor) |

| <b>Denis MACHON</b> | Professeur, Université de Sherbrooke           | (Reporter)      |

| Gilles PATRIARCHE   | Professeur, Directeur de Recherche, CNRS-C2N   | (Examiner)      |

| Yvon CORDIER        | Professeur, Directeur de Recherche, CNRS-CRHEA | (Examiner)      |

December 21, 2021.

Sherbrooke, QC CANADA

"To accomplish great things, we must not only act, but also dream, not only plan, but also believe." « Anatole France »

# Résumé en français

Les énormes demandes de systèmes à hautes performances motivées par des contraintes économiques ont forcé l'industrie des semi-conducteurs à réduire considérablement les dimensions des dispositifs pour compenser les propriétés physiques relativement modestes du silicium. Ces limitations ouvrent la voie aux semi-conducteurs III-V, qui sont d'excellentes alternatives au silicium et peuvent être déclinés dans de nombreuses compositions. Par exemple, le nitrure de gallium (GaN) a été considéré comme un concurrent fabuleux pour faciliter l'horizon de l'industrie des semi-conducteurs au-delà des limitations de performances du silicium en raison de sa grande mobilité, de sa large bande interdite et de ses propriétés de conductivité thermique élevées pour T>300K (Bulk GaN). Il promet de réduire les pertes dans les circuits de conversion de puissance et de réduire de 10 % la consommation d'énergie.

À l'heure actuelle, les structures latérales et verticales ont été considérées pour les dispositifs de puissance en GaN. L'immense potentiel du dispositif HEMT AlGaN/GaN provient du gaz d'électrons à haute densité et à haute mobilité formé au niveau de son hétérojonction. Le dispositif est vulnérable aux problèmes de fiabilité résultant de l'exposition fréquente à des conditions d'effondrement de champ électrique, de température et de contrainte élevés, limitant ainsi ses performances et sa fiabilité. En revanche, les dispositifs de puissance verticaux en GaN ont attiré beaucoup d'attention en raison de leur capacité à atteindre des niveaux de tension et de courant élevés sans augmenter la taille de la puce. De plus, ces dispositifs verticaux présentent des performances thermiques supérieures à leurs homologues latéraux.

Par ailleurs, les dispositifs GaN verticaux sont confrontés aux défis d'un courant de fuite élevée et de claquage se produisant aux coins du canal. Un autre défi associé aux dispositifs normalement bloqués est l'absence d'une méthode optimisée pour éliminer la diffusion de magnésium de la couche p-GaN.

Cette thèse a deux objectifs stratégiques ; premièrement, un dispositif de puissance FinFET GaN normalement bloqué a été conçu et optimisé pour surmonter les défis du FinFET vertical en GaN. Cela a été fait en optimisant les paramètres de performance tels que la tension de seuil V<sub>TH</sub>, la tension de claquage V<sub>BR</sub> et la résistance

spécifique à l'état passant R<sub>ON</sub>. En conséquence, l'impact des paramètres structurels et physiques doit être incorporé pour avoir un processus d'optimisation précis. Par la suite, l'identification et l'optimisation d'un processus de fabrication à faible coût et de haute qualité pour la structure proposée à souligner cette thèse comme deuxième objectif.

#### Mots clés:

Nitrure de gallium (GaN), Simulation, TCAD Sentaurus, Normalement Bloqués, Tension de claquage (V<sub>BR</sub>), Résistance à l'état passant (R<sub>ON</sub>), GaN FinFET vertical, Plans cristallographiques GaN, Hydroxyde de tétraméthylammonium (TMAH), Nanofabrication, source d'abord approcher.

## **Abstract (in English)**

The tremendous demands for high-performance systems driven by economic constraints forced the semiconductor industry to considerably scale the device's dimensions to compensate for the relatively modest Silicon physical properties. Those limitations pave the way for III-V semiconductors, which are excellent alternatives to Silicon and can be declined in many compositions. For example, Gallium Nitride (GaN) has been considered a fabulous competitor to facilitate the semiconductor industry's horizon beyond the performance limitations of Silicon due to its high mobility, wide bandgap, and high thermal conductivity properties for T>300K (Bulk GaN). It promises to trim the losses in power conversion circuits and drive a 10 % reduction in power consumption.

Both lateral and vertical structures have been considered for GaN power devices. The AlGaN/GaN HEMT device's immense potential comes from the high density, high mobility electron gas formed at its heterojunction. The device is vulnerable to reliability issues resulting from the frequent exposure to high electric field collapse, temperature, and stress conditions, thus limiting its performance and reliability. Contrariwise, the vertical GaN power devices have attracted much attention because of the potential to reach high voltage and current levels without enlarging the chip's size. Furthermore, such vertical devices show superior thermal performance to their lateral counterparts.

Meanwhile, Vertical GaN devices have the challenges of high leakage current and the breakdown occurring at the corners of the channel. Another challenge associated with Normally off devices is the lack of an optimized method for eliminating the magnesium diffusion from the p-GaN layer.

This thesis has two strategic objectives; Firstly, a Normally-OFF GaN Power FinFET has been designed and optimized to overcome the vertical GaN FinFET challenges. It was done by optimizing the performance parameters such as threshold voltage  $V_{TH}$ , high breakdown  $V_{BR}$ , and the specific ON-state-resistance  $R_{ON}$ . Accordingly, the impact of both structural and physical parameters should be incorporated to have an exact optimization process. Afterward, the identification and optimization of a low-cost and high-quality fabrication process for the proposed

structure underlined this thesis as the second objective.

## **Keywords:**

Gallium Nitride (GaN), Simulation, TCAD *Sentaurus*, Normally-OFF, Breakdown Voltage (V<sub>BR</sub>), On-state resistance (R<sub>ON</sub>), Vertical GaN FinFET, GaN crystallographic planes, Tetramethylammonium hydroxide (TMAH), Nanofabrication, source first approach.

# **Table of Contents**

|                                                                               | l    |

|-------------------------------------------------------------------------------|------|

| Abstract (in English)                                                         | III  |

| Table of Contents                                                             | V    |

| Acknowledgment                                                                | VIII |

| List of Abbreviations and Acronyms                                            | X    |

| List of Figures                                                               | Xl   |

| List of Tables                                                                | XV   |

| General Introduction                                                          | 1    |

| CHAPTER ONE: GAN POWER TECHNOLOGY STATUS AND CHALLENGES                       | 4    |

| 1.1 The Growth of GaN's industry                                              | 4    |

| 1.1.1 Device Power Market                                                     | 4    |

| 1.1.2 GaN RF Market                                                           | 6    |

| 1.2 Introduction to GaN Physics                                               | 7    |

| 1.2.1 GaN crystallographic structure                                          | 7    |

| 1.2.2 The electrical properties Of Gallium Nitride                            | 8    |

| 1.3 GaN Substrates options                                                    | 10   |

| 1.4 Lateral GaN HEMTs Transistors                                             | 11   |

| 1.4.1 Enhanced HEMTs Transistors                                              | 12   |

| 1.4.2 Challenges of GaN HEMTs devices                                         | 13   |

| 1.5 Vertical GaN Power Devices:                                               | 13   |

| 1.5.1 Challenges of vertical GaN devices:                                     | 14   |

| 1.6 Main Objectives and methodology                                           | 17   |

| 1.7 Thesis Outline                                                            | 18   |

| CHAPTER TWO: STATE -OF- THE ART OF VERTICAL GAN-BASED TECHNOLOGY              | 20   |

| 2.1 Introduction                                                              | 20   |

| 2.2 Vertical Heterojunction Field-Effect Transistor (VHFET)                   | 20   |

| 2.3 Transistor Vertical MOS field-effect transistor (MOSFET)                  | 21   |

| 2.3.1 Inversion GaN MOSFET (GaN Trench MOSFET)                                | 21   |

| 2.3.2 Accumulation MOSFET (or Fin power FET)                                  | 22   |

| 2.4 Current Aperture Vertical Electron Transistor (CAVET)                     | 24   |

| 2.4.1 Non-trench Gate CAVET:                                                  | 24   |

| 2.5 Comparison of different vertical architectures                            | 26   |

| 2.6 History and progress in the fabrication of the most promising transistors | 27   |

| 2.6.1 CAVET                                                                   | 28   |

| 2    | 2.6.2    | Normally Off GaN (FinFET)                                                                       | 30        |

|------|----------|-------------------------------------------------------------------------------------------------|-----------|

| CHA  | PTER T   | HREE: DESIGN AND OPTIMIZATION OF NORMALLY-OFF VERTICAL GAN FINFET U                             | JSING     |

| TCAI | D TOOI   |                                                                                                 | 31        |

| 3.1  | Int      | roduction:                                                                                      | 31        |

| 3    | 3.1.1    | Introduction to TCAD Sentaurus tool:                                                            | 31        |

| 3.2  | Th       | e incorporated parameters and models incorporated in the Simulations                            | 32        |

| 3.3  | Int      | roducing the Vertical GaN FinFET starting structure                                             | 33        |

| 3    | 3.3.1    | The meshing                                                                                     | 35        |

| 3    | 3.3.2    | Contacts definition                                                                             | 36        |

| 3    | 3.3.3    | Voltage                                                                                         | 36        |

| 3    | 3.3.4    | Ohmic / Schottky                                                                                | 36        |

| -    | 3.3.5    | Contact resistance                                                                              | 37        |

| 3.4  | Ex       | traction of performance parameters                                                              | 37        |

| 3    | 3.4.1    | Comparison of simulation results with Literature                                                | 37        |

| 3.5  | Su<br>38 | mmary of the optimization process of vertical GaN power FinFET starting design using TCAD Senta | urus tool |

| 3    | 3.5.1    | Optimization of GaN Fin channel region parameters                                               | 40        |

| 3    | 3.5.2    | Optimization of GaN drift region parameters                                                     | 42        |

| 3    | 3.5.3    | Comparison between the first optimized version and the real epitaxial-GaN wafers                | 47        |

| 3.6  | Pa       | rameter's sensitivity in the design of Vertical GaN power FinFET                                | 49        |

| 3.7  | Co       | onclusion                                                                                       | 51        |

| CHA  | PTER F   | OUR: INTRODUCTION TO VERTICAL GAN FINFET FABRICATION PROCESS                                    | 52        |

| 4.1  | Int      | roduction                                                                                       | 52        |

| 4.2  | Ga       | N epitaxial growth                                                                              | 52        |

| 4.3  | Int      | roduction to vertical GaNFinFET fabrication process                                             | 54        |

| 4.4  | - A      | detailed description of vertical GaNFinFET processing modules                                   | 55        |

| 2    | 4.4.1    | Wafers dicing                                                                                   | 55        |

| 4    | 4.4.2    | Samples Cleaning process                                                                        | 56        |

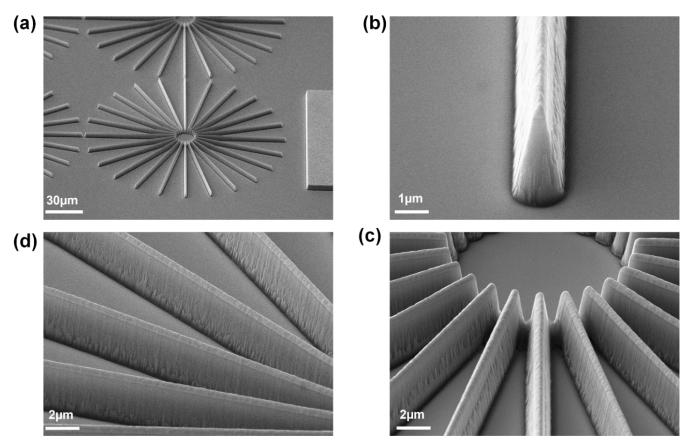

| 2    | 4.4.3    | Orientation determination process (OD)                                                          | 57        |

| 2    | 4.4.4    | Device Isolation( Li)                                                                           | 58        |

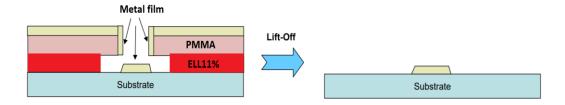

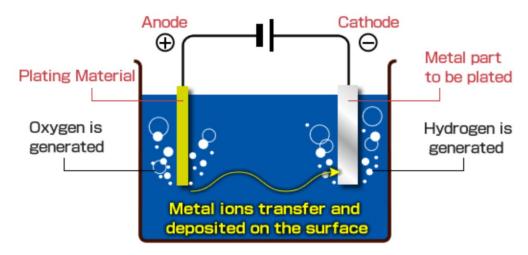

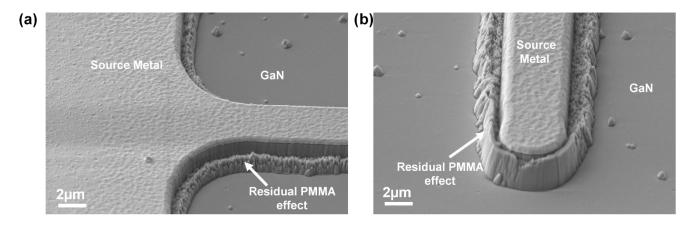

| 2    | 4.4.5    | Source deposition process (OH)                                                                  | 60        |

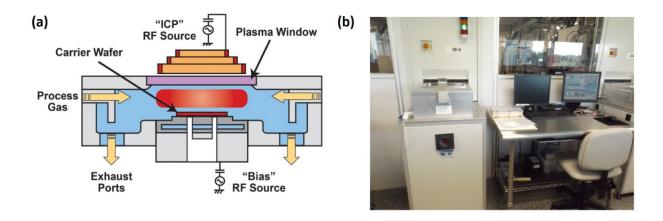

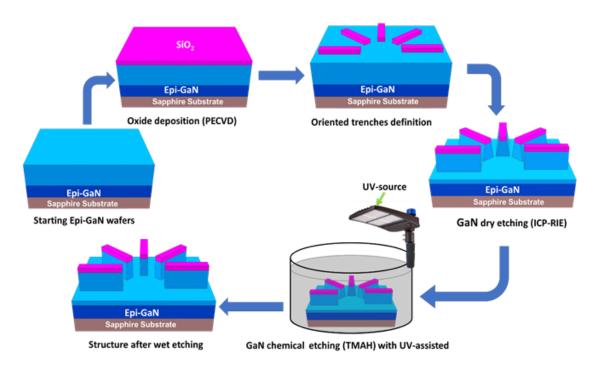

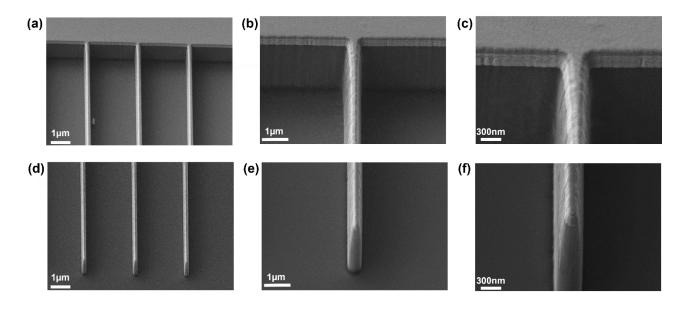

| 2    | 4.4.6    | GaN etching process (GaN)                                                                       | 63        |

| 2    | 4.4.7    | Gate Oxide Deposition (Al <sub>2</sub> O <sub>3</sub> ):                                        | 72        |

| 2    | 4.4.8    | Al <sub>2</sub> O <sub>3</sub> opening process                                                  | 74        |

| 4    | 4.4.9    | Gate Metallization process                                                                      | 75        |

| 2    | 4.4.10   | The interconnection step (IN)                                                                   | 77        |

| 4.4     | 4.11            | Device Passivation(SiN)                                                                             | 78  |

|---------|-----------------|-----------------------------------------------------------------------------------------------------|-----|

| 4.4     | 4.12            | Drain deposition (Drain)                                                                            | 78  |

| 4.4     | 4.13            | contact opening (CO)                                                                                | 79  |

| 4.5     | con             | clusion                                                                                             | 79  |

|         |                 | IVE: CHARACTERIZATION OF M-GAN AND A-GAN CRYSTALLOGRAPHIC PLANES AF MICALLY ETCHED IN TMAH SOLUTION |     |

| 5.1     | Do              | cument descriptions                                                                                 | 80  |

| 5.2     | Ab              | stract:                                                                                             | 81  |

| 5.3     | Inti            | oduction                                                                                            | 81  |

| 5.4     | Ex              | periment Technique                                                                                  | 83  |

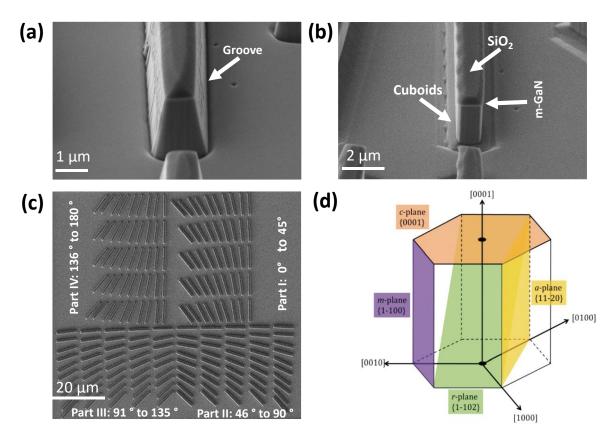

| 5.5     | Res             | sults and Discussion                                                                                | 85  |

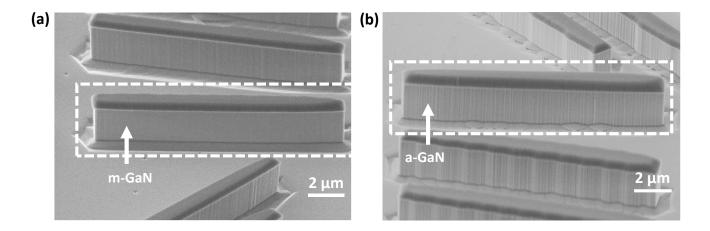

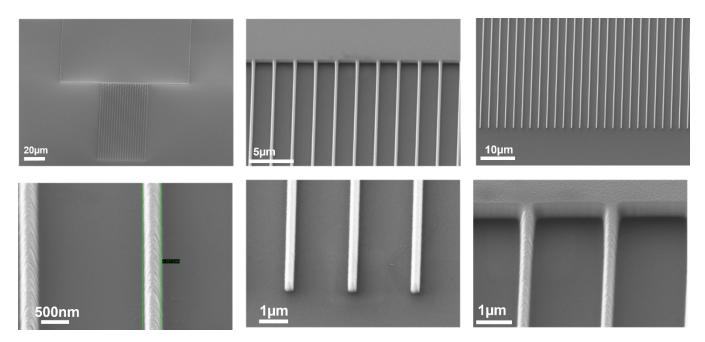

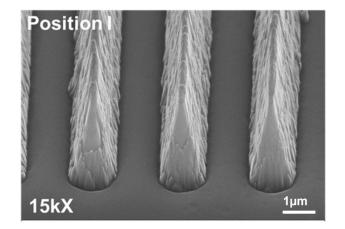

| 5.5     | 5.1             | GaN Channel Sidewalls Etching Using the Proposed OD Procedure                                       | 85  |

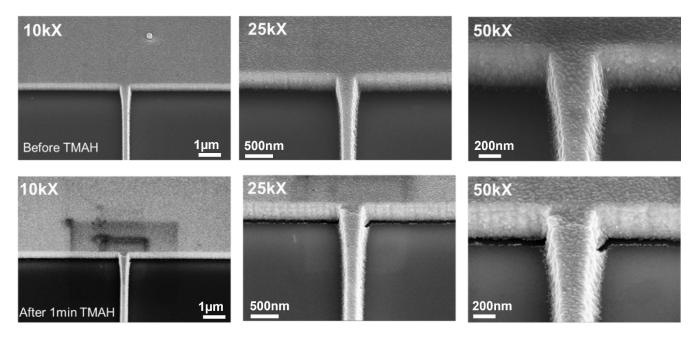

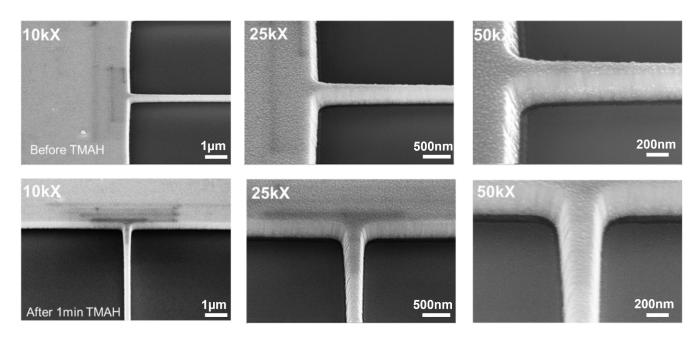

| 5.5     | 5.2             | Investigation of the Morphology of the Groove Surrounding the Fins after TMAH Etching               | 86  |

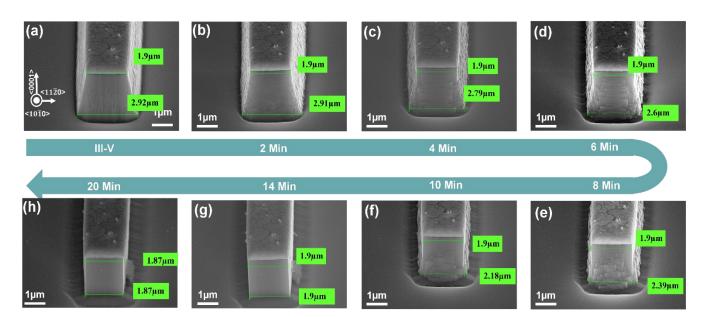

|         | 5.3<br>ilizatio | GaN Non-Polar Planes Wet Etching Rate Estimation in TMAH Solution with and without UV So            |     |

| 5.6     | Coı             | nclusions                                                                                           | 90  |

| СНАРТ   | ER S            | X: OPTIMIZATION OF VERTICAL FINFET FABRICATION PROCESS MODULES                                      | 91  |

| 6.1     | Inti            | oduction                                                                                            | 91  |

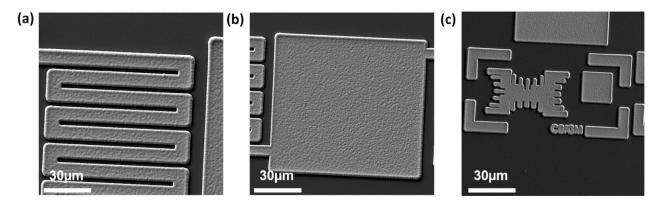

| 6.2     | Ma              | sks Design and Fabrication                                                                          | 91  |

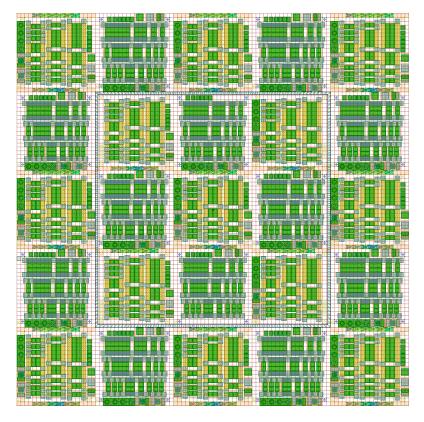

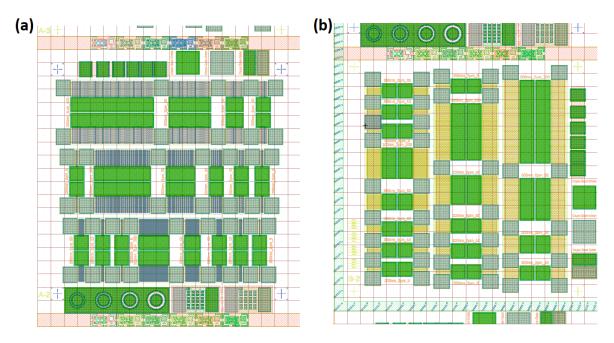

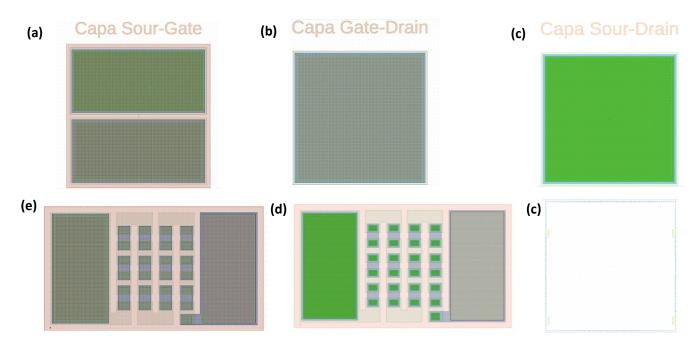

| 6.2     | 2.1             | Optimization-based mask design:                                                                     | 92  |

| 6.2     | 2.2             | Final device mask design:                                                                           | 93  |

| 6.3     | Wa              | fers availability for the optimization and final fabrication process                                | 96  |

| 6.4     | Op              | timization of source metallization process (OH)                                                     | 97  |

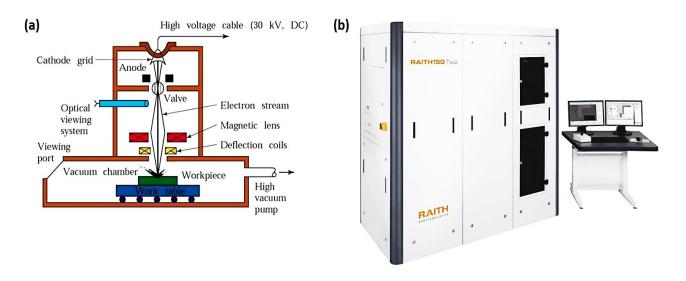

| 6.4     | 4.1             | Optimization of EBL recipe for lift-off process.                                                    | 97  |

| 6.4     | 4.2             | Design of source metallization stack composition.                                                   | 100 |

| 6.4     | 4.3             | Optimization of GaN dry etching process                                                             | 107 |

| 6.4     | 1.4             | Optimization of GaN wet etching process                                                             | 108 |

| 6.5     | Op              | timization of Gate metallization process(GM)                                                        | 112 |

| 6.5     | 5.1             | Optimization of Gate metallization by Electroplating:                                               | 113 |

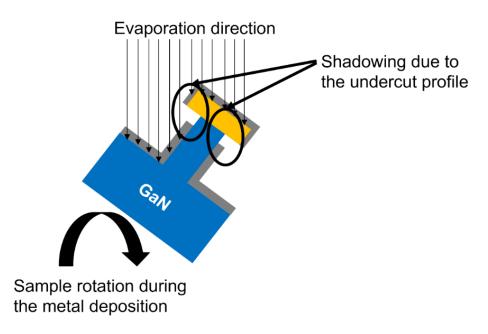

| 6.5     | 5.2             | Optimization of Gate metallization by Evaporation with rotation and angle:                          | 118 |

| СНАРТ   | ER S            | EVEN: GENERAL CONCLUSIONS AND PERSPECTIVES                                                          | 119 |

| 7.1     | Cor             | nclusions générales et perspectives (en français)                                                   | 119 |

| 7.2     | Ger             | neral conclusions and perspectives (English)                                                        | 121 |

| 7.3     | Cu              | rrent and upcoming publications                                                                     | 122 |

| Dafarar | 2000            |                                                                                                     | 124 |

# Acknowledgment

The beyond four years are a completely critical period in my life. The training I acquired at Pr. Hassan's lab makes me a higher education researcher. Meanwhile, it additionally makes me mature as someone with a stronger personality, insights, and ambitions. During those years, many people have helped me alongside the manner, and I would love to specify my gratitude to them:

I am deeply grateful to all of the reviewers who took the time to review this work, especially to the scientific reviewers: Mr. Denis MACHON, professor at the University of Sherbrooke (Reporter), and Mr.Gilles PATRIARCHE, Professeur, Directeur de Recherche, CNRS-C2N (as an external examiner), and Mr. Yvon CORDIER, Directeur de Recherche, CNRS-CRHEA (as an external examiner).

I am indebted to all my supervisors, professors at the University of Sherbrooke for their knowledge and guidance during my Ph.D. I also take this opportunity to apologize to them for the many random questions, the somewhat long presentations, and all the last-minute submissions.

Indeed, I would like to thank Prof. Hassan MAHER for giving me the wonderful opportunity to work in this exciting field of research under his supervision. His insights, encouragement, patience, optimism, and trust always motivate me to work on new ideas and approaches and tackle the most fundamental problems. He creates many opportunities for me to gain industrial experiences and establish connections in my research domain. Outside the technical world, I also learned a lot from him in many other aspects. I learned a lot from him to be an impactful researcher in academia and combine research and entrepreneurship. All these learnings from him are invaluable in my life. He is surely a professor, a father, and a great supporter of anyone seeking knowledge and innovation.

I am also thankful to Dr. Ali SOLTANI, my co-supervisor, for his guidance and suggestions and for being willing to validate the outputs that arise from my research. I appreciate his constant encouragement, timely pieces of advice, and suggestions throughout this research. I am also grateful for the kind support that he provided me during my stay in the city of Sherbrooke.

A special thanks to the people in The Nanotechnologies and NanoSystems Laboratory (LN2) laboratory who have always been friendly, and their kind support always made my university life easier. Then I would like to thank my colleagues in group GaN. I want to thank Mr. Christophe RODRIGUEZ, a Research professional at the University of Sherbrooke, for his great support in training and leading my progress in the cleanroom. A special thanks to the previous and current research group members: Faissal El Hamidi, Mohammed Benjelloun, Aomar Ezza, Zahraa Zaidan, Gwen Rolland, Oleh Fesiienko, Nabil Chakhchaoui, and Bilal Hassan, who gave a lot of support during my first academic year.

Finally, I would like to express my sincere thanks to my family members for their everlasting love. Even though most of them are far from me, they always support me, providing constant encouragement to do my best in my thesis. To my dear parents, your kind support and supplications make me more dedicated to pursuing my Ph.D.

# **List of Abbreviations and Acronyms**

| AlGaN                      | Aluminum Gallium Nitride                                    |

|----------------------------|-------------------------------------------------------------|

| AlN                        | Aluminum Nitride                                            |

| InAlN                      | Indium Aluminum Nitride                                     |

| GaN                        | Gallium Nitride                                             |

| GaAs                       | Gallium Arsenide                                            |

| Si                         | Silicon                                                     |

| SiC                        | Silicon Carbide                                             |

| SiGe                       | Silicon Germanium                                           |

| InP                        | Indium Phosphide                                            |

| FET                        | Field-effect transistor                                     |

| HEMT                       | High Electron Mobility Transistor                           |

| RF                         | Radio Frequency                                             |

| LDMOS                      | Laterally diffused metal oxide semiconductor                |

| MESFET                     | Metal-Semiconductor Field-Effect Transistor                 |

| MOSHEMT                    | Metal-Oxide-Semiconductor High Electron Mobility Transistor |

| CAVET                      | Current aperture Vertical Electron Transistor               |

| VHFET                      | Vertical Heterojunction Field-Effect Transistor.            |

| MOSFET                     | Metal Oxide Semiconductor vertical field effect Transistor  |

| UID gallium                | Unintentionally doped GaN                                   |

| CBLs                       | Current blocking layers                                     |

| HBL                        | Hybrid blocking layers                                      |

| 2DEG                       | Two-dimensional electron gas                                |

| MOCVD                      | Metal-organic chemical vapor deposition                     |

| MBE                        | Molecular Beam epitaxy                                      |

| FOM                        | Figure of merit                                             |

| JFM                        | Johnson's face merit of merit                               |

| KFM                        | Keye's figure of merit                                      |

| BFM                        | Baliga's Figure of Merit                                    |

| TMAH                       | Tetramethylammonium hydroxide                               |

| EBL                        | Electron Beam Lithography                                   |

| $\mathbf{V}_{\mathrm{TH}}$ | Threshold voltage                                           |

| Ron                        | Specific on-state-resistance                                |

| $V_{BR}$                   | Breakdown voltage                                           |

| L <sub>GTG</sub>           | Gate to Gate Length                                         |

| EBR                        | Edge Bead Removal                                           |

| AFM                        | Atomic Force Microscopy                                     |

| SEM                        | Scanning Electron Microscopy                                |

| RTA                        | Rapid Thermal Annealing                                     |

| OD                         | Orientation Determination                                   |

| AOE                        | Advanced Oxide Etching                                      |

| AOL                        | Advanced Oxide Etening                                      |

# **List of Figures**

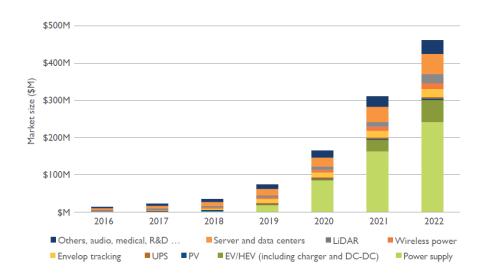

| Figure 1:Predictive distribution of the energy market GaN[13] compiled in 2017 for supporting applications, including food,       |

|-----------------------------------------------------------------------------------------------------------------------------------|

| energy, wireless, electric/hybrid electric vehicles (EV / HEV), sources of uninterruptible power supply (UPS), Photovoltaics 4    |

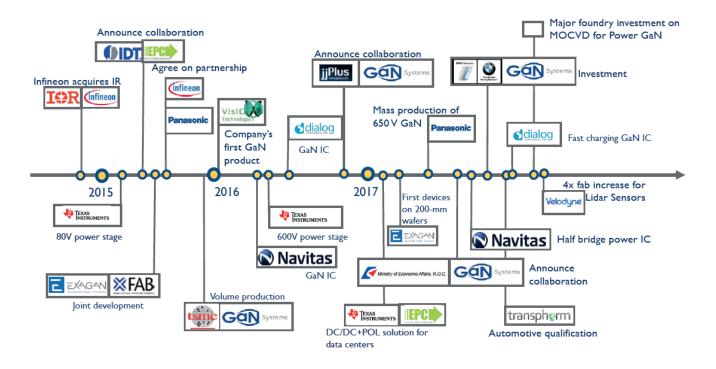

| Figure 2:Business investment GaN by companies established in 2017 [14]5                                                           |

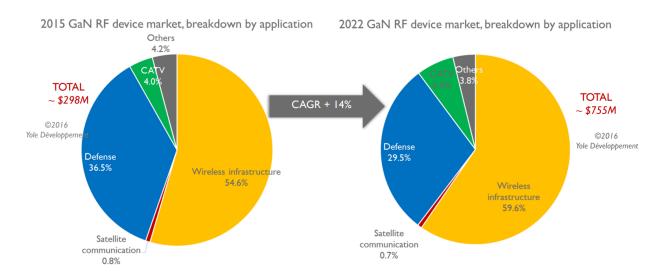

| Figure 3:GaN RF market breakdown by an application between 2015-2022, including major telecommunications and military             |

| contributions predicting an annual growth rate of 23% to an estimated \$ 1.3 billion of 2023[16]6                                 |

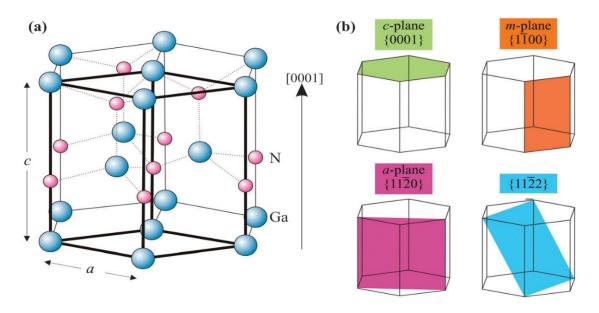

| Figure 4:Crystal structure of GaN (a)Wurtzite Phase, (b) highlights the polar c-plane, the nonpolar a-, and m-planes, and the     |

| semi-polar plane [18][19]                                                                                                         |

| Figure 5:Map of distribution of III-V materials and their alloys according to their mesh sizes and their forbidden bands [24].8   |

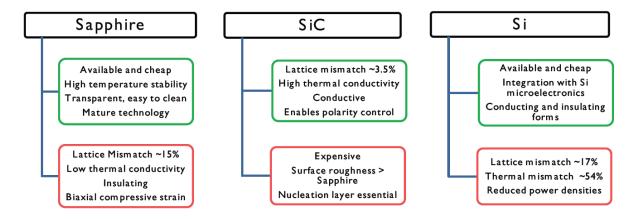

| Figure 6: Advantages and drawbacks of substrates options for GaN epitaxy                                                          |

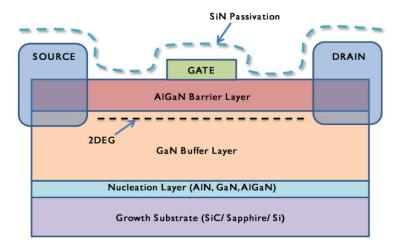

| Figure 7: Structure of an AlGaN / GaN HEMT [39].                                                                                  |

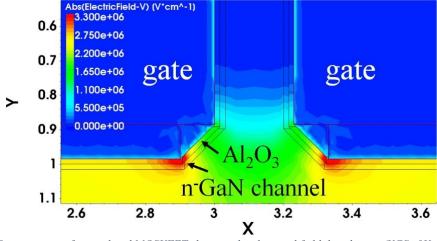

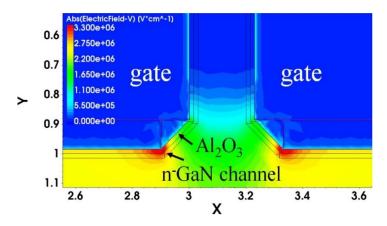

| Figure 8: Cross-section of a simulated MOSVFET showing the electrical field distribution (VGS=0V, VBR=697V)16                     |

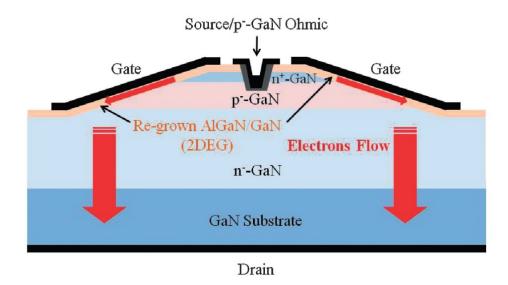

| Figure 9:Structure a vertical transistor and a heterojunction field-effect transistor (VHFET)[9]20                                |

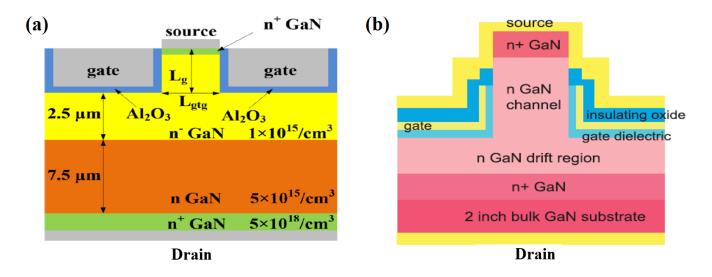

| Figure 10: Structure of vertical GaN field-effect transistor MOSVFET[10].                                                         |

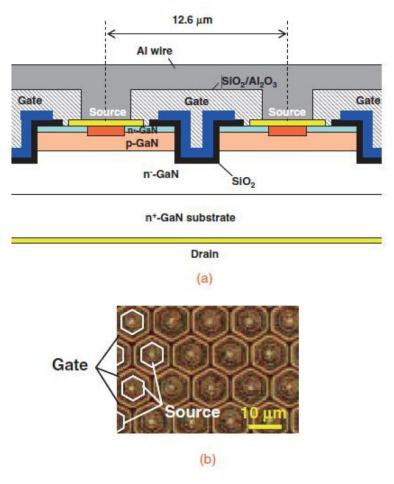

| Figure 11: Schematic of MOSVFET device (a) simulated structure of a Normally Off MOSVFET [46]. (b) Structure of                   |

| fabricated MOSVFET to accumulation (FinFET)[47]                                                                                   |

| Figure 12:Structure an AlGaN / GaN CAVET[35]                                                                                      |

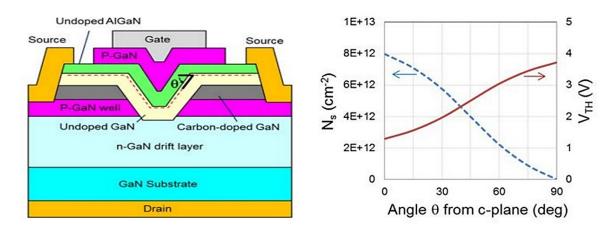

| Figure 13:Trench CAVET. (a)Structure of an AlGaN / GaN CAVET inclined channel [11]. (b) carrier density ns and tension            |

| threshold Vth calculated in the channel p-GaN / AlGaN / GaN depending on the angle of inclination $\theta$ concerning the c-plane |

| (0001)                                                                                                                            |

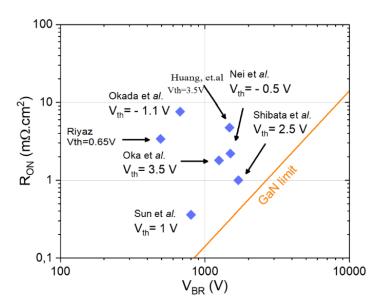

| Figure 14: Resistance in the conducting state RON depending on the voltage Vbr breakdown different architectures of               |

| vertical transistors                                                                                                              |

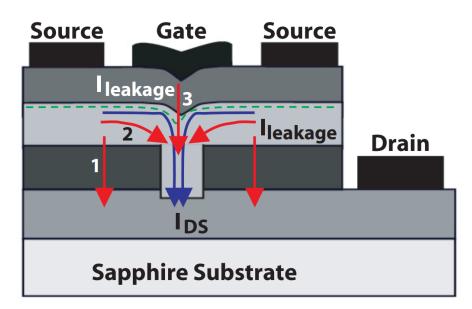

| Figure 15:Schematic leakage current resources in CAVET represented by arrows pale gray color [14]28                               |

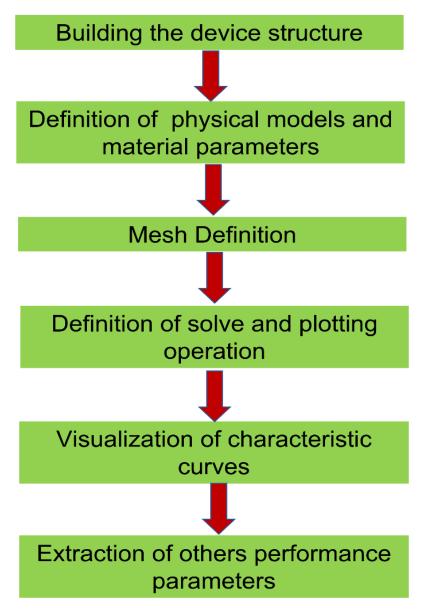

| Figure 16: The flow of TCAD simulation procedures.                                                                                |

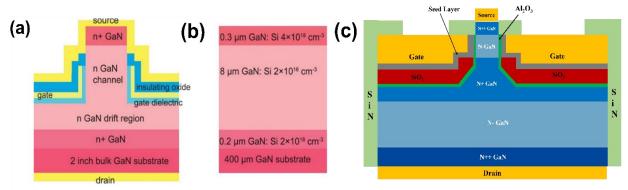

| Figure 17: a)Schematic of the calibration structure of vertical GaN FinFET. b). c) schematic of the simulated structure in        |

| TCAD Sentaurus                                                                                                                    |

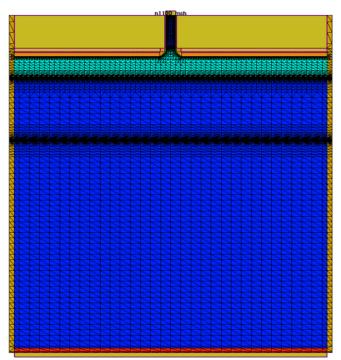

| Figure 18: Schematic of the generated mesh using SNMESH                                                                           |

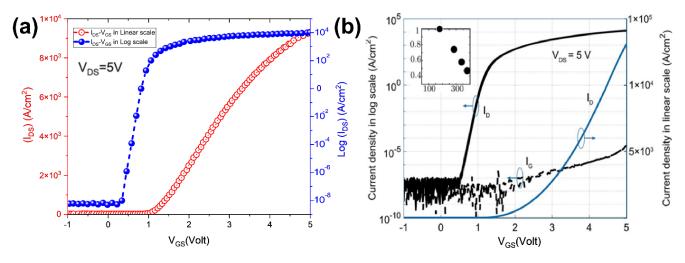

| Figure 19: Comparison between the transfer characteristics of simulated vertical GaN FinFETand and reference article,             |

| (a)Transfer characteristics of the simulated transistor. Lgtg is 200 nm[39], (b) Reference material transfer characteristics[37], |

| Lgtg is 180 nm                                                                                                                    |

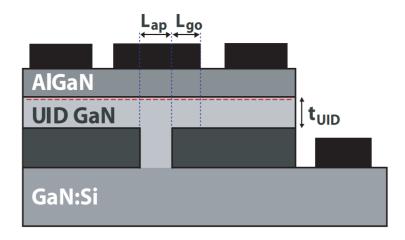

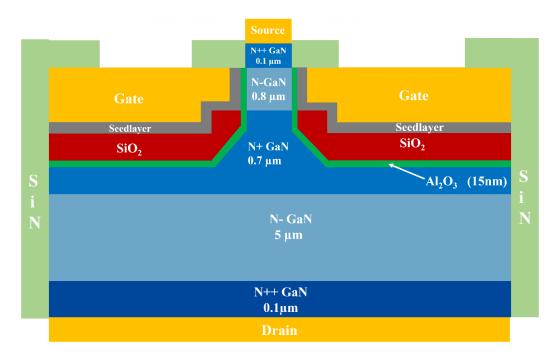

| Figure 20: Schematic cross-section of a simulated normally-off GaN Fin Power FET                                                  |

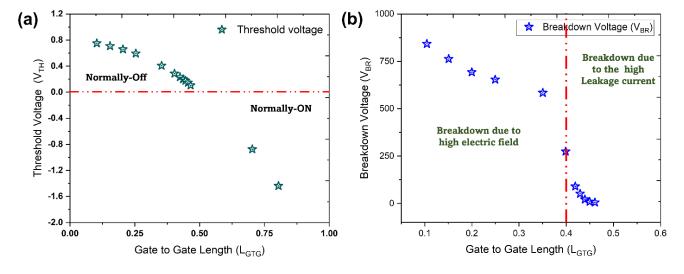

| Figure 21: The gate-to-gate length (Lgtg) impacts a) the threshold voltage (Vth) and b) the breakdown voltage ( $V_{BR}$ ) at     |

| $V_{GS}$ =0 $V$ 40                                                                                                                |

| Figure 22: Cross-section shows the electric field distribution for the simulated vertical GaN FinFET (VGS=0V, VBR=697V).          |

| 41                                                                                                                                |

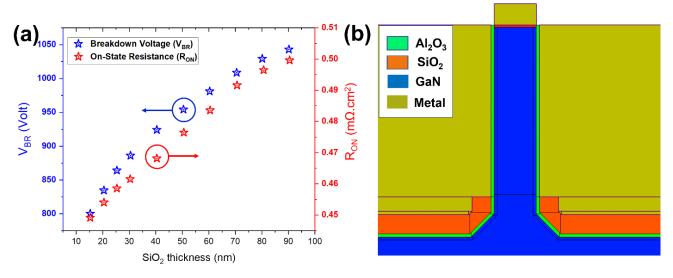

| Figure 23: a) The influence of $SiO_2$ thickness on the $V_{BR}$ and $R_{ON}$ . b). Schematic of simulated vertical GaN FinFET v                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| SiO <sub>2</sub> /Al <sub>2</sub> O <sub>3</sub> composite as gate oxide                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 42                               |

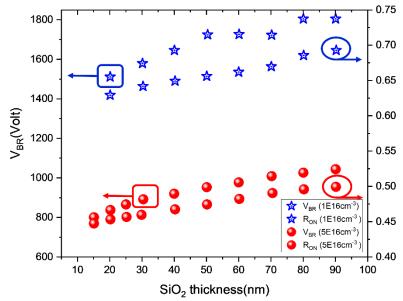

| $Figure\ 24: Impact\ the\ SiO_2\ thickness\ on\ the\ V_{BR}\ and\ the\ R_{ON}\ for\ two\ different\ Drift\ Layer\ doping\ concentrations\ (5x)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 10 <sup>16</sup> cm <sup>-</sup> |

| <sup>3</sup> : Red and 1x10 <sup>16</sup> cm <sup>-3</sup> : blue).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 43                               |

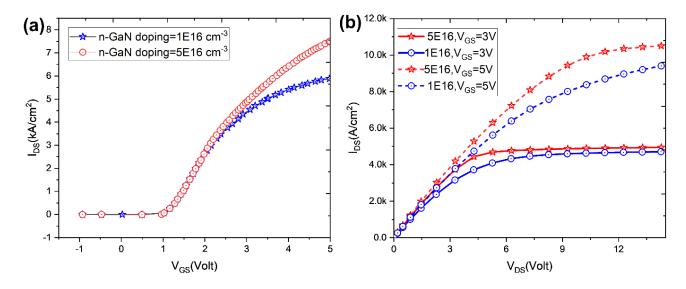

| $Figure~25: Current~characteristics~for~two~different~drift~layer~doping~concentration~(5x10^{16}~cm^{-3}and~1x10^{16}~cm^{-3}), t_{SiO}~cm^{-2}~drift~layer~doping~concentration~(5x10^{16}~cm^{-3}and~1x10^{16}~cm^{-3}), t_{SiO}~cm^{-2}~drift~layer~doping~concentration~(5x10^{16}~cm^{-3}and~1x10^{16}~cm^{-3}and~1x10^{16}~cm^{-3}and~1x10^{16}~cm^{-3}and~1x10^{16}~cm^{-3}and~1x10^{16}~cm^{-3}and~1x10^{16}~cm^{-3}and~1x10^{16}~cm^{-3}and~1x10^{16}~cm^{-3}and~1x10^{16}~cm^{-3}and~1x10^{16}~cm^{-3}and~1x10^{16}~cm^{-3}and~1x10^{16}~cm^{-3}and~1x10^{16}~cm^{-3}and~1x10^{16}~cm^{-3}and~1x10^{16}~cm^{-3}and~1x10^{16}~cm^{-3}and~1x10^{16}~cm^{-3}and~1x10^{16}~cm^{-3}and~1x10^{16}~cm^{-3}and~1x10^{16}~cm^{-3}and~1x10^{16}~cm^{-3}and~1x10^{16}~cm^{-3}and~1x10^{16}~cm^{-3}and~1x10^{16}~cm^{-3}and~1x10^{16}~cm^{-3}and~1x10^{16}~cm^{-3}and~1x10^{16}~cm^{-3}and~1x10^{16}~cm^{-3}and~1x10^{16}~cm^{-3}and~1x10^{16}~cm^{-3}and~1x10^{16}~cm^{-3}and~1x10^{16}~cm^{-3}and~1x10^{16}~cm^{-3}and~1x10^{16}~cm^{-3}and~1x10^{16}~cm^{-3}and~1x10^{16}~cm^{-3}and~1x10^{16}~cm^{-3}and~1x10^{16}~cm^{-3}and~1x10^{16}~cm^{-3}and~1x10^{16}~cm^{-3}and~1x10$ | <sub>02</sub> =90nm.             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 43                               |

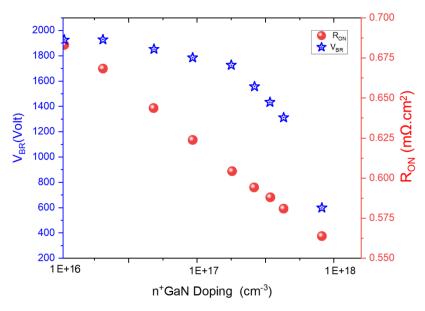

| Figure 26:Impact of the n+GaN doping concentration on the $V_{BR}$ and $R_{ON}$ . at 0.3 $\mu$ m N+GaN thickness.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 44                               |

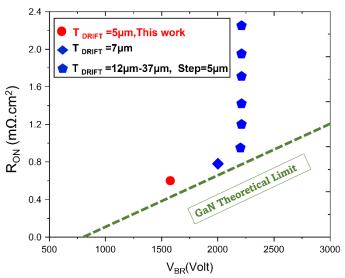

| Figure 27:Impact of the Drift Layer thickness on the $V_{BR}$ and the $R_{ON}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 45                               |

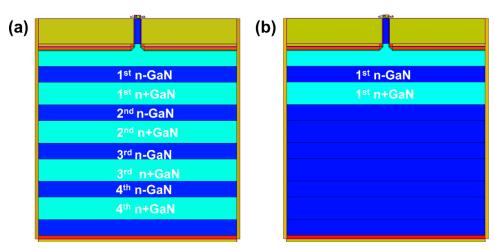

| Figure 28: Schematic of n-GaN/n+GaN blocks in Drift Layer (zebra model) a) for all residual n-GaN drift region b) o                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | nly one                          |

| n-GaN/n+GaN blocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 46                               |

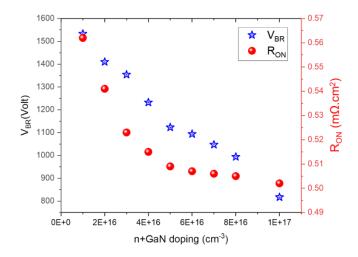

| Figure 29:Impact of the doping concentration of added n+GaN on VBR and RON values                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 47                               |

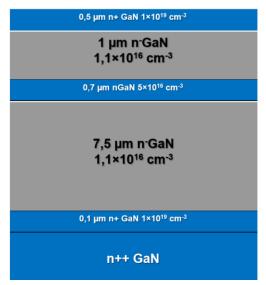

| Figure 30: Schematic of real GaN epitaxial wafer ready for the fabrication process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 47                               |

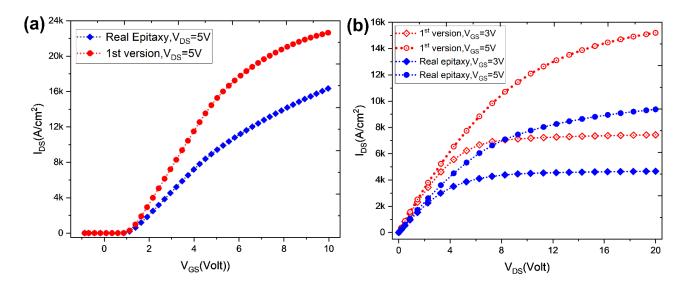

| Figure 31: $I_{DS}$ - $V_{DS}$ and $I_{DS}$ - $V_{GS}$ of the 1 <sup>st</sup> optimized version and the one based on the real epitaxial structure, a) $I_{DS}$ - $V_{DS}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | GS and b)                        |

| $I_{DS}$ - $V_{DS}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 48                               |

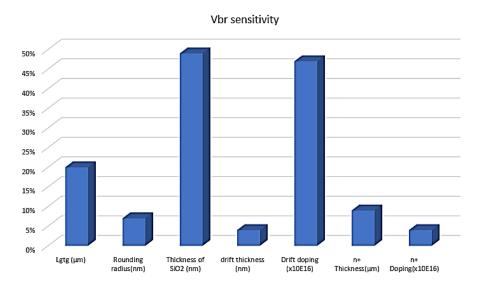

| Figure 32: The sensitivity of parameters to VBR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 50                               |

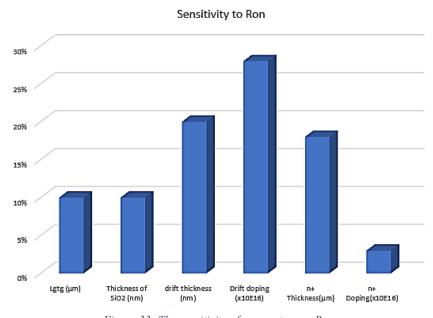

| Figure 33: The sensitivity of parameters on R <sub>ON</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 50                               |

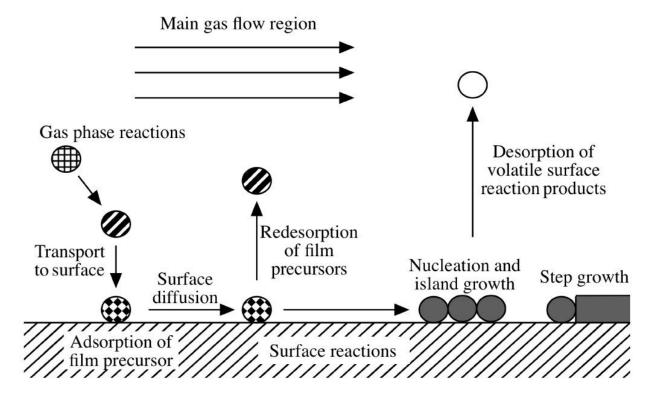

| Figure 34:Schematic representation of the fundamental transport and reaction steps underlying MOCVD [50]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 53                               |

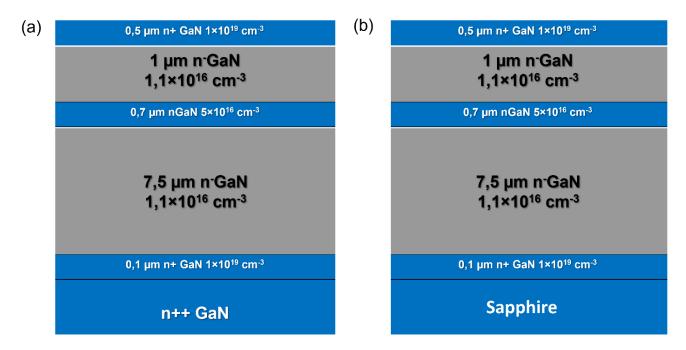

| Figure 35:The schematic of real GaN epitaxial wafers on GaN and sapphire substrates;(a) GaN wafer and (b)Sapphi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | re wafer                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 54                               |

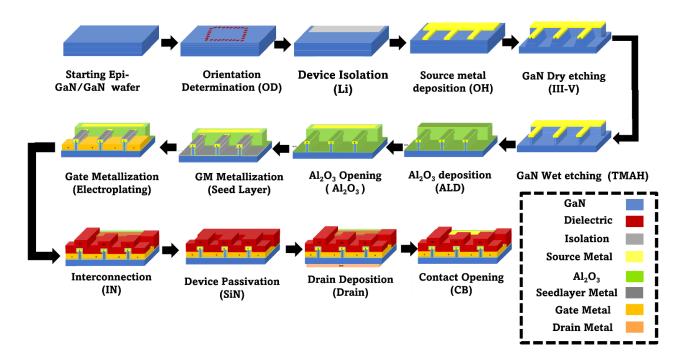

| Figure 36:Sequence of final vertical GaN FET processing modules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 55                               |

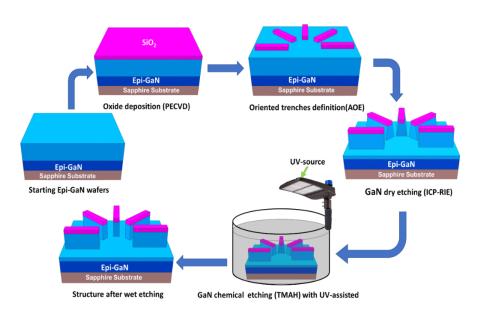

| Figure 37:Fabrication process for GaN fingers sidewalls engineering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 58                               |

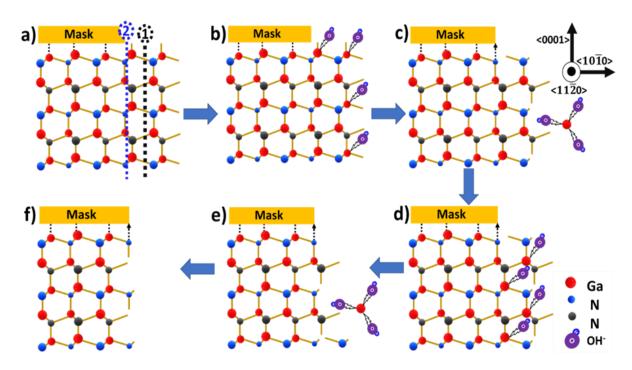

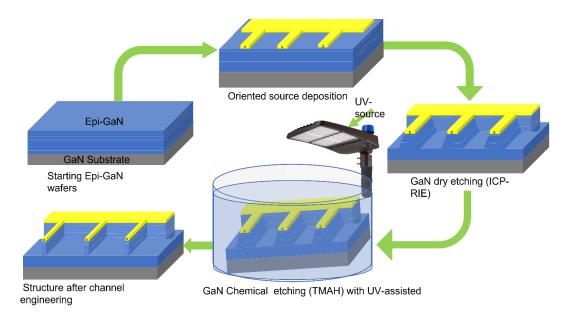

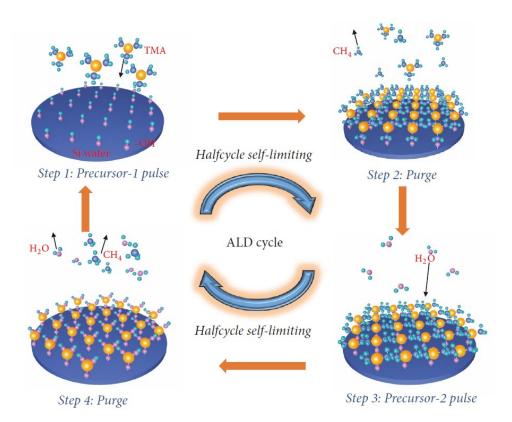

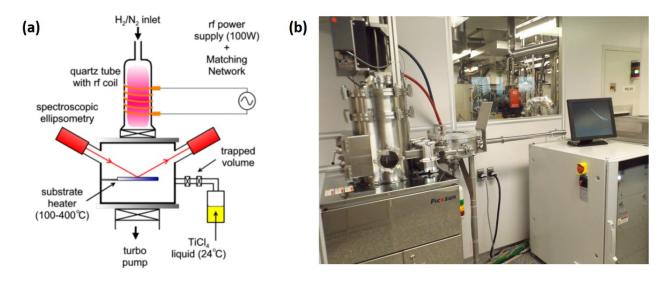

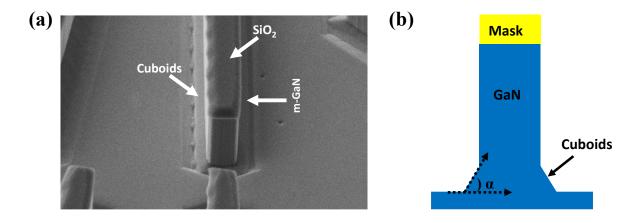

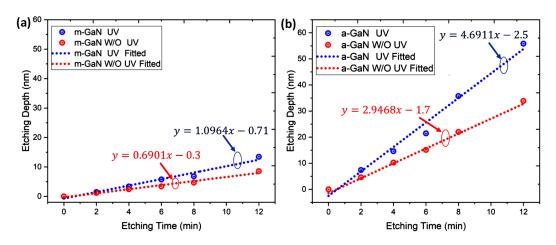

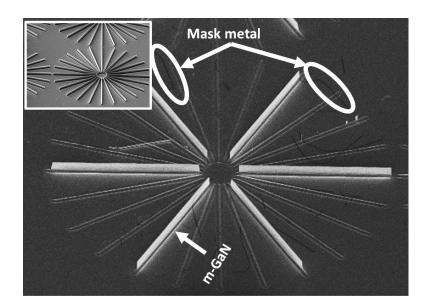

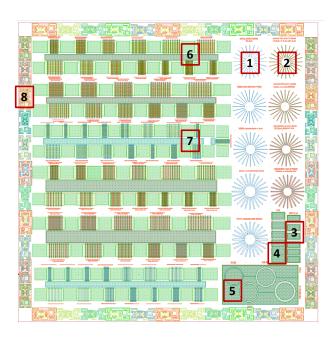

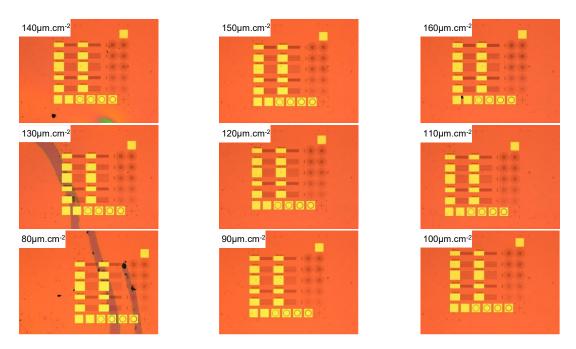

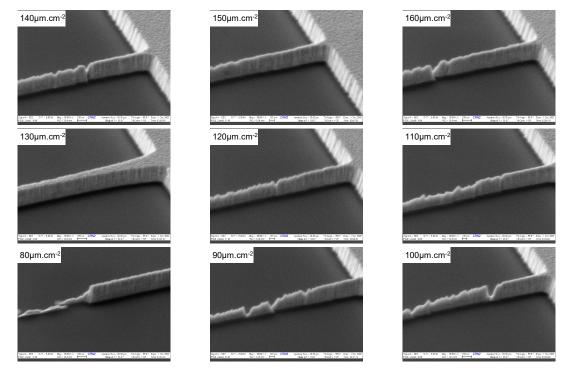

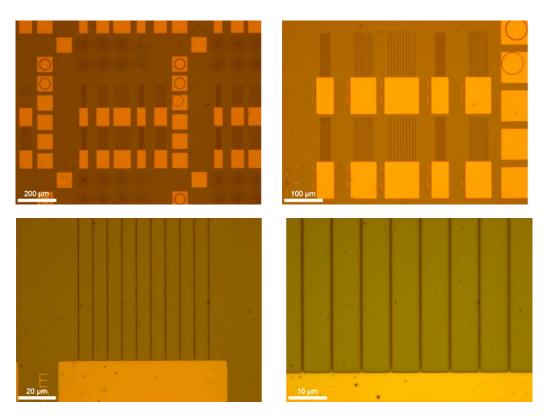

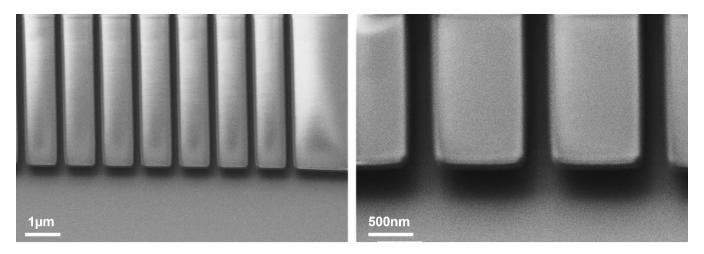

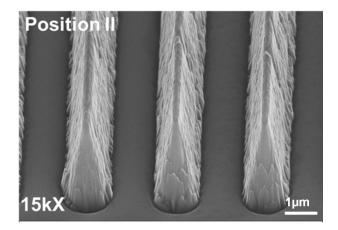

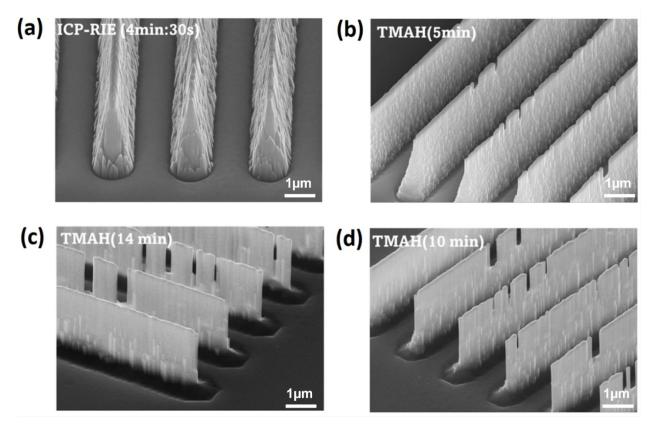

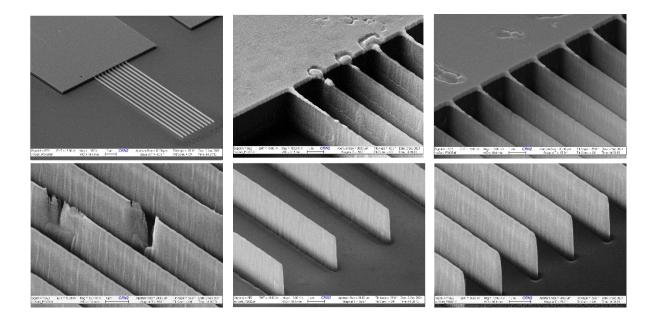

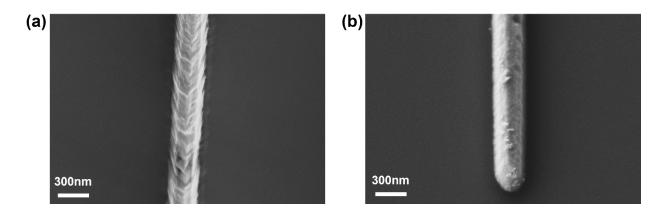

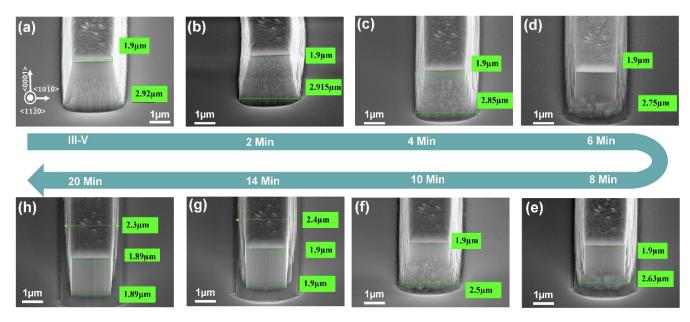

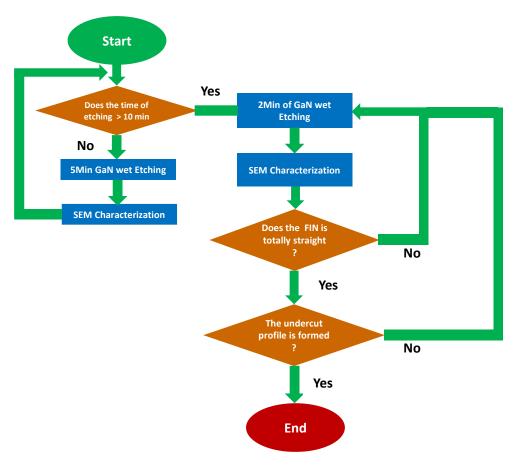

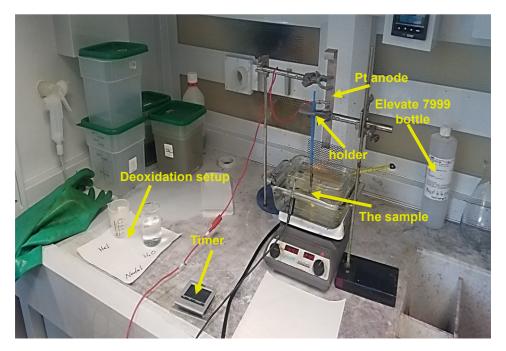

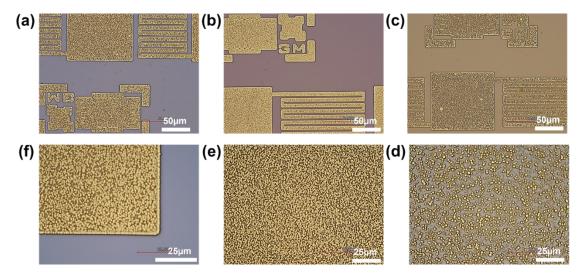

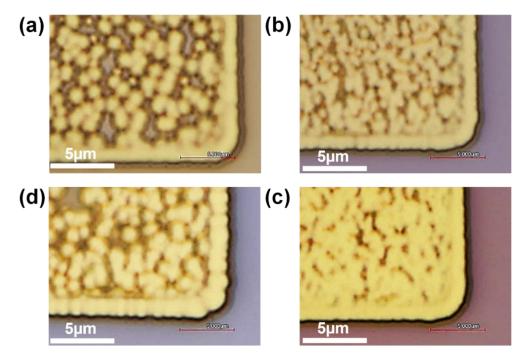

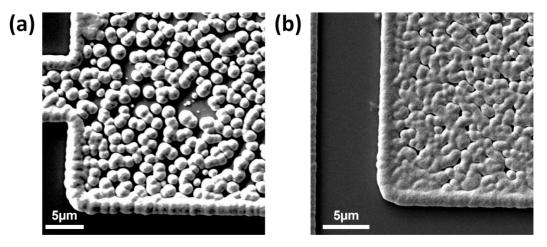

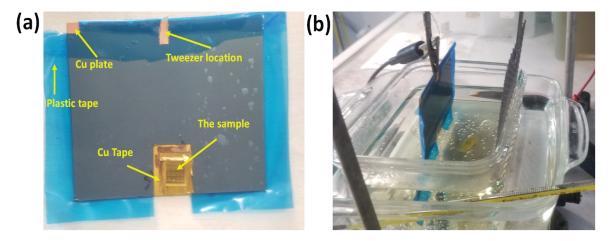

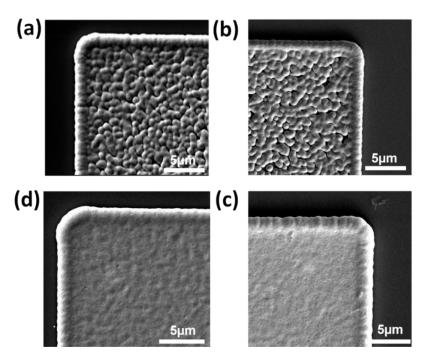

| Figure 38:The metal deposition by the lift-off process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 60                               |