# Heterostructure Tunnel Diodes for Terahertz and mm-Wave applications

A Thesis submitted to the University of Manchester for the degree of

Doctor of Philosophy

In the Faculty of Science and Engineering

### 2021

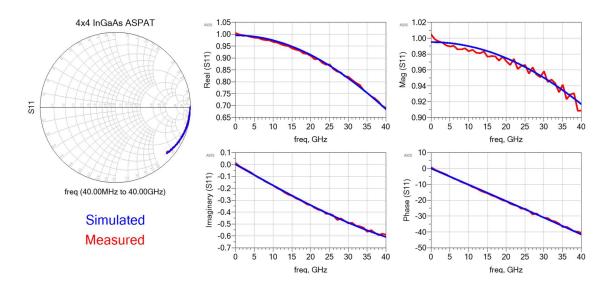

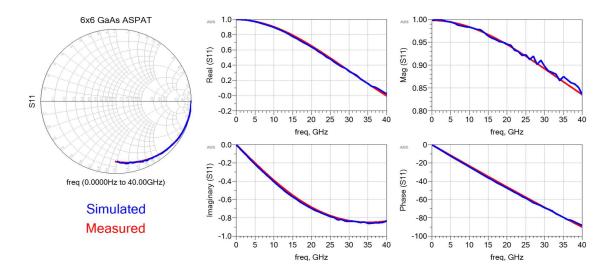

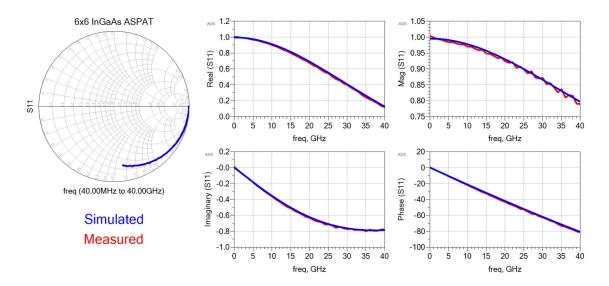

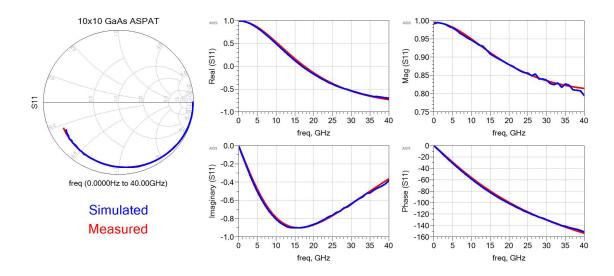

### **Andrew James Hadfield**

**Supervisor: Professor Mohamed Missous**

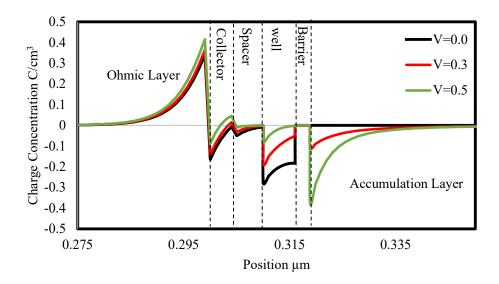

Department of Electrical and Electronic Engineering

# Contents

| ABSTRACT                                                                  |

|---------------------------------------------------------------------------|

| DECLARATION                                                               |

| COPYRIGHT STATEMENT                                                       |

| ACKNOWLEGMENTS9                                                           |

| PUBLICATIONS10                                                            |

| PRESENTATIONS11                                                           |

| AWARDS                                                                    |

| INTRODUCTION                                                              |

| 1.1. Terahertz and mm-Wave technologies12                                 |

| 1.2. Semiconductor THz devices                                            |

| 1.3. Thesis Outline                                                       |

| BACKGROUND AND THEORY OF SEMICONDUCTOR DEVICES AND<br>TUNNEL DIODES       |

| 2.1. Introduction                                                         |

| 2.2. III-V Semiconductors and Heterojunctions                             |

| 2.2.1. Bandgap and Discontinuities                                        |

| 2.2.2. Lattice Matching and Pseudomorphism                                |

| 2.3. Quantum Tunnelling Principles                                        |

| 2.3.1. Single Barrier Quantum Tunnelling                                  |

| 2.3.2. Double Barrier Resonant Tunnelling                                 |

| 2.4. Tunnel Diodes                                                        |

| 2.4.1. Esaki Diodes                                                       |

| 2.4.2. ASPAT Devices                                                      |

| 2.4.3. Resonant Tunnelling Diodes                                         |

| 2.5. Applications of Tunnel Diodes as Microwave Emitters and Detectors 44 |

| 2.5.1. Tunnel Diodes as Emitters                                          |

| 2.5.2.  | Tunnel Diodes as Detectors                    |    |

|---------|-----------------------------------------------|----|

| 2.6. St | ummary                                        |    |

|         | NDUCTOR MATERIALS SYNTHESIS AND DEVICE FABRIC |    |

| 3.1. In | ntroduction                                   |    |

| 3.2. Se | emiconductor Synthesis                        |    |

| 3.2.1.  | Molecular Beam Epitaxy                        | 54 |

| 3.2.2.  | Metal Organic Vapour Phase Epitaxy            | 55 |

| 3.3. D  | Device Fabrication                            |    |

| 3.3.1.  | Sample Cleaning                               | 56 |

| 3.3.2.  | Photolithography                              | 57 |

| 3.3.3.  | Chemical Wet etching                          | 59 |

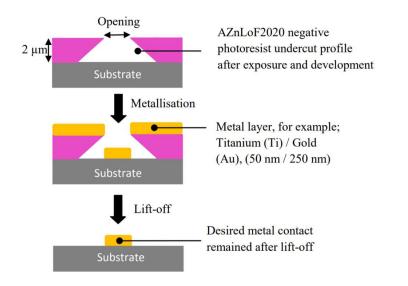

| 3.3.4.  | Metallisation and Lift-off                    | 59 |

| 3.3.5.  | Device Fabrication Process                    | 60 |

| 3.4. D  | Device Testing                                |    |

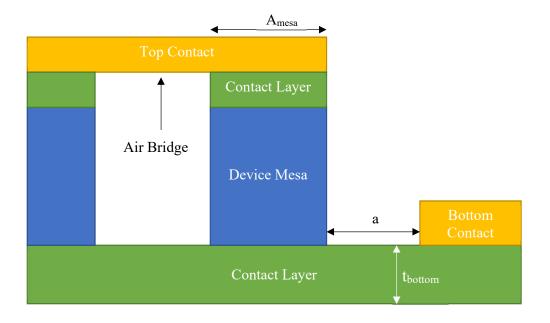

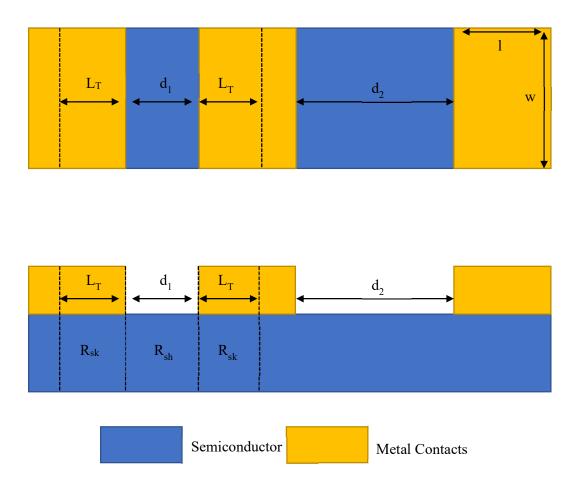

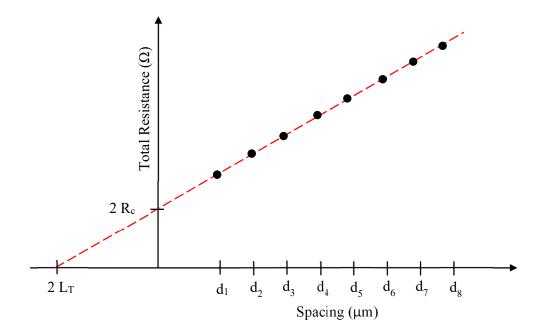

| 3.4.1.  | Series Resistance & Transmission Line Method  | 62 |

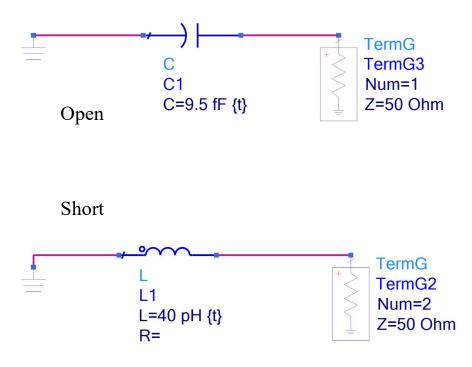

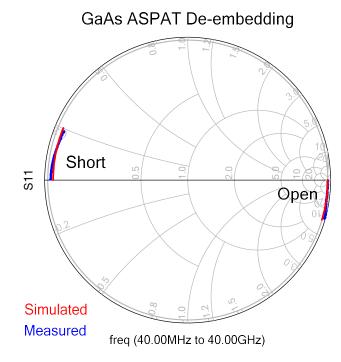

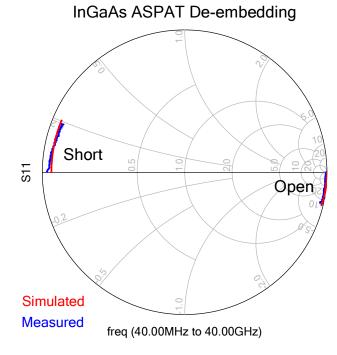

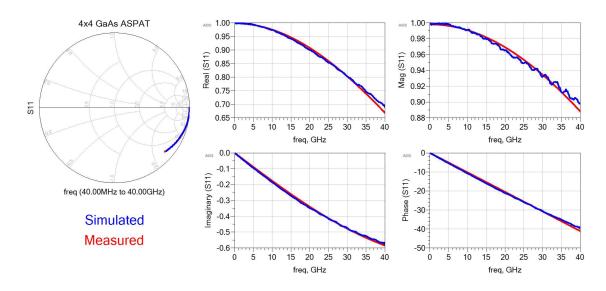

| 3.4.2.  | De-embedding procedure                        | 66 |

| 3.5. C  | Conclusion                                    | 66 |

| PHYSICA | L MODELLING                                   | 68 |

| 4. In   | ntroduction                                   | 68 |

| 4.1. Fi | undamentals of Numerical Analysis             | 68 |

| 4.1.1.  | The Schrödinger Equation                      | 69 |

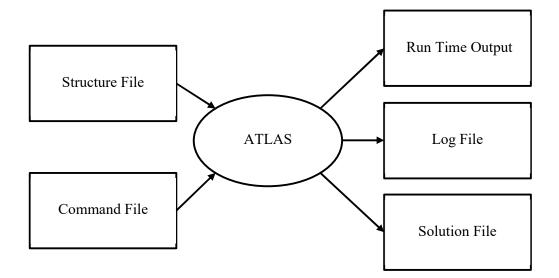

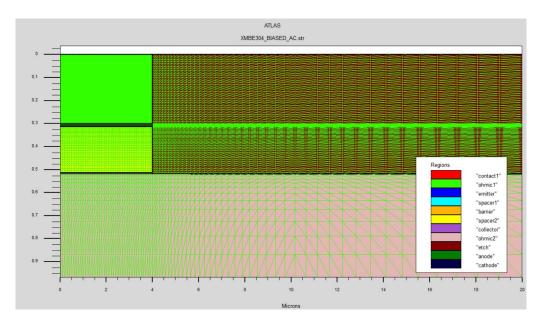

| 4.2. S  | ILVACO ATLAS                                  | 70 |

| 4.2.1.  | ATLAS Syntax                                  | 72 |

| 4.2   | .2. Structure Specification                   | 74             |

|-------|-----------------------------------------------|----------------|

| 4.2   | .3. Material Models                           | 75             |

| 4.2   | .4. Simulation Models                         | 77             |

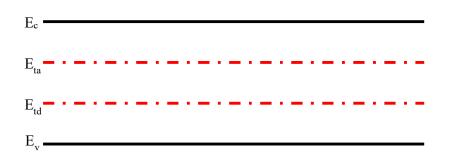

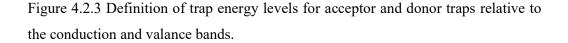

| 4.2   | .5. Traps and Defects                         | 78             |

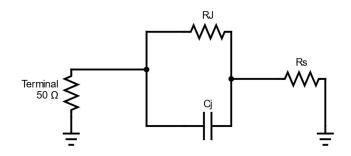

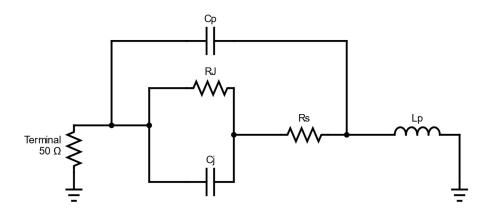

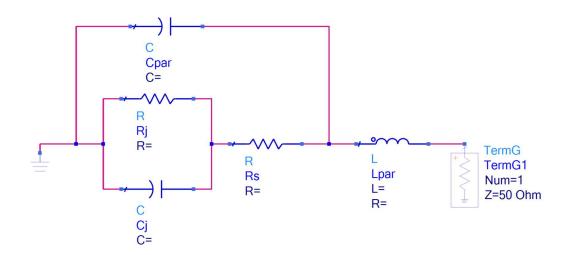

| 4.3.  | Equivalent Modelling and Parameter Extraction | 30             |

| 4.4.  | Conclusion                                    | 32             |

| ASPAT | DIODES                                        | 34             |

| 5.1.  | Introduction                                  | 34             |

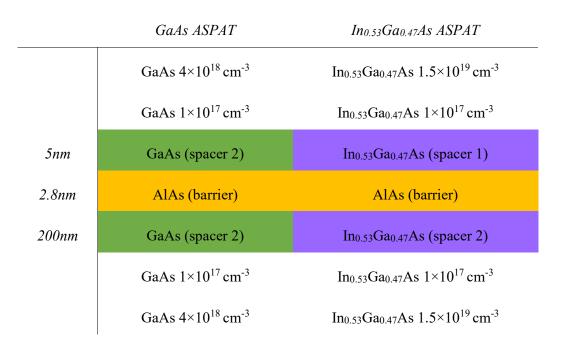

| 5.2.  | Diode Structures                              | 35             |

| 5.3.  | Diode Models                                  | 36             |

| 5.3   | .1. Model Definition                          | 36             |

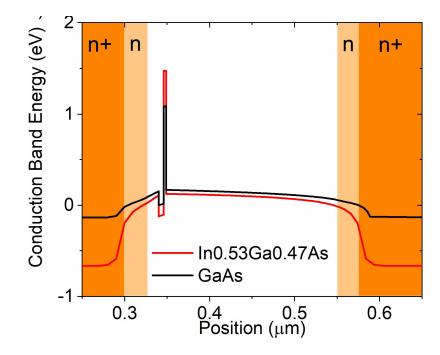

| 5.3   | .2. Material Definition                       | 37             |

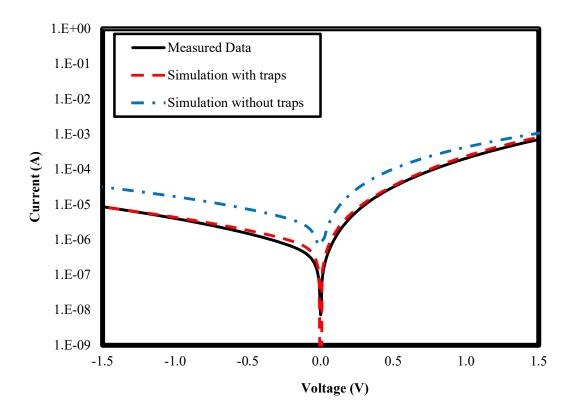

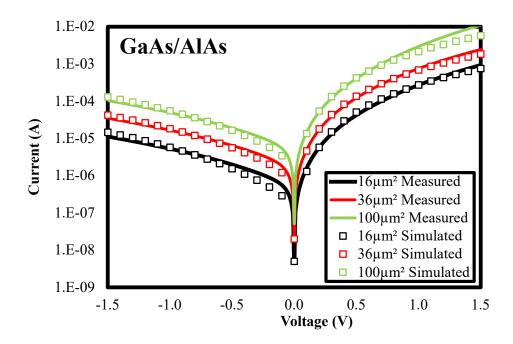

| 5.4.  | DC Characteristics                            | 39             |

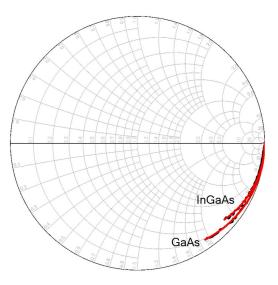

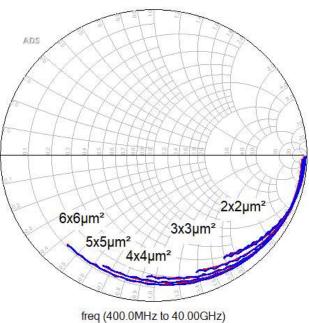

| 5.5.  | RF Characteristics                            | <del>)</del> 6 |

| 5.6.  | Conclusion10                                  | )7             |

| METAN | MORPHIC ASPAT DIODES10                        | )9             |

| 6.1.  | Introduction                                  | )9             |

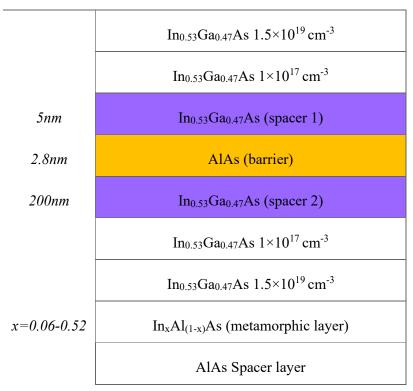

| 6.2.  | Diode Structures                              | )9             |

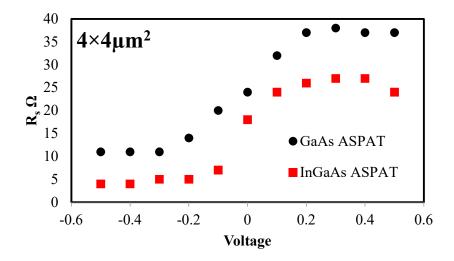

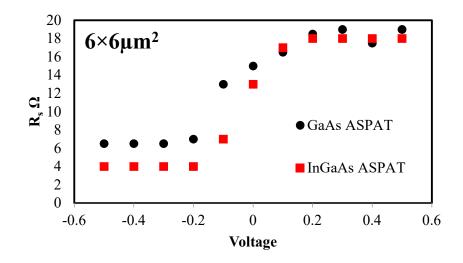

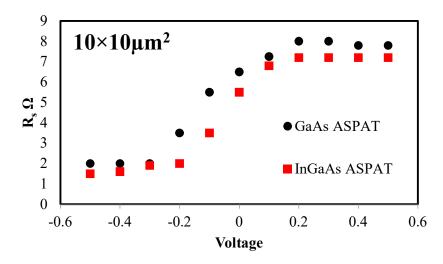

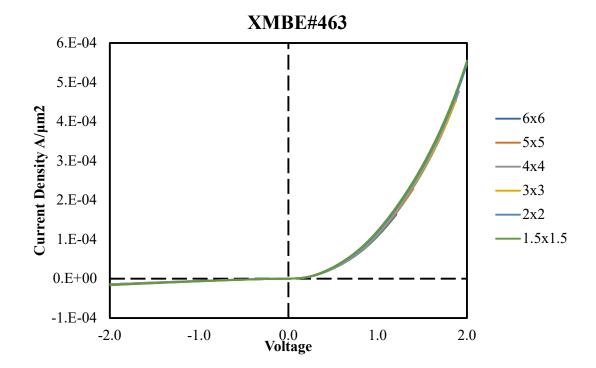

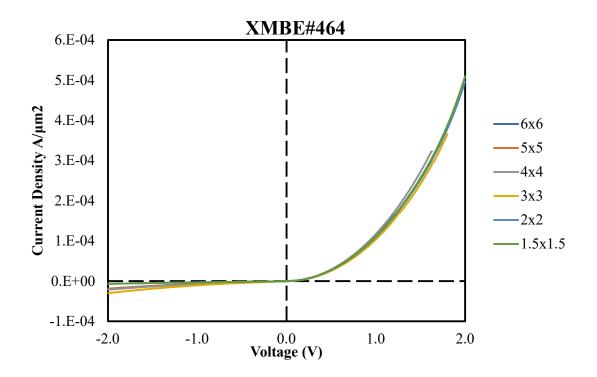

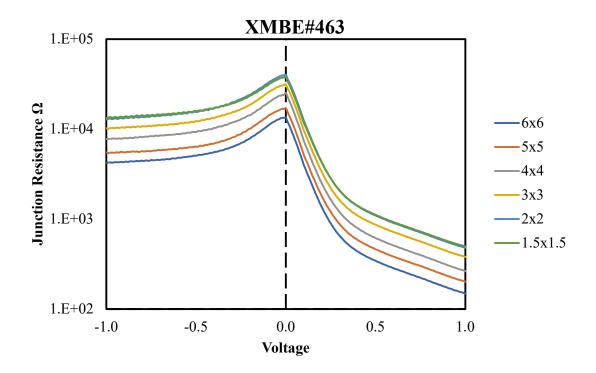

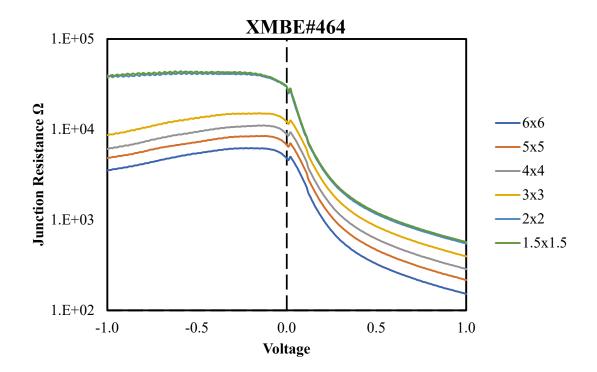

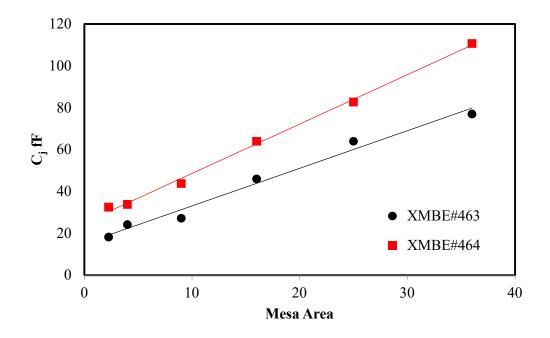

| 6.3.  | mASPAT DC Characteristics                     | 1              |

| 6.4.  | mASPAT RF Characteristics                     | 17             |

| 6.5.  | Conclusion                                    |                |

| QUAN  | ГUM WELL ASPAT DIODES12                       | 23             |

| 7.1.  | Introduction                                  | 23             |

| 7.2.  | QW-ASPAT Structures                           | 23             |

| 7.3.  | Physical Modelling12                          | 25             |

| 7.4.                             | QW-ASPAT DC Characteristics                                                | 127 |

|----------------------------------|----------------------------------------------------------------------------|-----|

| 7.5.                             | Device Optimisation                                                        | 131 |

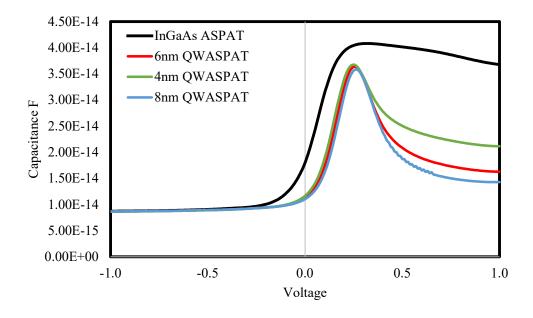

| 7.6.                             | QW-ASPAT CV Characteristics                                                | 133 |

| 7.7.                             | Conclusion                                                                 | 136 |

| Al <sub>x</sub> Ga <sub>(1</sub> | -x)As-AlAs-In <sub>0.18</sub> Ga <sub>0.82</sub> As Heterostructure Diodes |     |

| 8.1.                             | Introduction                                                               | 139 |

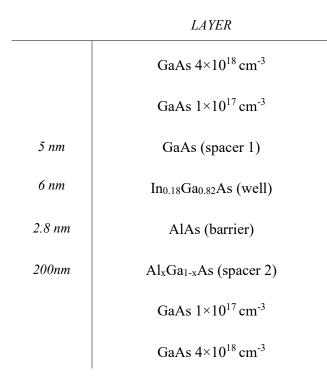

| 8.2.                             | Device Epitaxial Structures                                                | 140 |

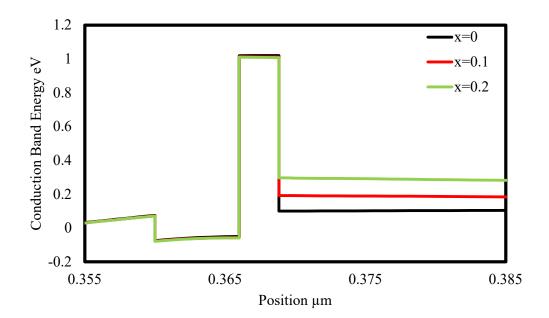

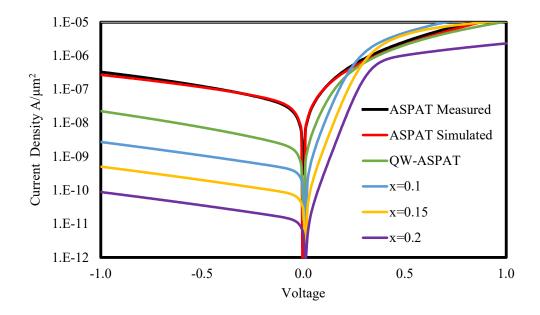

| 8.3.                             | Device Models                                                              | 141 |

| 8.4.                             | DC Characteristics                                                         | 143 |

| 8.5.                             | Device Optimization                                                        | 146 |

| 8.6.                             | Device C-V characteristics                                                 | 153 |

| 8.7.                             | Conclusion                                                                 | 156 |

| CONCI                            | LUSIONS AND FUTURE WORK                                                    | 158 |

| 9.1.                             | Research Conclusions                                                       | 158 |

| 9.2.                             | Future Work                                                                | 161 |

| APPEN                            | DICES                                                                      | 163 |

| Append                           | lix A- ATLAS Simulation Physics                                            | 163 |

| Ι                                | Poisson's Equation                                                         |     |

| II                               | Carrier Continuity Equations                                               | 164 |

| III                              | Transport Equations                                                        | 164 |

| Append                           | lix B-Example Silvaco Code for ASPAT simulation                            | 166 |

| Append                           | lix C-Example Silvaco Code for QW-ASPAT simulation                         | 169 |

| Append                           | lix D-Example Silvaco Code of AlGaAs-QW-ASPAT                              | 173 |

| REFER                            | ENCES                                                                      | 177 |

This thesis contains exactly 38,300 words

## ABSTRACT

The primary work presented in this thesis is the development and improvement of zero-bias detector diodes, for mm-Wave and THz applications. These devices were based on Asymmetric Spacer Layer Tunnel (ASPAT) diodes made on the GaAs and InP platforms.

Accurate physical models of two state of the art ASPATs were created, which showed close agreement to experimental results obtained from ASPAT devices grown by Molecular Beam Epitaxy and processed using i-line photolithography techniques. These models were then used to develop two new novel device structures, one based on InP and one based on GaAs, in which quantum wells were added to the conventional ASPAT structures.

These new QW-ASPAT devices showed curvature coefficients of  $32V^{-1}$  and  $35V^{-1}$  for In<sub>0.18</sub>Ga<sub>0.82</sub>As/AlAs/GaAs and In<sub>0.8</sub>Ga<sub>0.2</sub>As/AlAs/In<sub>0.53</sub>Ga<sub>0.47</sub>As devices respectively. This represents an increase by a factor of over 2.5 from the standard ASPAT devices. The addition of quantum wells also reduced the zero-bias capacitance of both QW-ASPAT devices. The cut-off frequencies were estimated for devices with  $4\times4\mu m^2$  mesa areas, with values of 532GHz being achieved for the In<sub>0.18</sub>Ga<sub>0.82</sub>As/AlAs/GaAs devices and over 800GHz for the In<sub>0.8</sub>Ga<sub>0.2</sub>As/AlAs/In<sub>0.53</sub>Ga<sub>0.47</sub>As device. These are both substantial improvements over the values achieved for the standard ASPAT divices are largely due to their inherently higher series resistance.

A third novel device structure based upon the  $In_{0.18}Ga_{0.82}As/AlAs/GaAs$  QW-ASPAT, was also investigated. This structure used  $Al_xGa_{1-x}As$  spacers to reduce the AlAs barrier height under forward bias. This new device structure allowed a zero bias curvature coefficient value of  $42V^{-1}$  to be achieved. This is higher than the inherent Schottky diode limit of  $40V^{-1}$  and represents the highest zero-bias curvature coefficient achieved on a GaAs platform to date. The introduction of  $Al_xGa_{1-x}As$  spacers also reduced the zero-bias capacitance of the devices when compared with the QW-ASPATs. The cut-off frequencies of  $4 \times 4\mu m^2$  mesa area devices were estimated with the highest value of 804GHz representing a 256% increase when compared with the standard GaAs ASPAT. As such the new device structure shows promise as a zerobias mm-Wave and THz detector diode, achieving higher curvature coefficients than the Schottky diode as well as increasing the cut-off frequency of the ASPAT significantly.

This thesis also investigated the growth of  $In_{0.53}Ga_{0.47}As/AlAs$  ASPATs on GaAs substrates through the use of metamorphic buffer layers. This work is intended to take advantage of the lower cost and easier processing available to GaAs substrates compared to InP, whilst maintaining the advantages of the  $In_{0.53}Ga_{0.47}As$  system. These metamorphic ASPATs (mASPAT) showed much lower detection characteristics than standard  $In_{0.53}Ga_{0.47}As/AlAs/InP$  ASPAT devices with cut off frequencies of 180GHz for devices with  $4 \times 4 \mu m^2$  mesa areas, mainly due to the large dislocation network in the metamorphic structure.

### DECLARATION

No portion of the work referred to in the thesis has been submitted in support of an application for another degree or qualification of this or any other university or other institute of learning.

### COPYRIGHT STATEMENT

i. The author of this thesis (including any appendices and/or schedules to this thesis) owns certain copyright or related rights in it (the "Copyright") and s/he has given The University of Manchester certain rights to use such Copyright, including for administrative purposes.

ii. Copies of this thesis, either in full or in extracts and whether in hard or electronic copy, may be made only in accordance with the Copyright, Designs and Patents Act 1988 (as amended) and regulations issued under it or, where appropriate, in accordance with licensing agreements which the University has from time to time. This page must form part of any such copies made.

iii. The ownership of certain Copyright, patents, designs, trademarks and other intellectual property (the "Intellectual Property") and any reproductions of copyright works in the thesis, for example graphs and tables ("Reproductions"), which may be described in this thesis, may not be owned by the author and may be owned by third parties. Such Intellectual Property and Reproductions cannot and must not be made available for use without the prior written permission of the owner(s) of the relevant Intellectual Property and/or Reproductions.

iv. Further information on the conditions under which disclosure, publication and commercialisation of this thesis, the Copyright and any Intellectual Property and/or Reproductions described in it may take place is available in the University IP Policy, in any relevant Thesis restriction declarations deposited in the University Library, The University Library's regulations and in The University's policy on Presentation of Theses.

# ACKNOWLEGMENTS

I would first like to acknowledge and thank my PhD supervisor Professor Mohamed Missous, for his advice, knowledge, time and guidance over the course of my studies and research. His supervision has been invaluable and allowed me to continuously improve my knowledge throughout my PhD.

I would also like to extend my gratitude to Dr James Sexton and Dr Abdelmajid Salhi for their expertise and willingness to help during this research. I would also like to acknowledge my PhD colleagues, Saad Muttlak and Omar Abdulwahid for their friendship and contributions.

I would like to thank my parents and all my family for their unconditional support throughout my life and for encouraging me in all my endeavours. I would not be the person I am today without them.

Finally, I would like to thank my partner Hannah for her love and support which have brought me such joy in the last few years. I cannot imagine a future without her in my life.

### PUBLICATIONS

**1. A. Hadfield**, A. Salhi, J. Sexton, and M. Missous, "Novel Barrier-Well Heterostructure Diodes for Microwave and mm-Wave Detection Applications," *Solid. State. Electron.*, p. 107963, 2021, doi: https://doi.org/10.1016/j.sse.2021.107963.

2. A. Salhi, **A. Hadfield**, S. G. Muttlak, J. Sexton, M. J. Kelly, and M. Missous, "Design and analysis of GaAs/AlAs asymmetric spacer layer tunnel diodes for highfrequency detection" Physica E: low dimensional systems and nanostructures. Volume 130, 2021, 114723, ISSN 1386-9477, https://doi.org/10.1016/j.physe.2021.114723.

3. A. Salhi, J. Sexton, S. G. Muttlak, O. Abdulwahid, A. Hadfield, and M. Missous, "InGaAs / AlAs / GaAs metamorphic asymmetric spacer layer tunnel (mASPAT) diodes for microwaves and millimeter-waves detection." J. Appl. Phys., vol. 194505, no. April, 2020, doi: 10.1063/5.0010369.

4. **A. Hadfield**, J. Sexton, A. Salhi, and M. Missous, "Experimentally Validated Physical Modelling of Asymmetric Spacer Layer Tunnel Diodes for THz Applications," in the 12th UK-Europe-China Workshop on Millimetre Waves and THz Technologies, 2019, pp. 47–49, doi: 10.1109/UCMMT47867.2019.9008347.

### PRESENTATIONS

1. **A. Hadfield**, J. Sexton, A. Salhi, and M. Missous, "Experimentally Validated Physical Modelling of Asymmetric Spacer Layer Tunnel Diodes for THz Applications," in the 12th UK-Europe-China Workshop on Millimetre Waves and THz Technologies, 2019 Poster Presentation.

2. **A. Hadfield**, M. Missous, "Experimentally Validated Physical Modelling of Asymetric Spacer Layer Tunnel Diodes" in the UK semiconductors conference, 2019 Oral Presentation.

3. **A. Hadfield**, M. Missous, "Experimentally Validated Physical Modelling of GaAs/AlAs Asymetric Spacer Layer Tunnel Diodes," in the Semiconductor and Integrated Optoelectronics Conference, 2019. Oral Presentation.

4. **A. Hadfield**, M. Missous "Simulation of Avalanche Photodiodes (APDs) Integrated with Distributed Bragg Reflectors (DBRs) for Telecom and Datacom Applications" in UK semiconductors conference, 2018 Poster Presentation.

### AWARDS

Best Student Poster Paper UCMMT 2019, London.

# CHAPTER 1 INTRODUCTION

#### 1.1. Terahertz and mm-Wave technologies

In the last two decades the number of people using the internet has exploded from 413 million in the year 2000 to 4 billion in 2019 [1]. This has been accompanied by large increase in the amount of data consumed across the world. It is estimated that the world data traffic will be 350 exabytes per month by 2022 [2]. This has been fuelled by the rise of video streaming, mobile communications and machine to machine communication (also referred to as the internet of things). As these technologies improve and as the number of internet users grow, the wireless internet infrastructure will need to be improved drastically to cope with the demand for high speed data transmission.

As such there has been a widescale push across the world to develop the 5<sup>th</sup> generation (5G) wireless and mobile communication networks. This is a paradigm shift in the way that cellular networks operate and not just an incremental improvement over the previous 4G LTE standard. It comprises of three new approaches. The first is the move to higher frequencies in the mm-Wave spectrum. The current microwave spectra used for cellular and Wi-Fi communications have become saturated and cannot keep up with the necessary improvements in data-rate that 5G will require. As such the 5G network will add new frequencies from the mm-Wave spectrum (30-300GHz), though operations starting at 6GHz will be used first.

These mm-Wave frequencies will be capable of higher data rates than the currently used bands [3], [4]. However, the reason they have not been previously used is due to their unfavourable transmission properties in air. The mm-Wave frequencies propagate in direct line of sight paths and are not reflected by the ionosphere. This limits the effective range of a mm-Wave communication system to a few kilometres[5]. They also suffer from atmospheric attenuation by oxygen and water vapour. This can be negated by operating in windows outside these absorption spikes.

Due to the short-range nature of these frequencies, the next part of the 5G approach is the extreme densification of cells. This could lead to cells with sub 1km<sup>2</sup> areas and cells with similar ranges to Wi-Fi. This allows for greater spectral efficiency and the reuse of frequencies to send signals within an area which was previously one cell. This leads to the third area of the 5G approach which is the massive multiple-input multipleoutput (MIMO) or large-scale antenna systems. The purpose of this is to allow the transmission and reception of multiple data signals over the same radio channel. This would allow for the increase in the network's capacity without the need for additional frequency bands. This is achieved by using beamforming techniques with many antennas. The move to the higher frequency mm-Wave bands is advantageous in this regard as beamforming is easier at higher frequencies and the shorter wavelength reduces the size of the antennas needed allowing for more compact systems.

Whilst 5G technology deployment is currently underway, with various enterprises demonstrating their 5G systems, there is already talk of what the next generation beyond 5G would entail [6]. As 5G increased the frequency bands used to the mm-Wave spectrum the next step would be to increase data carrier frequencies even further into sub mm-Wave frequencies in the THz regime (0.3THz - 3THz) [7].

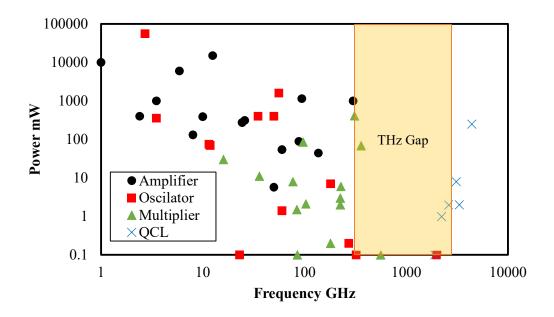

This regime is sometimes termed the "THz gap" as it falls between mature microwave technologies in the highest frequencies of the radio spectrum and the well-developed optical engineering of infrared detectors in their lowest frequencies. THz and mm-Wave radiation have may potential applications beyond communications including non-destructive testing[8], security imaging[9], biomedical applications[10], [11] and automotive radar[12]. Figure 1.1.1 shows the output power plotted against frequency of various THz and mm-Wave radiation emitters. As can be seen from the figure there is a significant gap in the THz region from 0.3THz - 3THz.

Figure 1.1.1 Output power and frequencies of different THz technologies; Amplifiers[13]–[28], Oscillators[29]–[41], Mixers [42]–[55] and Quantum Cascade Lasers[56]–[61].

Due to mm-Wave and THz radiations ability to penetrate clothing and their nonionizing nature, they are ideal for use in airport security full body scanners and other security related fields. Imaging systems fall into two types of categories passive and active. Active systems produce a THz or mm-Wave signal and then form an image from the reflected radiative signal. Recently, Rohde & Schwarz introduced an active mm-Wave based scanner which operates at 70-80GHz to produce high resolution images with no moving parts. The system outputs mm-wave radiation at a power of 1mW[62].

Passive systems do not require a radiation source and measure the thermally emitted THz radiation of the imaged objects. This simplifies the imaging system and reduces cost however it requires a detector with low noise and a high sensitivity. The Fujitsu company has developed a passive image scanning system based around a frequency of 94GHz [63]. The sensor includes a high electron mobility transistor (HEMT), a low noise amplifier (LNA) and a zero-bias Schottky diode.

Another promising commercial application for THz and mm-Wave radiation is in the field of automotive radar [12], [64], [65]. As autonomous vehicles become more prevalent the need for the vehicle to have an accurate picture of the surrounding environment is paramount to ensure the safety of passengers and pedestrians. As such automotive radar systems have been developed to determine the distance, angle, velocity and position of nearby objects. This is achieved through the use of radio signals in the band 76-80GHz [66]. These systems when combined with active safety measures reduce the probability of accidents by being less sensitive to environmental conditions such as fog and darkness.

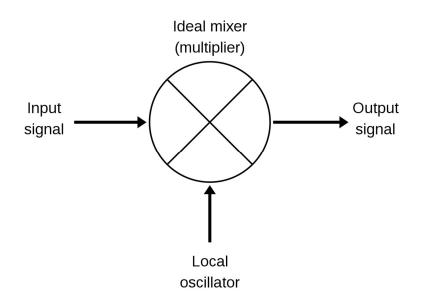

As such it is imperative that the THz gap is filled and that THz technologies are developed from both ends of the spectrum. These THz technologies fall into three categories sources, mixers and detectors. The purpose of sources is to generate the THz carrier frequencies in the case of communications and to provide the illumination in the case of imaging systems and radar systems. This has been one of the main blockages in the filling of the THz gap as the generation of high power THz frequencies requires large bulky systems such as gyrotrons [67] or can only be generated at ultra-low powers in the case of solid-state systems [41].

THz detectors have been created using both heterodyne and direct detection techniques. Direct detection directly demodulates the incoming signal without altering the frequency. By contrast, heterodyne detection mixes the signal with a local oscillator to down-convert the signal to a lower frequency. The signal is then demodulated from this lower intermediate frequency. This requires the use of a mixer to mix the local oscillator frequencies and the received signal. The detection process uses non-linear semiconductor devices for both the mixing and direct detection processes. It is common to use Schottky barrier diodes and complementary metal oxide semiconductors (CMOS) for these purposes, however tunnel diodes have shown recent development for this role and show promise in this area for a number of reasons as will be outlined later.

#### 1.2. Semiconductor THz devices

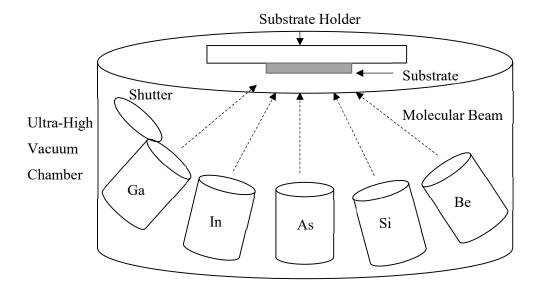

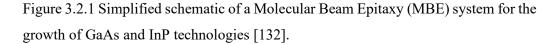

The development of the Molecular Beam Epitaxy (MBE) and Metal Organic Chemical Vapour Deposition (MOCVD) techniques have allowed for the development of high-

quality semiconductor heterojunction devices to bridge the THz gap. These techniques allow for extremely well controlled semiconductor growth down to the monolayer level. This has led to the development of a large number of devices which could be used as THz emitter sources or THz and mm-Wave receivers.

MBE has been used to grow Gunn diodes and Resonant Tunnelling Diodes (RTD), which have been used to create THz and mm-Wave oscillators. Gunn diode oscillators are usually based on the GaAs platform and have achieved oscillations at 125GHz with output powers of 32mW[68]. Whilst Gunn diodes based on the InP platform have reached oscillation frequencies of over 300GHz these have been achieved with a low output power of 28µW[69].

RTDs are the current devices with the highest oscillation frequency demonstrated in the literature with the Asada group demonstrating an oscillator at 1.98THz based on the InP platform [41]. This group has also demonstrated wireless transmission rates of 34Gbit/s at a frequency of 500GHz using RTDs as the emitter [70]. Our group at the University of Manchester has recently developed RTDs capable of oscillation up to 2.7THz [33]. RTDs have also been developed on other platforms such as GaN [71] and show potential to be the leading device for compact, room temperature THz emitters.

THz detectors and mixers have been achieved using both two terminal [72]–[76]and three terminal devices[77]–[79]. Three terminal devices such as HBT and HEMT transistors require external biasing and must be fabricated at the nanoscale if they are to achieve mm-Wave operating frequencies. This increases the cost and complexity of device fabrication and is undesirable. As a result, a large number of two terminal devices have been developed using MBE and MOCVD to be used as mixers and detectors.

The current standard device is the Schottky diode created with a metal-semiconductor junction. This diode controls the flow of current with the barrier created at the semiconductor-metal interface. The main transport mechanism of the Schottky diode is thermionic emission and as such it is more susceptible to temperature fluctuations than a device which operates through quantum tunnelling. Similarly, the Schottky diodes curvature coefficient, which is directly proportional to the voltage sensitivity, is inherently limited to  $40V^{-1}$  [80].

Due to these limitations several alternative devices have been attempted. These include the Sb-Heterojunction backward diode [75], [81]–[85] which boasts curvature coefficients of  $47V^{-1}$  at 94GHz making it ideal as a mm-Wave detector. However, the backward diode is not yet commercially available and utilises a complex epi-layer structure. The back diode also exhibits a junction capacitance of  $15fF\mu m^{-2}$  which requires sub-micron fabrication to achieve THz and mm-Wave operation.

Another competitor to the Schottky diode is the <u>Asymmetric Spacer Layer Tunnel</u> (ASPAT) diode which was developed by R.T. Syme and M. J. Kelly [86] and optimized by M. Missous at the University of Manchester [87]–[89]. The ASPAT shows a greater temperature independence than the Schottky diode and a maximum curvature coefficient at zero-bias. However, it does not match the Schottky diodes curvature coefficient. The main aim of this work is to develop the ASPAT diode so that it can surpass the Schottky diode as a detector diode for mm-Wave and THz applications. To do this the devices curvature coefficient will need to be increased above 40V<sup>-1</sup>. Other improvements to the ASPATs characteristics such as reducing the junction capacitance and reducing cost will also be explored.

#### 1.3. Thesis Outline

This work focusses on the improvement of the ASPAT diode as a zero-bias detector diode. This will be done using a combination of experimental work, in which devices will be grown in house at the University of Manchester using molecular beam epitaxy, and simulation work, in which TCAD tools such as Silvaco ATLAS and circuit simulators such as Agilent Advanced Design Systems will be used to explore new device concepts.

This chapter has introduced the demand for mm-Wave and THz technologies and briefly discussed some of the current semiconductor devices used in this area. It will also briefly outline the structure and content of the remaining thesis chapters.

Chapter 2 will focus on the background and theory of III-V semiconductors and tunnel devices. It will discuss the properties of semiconductor materials and how

semiconductor heterojunctions are formed. It will then go on to provide a brief overview of the physics of quantum and resonant tunnelling before moving on to look at specific semiconductor tunnel diodes. These diodes will include the Esaki diode, the ASPAT and the RTD. The characteristics of each of these diodes will be discussed before the chapter moves on to the applications of tunnel diodes. The use of RTD and Esaki diodes as part of THz and mm-Wave oscillator sources will be discussed and the use of ASPAT devices as direct detectors will also be covered. Finally, the chapter will discuss the use of non-linear components such as tunnel diodes as mixers for heterodyne detection systems.

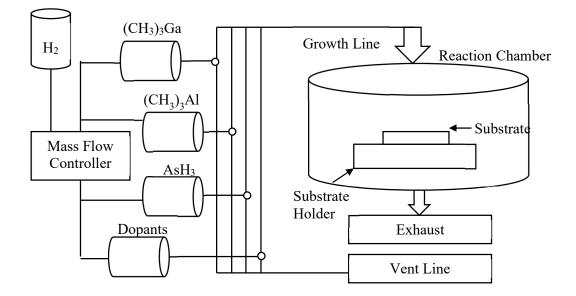

Chapter 3 will cover the synthesis of semiconductor wafers and the fabrication of devices. This chapter will contain an overview of MBE and MOCVD growth techniques. Following this device fabrication techniques will be discussed. This will include photolithography, wet and dry etching techniques and metal deposition. The final part of this chapter will focus on the measurement and characterisation of devices including the components that make up the series resistance, the parasitic capacitance and inductance.

Chapter 4 will cover the modelling and simulation of devices. This will mainly be focussed on the implementation of physical models in Silvaco ATLAS TCAD software. These physical models will be used throughout this work to explore new device concepts and simulate their characteristics. The chapter will discuss the atlas file structure, syntax and methods of specifying a structure before moving on to the material and transport simulation models which will be used in this work. This chapter will also discuss the implementation of traps and defects in the model. After this the chapter will discuss the equivalent circuit models created in Agilent Advanced Design Systems (ADS) to model the devices RF parameters.

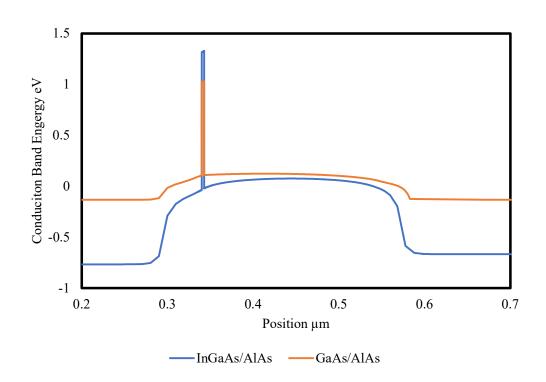

Chapter 5 will characterise the DC and RF characteristics of two well-understood ASPAT diodes grown via MBE at the University of Manchester. One GaAs/AlAs structure grown on a GaAs substrate and an In<sub>0.53</sub>Ga<sub>0.47</sub>As/AlAs ASPAT grown on an InP substrate. From this characterisation accurate physical models will be created for use in the rest of this work. These ASPATs will form the benchmark of performance against which new structures, developed in chapters 7 and 8, will be measured against.

The ASPATs in this chapter are designed for applications as part of a detection circuit for microwaves, mm-Waves and the low end of the THz spectrum.

Chapter 6 will cover the growth of In<sub>0.53</sub>Ga<sub>0.47</sub>As/AlAs ASPATs on GaAs substrates through the use of metamorphic layers. The purpose of this would be to maintain the superior qualities of In<sub>0.53</sub>Ga<sub>0.47</sub>As/AlAs ASPATS whilst removing the need for costly and difficult to work with InP substrates. The effect of the growth temperature of the metamorphic layers on the devices DC and RF characteristics will be investigated and discussed. The overall performance of the new metamorphic ASPAT (mASPAT) devices will be compared to conventionally grown In<sub>0.53</sub>Ga<sub>0.47</sub>As/AlAs ASPATs on InP substrates with the same active device structure. The physical models developed in chapter 5 will also be used as part of the analysis of the new mASPAT structures.

In chapter 7 two new diode structures with quantum wells added to the short spacer side of the device will be explored as a method of increasing the devices curvature coefficient. This will be done for both the GaAs ASPAT and the In<sub>0.53</sub>Ga<sub>0.47</sub>As ASPAT. These new quantum-well ASPAT (QW-ASPAT) structures will be explored using the physical models developed in chapter 5. The new structures DC characteristics will be simulated, and the DC parameters extracted. Once these have been compared with the standard reference ASPATs the effects of varying the AlAs barrier thickness and quantum well thickness on the devices DC characteristics will be explored to optimize the device structure. The effect of adding quantum wells to the devices on the junction capacitance and cut-off frequency will also be explored using AC simulations of the physical models.

Chapter 8 will focus on the use of  $Al_xGa_{1-x}As$  in the QW-ASPAT to reduce the barrier height on the long spacer side of the devices. These new structures will be investigated using Silvaco ATLAS by modifying the QW-ASPAT models used in chapter 7. DC simulations of the new structures will be performed, and the devices junction resistance and curvature coefficients will be extracted. The new devices parameters such as barrier thickness, quantum well thickness and  $Al_xGa_{1-x}As$  composition will be explored in detail via simulation to determine their effect on the device performance. The emitter and collector layer doping and thickness will also be explored in this chapter as a method to improve the device performance. The devices C-V characteristics will also be simulated to determine the devices suitability for high frequency detection. The cut-off frequency of the new devices will be estimated and compared with the QW-ASPAT devices from chapter 7 and the standard ASPAT devices from chapter 5.

Chapter 9 will recap the research conclusions of this work as well as providing recommendations for future work in this field.

# CHAPTER 2

## BACKGROUND AND THEORY OF SEMICONDUCTOR DEVICES AND TUNNEL DIODES

#### 2.1.Introduction

This chapter will focus on the background and theory of semiconductor devices, with particular emphasis on tunnel diodes. It will initially start with explanations of the electronic band gap seen in semiconductor crystals and the formation of semiconductor homojunctions and heterojunctions. Following this, the impact of the lattice constant on constraining the material systems used will be discussed including how metamorphic and pseudomorphic layers can be used to circumvent this.

The principles of quantum tunnelling and resonant tunnelling are included in this chapter and semiconductor devices which utilise these mechanisms will be discussed. These devices include the Esaki diode, the <u>A</u>symmetric <u>Spacer Layer T</u>unnel (ASPAT) diode and the Resonant Tunnelling Diode (RTD). Their principles of operation will be explored, and their relevant characteristics discussed, such as negative differential resistance (NDR). To finish this section, the applications of tunnel diodes as microwave emitters and detectors will be discussed. This will include discussion on their use in higher frequency regimes such as mm-Wave and the THz regimes and the implications for higher frequency data communications technologies such as 5G.

#### 2.2. III-V Semiconductors and Heterojunctions

#### 2.2.1. Bandgap and Discontinuities

Semiconductors are materials which fall between traditional insulators and conductors and can therefore be influenced to act as both insulators or conductors in different circumstances. This allows them to be used to create active devices whose electrical properties can change during operation such as diodes, and transistors. Most semiconductor devices in the world today are made from silicon; however, there are applications in which using silicon is not preferable. For example, the III-V compound semiconductors are frequently used in optoelectronic and photonic applications due to their direct bandgap, a property that silicon does not possess. These III-V compound semiconductors are crystalline compounds of group III and group V elements such as Gallium Arsenide, Aluminium Arsenide and Indium Phosphide[90], [91].

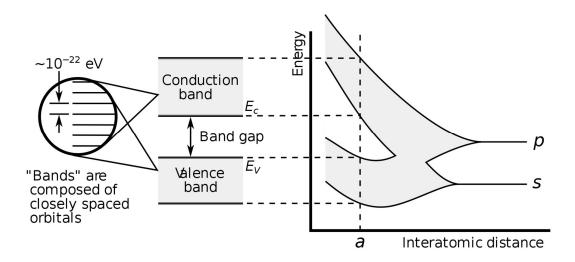

To understand semiconductors, we must consider the structure of crystalline solids. In a single atom the electrons are bound in quantum states with specific energies. The energy for two identical states in two identical atoms will be identical in normal circumstances. In the case of crystal structures, as the atoms come closer together the electronic states of the outermost electrons, and their corresponding wave functions, will begin to overlap. Since two fermions cannot have the same quantum numbers according to the Pauli Exclusion Principle[92], and electrons are fermions, the energy levels of the electrons are shifted to create a series of close energy levels with a difference of the order  $10^{-22}$  eV[93]. As this is a very small difference, it is easier to consider these close energy levels as energy bands. There are usually considered to be 2 bands in most solids, the valence band and the conduction band. The valence band is the band of the outermost electrons can freely move. A diagram of this is shown in Figure 2.2.1.

The bandgap is a left-over area between the bands in which no energy states form. The size of the bandgap is very important in determining the electrical, optical and thermal properties of crystalline solids. Materials with high bandgaps are generally insulators. Conductors often have a small bandgap or no bandgap at all as the valence and conduction bands overlap.

A semiconductor is a material in which the band gap is capable of being overcome with a small amount of help in the form of thermal energy or small applied electric field.

Figure 2.2.1 Diagram showing the formation of conduction and valence energy bands when interatomic distance is reduced. [90]

The position of the conduction and valence bands can be adjusted by the addition of impurities to the semiconductor. This process is called doping. In the case of silicon, a group IV element, the dopants can be group III acceptors and group V donors. The group III elements will have an additional space or "hole" in which an electron can be accepted, these holes act as positive charge carriers and hence semiconductors doped with acceptors are called p-type. Similarly, the group V dopants will have an additional free electron which can act as a negatively charged carrier and semiconductors doped with donors are called n-type. A junction is formed when n-type and p-type semiconductors are brought together. A diode for example is made of a p-type and n-type silicon junction. These types of junctions are called homo-junctions.

In an intrinsic (i.e. undoped) semiconductor, the Fermi level lies in the middle of the band gap at room temperature. The Fermi level represents the energy at which the probability of an energy state being filled is <sup>1</sup>/<sub>2</sub> according to the Fermi-Dirac distribution. When a semiconductor is doped, the position of the conduction and valance bands move in relation to the Fermi level. For an n-type semiconductor, the Fermi level is closer to the conduction band and for a p-type semiconductor the Fermi level is closer to the valence band [94].

In equilibrium the Fermi level is constant throughout the device and as such when a p-n junction is formed there is a significant difference in the conduction and valance

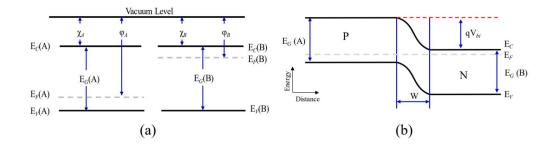

bands positions, relative to the Fermi level, on either side of the junction. The bands then bend smoothly at the junction so that they can meet. This is shown in Figure 2.2.1 below.

Figure 2.2.2 Homojunction between two semiconductors A and B, (a) in isolation (b) in contact. Notes:  $E_G$  = Bandgap,  $E_C$  = Conduction Band,  $E_V$  = Valence Band,  $V_{bi}$  = Built-in Potential,  $\chi$  = Electron Affinity,  $\varphi$  =Work function.

The properties of the junctions are entirely dependent on the doping concentrations which can be varied to produce a wide range of devices. As, such homojunctions like these are used in silicon diodes, solar cells [95], light emitting diodes (LEDs)[96], [97] as well as transistors such as Bipolar Junction Transistors (BJTs)[94], [98], [99].

Where homo-junctions are created by two different doping levels of the same semiconductor, a heterojunction is created at the interface of two different semiconductors with different band gaps, irrespective of doping polarities in the two sides. Unlike homo-junctions, heterojunctions have sharp discontinuities in the bands at the junction[100]. These sharp discontinuities can be used to create barriers and wells for charge carriers and allow for different physics behaviours to be exploited such as quantum tunnelling [86]–[88], [101]–[103] and resonant tunnelling [33], [41], [104]–[106].

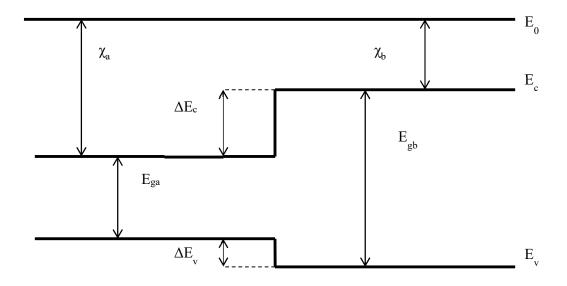

The behaviour of any device that utilises heterojunctions will be heavily dependent on the nature of the band gap discontinuities. It is vital that they are understood properly. The simplest method of calculating band gap discontinuities is Anderson's rule, also called the electron affinity rule, in which it is assumed that the vacuum level of the electrons on either side of the junction are aligned[107]. The electron affinity, defined as the difference between the bottom of the conduction band and the vacuum level, and the bandgaps of the two semiconductors are then used to determine the band gap discontinuities. This is shown in Figure 2.2.3.

Figure 2.2.3 Diagram of Conduction and valence band offsets for two materials A and B with affinities  $\chi_{a}$ ,  $\chi_{b}$ , and bandgaps  $E_{ga}$  and  $E_{gb}$ .

If we assume that two semiconductors, A and B with bandgaps  $E_{gq}$  and  $E_{gb}$  and affinities  $\chi_{a}$  and  $\chi_{b}$  the conduction band discontinuity  $\Delta E_{c}$  will be given by

$$\Delta E_c = (\chi_a - \chi_b)$$

2.2.1

and the valence band discontinuity will be given by

$$\Delta E_{\nu} = (\chi_a + E_{ga}) - (\chi_b + E_{gb})$$

2.2.2

From here the Femi level of both semiconductors will be calculated and band bending effects will be considered to produce the full band diagram.

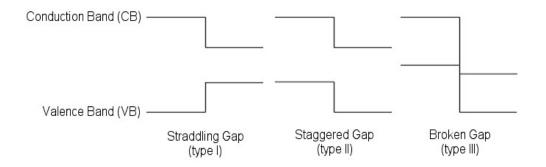

There are three different types of heterojunctions[100], the most common being straddle gap or type I heterojunctions. In these heterojunctions, the conduction and

valence bands of the smaller bandgap semiconductor lie inside the bandgap of the larger bandgap semiconductor. Type II heterojunctions, also called staggered gap heterojunctions, see both the conduction and valence bands of one semiconductor lying below their corresponding bands in the second semiconductor. The final type of heterojunction is the broken gap, or type III heterojunction, in which the conduction band of one of the semiconductors is below the valence band of another. These heterojunction types are all shown below in Figure 2.2.4.

Figure 2.2.4 Diagram of Type I, Type II and Type III heterojunctions conduction and valence band alignments.

The formation of heterojunctions is usually performed using a range of epitaxial techniques, in which the semiconductor crystal is formed one atomic layer at a time. Examples of these techniques include Molecular Beam Epitaxy (MBE)[108] and Metalorganic Vapour-Phase Epitaxy (MOVPE)[109]. These methods allow for very precise control over the growth of the crystal in the vertical growth direction and allow structures to be formed that are only a few monolayers thick.

#### 2.2.2. Lattice Matching and Pseudomorphism

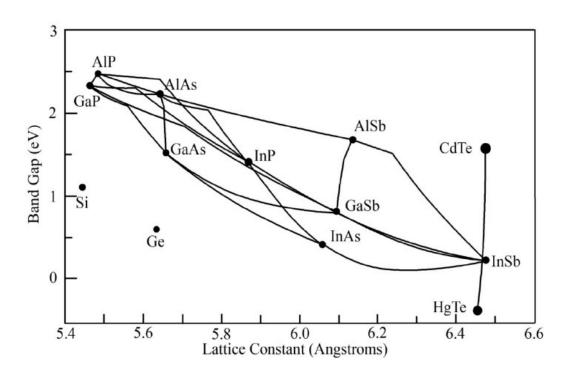

Bandgap is not the only parameter to be considered when growing heterojunction structures, the lattice constant is also of vital importance. The quality of the interface between two semiconductors is determined, in a large part, by the number of dislocations the interface suffers from. To reduce these, it is imperative that the lattice constant of the two semiconductors is near identical or there will be dislocations. This condition is called lattice matching. For electronic devices, it is common to work only with semiconductors that are lattice matched to the substrate upon which the structure is grown. This is not necessarily true for photonic and optoelectronic devices, in which the advantages of modifying the bandgap outweigh the disadvantages of an increased number of dislocations. Figure 2.2.5 depicts the lattice constants and bandgaps of various III-V semiconductors. One clear example of closely matched lattice constants is the GaAs and AlAs pair. This combination has been used to produce semiconductor devices for some time. Another less obvious combination is the ternary semiconductor alloys of InGaAs and InAlAs, where the proportion of indium is varied to match the lattice constants. It is common to lattice match these two semiconductors to the lattice constant of InP which can be used as a substrate for the growth of the epitaxial layers forming the structures. The lattice constants and bandgaps of common III-V compound semiconductors are given below in Table 2.2.1.

Figure 2.2.5: Lattice constant versus bandgap for III-V and group IVsemiconductors. Image from [110]

Table 2.2.1: Table of lattice constants and bandgap energies for III-V semiconductors

[91], [111]–[113]

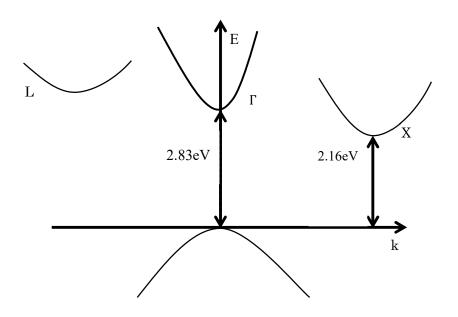

| Alloy | Lattice constant, a <sub>0</sub> (Å) | Band gap, Eg (eV) |

|-------|--------------------------------------|-------------------|

| GaAs  | 5.653                                | 1.42              |

| AlAs  | 5.661                                | 2.16              |

| InAs  | 6.058                                | 0.37              |

| InP                    | 5.869 | 1.35 |

|------------------------|-------|------|

| $Al_{0.52}Ga_{0.48}As$ | 5.657 | 2.07 |

| $In_{0.53}Ga_{0.47}As$ | 5.868 | 0.76 |

| $In_{0.52}Al_{0.48}As$ | 5.852 | 1.48 |

Whilst choosing a lattice matched material system is preferable, it is sometimes necessary or even advantageous to grow structures with a lattice mismatch. One method of doing this is lattice grading in which the lattice alloy composition is slowly changed, from one that lattice matches the substrate to a composition with the desired lattice constant.

This technique is used in metamorphic high electron mobility transistors (mHEMTs) [114]–[116] to change the lattice constant of the structure, from that of the GaAs substrate at the bottom to the value needed by the active device on the top. This allows for the use of larger, cheaper GaAs substrates instead of more expensive and difficult to work with InP substrates.

Another example of a lattice mismatched device is the pseudomorphic high electron mobility transistor (pHEMT)[117]–[120]. Unlike the mHEMT, the pHEMT does not gradually change the lattice constant to the desired value. Instead it has a thin layer of the lattice mismatched alloy. This layer undergoes strain and its thickness must be kept below a critical thickness or dislocations will form. These dislocations will form localised states which trap electrons and holes degrading the electrical properties of the device.

The strain,  $\varepsilon$ , of a system with two lattice mismatched semiconductors can be given by

$$\varepsilon = \frac{a_0 - a_1}{a_0}$$

2.2.3

Where  $a_0$  and  $a_1$  are the lattice constants of the semiconductors. From, this the critical thickness,  $h_c$ , of the pseudomorphic layer can be determined simplistically by Equation 2.2.4. A more accurate determination of the critical thickness must also consider growth conditions, surface conditions and dislocation kinetics. However,

Equation 2.2.4. can be used for a simple two-layer system with a given lattice mismatch.

$$h_c = \frac{a_0}{2\varepsilon}$$

The use of pseudomorphic layers allows for heterojunctions to be grown with larger bandgap discontinuities than would be achievable using only lattice matched systems.

#### 2.3. Quantum Tunnelling Principles

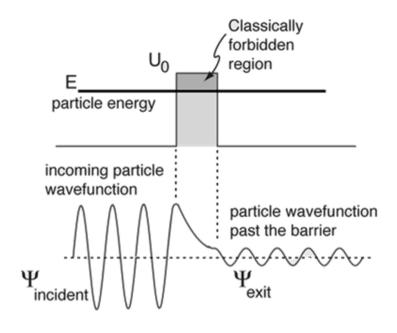

#### 2.3.1. Single Barrier Quantum Tunnelling

In classical physics for a particle to pass a potential barrier, the particle must have an energy higher than the value of the barrier. It must in essence "get over" the barrier. This fundamental assumption is untrue for quantum mechanics. As particles exhibit wave like properties and are described by wave functions, there becomes a small but finite probability that a particle will simply pass through a finite potential barrier. This phenomenon is known as quantum tunnelling. For most barrier structures this is usually a small enough number to have little or no difference from the expected results of classical physics. It is only when the barrier becomes very thin that tunnelling occurs in any significant amount.

To explain this phenomenon, we must first look at the wave function of particles such as electrons travelling through semiconductor crystals. This wave function, often denoted by  $\Psi$ , contains all the relevant information of a specific particle. The evolution of the particle and its wave function is governed by the time independent Schrodinger Equation. The one-dimensional time-independent Schrodinger Equation is shown below in Equation 2.3.1

$$-\frac{\hbar^2}{2m^*}\frac{d^2\psi}{dx^2} + V(x)\psi = E\psi$$

2.3.1

2.2.4

Where x is the position of the particle,  $m^*$  is the effective mass of the particle, E is the energy of the particle and  $\hbar$  is the reduced Planck's constant. After some rearranging this can then become

$$\frac{d^2\psi}{dx^2} + \frac{2m^*}{\hbar} [V(x) - E]\psi = 0$$

2.3.2

The solution to this equation will then be in the form

$$\psi = Ae^{ikx}$$

2.3.3

where k is yet to be defined. If we imagine a situation in which a particle is incident on a square potential barrier of height  $U_0$  and width W, as shown in Figure 2.3.1, then the wave functions on both the left and the right hand sides of the barrier will be plane waves in which k is the wavenumber and can be given by

$$k = \frac{\sqrt{2m^*E}}{\hbar}$$

2.3.4

Figure 2.3.1: Wavefunctions and potential barriers of a particle tunnelling thorough a single barrier.

If we then consider the situation of the particle inside the potential barrier the wavenumber will be given by

$$k = \frac{\sqrt{2m^*(E - U_0)}}{\hbar}$$

2.3.5

In the case that the energy E of the electron is higher than the barrier, then the wave function will again be a simple plane wave. However, in the case that the energy of an incoming electron is lower than the barrier, the contents of the square root will be negative, and the wavenumber will become imaginary. This corresponds to an evanescent wave function which decays when in the barrier.

It is to be noted that the amplitude of the wave function does not represent the energy of the electrons and is only related to the probability of finding the electron at a particular position. To calculate the probability of tunnelling, we must find the ratio of the amplitudes of the plane waves on either side of the barrier.

If we assume that on the left of the barrier, we have

$$\psi_1 = Ae^{ikx} + Be^{-ikx}$$

2.3.6

which represents an incident wave with amplitude A and a reflected wave with amplitude B. In the barrier we will have the wave function representing two evanescent waves with amplitudes C and D where K is the wavenumber from Equation 2.3.5.

$$\psi_2 = Ce^{\kappa x} + De^{-\kappa x}$$

2.3.7

On the right-hand side of the barrier we will simply have the transmitted plane wave function with amplitude F.

$$\psi_3 = F e^{ikx}$$

2.3.8

Since wave functions are continuous and well behaved then at the boundaries on either side of the barrier, we can say that

$$\psi_1(0) = \psi_2(0)$$

$$2.3.9$$

$$\frac{d\psi_1(0)}{dx} = \frac{d\psi_2(0)}{dx}$$

$$2.3.10$$

$$\psi_2(W) = \psi_3(W)$$

$$2.3.11$$

$$\frac{d\psi_2(W)}{dx} = \frac{d\psi_3(W)}{dx}$$

2.3.12

We can substitute our wave functions into these equations and evaluate them at x = 0and x = W to get

$$Ae^{0} + Be^{0} = Ce^{0} + De^{0}$$

$$2.3.13$$

$$A + B = C + D$$

2.3.14

$$Aike^0 - Bike^0 = CKe^0 - DKe^0$$

2.3.15

$$CKe^{KW} - DKe^{KW} = Fike^{ikW}$$

32

From these four equations it can be shown that the ratio of the amplitudes A and F is given by

$$\frac{F}{A} = \frac{i4Kk}{(K+ik)^2 e^{-KW} - (K-ik)^2 e^{KW}}$$

2.3.17

If we assume that the barrier height is a lot higher than the energy of the particle. i.e  $U_0 \gg E$  and that the barrier is wide enough that KW > 1 then the above equation can be simplified to

$$\frac{F}{A} \approx \frac{-i4Kk}{(K-ik)^2} e^{-KW}$$

2.3.18

To find the probability of a particle passing through the barrier we need to multiply the amplitudes by their complex conjugates. This will give us the tunnelling coefficient T.

$$T = \frac{F^*F}{A^*A} = \frac{(4kK)^2 e^{-2KW}}{(k^2 + K^2)^2}$$

2.3.19

The tunnelling probability is then usually given in terms of the electron energy and the barrier height as shown below

$$T = \frac{16(U_0 - E)}{U_0^2} e^{-2\frac{\sqrt{2m^*(E - U_0)}}{\hbar}W}$$

2.3.20

As can be seen from Equation 2.3.20, the tunnelling probability is exponentially dependent on the width of the barrier. This means that any devices which utilise quantum tunnelling must control the barrier width to a very high level of precision to ensure uniformity in the characteristics of devices across the whole device yield.

#### 2.3.2. Double Barrier Resonant Tunnelling

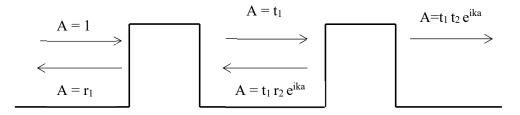

Resonant tunnelling is another quantum tunnelling process in which particles pass through potential barriers similarly to the way described in the previous section. However, in the case of two potential barriers a more interesting result occurs. Let us consider a situation in which two barriers exist separated by a distance, a, the barriers will have transmission and reflection coefficients  $t_1$ ,  $t_2$  and  $r_1$ ,  $r_2$ .

Figure 2.3.2: Amplitudes of wavefunctions for particles travelling through a double barrier resonant tunnelling structure with transmission and reflection coefficients.  $t_1$ ,  $t_2$  and  $r_1$ ,  $r_2$ .

Now let's consider a particle travelling towards the double barrier structure. This particles wave function will essentially be that of a plane wave as described by

$$\psi = Ae^{ikx - \omega t}$$

2.3.21

Where A is an arbitrary constant, k, is the wavenumber and  $\omega$  is the angular frequency. Now consider the form of the waves after passing through the barrier structure. These will be similar to the form given by Equation 2.3.21 but with the amplitude multiplied by some factor. The first case is a wave which passes straight through the barrier as shown in Figure 2.3.2. This will have an amplitude of

$$A = t_1 t_2 e^{ika}$$

2.3.22

where *ka* is the phase change of a particle with energy  $E = \frac{\hbar^2 k^2}{2m}$  after travelling a distance *a*.

Now consider the case in which a particle tunnels through the first barrier, is reflected by both barriers inside the quantum well and then tunnels through the second barrier to leave the structure. In this case the Amplitude will be given by

$$A = t_1 t_2 r_1 r_2 e^{i3ka}$$

2.3.23

This is because it has tunnelled through both barriers once and been reflected by both barriers once. The phase change is 3ka as the particle has travelled the length of the well three times. This can also be done for the case in which the particle reflects off both sides twice to give and amplitude of

$$A = t_1 t_2 r_1^2 r_2^2 e^{i5ka}$$

2.3.24

This can go on indefinitely with more internal reflections being added.

Due to the theory of superposition the amplitude for the particles which tunnel through both barriers can be found through summing the amplitude for all cases to give.

$$t = t_1 t_2 e^{ika} + t_1 t_2 r_1 r_2 e^{i3ka} + t_1 t_2 r_1^2 r_2^2 e^{i5ka} + \cdots$$

$$= t_1 t_2 e^{ika} \sum_{n=0}^{n=\infty} (r_1 r_2 e^{i2ka})^n$$

2.3.25

This is the sum of a geometric series and as such can be written as

$$t = t_1 t_2 e^{ika} \left[ \frac{1}{(1 - r_1 r_2 e^{i2ka})} \right]$$

2.3.26

In quantum mechanics the transmission probability, T, for both barriers is given by the squared modulus of the total amplitude t. Therefore

$$T = |t|^{2} = \frac{|t_{1}|^{2}|t_{2}|^{2}}{1 + |r_{1}|^{2}|r_{2}|^{2} - 2|r_{1}||r_{2}|\cos\Psi}$$

$$2.3.27$$

Where  $\Psi = 2ka + \psi r_1 + \psi r_2$ . This is the phase change due to the additional travel time when being reflected and the inherent phase change that occurs with reflection. Clearly Equation 2.3.27 is maximised when  $\cos \Psi = 1$ . This occurs when  $\Psi = 2ka + \psi r_1 + \psi r_2 = 2n\pi$ . Where n is an integer. This can be thought of as the case when all the contributions for multiple reflections are in phase and combine constructively. If the barriers are of equal thickness so that  $t_1 = t_2$  and  $r_1 = r_2$  then the transmission probability on resonance is given by

$$T_{resonance} = \frac{|t_1|^4}{(1-|r_1|^2)^2}$$

2.3.28

Since  $|t_1|^2 + |r_1|^2 = 1$  this becomes

$$T_{resonance} = \frac{|t_1|^4}{|t_1|^4} = 1$$

2.3.29

This is a remarkable result which shows that provided the incoming electron or particle has a wavenumber and therefore energy that matches the resonance condition the probability that it will pass through the barrier structure is 100%. This wave number corresponds to the same wavenumber of the confined energy states of the well between the two barriers.

# 2.4. Tunnel Diodes

#### 2.4.1. Esaki Diodes

The Esaki diode was the first tunnel diode to be invented and won Leo Esaki, after which it is named, the Nobel prize in 1973 [121]. This diode was based on an extremely highly doped p-n junction with a very thin depletion region and overlapping valence and conduction bands. As the diode is biased, band to band tunnelling occurs and electrons tunnel between the n-type conduction band and the p-type valence band.

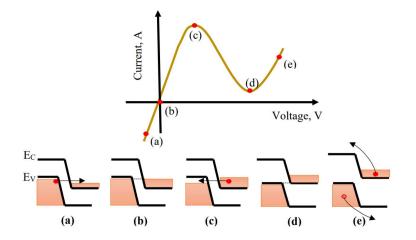

The Figure 2.4.1 below shows the band structure and current voltage curve of an Esaki diodes. When the device is reverse biased at point a) the electrons from the p-type valence band tunnel into the n-type conduction band. At point b) at zero bias the device is in equilibrium and no current flows. When the device is first forward biased the electrons tunnel from the n-type conduction band to the p-type valence band. As the device is further biased at point c) the p-type valence band becomes misaligned with the n-type conduction band and no tunnelling can occur leading to a drop in the current of the device. This continues to happen until the voltage is high enough for standard current flow to occur in the same manner as all p-n junctions at point d). After this the diode behaves in the same manner as a standard p-n junction e).

Figure 2.4.1 Current-Voltage characteristic and band diagram of an Esaki diode at different bias points. a) reverse bias, b) zero-bias c) peak bias d) valley bias e) forward bias.

The interesting piece of physics in this device is the current drop as the voltage increases after the n-type conduction band to the p-type valence band are no longer aligned. This is a negative differential resistance and the uses of negative resistances will be explored later in the chapter.

#### 2.4.2. ASPAT Devices

As discussed before, when two dissimilar semiconductors are brought together as a heterojunction, band gap discontinuities can form. These band gap discontinuities can be used to create potential barriers such as those seen in section 2.3.1. These potential barriers can then be used as part of active devices. One example of such a device is the Asymmetric Spacer Layer Tunnel Diode (ASPAT). This device, first invented in 1992 by Syme and Kelly [86], comprises of a single very thin barrier (of the order a few nm) sandwiched between two layers of intrinsic semiconductor. The two intrinsic layers are spacers from the doped layers used for contacts and carrier providers. These layers are asymmetric in thickness with a typical ratio of 40:1.

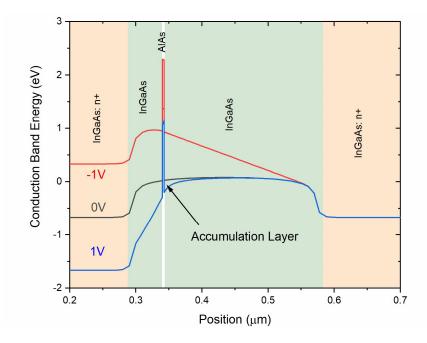

As can be seen from Figure 2.4.2, under forward bias the electrons accumulate at the base of the barrier in the small triangular quantum well. From here the electrons can either jump over the barrier via thermionic emission or tunnel through the barrier providing a current. Under reverse bias conditions this accumulation layer does not form and so the current is significantly reduced giving rise to an asymmetric current voltage curve as shown in Figure 2.4.3. This asymmetric behaviour allows for the ASPAT to behave as a rectifying diode.

Figure 2.4.2 Conduction band diagram of an InGaAs ASPAT diode under forward and reverse bias conditions showing the formation of an accumulation layer.

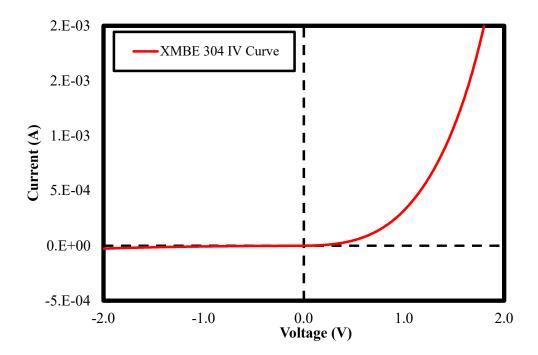

Figure 2.4.3 Measured current-voltage curve form -2V to 2V for a GaAs/AlAs ASPAT diode denoted XMBE304.

The current-voltage curve for the ASPAT diode can be determined theoretically by solving the Schrodinger and Poisson equations. To do this we make the assumptions

that the tunnelling is only from the accumulation layer and only through the direct gamma valley of the bandgap. The current in the x and y directions is taken to be uniform reducing the problem to a one-dimensional solution of the Schrodinger equation in the z direction.

$$-\frac{\hbar^2}{2m^*}\frac{d^2\psi}{dz^2} + e(\phi - \Delta\phi)\psi = E_z\psi$$

2.4.1

where is ( $\phi$ ) the potential at point  $\mathbf{z}$ , and ( $\Delta \phi$ ) is a correction term which reduces the effective barrier height and can be neglected since there is virtually no band bending when the bias (V) increases. The current density in the z-direction ( $J_z$ ) is then calculated by solving Equation 2.4.1 at different values of  $E_z$ . Thus,  $J_z$  is expressed as:

$$J_{z} = \frac{-e\hbar}{2m^{*}} \left( \psi^{*} \frac{d\psi}{dz} - \psi \frac{d\psi^{*}}{dz} \right)$$

2.4.2

Due to the heavily doped contacts on either side of the barrier the wavefunction can be described as plane waves as was shown earlier in the chapter for single barrier tunnelling. Thus giving

$$\psi_L = e^{ik_l z} + Re^{-ik_l z}$$

2.4.3

$$\psi_R = Te^{ik_R z}$$

2.4.4

From here T and R can be found using a transfer matrix method for all possible values of  $E_z$ . If this is then multiplied by the fermi function

$$f(E) = \frac{1}{1 + e^{\left(\frac{E_Z - E_F}{k_B T}\right)}}$$

2.4.5

40

and integrated across all possible energy values a final expression of the current density is achieved.

$$J_{z} = \frac{em^{*}k_{B}T}{2\pi^{2}h^{3}} \int_{0}^{\infty} T(E_{z}) \ln\left\{\frac{1 + e^{\left(\frac{E_{F} - E_{z}}{k_{B}T}\right)}}{1 + e^{\left(\frac{E_{F} - eV - E_{z}}{k_{B}T}\right)}}\right\} dE_{z}$$

2.4.6

Current ASPATs are typically made using AlAs barriers and either GaAs or InGaAs as the main semiconductor. In the case of InGaAs the percentage of Indium is typically 53% to lattice match it to InP which is typically used as a substrate for the growth. These ASPATs are grown using the Molecular Beam Epitaxy (MBE) technique in which the semiconductor crystal is grown in a vacuum, with semiconductor elements heated to the point that they sublime into atoms. These atoms then condense on the substrate growing the crystal.

It is necessary to use MBE to grow ASPAT structures to control the barrier layer thickness. As discussed earlier, quantum tunnelling is exponentially dependent on the width of the barrier. It has been shown in simulations that for an AlAs barrier a single monolayer difference results in a 270% difference in current in the device [101], [102]. As industry requires devices with a variation of less than 15% the control of the barrier thickness is one of the key barriers preventing large scale manufacture of ASPAT diodes. However, recent work has shown that through careful growth, a 1% variation across the wafer can be produced and a 1% variation from wafer to wafer [101]. Allowing for the possibility that ASPATs and other tunnel diodes may be manufactured in large scales in the future.

The ASPAT has potential applications as part of a detection circuit for both microwaves, millimetre waves and the low end of the THz spectrum. Current ASPATs are comparable to Schottky and Planar doped diodes in terms of dynamic range, low noise performance, and have a comparable transfer function[88]. The ASPAT diode is especially suited to zero bias detection and due to the fact that the main carrier process is quantum tunnelling and not thermionic emission, the ASPAT shows a much-reduced temperature dependence[87] allowing it to be used in applications in which temperature insensitivity is a key requirement.

#### 2.4.3. Resonant Tunnelling Diodes

An example of a typical RTD structure is the double barrier quantum well which consists of an undoped quantum well of low bandgap semiconductor (GaAs, InGaAs, etc) sandwiched between two thin barriers of high bandgap semiconductor (AlAs, InAlAs, etc). This creates a band diagram similar to the potential barrier shown in Figure 2.4.4.

Most RTD structures created with III-V semiconductors are created using molecular beam epitaxy (MBE)[33], [122] to deposit layers of semiconductor with high precision. This is of key importance as the barrier widths have a large impact on the tunnelling probability. MBE techniques allow for control of the crystal growth to the atomic monolayer level. Some RTD devices have been created using metal-organic vapour phase epitaxy (MOVPE)[123], however MBE remains the most common method of growth for RTD devices.

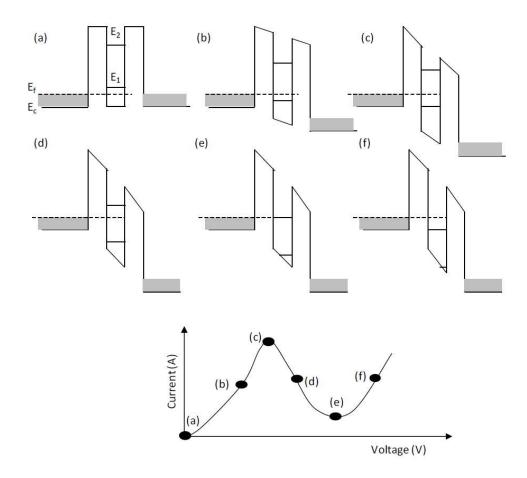

To further understand RTDs. we must look at the effects of biasing the RTD. Figure 2.4.4 shows the band diagram for an RTD under various bias points as well as the I-V characteristics of the RTD.

Figure 2.4.4: RTD band diagrams and IV characteristics at various bias points. a) zerobias c) peak bias e) valley bias f) forward bias. b) and d) are intermdeiate bias points. [124]

At zero bias (point (a)) the electrons on either side of the barrier act as a Fermi gas populating the energy levels up to the fermi level. As the fermi level is below the first resonant energy  $E_1$  the electrons cannot tunnel through the barrier. In this condition no current flows. As the voltage is increased, a small current flows as the resonant energy drops below the fermi level allowing electrons to tunnel across the structure (b). When the resonant level is at the same energy as the conduction band on the emitter (left) side of the device the current due to tunnelling is at a maximum (c). This is the peak voltage of the RTD. After the resonant level falls below the conduction band the current falls again (d) to a minimum (e). After this point electrons gain the necessary kinetic energy to overcome the barrier and current again starts to rise until the second resonant level allows electrons to tunnel through the barrier (f). After this point the voltage is high enough that the main current mechanism is through thermionic emission.

If we look at the I-V curve of the RTD in Figure 2.4.4 the current decreases as the voltage increases between the peak voltage at (c) and the minimum at (e). This implies, as with the Esaki diode, that the RTD displays negative differential resistance. The use of this NDR region in microwave emission and detection will be discussed in the next section.

# 2.5. Applications of Tunnel Diodes as Microwave Emitters and Detectors

# 2.5.1. Tunnel Diodes as Emitters

As discussed previously, the Esaki diode and the RTD both exhibited a negative differential resistance. This property allows for their use as amplifiers and as part of oscillator circuits. These oscillators can then be used to emit radiation for the purposes of data communication and imaging. To better understand this, we will start by exploring the properties of circuits including negative differential resistance.

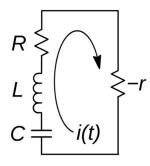

If we consider a simple RLC circuit containing a resistor, R, an inductor, L, and a capacitor, C, and then add an element with a negative resistance, -r, as shown below, we can further understand negative resistance.

Figure 2.5.1: Circuit diagram of and RLC circuit with a negative resistor.

From Kirchhoff's voltage law the current,  $i\{t\}$  around this circuit can be given as

$$\frac{di\{t\}}{dt}L + i\{t\}(R-r) + \int \frac{i\{t\}}{C}dt = 0$$

$$\therefore \frac{d^2 i\{t\}}{dt^2} + \frac{d i\{t\}}{dt} \frac{(R-r)}{L} + \frac{i\{t\}}{LC} = 0$$

2.5.1

This is the differential equation for damped simple harmonic motion and has the solution

$$i\{t\} = i_0 e^{-\alpha t} \cos(\omega t + \varphi)$$

2.5.2

Where

$$\alpha = \frac{(R-r)}{2L}$$

$$\omega = \sqrt{\frac{1}{LC} - \left(\frac{R-r}{2L}\right)^2}$$

From this it is clear that if  $\alpha$  is negative the current will oscillate with an exponentially increasing current. For real devices, such as the Esaki diode and the RTD, the current would stabilise as the device moves to the edge of the negative differential resistance region, where R = r. The frequency of operation, f, at the point of stability is easy to find and is given by Equation 2.5.3.

$$f = \frac{1}{2\pi} \sqrt{\frac{1}{LC}}$$

2.5.3

As we have seen both the Esaki diode and the RTD exhibit negative differential resistance. A common figure of merit for these types of devices is the peak to valley current ratio (PVCR) which is simply the ratio of the current at the peak (Figure 2.4.4 (c)) to the current at the valley (Figure 2.4.4 (e)). As given by Equation 2.5.4.

$$PVCR = \frac{I_P}{I_V}$$

2.5.4

The negative differential resistance,  $R_d$ , itself can be characterised simply by Equation 2.5.5

$$R_d = \frac{V_p - V_v}{I_p - I_v} = \frac{\Delta V}{\Delta I}$$

2.5.5

The gain provided by the negative differential resistance allows free running oscillations, which are limited by the capacitance of the circuit. As such it is important to reduce the capacitance of the Esaki diodes or the RTD to as low a figure as possible. Both devices can be considered to be two charged layers separated by undoped semiconductor and as such the standard capacitor equation can be used to approximate the capacitance. This is shown in Equation 2.5.6.

$$C = \frac{A\varepsilon_0\varepsilon_r}{t}$$

2.5.6

Where A is the device area, t the thickness of the double quantum barrier structure and undoped spacer layers for the RTD and the size of the depletion region for the Esaki diode,  $\varepsilon_0$  the permittivity of free space and  $\varepsilon_r$  the relative permittivity of the undoped regions of the device.

The theoretical maximum power emitted by the device as radiation can be described by the relation given in Equation 2.5.7.

$$P_{Max} = \frac{3\Delta V\Delta I}{16}$$

2.5.7

Clearly to generate large amounts of RF power, the voltage and current differences between the peak and the valley must be as large as possible. Practical device RF power at high frequency will not be as high as the power given by the relation due to the transit time of the electrons across the device [33]. This becomes more of a factor as the frequency of operation is increased and a more accurate power equation is given by

$$P_{RF} = \frac{3\Delta V\Delta I}{16} \cos \omega \tau$$

2.5.8

where  $\omega$  is the angular frequency and  $\tau$  is the transit time across the device.

The Esaki diode was a promising element for room temperature emitter applications. However, the thin barrier and consequently high junction capacitance, as well as the slow transit time of minority carriers limits its use at high-frequency and as such RTDs are the subject of a more concentrated effort in recent years. The current highest measured frequency for RTD oscillators was reported by the Asada group to be 1.98THz [41]. No power output was reported for this frequency, however previous work showed an output power of  $0.4\mu$ W for a frequency of 1.92THz [125]. Whilst RTDs with the capability to operate at frequencies above 2THz have been shown by the University of Manchester[33], direct measurement of these frequencies has not been possible.

As data communications such as 5G and the IEEE 802.11ad WiFi standard move towards higher frequency [4], [6], [126]–[128], low power emitter technologies, the advantages of the RTD become more relevant. High frequencies in the mm-Wave and THz regimes allow for extremely high data rates. These frequencies have previously been ignored due to their poor propagation properties limiting their range. However, the 5G proposals to utilise small cells with high density mitigate these problems. As such recent research by the Asada group has shown wireless data rates of 34Gbit/s utilising RTD oscillator circuits[70].

#### 2.5.2. Tunnel Diodes as Detectors

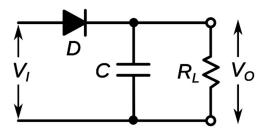

One of the main applications of all diodes is rectification. That is to allow current to pass through in only one direction. Rectification is of vital importance in the detection of microwave and radio wave communications. As such one of the key applications of some of the tunnel diodes discussed in the previous section is as a detector for telecommunications and data communications purposes. There are two types of detection in which tunnel diodes can be useful. The first is direct detection in which the diode is used in the detector circuit to demodulate the signal from the carrier wave. To better understand how this is achieved, we shall look at a simple diode detector.

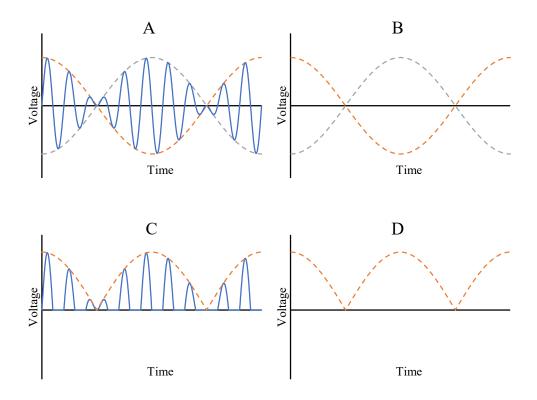

One of the simplest diode detector circuits is used to detect amplitude modulated radio signals[129]. So, let's imagine a signal carried by a cosine wave with amplitude, A, and angular frequency  $\omega_c$ . If the modulating signal is some function f(t). Then the signal seen by the detector will be given by Equation 2.5.9 and look like Figure 2.5.3(A)

$$signal = (A + f(t)) \cos \omega_c t$$

2.5.9

The detector circuit will consist of an antenna with some filtering to match the carrier frequency, a diode and a low pass filter. The diode and low pass filter are shown in Figure 2.5.2. The low pass filter will filter out the carrier frequency leaving just the modulating signal. If just the low pass filter was used, there would be two modulating signals one positive and one negative, and these would cancel out and the signal would be lost. This can be seen in Figure 2.5.3 (B). To stop this, the diode rectifies the signal before the low pass filter, removing the negative modulation. After the signal passes through the low pass filter only the positive modulation remains, and the full original signal is recovered. This is clearly demonstrated in Figure 2.5.3.

Figure 2.5.2:A simple microwave detector circuit containing a diode D, a capacitor C and a load resistor  $R_L$ .

Figure 2.5.3 Plots of an amplitude modulated signal after various processing stages A) Full signal recieved from antena B) Signal after low pass filter only C) Signal after rectification. D) Signal after low pass and rectification.

This is the simplest form of RF modulation and direct detection, other more complex modulation processes such as frequency modulation and pulse modulation also exist using more complex detector circuit designs. These more complex detector circuits still make use of the non-linear nature of the diodes to recover the signal from the carrier wave. Of the tunnel diodes discussed so far in this section the ASPAT diodes are the more suitable diodes for direct detection applications.

The suitability of a diode for direct detection is determined by a few key factors. The most important of which is the voltage sensitivity. This is given by the ratio of the output voltage to the input RF power and is given in units of V/W. The voltage sensitivity is easily measured at low frequency using a  $50\Omega$  RF source. The unmatched voltage sensitivity is given by

$$S_V = 2Z_s k_V$$

2.5.10

where  $Z_s$  is the source impedance, and  $k_V$  is the curvature coefficient [82].  $k_V$  is one of the most important figures of merit for detector diodes, as it is a measure of the nonlinearity of the diode. This is done by taking the quotient of the second and first derivatives of the current voltage curve as given by

$$k_{v} = \frac{\frac{\partial^{2}I}{\partial V^{2}}}{\left|\frac{\partial I}{\partial V}\right|}$$

2.5.11

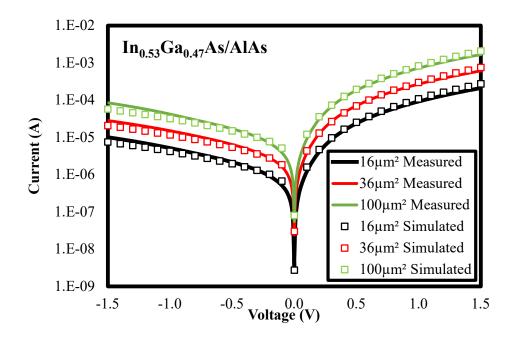

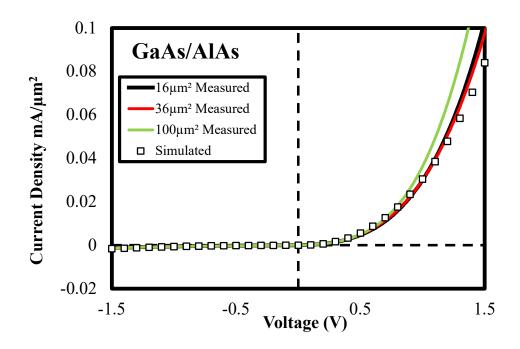

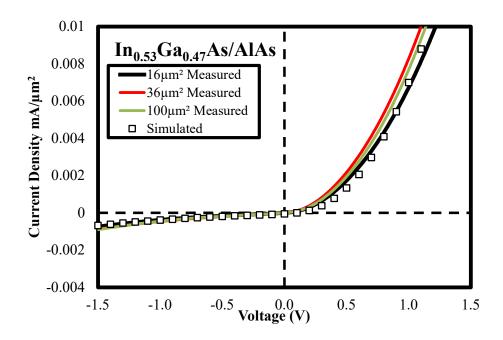

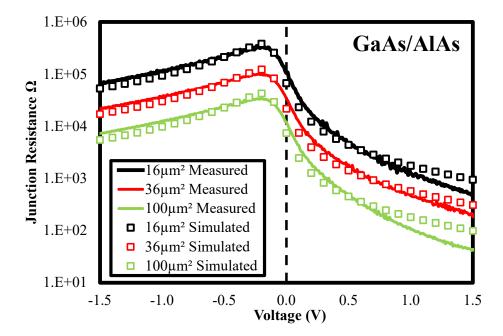

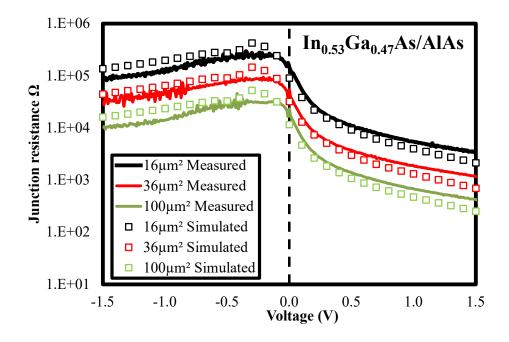

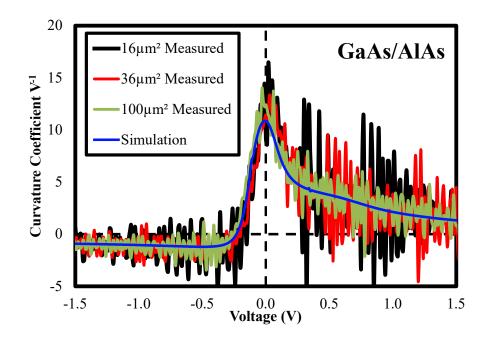

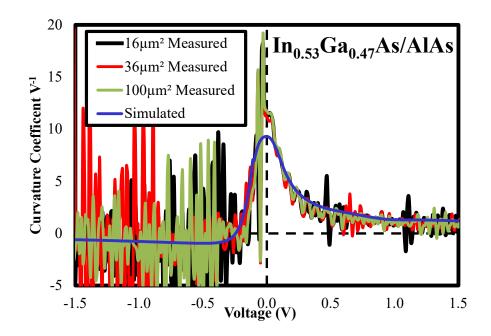

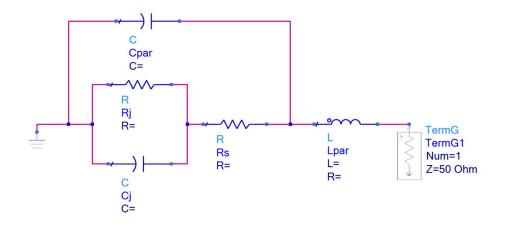

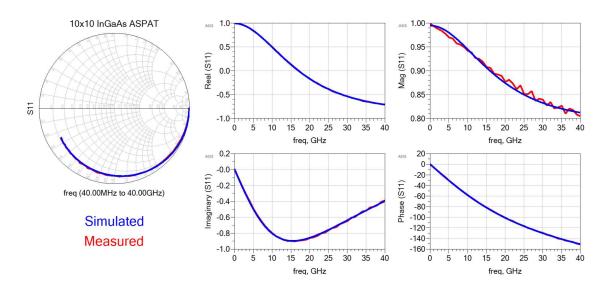

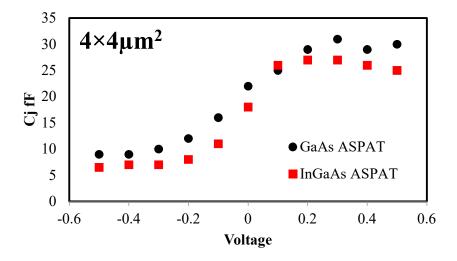

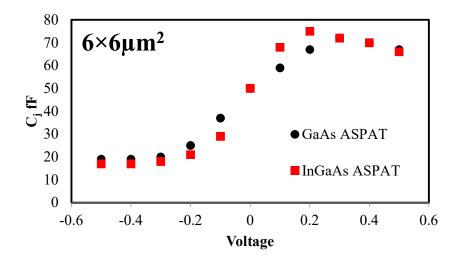

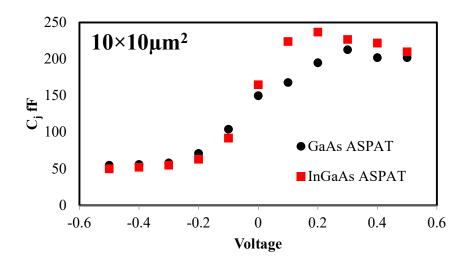

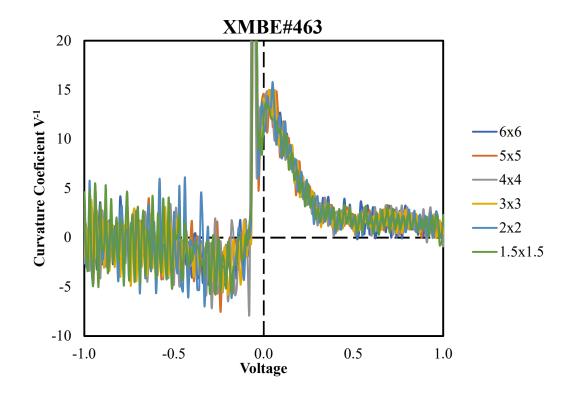

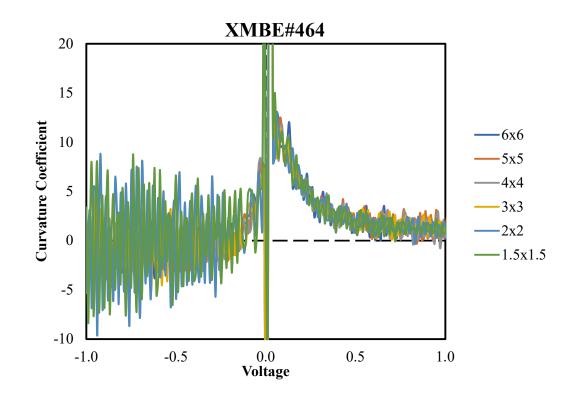

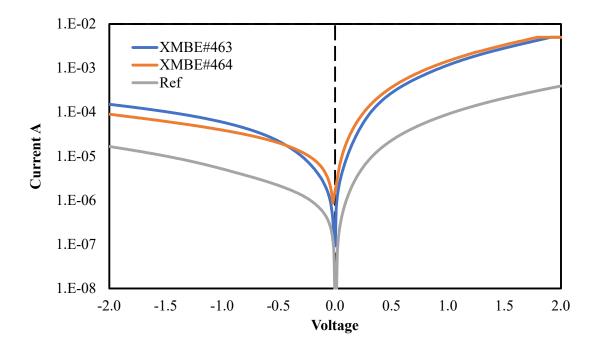

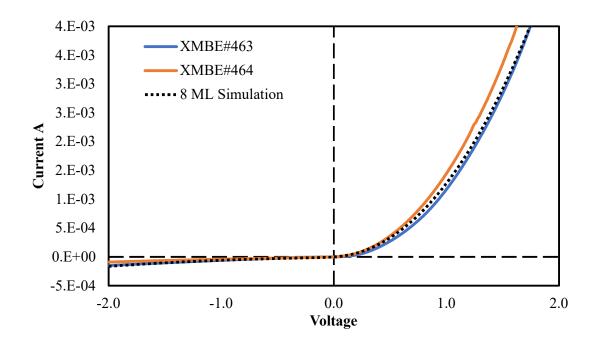

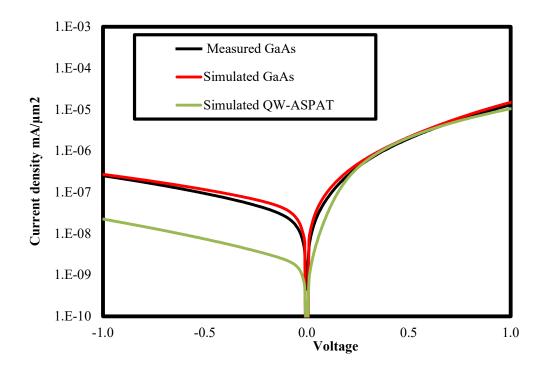

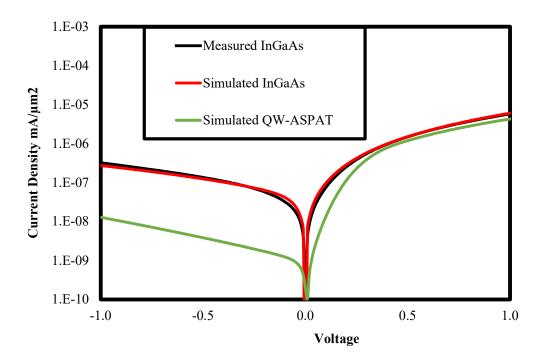

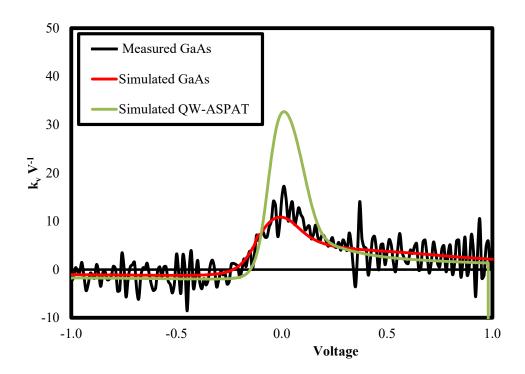

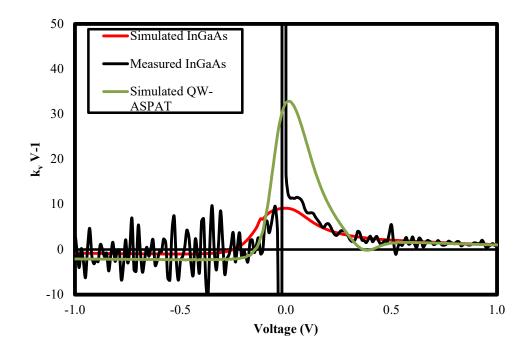

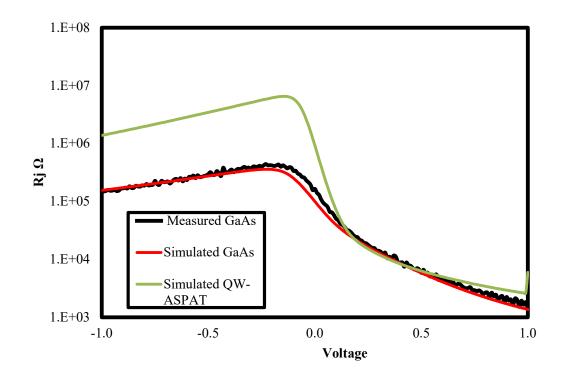

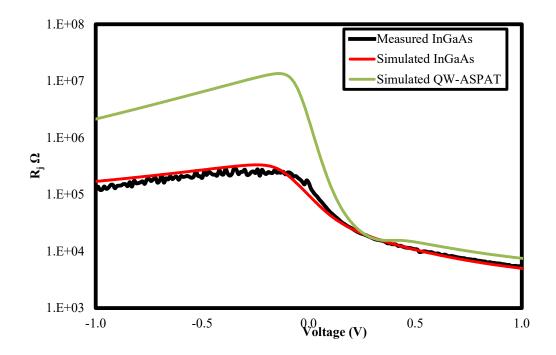

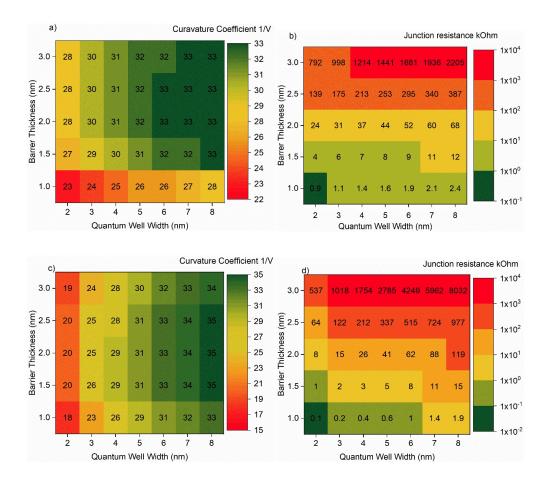

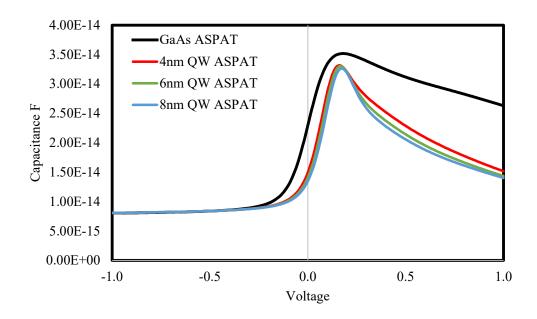

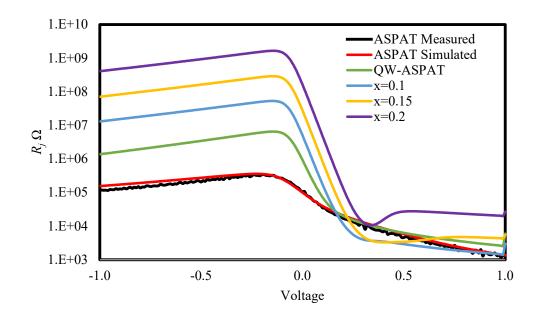

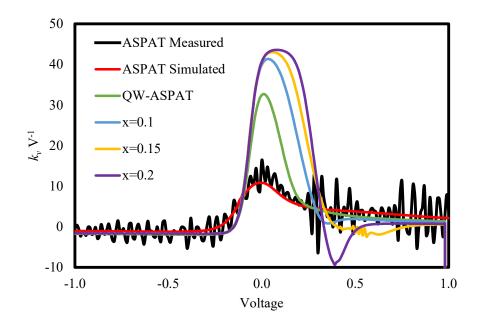

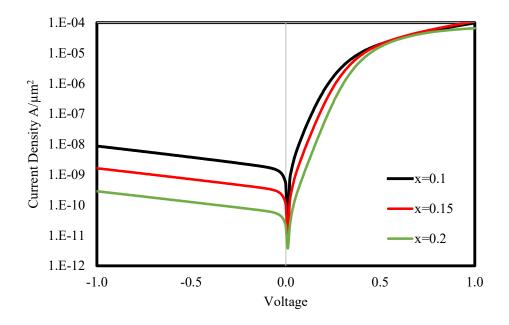

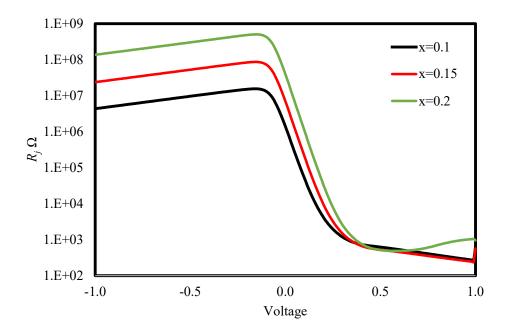

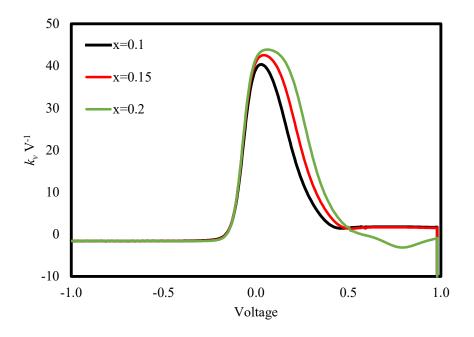

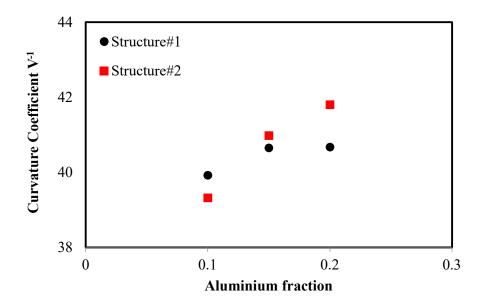

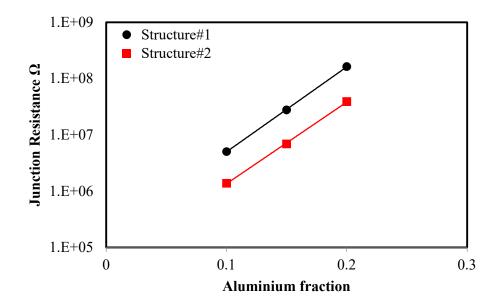

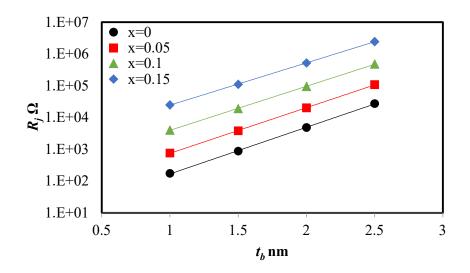

For the Schottky diode, in which thermionic emission is the main transport method, the curvature coefficient can also be calculated using the expression  $(q/k_bT)$ . For Schottky diodes, this has an upper theoretical limit of ~40V<sup>-1</sup>. Moreover, Schottky diodes are often biased to the point of highest non-linearity to improve sensitivity. This adds additional complexity to the circuit compared with a zero-bias detector device such as the ASPAT diode, in which  $k_v$  is at a maximum at 0V. As the ASPATs main transport mechanism is quantum tunnelling, it is possible that the ASPAT could be engineered to a value of  $k_v$  above 40V<sup>-1</sup>.