The University of Manchester

The University of Manchester Research

# Emulation of synaptic functions with low voltage organic memtransistor for hardware oriented neuromorphic computing

DOI:

10.1038/s41598-022-07505-9

#### **Document Version**

Final published version

Link to publication record in Manchester Research Explorer

#### Citation for published version (APA):

Sagar, S., Udaya Mohanan, K., Cho, Ś., Majewski, L., & Das, B. C. (2022). Emulation of synaptic functions with low voltage organic memtransistor for hardware oriented neuromorphic computing. *Scientific Reports*, 1-12. [3808]. https://doi.org/10.1038/s41598-022-07505-9

### Published in:

Scientific Reports

#### Citing this paper

Please note that where the full-text provided on Manchester Research Explorer is the Author Accepted Manuscript or Proof version this may differ from the final Published version. If citing, it is advised that you check and use the publisher's definitive version.

#### **General rights**

Copyright and moral rights for the publications made accessible in the Research Explorer are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

#### Takedown policy

If you believe that this document breaches copyright please refer to the University of Manchester's Takedown Procedures [http://man.ac.uk/04Y6Bo] or contact uml.scholarlycommunications@manchester.ac.uk providing relevant details, so we can investigate your claim.

## scientific reports

## **OPEN** Emulation of synaptic functions with low voltage organic memtransistor for hardware oriented neuromorphic computing

Srikrishna Sagar 101, Kannan Udaya Mohanan3, Seongjae Cho 1013, Leszek A. Majewski 1012 & Bikas C. Das<sup>1</sup>□

Here, various synaptic functions and neural network simulation based pattern-recognition using novel, solution-processed organic memtransistors (memTs) with an unconventional redox-gating mechanism are demonstrated. Our synaptic memT device using conjugated polymer thin-film and redox-active solid electrolyte as the gate dielectric can be routinely operated at gate voltages ( $V_{GS}$ ) below - 1.5 V, subthreshold-swings (S) smaller than 120 mV/dec, and ON/OFF current ratio larger than 108. Large hysteresis in transfer curves depicts the signature of non-volatile resistive switching (RS) property with ON/OFF ratio as high as 10<sup>5</sup>. In addition, our memT device also shows many synaptic functions, including the availability of many conducting-states (> 500) that are used for efficient pattern recognition using the simplest neural network simulation model with training and test accuracy higher than 90%. Overall, the presented approach opens a new and promising way to fabricate high-performance artificial synapses and their arrays for the implementation of hardwareoriented neural network.

Since the inception of civilization, researchers have dreamt about building an electronic machine with similar functionality as a brain. As a result, brain structure-inspired neuromorphic computing has been extensively explored as a promising way to realise artificial intelligence systems that are capable of learning and performing complex tasks<sup>1,2</sup>. The first hardware-based neural functionality was demonstrated using Si-based CMOS logic but the demonstrated electronic circuits were cumbersome and consumed huge amount of energy3. To date, substantial developments have been made in both software algorithms and hardware designs<sup>4,5</sup>. However, in terms of size, power efficiency, massively parallel connectivity, self-learning capability, fault-tolerant operation, data storage, and data processing, the human brain is still much more efficient than any neuromorphic platform built thus far<sup>6</sup>. In fact, the brain can efficiently process real-time unstructured signals such as sound, light, pressure, heat, and taste, which is impossible to realise using today's computers. To perform such complex tasks, the brain functions in massively parallel ways using interconnected neurons and synapses. Typically, the action potential signal is passed from one neuron to the next by modulating the chemical fluxes inside the synaptic cleft that changes the synaptic weight in response to the signal frequency. Neurons also emulate the Hebbian learning principle and spike-timing-dependent plasticity (STDP), which forms the basis of learning and memory functions. Notably, the Hebbian postulate states that the synaptic strength among pre- and post-neurons can only be modulated if both are fired momentarily with a mandatory temporal correlation8. Mimicking various synaptic functionalities such as excitatory postsynaptic current (EPSC), short-term potentiation and depression (STP/STD), long-term potentiation and depression (LTP/LTD), paired-pulse facilitation (PPF), post-tetanic potentiation (PTP), as well as many others have recently been reported in the literature<sup>6,9,10</sup>. However, reaching the energy efficiency close to the brain (1–100 fJ) for an artificial synaptic event is still very challenging<sup>6,11</sup> to achieve.

Consequently, many efforts have been devoted to develop low energy consuming synaptic devices and neural circuits using unconventional electronic materials and devices9. For example, the demonstration of memristor (MR) in 2008 sparked a strong interest in building neuromorphic circuits using MR<sup>12</sup>. Since then, many memristor designs have been proposed to emulate biological synaptic plasticity, including phase-change memories,

<sup>1</sup>School of Physics, Indian Institute of Science Education and Research Thiruvananthapuram (IISER TVM), Vithura, Trivandrum, Kerala 695551, India. <sup>2</sup>Department of Electrical and Electronic Engineering, University of Manchester, Manchester M13 9PL, UK. <sup>3</sup>Department of IT Convergence Engineering, Gachon University, Seongnam, Republic of Korea.  $^{oxtimes}$ email: bikas@iisertvm.ac.in

resistive switching devices, and so on 13-22. However, even though these devices consume much less energy compared with the software-driven neural network hardwares, they still cannot achieve the energy efficiency close to the brain. Recently, three-terminal ferroelectric, floating-gate, and electrolyte-gated thin-film transistors (TFTs) based memory devices have been under intense study to mimic synaptic actions 23-25. In particular, electrolyte gated TFTs have been broadly investigated as their structure is quite similar to that of a biological synapse and they can be operated at low gate voltages (< 3.0 V) due to the large specific capacitance offered by the electrolyte gate dielectrics 26-29. In these TFTs, the gate electrode resembles a presynaptic input terminal called the axon and the drain electrode corresponds to the postsynaptic output terminal called the dendrite. Accordingly, functionalities of a biological synapse can be simulated by modulating/demodulating the channel conductance (so-called synaptic weight) by applying voltage pulses to the gate (presynaptic) and drain (postsynaptic) terminals. However, the efficacy of a synaptic device depends on several factors including the device structure, used active channel materials, stability of operation, synaptic behaviours, and energy consumption per synaptic event. Hence, exploring and studying alternative materials and device structures is essential to realize high-performance artificial electronic synapses and large-area synaptic arrays.

Here, high-performance, low-voltage redox-gated organic memtransistors (memTs) which efficiently emulate various synaptic actions of a brain are demonstrated. Thin-film of poly(3-hexylthiophene-2,5-diyl) (P3HT) is used as the channel and redox-active ethyl viologen diperchlorate (EVP) with polyethylene oxide (PEO) solid electrolyte as the gate dielectric. It is shown that the availability of large number of discrete conducting states programmed by voltage pulses applied to the gate and improved transistor performance make memTs very promising devices to be used as artificial synapses that consume as little energy as 250 pJ per synaptic action (SA). The analog synaptic device concept proposed here can be explored further as the employed organic materials are relatively easy to process and their electronic properties can be tuned as desired using conventional chemical routes and approaches.

#### Results and discussion

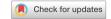

Memtransistor characteristics with the multilevel memory property. An organic memory transistor or memtransistor (memT) is basically a thin-film transistor (TFT) possessing additional resistive switching and memory storage capabilities<sup>30</sup>. Fig. 1a shows the structure of our top-gate bottom-contact organic memT devices using ~ 30 nm thick poly(3-hexylthiophene-2,5-diyl) P3HT thin film as active channel and a ~ 2.5 µm thick drop-cast solid electrolyte film of ethyl viologen diperchlorate ((EV(ClO<sub>4</sub>)<sub>2</sub>) in poly(ethylene oxide) (PEO) as the gate dielectric<sup>26,29</sup>. Typical transistor characteristics reveal that the fabricated memT devices show usual p-channel transistor behaviour with a ON/OFF current ratio >  $10^8$  and operational voltage  $|V_{GS}|$  or  $|V_{G}| < 1.5$  V as illustrated in the Supplementary Information Fig. S1. This result also confirms that a suitable negative (-ve) voltage at gate is needed to switch the channel conductivity from a low to a high value. To depict the memory and information storage capability of our memT devices, current-voltage (I-V) characteristics were recorded to demonstrate the resistive switching (RS) property as per the scheme illustrated in Fig. 1b. Usually, RS property of 3-terminal devices is demonstrated by the channel conductivity switching from a low (OFF) to a high (ON) state by applying a suitable gate voltage  $(V_{GS})^{26,31}$ . As per the scheme, current–voltage  $(I_D - V_{DS})$  characteristics at the drain were recorded by sweeping the  $V_D$  (or  $V_{DS}$ ) in a loop between – 1.0 and + 1.0 V before and after applying suitable gate voltage pulses of amplitude  $V_{GS}$  and width  $t_w$  as shown in Fig. 1c-d, respectively. Interestingly, multiple conducting states have been observed by varying gate voltage or write pulses from -0.4 to -3.0 V in multiple steps keeping the width  $(t_w)$  constant at 2.0 s as shown in Fig. 1c. Similarly, multi-level high-conducting (ON) states have been observed just by varying the pulse width  $t_w$  from 0.1 to 2.0 s keeping the write pulse ( $V_G$ ) amplitude constant at -3.0 V as shown in Fig. 1d. Moreover, the device shows consistent behaviour of switching back to the low-conducting (OFF) state just by applying an erase (E) voltage bias pulse + 3.0 V, 2.0 s as depicted in both the Fig. 1c-d, respectively. We also observed similar result of consistent RS property for a device fabricated later as illustrated in the Supplementary Information Fig. S2. Calculation shows a minimum energy of 3 nJ  $(E = V_{GS} \times I_G \times t_w)$  per switching event considering input pulse – 3.0 V, 0.1 s and gate current 10 nA. Furthermore, this value can be reduced further by optimizing all parameters of energy consumption that is necessary to artificially emulate energy efficient synaptic plasticity as observed in a brain<sup>3</sup>.

Transfer characteristics for the drain voltages ( $V_{\rm DS}$ ) starting from – 0.5 to – 2.0 V in step of – 250 mV have also been recorded and it has been found that the value of  $V_{\rm DS}$  has negligible influence as shown in Supplementary Information Fig. S3a. As such, threshold voltage ( $V_{\rm TH}$ ) was calculated at  $V_{\rm DS}$  = – 0.5 V and was found to be – 1.87 V (Supplementary Information Fig. S3b)<sup>26</sup>. Here, the observed hysteresis loop area of the transfer curve is crucial to show memory or RS property and is the signature of redox-reactions occurred between the dissociated ethyl viologen (EV<sup>2+</sup>) ions in the dielectric layer and P3HT monomer unit of the polymeric backbone in the active channel<sup>29</sup>. Principally, EV<sup>2+</sup> is reduced to EV<sup>+</sup> by accepting an electron and P3HT is oxidized to P3HT<sup>+</sup> (polaron) by releasing an electron under a suitable negative voltage bias at gate following the chemical equations below<sup>31</sup>.

$$P3HT + EV^{+2} \rightleftharpoons P3HT^+ + EV^+,$$

$$EV(ClO_4)_2 \rightleftharpoons EV^{+2} + 2 \cdot ClO_4^-.$$

The minimum potential required for this coupled redox-reaction is found to be about 0.97 V assuming no ohmic losses and considering standard electrode potential (E<sup>0</sup>) values of + 0.52 V ( $P3HT \rightarrow P3HT^+$ ) and – 0.45 V ( $EV^{+2} \rightarrow EV^+$ ) vs. NHE, respectively<sup>32</sup>. Therefore, the devices need at least – 1.0 V applied to the gate to initiate the redox reaction considering unavoidable ohmic losses for RS based memory application and projected

**Figure 1.** (a) Schematic diagram of the redox-electrolyte gated thin-film memtransistor (memT) including the details of the pulse and sweep measurement protocol. (b) Schematic representation of the voltage pulses at the gate terminal and DC voltage sweep across source-drain (S-D) contacts to measure the channel conductivity of the fabricated 3-terminal memT devices. (c, d) Show multiple discrete conducting states of the device channel measured after applying different voltage pulse amplitudes ( $V_{\rm GS}$ ) and widths ( $t_{\rm w}$ ), respectively.

neuromorphic device functionalities. Moreover, the subthreshold swing (S) as low as 120 mV/dec was routinely obtained as shown in the inset of Supplementary Information Fig. S3b, which is equal or indeed much smaller S than the similar devices reported previously<sup>26,33</sup>. Notably, this low value of S indicates that our memT devices are suitable for low-power circuit design of artificial synaptic plasticity and neural functionalities<sup>30</sup>.

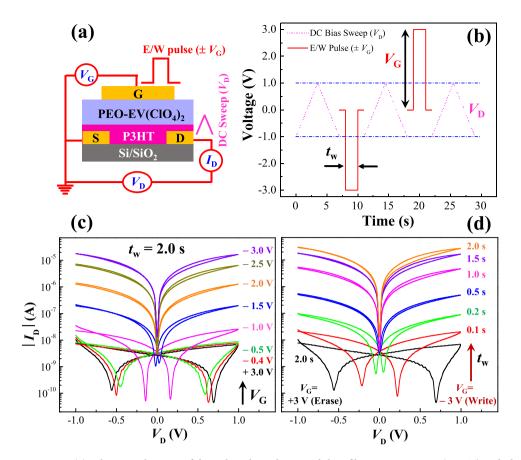

Modulation of synaptic weight by varying training pulse numbers. For any biological neural action, the delay time required to reach the OFF conducting or baseline state after the excitatory postsynaptic current (EPSC) facilitation is crucial to classify the synaptic weight changes in terms of the short-term (STP) or long-term (LTP) potentiation. Fig. 2a represents the testing setup to study the effect of consecutive presynaptic spike numbers on EPSC potentiation and related relaxation time. The consecutive – 3.0 V, 2 s presynaptic pulses were programmed to appear at the gate terminal and the corresponding postsynaptic current at the drain was recorded by applying a voltage bias – 0.5 V until the OFF-conducting state was reached. As illustrated in Fig. 2b, the EPSC responses were monitored temporally by applying 1 to 25 consecutive presynaptic pulses at the gate in open circuit condition (relay-based isolation) to observe the neural decay. We found that the retention for single and dual pulses are of the order of 200 ms which increased further with the applied pulse numbers by following a power law ( $t_R = Ax^B$ ) as illustrated in Fig. 2c. Retention or relaxation time is estimated by the time required for the EPSC response after applying the pulses to reach the current value ~ 1.0 nA through natural decay. Clearly, the result shows that there is at least sixfold enhancement in the retention time as the number of incoming pulses increases from 1 to 25. Interestingly, these results clearly resemble the synaptic plasticity observed in brain that shows the strengthening of synaptic connectivity with the increase of propagation of action potential spikes. Moreover, this response is reflected as the facilitation of memory level, which can be retained for a longer time through training and rehearsal. This is almost similar to the structural model of human brain proposed in 1968 by Atkinson and Shiffrin<sup>34</sup>. Particularly, the model classifies memorization into three separate variants—the sensory register (SR), short-term store, and long-term store. First, the incoming information is stored in the SR for a short while, then it decays, and eventually it is either completely lost or it is transmitted to the short-term store. However, the retention of SR can be improved upon rehearsal and subsequent transformation to short-term store. Then, the information can be transmitted to the long-term store, which can last for few minutes lifetime

**Figure 2.** (a) Schematic diagram of the *mem*T devices to study EPSC potentiation and retention by varying presynaptic voltage pulse numbers up to 25 pulses. (b) Potentiation and retention of EPSC result with increasing number of consecutive presynaptic pulses (– 3.0 V, 2 s) at the gate. (c) Dependency of the relaxation time in terms of natural decay of EPSC in open circuit mode to the off-conducting state on number of consecutive pulses applied at the gate.

based on the duration of the rehearsal as observed here for our *mem*T device<sup>34</sup>. Retention around 100 s can be classified as the short-term memory (STM) and higher values of retention represent the long-term memory (LTM).

Influence of the training voltage pulse anatomy on the synaptic weight change. The temporal retention in the order of  $10^3$ - $10^8$  s has been proposed as one of the highly desired metrics for organic neuromorphic devices<sup>7</sup>. Therefore, investigations to visualize the temporal retention varying pulse anatomy and repetition (rehearsal) were performed which would be useful further for classifying memorization process in a brain. Hence, we have varied presynaptic pulse number (N), width  $(t_w)$ , and amplitude ( $V_{GS}$ ) and simultaneously measured postsynaptic currents for longer time as shown in the Supplementary Information Fig. S4a-c, respectively. Repeated rehearsals using voltage pulse – 3.0 V, 50 ms result in huge variation in retention by increasing number of pulses. We found that the retention time depends much stronger on the number of the applied pulses rather than on the pulse amplitude and width. These results are in strong agreement with our previous reports on the retention times of high-conducting states in memTs<sup>29,31,35</sup>. However, a minimal amplitude of the presynaptic voltage pulse is necessary to see the prominent potentiation as we observed in a separate test with 50 consecutive spikes and varying amplitude as illustrated in the Supplementary Information Fig. S5. Now, the EPSC response of up to 60 s is considered as a reference value to classify the information storage and processing steps in our synaptic memT device. Typically, EPSC responses below 1 nA are considered as the sensory memory (SM), 1 to 10 nA as STM, and above 10 nA as LTM. Interestingly, rehearsal with 200 pulses results in LTM with estimated retention to be about 85 days ( $\approx 3 \times 10^6$  s) by extrapolating to the EPSC value of 1 nA<sup>7</sup>. Here, all three basic information storage and processing steps, namely SM, STM, and LTM, have successfully been demonstrated as illustrated in the Supplementary Information Fig. S4a<sup>36</sup>. We also observed the similar response in our device just varying number of pulses increasing from 1 to 100 i.e. gradual transformation of synaptic weight from SM to STM and finally to LTM as depicted in the Supplementary Information Fig. S6. Here, STM and LTM are used frequently in neuroscience and represent the same quantities as STP and LTP, respectively in psychology.

Availability of at least 100 discrete states is also one of the recommended projection to design efficient organic neuromorphic devices<sup>7</sup>. Consequently, the fabricated *mem*T devices were characterized for resistive random-access memory (ReRAM) applications and we found consistent two-level and multi-level results as shown in the Supplementary Information Fig. S7. Therefore, these *mem*T devices could be investigated further to induce large number of discrete conducting states by varying input voltage pulse parameters at the presynaptic terminal.

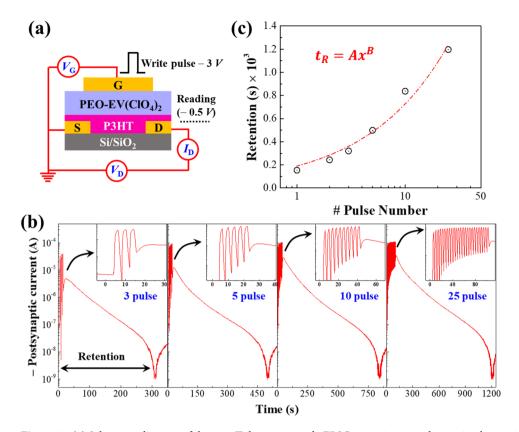

**Figure 3.** (a) Presynaptic pulse width  $(t_w)$  dependent variation of the EPSC response to demonstrate spikewidth-dependent plasticity (SWDP). 25 write pulses (-3.0 V) followed by 25 erase pulses (+3.0 V) were consecutively applied at the gate by varying  $t_w$  from 50 to 2000 ms. Insets, enlarged portion of the obtained curves to show the potentiation of EPSC for each of the incoming pulses. (b) Variation of the synaptic potentiation ratio (SPR) calculated from the two consecutive write (W) pulses for every pulse widths as obtained in (a). (c) Dependency of the sequential paired-pulse facilitation (SPPF) of synaptic weight on pulse widths and numbers as estimated from the results shown in (a).

Hence, the EPSC response was recorded at the drain of our biomimetic synaptic memT device by varying presynaptic pulse width from 50 to 2000 ms as shown in Fig. 3a keeping amplitude constant. In this test, 25 consecutive write pulses (-3.0 V) followed by 25 erase pulses (+3.0 V) were applied at the presynaptic gate terminal for each cases. Results show that the potentiation of EPSC response of our memT device becomes more and more prominent by increasing the width of presynaptic pulses. This is similar to the memorization process through rehearsing many times with longer incoming signals in a brain. In addition, it can also be termed as spike-width-dependent plasticity (SWDP) of an artificial synapse. However, the depression of the synaptic weight here looks very quick upon applying 25 erase pulses and it appears to be almost similar for all measurements in Fig. 3a. Hence, this happens due to the testing protocol in closed circuit configuration as described in the experimental details.

Furthermore, the EPSC response shows an incremental enhancement for every presynaptic pulse that appeared at the gate as highlighted in the insets of all sub-panel of Fig. 3a. This is further investigated through a surface plot by considering both the pulse widths ( $t_w$ ) and numbers (N) as an independent variable to depict the respective synaptic potentiation ratio (SPR) as shown in Fig. 3b. Here, the SPR is estimated by taking the ratio of postsynaptic high-conducting state for a presynaptic pulse to the premeditated low-conducting state. This result strongly suggests that any point on the surface plot can have the SPR values of up to  $\sim 10^2$  just by

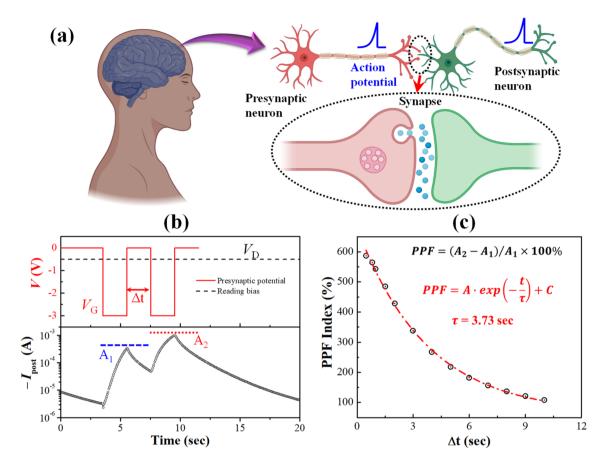

**Figure 4.** (a) Schematic representation of neural connectivity via synapse in a biological brain for the action potential transmission. (b) Short-term potentiation by applying a pair of presynaptic spikes ( $V_{GS} = -3.0 \text{ V}$ ) with Δt of 2 s. Postsynaptic currents ( $I_{post}$ ) were recorded by biasing the drain at -0.5 V. (c) Paired pulse facilitation (PPF) of the synaptic *mem*T devices obtained by varying the time interval Δt from 100 to 10 s.

selecting a pair of values of presynaptic pulses ( $t_w$ , N). It is very significant and resembles the availability of very large number (> 100) of discrete conducting states. In fact, the pulse width and number can be correlated with the stability of incoming information and rehearsal phenomena in a biological brain. This clearly resembles that a stable presynaptic signal initially shows more prominent SPR value i.e., potentiation of synaptic connection or weight and then gradually decreases with further increasing the rehearsal, which is almost similar to the mental fatigue in brain  $^{37,38}$ . Another quantity similar to paired-pulse facilitation (PPF) is also estimated considering the change in EPSC response for two consecutive pulses in the entire set of 25 pulses as shown in Fig. 3c. This quantity is termed as the sequential paired-pulse facilitation (SPPF) and can be found using the following equation  $SPPF\% = ((S_N - S_{N-1})/S_{N-1}) \times 100\%$ , where  $S_{N-1}$  and  $S_N$  represent two consecutive EPSC signals. The obtained results show that the SPPF% can also be varied up to about  $10^3$ . It also emphasizes that a strong facilitation can be observed for fewer rehearsal events and very strong fatigue is observed when rehearsal increases with more incoming signals. Our perception here is that the attained results and corresponding analysis strongly resemble the potentiation of synaptic weight with a very large number of discrete states as it happens in a biological nervous system after receiving various input signals  $^{37,39}$ .

Paired pulse facilitation of synaptic weight and memorization in the brain. In neurons, STM and paired pulse facilitation (PPF) play a very crucial role for any sub-threshold potentiation or strengthening of synaptic weight and these functions are validated in our redox-gated organic *mem*T devices as demonstrated schematically in Fig. 4a. In this testing, two consecutive presynaptic spikes (-3.0 V, 2 s) with a time gap of  $\Delta t$  are applied at the gate and corresponding EPSC responses were measured at the drain by applying a small voltage bias of -0.5 V as shown in the top and bottom panels of Fig. 4b, respectively. As a result, EPSC value for the first spike facilitated to a certain peak value of  $A_1$  and this clearly resembles the strengthening of biological synaptic weight. When a second presynaptic spike appears after a time interval of  $\Delta t$ , the EPSC increases further and reaches to a higher value,  $A_2$ . This is commonly known as paired-pulse facilitation (PPF) of a biological nervous system, which solely depends on the time delay ( $\Delta t$ ) between the applied input pulses. Moreover, this is normally demonstrated by calculating the PPF index [=  $(A_2 - A_1)/A_1 \times 100\%$ ] by varying  $\Delta t$  as shown in Fig. 4c. Significantly, the PPF index result exhibits an excellent fitting with a popular function, called modified Kohlrausch formula [ $PPF = A \cdot exp(-\frac{t}{\tau}) + C$ ], which is well accepted in psychology to manifest one of the de-memorising functions in brain  $\frac{t}{t}$

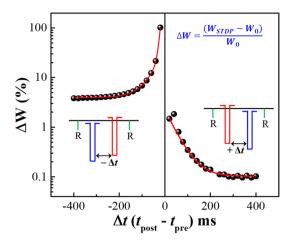

**Figure 5.** Synaptic weight changes estimated STDP ( $\Delta$ W %) for both of negative and positive time delays ( $\pm \Delta t$ ) with a postsynaptic read (-2.0 V, 10 ms) pulse before and after paired pulse propagation. Insets, schematic representation of temporally correlated presynaptic (-3.0 V, 2 s) and postsynaptic (-3.0 V, 2 s) pulses for both the time delay of  $\pm \Delta t$  to probe STDP responses.

Spiking-timing-dependent plasticity and learning behavior. Hebbian learning rule (HLR) is a very basic learning rule to train neural networks but it is very important in validating the performance of artificial electronic synaptic devices. Normally, the most common practice to implement HLR for artificial synapses is to demonstrate the spike-timing-dependent plasticity (STDP). Practically, STDP represents the change in synaptic weight  $\Delta W$  by varying the time delay  $\Delta t$  between the presynaptic and postsynaptic pulses. If presynaptic pulse stimulates momentarily before a postsynaptic pulse,  $\Delta t$  is considered as positive and  $\Delta W$  is also positive, but if a postsynaptic pulse is followed by a presynaptic pulse,  $\Delta t$  is negative and  $\Delta W$  can be either positive or negative  $^{11,42}$ . Insets of Fig. 5 show the pulses scheme with negative and positive time delay  $(+ \Delta t)$  including the postsynaptic read voltage bias pulses appeared before and after the temporally correlated pulse pair at the pre- and post-neural terminal. In this test, a voltage pulse of – 3.0 V, 2 s is used for both the pre and postsynaptic signal to measure the change in synaptic weight ( $\Delta W$ ) and a voltage pulse of -2.0 V, 10 ms is used to record the EPSC values before  $(W_0)$  and after  $(W_{STDP})$  the pair-pulse transmission event. Then the  $\Delta W\%$  for a  $\Delta t$  value is calculated with the help of equation  $\Delta W = (W_{STDP} - W_0)/W_0$  multiplied by 100 only<sup>3</sup>. Finally, changes of  $\Delta W$  % by varying  $\Delta t$ between ± 400 ms were measured and plotted as shown in Fig. 5, which agreeably follows the Hebbian learning rule<sup>43</sup>. Since the synaptic weight change by varying  $\Delta t$  can be fitted with exponential decay functions, it confirms that the STDP behaviour similar to a biological synapse can be achieved with higher efficacy using redox-gated organic memtransistor (memT) devices<sup>44,45</sup>.

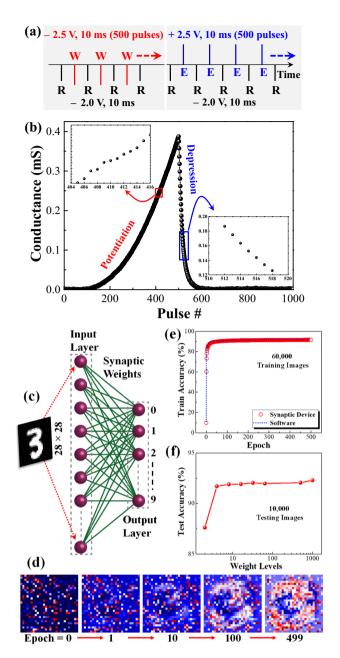

Achieving almost analogous states during potentiation and depression. In brain, neurons and synapses are the crucial components for perception and consequent thought<sup>46</sup>. Normally, neurons are stimulated by external stimuli and produce action potentials, which propagate to the connecting neurons through the synaptic cleft which result in a change in the strength of connection (synaptic weight). This change in synaptic weight could be either excitatory or inhibitory. To establish if our redox-gated organic memT devices posses this functionality, EPSC and inhibitory postsynaptic current (IPSC) response were recorded by applying 500 consecutive presynaptic pulses of -2.5 V, 10 ms and +2.5 V, 10 ms, respectively as illustrated with a scheme shown in Fig. 6a. Here, a postsynaptic voltage pulse – 2.0 V, 10 ms was used after every incoming input pulses at the gate to probe the incremental potentiation (P) and depression (D) in terms of EPSC and IPSC response as depicted in Fig. 6b. As shown in Table 1, our organic mem Ts display similar performance when compared with the previously reported devices using various electrolytes as the gate dielectric. The result obtained here is almost similar to the learning experience in psychology by the sequentially administered presynaptic excitatory rehearsal with voltage pulses. Similarly, consecutive inhibitory pulses at presynaptic terminal can cause weakening of the synaptic weights that is reflected as loss of memory or depression as evidenced in psychological forgetting. This potentiation and depression result is obtained in our redox-gated memT-based artificial synapse just by consuming energy of 250 pJ per input spike which is definitely a remarkable achievement as this is indeed very close to the desired and recommended metrics for artificial organic synaptic devices7. Moreover, this result clearly evidences the capability of our memT devices to continuously modulate the channel conductance to more than 500 discrete conducting states during potentiation and depression which is also much higher than the prerequisite to effectively mimic a synapse and very useful to demonstrate neural network based pattern recognition<sup>7</sup>.

**Efficient pattern recognition using artificial neural network simulation.** In order to evaluate the pattern recognition capabilities of the proposed synaptic *memT* devices for neuromorphic hardware implementation, we have simulated a single layer artificial neural network (ANN) without any hidden layers using the normalized conductance values (weights) extracted from the recorded potentiation/depression curve of our

**Figure 6.** (a) Pulsing scheme to demonstrate the excitatory postsynaptic current (EPSC) and inhibitory postsynaptic current (IPSC) response based potentiation (P) and depression (D) of synaptic weight by applying 500 consecutive write (W) pulses (– 2.5 V, 10 ms) and erase (E) pulses (+ 2.5 V, 10 ms), respectively. A read pulse (– 2.0 V, 10 ms) is used to record synaptic weight change after every set of W/E pulses. (b) Potentiation and depression curve of synaptic weight change. Insets illustrate enlarged marked areas to visualize discrete conducting states during potentiation and depression. (c) Schematic of a single layer neural network used for MNIST pattern recognition. (d) Selected weight evolution mapping images from the output neurons layer corresponding to class "3" at different epochs starting from 0 to 499. (e) Training accuracy (%) vs number of epochs for both software and actual synaptic device based weight distribution. (d) Test accuracy (%) variation with the number or strength of device weight levels.

synaptic device in Fig.  $6b^{53,54}$ . All the simulations were performed using PyTorch package and the detail simulation protocols are demonstrated in the Supplementary Information (Section H)<sup>55</sup>. The well-known Modified National Institute of Standards and Technology (MNIST) dataset is used here for the image recognition  $task^{56}$ . Each of the  $(28 \times 28)$  pixel images are linearized to form a  $(784 \times 1)$  input matrix where each of the pixel values are connected to a neuron in the input layer of the neural network as illustrated with schematic in Fig. 6c. Hence, our simulated neural network has 784 input neurons, number of pixels per label number, and 10 output neurons corresponding to the 10 output classes in the MNIST dataset. We have considered the mean cross entropy loss

| Channel*                    | Electrolyte* (Phase)                             | Operation voltage (V) | Energy/SA (pJ) | ON/OFF ratio    | Analog states |

|-----------------------------|--------------------------------------------------|-----------------------|----------------|-----------------|---------------|

| P3HT <sup>47</sup>          | [EMIM][TFSA] + P(VDF-TrFE)<br>(Solid)            | 7.0                   |                |                 |               |

| P3HT <sup>48</sup>          | [EMIM][TFSA] + P(VDF-HFP)<br>(Solid)             | 3.0                   |                |                 |               |

| P3HT <sup>49</sup>          | [EMIM][TFSA] + P(VDF-HFP)<br>(Gel)               | 5.0                   | 510            |                 |               |

| PTIIG-Np <sup>50</sup>      | [EMIM][TFSI] + PS-PMMA-PS<br>(Gel)               | 2.5                   |                |                 |               |

| PEDOT:PTHF <sup>51</sup>    | KCl in DI water (Liquid)                         | 1.0                   |                |                 |               |

| PEDOT:PSS/PEI <sup>11</sup> | Aqueous NaCl (Liquid)                            | 1.0                   | 10             |                 | ~ 500         |

| P3HT <sup>52</sup>          | PEO/RbAg <sub>4</sub> I <sub>5</sub> (Solid)     | 2.0                   | 2              |                 | ~ 2000        |

| P3HT (This work)            | EV(ClO <sub>4</sub> ) <sub>2</sub> + PEO (Solid) | 1.5                   | 250            | 10 <sup>5</sup> | > 500         |

**Table 1.** Performance comparison of the fabricated *mem*Ts with previously reported memory devices using electrolytes as the gate dielectric. \*[EMI][TFSA/I] → 1-Ethyl-3-methylimidazolium bis(trifluoromethylsulfonyl) amide/imide, P(VDF-TrFE) → poly(vinylidene fluoride-co-trifluoroethylene), P(VDF-HFP) → poly(vinylidene fluoride-co-hexafluoropropylene), PTIIG-Np → poly(thienoisoindigo-alt-naphthalene), PMMA → polymethyl methacrylate, PS → polystyrene, PEDOT:PTHF → poly(3,4-ethylenedioxythiophene):poly(tetrahydrofuran), KCl → potassium chloride, NaCl → sodium chloride, PSS → poly(styrenesulfonate), PEI → polyethylenimine, RbAg<sub>4</sub>I<sub>5</sub> → rubidium silver iodide.

for the error determination. The as-computed errors are then back propagated for adjusting the weight values for the next iteration. When the full set of training data are passed through the network in several batches, an epoch of training is completed. We have used 500 epochs of training for minimizing the loss function to a low and stable value. Fig. 6d shows the weight evolution images during ANN training using actual synaptic weights obtained from the proposed ST for the output neuron corresponding to digit "3"57. It is seen that as the training epochs increase, there is a clear evidence of "learning" observed for the neural network as the corresponding neuron clearly distinguishes between the target label ("3") from the other digits. Once the training process is completed, we use the test data to compute the pattern recognition accuracy of the network. The entire process (training and testing) has been repeated 5 times for ensuring the reproducibility of the reported data and hence each data point is the mean value for 5 repetitions of the process. In Fig. 6e, we report the training accuracy and mean loss (Supplementary Information Fig. S8) as a function of the number of epochs for both software and synaptic device-based weight distributions. It is clearly observed that the device based (test accuracy = 92.30%) neural network performs similar to the purely software-based (test accuracy = 92.53%) ANN model. This reveals that our synaptic device is highly suited for neuromorphic hardware implementations. Such a high test accuracy for the device based ANN model might be due to the large number of conductance states or weights available for the network training. Further, we have investigated the variation in ANN test accuracy with respect to the weight levels available from the device. This is particularly important from a hardware realization perspective, since many of the conductance levels of the device may not be accessible or stable for cross-bar array implementation. Hence, the performance of the ANN model with the reduced weight levels needs to be studied carefully. From Fig. 6f, we see that the test accuracy for the device is almost constant until about 8 weight levels, below which there is only a marginal drop in test accuracy. This is indicative of the highly robust nature of weight values available from our proposed synaptic transistor for ANN training applications.

#### Conclusions

In conclusion, organic memtransistors (memT) that can efficiently mimic the synaptic functionalities as observed in a biological brain are demonstrated. A single memT can serve as a data storage device, as well as as an artificial synapse with various synaptic plasticities, including the EPSC, STP, LTP, PPF, and STDP. The proposed memTs can also exhibit huge variation in synaptic weight just by tuning the anatomy of incoming presynaptic pulses and increasing rehearsal. In particular, retention of an ON-state is enhanced from  $10^3$  to  $10^6$  just by increasing repetition or rehearsal from 25 to 200 times even though the pulse width decreased 40 times. Moreover, the presented redox-gated memTs also performed superiorly as TFTs with ON/OFF current ratios larger than  $10^8$ , subthreshold swings around 120 mV/dec, and operating voltage  $V_G < -1.5$  V. In addition, it was estimated that the energy consumption is as low as 250 pJ per synaptic event that is a significant achievement to mimic synaptic plasticity in a single organic memT device. The energy consumption can be reduced further just by improving the response speed, reducing the input redox-current, and decreasing the threshold voltage as large varieties of organic semiconducting materials are available. Moreover, the ANN simulation result further confirms that our synaptic device performs extremely well for realistic pattern recognition task with a high level of accuracy and reproducibility.

#### Methods

**Device fabrication.** Redox-gated thin-film transistors were fabricated on the Si/SiO<sub>2</sub> substrates in a bottom-contact top-gated configuration. The detailed fabrication procedure can be found in reference 25. Briefly, Ti/Au (5/50 nm) source (S) and drain (D) electrodes were formed on the substrates using the standard pho-

tolithography and lift-off process. Then, hexamethyldisilazane (HMDS) and 5 mg/ml poly(3-hexylthiophene-2,5-diyl) (P3HT) solutions were spin-coated on the substrates and annealed at 96  $^{\circ}$ C and 140  $^{\circ}$ C, respectively. Then, the electrolyte was prepared by mixing equal weight of 4 wt% EV(ClO<sub>4</sub>)<sub>2</sub> and 5 wt% PEO in acetonitrile and dropcasted in between the S/D electrodes. Finally, 50 nm thick gold (Au) electrode was deposited on top of the electrolyte drop as the top gate contact to complete the fabrication process.

**Electrical characterizations of memTs.** Electrical measurements were performed either with a Keithley 4200-SCS parameter analyzer or by combining it with a Keithley 2602B source measurement unit (SMU). Standard transistor characterizations were performed using Keithley 4200. For DC sweep and pulse based memory measurements, a DC sweep voltage was applied between source (S) and drain (D) in dual sweep mode and corresponding drain current ( $I_{\rm D}$ ) was measured with the 2602B keeping gate (G) terminal open for initial OFF-conducting state. Then a write pulse voltage ( $V_{\rm G}$ ) of width ( $t_{\rm w}$ ) was applied at the gate using Keithley 4200 to switch the channel conductivity to the ON state and that was probed by measuring drain current similar to the initial I-V recording with Keithley 2602B SMU. To switch back the channel conductivity to the OFF state, an erase voltage pulse was applied to the gate followed by DC I-V measurement for probing. This measurement protocol is clearly demonstrated with the results using schematic diagram of device connections and sweep-pulse sequences, as shown in Fig. 1.

Random access memory (RAM) measurements. The drain current ( $I_{\rm D}$ ) was monitored continuously by applying a drain bias voltage – 0.5 V using 2602B SMU. And the ON and OFF states were induced by applying a write (W) pulse – 3.0 V, 2 s and a erase (E) pulse of + 3.0 V, 5 s, respectively, with 5 s wait time between them using a Keithley 4200-SCS. This W/E cycle was repeated for 10 times and corresponding drain current response was recorded as the resistive RAM application test. During the wait time of gate voltage pulses, the gate terminal was kept open or in the floating mode with the help of electrical relay. The schematic diagram of the device connections for performing RAM and the corresponding output is shown in the Supplemental Information Fig. S7.

**Electrical characterizations for synaptic plasticity.** Drain current ( $I_D$ ) or postsynaptic current (PSC) response was measured continuously by biasing the drain terminal with – 0.5 V using the 2602B SMU. 25 presynaptic square voltage pulses of – 3.0 V followed by 25 presynaptic square voltage pulses of + 3.0 V with different pulse width ( $t_w$ ) starting from 50 to 2000 ms were applied to the gate terminal using 4200-SCS to modulate the channel conductance similar to the synaptic weight or connection strength. Similar measurement protocol was followed for other synaptic tests just varying parameters as required that are explained in the "Results and discussion" section. The time gap between the two presynaptic pulses was varied from 500 ms to 10 s to extract the paired-pulse facilitation (PPF) Index. Schematic of the spike-timing-dependent plasticity (STDP) measurement scheme is demonstrated in the result and discussions section. Initial postsynaptic current response  $W_0$  was measured by applying a read voltage pulse – 2.0 V, 10 ms at the drain. Then a pair of presynaptic (– 3.0 V, 2 s) and postsynaptic (+ 3.0 V, 2 s) voltage pulses with the time delay of ±  $\Delta t$  was applied to the gate terminal followed by the final postsynaptic current response  $W_{\rm STDP}$  measurement using the same read voltage pulse. The read pulses were applied 10 ms prior to the pre- and postsynaptic pulses and 10 ms after the pre- and postsynaptic pulses to measure  $W_0$  and  $W_{\rm STDP}$  respectively.

#### Data availability

Data for the experimental and simulation results are available from the corresponding author upon request.

Received: 12 November 2021; Accepted: 14 February 2022 Published online: 09 March 2022

#### References

- 1. LeCun, Y., Bengio, Y. & Hinton, G. Deep learning. Nature 521, 436-444. https://doi.org/10.1038/nature14539 (2015).

- Feng, P. et al. Printed neuromorphic devices based on printed carbon nanotube thin-film transistors. Adv. Funct. Mater. 27, 1604447. https://doi.org/10.1002/adfm.201604447 (2017).

- Kuzum, D., Yu, S. M. & Wong, H. S. P. Synaptic electronics: Materials, devices and applications. Nanotechnology 24, 382001. https://doi.org/10.1088/0957-4484/24/38/382001 (2013).

- Schrittwieser, J. et al. Mastering Atari, Go, chess and shogi by planning with a learned model. Nature 588, 604–609. https://doi. org/10.1038/s41586-020-03051-4 (2020).

- Wan, Q. Z., Sharbati, M. T., Erickson, J. R., Du, Y. H. & Xiong, F. Emerging artificial synaptic devices for neuromorphic computing. Adv. Mater. Technol. U.S. 4, 1900037. https://doi.org/10.1002/admt.201900037 (2019).

- Yu, H. Y. et al. Evolution of bio-inspired artificial synapses: Materials, structures, and mechanisms. Small 17, 2000041. https://doi. org/10.1002/smll.202000041 (2021).

- 7. van de Burgt, Y., Melianas, A., Keene, S. T., Malliaras, G. & Salleo, A. Organic electronics for neuromorphic computing. *Nat. Electron.* 1, 386–397. https://doi.org/10.1038/s41928-018-0103-3 (2018).

- 8. Hebb, D. O. The Organization of Behavior: A Neuropsychological Theory 335 (Wiley, 1949).

- Zhu, J. D., Zhang, T., Yang, Y. C. & Huang, R. A comprehensive review on emerging artificial neuromorphic devices. Appl. Phys. Rev. 7, 011312. https://doi.org/10.1063/1.5118217 (2020).

- Korte, M. & Schmitz, D. Cellular and system biology of memory: Timing, molecules, and beyond. *Physiol. Rev.* 96, 647–693. https://doi.org/10.1152/physrev.00010.2015 (2016).

- 11. van de Burgt, Y. et al. A non-volatile organic electrochemical device as a low-voltage artificial synapse for neuromorphic computing. Nat. Mater. 16, 414–418. https://doi.org/10.1038/Nmat4856 (2017).

- 12. Strukov, D. B., Snider, G. S., Stewart, D. R. & Williams, R. S. The missing memristor found. *Nature* 453, 80–83. https://doi.org/10.1038/nature06932 (2008).

- 13. Kuzum, D., Jeyasingh, R. G. D., Lee, B. & Wong, H. S. P. Nanoelectronic programmable synapses based on phase change materials for brain-inspired computing. *Nano Lett.* 12, 2179–2186. https://doi.org/10.1021/nl201040y (2012).

- 14. Meladom, S. K., Arackal, S., Sreedharan, A., Sagar, S. & Das, B. C. Microwave assisted robust aqueous synthesis of Mn2+-doped CdSe QDs with enhanced electronic properties. RSC Adv. 8, 26771–26781. https://doi.org/10.1039/c8ra03631d (2018).

- 15. Choi, S. *et al.* SiGe epitaxial memory for neuromorphic computing with reproducible high performance based on engineered dislocations. *Nat. Mater.* 17, 335–340. https://doi.org/10.1038/s41563-017-0001-5 (2018).

- Majumdar, S., Tan, H. W., Qin, Q. H. & van Dijken, S. Energy-efficient organic ferroelectric tunnel junction memristors for neuromorphic computing. Adv. Electron. Mater. 5, 1800795. https://doi.org/10.1002/aelm.201800795 (2019).

- 17. Srinivasan, G., Sengupta, A. & Roy, K. Magnetic tunnel junction based long-term short-term stochastic synapse for a spiking neural network with on-chip STDP learning. Sci. Rep. U.K. 6, 29545. https://doi.org/10.1038/srep29545 (2016).

- Liu, G. et al. Organic biomimicking memristor for information storage and processing applications. Adv. Electron. Mater. 2, 1500298. https://doi.org/10.1002/aelm.201500298 (2016).

- Valov, I. et al. Atomically controlled electrochemical nucleation at superionic solid electrolyte surfaces. Nat. Mater. 11, 530–535. https://doi.org/10.1038/Nmat3307 (2012).

- Schneider, M. L., Donnelly, C. A. & Russek, S. E. Tutorial: High-speed low-power neuromorphic systems based on magnetic Josephson junctions. J. Appl. Phys. 124, 161102. https://doi.org/10.1063/1.5042425 (2018).

- Hasegawa, T., Terabe, K., Tsuruoka, T. & Aono, M. Atomic switch: Atom/ion movement controlled devices for beyond Von-Neumann computers. Adv. Mater. 24, 252–267. https://doi.org/10.1002/adma.201102597 (2012).

- 22. Manamel, L. T., Madam, S. C., Sagar, S. & Das, B. C. Electroforming-free nonvolatile resistive switching of redox-exfoliated MoS<sub>2</sub> nanoflakes loaded polystyrene thin film with synaptic functionality. *Nanotechnology* **32**, 35LT02. https://doi.org/10.1088/1361-6528/ac056e (2021).

- Tian, B. B. et al. A Robust artificial synapse based on organic ferroelectric polymer. Adv. Electron. Mater. 5, 1800600. https://doi. org/10.1002/aelm.201800600 (2019).

- Ziegler, M. & Kohlstedt, H. Mimic synaptic behavior with a single floating gate transistor: A MemFlash synapse. J. Appl. Phys. 114, 194506. https://doi.org/10.1063/1.4832334 (2013).

- Lai, Q. X. et al. Ionic/electronic hybrid materials integrated in a synaptic transistor with signal processing and learning functions. Adv. Mater. 22, 2448–2453. https://doi.org/10.1002/adma.201000282 (2010).

- Sagar, S., Dey, A. & Das, B. C. Unconventional redox-active gate dielectrics to fabricate high performance organic thin-film transistors. ACS Appl. Electron. Mater. 1, 2314–2324. https://doi.org/10.1021/acsaelm.9b00522 (2019).

- Khodagholy, D. et al. High transconductance organic electrochemical transistors. Nat. Commun. 4, 2133. https://doi.org/10.1038/ncomms3133 (2013).

- 28. Rivnay, J. et al. Organic electrochemical transistors. Nat. Rev. Mater. 3, 17086. https://doi.org/10.1038/natrevmats.2017.86 (2018).

- 29. Das, B. C., Pillai, R. G., Wu, Y. L. & McCreery, R. L. Redox-gated three-terminal organic memory devices: Effect of composition and environment on performance. ACS Appl. Mater. Interface 5, 11052–11058. https://doi.org/10.1021/am4032828 (2013).

- 30. Zheng, C. Y., Liao, Y., Xiong, Z. Y., Zhou, Y. & Han, S. T. Mimicking the competitive and cooperative behaviors with multi-terminal synaptic memtransistors. *J. Mater. Chem. C* 8, 6063–6071. https://doi.org/10.1039/d0tc01076f (2020).

- 31. Kumar, R., Pillai, R. G., Pekas, N., Wu, Y. L. & McCreery, R. L. Spatially resolved raman spectroelectrochemistry of solid-state polythiophene/viologen memory devices. *J. Am. Chem. Soc.* **134**, 14869–14876. https://doi.org/10.1021/ja304458s (2012).

- Gasiorowski, J., Mardare, A. I., Sariciftci, N. S. & Hassel, A. W. Electrochemical characterization of sub-micro-gram amounts of organic semiconductors using scanning droplet cell microscopy. J. Electroanal. Chem. 691, 77–82. https://doi.org/10.1016/j.jelec hem.2012.11.008 (2013).

- 33. Panzer, M. J., Newman, C. R. & Frisbie, C. D. Low-voltage operation of a pentacene field-effect transistor with a polymer electrolyte gate dielectric. *Appl. Phys. Lett.* **86**, 103503. https://doi.org/10.1063/1.1880434 (2005).

- 34. Spence, K. W. & Spence, J. T. (eds) Psychology of Learning and Motivation Vol. 2, 89-195 (Academic Press, 1968).

- Das, B. C., Szeto, B., James, D. D., Wu, Y. L. & McCreery, R. L. Ion transport and switching speed in redox-gated 3-terminal organic memory devices. J. Electrochem. Soc. 161, H831–H838. https://doi.org/10.1149/2.0831412jes (2014).

- Zucker, R. S. & Regehr, W. G. Short-term synaptic plasticity. Annu. Rev. Physiol. 64, 355–405. https://doi.org/10.1146/annurev. physiol.64.092501.114547 (2002).

- Ohno, T. et al. Short-term plasticity and long-term potentiation mimicked in single inorganic synapses. Nat. Mater. 10, 591–595. https://doi.org/10.1038/Nmat3054 (2011).

- 38. Qi, P. et al. Neural mechanisms of mental fatigue revisited: New insights from the brain connectome. Engineering 5, 276–286. https://doi.org/10.1016/j.eng.2018.11.025 (2019).

- 39. Martin, S. J., Grimwood, P. D. & Morris, R. G. M. Synaptic plasticity and memory: An evaluation of the hypothesis. *Annu. Rev. Neurosci.* 23, 649–711. https://doi.org/10.1146/annurev.neuro.23.1.649 (2000).

- 40. Yan, X. B. *et al.* Flexible transparent organic artificial synapse based on the tungsten/egg albumen/indium tin oxide/polyethylene terephthalate memristor. *ACS Appl. Mater. Interface* **11**, 18654–18661. https://doi.org/10.1021/acsami.9b04443 (2019).

- 41. Zamarreno-Ramos, C. et al. On spike-timing-dependent-plasticity, memristive devices, and building a self-learning visual cortex. Front. Neurosci. Switz. 5, 26. https://doi.org/10.3389/fnins.2011.00026 (2011).

- 42. Kim, S. G., Han, J. S., Kim, H., Kim, S. Y. & Jang, H. W. Recent advances in memristive materials for artificial synapses. *Adv. Mater. Technol. U.S.* 3, 1800457. https://doi.org/10.1002/admt.201800457 (2018).

- 43. Jo, S. H. et al. Nanoscale memristor device as synapse in neuromorphic systems. Nano Lett. 10, 1297–1301. https://doi.org/10.1021/nl904092h (2010).

- 44. Li, S. Z. et al. Synaptic plasticity and learning behaviours mimicked through Ag interface movement in an Ag/conducting polymer/ Ta memristive system. J. Mater. Chem. C 1, 5292–5298. https://doi.org/10.1039/c3tc30575a (2013).

- 45. Zhou, L. et al. Biological spiking synapse constructed from solution processed bimetal core-shell nanoparticle based composites. Small 14, 1800288. https://doi.org/10.1002/smll.201800288 (2018).

- 46. Abbott, L. F. & Regehr, W. G. Synaptic computation. Nature 431, 796-803. https://doi.org/10.1038/nature03010 (2004).

- Kong, L. A. et al. Long-term synaptic plasticity simulated in ionic liquid/polymer hybrid electrolyte gated organic transistors. Org. Electron. 47, 126–132. https://doi.org/10.1016/j.orgel.2017.05.017 (2017).

- 48. Qian, C. et al. Artificial synapses based on in-plane gate organic electrochemical transistors. Acs Appl. Mater. Interface 8, 26169–26175. https://doi.org/10.1021/acsami.6b08866 (2016).

- 49. Fu, Y. et al. Flexible neuromorphic architectures based on self-supported multiterminal organic transistors. Acs Appl. Mater. Interface 10, 26443–26450. https://doi.org/10.1021/acsami.8b07443 (2018).

- Seo, D. G. et al. Versatile neuromorphic electronics by modulating synaptic decay of single organic synaptic transistor: From artificial neural networks to neuro-prosthetics. Nano Energy 65, 104035. https://doi.org/10.1016/j.nanoen.2019.104035 (2019).

- 51. Gkoupidenis, P., Schaefer, N., Strakosas, X., Fairfield, J. A. & Malliaras, G. G. Synaptic plasticity functions in an organic electrochemical transistor. *Appl. Phys. Lett.* **107**, 263302. https://doi.org/10.1063/1.4938553 (2015).

- 52. Mukherjee, A., Sagar, S., Parveen, S. & Das, B. C. Superionic rubidium silver iodide gated low voltage synaptic transistor. *Appl. Phys. Lett.* **119**, 253502. https://doi.org/10.1063/5.0069478 (2021).

- Ansari, M. H., Kannan, U. M. & Cho, S. Core-shell dual-gate nanowire charge-trap memory for synaptic operations for neuromorphic applications. *Nanomaterials* 11, 1773. https://doi.org/10.3390/nano11071773 (2021).

- Ryu, J. et al. Zinc tin oxide synaptic device for neuromorphic engineering. IEEE Access 8, 130678–130686. https://doi.org/10.1109/ ACCESS.2020.3005303 (2020).

- 55. Paszke, A. et al. PyTorch: An imperative style, high-performance deep learning library. http://arXiv.org/1912.01703 (2019).

- Lecun, Y., Bottou, L., Bengio, Y. & Haffner, P. Gradient-based learning applied to document recognition. *Proc. IEEE* 86, 2278–2324. https://doi.org/10.1109/5.726791 (1998).

- 57. Kim, S. K. et al. 3D stackable synaptic transistor for 3D integrated artificial neural networks. Acs Appl. Mater. Interface 12, 7372–7380. https://doi.org/10.1021/acsami.9b22008 (2020).

#### **Acknowledgements**

This work is supported by the UGC-UKIERI Joint Research Programme (UKIERI-III) with File Number 184-15/2018(IC), the SERB project with File Number EEQ/2016/000045, and the Korean Ministry of Science and ICT (2021M3F3A2A01037927). Partial support was also received from another SERB project with File Number ECR/2017/000630. The authors would like to thank the University of Manchester for paying the article processing charge (APC).

#### **Author contributions**

B.C.D. conceived the ideas. B.C.D and S.K.S. designed the study and analysed the results, S.K.S. did the measurements and data curation, S.C. and K.U.M. formulated the ANN and did simulation task, B.C.D and S.K.S. wrote the original draft, L.A.M., S.C. and K.U.M. did the revisions, B.C.D. did the supervision of the entire work and assessed the progress. All authors have read, reviewed, and approved the final manuscript.

### Competing interests

The authors declare no competing interests.

#### Additional information

**Supplementary Information** The online version contains supplementary material available at https://doi.org/10.1038/s41598-022-07505-9.

Correspondence and requests for materials should be addressed to B.C.D.

Reprints and permissions information is available at www.nature.com/reprints.

**Publisher's note** Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

© The Author(s) 2022