# THE UNIVERSITY of EDINBURGH

This thesis has been submitted in fulfilment of the requirements for a postgraduate degree (e.g. PhD, MPhil, DClinPsychol) at the University of Edinburgh. Please note the following terms and conditions of use:

- This work is protected by copyright and other intellectual property rights, which are retained by the thesis author, unless otherwise stated.

- A copy can be downloaded for personal non-commercial research or study, without prior permission or charge.

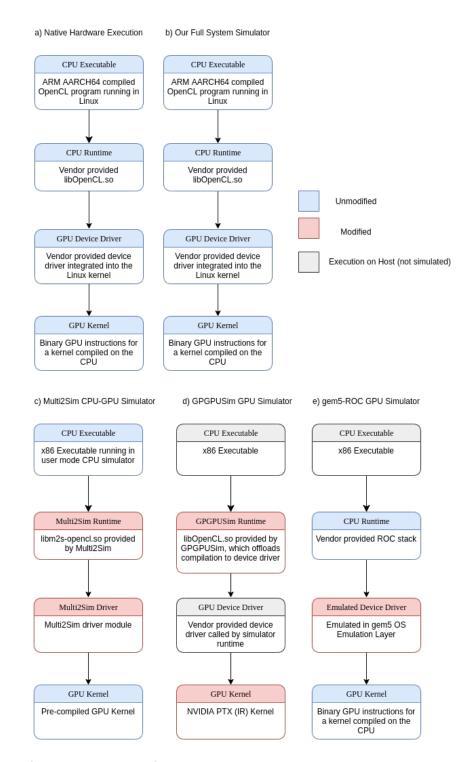

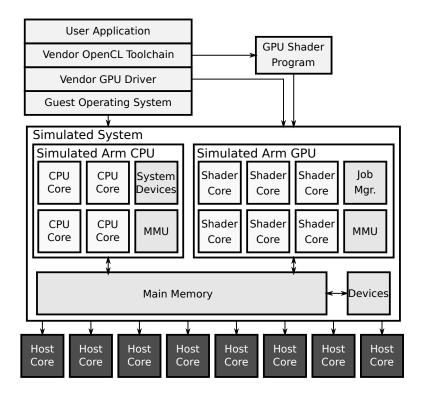

- This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the author.

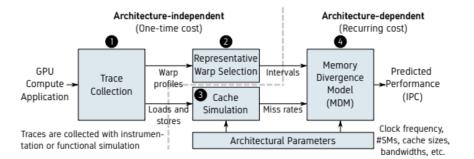

- The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the author.

- When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given.

# Simulation Methodologies for Mobile GPUs

Kuba Kaszyk

Doctor of Philosophy Institute of Computing Systems Architecture School of Informatics University of Edinburgh 2021

## Abstract

Graphics Processing Units (GPUs) critically rely on a complex system software stack comprising kernel- and user-space drivers and Just-in-time (JIT) compilers. Yet, existing GPU simulators typically abstract away details of the software stack and GPU instruction set. Partly, this is because GPU vendors rarely release sufficient information about their latest GPU products. However, this is also due to the lack of an integrated CPU/GPU simulation framework, which is complete and powerful enough to drive the complex GPU software environment. This has led to a situation where research on GPU architectures and compilers is largely based on outdated or greatly simplified architectures and software stacks, undermining the validity of the generated results. Making the situation even more dire, existing GPU simulation efforts are concentrated around desktop GPUs, making infrastructure for modelling mobile GPUs virtually non-existent, despite their surging importance in the GPU market. Still, mobile GPU designers are faced with the challenge of evaluating design alternatives involving hundreds of architectural configuration options and micro-architectural improvements under tight time-to-market constraints, to which currently employed design flows involving detailed, but slow simulations are not well suited. In this thesis we develop a full-system simulation environment for a mobile platform, which enables users to run a complete and unmodified software stack for a state-of-the-art mobile Arm CPU and Mali Bifrost GPU powered device, achieving 100% architectural accuracy across all available toolchains. We demonstrate the capability of our GPU simulation framework through a number of case studies exploring modern, mobile GPU applications, and optimize them using functional simulation statistics, unavailable with other approaches or hardware. Furthermore, we develop a trace-based performance model, allowing architects to rapidly model GPU configurations in early design space exploration.

# Lay Summary

Computers are found all around us, from large data centers, to mobile phones, TVs, cars, refrigerators, and many other places. These computers, are made up of multiple components, one of which, is a Graphics Processing Unit (GPU). GPUs are the component responsible for drawing images to your screen, however, in recent years, they have also been used to do similar tasks to the CPU. This thesis focuses primarily on mobile systems, which typically include any system that has a battery and can operate away from its main power source.

Designing new computer systems, including GPUs, is expensive and time consuming, especially if things go wrong. It's therefore critically important to model as many components as possible, before actually fabricating the chips. One of the most important modelling tools is simulation, which means that you write a program which behaves just like the hardware component that you want to model. This program can then be used to identify any problems with the design, and to predict its performance.

Just like the entire design process, simulation has its challenges. For example, GPUs operate in a complex environment, and it can be very difficult to re-create a realistic environment to simulate a GPU. The first goal of this thesis is to examine and develop techniques which would allow us to model GPUs in the exact same environment as they ultimately execute in. We achieve this by simulating not only the GPU, but the entire surrounding system.

Another challenge is simulation speed. Programs written to simulate hardware are often excruciatingly slow, as they have to model a lot of internal components, especially if you have to model the entire system, as we do when simulating GPUs. One option to speed up the simulation, is to limit the amount of detail modelled. The second goal of this thesis is to ensure that modelling the full environment that a GPU executes in does not slow the simulation down.

Reducing the level of detail is often discounted as a technique, because it limits the amount of useful information that can be obtained from the simulation. However, the final goal of this thesis is to ensure that even with the additional cost of simulating the GPU's environment, and with the loss of detail when accelerating the simulation, there is still useful performance information that can be extracted from the simulation framework. We achieve this goal by splitting the simulation into two phases - the first one collecting information, and the second analyzing it.

# **Acknowledgements**

There are a number of people I would like to thank for their support during my time as a PhD student, starting with my supervisor, Björn Franke, for getting me involved in the topic years before I started my PhD, and his irreplaceable guidance over the years. I would also like to thank my second supervisor, Mike O'Boyle, for the feedback, and many valuable discussions.

Deserving a special mention are Harry Wagstaff and Tom Spink, who laid the groundwork for my own research; Bruno Bodin, for the excitement and mentorship he brought to the project; and Chris Vasiladiotis and Calum Imrie, for their excellent company and collaboration.

Finally, I would like to thank my family, in particular my wife, Roksana, and my daughters, Julia and Sofia, for the patience and understanding they have shown me.

# **Declaration**

I declare that this thesis was composed by myself, that the work contained herein is my own except where explicitly stated otherwise in the text, and that this work has not been submitted for any other degree or professional qualification except as specified.

(Kuba Kaszyk)

# **Publications**

The following publications have been made during the course of this PhD, some of which are used as the basis for chapters:

• Kuba Kaszyk, Harry Wagstaff, Tom Spink, Björn Franke, Michael O'Boyle, Bruno Bodin, Henrik Uhrenholt

"Full-System Simulation of Mobile CPU-GPU Platforms"

In Proceedings of the 2019 IEEE International Symposium on Performance Analysis of Systems and Software (ISPASS'19), Madison, Wisconsin, February 2019

This publication forms the basis for Chapter 4.

• Valentin Radu, **Kuba Kaszyk**, Yuan Wen, Jack Turner, Josè Cano, Elliot J Crowley, Björn Franke, Amos Storkey, Michael O'Boyle

"Performance aware convolutional neural network channel pruning for embedded GPUs"

In Proceedings of the 2019 IEEE International Symposium on Workload Characterization (IISWC'19), Orlando, Florida, November 2019

This publication forms the basis for case studies presented in Chapter 4.

• Kuba Kaszyk, Björn Franke

"Full-System GPU Design Space Exploration"

Workshop on Modeling & Simulation of Systems and Applications (ModSim 2020)

This publication forms the basis of the machine-learning based approach presented in Chapter 5.

Subhankar Pal, Kuba Kaszyk, Siying Feng, Björn Franke, Murray Cole, Michael O'Boyle, Trevor Mudge, Ronald G. Dreslinski

"HETSIM: Simulating Large-Scale Heterogeneous Systems using a Trace-driven, Synchronization and Dependency-Aware Framework"

In Proceedings of the 2020 IEEE International Symposium on Workload Characterization (IISWC'20)

# Table of Contents

| 1 | Intr | oductio | 'n                                         | 1  |

|---|------|---------|--------------------------------------------|----|

|   | 1.1  | The Pa  | ast, Present, and Future of GPUs           | 1  |

|   | 1.2  | The C   | omplexities of GPU Systems                 | 4  |

|   | 1.3  | Simula  | ation as a Key Design and Development Tool | 5  |

|   | 1.4  | Motiva  | ation                                      | 7  |

|   | 1.5  | Goals   |                                            | 8  |

|   | 1.6  | Thesis  | Overview                                   | 8  |

| 2 | Bac  | kgroun  | d                                          | 11 |

|   | 2.1  | Introd  | uction                                     | 11 |

|   | 2.2  | How d   | lo we program a GPU?                       | 11 |

|   |      | 2.2.1   | The Software Stack                         | 12 |

|   |      | 2.2.2   | Low-Level Programming Frameworks           | 15 |

|   |      | 2.2.3   | High-Level Libraries                       | 21 |

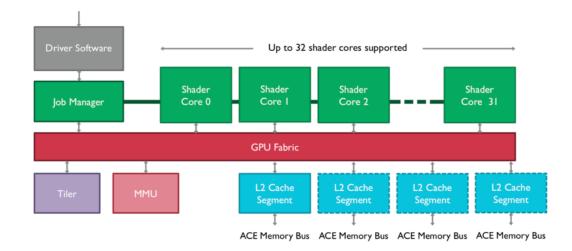

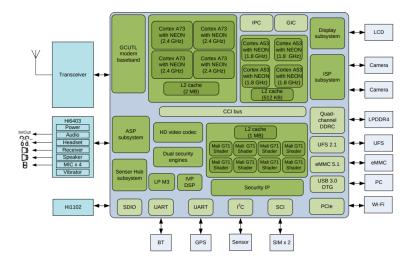

|   | 2.3  | The A   | rm Mali Bifrost Architecture               | 23 |

|   |      | 2.3.1   | Overview                                   | 24 |

|   |      | 2.3.2   | Starting a GPU Job                         | 25 |

|   |      | 2.3.3   | Interaction with the CPU                   | 25 |

|   |      | 2.3.4   | Details of the Job Manager                 | 25 |

|   |      | 2.3.5   | The Arm Mali Memory System                 | 26 |

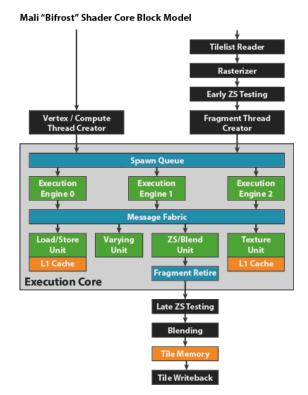

|   |      | 2.3.6   | The Bifrost Shader Core                    | 28 |

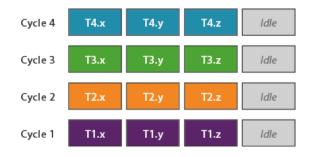

|   |      | 2.3.7   | The Clause Based Execution Model           | 29 |

|   |      | 2.3.8   | Graphics Hardware                          | 32 |

|   | 2.4  | GenSi   | m - A Head Start on Fast Simulation        | 32 |

|   |      | 2.4.1   | ArcSim                                     | 37 |

|   | 2.5      | Captiv  | re - Making the most of host hardware             | 38       |

|---|----------|---------|---------------------------------------------------|----------|

|   | 2.6      | Valida  | ting Simulation Through Benchmarking              | 38       |

|   |          | 2.6.1   | Parboil                                           | 39       |

|   |          | 2.6.2   | Polybench                                         | 39       |

|   |          | 2.6.3   | AMD APP SDK 2.5                                   | 40       |

|   |          | 2.6.4   | Rodinia                                           | 40       |

|   |          | 2.6.5   | SLAMBench                                         | 41       |

|   |          | 2.6.6   | DeepSmith                                         | 41       |

|   |          | 2.6.7   | SGEMM                                             | 41       |

|   |          | 2.6.8   | Convolutional Neural Network Channel Pruning      | 44       |

|   | 2.7      | Genera  | ating New Benchmarks                              | 46       |

|   |          | 2.7.1   | Measurement                                       | 47       |

|   | 2.8      | Conclu  | usion                                             | 48       |

| 2 | Cim      | ulation | Deskanound & Deleted Work                         | 55       |

| 3 |          |         | Background & Related Work                         | 55<br>55 |

|   | 3.1      | -       | vs. Detail                                        | 55       |

|   |          | 3.1.1   | Cycle-Accurate Simulation                         | 56       |

|   |          | 3.1.2   | Functional Instruction Set Simulation             | 58       |

|   | <b>.</b> | 3.1.3   | Emulation                                         | 59       |

|   | 3.2      |         | ation Environments                                | 60       |

|   |          | 3.2.1   | User Mode Simulation                              | 60       |

|   |          | 3.2.2   | Full-System Simulation                            | 60       |

|   | 3.3      |         | ling the Software Stack                           | 61       |

|   |          | 3.3.1   | Accuracy of the Simulated Software Stack          | 62       |

|   |          | 3.3.2   | Speed of Simulation                               | 71       |

|   |          | 3.3.3   | Ease of maintenance as software is updated        | 72       |

|   |          | 3.3.4   | Usability                                         | 73       |

|   |          | 3.3.5   | Comparison Against Existing Hardware and Software | 74       |

|   | 3.4      |         | mance Modelling Techniques                        | 76       |

|   |          | 3.4.1   | Cycle-Accurate Simulation                         | 76       |

|   |          | 3.4.2   | Trace Based Simulation                            | 76       |

|   |          | 3.4.3   | Analytical Modelling                              | 78       |

|   |          | 3.4.4   | Machine Learning and Statistical Modelling        | 82       |

|   | 3.5      | Conclu  | usion                                             | 85       |

| 4 | Full | -Systen | n Simulation of Mobile CPU/GPU Platforms               | 87  |

|---|------|---------|--------------------------------------------------------|-----|

|   |      | 4.0.1   | State-of-the-Art                                       | 88  |

|   |      | 4.0.2   | Contributions                                          | 90  |

|   | 4.1  | Our Si  | mulation Approach                                      | 91  |

|   |      | 4.1.1   | CPU Simulation                                         | 92  |

|   |      | 4.1.2   | GPU Simulation                                         | 92  |

|   | 4.2  | Instru  | mentation                                              | 94  |

|   |      | 4.2.1   | Program Execution                                      | 95  |

|   |      | 4.2.2   | System                                                 | 95  |

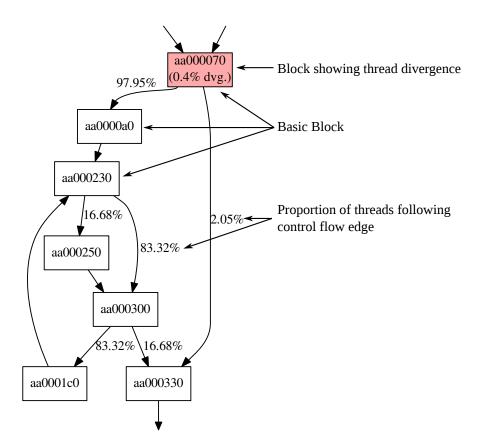

|   |      | 4.2.3   | Control Flow                                           | 95  |

|   | 4.3  | Valida  | tion and Quantitative Evaluation                       | 95  |

|   |      | 4.3.1   | Validation and Accuracy                                | 96  |

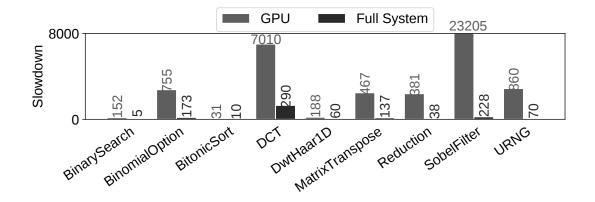

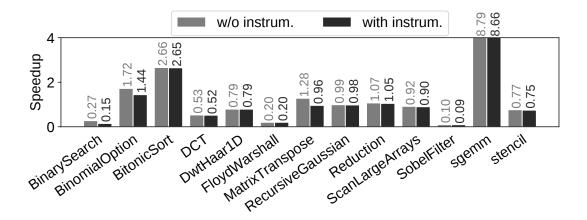

|   |      | 4.3.2   | Simulation Performance                                 | 98  |

|   | 4.4  | Qualit  | ative Evaluation                                       | 100 |

|   |      | 4.4.1   | Accuracy of the Software Stack                         | 101 |

|   |      | 4.4.2   | Speed of Simulation                                    | 103 |

|   |      | 4.4.3   | Ease of maintenance                                    | 103 |

|   |      | 4.4.4   | Usability & Flexibility                                | 103 |

|   | 4.5  | Applic  | cation Results                                         | 104 |

|   |      | 4.5.1   | Identifying Empty Instruction Slots on the GPU         | 105 |

|   |      | 4.5.2   | Moving Data Closer to the Core                         | 105 |

|   |      | 4.5.3   | Evaluating the Bifrost Clause Model                    | 106 |

|   |      | 4.5.4   | System Level Results                                   | 107 |

|   | 4.6  | Optim   | izing OpenCL Applications                              | 107 |

|   |      | 4.6.1   | SLAMBench                                              | 107 |

|   |      | 4.6.2   | SGEMM                                                  | 108 |

|   |      | 4.6.3   | Performance Aware Convolutional Neural Network Channel |     |

|   |      |         | Pruning                                                | 109 |

|   | 4.7  | Implei  | mentation Details                                      | 122 |

|   |      | 4.7.1   | User-Mode Simulation (CPU)                             | 122 |

|   |      | 4.7.2   | GenC Thumb2 Model                                      | 122 |

|   |      | 4.7.3   | GenC GPU Model                                         | 122 |

|   |      | 4.7.4   | Standalone GPU Hexdump Simulator                       | 124 |

|   |      | 4.7.5   | Fuzz Testing                                           | 124 |

|   |      | 4.7.6   | GenSim & Captive Integration                           | 127 |

|   | 4.8  | Summ     | ary & Conclusion                                        | 128 |

|---|------|----------|---------------------------------------------------------|-----|

| 5 | Fast | Perform  | mance Modelling                                         | 131 |

|   | 5.1  | Motiva   | ution                                                   | 131 |

|   |      | 5.1.1    | The Arm Mali GPU                                        | 133 |

|   | 5.2  | Predict  | tion Using Machine Learning                             | 134 |

|   |      | 5.2.1    | A Näive Machine Learning Approach                       | 134 |

|   |      | 5.2.2    | Feature Selection                                       | 135 |

|   |      | 5.2.3    | Principal Component Analysis                            | 136 |

|   |      | 5.2.4    | Manual Feature Modification                             | 136 |

|   |      | 5.2.5    | An Artificial Neural Network Model                      | 137 |

|   |      | 5.2.6    | Conclusions                                             | 137 |

|   | 5.3  | REAS     | SEMBLE: A Trace Based Approach to Fast Performance Mod- |     |

|   |      | elling   |                                                         | 140 |

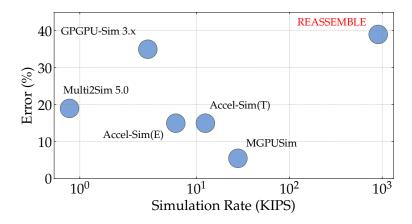

|   |      | 5.3.1    | Design and Methodology                                  | 141 |

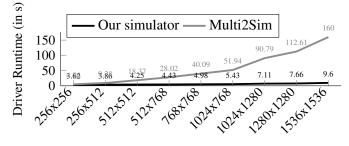

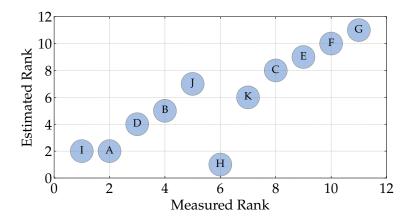

|   |      | 5.3.2    | Validation                                              | 144 |

|   |      | 5.3.3    | Comparison Against State-of-the-Art                     | 147 |

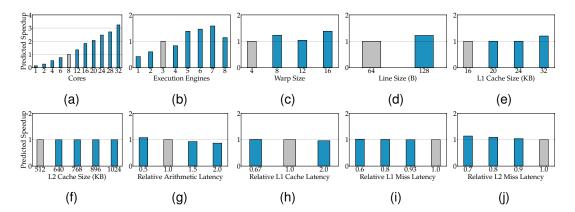

|   |      | 5.3.4    | Design Space Exploration                                | 151 |

|   |      | 5.3.5    | Critical Evaluation                                     | 158 |

|   |      | 5.3.6    | Recent Developments                                     | 165 |

|   |      | 5.3.7    | Conclusion                                              | 167 |

|   | 5.4  | Summa    | ary                                                     | 168 |

| 6 | Con  | clusions | 6                                                       | 169 |

|   | 6.1  | Contril  | butions                                                 | 170 |

|   |      | 6.1.1    | Full-System GPU Simulation                              | 170 |

|   |      | 6.1.2    | Fast Performance Modelling                              | 170 |

|   | 6.2  | Curren   | t Limitations                                           | 172 |

|   |      | 6.2.1    | Significant changes to GPU architectures                | 172 |

|   |      | 6.2.2    | GenSim and Captive Limitations                          | 172 |

|   |      | 6.2.3    | Limitations of the GPU Model                            | 173 |

|   |      | 6.2.4    | Software Availability Assumptions                       | 173 |

|   | 6.3  | Future   | Work                                                    | 173 |

|   |      | 6.3.1    | Functional Simulation                                   | 174 |

|   |      | 6.3.2    | Performance Modelling                                   | 174 |

|   |      | 6.3.3    | Power and Area Modelling                                | 175 |

|   |      |          |                                                         |     |

| Bi | bliogr | aphy 1                                                           | 183 |

|----|--------|------------------------------------------------------------------|-----|

| A  | Арр    | endix 1                                                          | 179 |

|    | 6.5    | Summary and Final Remarks                                        | 77  |

|    | 6.4    | The Future of Simulation                                         | 77  |

|    |        | Modelling                                                        | 76  |

|    |        | 6.3.4 Applications of Functional Simulation and Fast Performance |     |

| Chapter

# Introduction

### 1.1 The Past, Present, and Future of GPUs

GPUs have become ubiquitous in today's computing world. They have grown from being fixed function blocks specific to computing graphics workloads, to general purpose parallel compute accelerators, found in devices ranging from TVs, smartphones and drones to supercomputers, and are being further specialized for accelerating workloads in specific domains. Nvidia, often considered the inventor of the GPU, currently lists 52 different categories whose applications target GPUs, including but not limited to Animation, Data Mining, Bioinformatics, Climate Modeling, Computational Fluid Dynamics, Databases, Computer Vision, and Machine Learning [1], showing just how pervasive GPUs are in modern day computer science.

The first graphics accelerators emerged in the 1970s, with the introduction of video shifters in various arcade systems. The 1980s saw the introduction of fully-integrated graphics display processors for PCs, and in 1986, Texas Instruments released the first fully programmable graphics processor - the TMS34010 [2]. The TMS34010 was essentially a 32-bit CPU with some graphics-oriented instructions, and brought with it the first generalized architecture for graphics processing - *Texas Instruments Graphics Architecture (TIGA)* [3], which guaranteed that a program written for TIGA, would work on any TIGA-compatible machine. The late 1980s and 90s saw the emergence of the first dedicated video cards for PCs used to accelerate fixed-function 2D primitives, with increasing numbers of colors and pixels supported. By the mid-1990s, 3D graphics had found their way into gaming consoles. At the same time, the OpenGL [4] and Glide [5] APIs appeared, and slowly hardware support for OpenGL was rolled out. Towards the late 1990s, DirectX became another popular choice for programming

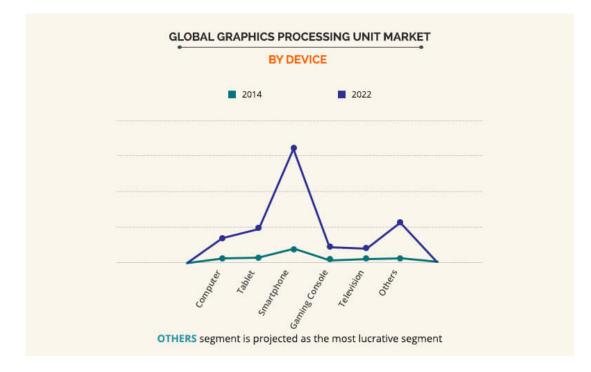

Fig. 1.1: GPU market breakdown by device [10].

graphics. In the early 2000s, Nvidia produced the first chip supporting programmable shading, the GeForce 3, which was used in the original Xbox gaming console [6]. The shading however, was still focused largely around dispatching fixed-function units of work. The Nvidia GeForce 8 series GPUs became the first generalized computing devices and represent Nvidia's first unified shader architecture [7]. This meant that all shaders could handle any type of shading task. In 2007, Nvidia introduced the CUDA platform [8], the earliest widely adopted programming model for GPU computing. This was followed by OpenCL [9]- an open standard developed and supported by many hardware vendors, with Apple breaking away and releasing Metal, its own compute and graphics API. In the last decade, GPUs have become increasingly powerful, with graphics driven by gaming and virtual reality, and compute driven by big data and the emergence of machine learning and computer vision. According to Allied Market Research, the GPU market size is expected to reach \$157.1 billion by 2022, growing by 35.6% during the 2016-2022 period [10]. Figure 1.1, sourced from the same report, breaks down the GPU market by device. It shows, that, as a percentage, the *others* category will have the largest growth as a percentage of its current market share, while *smartphones* are and will remain the largest category by volume. Jointly, smartphones and other, newly-developed emerging devices, will far outpace the remaining categories by 2022.

The mobile GPU space was until recently dominated by Arm, whose GPUs powered 52.6% of smartphones sold in 2018, thanks to strong partnerships with Samsung and Huawei. The mobile GPU space however, is evidently of interest to many leading companies. Samsung, a leader in the field of mobile devices, has recently partnered with AMD to create their own in-house GPU, using AMD intellectual property (IP) for a scalable GPU design [11]. For many years, Apple licensed its GPU IP from Imagination Technologies, and after a brief two-year period of attempting to design GPUs in house, Apple has once again signed an agreement with Imagination to source future graphics IP [12]. This announcement comes shortly after Imagination announced its new, scalable, GPU-of-everything family [13], showing that Imagination GPUs can target a wide variety of devices and domains. Furthermore, Apple is shifting it's technology away from separate chips, having recently announced its first System-on-Chip (SoC)-based computers with the M1 chip. The M1 chip, similarly to smartphones, integrates the CPU, GPU, and Neural Processor into a single SoC, sharing memory between all processing units, and delivering a record performance per watt, and outperforming high-end Intel processors in raw performance measurements.

The market for AI augmentation, which requires compute and graphics processing locally on device, is estimated to be worth 3.3 trillion dollars [14]. Coupled with concerns about security and privacy, much of the processing is moving from the cloud to edge devices. Driven by this unique set of circumstances, vendors are specializing their embedded GPUs, optimizing not only for graphics, but highly-parallel computer vision and machine learning applications as well. Computer vision accelerators have been developed by companies such as Movidius (now part of Intel), and many companies, including Arm and Huawei, are increasingly introducing GPUs optimized for machine learning, and even adding additional, dedicated chips with the sole purpose of accelerating machine learning algorithms [15].

GPUs are found all around us - from servers, desktops, and game consoles, to small mobile GPUs in mobile phones and VR headsets - and they're continuously being redesigned and altered to fit emerging applications that require vast parallel compute capabilities. Figure 1.4 shows the number of vendors designing new machine learning accelerators alone. Technology is quickly migrating from being server/desktop dominated into the IoT (Internet-of-Things) space, meaning that energy efficient processors are in high demand. In the future, we'll see more and more demand for these types of systems, and it's critical that we have tools to support their design and development.

Very little of the original graphics-specific GPU design remains visible in modern

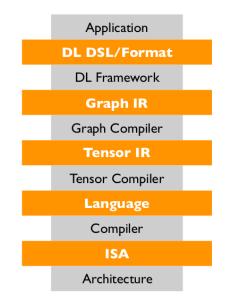

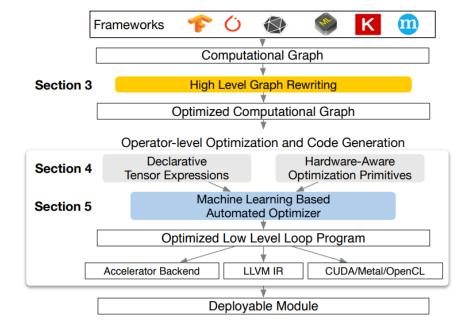

Fig. 1.2: Modern deep learning compute stacks include multiple libraries, with different purposes, and using different intermediate representations. (Fig. Source: [16])

multi-purpose parallel GPGPU architectures. GPUs however, have not evolved on their own. The applications accelerated by GPUs are supported by exceptionally complex heterogeneous systems, with multiple processors, and convoluted software stacks driving the applications, which a standalone GPU would not be capable of executing. The intricacies of systems supporting GPU execution are explored in the following section.

## 1.2 The Complexities of GPU Systems

Modern GPUs form just one component of complex, heterogeneous systems, with a CPU, and potentially other accelerators executing in parallel, sharing resources, and completing mutual tasks, and consideration for this environment must be at the heart of the design. The systems themselves are growing increasingly complex, with additional levels of the software stack both co-existing and being layered one on top of the next.

The original GPU compute stack has grown to include multiple abstractions and libraries in the software layer, for example, Figure 1.2 shows an abstraction of the deep learning compute stack. A neural network is specified in a high-level programming language within a deep learning framework, which is then compiled down into an intermediate graph representation, which forms the network. The operations performed on this network are further compiled into Tensor IR, which is a matrix representation of the operations to be executed. Only then, these intermediate representations are trans-

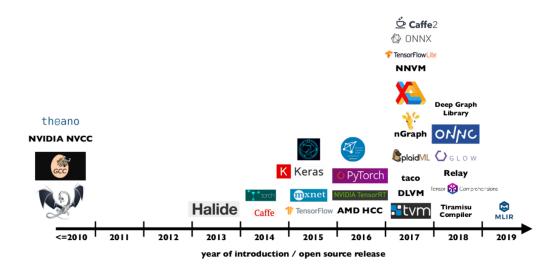

Fig. 1.3: The number of Machine Learning frameworks has grown dramatically in recent years. (Fig. Source: [16])

formed into a more traditional programming language, for example C++, from which point the traditional compute stack, forming the language, compiler, ISA, and architecture, is once again recognizable. But this is just one example - Figure 1.3 shows how the number of programming frameworks for machine learning has exploded in recent years.

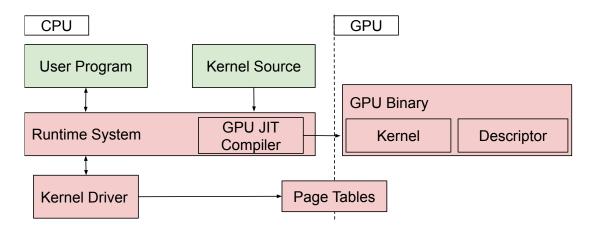

The software stack doesn't execute just on the GPU. In fact, only the final, optimized, binary GPU kernel executes on the GPU, while the remainder of the complex software stack executes entirely on the CPU, demonstrating just how critical the CPU is to correct and efficient GPU execution - without CPU execution, there is no GPU execution. A CPU further relies on other system components for correct execution - timers, interrupt controllers, memory. The only way to completely and correctly execute the entire software stack, is to have a complete view of the hardware that the software executes on. This is true not just for native execution, but also for all tools used to design and develop GPUs and their software stacks. The following section introduces simulation - the backbone behind the development of modern GPU devices.

### **1.3** Simulation as a Key Design and Development Tool

At the heart of GPU design tools, lies simulation. Simulation is a critical component of any computer architecture design phase. It is increasingly used for designing, prototyping, and testing new hardware. Simulation is also used by systems, compiler, and

| Tech Giants/System         | IC Vender/Fabless | Startup in China                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ·                 | Worldwide FPGA/eFPGA               | IP/Design Sevice           |

|----------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------------------------------|----------------------------|

| Ŭ                          |                   | 4 平 tt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Cerebras          | Achronix                           |                            |

| Microsoft                  | SAMSUNG           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | VVAVE             | <u>fle</u> xlogiX                  | SYNOPSYS.                  |

| facebook                   |                   | intellUlusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Graphcore'        | Processing in Memory               |                            |

| 214/5                      |                   | A Think Force                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                   |                                    | CEVA                       |

| aws                        | E XILINX.         | M 筆版电子<br>NextVPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                   |                                    | cādence                    |

| Ś.                         | MEDIATEK          | Concor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | HAILD             | technology                         |                            |

| IBM.                       | 囤 UNISOC          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                   | Optical Computing                  | Si Five                    |

| Ð                          | <b>A</b>          | (/Enflame                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 🕞 thinci          | LIGHTELLIGENCE                     | ARTERIS                    |

| Alibaba Group<br>周盟巴巴県図    | Rockchip<br>BERGY |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                   | LIGHTMATTER                        |                            |

| <b>S</b> 16                | Ambarella         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | grog              |                                    | Design service wit         |

| HUAWEI                     | 2                 | いた<br>での<br>にの<br>にの<br>にの<br>の<br>で<br>の<br>で<br>の<br>の<br>の<br>の<br>の<br>の<br>の<br>の<br>の<br>の<br>の<br>の<br>の                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Tachyum           | Neuromorphic                       | In-nouse IP                |

| Bai 🖉 ēķ                   | Automated Driving |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Esperanto         | () aiCTX                           | _                          |

| Ŷ                          | NP                | Smart Voice                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | TECHNOLOGIES      | brainchip <sup>**</sup>            | & BROADCOM                 |

| _                          | TEXAS             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | PEZY Computing    | Preferred<br>Networks              | GUC                        |

| Hewlett Pack<br>Enterprise | RENESAS           | Rokid                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Eta Compute       |                                    | alchip                     |

| FUĴITSU                    | TOSHIBA           | AISPEBCH 8 0 M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | GREENWAVES        | NeuroBlade 🚳 NOVUMIND              | FARADAY                    |

| Deell                      | <b>677</b>        | 10 No. 10 |                   | https://basicmi.github.io/Al-Chip/ | <pre></pre>                |

| Western Digital            |                   | Compilers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                   | Benchi                             | marks                      |

|                            | 1 TensorFlow 💫    | J <sub>GLOW</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | NVIDIA. Tensor RT | MLPerf AI - Benc                   | hmark 🛛 🗛 🗛 🗛 🗛 ΔΙ Matrix. |

Fig. 1.4: Both established vendors and startups are designing machine learning accelerators. (Source: [16])

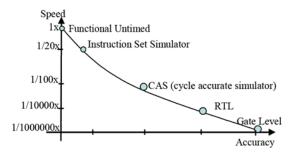

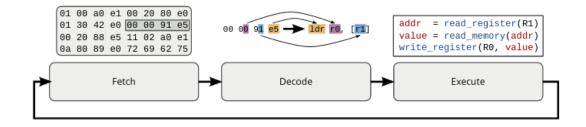

software developers to design software before the silicon is available, and can further be exploited to explain causes and effects which can't be observed using real hardware. This thesis primarily concerns itself with two types of simulators - functional, instruction set simulators, and cycle-accurate simulators. Functional, instruction set simulators model the architecture at the ISA-level, executing instruction-by-instruction, without any overview of the micro-architecture. Cycle-accurate simulators on the other hand, follow each instruction through all of the pipeline stages, and at the cost of simulation speed, have greater observability.

The primary use of simulators is two-fold. Firstly, by computer architects, they are used to model hardware prior to developing physical chips. In this case, strong focus is placed on modeling hardware components, and their interactions, in order to accurately predict hardware power consumption, performance, and area. Most commonly for this purpose, cycle-accurate simulators are used by computer architects.

Secondly, simulators are used by software developers, who use them to develop application and system software prior to hardware becoming available, or using them in environments where a high number of potential configurations is possible, and where it would be infeasible to obtain and test all available hardware platforms (e.g. Android app and system development). In this case, a stronger focus is placed on functional correctness, and performance prediction, while still important, becomes secondary. Commonly, in software development, functional emulators, or instruction set simulators are used, which trade-off accuracy in the performance model for execution speed.

The following section introduces some of the trade-offs that need to be considered when simulating GPUs, as well as limitations of existing GPU simulators.

### 1.4 Motivation

In both of the scenarios described in the previous section, speed is of utmost importance. When designing hardware, there are infinitely many possible configurations, and with the high cost of detailed simulation, only a limited number of configurations can be explored within the timeframe of the development cycle. Software developers face the problem of long latencies when running simulations and testing different software implementations. For example, a software developer may want to test a new piece of software, and executes it in the simulator. In real hardware, this execution might take a few hundred milliseconds, however in functional simulation, it could take hours, and in detailed simulation, days, weeks, or months. Now let's say this software contains a number of bugs that need to be discovered, and addressed. This is an iterative process, and each bug requires another execution of the software, significantly extending development time.

GPUs are particularly vulnerable to the issues mentioned, as they are highly-parallel SIMD machines designed to accelerate parallel workloads. In short, in the same amount of time as a CPU, they are capable of executing thousands of times more code, provided that the application is parallelizable. As the host hardware (CPU) that the GPU simulator is executing on does not have the same parallel capabilities as the guest (GPU), this has a significant impact on simulation time. Detailed architecture simulation clearly does not scale to increasingly parallel modern workloads.

Furthermore, in order to execute modern applications with a complex software stack, and to guarantee accurate binary execution, the supporting software stack must also be faithfully simulated in full.

Existing state-of-the-art GPU simulators however, primarily focus on detailed modelling of the hardware, while cutting many corners when simulating the software stack and surrounding system by treating the GPU as a standalone device, simulating the GPU at levels other than the binary instruction set level, or replacing the software stack. In addition, simulation speeds associated with detailed simulators make these simulators unsuitable for modelling modern workloads. Finally, existing state-of-theart GPU simulators in the open domain are developed around large desktop or server class GPUs, while leaving a void in the mobile GPU space. These problems are explored in detail in Section 3.3, while the following section introduces the goals behind the work presented in this thesis.

### 1.5 Goals

The work presented in this thesis aims to provide better simulation technology for GPU-based systems that cut fewer corners, but are faster than existing cycle-accurate simulators, and which fully supports mobile GPU simulation. In particular, we aim to develop a simulation system that:

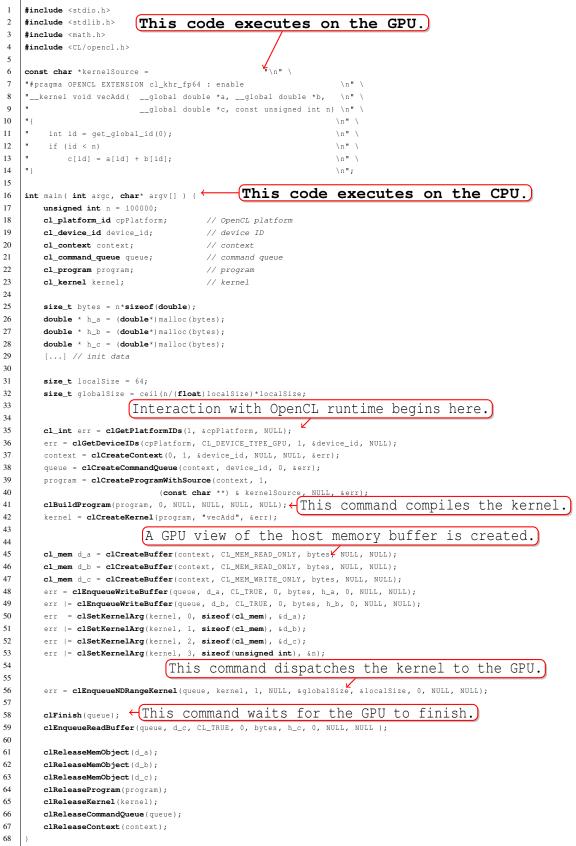

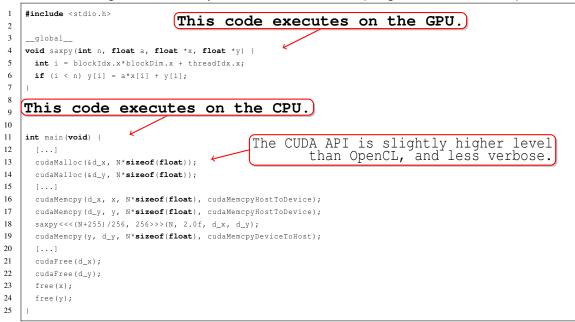

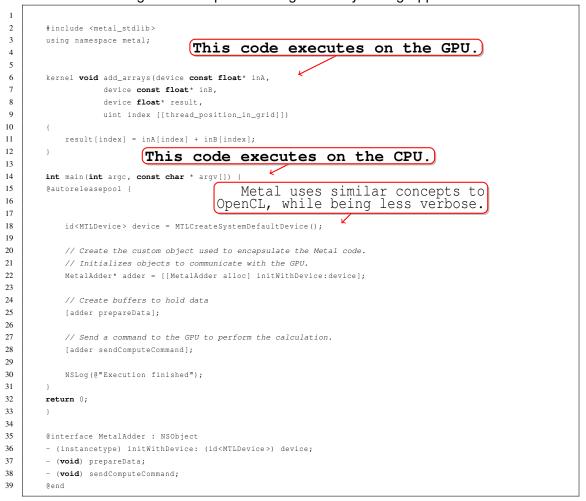

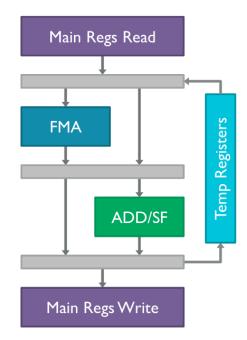

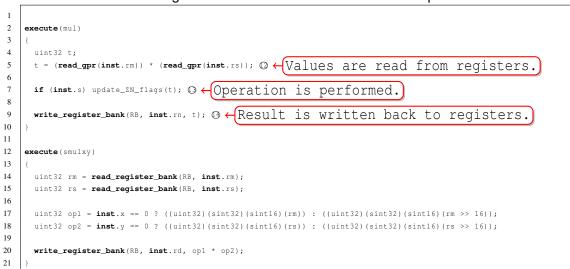

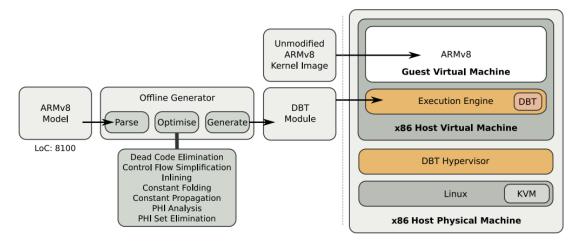

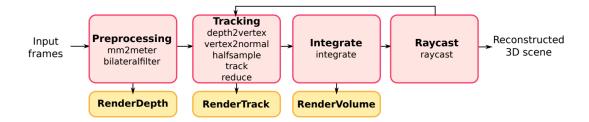

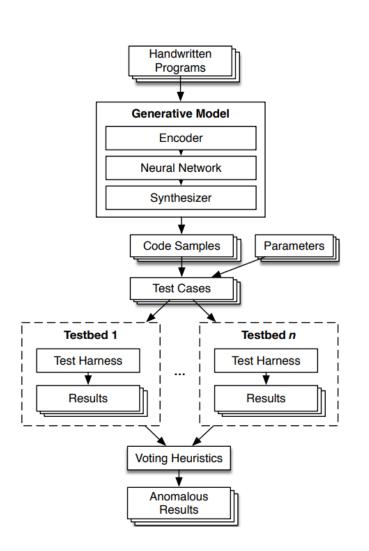

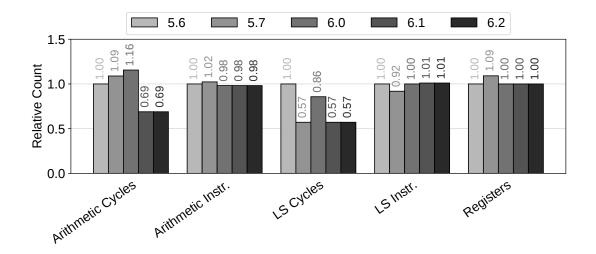

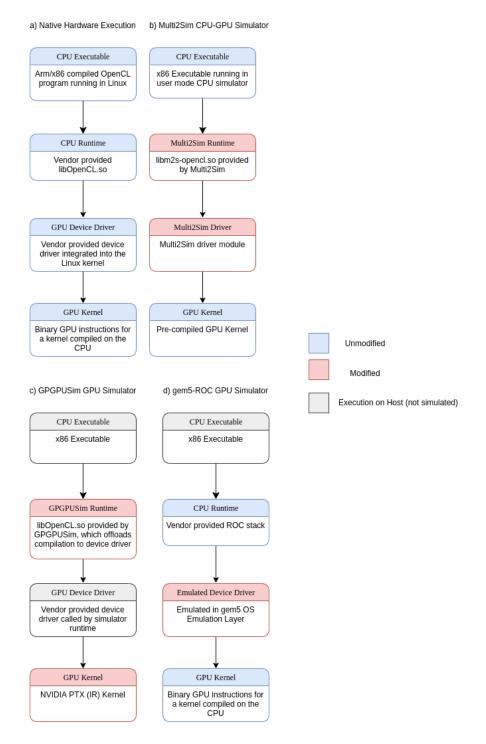

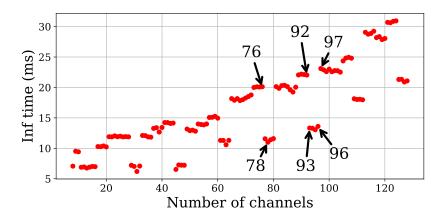

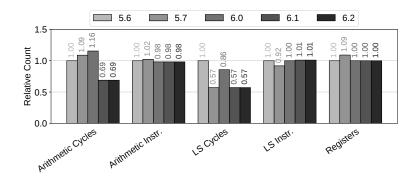

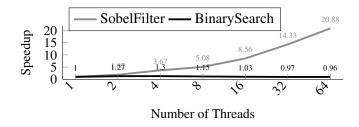

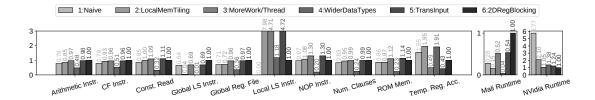

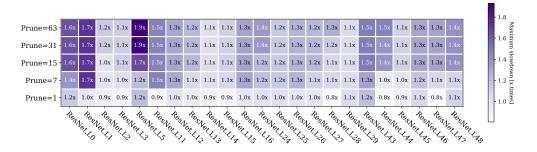

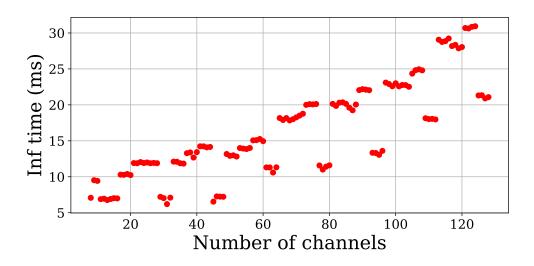

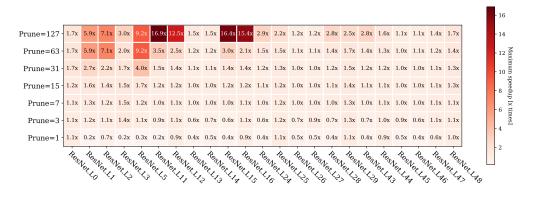

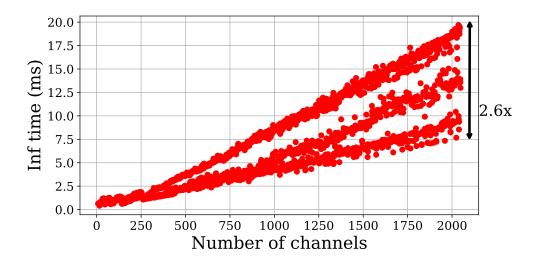

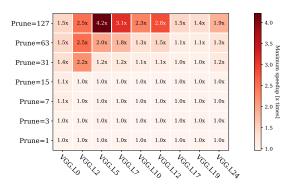

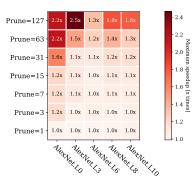

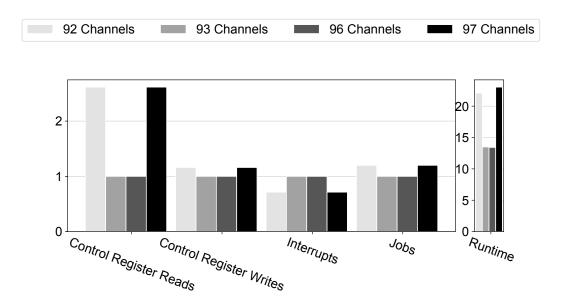

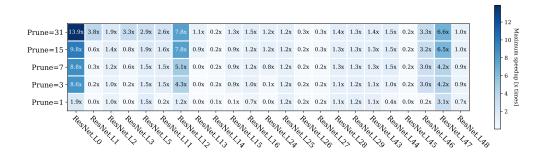

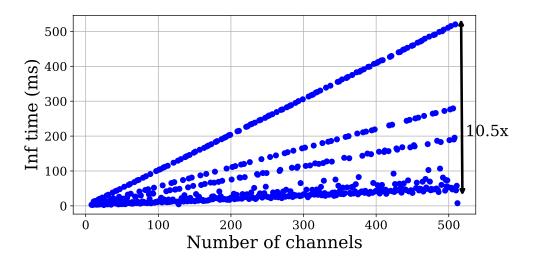

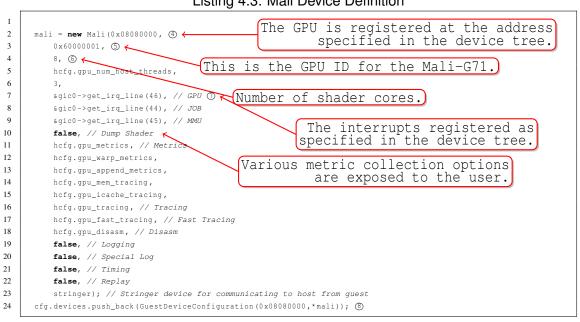

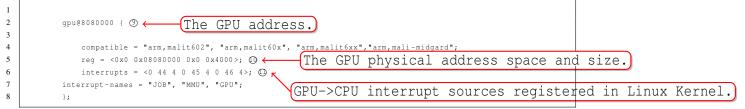

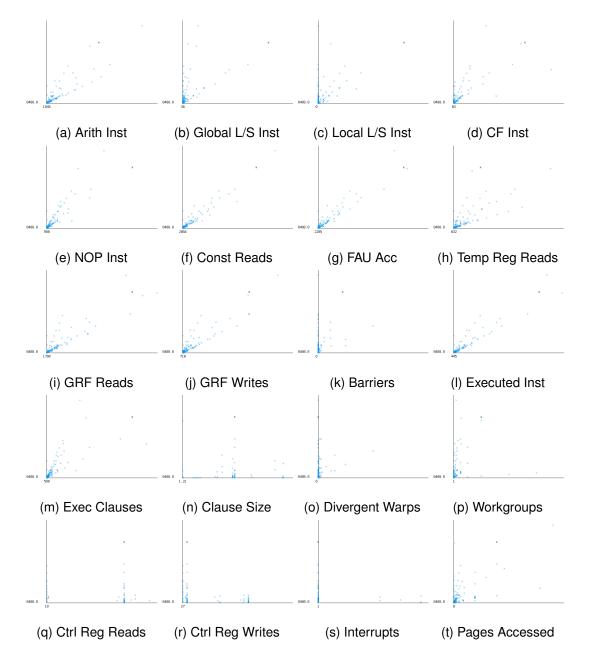

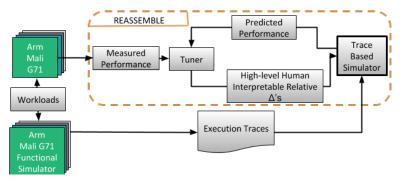

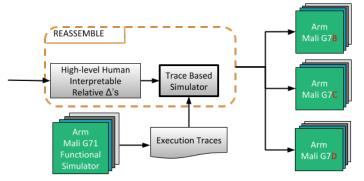

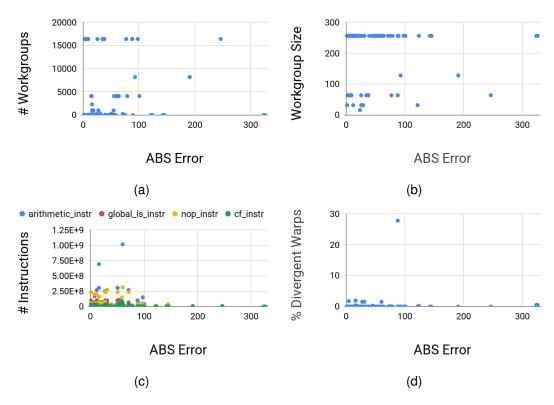

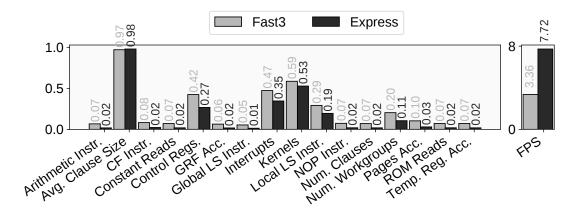

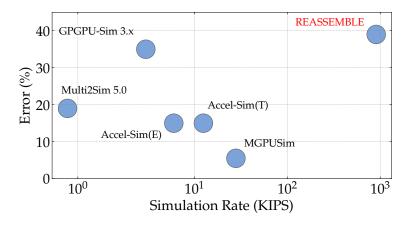

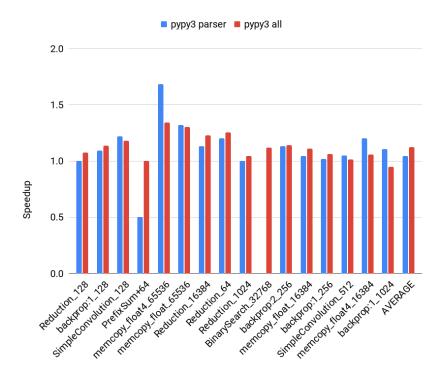

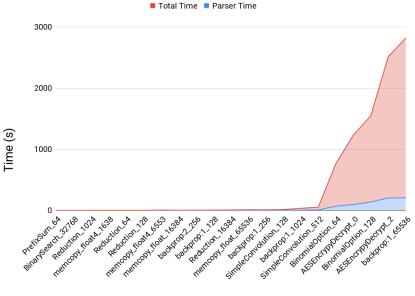

- Accurately simulates a state-of-the-art mobile GPU in a full-system context, enabling the use of *unmodified* vendor-supplied drivers and JIT compilers, operating in an *unmodified* target operating system, and executing *unmodified* applications.