# Instituto Tecnológico y de Estudios Superiores de Occidente

Reconocimiento de validez oficial de estudios de nivel superior según acuerdo secretarial 15018, publicado en el Diario Oficial de la Federación del 29 de noviembre de 1976.

Departamento de Electrónica, Sistemas e Informática Especialidad en Diseño de Sistemas en Chip

Voltaje de Referencia BandGap y Módulo de Comunicación Serial para SAR ADC 10 Bits de Baja Potencia para Aplicaciones Biomédicas

**TRABAJO RECEPCIONAL** que para obtener el **GRADO** de **ESPECIALISTA EN DISEÑO DE SISTEMAS EN CHIP**

Presenta: LUIS ANGEL GONZÁLEZ ORNELAS

Director: JOSE LUIS CHÁVEZ HURTADO, ESTEBAN MARTINEZ GUERRERO Y CUAUHTÉMOC RAFAEL AGUILERA GALICIA

Tlaquepaque, Jalisco. Octubre de 2021.

# ITESO – The Jesuit University of Guadalajara

Department of Electronic, System, and Informatics. Specialization Program in SoC Design.

## BandGap Reference Voltage and Serial Communication Module for a Low Power 10 Bits SAR ADC to Biomedical Applications

Thesis/Project to achieve the degree of SoC Design Specialist

Present: Luis Angel González Ornelas

Thesis Director: Jose Luis Chávez Hurtado, Esteban Martinez Guerrero and Cuauhtémoc Rafael Aguilera Galicia.

Tlaquepaque, Jalisco. October 2021

## Acknowledgments

I principally would like to thank my family, especially my mother that who has always supported me in every stage of my life.

Then thanks to NXP Semiconductors and CONACYT, both entities help me financially to achieve this goal in my personal and professional life.

I want to thank Esteban Martinez Guerrero for the design of the Bandgap voltage reference circuit that is presented in this work.

Finally, I would like to thank ITESO that has guided us in a better way to reach this new goal.

## Abstract

The document presents two designs a BandGap Reference Voltage, and a Communication Serial Module for a 10 bits SAR ADC for low-power applications. Designs were implemented using TSMC 0.18 µm CMOS technology with 1.8 V supply voltage.

The BandGap Reference Voltage was designed to provide a reference voltage of 900 mV  $\pm$ 500  $\mu$ V. The bandgap was tested at simulation level under different temperature conditions to ensure constant output in a temperature range from -40 °C to 85 °C. The Communication Serial Module is designed using the hardware description language Verilog. This module receives the 10 bits parallel output of the SAR ADC and retransmits the conversion result into a serial format using the SPI format. The Communication Serial Module was tested under a simulator, where multiple test cases were applied to stimulate in different ways the module.

Both circuits were designed to accomplish the SAR ADC requirements in which BandGap supplies the reference voltage to the capacitor array in the SAR ADC and the Serial Module sends the data values after the conversion is finalized.

# Acronyms and Abbreviation

| Analog to Digital Converter.        |

|-------------------------------------|

| BandGap Reference.                  |

| Digital to Analog Converter.        |

| Successive Approximation Registers. |

| Process, Voltage, Temperature       |

| Design Rule Check                   |

| Layout vs Schematic                 |

| Integrated Development Environment  |

| Register Transfer Level             |

| Digital Signal Processor            |

|                                     |

# Contents

| Ab | strac                                                                                                        | 2t                                                                                                                                                                                                                                                                                                                      | vi                                                                                     |

|----|--------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| Ac | rony                                                                                                         | ms and Abbreviation v                                                                                                                                                                                                                                                                                                   | 7 <b>iii</b>                                                                           |

| Co | nten                                                                                                         | ts                                                                                                                                                                                                                                                                                                                      | . X                                                                                    |

| 1. | AD                                                                                                           | Cs For Biosensor Applications                                                                                                                                                                                                                                                                                           | . 1                                                                                    |

|    | <ol> <li>1.1.</li> <li>1.2.</li> <li>1.3.</li> <li>1.4.</li> <li>1.5.</li> </ol>                             | ANALOG TO DIGITAL CONVERSION.<br>1.1.1 Sample and Hold.<br>1.1.2 Analog to Digital conversion.<br>1.1.3 Digital Signal Processor (DSP)<br>1.1.4 Digital to Analog Conversion.<br>SAR ADC ARCHITECTURE.<br>CAPACITIVE SPLIT – ARRAY DAC ARCHITECTURE.<br>SAR ADC BLOCK DIAGRAM.<br>BLOCK DIAGRAM FUNCTIONAL DESCRIPTION. | 1<br>2<br>3<br>3<br>4<br>7                                                             |

| 2. | Ban                                                                                                          | dGap Reference Voltage                                                                                                                                                                                                                                                                                                  | . 9                                                                                    |

| 3. | <ul> <li>2.1.</li> <li>2.2.</li> <li>2.3.</li> <li>2.4.</li> <li>Seri</li> <li>3.1.</li> <li>3.2.</li> </ul> | INTRODUCTION<br>BGR VOLTAGE TOPOLOGIES                                                                                                                                                                                                                                                                                  | .10<br>.13<br>.15<br>.16<br>.17<br>.18<br>.21<br>.22<br><b>23</b><br>.23<br>.24<br>.25 |

|    | 3.3.<br>3.4.                                                                                                 | SPI MODELSIMS SIMULATION RESULTS                                                                                                                                                                                                                                                                                        | .26                                                                                    |

| 4. | AD                                                                                                           | C Integration                                                                                                                                                                                                                                                                                                           | 29                                                                                     |

|    |                                                                                                              | Logic Synthesis<br>Physical Synthesis                                                                                                                                                                                                                                                                                   |                                                                                        |

| 5. | Con                                                                                                          | clusions                                                                                                                                                                                                                                                                                                                | 38                                                                                     |

| 6. | App                                                                                                          | oendix A                                                                                                                                                                                                                                                                                                                | 39                                                                                     |

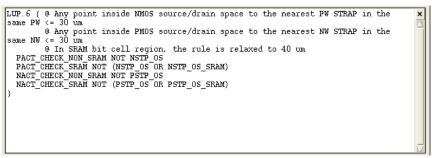

|    | 6.1.                                                                                                         | LUP.6 40                                                                                                                                                                                                                                                                                                                |                                                                                        |

| 7. | Bibl                                                                                                         | liography                                                                                                                                                                                                                                                                                                               | 43                                                                                     |

## **1.** ADCs For Biosensor Applications

## 1.1. Analog to Digital Conversion

Analog to Digital converters (ADCs) translate analog signals, which are characteristic of most phenomena in the world, into a digital signal, to be processed in digital systems (Floyd T. L., 2014). Since the "real world" is analog and processing is digital, data converters are used in electronic circuits at the interface between analog and digital world, and play a fundamental role in most of the applications, such as industrial, telecommunications, automotive, medical, etc.

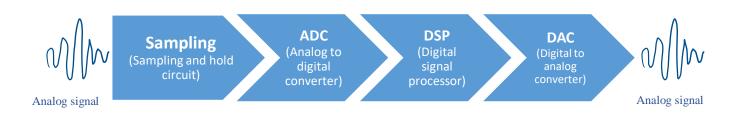

The basic operation of an ADC in signal processing flux can be explained in four steps (Fig. 1.1): sampling, analog to digital conversion, digital signal processing, and digital to analog conversion (Floyd T. L., 2006). These steps are shown in the next figure:

Figure 1.1 : Analog to digital conversion process

#### 1.1.1 Sample and Hold

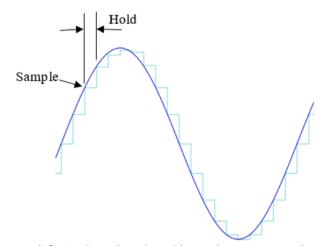

Sampling is the process to take the value of the input signal sufficient times to have enough information of the input signal. This process converts an analog signal into a series of impulses, each one representing the amplitude of the signal at an instant in time. The more samples are taken, the more accurate is the waveform.

The holding operation ensures the sampled value must be held constant for an instant defined until the next sample is taken. This is necessary for the ADC to have time to process the sampled value. This sample and hold process results in a stairstep waveform that approximates the analog input signal (Fig. 1.2).

#### **1.1.2** Analog to Digital conversion

It is the process of converting the output of the sample and hold circuit into a series of binary codes that represent the amplitude of the analog input signal at each of the sample times. The ADC makes the codification in the time between sample pulses, or the time that sample and hold circuit is holding the sampled value. This process is called quantization.

Figure 1.2 Analog signal and its stairstep approximation.

#### **1.1.3** Digital Signal Processor (DSP)

The Digital Signal Processor (DSP) consists of a specialized microprocessor chip which architecture has been optimized for processing the digital signal received from the previous step. The goal of the DSP is to process data in real-time.

#### **1.1.4 Digital to Analog Conversion**

It is the process of transforming data or the result of the digital processing, back to an analog signal to send it back to the "real world". Most of the DACs perform two basic functions: conversion of the digital input into an equivalent analog signal and reconstruction of the signal.

### **1.2. SAR ADC Architecture**

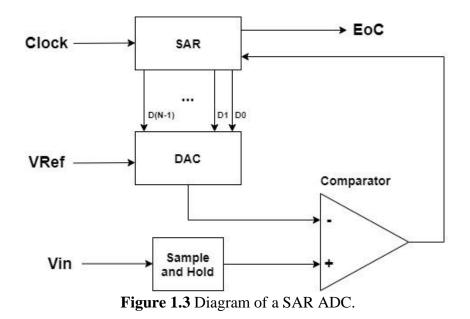

There are many conversion techniques to change analog signals to digital. In our proposal, a SAR ADC technique is selected. Fig. 1.3 shows the main components of a SAR ADC. The operation principle is as follows: the circuit samples an input signal and compares it to several voltages that are generated by a Digital to Analog Converter (DAC). The Successive Approximation Register (SAR) controls the voltage of the DAC and saves the results of the comparison.

In Figure 1.3, the block diagram of a basic SAR ADC is shown. The main modules of this architecture are a sample and hold circuit, a comparator, a DAC, and a SAR.

As stated before, the SAR controls the voltage that the DAC outputs. It starts by assigning a 1 to the most significant bit (MSB). This is done because that is the halfway value of the voltage that the DAC works with. The next step is to compare the DAC voltage with the sampled input voltage. If the analog input is higher than the voltage of the DAC, the Comparator has an output of 1 (or the equivalent analog voltage) that the SAR saves, and then the SAR will assign a 1 to the next significant bit, repeating the process. But if the sampled voltage is smaller than the original DAC's voltage, then the SAR saves a 0, turns the MSB to 0, and assigns a 1 to the next significant bit, starting the cycle again.

A SAR ADC converts a bit in each cycle, so depending on the resolution of the ADC is the minimum number of cycles needed to finish an analog conversion.

### 1.3. Capacitive Split – Array DAC Architecture

As explained before, a SAR ADC needs a Digital to Analog Converter (DAC) to generate the voltages that will be compared against the input voltage. Since this project wants to be used in a Biosensor application, the proposal that we choose must consume the least amount of power and must be as small as possible. For this reason, we choose Capacitive Split-Array Architecture for our DAC.

There are many architectures for implementing a DAC and most of them use either resistors or capacitors to generate voltage as their main component. The difference between using one or the other component is that resistors are components that are constantly consuming power since they only work in a state, meanwhile, capacitors consume power depending on the state the capacitor is in. When the capacitor is working then it consumes power, but if it is not working then it won't. This behavior is what pushes us to use an architecture based on capacitors.

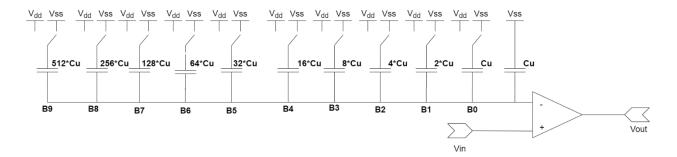

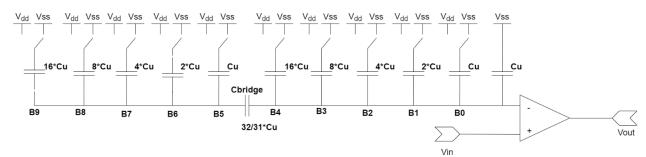

The most commonly used capacitor architecture is called Charge-Scaling Capacitors, which can be seen in Figure 1.4.

**Figure 1.4** Schematic diagram of Charge-Scaling Capacitor topology for a 10-bit resolution DAC (Baker, 2010).

The number of capacitors of Charge-Scaling Capacitor DAC defines the bits in the DAC. Figure 1.4, shows the schematic of a 10 bits DAC. Each of the capacitors represents a bit, except for the last one that is used to provide the correct divisor factor in the inverting node. Each capacitor will switch between VSS and VDD, depending on what the SAR will assign to the control signals. This process will start from the MSB to the LSB.

The main problem with this architecture ¿reamins? in the capacitor value of the MSB; where n is the DAC resolution. In the example of Figure 1.4, the MSB capacitor is 512 times bigger than the smallest one, i.e., the unity capacitance Cu. Having large capacitors is not desirable because they are area-consuming, and this is an important tradeoff when designing a chip. The larger they are, the more expensive they are, and they consume more power.

To reduce the power consumption of DAC, the Capacitive Split-Array topology is utilized. It is shown in Figure 1.5.

Figure 1.5 Schematic diagram of Capacitive Split-Array Architecture (Baker, 2010).

The architecture called "Capacitive Split-Array" reduces power consumption by dividing the capacitors into two arrays, one for the least significant bits (LSB) b0 to b4 and the other one for the most significant bits (MSB) b5 to b9. Both arrays have capacitors of the same magnitude, and this works because of the bridge capacitor between both arrays (Cbridge). The only difference between the array is that the one for the LSB also has an extra capacitor to provide the correct divisor factor in the inverting node. The value of the bridge capacitor can be calculated using Equation 1:

$$C_{bridge} = \frac{Sum of LSB Capacitance}{Sum of MSB Capacitance} * Cu$$

Eq 1: Equation for calculation the bridge capacitor in Capacitive Split-Array architecture.

The DAC Capacitive Split-Array has all the benefits of the DAC Charge-Scaling Capacitors but uses smaller capacitors. The only disadvantage is that by adding the Cbridge, the system will not have a linear behavior which could complicate fixing mistakes if the capacitor arrays are not properly balanced (Yan Zhu, 2014).

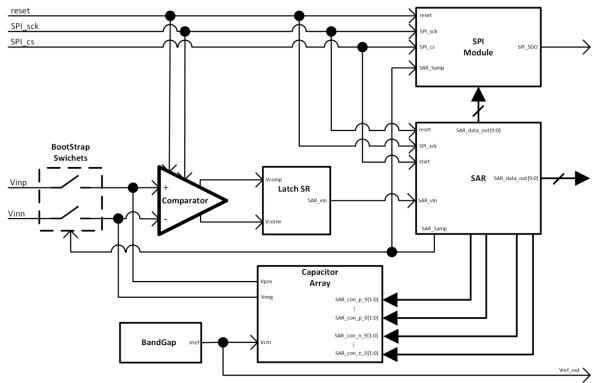

## 1.4. SAR ADC Block Diagram

Figure 1.5 SAR ADC Block Diagram.

## **1.5.** Block Diagram Functional Description

The SAR ADC is made by different functional blocks, shown in Fig 1.5, which are described in the following sentences:

- Serial Peripheral Interface (SPI) module: the SPI module is responsible to send the conversion result from the SAR module to an external signal in a serial format.

- BandGap Reference module: This module supplies a reference voltage to the capacitors array. This module is supplied by 1.8 V and provides a stable output of 900 mV  $\pm$ 500  $\mu$ V.

- SAR module: It converts the analog signal into a digital signal. The digital signal contains 10 bits, named *SAR\_data\_out [9:0]*, that are sent directly to the SPI module and the exterior.

- Capacitor Array module: This module consists on a Digital to Analog block that generates voltages to be compared against two external signals, *V*<sub>ip</sub> and *V*<sub>inn</sub>.

- Comparator module: It compares the two external signals, *V*<sub>ip</sub> and *V*<sub>inn</sub> after they have been sampled by the BootStrap Switches.

- Latch SR module: once the comparison between V<sub>ip</sub> and V<sub>inn</sub> has been finished, the Latch SR module converts the pair signals to a single wire.

## 2. BandGap Reference Voltage

In this section, the BandGap Reference (BGR) Voltage is described in detail. The BGR is designed in TSMC 0.18  $\mu$ m CMOS technology with 1.8 V supply voltage. The BGR works with an input voltage of 1.8 V as supply and an output voltage or Vref = 900 mV, from -40 °C to 85 °C, across PVT corners with a variation of ±500  $\mu$ V.

#### **2.1.** Introduction

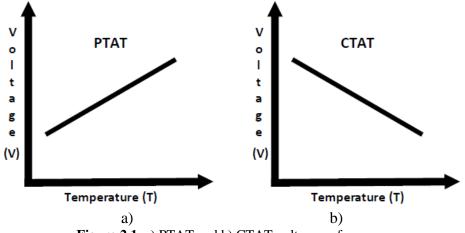

An ideal voltage reference is a circuit used to generate a fixed voltage,  $V_{ref}$ , that is independent of the power supply voltage  $V_{DD}$  (where  $V_{ref} < V_{DD}$ ), the temperature, and the process variations. In other words, the ideal reference voltage is independent of PVT variations. In some cases, we want to design a reference that varies with temperature. When  $V_{ref}$  increases with temperature, as shown in Fig. 2.1a, we say that the reference voltage is proportional to the absolute temperature (PTAT), meanwhile, if the reference voltage decreases when the temperature increases, as shown in Fig. 2.1b, we say that the reference is complementary to the absolute temperature (CTAT) (Baker, 2010). Then the BGR circuit works on the compensation of the two PTAT and CTAT curves.

Figure 2.1. a) PTAT and b) CTAT voltages references.

## 2.2. BGR Voltage Topologies

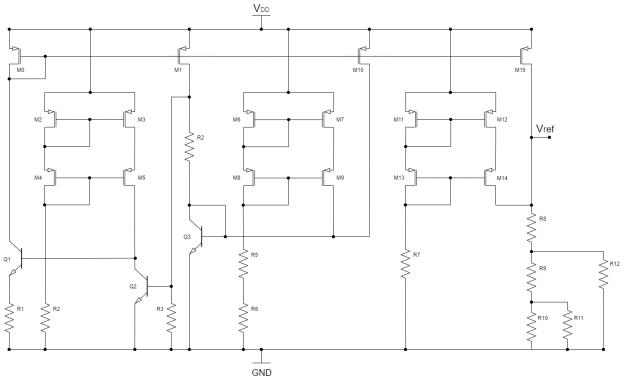

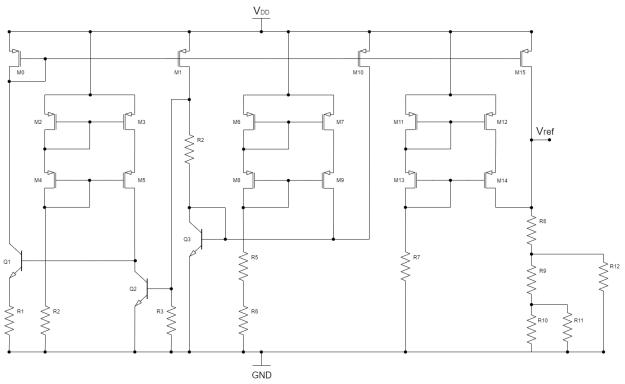

In this work, two BGR topologies were analyzed: a full CMOS transistor topology (Fig. 2.2) (Ribeiro, Gama, Costa, Neves, & Horta) and a hybrid CMOS – BJT transistor topology which was designed by (Martinez Guerrero, 2021) from the conceptual approach reported in (Naganadhan, 2019) (Fig. 2.3).

Both topologies were calculated to obtain a voltage reference  $V_{ref} = 900 \text{ mV}$ , and are based on current mirrors to deal with the current consumption and to equilibrate the temperature variation. To validate the correct functionality, each circuit was calculated, simulated, and optimized.

Figure 2.3 Hybrid CMOS – BJT transistor topology.

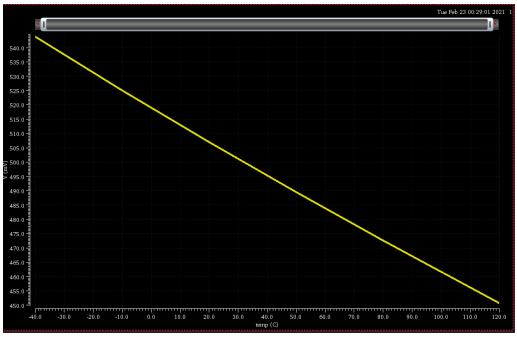

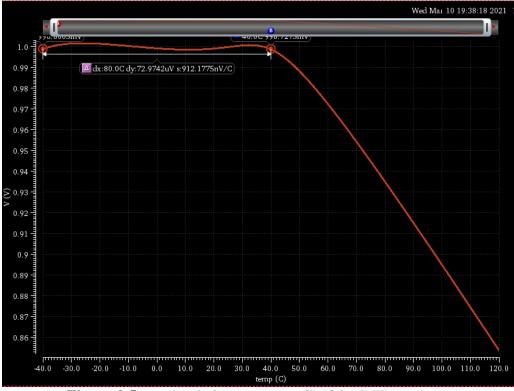

The first simulation draft was performed to observe the effect of the temperature on  $V_{ref}$ . The simulation was performed on the Virtuoso environment using the Spectre simulator and the values shown in Table 2.1 and Table 2.4.

A DC analysis was done, taking the temperature as a sweep variable from -40 °C to 120 °C. Corresponding responses for both circuits are shown in Table 2.2, Fig. 2.4, and 2.5.

| Topology     | M1, M2,<br>M6, M7<br>[µm] | M4,<br>M5<br>[μm] | M3<br>[μm] | M8<br>[μm] | R1<br>[kΩ] | R2<br>[kΩ] |

|--------------|---------------------------|-------------------|------------|------------|------------|------------|

| FULL<br>CMOS | 28.8                      | 2                 | 180        | 2          | 25         | 22         |

**Table 2.1** Values to be testes on Virtuoso for the Full CMOS Technology.

Figure 2.4 V<sub>ref</sub> simulation response. Full CMOS topology.

Figure 2.5 V<sub>ref</sub> simulation response. CMOS - BJT topology.

| Topology | Vref Max | Vref Min | Min Temp | Max Temp | Voltage        |

|----------|----------|----------|----------|----------|----------------|

|          | [mV]     | [mV]     | [ °C ]   | [ °C ]   | Variation [mV] |

| First    | 540      | 450      | -40      | 120      | 90             |

| Second   | 990      | 860      | -40      | 120      | 130            |

Table 2.2 V<sub>ref</sub> results after first simulation draft on Virtuoso.

#### 2.2.1 Topologies Optimization

After the simulation draft, the full CMOS topology (first one) was optimized. Even with the optimization process, the  $V_{\text{ref}}$  response exhibits a big variation between  $V_{\text{ref MAX}}$  and  $V_{\text{ref MIN}}$ . For this reason, the full CMOS topology was no longer used.

| Model   | V <sub>ref</sub> Max<br>[mV] | V <sub>ref</sub> Min<br>[mV] | Voltage at<br>Room<br>[mV] | Min Temp<br>[ °C ] | Max Temp<br>[ °C ] | Voltage<br>Variation<br>[mV] |

|---------|------------------------------|------------------------------|----------------------------|--------------------|--------------------|------------------------------|

| OPT - 1 | 1380                         | 1060                         | 1190                       | -40                | 120                | 320                          |

| OPT - 2 | 830                          | 755                          | 776                        | -40                | 120                | 75                           |

| OPT - 3 | 1090                         | 910                          | 975                        | -40                | 120                | 180                          |

| OPT - 4 | 1070                         | 900                          | 965                        | -40                | 120                | 170                          |

| OPT - 5 | 1120                         | 920                          | 995                        | -40                | 120                | 200                          |

| OPT - 6 | 1170                         | 940                          | 1020                       | -40                | 120                | 770                          |

| OPT - 7 | 701                          | 687                          | 688                        | -40                | 120                | 4                            |

| OPT - 8 | 670                          | 661                          | 662                        | -40                | 120                | 9                            |

Table 2.3 V<sub>ref</sub> results after optimization were applied on Full CMOS topology.

As mentioned previously, the main purpose of this BGR is to be part of an ADC for biosensors applications, for this reason, the stability of  $V_{ref}$  is critical. A maximum variation on  $V_{ref}$  must be under ±500 µV. Simulation results have shown that hybrid CMOS – BJT topology performs better than the Full CMOS topology, showing a voltage variation of ±72 µV, during the early temperature range, from -40 °C to 40 °C. Then, optimization techniques were applied to the CMOS – BJT topology to obtain the desired  $V_{ref}$ .

To optimize the hybrid CMOS – BJT topology, a surrogate-based optimization technique was applied. First, a set of training points was obtained to develop a surrogate model. Five surrogate model techniques were implemented: polynomial surrogate models, response surface methodology, support vector machines, Kriging, and generalized regression neural networks.

By using the best-performed surrogate model, a direct optimization technique (such as nelder mead, pattern search, and genetic algorithms) was applied to obtain the desired  $V_{ref}$  response. The optimization techniques used on the CMOS – BJT topology was the one called surrogate based optimization (Chávez-Hurtado, Rayas-Sánchez, & Brito-Brito, 2016).

After each surrogate-based optimization process, the final value was used as a seed value to generate a new surrogate model and restart the optimization process. This was done consecutively until the specification design was achieved. These groups of values were called "Center" and are shown in Table 2.4 (Chávez-Hurtado & Rayas-Sánchez, 2016).

| Center      | M0, M1,<br>M10, M15<br>[μm] | M2, M3,<br>M4, M5,<br>M6, M7,<br>M8, M9<br>[µm] | Q1,<br>Q2, Q3<br>[µm] | R1<br>[kΩ]  | R2<br>[kΩ] | R3<br>[kΩ]  | R4<br>[kΩ]  | R5, R6<br>[kΩ] | R7<br>[kΩ]  | R8,<br>R9,<br>R10,<br>[kΩ] | R11<br>[kΩ] | R12<br>[kΩ] |

|-------------|-----------------------------|-------------------------------------------------|-----------------------|-------------|------------|-------------|-------------|----------------|-------------|----------------------------|-------------|-------------|

| Center<br>1 | 2.866                       | 10.9847                                         | 10                    | 13.717<br>9 | 59.58      | 12.014<br>4 | 43.085<br>8 | 156.52         | 54.621<br>6 | 7.8185                     | 19.8<br>9   | 31.2<br>5   |

| Center 2    | 3                           | 10                                              | Х                     | 14.5        | Х          | 13.200<br>2 | 45.148<br>7 | Х              | 57.015<br>4 | 8.2307                     | Х           | Х           |

| Center<br>3 | 2.85                        | 9.5                                             | Х                     | 13.775      | Х          | 12.540<br>1 | 42.891<br>2 | Х              | 54.193<br>1 | 7.8192                     | Х           | Х           |

| Center<br>4 | 2.8785                      | 9.595                                           | Х                     | 13.912<br>7 | Х          | 12.665<br>5 | 43.320<br>1 | Х              | 54.735<br>0 | 7.8974                     | Х           | Х           |

**Table 2.4** Transistors and resistors values taken as center after simulation techniques.

After the first optimization process, it was found that components Q1, Q2, Q3, R2, R5, R6, R11, and R12 are in their ideal value, then these components were no longer included in the following optimization process.

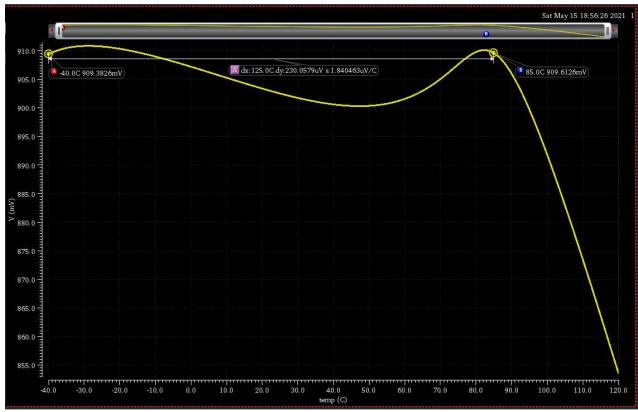

Due to the long temperature range, from -40 °C to 120 °C, it was not possible to find an optimal solution, then, the maximum temperature was reduced to 85 °C, since this new temperature range still complies with the biosensor applications. The optimal component values, shown in Table 2.5, correspond to the best response on  $V_{ref}$  for this topology.

| Center | M0, M1,<br>M10, M15<br>[μm] | M2, M3,<br>M4, M5,<br>M6, M7,<br>M8, M9<br>[µm] | Q1,<br>Q2, Q3<br>[µm] | R1<br>[kΩ] | R2<br>[kΩ] | R3<br>[kΩ] | R4<br>[kΩ] | R5, R6<br>[kΩ] | R7<br>[kΩ] | R8,<br>R9,<br>R10,<br>[kΩ] | R11<br>[kΩ] | R12<br>[kΩ] |

|--------|-----------------------------|-------------------------------------------------|-----------------------|------------|------------|------------|------------|----------------|------------|----------------------------|-------------|-------------|

| BGR    | 2.90                        | 9.69                                            | 10                    | 14.05      | 59.58      | 12.79      | 43.75      | 126.52         | 55.28      | 7.97                       | 79.89       | 31.25       |

| Table 2.5 CMOS – BJT topology | v values for the best respond on | V <sub>ref</sub> . |

|-------------------------------|----------------------------------|--------------------|

|-------------------------------|----------------------------------|--------------------|

Figure 2.6 Graph from V<sub>ref</sub> using the finals BGR values.

| Model | V <sub>ref Max</sub><br>[mV] | V <sub>ref Min</sub><br>[mV] | Voltage at<br>Room<br>[mV] | Min Temp<br>[ °C ] | Max Temp<br>[ °C ] | Voltage<br>Variation<br>[µV] |

|-------|------------------------------|------------------------------|----------------------------|--------------------|--------------------|------------------------------|

| BGR   | 909.6126                     | 909.3826                     | 230                        | -40                | 85                 | 230.0579                     |

Table 2.6 V<sub>ref</sub> respond using the values on BGR model.

## 2.3. BGR PVT Analysis

In order to guarantee that our chip properly works in all the possible operable conditions, we must simulate it at different values of process, voltage, and temperature. These conditions are called PVT corners (TemplatesYard, 2020).

These variations will effect operational conditions like threshold voltage since PVT corners affect parameters like doping concentration, surface potential, channel length, oxide thickness, temperature, source-to-body voltage, implant impurities, among others (TemplatesYard, 2020).

### 2.3.1 PVT Corner Implementation

For the PVT corner analysis, the supply voltage was not modified due to the complete BGR circuit was calculated to give a  $V_{ref}$  of 900 mV ±500  $\mu$ V using a supply voltage of 1.8 V. For that reason the PVT corner analysis includes only variations on process and temperature.

| Corner Name              | Process | Temperature | Voltage |

|--------------------------|---------|-------------|---------|

| Comer Name               | 1100035 | [ °C ]      | [V]     |

| tmsc018_tt_1p8V_Tri_Temp | tt      | -40         | 1.8     |

| tmsc018_tt_1p8V_Tri_Temp | tt      | 27          | 1.8     |

| tmsc018_tt_1p8V_Tri_Temp | tt      | 85          | 1.8     |

| tmsc018_ff_1p8V_Tri_Temp | ff      | -40         | 1.8     |

| tmsc018_ff_1p8V_Tri_Temp | ff      | 27          | 1.8     |

| tmsc018_ff_1p8V_Tri_Temp | ff      | 85          | 1.8     |

| tmsc018_ss_1p8V_Tri_Temp | SS      | -40         | 1.8     |

| tmsc018_ss_1p8V_Tri_Temp | SS      | 27          | 1.8     |

| tmsc018_ss_1p8V_Tri_Temp | SS      | 85          | 1.8     |

Table 2.7 PVT Corner performed on the CMOS – BJT topology for tt, ff, and ss process.

| Corner Name              | Process | Temperature | Voltage |

|--------------------------|---------|-------------|---------|

|                          | 1100035 | [ °C ]      | [V]     |

| tmsc018_sf_1p8V_Tri_Temp | sf      | -40         | 1.8     |

| tmsc018_sf_1p8V_Tri_Temp | sf      | 27          | 1.8     |

| tmsc018_sf_1p8V_Tri_Temp | sf      | 85          | 1.8     |

| tmsc018_fs_1p8V_Tri_Temp | fs      | -40         | 1.8     |

| tmsc018_fs_1p8V_Tri_Temp | fs      | 27          | 1.8     |

| tmsc018_fs_1p8V_Tri_Temp | fs      | 85          | 1.8     |

Table 2.8 PVT Corner performed on the CMOS – BJT topology for sf, and fs process.

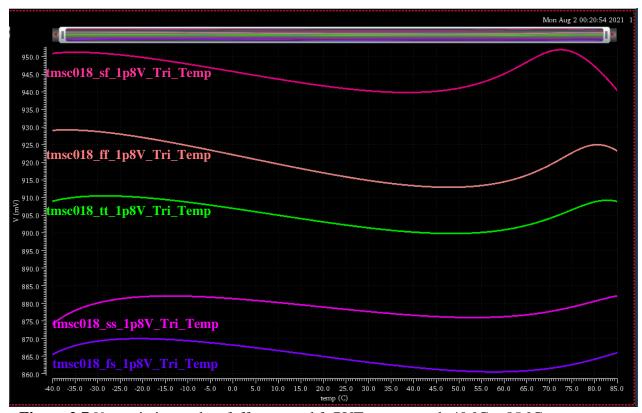

**Figure 2.7**  $V_{\text{ref}}$  variation under sf, ff, tt, ss and fs PVT corners and -40 °C – 85 °C temperature range.

As shown in Fig 2.7, the temperature variation does not affect the circuit performance, it can be seen that the three temperature plots are overlapped. However, the model variation has a huge effect on the  $V_{ref}$  voltage, where models such as slow-fast and fast-slow correspond to the worst performance case.

The voltage variation between models slow-fast and fast-slow is 81.7735 mV. The fast-fast model is the closest one to the typical case, exhibiting a voltage variation of 18.2763 mV.

Taking into consideration the PVT results, and how they affect the  $V_{ref}$  voltage on the BGR, only the typical model will be taken into consideration for the test inside the SAR ADC system.

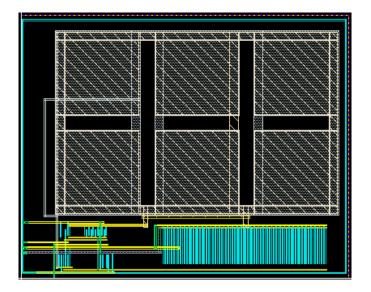

## 2.4. BGR Physical Design

#### 2.4.1 Layout and Verification

The Bandgap Layout was developed using Virtuoso Tools. The Layout XL imports the cell view of each component from the Bandgap schematic shown in Fig. 2.8.

Figure 2.8 Bandgap reference schematic.

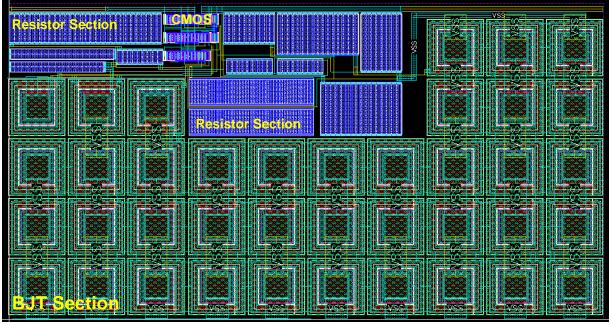

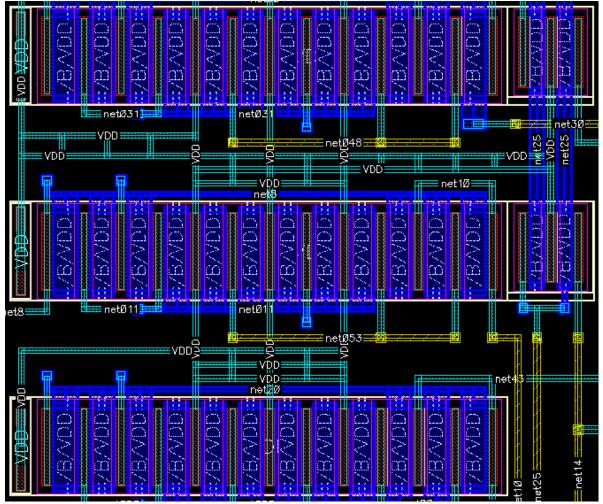

The placement of the components and routing was made manually. The height for the BGR were chosen considering the height of a standard cell in  $0.18\mu m$  CMOS technology, shown in Table 2.9. The BGR has a height of 140.48  $\mu m$  which is 32 times a standard cell height.

|               | Height [µm] | Base [µm] | Times |

|---------------|-------------|-----------|-------|

| Standard Cell | 4.39        | N/A       | 1     |

| BGR           | 140.48      | 264.18    | 32    |

Table 2.9 BandGap Reference dimension and comparation with standard cell.

Figure 2.9 BandGap layout after placement and routing.

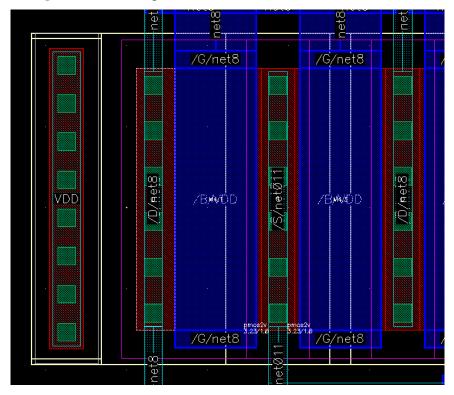

For routing components, metals 1, 2, and 3 were used. The pins were made using metal 3. As shown in Fig. 2.9, a big amount of the area corresponds to BJT transistors. Resistors were implemented using high resistance polysilicon resistor (nrhpoly) available in the TSMC18 process, and a finger technique was applied to them to reduce the final length.

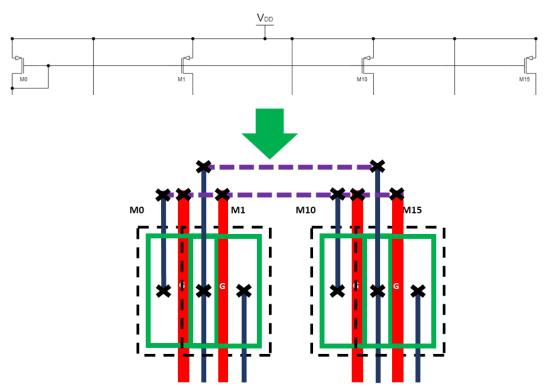

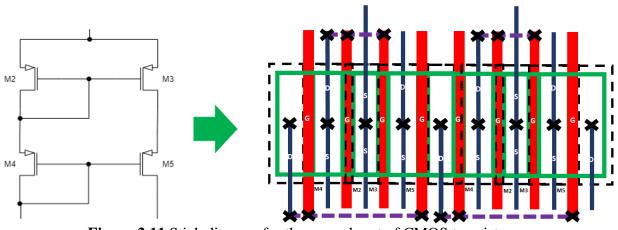

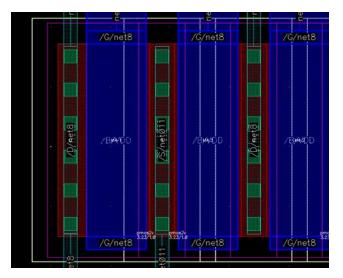

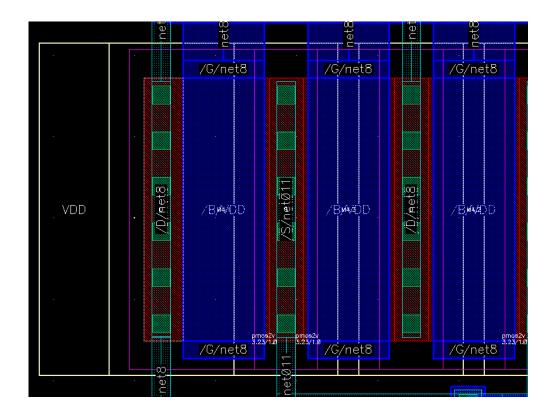

Before performing the layout of the BGR circuit, a stick diagram was developed to visualize the placement of CMOS transistors. In order to improve matching, the CMOS transistors were divided on fingers and arrayed using interdigitated techniques, as shown in Fig. 2.10 and 2.11.

Figure 2.10 Stick diagram for the first part of CMOS transistors.

Figure 2.11 Stick diagram for the second part of CMOS transistors.

Figure 2.12 CMOS Section routed and using interdigitated techniques on transistors.

#### 2.4.2 Design Rule Checking (DRC)

The layout must be drawn according to strict design rules. After the routing and placement have been finished, an automatic program will check each and every polygon in the BGR against the design rules. This process is called Design Rule Checking (DRC) and MUST be done for the BGR layout to ensure it will function properly when fabricated (AMSaC Lab Group, 2021). All the DRC errors were corrected during the layout design. One of these errors found during DRC checking is described in Appendix A. This is reported because it is not a common error in the layout of analog cells and its documentation can serve other designers as a guide for correcting this error.

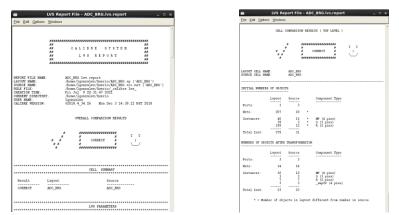

#### 2.4.3 Layout vs Schematic (LVS)

The next step in debugging the layout is to compare the netlist extracted from the layout with the schematic to ensure the BGR layout is an identical match to the cell schematic (AMSaC Lab Group, 2021). Just a few errors were reported by the LVS tool but were corrected without problems. Figure 2.13 shows the final LVS report in which we can appreciate that the BGR layout is LVS error free.

Figure 2.13 LVS report once the errors were corrected.

## 3. Serial Peripheral Interface Module

The serial peripheral interface (SPI) module was designed by describing the hardware on Verilog language using the Quartus IDE by Intel. Simulations of the description were performed on ModelSim. This SPI module is part of a low-power ADC for Biosensor applications.

### 3.1. Introduction

The SPI is one of the most widely used interfaces between the microcontroller and IC peripherals, such as sensors, ADCs, DACs, shift registers, SRAM, among others. The SPI module is asynchronous communication, full-duplex master-slave interface (Dhaker, 2018).

### 3.2. SPI Module Development

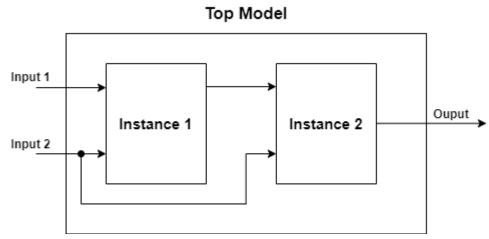

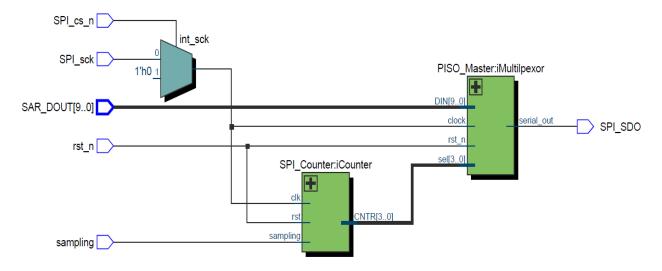

The SPI module was designed using Quartus IDE. The SPI module has two instantiations inside, one called PISO Master, and a second one called SPI Counter (Fig. 3.1).

Once the code has been finished, the IDE gives a graphic representation of each instance and its connection inside a top model. This is called Register Transfer Level (RTL) Block Diagram. It is shown in Fig. 3.2.

Figure 3.1 Graphic representation of instantiation.

Figure 3.2 RTL Block Diagram of the SPI Module.

#### 3.2.1 SPI Module

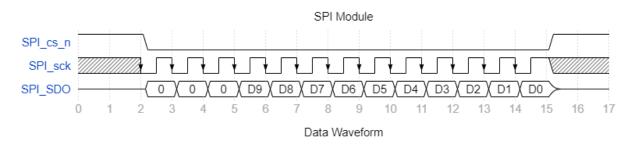

This is the main module, also called Top Model. It receives the main signal to start to work such as SPI\_cs\_n, SPI\_sck, rst\_n,...etc. As mentioned before this module works similar to SPI communication, therefore once the chip – select signal (CS) is in a low state, the clock signal (SCK) is available for the rest of the instances. Both signals are handled externally and should comply with SPI communication standards.

#### 3.2.2 PISO Master

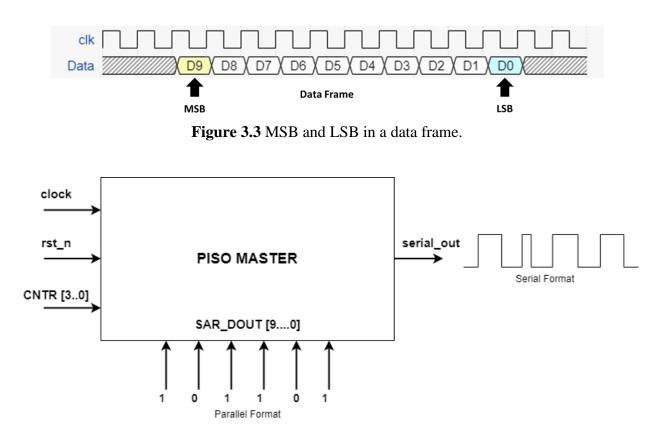

The PISO Master is a module that handles the data that will be sent. After the clock signal is available, the module receives data composed of 10 bits from the SAR module, through the SAR\_DOUT [9...0] signal, in a parallel format (Fig. 3.4). The PISO receives the data and allocates the most significant bit (MSB) to the serial data out (SDO) signal. This process continues until the PISO allocates the low significant bit (LSB) on the SDO signal (Fig. 3.5). Once the bits are on the SDO, they can be managed externally in a serial format.

Figure 3.5 PISO Master block diagram functionality.

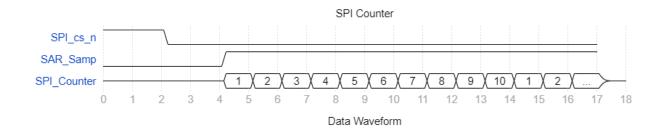

#### 3.2.3 SPI Counter

The SPI counter counts the number of bits for the PISO Master. This module is active after the CS is in a low state and the clock signal is available. After the clock is available the module waits until the sampling signal is in a high state (Fig. 3.6). The sampling is in a high state once the SAR has started with the conversions.

Figure 3.6 SPI Counter data waveform description.

### 3.3. SPI ModelSims Simulation Results

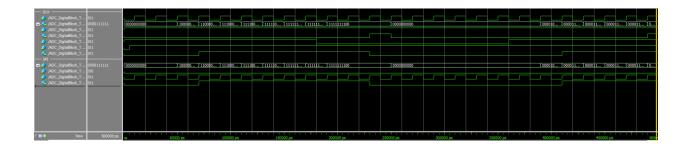

The simulation of the SPI Module was performed on ModelSim, a tool from Siemens that makes a representation of the bench test. The bench test code was developed in Verilog. All the signals have an initial value or reset state to have a known state.

During the simulation, ten different data were sent. All data changes just the bit that will be sent e.g. the first data has just the D9 on 1 and the rest of them in 0, the second one has the D8 on 1 and the rest on 0. this sequence continues until the LSB is sent (Fig. 3.7).

| #10 | SAR_DOUT | 10'b10_0000_0000; |

|-----|----------|-------------------|

| #10 | SAR_DOUT | 10'b01_0000_0000; |

| #10 | SAR_DOUT | 10'b11_0111_1111; |

| #10 | SAR_DOUT | 10'b00_0100_0000; |

| #10 | SAR_DOUT | 10'b11_1101_1111; |

| #10 | SAR_DOUT | 10'b11_1110_1111; |

| #10 | SAR_DOUT | 10'b00_0000_1000; |

| #10 | SAR_DOUT | 10'b00_0000_0100; |

| #10 | SAR_DOUT | 10'b11_1111_1101; |

| #10 | SAR_DOUT | 10'b00_0000_0001; |

|     |          |                   |

Figure 3.7 Sequence of data to be sent.

Before running the simulation, ModelSim reviews the code to identify no typos or any other issues. Once the design has no errors the simulation can be performed (Fig. 3.8).

| Wave - Default |           | 1         |   | 1 |        |        |        |        |        |        |        |        |         |           |   |  |

|----------------|-----------|-----------|---|---|--------|--------|--------|--------|--------|--------|--------|--------|---------|-----------|---|--|

| 💫 🗸            | Msgs      |           |   |   |        |        |        |        |        |        |        |        |         |           |   |  |

| 🔷 rst_n        | 1         |           |   |   |        |        |        |        |        |        |        |        |         |           |   |  |

| I SPI_sck      | 0         |           |   |   |        |        |        |        |        |        |        |        |         |           |   |  |

| SPI_cs_n       | 0         |           |   |   |        |        |        |        |        |        |        |        |         |           |   |  |

| In sampling    | 1         |           |   | l |        |        |        |        |        |        |        |        |         |           |   |  |

| E-             | 111111110 | 000000000 | 0 |   | 100000 | 010000 | 110111 | 000100 | 111101 | 111110 | 000000 | 000000 | 1111111 | 000000000 | 1 |  |

|                | 1         |           |   |   |        |        |        |        |        |        |        |        |         |           |   |  |

|                | 1         |           |   |   |        |        |        |        |        |        |        |        |         | ļ         |   |  |

|                | 1         |           |   |   |        |        |        |        |        |        |        |        |         | ļ         |   |  |

|                | 1         |           |   |   |        |        |        |        |        |        |        |        |         |           |   |  |

|                | 1         |           |   |   |        |        |        |        |        |        |        |        |         | 1         |   |  |

|                | 1         |           |   |   |        |        |        |        |        |        |        |        |         | ļ         |   |  |

|                | 1         |           |   |   |        |        |        |        |        |        |        |        |         | ļ         |   |  |

|                | 1         |           |   |   |        |        |        |        |        |        |        |        |         | 1         |   |  |

|                | 1         |           |   |   |        |        |        |        |        |        |        |        |         |           |   |  |

| L              | 0         |           |   |   |        |        |        |        |        |        |        |        |         |           |   |  |

| I SPI_SDO      | St0       |           |   |   |        |        |        |        |        |        |        |        |         |           |   |  |

Figure 3.8 SPI Module simulation.

## 3.4. SPI Module Integration with SAR

After the simulation is working as expected, the SPI Module is imported to Virtuoso. Using the Verilog option on the cell view, Virtuoso creates a black box that recreates the functionality of the Verilog code in the Virtuoso environment (Fig. 3.9).

Figure 3.9 SPI Module Figure created by Virtuoso

Figure 3.10 SPI and SAR integration waveform.

Once the integration was made, and the SAR and SPI's waveforms were reviewed (Fig. 3.10), the results indicate that after three clock cycles the first bit, means the MSB, will be sent through SPI SDO to be handled externally (Fig. 3.11).

Figure 3.11 SPI and SAR integration results.

# 4. ADC Integration

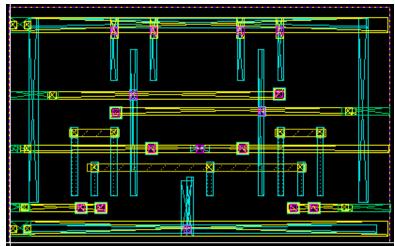

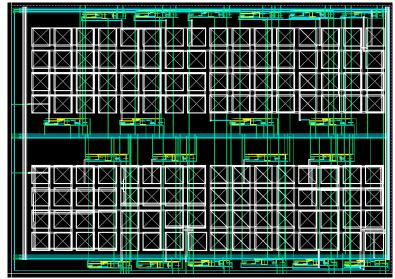

## 4.1. Logic Synthesis

Logic synthesis transforms behavioral hardware description language (HDL) code into a *netlist* describing the hardware as a model represented by logic blocks and the connections between them. In this project, logic synthesis was done by Encounter RTL Compiler (RC) which needs several files as inputs so it can do the synthesis of the design. The output of the RC tool is a netlist and some reports with parameters like total area, fanout, total power consumption, number of used cells, etc.

To synthesize the full custom modules as the bandgap reference, dynamic comparator, bootstrap switch, and DAC capacitive, it is necessary to generate the Library Exchange Format (LEF) files of each cell. LEF Files contain information about the area of the cell, metal connection, and vias. It is the representation of the layout of the cell using coordinates.

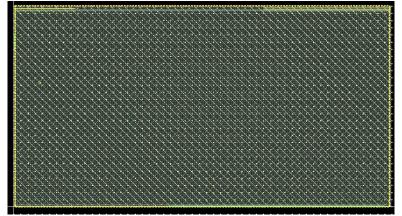

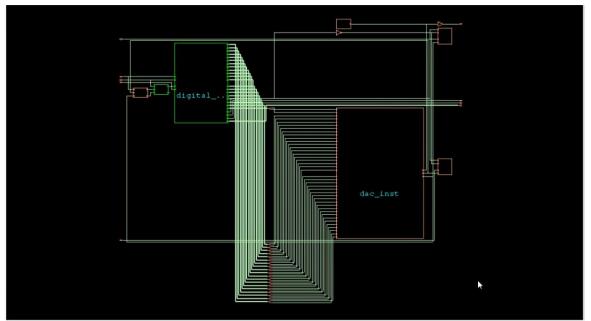

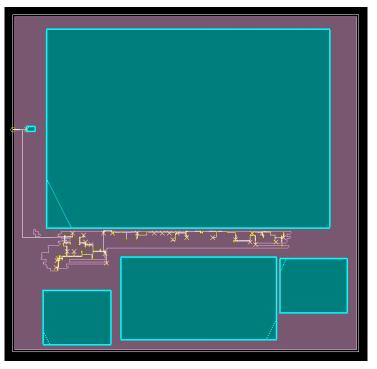

The LEF Files are generated from the abstract view of the layout once it is DRC and LVS verified. Figures 4.1 - 4.4 show the abstracts of the full custom modules of the ADC.

Figure 4.1 Boostrap Swtich Abstract.

Figure 4.2 Dynamic Comparator Abstract.

Figure 4.3 DAC Capacitive Abstract.

Figure 4.4 BandGap Abstract.

The SAR ADC was synthesized using the RC tool. For doing a logic synthesis, constraints were defined. This information can be found completely in a sdc file, but some of the most important are the next ones:

- There's only 1 clock (Main\_CLK) that works with a period of 4000 picoseconds

- Both the input and the output delay where 10% of the main clock's period

- The external driver that was used as the buffer BUFFD12BWP7T using the pin Z

- The max transition was 65% of the clock's period

- The max capacitance is 6000 femtofarads

- The maximum fanout is 50

Figure 4.5 shows the schematic of the design. There is a top module that connects all the modules that conform to the ADC, full custom modules are shown in orange color. The RTL diagram shows all connections are correct.

Figure 4.5 Schematic of Synthesized RTL.

The following reports were generated by the RC tool for the typical and worst-case after the SAR ADC were synthesized.

| Operating conditions:                                                                                                                                                                                                                                                                                                                                                                                                            | tpd018nvv<br>physical_<br>WCCOM                        | tcb018gbwp7twc 270<br>tpd018nvwc 280a<br>physical_cells<br>WCCOM                                                                                                                                                                                   |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Interconnect mode:<br>Area mode:                                                                                                                                                                                                                                                                                                                                                                                                 | global<br>physical                                     | dlobal                                                                                                                                                                                                                                             |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                        |                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| Fiming                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                        |                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                        |                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| Clock Period                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                        |                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| <br>Main Clk 4000.0                                                                                                                                                                                                                                                                                                                                                                                                              |                                                        |                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| _                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                        |                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| Cost Critical<br>Group Path Slack TNS                                                                                                                                                                                                                                                                                                                                                                                            | Paths                                                  |                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| c2c 947.2 0                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                        |                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| C2C         947.2         0           C2O         1490.4         0           default         3683.9         0           I2C         3329.5         0                                                                                                                                                                                                                                                                             | (                                                      |                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| I2C         3329.5         0           I2O         No paths         0                                                                                                                                                                                                                                                                                                                                                            | (                                                      |                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                        |                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                        |                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| Total 0                                                                                                                                                                                                                                                                                                                                                                                                                          | (                                                      | 5                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| Instance Count                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                        |                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| Instance Count                                                                                                                                                                                                                                                                                                                                                                                                                   | 249<br>t 72<br>ount 177                                | 9<br>2<br>7                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| Instance Count<br>Leaf Instance Count<br>Sequential Instance Coun<br>Combinational Instance C<br>Hierarchical Instance Co                                                                                                                                                                                                                                                                                                        | 249<br>t 72<br>ount 177                                | 9<br>2<br>7                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| Instance Count<br>Leaf Instance Count<br>Sequential Instance Coun<br>Combinational Instance C<br>Hierarchical Instance Co<br>Area<br><br>Cell Area                                                                                                                                                                                                                                                                               | 245<br>t 72<br>ount 177<br>unt 44                      | 227032.622                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| Instance Count<br><br>Leaf Instance Count<br>Sequential Instance Coun<br>Combinational Instance Co<br>Hierarchical Instance Co<br>Area<br><br>Cell Area<br>Physical Cell Area                                                                                                                                                                                                                                                    | 249<br>t 72<br>ount 177<br>unt 44                      | 9<br>2<br>7<br>4<br>227032.622<br>0.000                                                                                                                                                                                                            |  |  |  |  |  |  |

| Instance Count<br>                                                                                                                                                                                                                                                                                                                                                                                                               | 249<br>t 72<br>ount 177<br>unt 44<br>ysical)           | 227032.622<br>0.000<br>227032.622<br>2232.648                                                                                                                                                                                                      |  |  |  |  |  |  |

| Instance Count<br><br>Leaf Instance Count<br>Sequential Instance Coun<br>Combinational Instance Co<br>Hierarchical Instance Co<br>Area<br><br>Cell Area<br>Physical Cell Area<br>Total Cell Area (Cell+Ph                                                                                                                                                                                                                        | 249<br>t 72<br>ount 177<br>unt 44<br>ysical)           | 227032.622<br>0.000<br>227032.622<br>2232.648                                                                                                                                                                                                      |  |  |  |  |  |  |

| Instance Count<br>Leaf Instance Count<br>Sequential Instance Coun<br>Combinational Instance C<br>Hierarchical Instance Co<br>Area<br><br>Cell Area<br>Physical Cell Area<br>Total Cell Area (Cell+Ph<br>Net Area<br>Total Area (Cell+Physica<br>Power                                                                                                                                                                            | 249<br>t 72<br>ount 177<br>unt 44<br>ysical)           | 227032.622<br>0.000<br>227032.622<br>2232.648                                                                                                                                                                                                      |  |  |  |  |  |  |

| Instance Count<br>Leaf Instance Count<br>Sequential Instance Count<br>Combinational Instance C<br>Hierarchical Instance Co<br>Area<br>Cell Area<br>Potal Cell Area (Cell+Ph<br>Net Area<br>Total Area (Cell+Physica<br>Power<br><br>Leakage Power                                                                                                                                                                                | 249<br>t 72<br>ount 177<br>unt 44<br>ysical)           | 227032.622<br>0.000<br>227032.622<br>2232.648<br>229265.270                                                                                                                                                                                        |  |  |  |  |  |  |

| Instance Count<br>Leaf Instance Count<br>Sequential Instance Coun<br>Combinational Instance C<br>Hierarchical Instance Co<br>Area<br><br>Cell Area<br>Physical Cell Area<br>Total Cell Area (Cell+Ph<br>Net Area<br>Total Area (Cell+Physica<br>Power<br>                                                                                                                                                                        | 249<br>t 72<br>ount 177<br>unt 44<br>ysical)           | 227032.622<br>0.000<br>227032.622<br>2232.648<br>229265.270                                                                                                                                                                                        |  |  |  |  |  |  |

| Instance Count<br>Leaf Instance Count<br>Sequential Instance Coun<br>Combinational Instance C<br>Hierarchical Instance C<br>Physical Cell Area<br>Potal Cell Area (Cell+Ph<br>Net Area<br>Total Area (Cell+Physica<br>Power<br><br>Leakage Power<br>Dynamic Power<br>Total Power                                                                                                                                                 | 249<br>t 72<br>ount 177<br>unt 44<br>ysical)           | 227032.622<br>0.000<br>227032.622<br>2232.648<br>229265.270<br>0.139 uW<br>2148.675 uW<br>2148.814 uW                                                                                                                                              |  |  |  |  |  |  |

| Instance Count<br>Leaf Instance Count<br>Sequential Instance Coun<br>Combinational Instance C<br>Hierarchical Instance C<br>Area<br><br>Cell Area<br>Physical Cell Area<br>Total Cell Area (Cell+Ph<br>Net Area<br>Total Cell Area (Cell+Physica<br>Power<br><br>Leakage Power<br>Dynamic Power<br>Total Power<br>Max Fanout<br>Min Fanout                                                                                       | 249<br>t 72<br>ount 177<br>unt 44<br>ysical)           | 227032.622<br>0.000<br>227032.622<br>2232.648<br>229265.270<br>0.139 uW<br>2148.675 uW<br>2148.814 uW<br>68 (ADC_SPI_sck)<br>0 (digital_inst/sar_lp_inst/DobleRegs/sw9n/SW_ctrl[0])                                                                |  |  |  |  |  |  |

| Instance Count<br>Leaf Instance Count<br>Sequential Instance Count<br>Combinational Instance C<br>Hierarchical Instance Co<br>Area<br><br>Cell Area<br>Physical Cell Area<br>Total Cell Area (Cell+Physica<br>Total Area (Cell+Physica<br>Fower<br><br>Leakage Power<br>Dynamic Power<br>Total Power<br>Max Fanout                                                                                                               | 249<br>t 72<br>ount 177<br>unt 44<br>ysical)           | 227032.622<br>0.000<br>227032.622<br>2232.648<br>229265.270<br>0.139 uW<br>2148.675 uW<br>2148.814 uW<br>68 (ADC_SPI_sck)                                                                                                                          |  |  |  |  |  |  |

| Instance Count<br>Leaf Instance Count<br>Sequential Instance Count<br>Combinational Instance C<br>Hierarchical Instance C<br>Area<br><br>Cell Area<br>Physical Cell Area<br>Total Cell Area (Cell+Ph<br>Net Area<br>Total Area (Cell+Physica<br>Power<br><br>Leakage Power<br>Dynamic Power<br>Total Power<br>Max Fanout<br>Min Fanout<br>Average Fanout<br>Terms to net ratio<br>Terms to net ratio                             | 249<br>t 72<br>ount 177<br>unt 44<br>ysical)           | 227032.622<br>0.000<br>227032.622<br>2232.648<br>229265.270<br>0.139 uW<br>2148.675 uW<br>2148.814 uW<br>68 (ADC_SPI_sck)<br>0 (digital_inst/sar_lp_inst/DobleRegs/sw9n/SW_ctrl[0])<br>2.5<br>3.3<br>3.6                                           |  |  |  |  |  |  |

| Instance Count<br>Leaf Instance Count<br>Sequential Instance Coun<br>Combinational Instance C<br>Hierarchical Instance C<br>Area<br><br>Cell Area<br>Physical Cell Area<br>Fotal Cell Area (Cell+Ph<br>Net Area<br>Fotal Cell Area (Cell+Physica<br>Power<br><br>Leakage Power<br>Dynamic Power<br>Total Power<br>Max Fanout<br>Min Fanout<br>Average Fanout<br>Terms to net ratio<br>Terms to instance ratio<br>Runtime         | 249<br>t 72<br>ount 177<br>unt 44<br>ysical)           | 227032.622<br>0.000<br>227032.622<br>2232.648<br>229265.270<br>0.139 uW<br>2148.675 uW<br>2148.814 uW<br>68 (ADC_SPI_sck)<br>0 (digital_inst/sar_lp_inst/DobleRegs/sw9n/SW_ctrl[0])<br>2.5<br>3.3<br>3.6<br>14.996 seconds                         |  |  |  |  |  |  |

| Instance Count<br>Leaf Instance Count<br>Sequential Instance Coun<br>Combinational Instance C<br>Hierarchical Instance C<br>Area<br><br>Cell Area<br>Potal Cell Area (Cell+Ph<br>Net Area<br>Total Cell Area (Cell+Physica<br>Power<br><br>Leakage Power<br>Dynamic Power<br>Total Power<br>Max Fanout<br>Average Fanout<br>Terms to net ratio<br>Terms to instance ratio<br>Runtime<br>ELapsed Runtime<br>RC peak memory usage: | 249<br>t 72<br>ount 177<br>unt 44<br>ysical)<br>l+Net) | 227032.622<br>0.000<br>227032.622<br>2232.648<br>229265.270<br>0.139 uW<br>2148.675 uW<br>2148.814 uW<br>68 (ADC_SPI_sck)<br>0 (digital_inst/sar_lp_inst/DobleRegs/sw9n/SW_ctrl[0])<br>2.5<br>3.3<br>3.6<br>14.996 seconds<br>31 seconds<br>175.00 |  |  |  |  |  |  |

| Instance Count<br>Leaf Instance Count<br>Sequential Instance Count<br>Combinational Instance C<br>Hierarchical Instance C<br>Area<br><br>Cell Area<br>Physical Cell Area (Cell+Ph<br>Net Area<br>Total Cell Area (Cell+Physica<br>Power<br><br>Leakage Power<br>Total Power<br>Total Power<br>Max Fanout<br>Min Fanout<br>Average Fanout<br>Terms to net ratio<br>Terms to instance ratio<br>Runtime<br>Elapsed Runtime          | 249<br>t 72<br>ount 177<br>unt 44<br>ysical)<br>l+Net) | 227032.622<br>0.000<br>227032.622<br>2232.648<br>229265.270<br>0.139 uW<br>2148.675 uW<br>2148.814 uW<br>68 (ADC_SPI_sck)<br>0 (digital_inst/sar_lp_inst/DobleRegs/sw9n/SW_ctr1[0])<br>2.5<br>3.3<br>3.6<br>14.996 seconds<br>31 seconds           |  |  |  |  |  |  |

and the MEMORY\_USAGE after FINAL is 173.00 MB

| Technology libraries: tck<br>tpc<br>phy<br>Operating conditions: WCC<br>Interconnect mode: glu<br>Area mode: phy                                                                                                    | d018nvwc 280a<br>ysical_cells<br>COM                                                                                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Timing                                                                                                                                                                                                              |                                                                                                                                               |

| Clock Period                                                                                                                                                                                                        |                                                                                                                                               |

| Main_CLK 4000.0                                                                                                                                                                                                     |                                                                                                                                               |

| Cost Critical Vic<br>Group Path Slack TNS F                                                                                                                                                                         | Paths                                                                                                                                         |

| C2C         934.7         0           C2O         1348.1         0           default         3574.9         0           I2C         3250.1         0           I2O         No paths         0                       | 0<br>0<br>0<br>0                                                                                                                              |

| Total 0                                                                                                                                                                                                             |                                                                                                                                               |

| Instance Count<br><br>Leaf Instance Count<br>Sequential Instance Count<br>Combinational Instance Count<br>Hierarchical Instance Count                                                                               | 177                                                                                                                                           |

| Area                                                                                                                                                                                                                |                                                                                                                                               |

| Cell Area<br>Physical Cell Area<br>Total Cell Area (Cell+Physica<br>Net Area<br>Total Area (Cell+Physical+Net                                                                                                       | 2232.648                                                                                                                                      |

| Power                                                                                                                                                                                                               |                                                                                                                                               |

| Leakage Power<br>Dynamic Power<br>Total Power                                                                                                                                                                       | 0.139 uW<br>2150.416 uW<br>2150.556 uW                                                                                                        |

| Max Fanout<br>Min Fanout<br>Average Fanout<br>Terms to net ratio<br>Terms to instance ratio<br>Runtime<br>Elapsed Runtime<br>RC peak memory usage:<br>EDI peak memory usage:<br>Hostname<br>Final Runtime & Memory. | <pre>68 (ADC_SPI_sck) 0 (digital_inst/sar_lp_inst/DobleRegs/sw9n/SW_ctr1[0]) 2.5 3.3 3.6 13.993 seconds 26 seconds 175.00 no_value FV00</pre> |

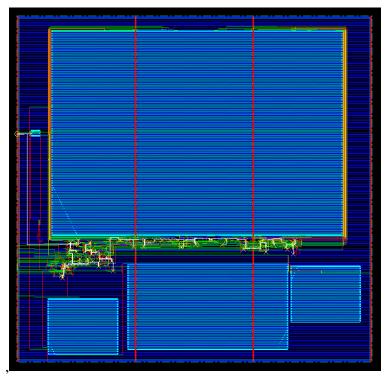

From this synthesis report, themain clock, Main\_CLK, was used for both cases with a 4000ps period, therefore working with a frequency of 250 MHz. The cost group did not show any path violation in the typical and worst case.

In this report, we can also see the number of instances that are in the design and the area that was used for design. Something that we notice is that the physical cell area is 0. To see the Physical cell area, we had to look for another report, that can be found in the next figure. We can see the area of our modules in the first 5 rows of the report.

| Generated by: Encounter(R) RTL Compiler                                                                                | /14.10-S022_1 (Sep 3 2014) |                                                |                                                                                        |  |

|------------------------------------------------------------------------------------------------------------------------|----------------------------|------------------------------------------------|----------------------------------------------------------------------------------------|--|

| Generated on: Aug 03 2021 22:04:26                                                                                     |                            |                                                |                                                                                        |  |

| Module: ADC_LP_bb                                                                                                      |                            |                                                |                                                                                        |  |