INSTITUTO DE ESTUDIOS DE POSTGRADO MÁSTER EN ENERGÍAS RENOVABLES DISTRIBUIDAS

# COST EFFECTIVE TECHNOLOGY APPLIED TO DOMOTICS AND SMART HOME ENERGY MANAGEMENT SYSTEMS

# JAVIER ALBERTO GUTIÉRREZ PEÑA

Tesis presentada a la Comisión integrada por los profesores:

DR. D. JOSÉ MARÍA FLORES ARIAS

DR. D. FRANCISCO JOSÉ BELLIDO OUTEIRIÑO

Para completar las exigencias del Máster en Energías Renovables Distribuidas

Córdoba, septiembre, 2020

## DEDICATORIA

A mi mujer, hijos, mis hermanos y mis padres sin cuya comprensión no habría podido compaginar la realización de este trabajo con mi vida profesional y personal.

#### AGRADECIMIENTOS

Agradezco a Eva María y a Javier y Juan Carlos, por el tiempo que debería haberles dedicado y en su lugar he empleado en la realización de este trabajo y en el máster.

A Rafael por la ayuda activa y el tiempo que me ha prestado para poder concluir este trabajo. A Pedro Antonio y a Charo por sus ánimos y apoyo, moral e intelectual.

A Chari y a Rafael por TODO, pues ellos me lo han dado todo, todo lo que soy; por encima de todo por los valores y educación que me han convertido en lo que soy.

A Juan Carlos, por su colaboración y acompañamiento durante esta aventura del saber.

Y a Francisco José y José María por su guía, paciencia y consejos que me han permitido mejorar en la realización de este documento; a ellos de nuevo y al resto de profesores que imparten este máster, que me ha permitido adquirir los conocimientos necesarios, parte de los cuales espero haber reflejado en este trabajo al nivel al que ellos supieron transmitirla.

## **GENERAL INDEX**

| AUT  | ORIZACIÓN DE PRESENTACIÓN DEL TRABAJO FIN DE MÁSTER                                    | ii   |

|------|----------------------------------------------------------------------------------------|------|

| DED  | ICATORIA                                                                               | vii  |

| AGR  | ADECIMIENTOS                                                                           | ix   |

| TAB  | LES INDEX                                                                              | xiii |

| LIST | OF FIGURES                                                                             | xiv  |

| RES  | UMEN                                                                                   | XV   |

| ABS  | TRACT                                                                                  | xvi  |

| 1.   | INTRODUCTION                                                                           | 1    |

| 2.   | PREVIOUS CONCEPT - SHEMS OVERVIEW                                                      |      |

|      | 2.1 SHEMS BASIC ARCHITECTURE                                                           |      |

|      | 2.2. SHEMS Infrastructure                                                              |      |

|      | 2.3. Energy Scheduling strategies SHEMS                                                | 7    |

| 3.   | METHODOLOGY - DOMOTICS COST EFFECTIVE ELEMENTS                                         | 10   |

|      | 3.1 Sensors/Actuators boards                                                           |      |

|      | 3.1.1 ESP8266                                                                          |      |

|      | 3.1.2 ESP32                                                                            |      |

|      | 3.1.3 Raspberry PI zero W                                                              |      |

|      | 3.2 Smart Centres Technologies                                                         |      |

|      | 3.2.1. Raspberry PI:                                                                   |      |

|      | 3.2.2. Cubieboard:                                                                     |      |

|      | 3.2.3. Gooseberry PI:                                                                  | 27   |

|      | 3.3 Firmware and Software                                                              |      |

|      | 3.3.1. ESP 8266 based devices firmware                                                 | 28   |

|      | 3.3.2. SHEMS APPLICATIONS                                                              | 34   |

| 4.   | METHODOLOGY - DOMOTICS COST EFFECTIVE ELEMENTS                                         | 41   |

| 4.   | 4.1 Low Cost Domotics Application to SHEMS                                             |      |

|      | <ul><li>4.1 Low Cost Domotics Application to SHEMS</li><li>4.2 Basic example</li></ul> |      |

|      | 4.2 Dasic example                                                                      | 43   |

| 5.   | CONCLUSIONS AND FUTURE WORKS                                                           | 46   |

|      | 5.1 Conclusions                                                                        | 46   |

|      | 5.2 Future works                                                                       | 46   |

| BIBI | LIOGRAPHY                                                                              | 48   |

| A P  | PENDIX                                                                                 | 55   |

|      | ENDIX A · Esperadata SHEET                                                             |      |

| APP  | ENDIX A : Esp8266ex dATA SHEET                                                         |      |

APPENDIX B: broadcom bcM2835 PERIPHERALS

APPENDIX C: CARBONTRACK SMART GATEWAY SPECIFICATIONS

APPENDIX D: CARBONTRACK SMARTPLUG SPECIFICATIONS

APPENDIX E: CARBONTRACK SMART THERMOSTAT ESPECIFICATIONS

APPENDIX F: CARBONTRACK CLIMATE COMMAND SPECIFICATIONS

APPENDIX G: ESP32 SERIES DATASHEET

APPENDIX H: SONOFF SCHEMATICS

# TABLES INDEX

| Table 1: Raspberry PI models (cost, year, SoC, GPU and memory) | 23 |

|----------------------------------------------------------------|----|

| Table 2: Raspberry PI models (interfaces, GPIOs, power)        |    |

| Table 3: "SHEMS best price" project budged                     | 45 |

| Table 4: "SHEMS best price" Return Of Investment (ROI)         | 45 |

# LIST OF FIGURES

| Figure 1 - From consumer to microgrid evolution [2].                         | 1   |

|------------------------------------------------------------------------------|-----|

| Figure 2 - Overall architecture of a representative SHEMS [7].               | 3   |

| Figure 3 - Block Diagram of the Smart Home System [24]                       |     |

| Figure 4 - Block Diagram of Air Condition Fuzzy-ANN Controlling Unit [24]    | 9   |

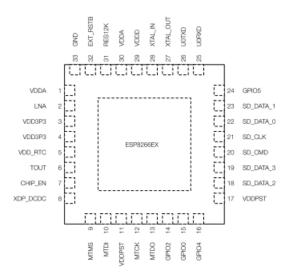

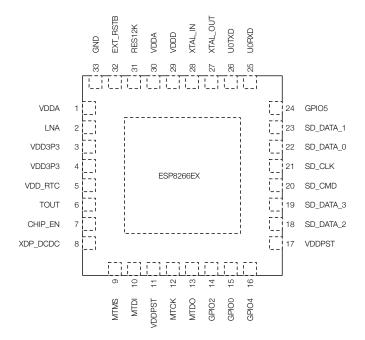

| Figure 5 - ESP 8266 pinlayout (top view) [25]                                |     |

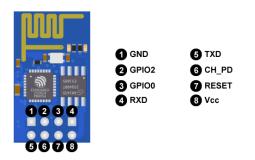

| Figure 6 - ESP01 main components (back view) [26]                            | .11 |

| Figure 7 - ESP01 pins function [27]                                          | .12 |

| Figure 8 - ESP05 upper view [28]                                             | .12 |

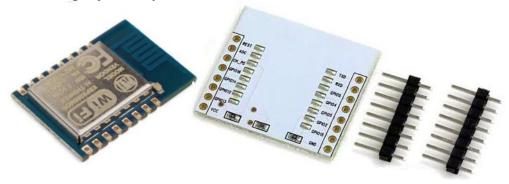

| Figure 9 - ESP12 and adapter plate (mounting board), upper view [28]         | .12 |

| Figure 10 - ESP201 upper view [28]                                           |     |

| Figure 11 - Typical board for using with NodeMCU firmware [28]               | .13 |

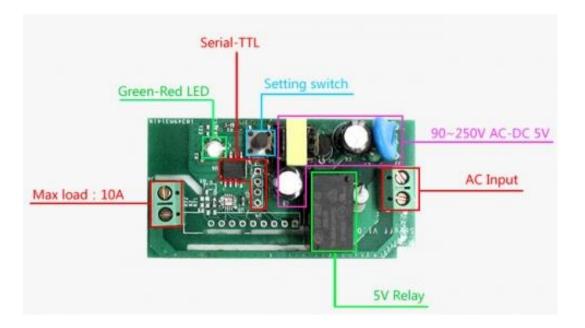

| Figure 12 - SonOff Basic device [28]                                         | .14 |

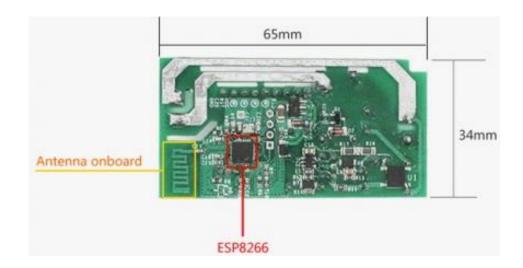

| Figure 13 - SonOff Basic R1 main components and functions [29]               | .14 |

| Figure 14 - SonOff Basic R1 dimensions [29]                                  | .15 |

| Figure 15 - SonOff Basic R1 pinout [29]                                      |     |

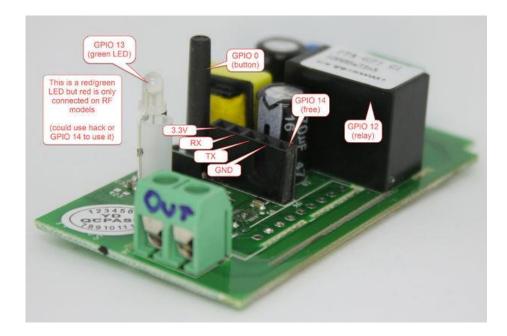

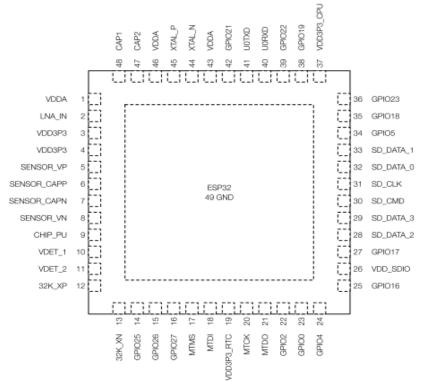

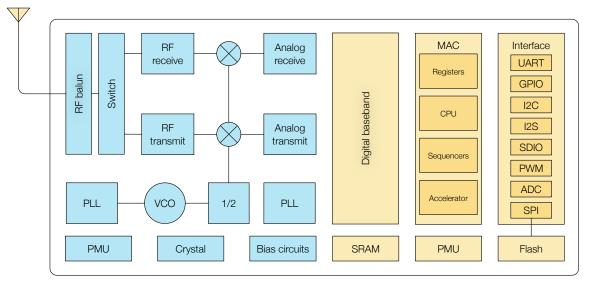

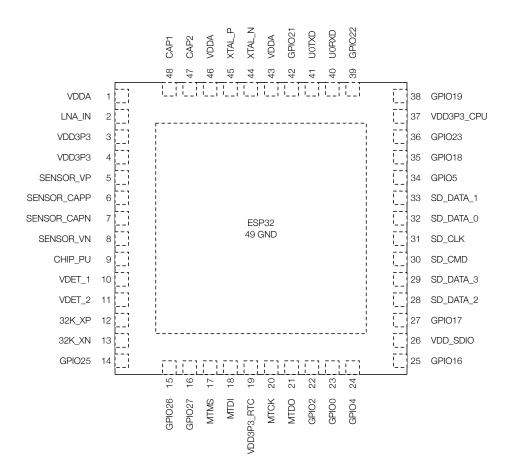

| Figure 16 - ESP32 pin layout (QFN 6*6, top view) [32]                        | .17 |

| Figure 17 - ESP32 Function block diagram [36]                                | .18 |

| Figure 18 - ESP32 DEVKIT DOIT top view [28]                                  | .19 |

| Figure 19 - Wemos Lolin32 top view [28]                                      |     |

| Figure 20 - ESP32 SX1278 top view [28]                                       | .20 |

| Figure 21 - ESP32 CAM top view [28]                                          |     |

| Figure 22 - TTGO T-Call ESP32 top view [28]                                  | .20 |

| Figure 23 - Broadcom BCM2835 blocks diagram [43]                             | .21 |

| Figure 24 - Raspberry Pi Zero W pinout [44].                                 | .22 |

| Figure 25 - Hardwarre specifications for Raspberry Pi (model 2B) [47]        | .26 |

| Figure 26 – Tasks table page on ESPEasy [49]                                 |     |

| Figure 27 - Configuring page ESPEasy allowing to configure relay module [49] | .29 |

| Figure 28 - Configuring Wi-Fi connection for Tasmota [53]                    | .31 |

| Figure 29 - Configuring MQTT protocol in Tasmota [53].                       |     |

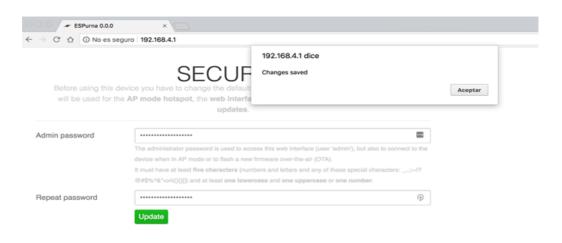

| Figure 30 - Changing password in ESPurna [56].                               |     |

| Figure 31 - General view UI for ESPurna[56].                                 | .33 |

| Figure 32 - OpeHAB UI [68].                                                  |     |

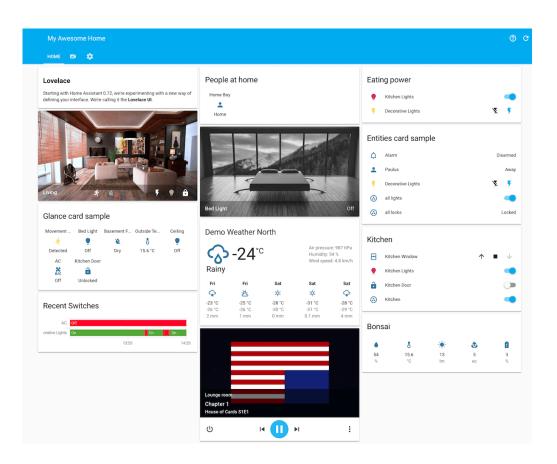

| Figure 33 - Home Assistant User Interface [71]                               |     |

| Figure 34 - Blockly example [74]                                             | .38 |

| Figure 35 - Domoticz user interface [78].                                    | .38 |

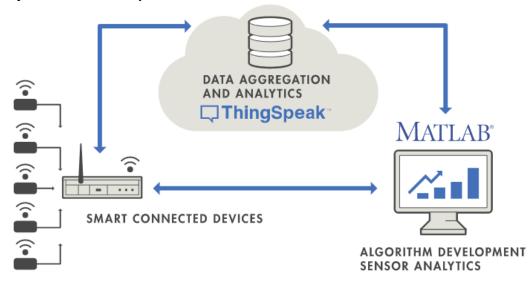

| Figure 36 - Thingspeak working flow [79].                                    | .39 |

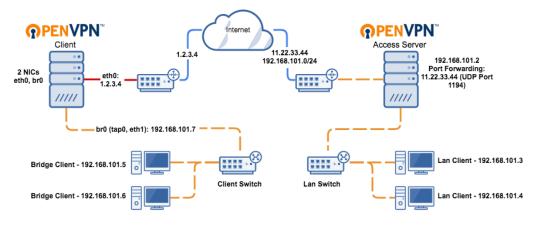

| Figure 37 – OpenVPN [82].                                                    |     |

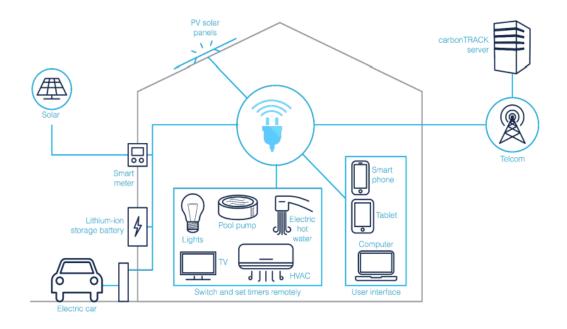

| Figure 38 - CarbonTRACK applied in SHEMS [86]                                |     |

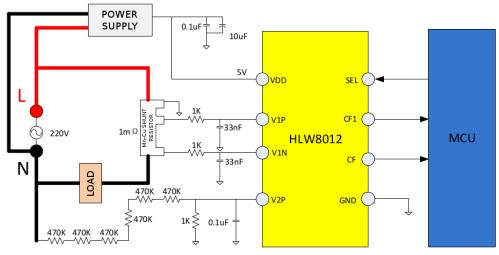

| Figure 39 - HLW8012 element on SonOff Pow R2 [89].                           |     |

| Figure 40 - Electricity hourly rate provided by official page [92]           | .43 |

| Figure 41 - Home Assistant SonOff as switch and Tasmota UI [99]              | .44 |

#### RESUMEN

En este documento se aborda el estado actual de la domótica de bajo coste disponible en el mercado actualmente y cómo aplicarlo en los sistemas inteligentes de gestión energética en la vivienda (SHEMS) permitiendo el recorte de las puntas de demanda, gestión de energías renovables y control de electrodomésticos, siempre en el contexto del bajo coste, con el objetivo de lograr la máxima difusión de los SHEMS. Adicionalmente, más allá del contexto de la tecnología SHEMS, se analizará cómo aplicar esta tecnología para aumentar la eficiencia energética de los hogares y para la supervisión de los electrodomésticos.

La gestión energética es uno de los factores principales para lograr la difusión de las energías renovables distribuidas; debido a que las fuentes de energía renovable no pueden ser planificadas, se requieren sistemas de control capaces de gestionar el intercambio de energía entre las fuentes convencionales (red eléctrica de distribución), energías renovables y dispositivos de almacenamiento energético.

Bajo esta perspectiva, este documento presenta un primer bloque en el que se exponen las bases de la arquitectura y módulos funcionales de los sistemas inteligentes de gestión energética en la vivienda (SHEMS); el siguiente paso será analizar los principios que han permitido a ciertos dispositivos convertirse en dispositivos de bajo coste.

Una vez analizada la tecnología, nos centraremos en los recursos (hardware y software) existentes que permitirán la realización de un SHEMS a bajo coste.

Conocidas las "herramientas" a nuestra disposición, se mostrará como adaptar un esquema SHEMS clásico a la tecnología de bajo coste. Primeramente, comparando de modo genérico la tecnología de bajo coste con una de las principales propuestas comerciales de SHEMS, para seguidamente desarrollar la solución de bajo coste a un caso específico real.

Palabras Claves: Domótica, bajo coste, SHEMS, Sistemas inteligentes de gestión energética en la vivienda, IoT, Internet de las cosas.

#### ABSTRACT

In this document is presented the state of art for domotics cost effective technologies available on market nowadays, and how to apply them in Smart Home Energy Management Systems (SHEMS) allowing peaks shaving, renewable management and home appliance controls, always in cost effective context in order to be massively applied. Additionally, beyond of SHEMS context, it will be also analysed how to apply this technology in order to increase homes energy efficiency and monitoring of home appliances.

Energy management is one of the milestones for distributed renewable energy spread; since renewable energy sources are not time-schedulable, are required control systems capable of the management for exchanging energy between conventional sources (power grid), renewable sources and energy storage sources.

With the proposed approach, there is a first block dedicated to show an overview of Smart Home Energy Management Systems (SMHEMS) classical architecture and functional modules of SHEMS; next step is to analyse principles which has allowed some devices to become a cost-effective technology.

Once the technology has been analysed, it will be reviewed some specific resources (hardware and software) available on marked for allowing low cost SHEMS.

Knowing the "tools" available; it will be shown how to adapt classical SHEMS to cost effective technology. Such way, this document will show some specific applications of SHEMS. Firstly, in a general point of view, comparing the proposed low-cost technology with one of the main existing commercial proposals; and secondly, developing the solution for a specific real case.

Keywords: Domotics, cost effective, SHEMS, Smart Home Energy Management System, IoT.

## 1. INTRODUCTION

Distributed renewable energy (DRE) is based on energy generation at the same point or as close as possible where it will be consumed. DRE additional to an alternative for increasing renewable energies use are an unprecedented opportunity to accelerate the transition to modern energy services in remote and rural areas [1].

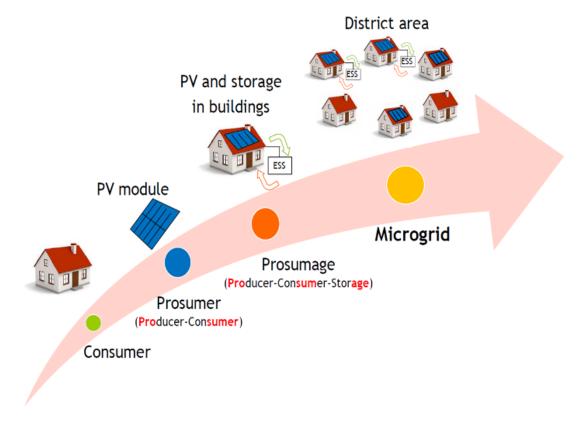

Implementing DRE systems in home, consumers become producers (prosumers). Usually, small energy store systems (ESS) are added to the individual cell (home), becoming in Prosumage:

Figure 1 - From consumer to microgrid evolution [2].

Finally, when a cluster of prosumages is created it can be considered a microgrid. But one step before conforming the microgrid, each individual cell, each home, must be capable of combining the three roles they are playing, individually. To get the higher efficiency possible a control system must be designed in order to synchronize those different roles in the best way possible, assuming the specifications for each of those roles:

• Consumers: they are connected to the wide traditional distribution grid. They must be synchronized to external grid; consuming of it the less possible in one hand, but securing the electrical supply to home, in the other hand. When it is required to consume, it must be at the lower cost possible; electrical companies offer the lower rates at peak-off periods, so, consume when the power consume is lower has a "premium" and our control system must take advantage of it. But it is not just the connection to external wide grid what needs to be

controlled. Also, each energy load, inside the home must be controlled. Each load will have some requirements: ones can be delayed and scheduled in time while others cannot (e.g. washing machine vs air conditioning); ones are critical, and others are not (e.g. fridge vs TV). Further than that, using a control system some consume patterns can be adapted to the most effective way, e.g. air conditioning can start to work before people arrives home, so that the house is over cooled in order to avoid power consumption during costly hours. And finally, home energy efficiency can be increased using the control system: in summer, activating sunshades automatically when the sun is up, and opening windows blinds when the day is cooler or regulating heaters temperature according to external temperature forecast.

• Producers: Each home can be equipped with different renewable energy sources, like photovoltaic solar and/or wind power (new technology Vortex Bladeless © [3] is allowing domestic wind energy production) and/or geothermal energy and/or thermal solar. Each of those sources has their own characteristics, but generally they are no stable, because they depend on external elements. Most of them cannot be accurately scheduled, just approximately using weather forecast. Control system must coordinate such energy sources dynamically with power consume, trying the get the best use of renewable energy, when the energy is produced, adjusting loads to the availability of those sources.

• Energy storage: Though it is not mandatory in this model, many houses can be equipped with ESS (Energy Storage Systems) which allow them to storage energy when it is more affordable and use it when it is more needed. So, when external energy is cheaper or when renewable energy is being generated but not consumed it can be stored; and it can be used when external energy is expensive or when renewable energy is not available. Also, those storage systems can have some requirements related to charging and discharging cycles. Control system must command when energy storage must be started, when must be stopped and when it must be used.

Finally, advantage can be taken on the fact that there is a network of appliances interconnected to central unit smart controller in order to develop not DRE related functions such as:

• Obtaining power consumption appliances fingerprint in order to detect deviations over the original; that deviation will indicate a wrong function before further damage is produced so they are easy to fix, and unplanned outage is avoided

• Remote start up or shut down of devices, allowing conditioning the house before arriving and/or life simulation when house is empty.

• Using voice or even just detecting presence at home (using, e.g. mobile connection to home Wi-Fi) for activating a system of devices so that when someone arrives home control system will turn on the lights, start heating systems and turn on oven for preparing dinner.

• ...

Anyway, above examples are out of this work scope, more focused to DRE than domotics; nonetheless, this possibility is pointed in order to remark the cost-effective perspective of the technology analysed, being able to be used beyond that a DRE context.

## 2. PREVIOUS CONCEPT - SHEMS OVERVIEW

At this chapter, a brief overview of classical architecture and functional modules of Smart Home Energy Management Systems is going to be carried on.

Advanced Metering Infrastructure (AMI) refers to the system composed of all devices, on both parts, consumers and utilities, which allows producers having exact data of power consumption on the demand side and consumers receive information from producers to adapt their loads to utilities requirements to get advantage of incentives in form of electricity prices and improvement in utilization efficiency of household appliances and residential energy conservation.

Hence, Smart Home Energy Management System (SHEMS) is defined as the optimal system providing energy management services in order to efficiently monitor and manage electricity generation, storage, and consumption in smart houses [4].

Sensing and actuating devices send and receive information to/from a central processor unit through the Home Area Network (HAN). Besides, SHEMS can provide not only the optimum utilization status of home appliances, but also energy storage and management services for distributed energy resources (DERs) and Home Energy Storage System (HESS) [5].

## 2.1 SHEMS BASIC ARCHITECTURE

Renewable energy Electrical power flow network

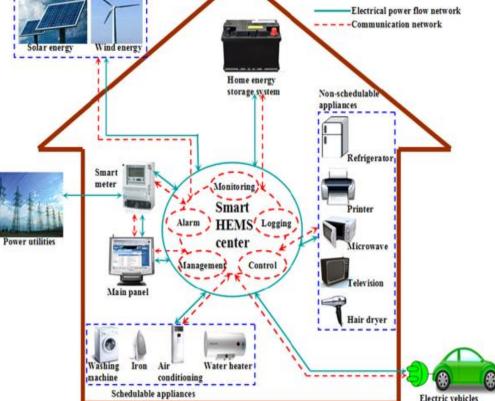

Bellow picture is showing an overall architecture of a representative SHEMS:

Figure 2 - Overall architecture of a representative SHEMS [7].

The central processor unit is called Centralized Smart Controller and provides to user with monitoring and control functionalities based on HAN.

SHEMS is collecting power consumption details from home and can communicate it to power utilities through the house gateway, which typically will be the smart meter device, owned by electric company. This house gateway can receive a demand response signal from power utilities as an input to SHEMS, and the optimization of home appliance scheduling can be implemented for the residential demand response [6].

Renewable energies are implemented in individual cells, so SHEMS must manage also their unpredictable profile; to develop this function takes relevance the electric vehicles, since EV are not only a load during charging, but also can be used as an storage mean, so that not consumed energy can be stored and used when renewable energy is not available. In this way consumers have become "prosumages", consuming, producing and storing energy.

Users can choose Human Machine Interface adapted to their specifications in order to schedule the different appliances service time or prioritize the different loads to be managed by SHEMS.

Basic functionalities provided by SHEMS system are:

• Monitoring: Offers easy access to real-time information on energy consumption and allows users to focus on the electricity saving. It can also provide display services for the operational modes and energy status of each home appliance.

• Premise energy status display service.

• Operation condition monitoring service.

• Logging: To collate and save the data information on the amount of electricity usage from appliances, generations from DERs and energy storage state. This service also contains demand response analysis for real-time prices from grid utility.

- Energy information system.

- Real time pricing related service.

• Control: There are two types of control, namely, direct control and remote control. Direct control is implemented on both the equipment and control system; whereas, remote control means customers can online access to monitor and control the usage patterns of inhome devices via handheld personal computer or smart phone from outside.

• Remote monitoring and control sservice using handheld device.

• Alarm: Alarm will be generated and sent to the SHEMS center with information on the fault locations, for example, if there is any abnormality detected.

• Home grid alarm service.

• Management: is the most important function of SHEMS to enhance the optimization and efficiency of electrical power usage in smart house. It covers a range of services including renewable energy system management service, energy storage management service, home appliance management service, and Plug-in EV and battery management service.

• Renewable energy system management service.

• Energy storage management service.

• Home appliance management service.

• Plug-in electric vehicle and battery management service.

## 2.2. SHEMS Infrastructure

Based on previously defined architecture, definition of the infrastructure of a generic SHEMS system is going to be develop, defining the following elements:

• SHEMS centre. It is the "core" of SHEMS corresponding to a Central Processor Unit, such a PC/barebone computer (Windows, iOS or Linux OS), PLC, but also a smart phone

though it must be considered that SHEMS centre needs to be permanently on home, tablet, Raspberry, ... Main functions of SHEMS centre [8]:

• Receiving a large amount of data sent by smart meters, main control panel, and real-time display. The control commands issued by the consumer are sent to all household equipment. Consequently, the automated demand response can be achieved;

• Providing a friendly human-machine interface and supporting user's real-time browsing, online monitoring, task setting and other functions to arrange the usage of electricity;

• With high scalability, the smart HEMS centre can set water, electricity, gas, and other indoor controls;

• Integrating DERs, energy storage devices and electricity regulator of EVs as well as analysing and forecasting distributed generations to achieve the optimal control of DERs.

• Developing control functions according to classical control schemes but also algorithms of fuzzy logic, neural network, genetic algorithm, ... or any other AI techniques.

• Smart meters: They allow two-direction communication; this is used, in one sense to send customer consumption and, in the other sense to provide information to consumers from power utilities and in such way consumers can optimize when turn on/off home appliances and regulate them and how to manage Distributed Energy Resources and Home Energy Storage System. Main functions for Smart Meters are [9]:

• Measuring the multi-period and multi-mode power rates of active and reactive energy metering usage;

• Supporting duplex (two-way) communication, sending data information and accepting instruction information, such as real-time information query, real-time electricity standard rates, meter upgrade program settings, etc.

• Enabling the response in terms of the requirements to achieve smart load shedding and cooperating with smart meter and smart interactive terminals during the islanding transition when a failure happens on the main power grid;

• Collecting data with smart gas meters, water meters and other versatile value-added services.

• Communication and networking systems: There are different options for implementing the required communication between the different architecture elements:

• Power Line Communication (PLC): This system takes advantage of the already laid power lines existing at home, introducing a wide band in the power network, splitting the network in power band and wide band (digital signal) by using frequency filters. Such filters are used too for avoiding digital signal going outside of home environment. For home applications, carrier signal is set between 20 and 200 kHz. But the main application nowadays in HEMS for PLC communication is for allowing smart meters two way communication between users and electric utilities; this application is called Broad Band Over Power Line (BPL, IEEE 1901-2010), being BPL Opera the wider spread standard used for smart meters and load management.

• ZigBee: It is IEE802.15.4 standard specification. MAC sublayer offers facilities that can be harnessed by upper layers to achieve the desired level of security. Main advantages of this protocol are low cost, simplicity and low power requirement (100 mW). Low power requirement implies limitation on transmission distances (10-100 meters) and low bandwidth, but this is not a problem for SHEMS where distance is limited to home area (if required further

distances, ZigBee mesh can be used) and amount of data to be transmitted is reduced (no need for a high band width. Those features have made ZigBee one of the most used protocols in home automation (and SHEMS). They can be based on mesh topologies for increasing the range, but in that case, they will need additional hardware and routers to provide user better connectivity; as such, these systems turn out to be very expensive [10]. E.g. Roomba interface works under Zigbee.

• Wi-Fi: Compared with another options, Wi-Fi is complex and requires high power; additionally, home Wi-Fi network is already congested, so that add to it more devices can be a problem. But even when Wi-Fi characteristics doesn't fit with SHEMS requirements, its huge spread and mass production has made the components less expensive than any other option in market considering Wi-Fi function already embedded in low cost Systems on a Chip (SoC) like ESP32 which is making Wi-Fi a good option for low-cost domotics. For avoiding congesting of Wi-Fi network, different solutions, as zones splitting, are present on market. Wi-Fi allows protocol MQTT, which has become the easiest way for devices communication.

• Bluetooth Low Energy: BLE has a power consume of 10 mW. Reduced range (10 m) it can be a problem, even in-home area, but latest review of Bluetooth allows Bluetooth mesh increasing the range. Components cost is the most reduced considering just communication elements (not SoC) and no mesh.

• ZWave: It consumes 1 mW, with a range of 30 meters, high scalability (above 6000 elements) and comparatively high cost. It works in 900 MHz. Each device can act as receiver and repeater. There is no interference of Wi-Fi or any other 2.4GHz wireless technology. Better interoperability than ZigBee. Complicated to work with.

• Home Appliances: There are two sides for considering home appliances: as a load (more focused on SHEMs perspective) and as a "function" to be monitor. As load perspective, they can be divided in two categories:

• Schedulable loads, which can be scheduled for optimal operation or switched on/off at any time. E.g.: washing machine, air conditioner, iron, water heater, Electric Vehicle, ... They can be sub-divided in:

• Interruptible: More easily schedulable.

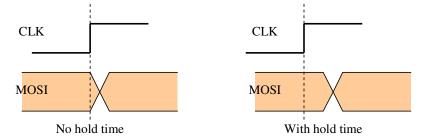

• Non-interruptible: Are constrained by fixed operation, "hold-time". Of special interest are Electric Vehicles. Expected to be widely broadcast in next years, EV can work in both directions, charging from energy source or discharging to energy source; it is called "vehicle to grid" and it will add ESS function to a majority of homes allowing peak shaving.

• Non-schedulable loads, those which need human control or presence or those critical that cannot be interrupted. e.g. lights, refrigerator, printer, microwave, television, hair dryer.

Attending to "function" point of view, home appliances can be categorized as:

• Smart home appliances: Those which can be directly using some type of digital communication based in some specific protocol and connected to SHEMS providing high degree of control level (regulation and others) and also providing high detail in home appliances information such as power consume, device self-diagnosis, timing, ... One issue with those devices is that communication protocol uses to be proprietary, not allowing easy integration with other third-party systems. Smart lighting can be included in this group, although they are adopting also standard protocols. • Traditional home appliances: They cannot be smartly controlled, in principle just ON/OFF. Nonetheless, they can be modified in order to provide more detailed control (e.g. connecting push buttons increase/decrease temperature in air conditioner to smart plugs).

• Smart plug: Acting as circuit breakers, to start-on/off different loads or connecting disconnecting power sources or batteries (or similar as EV).

• Smart regulators: Providing a variable electric variable (resistance, current, ...) to control a device.

• Smart Sensors: Providing information such as ambient temperature, individual power consumption (and even load fingerprint), light intensity, ... but also more complex sensors, like RFID for control access or even router configured to signal when some smart phone is within range.

• ESS: Energy Storage management: As already discussed, not only dedicated ESS system, but also PEV can be considered as ESS; furthermore, in terms of management, possibility of selling electric energy to grid can be also considered as ESS system, but different price rate for selling and purchasing energy must be took into account, in order to optimize energy management.

#### 2.3. Energy Scheduling strategies SHEMS

In the deregulated energy market cost reduction has acquired critical relevance; in order to reduce costs, it is important to get the energy demand as stable as possible, so the surplus generation capability is reduced to minimum and utilization of energy transmission infrastructures is maximized. At the end of the day, this is a basic economic principle: the more use of the resource the faster payoff of the investment and the better apply of economies of scale.

In order to adapt the demand so that it fit the best efficiency of the system utilities offer better prices for those periods in which the cumulative demand is lower. It can be simplified as the offer and demand law, as greater the demand is, higher the price raise.

As commented in third paragraph, section 2.1, plug-in electric vehicles (PEV) can be considered as dynamic storage systems. As also it has been commented, home renewables systems provide alternative energy sources.

So, combining all three previous factors, different strategies can be adopted attending to different objectives:

• Optimize and implement the home the home appliance scheduling with electrical energy services for the residential consumers in smart houses [11].

• The application of PEVs as dynamic energy storages with their travel patterns to coordinate the optimal home energy scheduling in a residential community has been presented in [12], [13] and [14].

• Automatic energy consumption scheduling strategies with price predictors to minimize electricity payment in a real-time pricing tariff environment was proposed in [15] and [16]. Application example showed in section 4.2. is based on this strategy.

• Considering various uncertainties on appliance operational time, intermittent renewable generations and variations of electricity prices, the stochastic efficient scheduling schemes for optimized SHEMSs have been addressed in [17] and [18].

• Moreover, based on the bidirectional communication network architecture to schedule the in-building appliances and renewable energy sources, the distributed control algorithms for household demand response have been presented in [19].

• A multi-objective Demand Response (DR) optimization model which is formulated as a multi-objective nonlinear programming problem and subjected to a set of constraints

which and is solved using the Non-Dominated Sorted Genetic Algorithm (NSGA-II), in order to determine the scheduling of home appliances for the time horizon is presented on [20] not only in order to minimize the cost of the electricity but also minimizing the level of inconvenience for residential consumers.

• A strategy based on the modeller system Game theory working with advanced metering system (GAMS), which provides numerical programming and optimization software points, provides to energy consumption reduction by 48% and maximizes the renewable energy consumed at the rate 65% of the total energy generated as it is proposed in [21].

Besides, a smart HEMS shall be able to respond to renewable generation fluctuations, electricity price, and other human behaviour influences in real-time or near real-time to achieve a comfortable lifestyle with financial incentives [22]. The system shall also be flexible enough to accommodate and manage various home appliances, renewable energy resources and HESSs for energy saving and demand response.

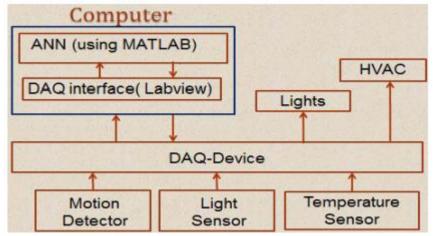

All those different strategies are implemented on SHEMS centre. Since SHEMS is a programmable device CPU (from a complete desktop system to a barebone computer or Raspberry Pi), depending on power of CPU, accessory chips (video processor, sound, mathematical, ...) practically, any algorithm can be implemented, using C+ code, or MATLAB routines, python, ... whatever is needed; high level smart programming methods can be applied on it, such as genetics, neural networks, fuzzy logic, ... can be integrated on a complex system. In conference paper [23] an approximation to such mixture of intelligence techniques is proposed to achieve a productive and cost-effective environment through optimization of air conditioning based on ambient temperature and humidity mainly, but also considering light and motion:

Figure 3 - Block Diagram of the Smart Home System [24]

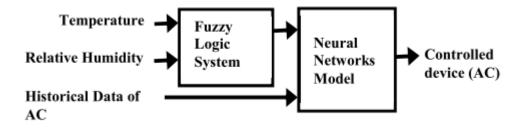

In this approximation, LabView is used as interface between sensors/actuators and MATLAB, being MATLAB the real intelligence on this system, which firstly classify data using fuzzy logic module and secondly, taking as inputs those classified data and previous history of the controlled device, constructs an ANN model which predicts the next setting of the controlled device. Section 3.3.2.4 Thigspeak application goes deeper in Matlab application for SHEMS.

Figure 4 - Block Diagram of Air Condition Fuzzy-ANN Controlling Unit [24]

Above proposed system is a simplified system regarding what have been previously defined as a real SHEMS, but it is helpful to understand how smart optimization of SHEMS can be done based on intelligent tools; one first stage for classifying the data using genetic-fuzzy logic algorithm, and a second stage using neural networks is becoming a useful tool for energy management.

## 3. METHODOLOGY - DOMOTICS COST EFFECTIVE ELEMENTS

At this chapter it will be reviewed the technology basics that have been adapted to domotics to become it cots affordable. Here, the target is not the final devices, but the elements used on them. Massive production of such elements is what has allowed price reduction on the devices; but final users cooperation for combining different applications and brilliant independent programmers working on their own and sharing with the community their achievements is what has develop th applications.

#### 3.1 Sensors/Actuators boards

Commercial domotics devices have been develop based on modules using low cost and low power requirements chips which are connected to basic actuators and sensors. Those chips are:

#### 3.1.1 ESP8266

Developed in 2014, ESP8266 is a system on a chip (SoC) microcontroller, low cost Wi-Fi microchip, with a full TCP/IP stack and microcontroller capability produced by Espressif Systems. Complete datasheet of the latest release of this chip is included on the Appendix.

Basic features of this chip are:

- CPU Tensilica L106 32 bits RISC processor.

- Operation voltage: 3-3.3 VDC.

• Operating current: Average value: 80 mA. Power saving architecture based on three basic modes of operation: active (170 mA), sleep (0.6 mA) and deep sleep (20  $\mu$ A).

• Operating temperature range: -40 to 125 °C. This provides high durability to it.

• Memory<sup>1</sup>: 32 kB instruction RAM, 32 kB instruction cache RAM, 80 kB user-data RAM, 16 kB ETS system-data RAM.

• External memory: Up to 16 MB is supported (depending on board used, 512 KiB-4 MiB are typically used). Note that chip doesn't have program memory, so external memory use is mandatory.

• IPv4 and TCP/UDP/HTTP/FTP protocols, Wi-Fi based (802.11 b/g/n). Though it is not natively available HTTPS protocol can be implement using a TLS1.2 client/server software.

• 17 general purpose input/output ports: but can only be used 9 or 10 of them. GPIO 16 is used for RTC; they can be configured using pull-up/down resistors. Also, they can be used as Pulse Width Modulation inputs.

• 10 bits Analog to Digital Converter (Tout pin, 0-1 VDC).

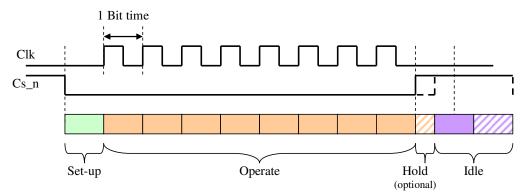

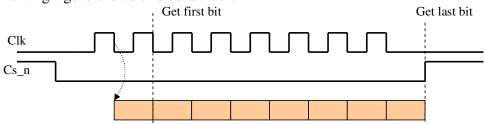

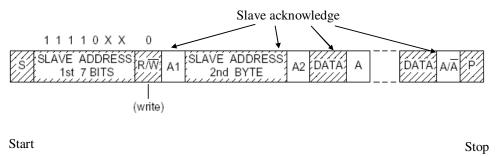

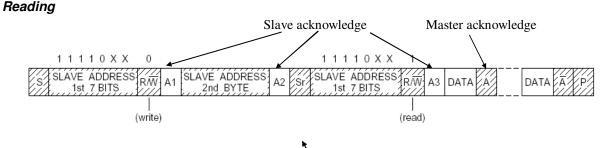

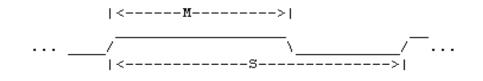

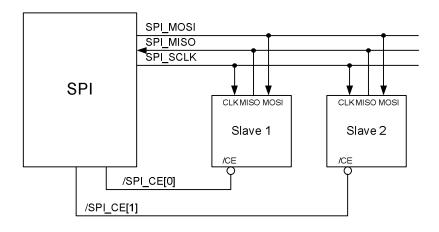

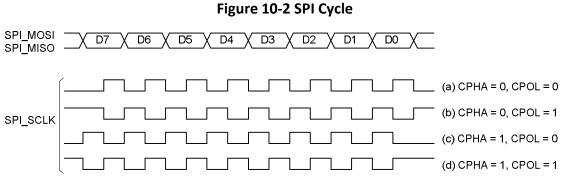

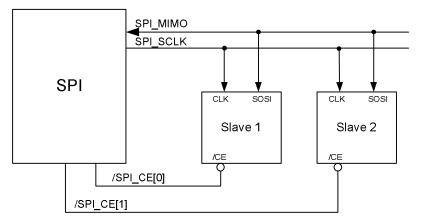

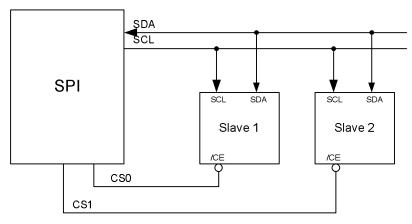

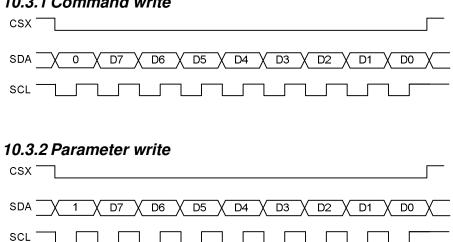

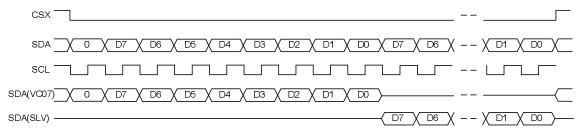

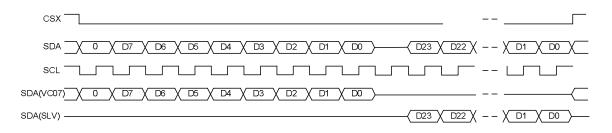

• Communication interface buses: SPI (Serial Peripherical Interface), I2C and UART (Universal Asynchronous Receiver Transmitter).

<sup>&</sup>lt;sup>1</sup> Note that some documents refer those memory values in KiB and MiB: kibibyte, equivalent to  $2^{10}$  bytes and  $2^{20}$  bytes. But official data sheet form vendor shows values in kB ( $10^3$  bytes) and MB ( $10^6$  bytes).

Figure 5 - ESP 8266 pin layout (top view) [25]

In the same way that Arduino is a print circuit board (PCB) using Atmel microchips, ESP 8266 is commonly used based on PCBs. Note that ESP 8266 has no program memory. Following list include just a few examples of what we can find on market.

• ESP-01: Develop by AI\_Thinker company. With a reduced price  $(3 \in)$ , it makes available 2 GPIO pins for sensors and actuators control. There are two additional pins which can be used also as GPIO, but the main function of those pins is serial communication, to allow programming of ESP 01. Following picture shows basic components of ESP01:

Figure 6 - ESP01 main components (back view) [26]

For ESP01 programming a USB/FTDI-TTL converter can be used, but also a Raspberry PI or Arudino board, keeping ESP01 in UART mode (GPIO=LOW, GPIO2=HIGH, considering they have a pull-up resistor so by default they are in HIGH); after reset, those GPIO can be used as input/output.

Figure 7 - ESP01 pins function [27]

• ESP05: It is the simplest version of board. It has been conceived for being a Wi-Fi Shield for Arduino. It has no GPIO ports available. It can be found around 4 €. It has a connector for an external antenna in order to increase Wi-Fi range.

Figure 8 - ESP05 upper view [28]

• ESP12: With a price around  $4 \in$  is the most used board nowadays. It is the most complete version, allowing access to the 11 ports GPIO, one of them is analog. It allows to be configured in sleep mode. It requires to be soldered in a mounting board (already included in the budged previously indicated).

Figure 9 - ESP12 and adapter plate (mounting board), upper view [28]

• ESP201: it is a develop board. Price around  $6 \in .11$  GPIO ports can be accessed and it is designed to fit in a protoboard plate. Same as ESP05 it has a connector for an external antenna in order to increase Wi-Fi range.

Figure 10 - ESP201 upper view [28]

• NodeMCU: Named after Node and Microcontroller (MCU). One board has a price around 8 €. Strictly speaking NodeMCU refers more to the firmware develop for ESP8266, more than a specific board. This firmware has been developed by ESP8266 open source community. It is based on ESP12 board, but boards use to come with mini-USB connector, already mounted serial/USB transducer, push buttons, … Regarding firmware, it uses Lua scripting language, through which Python, Basic or JavaScript languages can be used. This firmware enables programming through IDE Arduino.

Figure 11 - Typical board for using with NodeMCU firmware [28]

• SonOff Basic (4 €): SonOff basic is a complete device manufactured by Itead company, more than a board. It is a Wi-Fi switch, for using trough developer web server.

Figure 12 - SonOff Basic device [28]

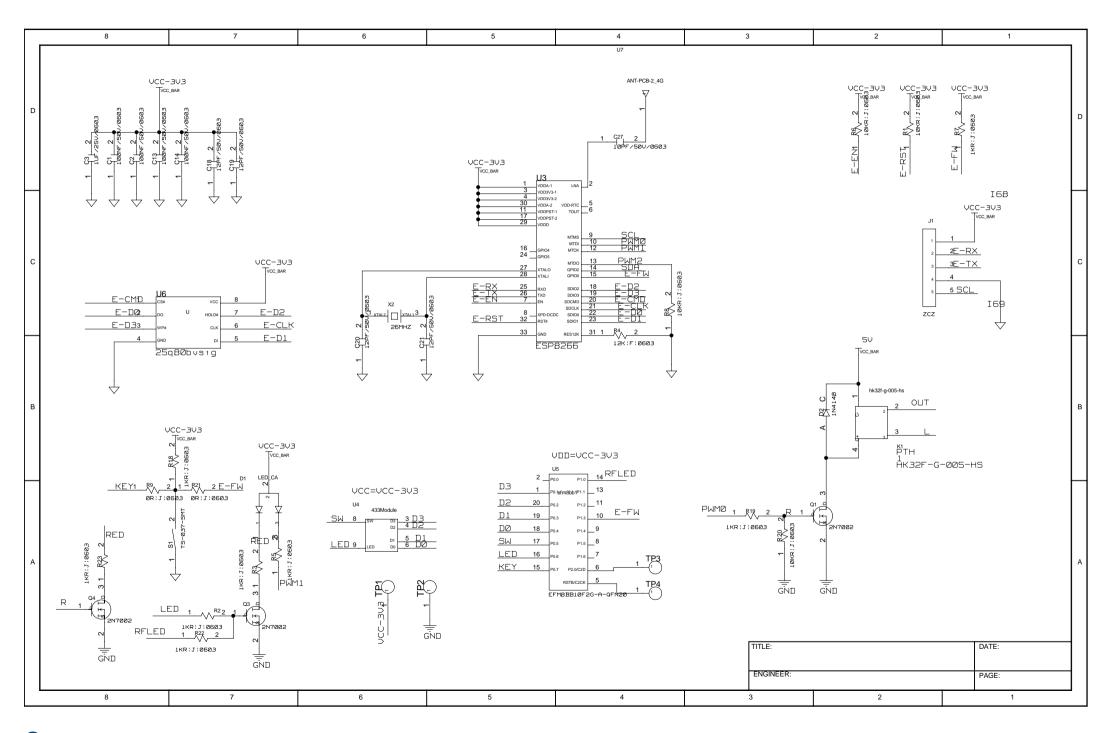

What makes this device so interesting is that it is based on ESP8266, having the programming ports available in such way that it can downloaded a new firmware on it, so, e.g. it can enable MQTT communication (Tasmota, ESPurna, ESP Easy and other firmware), can be programmed in Python, Basic or JavaScript (NodeMCU firmware), .... In SonOff board it is already implemented a power supply from 120-240 VAC, one relay commanded by GPIO12 and 10 A of interrupting current and wiring already done. So, at the end of the day, what we have is a compact Wi-Fi switch, programmable and customizable, ready to be integrated as a remotely controlled switch for 10 A loads, or connecting/disconnecting batteries, ....

Referring to hardware, on the pictures bellow can be found the main components:

Figure 13 - SonOff Basic R1 main components and functions [29]

Figure 14 - SonOff Basic R1 dimensions [29]

Figure 15 - SonOff Basic R1 pinout [29]

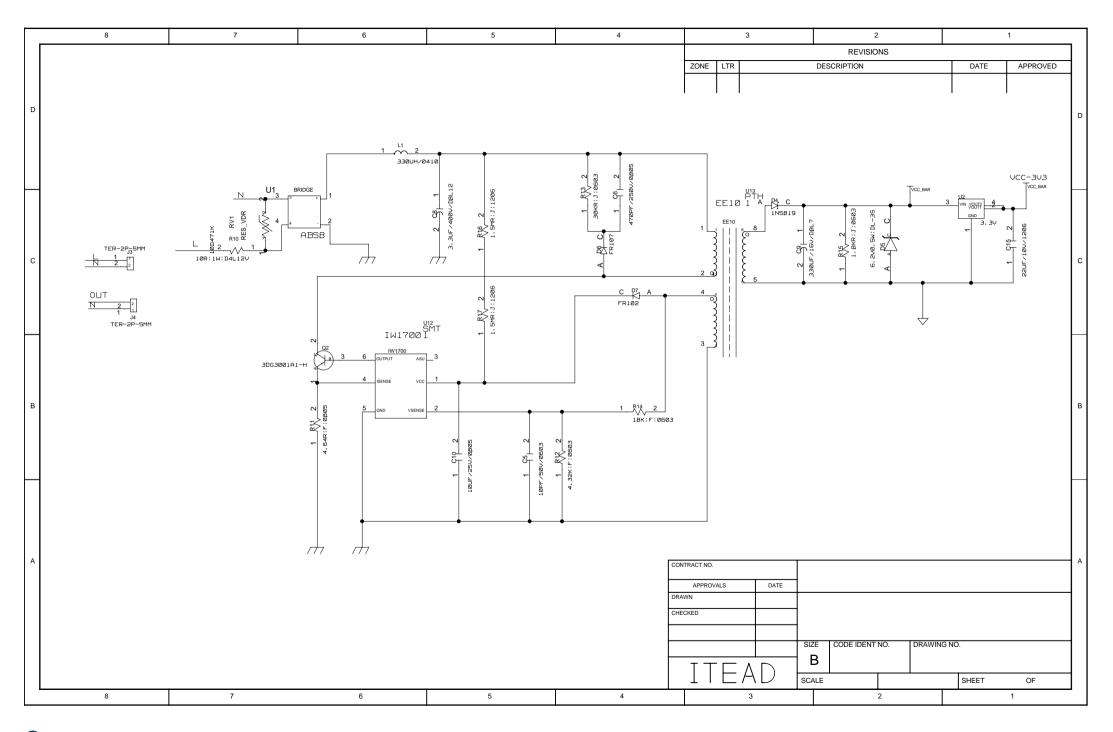

SonOff Basic schematic is provided in appendix.

• Another ITEAD/SonOff devices: based also in ESP8266, which allows to change the firmware to include the above referred features (MQTT, different programming languages, ...) there are a bunch of devices. Follow a non-exclusive list of some of those devices, with a short description of functionality:

• Switches: SonOff Basic, SonOff RF (with radio frequency added control), SonOff Dual (2 switches), SonOff 4CH (4 switches), SonOff 4CH PRO and PRO R2(4 switches and RF receiver), SonOff Touch (Gang Touch Wall

Switch), SonOff T1-T2-T3 (1-3 Gang Touch Wall Switch including RF control), Slamper & Slamper 2.0 (Bulb light switch with RF), SonOff S20 and S26 (outlet), SonOff S31 lite (outlet US standard), SonOff S55 (outlet for wall embedded mounting), 1CH Inching (relay module powered at 5VDC, dry contacts and 10 A burden).

• Switches with power measuring capability: SonOff POW, SonOff POW R2, SonOff S31 (outlet).

$\circ$  Switches with Humidity and Temperature sensor: SonOff TH10, SonOff TH16.

• Dimmable E27 LED Lamp RGB Color Light Bulb: SonOff B1.

• RF-WiFi bridge: SonOff RF Bridge (Bridge between 433MHz RF and Wi-Fi)

• SonOff Zigbee devices: Taking advantage of the low power requirement of ZigBee there are some devices available: ZigBee Bridge (bridge between Wi-Fi and ZigBee), Wireless Switch SNZB-01, temperature and humidity sensor (SNZB-02), movement sensor (SNZB-03), Door-Window sensor (SNZB-04), ...

#### 3.1.2 ESP32

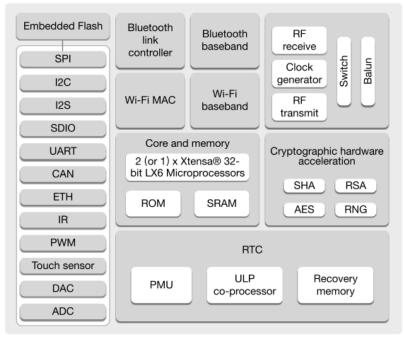

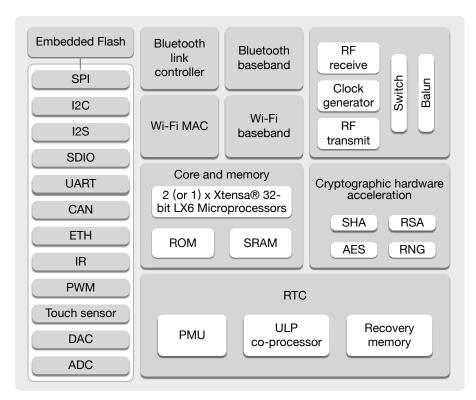

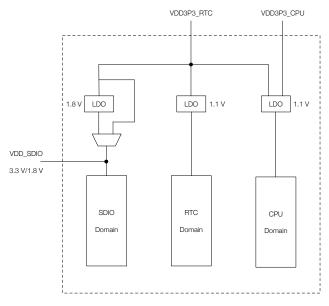

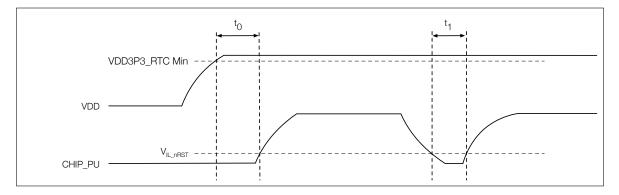

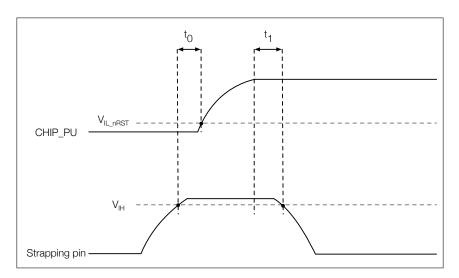

Develop in 2016 by Espressif Systems [30], ESP32 is the successor of ESP8266. It is a low cost, low power system on a chip microcontroller (SoC), with integrated Wi-Fi and dual mode Bluetooth [31]. Complete datasheet of the latest release of this chip is included on the Appendix. Basic features of this chip are:

• CPU Tensilica Xtensa LX6 microprocessor single or dual core, 32 bits processor. 200 or 400 or 600 MIPS. ULP co-processor.

• Operation voltage: 2.3-3.6 VDC.

• Bluetooth: v4.2 BR/EDR and BLE (shares the radio with Wi-Fi).

• Operating current: Average value: 80 mA. Power saving architecture based on six basic modes of operation: active (240-100 mA depending on Wi-Fi, BLE mode), modem sleep (at 80 MHz, 20-31 mA for dual core or 20-25 mA for single core), light sleep (0.8 mA), deep sleep (150  $\mu$ A ULP processor active, 100  $\mu$ A ULP sensor monitored pattern, 10  $\mu$ A RTC timer + RTC memory) and Hibernation (5  $\mu$ A, just RTC memory) and power off mode (with CHIP-PU at low level, 1  $\mu$ A).

• Operating temperature range: -40 to 125 °C. This provides high durability to it. Models ESP32-D2WD and ESP32-U4WDH has integrated some chips with temperature range - 40°C to 105°C, reducing their maximum temperature of system to 105°C.

• Memory: 448 kB ROM for booting and core functions; 520 kB for data and instructions; 8 kB for SRAM in RTC fast memory accessible during boot and deep sleep mode; 8 kB for SRAM in RTC slow memory accessible during deep sleep mode by co-processor; 1000 bit of eFuse: 256 bits are used for the system (MAC address and chip configuration) and the remaining 768 bits are reserved for customer applications, including flash-encryption and chip-ID. Embedded memory depending on model 0-4 MB.

• External memory: Up to 16 MB is supported or SRAM 8 MB (no need for refreshing circuit).

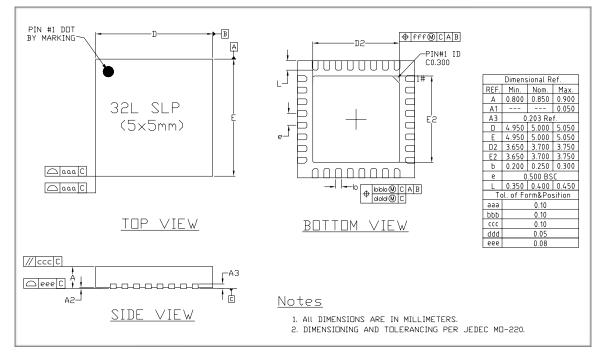

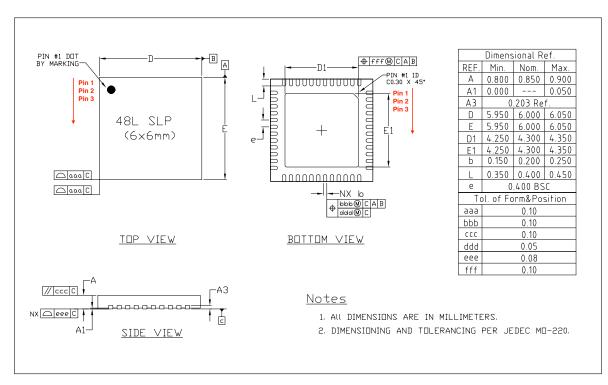

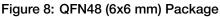

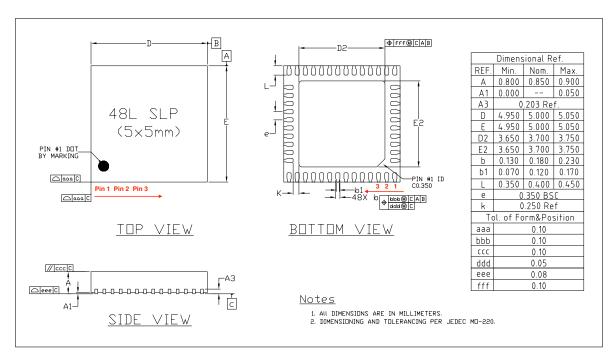

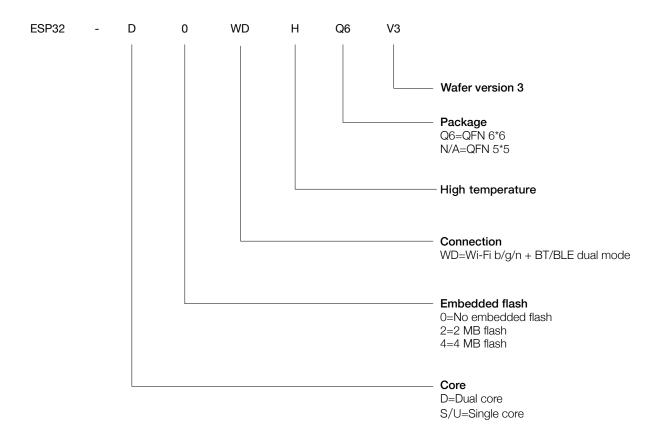

• Models available: keeping in mind this paper is focused in low cost, remark that the price for different models of chips are going from  $1,43 \in$  up to  $3.45 \in$ :

- ESP32-D0WD, Dual core, no embedded memory, 5 x 5 mm.

- ESP32-D0WDQ6, Dual core, no embedded memory, 6 x 6 mm.

- ESP32-D2WD, Dual core, 2 MB embedded memory, 5 x 5 mm.

- ESP32-SOWD, Single core, no embedded memory, 5 x 5 mm.

- ESP32-U4WDH, Single core, 4 MB embedded memory, 5 x 5 mm.

• ESP32-D0WD-V3, Dual core, no embedded memory, 5 x 5 mm. ECO V3 series.

• ESP32-D0WDQ6-V3, Dual core, no embedded memory, 6 x 6 mm. ECO V3 series.

ECO V3 is a series which changes over the base modules consists in manufacturing them in one wafer-level. Additionally, some minor bugs have been corrected and as improvement, minimum baud rate in CAN module has been reduced from 25 kHz to 12.5 kHz.

Figure 16 - ESP32 pin layout (QFN 6\*6, top view) [32].

Another interesting pinout map for ESP32 can be seen on [33].

• FTP, HTTP, IBM MQTT, IPv4, IPv6, SSL, TCP, UDP protocols, Wi-Fi based (802.11 b/g/n). Manufacturer project HTTPS server provides a complete library for using HTTPS protocol [34].

• 34 general purpose input/output ports. They are used for different additional functions digital-only, analog-enabled, capacitive-touch-enabled, etc. Analog-enabled GPIOs and Capacitive-touch-enabled GPIOs can be configured as digital GPIOs but not the opposite. They can set pull-up, pull-down or high impedance in configuration.

• 2 analog inputs based on successive approximation analog to digital converter (ADC) based on 12 bits inputs. CPU can be configured to be wake-up depending on pre-defined threshold.

• 2 8 bits Digital to Analog outputs (DAC).

• Hall sensor: Chip integrates a Hall Sensor based on a N-carrier resistor. This resistor can be connected to an analog input, so magnetic field can be measured. Note that this sensor is not calibrated. It can be applied to implement a proximity sensor magnet based.

• Touch sensors: 10 capacitive-sensing GPIO are integrated to detect touch or approach of fingers.

• Pulse counter inputs.

• Pulse Width Modulation.

• LED PWM output (16 channels).

• Infrared remote controller: The infrared remote controller supports eight channels of infrared remote transmission and receiving.

• ULP: Allows to run micro-programs when CPU is sleeping.

• SD/SDIO/MMC Host controller: allowing reading/writing on storage systems such as SD, MMC, ... cards.

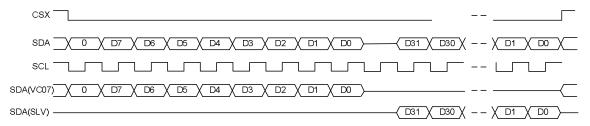

• Communication interface buses: SPI (Serial Peripherical Interface), SPDIO (SDIO Card Specification v2), I2C, I2S and UART (Universal Asynchronous Receiver Transmitter).

• Hardware accelerator for general algorithms such as AES (FIPS PUB 197), SHA (FIPS PUB 180-4), RSA, and ECC. Those accelerators increase significantly the operation speed of microprocessor. They also support code encryption and dynamic encryption.

Quick guide for getting started with ESP32 can be found on [35].

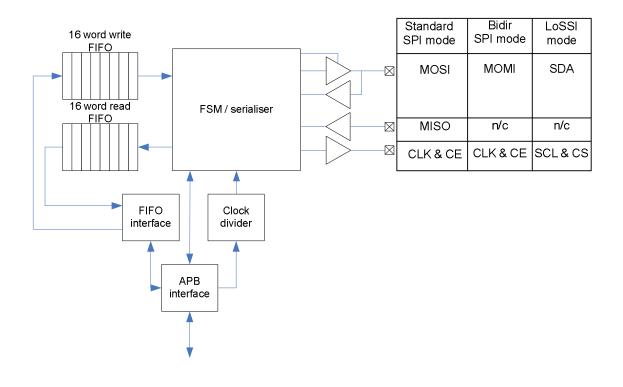

Figure 17 - ESP32 Function block diagram [36].

Same as ESP8266, ESP32 is available mounted in different boards, according to final purpose. This list are just a few examples of what we can find on market:

• ESP32 DEVKIT DOIT (5.59 €): There are two versions, 30 and 36 GPIOs, but the added pins available on 36 GPIOs version are connected to internal flash memory, so they are difficult to use. Pins are labelled on the board. Additionally, to chip ESP-WROOM-32 functions, on the board has been added the following features: reset and boot buttons, USB to UART interface (for easier programming) and voltage regulator circuit.

Figure 18 - ESP32 DEVKIT DOIT top view [28]

• Wemos Lolin32 (8,50  $\in$ ): Similar to previous ones but adding an 0.96" OLED display. This allows basic interface with user.

Figure 19 - Wemos Lolin32 top view [28]

• ESP32 SX1278 (LoRa): This board comes with a SX1278 chip which is a LoRa transceiver chip. LoRa (Long Range) is a low-power wide-area network (LPWAN) protocol developed by Semtech. It is based on spread spectrum modulation techniques derived from chirp spread spectrum (CSS) technology. It was developed by Cycleo of Grenoble, France and acquired by Semtech, the founding member of the LoRa Alliance [37]. LoRa is intended for long range communications, small amounts of data and low power consumption. This board also includes 0.96" OLED display.

Figure 20 - ESP32 SX1278 top view [28]

• ESP32 CAM (6.99 €): This board includes 2 Mpx camera OV2640. Also includes TF support card up to 4G. Just 9 GPIO are available and it has no added the USB to UART interface. Some applications for this board are: surveillance camera, take photos and videos to SD card, PIR motion detection with Photo capture, take photo and display on Web server, ...

Figure 21 - ESP32 CAM top view [28]

• TTGO T-Call ESP32 (11.99  $\in$ ): Main advantage of this board is to include SIM800L GSM/GPRS module, allowing connecting to the internet using your SIM card data plan, or communicate with the board via SMS or phone calls. Note that this module just allow connection to 2G network.

Figure 22 - TTGO T-Call ESP32 top view [28]

More details comparing different ESP32 boards models can be found on [38], [39], [40], [41] and [42].

## 3.1.3 Raspberry PI zero W

Develop by Raspberry foundation. Next chapter it will go in deep in other Raspberry products, but this model must be included in this section, though their technical specifications are above the simple sensor/actuator boards, price of  $10.53 \in$  allows to include it in the same group.

Launched to market on 2017, includes WiFi and Bluetooth LE which enables to include this model in this category (Raspberry "just" Zero (not W) has no Wi-Fi nor BLE so it is not useful as sensor/actuator).

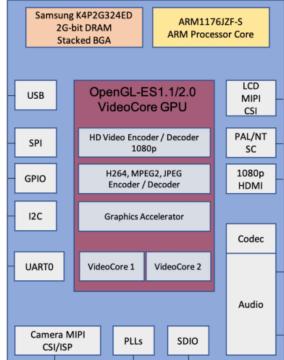

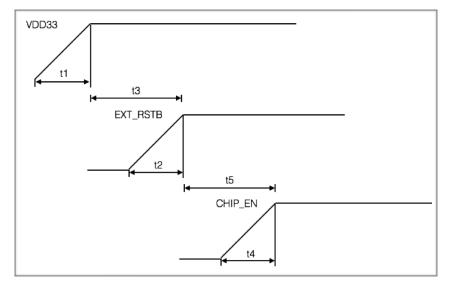

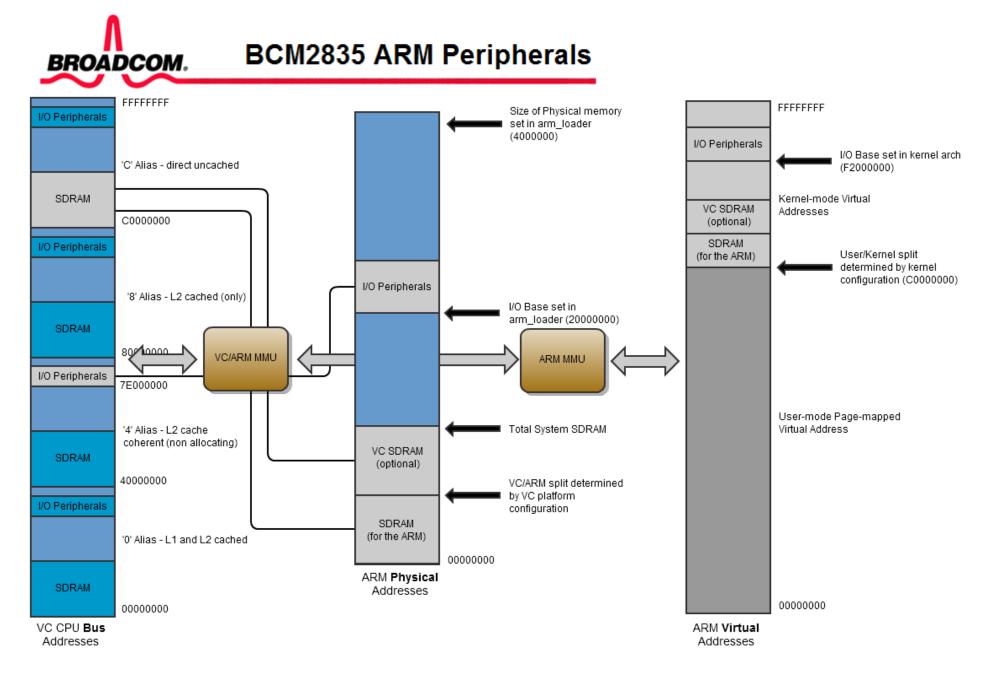

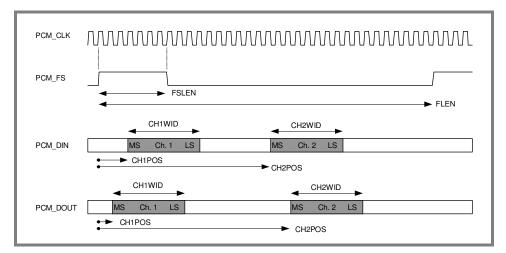

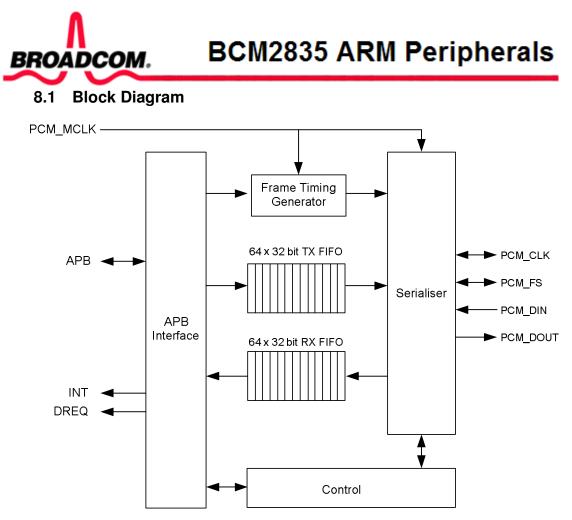

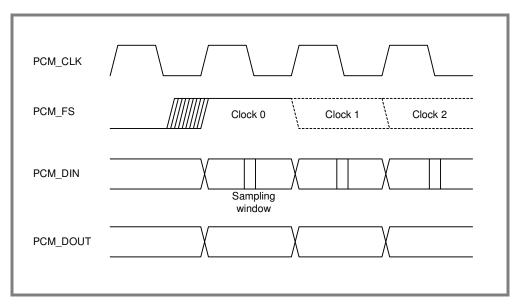

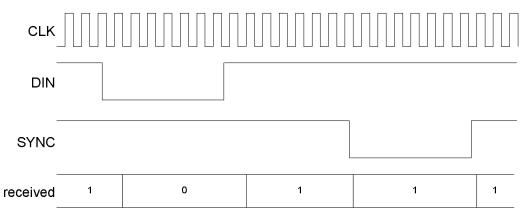

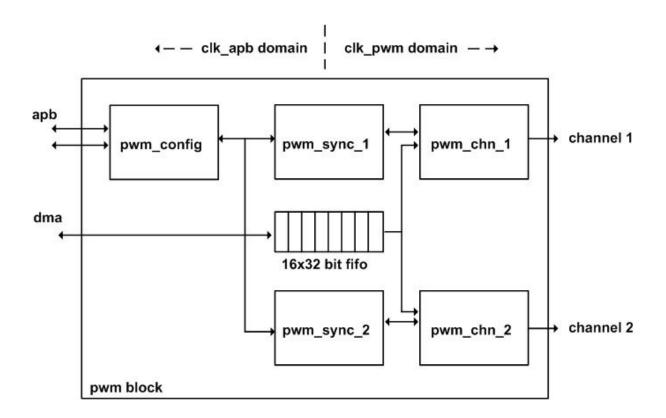

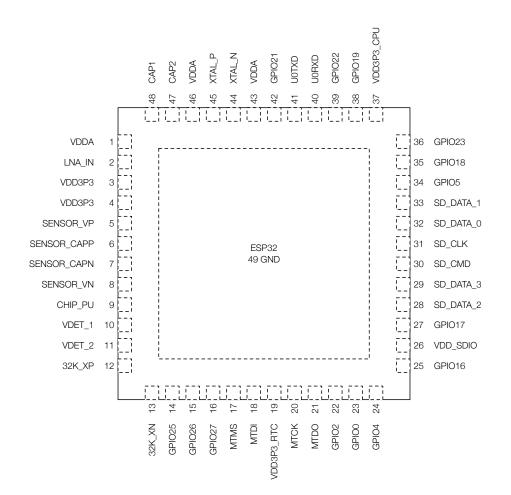

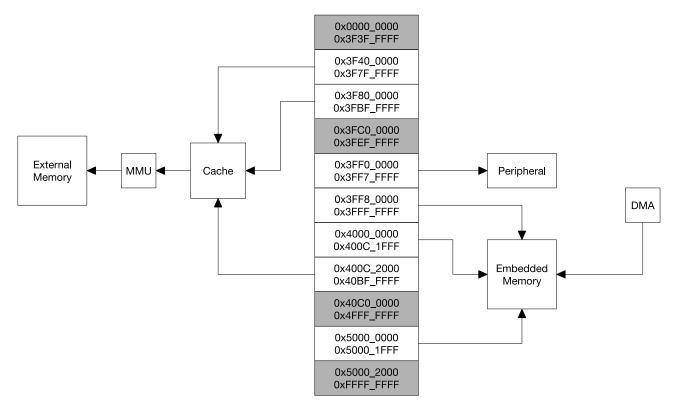

System on a Chip, SoC for this model of Raspberry is Broadcom BCM2835 (Periphals specs. Included on appendix):

• CPU ARM1176JZFS, 700 MHz (1 GHz overclocking)

• GPU: Videocore 4: H.264 at 40 MBits/s, Fast 3D core access, 1Gpixel/s, 1.5Gtexel/s or 24 GFLOPs.

• FPU (Floating Point Unit): VFPv2

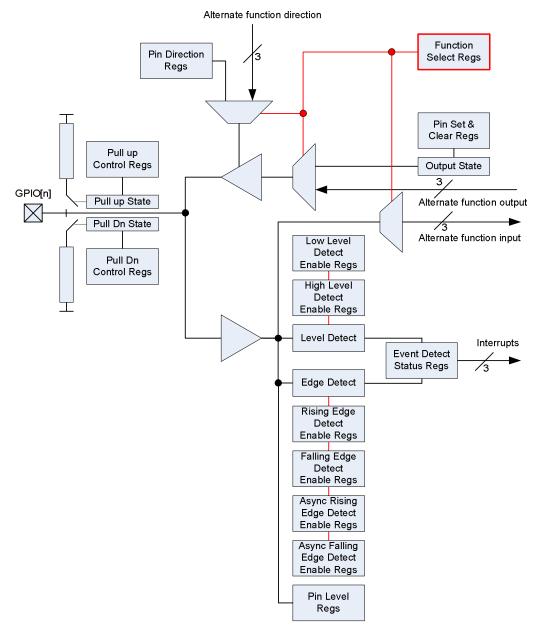

Figure 23 - Broadcom BCM2835 blocks diagram [43]

Main features of Raspberry Pi Zero W are:

- 802.11 b/g/n wireless LAN

- Bluetooth 4.1

- Bluetooth Low Energy (BLE)

- 1GHz, single-core CPU

- 512MB RAM

• Mini HDMI and USB On-The-Go ports

• 5 VDC Micro USB or GPIO power, 100 mA average when idle, 350 mA maximum with keyboard, mouse and monitor connected.

- Composite video and reset headers

- CSI camera connector

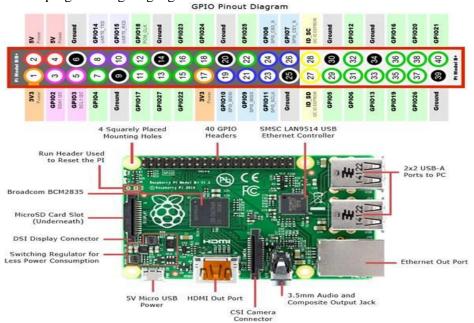

$\bullet$  HAT compatible 40 GPIO header (WH version has those GPIO already soldered to board).

- 17 GPIO

- o UART

- o I2C

- SPI

- PCM (Pulse Code Modulation)

- o PWM

- Chipset

- Micro SDHC slot (SD card will include OS)

- Composite video

| -              | GPI0# | NAME                    |    |   |         |    | NAME                    | GPIO |

|----------------|-------|-------------------------|----|---|---------|----|-------------------------|------|

|                |       | 3.3 VDC<br>Power        |    | 0 | 0       | ~  | 5.0 VDC<br>Power        |      |

|                | 8     | GPIO 8<br>SDA1 (I2C)    | m  | 0 | 0       |    | 5.0 VDC<br>Power        |      |

|                | 9     | GPIO 9<br>SCL1 (I2C)    | ŝ  | 0 | 0       |    | Ground                  |      |

| : Bussesses    | 7     | GPIO 7<br>GPCLK0        | ~  | 0 | 0       |    | GPIO 15<br>TxD (UART)   | 15   |

|                |       | Ground                  | o, | 0 | 0       | to | GPIO 16<br>RxD (UART)   | 16   |

| 0000000        | 0     | GPIO 0                  | я  | 0 | 0       | 12 | GPIO 1<br>PCM_CLK/PWM0  | 1    |

| CONSUSTIE O O  | 2     | GPIO 2                  | 11 | 0 | $\odot$ | и  | Ground                  |      |

|                | 3     | GPIO 3                  | 2  | 0 | 0       | 16 | GPIO 4                  | 4    |

|                |       | 3.3 VDC<br>Power        | 12 | 0 | 0       | 18 | GPIO 5                  | 5    |

|                | 12    | GPIO 12<br>MOSI (SPI)   | 5  | 0 | 0       | 20 | Ground                  |      |

|                | 13    | GPIO 13<br>MISO (SPI)   | 12 | 0 | 0       | 2  | GPIO 6                  | 6    |

|                | 14    | GPIO 14<br>SCLK (SPI)   | 8  | 0 | $\odot$ | 24 | GPIO 10<br>CE0 (SPI)    | 10   |

| England Harris |       | Ground                  | 52 | 0 | $\odot$ | 35 | GPIO 11<br>CE1 (SPI)    | 11   |

| 1              | 30    | SDA0<br>(I2C ID EEPROM) | 27 | 0 | $\odot$ | 28 | SCL0<br>(I2C ID EEPROM) | 31   |

|                | 21    | GPIO 21<br>GPCLK1       | 29 | 0 | 0       | 8  | Ground                  |      |

|                | 22    | GPIO 22<br>GPCLK2       | 31 | 0 | 0       | 8  | GPIO 26<br>PWM0         | 26   |

| 11: XOX !!!    | 23    | GPIO 23<br>PWM1         | 8  | 0 | 0       | ×  | Ground                  |      |

|                | 24    | GPIO 24<br>PCM_FS/PWM1  | ŝ  | 0 | 0       | 8  | GPIO 27                 | 27   |

|                | 25    | GPIO 25                 | 32 | 0 | 0       | 8  | GPIO 28<br>PCM_DIN      | 28   |

|                |       | Ground                  | 39 | 0 | 0       | \$ | GPIO 29<br>PCM_DOUT     | 29   |

Figure 24 - Raspberry Pi Zero W pinout [44].

Operative system confirmed to be used in this board are NOOBS and Raspian (Jessie), LibreELEC, RetroPie, KaliLinux, MusicBox, MotionEyeOS, RuneAudio, ArchLinux, PuppyLinux, PwnPi, Open Media Vault. Other OS supported by Raspberry are to be confirmed.

GPIOs 0-53 and can work as input, output, or advanced function, though, not all GPIO can get all possible functions. Refer to BroadCom BCM2835 peripherals for detailed information. Available functions are: BSC master/slave (I2C), general purpose clock, SPI interface, PWM (2 inputs), UART interface, PCM Audio, secondary memory interface and chip interface. We don't find DAC or ADC or Hall Sensor, which makes this module less accurate as sensor/actuator, and there is no camera or relays integration and current consumed is considerably higher than other modules ... but, in the other hand, provides a processing capability and high level programming possibilities that are not available in more dedicated modules.

## 3.2 Smart Centres Technologies

In order to develop the Smart Centres, there are available basic devices which can be assimilated to personal computers, but with a cost of just a little part of the cost for a personal computer. They will be the brain of our low cost SHEMS:

## 3.2.1. Raspberry PI:

This is the most extended and main option. The basic definition of this device is "a computer of the size of a credit card which can connect to a TV or monitor and a keyboard". Note that size is a little above a credit card: from 85.6x56.5 mm (most distributed models) to 65x56.5 mm (models 1A+ and 3A+) or 65x30 mm (Zero). The idea was born in 2006, but until 2012 was not launched to market. It has been developed by the Raspberry Pi Foundation to put the power of computing and digital making into the hands of people all over the world [45].

PI computers are used in many ways: as a Web server, media centre, robot and model railroad controller, YouTube live streamer, NAS storage, network monitor, digital photo frame, security system, game server, desktop computer, domotics control centre (of course) and whatever can be though ... They give hobbyists and tinkerers an economical computer to experiment with, and although they were first touted as a learning tool, a Raspberry Pi can run myriad applications. Existing models:

| Raspberry<br>Model | Cost   | Year | System on a Chip Model                                                                      | GPU                                          | Memory       |

|--------------------|--------|------|---------------------------------------------------------------------------------------------|----------------------------------------------|--------------|

| RPi1 A             | 25,00€ | 2013 | SoC Broadcom<br>BCM2835 (ARM v6Z,<br>32 bits, CPU 1×<br>ARM1176JZF-S 700<br>MHz, FPU VFPv2) | GPU<br>Broadcom<br>VideoCore IV<br>@ 250 MHz | 256 MB SDRAM |

| RPi1 B             | 35,00€ | 2012 | SoC Broadcom<br>BCM2835 (ARM v6Z,<br>32 bits, CPU 1×<br>ARM1176JZF-S 700<br>MHz, FPU VFPv2) | GPU<br>Broadcom<br>VideoCore IV<br>@ 250 MHz | 512 MB SDRAM |

| RPi1 A+            | 20,00€ | 2014 | SoC Broadcom<br>BCM2835 (ARM v6Z,<br>32 bits, CPU 1×<br>ARM1176JZF-S 700<br>MHz, FPU VFPv2) | GPU<br>Broadcom<br>VideoCore IV<br>@ 250 MHz | 512 MB SDRAM |

| RPi1 B+        | 25,00€                                             | 2014 | SoC Broadcom<br>BCM2835 (ARM v6Z,<br>32 bits, CPU 1×<br>ARM1176JZF-S 700<br>MHz, FPU VFPv2)             | GPU<br>Broadcom<br>VideoCore IV<br>@ 250 MHz | 512 MB SDRAM                 |

|----------------|----------------------------------------------------|------|---------------------------------------------------------------------------------------------------------|----------------------------------------------|------------------------------|

| RPi2 B         | 35,00€                                             | 2015 | SoC Broadcom<br>BCM2836 (ARM v7A,<br>32 bits, CPU 4× Cortex-<br>A7 900 MHz, FPU<br>VFPv3 + NEON)        | GPU<br>Broadcom<br>VideoCore IV<br>@ 250 MHz | 1 GB SDRAM                   |

| RPi2 B<br>v1.2 | 35,00€                                             | 2016 | SoC Broadcom<br>BCM2837 (ARM v8A,<br>32 bits, CPU 4× Cortex-<br>A53 900 MHz, FPU<br>VFPv4 + NEON)       | GPU<br>Broadcom<br>VideoCore IV<br>@ 250 MHz | 1 GB SDRAM                   |

| RPi3 B         | 35,00€                                             | 2016 | SoC Broadcom<br>BCM2837 (ARM v8-A,<br>64/32 bits, CPU 4×<br>Cortex-A53 1.2 GHz,<br>FPU VFPv4 + NEON)    | GPU<br>Broadcom<br>VideoCore IV<br>@ 250 MHz | 1 GB SDRAM                   |

| RPi3 B+        | 35,00€                                             | 2018 | SoC Broadcom<br>BCM2837B0 (ARM v8-<br>A, 64/32 bits, CPU 4×<br>Cortex-A53 1.4 GHz,<br>FPU VFPv4 + NEON) | GPU<br>Broadcom<br>VideoCore IV<br>@ 250 MHz | 1 GB SDRAM                   |

| RPi3 A+        | 25,00€                                             | 2018 | SoC Broadcom<br>BCM2837B0 (ARM v8,<br>64 bits, CPU 4× Cortex-<br>A53 1.4 GHz, FPU<br>VFPv4 + NEON)      | GPU<br>Broadcom<br>VideoCore IV<br>@ 250 MHz | 512 MB SDRAM                 |

| RPi4 B         | 35/55/75<br>€<br>(depends<br>on<br>memory<br>size) | 2018 | SoC Broadcom<br>BCM2711 (ARM v8-A,<br>64/32 bits, CPU 4×<br>Cortex-A72 1.5 GHz,<br>FPU VFPv4 + NEON)    | GPU<br>Broadcom<br>VideoCore VI<br>@ 500 MHz | 1 or 2 or 4 or 8<br>GB SDRAM |

Table 1: Raspberry PI models (cost, year, SoC, GPU and memory) [46]

| Raspberry<br>Model | Interfaces                                                                                                                                                                                                                                                                                                                                                              | GPIOs                                                | Power<br>Ratings     |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|----------------------|

| RPi1 A             | 1 USB2.0, 1 camera interface (Camera Serial Interface, CSI),<br>1 HDMI port, RCA jack composite video, Display Serial<br>Interface (DSI) used for LCD and similar displays, audio<br>input via I2C, audio output via jack, SD, MMC, SDIO card<br>slot                                                                                                                   | 8 GPIOs<br>plus UART,<br>I2C, SPI                    | 300 mA               |

| RPi1 B             | 2 USB2.0, 1 camera interface (Camera Serial Interface, CSI),<br>1 HDMI port, RCA jack composite video, Display Serial<br>Interface (DSI) used for LCD and similar displays, audio<br>input via I2C, audio output via jack, SD-MMC-SDIO card<br>slot. Ethernet 10/100Mbits/s                                                                                             | 8 GPIOs<br>plus UART,<br>I2C, SPI                    | 700 mA               |

| RPi1 A+            | 1 USB2.0, 1 camera interface (Camera Serial Interface, CSI),<br>1 HDMI port, RCA jack composite video, Display Serial<br>Interface (DSI) used for LCD and similar displays, audio<br>input via I2C, audio output via jack, microSDHC card slot                                                                                                                          | 17 GPIOs<br>plus UART,<br>I2C, SPI,<br>HAT ID<br>Bus | 200 mA               |

| RPi1 B+            | 4 USB2.0, 1 camera interface (Camera Serial Interface, CSI),<br>1 HDMI port, RCA jack composite video, Display Serial<br>Interface (DSI) used for LCD and similar displays, audio<br>input via I2C, audio output via jack, microSDHC card slot.<br>Ethernet 10/100Mbits/s                                                                                               | 17 GPIOs<br>plus UART,<br>I2C, SPI,<br>HAT ID<br>Bus | 200-350<br>mA        |

| RPi2 B             | 4 USB2.0, 1 camera interface (Camera Serial Interface, CSI),<br>1 HDMI port, RCA jack composite video, Display Serial<br>Interface (DSI) used for LCD and similar displays, audio<br>input via I2C, audio output via jack, microSDHC card slot.<br>Ethernet 10/100Mbits/s                                                                                               | 17 GPIOs<br>plus UART,<br>I2C, SPI,<br>HAT ID<br>Bus | 220-820<br>mA        |

| RPi2 B<br>v1.2     | 4 USB2.0, 1 camera interface (Camera Serial Interface, CSI),<br>1 HDMI port, RCA jack composite video, Display Serial<br>Interface (DSI) used for LCD and similar displays, audio<br>input via I2C, audio output via jack, microSDHC card slot.<br>Ethernet 10/100Mbits/s                                                                                               | 17 GPIOs<br>plus UART,<br>I2C, SPI,<br>HAT ID<br>Bus | 220-820<br>mA        |

| RPi3 B             | 4 USB2.0, 1 camera interface (Camera Serial Interface, CSI),<br>1 HDMI port, RCA jack composite video, Display Serial<br>Interface (DSI) used for LCD and similar displays, audio<br>input via I2C, audio output via jack, microSDHC card<br>slot. <u>Wi-Fi</u> (b/g/n/ac dual band 2.4/5 GHz), <u>Bluetooth</u> 4.1<br>BLE. Ethernet 10/100Mbits/s                     | 17 GPIOs<br>plus UART,<br>I2C, SPI,<br>HAT ID<br>Bus | 300 mA<br>- 1.4 A    |

| RPi3 B+            | 4 USB2.0, 1 camera interface (Camera Serial Interface, CSI),<br>1 HDMI port, RCA jack composite video, Display Serial<br>Interface (DSI) used for LCD and similar displays, audio<br>input via I2C, audio output via jack, microSDHC card slot,<br><u>USB Boot mode. Wi-Fi</u> (b/g/n/ac dual band 2.4/5 GHz),<br><u>Bluetooth</u> 4.2 BLE. Ethernet 10/100/1000 Mbit/s | 17 GPIOs<br>plus UART,<br>I2C, SPI,<br>HAT ID<br>Bus | 459<br>mA-<br>1.13 A |

| RPi3 A+ | 1 USB2.0, 1 camera interface (Camera Serial Interface, CSI),<br>1 HDMI port, RCA jack composite video, Display Serial<br>Interface (DSI) used for LCD and similar displays, audio<br>input via I2C, audio output via jack, microSDHC card slot.<br><u>Wi-Fi</u> (b/g/n/ac dual band 2.4/5 GHz), <u>Bluetooth</u> 4.2 BLE                                                                       | 17 GPIOs<br>plus UART,<br>I2C, SPI,<br>HAT ID<br>Bus          |                                                               |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|---------------------------------------------------------------|

| RPi4 B  | 2 USB2.0, 2 USB 3.0, 1 camera interface (Camera Serial<br>Interface, CSI), 2 HDMI port, RCA jack composite video,<br>Display Serial Interface (DSI) used for LCD and similar<br>displays, audio input via I2C, audio output via jack,<br>microSDHC card slot, <u>USB Boot mode</u> , <u>Wi-Fi</u> (b/g/n/ac dual<br>band 2.4/5 GHz), <u>Bluetooth</u> 5.0 BLE. Ethernet 10/100/1000<br>Mbit/s. | 17 GPIOs<br>plus<br>4xUART,<br>4xI2C,<br>4xSPI, HAT<br>ID Bus | 600<br>mA-<br>1.25<br>APower<br>Supply<br>USB-C<br>or<br>GPIO |

Table 2: Raspberry PI models (interfaces, GPIOs, power) [46]

We can also find Raspberry Pi Zero, which has been commented in section 3.1.1 and Raspberry Pi Compute module, which being for industrial applications is out of scope of this work.

Operative System: OS is stored in the SD card. Though the vendor remains control of hardware platform, OS it is open source officially is an adapted version of Linux Debian distribution, named as Raspbian; but there are many different OS available such as Windows 10 IoT Core (former Windows Embedded), RISC OS Pi, Broadcom VCOS, Free BSD, Open BSD and NetBSD (Unix like OS), Plan 9 from Bell Labs and Inferno (also UNIX like, from Bell Lab), Haiku, HelenOS, and other Linux based: Ubuntu, LibreELEC (short for Libre Embedded Linux Entertainment Center), Android Things (Android for IoT), Fedora, ... and 21 more Linux based OS. It supports Python and Scratch as main programming languages.

Figure 25 - Hardwarre specifications for Raspberry Pi (model 2B) [47].

# 3.2.2. Cubieboard:

Launched to market on 2012. It can work with Android 4 ICS, Ubuntu 12.04 desktop, Fedora 19 ARM Remix desktop, Armbian, Arch Linux ARM, a Debian-based Cubian distribution, FreeBSD, or OpenBSD. From 2012 there has been many actualizations: Cubieboard1 (49.84  $\in$ ), Cubieboard2 (49.92  $\in$ ), Cubietruck (83.10  $\in$ ), Cubieboard4 (107.67  $\in$ ), Cubieboard5 (89.81  $\in$ ). Let's see specifications for Cubieboard 2 and CubieBoard5, since they are the most representative models:

CubieBoard2:

- SoC: AllWinner A20

- CPU: Dual core ARM Cortex-A7 MPCore, 1.5 GHz

- GPU Dual Core Mali-400MP2

- video acceleration: CedarX able to decode 2160p video

- 512 MiB (beta) or 1GiB (final) DDR3

- 4 GB NAND flash built-in, 1x microSD slot, 1x SATA port.

- 10/100 Ethernet connector

- 2x USB Host, 1x USB OTG, 1x CIR.

- 96 extend pin including I<sup>2</sup>C, SPI, LVDS

- Dimensions: 10 cm × 6 cm

Cubieboard5:

- SoC: Allwinner H8

- CPU: ARM Cortex-A7 @ 2 GHz octa-core

- GPU: PowerVR SGX544 @ 700 MHz

- o display controller: Toshiba TC358777XBG, supports HDMI 1.4 1080p

- and DisplayPort, no LVDS support

- 2 GiB DDR3

• 8 GB EMMC flash built-in, 1x microSD slot, 1x SATA 2.0 port (Hard Disk of 2,5") via USB bridge.

- 10/100/1000Mbps RJ45 Gigabit Ethernet

- 2x USB Host, 1x USB OTG, 1x CIR.

• S/PDIF, headphone, and HDMI audio out, mic and line-in via 3.5mm jack, and onboard mic.

- Wi-Fi (dual-radio 2.4 and 5 GHz) and Bluetooth on board with PCB antenna

- 70 extended pins including I<sup>2</sup>C, SPI

- Dimensions:  $11 \text{ cm} \times 8 \text{ cm}$

### 3.2.3. Gooseberry PI:

Cost a little above 40 €. A10 ARM Cortex-A8 processor, Mali 400 graphics, 512 RAM memory, 4 GiB storage, Wi-Fi, SD Card input, mini-HDMI port, USB port and Android OS by default.

# **3.3 Firmware and Software**

Even when low cost hardware has been one key factor for low cost domotics development, the actual strongest factor has been community firmware and software open source develop. There is a vast and huge network of developers working in open code but also supporting to users, and

sharing knowledge through public channels, forums and dedicated webs (a list of such knowledge channels is provided on appendix).

## 3.3.1. ESP 8266 based devices firmware

One most used base board for domotics devices is ESP8266 and this is mainly due to different firmware versions for this SoC (System on a Chip). Most of them has been extrapolated to ESP32. Following are the main options for firmware:

## 3.3.1.1. ESPEasy

Launched in 2015, was the first alternative firmware. Develop by Letscontrolit community its source code is available at [48]. The firmware is built on the ESP8266 core for Arduino which in turn uses many open source projects. Same than other alternatives, it is a web configurable multisensor (with some actuator things in progress). It started with generic ESP8266 platform and added documentation on how it can be used for fabricated boards, such as Sonoff. This approach makes it very flexible and able to support any combination of sensors / actuators but requires a bit more configuration to get started.

Project is updated many times a day, mostly by few core developers from Lets Control It, but they also merge code from other contributors, which is quite nice and in the spirit of true OpenSource project.community size is big, with a balance between developers and "regular" users.

Once firmware is downloaded on the device using UART port (TTL levels, Rx-Tx, it can be used a USB/TTL converter, an Arduino board, a Raspberry Pi device, ...), and using SonOff button for entering ESP8266 in programming mode, and once device is restarted a Wi-Fi network owned by device can be accessed.

We can connect to Wi-Fi network "esp\_0", and at http://192.168.4.1 it can be found the embedded webpage for configuring home Wi-Fi network and password.

After rebooting the device will connect to home Wi-Fi network, obtaining an IP address from home router DHCP server. Connecting to such new IP address in our web browser we can start to configure it and manage our device.

| < >  | Task | Device | Name | Port | IDX/Variable | GPIO | Values |

|------|------|--------|------|------|--------------|------|--------|

| Edit | 1    |        |      |      |              |      |        |

| Edit | 2    |        |      |      |              |      |        |

| Edit | 3    |        |      |      |              |      |        |

| Edit | 4    |        |      |      |              |      |        |

Main Config Hardware Devices Rules Tools

Figure 26 – Tasks table page on ESPEasy [49].

| Task Settings            |               | Value                      |

|--------------------------|---------------|----------------------------|

| Device:                  | Switch input  | ▼ ?                        |

| Name:                    | relais        | <u>á</u>                   |

| Delay:                   | 0             | (Optional for this device) |

| IDX / Var:               | 1             |                            |

| 1st GPIO:                | GPIO-12 V     |                            |

| Pull UP:                 | Ø             |                            |

| Inversed:                |               |                            |

| Switch Type:             | Switch •      |                            |

| Switch Button Type:      | Normal Switch | T                          |

| Send Boot state:         |               |                            |

| Send Data:               |               |                            |

| <b>Optional Settings</b> |               | Value                      |

| Value Name 1:            | Switch        |                            |

|                          | Close Submit  |                            |

Figure 27 - Configuring page ESPEasy allowing to configure relay module [49].

After rebooting the device will connect to home Wi-Fi network, obtaining an IP address from home router DHCP server. Connecting to such new IP address in our web browser we can start to configure it and manage our device.

Scripts can be used, of the type:

On TurnOn do gpio, 12, 1 EndOn On TurnOff do gpio, 12,0 EndOn

The Sonoff http command to switch the to On will be: http://<ip-of-Sonoff>/control?cmd=event,TurnOn http command http://<ip-of-The to switch the Sonoff Off will be: to Sonoff>/control?cmd=event,TurnOff

It supports:

• Various WiFi connection modes, including AP (hotspot) or STA (client) mode, with multiple SSID configuration and Wifi Network scanning.

• Over-the-Air update (OTA) and configuration backup and restore.

• Logging over some interfaces, such as Serial, Syslog or HTTP, with configurable log levels.

• Time synchronization via NTP

In order to use with SHEMS Center (applications) it is important considering protocols available for the device [50]:

- Domoticz HTTP

- Domoticz MQTT

- OpenHAB MQTT

- PiDome MQTT

- Nodo Telnet

- ThingSpeak

- EmonCMS

- Generic HTTP

- Generic HTTP Advanced

- InfluxDB HTTP Api (via Generic HTTP Advanced)

- Nettemp HTTP Api (via Generic HTTP Advanced)

- FHEM HTTP

- Generic UDP

# 3.3.1.2. SonOff Tasmota

Project started in 2016 (but officially launched in 2017). The name stands for: Theo-Arends-Sonoff-MQTT-OTA, being Theo Arends the developer. Supports many more ESP8266 based boards, much more than mere Son Off [51]. Project is practically daily updated, by Theo, reworking some of the contributions made by community. This community is a mix of developers and users, a little unbalanced, in reference to ESPEasy community; community produce regularly Youtube tutorials and wiki pages, being important part of the success of this firmware.

Most of the features are the same than ESPEasy.

One significant difference is that Tasmota has all possible devices integrated in just one code: this makes it easy to use but produces a heavier code.

It has same protocols than ESPEasy, but they have not been customized per applications, so, instead of MQTT Domoticz, what we have is generic MQTT and some parameters which must be adapted to Domoticz application. In the other hand, some IR protocols are available, allows mDNS MQTT discovering mode and 433 MHz receiving, learning and sending codes.

The programming method is the same than for ESPEasy and it will be the same than for next analysed firmware, ESPurna. Same that other firmware it can be downloaded using a Raspberry or even Arduino IDE, as it shown in [52]

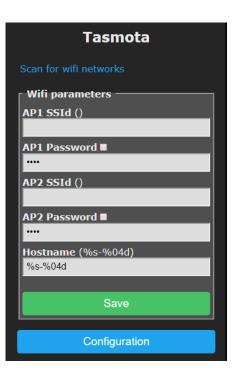

Once the device has been flashed, the Wi-Fi connection available is tasmota\_XXXXX-####, now the IP address is http://192.168.4.1.

Figure 28 - Configuring Wi-Fi connection for Tasmota [53].

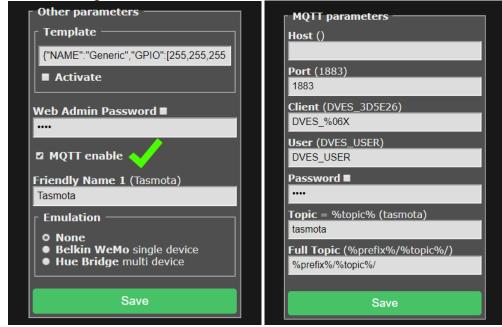

As it can be seen on above picture, two different Wi-Fi networks can be configured for our device. Now, MQTT must be configured.

Figure 29 - Configuring MQTT protocol in Tasmota [53].

Next step will be to configure template or module, selecting in such way the device that we are using (as previously said, firmware is the same for all different devices).

## 3.3.1.3. ESPurna