# Design of an image acquisition and processing system using configurable devices

**A Master's Thesis**

Submitted to the Faculty of the

Escola Tècnica d'Enginyeria de Telecomunicació de Barcelona

Universitat Politècnica de Catalunya

by

**Miquel López Muñoz**

In partial fulfilment of the requirements for the degree of MASTER IN ELECTRONICS ENGINEERING

Advisor: Juan Manuel Moreno Arostegui

Barcelona, June 2021

# <u>Title of the thesis:</u> Design of an image acquisition and processing system using configurable devices

Author: Miquel López Muñoz

Advisor: Juan Manuel Moreno Aróstegui

# Abstract

This thesis consists of the evaluation of the possibility to implement a Neural Network in an FPGA instead on the more used GPU. Theoretically, an FPGA is a better choice in terms of processing power, latency, or flexibility but its configuration is harder.

In this report, the implementation process for an FPGA is followed, including the creation of an embedded Operating System, video capture and display pipelines, testing of the chosen model and the final implementation of the model in the board.

As a result of the evaluation, the conclusion is that nowadays the way to implement a neural network in an FPGA is not mature enough to compete with GPU alternative. The tools needed to achieve this implementation are very limited and the process is confusing. In the other hand, the GPU implementations has a huge catalogue of HW options and one can choose the better solution for its model.

# **Acknowledgements**

This project would not have been possible without the help of my Idneo partners Rubén Veloso and Aitor Sanchez, as well as my supervisor Martí Cobos. With special thanks to Ruben for proposing me this topic and for helping me in the first steps of the project to understand and install all the required tools.

I must thank also my Idneo partners Joan Sintes and Biel Tura for their patience in explaining me the basis of Machine Learning from my absolute lack of knowledge in these field.

I must also thank Ignacio Espinel and Stefano Tabanelli from Avnet for providing me a large amount of Documentation, Trainings and project examples to manage the ZCU104 Development board and all the Xillinx development tools.

Finally, I have to thank my project supervisor Juan Manuel Moreno Aróstegui to help me to understand the complexity of the project and advise me in the steps of the development project and its structure. Also, to the project follow up which it has been exactly the kind of tracing that I need.

# **Revision history and approval record**

| Revision | Date       | Purpose            |

|----------|------------|--------------------|

| 0        | 13/05/2021 | Document creation  |

| 1        | 30/08/2021 | Document corrected |

| 2        | 03/10/2021 | Document revised   |

| 3        | 05/10/2021 | Document approved  |

| Written by: |                | Reviewed and approved by: |                    |

|-------------|----------------|---------------------------|--------------------|

| Date        | 13/05/2021     | Date                      | 05/10/2021         |

| Name        | Miquel López   | Name                      | Juan Manuel Moreno |

| Position    | Project Author | Position                  | Project Supervisor |

# Table of contents

| Abstract       |                                                                   | 1  |

|----------------|-------------------------------------------------------------------|----|

| Acknowledg     | ements                                                            | 2  |

| Revision his   | tory and approval record                                          | 3  |

| Table of cor   | itents                                                            | 4  |

| List of Figure | es                                                                | 6  |

| List of Table  | S                                                                 | 7  |

| 1. Introduc    | ction                                                             | 8  |

| 2. State of    | the art of the technology used or applied in this thesis          | 10 |

| 3. Project     | development                                                       | 12 |

| 3.1. Sys       | stem architecture and description                                 | 12 |

| 3.1.1.         | System architecture                                               | 12 |

| 3.1.2.         | HW Components description                                         | 13 |

| 3.2. Em        | bedded PetaLinux Image                                            | 18 |

| 3.2.1.         | Basic Programable Logic                                           | 21 |

| 3.2.2.         | Create PetaLinux project, export HW and set general configuration | 21 |

| 3.2.3.         | Rootfs generation                                                 | 22 |

| 3.2.4.         | Build project and generate Boot Image                             | 23 |

| 3.2.5.         | Configure boot SD card                                            | 24 |

| 3.3. Ca        | pture, display and store video image from USB camera              | 25 |

| 3.3.1.         | Programable logic                                                 | 25 |

| 3.3.2.         | PetaLinux project changes                                         | 26 |

| 3.3.3.         | GStreamer video pipelines                                         | 28 |

| 3.4. Pro       | cessing image in host PC using a Convolutional Neuronal Network.  | 32 |

| 3.4.1.         | SegNet                                                            | 32 |

| 3.4.2.         | SegNet Image processing code                                      | 33 |

| 3.5. lmp       | blementing Convolutional Neuronal Network in embedded system      | 35 |

| 3.5.1.         | Full System Programable logic                                     | 36 |

| 3.5.2.         | PetaLinux changes                                                 |    |

| 3.5.3.         | CNN files generated with DNNDK                                    | 42 |

| 3.5.4.         | XSDK Bare metal application                                       | 44 |

| 3.5.5.         | Boot the Application                                              | 47 |

| 4.   | Resul   | ts                                     | 49 |

|------|---------|----------------------------------------|----|

| 4    | .1. F   | Results Embedded PetaLinux             | 49 |

| 4    | .2. Ir  | nage Capture                           | 51 |

|      | 4.2.1.  | Image Displayed in Screen              | 51 |

|      | 4.2.2.  | Captured Video                         | 51 |

| 4    | .3. C   | CNN capture in host PC                 | 52 |

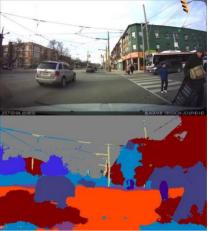

|      | 4.3.1.  | Single frame                           | 52 |

|      | 4.3.2.  | Sample Video                           | 52 |

|      | 4.3.3.  | Captured Video                         | 53 |

| 4    | .4. F   | inal PL Vivado Block Design reports    | 53 |

|      | 4.4.1.  | Utilization Report                     | 53 |

|      | 4.4.2.  | Timing Report                          | 60 |

| 4    | .5. F   | ull system Implementation              | 63 |

|      | 4.5.1.  | PetaLinux built                        | 63 |

|      | 4.5.2.  | DPU utilities available                | 64 |

|      | 4.5.3.  | DNNDK SegNet error                     | 64 |

| 5.   | Budge   | ət                                     | 66 |

| 6.   | Concl   | usions and future development          | 67 |

| Bibl | iograp  | hy                                     | 69 |

| Арр  | endice  | es                                     | 72 |

| APF  |         | X A: PetaLinux Configuration           | 72 |

| Ρ    | etaLin  | ux HW configuration window             | 72 |

| R    | ootfs o | configuration Windows                  | 73 |

| APF  |         | X B: VCU Demo files                    | 74 |

| V    | cu-den  | no-camera-encode-decode-display.sh     | 74 |

| V    | cu-den  | no-camera-encode-file.sh               | 77 |

| APF  |         | X C: Image Capture Vivado Block Design | 80 |

| APF  |         | X D: Full System Vivado Block Design   | 81 |

| Glo  | ssary a | and Acronyms                           | 82 |

# List of Figures

| Figure 1-1: Gantt diagram of the project                                                                    |

|-------------------------------------------------------------------------------------------------------------|

| Figure 3-1: System architecture draft12                                                                     |

| Figure 3-2: See3CAM CU30_CHL_TC_BX Cam. Source: [12]13                                                      |

| Figure 3-3: ZCU104 development board main components for this project. Source: [7]14                        |

| Figure 3-4: USB interface. Source: [7]16                                                                    |

| Figure 3-5: JTAG Chain Block Diagram. Source: [7]16                                                         |

| Figure 3-6: Embedded Linux boot process. Source: [25]19                                                     |

| Figure 3-7: Boot.bin container file diagram. Source: [25]20                                                 |

| Figure 3-8: PetaLinux Embedded Image project steps diagram20                                                |

| Figure 3-9: Basic Programable Logic Vivado Block Design21                                                   |

| Figure 3-10: SW6 SD boot configuration24                                                                    |

| Figure 3-11: Image Capture PL Diagram25                                                                     |

| Figure 3-12: Software stack. Source: [26]                                                                   |

| Figure 3-13: GStreamer custom capture-encode-store_file pipeline                                            |

| Figure 3-14: H.264 (AVC) frame distribution                                                                 |

| Figure 3-15: SegNet architecture. Source: [33]                                                              |

| Figure 3-16: SegNet project code file architecture                                                          |

| Figure 3-17: Development Flow of an Edge-based AI Application example. Source: [48]35                       |

| Figure 3-18: Full system PL Diagram                                                                         |

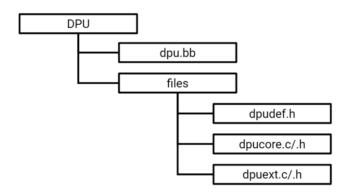

| Figure 3-19: dpu module file structure. It includes the recipe and the source code files39                  |

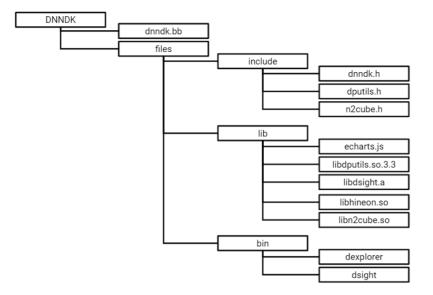

| Figure 3-20: DNNDK app file structure. It includes the recipe, the DPU utilities and the required libraries |

| Figure 3-21: DECENT Pruning and Quantization Flow. Source: [46]42                                           |

| Figure 3-22: DNNC Components. Source: [46]                                                                  |

| Figure 3-23: DECENT Workflow. Source: [46]                                                                  |

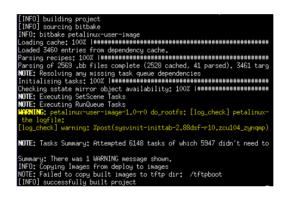

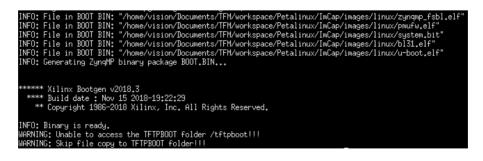

| Figure 4-1: Terminal capture showing success in build PetaLinux project49                                   |

| Figure 4-2: Terminal capture showing success in generating PetaLinux image files49                          |

| Figure 4-3: BOOT and rootfs partitions of the boot SD card                                                  |

| Figure 4-4: Terminal capture when using minicom to log in the embedded PetaLinux in the zcu104 Board        |

| Figure 4-5: foto taken when the USB camera is capturing image of the balcony a displaying in the monitor. |     |

|-----------------------------------------------------------------------------------------------------------|-----|

| Figure 4-6: Frames from the captured video.                                                               | .51 |

| Figure 4-7: Input-output of a single image to the SegNet.                                                 | .52 |

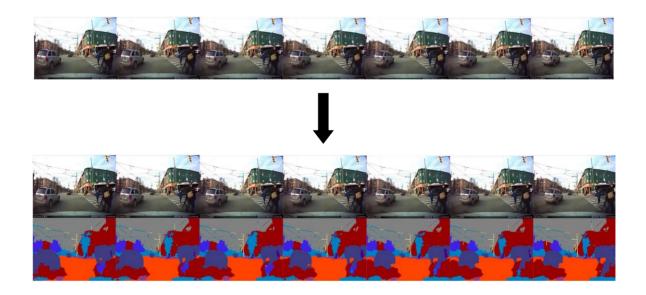

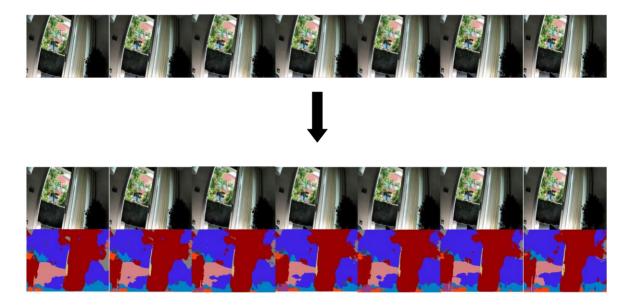

| Figure 4-8: Input and output video of SegNet in host PC. Sample Video                                     | .52 |

| Figure 4-9: Input and output video of SegNet in host PC. Captured Video                                   | .53 |

| Figure 4-10: Screen captured showing success in building the project.                                     | .63 |

| Figure 4-11: Screen captured showing success in building the project with sdk                             | .63 |

| Figure 4-12: Screen captured showing success in packaging the rootfs for XSDK                             | .63 |

| Figure 4-13: Screen capture showing the DPU utilities in their folder                                     | .64 |

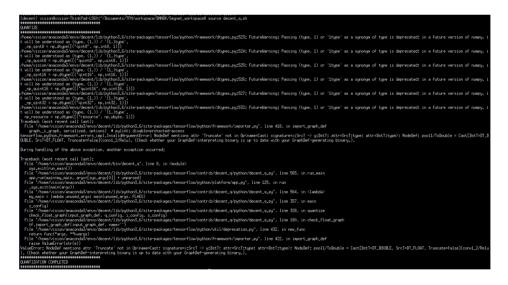

| Figure 4-14: Screen captured when truing to quantize the model with DNNDK                                 | .64 |

# List of Tables

| Table 3-1: Switch Configuration. Source: [7]                   | .17 |

|----------------------------------------------------------------|-----|

| Table 3-2: petalinux-create Command Line Options. Source: [14] | .22 |

| Table 3-3: VCU Encoder features. Source: [26]                  | .29 |

| Table 3-4: Camera Video features. Source [11]                  | .29 |

| Table 3-5: Display Port Live Video Format. Source: [8]         | .29 |

| Table 3-6: Supported layers order in DPU IP. Source: [48]      | .37 |

# 1. Introduction

The main objective of this project is to explore the possibility to implement a Convolutional Neural Network in an FPGA instead of in the most used solution GPU, testing the availability and the difficulty of the process and apprise if it could be a better solution.

This project is realized in collaboration between ETSETB-UPC and Idneo Technologies Vision team. Vision is an engineering team that is focused on computer video applications, developing from the automotive cameras until Machine Learning algorithms to process the captured video. In this context, it is reasonable to explore the possibility to get a more efficient way to implement the Convolutional Neural Network that applies the algorithm. However, since this new implementation is so recent and still under development and because there is nobody in the company with an expertise regarding FPGA, there is no know-how about the needed knowledge of this project. This has caused that the objectives of the project and its process are splitted into steps.

The main scope of the project is to develop an image capture system embedded in a development board with an embedded Linux-based OS and process this acquired video with a Deep Learning algorithm. Since the main field of work of Vision team is the automotive cameras, it has been decided to implement a Deep Learning algorithm that can be used in autonomous driving such as Semantic Segmentation of a video captured with a car front camera.

The first implementation is based in an embedded Linux-based OS in a development board that captures video with a USB camera and stores a video file that is then processed with a CNN in the host PC. The second and final implementation consists on implement this CNN in the FPGA of the development board and write a C++ application running in the board that captures the video, process each frame in the CNN and shows the resulting video in an external monitor.

To do so, numerous Xilinx trainings and project examples which are mentioned in the Bibliography, have been followed. As mentioned, this kind of implementation is under development so it is not as flexible as they should be, and this has been caused some troubles and delays.

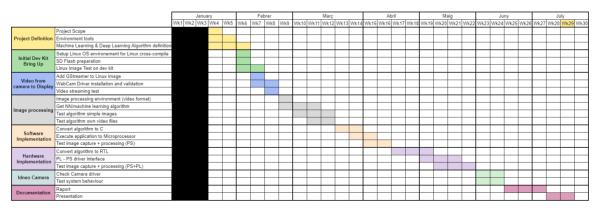

Figure 1-1 shows the original Gantt diagram of the project.

Figure 1-1: Gantt diagram of the project.

At first, the project is intended to be finished in one semester, but due to the complexity of each step and the lack of know-how regarding every configuration to be performed, remarkable delays have been added. Despite this, the project could be finished in time, but as already mentioned, this kind of implementation is under development and this implies that the process works fine in the trainings and examples but when trying something different, unexpected errors occur which do not have a known solution. These issues caused that the project could not be finished in a single semester and an additional one has been needed to realize some workarounds.

The chapters that this thesis document contains are briefly described below:

## State of the art of the technology used or applied in this thesis

In this step, the context of the field of study regarding Machine Learning and the most used implementation are introduced. Also, the alternative of implement the NN with FPGA and the set of tools used to explore this possibility are explained.

### Project development

This is the core chapter of the thesis. In this chapter there is first a description of the architecture of the system. Then, each step of the project development is described. These steps are: Embedded PetaLinux Image; Capture, display and store video image from USB camera; Processing image in host PC using a Convolutional Neuronal Network; Implementing Convolutional Neuronal Network in embedded system.

### <u>Results</u>

The results of the study are collected in this chapter, this includes screen captures and reports. To represent a video in this report, it has been decided to make a collage with a set of the frames of the video.

### Budget

In this chapter, a summary of the required budget is included in a table.

### **Conclusions and future development**

The conclusions of the project are described in this chapter including a brief discussion of the availability to implement the NN in an FPGA instead of a GPU. Also, some future developments are commented to motivate future thesis or research projects.

At the end of the project, there is detailed the literature consulted in this thesis, as well as the project examples and trainings followed in the Bibliography chapter. And finally, there are a set of Appendixes and a section defining the Acronyms and Glossary appearing in the report.

# 2. <u>State of the art of the technology used or applied in this</u> thesis

Machine Learning Algorithms are mathematical algorithms that, with the help of a training process, learn how to perform a specific task. Nowadays, this field of study is growing and every day is used more to develop applications. These algorithms have the advantage in front of the traditional algorithms that the developer does not need the way to reach the solution. In this project, Convolutional Neural Network machine learning algorithms are used. This kind of algorithms are a multi-layer bidimensional matrix algorithm used in the Deep Learning algorithms specifically to process images.

Most of the video processing applications realized nowadays are implemented in a Graphics Processing Unit (GPU) to free the CPU from the large number of calculations needed by the algorithm. The two main suppliers of Deep Learning platforms are NVIDIA and AMD. They have development boards to use one or more GPUs along with the CPU, to implement neural networks in the board or in the cloud, training all frame kind of models with all the available frameworks, etc...

Since the implementation in the GPU is so advanced, most of the main frameworks like TesnorFlow, Caffe, PyTorch and so on, are intended to be used with Python. Also, the computer vision libraries like OpenCV or CUDA works better with Python. Even if they have C++ version, they are not working as good as they do in Python.

In this field lead by Graphics Processing Unit, it arises the possibility to implement the Neural Network in a FPGA instead. Since both solutions fulfil the main objective which is free the CPU to the large amount of processing, the idea to use a FPGA instead of GPU is quite interesting. Since the FPGA is programable HW, it has some advantages in front of a GPU that could make them a better solution to implement the Neural Network. FPGA can process more operations per second, is more flexible since the HW can be changed by programming so it can be adapted better to each application, the latency is lower because it is not instruction-based execution but parallel HW execution and the connection between components and peripherals can be more efficient since is programmed by the developer. The drawback is that configuring an FPGA is much more difficult than a GPU. In addition, the GPU implementation is so stablished that it is easier to find a suitable GPU for your certain application.

This is the reason why nowadays almost every developer is using a GPU instead of the theoretically better solution FPGA. Nevertheless, Xilinx is trying to launch an easy way to implement the NN in an FPGA and perform a Deep Learning Video Processing application, but it is still under development, and it is not as robust and as flexible as advertised. There are a lot of incompatibilities between software versions, and a lot of tools to each task and it is not clear what can be done and what is not compatible.

The following tools are used in this project. The version of each tool has to be the specified or it would be incompatible with the rest:

- Host Operating System: Ubuntu 16.04 LTS

- FPGA development software: Vivado Design Suite v2018.3

- Embedded OS: PetaLinux v2018.3

- Software to compile NN model to be used by the FPGA IP: DNNDK 3.0

- FPGA IP to implement model: DPU IP v2.0

- Software environment to compile Application: Xilinx SDK (XSDK) 2018.3

And the Hardware used in the project is the following:

- Host PC: Lenovo ThinkPad L560

- Development board: Zynq UltraSCALE+MPSoC ZCU104

- USB Camera: See3CAM\_CU30\_CHL\_TC\_BX e-con Systems

- SD card: SanDisk Ultra 16GB

- DP Monitor: BenQ GW2780 27 LED IPS Eye Care

# 3. Project development

The development of the project is divided into different steps in order to easily focus each part of the whole system and make it work itself as a smaller system. This way, at the end of the project, the whole system will be merged using the acquired know-how from the previous steps. This working methodology has been selected because of the complexity of the work field and the lack of knowledge about it from the company.

Accordingly, this section is composed by first a description of the final system and its architecture and then all the steps required to complete the work.

- 3.2. Embedded PetaLinux Image,

- 3.3. Capture, display and store video image from USB camera

- 3.4. Processing image in host PC using a Convolutional Neuronal Network

- 3.5. Implementing Convolutional Neuronal Network in embedded system

## 3.1. System architecture and description

#### 3.1.1. System architecture

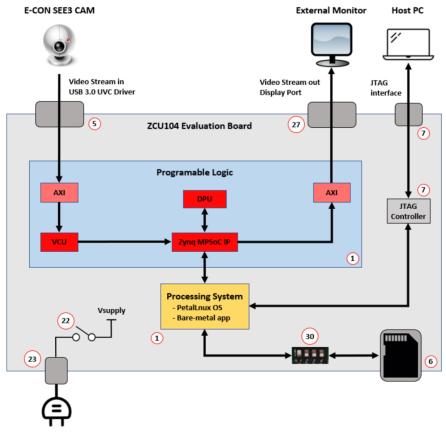

The architecture of the final system is described in Figure 3-1 below:

Figure 3-1: System architecture draft.

The reference numbers in *Figure 3-1* are the same than in *Figure 3-3* to easily relate these components to their descriptions in section below.

In Host PC, PetaLinux Embedded Image is configured and build and properly mounted in a boot SD card. This SD card is introduced in its ZCU104 Board slot (6) and SW6 (30) is set to realize the system boot from the SD card.

After powering the development board trough Power connector (23), being power switch (22) in ON position, the Processing system of the Zynq UltraScale+ MPSoC (1) boots from SD card and launches de PetaLinux OS and the bare-metal application.

System can be monitoring by the host PC through JTAG connection using a software such as Minicom. This way we can introduce the user and password of the OS in the host PC terminal.

Using the Linux drivers and the open-source multimedia framework GStreamer, a Video pipeline for the video stream can be defined. The first half of his pipeline starts from the USB Camera sending the video trough USB Video Class driver, this stream is received in the Programable Logic and either routed to the VCU to be encoded and stored as a file or passed through the VCU to the PS.

The C++ code running in the PS sends each frame to the DPU in the PL to be processed by Segnet CNN. The processed frame returns to the PS and it is sent to the second half of the video pipeline, in which the processed video is sent to an external monitor via Display Port.

# 3.1.2. HW Components description

Apart of the host PC which is Lenovo Think Pad L560 with Ubuntu 16.04 LTS OS and an external monitor with Display Port input, there are two basic HW components needed in the project:

1. USB Camera: See3CAM\_CU30\_CHL\_TC\_BX e-con Systems [11] (picture in *Figure 3-2*)

Figure 3-2: See3CAM CU30\_CHL\_TC\_BX Cam. Source: [12]

- 1/3" On Semiconductor AR0330 CMOS + Image Signal Processor (ISP)

- 3.4 Mp, color. Uncompressed UYVY format and Compressed MJPEG format

- USB 3.1 Gen 1 Super Speed<sup>1</sup>

- USB type-C connector

- Operating Voltage: 5V ± 5%, Current: 433mA

- High compatible with Linux OS. Plug and Play V4L2 driver.

<sup>&</sup>lt;sup>1</sup> This nomenclature is a little bit confusing. USB 3.1 Gen 1 is also known as USB 3.0 (up to 5 Gbit/s), may not be confused with USB 3.1 Gen 2 which allows data transfers up to 10 Gbit/s.

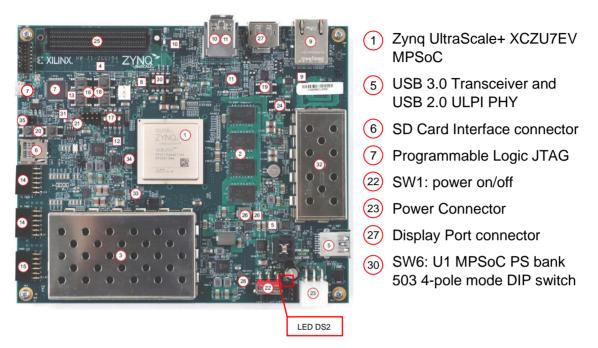

2. Development Board: Xilinx ZCU104 (picture in Figure 3-3)

This is a very complete board with a large number of capabilities intended to be used in a lot of different applications. Only the most relevant for this project are listed below.

Figure 3-3: ZCU104 development board main components for this project. Source: [7]

(1) The ZCU104 board is populated with the Zynq UltraScale+ XCZU7EV-2FFVC1156 MPSoC, which combines a powerful processing system (PS) and programmable logic (PL) in the same device. The PS in a Zynq UltraScale+ MPSoC features the Arm® flagship Cortex®-A53 64-bit quad-core processor and Cortex-R5 dual-core real-time processor [7].

# PS

The Zynq UltraScale+ MPSoC PS block has three major processing units [7]:

- Cortex-A53 application processing unit (APU)-Arm v8 architecture-based 64-bit quad core multiprocessing CPU.

- Cortex-R5 real-time processing unit (RPU)-Arm v7 architecture-based 32-bit dual real-time processing unit with dedicated tightly coupled memory (TCM).

- Mali-400 graphics processing unit (GPU)-graphics processing unit with pixel and geometry processor and 64 KB L2 cache.

# PL

The Xilinx® UltraScale<sup>™</sup> architecture in the programmable logic (PL) provides an extensive set of functions and resources. The Zynq® MPSoC devices include several peripherals controllers and functional units [8]. The relevant ones for this project are:

• DisplayPort Video and Audio Interfaces

- USB Interfaces

- Video Codec Unit (VCU). It provides multi-standard video encoding and decoding, including support for the high-efficiency video coding (HEVC) H.265 and advanced video coding (AVC) H.264 standards. The main features are:

- H.264 and H.265 standards encoding/decoding.

- $\circ$   $\;$  Up to eight simultaneous streams.

- 8K x 4K at a reduced frame rate.

- Progressive video only (no interlace support).

- I, IP, and IPB encoding/decoding.

- $\circ~$  8-bit and 10-bit color depth, YCbCr 4:2:2 and 4:2:0 video formats, and up to a 4K x 2K@60/8K x 2K@15 Hz rate.

- DPU. The Xilinx® Deep Learning Processor Unit (DPU) is a programmable engine dedicated for convolutional neural network. The unit contains a register configure module, a data controller module, and a convolution computing module. There is a specialized instruction set for DPU, which enables DPU to work efficiently for many convolutional neural networks [12].

# **USB** Controller

The USB 3.0 controller consists of two independent dual-role device (DRD) controllers. Both can be individually configured to work as host or device at any given time. The USB 3.0 DRD controller provides an eXtensible host controller interface (xHCI) to the system software through the advanced eXtensible interface (AXI) slave interface. An internal DMA engine is present in the controller, and it utilizes the AXI master interface to transfer data. The three dual-port RAM configurations implement the RX data FIFO, TX data FIFO, and descriptor/register cache. The AXI master port and the protocol layers access the different RAMs through the buffer management unit [8]. Its most important features are:

- Two USB 2.0/3.0 controllers.

- Supports a 5.0 Gb/s data rate.

- 64-bit AXI master port with built-in DMA.

- Supports 12 endpoints (six out and six in).

# **Display Port Controller**

The DisplayPort controller can source data from memory (non-live input) or the (live input) programmable logic (PL). The DisplayPort processes data and sends it out through the DisplayPort source-only controller block to external display devices or to the PL (live output). The DisplayPort pipeline consists of the DisplayPort direct memory access (DMA) for fetching data from memory, a centralized buffer manager, a display rendering block, an audio mixer block, and the DisplayPort source controller, along with the PS-GTR block, which contains the multi-gigabit transceivers that provide high-speed communication link between the media access controllers of the peripherals and their link partners outside the board. The DisplayPort pipeline supports an ultra-high definition (UHD) aggregate video bandwidth of 30 Hz [8].

It provides support for the following video formats:

- Resolution up to 4K x 2K at 30Fps.

- Y-only, YCbCr444, YCbCr422, YCbCr420, and RGB video formats.

- 6, 8, 10, or 12 bits per color components.

- Progressive video.

- A 36-bit native video input interface to capture live video.

- Non-live video from frame buffers using local DPDMA.

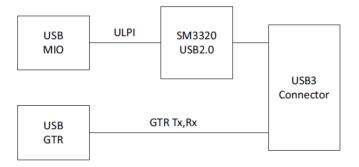

<sup>(5)</sup> The ZCU104 board uses a Standard Microsystems Corporation USB3320 USB 2.0 ULPI transceiver at U116 to support a USB connection to the host computer (see *Figure 3-4*). In this project, the USB 3.0 (USB 3.1 gen 1) connection to Zynq UltraScale USB GTR is used [7].

Figure 3-4: USB interface. Source: [7]

6 The ZCU104 board includes a secure digital input/output (SDIO) interface to provide access to general purpose non-volatile SDIO memory cards and peripherals. The ZCU104 SD card interface supports the SD1\_LS configuration boot mode documented in the *Zynq UltraScale+ MPSoC Technical Reference Manual (UG1085)* [8][7].

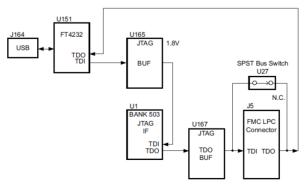

7 The ZCU104 board JTAG chain is shown in *Figure 3-5.*

Figure 3-5: JTAG Chain Block Diagram. Source: [7]

(22)(23) The ZCU104 board power switch is SW1. Sliding the switch actuator from the off to the on position applies 12V power from J52, a 6-pin mini-fit connector. Green LED DS2 illuminates when the ZCU104 board power is on [7].

<sup>(27)</sup> The Zynq UltraScale+ MPSoC provides a VESA DisplayPort 1.2 source-only controller that supports up to two lanes of main link data at rates of 1.62 Gb/s, 2.70 Gb/s, or 5.40 Gb/s. The DisplayPort standard defines an auxiliary channel that uses LVDS signaling at a 1 Mb/s data rate. [7]

<sup>30</sup> Configuration switch with 4-bit position. Boot mode is selected setting the 4 stitches as shown in table *Table 3-1*.

| Boot Mode | Mode Pins [3:0]      |

|-----------|----------------------|

| JTAG      | 0x0 - 0000           |

| QSPI32    | 0x2 - 0010 (default) |

| SD1       | 0xE - 1110           |

Table 3-1: Switch Configuration. Source: [7]

# 3.2. Embedded PetaLinux Image

As shown in 3.1. System architecture and description, Zynq UltraSCALE + MPSoC ZCU104 board is intended to be driven by an embedded OS called PetaLinux. So, the first step is focused in understanding and mounting an embedded OS image in an SD card and boot the ARM Cortex-A53 from it. The OS used in this step is composed with the minimal features and applications for simplicity. The chosen embedded Operating System is PetaLinux, it is the one recommended by Xilinx® due to its compatibility with the HW and the rest of the tools.

PetaLinux is an Embedded Linux System Development Kit targeting Xilinx® FPGA-based System-on-Chip designs [2]. It uses Yocto Project, which allows the developer to customize the embedded image and adapt it to a certain HW architecture.

PetaLinux contains [2]:

- Yocto Extensible SDK (e-SDK): allows the user to add new libraries and apps in the project. E-SDK consists of all the layers for the architecture (core, meta-oe...), sstate-cache that allows incremental project builds and the sysroots of the embedded OS.

- Minimal downloads: use of premirrors to download the needed source files.

- XSCT and tool chains: The PetaLinux tool uses XSCT underneath for all embedded SW apps. Linux tool chain for all architectures is from Yocto.

- PetaLinux CLI tools: This contains all the required PetaLinux commands.

The followed steps to successful build a PetaLinux Image to be used in Zynq UltraSCALE + MPSoC ZCU104 board are described below. However, to understand these steps it is necessary to know the structure of the Embedded OS Image and its required files, as well as the boot process of a Linux OS.

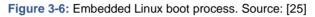

The basic boot process of a Linux OS starts with the named Stage 0. In this Stage, the ROM code detects boot mode and loads the executable code of First Stage Boot Loader (FSBL) from selected interface, in this case the SD card. Then, in Stage 1, the FSBL initializes an external memory and system clocks allowing to load a larger bootloader file, in this case U-Boot. In Stage 2 the U-Boot file loads the Linux Kernel and passes him the device tree. Finally, the Kernel initializes the Hardware and mounts the root file system. [25]

Figure 3-6 shows a summary of the basic Linux boot process

To go through these stages, there are some files that needs to be generated and stored in a certain mode in the SD card. These files are:

- PL Bitstream: Stored in *boot.bin* container. Definition of the PL (Programable Logic) exported by Vivado in the *wrapper\_file.hdf*. After adding it to PetaLinux project, the file is automatically stored with the name: *system.bit*

- FSBL: Stored in *boot.bin* container. Generated by building PetaLinux project with name: *zynq\_fsbl.elf*.

- PMU (Platform Management Unit) Firmware: Stored in *boot.bin* container. This is an optional file only for Zynq UltraScale+ MPSoC that controls the power-up, reset, and monitoring of resources within the system. Generated by building PetaLinux project with name: *pmufw.elf*.

- ATF (Arm Trusted Firmware): Stored in *boot.bin* container. It provides a reference to secure software for ARMv8-A architecture, and it provides implementations of various interface standards and Secure monitor code for interfacing to Normal world software. This firmware is for Zynq UltraScale+ MPSoC only. Generated by building PetaLinux project with name: *bl31.elf*.

- U-Boot: Stored in *boot.bin* container. Generated by building PetaLinux project with name: *u-boot.elf*.

- Kernel: Stored in Image.ub. Generated by building PetaLinux project.

- Root file System: Generated by building PetaLinux project with name: rootfd.tar.gz.

- Device tree: Stored in Image.ub. Generated by building PetaLinux project.

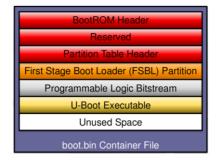

Some of these files are stored in a bigger file called *boot.bin* container. After the PetaLinux project build, when all the required files have been generated, this container is mounted. This is the last step of the embedded PetaLinux Image.

Figure 3-7 Shows the structure of the boot.bin container.

Figure 3-7: Boot.bin container file diagram. Source: [25]

Once it is known the structure of a PetaLinux Image, the required steps to create, configure and build a PetaLinux project can be detailed.

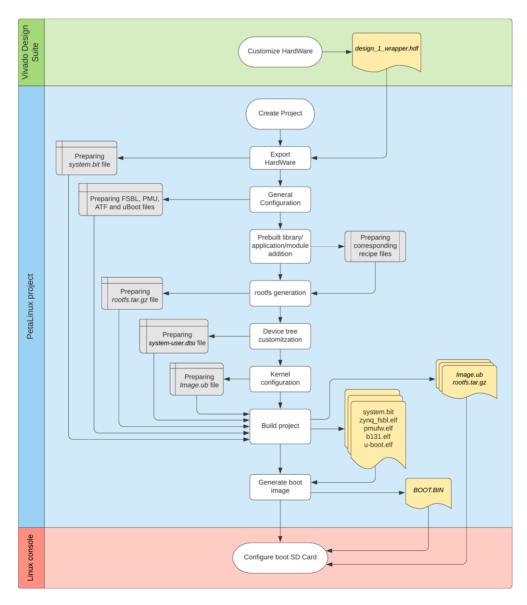

In *Figure 3-8* a summary of the steps to go through and the flow of the generated files is shown:

Figure 3-8: PetaLinux Embedded Image project steps diagram.

In this project step, the simplest PetaLinux image has been generated because the objective at this point is to learn the basic needs of the embedded PetaLinux and how to create the image, properly configure the SD boot and be able to have the OS running in the board. Therefore, some of the previous steps are not followed in this project step, the scheme above is the full project process. Specifically in this step there is no custom library, application or module addition, and default kernel and device tree are used.

# 3.2.1. Basic Programable Logic

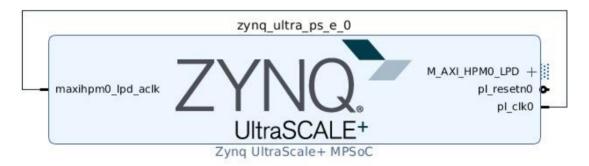

As already mentioned, this project step is kept as simple as possible. No peripherals are used, or PL functionality is required. Only the processing system IP (Zynq UltraScale+MPSoC) is added to Vivado project as shown in *Figure 3-9*.

Figure 3-9: Basic Programable Logic Vivado Block Design.

After creating an HDL wrapper, compile, build and generate Bitstream, it is necessary to export HW to use it in the next step.

# 3.2.2. Create PetaLinux project, export HW and set general configuration

Once the programmable logic is defined and exported, the PetaLinux project can be created. Due to the difficulties at download and install all the tools with the certain versions it is highly recommended to use a virtual environment. In this project, the default Python virtual environment for Linux has been used.

Before start using PetaLinux, the file *settings.sh* from the PetaLinux installation file needs to be sourced to Ubuntu using this command line:

\$: source <path to petalinux .sh file>/settings64.sh

Then the system is able to use PetaLinux commands. Then, the easiest way is to create a project from a template using the next command (parameters explained in *Table 3-2*):

\$: petalinux-create --type project --template zynqMP --force -name

<project name>

| Option             | Functional Description                                                                                                                   | Value Range                                               | Default Value        |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|----------------------|

| -t,type TYPE       | Specify the TYPE of object to create. This is required.                                                                                  | <ul><li> project</li><li> apps</li><li> modules</li></ul> | None                 |

| -n,name NAME       | Create object with the specified<br>NAME. This is optional when<br>creating a project from a BSP<br>source. Otherwise, this is required. | User-specified                                            | None                 |

| -p,project PROJECT | PetaLinux project directory path.<br>This is optional.                                                                                   | User-specified                                            | Current<br>Directory |

| force              | Overwrite existing files on disk.<br>This is optional.                                                                                   | None                                                      | None                 |

| -h,help            | Display usage information. This is optional.                                                                                             | None                                                      | None                 |

| Table 3-2: | petalinux-create | Command Line | Options. | Source: [14] |

|------------|------------------|--------------|----------|--------------|

|            | petalinax ereate |              | options. |              |

A new folder with the name "project name" will be created. After entering this folder, we can export the HW writing the following command:

\$: petalinux-config --get-hw-description=<path to .hdf directory in Vivado project folder>

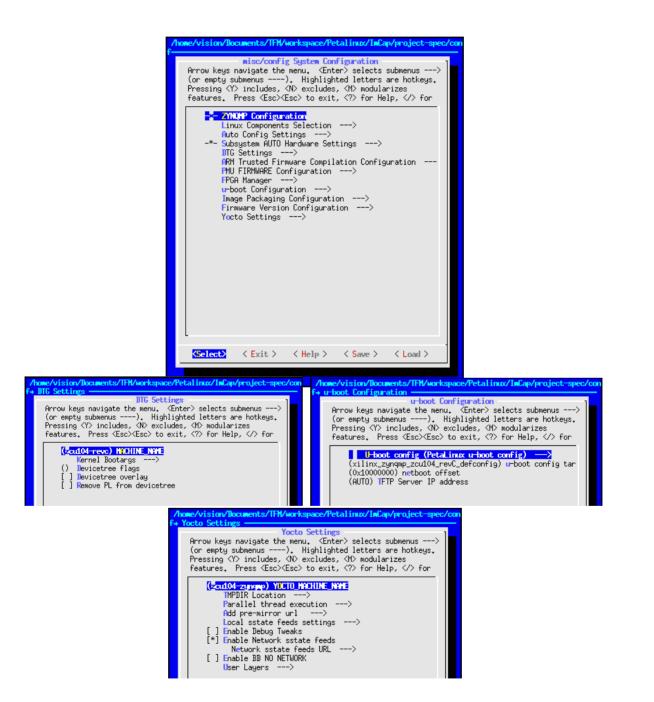

A new window with the HW configurations will open and the following parameters must be specified (see APPENDIX A):

- DTG Settings  $\rightarrow$  (zcu104-revc) MACHINE NAME

- u-boot Configuration → (xilinx\_zynqmp\_zcu104\_revC\_defconfig) uboot config target

- Image Packaging Configuration  $\rightarrow$  Root file System type  $\rightarrow$  SD card

- Yocto Settings  $\rightarrow$  (zcu104-zynqmp) YOCTO MACHINE NAME

In this way, we are configuring properly the HW configurations with our development board and telling PetaLinux that rootfs will be stored in a SD card. When pressing the *ok* button, the window automatically closes itself and PetaLinux may configure all and generate the *system.bit* file to be later included in the BOOT.BIN container. Also, FSBL, ATF, PMU and uboot files are prepared to be built. These files are configured by default, so no special configuration needs to be specified apart of u-boot configuration.

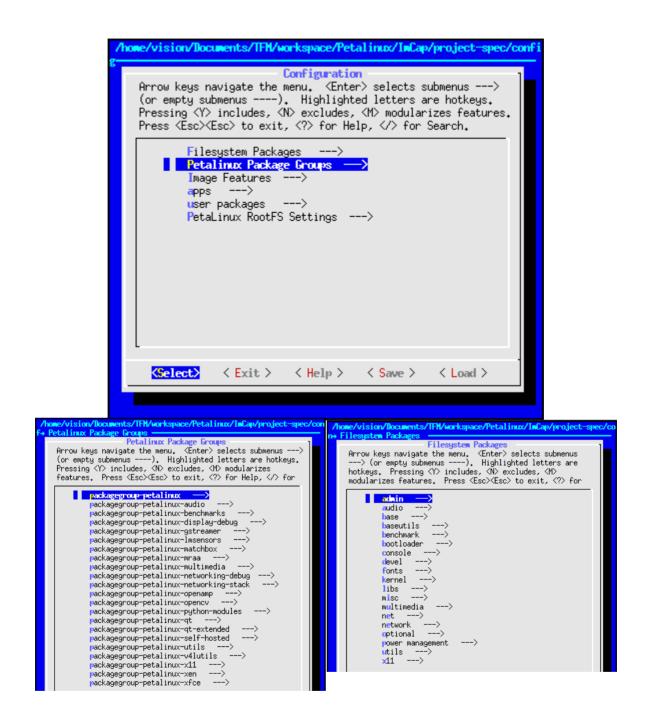

### 3.2.3. Rootfs generation

As already mentioned, in this first PetaLinux image there is no custom application or module, so directly we can configure rootfs using this command:

**\$:** petalinux-config -c rootfs

-c term indicates that the configuration to be open refers to a component. A component can be rootfs, kernel, bootloader, device-tree, etc.

A new window will open to customize the rootfs of the PetaLinux image (see APPENDIX A). At this point, we don't need any specific library or application because it is only a test to set-up the PetaLinux image, but to display the default GUI in a monitor we activate the following:

- filesystem Packages  $\rightarrow$  misc  $\rightarrow$  python3  $\rightarrow$  all

- filesystem Packages  $\rightarrow$  misc  $\rightarrow$  python3-async

- filesystem Packages  $\rightarrow$  misc  $\rightarrow$  python3-git

- filesystem Packages  $\rightarrow$  misc  $\rightarrow$  python3-gitdb

- filesystem Packages  $\rightarrow$  misc  $\rightarrow$  python3-setuptools

- filesystem Packages  $\rightarrow$  misc  $\rightarrow$  python3-smmap

- filesystem Packages  $\rightarrow$  x11  $\rightarrow$  base  $\rightarrow$  libdrm  $\rightarrow$  libdrm

- filesystem Packages  $\rightarrow$  x11  $\rightarrow$  base  $\rightarrow$  libdrm  $\rightarrow$  libdrm-tests

- filesystem Packages  $\rightarrow$  x11  $\rightarrow$  base  $\rightarrow$  libdrm  $\rightarrow$  libdrm-kms

- Petalinux Package Groups  $\rightarrow$  packagegroup-petalinux-matchbox

- Petalinux Package Groups  $\rightarrow$  packagegroup-petalinux-x11

After pressing ok in the window, PetaLinux prepares rootfs to be built.

### 3.2.4. Build project and generate Boot Image

When all the files are ready and well configured, the following command launches the build of the whole project:

#### **\$:** petalinux-build

This will take a significant amount of time, the larger the project, the slowest the building.

Once the building finishes, the generated files will appear in their corresponding folders inside the project folder. These files are: *system.bit, zynq\_fsbl.elf, pmufw.elf, b131.els, u-boot.els, image.ub* and *rootfs.tar.gz.*

The first five ones are then combined to form the *boot.bin* container using the following command:

```

$: petalinux-package --boot --format BIN -fsbl

images/linux/zynqmp_fsbl.elf --u-boot images/linux/u-boot.elf --pmufw

images/linux/pmufw.elf -atf images/linux/bl31.elf --fpga

images/linux/system.bit -force

```

When the process finishes, *boot.bin* is also generated and ready to mount the boot SD card.

### 3.2.5. Configure boot SD card

To boot from SD card, it is necessary to properly configure it and store the files. In this project, 2 partitions are needed for the SD card:

- boot partition: FAT32 format. ≥ 60 MB. boot.bin and image.ub files.

- root partition: Ext4 format.  $\geq$  3 GB. rootfs.tar.gz file.

Files in the *boot* partition stores required files for booting the image and in *root* partition, the rootfs will be mounted.

Finally, in the zcu104 board, the SW6 should have a specific configuration indicated in *Table 3-1* of section 3.1.2. HW Components description in order to boot from SD card. This is 1110 (ON, ON, ON, OFF) as shown in *Figure 3-10*.

Figure 3-10: SW6 SD boot configuration.

# 3.3. Capture, display and store video image from USB camera

This second project step is focused on modifying the PetaLinux Embedded Image to be able to capture image from a USB camera, display a Video stream in an external monitor via Display Port, and store a video file to be processed in the host PC.

With this objective, it is necessary to develop a complete HW design in the FPGA to capture video, process it in the VCU and Display the video. Also, some changes in the PetaLinux project may be introduced to add more functionality than in the basic one. Lastly, one need to know how to define video pipelines from the host PC terminal.

Since the camera is a USB camera compatible with UVC driver, we can use the V4L2 driver to enumerate and manage the device. Also, the external monitor can be managed with the GStreamer video sink kmssink so both devices and the VCU can be connected and configured using the open-source multimedia framework GStreamer.

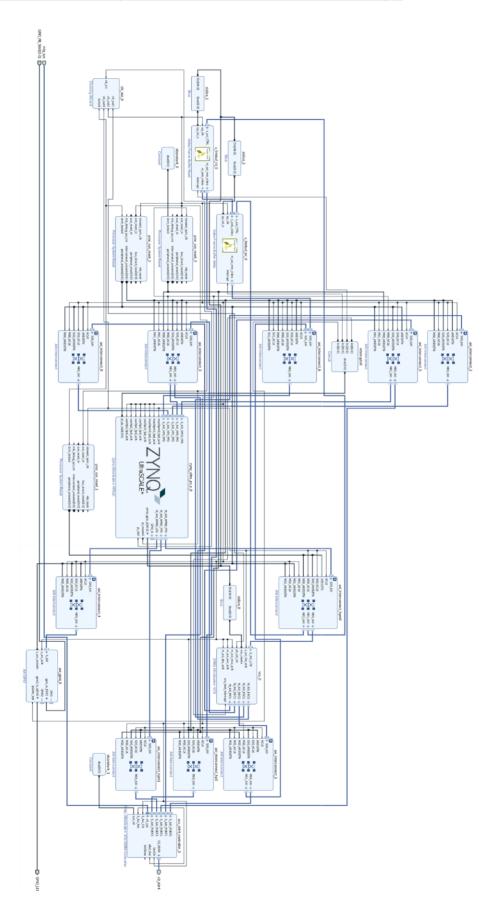

# 3.3.1. Programable logic

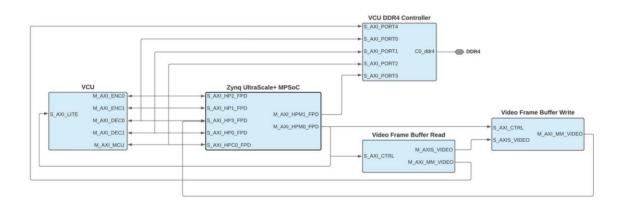

In the previous project step, the definition of the HW in the FPGA was only the Zynq UltraScale+ MPSoC IP. In this step, it is necessary to add some peripherals in order to manage the video pipeline. *Figure 3-11* shows a simplified diagram of the PL design, and each part is explained below. This project is based on rdf0428-zcu106-vcu-trd-2018-3 and *zcu102-dpu-trd-2018-2-190531* [6] projects, but for simplification purposes only the main IPs needed to properly understand the system are shown in the diagram, omitting the reset circuitry, the AXI communication interconnections and an unused GPIO (see full diagram in APPENDIX C).

Figure 3-11: Image Capture PL Diagram.

The main IP is the Zynq UltraScale+ MPSoC where PetaLinux OS is running. In the PS, the USB3.0 camera is enumerated and configured, and the video stream is captured. This stream can be sent to the Display port through DMA Video Frame buffers or to VCU to encode it. Zynq UltraScale+ MPSoC has four bidirectional AXI interfaces with VCU to exchange video data, one Master AXI interface to control VCU and DMA buffers, one

Master AXI to control VCU DDR4 Controller and one Slave AXI interface coming from VCU.

VCU IP is composed by two modules, the Encoder and the Decoder and each implement a 32-bit MCU to run the firmware, control both blocks and handle interaction between hardware blocks and with APU [26].

- The Encoder module data path is built with two 128-bit AXI4 interconnections to fetch and write video data from external DDR memory attached to either the Processing System (PS) or the Programmable Logic (PL). [26]

- The Decoder module data path is built with two 128-bit AXI4 interconnections used to fetch video input data and store video output data from/to the system memory in the Processing System (PS) or in the Programable Logic (PL). [26]

- Control path for both modules is processed by MCU using two 32-bit AXI4 interconnections. One AXI-Lite slave used by the APU to control the MCU and one master interface used by MCU to communicate with the APU.

Finally, the video stream is sent to the Display Port Controller in two ways:

- Using DMA Video Frame Buffers. (Live-Video)

- Storing the frames in the DDR4 to be read by DPDMA, Display Port DMA. (Nonlive Video)

#### 3.3.2. PetaLinux project changes

Once the HW is defined and exported from Vivado, it is time to create and configure the PetaLinux project. The main difference between the previous PetaLinux image and the new one is in the rootfs libraries. In this new set of libraries, gstreamer, V4L2, OpenCV and OpenAmp functionalities are added to successfully build the desired video pipelines.

First, we create the project and export HW in the same way than in previous project step and with the same configuration:

\$: petalinux-create --type project --template zynqMP --force -name

<project name>

\$: petalinux-config --get-hw-description=<path to .hdf directory in Vivado project folder>

Then, there are a set of VCU functions using GStreamer that needs to be added in a recipe file to make it selectable later in the rootfs configuration by means of this code line:

```

$: echo 'IMAGE_INSTALL_append = " gstreamer-vcu-examples"' >> <project

root>/project-spec/meta-user/recipes-core/images/petalinux-image-

full.bbappend

```

This way, when preparing the set of libraries of rootfs to be build, we can select all the needed functionalities.

Rootfs configurated is called as in previous section:

\$: petalinux-config -c rootfs

In addition to all the libraries selected in the basic project, the following ones must be added too:

- filesystem Packages  $\rightarrow$  libs  $\rightarrow$  opencv  $\rightarrow$  opencv, opencv apps

- filesystem Packages  $\rightarrow$  misc  $\rightarrow$  gst-player

- filesystem Packages  $\rightarrow$  misc  $\rightarrow$  gst-plugins-base  $\rightarrow$  base, apps

- filesystem Packages  $\rightarrow$  misc  $\rightarrow$  gst-plugins-good

- filesystem Packages → misc → gstreamer1.0-meta-base → base, video, x11

- filesystem Packages  $\rightarrow$  misc  $\rightarrow$  gstreamer1.0-plugins-bad

- filesystem Packages → misc → gstreamer1.0-plugins-base → base, apps

- filesystem Packages  $\rightarrow$  misc  $\rightarrow$  gstreamer1.0-plugins-good

- filesystem Packages  $\rightarrow$  misc  $\rightarrow$  openamp-fw-echo-testd

- filesystem Packages → misc → openamp-fw-mat-muld

- filesystem Packages → misc → openamp-fw-rpc-demo

- filesystem Packages → misc → v4l-utils → v4l-utils, libv4l, irkeytable, media-ctl, rc-keymaps

- filesystem Packages  $\rightarrow$  multimedia  $\rightarrow$  all gstreamer

- Petalinux Package Groups  $\rightarrow$  packagegroup-petalinux-gstreamer

- Petalinux Package Groups  $\rightarrow$  packagegroup-petalinux-openamp

- Petalinux Package Groups → packagegroup-petalinux-opencv

- Petalinux Package Groups  $\rightarrow$  packagegroup-petalinux-v4lutils

- user packages  $\rightarrow$  gstreamer-vcu-examples

After configuring the rootfs, the project needs to be built and Image files needs to be packaged with the same commands:

\$: petalinux-build

```

$: petalinux-package --boot --format BIN -fsbl

images/linux/zyngmp fsbl.elf --u-boot images/linux/u-boot.elf --pmufw

```

images/linux/pmufw.elf -atf images/linux/bl31.elf --fpga images/linux/system.bit -force

Then, the SD card can be configured and the new OS launched in the board.

# 3.3.3. GStreamer video pipelines

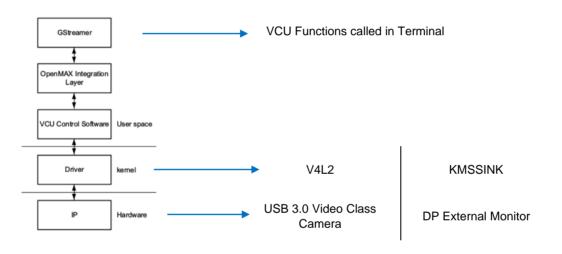

Using a text-based serial port communications program like Minicom, one can navigate into the root file system of the OS and manage some functions. To generate the video pipelines, GStreamer functions already added are needed among with V4L2 driver and KMSSINK plugin. Also, VCU is used to encode and/or decode the incoming video. The needed Software/Hardware stack is shown in *Figure 3-12*:

Figure 3-12: Software stack. Source: [26]

In the GStreamer VCU Demo functions there are two that can be used directly to display and store video (see APPENDIX C). The first one is *vcu-demo-camera-encode-decode-display.sh* in which the only parameter that may be changed is the resolution Full HD (1920x1080). This function is called by typing:

\$: vcu-demo-camera-encode-decode-display.sh -s 1920x1080

The function directly enumerates the camera and the display, configures the devices parameters, and builds the pipeline. The Video Stream should be playing in the monitor after calling this function.

The second one is *vcu-demo-camera-encode-file.sh*. This function stores a video file called *camera\_output.ts* in the current directory. In this function one can specify the resolution and the number of frames to be captured and stored.

\$: vcu-demo-camera-encode-file.sh -s 1920x1080 -n 1000

Again, by calling the function, the camera and display are enumerated and the pipeline is mounted.

These two functions are useful but GStreamer allows the developer to directly build and configure the pipeline in the terminal. This way one can simplify or modify the parameters and devices used. For example, in the first function it is not needed to encode and decode the video and the second pipeline can be improved controlling the quality of the encoding. To do so, the developer will need to know how to enumerate the devices, the supported parameters of each one and how to build the pipeline.

To enumerate the USB camera and know its properties, two V4L2 commands can be used:

| \$: | v4l2-ctl | list-devices      | $\rightarrow$ | to enumerate devices          |

|-----|----------|-------------------|---------------|-------------------------------|

| \$: | v4l2-ctl | -list-formats-ext | $\rightarrow$ | to list devices input formats |

To know the display modes supported for the decive one can consult the modes file using the command:

\$: cat /sys/class/drm/card0-DP-1/modes

And check the kmssink capabilities with the command:

**\$:** gst-launch-1.0 videotestsrc ! kmssink

Once the video source and the video sink are determined, the capabilities of the VCU encoder can be checked with the command:

\$: gst-inspect-1.0 omxh264enc

Tables 3-3, 3-4 and 3-5 show the specifications summary of each device:

| 1                |                                     |                              |  |

|------------------|-------------------------------------|------------------------------|--|

|                  | Camera                              |                              |  |

| Uncompressed YUV |                                     | Compressed MJPEG             |  |

|                  | VGA (640&480) @ 30 & 60 fps         | VGA (640&480) @ 30 & 60 fps  |  |

|                  | HD (1280 x 720) @ 30 & 60 fps       | HD (1280 x 720) @ 60 fps     |  |

|                  | FHD (1920 x 1080) @ 15, 30 & 60 fps | FHD (1920 x 1080) @ 60 fps   |  |

|                  | 3MP (2304 x 1296) @ 15 & 30 fps     | 3MP (2304 x 1296) @ 60 fps   |  |

|                  | 3.4MP (2304 x 1536) @ 12 & 24 fps   | 3.4MP (2304 x 1536) @ 48 fps |  |

|                  | 1920 x 1280 @ 25 & 50 fps           | 1920 x 1280 @ 50 fps         |  |

|                  | 1152 x 768 @ 30 & 60 fps            | 1152 x 768 @ 60 fps          |  |

|                  | 1280 x 960 @ 30 & 58 fps            | 1280 x 960 @ 58 fps          |  |

|                  | 2048 x 1536 @ 21 & 42 fps           | 2048 x 1536 @ 50 fps         |  |

Table 3-4: Camera Video features. Source [11]

| Format   | BPC/BPP | R       | G       | В      | Cr      | Y       | Cb     | Cr/Cb   | Y       |

|----------|---------|---------|---------|--------|---------|---------|--------|---------|---------|

| RGB      | 6/18    | [35:30] | [23:18] | [11:6] |         |         |        |         |         |

| RGB      | 8/24    | [35:28] | [23:16] | [11:4] |         |         |        |         |         |

| RGB      | 10/30   | [35:26] | [23:14] | [11:2] |         |         |        |         |         |

| RGB      | 12/36   | [35:24] | [23:12] | [11:0] |         |         |        |         |         |

| YCbCr444 | 6/18    |         |         |        | [35:30] | [23:18] | [11:6] |         |         |

| YCbCr444 | 8/24    |         |         |        | [35:28] | [23:16] | [11:4] |         |         |

| YCbCr444 | 10/30   |         |         |        | [35:26] | [23:14] | [11:2] |         |         |

| YCbCr444 | 12/36   |         |         |        | [35:24] | [23:12] | [11:0] |         |         |

| YCbCr422 | 8/16    |         |         |        |         |         |        | [35:28] | [23:16] |

| YCbCr422 | 10/20   |         |         |        |         |         |        | [35:26] | [23:14] |

| YCbCr422 | 12/24   |         |         |        |         |         |        | [35:24] | [23:12] |

| YONLY    | 8/8     |         |         |        |         |         |        |         | [35:28] |

| YONLY    | 10/10   |         |         |        |         |         |        |         | [35:26] |

| YONLY    | 12/12   |         |         |        |         |         |        |         | [35:24] |

| Video Coding Parameter           | H.265 (HEVC)               | H.264 (AVC)                |  |

|----------------------------------|----------------------------|----------------------------|--|

| Profiles                         | Main                       | Baseline                   |  |

|                                  | Main Intra                 | Main                       |  |

|                                  | Main10                     | High                       |  |

|                                  | Main10 Intra               | High10                     |  |

|                                  | Main 4:2:2 10              | High 4:2:2                 |  |

|                                  | Main 4:2:2 10 Intra        | High10 Intra               |  |

|                                  |                            | High 4:2:2 Intra           |  |

| Levels                           | Up to 5.1 High Tier        | Up to 5.2                  |  |

| Resolution and Frame Rate (1)(2) | 4096x2160p60 with specific | 4096x2160p60 with specific |  |

|                                  | device (-2, -3)            | device (-2,-3)             |  |

|                                  | 3840×2160p60               | 3840×2160p60               |  |

|                                  | 3840×2160p30               | 3840×2160p30               |  |

|                                  | 1920×1080p60               | 1920×1080p60               |  |

|                                  | 1920×1080p30               | 1920×1080p30               |  |

|                                  | 1280×720p60                | 1280×720p60                |  |

|                                  | 1280×720p30                | 1280×720p30                |  |

| Bit Depth                        |                            |                            |  |

| GStreamer                        | 8-bit, 10-bit              | 8-bit, 10-bit              |  |

| OMX                              | 8-bit, 10-bit              | 8-bit, 10-bit              |  |

| VCU Control Software             | 8-bit, 10-bit              | 8-bit, 10-bit              |  |

| Chroma Format                    |                            |                            |  |

| GStreamer                        | 4:2:0, 4:2:2               | 4:2:0, 4:2:2               |  |

| OMX                              | 4:2:0, 4:2:2               | 4:2:0, 4:2:2               |  |

Table 3-3: VCU Encoder features. Source: [26]

[35:24] Table 3-5: Display Port Live Video Format. Source: [8]

The video specifications of the camera need to match with the supported specifications of the VCU and Display Port controller.

To display the video without encoder and decoder, it is only needed to list the video source (camera) and its settings and the video sink (external monitor). For this test, the video format chosen is 8-bit YUV 422 at FHD (1920x1080) at 60fps.

```

$: gst-launch-1.0 v4l2src device=/dev/video0 ! video/x-raw, \

> format=\(string\)UYVY, width=1920, height=1080, framerate=60/1 ! \

> kmssink bus-id=fd4a0000.zynqmp-display fullscreen-overlay=1

```

To improve the quality of the encoded video [26], the following pipeline has been used:

```

$: gst-launch-1.0 -e v4l2src device=/dev/video0 num-buffers=300 ! \

> video/x-raw,width=1920,height=1080,framerate=30/1 ! \

> videoconvert ! video/x-raw, format=\(string\)NV16 ! \

> omxh264enc control-rate=constant gop-mode=low-delay-p gdr-

mode=vertical \

> gop-length=0 target-bitrate=5500 ! \

> video/x-h264, profile=high-4:2:2 ! h264parse ! queue ! \

> mpegtsmux name=mux mux. ! filesink location=/home/improved.ts

```

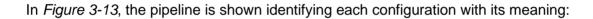

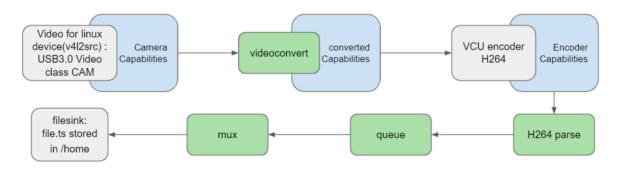

Figure 3-13: GStreamer custom capture-encode-store\_file pipeline

- 300 frames of the video source set as default video format (YUYV 422 8-bit) at FHD, 30 fps are captured.

- These frames are converted into NV16 format: YUV file contains 4:2:2 8-bit video samples stored in planar format with all picture Luma (Y) samples followed by interleaved U and V Chroma samples [26].

- Encoder is configured using H.264 (AVC) high 4:2:2 profile and optimized parameters to be stored at maximum quality with the better performance:

- Control rate = constant.

- Gop-mode = low-delay-p. Specifies group of pictures configuration. lowdelay-p ( IPPPPP....). [26]

- Gdr-mode = vertical. When gop-mode is set to low\_delay\_p, gdr-mode specifies which scheme should be used for Gradual Decoder Refresh: vertical option means that a vertical bar moving from left to right is used.

[26]

- Gop-length = 0. Distance between two consecutive Intra frames. Specify integer value between 0 and 1,000. Value 0 and 1 corresponds to Intraonly encoding. [26]

For better understanding of Gop-mode and Gop-length, some knowledge of H.264 Video Codec is required.

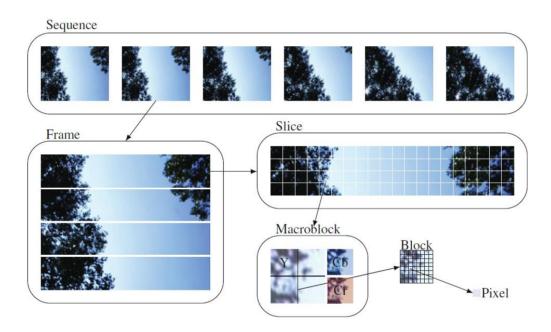

To reduce the size of a video, the frame is divided into independent sections called slices, that are also divided into smaller sections called Macro Blocks (MBs). These MBs are groups of blocks containing Luma pixels (Y) or croma pixels (Cb, Cr). See *Figure 3-14*

Figure 3-14: H.264 (AVC) frame distribution.

This way, MB of some frames can be predicted using different techniques instead of recording and storing each full frame.

The H.264 video codec defines three main types of frames which are I-frames, P-frames and B-frames. A Gop (group of pictures) is a set of combined frames of different type.

- I-frames: Intra prediction frames. Is independent of the other frames and its MBs are predicted based on adjacent MBs of the same frame.

- P-frames: Predicted frames. Uses Intra prediction and motion estimation to predict its MBs. It depends on previous frames that can be either I-, P- or B-frames.

- B-frames: Bidirectional predicted frames. It uses bidirectional motion estimation to predict its MBs. It depends on previous and/or future frames.

# 3.4. Processing image in host PC using a Convolutional Neuronal Network

This project step is focused on processing the captured images taken with the system configured in the previous one in the host PC to validate the CNN before implementing it in the development board.

Once the CNN is chosen, it is tested first with a single image to understand the performance. Then, the code is adapted to process a downloaded sample video and validated with own captured video.

The original code can be downloaded from the Cornell University website [40].

# 3.4.1. SegNet

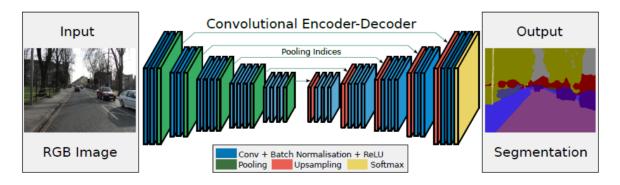

Basing in the objectives and the scope of the project, any of the CNN may be used since the main issue is how to successfully implement a system running this NN in an FPGA. However, the main purpose is to make the first move to finally achieve an automotive application using FPGA in front of GPU to run ML algorithms. So, even if this final application is out of the scope of the project, it seems appropriate to work with a Semantic Segmentation Neural Network, for instance SegNet.

SegNet is a Deep fully convolutional Neural Network for semantic pixel-wise segmentation. The architecture of its core trainable segmentation engine consists of an encoder network with its corresponding decoder network followed by a final pixel-wise classification layer. (See *Figure 3-15*). The encoder network is built with 13 convolutional layers which corresponds to the first 13 convolutional layers in the VGG16 network [38] designed for object classification. Each encoder layer has a corresponding decoder layer, so the decoder network is also composed with 13 convolutional layers. The output of the decoder network is fed to a multi-class soft-max classifier to produce class probabilities for each pixel independently. [33]

*Figure 3-15* shows the architecture of SegNet, its layer types and an example of inputoutput images:

Figure 3-15: SegNet architecture. Source: [33]

# 3.4.2. SegNet Image processing code

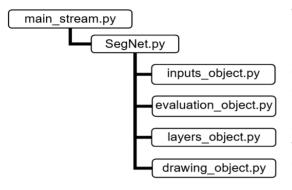

To test the SegNet CNN, sample images have been processed in a python project. This project consists in a main file that reads the image from a folder and calls the SegNet to process it. Its file structure is shown in *Figure 3-16:*

Figure 3-16: SegNet project code file architecture.

The main file reads images from a specified path using the OpenCV command cv.imread(). This command, by default, converts from the YUV colour space to BGR colour space. Since SegNet class expects RGB image, before calling it, the image should have another colour space transformation from BGR to RGB using the command cv2.cvtColor(image, cv2.COLOR\_BGR2RGB). Then, SegNet is called and the output image is stored in a specified folder.

The code of the main function is:

```

def main():

for arg in sys.argv[1:]:

print('Analysis of file: ', arg)

if os.path.isfile(arg):

im = cv2.imread(arg)

im = cv2.cvtColor(im, cv2.COLOR BGR2RGB)

pred tot, var tot, inference time, im =

SegNet().visual results external image(im,

FLAG_MAX_VOTE=False)

cv2.imwrite('res image/img.jpg', im)

else:

print('File ', arg, ' is not found.')

exit()

if name_

== "__main__":

main()

```

The SegNet.py file is in charge to resize the image to its required size (480x360), process the image with the help of *inputs\_object.py*, *evaluation\_object.py* and *layers\_object.py*, draw the output image with *drawing\_objects.py* and return the image.

This code has been tested with sample images and works properly. This may be enough since in the ZCU104 development board, in the ideal case, it may work frame by frame. But since the processing time for each frame predictably will exceed the required timing to get real time operation, it may be useful to leave open the possibility to process a video file stored in the system.

To do so, first the code of main file needs to be modified to read and write a video file instead of a single image. Instead of opening a single image with *cv.imread()* function, now the video needs to be opened with the OpenCV function *cv2.VideoCapture()*. Then, go through the video frame per frame processing each and store all the frames in a selected folder. Finally, a custom function to build the video from the stored frames is called and the resulting video is stored. The modified code is as follows:

```

def main():

for arg in sys.argv[1:]:

print('Analysis of file: ', arg)

if os.path.isfile(arg):

cap = cv2.VideoCapture(arg)

i = 1

while (cap.isOpened()):

ret, frame = cap.read()

if ret == False:

break

frame = cv2.cvtColor(frame, cv2.COLOR BGR2RGB)

pred tot, var tot, inference time, im =

SegNet().visual results external image(frame,

FLAG MAX VOTE=False)

cv2.imwrite('res frames/frame'+ str(i).zfill(4)

+'.jpg',im)

i += 1

cap.release()

cv2.destroyAllWindows()

createVideo('res frames')

else:

print('File ', arg, ' is not found.')

exit()

if __name__ == "__main__":

main()

def createVideo(frames path):

img array = []

frame array = glob.glob(frames path+'/*.jpg')

frame array.sort()

for filename in frame array:

img = cv2.imread(filename)

height, width, layers = img.shape

size = (width, height)

img array.append(img)

out = cv2.VideoWriter('output.avi', cv2.VideoWriter fourcc(*'DIVX'),

15, size)

for i in range(len(img array)):

out.write(img_array[i])

out.release()

return

```

Using the new code, two video samples are checked. The first one is a sample video downloaded from internet captured with a car front camera recording a journey through a city. The point to use this video is to simulate the output of the CNN when an autonomous driving camera is used.

Then, the second video is one recorded with the capture image system built in the previous step in order to verify that the output images from the capture pipeline are a proper input for the processing stage.

See the results in the section 4.3. CNN capture in host PC

## 3.5. Implementing Convolutional Neuronal Network in embedded system

Finally, this is the last stage of the project. At this stage, all the previous subsystems and the acquired knowledge are merged and applied to build the final full system.

This stage may result in a complete embedded system that captures video from a USB camera, process either each frame in real time or a stored video file with a segmentation CNN and shows the image in a screen via display port. Nevertheless, it cannot be completed because the Xilinx process to implement the CNN in its DPU IP using its software DNNDK is not as robust as advertised. It is explained later but, in this report, the process has been followed properly and at the end an error that even the Xilinx specialist doesn't know how to fix occurs.

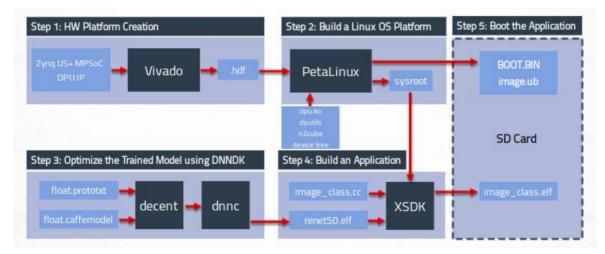

Even so, the process to implement an embedded PetaLinux operating system with a capture, process and display a video pipeline implementing a CNN in PL is the shown in *Figure 3-17* and explained below.

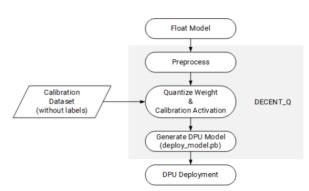

Figure 3-17: Development Flow of an Edge-based AI Application example. Source: [48]

The first step is, as in previous project stages, to define de HW in the PL side, and export it to be included in the PetaLinux project. Then, the OS image is built in a same way than done until now but adding the DPU capabilities and modifying the device tree. The main difference is that before configuring the rootfs, the CNN needs to be implemented in the

DPU using the DNNDK Xilinx software. Finally, the resulting files along with the bare metal code to call the Net are managed in the Xilinx SDK.

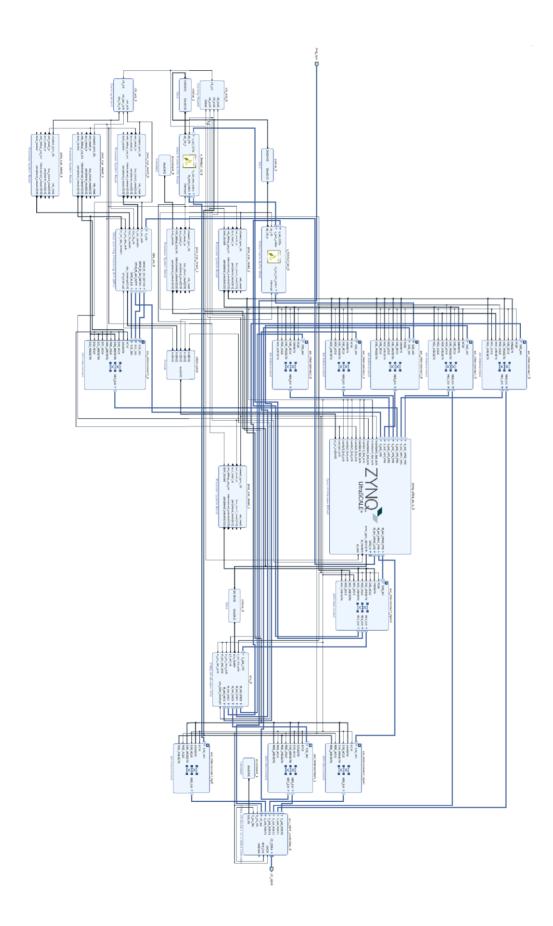

## 3.5.1. Full System Programable logic

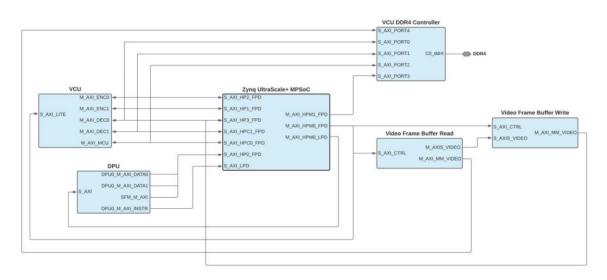

The block design in the PL side is almost the same as that used in the Image Capture subsystem. All its functionalities have been kept and only the Deep Learning Processing Unit (DPU) has been added in order to implement the CNN and process the obtained images using that IP. *Figure 3-18* illustrates the final HW Diagram. (See Appendix D for the complete Block Design).

Figure 3-18: Full system PL Diagram.

When adding the DPU in the project, there are some aspects to consider.

1. The chosen CNN can be implemented in the DPU.

The DPU has a set of layer operations that are supported and not in any order. One needs to ensure that the layers in the chosen Network and its order are supported. In the case of this project, this verification has been done at the moment of selecting the SegNet network. The supported operations in the DPU are:

- Conv

- o Dilation

- Pooling

- o Max

- $\circ$  Average

- ReLU/Leaky Relu/ Relu6

- Full Connected (FC)

- Concat

- Elementwise

- Deconv

- Depthwise conv

- Batch Normalization

- Mean scale

- Upsampling

- Split

- Reorg

- Softmax (additional core)

Since as shown in *Figure 3-15*, SegNet uses Conv, Batch Normalisation, ReLU, Pooling, Upsampling, Deconv and Softmax layers, it seems a suitable Net.

Regarding the order, *Table 3-6* can be consulted to check the availability of the operations order:

| Next<br>Layer<br>Type | Conv | Deconv | Depth-<br>wise<br>Conv | Inner<br>Product | Max<br>Pooling | Ave<br>Pooling | BN | ReLU | LeakyReLU | Element-<br>wise | Concat | As Input | As<br>Output |

|-----------------------|------|--------|------------------------|------------------|----------------|----------------|----|------|-----------|------------------|--------|----------|--------------|

| Conv                  | •    | •      | 0                      | •                | •              | 0              | •  | •    | 0         | •                | •      | •        | •            |

| Deconv                | •    | •      | 0                      | •                | •              | 0              | •  | •    | 0         | •                | •      | •        | •            |

| Depth-wise<br>Conv    | •    | •      | 0                      | •                | •              | 0              | •  | •    | 0         | •                | •      | •        | •            |

| Inner<br>Product      | •    | •      | 0                      | •                | •              | 0              | •  | •    | 0         | •                | •      | •        | •            |

| Max Pooling           | •    | •      | 0                      | •                | •              | 0              | 0  | ×    | ×         | •                | •      | •        | •            |

| Ave Pooling           | 0    | 0      | 0                      | 0                | 0              | 0              | 0  | ×    | ×         | 0                | 0      | 0        | 0            |

| BN                    | •    | •      | 0                      | •                | •              | 0              | 0  | •    | ×         | •                | •      | 0        | 0            |

| ReLU                  | •    | •      | 0                      | •                | •              | 0              | 0  | ×    | ×         | •                | •      |          | •            |

| LeakyReLU             | 0    | 0      | 0                      | 0                | 0              | 0              | 0  | ×    | ×         | 0                | 0      |          | 0            |

| Element-<br>wise      | •    | •      | 0                      | •                | •              | 0              | 0  | •    | 0         | •                | •      |          | •            |

| Concat                | •    | •      | 0                      | •                | •              | 0              | 0  | ×    | ×         | •                | •      |          | •            |

Table 3-6: Supported layers order in DPU IP. Source: [48]

One can see that in these tables there are not all the available nets. It is a resume of the more relevant ones but to be sure, the compatibility of SegNet with the DPU has been asked to the Xilinx contact and he confirms that the net is suitable also regarding the layers order.

2. The DPU configuration.

The DPU IP has a few parameters that can be configured when adding it to the block design. The more relevant are:

- The number of DPU cores: DPU can run with multiple cores (up to 3) to achieve higher performance. This also implies more resources consumption of the programable logic. In this case, considering the trade-off between the required performance and the available resources, only one core has been decided to use.

- The Arch of DPU: The DPU has different architecture configurations depending on the level of parallelism of the convolution unit. It depends also on the board used. In the case of the Zynq UltraScale +MPSoC and the performance required for SegNet, the chosen architecture is B2304.

- Number of SFM cores: The Softmax function is a layer of a CNN that converts the output vector of n real numbers into a vector of n real numbers that sum to 1. This operation is supported using an additional core to handle it, so since the SegNet uses Softmax operation, this parameter needs to be set as 1.

- 3. Connect DPU with Zynq UltraScale +MPSoC and Assign register address for DPU.

The DPU IP has only one slave interface and a variable number of master interfaces depending on the number of used cores. Each DPU core has three master interfaces, one for instruction fetch and two for data. The SFM core, if enabled, has one additional master interface.

In the project use case, only one DPU core is used and Softmax is enabled so there are one slave interface and four master interfaces in total.

Xilinx recommends connecting the slave port with the M\_AXI\_HPM0\_LPD port of the Zynq UltraScale +MPSoC. This recommendation has been followed since that port was unused in the previous block design.

Regarding the Master interfaces, Xilinx recommends avoiding AXI\_interconnections if possible because it may add some delay in comparison with direct connection with the PS. Nevertheless, due to the high number of interconnections it is not possible in this design. When this is not possible, Xilinx recommends connecting the master port for instruction fetching to the S\_AXI\_LPD port of the PS due to its low bandwidth requirements and the data master ports to the higher priority (low number) port of the PS high bandwidth ports. In this project, the three data master ports are connected with S\_AXI\_HP0\_FPD port of the PS so both recommendations have been fulfilled.

In addition, it is important to properly connect the interruption, reset and clocking signals.

Once all the connections are well configured, the base address of the AXI slave interface must be assigned to any of the accessible address by the CPU in the Vivado address editor. Xilinx recommend setting the DPU slave interface to 0x8F00\_0000 for MPSoC devices allowing a minimum space of 16 MB. This recommendation has been followed.