### Design under test interface implementation and stimulus in the verification of a RISC-V Vector Accelerator

January 26th, 2022 Author: Víctor Jiménez Arador

**Supervisor:** Nehir Sonmez **Co-supervisor:** Óscar Palomar **Tutor:** Miquel Moretó Barcelona Supercomputing Center Barcelona Supercomputing Center Universitat Politècnica de Catalunya

Fall 2021 Master in Innovation and Research in Informatics High Performance Computing Specialization Facultat d'Informàtica de Barcelona Universitat Politècnica de Catalunya

# Acknowledgments

First of all, I would like to thank my thesis supervisors: Miquel Moretó, Óscar Palomar and Nehir Sonmez from the Barcelona Supercomputing Center. I want to thank them for their help and supervision, both for this thesis and my work at BSC. Thanks to them, I could learn and start my current career.

Then, I would like to shout out to the whole BSC Verification team involved in verifying the Vector Accelerator, as their efforts are also reflected in this thesis. Extra mention to Francesco Minervini from the RTL team, who made our job much easier and was always really kind to us.

Special thanks to my closest partners and friends in the BSC Verification team, Josep Sans, Marc Domínguez and Mario Rodríguez, without whom a big part of my work would not have been possible.

Finally, I would like to give a huge thanks to my family for keeping me motivated and supporting me at every moment of my life.

# Abstract

The production of a microprocessor is one of the most complex and expensive processes in the industry these days. These high costs are why big companies dedicate most of their efforts to design verification during the development of these projects. Design verification is vital to be able to deliver an error-free design. As the final manufacturing of these products is expensive, no company can afford to spend money on defective designs. Governments and associations are investing in research projects with the recent open-source trends. These allowed entities like the Barcelona Supercomputing Center (BSC) to start developing their designs. Considering how hard it is for these entities to receive inversions of this type, they have to work hard in design verification.

One of the critical aspects of design verification involves applying the correct stimulus to the IPs or modules to be verified. The verification engineers must generate a correct but diverse stimulus to drive the design under test. These stimuli are often achieved using Universal Verification Methodology (UVM) and directed testbenches. However, this task is sometimes not easy, where the design under verification might have a very complex interface or have a vast range of stimulation possibilities.

In this thesis, a UVM-based testbench is presented for the design verification of a RISC-V Vector Accelerator. From design specifications to the testbench implementation, this work explains its structure and the reasoning behind its specific characteristics. This testbench can provide random stimulus through the interface of the Accelerator and handle the execution of vector instructions from the RISC-V Vector specifications. Although it is full of features, we will be focusing on the module interface treatment part of the testbench in this work. Finally, we will review its strengths and weaknesses and how we could improve these.

# Contents

| 1 | Intr             | oduction 9                                        |  |  |  |  |  |  |  |  |

|---|------------------|---------------------------------------------------|--|--|--|--|--|--|--|--|

|   | 1.1              | Motivation                                        |  |  |  |  |  |  |  |  |

|   | 1.2              | Contributions 10                                  |  |  |  |  |  |  |  |  |

|   | 1.3              | Thesis structure    11                            |  |  |  |  |  |  |  |  |

| 2 | Bac              | kground and Related Work 12                       |  |  |  |  |  |  |  |  |

|   | 2.1              | Processor Production                              |  |  |  |  |  |  |  |  |

|   | 2.2              | Processor Verification                            |  |  |  |  |  |  |  |  |

|   |                  | 2.2.1 UVM                                         |  |  |  |  |  |  |  |  |

|   | 2.3              | European Processor Initiative    18               |  |  |  |  |  |  |  |  |

|   | 2.4              | RISC-V                                            |  |  |  |  |  |  |  |  |

|   |                  | 2.4.1 RISC-V Vector Extension                     |  |  |  |  |  |  |  |  |

|   | 2.5              | Related Work         21                           |  |  |  |  |  |  |  |  |

| 3 | FΡΔ              | C Architecture and DV Infrastructure 24           |  |  |  |  |  |  |  |  |

| 0 | 3.1              | EPAC Architecture                                 |  |  |  |  |  |  |  |  |

|   | 3.2              | Open Vector Interface                             |  |  |  |  |  |  |  |  |

|   | 3.3              | Vector Accelerator Architecture                   |  |  |  |  |  |  |  |  |

|   | 3.4              | Verification environment                          |  |  |  |  |  |  |  |  |

|   | 0.1              | 3.4.1 Riscv-dv                                    |  |  |  |  |  |  |  |  |

|   |                  | 3.4.2 Spike ISS                                   |  |  |  |  |  |  |  |  |

|   |                  | 3.4.3 UVM Scoreboard                              |  |  |  |  |  |  |  |  |

|   |                  | 3.4.4 Assertions                                  |  |  |  |  |  |  |  |  |

|   |                  | 3.4.5 Coverage                                    |  |  |  |  |  |  |  |  |

|   |                  | 3.4.6 Continuous integration                      |  |  |  |  |  |  |  |  |

| 4 | <b>U</b> I I I I | M and interface interaction 38                    |  |  |  |  |  |  |  |  |

| T | 4.1              | UVM Environment overview       38                 |  |  |  |  |  |  |  |  |

|   | 4.2              | Issue sub-interface                               |  |  |  |  |  |  |  |  |

|   | 4.3              | Dispatch sub-interface                            |  |  |  |  |  |  |  |  |

|   | 4.4              | Completed sub-interface                           |  |  |  |  |  |  |  |  |

| _ |                  | -                                                 |  |  |  |  |  |  |  |  |

| 5 |                  | nory operations emulation in the UVM testbench 54 |  |  |  |  |  |  |  |  |

|   | 5.1              |                                                   |  |  |  |  |  |  |  |  |

|   | 5.2              |                                                   |  |  |  |  |  |  |  |  |

|   | 5.3              |                                                   |  |  |  |  |  |  |  |  |

|   | 5.4<br>5.5       | Store interface                                   |  |  |  |  |  |  |  |  |

|   | 5.5              | Mask sub-interface                                |  |  |  |  |  |  |  |  |

| 6   | Eval           | luation of Contributions                | 84              |  |  |  |  |  |  |  |  |

|-----|----------------|-----------------------------------------|-----------------|--|--|--|--|--|--|--|--|

|     | 6.1 Results    |                                         |                 |  |  |  |  |  |  |  |  |

|     |                | 6.1.1 Test results                      | 84              |  |  |  |  |  |  |  |  |

|     |                | 6.1.2 Coverage results                  | 89              |  |  |  |  |  |  |  |  |

|     | 6.2            | Environment evaluation                  | 91              |  |  |  |  |  |  |  |  |

| 7   |                | clusions and Future Work<br>Future Work | <b>95</b><br>96 |  |  |  |  |  |  |  |  |

| Bil | ibliography 98 |                                         |                 |  |  |  |  |  |  |  |  |

# **List of Figures**

| 2.1  | Design production flow [7]                                      | 13 |

|------|-----------------------------------------------------------------|----|

| 2.2  | UVM Inheritance Diagram [17]                                    | 14 |

| 2.3  | UVM Phases [17]                                                 | 16 |

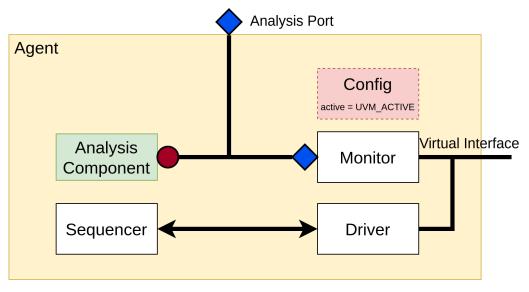

| 2.4  | UVM Testbench Overview                                          | 17 |

| 3.1  | EPAC Architecture Diagram [35]                                  | 25 |

| 3.2  | EPAC first tape out [1]                                         | 25 |

| 3.3  | Open Vector Interface buses description                         | 26 |

| 3.4  | VPU Overview                                                    | 28 |

| 3.5  | Vector Register File diagram [15]                               | 29 |

| 3.6  | Typical UVM Scoreboard structure and connections, based on [47] | 32 |

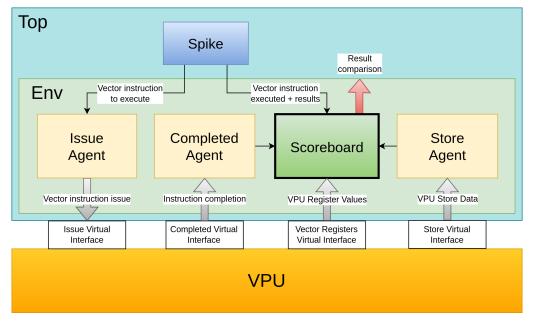

| 3.7  | Scoreboard structure and connections for the VPU                | 34 |

| 3.8  | Simplified full environment diagram                             | 36 |

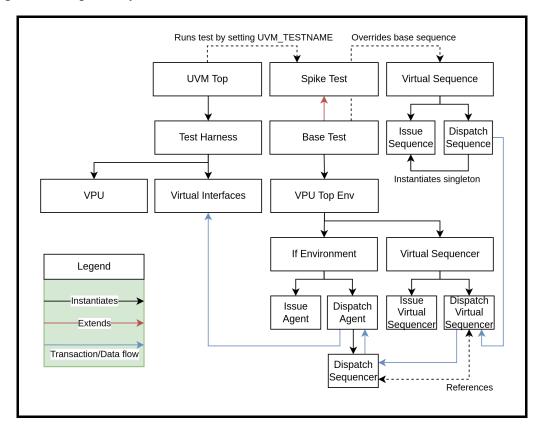

| 4.1  | Full UVM Testbench                                              | 39 |

| 4.2  | Virtual Sequences in UVM Testbenches, based on [17]             | 40 |

| 4.3  | Class diagram of our UVM Testbench                              | 41 |

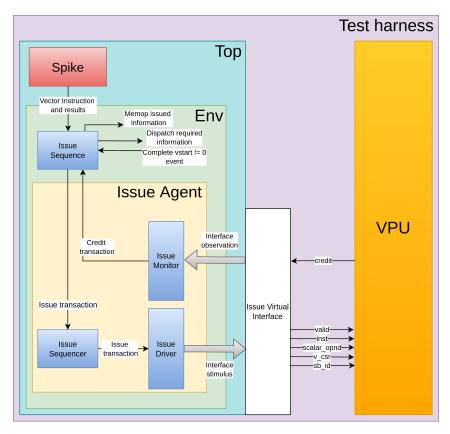

| 4.4  | Issue UVM agent and connections in detail                       | 44 |

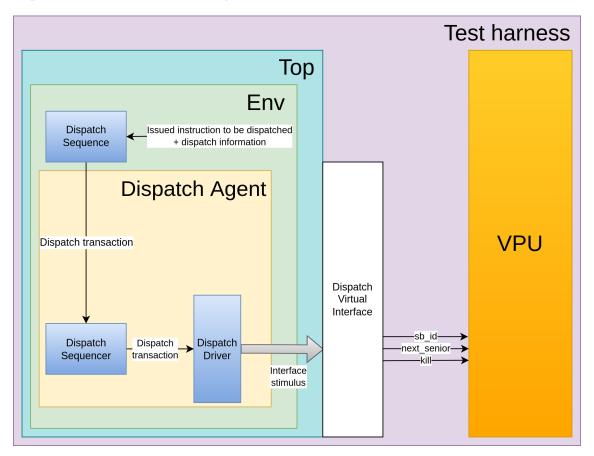

| 4.5  | Dispatch UVM Agent and connections in detail                    | 47 |

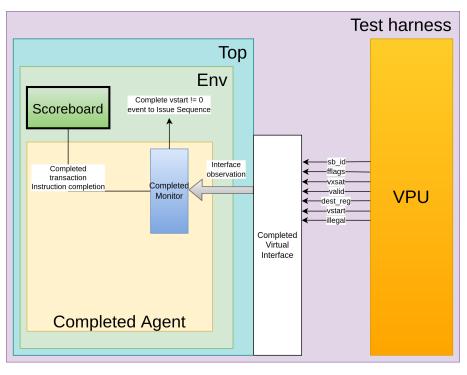

| 4.6  | Completed UVM Agent and connections in detail                   | 51 |

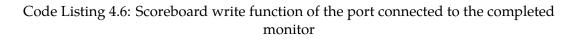

| 4.7  | Simplified diagram of the arithmetic instructions flow          | 52 |

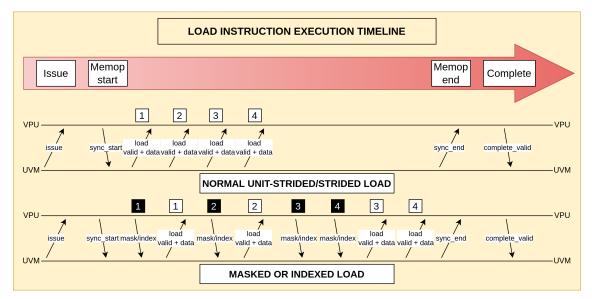

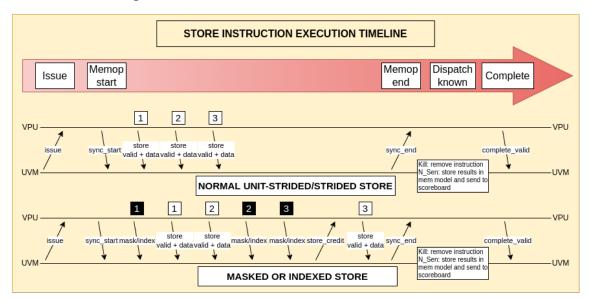

| 5.1  | Memory operation related sub-interfaces during three memops     | 55 |

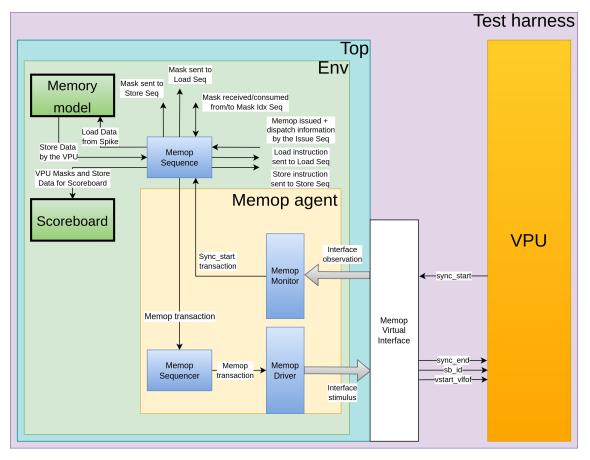

| 5.2  | Memop UVM Agent and connections in detail                       | 57 |

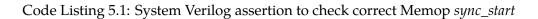

| 5.3  | Dispatch timing in the memory operation execution timeline      | 62 |

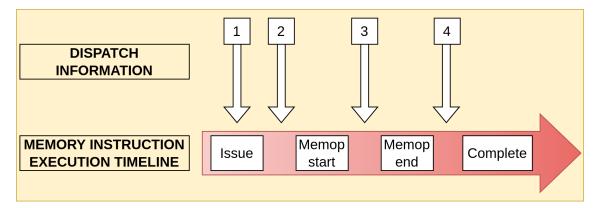

| 5.4  | Cache line examples for load operations                         | 65 |

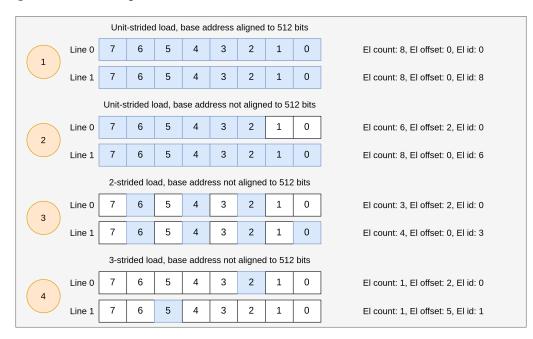

| 5.5  | VPU Load Buffers structure                                      | 67 |

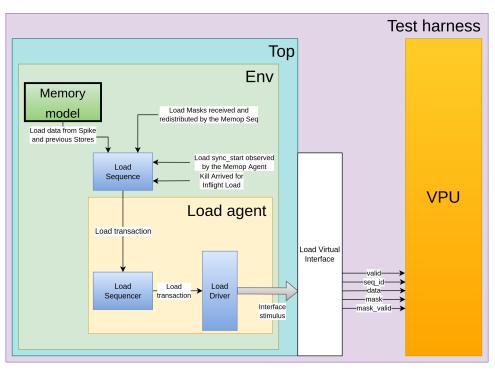

| 5.6  | Load UVM agent and connections in detail                        | 68 |

| 5.7  | Configuration objects in UVM, based on [39]                     | 71 |

| 5.8  | Load memory operations flow between the UVM and the VPU         | 74 |

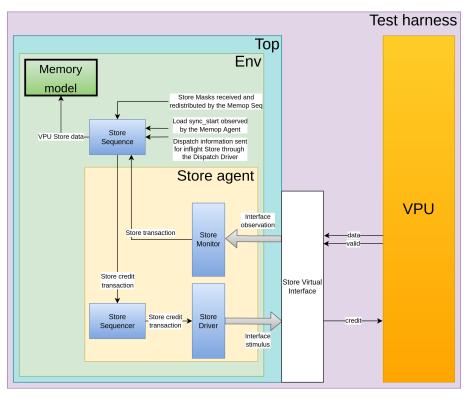

| 5.9  | Store UVM Agent and connections in detail                       | 76 |

| 5.10 | Store memory operations flow between the UVM and the VPU        | 78 |

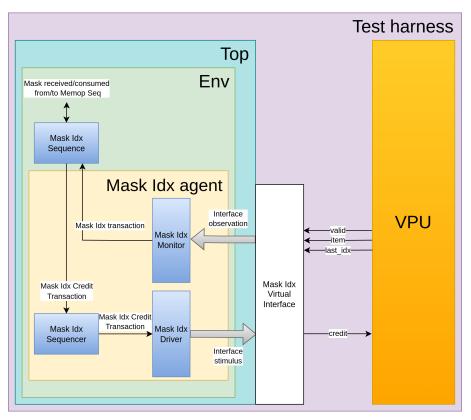

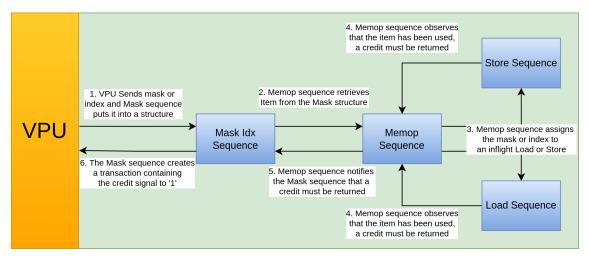

| 5.11 | Mask Idx UVM Agent and connections in detail                    | 80 |

| 5.12 | Mask distribution and usage in the UVM testbench                | 81 |

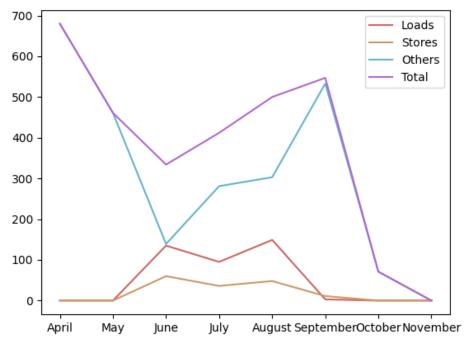

| 6.1  | Errors encountered per month                                    | 85 |

| 6.2  | VPU Bug Gitlab Issue example                                    | 87 |

| 6.3  | Issue waveform example                                          | 87 |

| 6.4  | Errors distribution among instruction types                     | 88 |

| 6.5 | Inter-sequence communication in the testbench | 92 |

|-----|-----------------------------------------------|----|

|-----|-----------------------------------------------|----|

# **List of Tables**

| 4.1        | Issue sub-interface signals                                                                    | 43       |

|------------|------------------------------------------------------------------------------------------------|----------|

| 4.2        | CSR signal fields                                                                              | 43       |

| 4.3        | Dispatch sub-interface signals                                                                 | 46       |

| 4.4        | Completed sub-interface signals                                                                | 49       |

| 5.1        | Memop sub-interface signals                                                                    | 56       |

| 5.2        | Load sub-interface signals                                                                     | 64       |

| 5.3        | Seq_id signal fields                                                                           | 65       |

| 5.4        |                                                                                                | 76       |

| 5.5        | Mask Idx sub-interface signals                                                                 | 79       |

| 6.1<br>6.2 | Functional coverage per design unit, interface-related modules Code coverage for the whole VPU | 90<br>90 |

| 0.2        |                                                                                                |          |

# List of Code Listings

| 4.1 | Transaction generation in the Issue Sequence                             | 45 |

|-----|--------------------------------------------------------------------------|----|

| 4.2 | Issue signals stimulus at the Issue Driver                               | 45 |

| 4.3 | Unknown Issue signals assertion                                          | 46 |

| 4.4 | Existing sb_id assertion for dispatch transactions                       | 49 |

| 4.5 | Fflags signal assertion                                                  | 50 |

| 4.6 | Scoreboard write function of the port connected to the completed monitor | 51 |

| 5.1 | System Verilog assertion to check correct Memop <i>sync_start</i>        | 58 |

| 5.2 | Memory model class derived from Opentitan project                        | 60 |

| 5.3 | Mask and Store credits assertions                                        | 82 |

## **Chapter 1**

## Introduction

Producing a microprocessor or a similar design is a costly and challenging process. Currently, almost all these designs are done by huge companies because those are the only entities with resources to afford these processes. These companies have big and diverse teams devoted to each step of the production process, one of which is the Design Verification team.

In the last few years, research entities have started developing their designs thanks to governments support. With as few chances as researchers have, the teams must assert that their design is as correct as possible before sending it to the factory. That is why verification has such enormous relevance in modern-day projects, as it is the primary tool that engineers have to ensure the correctness of their designs.

In this chapter, Section 1.1 introduces the circumstances and the need for verification that motivates this master thesis. In Section 1.2, the contributions provided in this master thesis are presented. Finally, in Section 1.3, the thesis structure is described.

#### 1.1 Motivation

Even if RTL design and CPU microarchitecture are well and widely taught at many degrees, it is not so common to dedicate the time it deserves to design verification. Although it is mandatory to have a verification process in such a project as a core or an accelerator, the techniques involved in them are almost unknown for most students. As one could expect, this secrecy is because big companies do not often disclose their tools and workflows to the public. As these processes are only performed in massive projects like producing the newest generation core, they never reach the smallest companies or researchers. The whole environment produces a cycle where the most prominent companies must train all the professionals and cannot always hire the desired level of experience.

At the same time, this cycle implies that smaller companies or research entities do not get access to optimal tools and knowledge commonly used that is standard in the industry, which means that their projects are behind right from the start. It gets even worse if we focus on research entities, like the Barcelona Supercomputing Center (BSC), that rely on government funding to produce their designs and most of the time do not sell them.

For the newly created microarchitecture department at BSC, the chance of participating in the *European Processor Initiative* (*EPI*) was a huge opportunity. In this project, the BSC takes on the design of a Vector Accelerator integrated with a scalar core in a more extensive environment. This accelerator needs to be bug-free and capable of communicating with the rest of the project modules. Therefore, thorough verification of the IP is mandatory and necessary in developing the Vector Accelerator.

As soon as this project came across the BSC's horizon, the corresponding teams started to get prepared or formed, in the case of the verification team. The experienced verification engineer is not very affordable and the previous verification experience in the BSC was almost inexistent, so the newly created team was formed by graduate engineers with no knowledge in verification. This little experience meant, apart from the delay due to the team's formation, that the team had to go through a ramp-up process that gave them the pointers to where they should direct the verification process. This delay caused the Vector Accelerator to be almost implemented by the time the verification efforts started and the need for a fast and efficient initial implementation.

#### 1.2 Contributions

In this document, we present two main contributions to the verification process of the Vector Accelerator:

- Design under test interface interaction: using Universal Verification Methodology (UVM ) and other sources, stimuli must be generated to observe and test as many capabilities of the design as possible.

- Memory operations emulation: in this project, the interaction with memory is done through the scalar core, and in simulations without it, the verification team must handle both the interaction with the core and the emulation of its memory.

The verification of the Vector Accelerator was a team effort and we developed multiple tools and features for that purpose. However, some members of the team specialized in certain aspects of the verification infrastructure. Josep Sans and Iván Díaz were in charge of tweaking a RISC-V binary generator to fit our needs. Mario Rodríguez was mainly in charge of adapting an Instruction Set Simulator (ISS) to our testbench and creating a set of Continuous Integration pipelines together with Marc Domínguez. These will be explained in Subsections 3.4.1, 3.4.2 and 3.4.6, respectively. Together, we developed a testbench for the Accelerator full of features, among which we find the ones explained in this document.

Firstly, we will describe how we managed to feed the Vector Accelerator with instructions to execute and the responses in the interface necessary to complete them. All the techniques used and their goals and motivations will be explained. In addition, we will explain how we asserted that we were taking the right approach. This interaction aimed to stimulate the Vector Accelerator in the broadest way possible, showing and testing all the design features.

After that, the document will focus on the Vector Accelerator memory operations. These had to be implemented in a particular way in the verification environment as they involve much communication with the scalar core. These operations implied significant changes

to the verification environment and a clever and complex way to follow and check their results.

Memory operations are one of the critical aspects of the Vector Accelerator, but they are also one of the most delicate points. That is why they were essential to verify and why their dedicated part of the environment was fundamental in the verification process.

#### 1.3 Thesis structure

The following chapters describe the contributions to the verification of the project mentioned above. The remainder of the document is structured as follows:

- In Chapter 2, there is an introduction to the project along with the necessary background of RTL design and verification.

- In Chapter 3, EPI Architecture and Design Verification Infrastructure, there are details on the Vector Accelerator, our design under test, and the whole verification environment the whole team created.

- Chapter 4 describes the first main contribution, the UVM environment and its stimulus generation, with a particular focus on its interaction with the Vector Accelerator interface.

- In Chapter 5, following with the interface interaction explanation, there is a description of the peculiarities and insights of the memory operations handling in the environment.

- Finally, in Chapter 6 and Chapter 7, there is a reflection on how the contributions helped in the verification process and how they could be improved along with possible future work and the conclusions.

### **Chapter 2**

# **Background and Related Work**

In this chapter, key microprocessor design and production concepts are introduced and explained in Section 2.1. A brief introduction to design verification and the EPI project are provided in Sections 2.2 and 2.3, respectively. In Section 2.4 the RISC-V ISA is presented, with particular focus on its vector specifications. Finally, pointers to related work and a description of the previous work in verification in the Barcelona Supercomputing Center are shown in Section 2.5.

#### 2.1 Processor Production

Since the Intel 4004, the first commercial semiconductor processor, came out in 1971, many companies and entities have produced their microprocessor designs. Fifty years and many generations of processors later, making a chip is still a complex task, or even more, considering designs have grown bigger. Producing a design involves several steps, from the initial conception and design to its physical manufacturing.

Every stage of this process must be done carefully and accurately to achieve a successful design. Among these stages, we find the following:

- Specification: In this step, the features and characteristics of the processor are listed and described. Often underestimated, the specification stage is one of the most critical steps in producing a design. All details must be specified and everything must be correctly connected, with no space for ambiguities. Any problem could lead to issues in the implementation and verification stages, complicating the work across teams. For example, a poor interface protocol description could lead to a misunderstanding between the engineers that would cause a delay in the already tight production schedule.

- Implementation: Once the specification is complete comes the implementation phase. The details in the specifications are portrayed in the RTL code, usually written in the Verilog or VHDL languages. In the beginning, each engineer will work in a module or set of modules, writing the code and the needed testbenches to test them quickly. After that, all the modules must be integrated, and all the engineers will collaborate to connect everything. If many engineers can work

independently in their assigned modules and integrate them easily, the quality of the specification is proven. This step tends to be the longest, but the quality of the specifications highly influences this.

- Verification: In the meantime, and with specifications in hand, a verification plan will be implemented to ensure that the design works as expected. Together with the specification stage, this step is one of the most important in the process. In it, as in the implementation one, the quality of the specifications is asserted. The verification engineer needs these to be complete and exact so that he or she can test all the necessary features and develop an ad-hoc environment to verify the design. This environment and all the verification features included in the plan must follow the specifications and a misunderstanding could cause the whole verification effort to be useless.

- Fabrication: After a design is verified, it will be sent to the factory for its manufacturing. This step is the most expensive one, as producing a physical chip is costly. Therefore, the design must be as perfect as possible before this stage. Very few companies or entities in the world can afford to produce a processor, but almost none can afford to produce a deficient processor. Once the processors are received, the engineers will perform further physical tests to ensure that the design works as expected in the real world.

In the previous list there are many missing steps, which are shown in Figure 2.1.

Figure 2.1: Design production flow [7]

Even if all engineers have improved these steps and have learned better and more efficient ways of producing their designs, the expensive nature of the fabrication of a processor still makes it a challenging task. Specialized teams for each step of the process collaborate with the rest to successfully carry out the production of the design.

The whole process is costly and almost no entities can afford to waste money on fabricating deficient processors. Hence, companies typically dedicate a big part of their project funds to verification. A good verification process ensures that the design sent to the factory is correct and follows the corresponding specifications.

#### 2.2 Processor Verification

Design verification is the set of techniques used to assert that a design works as expected. These include tasks like creating a simulation environment, finding ways to check the behaviour of the design or setting up automatic testing tools. As stated, verification is vital to avoid producing a deficient design. However, it is also beneficial to help the design team ensure that everything specified has been implemented as expected.

Initially, the verification strategy was custom and made up for every project. For example, for the Intel 4004, Federico Faggin says that he "had to figure out and create a random-

page 14

logic design methodology for silicon gate technology that did not yet exist" [14]. He worked under a tight schedule and had to do the design and verification tasks simultaneously. However, after decades of refining the verification process, it is much more standard and straight than then. Even if each design requires verification planning and thinking before the process starts, we have tools and previous work that leads us to at least a reasonable verification process.

Strangely enough, the basic methodology has not changed that much since the first Intel 4004 was sold. Random testing, if well implemented, is still one of the best ways of verifying a design. Random stimulus, together with many other techniques, allows verification teams across the world to assert the correct behaviour of their designs. Even though each process is different, their verification processes resemble many aspects. For example, they all usually have a testbench or similar, where the design unit is instantiated and through which stimuli are provided. Additionally, extra features are added to this testbench to check the correctness of the behaviour (like *Scoreboards* or *Assertions*) and to measure the quality of the verification process (*Coverage*). More recently, automatic testing pipelines have been implemented to increase the number of situations to which the design under test (*DUT*) has been exposed (*Continuous Integration* (*CI*)). These techniques will be described in the following sections of this document.

#### 2.2.1 UVM

Universal Verification Methodology (UVM) [2][17] is a standardized methodology for verifying RTL designs. Based on System Verilog [10] and standardized by Accelera, it inherits many ideas from Open Verification Methodology (OVM).

The structure of UVM testbenches makes it easy to support constrained random stimulus, which is one of their essential parts, as it enables the users to generate a wide range of cases to test a design. In addition, UVM is thought to be re-usable and extendable. For that, it takes advantage of Object-Oriented Programming (OOP).

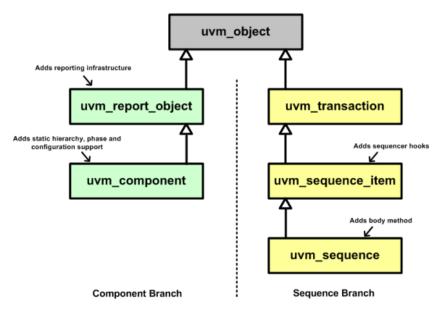

Figure 2.2: UVM Inheritance Diagram [17]

All of the types of classes in UVM inherit from a base class called UVM Object. In Figure 2.2, from the UVM Cookbook, all the basic children classes from UVM Object can be seen. This way, the main classes that *extend* from UVM Object are: UVM Component, UVM Sequence Item and UVM Sequence.

In summary, UVM Sequences produce Sequence Items following a determined or random pattern, which UVM Components use to communicate data between them. Generally, a UVM testbench strength in producing valid and complete stimulus comes with a proper Sequence implementation.

Class instances are created and destroyed as in many other OOP utilities or languages. In the case of UVM, Sequences are requested Sequence Items (also called *transactions*), so they create an instance of the class Sequence Item and *randomize* it with the corresponding function, particular of the class. By extending the base Sequence Item class, one can create a transaction class that fits the needs of its testbench. In addition, the base class methods can be overridden to customize the new one.

In this way, one can create a transaction class that contains different values and has a custom randomize method that sets these to random, using UVM standard methods or custom values. This transaction is created and randomized inside a Sequence that will send it to the component that requested it through the Sequence methods.

Furthermore, one could have more than one custom transaction type and Sequence, randomizing what type of transaction it creates at every request. This feature makes it possible to introduce random stimuli in a directed test.

This is possible thanks to polymorphism and OOP, which eases reusability and future environment extensions. For example, one could create a custom "base class" of many of the UVM Objects needed to verify a design. Later in that same project, the engineer could extend his class to create a custom dedicated case. Additionally, later in some other project, the engineer could use that same base class, if generic enough, to extend it and create a custom dedicated class for the other project.

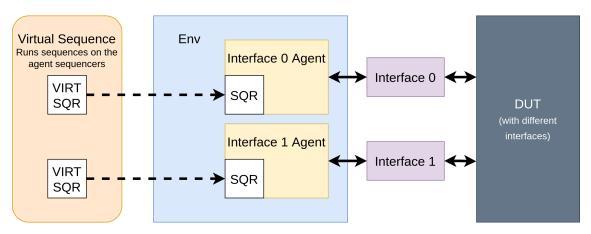

Apart from ordinary objects, polymorphism is used in UVM Components, which typically compose a UVM testbench. These perform actions related to the testbench and have their functionalities. For example, some components create Sequences (and transactions) and others communicate with the DUT.

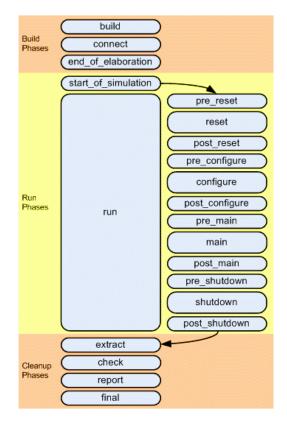

UVM Components make use of what is called UVM Phases. These are used to have a consistent testbench execution flow and in them, big steps are executed in order. There are three groups of phases:

- Build phases: where the testbench is configured and constructed.

- Run-time phases: where the testbench runs the test case.

- Clean-up phases: where the results of the run-time phases are collected and reported.

The complete set of phases and the group that they belong to can be seen in Figure 2.3.

Figure 2.3: UVM Phases [17]

The UVM Component base class contains virtual methods that are called during each phase. When extending from this base class, the engineer can choose whether to implement these methods or not. If so, the component will take part in the corresponding phase.

For example, one component might need to initialize the instance of another one in the build phase. To do so, it must have its virtual method *build\_phase* implemented. Otherwise, the component will do nothing in phase. It is worth noting that all components execute the specific phases in the same time window. That means that if two components implement the run phase, they will execute them simultaneously.

Using these phases allows UVM Components to be developed independently but still cooperate and execute their tasks with the certainty that things they depend on are ready as they were processed in previous phases.

In addition to the previous and to ease the use of polymorphism, UVM has the UVM Factory. Its purpose is to enable an object of one type to be substituted with an object of a derived type without changing the testbench structure or even the testbench code. This replacement is called "override" by either instance or type. This functionality is convenient for changing Sequence behaviour or replacing one component with another. Certain coding conventions must be followed to take advantage of the factory, where the components or objects must be registered in it, default constructors must be added to these and they have to be *created* in a particular way.

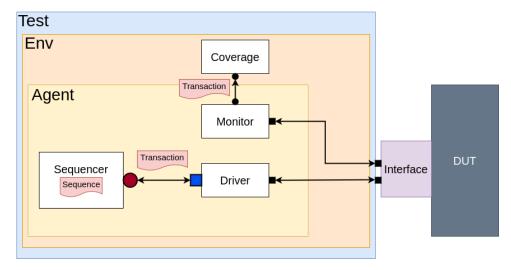

In Figure 2.4 we have an overview of a simple UVM environment. In it, we can see the

Figure 2.4: UVM Testbench Overview

main UVM Components that are almost essential to building a UVM testbench. These are:

- Test: It contains all the components of the UVM environment. In essence, the test is a wrapper for the environment. A UVM testbench could have more than one, being able to switch between very different environments by just instantiating one or another test.

- Environment: Instantiated inside the UVM Test, the environment is where all the interacting UVM Components are instantiated and connected. For example, the different communicating components are connected inside it using communication ports.

- Agent: The agent contains all the UVM Components that generate or receive values from the DUT. These are the following:

- Sequencer: Is in charge of obtaining the transactions from the Sequences and sending them to the driver through the ports.

- Driver: Requests for data transactions to the Sequencer and stimulates the DUT with the corresponding values after receiving them.

- Monitor: Observes the DUT interface or values and creates transactions. These

could be incoming or outgoing values from the DUT and will later be used to

react or create different driver or sequence values.

- Coverage: Additionally, UVM can be used to record coverage numbers. Coverage, as will be explained in further sections, is used in design verification to track how many possible values have been observed in the environment, both as inputs and outputs of the DUT.

The UVM Test is run from the UVM Top module. This top module also instantiates the *test harness*, which is the entity containing the DUT connected to a SystemVerilog interface.

This interface is then declared in the UVM database, a utility of UVM in which one can declare objects to be used and communicate between different points of the testbench. Using this UVM database, this *virtual* interface can be accessed in the Driver and the Monitor, amongst others, as seen in Figure 2.4.

As mentioned before, one could create a generic UVM Driver class with the main methods and attributes and extend it to a custom class adapted to the DUT connected to and with the type of transactions required. This makes it faster to build whole environments for multiple modules or projects. There are tools such as Easier UVM [13] that provide empty testbenches adapted to the DUT that the user specifies.

A typical use case is creating a base test class and then extending it to other child classes that can be switched easily in the testbench, stimulating the DUT very differently by just instantiating one or another UVM test. These tests could be, for instance, a random one in which all components work randomly or a directed one, where specific sequences produce controlled stimulus. These different tests could also use the same UVM Components but change the generation of values.

#### 2.3 European Processor Initiative

In recent years, governments and other entities have been investing in different research areas, one of them being microprocessor design and production. This is the case of the European Processor Initiative (EPI). In this project, funded by the European Commission, many research entities and companies collaborate to design and build a new family of European low-power and high-performance processors for various applications like supercomputers, Big Data, automotive or Machine Learning. These processors will use the open-source Instruction Set Architecture (ISA) RISC-V, explained in Section 2.4. This and more details will be further discussed in the following sections, but the fact that it is an open-source ISA favours the proliferation of these projects. Without setting these correctly, vector instructions may be executed differently depending on the architecture and the code executed. If used well, this is one of the most attractive features of the RISC-V vector extension [23]. Many entities cooperate to take this project to terms and each of them has its tasks and responsibilities. For example, the BSC is mainly in charge of producing a Vector Accelerator that implements the recent vector extension of the RISC-V ISA. Similarly, other companies or entities design scalar cores, floating-point units and other accelerators. In the end, all partners combine their efforts and collaborate to integrate the different units.

Considering the costs of producing a design and how hard it is for a research project to start and be funded, verification takes an even more significant part and relevance. Therefore, all partners must deliver their units thoroughly verified and a narrow margin can be given to them to fail post-integration. If some of the units failed or were deficient, it would be a catastrophe and it would probably be preferable to leave it out of the final tape out. An integration failure would be a considerable drawback for the project and the responsible entity.

The module itself and the interface with the rest of the design must be verified. The interconnections of the module are one of the crucial and most essential parts of the unit. They must be a collaborative effort with the corresponding colliding partners to ensure the perfect functioning of the interfaces. In this document, we will focus on the interface verification of the Vector Accelerator, among others, which involves the connection to a scalar core.

#### 2.4 RISC-V

RISC-V is an open-source Instruction Set Architecture (ISA) [22] based on reduced instruction set computer (RISC) principles. As said, the main difference between RISC-V and other ISA is its open-source license, which means that using it for producing a design does not require paying a fee.

Since its appearance in *University of California Berkeley* in the year 2010, it has been used in several projects to produce open-source designs. Being open-source is especially interesting for research and academic entities, which cannot sometimes afford to pay for other ISAs. With already ten years of history, the RISC-V ISA is at its best moment and has become a popular choice even for big companies when looking for an ISA to produce their designs. Early 2021, Huawei has announced the development of its first RISC-V design, the HiSilicon Hi3861 development board [19]. Giant e-commerce company Alibaba has also recently announced that its Xuantie 910 processor aimed at cloud servers would be using a RISC-V core [46]. Previous to that, storage drives companies Western Digital and Seagate had announced that they would be producing RISC-V processors to control storage and security of data [8].

RISC-V has established itself as a modular ISA, which means that it has a base specification to be implemented and many optional extensions. The base specifications are called *rv32* and *rv64* depending on the size of registers and buses in the design.

Among the ratified RISC-V extensions [21] that can be implemented we find the following:

- Multiplication (M): which contains the scalar multiplication and division instructions.

- Atomic (A): which contains the atomic memory operations, used to operate safely on values inside memory when communication between different cores is required.

- Floating Point (F): specifies the single-precision floating-point operations.

- Double Precision Floating Point (D): which specifies the double-precision floatingpoint operations

- Quad Precision Floating Point (Q): which specifies the quad-precision floating-point operations

- Compressed (C): contains the compressed set of instructions, encoded in 16 bits.

- Vector (V): contains the specifications for vector-processing operations and architecture-specific details.

Most of these will be implemented in the EPI project. However, we will focus on the Vector Extension, which is the part of the RISC-V ISA that the Vector Accelerator developed by

page 20

the Barcelona Supercomputing Center is implementing. More details on the RISC-V ISA can be found in their website and their specification documents [5] [6].

#### 2.4.1 RISC-V Vector Extension

Vectors could be described as elements of the same type arranged in the same structure. Typically these are used to operate on big groups of data to which one has to perform the same operation. For example, a vector ADD immediate instruction can be used to add the same immediate value to a vector. This type of instruction is typically used while operating with media like video and audio. Nowadays, most CPU designs contain Vector Accelerators that are exclusively in charge of implementing vector instructions.

Vector processors allow operating on multiple data with one instruction because operations ensure that there are no dependencies within a vector [34]. Vector instructions reduce fetch bandwidth requirements as each of them generates multiple operations. Additionally, these operations follow a very regular execution pattern, which eliminates unnecessary delays in the execution and allows removing explicit code loops, which means fewer branches in the execution and potentially fewer delays.

This type of processor is typically divided into lanes. Each lane contains a set of elements of the vector and one or more functional units, which are used to operate on the elements. This way, multiple elements of the vector can be operated on simultaneously, one in each lane. The elements are stored in vector registers, often interleaved in the different lanes. When a vector operation starts, the lane retrieves elements successively from the vector register and performs the execution pipeline for the instruction for each of them until it potentially saves the resulting element in the vector register again.

Classic Vector architectures required the programmer or compiler to make data structures in the code fit the size of the structure in the hardware. This is one of the disadvantages of standard Vector processors, where they would only work efficiently if parallelism is regular.

In addition, in typical Vector or SIMD extensions, a change in the size of the elements in the code forces a change in the instruction set to expand the vector registers (in the case of x86, from 64-bit MMX registers to 128-bit Streaming SIMD Extensions (SSE), to 256-bit Advanced Vector Extensions (AVX), and AVX-512 [11]). The result is a growing instruction set and a need to port previously working code to the new instructions.

In the RISC-V Vector extension, rather than fixing the vector length in the architecture, the *vsetvl* instruction can be used to vary both the vector length and element width of the registers. This way, operations are agnostic to architecture and implementations. This approach makes it easier to be compatible with a broader range of vector processing units.

The vector extension introduces 32 new vector registers, which are used in the vector units to do their operations. In addition, it presents new *Control Status Registers* (CSR) that are used to configure the execution of vector instructions. The most important ones are:

- Vector length (VL): which indicates vector elements used in each vector instruction.

- Vector Type (vtype): which contains other configuration fields such as:

- Standard Element Width (vsew): specifies the length of the elements in the vector. It can take values corresponding to 8, 16, 32, 64 and 128 bits.

- Vector register group multiplier (vlmul): specifies the number of vectors to operate with for each instruction. It can take values corresponding to 1, 2, 4 and 8.

- Vector start position (vstart): indicates the element from which the operation must be performed on the vector register.

There exist more CSRs than the previous ones that control how particular instructions are executed and other relevant features of the vector extension. Without setting these correctly, vector instructions may be executed differently depending on the architecture and code. If used well, this is one of the most exciting features of the RISC-V vector extension.

At the start of the EPI project, the vector extension was in a pre-release state, with version 0.7.1. Therefore, the partners decided to stick to it until the end of the project and the Vector Accelerator implemented it [23]. In the later stages of the project, version 1.0 [24] of the vector extension was released, which the Vector Accelerator will use in the future.

#### 2.5 Related Work

When looking at previous work in design verification, there is not much disclosure for the verification of decoupled accelerators. Big companies tend to be hermetic and do not detail their work. They use UVM, formal techniques and continuous integration pipelines, but they do not release any code or documentation. This secrecy makes it hard for newcomers to learn the "industry standard way to verify designs".

Therefore, we must rely on the few design verification efforts done in open source hardware projects, where there is not much consensus. Every team interprets the verification process differently, coming up with ideas and flows that put together the techniques that must be used. However, these teams often publish articles and write documentation on how they worked and what they used or not during the verification process. In this sense, we have examples like the Opentitan [32] project from lowRISC [30], the OpenHW Group projects [18], and the rocket-chip [9] and Syntacore SCR1 [44] projects. All these are open source projects that aim to produce a RISC-V core (among other designs).

Opentitan is a massive project with exhaustive documentation. They have an entire site with information related to the project, but they also explain how they generate this information and provide pointers to all the tools they used. Additionally, this site contains a dedicated verification section with clear and detailed explanations of their verification process features, from which we took inspiration.

In Opentitan they developed a whole integrated chip containing, among other IPs, the RISC-V Ibex [29] core. For the whole design, they developed multiple verification tools. They created testbenches, test plans for their IPs and multiple scripts that automatically create from UVM testbenches to register models to verify the RISC-V CSRs.

They targeted the design in three ways; IP Level, Core level and Chip level, in which they verify all the IPs integrated with the core. For each of these levels, they developed dedi-

cated UVM testbenches. Their core testbench, for example, runs binaries in co-simulation with an Instruction Set Simulator (ISS), to which then they compare the execution trace logs to determine whether the DUT functionality was correct or not. The rest are very IP or module-specific testbenches that use features that range from UVM to memory models, depending on the DUT. The core level testbench resembles in many aspects, like ISS co-simulation, what we have done with the Vector Accelerator and it is much more relevant for this work. However, the IP or module level demands a large amount of resources as it involves creating a testbench for each submodule of the Accelerator, which we could not afford due to lack of time and people.

In addition to all the previous points, they implemented functional coverage and assertions for their modules. All this is explained in the design verification methodology page of the Opentitan site [28].

The other big source of data is the OpenHW Group. This is an organization composed of multiple contributors where hardware and software designers collaborate to develop open-source cores, related IP, tools and software. They are making considerable efforts to open-source as much information and code as possible to help create open-source IPs. The Barcelona Supercomputing Center is a member of the group. In their own words: "OpenHW provides an infrastructure for hosting high-quality open-source HW developments in line with industry best practices" [18].

They have multiple parallel projects, but it is of particular interest for this thesis the verification efforts performed on the CORE-V family of RISC-V cores. These are a collection of open-source RISC-V cores (such as RI5CY [36] or Ariane [27]) to which they execute industrial grade verification. All the code is in the same Github repository [18], which to begin with, makes it very handy to access their resources. Then, inside each core folder, the structure is clear; they have separate folders for the modules related to the DUT and the modules related to the testbenches.

For each core, they have a massive UVM testbench that contains assertions and functional coverage. In these testbenches, they generate the instructions that the core will be executing and check the results that it produced comparing to ovpsim [20], an Instruction Set Simulator developed by Imperas. All these are features that we have also adopted in our testbench, from co-simulation with an ISS, as explained, to checking specific properties with assertions and counting coverage, so these are valuable references for the work explained in this thesis.

Another interesting feature is the RISC-V Formal Interface [43]. This is an interface that can be potentially connected to any RISC-V scalar core, using certain signals that characterize the execution of an instruction. The model will then determine its result after detecting which instruction is being executed and compare it with the one in the core. This can speed up the initial stages of the verification process of many designs, as the engineers must only find the necessary signals and connect the formal interface to these. All this and more information is provided in the CV32E40X User Manual [12] and the CORE-V Verification Strategy [33] pages.

Finally, the rocket-chip and SCR1 projects, even though they have simulation environments, have more insufficient verification documentation. We may only find pointers to external repositories with tests used to stimulate the core and how to run them, but no actual description of their environments is provided. In both cases, their repositories only contain testbenches on which they instantiate the core and provide instructions to it reading from a memory that has previously been loaded with the binary to execute. It is worth noting that these projects are usually made up of different partners and contributors so that this documentation may be distributed between the separate repositories.

As seen, what all these projects have in common is that they provide a complex simulation environment for their designs. These execute a test and stimulate the design to collect the results later and check their correctness.

The Barcelona Supercomputing Center had previously produced a few designs, but no similar environment was developed. The previous project was the preDRAC [4] tape out, a RISC-V 5-stage in-order core. This design was tested using random binaries generated with a RISC-V random binary generator, riscv-torture [37], loaded in a RAM. At the end of these tests, contents of the registers were dumped into this RAM using store instructions and then compared with a reference model. Additionally, in the later stages of the project, this tool was improved and extended to provide more information to the engineers, displaying the values resulting from each independent instruction and making it easy to debug possible errors in the design.

Even if this is a clever way of building an environment and was good enough to find many bugs in the design, it is not the standard way of implementing a verification environment. UVM is typically in the centre of these, and randomness is a critical factor for the proper verification of a design. It is worth noting that no dedicated verification team existed in the BSC at the time, which means that both the RTL design and the testing environment were developed simultaneously and by the same engineers for the preDRAC tapeout. Nevertheless, this vast effort resulted in a mostly successful tape out. Still, it showed the need for a dedicated verification team, which was formed shortly after the design was sent for production.

## **Chapter 3**

# EPAC Architecture and DV Infrastructure

This chapter will focus on the closest background, the design under test and a summary of the full verification environment. In Section 3.1 we will describe the EPAC Architecture. Then, the Vector Accelerator interface, OVI, and its architecture, will be explained in Sections 3.2 and 3.3, respectively. Finally, we will have a short description of the whole verification environment for the Vector Accelerator that we developed in Section 3.4.

#### 3.1 EPAC Architecture

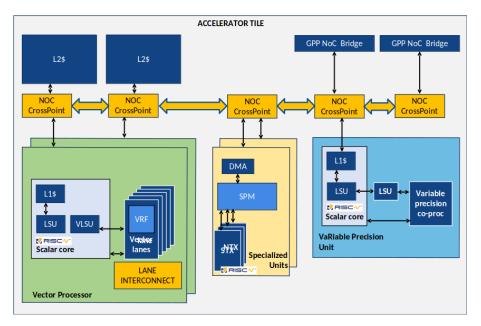

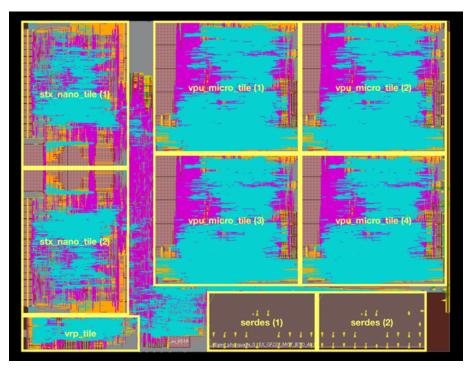

As said in Section 2.3, the EPI project comprises multiple partners, each with its module or purpose. The resulting chip of the project is called EPAC (European Processor Accelerators). This chip contains four vector-processing micro-tiles composed of an Avispado RISC-V core, designed by SemiDynamics, and a vector processing unit designed by the Barcelona Supercomputing Center and the University of Zagreb.

Each tile also contains a Home Node and L2 cache, designed by Chalmers and FORTH. In addition, the chip contains a Stencil and Tensor accelerator (STX), designed by Fraunhofer IIS, ITWM and ETH Zürich, and a variable precision processor (VRP) designed by CEA LIST. These tiles and accelerators are connected through a high-speed network on chip (NOC) and SERDES technology from EXTOLL.

The EPAC chip integration in GLOBALFOUNDRIES 22FDX low-power technology is led by Fraunhofer IIS. The architecture above can be seen in Figure 3.1, in which we can see all the accelerators and tiles along with the NOC. Additionally, the EPAC is integrated and evaluated in the FPGA-based board designed by FORTH, E4 and the University of Zagreb.

In around two years, the different partners have developed and verified this whole structure. In the second half of 2021, the chip has been taped out, marking the end of the project's first phase. This tapeout took the name of EPAC 1.0 [1] and in Figure 3.2 we can see the layout with 25 mm2 in GF 22FDX technology. The figure shows the area distribution between the tiles and the rest of the accelerators.

Figure 3.1: EPAC Architecture Diagram [35]

Figure 3.2: EPAC first tape out [1]

These tiles are the ones composed, as seen in previous images, of one Avispado core and one Vector Accelerator. We developed the accelerator in the Barcelona Supercomputing Center, while Semidynamics developed the Avispado RISC-V scalar core. As well as in the rest of the design, communication between two modules developed by different partners was vital for success and one of the critical parts of the chip. To communicate these two IPs (intellectual properties), the different partners decided to use Open Vector Interface (OVI).

#### 3.2 Open Vector Interface

This interface was released and open-sourced by Semidynamics [41] to connect Vector Units to their cores. OVI eases the collaboration between the entities and helps focus only on the computation capabilities of the module one is developing. This is achieved by providing a specified interface to which the module must adapt instead of coming up with it. In its Github repository, one may find the specifications document for this interface [40].

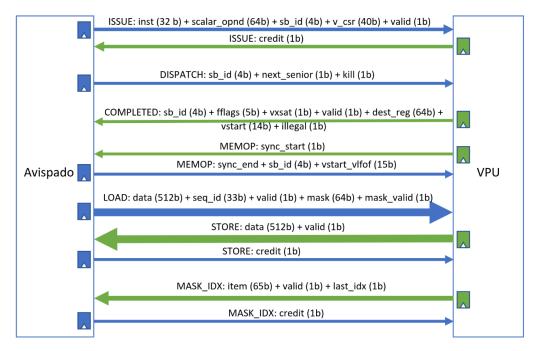

Figure 3.3: Open Vector Interface buses description

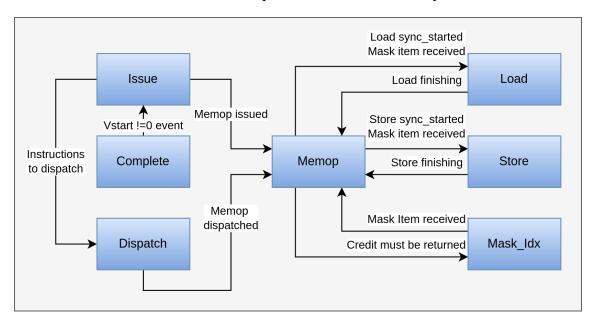

As seen in Figure 3.3, OVI is divided into multiple sub-interfaces. These are the Issue, Dispatch, Completed, Memop, Load, Store and Mask Idx sub-interfaces. Together, they send instructions and meta-data to execute them to the Vector Unit connected to the core. Each sub-interface is in charge of the following:

- Issue: Through this sub-interface, the core sends the Vector Accelerator the instructions and the necessary data for them. This sub-interface also has a credit system through which the Vector Unit controls how many instructions can be *issued*. Once the Vector Unit has treated (not necessarily executed) the incoming instructions, it will return a credit. If the core sends instructions non-stop without receiving a credit, it will have to stop sending them once it runs out of credits.

- Dispatch: All instructions must be *seniored* to finish execution or *killed* through this sub-interface. The Dispatch sub-interface is necessary due to the possibility of having an out-of-order core connected, which may discard already *issued* instructions. In addition, memory exceptions can cause instructions to fail execution and force the core to *kill* the following instructions.

- Completed: When the Vector Unit finishes the execution of an instruction, it will notify the core using the signals inside this bus. Along with this notification, the

buses may contain results and other meta-data.

- Memop: Previously *issued* memory instructions will start and finish their operation through the interface using this sub-interface.

- Load: If a load memory operation starts, the core will send the corresponding data and meta-data using this sub-interface. This meta-data includes a mask and a bus called *seq id* that specifies where the valid elements can be found inside the data.

- Store: If a store memory operation starts, the Vector Unit will use this sub-interface to send the corresponding data. This sub-interface uses a similar credit system to the one used by the Issue one, but it is the core now providing the credits instead of the Vector Unit.

- Mask Idx: If a masked memory operation starts, the Vector Unit will send the masks using this sub-interface. Indexed memory operations, usually called *scatter* and *gather*, also make use of the buses inside this group. The Mask Idx sub-interface also uses credits the same way as the Store one.

Not all cases were explained in the previous list but will be run down in depth in the following sections as these complicate the verification environment implementation.

As seen, many of these sub-interfaces may be used together to execute only one instruction. For example, if we wanted to execute a masked vector load, we would *issue* the load instruction through the Issue sub-interface and then confirm its execution using the Dispatch sub-interface. Afterwards, we would start and finish its memory operation through the Memop one, send the masks using the Mask Idx one, send the memory data through the Load one and communicate its ending through the Completed sub-interface.

Therefore, all these sub-interfaces are connected and must be used appropriately. Although the whole verification environment and process will be described, this work focuses mainly on the stimulus and verification of the OVI interface, because as can be seen, it carries many difficulties.

#### 3.3 Vector Accelerator Architecture

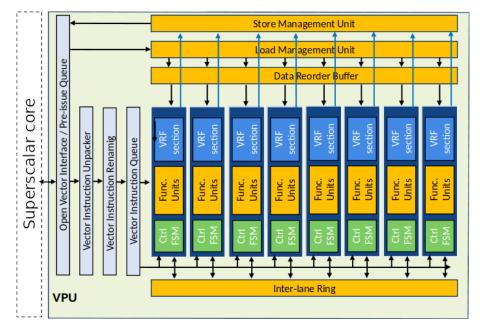

In our case, the Vector Accelerator [15] is our design under test (DUT). This work and the whole verification process concerns this Vector Processing Unit, which we will call VPU from this point on. In the EPAC architecture, each tile connected to the NOC has one VPU exclusively dedicated to executing vector instructions.

Our VPU supports 64 and 32-bit floating-point vector operations and 64, 32, 16 and 8-bit integer vector operations. It has 32 logical and 40 physical vector registers. With these, the VPU can handle vectors up to a maximum vector length of 256 elements of 64 bits each (16Kb in total). The VPU is connected to the scalar core through the OVI, as explained in Sections 3.1 and 3.2. The module that first receives the instructions, connected to the issue sub-interface, is the Pre Issue Queue, which controls the credit system of the sub-interface.

Once the instructions can be executed and after being decoded, these will be sent to the Store or Load Management Unit or the Vector Instructions Queue. The first two control

Figure 3.4: VPU Overview

the execution of memory instructions, while the Vector Instructions Queue provides the arithmetic ones to the Vector Lanes.

As seen in Figure 3.4, the VPU is composed of eight vector lanes. A vector lane is mainly in charge of processing vector arithmetic instructions. Each lane also has access and a part of the vector register file, used in almost every vector instruction. These lanes are interconnected thanks to the Inter-lane Ring.

Dividing the execution units into different vector lanes allows the operations to be performed concurrently. This parallelization is achieved by slicing the vector register file, which means that each lane contains only a portion of the vectors. Figure 3.5 shows the distribution of the elements of a vector in each slice of the vector register file.

In the figure, we can see the eight lanes. In every lane there are five banks with 256 registers of 64 bits each. The mapping of vector register elements is shown in the image. For the first vector (v0), element 0 is in lane 0; element 1 is in lane one and so on. This increases the throughput, as all lanes could be operating concurrently for the same vector to compute a vector instruction.

In addition, this parallel capability is also exploited in writing in the registers. It perfectly suits the data buses of the load and store sub-interfaces from OVI, which are 512 bits wide, meaning that from each transaction with the scalar core, potentially all the elements sent or received can be treated at once.

As seen in Figure 3.4, memory operations are treated in the corresponding Load or Store Management unit. Load memory operations have a limited out-of-order capability, as the scalar core could send some elements sooner than it should. This happens, for example, when it has a longer memory latency to access a previous element. This particularity of OVI is supported and handled in the VPU. Therefore, simulating all the possible OVI inter-

|           | 7   | 7          | _   | _               |           |     |     |     |     |        | ,   |     |

|-----------|-----|------------|-----|-----------------|-----------|-----|-----|-----|-----|--------|-----|-----|

| 1         | BO  | BO         | BO  |                 |           |     |     |     |     | LANE 0 |     |     |

| 1         | 7   | 6          | 5   | BO              | <b>B0</b> | BO  | BO  |     |     |        |     |     |

|           | 47  | 46         | 45  | 4               | 3         | 2   | 1   | BO  | B1  | B2     | B3  | B4  |

| 1         | 87  | 86         | 85  | 44              | 43        | 42  | 41  | 0   | 8   | 16     | 24  | 32  |

| <b>V0</b> | 127 | 126        | 125 | 84              | 83        | 82  | 81  | 40  | 48  | 56     | 64  | 72  |

|           | 167 | 166        | 125 | 124             | 123       | 122 | 121 | 80  | 88  | 96     | 104 | 112 |

| ]         | 207 | 206        | 205 | 164             | 163       | 162 | 161 | 120 | 128 | 136    | 144 | 152 |

| 1         | 247 | 246        |     | 204             | 203       | 202 |     | 160 | 168 | 176    | 184 | 192 |

|           | 31  | 30         | 245 | 244             | 243       | 242 | 201 | 200 | 208 | 216    | 224 | 232 |

| 1         | 71  | 70         | 29  | 28              | 27        | 26  | 241 | 240 | 248 | 0      | 8   | 16  |

| 1         | 111 | 110        | 69  | <mark>68</mark> | 67        | 66  | 25  | 24  | 32  | 40     | 48  | 56  |

| V1        | 151 | 150        | 109 | 108             | 107       | 106 | 65  | 64  | 72  | 80     | 88  | 96  |

| +         | 191 | 190        | 149 | 148             | 147       | 146 | 105 | 104 | 112 | 120    | 128 | 136 |

|           | 231 | 230        | 189 | 188             | 187       | 186 | 145 | 144 | 152 | 160    | 168 | 176 |

| 1         | 15  | 14         | 229 | 228             | 227       | 226 | 185 | 184 | 192 | 200    | 208 | 216 |

| 1         | 55  | 54         | 13  | 12              | 11        | 10  | 225 | 224 | 232 | 240    | 248 | 0   |

| -<br>     | 95  | 94         | 53  | 52              | 51        | 50  | 9   | 8   | 16  | 24     | 32  | 40  |

|           | 135 | 134        | 93  | 92              | 91        | 90  | 49  | 48  | 56  | 64     | 72  | 80  |

| 1         | 175 | 134        | 133 | 132             | 131       | 130 | 89  | 88  | 96  | 104    | 112 | 120 |

| 1         | 215 | 214        | 173 | 172             | 171       | 170 | 129 | 128 | 136 | 144    | 152 | 160 |

| 1         | 255 | 214        | 213 | 212             | 211       | 210 | 169 | 168 | 176 | 184    | 192 | 200 |

| -         | 39  |            | 253 | 252             | 251       | 250 | 209 | 208 | 216 | 224    | 232 | 240 |

| 1         | 79  | 38         | 37  | <u>36</u>       | 35        | 34  | 249 | 248 | 0   | 8      | 16  | 24  |

| - V3      | 119 | 78         | 77  | <b>76</b>       | 75        | 74  | 33  | 32  | 40  | 48     | 56  | 64  |

|           | 159 | 118        | 117 | 116             | 115       | 114 | 73  | 72  | 80  | 88     | 96  | 104 |

|           | 199 | 158        | 157 | 156             | 155       | 114 | 113 | 112 | 120 | 128    | 136 | 144 |

|           | 239 | <u>198</u> | 197 | 196             | 195       | 194 | 153 | 152 | 160 | 168    | 176 | 184 |

| V4        | 23  | 238        | 237 | 236             | 235       | 734 | 193 | 192 | 200 | 208    | 216 | 224 |

|           | 63  | 22         | 21  | 20              | 19        |     | 233 | 232 | 240 | 248    | 0   | 8   |

|           | 103 | 62         | 61  | 60              | 59        | 18  | 17  | 16  | 24  | 32     | 40  | 48  |

|           | 143 | 102        | 101 | 100             | 99        | 58  | 57  | 56  | 64  | 72     | 80  | 88  |

|           | 145 | 142        | 141 | 140             | 139       | 98  | 97  | 96  | 104 | 112    | 120 | 128 |

|           | 223 | 182        | 181 | 180             | 139       | 138 | 137 | 136 | 144 | 152    | 160 | 168 |

|           | 223 | 222        | 221 | 220             | 219       | 178 | 177 | 176 | 184 | 192    | 200 | 208 |

|           |     |            |     |                 | 213       | 218 | 217 | 216 | 224 | 232    | 240 | 248 |

Figure 3.5: Vector Register File diagram [15]

face behaviours along with these semi-random events complicate the verification process of the VPU.

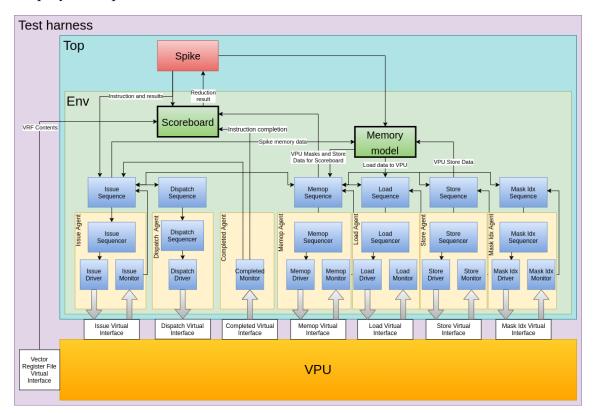

#### 3.4 Verification environment

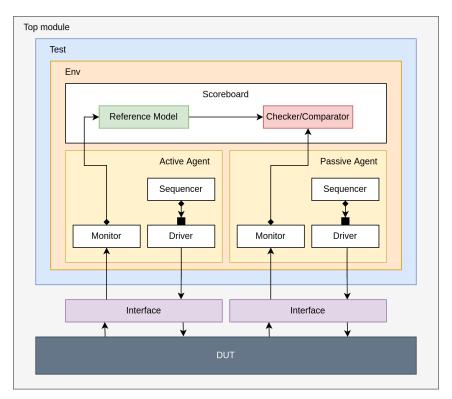

We first thought we could do block-level verification when planning the verification environment. That is, creating a verification environment for each module of the VPU. We came up with this idea from a mixture of the little information we had from the industry. However, big companies have big verification teams and the resources to take these projects to terms. In our case, we were four very junior verification engineers with no experience who had just learned what UVM was, so we soon saw that this strategy was unfeasible. In any case, developing the environments for some of these modules gave us the chance to make our first steps in UVM.

In the end, though, we decided to go directly for a full big UVM testbench for the whole design. Although it seemed pretty scary initially, this type of environment would help us verify the whole design at once, which would have taken months with the other strategy. We needed to emulate the OVI interface, such as the scalar core, to stimulate the whole design. For that purpose, as we had multiple "independent" sub-interfaces, we thought it would be interesting to have a sub-interface divided UVM testbench. These divided agents could all extend from a base agent class, making its development more manageable.

The UVM testbench and all of its features will be explained in detail in Chapters 4 and 5,

as this work mainly focuses on this part of the verification process.

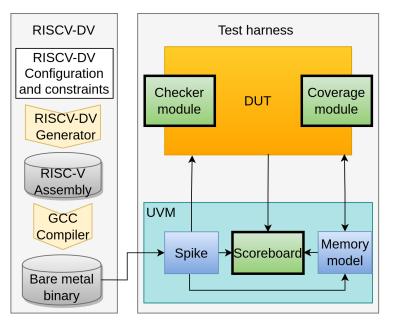

#### 3.4.1 Riscv-dv

Even if we planned on producing random stimulus, generating a valid instruction for the VPU would mean creating a complex set of constraints for the transaction. To solve this issue, we decided to go with an instruction generator.

After some search, we found a RISC-V instruction generator that supported the generation of vector instructions, Riscv-dv [16]. Riscv-dv is a System Verilog and UVM based open-source random instruction generator developed by Google.

However, we needed to perform several additions to the tool to use the generator. Among these, we find:

- Generation of *vsetvl* instructions through the code. The vsetvl instructions are used to change the element width and vector length of the registers during the execution of a binary. In addition to the prior, modifications in the generation of memory operations were done to allow the change of element width and vector length.

- An option was added to select the initialization pattern of the data pages of the generated binary.

- Constraining the memory addresses accessed by the binary to avoid memory exceptions, especially for vector memory indexed instructions, where some addresses could cause page or access fault exceptions.

- Adapting the generator to the 0.7.1 RISC-V Vector specifications.

Additionally, we had to blacklist different instructions in some stages of the project. This was either due to the VPU not supporting some instructions, because some modules were still under development, or because specific features needed to be tested and we needed a cleaner test.

The tool comes with a script to make it easier to execute. It offers capabilities like generating tests for different target architectures or generating multiple tests in only one command. When we run the generator, we obtain an assembly code, which becomes a binary after being compiled. This binary contains different random instructions, which we can feed to the VPU using the UVM and other environment features explained in the following sections.

#### 3.4.2 Spike ISS

With the features explained so far, we have the stimulus of the DUT and its generation. However, we need to check that the responses of the VPU are correct. This is often done in design verification using a reference model, which can be developed specifically for the project or borrowed from previous ones.

In addition to this, while we were developing the environment, we thought it would be more interesting to generate scalar instructions with Riscv-dv to simulate better the actual case with the scalar core. The VPU would be connected to a core that would only send the vector instructions while executing the scalar ones in the real environment.

Although this might seem inherent to the VPU, scalar instructions may modify values used in vector instructions. For instance, we have scalar to vector instructions, where a value in a scalar register is used for modifying vector registers, and memory instructions, where the memory space is shared between the scalar core and the VPU.

If we were not executing scalar instructions between the vector ones, the source values for the instructions mentioned above would always be the same, leading to possible missing cases or straight unreal situations.

For these two purposes, executing scalar instructions (acting as scalar core in general) and as a reference model for vector instructions, we decided that we needed an Instruction Set Simulator (ISS). These tools can execute binaries of the corresponding ISA and act as a design capable of interpreting their instructions. In the Barcelona Supercomputing Center, we have had previous experience with Spike [25], a RISC-V ISS, and we knew it satisfied our needs, so we decided to go with it.

However, we needed to perform some modifications and additions to use Spike as we wanted. These are the following:

- To call Spike from System Verilog, we defined functions that use Direct Programming Interface (DPI). This is necessary because Spike had to be compiled as a C++ library to be included. The main DPI functions are:

- Method that resumes the Spike simulation until a vector instruction is found. The instruction is then executed and the reference results are returned to the UVM. The instruction is issued in the VPU and when it completes, the DUT results are compared against the Spike ones.

- Function to set the result of specific instructions into Spike. This was necessary to avoid execution divergence in unordered floating-point reductions, as the VPU method for performing this operation was different from the Spike one, while both being correct. Even if we found a way to check that both results were correct, Spike would have a different value in its registers, which may later be used in another instruction, resulting in a mismatch. To avoid this, we inserted the result from the VPU into Spike.

- Functions to read from Spike memory, used in vector load instructions to provide the same data as Spike.

All the methods above allow Spike to act as the scalar core, providing instructions and the tools to emulate a real environment. However, the version of Spike that we had at the time was not the exact ISA version that we needed, which was the 0.7.1 of the RISC-V Vector Specification.

To tackle this issue, we had to introduce some modifications in the actual Spike implementation, which are detailed below:

• Change in the implementation of the vector tail zeroing, replaced by a different policy after version 0.7.1.

- Change in the decoding of some instructions to follow the 0.7.1 specification.

- Change in the requirements of the Vector Context Status (VCS) fields in the *mstatus* Control Status Registers (CSRs).

Once Spike fitted our needs perfectly, it allowed the execution of all kinds of instructions between Spike and the VPU. In addition, we could obtain the results of the vector instructions from both sources and compare them to assert that the VPU worked as expected, as will be explained in Subsection 3.4.3.

#### 3.4.3 UVM Scoreboard

The UVM Scoreboard is an optional UVM Component commonly used to ensure that the DUT works correctly. It is often composed of two main parts, the predictor and the comparator. The first obtains the expected outputs from the DUT resulting from the inputs it receives: a reference model. Usually, this reference model is written in a different, higher-level language than the DUT to make sure the implementation is different enough and correct to be used as a reference. On the other hand, the comparator takes the results from the predictor and the DUT and compares them to decide whether the DUT worked as expected or not.

In summary, the Scoreboard receives the same inputs as the DUT and compares the results it produces to those that the DUT produced. The UVM Scoreboard details can be seen in Figure 3.6.

Figure 3.6: Typical UVM Scoreboard structure and connections, based on [47]

This figure shows that the UVM Scoreboard is typically instantiated in the UVM Environment component. We can see that the image has two agents, one active and one passive.

These stimulate and observe the DUT, respectively.

The active agent also contains a monitor in charge of recording the interface's state when new stimuli are being sent. This is how the Scoreboard's predictor gets the input values, in this case, the "Reference Model" box in the figure. The reference model will generate the corresponding expected outputs from the DUT and send them to the "Checker/Comparator" component.

On the other hand, the passive agent is in charge of recording the output values of the DUT through its monitor. For this, the whole environment must be aware of the delay of the interaction with the DUT because otherwise, it would capture incorrect values. Afterwards, the monitor sends the transaction to the "Checker/Comparator" component in the Scoreboard, where the predictor results are waiting.

Once both values are in the comparator part of the Scoreboard, this will determine whether the DUT responded well to the stimulus or not. After this comparison is done, the Scoreboard might use the *uvm\_info* to display some information about it and *uvm\_warning* or *uvm\_error* to warn that something went wrong. Additionally, *uvm\_fatal* might be used to terminate the simulation instantly and show a message indicating what happened.

In the case of our verification environment, we decided to have a scoreboard for the results of the vector instructions. For this, we have a queue where issued instructions are stored as they come from Spike, with results and their sources. This works at the same time as the monitor before the predictor and the predictor itself from Figure 3.6 because it straight contains the results. Once one of these instructions completes, the monitor in the completed interface, which will be detailed in Chapter 4, will communicate to the Scoreboard that it can start its comparison.

For this, we could not use the typical scheme just described, as we did not have a monitor for the vector registers, only for the interface. We decided to create a different virtual interface to extract the values from the vector registers to face this issue. This is set up in the test harness and has two main issues:

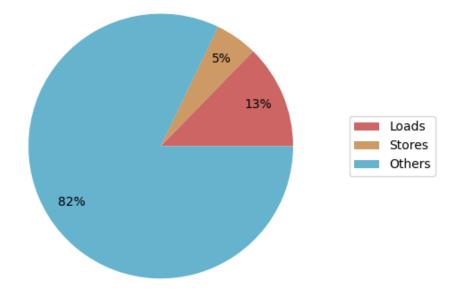

- It has to keep track of the actual destination vector register. Due to the VPU having register renaming, the physical vector register where the actual values are may not match the one specified in the instruction. To solve this issue, we maintained discussions with the RTL team and found a signal that pointed to the corresponding physical register when the instruction was completed. We decided to send this signal with the contents of all the physical registers to the scoreboard to select the correct register.