Escola Tècnica Superior d'Enginyeria de Telecomunicació de Barcelona

# **Countermeasure implementation and effectiveness analysis for AES resistance against side channel attacks**

A Master's Thesis

Submitted to

Escola Tècnica d'Enginyeria de Telecomunicació de Barcelona

Universitat Politècnica de Catalunya

by

Asier Matias Zubeldia Otaegui

In partial fulfilment of the requirements for the degree of MASTER IN ELECTRONIC ENGINEERING

Advisors: David Hernández García & Isidro Martín García Barcelona, June 2021

<u>Title of the thesis:</u> Countermeasure implementation and effectiveness analysis for AES resistance against side channel attacks

Author: Asier Matias Zubeldia Otaegui

Advisor: David Hernández García, Isidro Martín García

#### Abstract

Side channel analysis (SCA) is composed of a bunch of techniques employed to extract secret information from hardware operations through statistical analyses of execution data. For instance, the secret key of a crypto-algorithmic implementation could be targeted and its value could be retrieved. The data is obtained by measuring the power consumption or electromagnetic radiation of a device while performing an operation, due to the linear relationship between the currents flowing through the circuitry during the execution of chip operations. Side channel is one of the most widely used attack methods in cryptanalysis.

In order to avoid such attacks, the algorithmic implementations can be protected from side channel leakage with the use of different countermeasures. These countermeasures can be built on either software or hardware. The objective is to reduce, or even completely eliminate, the leakage of the device related to confidential data. Generally speaking, there are two main approaches to do so. The first aims to reduce the side channel observability, while the second intends to undermine the predictability of the data.

This project focuses on designing and implementing different countermeasures that protect cryptographic implementations from side channel attacks, and test and analyze them afterwards. The countermeasures will be implemented in software and then tested though Correlation Power Analysis in a hardware device.

The Advanced Encryption Standard (AES) algorithm will be used as a base structure, in order to improve its cryptographic security with the different countermeasures designed. However, the election of AES does not reduce the scope of this project since the implemented countermeasures could be applied to other cryptographic algorithms as well.

#### **Acknowledgements**

First of all, I would like to thank David Hernandez, advisor of this project, for all his help and support during the realization of this project. I would also like to thank the members of the IT department of Applus+ Laboratories.

In addition, I would like to thank the many friends from my years in UPV/EHU, who were part of my first steps in university. Thanks specially to Jon Martinez, who supported me and stayed next to me along the road.

Regarding this last years in the UPC, I would also like to thank Isidro Martín García, master coordinator, professor and advisor of this thesis, for his help and consideration. Additionally, I would like to thank Marina Martí, Romà Macario and Marcel Palets for the great moments we shared and for their support and patience as well.

Finally, I would like to thank my family, who have given me the opportunity to build my future , who have given me the means to grow as a man, who have showed me how to persevere in life and who have always stayed close to me.

### **Revision history and approval record**

| Revision | Date       | Purpose           |

|----------|------------|-------------------|

| 0        | 12/10/2021 | Document creation |

|          |            |                   |

|          |            |                   |

|          |            |                   |

| Written by: Asier Matias Zubeldia Otaegui |                               | Reviewed and approved by: David<br>Hernández García |                           |

|-------------------------------------------|-------------------------------|-----------------------------------------------------|---------------------------|

| Date                                      | 12/10/2021                    | Date                                                | 13/10/2021                |

| Name                                      | Asier Matias Zubeldia Otaegui | Name                                                | David Hernández<br>García |

| Position                                  | Project Author                | Position                                            | Project Supervisor        |

## Table of contents

| Abstrac   | :t      |                                                   | 2  |

|-----------|---------|---------------------------------------------------|----|

| Acknow    | ledge   | ements                                            | 4  |

| Revisio   | n hist  | ory and approval record                           | 5  |

| Table o   | f cont  | tents                                             | 6  |

| List of F | igure   | 2S                                                | 9  |

| List of T | ables   | δ                                                 | 10 |

| 1. Intr   | oduct   | tion                                              | 11 |

| 1.1.      | Cyb     | ersecurity                                        | 11 |

| 1.2.      | Soft    | tware, Hardware and Security                      | 11 |

| 1.3.      | Sec     | urity evaluations: White and black box approaches | 12 |

| 1.4.      | Ove     | erview of hardware attacks                        | 13 |

| 1.4       | .1.     | Physical Attacks                                  | 13 |

| 1.4       | .2.     | Fault Injection Attacks                           | 14 |

| 1.4       | .3.     | Side Channel Attacks                              | 15 |

| 1.5.      | Proj    | ject definition                                   | 15 |

| 1.5       | .1.     | Motivation                                        | 15 |

| 1.5       | .2.     | Objectives, procedure and experimental set-up     | 16 |

| 2. Sta    | ate of  | the art                                           | 17 |

| 2.1.      | Adv     | anced Encryption Standard                         | 17 |

| 2.2.      | Side    | e Channel Analysis (SCA)                          | 19 |

| 2.2       | .1.     | Side Channel basics                               | 19 |

| 2.2       | .2.     | Power consumption and leakage models              | 20 |

| 2.2       | .3.     | Side Channel attacks                              | 22 |

| 2         | 2.2.3.7 | 1. Simple Power Analysis (SPA)                    | 22 |

| 2         | 2.2.3.2 | 2. Differential power analysis (DPA)              | 23 |

| 2         | 2.2.3.3 | 3. Correlation Power Analysis                     | 24 |

|           | 2.2.    | 3.3.1. The Pearson's correlation coefficient      | 24 |

|           | 2.2.    | 3.3.2. CPA attack                                 | 25 |

| 2         | 2.2.3.4 | 4. Higher order attacks                           | 25 |

| 2         | 2.2.3.5 | 5. Profiling attacks                              | 26 |

| 2.3.      | Cou     | Intermeasures against side channel attacks        | 26 |

| 2.3       | .1.     | Hiding Countermeasures                            | 27 |

| 2         | 2.3.1.1 | 1. Amplitude hiding                               | 27 |

|     | 2.3.1.  | 2. Hiding in the time dimension                     | 27 |

|-----|---------|-----------------------------------------------------|----|

|     | 2.3.    | 1.2.1. Dummy executions                             | 28 |

|     | 2.3.    | 1.2.2. Randomizing or shuffling                     | 28 |

|     | 2.3.    | 1.2.3. Random time delay                            | 28 |

|     | 2.3.2.  | Masking countermeasures                             | 30 |

|     | 2.3.2.  | 1. Boolean masking vs Multiplicative masking        | 31 |

|     | 2.3.2.  | 2. Higher order masking                             | 31 |

|     | 2.3.3.  | Countermeasure effectivity                          | 32 |

|     | 2.3.4.  | Importance of unpredictability in randomization     | 33 |

| 3.  | Methodo | blogy and project development                       | 34 |

| 3.  | 1. Exp  | erimental setup                                     | 34 |

|     | 3.1.1.  | Chipwhisperer - Lite                                | 34 |

|     | 3.1.1.  | 1. Capture configuration                            | 35 |

|     | 3.1.2.  | Implementation environment                          | 35 |

| 3.2 | 2. Ana  | Ilysis metrics                                      | 36 |

|     | 3.2.1.  | Attack point: SBOX output                           | 36 |

|     | 3.2.2.  | Attack technique                                    | 37 |

|     | 3.2.3.  | Figures of merit and comparison metrics             | 38 |

| 3.3 | 3. Imp  | lementation development and analysis                | 38 |

|     | 3.3.1.  | AES without countermeasures                         | 38 |

|     | 3.3.1.  | 1. Implementation aspects                           | 38 |

|     | 3.3.1.  | 2. Leakage assessment of AES                        | 39 |

|     | SP      | A on AES                                            | 39 |

|     | CP      | A on AES                                            | 41 |

|     | 3.3.2.  | AES with hiding countermeasures                     | 45 |

|     | 3.3.2.  | 1. Dummy rounds                                     | 45 |

|     | SPA     | A on dummy round implementations                    | 46 |

|     | CP      | A on dummy round implementations                    | 48 |

|     | 3.3.2.  | 2. Shuffling                                        | 50 |

|     | SP      | A on shuffled implementation                        | 50 |

|     | CP      | A on shuffled SBOX and MixColumns                   | 51 |

|     | 3.3.2.  | 3. Random delays                                    | 52 |

|     | 3.3.    | 2.3.1. Single delay analysis: plain uniform delay   | 53 |

|     | SPA     | A on desynchronized traces by a single random delay | 53 |

|     | CP/     | A on desynchronized traces by a single random delay | 54 |

| 3.3.2.3.2. Multiple delay analysis                      | 56  |

|---------------------------------------------------------|-----|

| CPA on desynchronized traces by multiple random delays  | 57  |

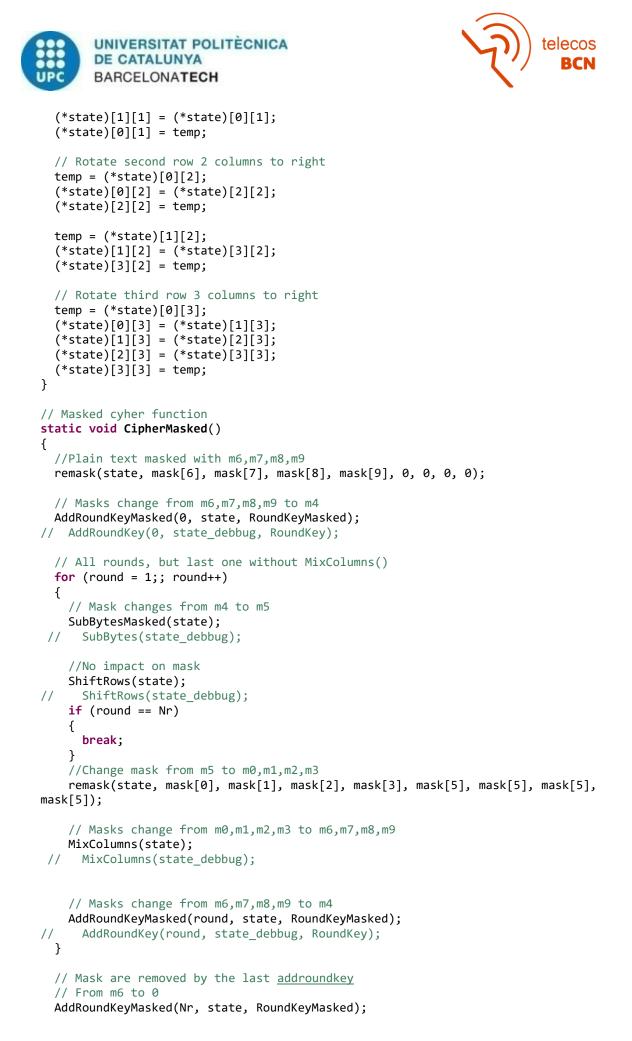

| 3.3.3. AES with Boolean masking                         | 57  |

| 3.3.3.1. Boolean masking implementation                 | 58  |

| SPA on Boolean masking implementation                   | 60  |

| CPA on Boolean masking implementation                   | 60  |

| 4. Conclusions and future work                          | 64  |

| 4.1. Conclusions                                        | 64  |

| 4.2. Future work                                        | 64  |

| 5. Budget                                               | 66  |

| Bibiliography                                           | 67  |

| Appendices                                              | 70  |

| Appendix A: AES in depth                                | 70  |

| A.1 Rijndael's finite field                             | 70  |

| A.2 AES round internal operations                       | 71  |

| A.2.1 SubBytes                                          | 71  |

| A.2.2 ShiftRows                                         | 72  |

| A.2.3 MixColumns                                        | 73  |

| A.2.4 AddRoundKey                                       | 74  |

| A.3 Key Schedule:                                       | 74  |

| Appendix B: AES LUTs                                    | 75  |

| B.1 AES SBOX and reverse SBOX                           | 75  |

| B.2 Galois multiply LUTs                                | 76  |

| Appendix C: Implementation codes                        | 80  |

| C.1 AES128                                              | 80  |

| C.2 AES128 with dummy round insertion (only encryption) | 86  |

| C.3 AES128 with randomization (only encryption)         | 94  |

| C.4 Random delay implementation                         | 99  |

| C.5 AES128 with Boolean masking                         | 100 |

| Glossary                                                | 116 |

## List of Figures

| Figure 1. State matrix                                                              | . 19 |

|-------------------------------------------------------------------------------------|------|

| Figure 2. AES encryption and decryption                                             | . 20 |

| Figure 3. SPA on AES encryption                                                     | . 24 |

| Figure 4. SPA on AES first round                                                    | . 25 |

| Figure 5. Power acquisitions with random delays                                     | . 31 |

| Figure 6. p.d.fs for the cumulative cases of 1,2,3,4 and 10 plain uniform delays    |      |

| Figure 7. Chipwhisperer lite capture and target boards                              |      |

| Figure 8: Experimental set-up                                                       | . 38 |

| Figure 9: Attack point: SBOX output                                                 | . 39 |

| Figure 10. SPA on AES128 implementation                                             | . 42 |

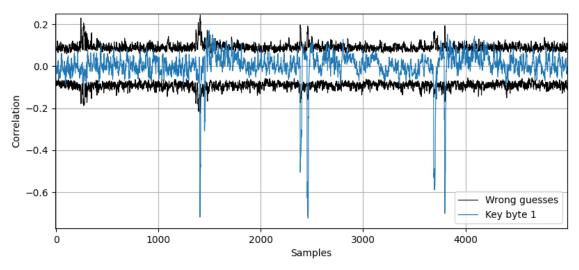

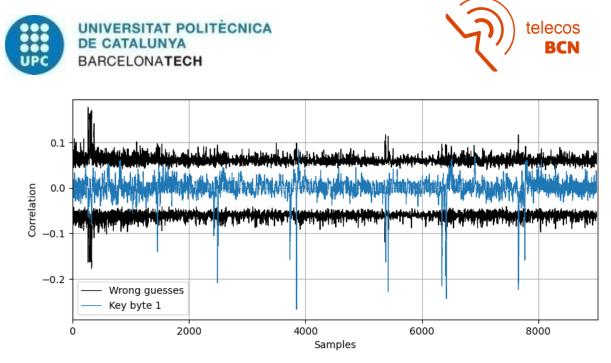

| Figure 11. Correlation vs time for key byte 1                                       | .44  |

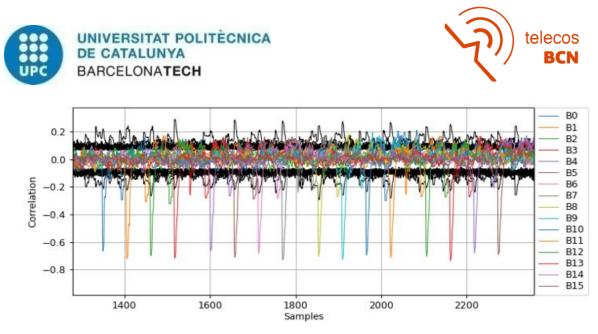

| Figure 12. Correlation vs time for all key bytes                                    | . 45 |

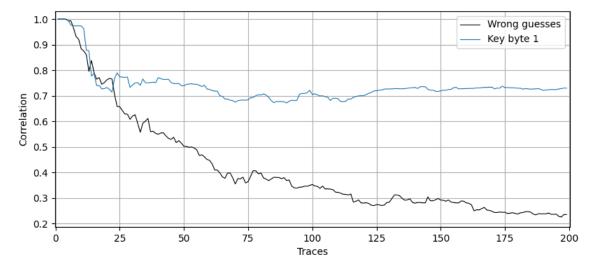

| Figure 13. Correlation evolution during the CPA for the key byte 1                  | . 46 |

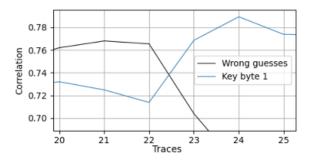

| Figure 14. Zoomed view of the divergence                                            | . 46 |

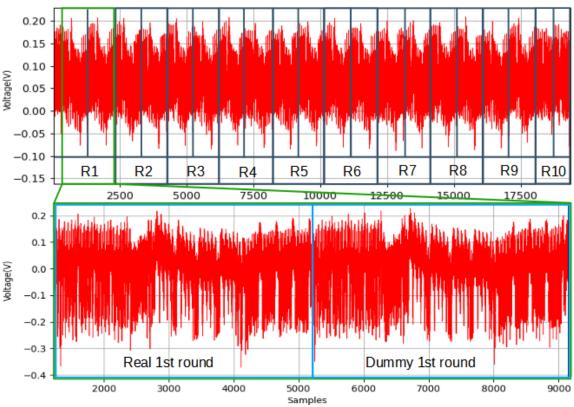

| Figure 15. SPA on the single dummy round implementation                             | . 48 |

| Figure 16: SPA on double dummy round implementation                                 | . 49 |

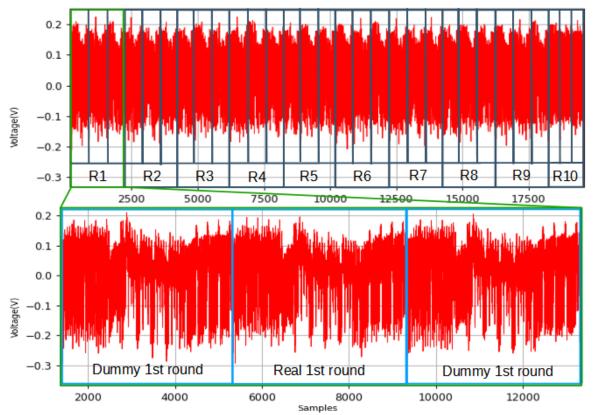

| Figure 17. AES length comparison for the unprotected, single dummy and double       |      |

| dummy                                                                               | . 50 |

| Figure 18: Correlation vs. time for key byte 1 on single dummy round implementation | า51  |

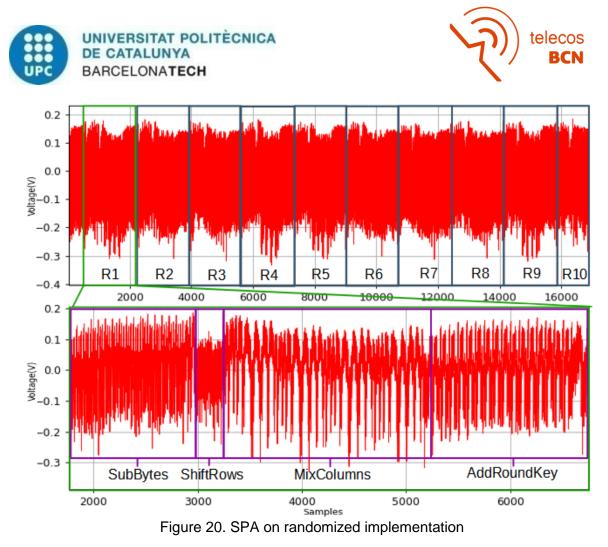

| Figure 19. SPA on randomized implementation                                         | . 53 |

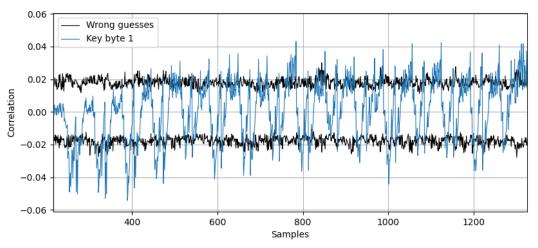

| Figure 20. Correlation vs time for key byte 1 with randomized SBOX-es               | . 54 |

| Figure 21: SPA on desynchronized traces by plain uniform delay                      | . 56 |

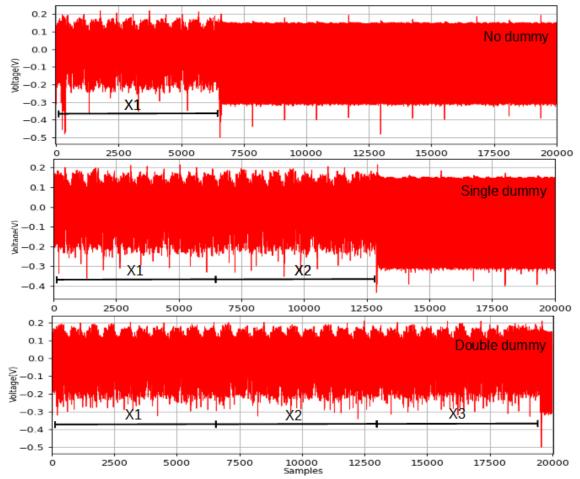

| Figure 22: Correlation vs. Time for key byte 1 with normal leaking behavior         | . 59 |

| Figure 23. Correlation vs. Time for key byte 3 with abnormal leaking behavior       | . 59 |

| Figure 24. Simple Boolean masking scheme                                            | . 62 |

| Figure 25. SPA on Boolean masking implementation                                    | . 63 |

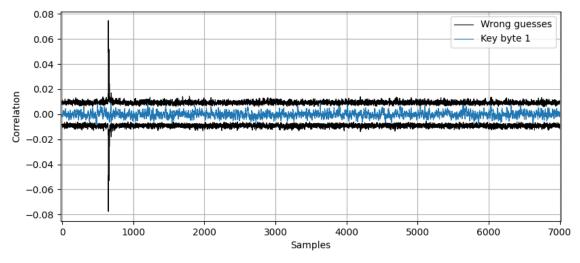

| Figure 26. Correlation vs. time for a perfectly masked key byte 1                   | . 64 |

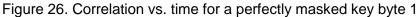

| Figure 27. Correlation vs. time for the only leaking key byte 11                    | . 65 |

| Figure 28. Correlation evolution during the CPA for perfectly masked key byte 1     | . 65 |

| Figure 29. Correlation evolution during the CPA for leaking key byte 11             | . 66 |

| Figure 30. ShiftRows permutation                                                    | .75  |

## List of Tables

| Table 1: Number of rounds for each AES key size                                | . 18 |

|--------------------------------------------------------------------------------|------|

| Table 2. Target MCU memory                                                     |      |

| Table 3. Capture configuration                                                 | . 36 |

| Table 4. Time measurements on the unprotected AES                              | . 42 |

| Table 5. CPA on first round results for unprotected AES128                     | . 42 |

| Table 6. CPA results on first round for the unprotected AES                    |      |

| Table 7. CPA results on different operations of the unprotected AES            | . 46 |

| Table 8. Encryption length for unprotected, single dummy and double dummy      | . 49 |

| Table 9. CPA results for single dummy and double dummy implementations         | . 50 |

| Table 10. Encryption length for the unprotected and randomized implementations | . 53 |

| Table 11. CPA results for the randomized SBOX-es                               | . 53 |

| Table 12. CPA results for the randomized MixColumns                            | . 54 |

| Table 13. Encryption length for AES128 with a single plain uniform delay       | . 56 |

| Table 14. CPA results for single plain uniform delay analysis                  | . 57 |

| Table 15. Results for multiple plain uniform delay analysis                    | . 59 |

| Table 16. Encryption length for the Boolean masked AES128 implementation       | . 62 |

| Table 17. CPA results for unprotected AES128 and Boolean masked AES128         | . 63 |

| Table 18. Overall results for hiding countermeasures                           | . 66 |

| Table 19. Overall results for Boolean masking implementation                   |      |

| Table 20. Hours dedicated to the project                                       | . 67 |

| Table 21. Cost of the project                                                  | . 68 |

| Table 22. Equivalent representations                                           | .72  |

| Table 23. Round constant values                                                | . 76 |

| Table 24. AES SBOX LUT                                                         |      |

| Table 25. AES reverse SBOX LUT                                                 | . 78 |

| Table 26. Galois LUT table for multiply by 2                                   | .78  |

| Table 27. Galois LUT table for multiply by 3                                   | . 79 |

| Table 28. Galois LUT table for multiply by 9                                   | . 80 |

| Table 29. Galois LUT table for multiply by 11                                  |      |

| Table 30. Galois LUT table for multiply by 13                                  | . 81 |

| Table 31. Galois LUT table for multiply by 14                                  | . 81 |

|                                                                                |      |

#### 1. <u>Introduction</u>

#### 1.1. <u>Cybersecurity</u>

Together with the growth of computer based systems over the last century, security has become an essential part of the modern electronic world. A world in which data is being constantly generated and processed for many purposes. Often, this data carries sensitive or confidential information and, thus, its protection is required. Payment information or personal identification data are some of the many examples of this sensitive information.

With the objective of securing this kind of information, the protection of the computer systems and networks is a must. This security scenario, known as **cybersecurity**, intends to protect users, systems and networks from the malicious intentions of an attacker willing to unveil confidential data.

Cybersecurity is an increasingly challenging field since the amount of interconnected devices is growing from day to day. The exchange of data is also spreading, which is translated into multiple new opportunities for malicious attackers. Consequently, hacking methods are being improved and attackers are becoming wiser on how to hack devices. In parallel, developers are also improving their defenses against cyberattacks.

For most of the people, cybersecurity is related to malicious malware known as "virus" or spam, or phishing though electronic mail. There has been some popular attacks along the last decades, driven to the massive filtering of sensitive user data from big servers; e.g. Yahoo (2013-2014), Facebook (2019) and LinkedIn (2021). However, the world of cybersecurity is much bigger than what is commonly thought. Cybersecurity includes hardware protection as well as software and network protection. For instance, additional related aspects to cybersecurity are the analyses of components and devices before reaching the market and the company departments for monitoring and responding to cyber-threats.

While the various security threats increase, cybersecurity is also in constant change and development in order to fight them.

#### 1.2. Software, Hardware and Security

Regarding modern computing systems, three main fields of software cybersecurity shall be considered. **Network security** focuses on the attacks on a network connecting multiple computer systems, and the mechanisms to ensure its availability, usability and integrity under potential attacks. **Software security** focuses on malicious attacks on software applications and operating systems, often exploiting different implementation bugs such as inconsistent error handling and buffer overflows. In addition, techniques to ensure reliable software operation in presence of potential security risks are also a part of this field. **Information security** focuses on the general practice of providing, among many other security attributes, confidentiality and integrity of information through protection against unauthorized access, use, modification, or destruction.

Historically, data security has been an issue of paramount concern for system designers and end users. Consequently, protection of systems and networks against various forms of attacks, targeting corruption or leakage of critical information and unauthorized access, have been widely investigated over the years. Information security, primarily based on cryptographic measures, has been analyzed and deployed in a large variety of applications. Software attacks in computer systems have also been extensively analyzed, and many diverse solutions have been proposed.

Study of **hardware cybersecurity**, on the other hand, has attracted little attention as opposed to network or software security, due to the higher complexity of protecting the hardware and the difficulty of breaking systems with attacks against hardware devices. In comparison with hacking devices through e.g. a buffer overflow vulnerability, a hardware attack requires a lot more effort and resources, i.e. expensive equipment capable of manipulating the hardware circuitry of the devices. Nevertheless, it is a field inside cybersecurity that has been considered since the early '90s when hardware attacks were used to hack payTV systems.

Hardware security really became a trend when credit cards moved from magnetic stripe payment to chip payment. Based on chips specialized in security and authentication applications, these devices were considered impossible to crack until the first fault injection demonstrations in 1996.

Hence, hardware security focuses on attacks and protection of hardware itself. More accurately, it deals with the security of electronic hardware, encompassing its design, architecture, implementation, and validation. It forms the foundation of system security, providing trust anchor for other components of a system that closely interact with it. Hardware should enable a secure and reliable operation of the software stack. If the hardware is not secure the full system can be vulnerable.

Over the years, many hardware attacks have been crafted in order to steal or compromise sensitive information from implementations. The targets of these attacks, known as assets, are typically the secrets stored inside the hardware components, e.g. cryptographic keys, digital rights management (DRM) keys, sensitive user data, firmware code, configuration data etc.

In order to ensure that hardware devices are secure, a set of security requirements and testing specifications must be defined, implemented by product developers, and tested by cybersecurity evaluation Labs.

#### 1.3. <u>Security evaluations: White and black box approaches</u>

With the objective of evaluating the security of a hardware, the evaluation Labs must consider all the applicable attacks, their associated vulnerabilities, the root causes for these vulnerabilities, and the countermeasures implemented by developers in their devices.

An evaluation can be "black box" or "white box" type. It is said to be a black box evaluation when the testing is made without any knowledge, or few knowledge, of what is happening inside the DUT (Device Under Test). An evaluation in these conditions is always complex and extensive, since the scope of security breaches that need to be covered is broad. A black box evaluation must consider every possible attack in order to assess the resistance of the DUT from all perspectives. In other words, if the Lab has no information about the DUT design, the only way to prove its resistance is by attacking.

On the contrary, when the evaluation Lab has access to the design and implementation features of the DUT, it is said to be a white box evaluation scenario. The developers can facilitate, for instance, hardware design code (Verilog/VHDL), schematics, firmware code, or application code. This way, the evaluators are able to accurately analyze the security architecture of the DUT and conduct a complete vulnerability assessment for all the assets against all kind of attacks, thus, limiting the testing campaign only to the identified vulnerabilities.

Normally, when performing an evaluation of a hardware device in a white box scenario, the next steps are followed:

- Firstly, a review of the hardware design and its security architecture is conducted.

- Based on it, a vulnerability assessment is carried out. This analysis identifies what vulnerabilities endanger any security attribute related to the assets.

- Next, an attack scenario is defined for each identified vulnerability. Depending on how feasible is to execute such attack, i.e. how easy is to exploit the vulnerability, the attack is executed or not. The attack is dismissed only when considered too complex for the given assurance level of the evaluation (some DUTs are evaluated in more depth and others with a more superficial assurance level).

- Lastly, attacks results are analyzed in order to give a verdict whether the DUT is vulnerable or resistant to the attacks.

Nowadays, security evaluations are always performed in a white box scenario due to the impracticability of performing the hundreds of existing hardware attacks in each evaluation. This scenario reduces the required effort for a security evaluation but, on the other hand, requires a deep knowledge on the effects of the countermeasures implemented on the DUT. In the end, the conclusions about the security of the DUT are based in the quality of the vulnerability assessment that the Lab performs.

As far as the development of this project is concerned, the implemented countermeasures were evaluated following a white box approach since both, developer and evaluator figures, were carried by myself. In these circumstances, a thorough analysis on the protective features of the countermeasures could be done. The flexibility of modifying the different implementations offered many points of view about what is happening when a developer introduces these countermeasures into their implementations.

#### 1.4. Overview of hardware attacks

The main difference between software and hardware attacks is that when performing a hardware attack, the attacker needs to interact physically with the device. This interaction is done through hardware tools and equipment, leading to a much more costly task in comparison with software attacks.

For instance, hardware attack scenarios may require oscilloscopes, real-time pattern recognition devices, function generators, *xyz*-positioning stages, signal conditioning hardware, filters and data processing techniques, etc. All of these are specialized instruments, which require an accurate and precise performance.

The most influential hardware attacks nowadays are grouped into three main types: Physical Attacks, Side Channel Attacks and Fault Injection Attacks.

#### 1.4.1. Physical Attacks

An attacker that performs physical attacks will substantially manipulate the device aiming to access its information. Reverse engineering is the first technique that falls into this group. The attacker analyzes in depth the chip layout from high resolution images taken with a Scanning Electron Microscope (SEM), after an etching process of the chip. The

analysis follows with the layer interconnections, the physical distribution of the memories, the analog and logic parts of the circuitry etc. If the reverse engineering is done well enough, an attacker could even illegally reproduce the device. In addition, the attacker can probe the data buses and observe the information that is traveling through them.

Another possibility is to introduce extra hardware to cause a malfunction of the device. This can be done by connecting some lines to ground or supply line in order to disable some security functionalities of the device. These tasks require high precision tools able to manipulate the chip's circuitry at a nanometer scale. For example, Focused Ion Beam (FIB) equipment is used to mill or deposit material. The milling of e.g. a power line will leave open circuit the power source of a hardware module, while the deposition of a conducting material between a circuit line and ground will generate a short-circuit permanently disconnecting the target module.

Alternatively, the attacker can focus directly on reading the memories from the high resolution images (SEM images). For instance, some ROM memories are often the easiest to read due to their physical construction that makes it possible to identify which cells are a '1' and which ones are a '0'. The simplest ROM cells can be read merely by observation of the physical presence or absence of a transistor in the cell. For this reason, it is recommended not to store critical information in these memories.

In general, Physical attacks are very powerful, allowing the physical tampering of the device and data in it. However, a great effort must be made and a deep knowledge on the chip is required in order to apply these techniques.

#### 1.4.2. Fault Injection Attacks

Fault injection (FI) is an invasive attack technique where an operating device is perturbed in order to inject a fault along its normal execution. This fault intends to either introduce a temporary malfunction or modify certain data stored inside the hardware device.

When the objective is to produce a malfunction of the device, an attacker usually targets the CPU. As the device operation continues, the fault can propagate to other locations and can generate a faulty chain effect in the execution of the device. For example, the objective of injecting a fault could be to jump a line of the firmware code of a device. Considering the case of a credit card, if a fault is injected exactly when the PIN number is verified, an attacker could proceed to purchase something with a stolen credit card, without actually knowing the PIN.

Alternatively, a register or memory position can be targeted in order to modify its content, e.g. set a register all to ones ("1") or all to zeros ("0"). As an example, it is known that UV light can be used to erase EEPROM cells. Hence, a target could be the memory position that stores the secret key of an algorithm which, after attacked with UV light, will be forced to be set all to zeros. If achieved, the attacker would know the value of the key.

There are different energy sources that can be used to inject faults into a device. One of the most used fault injection sources are laser beams. The main advantage of the laser beam in comparison with other sources of perturbation is the ability to focus in very specific areas of the chip to inject the fault.

Electromagnetic fault injection (EM-FI) is another efficient source of perturbation. A coil that generates EM pulses can induce computational faults without any physical contact with the device.

Another fault source is the voltage glitching. In this case, a transient voltage spike causes the malfunction of the system. This glitch is coupled to the device's power supply and is enough to disrupt the normal cycle of a firmware execution, without causing permanent damage to the circuitry. This is one of the first sources of perturbation used to hack the old payTV cards.

#### 1.4.3. Side Channel Attacks

Side channel analysis (SCA), unlike physical and fault injection attacks, is a non-invasive attack that uses statistical analyses of data in order to unveil sensitive information from a device. The analyzed data can be obtained through measurement of information that the device generates while operating, such as the variations of the power consumption, the signal propagation delay, and/or the electromagnetic emissions.

In order to apply SCA, an attacker first needs to acquire the data samples. For the power consumption analysis, a small resistor is usually placed between the power supply line and the cryptographic device in order to measure the voltage drop across it. In the case of EM radiation analysis, the signal is obtained using dedicated antennas.

Once the power or EM signal is available to the attacker, it can be taken into an oscilloscope in order to sample and record it. The attacker needs to gather big amounts of data, all proceeding from the same operation performed by the hardware DUT. Once this is done, the recorded data can be analyzed.

In order to infer useful information from the attack, the attacker will need to model the power consumption of the device and then apply statistics involving both measured and expected data. It is therefore, the relation between the measured data and the modelled data which establishes an analyzable and exploitable link for the attack.

Countermeasures against SCA can be implemented aiming to break that link or at least intending to debilitate this relationship between the power consumed and the data processed by the hardware device. Since this is the attack method chosen to conduct the countermeasure testing of this project, the topic will be more deeply addressed later in section 2.2 of this document.

#### 1.5. Project definition

#### 1.5.1. Motivation

Side cannel analysis is probably one of the most challenging attack methods nowadays. For this reason, it is widely-used against hardware devices. An increasing number of attack techniques are being developed and published every day and many cryptoalgorithmic implementations are shown to be vulnerable to such attacks.

Together with the development of SCA, engineers are trying to introduce countermeasures into their implementations in order to compensate for their vulnerabilities. However, each countermeasure has a distinct protective effectivity, each of them introduces a different complexity level into the design, each of them requires a different memory allocation and each of them adds a different overhead into the firmware

execution time. In overall, every countermeasure has some positive and negative aspects and, hence, some of them can be more or less useful depending on the context. In order to be capable of providing assurance on the security of a device, a deep and thorough knowledge on the different aspects involving algorithmic implementations and its countermeasures is required.

For the various countermeasures that exist nowadays, gaining knowledge about their fundamental effects is essential, including their protective effectivity and other improvable facets.

#### 1.5.2. Objectives, procedure and experimental set-up

The objectives of this project are to design, implement, test, analyze and compare firmware secure cryptographic countermeasures against side channel attacks.

The Advanced Encryption Standard (AES) algorithm is chosen as base structure to implement the countermeasures onto. The Correlation Power Analysis (CPA) is chosen as the side channel technique to test the various implementations developed. The results of the CPA are used as a metric to compare the effectiveness of the countermeasures.

For the development of this project, theoretical and practical works were conducted.

For the theoretical part, a brief description of the AES algorithm is given. Afterwards, SCA basics are introduced, in addition to the side channel attacks available nowadays. Lastly, an insight on side channel countermeasures is given to the reader.

For the practical part, the next experimental steps were followed:

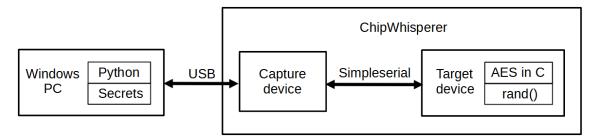

- *Chipwhisperer* platform was chosen for the AES implementation and the development of the side channel countermeasures.

- A leakage assessment was carried out on an unprotected implementation of AES, where a CPA was performed. The results were used as reference point for future comparisons with protected implementations of AES.

- Different countermeasures were designed and implemented on the cryptographic algorithm.

- Dummy round insertion

- Shuffling

- Random delay

- o Masking

- For each countermeasure implemented, a new leakage analysis was done in order to assess its protective effectivity.

- The different implementations were analyzed in terms added overhead (i.e. performance) with respect to the original unprotected AES.

- Results were gathered and compared.

## 2. <u>State of the art</u>

#### 2.1. Advanced Encryption Standard

The AES symmetric algorithm was chosen as base implementation for the development of this project. The Rijindael cypher, later renamed as Advanced Encryption Standard, is a specification for the encryption of electronic data established by the U.S. National Institute of Standards and Technology (NIST) in 2001 [1]. Two Belgian cryptographers, Vincent Rijmen and Joan Daemen, developed this algorithm that was used to replace the DES as the official encryption standard for protecting sensitive information.

The AES encryption finds applications in Mobile Phones, Smart Cards, Intel Core Processors Family, Automated Teller Machines (ATM), WWW servers, SSD Devices, IPSec and SSL Protocols, etc. It is massively spread and can be found in practically all security cryptosystems nowadays.

This cryptosystem is an iterative symmetric block cypher. It processes individual data blocks, having a fixed length of 128 bits, with a cipher key of variable lengths. The key length has to be chosen independently as 128, 192 or 256 bits. Hence, this algorithm can be used with three different key lengths, which result in three distinct formats referred to as AES-128, AES-192 and AES-256. It is an iterative cypher because the steps involved in this algorithm are repeated a fixed number of rounds The total number rounds of the cypher depends on the size of the key used. Table 1 shows the relation between key size and the total number of rounds for each AES format.

| AES format                                    | AES-128 | AES-192 | AES-256 |

|-----------------------------------------------|---------|---------|---------|

| Number of rounds                              | 10      | 12      | 14      |

| Table 1: Number of rounds for each AES format |         |         |         |

Table 1: Number of rounds for each AES format

In order to encrypt data, the 128-bit data block is divided into 16 bytes and correspondingly mapped into an array of size 4x4 known as the State matrix. All the internal operations (*SubBytes*, *ShifRows*, *MixColumns* and *AddRoundKey*), repeated round by round, are performed on the State matrix (Figure 1).

| <b>S</b> <sub>0,0</sub> | <b>S</b> <sub>0,1</sub> | <b>S</b> <sub>0,2</sub> | <b>S</b> <sub>0,3</sub> |

|-------------------------|-------------------------|-------------------------|-------------------------|

| <b>S</b> <sub>1,0</sub> | <b>S</b> <sub>1,1</sub> | <b>S</b> <sub>1,2</sub> | <b>S</b> 1,3            |

| <b>S</b> <sub>2,0</sub> | <b>S</b> <sub>2,1</sub> | <b>S</b> <sub>2,2</sub> | <b>S</b> <sub>2,3</sub> |

| <b>S</b> <sub>3,0</sub> | <b>S</b> <sub>3,1</sub> | <b>S</b> <sub>3,2</sub> | <b>S</b> <sub>3,3</sub> |

Figure 1. State matrix

When using AES, and also with every other symmetric algorithm, we look for an avalanche effect, where one single bit change influences as many output bits as possible, offering high diffusion and confusion to the message encryption. The diffusion and confusion of the message are obtained through the round internal operations of the AES, that perform permutations and substitutions on the state matrix.

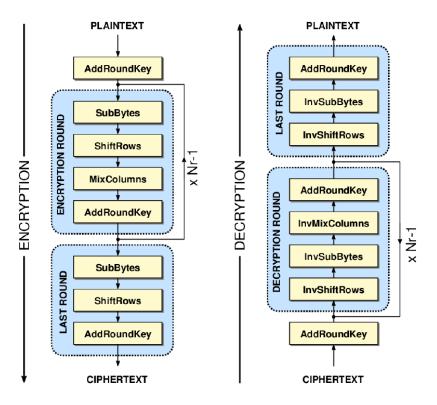

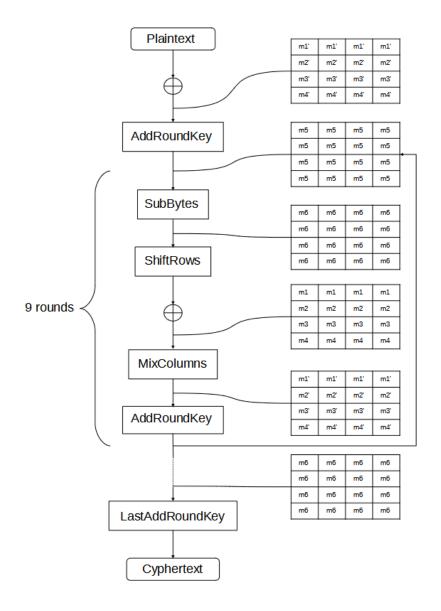

Figure 2. AES encryption and decryption

As shown in Figure 2, the algorithm starts with an initial *AddRoundKey* step. It is then followed by each of the rounds with the next internal transformations, in the following order: *SubBytes, ShifRows, MixColumns* and *AddRoundKey*. Note that, there is no *MixColumns* step in the last round. The same happens when decrypting that there is no *InvMixColumns* step in the last round. From a high-level perspective, each transformation step can be explained as:

- *SubBytes*: non-linear substitution step where each byte is replaced by another according to a LUT (Look-Up Table).

- *ShiftRows*: byte permutation step where the last three rows of the state are leftshifted cyclically a certain number of positions. The shifting applied is equal to the row number (from 0 to 3).

- *MixColumns*: linear algebraic mixing operation that operates on the columns of the state, combining the four bytes in each column through a multiplication with a constant matrix.

- AddRoundKey: recombination step where each byte of the state is merged with a byte of the round key through a bitwise XOR operation

In addition, AES uses a key schedule to expand the secret key into a number of separate round keys. The algorithm requires a separate 128-bit round key for each round plus one more, due to the initial *AddRoundKey* step. Thus, the key schedule produces all the required sub-keys from the initial cypher key.

As far as the decryption is concerned, all the transformation steps are reversed (*InvSubBytes, InvShiftRows and InvMixColumns*) in order to modify the ciphertext back to plaintext. Note that *AddRoundKey* is just an XOR, so it is its own inverse.

In case the reader was interested, a more detailed description of the AES algorithm and its internal operations is given in Appendix A, considering both mathematic and implementation aspects.

#### 2.2. Side Channel Analysis (SCA)

#### 2.2.1. Side Channel basics

Side channels are unintended sources of information that can be exploited by any attacker in order to extract secret data. Therefore, side-channel attacks take advantage of unexpected leakages of information. The designer of any implementation does not intentionally add this information sources into their design; however, the raw functionality of an electronic design carries, inevitably, analyzable side channels. For instance, an electronic circuit always generates a characteristic proportional to the power consumption and it always emanates electromagnetic radiation as the currents flow through the circuitry.

It is important to remark that unlike other attack methods, side channel analysis only requires to "listen" to the target device while it operates. We are talking about a non-invasive attack, where there is no need to influence or modify the target device in order to obtain information from it.

The simplest side channel attack technique is the timing attack. Timing attacks are based on the idea of analyzing different operations that take different computation times. Every logical operation in a computer takes certain time to execute, and these times can differ based on the inputs for example. In 1996, *Timing attacks on implementations of Diffie-Hellman, RSA, DSS, and other systems* [2] was one of the first side channel based attack ever published. Paul Kocher described the methodology to compromise keys of RSA, DSS and other cryptosystems, by measuring the execution time for the overall cryptographic operations.

In a similar way, sound can also be a useful side channel source. Acoustic emissions occur in coils and capacitors because of small movements when a current passes through them. Capacitors in particular change diameter slightly, generating sound, as their many layers experience electrostatic forces. One example is the first Side Channel attack performed in 1965 where the sound of a router was used to extract secret information [3].

Nevertheless, power consumption is the most widely used side channel source. As a general concept, it lays on the simple idea of some operations consuming more power than others. By measuring variations in the instantaneous power consumption of a device, it is possible to learn a considerable amount of information about the data being manipulated. For example, transistors, the most used elements in digital electronics, generate dynamic power consumption when changing from low to high state and vice-versa.

Therefore, power analysis attacks exploit the fact that the power consumption of a device depends on the operations it performs and on the data it processes. Usually, the total power consumption of the device is measured just by inserting a small resistor ( $1\Omega$  -  $50\Omega$ ) between the supply line and the cryptographic device. The voltage drop across this resistor is then proportional to the current that is flowing trough the device.

Electromagnetic radiation coming from the target device is another powerful side channel source. The analysis is equivalent to power consumption analysis with one main particularity: an EM prove (e.g. antenna) is used to receive the radiation, which can be placed accurately on the DUT surface (e.g. on top of the cryptographic co-processor to precisely acquire the targeted signal).

#### 2.2.2. Power consumption and leakage models

In CMOS circuits, the power consumption is derived from two parts, the static and dynamic power consumption. In the context of side channel attacks, the latter is generally the main source of exploitable power consumption as it is both operation and data dependent. It can be calculated as:

$$P_{dyn} = \alpha \cdot C \cdot V_{dd}^2 \cdot f \tag{1}$$

The parameter  $\alpha$  is the switching factor, *C* is the load capacitance,  $V_{dd}$  is the supply voltage and *f* denotes the clock frequency.

Since the power consumption at a given point in time is related to the number of transistors that change state, it is also related to the data being processed. If the same point in time over many acquisitions of the same operation is targeted, any operation dependent power consumption can be viewed to be part of the static power consumption and, thus, can be ignored.

Any side channel attack proceeds by using some statistical distinguisher, such as Pearson's correlation coefficient, to compare the hypothetical leakage model and the acquired power traces. A power trace refers to a set of power consumption measurements s(t) taken across the target operation. Considering this, the leakage model is constructed to estimate the power consumption of algorithmic intermediate values during the operation of a cryptosystem. In other words, the leakage model is a simplified model that describes the leaking signal (power consumption or EM radiation) in a workable manner, e.g.:

$$s(t) = f(algorithm, data, time)$$

<sup>(2)</sup>

The simpler the model, the easier to work with, but more distant to reality. When enough traces are available, and the hypothetical leakage model is accurate enough, the secret can be retrieved from the acquired power consumption. Therefore, the leakage model is required to approximate the actual power consumption as much as possible. When the acquisition of traces is limited by available equipment and limited access to the target device, a well-built leakage model can significantly enhance the performance of the attack method.

In the case of a DPA attack, the simplest of the models is considered: it is a single bit model that relies on the elementary idea of ones ('1') consuming more than zeros ('0'). However, the most commonly used models to estimate the power consumption are the linear models of Hamming weight and Hamming distance.

The Hamming weight model corresponds to the number of bits set to 1 in a binary data element.

$$B = \{b_m, b_{m-1}, b_{m-2}, b_{m-3}, \dots, b_0\}_2 \to Hw(B) \in [0, m]$$

(3)

For example, bytes considered, all the possible resulting Hamming weights range from 0 to 8. The following equations show two byte examples and their related Hamming weight values:

$$B_1 = \{10000100\}_2 \to Hw(B_1) = 2 \tag{4}$$

$$B_2 = \{10110001\}_2 \to Hw(B_2) = 4$$

(5)

Therefore, the Hamming weight model states a linear relationship between the power consumption and the number of ones travelling through the circuitry:

$$s(t) = a(t) \cdot Hw(B) + b \tag{6}$$

s denotes our power estimate, while a is the scalar gain between the Hamming weight and s. All the remaining aspects in the power consumption of a chip are assigned to a term denoted b which is assumed independent from the other variables. b encloses offsets, time dependent components and noise (typically Gaussian noise).

However, the Hamming weight model has a limitation. As stated in [4]: "It is generally assumed that the data leakage through the power side channel depends on the number of bits switching from one state to the other at a given time. This seems relevant when looking at a logical elementary gate as implemented in CMOS technology. The current consumed is related to the energy required to flip the bits from one state to the next" [4].

Consequently, it makes sense to define a leakage model as the Hamming distance. The basic power consumption model for the data dependency can be written as:

$$s(t) = a(t) \cdot Hd(R \oplus M) + b \tag{7}$$

This model represents the transition from a reference state R to a modified state M, where some bits, or all bits, have already been flipped. It is assumed that the switching of a bit from 0 to 1 or from 1 to 0 requires the same amount of energy and that all the machine bits handled at a given time are perfectly balanced and consume the same. This can be seen as a limitation, but considering a chip as a large set of elementary electrical components, this linear model fits reality quite well from a statistical point of view.

The Hamming distance can be easily calculated as the Hamming weight of the XOR-ed values of both bytes, i.e. the reference byte and the modified one. Applied to the example bytes of equations (4) and (5) and considering them, respectively, the reference and modified states:

$$Hd(B_1, B_2) = Hw(B_1 \oplus B_2) = 4$$

(8)

Looking at the equation (8), it is easy to deduce that the Hamming weight is just a particular case of the Hamming distance where the reference state is set to 0.

In many cases, the Hamming weight or Hamming distance models will not be an optimal leakage model for a given device. However, both linear models do provide an easily computable and robust approximation of the leakage, which is applicable in a wide range of scenarios.

Non-linear models have also been widely investigated, trying to improve the approximation of the actual leakage. In [4], the authors proposed a switching distance leakage model to improve the attack performance. In their work they suggest a model where the transistor switching from 1 to 0 consumes less power than from 0 to 1, i.e. different power is consumed in the charging and discharging phases. The experimental results showed that the attack performance is improved for a particular setup; however, some sort of profiling of the specific DUT is required.

In summary, a leakage model is always assumed in side channel attacks in order to estimate the relationship between the signal acquired with the oscilloscope and the data processed by the device. If the leakage model is accurate to reality, as Hamming weight and distance models are, we can find a linear relationship between the data processed by the device (sensitive data such as secret keys) and the power traces acquired.

#### 2.2.3. Side Channel attacks

Historically, many powerful side channel attacks are based on statistical methods pioneered by Paul Kocher. In 1995 Paul Kocher stated: "*Chip power consumption is somehow clearly linked to the manipulated data*". Later in 1999, an efficient side channel attack was introduced by himself: *Differential Power Analysis* [5]. The power consumption turned out to include deterministic data dependent parts, which could be exploited by simple and differential power analysis. Later, Eric Brier published *Correlation Power Analysis with a Leakage Model* [6], where correlations between power measurements and data were used to improve the previously introduced differential attacks through the Hamming distance leakage model.

As an evolution of first order attacks, in which the power consumption is analyzed in a time-independent manner, the SCA attacks took a more general perspective that resulted in higher order SCA, as originally proposed by Messerges [9] and Chari et al. [10]. Higher order SCA considers various time instants within a power trace to combine and build more complex leakage models.

Finally, one of the most powerful SCA techniques are the profiling attacks, in which the power consumption of a "twin" device is characterized creating templates that are later used against the victim's device to extract sensitive data. Besides Template Attacks and its variants [11,12, 13], the SCA community started using machine learning (e.g. Artificial Neural Networks) to conduct profiling attacks [14] [15].

#### 2.2.3.1. Simple Power Analysis (SPA)

SPA, known as SEMA in the case of electromagnetic radiation analysis, is the side channel analysis that involves the visual inspection of one, or a few number, of power traces. SPA is based on the identification of recognizable patterns, which may correspond to the target operation to be analyzed (e.g. crypto-operation or the load of an asset from memory). The objective is to identify instructions, security mechanisms or countermeasures, or directly read sensitive data as proposed by Kocher in his original work.

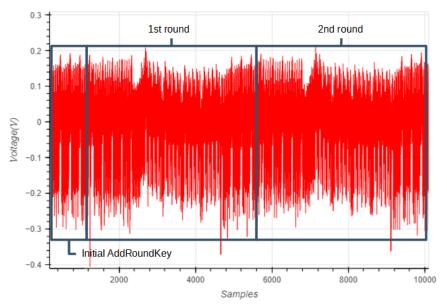

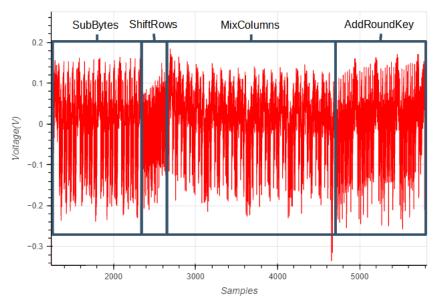

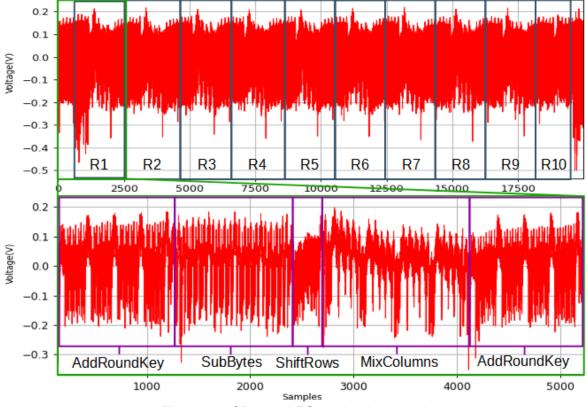

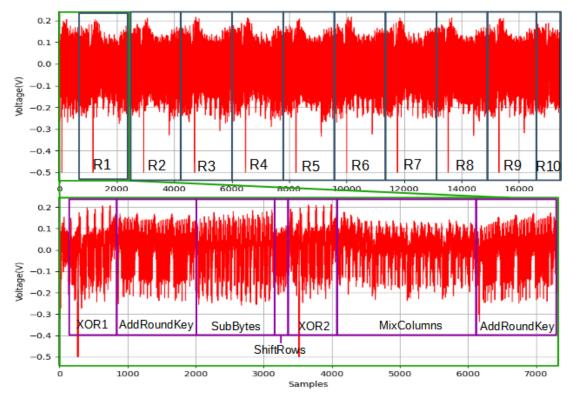

Figure 3. SPA on AES encryption

Figure 3 shows an example of SPA. The region of the initial *AddRoundKey* step in AES can be seen in the signal, followed by the power consumption of the first and second rounds of the algorithm.

Figure 4. SPA on AES first round

In Figure 4 the first round of AES encryption is shown from a closer view, were the different internal operations can be distinguished thanks to the distinguishable patterns that can be observed in the signal.

Performing an SPA is always an interesting initial step for extracting relevant features of the algorithm, such as the position of the rounds or the power consumption and duration of the internal operations of each round. Note that apart from the power consumption, timing also gives us valuable information in a SPA.

## 2.2.3.2. Differential power analysis (DPA)

DPA is a statistical analysis that involves working with a high number of power traces. The attack focuses on those small power variations and follows a "*divide and conquer*" strategy: find a point in the algorithm that works with smaller pieces of the key to be able to compute all possible values of the key for that smaller pieces.

If we consider an AES-128 that has a 128 bits key length, all the possible keys add up to  $2^{128}$  possibilities. However, let's consider the *SubBytes* operation as the target of the attack. The *SubBytes* operation is performed byte by byte 16 consecutive times, meaning that there will be different instants of time within the power consumption signal corresponding to the management of the 16 bytes independently. When attacking the SubBytes operation, instead of  $2^{128}$  possibilities we only have  $16 \cdot 2^8$  possible key guesses to assess in the power traces.

With this in mind, in order to carry out a DPA the next steps need to be followed:

- Obtain an amount of power traces of a known cryptographic operation, where the related inputs or outputs (plaintext or ciphertext) are random and known, but not the key, which has to be fixed (this is the secret to guess).

- Select the attack point in the algorithm where the differential attack will be carried out (e.g. the SubBytes operation of AES algorithm).

- Compute the reduced sub-key set and calculate the intermediate values at the attack point, for each sub-key, based on the inputs or outputs. In other words, guess the key is 0, then guess the key is 1, then guess it is 2, and so on, and for each possible key guess, calculate the data at the attack point.

- Select a bit of that intermediate data and observe if it is a 1 or a 0 in each case. Then, classify the traces into two groups depending on the value of its related bit.

- Lastly, obtain the difference among the averages of the two groups of traces.

When a wrong key is guessed, wrong intermediate data are calculated, hence wrong classification of traces is performed. In plain words, the group of '1's will contain traces related '1' and also traces related to '0', and the same for the group of '0's. Therefore, the subtraction of the average traces of the two groups will be noise.

However, when the correct key is guessed, the right intermediate data are calculated and traces are properly classified, meaning that in a specific instant of time, all traces in the group of '1's work with data that have one bit to '1' in all those traces (same for the group of '0's and data having a '0' in all traces). As a consequence, the average trace of the ones group will present a mean value higher than the average trace of the zeros group at the time instant that the tracked bit is handled in the power traces. The subtraction of the two averages will result in a peak in the differential signal.

From the mathematical point of view, the DPA can be represented with equation (9).

$$\Delta_{D}[j] = \frac{\sum_{i=1}^{m} D(C_{i}, b, K_{S}) T_{i}[j]}{\sum_{i=1}^{m} D(C_{i}, b, K_{S})} - \frac{\sum_{i=1}^{m} (1 - D(C_{i}, b, K_{S})) T_{i}[j]}{\sum_{i=1}^{m} (1 - D(C_{i}, b, K_{S}))}$$

(9)

*m* represents the total amount of encryption measurements and  $T_i[j]$  denotes the sample *j* at each of the related power traces  $T_i$ . The selection function  $D(C_i, b, K_s)$  is defined as the computation, at the attack point, of the selected bit *b*. This computation starts from the plaintext or ciphertext  $C_i$  and considers the key guess  $K_s$ .

Note the differential signal has to be computed for each one of the key guesses. The highest peak among the differential signals per each key guess will be related to the right guess of the secret key.

#### 2.2.3.3. Correlation Power Analysis

The main drawback of DPA is that it only focuses on one single bit of the whole data, while the power consumption of the device is not proportional to a single bit, but to the whole data manipulated by the device. So, despite DPA works, a more efficient attack results when analyzing the whole data and not a single bit. Continuing with the previous example in AES, a more efficient attack results when considering the whole byte value at the SubBytes operations rather than a single bit of this byte.

#### 2.2.3.3.1. The Pearson's correlation coefficient

Once we have a way to model our power consumption, we need a way to compare our power estimations to our measurements. A helpful tool to find this relationship is Pearson's correlation coefficient, which is:

$$\rho_{X,Y} = \frac{cov(X,Y)}{\sigma_X \sigma_Y} = \frac{E[(X-\bar{x})(Y-\bar{y})]}{\sqrt{E[(X-\bar{x})^2]E[(Y-\bar{y})^2]}} \quad , \quad \rho_{X,Y} \in [-1,1]$$

(10)

The covariance of two random variables, X and Y, divided by the multiplication of their respective standard deviations, gives us the linear correlation value between them. A coefficient of 1 represents direct proportionality between the random variables, while a coefficient of -1 denotes an inverse proportionality. Independency between the variables is, thus, represented with a coefficient value of 0.

#### 2.2.3.3.2. CPA attack

CPA targets the correlation between the power traces and the estimated values of the handled data in the algorithm.

Compared to the DPA, the CPA is better in terms of efficiency and robustness. On the one hand, DPA requires more sample curves since all the unpredicted data bits penalize the signal to noise ratio. CPA can use the Hamming weight or distance models, which consider bit groups as a whole.

The procedure for CPA attack is equivalent to the one described for DPA. The only difference resides on the metric, being the Pearson's coefficient in each sample the metric for the CPA. Each of the correlation factors, related to a key guess, can be obtained applying equation (11):

$$\rho_{i,j} = \frac{\sum_{d=1}^{D} [(h_{d,i} - \overline{h_i})(t_{d,j} - \overline{t_{d,j}})]}{\sqrt{\sum_{d=1}^{D} (h_{d,i} - \overline{h_i})^2} \sum_{d=1}^{D} (t_{d,j} - \overline{t_{d,j}})^2}$$

(11)

After taking our measurements, we have a total of *D* power traces and each of these *d* traces has *J* data points. Using subscript notation  $T_{d,j}$  refers to the point *j* in trace *d*. There are *I* different key guesses that we have to try. Then,  $h_{d,i}$  refers to our power estimate in trace *d*, for the subkey guess *i*. With these data we can calculate how well our model and measurements match for each subkey guess through time. This will be done by finding how *t* and *h* correlate over the D traces.

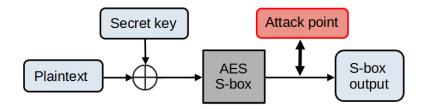

In other words, for each key guess it is calculated the data at the attack point and, instead of looking at the value of one bit, we apply a leakage model, e.g. the Hamming weight model, and correlate the power consumption traces with the Hamming weight of the intermediate data calculated. The highest correlation peaks will be the ones related to the right key. For wrong keys, wrong intermediate data is calculated which will result in no correlation with the power traces.

#### 2.2.3.4. Higher order attacks

In order to protect devices against DPA/CPA, one can break the correlation between power traces and calculated intermediate data by randomizing the data manipulated by the DUT. This is known as data masking. This topic will be addressed in more depth in section 2.3. The idea is to conceal intermediate data through addition or multiplication with random values [16], which might be impossible to predict for an attacker. However, the so-called first order masking countermeasure succumbs to second order DPA/CPA attacks as originally proposed in [9] and [10].

The mounting point for second order attacks is the fact that the side channel leakage of a masked value depends on a predictable value (the original data) and an unpredictable

one (the mask). The core idea is to jointly analyze the leakage of the masked value and the leakage of the mask to establish a relationship within the power consumption with the two values. These attacks are based on the joint statistical properties of multiple aspects of the signal, i.e. joint analysis of the power consumption at two (or more) points in time [17, 18, 19].

Higher order attacks imply bigger costs in terms of number of samples and computational complexity. In addition, the identification of the points in time at which to take the signals is a hard problem.

#### 2.2.3.5. Profiling attacks

Nowadays, profiling attacks are probably the most powerful and most widely used type of side channel attacks due to its high effectivity. The attack consists of two stages: the profiling stage and the extraction stage. The goal of the first is to fully characterize the operation of a given device with "profiles" for all the possible values that the operation can work with. A "profile" is essentially a set of probability distributions that describe how similar power or EM traces look for all different inputs.

Once the characterization is made, the developed profiles can be applied to the same device or to executions of the same operation from other "twin" devices, in order to rapidly extract the sensitive data. This application is made by comparing the power consumption of the victim's device with the obtained profiles. The *maximum likelihood* estimator is often used as a metric of similarity for this purpose.

In order to succeed, an attacker needs to gather a huge quantity of data related to the target operation intended to characterize. We are talking about data sets reaching usually more than a million traces. On the other hand, when the template is applied to the victim's device, only a few traces of the target operation are required to complete the attack.

Taking our example of the AES128, 256 possible values exist per each byte of the 16 that the AES master key has. Therefore, 4096 ( $256 \times 16$ ) profiles need to be created. Note that if the Hamming weight model is used, only 9 possible values exist per each byte (9 Hamming weights in a byte) and the profile amount required is reduced to 144.

The classical technique for applying profiling attacks is known as Template Attacks (TA). This methodology, based on a Gaussian assumption [5] for the characterization of the templates, can offer robust and accurate results.

Nevertheless, as machine learning keeps gaining strength in the modern era, profiling attacks are also turning into this field [14]. Profiling by deep learning using Artificial Neural Networks as analyzed in [15] and [22] has been reported to be a more a powerful tool that the others, with a huge potential still to be discovered.

#### 2.3. <u>Countermeasures against side channel attacks</u>

Every algorithmic implementation can succumb to attacks by power analysis methods if it is not properly protected. In general, the solution is to re-implement cryptosystems

taking into account a wide range of countermeasures, even if the cost in terms of performance could be high.

The followings are the two general approaches for cryptographic countermeasures against side channel:

- Data hiding to reduce the side channel observability.

- Data masking to undermine the intermediate variable predictability.

#### 2.3.1. Hiding Countermeasures

Power analysis attacks work because the power consumption of cryptographic devices depends on intermediate values of the executed algorithm. Therefore, the goal of countermeasures is to avoid, or at least to reduce, these dependencies. In the case of data hiding, this is done by breaking the link between the power consumption of the devices and the processed data values. There are two options: one is to hide power consumption in amplitude and the other is to hide it in time.

Hence, cryptographic devices that are protected by hiding execute cryptographic algorithms in the same way as unprotected devices. In particular, they calculate the same intermediate values. Yet, the hiding countermeasures make it difficult for an attacker to find exploitable information in power traces.

#### 2.3.1.1. Amplitude hiding

The objective is to directly change the power consumption characteristics of the performed operations. These techniques lower the leakage of a cryptographic device by lowering the SNR of the performed operations. It can be done in two ways: Increasing the noise or reducing the measured signal.

On the one hand, the most obvious way of increasing the noise is introducing any kind of noise in parallel, either performing several operations in parallel or using dedicated noise engines.

On the other hand, the most commonly used strategy for signal reduction is to employ dedicated logic styles for the cells of cryptographic devices. The overall power consumption of a cryptographic device is the sum of the power that is consumed by its cells. If each cell is built in such a way that its power consumption is constant, the overall power consumption will also be constant.

For instance, a practical example of amplitude hiding is the replacing of critical assembler instructions with ones whose "consumption signature" is hard to analyze. Another example is the process of re-engineering the critical circuitry which performs arithmetic operations and memory transfers.

In software, the options to alter the consumption of a cryptographic device are very limited. The power consumption characteristics of the instructions that are executed on a device are defined by the underlying hardware. Since this project is based on firmware implementations, this type of countermeasures were disregarded.

#### 2.3.1.2. Hiding in the time dimension

An important characteristic of power analysis attacks is that they need to acquire power traces that are aligned in time. If single points between power measurements belong to different time moments (i.e. distinct operations of the device), the statistical analysis of this point cannot be performed efficiently. In case of a CPA attack, the better alignment, the higher correlations that could be obtained.

#### 2.3.1.2.1. Dummy executions

This technique is based on inserting dummy executions in a random basis. These dummy executions must use dummy inputs and must never act on the real data that the algorithm is working with. As a result the output of the algorithm will not be affected by the countermeasure.

If any statistical analysis is applied to the measured traces, there will be random data that will obfuscate the results, while the real data will be displaced in the time axis.

It is important to make sure that every added dummy operation is undistinguishable from the real operations. Otherwise the attacker could simply identify the pattern of the fake operation within the power signal and filter it out.

In the case of an AES, dummy operations can be inserted in many formats, from high to low abstraction level. A full dummy encryption could be executed just before or after the real one. However, this option is usually not considered since it doubles the throughput. Alternatively, extra rounds could be added within a single AES execution, dummy operations can be inserted inside the rounds or individual dummy instructions, such as register data assignations, can be introduced into the algorithm.

#### 2.3.1.2.2. Randomizing or shuffling

Another option is to randomize the order of execution inside the algorithm. Usually, there are some executions inside an algorithm that have no order dependency between them, which means they could be randomized without influencing the final result.

Shuffling is a countermeasure that randomizes the power consumption in a similar way as the random insertion of dummy operations. However, shuffling does not affect the throughput as much as the insertion of dummy operations. The two countermeasures differ in the fact that the first one is adding extra data which enlarges the total execution time, while the other is only shuffling the data that is already there.

In the case of an AES, the most obvious part to be shuffled is the AES SBOX, which performs 16 independent fetches from the LUT. In the same manner, the *AddRoundKey* function can be shuffled in the order that establishes to XOR the state bytes with the round key bytes. Apart from that, the *ShiftRows* function internally acts independently on three rows and the *MixColumns* performs its operations in each independent column as well. Therefore, either the row order or column order can be shuffled as well in each function.

When an attacker tries to correlate data with the power traces, he will face difficulties because at the same instant of time, in different power traces it will be handled different data bytes.

The disadvantage of shuffling is that it can only be applied to a certain extent. The number of operations that can be shuffled in a cryptographic algorithm are limited, e.g. we can only shuffle the 16 bytes of the SBOX or the 4 columns of the MixColumns operation in AES. This number depends on the algorithm and on the architecture of the implementation.

In practice, both shuffling and the random dummy insertion are often combined.

#### 2.3.1.2.3. Random time delay

One of the most common countermeasures against SCA is the introduction of random delays. Instead of executing all the operations sequentially, the CPU interleaves the code's execution with that of dummy instructions so that the corresponding operation cycles do not match between different power traces because of the time shifts. These

time delays must be randomly generated along each execution and their effect can be considered as additive noise that worsens the SNR.

In general, random delays consist of a dummy loop where a random value is generated and then decremented until the accumulator reaches zero before executing any further code. Usually, the value generated and then decremented is uniformly distributed across all the values it can take.

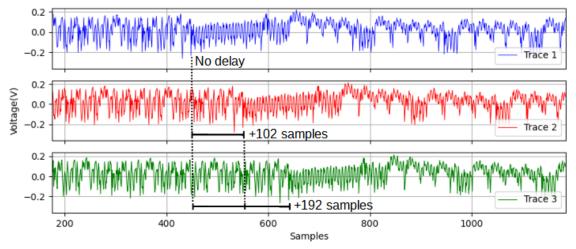

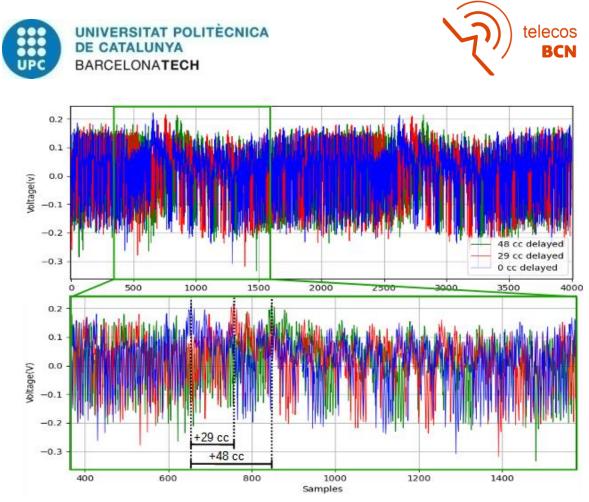

An example of three power consumption acquisitions that include random delays is shown in Figure 5. The three acquisitions belong to the first round of an AES and perform exactly the same operations, resulting in the exact same power profile. However, delays of 102 and 192 measured samples have been applied to trace 2 and trace 3, respect to the non-delayed trace 1. As a result, the acquisitions are no longer synchronous.

Figure 5. Power acquisitions with random delays

As the size of the random delay increases, an attacker is obliged to acquire more samples, so it is of interest to maximize the length of the delays, which on the contrary penalizes the performance of the execution in terms of added overhead.

Delays are rarely used in one single place. A single delay is easy to identify for an attacker and, therefore, its effect is easy to correct. This can be seen in the previous image where the high frequency pattern in the middle of the signals is only shifted some positions to the right in the case of the red and green signals. Therefore an attacker simply needs to re-align the traces to make that pattern match again. This is why random delays are usually implemented with short lengths and placed at different points through the whole algorithm. The objective is to break the trace with relatively short delays in multiple places so that it is undistinguishable where the attack point is.

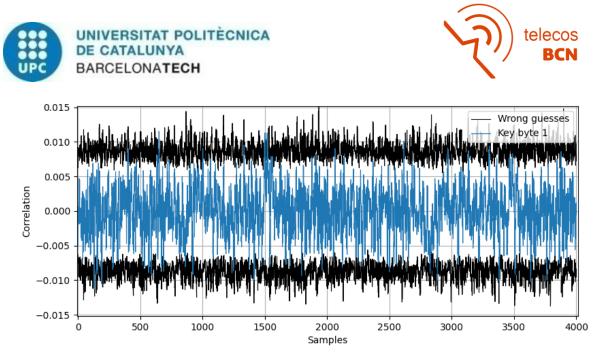

Hence, it is usually the cumulative effect of several random delays what protects an implementation from a SCA attack. Following the Central Limit Theorem, when the sum of random delays is generated from uniformly distributed random variables, the sequence of themselves rapidly becomes binomial, which approximates to a normal Gaussian distribution. This is why the cumulative delays are usually measured in terms of the mean  $\mu$ , variance  $\sigma$  and standard deviation  $\sigma^2$ .

Figure 6. p.d.f.-s for the cumulative cases of 1,2,3,4 and 10 plain uniform delays

Figure 6 displays the distribution for the cumulative effect of random delays when 1,2,3,4 and 10 sums of uniformly distributed delays are considered. It can be seen how the sum of two delays is not enough for the approximation to a Gaussian curve to be acceptable. However, from three delays on, the p.d.f. shape resembles well enough that of the normal Gaussian distribution.

From [26], we know that the variance and standard deviation are closely related to the protective effectivity of the random delays. The bigger the standard deviation is the better misalignment that will be obtained. On the other side, the lower the mean the lower the total overhead added by the random delays. Therefore, the cumulative effect of random delays is more efficient for high standard deviations and low mean values [25] [26] [27].

#### 2.3.2. Masking countermeasures

There is a different kind of countermeasure that must be always considered: data masking. Data masking intends to break all correlation between the power consumption and the actual intermediate data. In other words, masking allows making the power consumption independent from the intermediate data, even if the device has a data-dependent power consumption.

An advantage of this approach is that it can be implemented at the algorithmic level without changing the power consumption characteristics of the cryptographic device.

Hence, a masked algorithm is an algorithm which with given inputs will produce the same output than the non-masked version, with the only difference that all intermediate computations will be masked with random values. The masks are internally generated by the device for each algorithmic execution.

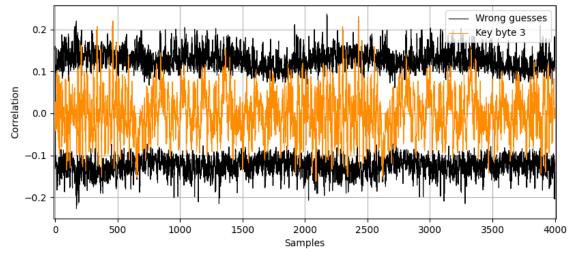

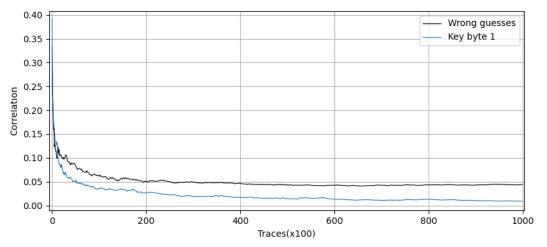

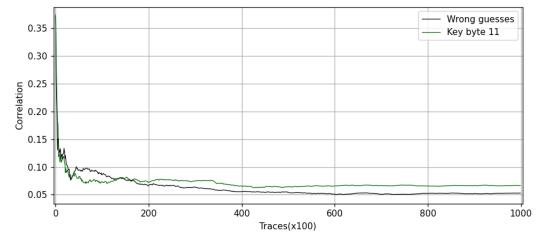

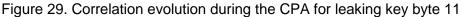

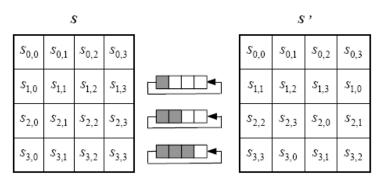

But what does masking mean? Data being masked means that the real value of the data is somehow mixed with more data. This mixing is usually done through XOR and AND operations. Since the data manipulated by the algorithm is not strictly the real data, the power consumption generated will not be the same and the leakage will be strongly reduced. If the masking is well implemented the leakage should disappear completely. In other words, if an attacker does not know to which values correlate the power traces (because the masking values are random and secret) the attack cannot be mounted.