## Characterization and Modeling of Atomic Memory Operations in Arm Based Architectures

## Víctor Soria Pardos

### DIRECTOR: ADRIÀ ARMEJACH (UPC, BSC-CNS) CO-DIRECTOR: DARÍO SUÁREZ (UNIZAR) RESPONSIBLE: MIQUEL MORETÓ (UPC)

# Master in Innovation and Research in Informatics: High Performance Computing

FACULTAT D'INFORMÀTICA DE BARCELONA (FIB)

Universitat Politècnica de Catalunya (UPC) BarcelonaTech

JANUARY 2022

## Abstract

Efficient fine-grain synchronization is a classic computer architecture challenge that has been profusely addressed in the past. Load Link and Store Conditional (LL/SC) became one of the few solutions to this problem and today it is still part of the State-of-the-art. However, as the core count keeps growing many Instruction Set Architectures (ISA) start to support other synchronization instructions that scale better like Atomic Memory Operations (AMO). In this work we present a characterization of LL/SC and AMO instructions in two current Arm-based server machines.

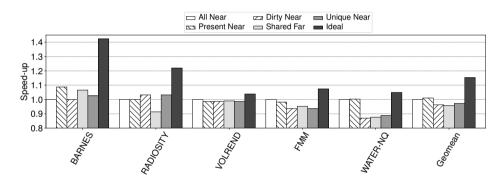

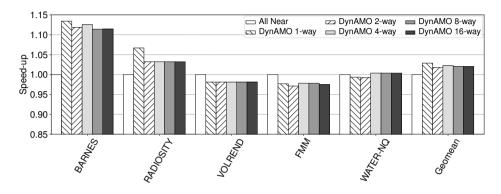

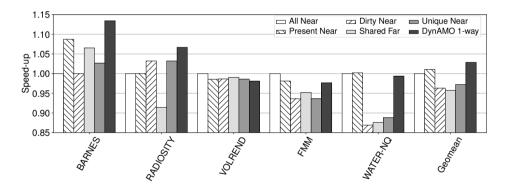

Furthermore, Arm has released its Network-on-Chip (NoC) specification enabling different hardware implementations of how AMO are executed in a multicore. Since the adoption of this new standard is still in its first stages, we have modeled six different AMO policies to explore the hardware design trade offs. We find out that there is no single implementation that outperforms the rest. Therefore, we have designed a hardware solution to dynamically select the best configuration obtaining up to 1.15x speed-ups on relevant benchmarks from the Splash-3 benchmark suite.

## Acknowledgements

First of all, I would like to thank Adrià Armejach, Darío Suárez and Miquel Moretó, for their support, patience and guidance. Thanks to all my coworkers for solved doubts, their helpful tools and lunch talks. I have to also thank my Friends for being there through thick and thin.

Finally, I would like to thank and dedicate this work to my parents for their support and love.

The project has been carried out within the Computer Sciences - High Performance Domain-Specific Architectures group of the BSC in collaboration with the Computer Architecture group of the Universidad of Zaragoza (gaZ).

# Contents

| 1        | Intr | roduction                                                 | 1 |

|----------|------|-----------------------------------------------------------|---|

|          | 1.1  | Context                                                   | 1 |

|          | 1.2  | Contributions                                             | 4 |

|          |      | 1.2.1 Characterization of Synchronization Instructions on |   |

|          |      | Arm-Based Architectures                                   | 4 |

|          |      | 1.2.2 Modeling of Atomic Memory Operations in             |   |

|          |      |                                                           | 5 |

|          |      | 1.2.3 Dynamic Atomic Memory Operations Policy             | 6 |

|          | 1.3  | Thesis Organization                                       | 6 |

| <b>2</b> | Stat | te of the Art                                             | 8 |

|          | 2.1  | Problem Statement                                         | 8 |

|          | 2.2  | Load Link and Store Conditional                           | 9 |

|          | 2.3  | Atomic Memory Operations                                  | 0 |

|          | 2.4  | Transactional Memory                                      | 2 |

|          | 2.5  | Related Work                                              | 3 |

| 3        | Exp  | perimental Framework 10                                   | 6 |

|          | 3.1  | Methodology and Environment                               | 6 |

|          |      | 3.1.1 Methodology                                         | 6 |

|          |      | 3.1.2 Software Environment                                | 7 |

|          |      | 3.1.3 Tools                                               | 9 |

|          | 3.2  | Workloads                                                 | 9 |

|          |      | 3.2.1 LockHammer                                          | 0 |

|          |      | 3.2.2 Splash-3                                            | 2 |

|          | 3.3  | Tests Machines                                            | 4 |

|          |      | 3.3.1 Kunpeng 920                                         | 4 |

|          |      | 3.3.2 Graviton 2                                          | 5 |

|          | 3.4  | The gem5 Simulator                                        | 8 |

|          |      | 3.4.1 CPU Microarchitecture                               | 8 |

|          |     | 3.4.2   | Cache Hierarchy and NoC Configuration           | 29        |

|----------|-----|---------|-------------------------------------------------|-----------|

| <b>4</b> | Cha | aracter | rization of Sync. Primitives                    | <b>31</b> |

|          | 4.1 | LockE   | Iammer Characterization                         | 31        |

|          |     | 4.1.1   | Kunpeng 920                                     | 32        |

|          |     | 4.1.2   | Graviton 2                                      | 36        |

|          |     | 4.1.3   | Summary                                         | 38        |

|          | 4.2 | Splash  | n-3 Characterization                            | 39        |

|          |     | 4.2.1   | Kunpeng 920                                     | 40        |

|          |     | 4.2.2   | Graviton 2                                      | 43        |

|          |     | 4.2.3   | Kunpeng 920 vs Graviton 2                       | 44        |

|          |     | 4.2.4   | Concluding Remarks                              | 47        |

| <b>5</b> | Mo  | deling  | Atomic Memory Operations                        | 48        |

|          | 5.1 | -       | A 5 CHI                                         | 48        |

|          |     | 5.1.1   | Channels                                        | 49        |

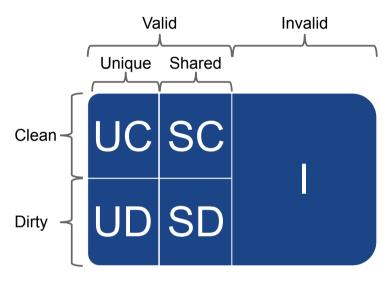

|          |     | 5.1.2   | Cache States                                    | 49        |

|          |     | 5.1.3   | Supported AMO                                   | 50        |

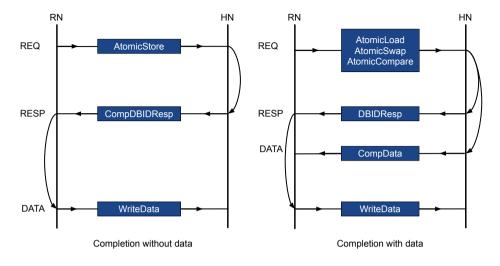

|          |     | 5.1.4   | AMO Transactions in AMBA 5 CHI                  | 52        |

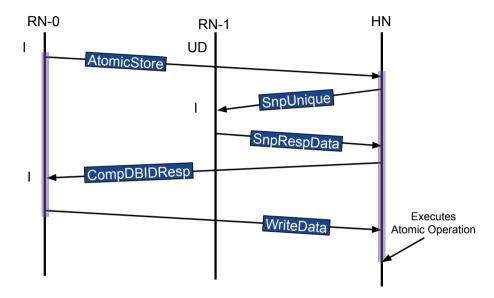

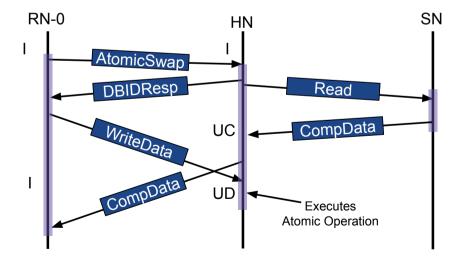

|          |     | 5.1.5   | Snoops                                          | 53        |

|          |     | 5.1.6   | Example Flowcharts                              | 54        |

|          |     | 5.1.7   | AMBA 5 CHI on Gem5                              | 56        |

|          | 5.2 | Desig   | n Space Exploration                             | 57        |

|          | 5.3 | Evalua  | ation                                           | 59        |

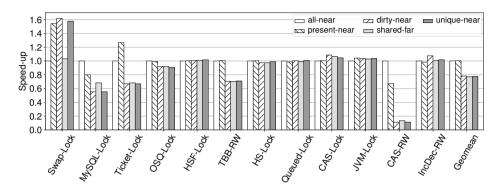

|          |     | 5.3.1   | Static AMO Results with LockHammer Serialized . | 59        |

|          |     | 5.3.2   | Static AMO Results with LockHammer Unserialized | 65        |

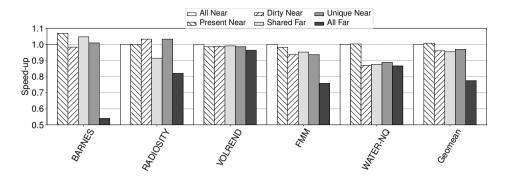

|          |     | 5.3.3   | Static AMO Results with Splash-3                | 67        |

|          | 5.4 | Concl   | uding Remarks                                   | 68        |

| 6        | Dyr | namic   | AMO Policy Predictor                            | 70        |

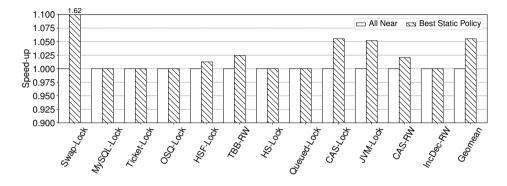

|          | 6.1 | Choos   | sing the Best Static Policy                     | 70        |

|          | 6.2 | Desigi  | n Philosophy                                    | 73        |

|          | 6.3 | Dynar   | mic AMO Predictor Heuristic                     | 74        |

|          | 6.4 | DynA    | MO Architecture                                 | 75        |

|          | 6.5 | Evalua  | ation                                           | 77        |

|          |     | 6.5.1   | DynAMO Results with LockHammer                  | 77        |

|          |     |         |                                                 |           |

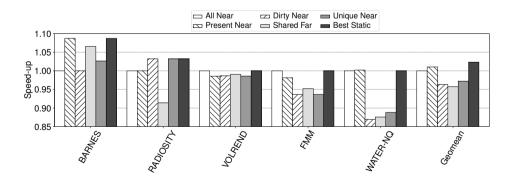

|   |     | 6.5.2 DynAMO Results with Splash-3 | 78        |

|---|-----|------------------------------------|-----------|

|   | 6.6 | Concluding Remarks                 | 81        |

| _ | C   |                                    | ~~        |

| 7 | Con | clusions and Future Work           | <b>82</b> |

|   | 7.1 | Conclusions                        | 82        |

|   | 7.2 | Future Work                        | 83        |

|   |     |                                    |           |

## Chapter 1

## Introduction

This chapter describes the historic evolution of semiconductor chips paying special attention to the emergence of multicore architectures. We explain the main challenges of current processors when facing multicore synchronization. Next, the main contributions of this thesis are summarized. Finally, we outline the organization of this document.

## 1.1 Context

During the last 40 years, the microchip industry has experimented an spectacular progress in microchip manufacturing. Every two years the top microchip manufacturers have been able to halve the transistor size, following what is known as the Moore's Law [34]. These advances not only improved transistor size, but also decreased their power consumption and their switching time. Thus, new chips incremented the switching frequency increasing performance [12]. However, this trend finished a few years ago because of the power density reached by the new manufacturing processes [9]. This effect was named as the "power-wall", which imposes challenges on heat dissipation, precluding the adoption of higher frequency chips.

Despite industry hitting the power-wall, Moore's Law continued delivering. However, instead of increasing frequency, new chips incorporated more computing elements to exploit those extra available transistors. In the High Performance Computing (HPC) area, which solves scientific and engineering problems with high computing demands, this extra computing elements translated into Central Processing Units (CPU) with a higher core count and internal memory capacity. Nevertheless, parallel computing is more complex to program than sequential computing. Apart from breaking the problem into independent parts or tasks to be executed concurrently, parallel computing requires program correctness. Frequently, independent tasks have dependencies that must be respected. Thus, parallel systems feature synchronization mechanisms to orchestrate those tasks. These dependencies make exploiting parallelism hard because they limit the maximum achieved speed-up. Furthermore, parallel computing is limited by the portion of code that is paralelizable, as stated by Amdahl's law [2].

Besides, as the amount of cores integrated in a chip increases, the interconnection delay to communicate them becomes a bottleneck. Whilst transistor switching time improves on every new process technology, wires have kept a constant delay and only small decreases have been achieved thanks to new metal layers and design partitioning [7]. Short distance wires have a controllable delay, but interconnections between different spread components have an exorbitant cost, taking several cycles to transverse these distances [7]. These limiting factors, have driven designer efforts to create new scalable interconnection designs based on Networks-on-Chip (NoC) [8]. The main idea behind NoC is that each component in the system has its own router to send and receive messages. Rather than using long and slow wires, connections are split using shorter links connected through routers. Consequently, systems based on NoC support higher frequencies, have higher bandwidth and are more scalable.

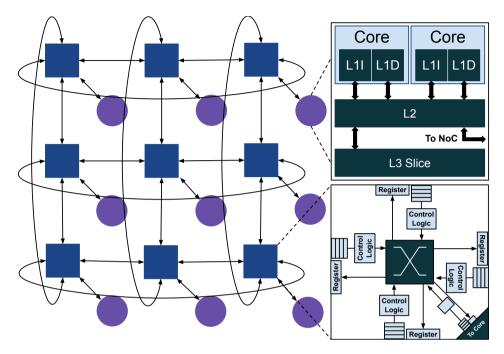

As the adoption of NoC spreads, new possible topologies are proposed to connect the different components in a system. A plethora of topologies exist, being the most popular the ring, the mesh, the crossbar, the hypercube and the torus. The common approach when designing a NoC chip is to distribute components in the network by placing one or several cores at every NoC crosspoint, forming a cluster. Each core is connected to one private first level of memory cache (L1). All the L1's are connected to a cluster-shared second level of memory cache (L2). Finally, it is common to place one slice of the shared third level of cache (L3) close to each cluster. Not all the NoC crosspoints have this structure, because there are other kinds of components that need to be placed on the chip, such as memory controllers, IO devices, DMAs, etc. Figure 1.1 depicts such a solution for a torus interconnection.

Another two fields that have experimented changes with the adoption

Figure 1.1: Torus 18-core diagram. Each crosspoint hosts a slice of shared L3 cache, private L2 and L1 caches and two cores.

of NoCs are Consistency and Cache Coherence. The former specifies how the cores see the memory updates, while the latter guarantees that each core reads the most recent version of the value stored in a given address. In snoop based protocols, this two conditions are satisfied broadcasting writes to all caches. In directory based protocols, all request are sent to the directory which orders the memory requests and selectively sends snoops to caches. NoCs have eased the transition from snoop-based to directory-based cache coherence protocols. The directory is now a distributed structure spread among the L3 slices. Thus, the centralization of memory request is no more a bottleneck. Now two different request can be processed in parallel in different directory slices. Moreover, NoCs typically use different physical channels to send requests, responses, snoops and data, enabling a higher message level parallelism between the two endpoints of a link. As we have seen, multicore architecture evolves with new technologies. In this work, we aim to revisit the current foundations of parallel synchronization relaying on the most recent developments.

## 1.2 Contributions

This thesis presents three contributions in the field of parallel synchronization. First, it analyzes the current state-of-the-art of parallel synchronization instructions doing a characterization. We limit the scope of this characterization to Arm-based systems for simplicity and availability. Second, we perform a design space exploration of modern parallel synchronization directives based on Atomic Memory Operations (AMOs) and evaluate them. We find that there is no single implementation that suits all cases. Third, based on this observation, we propose a mechanism to dynamically switch between implementations.

### 1.2.1 Characterization of Synchronization Instructions on Arm-Based Architectures

Parallel synchronization received a lot of attention in the parallel computing community back in the 80's and 90's [10] [18]. Nevertheless, as solutions were developed and integrated into final products, the interest on this topic has been relegated to academic discussion (parallel synchronization history is reviewed in Chapter 2). However, as the core-count of chips increases and new technologies like NoCs are adopted, synchronization is again starting to gain relevance.

Our first contribution consists on characterizing the behavior of available synchronization instructions on different Arm-based systems. The goal of this characterization is to find which synchronization instructions work better in different situations and what are their bottlenecks. A secondary goal of these experiments is to gather insights for the design and verification of a model that supports Atomic Memory Operations (AMOs) used for the second contribution. This characterization uses different experiments that include microkernels and real world applications. We use two different machines to compare possible different implementations, the Kunpeng 920 and the Graviton 2.

#### 1.2. CONTRIBUTIONS

In our experiments, we find that both machines behave different because of their specific implementations of LL/SC and AMOs. In the case of Kunpeng 920, AMOs have a higher cost than LL/SC. This higher cost makes that HPC applications scale better with LL/SC than with AMOs. However, in those scenarios with high contention AMOs are more efficient than LL/SC, despite their higher cost. In the case of Graviton 2, we find out that AMOs perform always better than LL/SC because of these pair of instructions frequently suffers from transient live locks. In the case of HPC applications we see how AMOs can speed-up  $1.25 \times$  the execution time.

#### 1.2.2 Modeling of Atomic Memory Operations in Arm-based systems

In last five years, Arm-based systems have expanded their market view to new sectors such as desktop (Apple's M1), server (AWS's Graviton 2) and HPC (Fujitsu's A64FX). As part of this expansion strategy, Arm has released an open standard for building large cache coherent systems based on NoC architectures, named Advanced Microcontroller Bus Architecture 5 Coherent Hub Interface (AMBA 5 CHI). This new standard has been used as the foundation of recent released many-core systems such as Graviton 2, Ampere Altra and Graviton 3.

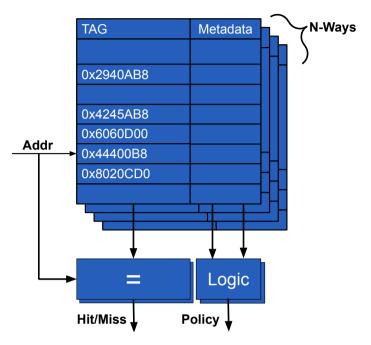

One of the key features introduced in this new NoC architecture (with respect to the previous AMBA specs) is the capability of performing remote or far Atomic Memory Operations. In several architectures, AMOs are performed only in the first level of cache next to the core. But in AMBA 5 CHI, AMOs can be sent inside a message to the cache coherence directory to be performed there to reduce pollution and further invalidations. We have followed AMBA 5 CHI specs to develop six different cache policies that execute AMOs in six different ways. Then, we have evaluated all six implementation using the same workloads of the characterization. In our experiments, we find out that each application has a different pattern access that fits different policies. Thus, we cannot use a single policy to obtain the highest performance in all applications.

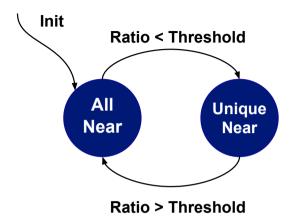

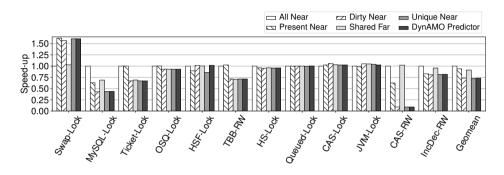

### 1.2.3 Dynamic Atomic Memory Operations Policy

The scenario opened by the second contribution gives us the opportunity to develop a hardware mechanism that is able to adapt to each application to select the best fitting AMO policy. In this third contribution we compute what is the achievable speed-up using an ideal policy. Next, we describe the design choices we have made to create an AMO policy predictor and what insights have motivated this design. Then, we perform a sensitivity study of the parameters of the predictor. Finally, we evaluate our predictor in the same conditions as the static policies. With our predictor we are able to some benchmarks significantly.

## 1.3 Thesis Organization

This document is structured in seven chapters that cover the following topics:

- Chapter 1 presents the context in which this thesis has been made. It also depicts briefly the contributions made in this work.

- Chapter 2 presents the challenges of parallel synchronization and summarizes the current solutions that have been used to tackle synchronization. It also describes some of the academic and industry proposals to improve current designs.

- Chapter 3 describes the methodology, tools and procedures used to perform the experiments presented in the thesis. It also explains the modeling environment used to develop our proposals.

- Chapter 4 presents the performed characterization to two current commercial multicore systems, focusing on the synchronization directives.

- Chapter 5 describes how we have modeled AMO in gem5, a well-known architectural simulator. It also explains the design space exploration we have performed to find AMO policies within AMBA 5 CHI specs. Finally, it evaluates the model using the same benchmarks used to characterize the real machines.

#### 1.3. THESIS ORGANIZATION

- Chapter 6 presents our hardware mechanism to select dynamically the best AMO policy. It contains an evaluation in which the dynamic mechanism is compared against static policies.

- Chapter 7 closes this thesis summing up all the contributions and publications.

## Chapter 2

## State of the Art

This chapter describes the main problems architects have to face when designing multicore systems. Then the most common solutions adopted by the industry to implement synchronization are explained. Finally, the chapter summarizes some solutions proposed in prior academic works.

## 2.1 Problem Statement

With the adoption of multicores two major types of architectures arised due to process intercommunication requirement. On one hand, Shared Memory systems have multiple processors reading and writing to the same shared data. On the other hand, Distributed Shared Memory (DSM) systems use processors that have its own local memory and send messages to communicate with other processors. Shared Memory multicores are the most common type of single-chip multicores, because Shared Memory offers a simple, fast and efficient method of communication. DSM systems with hundreds of processors employ Message Passing to communicate across nodes. The Message Passing Interface (MPI) [36] is the preferred standard to implement Message Passing.

though Shared Memory systems can provide efficient Even communication, the correct use of these systems demands deep knowledge different synchronization techniques. bv the programmer on Synchronization is used in modern multicore systems to orchestrate how different threads execute in parallel (i.e. forcing a Critical Section (CS) in which only one thread executes a part of the code, while other cores execute other parts or wait [20]). There are many synchronization directives that have been developed through the years, such as locks,

barriers, semaphores and transactions, among many others.

synchronization directives these require special A 11 support implemented in hardware, usually through specific instructions. Most of atomic Read-Modify-Write these instructions implement (RMW) operations that read a memory location, perform an operation with the read data and, finally write again the memory position with the result in an indivisible way. As we will see in Section 2.5, numerous hardware synchronization mechanisms have been proposed throughout the years, but only a few of them have been adopted by real systems. The most common solutions implemented are Load Link and Store Conditional (See Section 2.2), Atomic Memory Operations (See Section 2.3), and Transactional Memory (See Section 2.4).

## 2.2 Load Link and Store Conditional

In the past, the number of cores integrated on a single chip was low enough to adopt simple solutions that did not required big changes in the architecture. This is the case of Load-Link and Store-Conditional (LL/SC), a pair of instructions that together achieve atomic RMW semantics. First, the programmer uses a Load-Link (LL) to get the value that will be modified atomically. This instruction not only returns the current value of a memory location, but also flags the memory position as accessed by a LL. Then, the programmer can modify the read value as needed. Finally, to update the memory position a Store-Conditional (SC) is issued. This SC only succeeds if the flag left by the LL has not been removed. To ensure that no other core updates that memory position, the system must clean the LL flag on every store performed.

LL/SC have been adopted by many Instruction Set Architectures (ISA) like MIPS, Power, Arm and RISC-V. The most common implementation of LL/SC is based on cache coherence invalidation protocols. When a write operation is performed by a core, the cache coherence protocol sends invalidations to other caches that hold the cache line to gain the exclusive access to it. Therefore, when a LL brings the block to the cache in a Shared state, if any other core writes to the same cache line, then the cache line will be invalidated. Thus, on a SC the cache line will no longer be present and it will fail. Other implementations, instead of issuing the invalidations when

the SC is executed, issue the invalidations when the LL is executed. This simplifies the execution of the SC because the block is already in exclusive state on the L1 cache. However, this approach can generate live-locks when several threads issue LLs that invalidate each other's cache lines.

Arm defines in its architecture that the LL/SC handling mechanism must be carried by Exclusive Monitors [22]. Each core has a local monitor that is associated with it. The local monitor can be constructed to hold the exclusive state for a particular address. Any exclusive store is treated as if it matches the address of the previous exclusive load. Thus, only one LL/SC pair can be handle at a time and other memory accesses are usually forbidden or restricted in number.

As can be derived from the previous example, LL/SC do not guarantee always forward progress for all cores, but for one of them. For example, when two cores want to increment a shared counter, both would emit LL, perform an addition and emit a SC. But only a single core can increment the shared counter, while the others fail.

One of the key advantages of LL/SC is that performing the computation associated with the RMW operation has free cost in hardware, because the Arithmetic Logic Unit (ALU) of the core can be reused. It also allows programmers to perform different sequences of integer/float operations. However, as the computation between a LL and a SC increases, the probability of failure for the SC also increases. Moreover, as the core count increases the performance of LL/SC can degrade as we will see in Chapter 4.

## 2.3 Atomic Memory Operations

Atomic Memory Operations (AMOs) are instructions that directly encode a basic operation that is performed with RMW semantics. The main difference with LL/SC is that the operation is done in an indivisible way. Some AMOs such as a swap (exchanges two values) or fetch-and-add (increment the value of a memory position) guarantee forward progress of all threads or cores that execute those instructions. Following the example seen in the previous subsection, two threads that want to increment a shared counter would emit a fetch-and-add instruction and both would succeed.

#### 2.3. ATOMIC MEMORY OPERATIONS

AMOs are widely adopted by most ISAs such as Power, Arm, RISC-V or x86. Analogously to LL/SC, AMOs can be implemented in such a way that, they reuse the hardware that already exist on a core. During the operation the core blocks the cache line, so invalidations are deferred until the operation completes. This is the approach Intel took to implement its instruction XCHG. This implementation, although correct and intuitive, sacrifices performance because of the complex control required between the core and the cache.

Another well known approach is to first obtain the cache block in Modified (M) state and then perform the operation inside the first Level of Cache. This requires an specific ALU and pipeline to perform AMOs. This solution can be found in the Lowrisc L1 cache [33].

A more complex solution consist on executing AMOs on other components of the chip, such as a memory controller or a shared cache bank [18] [21] [14]. This remote execution of an AMO is known as Far AMO. The idea is interesting when several cores access a specific cache line and the block "ping-pongs" from one core to another. Thus, instead of bringing the data to the computation, the computation is sent where the data resides.

Far AMOs were implemented in commercial projects like the Cray T3D [24], T3E [40], and SGI Origin [27], in which Far AMOs were implemented at the memory controllers. TilePro64 [43] and recent GPUs [46] implemented Far AMOs in shared caches. While, this idea was deeply explored in the past, it has not been used in mainstream processors until recently. Power9 has adopted Far AMOs at the memory controllers, while Arm supports different solutions in its Advanced Microcontroller Bus Architecture (AMBA) 5 Coherent Hub Interface (CHI) specs.

Despite AMOs were designed to reduce the latency and NoC traffic, they still cause significant global traffic since operations are sent to a shared, fixed location. Serialization can be another problem because each Far AMOs has both read and write semantics (they return the latest value of the memory position they update). Therefore, consistency needs to be preserved issuing the AMOs only at commit (like a store) and waiting until the value returns (like a load). This is the reason why ISAs like RISC-V, Arm and Power9 have included atomic-no-return instructions, in which the previous data to the update is not fetch to the core. These instructions reduce the cost of AMOs, because cores are able to commit AMOs earlier due to the weak consistency memory model.

## 2.4 Transactional Memory

Both LL/SC and AMOs are widely used to implement high level directives like mutexes, spinlocks and barriers among others. However, programming parallel applications using those directives can be complex and requires experienced programmers. Transactional Memory (TM) [19] aims to address the need for a simpler parallel programming model. TM promises good parallel performance and easy-to-write parallel code. With TM, programmers simply demarcate sections of code (called transactions) where synchronization occurs. Then the Hardware Transactional Memory (HTM) system executes those transactions guaranteeing the following properties: atomicity, isolation, and serialisability.

To provide atomicity, the HTM system ensures that transactions are executed under all-or-nothing semantics, either all the code in a transaction is executed or none of it. Isolation is provided by ensuring that no partial results are visible to the rest of the system, results are made visible only when a transaction completes its execution successfully. Finally, serialisability requires the execution order of concurrent transactions to be equivalent to some sequential execution order of the same transactions. To guarantee this properties all TM systems need to perform two important tasks: conflict detection and version management [6].

To detect conflicts, each transaction tracks the memory accesses into two different sets the read-set and the write-set. Then, when the transaction is committing read and write sets are compared to detect fine-grain read-write and write-write conflicts. If a conflict is found, one of the conflicting transactions has to be aborted, the execution state is then rolled back to the point where the transaction started, and the transaction is retried. Otherwise, if no conflicts are found, the transaction commits successfully.

## 2.5 Related Work

Academic literature has profusely explored hardware and software techniques that reduce the cost of updates to shared data. Apart from the aforementioned solutions, there are other ideas that were not widely implemented in real systems that are related with the topic that we will cover in this section.

One of the first proposals made in 1995 is Dynamic Self-Invalidation (DSI)[28]. DSI is a technique that tries to eliminate invalidation messages by automatically invalidating private cache line copies. This must be done before a conflicting access by another processor triggers an invalidation message. The directory is the component that identifies which blocks should use self-invalidation by maintaining a history of its sharing pattern. When servicing a request for a cache block, the directory uses an extra bit to signal if the block is likely to be invalidated in the future. Then, the self-invalidation is triggered in two scenarios: when a synchronization instruction is executed or when the tag of the cache line is evicted from a FIFO queue. The main weakness of this idea is the mechanism that triggers the auto-invalidation, because the FIFO queues need to be sized properly for each workload and synchronization instructions can evict blocks needed in the next cycles.

Active Memory Operations [50] explore the idea of fine grained updates of AMOs. Unlike traditional Cache Coherent writes that require to invalidate sharers to achieve one private copy with read-and-write permission, the Active Memory Operations can modify the data without obtaining exclusive state. To maintain coherence the updates are sent to the directory which will forward the update to all the sharers with a local copy. This approach substitutes invalidations by update messages and reduces the writer-consumer latency. Although the approach is tested in some microbenchmarks, the impact of the optimization is unclear for real world applications.

Similarly, Sharing/Timing Adaptive Push [35] (STAP), is a complex dynamic mechanism that preemptively sends data from producers to consumers to minimize critical path communication latency. To do so, it detects three types of data sharing patterns: Producer-Consumer, Broadcast and Migratory Exclusive Ownership (a.k.a. cache-line ping-pong effect). These patterns are detected using additional and expensive hardware at the L1 and L3 caches, and performing extra communication between these two structures. The main advantage is that updates can be forwarded directly to consumers.

Even though NoCs have been adopted by the industry, core to core communication is transparent to programmers. A notable exception is the SW26010 (the Sunway TaihuLight processor [15]), which exposes the inter-core network to developers for better architecture scalability. pLock [42] is a fast lock designed for architectures that support Explicit inter-core Message Passing (EMP). pLock proposes two techniques: chaining lock, and hierarchical lock, both to reduce message count and mitigate network congestion. The chaining lock when a thread releases a lock instead of freeing it, the thread passes the lock to the next waiting client. The hierarchical lock removes slow long-distance communication using intermediate cores as local servers to avoid long-distance communication. Both ideas combined can reduce the amount of messages and the average latency of messages. However, instead of using cache coherent caches, EMP needs scratchpad caches, which are very complex to program.

MiSAR [29], is a minimalistic synchronization accelerator that is added to each L3 slice. The accelerator is designed to support the classic Pthread directives Mutex Lock/Unlock, Barriers and Conditional Variables through custom instructions. For example a LOCK instruction is always sent to the corresponding accelerator. In case the lock is free it returns a free message to the requester. If the lock is not available, the accelerator simply delays the response until the lock is freed. This prevents the requesting core's LOCK instruction from being committed, stalling its core until the lock is obtained. The biggest weakness apart from introducing extra instructions on the ISA, is that MiSAR assumes that there is no thread oversuscription or any other process running on the system and thus it can stall cores from committing instructions.

Another high level directive that is targeted in Carbon [25] is task scheduling. Carbon introduces hardware distributed task queues that implement task stealing. In this scheme, each thread has its own queue, where it enqueues a tasks. When the thread finishes executing a task and needs a new task to execute, it first looks at its own queue. When there is no task available in its own queue, it steals a task from one of the other queues.

Multi-Address atomic operations (MAD atomics) [17] are a set of individual instructions that achieve complexity-effective, non-speculative, non-deadlocking, fine-grained locking for multiple addresses. These instructions target the Dijkstra philosophers problem of taking several locks, giving a predefined order of acquiring the locks to avoid deadlocks based on the address of the variables.

Research has recently turn towards exploiting the capabilities of RMW updates. For example, COUP [49] presents an aggressive reordering of AMOs that exploit the commutativity of this type of operations. However, this approach requires support for Floating Point AMOs. RICH [13], presents a similar approach that targets OpenMP reductions, where the runtime is supposed to delimit which code blocks contain reduction functions, so the hardware is able to optimize them using a hierarchical reduction module present in the different levels of cache.

## Chapter 3

# **Experimental Framework**

This Chapter describes the methodology used to carry out our experiments and the workloads used as representative code of real world applications. It includes a short description of the machines we have used in the experiments. Moreover, we describe the simulation infrastructure used to model the different implementations of AMO and a discussion on the microarchitecture that is being simulated.

## 3.1 Methodology and Environment

In order to run our native and simulated experiments, we have developed a methodology that enables fair comparisons between machines and experiments. In this section, we will describe how we have set-up and run the experiments following that methodology. Moreover, to ensure the software stack and OS environment does not introduce any artifact, we have followed a rigorous set-up of the software environment, which is described in the following subsection. Finally, we close this section listing and describing the tools used in the characterization to understand the behaviour of some applications.

### 3.1.1 Methodology

The first step to fairly execute a benchmark natively or on a simulated machine is to define a Region-of-Interest (ROI). The ROI delimits which part of the application is going to be captured by the time measuring tools, tracing mechanisms or profiling tools. This way ROIs help us to characterize exactly the execution patterns of applications. Moreover, a good definition of the ROI is fundamental when we running an experiment

in a simulated machine because the cost of simulating extra cycles is very expensive. This is specially important for full system simulations, in which the system calls can generate noise in the results. Therefore, we have excluded from the ROI all the file system calls, data initialization and thread creation and destruction.

For the characterization of commercial multicore machines we have developed an automatic framework to carry out the experiments. The purpose of this framework is to launch all the experiments, pin the threads to physical cores and repeat the experiments several times. Thus, the results of the experiments are isolated from the noise of other processes running on the same system. Using the standard deviation obtained from the experiments we have fixed the amount of repetitions to 10 times. In the case of simulations we have conducted only one repetition due to simulation time restrictions.

Finally, in order to ensure the same conditions for all the experiments we have used the same binaries in all the experiments. This requirement is essential to avoid possible differences on the libraries available in the machines. Further details can be found in the next section.

#### 3.1.2 Software Environment

Since our test machines have different Kernel versions, OS distributions, library versions, and compilers installed, we have used a common environment to compile our applications. This environment is the same our simulator uses to run the applications along with the kernel and file system. We use Kernel 4.15.0 and an Ubuntu image of version 16.04.9.

To compile our applications we have used the Arm HPC compiler (version 20.1), a commercial compiler developed by Arm. We have opted for this compiler instead of GCC or CLANG based on previous results that demonstrate that the Arm HPC Compiler can generate well optimized code [41]. We also tested the benchmarks to verify that this premise is true.

For every benchmark we have compiled two binaries that contain two different set of instructions. On one hand, we have binaries that use exclusively LL/SC to implement locks, barriers, or atomic updates. On the other hand, we have binaries that only use AMOs for the same

| LL/SC | -march=armv8-a+nolse -pthread -static                                                |

|-------|--------------------------------------------------------------------------------------|

| AMO   | $-march{=}armv8{-}a{+}lse\ -lpthread\ -L/lib/aarch64{-}linux{-}gnu/atomics\ -static$ |

Table 3.1: Compiler flags used to obtain LL/SC and AMO binaries

primitives. In the case of libraries like POSIX, by default they are compiled to support only LL/SC. Therefore, we have recompiled those libraries forcing the use of AMOs. The flags we have used to get these binaries are listed on Table 3.1.

To verify that the generated code is free from instructions of the wrong type, in each binary we have used a postprocessing over the binary to disassembly it and then count the instructions of each type. We have also checked manually the assembly of some primitives like the CAS (see Listings 3.1 and 3.2).

| #0: | ldr    | x1, | [x4]   | # Load | Lock        | #0: | ldr  | x1, | [x4] | # | Load  | Lock    |   |

|-----|--------|-----|--------|--------|-------------|-----|------|-----|------|---|-------|---------|---|

|     | cbnz   | x1, | #0     | # Lock | != Zero     |     | cbnz | х1, | #0   | # | Lock  | ! = Zer | С |

| #1: | ldxr   | x2, | [x4]   | # Load | Lock        | #1: | mov  |     |      |   |       | = expec |   |

|     |        |     | x2, x1 | # Lock | unchanged   |     |      |     |      |   |       | Lock by | 1 |

|     | cbnz   |     |        | #      |             |     | cbnz | х2, | #0   | # | CAS ! | = Fail  |   |

|     |        |     |        |        | e 1 in Lock |     |      |     |      |   |       |         |   |

|     | cbnz · |     |        | # STX  |             |     |      |     |      |   |       |         |   |

| #3: | cbnz   | x2, | #0     | # LL = | 0           |     |      |     |      |   |       |         | " |

Figure 3.1: CAS implemented with Figure 3.2: CAS implemented with LL/SC AMO

Listing 3.1 shows the implementation of a CAS using only LL/SC instructions. Initially the code waits until the Lock variable is equal to 0 (lock is not busy) using a load and a conditional branch. When the Lock is released by other thread writing a 0 on it the CAS builtin tries to capture the lock. First, the thread reads with a LL (ldxr) the lock value, then performs an Exclusive OR and a conditional branch to check that the value did not change during the process. In case of a change, the function comes back to waiting until the value is zero again. Otherwise, the CAS builtin tries to write a 1 using a SC (stxr) instruction. Finally, the builtin checks that the SC did not fail and that the read value was zero with two conditional branches.

Listing 3.2 shows the same builtin using AMO instructions. Again, the

code starts waiting until the lock is released. Once the lock is free, the thread performs a CAS instruction, but first it needs to set the expected value in the destination register. This register is overwritten by the original value of the Lock before issuing the CAS. Thus, after issuing a CAS, the thread checks if the destination register contains a 0 that means that it succeeded.

#### 3.1.3 Tools

During our experiments, we have used several applications for different purposes, one of them is thread pinning. *Taskset* [30] is a simple Linux command that pins threads to physical cores. This is essential in our case because our test machines have multiple sockets that are visible to the OS, but we want to test only on a single chip.

Another tool we have used is *time* [31]. This tool apart from returning the execution time, performs a break down of the amount of CPU time spent in kernel mode, the percentage of the CPU used, the amount of memory used and the number of swap out of the process and number of page faults. This tool has been used as a sanity check, not as a time measuring tool.

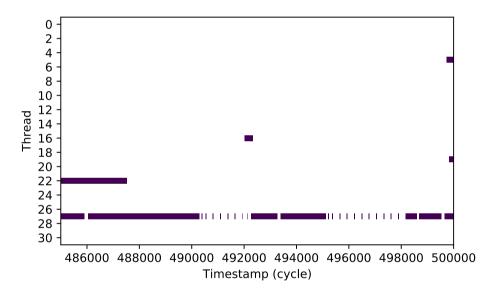

When performing a characterization just capturing the execution time and scalability of applications is insufficient to understand and obtain useful insights. Therefore, we have used *extrae* [11] tracing tool to dig into the behavior of applications. This tool creates trace files from the execution events captured during the execution. In this case we have used POSIX events for our traces. In order to visualize the traces we have used the trace visualization tool *paraver* [26]. We have used *paraver* also to visualize our custom made traces generated from simulator events.

## 3.2 Workloads

Workloads are a major concern when performing experiments, because the use of non representative applications can lead researchers to wrong conclusions. Therefore, we have selected the workloads following this criteria:

- Benchmarks should represent parallel and sequential patterns present in common and HPC applications (such as consumer-producer, group sync, etc).

- Benchmarks should allow a comparison of different synchronization directives implemented across multiple systems.

- Benchmarks should present different scalability patterns to study the effects of AMOs.

The best way accomplish these requirements was to use different benchmarks suites. This way, we decided to use one suite of microkernels named LockHammer [23] and Splash-3 [39] a popular parallel application suite.

#### 3.2.1 LockHammer

LockHammer [23] is a performance evaluation tool for locks, barriers and read-write locks, which can be used to characterize the performance of high core-count systems or compare different synchronization directives. Several basic primitives and well known lock implementations are included in the suite. Table 3.2 list the synchronization directives we have used in our experiments. This list includes a short description of the implemented directives we have tested.

The general structure of the micro-benchmark consists of a for loop that all threads execute in parallel. In the loop each thread tries to capture the lock, once acquired the thread executes a variable number of NOP instructions that represent the Critical Section (CS) of a program and then releases the lock. After releasing the lock the thread can execute again a parameterized number of NOP instructions, which represent the parallel section (PS). Thus, we can model different SC/PS ratios tweaking the number of NOP operations executed inside and outside the critical section. Note that the amount of CS increases with the number of threads instantiated, therefore this is a weak scaling application.

We have selected two configurations to simulate two different high contention scenarios. The first configuration named *serialized* because each thread executes 500 NOP instructions in the CS, and 0 NOP

### 3.2. WORKLOADS

| Synchronization Directive   | Abbreviation | Description                                                                                                                                                                                                                                                                                              |

|-----------------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Empty                       | Empty        | Null implementation of lock that simulates no synchronization cost                                                                                                                                                                                                                                       |

| CAS Lockref                 | CAS-Lock     | Basic spinlock implementation that<br>uses CAS instruction with 64 bit word                                                                                                                                                                                                                              |

| CAS RW Lock                 | CAS-RW       | Basic multiple reader lock that uses<br>CAS instruction to increment lock                                                                                                                                                                                                                                |

| Incdec Refcount             | IncDec-RW    | Shared incrementable counter                                                                                                                                                                                                                                                                             |

| Swap Mutex                  | Swap-Lock    | Basic spinlock implementation that uses SWAP instruction with 64 bit word                                                                                                                                                                                                                                |

| JVM Monitor                 | JVM-Lock     | Java virtual machine implementation of<br>a monitor for shared objects. Initial<br>phase tries to acquire the lock with<br>a Spin within a maximum number of<br>iterations. In case of failure, the thread<br>adds itself in a list of waiting threads<br>and stops on a pthread conditional<br>variable |

| Hybrid Spinlock             | HS-Lock      | Behaves like a normal spinlock at first,<br>in case of contended lock uses a back-off<br>strategy. Similar to Queued Spinlock<br>from Linux. The MCS Lock is used to<br>provide fairness, since is equivalent to<br>FIFO queue                                                                           |

| Hybrid Spinlock Fastdequeue | HSF-Lock     | Same as as Hybrid Spinlock with<br>special fast path for thread that acquire<br>the lock after waiting                                                                                                                                                                                                   |

| Optimistic Spin Queue Lock  | OSQ-Lock     | MCS like lock that uses spin relax instead of sleeping                                                                                                                                                                                                                                                   |

| Queued Spinlock             | Queued-Lock  | Extracted from Linux 4.13<br>implementation. Is a complex version<br>of the MCS Lock with several slowpaths                                                                                                                                                                                              |

| Ticket Spinlock             | Ticket-Lock  | Linux 4.13 spinlock that uses a shared counter to implement fair CS access                                                                                                                                                                                                                               |

| Event Mutex                 | MySQL-Lock   | MySQL 5.7 implementation of mutex.<br>Uses CAS instruction to obtain the<br>lock, an uses delays as back-off method                                                                                                                                                                                      |

| TBB Spin RW Mutex           | TBB-RW       | Threading Building Block Reader-<br>Writer lock, that is fast, unfair, with<br>back-off and writer-preference                                                                                                                                                                                            |

Table 3.2:

Lock description of LockHammer Micro-benchmark Suite

instructions in the PS. Therefore, all the work is done in the CS and all the work needs to be serialized (in the case of RW locks this is not true). With this configuration, on each thread acquisition, all threads in the system will fight to access the CS. However, one problem of this scenario is that the latency between L1 and L2 is not 0. Therefore, threads that release a lock will keep lock cache line in M state in the L1. Since the PS is 0 instructions and invalidations need some cycles to arrive from L2 to L1, threads that release a lock are able to gain the CS again. This happens more frequently in locks that have pauses or sleep directives.

There are some lock implementations that constantly read the variable to check if has been updated, like in spinlocks and RW locks. In these locks the problem is attenuate, because a thread can receive an invalidation just after gaining ownership of a cache line. So when releasing the lock, it might lose the ownership of the block.

Therefore, we have designed a second configuration that tries to avoid this problem. We named this configuration *unserialized* because it uses 250 NOP instructions in the CS and PS. Therefore, half of the work is now split in a parallel region, which is short enough to have high contention when using high number of threads. If we revisit the previous problem we see now that a thread releasing a lock, needs to execute 250 NOP instructions before trying to acquire again the lock. This creates a window of time big enough to wake up a sleeping thread and send a lock acquire that invalidates the cache line.

#### 3.2.2 Splash-3

Splash-2 [47] is a benchmark suite that comprehends different scientific applications. It was one of the first shared-address-space multiprocessing benchmarks that were publicly available. Soon, it became a reference for parallel application for two decades. Recently, an updated version (Splash-3 [39] has ported this benchmark suite to a modern C-language memory model and without data races. In Table 3.3 we can see all the applications present in this suite, a short description of them and the check list of synchronization directives used (barriers, mutexes or condition variables). By default Splash-3 uses Mutex, Semaphore and Condition Variables of the POSIX thread (pthread) library.

| Application    | Description                                                              | Barriers | Locks | Pauses |

|----------------|--------------------------------------------------------------------------|----------|-------|--------|

| BARNES         | N-body method                                                            | *        | *     | *      |

| CHOLESKY       | Sparse matrix factorization                                              | *        | *     | *      |

| $\mathbf{FFT}$ | 1-D Fast Fourier Transform                                               | *        |       |        |

| FMM            | Hierarchical N-body method                                               | *        | *     | *      |

| LU-C           | Dense matrix factorization with blocking                                 | *        |       |        |

| LU-NC          | Dense matrix factorization                                               | *        |       |        |

| OCEAN-C        | Optimized large-scale ocean<br>movement partial differential<br>equation | *        |       |        |

| OCEAN-NC       | Large-scale ocean movement<br>partial differential equation              | *        |       |        |

| RADIOSITIY     | Finite Element Method for scene rendering                                | *        | *     |        |

| RAYTRACE       | 3D raytracing scene rendering                                            | *        | *     |        |

| VOLREND        | 3D raycasting scene rendering                                            | *        | *     |        |

| WATER-NQ       | Watermoleculeforcecomputationusing $O(n^2)$ algorithm                    | *        | *     |        |

| WATER-SP       | Watermoleculeforcecomputationusing $O(n)$ algorithm                      | *        | *     |        |

Table 3.3:Application description and Synchronization directive list of the<br/>Splash-3 Benchmark Suite

Splash-3 features different predefined inputs to be executed in different scenarios. One of these default inputs consist on a big workload mean to be executed on multicores with big core counts named NATIVE. However, these inputs are not suitable for simulations since the CPU time that they consume can be enormous. Therefore, we have use one of the pre-defined inputs, which is several times smaller and it was mean to be used in simulators.

When performing our simulations we have observed that the use of Mutex locks from POSIX library can introduce variations in the experiments due to the variable sleep times. Two experiments with the same configuration, but some small changes in the kernel execution environment can lead to completely different execution times. This happens because we use a small computation time that is heavily affected by kernel interruptions. In order to reduce this variability we have decided to use POSIX spinlocks to implement locks in the simulations.

## 3.3 Tests Machines

To characterize the current synchronization instructions present in Arm based multicores, we have selected a group of machines that is representative of Server and HPC ecosystems: Huawei's Kunpeng 920 and AWS's Graviton 2.

#### 3.3.1 Kunpeng 920

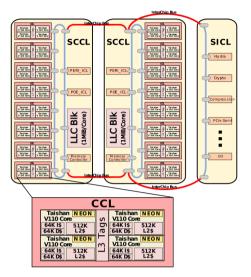

Huawei's Kunpeng 920-4826 is a 64-bit Armv8.2 server microprocessor developed by HiSilicon on 7nm. The multicore features 48 TaiShan v110 cores, a 4-way OoO core based on the Cortex-A72 that runs at 2.6 GHz. The chips uses a multi-die architecture to integrate such a big number of cores. Each die uses an internal ring NoC to interconnect cores [48] (see Figure 3.3 for the 64-core version diagram). Table 3.4 lists the cache hierarchy of the Kunpeng 920.

Kunpeng 920 supports Atomic Memory Operations included in the LSE extension of Armv8.2. Architectural details on how these instructions are supported are not disclosed.

Figure 3.3: Kunpeng 920 64-core mesh and die diagram [44].

#### 3.3.2 Graviton 2

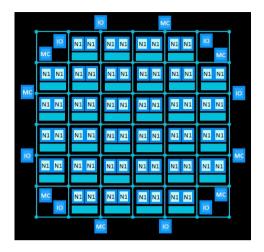

Graviton 2 is a custom multicore developed by Annapurna Labs exclusively for Amazon. Currently these multicores are used to power EC2 instances for Amazon Web Services. Graviton 2 is a 64-bit Armv8.2 multicore SoC that features 64 custom Neoverse N1 cores running at 2.5GHz. Neoverse cores are identical to the A76 architecture, featuring Out-of-Order(OoO or O3) execution with 11 stages, 4-way decode and 8-way issue. The 7nm multicore integrates these 64 cores through a CMN-600 mesh interconnection, which implements AMBA 5 Coherent Hub Interconnection (CHI) architecture at 2.0GHz (see Figure 3.4). Table 3.5 lists the cache hierarchy parameters of the Graviton 2.

Neoverse N1 cores support Large System Extension (LSE) as part of the Armv8.2 specs, which introduces AMOs in Armv8 ISA. As we have seen in section 2.3, atomic instructions to cacheable memory can be performed as either near atomics or far atomics, depending on where the cache line containing the data resides. The Neoverse N1 manual states:

• When an instruction hits in the L1 data cache in a unique state, then

| L1 Instruction Cache | Size<br>Block Size            | 64KiB<br>64-bytes            |  |

|----------------------|-------------------------------|------------------------------|--|

| L1 Data Cache        | Size<br>Block size<br>Type    | 64KiB<br>64-bytes<br>Private |  |

| L2 Cache             | Size<br>Associativity<br>Type | 512KiB<br>8-way<br>Private   |  |

| L3 Cache             | Size<br>Type                  | 48x1MiB<br>Shared and Sliced |  |

Table 3.4: Kunpeng 920 cache hierarchy [48].

| L1 Instruction Cache | Size<br>Associativity<br>Block Size                              | 64KiB<br>4-way<br>64-bytes                                                       |

|----------------------|------------------------------------------------------------------|----------------------------------------------------------------------------------|

| L1 Data Cache        | Size<br>Associativity<br>Block Size<br>Type<br>Latency           | 64KiB<br>4-way<br>64-bytes<br>Private<br>4 cycles                                |

| L2 Cache             | Size<br>Associativity<br>Block Size<br>Type<br>Policy<br>Latency | 1MiB<br>8-way<br>64-bytes<br>Private<br>Inclusive (only L1D) MESI<br>9/11 cycles |

| L3 Cache             | Size<br>Associativity<br>Type                                    | 32MiB<br>16-way<br>Shared and Sliced                                             |

Table 3.5: Graviton 2 cache hierarchy [3].

Figure 3.4: Graviton 2 64-core mesh diagram [5]. N1 boxes represent cores

it is performed as a near atomic in the L1 memory system. If the atomic operation misses in the L1 cache, or the line is shared with another core, then the atomic is sent as a far atomic on the core CHI interface.

• If the operation misses everywhere within the cluster, and the interconnect supports far atomics, then the atomic is passed on to the interconnect to perform the operation. When the operation hits anywhere inside the cluster, or when an interconnect does not support atomics, the L3 memory system performs the atomic operation. If the line it is not already there, it allocates the line into the L3 cache. This depends on whether the directory is configured with an L3 cache.

Alternatively, the Neoverse N1 manual specifies that the CPUECTLR system register can be programmed such that all atomic instructions execute as a near atomic. However, the programming of this register is restricted to firmware privilege level.

### 3.4 The gem5 Simulator

In order to model AMOs, we have selected gem5 [32] as our reference simulator. gem5 is one of the most popular cycle-accurate simulators used in computer architecture research. This simulation infrastructure allows researchers to model modern computer hardware systems in detail. One of the main features is its full-system mode that is capable of booting unmodified Linux-based Operating Systems (OS) and run full applications for multiple architectures including Armv8+.

However, the default gem5 package is not meant to simulate accurately cache hierarchies, cache coherence or NoCs. Therefore, gem5 features the Ruby cache model that specifically simulates these components. Ruby uses a domain-specific language that enables new definitions of coherence protocols. Recently Arm has published its CHI protocol for Ruby, partially based on the AMBA 5 CHI specification. This protocol supports LL/SC operations but does not support AMOs in any form. In Chapter 5 we will explain how we have modified gem5 in order to support AMOs in compliance with the AMBA 5 CHI protocol.

gem5 uses several configuration files to specify all the components that will be simulated. In this section, we will describe how we have configured all these parameters for our simulations.

#### 3.4.1 CPU Microarchitecture

In gem5, the basic building block is the CPU. There are four CPU models with different levels of detail and performance. For this work we have used the detailed model of an out-of-order CPU (O3). This model has several configuration files that can be tweak to model different architectures. In our case we have configured the O3 model with the same parameters the Arm Cortex X1 [45], a high performance core with wide and complex datapath that enhances single thread performance. Since we target next generation cores, we have introduce some modifications influenced by the recent Apple M1 [4]. We have increased the amount of resources of internal structures such as Reorder Buffer, Load-Store Queue, etc. These parameters are listed in Table 3.6

| Fetch              | 8-way                                                                                                                                                            |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Decode             | 8-way                                                                                                                                                            |

| Issue              | 14-way                                                                                                                                                           |

| Writeback          | 14-way                                                                                                                                                           |

| Commit             | 8-way                                                                                                                                                            |

| Instruction Window | 472 entries                                                                                                                                                      |

| Reorder Buffer     | 630 entries                                                                                                                                                      |

| Load-queue         | 154 entries                                                                                                                                                      |

| Store-queue        | 106  entries                                                                                                                                                     |

| Type of predictor  | Tournament                                                                                                                                                       |

| Size               | 8192 entries                                                                                                                                                     |

| BTB size           | 8192 entries                                                                                                                                                     |

| RAS size           | 64 entries                                                                                                                                                       |

| 2.5 GHz            |                                                                                                                                                                  |

|                    | Decode<br>Issue<br>Writeback<br>Commit<br>Instruction Window<br>Reorder Buffer<br>Load-queue<br>Store-queue<br>Type of predictor<br>Size<br>BTB size<br>RAS size |

Table 3.6: X1 gem5 configuration.

#### 3.4.2 Cache Hierarchy and NoC Configuration

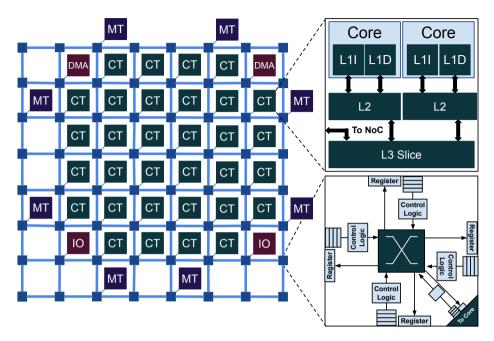

The architecture of Graviton 2 has inspired the way we have configured our multicore. The configuration file instantiates 64 cores with three levels of cache. The NoC layout is a square mesh of 8x8 crosspoints that runs at 2GHz. The latency of routing a packet and traversing a link is for both cases one cycle. Figure 3.5 depicts the actual shape of the mesh.

In each crosspoint there are two X1 cores, each connected to three private caches (Instruction L1, Data L1 and L2) and one slice of the shared distributed cache (L3) that works as a directory. The details of the caches are listed in Table 3.7. The L2 is fully inclusive with respect to the L1 and total amount memory is 64 MiB (1MiB per core). Meanwhile, the L3 is exclusive with a total of 64 MiB of memory (also 1 MiB per core). We have placed one prefetcher on each private cache based on some small tests done with the STREAM benchmark [37]. We have choosen High Bandwidth Memory 3 (HBM3) as the main memory technology. The chip has 8 channels of 64GB/s that sum up a total memory bandwidth of 512GB/s.

Figure 3.5: gem5 64-core mesh diagram. Boxes represent: Compute Tile (CT), Memory Tile (MT), Input Output device (IO), Direct Memory Access (DMA)

| Thread Count      | 1 - 8 - 16 - 32 - 64 threads          |

|-------------------|---------------------------------------|

| Deriverte         | L1I: 64KiB, 4-way, 2 cycles access    |

| Private<br>Caches | L1I Prefetcher: Next Line             |

| Caches            | L1D: 64KiB, 4-way, 3 cycles           |

|                   | L1D Prefetcher: Strided               |

|                   | L2: 1MiB, 8-way, 10 cycles            |

|                   | L2 Prefetcher: Best Offset Prefetcher |

| LLC and           | 2MiB, 8-way, 40-70 cycles             |

| HNF slice         | Cache Coherency: MOESI                |

| intri shee        | Exclusive                             |

| -                 | 8x8 mesh with 64 cores                |

| NoC               | 2GHz                                  |

| Main Memory       | 8 channels of 64GB/s each             |

Table 3.7: X1 Cache Hierarchy configuration.

## Chapter 4

# Characterization of Synchronization Primitives

This chapter presents and analyzes the results of the experiments performed in the tests machines. We employ the experimental infrastructure and the methodology explained in Section 3.1.1. First, we evaluate the LockHammer microbenchmark in which multiple locks and Read-Writer locks are tested. Then, we run the Splash-3 benchmark suite and analyze the scalability of the applications.

#### 4.1 LockHammer Characterization

In this section we present and analyze the results obtained executing the LockHammer microbenchmark on the Kunpeng 920 and the Graviton 2. We present three case studies for each machine.

In the first one, we plot the single thread execution time of all the lock implementations. The goal behind this experiment is to find out what is the latency of LL/SC and AMO instructions. Since kernels are run with a single thread pinned to a core, the memory block that contains the lock will always be placed in the L1 of that core. Thus, the execution time will be determined by how fast LL/SC or AMO instructions are executed. We use the *Empty* kernel, which does not implement any synchronization directive, to measure the overhead of each directive.

In the second one, the benchmark is executed with *serialized* configuration. As explained in section 3.2.1, this configuration executes each kernel maximizing the amount of cores that fight for capturing the lock and removes the parallel execution. This way the shared lock is highly contended. To run this experiment we have used one thread per

core (48 threads in Kunpeng 920 and 64 threads in Graviton 2).

Finally, we execute a third scenario in which we use *unserialized* configuration (see section 3.2.1 for further details). In this configuration the size of the parallel region and the critical section (CS) is equal. In this configuration the contention of the locks is lower, but we avoid that a single thread could access several times in a row the critical section.

#### 4.1.1 Kunpeng 920

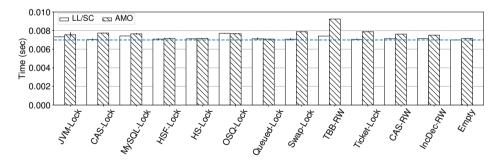

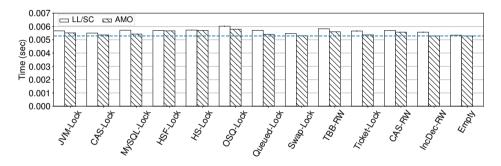

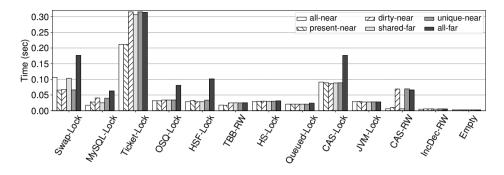

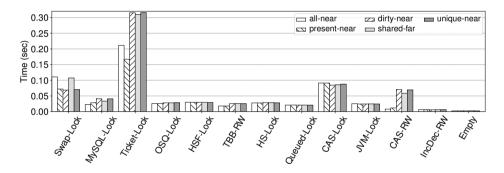

obtained the absolute execution First. we time all the lock implementations using only one thread (see Figure 4.1). The lowest execution time corresponds to Empty microkernel, in which locks are removed to check what is the ideal execution time. We have placed an horizontal line that corresponds the execution time of *Empty* microbenchmark. Thus, we can see what is the overhead of each lock with respect to the ideal execution with no synchronization instructions. In most LL/SC experiments, we see that the overhead is minimal except for the OSQ and MySQL locks. However, in 8 out of 12 kernels the overhead of AMO instructions is non negligible. We can conclude from these results that the AMOs have a higher delay than the LL/SC in Kunpeng 920.

Figure 4.1: Absolute execution time of LockHammer locks on Kunpeng 920 with 1 thread

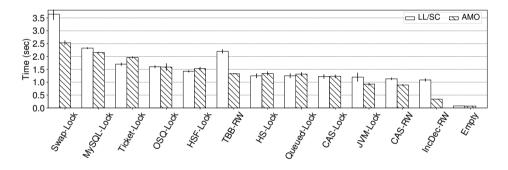

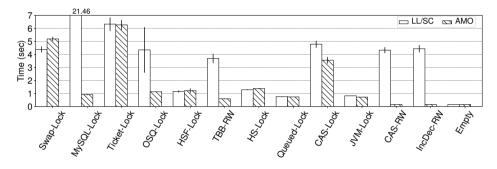

Next, we obtained the absolute execution time all the lock implementations using one thread per core (48 cores) and *serialized* configuration (see Figure 4.2). We execute each benchmark 10 times and represent the standard deviation using a vertical line on the top of each bar. Locks are sorted by the best execution time among LL/SC and AMOs versions. Thus, we know what is the best implementation of a lock for this specific machine. For Read-Write locks we can conclude that CAS-RW is the best implementation, while for classic locks JVM-Lock is the fastest. We can see that in both locks using AMOs speeds-up the execution of the benchmark. While 6 locks obtain speed-up when using AMOs, there are 4 locks (Ticket-Lock, HS-Lock, HSF-Lock and Queued-Lock) that are faster using LL/SC rather than AMOs.

Regarding the variability of the experiments we can see that AMO have lower variability than LL/SC instructions. This observation is noticeable in most RW locks (TBB-RW, CAS-RW, IncDec-RW) and some regular locks (MySQL-Lock, JVM-Lock). This characteristic may be of interest in Real Time systems to implement predictable synchronization mechanisms.

Figure 4.2: Absolute execution time of LockHammer locks on Kunpeng 920 with 48 threads using *serialized* configuration

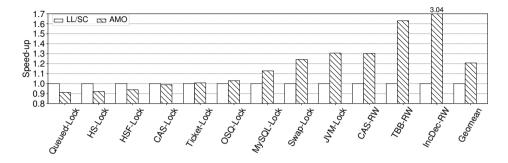

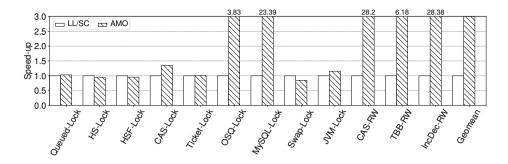

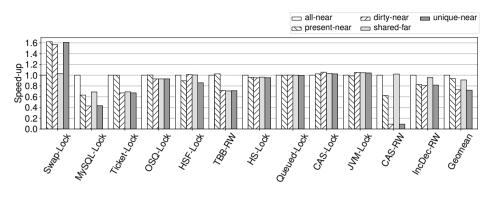

The performance difference between LL/SC and AMOs is different in every lock implementation. In order to measure how big is the difference between versions we have plotted Figure 4.3. This figure shows the relative speed-up of AMO versions normalized to LL/SC version using again 48 threads. We have sorted each lock implementation from the lowest to the highest speed-up. The highest speed-up is achieved when we implement a shared counter using AMOs, reaching a  $3.2\times$ . Next, Intel TBB fair RW-lock implementation achieves a  $1.67\times$ ; however, CAS-RW is faster in absolute execution time. Despite that both Swap-Lock and MySQL-Lock obtain more than  $1.15\times$ , these lock implementations are the slowest compared to the rest. Finally, JVM-Lock has speed-ups of  $1.3\times$ , which make it the fastest lock implementation.

Figure 4.3: Speed-up of LockHammer locks (w.r.t LL/SC version) on Kunpeng 920 with 48 threads using *serialized* configuration

Regarding slowdowns, all the Linux locks except OSQ-lock obtain between  $0.95 \times$  and  $0.86 \times$  slowdowns. Despite these locks are not the fastest implementations, they play an important role in the software stack. Therefore, these slowdowns can affect many applications that use the POSIX library. All these Linux locks use sleeps when they fail to acquire a lock after a number of tries. This way they enable a context switch of other threads that may free the requested lock. This also avoids pooling accesses to the mutex address that produce noise in the cache hierarchy. Hence, if the catch function is enhanced to execute faster, the lock can put to sleep the thread faster because it consumes faster its attempts.

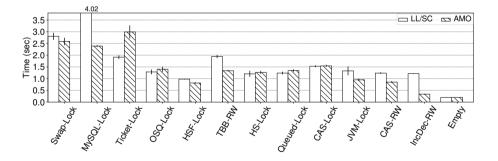

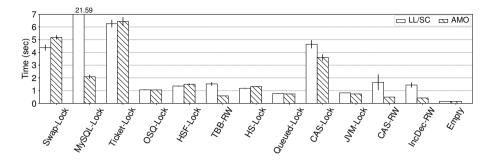

Finally, we execute our third set of experiments using one thread per core and the *unserialized* configuration (see Figure 4.4). In this case we have kept the axis size and the ordering of the benchmarks we have used in Figure 4.2. This way we can see how the execution time changes from *serialized* to *unserialized* configurations. Since the latter uses a CS that has half the workload, we observe a reduction in execution time for many benchmarks: Swap-Lock (only for LL/SC version), OSQ-Lock, HSF-Lock and TBB-RW (only for LL/SC version).

Nonetheless, three kernels increase their execution time because the thread releasing the lock cannot take advantage of having the memory block that contains the lock in the L1 to acquire it again. MySQL-Lock (specially in LL/SC version) and CAS-Lock are two of these locks that experience the slowdown. Both kernels have a fast path that tries to catch the lock with a CAS, while those that failed in the fast path are waiting a signal from the thread that releases the lock. Other lock implementations are not affected by this because they use a data structure to hold the threads that want to access the CS (like OSQ, HSF, HS, Queued or JVM). So, while the releasing thread updates the structure receives an invalidation. The third kernel that increases its execution time is Ticket-Lock. This kernel enforces that fairness using a FIFO order ticket. The increase of the execution time in this kernels is caused by the fight between the thread that is releasing the lock and other previous threads that are modifying the lock to get a new ticket.

With unserialized configuration, HSF-Lock is the fastest lock implementation because AMO version is faster than in *serialized*. But, the overall speed-up of AMOs over LL/SC is still  $1.2 \times$ .

Figure 4.4: Absolute execution time of LockHammer locks on Kunpeng 920 with 48 threads using *unserialized* configuration

Summarizing, AMOs obtain on average a  $1.2 \times$  speed-up with respect to LL/SC in both *serialized* and *unserialized* experiments with 48 threads. Whilst, AMO seems to outperform LL/SC for most locks, AMOs have a higher latency.

#### 4.1.2 Graviton 2

We perform the same experiments on the Graviton 2. We start with the absolute execution time of the different lock implementations with only one thread (see Figure 4.5). This time, we see how the trends reverse and LL/SC are more expensive than AMOs. However, the differences between these two versions are smaller. Moreover, Graviton 2 executes the experiments almost  $1.2 \times$  faster with respect to Kunpeng 920.

Figure 4.5: Absolute execution time of LockHammer locks on Graviton 2 with 1 thread

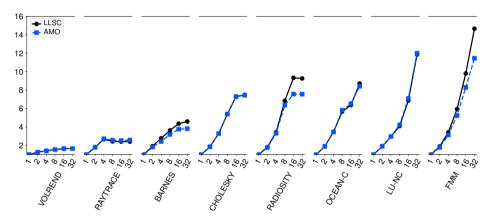

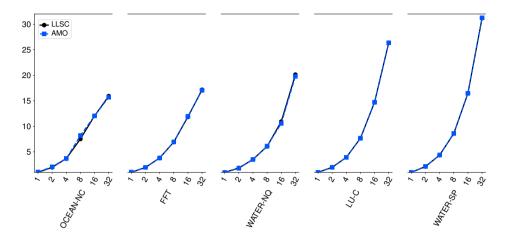

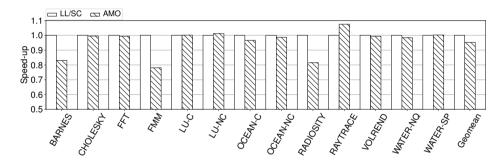

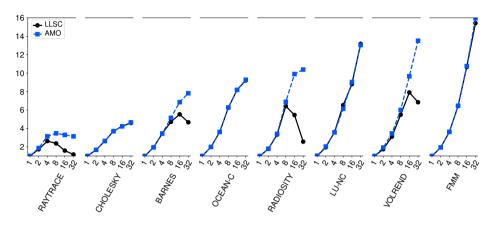

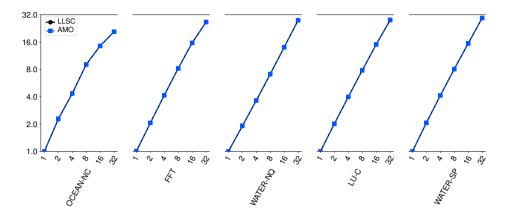

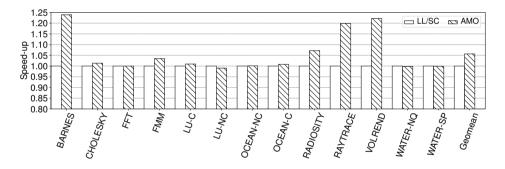

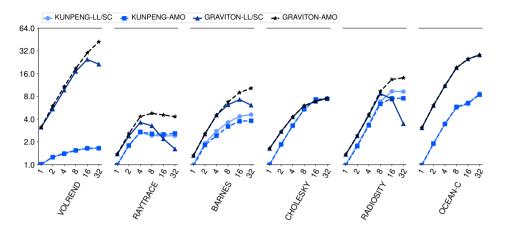

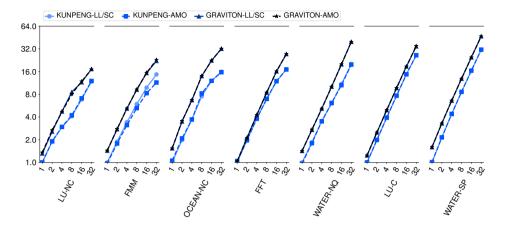

Figure 4.6 shows the absolute execution time of LockHammer benchmark using one thread per core with configuration one. Note that this time the number of threads used is 64. Again, locks are sorted using the order used in Figure 4.2. We can see that the results change dramatically from those observed in the Kunpeng 920. However, the fastest implementation for locks and RW-lock are the same (JVM-Lock and CAS-RW).