# Quasi Type-1 PLL With Tunable Phase Detector for Unbalanced and **Distorted Three-Phase Grid**

Ahmed, Hafiz; Tir, Zoheir; Verma, Anant Kumar; Elghali, Seifeddine Ben; Benbouzid, Mohamed

# **IEEE Transactions on Energy Conversion**

DOI: https://doi.org/10.1109/TEC.2021.3130492

E-pub ahead of print: 24/11/2021

Peer reviewed version

Cyswllt i'r cyhoeddiad / Link to publication

Dyfyniad o'r fersiwn a gyhoeddwyd / Citation for published version (APA): Ahmed, H., Tir, Z., Verma, A. K., Elghali, S. B., & Benbouzid, M. (2021). Quasi Type-1 PLL With Tunable Phase Detector for Unbalanced and Distorted Three-Phase Grid. *IEEE Transactions on* Energy Conversion. https://doi.org/10.1109/TEC.2021.3130492

Hawliau Cyffredinol / General rights Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

• Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal ?

Take down policy If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

## **GENERAL INSTRUCTIONS**

- Authors: Carefully check the page proofs (and coordinate with all authors); additional changes or updates WILL NOT be accepted after the article is published online/print in its final form. Please check author names and affiliations, funding, as well as the overall article for any errors prior to sending in your author proof corrections. Your article has been peer reviewed, accepted as final, and sent in to IEEE. No text changes have been made to the main part of the article as dictated by the editorial level of service for your publication.

- Authors: Please check ALL author names for correct spelling, abbreviations, and order of first and last name in the byline, affiliation footnote, and bios.

- Authors: We cannot accept new source files as corrections for your article. If possible, please annotate the PDF proof we have sent you with your corrections and upload it via the Author Gateway. Alternatively, you may send us your corrections in list format. You may also upload revised graphics via the Author Gateway.

- Authors: Please note that once you upload your changes, they will be entered and your article finalized. The proofing process is now complete and your article will be sent for final publication and printing. If you would like an additional proof to review, this should be noted as it is not IEEE policy to send multiple proofs. Once your article is posted on Xplore, it is considered final and the article of record. No further changes will be allowed at this point so please ensure scrutiny of your final proof.

- Authors: Unless invited or otherwise informed, a mandatory Excessive Article Length charges will be incurred if your article is over the page limit set by the society in the Information for Authors. If you have any questions regarding overlength page charges, need an invoice, or have any other billing questions, please contact reprints@ieee.org as they handle these billing requests.

# QUERIES

- Q1. Author: Please provide the name of the corresponding author.

- Q2. Author: Please confirm or add details for any funding or financial support for the research of this article.

- Q3. Author: Please check and confirm whether the author affiliations in the first footnote are correct as set.

- Q4. Author: Please provide the postal code for the affiliation of author Seifeddine Ben Elghali.

- Q5. Author: Please update Refs. [1] and [33].

# Quasi Type-1 PLL With Tunable Phase Detector for Unbalanced and Distorted Three-Phase Grid

Hafiz Ahmed<sup>®</sup>, Senior Member, IEEE, Zoheir Tir<sup>®</sup>, Senior Member, IEEE, Anant Kumar Verma<sup>®</sup>, Member, IEEE,

Seifeddine Ben Elghali<sup>®</sup>, and Mohamed Benbouzid<sup>®</sup>, Fellow, IEEE

Q1

2

Abstract-Out of various moving average filter (MAF)-based 5 phase-locked-loop (PLL), quasi type-1 PLL (QT1-PLL) is widely 6 adopted due to its fast dynamic performance, implementation 7 simplicity, and harmonics rejection abilities. However, the perfor-8 9 mance of QT1-PLL deteriorates in the presence of an off-nominal frequency unbalanced grid voltage component. Moreover, the 10 sensitivity towards the fundamental frequency negative sequence 11 (FFNS) component is high. Hence, this paper proposes a novel 12 13 enhanced QT1-PLL solution that is insensitive to unbalance in the grid voltage signal during off-nominal frequency conditions. 14 The proposed adaptive phase detector makes it possible to esti-15 mate both the fundamental frequency positive sequence (FFPS) 16 and FFNS components with a high degree of immunity against 17 harmonics. Notably, the pre-loop separation of the FFPS and the 18 FFNS components helps suppress the second harmonic oscillations 19 20 for improving the parameter estimation accuracy. The loop-filter design of QT1-PLL remains unaffected and requires a proportional 21 22 gain to estimate the fundamental phase and frequency information. 23 To address the DC offset issue, a modified delayed signal cancellation method is also proposed, which can theoretically eliminate 24 the DC offset for any arbitrary delay length. A small-signal model 25 26 of the proposed PLL is developed for the sake of stability analysis. Comparative numerical simulation and experimental results are 27 provided with various variants of QT1-PLLs to demonstrate the 28 29 performance improvement achieved with the proposed technique.

Index Terms—Phase locked-loop, delayed signal cancellation,

moving average filter.

Manuscript received June 15, 2021; revised October 9, 2021; accepted November 20, 2021. The work of H. Ahmed was supported through the Sêr Cymru Programme by Welsh European Funding Office (WEFO) under European Regional Development Fund (ERDF). The experimental part of the present work was supported by the General Directorate of Scientific Research and Technological Development through the Ministry of Higher Education and Scientific Research of Algeria under Grant A01L07UN390120180001. Paper

no. TEC-00636-2021. Hafiz Ahmed is with Nuclear Futures Institute, Bangor University, LL57 2DG

Bangor, U.K. (e-mail: hafz.h.ahmed@ieee.org).

Zoheir Tir is with LEVRES Laboratory, University of El Oued, El Oued 39000, Algeria (e-mail: tir-zoheir@univ-eloued.dz).

Anant Kumar Verma is with the Department of Electrical Engineering, National Institute of Technology Hamirpur, Hamirpur 177001, India (e-mail: anant\_verma12@hotmail.com).

Seifeddine Ben Elghali is with the UMR CNRS 7020 LIS, Aix-Marseille University, Marseille, France (e-mail: Seifeddine.BenElghali@lis-lab.fr).

Mohamed Benbouzid is with the UMR CNRS 6027 IRDL, University of Brest, 29238 Brest, France, and also with the Logistics Engineering College, Shanghai Maritime University, Shanghai 201306, China (e-mail: mohamed.benbouzid@univ-brest.fr).

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TEC.2021.3130492.

Digital Object Identifier 10.1109/TEC.2021.3130492

#### I. INTRODUCTION

THE penetration of grid-interfaced power electronic con-33 verters into traditional electric power grid is increas-34 ing day-by-day. They are used for various purposes such as 35 grid-integration of distributed energy resources [1]-[5], power 36 quality improvement [6], supplying domestic and industrial 37 loads [7], charging electric vehicles [8], to name a few. These 38 applications require grid-synchronous operation of the con-39 verter with the grid. This process is commonly known as grid-40 synchronization in the literature. Grid-synchronization necessi-41 tates the real-time extraction of unknown grid voltage parame-42 ters. As a result, a significant research attention has been given 43 to this problem in the last few decades. 44

Many fast, efficient, and accurate techniques are already 45 reported in the literature. Out of them, phase-locked loop 46 (PLL) [9]-[13] and it's various variants are particularly popu-47 lar. Traditional synchronous reference frame-PLL (SRF-PLL) 48 uses Park's transformation as the phase detector and uses a 49 proportional-integral low-pass filter to estimate the unknown 50 grid frequency and phase. The SRF-PLL has fast convergence 51 speed and good disturbance rejection capability. However, this 52 PLL is designed for a balanced grid i.e. only the fundamental 53 frequency positive sequence (FFPS) component is present. In 54 practice, especially at the distribution network level, the grid 55 often has a level of phase unbalance, e.g., more than 50% of the 56 800 low voltage substations in Cardiff, U.K. have serious phase 57 unbalance [14]. So, enhanced filtering capability is essential to 58 ensure efficient operation of PLL under the presence of phase 59 unbalance i.e. both FFPS and fundamental frequency negative 60 sequence (FFNS) components exist simultaneously. 61

In the presence of phase unbalance, the phase detector of SRF-62 PLL generates an undesirable double frequency components. To 63 eliminate the undesirable components, several solutions propose 64 the application of additional filtering stage(s) through pre-loop, 65 in-loop and a combination of both. In the case of pre-loop, filters 66 are applied in the stationary reference frame, i.e.,  $\alpha\beta$ -frame 67 where as in-loop filters are applied in the synchronous reference 68 frame, i.e., dq-frame. In the case of hybrid filtering, filters are 69 applied at both stationary and synchronous reference frames. 70

Some popular filters proposed in the literature are: delayed signal cancellation (DSC) [15]–[17], complex coefficient filter (CCF) [18], [19], moving average filter [20]–[24], orthogonal signal generator (OSG) filter such as second-order generalized integrator (SOGI) [25], adaptive notch filter (ANF) [26], to 75

See https://www.ieee.org/publications/rights/index.html for more information.

Q2

Q3

Q4

<sup>0885-8969 © 2021</sup> IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission.

name a few. In addition to the filter-based SRF-PLLs, multiple

reference frame-based SRF-PLLs such as double decoupled

SRF-PLL [27] are also popular in the literature.

79 Delayed signal cancellation (DSC) [15]–[17], [28] is a popular technique to eliminate the FFNS from the measured grid 80 voltages at the point of common coupling. In order to make 81 DSC-PLL immune to harmonics, multiple DSC operators are 82 used in cascade. So, prior information about the grid harmonics 83 is needed.. Moreover, in the case of off-nominal frequency 84 85 operation, frequency-adaptive DSCs are proposed [29]. This can potentially increase the computational complexity. By using 86 cross-coupling between two CCF, CCF-PLL [18], [19] can 87 extract grid-synchronized FFPS and FFNS components. CCF 88 is very suitable for selective harmonic elimination. However, 89 multiple CCFs are required to eliminate the effect of harmonics 90 which causes additional computational burden. 91

OSG-PLLs operate in the stationary reference frame, i.e., 92  $\alpha\beta$ -frame and uses OSGs to separate the FFPS and FFNS com-93 94 ponents followed by traditional SRF-PLL. OSGs typically have band-pass (cf. SOGI [25]) or notch (cf. ANF [26]) characteris-95 96 tics. To enhance the harmonic robustness of OSG-PLLs, multiple parallel OSGs are often recommended in the literature [30]. This 97 can be computationally complex. Moreover, discretization of 98 parallel OSGs is not straightforward, specially for high-order 99 100 harmonics. Multiple reference frame PLLs use multiple SRFs to separate the FFPS and FFNS components. In the case of 101 DDSRF-PLL, two cross-coupled reference frames operating at 102 opposite instantaneous phases are used. This helps to make the 103 PLL insensitive to FFNS components. However, the presence of 104 harmonics and/or DC-offset deteriorates the performance. This 105 106 necessitates the application of several reference frames where each operates at the relevant instantaneous phases. This kind 107 of structure is complex and not suitable for low-cost embedded 108 devices-based real-time implementation. 109

MAF-PLLs [20]-[24] provides an interesting solution to elim-110 inate the effect of harmonics and/or DC offset. Here, MAF is 111 used to eliminate the effect of FFNS component. Depending on 112 the MAF window length, MAF-PLL can be very effective to 113 block all harmonics and DC offset. However, this comes at the 114 cost of slow dynamic response [20]. To enhance the convergence 115 speed of MAF-PLL, quasi type-1-PLL (QT1-PLL) is proposed 116 in [21]. The QT1-PLL uses the idea of frequency-adaptive 117 demodulation [31]. An advantage of this approach is that 118 only a proportional loop-filter can estimate the unknown grid-119 frequency whereas proportional-integral loop filter is required 120 for conventional MAF-PLL. However, QT1-PLL is sensitive to 121 off-nominal FFNS component. Since, fundamental frequency 122 tuned MAFs are used in QT1-PLL, it cannot completely block 123 the FFNS component if they appear at off-nominal frequency 124 condition. To speed-up the convergence speed of QT1-PLL, hy-125 brid QT1-PLL (HQT1-PLL) [22] is proposed. In this case, DSC 126 127 operators are applied in the  $\alpha\beta$ -frame whereas MAF is applied in the dq-frame. However, fast dynamic response comes at the 128 cost of sacrificing the high phase margin. Moreover, HQT1-PLL 129 is also sensitive to off-nominal FFNS component. To reduce 130 the effect of off-nominal frequency FFNS component sensitivity 131 132 of QT1-PLL, total QT1-PLL (TQT1-PLL) is proposed in [24].

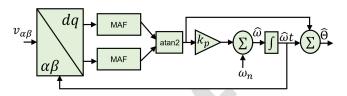

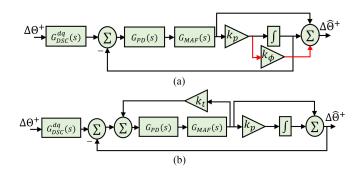

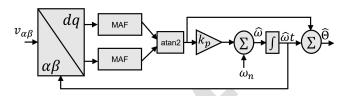

Fig. 1. Overview of QT1-PLL [21].

In this case, a third-order non-adaptive MAF is proposed. This 133 MAF has same window length as QT1-PLL but has significantly 134 lower steady-state errors in the presence of off-nominal FFNS 135 component. However, this comes at the cost of high sensitivity 136 to sub- and inter-harmonics. In [32], the authors have proposed 137 the application of all-pass filter (APF) [33] as the sequence 138 components separator for HQT1-PLL. Although this technique 139 can reduce the sensitivity, however, APF on its own has limited 140 filtering capability. This can be a limiting factor when the grid 141 voltage has inter- and/or sub-harmonics components. Similar 142 line of investigation is considered in [34] where third-order 143 generalized integrator is considered as the pre-loop filter. It is to 144 be noted here that none of the QT1-PLL techniques discussed 145 in this section can extract the FFNS component with high de-146 gree of harmonic immunity. This limits their application where 147 sequence extraction is important [35]. 148

Comparative analysis in [23] shows that out of various MAF-149 PLLs, QT1-PLL is very suitable for grid-connected converters. 150 This motivates the current work of improving the performance 151 of QT1-PLL. Our main objective is to use QT1-PLL for FFPS 152 and FFNS sequence extraction. For this purpose, an enhanced 153 phase detector is constructed in this work. This phase detector 154 can separate the FFPS and FFNS initial phase-angle and am-155 plitudes. Output of the phase detectors are passed through a 156 proportional loop-filter to estimate the unknown frequency and 157 instantaneous phase of the grid voltage. A small-signal model 158 is derived through analytical calculations and constructive gain 159 tuning procedures are developed for the proposed enhanced 160 QT1-PLL. Finally, the performance of the proposed technique 161 is verified through simulation and experiments on a PWM-162 controlled voltage source inverter. In contrast to the conventional 163 QT1-PLLs, the proposed approach is insensitive to off-nominal 164 FFNS component. Moreover, it can extract FFPS and FFNS 165 components unlike conventional QT1-PLLs. These are the main 166 contributions of this work. 167

The rest of this paper is organized as follows: Section II 168 summarizes the conventional QT1-PLL. Development of the 169 proposed enhanced QT1-PLL is given in Section III. Results and 170 discussions are given in Section IV. Finally, concluding remarks 171 are given in Section V. 172

#### II. QUASI TYPE-1 PLL: BRIEF OVERVIEW 173

This section summarizes the basic idea of the conventional 174QT1-PLL as proposed in [21]. Block diagram of the QT1-PLL 175 is given in Fig. 1. To analyze the phase detector of the QT1-PLL, 176 let us consider the three-phase grid voltages in  $\alpha$ ,  $\beta$ -frame as: 177

$$v_{\alpha}(t) = V \cos\left(\omega t + \phi\right), \tag{1}$$

$$v_{\beta}(t) = V \sin\left(\omega t + \phi\right), \qquad (2)$$

where the amplitude, angular frequency, and the initial phaseangle are given by V,  $\omega$ , and  $\phi$ , respectively. The instantaneous phase of the signals (1) and (2) is given by  $\Theta = \omega t + \phi \in$  $[0, 2\pi)$ . The voltages in (1) and (2) are converted into the synchronous reference frame (d, q) by applying the Park-type transformation and given by:

$$\begin{bmatrix} v_d \\ v_q \end{bmatrix} = \begin{bmatrix} \cos\left(\hat{\omega}t\right) & \sin\left(\hat{\omega}t\right) \\ -\sin\left(\hat{\omega}t\right) & \cos\left(\hat{\omega}t\right) \end{bmatrix} \begin{bmatrix} v_\alpha \\ v_\beta \end{bmatrix}.$$

(3)

From (3), the direct and quadrature-axis voltages can be rewritten as:

$$v_{d} = v_{\alpha} \cos\left(\hat{\omega}t\right) + v_{\beta} \sin\left(\hat{\omega}t\right),$$

$$= \frac{V}{2} \left[\cos\left\{\left(\omega - \hat{\omega}\right)t + \phi\right\} + \cos\left\{\left(\omega + \hat{\omega}\right)t + \phi\right\}\right]$$

$$+ \frac{V}{2} \left[\cos\left\{\left(\omega - \hat{\omega}\right)t + \phi\right\} - \cos\left\{\left(\omega - \hat{\omega}\right)t + \phi\right\}\right]. \quad (4)$$

$$v_{q} = v_{\beta} \cos\left(\hat{\omega}t\right) - v_{\alpha} \sin\left(\hat{\omega}t\right),$$

$$= \frac{V}{2} \left[\sin\left\{\left(\omega + \hat{\omega}\right)t + \phi\right\} + \sin\left\{\left(\omega - \hat{\omega}\right)t + \phi\right\}\right]$$

$$- \frac{V}{2} \left[\sin\left\{\left(\omega + \hat{\omega}\right)t + \phi\right\} - \sin\left\{\left(\omega - \hat{\omega}\right)t + \phi\right\}\right]. \quad (5)$$

In the quasi-locked condition i.e.  $\hat{\omega} \approx \omega$ , it can be assumed that  $\omega - \hat{\omega} \approx 0$ . Then, (4) and (5) can be simplified as:

$$v_d \approx V \cos\left(\phi\right). \tag{6}$$

$$v_q \approx V \sin\left(\phi\right). \tag{7}$$

188 It is to be noted here that only when  $\phi = \pm n\pi$ , n = 0, 1, 2, ...,189  $v_d \approx V$  and  $v_q \approx 0$  which is the same as the output of the phase 190 detector of SRF-PLL [9]. From (6) and (7), the initial phase-191 angle can be estimated as:

$$\hat{\phi} = \operatorname{atan2}\left(v_q, v_d\right),\tag{8}$$

192 where atan2 is the double quadrant arctangent function. In the above analysis, it is assumed that the grid is balanced and does 193 not contain any harmonics. In practice, the grid is unbalanced, 194 then, the FFNS component will appear as a double the funda-195 mental frequency component in (6) and (7). Similarly, odd-order 196 harmonics in the grid voltage will also appear as even-order 197 harmonics in (6) and (7). These high frequency components 198 will introduce ripple in the estimated phase-angle. Hence, the 199 frequency even-order AC components can be filtered out by us-200 ing a moving average filter (MAF) of window length,  $T_w = T/2$ , 201 where T is the period of the fundamental component. The 202 transfer function of the MAF in continuous and discrete-time 203 204 are given by

$$G_{MAF}(s) = \left(1 - e^{-T_w s}\right) / T_w s.$$

(9)

$$G_{MAF}(z) = \frac{1}{N} \frac{1 - z^{-N}}{1 - z^{-1}},$$

(10)

where  $N = T/T_s$  with  $T_s$  being the sampling period. There are three major issues that affect the performance of the standard QT1-PLL. Firstly, the phase detector part does not use any gain i.e. no design freedom. Secondly, off-nominal frequency208negative-sequence component will introduce high frequency rip-209ple in the estimated phase. Finally, it is not capable of extracting210the FFNS component. These issues will be addressed in the next211section.212

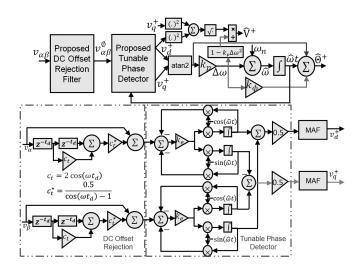

In this section, the proposed modifications are detailed. First, 214 the development of the proposed modified delayed signal cancellation (DSC) is detailed. Then, tunbale phase detector is given 216 followed by the small-signal model-based stability analysis and 217 tuning of the proposed PLL. For the remainder of this Section, 218 let us consider the unbalanced grid voltages in the  $\alpha\beta$ -frame 219 as: 220

$$v_{\alpha} = V_{\alpha}^{0} + V^{+} \cos(\omega t + \phi^{+}) + V^{-} \cos(\omega t + \phi^{-}), \quad (11)$$

$$v_{\beta} = V_{\beta}^{0} + V^{+} \sin(\omega t + \phi^{+}) - V^{-} \sin(\omega t + \phi^{-}), \quad (12)$$

where DC offsets are denoted by  $V_{\alpha}^{0}$  and  $V_{\beta}^{0}$ , the superscript + 221 and – indicate the positive- and negative-sequence component 222 and the remaining variables retain the same meaning as defined 223 in Section II. 224

# A. DC Offset Rejection 225

To reject DC offset, half-cycle DSC is a popular solution in the226literature [22], [24], [28], [32]. In this work, we are considering a227modified version of the DSC method for DC offset rejection. For228this purpose, let us consider the delayed versions of the signals229(11) and (12) as given below:230

$$v_l^{nt_d} = v_\alpha \left( t - nt_d \right), \tag{13}$$

for  $l \in \{\alpha, \beta\}$ , n = 1, 2 with  $t_d$  being the basic time delay. Let us denote the DC offset-free version of the signals (11) and (12) as  $v_{\alpha}^{\emptyset}$  and  $v_{\beta}^{\emptyset}$ . Then, these signals can be estimated using (11), (12), and (13) as given below: 234

$$v_l^{\emptyset} = v_l + \frac{0.5}{\cos(\omega t_d) - 1} \left( v_l - 2\cos(\omega t_d) v_l^{t_d} + v_l^{2t_d} \right).$$

(14)

Using (14), DC offset-free signals can be estimated using any 235 arbitrary amount of time-delay as opposed to the half-cycle delay 236 requirement of traditional DSC method. To implement (14), real-237 time information of the grid frequency  $\omega$  is required. However, 238 real-time frequency adaptation can complicate the modeling 239 and tuning process. As such, frequency-fixed version of (14) 240 is considered similar to [22], [24], [32] where the frequency  $\omega$ 241 is substituted by its nominal value. However, this will introduce 242 amplitude and phase attenuation in the off-nominal frequency 243 condition. So, compensation of these deviations need to be 244 considered. For this purpose, transfer function of the filter (14) 245 needs to be considered. Then, based on the developed transfer 246 function, quantification of the amplitude and phase attenuation 247 need to be studied. Filter (14) has the same transfer function of 248 convention half-cycle DSC if  $t_d = T/4$  is considered. For this 249 value of  $t_d$ , the total delay of the proposed DSC filter (14) is 250 the same as the standard DSC, i.e., T/2. As such, this value 251 of  $t_d$  is selected. For this value, transfer function of (14) in the 252

253 phasor-form is given by:

$$G_{DSC}^{\alpha\beta}(s) = \left(1 - e^{-2t_d s}\right)/2.$$

(15)

Let us consider that  $\omega = \omega_n + \Delta \omega$ , where  $\omega_n$  is the nominal value and  $\Delta \omega$  is the deviation. Then, the amplitude and phase of transfer function (15) can be found as [36]:

$$\left| G_{DSC}^{\alpha\beta}(s) \right| \approx 1 - k_v \left( \Delta \omega \right)^2, \tag{16}$$

$$\angle G_{DSC}^{\alpha\beta}(s) = -k_{\phi}\Delta\omega, \qquad (17)$$

where  $k_v = T^2/32$  and  $k_\phi = T/4$ . From (16) and (17), it is 258 clear that in the off-nominal frequency case, amplitude and 259 phase attenuation are characterized by  $k_v$  and  $k_{\phi}$ . As such, 260 261 compensation of these pre-loop filter induced attenuation need to be considered in the in-loop of the PLL. It is to pointed out here 262 that as a particular case of (14), convention half-cycle DSC filter 263 can be be obtained. However, unlike conventional DSC, (14) 264 can eliminates DC offset for any value of  $t_d$ . Moreover, despite 265 the transfer functions being equal for  $t_d = T/4$ , the dynamic 266 267 response is not the same for our DSC and the conventional counterpart. 268

Transfer function (15) in the dq-frame is given by:

$$G_{DSC}^{dq}(s) = \left(1 + e^{-2t_d s}\right)/2.$$

(18)

Transfer function (18) will be used for small-signal modelingpurpose later in Section III-C.

#### 272 B. Tunable Phase Detector

To develop the phase detector with tunable gain, let us consider the offset-free signal in (11) and (12), i.e.,  $v_{\alpha}^{\emptyset}$  and  $v_{\beta}^{\emptyset}$ . By applying basic trigonometric identities, expressions of  $v_{\alpha}^{\emptyset}$  and  $v_{\beta}^{\emptyset}$ can be expanded and rewritten into the parametric form as [37], [38]:

$$v_{\alpha}^{\emptyset} = \Omega_{\alpha}^{T} \theta_{\alpha}, \tag{19}$$

$$v^{\emptyset}_{\beta} = \Omega^T_{\beta} \theta_{\beta}, \qquad (20)$$

278 where

$$\Omega_{\alpha} = \Omega_{\beta} = \left[\cos\left(\omega t\right) \sin\left(\omega t\right)\right]^{T},$$

$$\theta_{\alpha} = \begin{bmatrix} \theta_{\alpha 1} \\ \theta_{\alpha 2} \end{bmatrix} = \begin{bmatrix} V^{+}\cos\left(\phi^{+}\right) + V^{-}\cos\left(\phi^{-}\right) \\ -V^{+}\sin\left(\phi^{+}\right) - V^{-}\sin\left(\phi^{-}\right) \end{bmatrix},$$

$$\theta_{\beta} = \begin{bmatrix} \theta_{\beta 1} \\ \theta_{\beta 2} \end{bmatrix} = \begin{bmatrix} V^{+}\sin\left(\phi^{+}\right) - V^{-}\sin\left(\phi^{-}\right) \\ V^{+}\cos\left(\phi^{+}\right) - V^{-}\cos\left(\phi^{-}\right) \end{bmatrix},$$

with the unknown parameter vectors being denoted by  $\theta_{\alpha}$ ,  $\theta_{\beta}$ while  $\Omega_{\alpha}$  and  $\Omega_{\beta}$  denote the known information vector. To estimate the unknown parameter vectors  $\theta_{\alpha}$  and  $\theta_{\beta}$  from the measured voltages  $v_{\alpha}$  and  $v_{\beta}$ , let us consider the estimated voltages as  $\hat{v}_{\alpha}^{\emptyset} = \Omega_{\alpha}^{T} \hat{\theta}_{\alpha}$  and  $\hat{v}_{\beta}^{\emptyset} = \Omega_{\beta}^{T} \hat{\theta}_{\beta}$ . Let us define the parameter vector estimation error as  $\tilde{\theta}_{\alpha} = \theta_{\alpha} - \hat{\theta}_{\alpha}$  and  $\tilde{\theta}_{\beta} = \theta_{\beta} - \hat{\theta}_{\beta}$ . Then, the output estimation error can be written as:

$$\tilde{v}^{\emptyset}_{\alpha} = v^{\emptyset}_{\alpha} - \hat{v}^{\emptyset}_{\alpha} = \Omega^T_{\alpha} \tilde{\theta}_{\alpha}.$$

(21)

$$\tilde{v}^{\emptyset}_{\beta} = v^{\emptyset}_{\beta} - \hat{v}^{\emptyset}_{\beta} = \Omega^T_{\beta} \tilde{\theta}_{\beta}.$$

(22)

Let us consider the following Lyapunov-like function with  $k_e > 0$ : 287

$$V\left(\tilde{\theta}_{\alpha},\tilde{\theta}_{\beta}\right) = \frac{1}{2}\left(\tilde{\theta}_{\alpha}^{T}k_{e}^{-1}\tilde{\theta}_{\alpha} + \tilde{\theta}_{\beta}^{T}k_{e}^{-1}\tilde{\theta}_{\beta}\right).$$

(23)

Time-derivative of (23) leads,

$$\dot{V} = -\tilde{\theta}^T_{\alpha} k_e^{-1} \dot{\hat{\theta}}_{\alpha} - \tilde{\theta}^T_{\beta} k_e^{-1} \dot{\hat{\theta}}_{\beta}.$$

(24)

Let us select the parameter vector update laws as:

$$\dot{\hat{\theta}}_{\alpha} = k_e \Omega_{\alpha} \tilde{v}_{\alpha}^{\emptyset}.$$

(25)

288

289

$$\hat{\theta}_{\beta} = k_e \Omega_{\beta} \tilde{v}^{\emptyset}_{\beta}.$$

(26)

By plugging in the update laws (25) and (26) into (24), one 290 can get that: 291

$$\dot{V} = -\left(\tilde{v}^{\emptyset}_{\alpha}\right)^2 - \left(\tilde{v}^{\emptyset}_{\beta}\right) \le 0.$$

This proves the boundedness of the parameter vector es-292 timation error. Parameter update laws (25) and (26) can be 293 used to extract the amplitude and phase angles. In obtaining 294 the update laws, it is assumed that the information vectors  $\Omega_{\alpha}$ 295 and  $\Omega_{\beta}$  are known *a priori*. In practice, the grid frequency is 296 unknown. In this case, an estimate of the grid frequency has 297 to be used. By considering the estimated grid frequency, the 298 unknown parameter estimation laws can be written in the scaler 299 form as: 300

$$\hat{\theta}_{\alpha 1} = k_e \cos\left(\hat{\omega}t\right) \tilde{v}_{\alpha}^{\emptyset}.$$

(27)

$$\hat{\theta}_{\alpha 2} = k_e \sin\left(\hat{\omega}t\right) \tilde{v}_{\alpha}^{\emptyset}.$$

(28)

$$\hat{\theta}_{\beta 1} = k_e \cos\left(\hat{\omega}t\right) \tilde{v}_{\beta}^{\emptyset}.$$

(29)

$$\hat{\theta}_{\beta 2} = k_e \sin\left(\hat{\omega}t\right) \tilde{v}_{\beta}^{\emptyset}.$$

(30)

From the estimated parameters, direct- and quadrature-axis 301 positive- and negative-sequence voltages can be obtained as: 302

$$v_d^+ = \frac{\hat{\theta}_{\alpha 1} + \hat{\theta}_{\beta 2}}{2}.$$

(31)

$$v_q^+ = \frac{\hat{\theta}_{\beta 1} - \hat{\theta}_{\alpha 2}}{2}.$$

(32)

$$v_{\overline{d}}^{-} = \frac{\hat{\theta}_{\alpha 1} - \hat{\theta}_{\beta 2}}{2}.$$

(33)

$$v_q^- = \frac{-\hat{\theta}_{\alpha 2} - \hat{\theta}_{\beta 1}}{2}.$$

(34)

Similar to QT1-PLL, estimated direct and quadrature-axis 303 positive- and negative-sequence voltages will also be passed 304 through MAF to enhance the harmonic robustness. Then, the amplitude and phase-angle of the positive- and negative-sequence 306 voltages can be obtained as: 307

$$\hat{V}^{+} = \sqrt{\left(v_{d}^{+}\right)^{2} + \left(v_{q}^{+}\right)^{2}}.$$

(35)

$$\hat{V}^{-} = \sqrt{\left(v_{d}^{-}\right)^{2} + \left(v_{q}^{-}\right)^{2}}.$$

(36)

$$\tilde{\phi}^+ = \operatorname{atan2}\left(v_q^+, v_d^+\right). \tag{37}$$

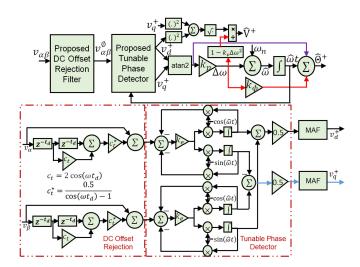

Fig. 2. Block diagram of the proposed enhanced QT1-PLL.

$$\hat{\phi}^- = \operatorname{atan2}\left(v_a^-, v_d^-\right). \tag{38}$$

Using (35)–(38) and the estimated  $\hat{\omega t}$ , FFPS and FFNS can easily be obtained. Block diagram of the proposed tunable phase detector based enhanced QT1-PLL for the FFPS case is given in Fig. 2.

### 312 C. Small-Signal Modeling and Tuning

313 1) Small-Signal Modeling: The considered parameter esti-314 mation technique described by (27)–(30) is nonlinear in nature 315 and not very suitable to find an analytical formula to tune the 316 phase detector gain  $k_e$ . To find an explicit gain tuning formula, 317 let us consider the FFPS phase-angle dynamics by using (37):

$$\dot{\hat{\phi}}^{+} = \frac{\dot{v}_{d}^{+} v_{q}^{+} - v_{d}^{+} \dot{v}_{q}^{+}}{\left(v_{d}^{+}\right)^{2} + \left(v_{q}^{+}\right)^{2}}.$$

(39)

318

$$\dot{\hat{\phi}}^{+} = \frac{\hat{V}^{+}\sin(\hat{\phi}^{+})(\dot{\hat{\theta}}_{\alpha 1} + \dot{\hat{\theta}}_{\beta 2}) - V^{+}\cos(\hat{\phi}^{+})(\dot{\hat{\theta}}_{\beta 1} - \dot{\hat{\theta}}_{\alpha 2})}{2\left(\hat{V}^{+}\right)^{2}}, \\ = \frac{k_{e}\sin(\hat{\Theta}^{+})\tilde{v}_{\alpha}^{\emptyset} - k_{e}\cos(\hat{\Theta}^{+})\tilde{v}_{\beta}^{\emptyset}}{2\hat{V}^{+}}, \\ = \frac{k_{e}V^{+}\sin(\Theta^{+} - \hat{\Theta}^{+})}{2\hat{V}^{+}} \\ + \frac{k_{e}\{\hat{V}^{-}\sin(\hat{\Theta}^{+} + \hat{\Theta}^{-}) - V^{-}\sin(\Theta^{-} + \hat{\Theta}^{+})\}}{2\hat{V}^{+}}.$$

(40)

By substituting (27)–(32) into (39), it can be found that:

In the quasi-locked condition,  $V^+ \approx \hat{V}^+$ ,  $V^- \approx \hat{V}^-$ ,  $\Theta^+ \approx \hat{\Theta}^+$ , and  $\Theta^- \approx \hat{\Theta}^-$ . In this case,  $\hat{V}^- \sin(\hat{\Theta}^+ + \hat{\Theta}^-) - V^- \sin(\hat{\Theta}^- + \hat{\Theta}^+) \approx 0$ . Moreover, by applying small-angle approximation formula, one can obtain that  $\sin(\Theta^+ - \hat{\Theta}^+) \approx (\Theta^+ - \hat{\Theta}^+) \approx \phi^+ - \hat{\phi}^+$ . Then, (40) can be simplified as:

$$\dot{\hat{\phi}}^+ \approx \frac{k_e}{2} (\Theta^+ - \hat{\Theta}^+),$$

$$\approx (k_e/2)(\phi^+ - \hat{\phi}^+).$$

(41)

From (41), the phase-angle transfer function can be obtained 324 as: 325

$$G_{PD}(s) = \hat{\phi}^+(s)/\phi^+(s) = 1/\tau_e s + 1,$$

(42)

where  $\tau_e = 2/k_e$ . From the transfer function (42), it is clear 326 that the considered phase detector has a first-order dynamics. 327 As such, the gain  $k_e$  can be tuned by using the formula: 328

$$k_e = 8\tau_s^{-1},\tag{43}$$

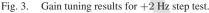

where  $\tau_s$  is the desired settling time. Using the transfer function 329 (42) and the block diagram of the proposed enhanced QT1-PLL 330 (*cf.* Fig. 2), the small-signal model can be obtained as shown in 512 Fig. 4. 332

2) *Tuning:* The proposed technique has three tuning parame-333 ters. They are: phase detector gain  $k_e$  and the frequency estimator 334 gain  $k_p$ . The proposed phase detector can be considered as the 335 observer while the loop-filter can be considered as the controller. 336 In traditional observer-based control system, the observer's con-337 vergence speed is typically selected as significantly faster than 338 the controller's convergence speed. Similar idea is considered 339 here also to tune the phase detector gain  $k_e$ . To tune this again, we 340 assume a quarter cycle convergence time i.e.  $\tau_s = T/4$ . With this 341 value of  $\tau_s$ , the phase detector gain can be found as  $k_e = 1600$ 342 from (43). 343

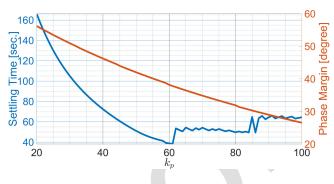

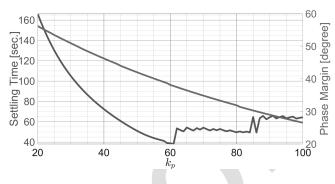

Finally, to tune the loop-filter parameter  $k_p$ , we have con-344 sidered settling time-based tuning approach similar to [22], 345 [24], [32]. For this purpose, frequency step test of +2 Hz is 346 considered. Then, the settling time (within 2% of the final value) 347 are calculated for different values of  $k_p$ . Results of the simulation 348 are given in Fig. 3. The lowest settling time is obtained for 349  $k_p = 61$ . As such, this value has been considered. This value 350 corresponds to a phase margin of  $\approx 37.8^{\circ}$  which is within the 351 widely accepted  $30^{\circ} - 60^{\circ}$  limit. 352

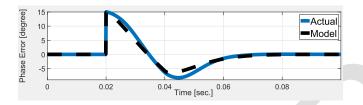

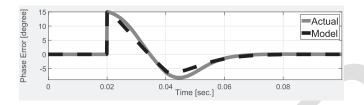

To validate the developed small-signal model and the tuning procedure, a validation test is performed. In this test, suddenly the grid voltage undergoes a  $+15^{\circ}$  phase-angle step change. Response of the model versus the actual estimator is given in Fig. 5. Result shows that the small-signal model developed in this section is fairly accurate to capture the nonlinear dynamics of the proposed technique. 359

Fig. 4. Small-signal model of the proposed enhanced QT1-PLL: (a) basic model and (b) alternative feedback representation with  $k_t = 1 + k_p k_{\phi}$ .

Fig. 5. Small-signal model validation for  $+15^{\circ}$  phase angle step change with  $k_e = 1600, k_p = 61, t_d = 0.005$  and  $T_w = 0.01$ .

TABLE I

CONTROL PARAMETERS OF THE SELECTED TECHNIQUES.

| Method            | QT1 | HQT1 | FH    | Proposed |

|-------------------|-----|------|-------|----------|

| $k_p$             | 64  | 81   | 61    | 61       |

| MAF Window Length | T   | T/2  | T/2   | T/2      |

| DSC Window Length | _   | T/2  | T/2   | T/2      |

| Phase Margin      |     | ≈    | 37.8° |          |

|                   |     |      |       |          |

### IV. RESULTS AND DISCUSSIONS

In this Section, performance of the proposed technique is 361 going to be investigated. Proposed technique is based on the 362 idea of QT1-PLL. As such QT1-PLL [21] and hybrid QT1-PLL 363 (HQT1-PLL) [22], and a recent variant of HQT1-PLL named 364 365 fast hybrid - PLL (FH-PLL) [32] are considered as comparison techniques. Control parameters are given in Table I. All four 366 techniques are implemented in Matlab/Simulink with a sampling 367 frequency of 10 kHz. 368

#### 369 A. Simulation Results

360

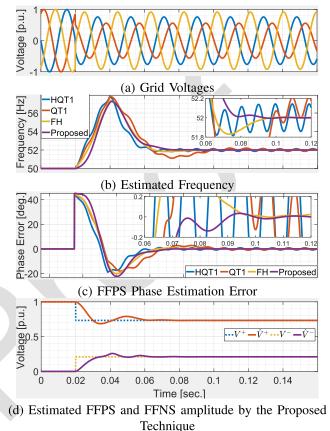

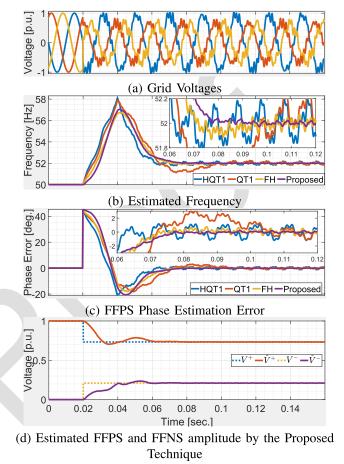

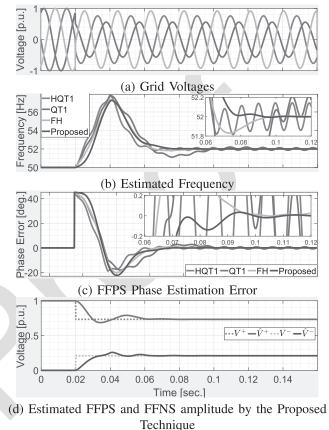

1) Test-I: Balanced to Off-Nominal Frequency Unbalanced 370 Grid: Effectiveness of the comparative techniques under unbal-371 anced fault at off-nominal frequency condition is tested in this 372 test. Pre-fault grid is made of  $V^+ = 1 \angle 0^\circ$ . Post-fault grid is com-373 posed of  $\overrightarrow{V}^{+1} = 0.733 \angle 45^{\circ}$  [p.u.] and  $\overrightarrow{V}^{-1} = 0.211 \angle -45^{\circ}$ 374 [p.u.] at f = 52 Hz. Simulation results are given in Fig. 6. 375 Results show that both FH-PLL and the proposed technique 376 have no steady-state oscillation in the steady-state parameters 377 whereas this is not the case for QT1- and HQT1-PLLs. In terms 378 of frequency estimation convergence time, the proposed tech-379 nique took 55 msec. to converge whereas FH-PLL took 68msec. 380

Item

Fig. 6. Test-I: Simulation results.

Similarly, the phase estimation error convergence time of the proposed technique was 6msec. faster compared to FH-PLL.The proposed technique was very rapid to estimate the amplitudes of FFPS and FFNS components as shown in Fig. 6(d). The convergence time is roughly two cycle which shows the effectiveness of the proposed method as a sequence extraction tool. 386

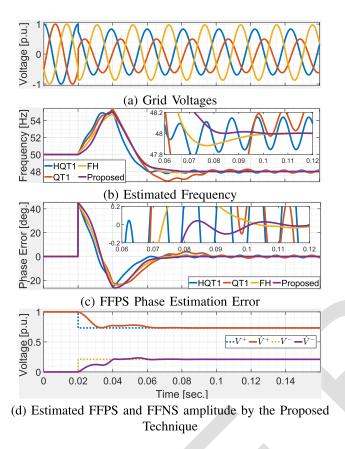

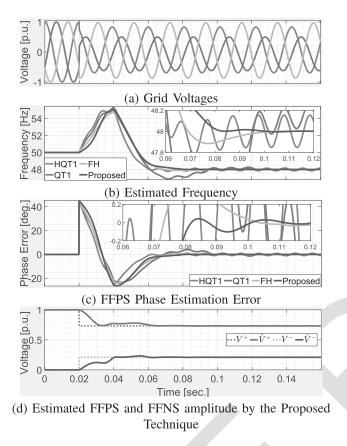

2) Test-II: Balanced to Off-Nominal Frequency Unbal-387 anced and Biased Grid: Here, the post-fault grid is com-388 posed of  $\overrightarrow{V}^{+1} = 0.733 \angle 45^{\circ}$  [p.u.] and  $\overrightarrow{V}^{-1} = 0.211 \angle -45^{\circ}$ 389 [p.u.] at f = 48 Hz. Moreover, unequal DC offsets of 390 0.07, 0.06, 0.05 p.u. are added in phase a, b, and c, respectively. 391 Simulation results for Test-II are shown in Fig. 7. Similar to 392 Test-I, steady-state values by QT1- and HQT1-PLLs are outside 393 the settling band. In terms of frequency estimation convergence 394 time, the proposed technique took 58msec. to converge whereas 395 FH-PLL took 12msec. more than the proposed technique. Sim-396 ilarly, the phase estimation error convergence time of the pro-397 posed technique was 14msec. faster compared to FH-PLL. 398

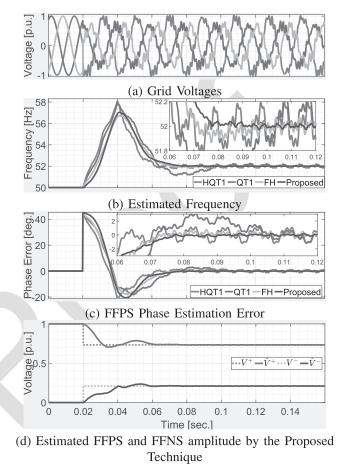

3) Test-III: Balanced to Off-Nominal Frequency Unbalanced and Distorted Grid: Here, the post-fault grid is composed of  $\overrightarrow{V}^{+1} = 0.733 \angle 45^{\circ}$  [p.u.] and  $\overrightarrow{V}^{-1} = 0.211 \angle -45^{\circ}$  401 [p.u.],  $\overrightarrow{V}^{+5} = 0.0625 \angle 45^{\circ}$ ,  $\overrightarrow{V}^{-5} = 0.0625 \angle -45^{\circ}$ ,  $\overrightarrow{V}^{-11} =$  402  $0.0625 \angle 180^{\circ}$ ,  $\overrightarrow{V}^{+13} = 0.0625 \angle -180^{\circ}$ , and 570 Hz interharmonics of  $0.0625 \angle 90^{\circ}$  at f = 52 Hz. Simulation results are given in Fig. 8. Results in this test are consistent with the previous two cases. Peak-to-peak oscillation in the estimated frequency 406

Fig. 7. Test-II: Simulation results.

by the proposed technique is 6 times higher for QT1-PLL 407 compared to the proposed technique. In case of phase estimation 408 error, the ratio is almost 4 times. Similar performance improve-409 ment by the proposed technqiue can also be seen compared to 410 FH-PLL. Total harmonic distortion is also the lowest for the 411 proposed technique. This is due to the fact that the MAFs are 412 used in all the comparative techniques, however, they are tuned at 413 the fundamental frequency. This makes the techniques sensitive 414 415 to frequency variation. However, the proposed technique is significantly less sensitive to same frequency condition despite 416 having the same fundamental frequency tuned MAFs. This is 417 due to the low-pass filter characteristics of the proposed phase 418 detector. This characteristics also helps to extract the FFPS and 419 420 FFNS amplitude with extremely low total harmonic distortion (THD) as can be seen in Fig. 8(d). Low THD sequence extraction 421 is very important to satisfy strict grid-integration standards for 422 distributed generation systems. 423

424 Comparative time-domain summary of the selected tech-425 niques are given in Table II.

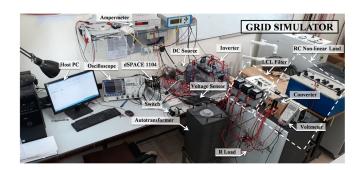

### 426 B. Experimental Results

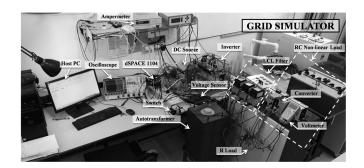

The experimental setup, shown in Fig. 9, is used to validate the

proposed enhanced QT1-PLL Here, a PWM-controlled threephase inverter is used to emulate the adverse grid voltage signal.

Three GW Instek GDP-100 high voltage differential probe are

used to measure the voltages at the load-side. Parameters of the

emulator are given in Table III.

Fig. 8. Test-III: Simulation results.

Fig. 9. Test setup.

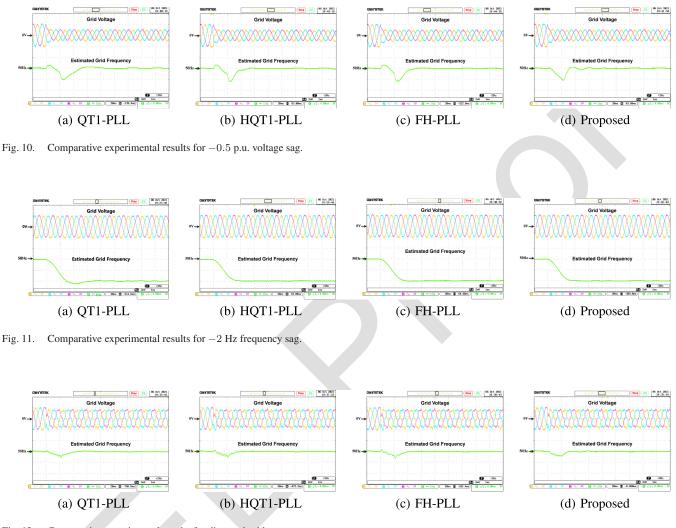

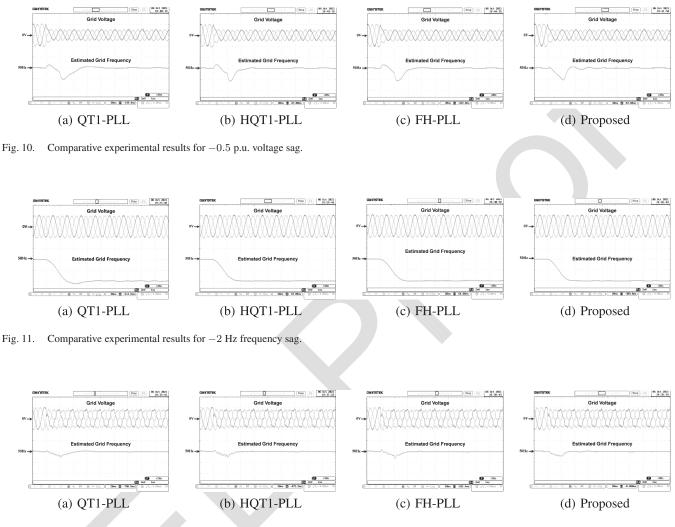

In the first test, a symmetrical voltage sag of 0.5 p.u. is considered. Performances of the comparative techniques are given in Fig. 11. Results show that the proposed technique and QT1-PLL had a peak overshoot of  $\approx$  1 Hz while it is  $\approx$  1.15 Hz for HQT1- and FH-PLLs. Frequency estimated by the proposed technique returns back to the nominal value in roughly 2 cycles whereas it is slightly higher for the other techniques. 433

In the second test, -2 Hz frequency sag is considered. Performance of the comparative techniques are given in Fig. 10. 441 Except QT1-PLL, the other techniques have first-order response. 442 Although the dynamic responses are similar, the proposed technique show less sensitivity to switching and measurement noises 444

Fig. 12. Comparative experimental results for distorted grid.

TABLE II

Comparative Summary of the Selected Techniques.

|                                                 | QT1  | HQT1 | FH   | Proposed |

|-------------------------------------------------|------|------|------|----------|

| Test-I: Balanced to Unbalanced Grid             |      |      |      |          |

| Settl. Time $(\pm 0.04 \text{Hz})$ (msec.)      | NA   | NA   | 68   | 55       |

| Frequency Overshoot                             | 5.78 | 5.83 | 5.34 | 5.25     |

| Settl. Time $(\pm 0.1^{\circ})$ (msec.)         | NA   | NA   | 71   | 65       |

| Test-II: Balanced to Unbalanced and Biased Grid |      |      |      |          |

| Settl. Time $(\pm 0.04 \text{Hz})$ (msec.)      | NA   | NA   | 70   | 58       |

| Frequency Overshoot (Hz)                        | 7.4  | 7.15 | 6.8  | 7        |

| Settl. Time $(\pm 0.1^{\circ})$ (msec.)         | NWB  | NWB  | 74   | 60       |

| Test-III: Distorted Grid                        |      |      |      |          |

| Oscillation (pk-pk) (Hz)                        | 0.27 | 0.35 | 0.14 | 0.04     |

| Oscillation (pk-pk) (°)                         | 1.55 | 2.2  | 0.96 | 0.41     |

| THD (%) (Grid - 23.84%)                         | 0.79 | 1.11 | 0.37 | 0.19     |

|                                                 |      |      |      |          |

NA - Not applicable as the steady-state value is outside of the band

TABLE III System Parameters.

| Parameter        | Value                                                     |

|------------------|-----------------------------------------------------------|

| DC-Link voltage  | $V_{dc} = 310 V$                                          |

| Inverter voltage | 110 V (rms)                                               |

| LCL filter       | Inverter and load side $L = 3 \text{ mH}, C = 84 \ \mu F$ |

| Inverter rating  | 20 kVA                                                    |

| Frequency        | Sampling and Switching: 10 kHz                            |

| Load parameter   | R = 167  Ohm                                              |

compared to the other techniques. As all the techniques are tuned445using phase margin, dynamic responses will be similar. How-446ever, the presence of low-pass filter-like phase detector makes447the proposed technique less sensitive to off-nominal frequency448components and/or various noises.449

In the final test, suddenly diode rectifier which is a highly 450 nonlinear load is added to generate distorted grid. Performance 451 of the comparative techniques are given in Fig. 12. The proposed technique had a peak overshoot of 0.4 Hz while it is 453 0.5 Hz, 0.55 Hz and 0.6 Hz for QT1-, HQT1-, and FH-PLL, 454

respectively. Moreover, the proposed technique's steady-state accuracy is also better than the comparative techniques due to the presence of low-pass filter-like phase detector.

Experimental results in Figs. 10–12 show that the proposed

technique has very good dynamic performance and high steadystate accuracy. These results validate the performance of the

proposed PLL.

#### V. CONCLUSION

462

478

483

This paper proposed an enhanced QT1-PLL that eliminates 463 464 the limitation of conventional QT1-PLLs. The proposed technique uses a novel enhanced phase detector that can separate the 465 FFPS and FFNS components. This makes the proposed tech-466 nique insensitive to off-nominal FFNS component. Moreover, a 467 468 novel DC offset rejection filter is also proposed. A systematic procedure for small-signal modeling and tuning is provided for 469 470 the proposed PLL. Comparative performance analysis using various challenging test scenarios showed that the proposed 471 technique is very suitable for unbalanced and distorted grid. 472 It has fast convergence speed, high degree of immunity to grid 473 abnormalities and it is easy to tune and implement. Thanks to the 474 475 FFPS and FFNS extraction capabilities, the proposed PLL is a very suitable candidate to be used as a grid-synchronization tool 476 inside fault-tolerant controller of grid-connected converters. 477

#### ACKNOWLEDGMENT

Hafiz Ahmed would like to acknowledge Dr. Denis Efimov

and Dr. Rosane Ushirobira from Inria, Lille, France for their

helpful comments and discussions on the development of the

DC offset rejection filter used in this work.

REFERENCES

- V. R. Chowdhury and J. W. Kimball, "Internal model based grid voltage estimation and control of a three-phase grid connected inverter for PV application," *IEEE Trans. Energy Convers.*, to be published, doi: 10.1109/TEC.2021.3079908.

- [2] M. Aourir, A. Abouloifa, I. Lachkar, C. Aouadi, F. Giri, and J. M. Guerrero,

"Nonlinear control and stability analysis of single stage grid-connected

photovoltaic systems," *Int. J. Elect. Power Energy Syst.*, vol. 115, 2020,

Art. no. 105439.

- Q5 492 [3] F. Benyamina, A. Benrabah, F. Khoucha, M. F. Zia, Y. Achour, and M. Benbouzid, "An augmented state observer-based sensorless control of grid-connected inverters under grid faults," *Int. J. Elect. Power Energy Syst.*, vol. 133, 2021, Art. no. 107222.

- 496 [4] F. Chishti, S. Murshid, and B. Singh, "Weak grid intertie WEGS with hybrid generalized integrator for power quality improvement," *IEEE Trans.*498 *Ind. Electron.*, vol. 67, no. 2, pp. 1113–1123, Feb. 2020.

- 499 [5] M. E. Meral and D. Çelík, "A comprehensive survey on control strategies

500 of distributed generation power systems under normal and abnormal

501 conditions," *Annu. Rev. Control*, vol. 47, pp. 112–132, 2019.

- [6] M. Kashif, M. Hossain, F. Zhuo, and S. Gautam, "Design and implementation of a three-level active power filter for harmonic and reactive power compensation," *Electr. Power Syst. Res.*, vol. 165, pp. 144–156, 2018.

- 505 [7] Ó. Lucia, L. A. Barragan, J. M. Burdio, O. Jimenez, D. Navarro, and I. Urriza, "A versatile power electronics test-bench architecture applied to domestic induction heating," *IEEE Trans. Ind. Electron.*, vol. 58, no. 3, pp. 998–1007, Mar. 2011.

- 509 [8] D. Mishra, B. Singh, and B. Panigrahi, "Adaptive current control for a

510 Bi-directional interleaved EV charger with disturbance rejection," *IEEE*511 *Trans. Ind. Appl.*, vol. 57, no. 4, pp. 4080–4090, Jul./Aug. 2021.

- 512 [9] V. Kaura and V. Blasko, "Operation of a phase locked loop system under distorted utility conditions," *IEEE Trans. Ind. Appl.*, vol. 33, no. 1, pp. 58–63, Jan./Feb. 1997.

- [10] F. Sadeque, J. Benzaquen, A. Adib, and B. Mirafzal, "Direct phase-angle detection for three-phase inverters in asymmetrical power grids," *IEEE Trans. Emerg. Sel. Top. Power Electron.*, vol. 9, no. 1, pp. 520–528, Feb. 2021.

[11] H. Chaoui, O. Okoye, and M. Khayamy, "Grid synchronization phase-519

- [11] H. Chaoui, O. Okoye, and M. Khayamy, "Grid synchronization phaselocked loop strategy for unbalance and harmonic distortion conditions," *J. Control, Automat. Elect. Syst.*, vol. 27, no. 4, pp. 463–471, 2016.

- [12] M. E. Meral and D. Çelik, "Benchmarking simulation and theory of various PLLs produce orthogonal signals under abnormal electric grid conditions," *Electr. Eng.*, vol. 100, no. 3, pp. 1805–1817, 2018.

- [13] S. Shah, P. Koralewicz, V. Gevorgian, and L. Parsa, "Small-signal modeling and design of phase-locked loops using harmonic signal-flow graphs," *IEEE Trans. Energy Convers.*, vol. 35, no. 2, pp. 600–610, Jun. 2020.

- [14] K. Ma, L. Fang, and W. Kong, "Review of distribution network phase unbalance: Scale, causes, consequences, solutions, and future research directions," *CSEE J. Power Energy Syst.*, vol. 6, no. 3, pp. 479–488, 2020.

- [15] M. Rasheduzzaman and J. W. Kimball, "Modeling and tuning of an improved delayed-signal-cancellation PLL for microgrid application," *IEEE Trans. Energy Convers.*, vol. 34, no. 2, pp. 712–721, Jun. 2019.

- [16] Q. Huang and K. Rajashekara, "An improved delayed signal cancellation PLL for fast grid synchronization under distorted and unbalanced grid condition," *IEEE Trans. Ind. Appl.*, vol. 53, no. 5, pp. 4985–4997, Sep./Oct. 2017.

- [17] H. A. Hamed, A. F. Abdou, E. H. Bayoumi, and E. El-Kholy, "Frequency adaptive CDSC-PLL using axis drift control under adverse grid condition," *IEEE Trans. Ind. Electron.*, vol. 64, no. 4, pp. 2671–2682, Apr. 2017.

- [18] M. Ramezani, S. Golestan, S. Li, and J. M. Guerrero, "A simple approach to enhance the performance of complex-coefficient filter-based PLL in grid-connected applications," *IEEE Trans. Ind. Electron.*, vol. 65, no. 6, pp. 5081–5085, Jun. 2018.

- [19] Y. Terriche, S. Golestan, J. M. Guerrero, and J. C. Vasquez, "Multiplecomplex coefficient-filter-based PLL for improving the performance of shunt active power filter under adverse grid conditions," in *Proc. IEEE Power Energy Soc. Gen. Meeting*, 2018, pp. 1–5.

- [20] F. D. Freijedo, J. Doval-Gandoy, O. Lopez, and E. Acha, "Tuning of phaselocked loops for power converters under distorted utility conditions," *IEEE Trans. Ind. Appl.*, vol. 45, no. 6, pp. 2039–2047, Nov./Dec. 2009.

- [21] S. Golestan, F. D. Freijedo, A. Vidal, J. M. Guerrero, and J. Doval-Gandoy, "A quasi-type-1 phase-locked loop structure," *IEEE Trans. Power Electron.*, vol. 29, no. 12, pp. 6264–6270, Dec. 2014.

- [22] S. Golestan, J. M. Guerrero, A. M. Abusorrah, and Y. Al-Turki, "Hybrid synchronous/stationary reference-frame-filtering-based PLL," *IEEE Trans. Ind. Electron.*, vol. 62, no. 8, pp. 5018–5022, Aug. 2015.

- [23] M. Hamouda *et al.*, "A comparative study and evaluation of improved MAF-PLL algorithms," *Int. J. Renewable Energy Res.*, vol. 7, no. 1, pp. 88–95, 2017.

- [24] M. S. Mellouli, M. Hamouda, J. B. H. Slama, and K. Al Haddad, "A thirdorder MAF based QT1-PLL that is robust against harmonically distorted grid voltage with frequency deviation," *IEEE Trans. Energy Convers.*, vol. 36, no. 3, pp. 1600–1613, Sep. 2021.

- [25] P. Rodriguez, R. Teodorescu, I. Candela, A. V. Timbus, M. Liserre, and F. Blaabjerg, "New positive-sequence voltage detector for grid synchronization of power converters under faulty grid conditions," in *Proc. 37th IEEE Power Electron. Specialists Conf.*, 2006, pp. 1–7.

- [26] S.-Y. Jung and K. Nam, "PMSM control based on edge-field hall sensor signals through ANF-PLL processing," *IEEE Trans. Ind. Electron.*, vol. 58, no. 11, pp. 5121–5129, Nov. 2011.

- [27] P. Rodríguez, J. Pou, J. Bergas, J. I. Candela, R. P. Burgos, and D. Boroyevich, "Decoupled double synchronous reference frame PLL for power converters control," *IEEE Trans. Power Electron.*, vol. 22, no. 2, pp. 584–592, Mar. 2007.

- [28] F. Sevilmiş and H. Karaca, "Implementation of enhanced non-adaptive cascaded DSC-PLLs for renewable energy systems," *Int. J. Elect. Power Energy Syst.*, vol. 134, 2022, Art. no. 107470.

- [29] S. Gude and C.-C. Chu, "Three-phase PLLs by using frequency adaptive multiple delayed signal cancellation prefilters under adverse grid conditions," *IEEE Trans. Ind. Appl.*, vol. 54, no. 4, pp. 3832–3844, Jul./Aug. 2018.

- [30] P. Rodríguez, A. Luna, I. Candela, R. Mujal, R. Teodorescu, and F. Blaabjerg, "Multiresonant frequency-locked loop for grid synchronization of power converters under distorted grid conditions," *IEEE Trans. Ind. Electron.*, vol. 58, no. 1, pp. 127–138, Jan. 2011.

- [31] H. Ahmed, S. Biricik, and M. Benbouzid, "Enhanced frequency adaptive demodulation technique for grid-connected converters," *IEEE Trans. Ind. Electron.*, vol. 68, no. 11, pp. 11053–11062, Nov. 2021.

520

521

522

523

524

525

526

527

528

529

530

531

532

533

534

535

536

537

538

539

540

541

542

543

544

545

546

547

548

549

550

551

552

553

554

555

556

557

558

559

560

561

562

563

564

565

566

567

568

569

570

571

572

573

574

575

576

577

578

579

580

581

582

583

584

585

586

587

588

- [32] F. Sevilmiş and H. Karaca, "A fast hybrid PLL with an adaptive all-pass filter under abnormal grid conditions," *Electr. Power Syst. Res.*, vol. 184, 2020, Art. no. 106303.

- [33] S. Gautam, W. Xiao, D. D.-C. Lu, H. Ahmed, and J. M. Guerrero, "Development of frequency-fixed all-pass filter based single-phase phase-locked loop," *IEEE Trans. Emerg. Sel. Top. Power Electron.*, to be published, doi: 10.1109/JESTPE.2021.3085124.

- [34] F. Sevilmiş and H. Karaca, "An advanced hybrid pre-filtering/in-loop-filtering based PLL under adverse grid conditions," *Eng. Sci. Technol., Int. J.*, vol. 24, no. 5, pp. 1144–1152, Oct. 2021.

- [35] L. B. Larumbe, Z. Qin, and P. Bauer, "On the importance of tracking

the negative-sequence phase-angle in three-phase inverters with double

synchronous reference frame current control," in *Proc. IEEE 29th Int. Symp. Ind. Electron.*, 2020, pp. 1284–1289.

- [36] S. Golestan, F. D. Freijedo, A. Vidal, A. G. Yepes, J. M. Guerrero, and

J. Doval-Gandoy, "An efficient implementation of generalized delayed

signal cancellation PLL," *IEEE Trans. Power Electron.*, vol. 31, no. 2,

pp. 1085–1094, Feb. 2016.

- [37] P. D. Achlerkar and B. K. Panigrahi, "Recursive least squares-based adaptive parameter estimation scheme for signal transformation and grid synchronization," *IEEE Trans. Emerg. Sel. Top. Power Electron.*, vol. 9, no. 2, pp. 2427–2439, Apr. 2021.

- [38] H. Ahmed, I. Salgado, I. Chairez, and M. Benbouzid, "Robust gradient estimator for unknown frequency estimation in noisy environment: Application to grid-synchronization," *IEEE Access*, vol. 8, pp. 70 693–70702, 2020.

Anant Kumar Verma (Member, IEEE) received 654 the bachelor's degree in instrumentation engineering 655 from University Science Instrumentation Center, Sri-656 nagar, India, in 2012, the master's degree in power 657 electronics and drives from the Dehradun Institute of 658 Technology, Dehradun, India, in 2014, and the Ph.D. 659 degree in electrical engineering from the National 660 Institute of Technology Hamirpur, Hamirpur, India, 661 in 2021. His research interests include renewable 662 energy systems, modeling of grid synchronization al-663 gorithms, and control of power electronic converters. 664 665

Seifeddine Ben Elghali received the B.Sc. degree 666 in electrical engineering from ENIT, Tunis, Tunisia, 667 in 2005, the M.Sc. degree in automatic control from 668 the University of Poitiers, Poitiers, France, in 2006, 669 and the Ph.D. degree in electrical engineering from 670 the University of Brest, Brest, France, in 2009. After 671 receiving the Ph.D. degree, he joined French Naval 672 Academy, Brest, France, as a Teaching and Research 673 Assistant. Since 2010, he has been an Associate Pro-674 fessor of electrical engineering with Aix-Marseille 675 University, Marseille, France. His current research 676

interests include modeling and control of renewable energy applications.

10

Hafiz Ahmed (Senior Member, IEEE) received the Ph.D. degree in automatic control from the University of Lille 1, Lille, France, in 2016. From 2016 to 2021, he was with Clemson University, Clemson, SC, USA, Asia Pacific University, Dhaka, Bangladesh, North South University, Dhaka, Bangladesh, Coventry University, Coventry, U.K., and Birmingham City University, and Birmingham, U.K. Since April 2021, he has been with Nuclear Futures Institute, Bangor University, U.K., where he is currently the Sêr Cymru Senior Lecturer (Associate Professor) of nuclear in-

strumentation and control. His current research focuses on applied control engineering with special focus in energy and environment.

Dr. Ahmed was the recipient of the European Embedded Control Institute (EECI) Ph.D. Award in 2017 and Best Ph.D. Thesis Award from the Research Cluster on Modeling, Analysis, and Management of Dynamic Systems (GDR-MACS) of the National Council of Scientific Research (CNRS) in France, in 2017. He is an Associate Editor for the *International Journal of Electrical Engineering Education*. He is also actively involved in organizing special issues and sessions at various international journals and conferences.

645

646 647

648

649

650

651 652

653

616 617

618 619

620

621

622

623

624

625

626

627

628

629

630

631

632

633

634

635

636

**Zoheir Tir** (Senior Member, IEEE) was born in El Oued, Algeria. He received the B.Sc. degree in electrical engineering from the University of Batna 2, Algeria in 2007, the M.Sc. degree in electrical engineering from the University of Setif, Algeria, in 2010, and the Sc.D. degree in electrical engineering from the University of Batna 2, in 2014. In 2008, he became an Instructor with the Department of Electrical Engineering, University of El Oued, Algeria, where he was a Lecturer in 2011. From 2014 to 2016,

he was an Assistant Professor, where he was also an Associate Professor from 2016 to 2020. In December 2020, he was promoted to the rank of a Professor in the field of electrical engineering with the University of El Oued. His research project involves automatic control and its implementation on AC motor drives, power electronics systems, renewable energy systems, and observers and estimators, and DSP-based real-time control.

Mohamed Benbouzid (Fellow, IEEE) received the 679 B.Sc. degree in electrical engineering from the 680 University of Batna, Batna, Algeria, in 1990, the 681 M.Sc. and Ph.D. degrees in electrical and com-682 puter engineering from the National Polytechnic In-683 stitute of Grenoble, Grenoble, France, in 1991 and 684 1994, respectively, and the Habilitation à Diriger des 685 Recherches degree from the University of Picardie 686 "Jules Verne," Amiens, France, in 2000. After receiv-687 ing the Ph.D. degree, he joined the Professional Insti-688 tute of Amiens, University of Picardie "Jules Verne," 689

where he was an Associate Professor of electrical and computer engineering.

Since September 2004, he has been with the University of Brest, Brest, France,

where he is currently a Full Professor of electrical engineering. Prof. Benbouzid

is also a Distinguished Professor and a 1000 Talent Expert with Shanghai Martitme University, Shanghai, China. His main research interests and experience

include analysis, design, and control of electric machines, variable-speed drives

of electric machines.

Prof. Benbouzid is a Fellow of the IET. He is the Editor-in-Chief of the698International Journal on Energy Conversion and the Applied Sciences (MDPI)699Section on Electrical, Electronics and Communications Engineering. He is a700Subject Editor of the IET Renewable Power Generation.701

702

## GENERAL INSTRUCTIONS

- Authors: Carefully check the page proofs (and coordinate with all authors); additional changes or updates WILL NOT be accepted after the article is published online/print in its final form. Please check author names and affiliations, funding, as well as the overall article for any errors prior to sending in your author proof corrections. Your article has been peer reviewed, accepted as final, and sent in to IEEE. No text changes have been made to the main part of the article as dictated by the editorial level of service for your publication.

- Authors: Please check ALL author names for correct spelling, abbreviations, and order of first and last name in the byline, affiliation footnote, and bios.

- Authors: We cannot accept new source files as corrections for your article. If possible, please annotate the PDF proof we have sent you with your corrections and upload it via the Author Gateway. Alternatively, you may send us your corrections in list format. You may also upload revised graphics via the Author Gateway.

- Authors: Please note that once you upload your changes, they will be entered and your article finalized. The proofing process is now complete and your article will be sent for final publication and printing. If you would like an additional proof to review, this should be noted as it is not IEEE policy to send multiple proofs. Once your article is posted on Xplore, it is considered final and the article of record. No further changes will be allowed at this point so please ensure scrutiny of your final proof.

- Authors: Unless invited or otherwise informed, a mandatory Excessive Article Length charges will be incurred if your article is over the page limit set by the society in the Information for Authors. If you have any questions regarding overlength page charges, need an invoice, or have any other billing questions, please contact reprints@ieee.org as they handle these billing requests.

# QUERIES

- Q1. Author: Please provide the name of the corresponding author.

- Q2. Author: Please confirm or add details for any funding or financial support for the research of this article.

- Q3. Author: Please check and confirm whether the author affiliations in the first footnote are correct as set.

- Q4. Author: Please provide the postal code for the affiliation of author Seifeddine Ben Elghali.

- Q5. Author: Please update Refs. [1] and [33].

2

Q1

Q2

Q3

Q4

# Quasi Type-1 PLL With Tunable Phase Detector for Unbalanced and Distorted Three-Phase Grid

Hafiz Ahmed<sup>®</sup>, Senior Member, IEEE, Zoheir Tir<sup>®</sup>, Senior Member, IEEE, Anant Kumar Verma<sup>®</sup>, Member, IEEE,

Seifeddine Ben Elghali<sup>®</sup>, and Mohamed Benbouzid<sup>®</sup>, Fellow, IEEE

Abstract-Out of various moving average filter (MAF)-based 5 phase-locked-loop (PLL), quasi type-1 PLL (QT1-PLL) is widely 6 adopted due to its fast dynamic performance, implementation 7 simplicity, and harmonics rejection abilities. However, the perfor-8 9 mance of QT1-PLL deteriorates in the presence of an off-nominal frequency unbalanced grid voltage component. Moreover, the 10 sensitivity towards the fundamental frequency negative sequence 11 (FFNS) component is high. Hence, this paper proposes a novel 12 13 enhanced QT1-PLL solution that is insensitive to unbalance in the grid voltage signal during off-nominal frequency conditions. 14 The proposed adaptive phase detector makes it possible to esti-15 mate both the fundamental frequency positive sequence (FFPS) 16 and FFNS components with a high degree of immunity against 17 harmonics. Notably, the pre-loop separation of the FFPS and the 18 FFNS components helps suppress the second harmonic oscillations 19 20 for improving the parameter estimation accuracy. The loop-filter design of QT1-PLL remains unaffected and requires a proportional 21 22 gain to estimate the fundamental phase and frequency information. 23 To address the DC offset issue, a modified delayed signal cancellation method is also proposed, which can theoretically eliminate 24 the DC offset for any arbitrary delay length. A small-signal model 25 26 of the proposed PLL is developed for the sake of stability analysis. Comparative numerical simulation and experimental results are 27 provided with various variants of QT1-PLLs to demonstrate the 28 29 performance improvement achieved with the proposed technique.

Index Terms—Phase locked-loop, delayed signal cancellation,

moving average filter.

Manuscript received June 15, 2021; revised October 9, 2021; accepted November 20, 2021. The work of H. Ahmed was supported through the Sêr Cymru Programme by Welsh European Funding Office (WEFO) under European Regional Development Fund (ERDF). The experimental part of the present work was supported by the General Directorate of Scientific Research and Technological Development through the Ministry of Higher Education and Scientific Research of Alexie Great Great Out 021102(2012002).

Scientific Research of Algeria under Grant A01L07UN390120180001. Paper no. TEC-00636-2021. Hafiz Ahmed is with Nuclear Futures Institute, Bangor University, LL57 2DG

Bangor, U.K. (e-mail: hafiz.h.ahmed@ieee.org).

Zoheir Tir is with LEVRES Laboratory, University of El Oued, El Oued 39000, Algeria (e-mail: tir-zoheir@univ-eloued.dz).

Anant Kumar Verma is with the Department of Electrical Engineering, National Institute of Technology Hamirpur, Hamirpur 177001, India (e-mail: anant\_verma12@hotmail.com).

Seifeddine Ben Elghali is with the UMR CNRS 7020 LIS, Aix-Marseille University, Marseille, France (e-mail: Seifeddine.BenElghali@lis-lab.fr).

Mohamed Benbouzid is with the UMR CNRS 6027 IRDL, University of Brest, 29238 Brest, France, and also with the Logistics Engineering College, Shanghai Maritime University, Shanghai 201306, China (e-mail: mohamed.benbouzid@univ-brest.fr).

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TEC.2021.3130492.

Digital Object Identifier 10.1109/TEC.2021.3130492

#### I. INTRODUCTION

THE penetration of grid-interfaced power electronic con-33 verters into traditional electric power grid is increas-34 ing day-by-day. They are used for various purposes such as 35 grid-integration of distributed energy resources [1]-[5], power 36 quality improvement [6], supplying domestic and industrial 37 loads [7], charging electric vehicles [8], to name a few. These 38 applications require grid-synchronous operation of the con-39 verter with the grid. This process is commonly known as grid-40 synchronization in the literature. Grid-synchronization necessi-41 tates the real-time extraction of unknown grid voltage parame-42 ters. As a result, a significant research attention has been given 43 to this problem in the last few decades. 44

Many fast, efficient, and accurate techniques are already 45 reported in the literature. Out of them, phase-locked loop 46 (PLL) [9]-[13] and it's various variants are particularly popu-47 lar. Traditional synchronous reference frame-PLL (SRF-PLL) 48 uses Park's transformation as the phase detector and uses a 49 proportional-integral low-pass filter to estimate the unknown 50 grid frequency and phase. The SRF-PLL has fast convergence 51 speed and good disturbance rejection capability. However, this 52 PLL is designed for a balanced grid i.e. only the fundamental 53 frequency positive sequence (FFPS) component is present. In 54 practice, especially at the distribution network level, the grid 55 often has a level of phase unbalance, e.g., more than 50% of the 56 800 low voltage substations in Cardiff, U.K. have serious phase 57 unbalance [14]. So, enhanced filtering capability is essential to 58 ensure efficient operation of PLL under the presence of phase 59 unbalance i.e. both FFPS and fundamental frequency negative 60 sequence (FFNS) components exist simultaneously. 61

In the presence of phase unbalance, the phase detector of SRF-62 PLL generates an undesirable double frequency components. To 63 eliminate the undesirable components, several solutions propose 64 the application of additional filtering stage(s) through pre-loop, 65 in-loop and a combination of both. In the case of pre-loop, filters 66 are applied in the stationary reference frame, i.e.,  $\alpha\beta$ -frame 67 where as in-loop filters are applied in the synchronous reference 68 frame, i.e., dq-frame. In the case of hybrid filtering, filters are 69 applied at both stationary and synchronous reference frames. 70

Some popular filters proposed in the literature are: delayed signal cancellation (DSC) [15]–[17], complex coefficient filter (CCF) [18], [19], moving average filter [20]–[24], orthogonal signal generator (OSG) filter such as second-order generalized integrator (SOGI) [25], adaptive notch filter (ANF) [26], to 75

32

name a few. In addition to the filter-based SRF-PLLs, multiple

reference frame-based SRF-PLLs such as double decoupled

SRF-PLL [27] are also popular in the literature.

79 Delayed signal cancellation (DSC) [15]–[17], [28] is a popular technique to eliminate the FFNS from the measured grid 80 voltages at the point of common coupling. In order to make 81 DSC-PLL immune to harmonics, multiple DSC operators are 82 used in cascade. So, prior information about the grid harmonics 83 is needed.. Moreover, in the case of off-nominal frequency 84 85 operation, frequency-adaptive DSCs are proposed [29]. This can potentially increase the computational complexity. By using 86 cross-coupling between two CCF, CCF-PLL [18], [19] can 87 extract grid-synchronized FFPS and FFNS components. CCF 88 is very suitable for selective harmonic elimination. However, 89 multiple CCFs are required to eliminate the effect of harmonics 90 91 which causes additional computational burden.

OSG-PLLs operate in the stationary reference frame, i.e., 92  $\alpha\beta$ -frame and uses OSGs to separate the FFPS and FFNS com-93 94 ponents followed by traditional SRF-PLL. OSGs typically have band-pass (cf. SOGI [25]) or notch (cf. ANF [26]) characteris-95 96 tics. To enhance the harmonic robustness of OSG-PLLs, multiple parallel OSGs are often recommended in the literature [30]. This 97 can be computationally complex. Moreover, discretization of 98 parallel OSGs is not straightforward, specially for high-order 99 100 harmonics. Multiple reference frame PLLs use multiple SRFs to separate the FFPS and FFNS components. In the case of 101 DDSRF-PLL, two cross-coupled reference frames operating at 102 opposite instantaneous phases are used. This helps to make the 103 PLL insensitive to FFNS components. However, the presence of 104 harmonics and/or DC-offset deteriorates the performance. This 105 106 necessitates the application of several reference frames where each operates at the relevant instantaneous phases. This kind 107 108 of structure is complex and not suitable for low-cost embedded devices-based real-time implementation. 109

MAF-PLLs [20]-[24] provides an interesting solution to elim-110 inate the effect of harmonics and/or DC offset. Here, MAF is 111 used to eliminate the effect of FFNS component. Depending on 112 113 the MAF window length, MAF-PLL can be very effective to block all harmonics and DC offset. However, this comes at the 114 cost of slow dynamic response [20]. To enhance the convergence 115 speed of MAF-PLL, quasi type-1-PLL (QT1-PLL) is proposed 116 in [21]. The QT1-PLL uses the idea of frequency-adaptive 117 demodulation [31]. An advantage of this approach is that 118 only a proportional loop-filter can estimate the unknown grid-119 frequency whereas proportional-integral loop filter is required 120 for conventional MAF-PLL. However, QT1-PLL is sensitive to 121 off-nominal FFNS component. Since, fundamental frequency 122 tuned MAFs are used in QT1-PLL, it cannot completely block 123 the FFNS component if they appear at off-nominal frequency 124 125 condition. To speed-up the convergence speed of QT1-PLL, hybrid QT1-PLL (HQT1-PLL) [22] is proposed. In this case, DSC 126 operators are applied in the  $\alpha\beta$ -frame whereas MAF is applied 127 in the dq-frame. However, fast dynamic response comes at the 128 cost of sacrificing the high phase margin. Moreover, HQT1-PLL 129 130 is also sensitive to off-nominal FFNS component. To reduce the effect of off-nominal frequency FFNS component sensitivity 131 132 of QT1-PLL, total QT1-PLL (TQT1-PLL) is proposed in [24].

Fig. 1. Overview of QT1-PLL [21].

In this case, a third-order non-adaptive MAF is proposed. This 133 MAF has same window length as QT1-PLL but has significantly 134 lower steady-state errors in the presence of off-nominal FFNS 135 component. However, this comes at the cost of high sensitivity 136 to sub- and inter-harmonics. In [32], the authors have proposed 137 the application of all-pass filter (APF) [33] as the sequence 138 components separator for HQT1-PLL. Although this technique 139 can reduce the sensitivity, however, APF on its own has limited 140 filtering capability. This can be a limiting factor when the grid 141 voltage has inter- and/or sub-harmonics components. Similar 142 line of investigation is considered in [34] where third-order 143 generalized integrator is considered as the pre-loop filter. It is to 144 be noted here that none of the QT1-PLL techniques discussed 145 in this section can extract the FFNS component with high de-146 gree of harmonic immunity. This limits their application where 147 sequence extraction is important [35]. 148

Comparative analysis in [23] shows that out of various MAF-149 PLLs, QT1-PLL is very suitable for grid-connected converters. 150 This motivates the current work of improving the performance 151 of QT1-PLL. Our main objective is to use QT1-PLL for FFPS 152 and FFNS sequence extraction. For this purpose, an enhanced 153 phase detector is constructed in this work. This phase detector 154 can separate the FFPS and FFNS initial phase-angle and am-155 plitudes. Output of the phase detectors are passed through a 156 proportional loop-filter to estimate the unknown frequency and 157 instantaneous phase of the grid voltage. A small-signal model 158 is derived through analytical calculations and constructive gain 159 tuning procedures are developed for the proposed enhanced 160 QT1-PLL. Finally, the performance of the proposed technique 161 is verified through simulation and experiments on a PWM-162 controlled voltage source inverter. In contrast to the conventional 163 QT1-PLLs, the proposed approach is insensitive to off-nominal 164 FFNS component. Moreover, it can extract FFPS and FFNS 165 components unlike conventional QT1-PLLs. These are the main 166 contributions of this work. 167

The rest of this paper is organized as follows: Section II 168 summarizes the conventional QT1-PLL. Development of the 169 proposed enhanced QT1-PLL is given in Section III. Results and 170 discussions are given in Section IV. Finally, concluding remarks 171 are given in Section V. 172

#### II. QUASI TYPE-1 PLL: BRIEF OVERVIEW 173

This section summarizes the basic idea of the conventional 174 QT1-PLL as proposed in [21]. Block diagram of the QT1-PLL 175 is given in Fig. 1. To analyze the phase detector of the QT1-PLL, 176 let us consider the three-phase grid voltages in  $\alpha$ ,  $\beta$ -frame as: 177

$$v_{\alpha}(t) = V \cos\left(\omega t + \phi\right), \tag{1}$$

$$v_{\beta}(t) = V \sin\left(\omega t + \phi\right), \qquad (2)$$

where the amplitude, angular frequency, and the initial phaseangle are given by V,  $\omega$ , and  $\phi$ , respectively. The instantaneous phase of the signals (1) and (2) is given by  $\Theta = \omega t + \phi \in$  $[0, 2\pi)$ . The voltages in (1) and (2) are converted into the synchronous reference frame (d, q) by applying the Park-type transformation and given by:

$$\begin{bmatrix} v_d \\ v_q \end{bmatrix} = \begin{bmatrix} \cos\left(\hat{\omega}t\right) & \sin\left(\hat{\omega}t\right) \\ -\sin\left(\hat{\omega}t\right) & \cos\left(\hat{\omega}t\right) \end{bmatrix} \begin{bmatrix} v_\alpha \\ v_\beta \end{bmatrix}.$$

(3)

From (3), the direct and quadrature-axis voltages can be rewritten as:

$$v_{d} = v_{\alpha} \cos\left(\hat{\omega}t\right) + v_{\beta} \sin\left(\hat{\omega}t\right),$$

$$= \frac{V}{2} \left[\cos\left\{\left(\omega - \hat{\omega}\right)t + \phi\right\} + \cos\left\{\left(\omega + \hat{\omega}\right)t + \phi\right\}\right]$$

$$+ \frac{V}{2} \left[\cos\left\{\left(\omega - \hat{\omega}\right)t + \phi\right\} - \cos\left\{\left(\omega - \hat{\omega}\right)t + \phi\right\}\right]. \quad (4)$$

$$v_{q} = v_{\beta} \cos\left(\hat{\omega}t\right) - v_{\alpha} \sin\left(\hat{\omega}t\right),$$

$$= \frac{V}{2} \left[\sin\left\{\left(\omega + \hat{\omega}\right)t + \phi\right\} + \sin\left\{\left(\omega - \hat{\omega}\right)t + \phi\right\}\right]$$

$$- \frac{V}{2} \left[\sin\left\{\left(\omega + \hat{\omega}\right)t + \phi\right\} - \sin\left\{\left(\omega - \hat{\omega}\right)t + \phi\right\}\right]. \quad (5)$$

In the quasi-locked condition i.e.  $\hat{\omega} \approx \omega$ , it can be assumed that  $\omega - \hat{\omega} \approx 0$ . Then, (4) and (5) can be simplified as:

$$v_d \approx V \cos\left(\phi\right). \tag{6}$$

$$v_a \approx V \sin\left(\phi\right). \tag{7}$$

188 It is to be noted here that only when  $\phi = \pm n\pi$ , n = 0, 1, 2, ...,189  $v_d \approx V$  and  $v_q \approx 0$  which is the same as the output of the phase 190 detector of SRF-PLL [9]. From (6) and (7), the initial phase-191 angle can be estimated as:

$$\hat{\phi} = \operatorname{atan2}\left(v_q, v_d\right),\tag{8}$$