# DESIGN OF LOW-COST ENERGY HARVESTING AND DELIVERY SYSTEMS FOR SELF-POWERED DEVICES: APPLICATION TO AUTHENTICATION IC

A Dissertation

Presented to

The Academic Faculty

By

Edward Lee

In Partial Fulfillment

of the Requirements for the Degree

Doctor of Philosophy in the

School of Electrical and Computer Engineering

Georgia Institute of Technology

December 2021

Copyright © Edward Lee 2021

# DESIGN OF LOW-COST ENERGY HARVESTING AND DELIVERY SYSTEMS FOR SELF-POWERED DEVICES: APPLICATION TO AUTHENTICATION IC

## Approved by:

Dr. Saibal Mukhopadhyay, Advisor School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Shimeng Yu School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Abhijit Chatterjee School of Electrical and Computer Engineering Georgia Institute of Technology Dr. Madhavan Swaminathan School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Satish Kumar School of Mechanical Engineering Georgia Institute of Technology

Date Approved: June 11, 2021

A journey of a thousand miles starts with a single step.

Lao-Tzu

#### ACKNOWLEDGEMENTS

My PhD years have been the most fruitful and rewarding years of my life and I am forever grateful to those who have encouraged me to seek down this path. First, I would like to express my appreciation and respect to my advisor Professor Saibal Mukhopadhyay for his guidance throughout my PhD studies here at Georgia Tech. He has been a great source of motivation and inspiration for pushing the depths and widths of my knowledge. I have learned from him, with his own example, what it takes to be successful in any field of expertise. I am thankful to him for giving me the opportunity to study and explore different research problems and supporting me both technically and financially along the way. This thesis would not have been possible were it not for his trust and faith.

I would like to thank my committee members, Professor Shimeng Yu, Professor Abhijit Chatterjee, Professor Madhavan Swaminathan and Professor Satish Kumar for their valuable time and suggestions towards improving the quality of this thesis. Additionally, I would like to thank all of my teachers at Georgia Tech for offering their experience and insights that have helped equip me with the knowledge to tackle challenges in the future. I would like to thank Keith May, Faith Midkiff and Daniela Staiculescu for their technical and administrative support. Their expertise has helped me focus on my research problems and have been extraordinarily helpful. I would also like to thank SRC and DARPA for providing funding to support the completion of this thesis.

I would like to express special thanks to my wonderful colleagues at GREEN lab who have offered their knowledge and non-withholding advice over the years. Thanks are due to Arvind Singh and Monodeep Kar for introducing me to the lab and to Chaitanya Krisha, Nael Rahman and Daehyun Kim who were my collaborators for multiple projects. I am grateful to have worked with and known Yun Long, Burhan Mudassar, Nihar Dasari, Xueyuan She, Minah Lee, Mandovi Mukherjee, Priyabrata Saha and others. In particular, I would like to thank Faisal Amir for his mentorship when I first approached this field of

research. I have learned a lot from all the members of GREEN lab in many ways and our interactions have contributed significantly to making this thesis successful. I wish them the best in their future endeavors and hope we will cross paths again.

Finally and foremost, I would like to take this opportunity to thank my family for supporting me in all aspects of my life. Their unconditional love and care has given me the strength and courage to seek my dreams. My parents, Ying-Haur Lee and Hsiang-Wei Ker, and my elder brother, Albert Lee, are my strongest backing and role models for life. My younger brother, Andrew Lee, has been a source of motivation to continuously make myself better. I would also like to thank Annie Wang for her companionship when I needed it the most. The challenges and hardships throughout my life have made me understand that I would not have been able to achieve this much were it not for the ones I cherish the most.

## TABLE OF CONTENTS

| Acknov    | vledgments                                                 |

|-----------|------------------------------------------------------------|

| List of   | Tables                                                     |

| List of 1 | Figures                                                    |

| Summa     | nry                                                        |

| Chapte    | r 1: Introduction                                          |

| 1.1       | Thesis Statement                                           |

| 1.2       | Key Contributions                                          |

| 1.3       | Organization of this thesis                                |

| Chapte    | r 2: Literature Survey                                     |

| 2.1       | Power management for increased lifetime                    |

| 2.2       | Energy Harvesting                                          |

|           | 2.2.1 Harvesting sources                                   |

|           | 2.2.2 Power Management Unit (PMU) Architecture Selection   |

| 2.3       | Full-System Design Challenges                              |

|           | 2.3.1 Maximum Power Point Tracking                         |

|           | 2.3.2 Challenges for System Start-up with Power Conversion |

| Chapte | r 3: En | ergy Delivery System Design And Analysis       | 16 |

|--------|---------|------------------------------------------------|----|

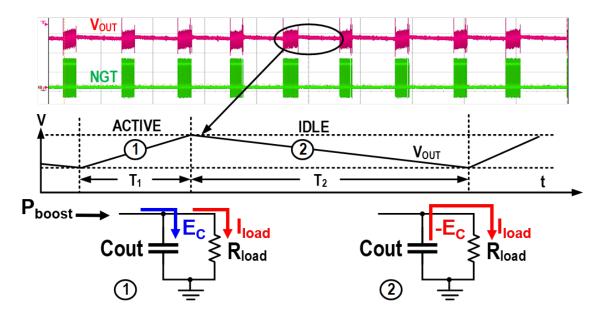

| 3.1    | PFM E   | Boost Regulator Operation                      | 17 |

|        | 3.1.1   | Fundamental Limitations of PFM control         | 20 |

| 3.2    | Analyt  | ical Model Development                         | 23 |

|        | 3.2.1   | Prior Work - Single-Pulse Model                | 23 |

|        | 3.2.2   | Charge-equilibrium Based Model                 | 24 |

|        | 3.2.3   | Loss Components Modeled                        | 28 |

| 3.3    | Model   | Results and Validation                         | 32 |

|        | 3.3.1   | DC-DC conversion                               | 33 |

|        | 3.3.2   | EHDS System-level optimization                 | 34 |

| 3.4    | Model   | Application: Co-design with embedded passives  | 45 |

|        | 3.4.1   | Co-Design and Results                          | 45 |

| Chapte | r 4: EH | DS-based load control for reduced system power | 49 |

| 4.1    | Target  | Application and Implementation                 | 49 |

| 4.2    | Embed   | Ided Wake-up mechanism with PMU control        | 51 |

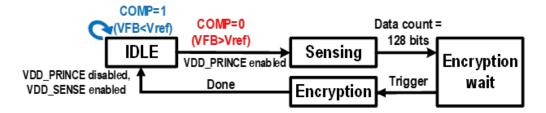

|        | 4.2.1   | Wake-up FSM                                    | 51 |

| 4.3    | Efficie | ncy Optimizations                              | 54 |

|        | 4.3.1   | IVR parallel power stages                      | 54 |

|        | 4.3.2   | Frequency reconfiguration                      | 55 |

| 4.4    | Discus  | sions                                          | 57 |

|        | 4.4.1   | Variation Analysis of Oscillator               | 57 |

|        | 4.4.2   | Reducing variation via re-configuration        | 58 |

| 4.5    | Systen   | m Analysis: Discrete conduction maximum power point tracking | . 60 |

|--------|----------|--------------------------------------------------------------|------|

|        | 4.5.1    | MPPT measurement waveforms                                   | . 62 |

|        | 4.5.2    | Limitations                                                  | . 64 |

| Chapte | r 5: De  | sign and Measurement of a Low-overhead EHDS                  | . 66 |

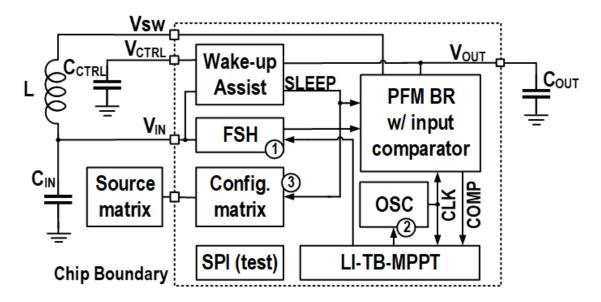

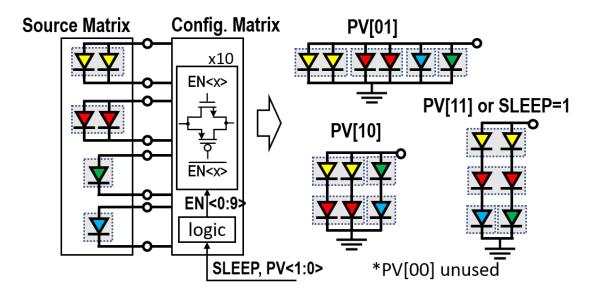

| 5.1    | Propos   | sed Approach and System Components                           | . 67 |

|        | 5.1.1    | Cold-start: Wake-up Assist                                   | . 68 |

|        | 5.1.2    | LI-TB-MPPT: Boosted Power Estimation                         | . 69 |

|        | 5.1.3    | Fractional Sample & Hold: Harvesting-window Control          | . 71 |

|        | 5.1.4    | Configurable Switching Frequency: EHDS efficiency tuning     | . 78 |

| 5.2    | Imple    | mentation                                                    | . 79 |

|        | 5.2.1    | Wake-up Assist circuit                                       | . 79 |

|        | 5.2.2    | Configurable Fractional Sample & Hold                        | . 81 |

|        | 5.2.3    | PFM control path                                             | . 83 |

|        | 5.2.4    | Configurable frequency oscillator                            | . 84 |

|        | 5.2.5    | Load Inclusive Time Based MPPT                               | . 84 |

| 5.3    | Measu    | rement Results                                               | . 88 |

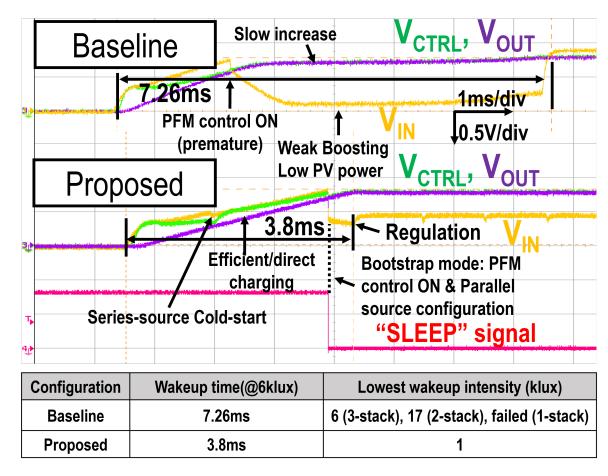

|        | 5.3.1    | Wake-up Assisted Cold-start                                  | . 90 |

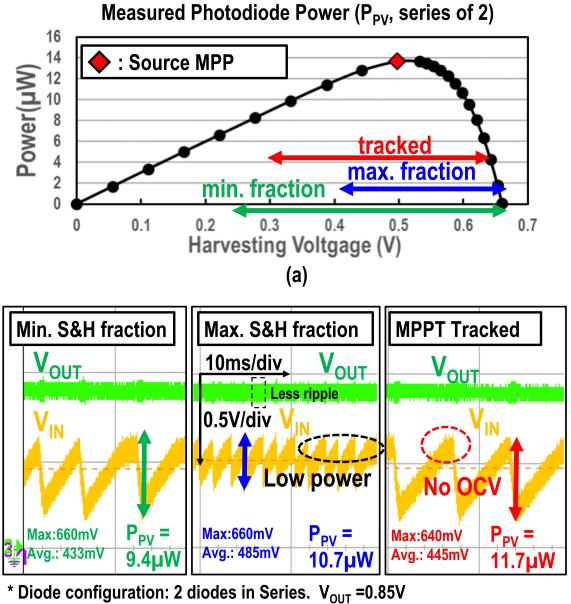

|        | 5.3.2    | Fraction tuning with LI-TB-MPPT                              | . 92 |

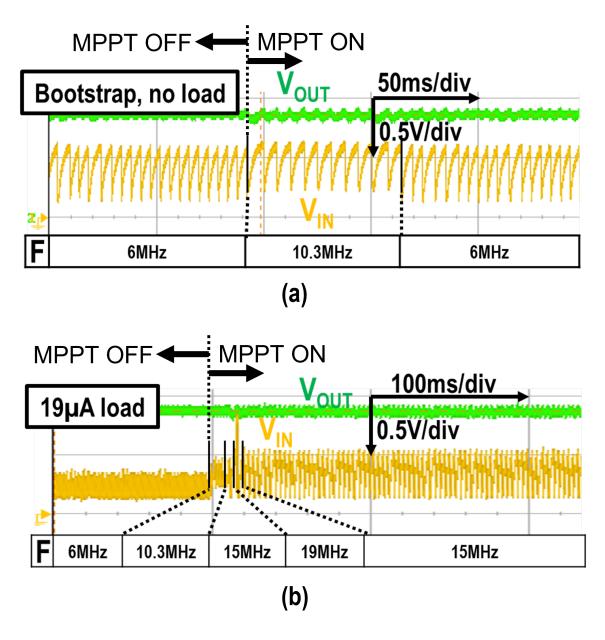

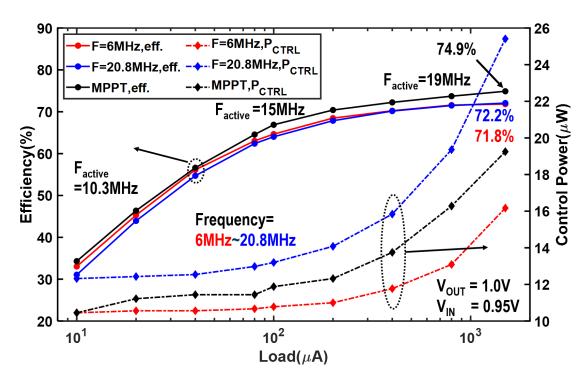

|        | 5.3.3    | Frequency tuning with LI-TB-MPPT                             | . 92 |

|        | 5.3.4    | Comparison with prior works                                  | . 96 |

| 5.4    | Summ     | nary and discussions                                         | . 99 |

| Chanta | r 60 Vie | sible light based authentication IC                          | 101  |

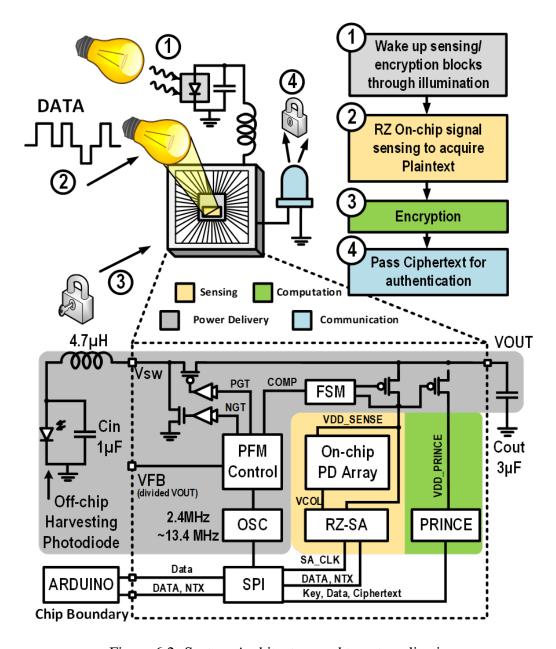

| 6.1               | Systen                                                  | n Architecture                             |

|-------------------|---------------------------------------------------------|--------------------------------------------|

| 6.2               | Sensin                                                  | g and Data Communication                   |

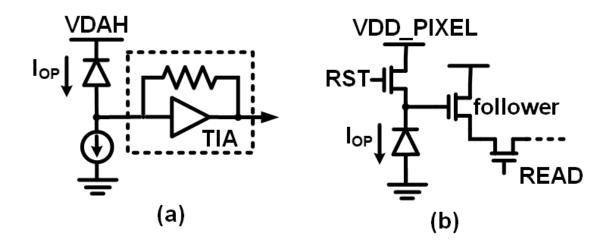

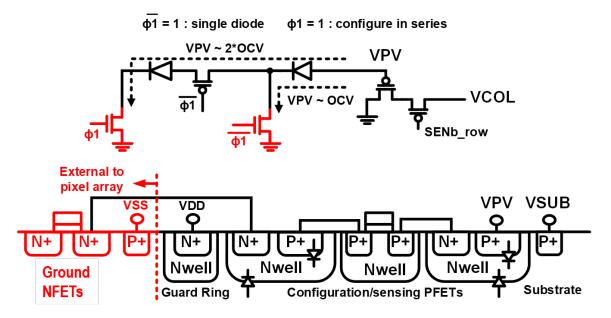

|                   | 6.2.1                                                   | Photodiode Design                          |

|                   | 6.2.2                                                   | CMOS Photodiode Voltage-to-Time conversion |

|                   | 6.2.3                                                   | Time-to-Digital Return-to-Zero Circuit     |

| 6.3               | Measu                                                   | rement Results                             |

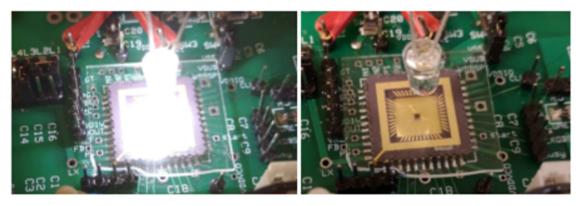

|                   | 6.3.1                                                   | Chip micrograph and Measurement Board      |

|                   | 6.3.2                                                   | System Operation                           |

|                   | 6.3.3                                                   | Demonstration of Operation                 |

| 6.4               | Compa                                                   | arison to prior works                      |

| 6.5               | Summ                                                    | ary                                        |

|                   |                                                         |                                            |

| Chapte            | r 7: Pro                                                | ojected Self-Powered Authentication        |

| Chapte            |                                                         | mance Projections                          |

| _                 |                                                         |                                            |

| _                 | Perfor                                                  | mance Projections                          |

| 7.1               | Perfor. 7.1.1 7.1.2                                     | mance Projections                          |

| 7.1               | Perfor. 7.1.1 7.1.2                                     | mance Projections                          |

| 7.1               | Perfor. 7.1.1 7.1.2 On-ch 7.2.1                         | mance Projections                          |

| 7.1               | Performance 7.1.1 7.1.2 On-character 7.2.1 Full Systems | mance Projections                          |

| 7.1<br>7.2<br>7.3 | Performance 7.1.1 7.1.2 On-character 7.2.1 Full Systems | mance Projections                          |

| 7.1<br>7.2<br>7.3 | Performance 7.1.1 7.1.2 On-chi 7.2.1 Full Sy            | mance Projections                          |

| Refere | nces                          |

|--------|-------------------------------|

| Append | lix A: Publication List       |

| 8.3    | Future Research Opportunities |

| 8.2    | Summary of Contributions      |

| 8.1    | Dissertation Summary          |

# LIST OF TABLES

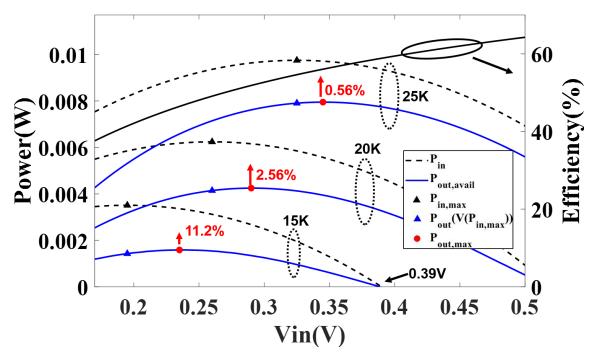

| 3.1 | Effect of System-MPPT on Harvesting Voltage and Maximum Output Power | 39 |

|-----|----------------------------------------------------------------------|----|

| 3.2 | Operating Frequency and Loss for Co-design                           | 48 |

| 5.1 | Comparison to state-of-the-art EHDSs                                 | 97 |

| 6.1 | Comparison to existing light-based IDs                               | 16 |

| 6.2 | Comparison to state-of-the-art authentication ICs                    | 17 |

| 7.1 | EHDS designs to target different applications                        | 27 |

# LIST OF FIGURES

| 2.1  | I-V and P-V characteristics of PV devices                                                                                                                                 | 8  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2  | Schematic of generic EHDS                                                                                                                                                 | 10 |

| 2.3  | Typical FOCV methods                                                                                                                                                      | 12 |

| 2.4  | Transient of single-input single-output PFM boosting                                                                                                                      | 13 |

| 3.1  | EHDS design considerations                                                                                                                                                | 16 |

| 3.2  | Analog PFM-BR schematic. ( $R_{LX}$ is only connected in simulations to increase simulation speed.)                                                                       | 17 |

| 3.3  | (a) Single-pulse operation (b) Multi-pulse operation for PFM-BR                                                                                                           | 18 |

| 3.4  | Effect of Inductance                                                                                                                                                      | 21 |

| 3.5  | Simulated loss and efficiency compared with single pulse model results. Output voltage is set to be 1.5V for different Vin (x-axis) and load current (colored dots) pairs | 23 |

| 3.6  | Inductor current with parasitic resistance from power stage/wire/bump etc                                                                                                 | 24 |

| 3.7  | Flow diagram for performing inductor current transient modeling                                                                                                           | 27 |

| 3.8  | Conduction loss from (a) inductor current (b) NFET drain current (c) PFET drain current, (d) current to capacitor                                                         | 28 |

| 3.9  | Inductor current behavior and parameters used for calculation                                                                                                             | 29 |

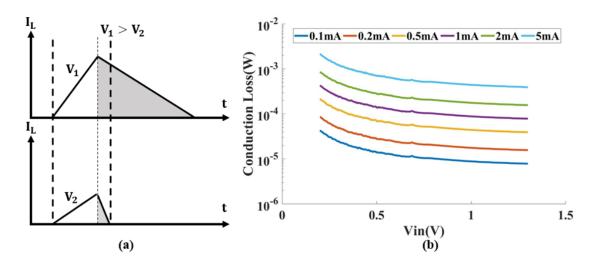

| 3.10 | (a) Effect of input voltage (b) Conduction loss obtained from model                                                                                                       | 30 |

| 3.11 | Switching loss occurrences included in the loss model (a) gate-drive losses (b) hard-switching loss                                                                       | 31 |

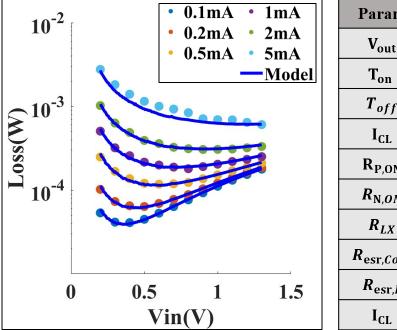

| 3.12 | Loss results of PFM regulator obtained from model compared with Spectre simulations                                                                                    | 33 |

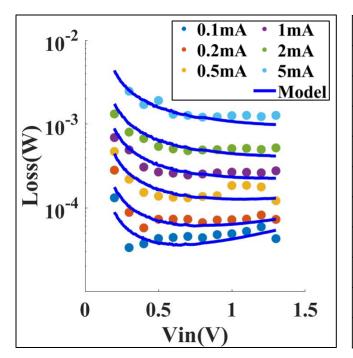

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.13 | Loss results of PFM regulator obtained from model compared with silicon measurements                                                                                   | 34 |

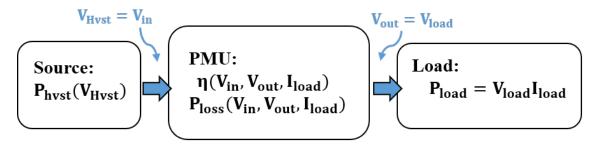

| 3.14 | Power delivery path and interfaces between each stage for a typical EHDS supplying target load                                                                         | 35 |

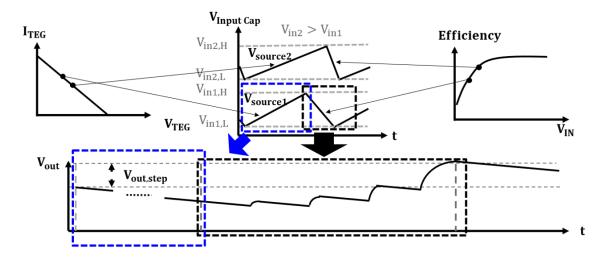

| 3.15 | Input hysteresis at different voltages and step-wise increase in output due to input hysteresis                                                                        | 36 |

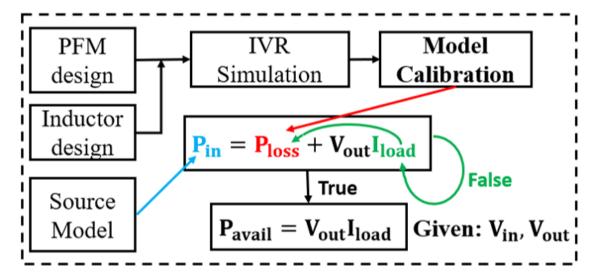

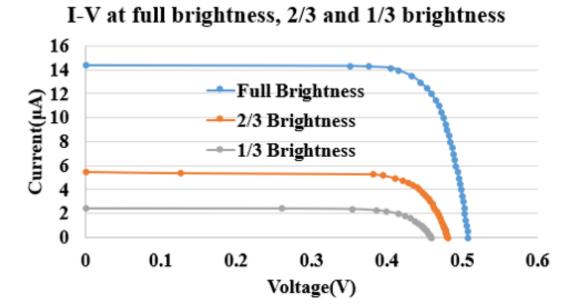

| 3.16 | Computing available output power                                                                                                                                       | 37 |

| 3.17 | TEG source power and available system output power at 15 K, 20 K, 25 K temperature difference. ( $V_{\rm OC}=0.39V, I_{\rm SC}=36mA@\Delta T=15K$ )                    | 38 |

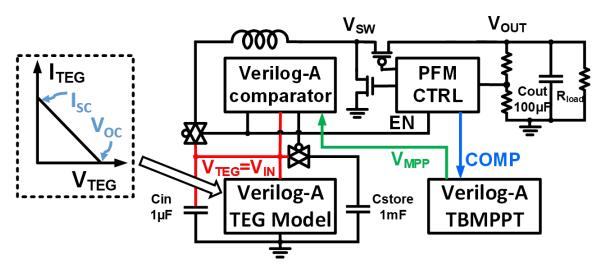

| 3.18 | Schematic for transient TB-MPPT tracking                                                                                                                               | 40 |

| 3.19 | Simulation results of Time-based System-MPPT (TEG@ $\Delta$ T=20)                                                                                                      | 41 |

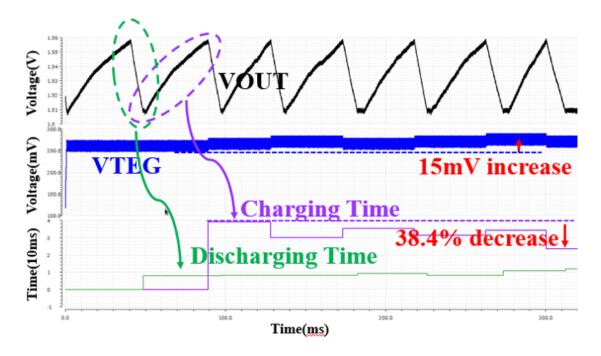

| 3.20 | I-V measurements of PV cell                                                                                                                                            | 42 |

| 3.21 | PV measurement data power and available output power                                                                                                                   | 43 |

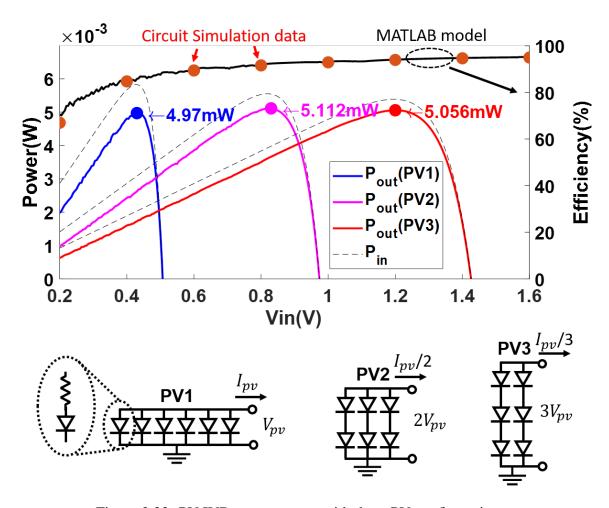

| 3.22 | PV-IVR output power with three PV configurations                                                                                                                       | 44 |

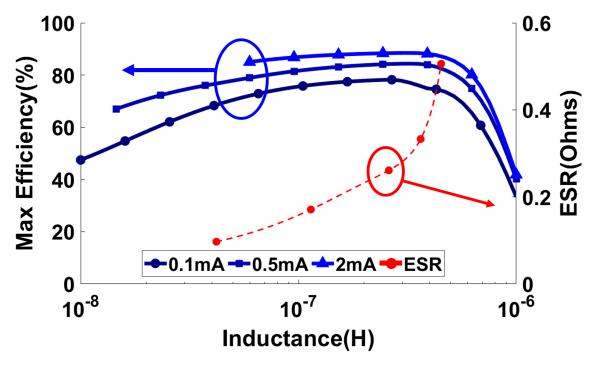

| 3.23 | Embedded inductor inductance effect on maximum efficiency                                                                                                              | 46 |

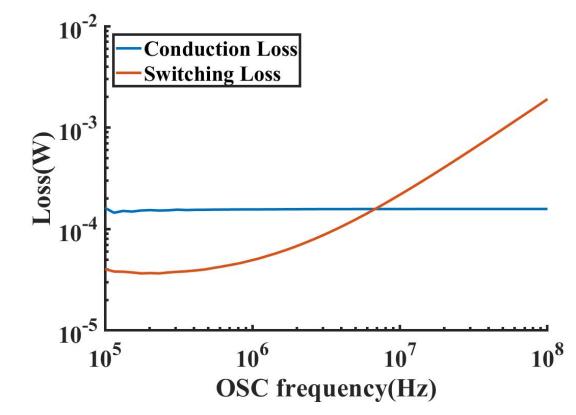

| 3.24 | Conduction loss and switching loss at different frequencies (Post-silicon optimization: Fixed power stage)                                                             | 47 |

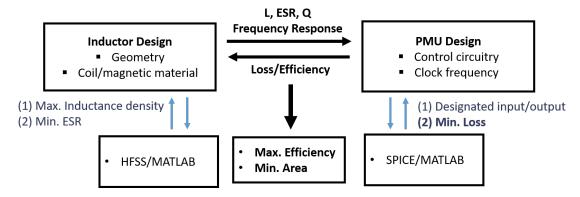

| 3.25 | Co-design flow for conversion efficiency optimization                                                                                                                  | 47 |

| 4.1  | Chip micrograph and specification of the testchip/package                                                                                                              | 50 |

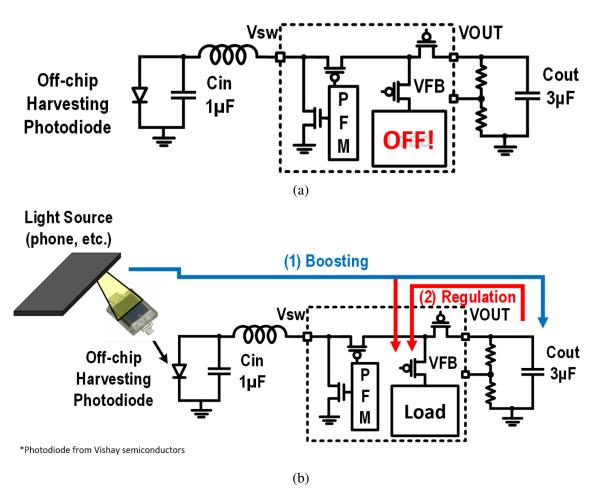

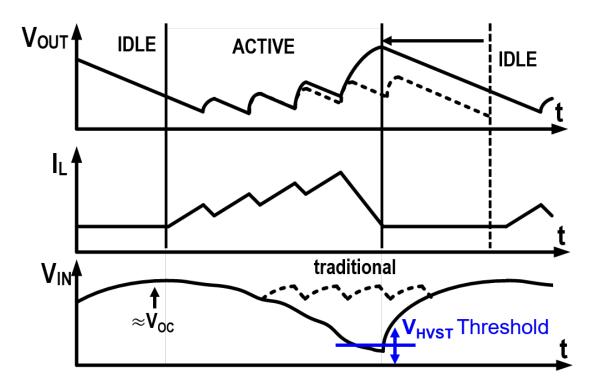

| 4.2  | Power management during (a)IDLE (b)ACTIVE for proposed EHDS                                                                                                            | 51 |

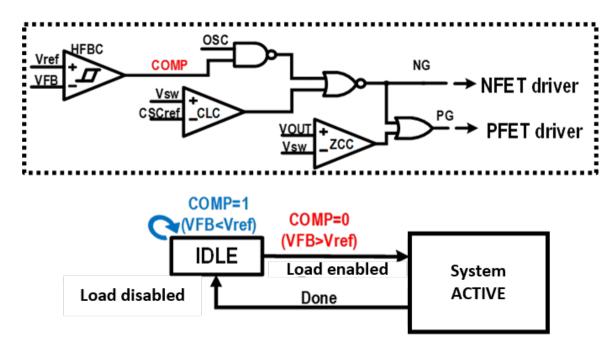

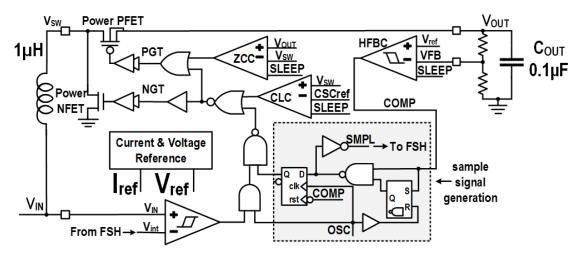

| 4.3  | PFM control path for IVR including HFBC, CLC, ZCC and on-chip finite state machine                                                                                     | 52 |

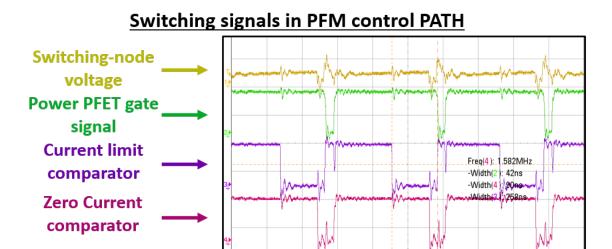

| 4.4  | Measured PFM control path switching behaviour. Switching node voltage $=V_{sw}$ in Fig. 4.2. Operating voltage increased to 1.1V for undistorted off-chip observation. | 53 |

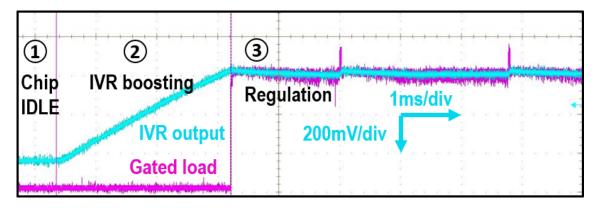

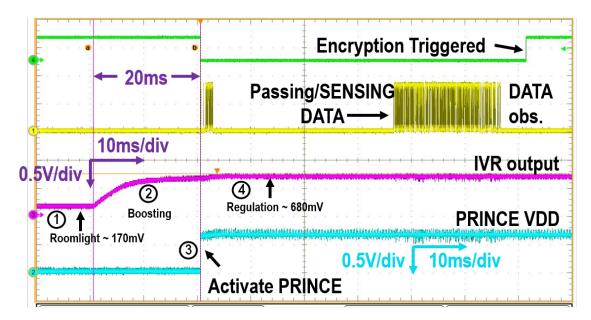

| 4.5  | Measured Waveform showing three phases of wake-up under low-to-high light intensity step.                                                                                                                                            | 53 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.6  | PFM boost IVR with parallel power switch enabled                                                                                                                                                                                     | 55 |

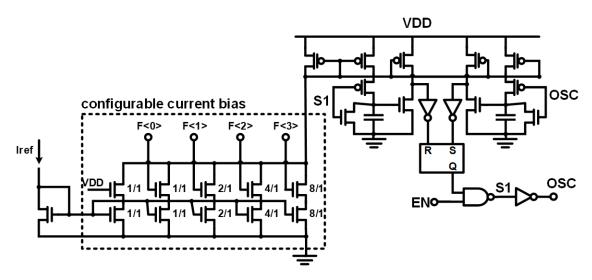

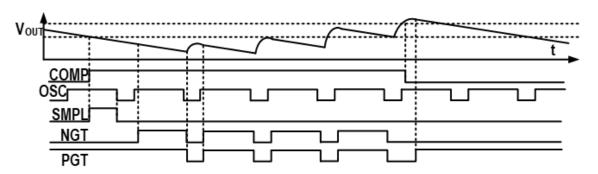

| 4.7  | Schematic of analog I-C oscillator with frequency configurability                                                                                                                                                                    | 56 |

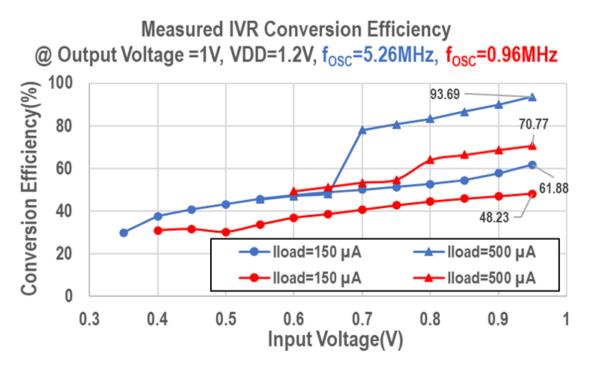

| 4.8  | Measured Efficiency of IVR configured at two oscillator frequencies (top) 5.26MHz (bot) 0.96 MHz                                                                                                                                     | 57 |

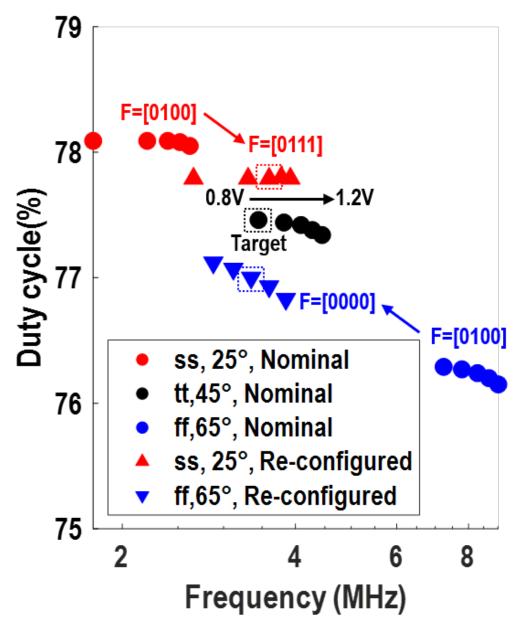

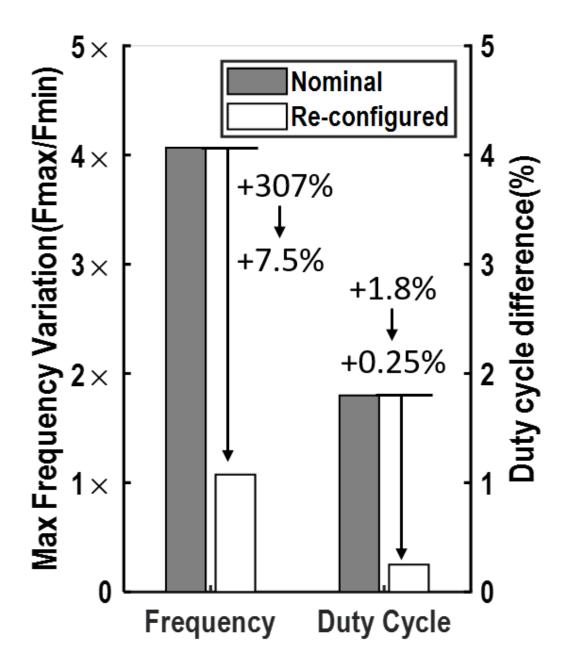

| 4.9  | Oscillator PVT variation simulation. Due to sub-threshold biasing, slow-slow process at low-temperature and fast-fast process at high-temperature produce maximum variation                                                          | 58 |

| 4.10 | Effectiveness of re-configuration.                                                                                                                                                                                                   | 59 |

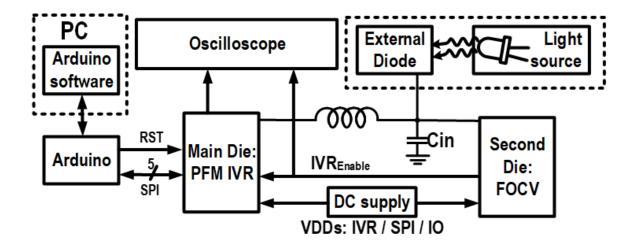

| 4.11 | Measurement setup with off-chip MPPT                                                                                                                                                                                                 | 60 |

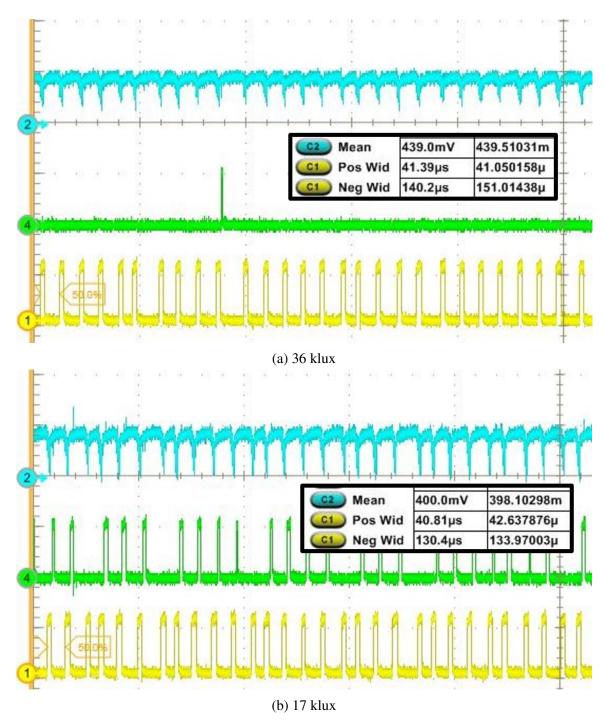

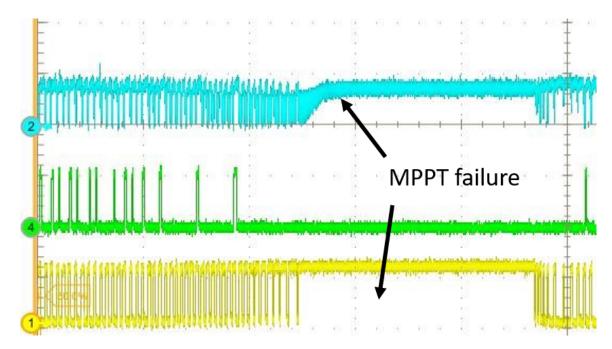

| 4.12 | measurement of MPPT at 36klux and 17klux. Blue: Input photodiode voltage; Green: FOCV-generated IVR disable signal to prevent voltage drop beyond threshold; Yellow: IVR output hysteresis comparator signal (high=active, low=idle) | 61 |

| 4.13 | Occasional MPPT failures at illuminance <17klux                                                                                                                                                                                      | 63 |

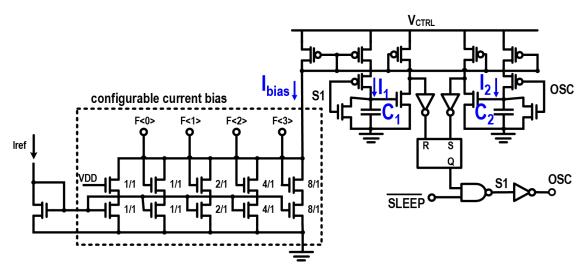

| 5.1  | Schematic of proposed system components                                                                                                                                                                                              | 67 |

| 5.2  | Possible source configurations                                                                                                                                                                                                       | 68 |

| 5.3  | Boosted-power estimation metric derivation                                                                                                                                                                                           | 70 |

| 5.4  | Current drawn from a single inductor pulse and drop in voltage                                                                                                                                                                       | 71 |

| 5.5  | PFM inductor current and input/output voltage                                                                                                                                                                                        | 73 |

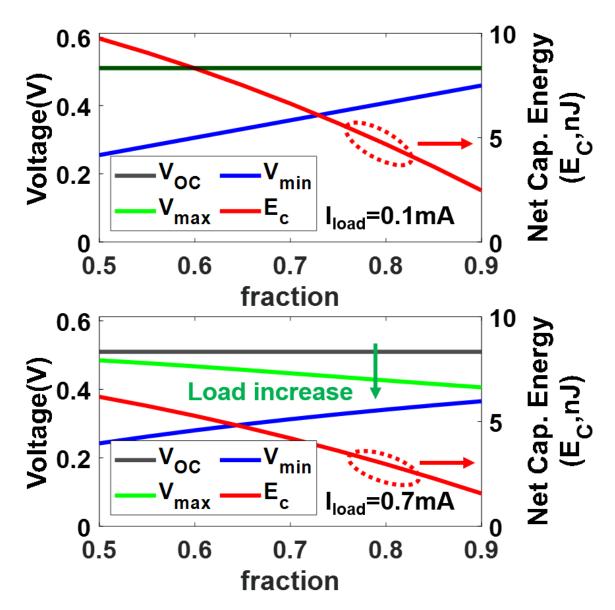

| 5.6  | Maximum/minimum voltage and hysteresis energy for different fractions $(V_{min}/V_{max})$ at equilibrium for load current=0.1mA (top), 0.7mA (bot). $(V_{OC}=0.51V, I_{SC}=1mA, C_{IN}=100nF, C_{OUT}=1.1\mu F)$                     | 75 |

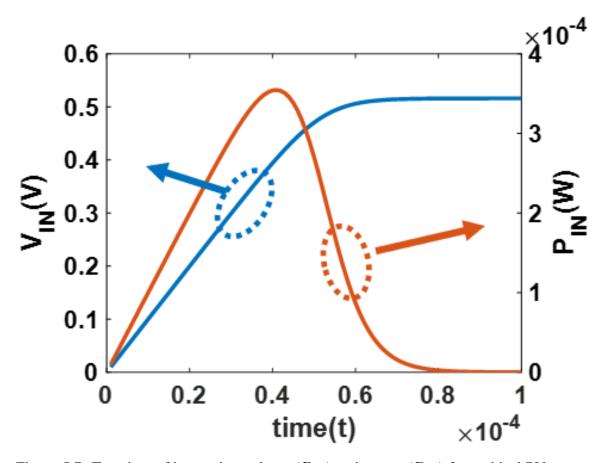

| 5.7  | Transient of harvesting voltage $(P_{IN})$ and power $(P_{IN})$ for an ideal PV source when PMU is IDLE                                                                                                                              | 76 |

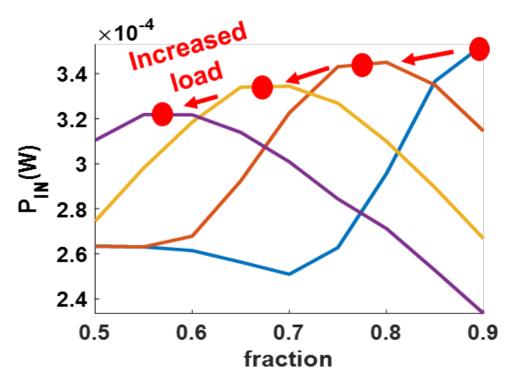

| 5.8  | Shift in maximum input power for different fractions with respect to change in load                                                                                                                                                  | 77 |

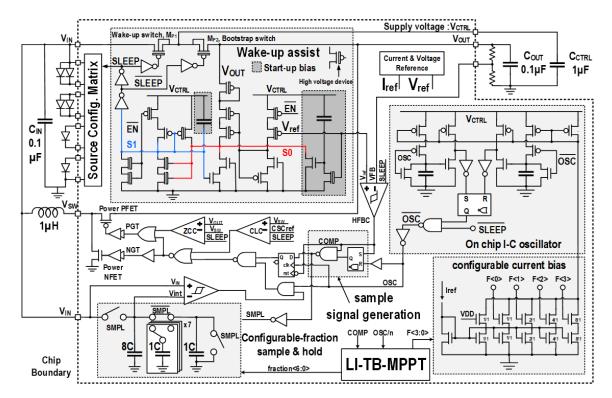

| 5.9  | Detailed schematic of proposed system implementation                                                                                                                                                                   | 79 |

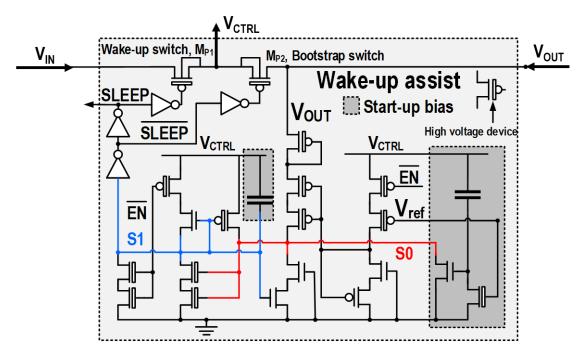

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5.10 | Analog wake-up assist (WUA) circuit schematic for robust wake-up configuration                                                                                                                                         | 80 |

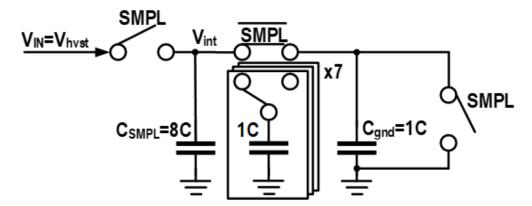

| 5.11 | Sample and hold circuit with configurable fractions through capacitive charge sharing.                                                                                                                                 | 81 |

| 5.12 | Main control path with embedded sample (SMPL) signal generation                                                                                                                                                        | 82 |

| 5.13 | Waveform for sample signal generation in the PFM control path                                                                                                                                                          | 82 |

| 5.14 | Configurable frequency oscillator schematic                                                                                                                                                                            | 83 |

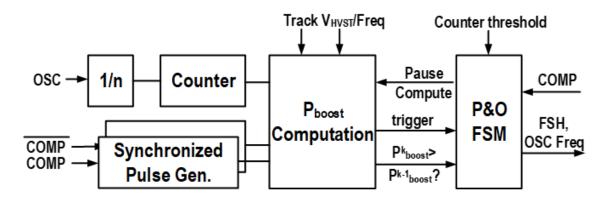

| 5.15 | LI-TB-MPPT block diagram                                                                                                                                                                                               | 84 |

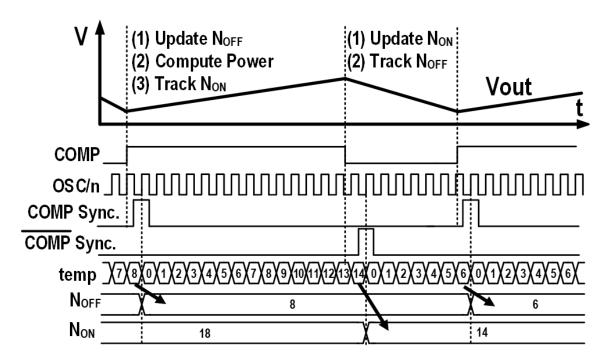

| 5.16 | MPPT operation waveform                                                                                                                                                                                                | 85 |

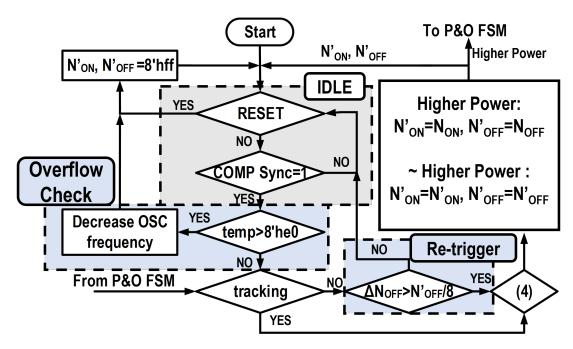

| 5.17 | $P_{boost}$ computation flow diagram with digital threshold checks                                                                                                                                                     | 86 |

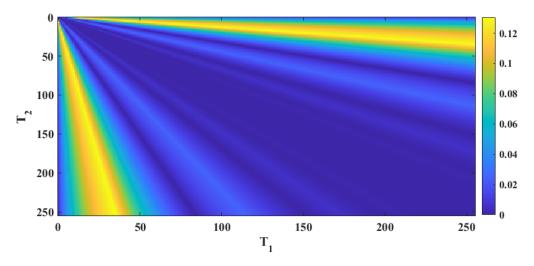

| 5.18 | Relative difference ratios from ideal computation of $y'^2/x$ to implemented quantized computation                                                                                                                     | 87 |

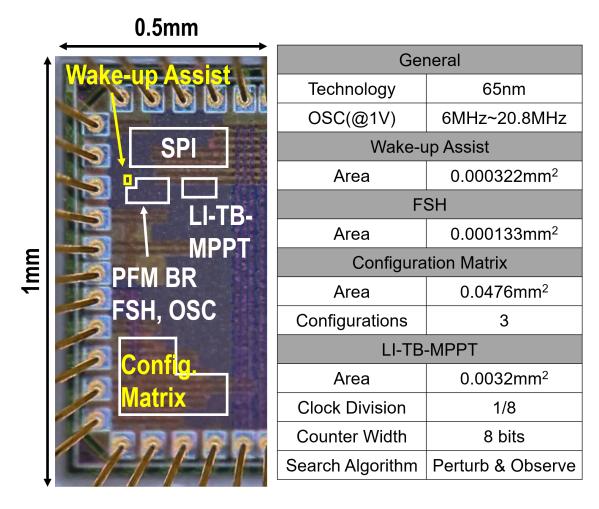

| 5.19 | Chip micrograph and specifications                                                                                                                                                                                     | 88 |

| 5.20 | Measurement waveforms for input voltage, output voltage, control voltage and SLEEP signal                                                                                                                              | 89 |

| 5.21 | Measurement waveforms for input voltage with fixed fractions (open-loop) v.s. with MPPT-tuned fractions (closed-loop). (a) DC Power-voltage. (b) Transient measurements                                                | 91 |

| 5.22 | Measurement waveforms for input voltage with frequency tuning. (a) Self-powered. (b)19 $\mu$ A load. (F is the switching frequency of the PMU.)                                                                        | 93 |

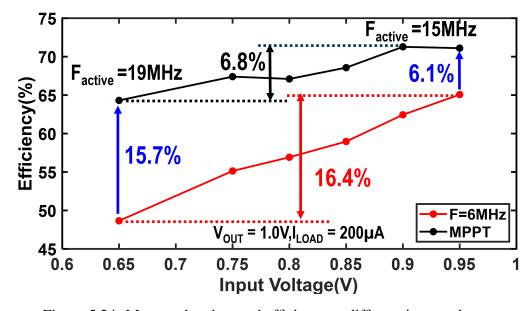

| 5.23 | Measured end-to-end efficiency and system power for MPPT tracking at different loads. (F <sub>active</sub> is active switching frequency of PMU, controlled configuring current bias in Fig. 5.14 through LI-TB-MPPT.) | 95 |

| 5.24 | Measured end-to-end efficiency at different input voltages                                                                                                                                                             | 95 |

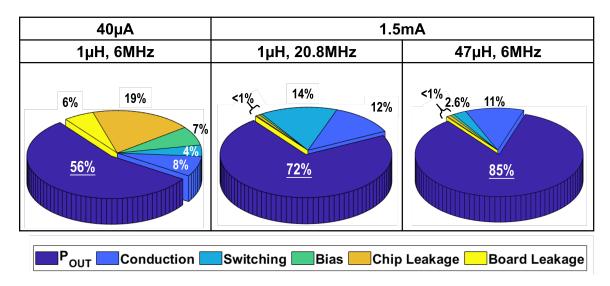

| 5.25 | Breakdown of loss components at 40 $\mu$ A and 1.5mA load ( $V_{OUT}=1.0V$ , $V_{IN}=0.95V$ ) with 1 $\mu$ H and 47 $\mu$ H inductance                                                                                 | 98 |

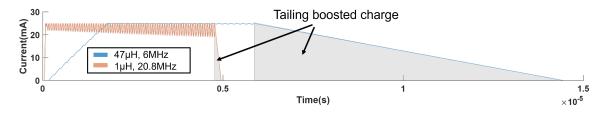

| 5.26 | 6MHz, boosting at 1.5mA load                                                                                                |

|------|-----------------------------------------------------------------------------------------------------------------------------|

| 6.1  | Comparison of RF and VL applications                                                                                        |

| 6.2  | System Architecture and target application                                                                                  |

| 6.3  | FSM for full interrogation cycle                                                                                            |

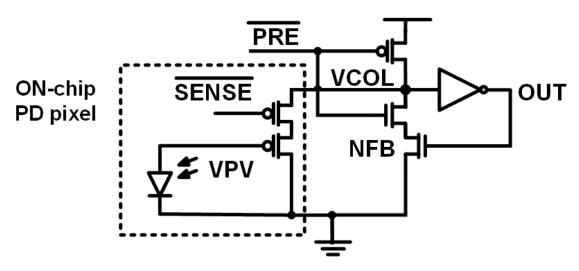

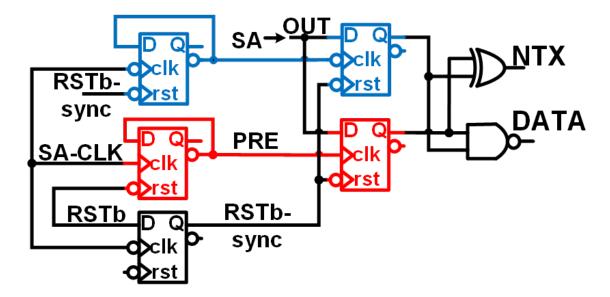

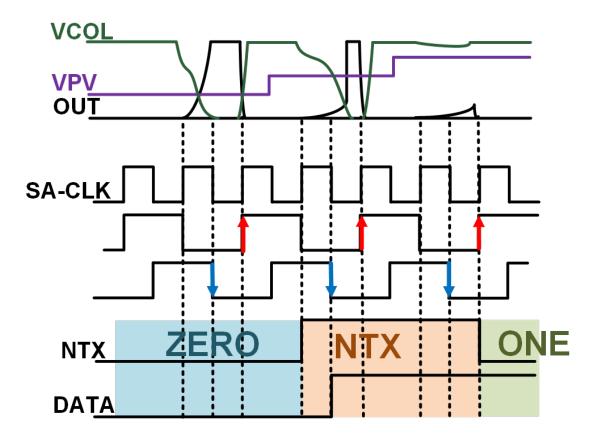

| 6.4  | (a) Optical receiver AFE input (b) CMOS APS                                                                                 |

| 6.5  | Configurable stacked photodiode array                                                                                       |

| 6.6  | Schematic for voltage-to-time conversion (VTC)                                                                              |

| 6.7  | Schematic for time-to-digital conversion (TDC)                                                                              |

| 6.8  | Sample waveform of critical nodes in RZ-SA operation                                                                        |

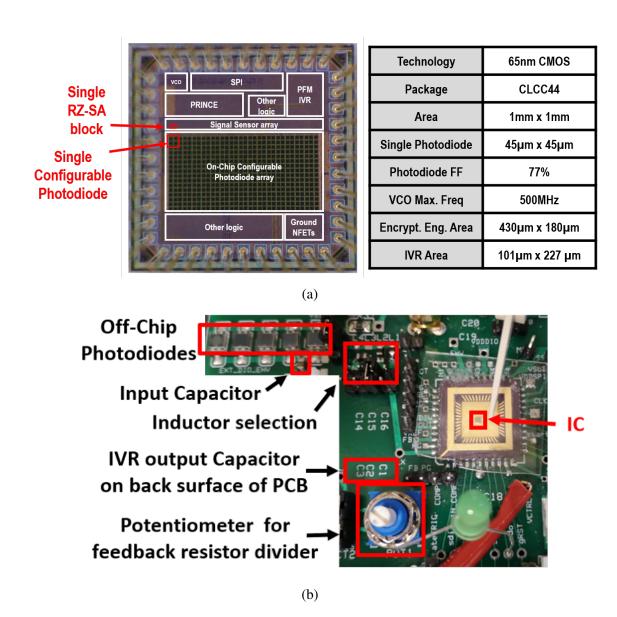

| 6.9  | (a) Chip micrograph (b) Measurement printed circuit board (PCB) 109                                                         |

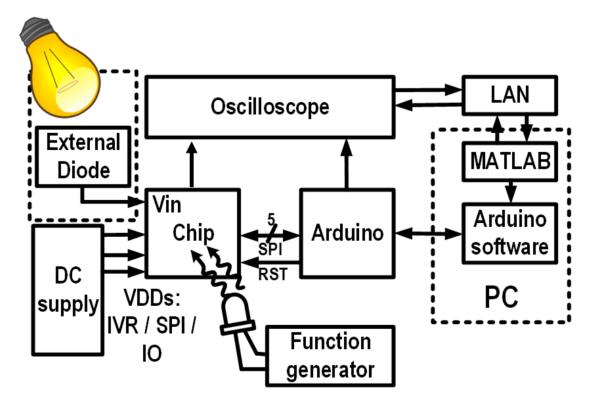

| 6.10 | Schematic of setup for measurement testing                                                                                  |

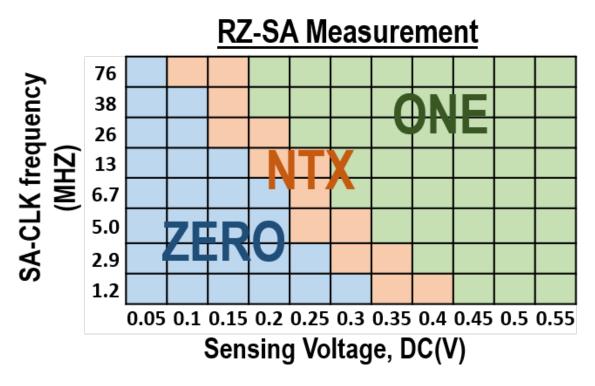

| 6.11 | Characterization of RZ-SA sensing thresholds                                                                                |

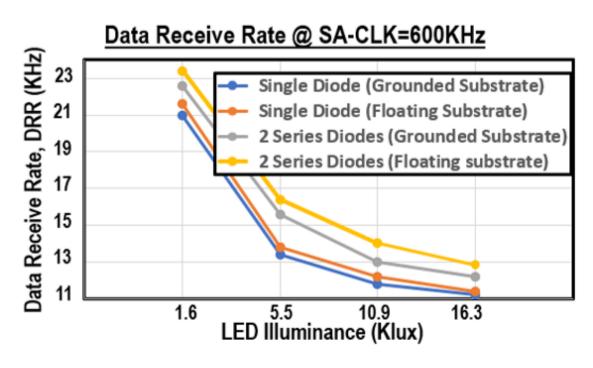

| 6.12 | Data receive rate of IC at different light intensity for fixed clock frequency 112                                          |

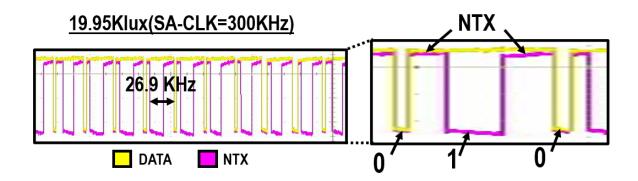

| 6.13 | Measured RZ-SA output from LED input                                                                                        |

| 6.14 | Measured critical waveforms of IC power-link during an interrogation 113                                                    |

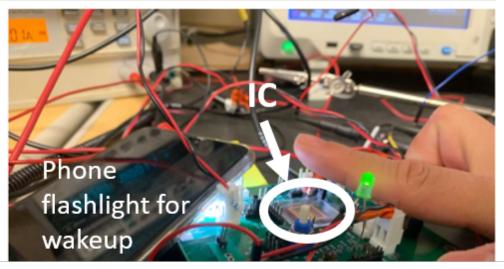

| 6.15 | Input modulation methods tested (LED and finger motions) and wake-up demonstrated with common cellphone flashlight (bottom) |

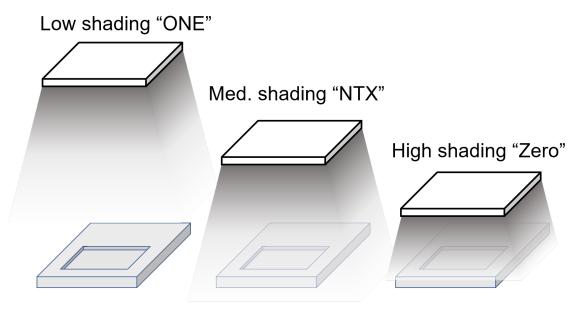

| 6.16 | Method of applying shade to IC                                                                                              |

| 7.1  | DC sweep of voltage/current reference circuit                                                                               |

| 7.2  | Power extracted from on-chip photodiodes in CMOS processes [12] 122                                                         |

| 7.3  | Layout of a single configurable diode                                                                                       |

| 7.4  | EHDS performance projection and optimization flow                                                                           |

| 7.5 | Flow diagram for performing harvesting voltage transient modeling                                             | 124 |

|-----|---------------------------------------------------------------------------------------------------------------|-----|

| 7.6 | Harvesting voltage computation steps                                                                          | 125 |

| 7.7 | Simulated capacitance of different MOS-caps per unit area of standard cell decoupling capacitor (std. decap.) | 128 |

| 7.8 | Simulated leakage of different MOS-caps                                                                       | 129 |

#### **SUMMARY**

High levels of mobility and accessibility of devices have been made possible through the development of wireless technologies. However, challenges in power delivery and security must also be addressed to realize the Internet of Everything (IoE). This is especially critical for standalone devices such as ultra-low-power sensors and active identification tags. Energy harvesting can be introduced as power links for these systems to address restrictions in cost and footprint. Increased operational lifetime and reduced maintenance cost can be achieved without relying on battery capacity to sustain depleted energy. For the purpose of authentication, wake-on-interrogate with harvesting-based power delivery can further improve security.

This thesis investigates the development of low-cost energy harvesting and delivery systems for low-power low-duty-cycle devices. Initially, we begin by designing a power management scheme for on-demand power delivery. The baseline implementation is also used to identify critical challenges for low-power energy harvesting. We further propose a robust self-powered energy harvesting and delivery system (EHDS) design as a solution to achieve energy autonomy in standalone systems. The design demonstrates a complete ecosystem for low-overhead pulse-frequency modulated (PFM) harvesting while reducing harvesting window confinement and overall implementation footprint. Two transient-based models are developed for improved accuracy during design space exploration and optimization for both PFM power conversion and energy harvesting. Finally, a low-power authentication IC is demonstrated and projected designs for self-powered System-on-Chips (SoCs) are presented. The proposed designs are prototyped in two test-chips in a 65nm CMOS process and measurement data showcase improved performance in terms of battery power, cold-start duration, passives (inductance and capacitance) needed, and end-to-end harvesting/conversion efficiency.

#### **CHAPTER 1**

#### INTRODUCTION

From motion activated lights and health monitoring devices to driver safety precautions and smart cities, the Internet of Everything (IoE), which connects not only networks of items but also users, has emerged as an inevitable outcome of increased expectations of electronic devices in this generation. The immersive user experience deeply integrated into our everyday lives has been enabled by ubiquitous devices that highlight not only machine-to-machine communication but also people-to-machine communication. The endless demand for "smart-er" electronic devices has brought many conveniences, and with them, many challenges that need to be overcome.

IoE edge devices can vary greatly in design and complexity depending on target applications but, fundamentally, a complete solution would contain four functionalities: sensing, computation, communication and power delivery. While all functions are essential to establish a self-sustained system, power delivery is the basis to guaranteeing robustness and integrity of other blocks, and the physical implementation is often the bottleneck of reducing form factor, which are all critical tributes to ensure a friction-less introduction of these devices during deployment.

Devices that can be embedded with existing appliances can conveniently utilize available power resources with proper conversion. However, standalone devices that do not have dedicated power supplies suffer under the restraint of energy storage capacity. Energy harvesting implementation in small-scale can extend lifetimes of battery-powered devices and full autonomy can be made possible by carefully balancing the trade-off between operation duty-cycle and quiescent/active power consumption.

Existing issues in prior approaches can be summarized as such:

• Low-power IoE devices and systems minimize overall power consumption through

reducing IDLE power for "OFF" periods between operations.

- Large storage capacitors/batteries are traditionally required to retain minimal system operation over long intervals (> 10s).

- Cold-start operation with harvesting sources can minimize IDLE power and provide increased robustness for self-powered operation. However, it also suffers from high overhead from additional auxiliary converters or slow boot-strapped operation.

- Energy harvesting from restricted source power (due to: limited form factor × power density) requires discrete conduction mode (PFM) harvesting systems for high efficiency.

- Compact models for discrete conduction mode power delivery lose accuracy at high conversion ratio and cannot be used for system-level design and analysis.

- Decoupled design of harvesting sources and power management units rely on near-DC fine-grain maximum power point tracking in PFM and results in wasted energy or additional system overhead.

#### 1.1 Thesis Statement

The objective of this thesis is to demonstrate that tracking maximum system power through output regulation metrics, controlling PMU operation based on harvesting capability of input sources and enabling robust cold-configuration of harvesting source networks to produce high voltage allows simultaneous tuning of harvesting efficiency and conversion efficiency, reduced passives, and shorter ACTIVE time and wake-up time, to ultimately achieve a low-cost low-overhead energy harvesting and delivery solution for self powered devices.

## **1.2** Key Contributions

The key contributions of this thesis can be summarized as:

- Development of an analytical model and simulator for PFM power conversion and harvesting: A high accuracy model is developed to quickly explore high-level design of PFM IVRs and enable tailoring the EHDS design depending on the target loading module/input source behavior. The model is verified by both simulation and silicon data. Harvesting voltage tracking is additionally implemented to constitute a semi-simulator for PFM harvesting to model EHDS operation with limited power and is used for design projections for different target specifications where harvesting sources can be integrated on-chip.

- Demonstrate system-focused solutions for ensuring robust PFM harvesting with reduced resources (capacitance, inductance, footprint): Critical challenges for PFM harvesting are identified with silicon measurements and used as guidelines to design an all-in-one solution for low-power energy harvesting. The proposed approach "borrows" energy from IDLE states by increasing the input regulation window while controlling thresholds to ensure energy equilibrium. A complete system is developed to adapt to this change including an output-based MPPT tracking algorithm, configurable sampling fraction based harvesting efficiency tuning and switching frequency based conversion efficiency tuning. The approach also reduces the passives needed for the EHDS. Wake-up assist circuitry is designed to accelerate bootstrapped cold-start operation while introducing little area overhead for implementation.

- Design and testing of a visible-light (VL) centric authentication SoC: A lowpower sensing method with on-chip photo-diodes for visible-light based data receiving is developed to and integrating with a off-chip harvesting power link to

demonstrate full interrogation cycle of a low-power authentication IC. A converter-embedded load-wake-up scheme is created with a pulse frequency modulated (PFM) boost regulator (BR) is designed with input-power based load control. The implementation decouples high-power loads from battery power and uses the PFM-BR for on-demand power delivery from harvesting sources. This approach reduces system IDLE power significantly by ensuring that only the PFM-BR remains ON and "waiting" for on-demand operation and that loads are activated only when input power is adequate. Additional power-gate control with existing PFM BR regulation signals enhances wake-up operation robustness by reducing BR load during system wake-up. Projected self-powered design with prior PFM EHDS is also presented.

#### 1.3 Organization of this thesis

**Chapter 2** will present a detailed survey of existing literature to explain and identify critical challenges for low-power self-powered systems. Existing methods that have been commonly implemented and the overhead that they introduce are also outlined.

**Chapter 3** will discuss and investigate operation of the PMU scheme that will be implemented for the EHDS in detail: a PFM boost regulator. Detailed steps to develop a high accuracy model are presented and followed by accuracy validation and possible applications.

**Chapter 4** demonstrates a power-management scheme that relieves the burden of high-power loading modules on battery power and uses the PMU to determine on-demand activation of loads. Test-chip measurements are provided to demonstrate the operation and are further used to identify and justify challenges in PFM harvesting.

**Chapter 5** presents an all-in-one PFM EHDS with fast cold-start, low area, low passives and embedded self-tuning. Design and implementation details are discussed and silicon measurements are presented.

Chapter 6 explores the target application space with a sample design: a visible light

based authentication IC. This chapter will focus on implementation details for developing a low-power on-chip signal sensing scheme. Silicon measurements for characterizing the sensing circuit and demonstrating a full interrogation cycle are discussed.

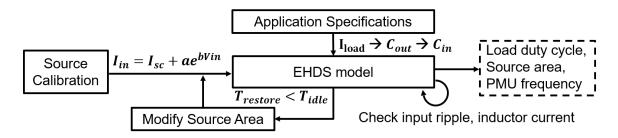

**Chapter 7** presents a design methodology to project fully self-powered SoCs that can be achieved with the designs presented in prior chapters. An EHDS semi-simulator is developed based on the DC-DC conversion model in Chapter 3 and observations in Chapter 5 to evaluate system performance and used for design space exploration.

Chapter 8 summarizes research contributions of this thesis and future research directions.

#### **CHAPTER 2**

#### LITERATURE SURVEY

#### 2.1 Power management for increased lifetime

The deployment of energy-constrained edge devices, such as ultra-low power sensors, is an integral part in the establishment of the Internet-of-Everything. One of the most critical challenges is designing power management solutions for these device platforms. Among the vast field of devices designed for IoE applications, there is a specific subset that can be distinguished by their nature of operation - devices that only operate when interrogated. A representative example of such designs can be explained by investigating the operation of authentication tags [1, 2, 3].

These devices are often required to operate over long periods of time with limited opportunities for battery replacement. Therefore, without additional measures, the system lifetime would be mainly limited by idle power, operation duty cycle and capacity of the storage [4]. Instead of remaining idle yet powered-on by batteries, the discrete and infrequent nature of operation for authentication tags has motivated the design to be normally inaccessible (powered down) to eliminate IDLE power completely and allow indefinite increase in deployment duration. These tags then wake-up only via power transfer from an interrogation probe through energy-harvesting based power links that have been developed for on-demand power delivery [5, 6, 7, 8, 9]. However, compared to typical power conversion from reliable sources, energy harvesting also brings many challenges along with its convenience.

## 2.2 Energy Harvesting

#### 2.2.1 Harvesting sources

Harvesting energy from surrounding environments, whether in the form of light, heat, or vibration is the key to relieving the usage of large batteries in a wireless application. Integrated harvesting sources such as Photovoltaic (PV) harvesters [10, 11, 12, 13, 6, 14] and Thermoelectric Generators (TEGs) [15, 16, 17, 18, 19] to achieve this goal have been proposed and demonstrated in previous literature. However, as the form factor also limits the power produced from these sources along with storage capacity, the harvested energy is generally low and highly variant. Therefore, maximizing harvested power and designing efficient power conversion with low-power solutions under these conditions are critical requirements to supplying loading modules with transduced ambient energy.

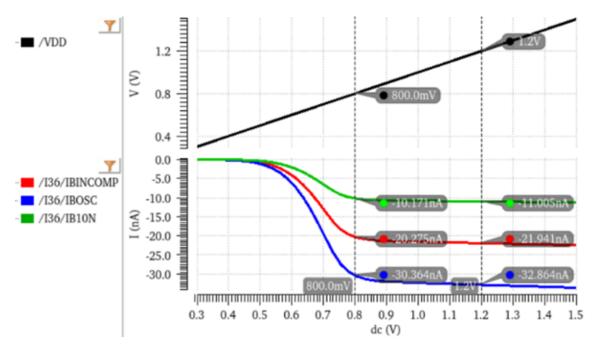

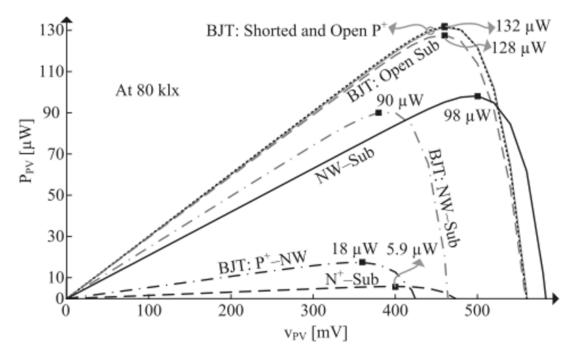

PV modules are DC harvesting sources that have been widely adopted for energy harvesting [11, 20, 14]. Electron-hole pairs are generated when light is applied to PV devices and are separated/collected through the electric field across the depletion region [12]. The biasing voltage directly modulates the depletion region and the generated photo-current  $(I_{ph})$ . Fig. 2.1 shows a plot of current-voltage and power-voltage characteristics for PV devices acquired from measurements. An advantage of PV harvesting sources is that they can generate relatively high voltage (> 0.2V) in nominal room-light environments. When properly controlled close to the maximum power point (MPP), PV harvesters can produce >1mW/cm² power density. When no current is drawn, PV devices enter open-circuit voltage (OCV) conditions, where equilibrium is reached and no photo-current is generated. When higher current is drawn from the harvesting node than what the harvester can produce, PV cells enter short-circuit/reverse-bias conditions. Therefore, a critical challenge for EHDS designs is controlling the PMU at the system level to prevent imposing undesired harvesting conditions on the harvesting source.

Figure 2.1: I-V and P-V characteristics of PV devices.

## 2.2.2 Power Management Unit (PMU) Architecture Selection

In most conventional applications, the architecture of the power converter defines the overall power conversion efficiency at given target load. However, when interfaced with non-ideal harvesting sources that have supply limited power, peak efficiency is no longer the highest priority when deciding which architecture to adopt. Instead, the adaptability to the designated range of operation conditions should be considered. Switch capacitor converters can have high efficiency when the conversion ratio is fixed but often experience efficiency drops outside of these ranges[21]. This makes the topology suitable for initial power conversion in multi-stage power conversion schemes and for applications where the operating condition can be pre-determined. pulse width modulated inductive voltage regulators can have low ripple, fast transient response time if the switching frequency and sampling rate are sufficiently high. In continuous conduction mode (CCM), the more-stable inductor current make impedance matching more controllable. However, the control is more complex and power hungry and the efficiency drop at low loads makes it more often used for high power applications [22]. Though adaptive-on-time (ADM) and PFM-controlled regulators all have lower efficiency at high load [23], they exhibit superior low-power conversion effi-

ciency by allowing idle periods in between active conversion operations. Furthermore, the nature of bang-bang PFM controls make it especially suitable for applications where the idle period is long and duty cycle is determined by the end user and not pre-designed and is the architecture that will be implemented in this thesis.

#### Conversion efficiency for low power PMUs

Regardless of architecture selected, custom design of the PMU is often required to ensure sufficiently high conversion efficiency based on the operating range of input source and output load. Techniques to improve designs and control methods of power converters have continuously been a celebrated topic of research. For example, control blocks with higher performance to improve efficiency by preventing inter-phase transition losses [24, 25] and designs with multiple control modes implemented to increase efficiency across a wide load range [23, 26] have been proposed over the years. While some methods may not be applicable when designing IVRs with a sub-mW harvested power budget, design of active control blocks in accordance with passive devices is increasingly important in this scenario. For low power operations, the efficiency bottleneck resides in the quiescent power consumed [27, 28]. Methods such as bias gating [29] to turn off certain unused functional blocks can reduce quiescent power to a minimum.

#### 2.3 Full-System Design Challenges

Self-powered devices that operate in standalone environments are critical foundations for Internet of Things applications. One of the key challenges for these end-devices is to provide a robust, yet low-cost, low-overhead system for power management. Scavenging energy from harvesting sources [30, 31] and smart management of power delivery [32, 11, 33] have become integral parts of Energy Harvesting and Delivery Systems (EHDS) for self-powered devices to alleviate the overhead of costly high-capacity batteries and minimize cost for maintenance. A compact EHDS to achieve autonomous devices can be

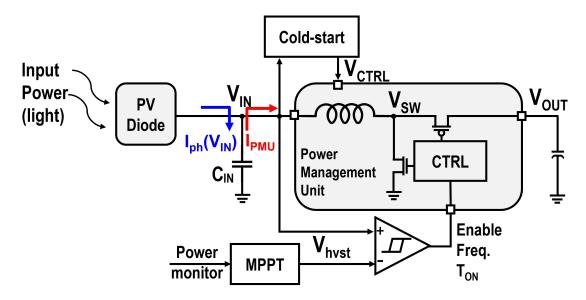

Figure 2.2: Schematic of generic EHDS.

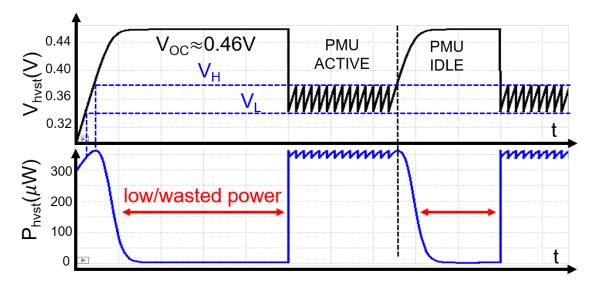

created by integrating harvesting sources with integrated voltage regulators (IVRs). However, compared to power conversion from steady sources, the power that harvesting sources can provide depends on the strength of the input (light, heat, etc.) and biasing conditions of the transducer; which are highly variant and intermittent/unstable [18, 34]. To address this unique concern, additional control circuits for maximum power point tracking (MPPT) methods and cold-start techniques have been proposed and implemented to increase the robustness of EHDSs [35, 36] to support PMU operation.

Fig. 2.2 shows a schematic for a typical EHDS. For MPPT to dynamically adapt to variations in harvesting conditions, it will need to monitor certain metrics such as voltage/current/time for power evaluation. Time-based [37, 38] and indirect MPPT methods such as Fractional Open Circuit Voltage (FOCV) [33, 36] do not require power-hungry sensors that are necessary for direct MPPT [30] and have been implemented widely for light-weight EHDSs. However, regardless of the MPPT method implemented, a common challenge for EHDSs is that large passives are often required to ensure a sufficiently tight tracking window. Cold-start methods allow the power management unit (PMU) to enter typical operating conditions from power-free ("cold") states by generating sufficiently high control voltage ( $V_{CTRL}$ ) for the PMU to initiate operation in a controlled manner.

## 2.3.1 Maximum Power Point Tracking

The harvested power from transducer sources is highly dependent on environmental settings and operating conditions. Maximum Power Point Tracking (MPPT) for harvesting sources is essential to achieving self-powered systems and extended lifetime. Without MPPT, the operating condition of the harvesting source will be dominated by the IVR operation and very likely converge close to short-circuit or open-circuit conditions, where little energy is harvested, depending on the target regulator load. Typical MPPT methods performed at the source are designed to determine the point of operation at which maximum power can be extracted from the source[10, 16, 39].

Various methods have been proposed over the years. Direct MPPT utilize voltage and/or current sensors[16] to obtain harvesting power information under different operating condition. One of the most simple and commonly adopted MPPT methods is the Fractional Open Circuit Voltage (FOCV), which is used when the harvesting source characteristics are know in advance. The maximum power point (MPP) is assumed to be at a fraction of the open circuit voltage by investigating the I-V and P-V curves. In implementation, a capacitive sample-and-hold circuits [40] are commonly used. Other methods include, but are not limited to, look-up-tables that are highly application dependent and incremental conductance (IC) and perturb and observe (P&O) methods that can be applied regardless of sensing method used [41].

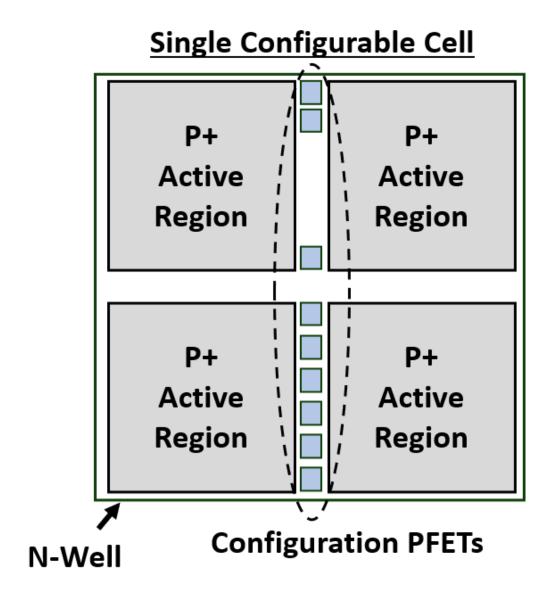

Lee et.al.[14] has proposed a different viewpoint for MPPT implementation. Instead of adapting converters to adjust to source variations, re-configuration of the source to match converter specifications when operating conditions vary can also be done. Configuration of sources is conventionally used to shift the conversion responsibility to the harvesting sources when overhead of high conversion-ratio becomes large. In this work, reconfiguration of PV cell networks that are directly connected to a battery when exposed light intensity changes is demonstrated. Because the output voltage is fixed by the battery harvesting ability of the photodiodes under illumination variations will change if this voltage is

Figure 2.3: Typical FOCV methods.

directly applied to the harvesting node. Instead of decoupling the harvesting voltage from battery voltage with a power converter, configuring the photodiode array to have more diodes in series under low light, low  $V_{MPP}$  and vice versa is done to ensure the voltage across each photodiode is closer to its  $V_{MPP}$ .

To bypass the use of voltage and current sensors that would consume a substantial amount of power, time-based MPPT has been introduced. Lopez et.al. [38] used the characteristic that increase/decrease in power can be observed at opposite sides of the MPP, which is mapped by the charging time of the input capacitor, along with perturb and observe(P&O) tracking algorithm to implement MPPT. Rawy et. al. [42] moves one step further to normalize the charging time based one DAC values to use as the metric for power estimation. Liu et.al. [20] embeds the MPPT within the power conversion and measures the time and number of steps it takes to charge the output of the converter. However, this scheme requires the overhead of an additional buffer capacitor.

#### Fractional Open Circuit Voltage MPPT

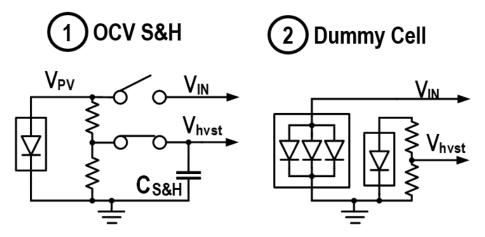

One of the most prevalent topologies used in small scale harvesting systems is the fractional open circuit voltage (FOCV) method [33, 35]. This method is based on the assumption that the maximum power point is close to a fixed fraction of the OCV ( $V_{OC}$ ), regardless of variations in input power. Fig. 2.3 shows two common FOCV implementations:

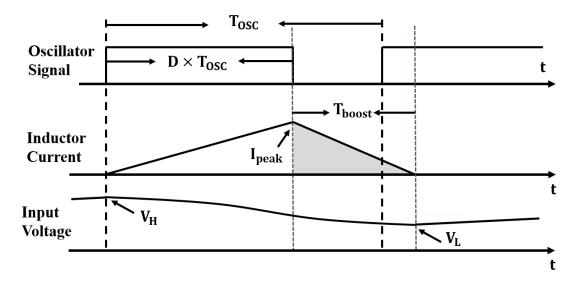

Figure 2.4: Transient of single-input single-output PFM boosting.

1) Sample & Hold through periodic disconnection of the source [40], 2) Utilizing never-harvesting dummy cells that remain in OCV conditions [11]. Once  $V_{OC}$  is obtained, a predesigned voltage division is sufficient to derive the MPP voltage  $V_{MPP}$  ( $V_{MPP} \sim 0.78 V_{OC}$  in Fig. 2.1), which is used as a reference to control the PMU for impedance matching within the EHDS. FOCV benefits from its simplicity, but also introduces undesired area/wasted-energy overhead due to the need to obtain  $V_{OC}$  [36, 31].

#### Impedance Matching Methods

Since the harvesting voltage  $(V_{hvst})$  dynamically varies with both the current generated by the harvesting source and the current drawn by the PMU (Fig. 2.2), one can also indirectly modulate the harvesting voltage by carefully controlling the impedance of the PMU. Several different impedance matching techniques have been devised to bias the harvesting source. For example, impedance matching for MPPT in EHDSs can be performed by controlling the PMU duty cycle to modulate the harvesting voltage [18]. At equilibrium, the net increase in harvesting voltage (charged by the harvester) on the input capacitor will be equal to the net decrease (discharged with current drawn by PMU). To interface with low-power PMUs such as pulse frequency modulation (PFM) integrated voltage regula-

tors (IVRs), input hysteresis comparators [32] and switching frequency modulation [19] have both been implemented in prior works. However, due to burst-harvesting periods, the use of high capacitance (> 10µF) and high inductance (> 10µH) is often necessary to filter/dampen harvesting voltage ripple (Fig. 2.4) for MPPT and reduce current ripple for improved conversion efficiency [4, 38, 27, 39, 18, 11, 19].

#### 2.3.2 Challenges for System Start-up with Power Conversion

System start-up is as crucial as its nominal operation. For small analog circuits, this is done by designing extra circuitry (often with capacitors/diode-connected transistors) to ensure initial biasing of critical nodes when supply undergoes a low to high transition. For larger systems, the startup is often built into the regulatory circuits.

Cold-start is a unique operation for EHDSs where the control voltage to the entire system starts from floating/grounded initial conditions and wakes up with harvested power. The ability to support cold-start is critical for self-powered EHDSs as it enables restoration of operation from power-drained conditions.

#### Prior Cold-start Approaches

Boot-strapped configuration of IVRs [43, 44] is the method of connecting IVR output back to its own voltage supply. When the input source is connected, boosting eventually brings the IVR to its nominal operating point and IVR regulation signifies the end of start-up. This is a commonly used method to allow the boost converters to completely power-down during idle, thus minimizing quiescent power. Kar et.al. [45] has also presented using stacked comparators to ensure initial states of switches can provide protection to circuits when the system is powered up with a voltage ramp. This is especially useful to ensure that output loads remain off to prevent start-up phases from exhausting source energy before control circuits kick in.

Bootstrapped cold-start requires voltage-invariant designs to allow boosting from low

voltages [29]. Before regulation can be reached, the PMU will be always-ON and continuously draws current from the harvesting source to boost the output voltage (which is connected back to the control voltage of the PMU). During this process, power consumption from control blocks (oscillator, analog comparators, power stage, etc.) within the PMU can be considered as increased load of the EHDS. The additional power burdens bootstrap operation and can result in excessive current drawn from the harvesting node. This reduces the harvesting voltage, and further lengthens cold-start periods.

A common approach is to have a secondary converter that is devoted for cold-start [18] to ensure that control power is decoupled from the load through a two-stage cold-start arrangement. This is usually implemented via switch-capacitor converters as they do not need high-performance voltage/current sensors to perform zero-current sensing [46]. Prior work has also demonstrated one-shot cold-start where only the control voltage of the low-side gate and driver needs to be charged [19] with the charge-pump. However, these designs present significant area overhead from large on-chip capacitance and increased transistor sizing to reduce transistor resistance at low voltages.

#### **CHAPTER 3**

#### ENERGY DELIVERY SYSTEM DESIGN AND ANALYSIS

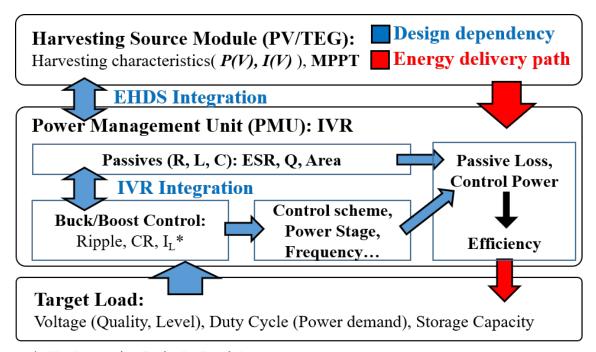

Prior approaches for designing energy harvesting and delivery systems (EHDS) often focus on tailoring the power conversion module to maximize conversion efficiency at typical operating ranges (harvesting voltage) of a target harvesting source. Then, the efficiency is used to determine the size of the input source needed based on the target load demand. By decoupling the design of each stage, integration becomes very straightforward and simple. However, while this approach provides satisfactory results, it also limits space for possible system-level optimizations. Fig. 3.1 shows a diagram of common design dependencies and considerations within an EHDS.

Viewing/co-designing the EHDS at the system level instead of treating harvesting sources and power converters as separate modules can bring many opportunities and challenges. It

<sup>\*</sup> CR: Conversion Ratio, I<sub>L</sub>: Load Current

Figure 3.1: EHDS design considerations.

Figure 3.2: Analog PFM-BR schematic. ( $R_{LX}$  is only connected in simulations to increase simulation speed.)

also requires fast analytical models for design space exploration. This is mainly because transient simulations of L/C components in the IVR often take long periods of time to converge and complete. To maximize the potential of self-powered devices, we will begin with constructing and analyzing a compact model that can be used for system-level analysis of EHDSs. This chapter presents the steps taken to create a system-level evaluation framework, which is then validated and employed to perform high-level co-design.

#### 3.1 PFM Boost Regulator Operation

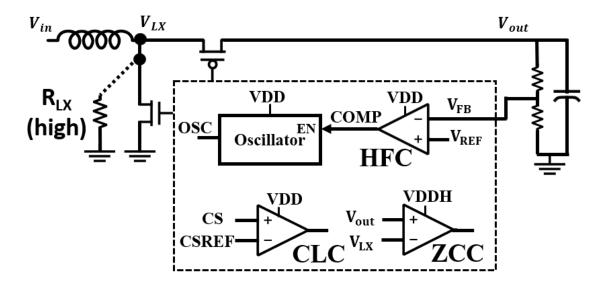

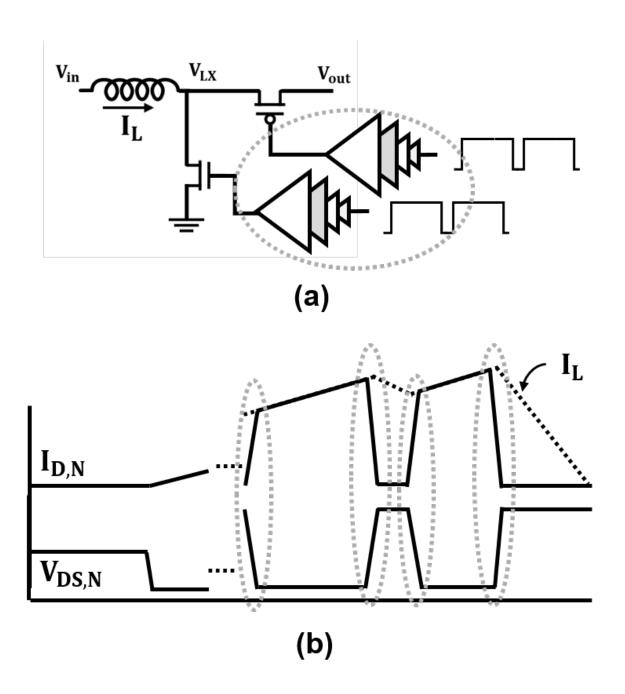

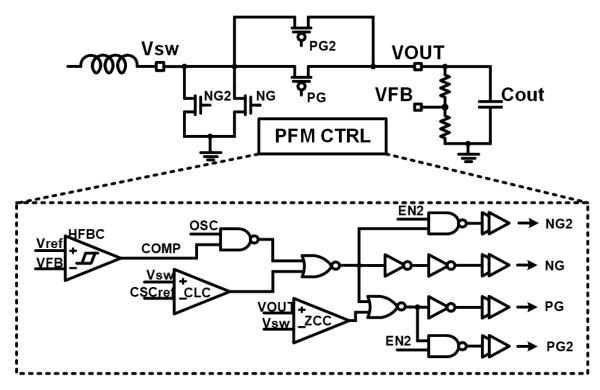

For the PMU, we will focus on PFM controlled inductive voltage regulators that have superior efficiency for a wide conversion ratio range at lower loads[26, 25]. This makes them especially suitable for creating boost regulators (PFM-BRs) for up-converting EHDS output voltage from a low harvester output voltage. The PFM boost regulator chosen to be implemented and modeled is adapted from Ahmed et. al. [47]. The regulator design consists of the following major functioning blocks: Current Limit Comparator (CLC), Zero Current Comparator (ZCC), Oscillator (OSC), and Hysteresis Feedback Comparator (HFC).

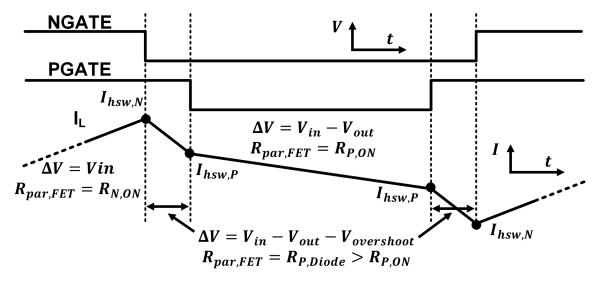

Fig. 3.2 shows a schematic of the PFM boost regulator. While the HFC defines voltage

Figure 3.3: (a) Single-pulse operation (b) Multi-pulse operation for PFM-BR

hysteresis and is the main block that controls output regulation, the CLC and ZCC are designed to modulate inductor current behavior to improve conversion efficiency. When the inductor current surpasses a pre-designed current limit (I<sub>CL</sub>), the CLC turns off the NFET and turns on the PFET to allow the current to decrease while charging the output capacitance. The ZCC is designed to turn off the PFET when the inductor current reaches zero to prevent reverse current flow from the output. The Oscillator (OSC) design defines duty cycle and switching frequency, which plays a critical role in determining power conversion capability and efficiency [43].

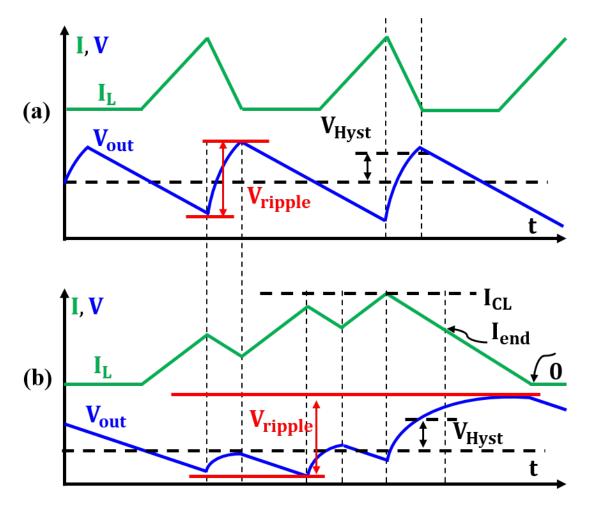

The internal operation of PFM BRs depends on the input voltage and the conversion ratio  $(V_{out}/V_{in})$ . Fig. 3.3 shows sample inductor current  $(I_L)$  and output voltage  $(V_{out})$

waveforms that represent typical PFM operations. If the input voltage is high, the boosted charge in a single pulse is sufficient to increase the output voltage above the set hysteresis level and regulation is reached (Fig. 3.3(a)). We will refer to this mode as the single-pulse mode. Under low conversion ratio and high duty cycle, this control scheme enters multipulse operation, with exemplary waveforms shown in Fig.3.3(b).

The criteria to enter multi-pulse operation is decided by whether the inductor current is allowed to build with succeeding oscillator cycles under the condition that  $V_{hyst}$  is not reached within a single pulse. This means, net change in inductor current at the end of the OFF time  $(\Delta I)$  for the oscillator should be higher than zero, as shown in (3.1-3.2). Where  $m_{pos}$  and  $m_{neg}$  represent the rising/falling slope of inductor current and  $T_{on}/T_{off}$  represent active high/low periods.

$$\Delta I = I_{\text{peak}} - I_{\text{drop}} = T_{\text{on}} m_{\text{pos}} - T_{\text{off}} m_{\text{neg}} \ge 0 \tag{3.1}$$

$$m_{\rm pos} = V_{\rm in}/L \tag{3.2}$$

$$m_{\text{neg}} = (V_{\text{out}} - V_{\text{in}})/L \tag{3.3}$$

The following derivation can be used to approximate the maximum output voltage ripple. Assuming for both single-pulse and multi-pulse operation, the hysteresis voltage threshold ( $V_{Hyst}$ ) is a designed parameter of the HFC, the output ripple can be expressed as:

$$V_{\text{out,ripple}} = V_{\text{hyst}} + V_{\text{os}} + V_{\text{droop}}$$

(3.4)

Where V<sub>os</sub> represents the overshoot above the hysteresis voltage can be expressed as:

$$V_{\text{os}} \le V_{\text{os,max}} = \left(\frac{I_{\text{CL}}}{2} - I_{\text{load}}\right) T_{\text{boost}} / C_{\text{out}}$$

(3.5)

$$T_{\text{boost}} = \frac{I_{\text{end}}L}{V_{\text{out}} - V_{\text{in}}} \le \frac{I_{\text{CL}}L}{V_{\text{out}} - V_{\text{in}}}$$

(3.6)

Where  $I_{CL}$ ,  $C_{out}$  and  $I_{load}$  are the inductor current limit, output capacitance, and load current respectively.  $T_{boost}$  is the time it takes for the inductor current to fall to zero after the hysteresis upper limit is reached. L,  $V_{out}$ ,  $V_{in}$ , are the inductance, the output voltage, and the input voltage.

From (eq. 3.5) and (eq. 3.6) it can be concluded that higher ripple occurs with higher input voltage and increase in the current limit, both of which are desired in order to supply higher load currents and higher output voltage. The droop below the lower limit of the hysteresis  $V_{droop}$  does not have a concise expression for multi-pulse operation, for single-pulse operation, it is simply  $T_{on}I_{load}/C_{out}$ .

# 3.1.1 Fundamental Limitations of PFM control

The linear slope approximations (eq.3.2-eq.3.3) can be used to quickly provide insights of fundamental limitations of the PFM control. An example is the derivation of theoretical maximum conversion ratio and its relationships with other design parameters.

During single pulse operation, the conversion ratio limit is determined by how much charge can be boosted within a single pulse and if it is sufficient to supply the target load. A mathematical expression can be derived by the following equations:

$$I_{\text{load}} \le \frac{Q_{\text{boost}}}{T_{\text{cycle}}} = \frac{Q_{\text{boost}}}{(T_{\text{on}} + T_{\text{boost}} + T_{\text{idle}})}$$

(3.7)

$$Q_{\text{boost}} = \frac{I_{\text{peak}} T_{\text{boost}}}{2} = \frac{(T_{\text{on}} m_{\text{pos}})^2}{2m_{\text{neg}}}$$

(3.8)

Because  $T_{on}$  and  $T_{boost}$  are both non-zero values, the minimum-period cycle occurs when  $T_{idle}$ =0, that is, when the idle time is exhausted by the load current. Thus, the follow-

ing equation can be derived:

$$V_{\rm in} \ge \sqrt{\frac{2V_{\rm out}I_{\rm load}L}{T_{\rm osc}D}} \tag{3.9}$$

We can observe that the duty cycle poses a lower limit to the input voltage when we wish to supply a load current at a specified output voltage with single pulse operation.

Substituting (eq. 3.2) into (eq. 3.1) we can come to the following equation (eq. 3.10), which poses a second limit to the conversion ratio during multi-pulse operation.

$$D \ge (V_{\text{out}} - V_{\text{in}})/V_{\text{out}} \tag{3.10}$$

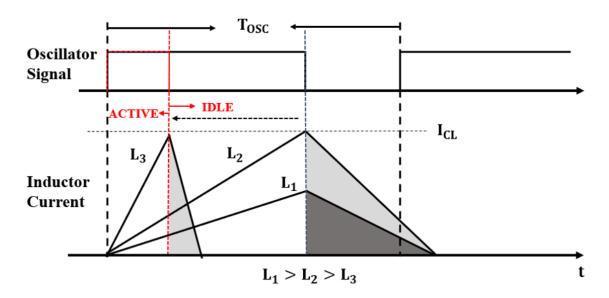

In addition to limitations of the duty cycle, the design of the oscillator also includes determining the frequency at which the oscillator would operate. However, the design of the frequency is highly associated with determining the value of the inductance. An implication of the correlation can be observed in (3.9) at fixed input and output conditions. To further explain the relationship, the effect of change in inductance at fixed frequency is shown in Fig.3.4.

Fig.3.4 shows possible outcomes of decreasing inductance in a PFM boost regulator.

Figure 3.4: Effect of Inductance.

Revisiting equations (3.2) and (3.3), decrease in inductance would increase the slope of the inductor current at fixed input/output voltage. A decrease in inductance will increase the current ripple when all other factors remain constant. The shaded area in Fig.3.4 indicates the charge that can be boosted to the output ( $Q_{boost}$ ).

For a single pulse, the charge boosted increases with a slight decrease in inductance from  $L_1$  to  $L_2$ . For multi-pulse operation, this would result in frequent exceeding of the current limit. In both cases, larger output voltage ripples can be observed due to higher peak current. The functionality of the regulator is maintained with a decrease in supply voltage quality.

Further decrease in inductance from  $L_2$  to  $L_3$  when an inductor current limit is applied will decrease the charge boosted. The current build-up behaviour observed in typical multi-pulse operation becomes restricted and converges to multiple single-pulse current packets. Not only is the benefit of increasing potential to supply higher load with multipulse operation lost, the maximum load that can be supplied is also reduced. Under the same conversion ratio and oscillator frequency, the maximum amount of charge that can be supplied to the output is limited by the inductor current pulse. It can thus be derived with the following equations:

$$Q_{\text{boost}} = \frac{I_{\text{peak}} T_{\text{boost}}}{2} = \frac{I_{\text{CL}}^2 L}{2(V_{\text{out}} - V_{\text{in}})}$$

(3.11)

$$I_{\text{load}} \le I_{\text{avg}} = \frac{Q_{\text{boost}}}{T_{\text{osc}}}$$

(3.12)

This places a theoretical upper limit to the load current at which regulation is feasible. In order to increase the ability to supply higher load currents at a smaller inductance, one can either decrease the IDLE time due to the early reach of the current limit to increase the average current or seek to re-establish multi-pulse operation. In both cases, an increase in oscillator frequency is necessary [4].

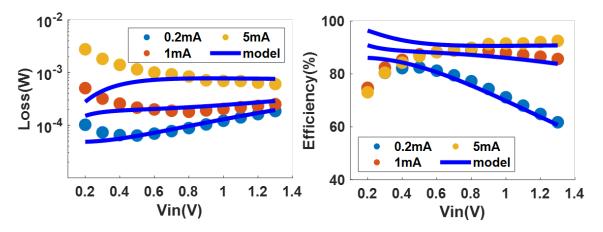

Figure 3.5: Simulated loss and efficiency compared with single pulse model results. Output voltage is set to be 1.5V for different Vin (x-axis) and load current (colored dots) pairs.

# 3.2 Analytical Model Development

PFM boost regulators use simple, low power control that directly modulates the inductor current based on pre-designed thresholds. However, the modeling of PFM operation is not as straightforward. Depending on operation conditions (input voltage, output voltage, load current, etc.) and design components (inductor value, capacitor value, oscillator frequency, etc.) transient behavior of PFM-BR can vary greatly making compact modeling of power loss challenging. Fortunately, the effect of variations in the design space can be traced by investigating their effect on changing the inductor current waveform and the transient behavior of feedback control loop.

# 3.2.1 Prior Work - Single-Pulse Model

Analytical loss models for single-pulse operation have been proposed [29]. The model can be used to evaluate conversion efficiency by computing loss factors (conduction loss, switching loss, and bias power) individually based on the derived peak current of the inductor. However, comparison with transistor-level simulations show under-estimation of loss at lower input voltage when multi-pulse operations are entered (Fig. 3.5). This is because the inductor current behaviour for multi-pulse operation is dependent of multiple factors

Figure 3.6: Inductor current with parasitic resistance from power stage/wire/bump etc.

and can no longer be approximated with triangular current pulses for single-pulse. Hence, a different approach for modeling loss is necessary to allow wide conversion ranges that cover both single and multi-pulse operations.

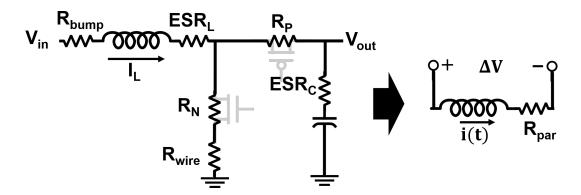

### 3.2.2 Charge-equilibrium Based Model

To address the loss in accuracy in single-pulse models, we have constructed a loss-model framework by computing and tracking inductor current behavior under design parameter variations. The model constructed in this section is based on charge equilibrium equations and includes non-ideal parasitic resistances (Fig. 3.6) when modeling inductor current behavior to increase the accuracy of the model. The effect of parasitic resistance is increasingly critical when the source voltage is low and size of power switches are limited to drive low output load. Switch resistances should be considered depending on the state of the switches as shown in the following equations [48].

When the NFET switch is ON and PFET switch is OFF (Charging phase):

$$V_{\rm in} - i(t)R_{\rm charge} = L\frac{di(t)}{dt}$$

(3.13)

When the NFET switch is OFF and PFET switch is ON (Boosting phase):

$$V_{\rm in} - V_{\rm out} - i(t)R_{\rm boost} = L\frac{di(t)}{dt}$$

(3.14)

$R_{charge}$  and  $R_{boost}$  indicate the parasitic resistances along the charging and boosting path, respectively. Assuming the schematic shown in Fig. 3.6, they can be computed as:

$$R_{\text{charge}} = R_{bump} + ESR_L + R_N + R_{wire} \tag{3.15}$$

$$R_{\text{boost}} = R_{bump} + ESR_L + R_P + ESR_C \tag{3.16}$$

These resistances pose an additional limit to the maximum inductor current  $i_{max}$  as shown in (3.17), when the voltage across the switch is equal to the input voltage and there can no longer be an increase in inductor current.

$$i_{\text{max}} = \frac{V_{\text{in}}}{R_{\text{charge}}} \tag{3.17}$$

Based on Fig. 3.6 and combining all parasitic resistances, the inductor current can be generalized to:

$$i(t) = \frac{\Delta V}{R_{\text{par}}} + \left(i_0 - \frac{\Delta V}{R_{\text{par}}}\right)e^{-\frac{t}{\tau}}$$

(3.18)

where  $i_0$  is the starting current, which is non-zero during multi-pulse operation;  $\tau$  is the time constant L/R<sub>par</sub>; i(t) is the inductor current;  $\Delta V$  is the voltage across the inductor and the parasitic resistance; and R<sub>par</sub> represents the sum of all parasitic resistances. As explained previously, the value of R<sub>par</sub> will need to be replaced when modeling different phases of IVR operation, depending on the state of the power switches (i.e. charging/boosting current path) and different values will need to be applied during transient modeling accordingly.

It can then be derived without loss of generality that the change in inductor current over a time period is:

$$i_{\text{step}}(t) = \left(\frac{\Delta V}{R_{\text{par}}} - i_0\right)(1 - e^{-\frac{t}{\tau}})$$

(3.19)

The total charge that flows through the inductor during a specific time period is:

$$Q_{\text{step}}(t) = \frac{\Delta V}{R_{\text{par}}} t - (\frac{\Delta V}{R_{\text{par}}} - i_0)(\frac{L}{R_{\text{par}}})(1 - e^{-\frac{t}{\tau}})$$

(3.20)

The time for the inductor current to reach a certain value can be approximated with:

$$\Delta T(i_0, I_{\text{end}}) = \frac{(I_{\text{end}} - i_0)L}{\Delta V - (I_{\text{end}} + i_0)R_{\text{par}}/2}$$

(3.21)

It can be proven that these equations converge to their linear-slope counterparts when  $R_{par}$  is negligible. Using these equations, the operation of a PFM boost regulator is simplified into identifying the inductor current behavior in the active and idle phases of one regulation cycle. The active (boosting) phase of the cycle is defined by the period of time for a number of pulses to boost a total amount of charge equal to the hysteresis difference in addition to the charge consumed by load current:

$$\sum_{n=1}^{k} Q_{\text{boost,k}} \ge C_{\text{out}} V_{\text{hyst}} + \int_{0}^{kT_{\text{osc}}} I_{\text{load}} dt$$

(3.22)

This phase can also be segmented into multiple sub-"packets" if the inductor current falls back to zero before the equation 3.22 is met (usually after surpassing  $I_{CL}$  early during ON time of OSC):

$$\sum_{n=1}^{m} I_{\text{step,m}} \le 0, m \le k \tag{3.23}$$

The idle phase is simply the time taken for the load current to discharge hysteresis voltage in the output capacitor.

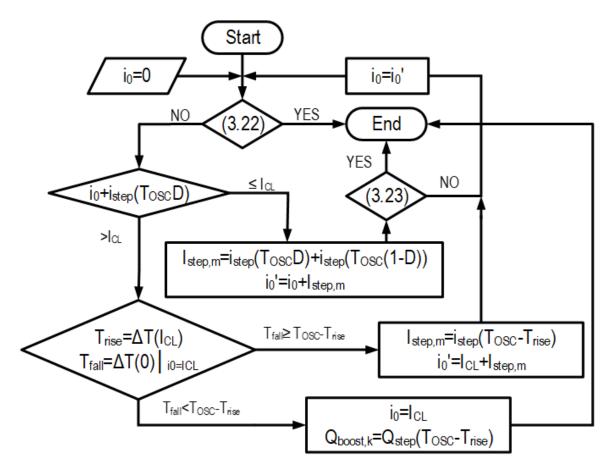

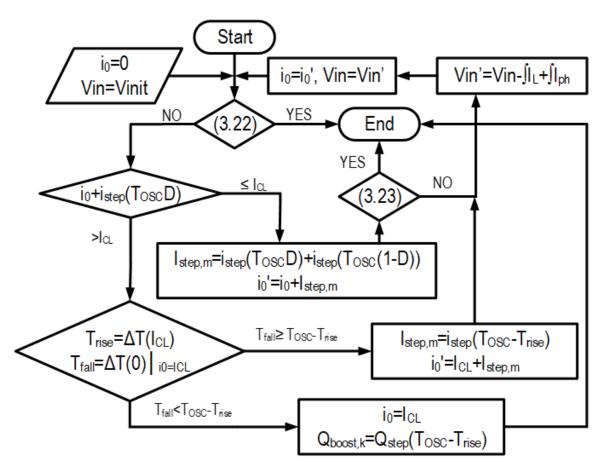

With these constraints for identifying high-level cycles and sub-packets of charge boosting known, the remainder of the model is built upon multiple check statements that mimic the operation of the CLC, OSC and ZC. A flow diagram for the model is as shown in Fig. 3.7. The computation begins with an initial current of zero and checks conditions for equation (3.22) and (3.23) while inductor current change is derived and tracked in a

Figure 3.7: Flow diagram for performing inductor current transient modeling.

# recursive manner.

For each loop, the step increase in current during the charging phase (low-side NFET ON, high-side PFET OFF) is summed with the initial current and then compared to the current limit ( $I_{CL}$ ). This criteria models an ideal current limit comparator behavior. If the current limit is reached, the inductor current step in this oscillator cycle is recomputed and checked if a zero current is resulted from the boosting phase (low-side NFET OFF, high-side PFET ON). This models zero current comparator behavior when boosting starts earlier within an OSC period after hitting  $I_{CL}$ . The loop continues until the constraints are met. The current behaviour is logged and used for loss computation with the loss model explained in the following subsection.

Figure 3.8: Conduction loss from (a) inductor current (b) NFET drain current (c) PFET drain current, (d) current to capacitor.

# 3.2.3 Loss Components Modeled

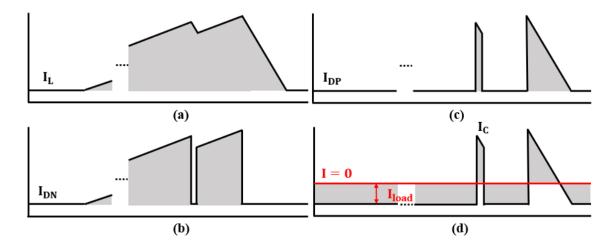

The tracked inductor current within a regulation period is used to compute the contribution of the following loss factors: conduction loss, switching loss, and control power [48].

#### Conduction Loss

Conduction loss is due to resistive loss when current flows through components and is converted into heat dissipation. Therefore, it is also often referred to as I<sup>2</sup>R loss. Similar to the phase-dependent computation of inductor current, conduction loss is calculated by first determining the contribution of each component depending on the phase of switching and applying eq. 3.18. The current waveforms of the components that contribute most to conduction loss along the EDS path are shown in Fig. 3.8, where the shaded areas indicate when conduction loss is present. Dead-time designed in driver stages to prevent reverse current can also be modeled as increased resistance in the PFET. Fig. 3.9 shows the voltage and parasitic resistance for power gates used during the boosting phase. Using these parameters, the I<sup>2</sup>R loss are estimated using a squared then integrated version of equation

Figure 3.9: Inductor current behavior and parameters used for calculation.

(3.18) and added across loops shown in Fig. 3.7:

$$\int {I^2}_{\rm step}(t) = (\frac{\Delta V}{R_{\rm par}})^2 t - (\frac{\Delta V}{R_{\rm par}} - i_0) (\frac{4\Delta V}{R_{\rm par}} + (i_0 - \frac{\Delta V}{R_{\rm par}}) (1 + e^{-\frac{t}{\tau}})) (\frac{L}{2R_{\rm par}}) (1 - e^{-\frac{t}{\tau}}) \end{(3.24)}$$