# DESIGN, MODELING, OPTIMIZATION, AND BENCHMARKING OF INTERCONNECTS AND SCALING TECHNOLOGIES AND THEIR CIRCUIT AND SYSTEM LEVEL IMPACT

A Dissertation Presented to The Academic Faculty

by

Victor Huang

In Partial Fulfillment

of the Requirements for the Degree

Doctor of Philosophy in the

School of Electrical and Computer Engineering

Georgia Institute of Technology December 2021

**COPYRIGHT © 2021 BY VICTOR HUANG**

# DESIGN, MODELING, OPTIMIZATION, AND BENCHMARKING OF INTERCONNECTS AND SCALING TECHNOLOGIES AND THEIR CIRCUIT AND SYSTEM LEVEL IMPACT

# Approved by:

Dr. Azad Naeemi, Advisor School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Sung-Kyu Lim School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Jeffrey Davis School of Electrical and Computer Engineering Georgia Institute of Technology Dr. Muhannad S Bakir School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Vanessa Smet School of Mechanical Engineering Georgia Institute of Technology

Date Approved: December 2, 2021

#### ACKNOWLEDGEMENTS

First, I would like to thank my advisor Professor Azad Naeemi. This entire research journey was only possible because of his kind and patient support. Whenever I encountered any difficulties with my work, he was always ready with kind words and unwavering support. I would also like to thank all my lab mates through the years: Shaloo, Ahmet, Vachan, Yu-Ching, Chia-Sheng, Sourav, Rouhollah, Ramy, Samantha, Siri, Daeun, Piyush, and Mohammad. I would like to give special thanks to my lab mates Chenyun and Divya who have always been there to help me during my research. Whenever I had questions or doubts about my work, they would always provide much needed insight, perspective, advice, and words of encouragement. I'm also very grateful to Nick, who personally rearranged his schedule twice to be there for my proposal and defense. He sat there with me all those late nights making sure I finished my slides. His presence helped me get across the finish line.

I have made so many wonderful and supportive friends throughout my time in Atlanta. I met Vanessa early into my degree and she quickly become one of my closest and longest friend. She is always there to provide emotional support and is always ready to cheer me on. My time here in Atlanta would not have been the same without all of my dearest friends: Janae and Maarten, Andrew and Jessica, Joan and Alicia, Subin and Nick, April, Scott, Christine, Osama, Bruce, and countless more.

I would like to thank my high school and college friends who have been with me for so long. We've all grown up and gone our own ways, forging our own paths in this world, and yet we still find the time to catch up with each other through the years.

Lastly, I would like to thank my parents Feng-Yueh Huang and Hwei-Yun Huang for their unfathomable patience during this journey. They have always been the bedrock of my life, giving me so many opportunities in life. I have never once doubted their love and support, and none of this would have been possible without them.

Thank you to everyone who has helped me through this journey. There have been so many meaningful interactions with people that I appreciate and will always remember. It has been a long ride, and I'm forever grateful for everyone's kindness, help, and support.

# TABLE OF CONTENTS

| ACKNOWLEDGEMENTS                                                     | iv        |

|----------------------------------------------------------------------|-----------|

| LIST OF TABLES                                                       | viii      |

| LIST OF FIGURES                                                      | ix        |

| LIST OF SYMBOLS AND ABBREVIATIONS                                    | xi        |

| SUMMARY                                                              | xiv       |

| CHAPTER 1. Introduction                                              | 1         |

| 1.1 Device Scaling: Moore's Law and Dennard Scaling                  | 1         |

| 1.1.1 Traditional Planar Device Scaling Challenges                   | 2         |

| 1.1.2 Challenges of device scaling sub 22nm: Movement to FinFET      | 2 2       |

| 1.1.3 Gate-All-Around devices and Complementary Logic                | 3         |

| 1.1.4 Beyond CMOS Devices: TFETs                                     | 4         |

| 1.2 Interconnect Scaling and Challenges                              | 5         |

| 1.2.1 Traditional Al interconnects to Cu                             | 6         |

| 1.2.2 Challenges of Cu interconnects and size effects                | 8         |

| 1.2.3 Low- κ dielectric and air gap                                  | 8         |

| 1.2.4 MB/Liner and Reliability Challenges                            | 9         |

| 1.2.5 New Metal Materials for Scaling of Local Interconnects         | 10        |

| 1.3 Thesis Overview                                                  | 11        |

| CHAPTER 2. Stacked Logic Device for Lateral Nanowire Field-Effect Tr | ansistors |

| (LFET) 12                                                            |           |

| 2.1 Stacked Device Layout and Structure                              | 13        |

| 2.2 Device Parasitic Modeling                                        | 18        |

| 2.2.1 Parasitic Capacitance                                          | 19        |

| 2.2.2 Parasitic Resistance                                           | 20        |

| 2.3 System-Level Modeling                                            | 20        |

| 2.4 System-level Benchmarking Results                                | 21        |

| 2.5 Conclusion                                                       | 26        |

| CHAPTER 3. Generic System-Level Modeling and Optimization for Beyo   |           |

| CMOS Device Applications                                             | 27        |

| 3.1 Generic System Model                                             | 28        |

| 3.1.1 Empirical CPI Model                                            | 28        |

| 3.1.2 Optimization Methodology Flow                                  | 29        |

| 3.1.3 Input Data and Device Technologies                             | 30        |

| 3.2 Simulation Results                                               | 31        |

| 3.2.1 System Model Comparison of ALU and Single Logic Core           | 31        |

| 3.2.2 Power Breakdown                                                | 32        |

| 3.2.3 Throughput Optimization                                        | 34        |

| 3.2.4 Throughput vs Power Budget                                            | 35       |

|-----------------------------------------------------------------------------|----------|

| 3.2.5 System Optimization Trends for V <sub>dd</sub> and N <sub>gates</sub> | 36       |

| 3.2.6 Optimization with minimum EDP: Single Core vs Optimized Single C      |          |

| 3.3 Conclusion                                                              | 41       |

| CHAPTER 4. Modeling and Benchmarking Back End Of The Line Techr             | ologies  |

| on Circuit Designs at Advanced Nodes                                        | 42       |

| 4.1 Design Flow and Methodology                                             | 42       |

| 4.1.1 Design Flow Overview                                                  | 42       |

| 4.1.2 ASAP7 PDK                                                             | 43       |

| 4.2 BEOL Modeling, Technology Development and Metal Barrier Scalin          | ıg Case  |

| Study                                                                       | 44       |

| 4.2.1 ICT Development and Wire and Via Resistance Models                    | 44       |

| 4.2.2 Metal Barrier Engineering                                             | 45       |

| 4.3 Experimental Setup and Results Comparison                               | 46       |

| 4.3.1 Experimental Setup                                                    | 46       |

| 4.3.2 Metal Barrier BKM vs Thin Scaling Results                             | 47       |

| 4.3.3 Metal Barrier Thin vs ImpVia Results                                  | 48       |

| 4.4 Conclusion                                                              | 49       |

| CHAPTER 5. From Interconnect Materials and Processes to Chip Level          |          |

| Performance: Modeling and Design for Conventional and Exploratory Con-      | cepts 51 |

| 5.1 Device and Interconnect Scaling Trends                                  | 52       |

| 5.2 Modeling and Benchmarking Methodology                                   | 54       |

| 5.3 Interconnect Scaling and Sensitivity Scenarios and performance Res      | ults 56  |

| 5.3.1 Scenario 1: BEOL Stack Metal Barrier Scaling                          | 58       |

| 5.3.2 Scenario 2:Local Interconnect/Via Metal Barrier Scaling               | 59       |

| 5.3.3 Scenario 3: Alternative Metals and High Aspect Ratio                  | 62       |

| 5.4 Conclusion                                                              | 62       |

| CHAPTER 6. Conclusion, Future Scaling Challenges and Outlook                | 66       |

| 6.1 Conclusion                                                              | 66       |

| 6.2 Future Work, Scaling Challenges and Outlook                             | 67       |

| REFERENCES                                                                  | 69       |

# LIST OF TABLES

| Table 1 – Standard 2D Cell and Stacked Cell Footprint Summary and Comparison        | 17 |

|-------------------------------------------------------------------------------------|----|

| Table 2 – Process Assumptions for 2x2 LFET                                          | 18 |

| Table 3 – Parasitic Input Capacitance for Standard and Stacked Cells, and Parasitic |    |

| Resistance for Stacked Cells for 2x2 LFET Inverter                                  | 19 |

| Table 4 – Table of Input Parameters for System Model Comparison of ALU and Single   | •  |

| Logic Core                                                                          | 33 |

| Table 5 – Optimized Minimum EDP Results for a Range of Power Budgets for Different  | nt |

| Device Technologies                                                                 | 40 |

| Table 6 – BEOL Key Layer Parameters and Resistances                                 | 46 |

| Table 7 – Iso-Area Performance Results Comparison between current industry BKM,     |    |

| Thin Scaled MB, and Improved Via BEOL RC Extraction                                 | 49 |

| Table 8 – Key ASAP7 Technology Design Parameters                                    | 55 |

| Table 9 – Different Scenario Assumptions in this Work for MB and Adhesion (TiO2)    |    |

| Thickness for Bottom and Sidewalls                                                  |    |

| Table 10 – AES Results for Fixed P&R Design                                         | 63 |

| Table 11 – LDPC Results for Fixed P&R Design                                        | 64 |

| Table 12 – Final Optimization Results for AES Circuit                               | 65 |

| Table 13 – Final Optimization Results for LDPC Circuit                              | 65 |

# LIST OF FIGURES

| Figure 1 – Moore's Law: History of Scaling and Innovations [4] 1                                             |

|--------------------------------------------------------------------------------------------------------------|

| Figure 2 – Eras of Transistor Scaling Innovations [2-5]                                                      |

| Figure 3 – (a) Transmission Electron Microscopy (TEM) of PMOS Tri-gate/FinFET                                |

| channel under the gate [4] (b) Tri-gate/FinFET transistor architecture [7]                                   |

| Figure 4 – CMOS Chip Structure in 2000s (Cepheiden, Wikipedia 2006)                                          |

| Figure 5 – Dual Damascene Process [5]: a) Deposition of ILD with etch stop, b) Pattern                       |

| and etch via trench, c) Pattern and etch wire trench, d) barrier and metal seed-layer                        |

| deposition, e) Cu electroplating, CMP, and capping layer                                                     |

| Figure 6 – Comparison of Cu, Ru, and Co Line Resistance versus Total Conductor Area                          |

| [23]                                                                                                         |

| Figure 7 – 3D sketch of a standard cell 2x2 LFET inverter and a stacked 2x2 LFET                             |

| •                                                                                                            |

| Figure 8 – Top view of stacked 2-Input NAND structure and inverter. The top layer                            |

|                                                                                                              |

| shows the M1 supply and ground rails with the PFET transistors connections, and the                          |

| bottom layer shows the NFET connections                                                                      |

| Figure 9 – Cross sectional view of stacked 2-Input NAND structure and inverter. The cell                     |

| height in metal pitches is numbered on top                                                                   |

| Figure 10 – (a) Projected power breakdown for standard 2x2 LFET at 0.6V supply                               |

| voltage and 1.1GHz. (b) Percent system power savings of stacked logic compared to                            |

| standard LFET cell at 1.1GHz. Supply voltage is varied from 0.6V to 0.4V and chip area                       |

| is varied from 1mm <sup>2</sup> to 0.7mm <sup>2</sup> . The percent power breakdown for different categories |

| are normalized to the total power                                                                            |

| Figure 11 – (a) Maximum operating frequency (Max f) and power density constrained                            |

| frequency comparison of standard and stacked cells. Stacked cell chip area is varied from                    |

| 1 to 0.7mm <sup>2</sup> . (b) Energy per clock cycle comparison for stacked and unstacked logic.             |

| Frequency is set to 1.1GHz, supply voltage is varied from 0.6 to 0.4V, and stacked cell                      |

| chip area is varied from 1mm <sup>2</sup> to 0.7mm <sup>2</sup>                                              |

| Figure 12 - Input on-current and on-resistance data for different device technologies 31                     |

| Figure 13 – Trend comparison of Energy vs Delay between BCB model with Generic                               |

| System model for a 32-bit ALU                                                                                |

| Figure 14 – Power breakdown comparison for 32-bit ALU and single core processor                              |

| (1Core) for different device technologies                                                                    |

| Figure 15 – CMOS HP optimal throughput contour plot. Area is fixed at 5mm <sup>2</sup> . Power               |

| budget is set to 4.6 W, with a power density of 93W/cm <sup>2</sup> 35                                       |

| Figure 16 – Optimal throughput result versus power budget for different device                               |

| technologies                                                                                                 |

| Figure 17 – Optimal V <sub>dd</sub> trends for different device technologies and power budgets 37            |

| Figure 18 – Optimal number of gates (Ngates) trend for different device technologies and                     |

| power budgets                                                                                                |

| Figure 19 – Energy vs Delay per instruction results for different device technologies. The                   |

| solid lines represent the optimized results for a range of power budget. The circle                          |

| indicates the optimized results that correspond to the minimum energy delay product for                      |

| that range of power budgets. The lower left-hand is the preferred corner that corresponds |

|-------------------------------------------------------------------------------------------|

| to a lower energy delay product                                                           |

| Figure 20 – Normalized energy delay product comparison between the non-optimized          |

| case and the optimized case from a range of power budgets                                 |

| Figure 21 - General Design Flow and Modeling framework for circuit-based analysis 44      |

| Figure 22 – (a) Local interconnect model cross-section and GDS layout of case BKM for     |

| (b) AES and (c) LDPC Circuit                                                              |

| Figure 23 – Interconnect and Device Capacitance Trends for advancing technology nodes     |

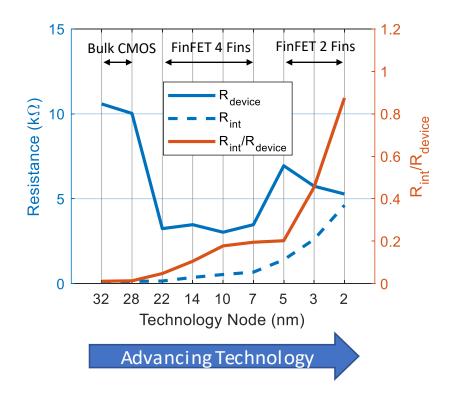

| Figure 24 – Interconnect and device resistance trends for advancing technology nodes . 53 |

| Figure 25 - BKM GDS layout for (a) AES and (b) LDPC Circuit 57                            |

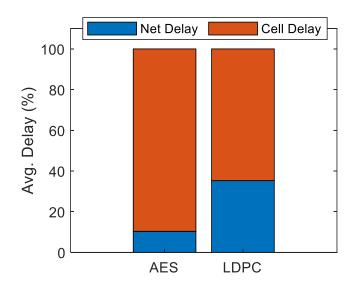

| Figure 26 – Percent net delay of top 50 critical paths for AES and LDPC circuits based    |

| on BKM P&R. Total net delay accounts for 10% and 35% of the total delay for the top 50    |

| critical paths of AES and LDPC circuits, respectively                                     |

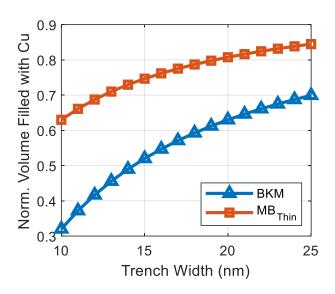

| Figure 27 – Proportion of wire filled with Cu                                             |

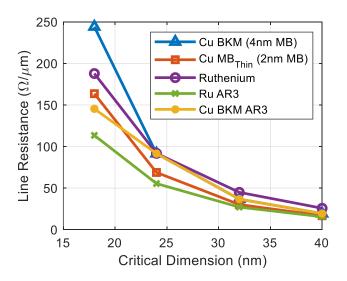

| Figure 28 – Line resistance for different CD                                              |

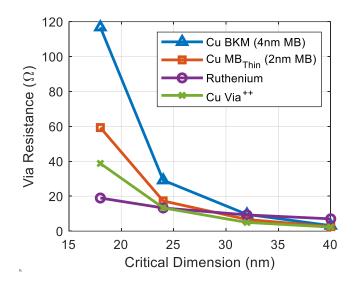

| Figure 29 – Via resistance for different CD                                               |

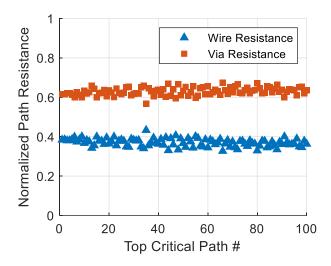

| Figure 30 – Normalized breakdown of net resistance from wire vs via for the top 100       |

| critical paths. Results are based on AES P&R for BKM. Average Rwire is 37% for top        |

| 100 paths                                                                                 |

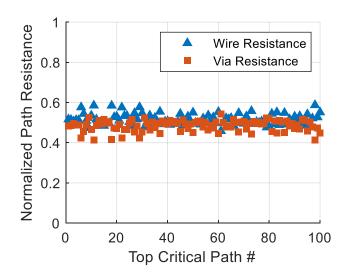

| Figure 31 – Normalized breakdown of net resistance due to wire vs via for the top 100     |

| critical paths based on P&R results for BKM of LDPC circuit. Average Rwire is 52% for     |

| top 100 paths                                                                             |

#### LIST OF SYMBOLS AND ABBREVIATIONS

**AES Advanced Encryption Standard** Al Aluminum ALD **Atomic Layer Deposition ALU** Arithmetic Logic Unit AR Aspect Ratio **BCB** Beyond CMOS Benchmarking BEOL Back End of Line CAD Computer Aided Design CD Critical Dimension CGP Contacted Gate Pitch CMOS Complementary Metal-Oxide-Semiconductor CMOSHP CMOS High Performance CMOSLV CMOS Low Voltage **CMP** Chemical-Mechanical Polishing Co Cobalt CPI Cycles per Instructions CPU Central Processing Unit Cu Copper CVD Chemical Vapor Deposition DTCO Design Technology Co-Optimization EDA Electronic Design Automation **Energy Delay Product** EDP

FEOL Front End of Line

FinFET Fin Field-Effect Transistor

GAA Gate-All-Around

IC Integrated Circuit (IC)

ILD Interlayer Dielectric

LDPC Low Density Parity Check

LER Line Edge Roughness

LFET Lateral Nanowire Gate-All-Around Field-Effect Transistor

MB Metal Barrier

MP Metal Pitch

NW Nanowire

P&R Place and Route

PDK Process Design Kit

PDP Power Delay Product

PPA Power Performance Area

PVD Physical Vapor Deposition

RC Resistance Capacitance

RMG Replacement Metal Gate

RTL Register Transfer Level

Ru Ruthenium

SCE Short Chanel Effect

Ta Tantalum

TaN Tantalum Nitride

TEM Transmission Electron Microscopy

TFET Tunneling Field Effect Transistors

ThinTFET Two-dimensional heterojunction interlayer TFET

TMD Transition Metal Dichalcogenide

VNW Vertical Nanowire

#### **SUMMARY**

This research focuses on the future of integrated circuit (IC) scaling technologies at the device and back end of line (BEOL) level. This work includes high level modeling of different technologies and quantifying potential performance gains on a circuit and system level. From the device side, this research looks at the scaling challenges and the future scaling drivers for conventional charge-based devices implemented at the 7nm technology node and beyond. It examines the system-level performance of stacking device logic in addition to tunneling field effect transistors (TFET) and their potential as beyond-CMOS devices. Finally, this research models and benchmarks BEOL scaling challenges and evaluates proposed technological advancements such as metal barrier scaling for copper interconnects and replacing local interconnects with ruthenium. Potential impact on performance, power, and area of these interconnect technologies is quantified for fully placed and routed circuits.

#### CHAPTER 1. INTRODUCTION

## 1.1 Device Scaling: Moore's Law and Dennard Scaling

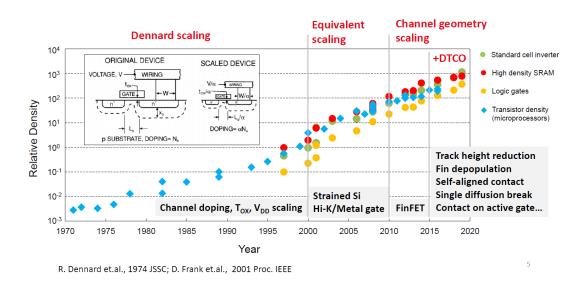

The computing and semiconductor revolution of the past 50 years has been driven by the extraordinary scalability of integrated circuits (IC). The transistor counts of ICs have roughly doubled every 2 years, enabling increasing functionality and reducing cost per transistor, accompanied by an era of improving device performance as showcased in Figure 1. The doubling of transistors every 2 years was first observed by Gordon Moore in 1965 [1]. Following Moore's observation, Dennard from IBM presented the traditional scaling relationship of planar MOSFETs. In his paper, he describes how scaling transistor dimensions and oxide thickness while increasing channel doping improves device performance at a similar rate for the same power density [2]. This continuous scaling of transistors provided a roadmap for the semiconductor industry to enable ever increasing performance at reduced cost for many decades [3].

Figure 1 – Moore's Law: History of Scaling and Innovations [4]

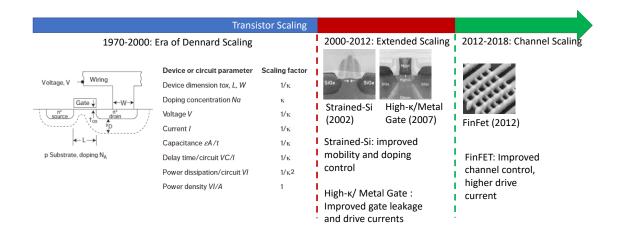

# 1.1.1 Traditional Planar Device Scaling Challenges

As device scaling successfully continued into the early 2000, new challenges started to arise. When device performance improvements slowed due to limits in channel doping, the industry moved to stressed and strained channels to help improve electron mobility while minimizing device leakage. In traditional Dennard scaling, gate oxide thickness scaling is also necessary to maintain the same gate capacitance. By the early 2000, the industry standard SiO<sub>2</sub> gate oxide had reached its scaling limits, with tunnelling current through the gate dielectric becoming a substantive portion of power dissipation. This required the industry to innovate towards high-κ dielectric materials like hafnium oxide, which enabled thicker oxides that reduced tunnelling currents. With these innovations, performance scaling was maintained through the 2000s [3].

Figure 2 – Eras of Transistor Scaling Innovations [2-5]

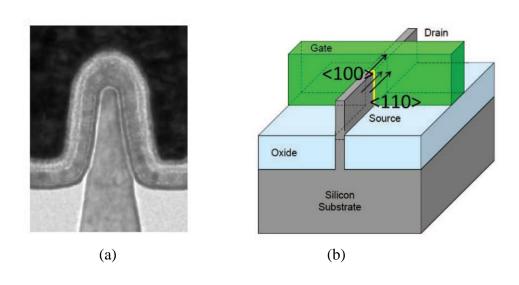

## 1.1.2 Challenges of device scaling sub 22nm: Movement to FinFET

Despite the many innovations to extend planar MOSFET scaling, there was difficulty maintaining the same progress below 32nm. At the 22nm technology node, the

industry started moving from planar MOSFETs to FinFET devices (also referred in literature as tri-gate) as shown in Figure 3. FinFETs offer better performance per unit power compared to traditional planar MOSFETs. This is achieved by increasing the effective gate capacitance by raising the channel above the substrate plane resulting in fin-like structures [6]. The gate wraps around the raised portion of the device on three sides, increasing the capacitive surface area per planar footprint area. This allows the reduction of device leakage currents and enables lowers threshold-voltages through better gate control. As device scaling continues to the 7nm and 5nm nodes, new device structures are being examined as potential successors to current FinFET technologies.

Figure 3 – (a) Transmission Electron Microscopy (TEM) of PMOS Tri-gate/FinFET channel under the gate [4] (b) Tri-gate/FinFET transistor architecture [7]

#### 1.1.3 Gate-All-Around devices and Complementary Logic

With the success and wide adoption of FinFET devices, additional challenges emerged for the sub-5nm technology nodes. Short-channel effects and doping variations become a challenge for maintaining device density and performance at these small

dimensions. Due to the increasing challenges of FinFET technology, the next evolution for the ultimate CMOS device is the gate-all-around (GAA) device. In a GAA device, the entire channel is surround by the gate on all sides, providing the ultimate electrostatic control. One promising candidate for GAA is the lateral nanowire gate-all-around FETs (LFET) with its improved electrostatic control and compatibility with high-κ gate dielectric and stressed channels [8-10].

While LFETs have promising scaling opportunities, interconnect scaling has increasingly become a bottleneck in IC performance. Interconnect resistivity is increasing with scaling due to size effects, and interconnect capacitance scaling faces many challenges and limitations due to mechanical requirements [11]. By stacking transistors on top of each other, a more compact logic cell can be achieved with a smaller footprint area. This helps to reduce the average interconnect length, improving overall system performance. Although both vertical and lateral stacked structures are possible for nanowire GAA FETs, the lateral topography of LFETs is less disruptive to existing CMOS technologies and design. In addition, a strain relax buffer can provide channel stress and improve mobility for LFETs [10, 12].

#### 1.1.4 Beyond CMOS Devices: TFETs

As traditional IC technologies approach fundamental scaling limits due to electron thermal energy and undesired tunneling currents, new classes of devices are being explored as potential alternatives to achieve optimal device performance and energy consumption. For low-power applications, in recent literature, the tunneling field-effect transistor (TFET) device has gained a lot of popularity due to its low leakage properties.

In a conventional thermionic MOSFET, device current is controlled by raising and lowering the energy barrier height through which electrons are injected from the source to drain. This barrier height is modulated by adjusting the gate voltage. In TFET devices, the primary current injection method is by interband tunneling. Instead of modulating the barrier height, the barrier width is modulated to allow interband tunneling when the TFET is turned on. TFETs promise low leakage, steep subthreshold slopes and low supply voltages, but also have low on-currents. In addition, TFETs generally have a larger footprint compared to CMOS and have unidirectional current flow. With these potential benefits and drawbacks, it becomes important to understand how these devices would perform compared to conventional CMOS technology [13, 14].

# 1.2 Interconnect Scaling and Challenges

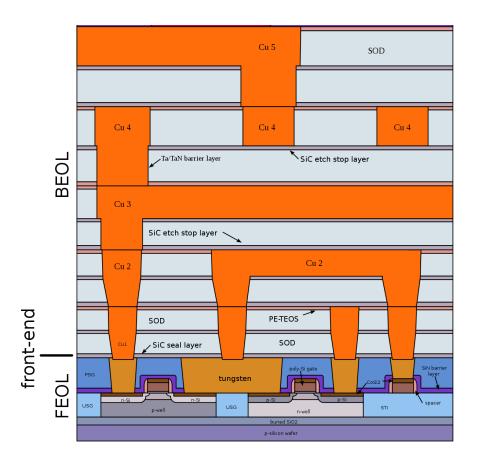

Transistors are fabricated on silicon wafers in a series of processes often referred to as the Front-End-of-Line (FEOL). After device fabrication, the transistors need to be functionally connected to one another. This is done through metallization layers that connect all the devices together and is often referred to as the Back End of Line (BEOL) as shown in Figure 4.

Figure 4 – CMOS Chip Structure in 2000s (Cepheiden, Wikipedia 2006)

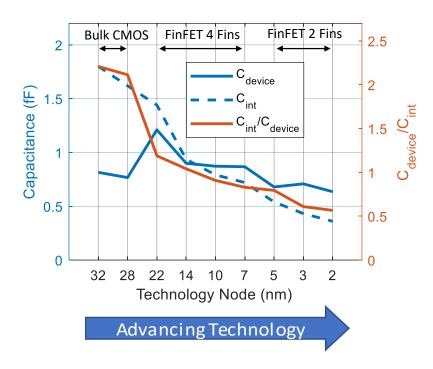

In traditional dimensional scaling of interconnects, when the transistors shrink in dimensions, the interconnect's parasitic capacitance also decreases. However, this scaling also increases the resistance of the interconnects because of the reduced cross-sectional area, ensuring the overall RC delay generally remains constant. Traditional with each successive technology node, device performance improves while interconnect RC delay stayed constant and increasingly contributed to a larger share of the total delay. New advances to interconnect delay are required to improve the performance of ICs.

#### 1.2.1 Traditional Al interconnects to Cu

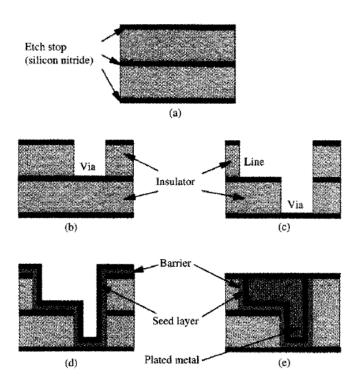

In the past, aluminium (AI) was used as the main interconnect conductive material due to its relative ease of processability and compatibility with silicon. However, due to the increasing share of the delay coming from interconnects, new materials were required to improve interconnect resistance and thereby IC performance. Copper (Cu) became the industry standard wiring metal of choice due to its high conductivity, better reliability and higher resistance to electromigration. Cu has a bulk resistivity of  $1.7\mu\Omega$ -cm compared to aluminium's  $2.7~\mu\Omega$ -cm. The two main challenges of using copper are that it requires a barrier/liner bi-layer material to prevent the diffusion of Cu into the surrounding dielectric and to ensure a void-free Cu fill. In 1997, IBM researchers demonstrated Cu dual damascene process integration for the BEOL stack which continues to be the industry standard to today [15]. A typical dual damascene process flow is show in Figure 5 [15, 16].

Figure 5 – Dual Damascene Process [5]: a) Deposition of ILD with etch stop, b) Pattern and etch via trench, c) Pattern and etch wire trench, d) barrier and metal seed-layer deposition, e) Cu electroplating, CMP, and capping layer

## 1.2.2 Challenges of Cu interconnects and size effects

Modern scaling of copper interconnects presents many challenges. As wire dimensions scale below 22nm, copper resistance increases exponentially due to size effects. Some of these factors include decreased grain size, higher surface reflectivity, and poor scaling of highly resistive MB/liner materials which take up large portions of the copper wire volume. Additional technology innovations are required to further extend scaling for future technology nodes.

### 1.2.3 Low- κ dielectric and air gap

Beyond just improving interconnect resistance, interconnect capacitance is another area of focus for scaling and improvements. Interconnect capacitance contributes not only to RC delay, but also to dynamic power dissipation. The power dissipated in the interconnects is due to switching activity in the wire of all the nets. The main contribution to this power dissipation is from the wire and cell pin load capacitance. The primary method of reducing the interconnect capacitance is to use a low-κ interlayer dielectric material (ILD) material. Conventionally, the ILD material used is SiO<sub>2</sub> with a dielectric constant of 3.9. To reduce the dielectric constant of a material, one can reduce the dipole interaction of the atoms and/or reduce the density of the material by increasing the interatom spacing. This can be achieved by doping the SiO<sub>2</sub> with carbon or fluorine. The integration of low-κ dielectric has been implemented using carbon doped SiO<sub>2</sub>. The silicon bond to carbon has both smaller dipole interaction and creates larger interatom spacing. This results is a reduction of dielectric constant with reported values in the range of 2.6–3 [17].

Another method to reduce the dielectric constant is to introduce voids in the ILD material by using porous silicon. Adding pores to the ILD material can reduce the capacitance of the ILD with the trade-off of reducing the mechanical strength of the material. The chemical-mechanical polishing (CMP) processing during the dual damascene process introduces a lot of mechanical stress. If the ILD material is not mechanically stable enough, it can be damaged during the CMP process.

For the ultimate low-κ dielectric material, an air gap would have a dielectric constant close to 1. Air gaps have been introduced to the BEOL stack starting in the 14nm technology node by Intel Corporation. However, there are many design rules and process challenges that restrict the usage of air gaps to a few layers in the overall stack [18].

#### 1.2.4 MB/Liner and Reliability Challenges

As IC scaling continues to 7nm technology node and beyond, wire dimensions are scaled to narrow pitches especially at the local metal-levels to accommodate dense logic and memory on chip. The copper metallization for the BEOL requires a barrier and liner material to prevent Cu from diffusing into the surrounding dielectric as well as provide a seed layer to ensure void free copper fill. The percentage of interconnect cross-sectional area occupied by the highly-resistive barrier liner for copper can be as much as 50% of the wire volume [19, 20]. The current industry standard metal barrier and liner bilayer material is Tantalum/Tantalum Nitride (Ta/TaN). While this bilayer material has been used successfully for many technology generations, it has been shown that it is difficult to scale beyond 4nm thickness [21, 22].

New bilayer materials have been proposed to extend scaling of the liner materials. It has been shown in literature that adding Ruthenium (Ru) or Cobalt (Co) to the barrier material TaN can help maintain barrier integrity of TaN for thicknesses as low as 0.8nm [22]. TaN/Ru and TaN/Co bilayer materials as thin as 2nm have been demonstrated to pass most reliability tests [22].

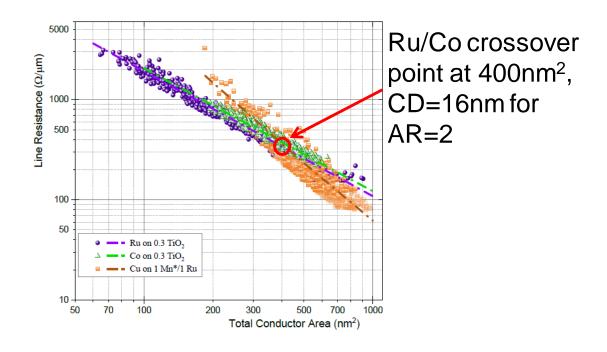

#### 1.2.5 New Metal Materials for Scaling of Local Interconnects

Due to increasing copper resistivity from size effects for sub-20nm wires and challenges in metal barrier scaling, there have been proposals to use new metals for local interconnects such as Ruthenium (Ru) and Cobalt (Co). While these metals have a higher bulk resistivity compared to copper, they do not require a barrier and are less prone to size-effects that are observed in copper. Ru also has superior reliability and is more resistant to electromigration compared to Cu. Experimental data from literature shows that Ru and Co have better resistances per unit length compared to copper for feature sizes below 16nm for aspect ratios (AR) of 2 [23] as seen in Figure 6. These new metal options have great potential to replace Cu interconnects for sub-16nm local interconnects.

Figure 6 – Comparison of Cu, Ru, and Co Line Resistance versus Total Conductor Area [23]

# 1.3 Thesis Overview

With IC scaling challenges driving many technological innovations, it becomes important to understand the performance implications. In the following chapters, we will explore some of these future scaling enablers and proposed new devices that will further extend scaling and performance gains in the future.

# CHAPTER 2. STACKED LOGIC DEVICE FOR LATERAL NANOWIRE FIELD-EFFECT TRANSISTORS (LFET)

Previous works have extensively examined the device performance of various configurations of LFETs with different source/drain contacting schemes [9, 10, 24]. A wrap-around contact scheme for the source and drain, where contact is directly made to a fin of Si and SiGe lattice, reduced contact resistance and improved ON currents for the device [10].

To further improve the device density and performance, two CMOS logic structures are proposed that utilize stacking of n- and p-type LFETs on top of each other to achieve a more compact logic cell. Reducing the cell area reduces the average interconnect length, improving interconnect and system performance. This stacked approach for a more compact device is complementary to current efforts to continue technology scaling and does not suffer from the same issues the industry faces in the scaling of gate pitch, metal pitch and fin pitch. Some of those issues include reduced electrostatic control due to short channel effects (SCE), increased wire resistance due to size effects, and increased contact resistance and gate fill considerations. To quantify the potential performance of such devices, the parasitic capacitance and resistances are accurately captured by an electrostatic field solver and are compared against LFETs. In addition, system-level performance analyses are performed to capture the impact of the reduced cell area on overall system performance. The stacked structure leads to shorter interconnects, reducing overall delay. System-level analyses also enable the study of trade-offs among performance, power, and

area, giving insights to interconnect and thermal related issues that cannot be captured at only the device-level benchmarking.

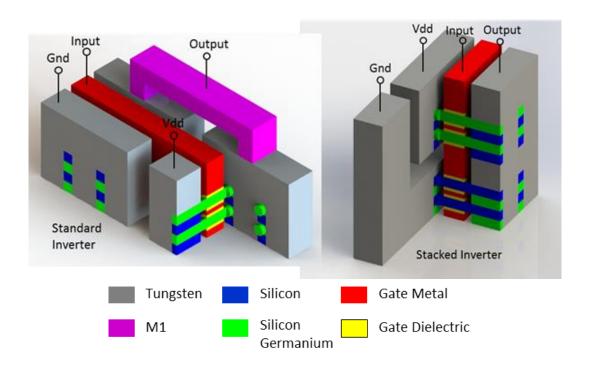

# 2.1 Stacked Device Layout and Structure

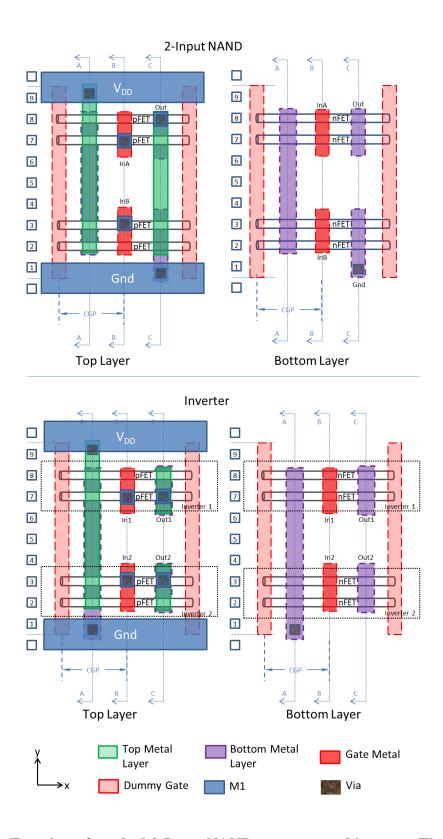

Two stacked logic CMOS structures for LFETs are proposed in this chapter: inverter and 2-input NAND. The basic LFET structures and device characteristics are based on work from [9, 10, 24]. The stacked logic CMOS structure consists of an NFET layer at the bottom and a PFET layer on top. This structure, where every NFET is paired with a PFET, is a natural complement for CMOS design. 3D models for a typical 2D inverter structure and stacked inverter are depicted in Figure 7.

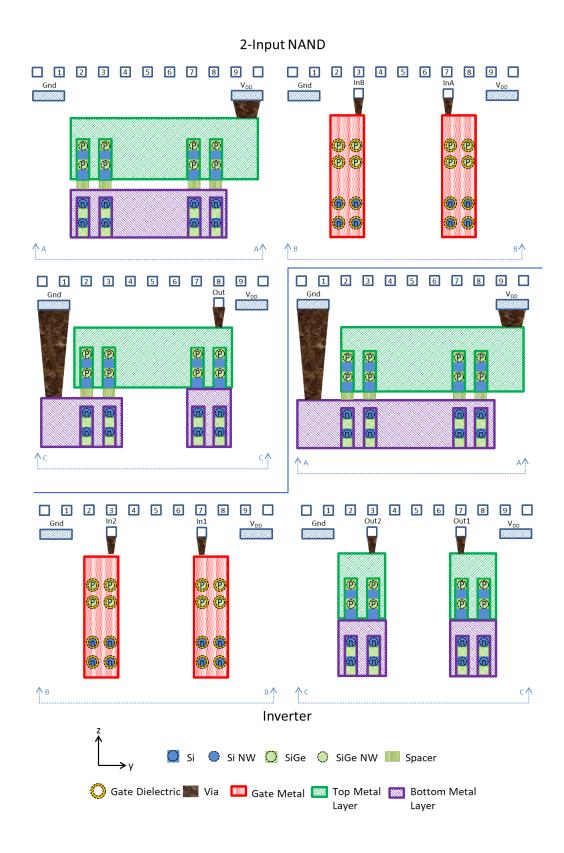

Figure 8 shows the top layout view for an inverter and NAND2 cell. The cell heights for both devices are 9 metal pitches (MP), with top and bottom supply and ground rails. Figure 9 shows the cross sections of the inverter and NAND2 cells. Separate V<sub>dd</sub> and ground rails at M1 allow ready access for chip level routing via higher metal levels.

Figure 7-3D sketch of a standard cell 2x2 LFET inverter and a stacked 2x2 LFET inverter.

Figure 8 – Top view of stacked 2-Input NAND structure and inverter. The top layer shows the M1 supply and ground rails with the PFET transistors connections, and the bottom layer shows the NFET connections.

Figure 9 – Cross sectional view of stacked 2-Input NAND structure and inverter. The cell height in metal pitches is numbered on top.

The layouts presented for the two logic cells use the same cell height to conform to physical layout design standards. The metal routing is also unidirectional for a lithography friendly design. The cell height for a single device is 3 metal pitches (MP) by 2 contacted gate pitches (CGP) wide. For a conventional structure, the inverter gate has a cell height of 9 MP and is 2 CGP wide, and for a NAND2 gate the cell height is 9MP and its width is 3 CGP. By stacking PFETs on top of the NFETs, two inverters can fit into the same footprint as the conventional layout, reducing the effective cell area of a single inverter by 50%. For the NAND2 cell, the stacked structure can fit in the same cell footprint of a 2D inverter, reducing the cell width from 3 CGP to 2CGP. This results in a reduction in area by 33%. The area comparison between the standard architecture and stacked LFET structure is summarized in Table 1. The basic process assumptions are summarized in Table 2.

Table 1 – Standard 2D Cell and Stacked Cell Footprint Summary and Comparison

| Logic Cell | Std. Cell Footprint | Stacked. Footprint | % Reduction |

|------------|---------------------|--------------------|-------------|

| NAND2      | 27 MP·CGP           | 18 MP∙CGP          | 33          |

| Inverter   | 18 MP∙CGP           | 9 MP·CGP           | 50          |

Table 2 – Process Assumptions for 2x2 LFET

| Parameters                            | Values                                             |

|---------------------------------------|----------------------------------------------------|

| Contacted Gate Pitch, CGP [nm]        | 32                                                 |

| Metal Pitch, MP [nm]                  | 24                                                 |

| NW Diameter, D <sub>nw</sub> [nm]     | 7                                                  |

| Gate Oxide Thickness, Tox [nm]        | 0.5 nm SiO <sub>2</sub><br>1.5 nm HfO <sub>2</sub> |

| Gate Length, Lg [nm]                  | 14                                                 |

| Spacer Thickness, S/D extension [nm]  | 5                                                  |

| Nanowire Pitch [nm]                   | 14                                                 |

| S/D Width [nm]                        | 20                                                 |

| Fin Pitch [nm]                        | 27                                                 |

| Vertical Nanowire Pitch (VNW) [nm]    | 14                                                 |

| $oldsymbol{arepsilon}_{	ext{spacer}}$ | 5.5                                                |

# 2.2 Device Parasitic Modeling

The device characteristics and performance for different configurations of LFETs using standard layout architecture are investigated in references [9, 10, 24]. The performance of LFETs with different configurations is benchmarked at the system level [24], indicating that a LFET structure utilizing 2fins/2stack (2x2) provides best performance-energy trade-offs. Therefore, the 2x2 LFET structure is used for the baseline and stacked structure. The parasitic capacitance and resistance for the stacked inverter structure are characterized and compared with a model of the standard inverter layout. The

3D field solver Raphael [25] is used to model the parasitic capacitance and resistance of the inverter structures.

### 2.2.1 Parasitic Capacitance

3D models of the standard inverter and the stacked structures are created in Raphael to analyze and compare the input gate capacitance for both structures. Key process assumptions and parameters in Table 2 are used to create the models in Raphael.

In the basic 2x2 LFET structure, the vertical nanowire pitch is 14 nm and the fin height is 28 nm. In the LFET models presented in [9], the LFET device has a gate-to-top dimension of 25 nm. This requirement is based on the replacement metal gate (RMG) process requirements and access resistance considerations [26, 27]. In the stacked inverter structure, the gate can be formed in the same process steps for both the NFET and PFET input since they are tied together for the inverter and NAND2. The gate-to-top dimension for the bottom transistor can therefore be relaxed, leading to a shorter device height. A shorter device height reduces the overlap capacitance between the gate and source/drain contacts, leading to a reduction in input gate capacitance of 13% compared to the standard inverter structure. The Raphael capacitance model results are summarized in Table 3.

Table 3 – Parasitic Input Capacitance for Standard and Stacked Cells, and Parasitic Resistance for Stacked Cells for 2x2 LFET Inverter

| Inverter Parasitic Parameters        | Values |

|--------------------------------------|--------|

| Standard Cell Input Capacitance [aF] | 403    |

| Stacked Parasitic Capacitance [aF]   | 351    |

| Stacked Parasitic Resistance [Ω]     | 229    |

#### 2.2.2 Parasitic Resistance

The parasitic resistance modeling of the LFET is based on the wrap contact reported in [10] where the source/drain contacts are made of tungsten. For the stacked inverter structure, the access to the bottom electrodes requires going through the top layer, increasing parasitic access resistance for the stacked structure.

For the stacked inverter, the pull-up network is the same as the unstacked case since it is located on top and readily accessible. However, the access resistance increases for the pull-down network. An additional resistance path exists from the drain contact of the top transistor to the bottom drain, as well as a long ground via to the bottom transistor on the source side. The additional resistance path is modelled in three parts in Raphael. The first part consists of the PFET drain contact down to the top contact of the of NFET drain. The second part consists of a long ground via from the M1 ground rail to the bottom NFET source contact. The last part consists of the side access of the source contact to the fins. The total stacked parasitic resistances for the top drain contact, ground via, and side access are evaluated in Raphael. The total additional access parasitic is evaluated to be 459  $\Omega$ . Since this resistance only exists for the pulldown network, an average parasitic resistance of 229  $\Omega$  is added to the intrinsic resistance for the benchmarking in the next section. This resistance provides an additional 38% of the parasitic access resistance evaluated in [24]. The stacked parasitic resistance is shown in Table 3.

### 2.3 System-Level Modeling

The system-level modeling is performed for the standard LFET structure and stacked logic structure. For the system-level simulation, a validated open source simulator IntSim [28] is adopted to efficiently evaluate the performance of the 2x2 LFET structures at the 5nm node. For a given operating frequency target, interconnect networks are optimized to obtain metal pitches on different metal levels for a given set of system parameters. The ON currents and leakage currents from [24] are used as input to the model. Device performance at three different supply voltages is analyzed: 0.6V, 0.5V and 0.4V. Total power is evaluated based on the dynamic and static components of the system. Input capacitance and resistances used in the system models are based on the minimum sized inverter.

The stacked logic structure reduces the cell footprint of an inverter by 50% and a NAND2 by 33%. This reduction in area leads to shorter interconnects, improving overall interconnect performance at the system level. Because of the reduced footprint of the stacked cell, the chip area can also be reduced by 30% while still maintaining the same gate density as the unstacked case. Reductions in chip area further decreases average interconnect length and improves overall system-level interconnect performance.

Device parasitic properties figure prominently in the model. The input capacitance is the dominant component for calculating dynamic logic and clock power, and an increase in access resistance impacts the critical path delay.

#### 2.4 System-level Benchmarking Results

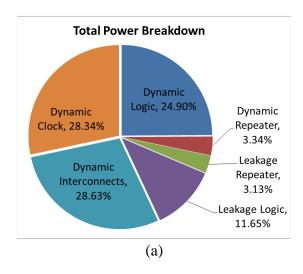

A total system power breakdown utilizing conventional standard cells for 2x2 LFET is presented in Figure 10(a). The supply voltage is set to 0.6V and the frequency is fixed at 1.1GHz. Dynamic power dissipations in interconnects, clock distribution and logic

gates are the largest components of the total power dissipation. Figure 10(b) shows the percent power savings for the stacked structure compared to the conventional layout for supply voltages of 0.6V, 0.5V, and 0.4V. The frequency is fixed at 1.1GHz and the available chip area for placement and routing is varied from 0.7mm<sup>2</sup> to 1mm<sup>2</sup>. The comparison in power savings is made with respect to the unstacked case with a chip area of 1mm<sup>2</sup>. A maximum power savings of 12.9% is observed at 0.6V supply voltage for a chip area of 0.7mm<sup>2</sup>. Shorter interconnects due to smaller cell footprint and chip area result in a 17.9% reduction in dynamic interconnect power, or 5.0% of the total power. A 13% reduction in input capacitance results in 12.5% reduction in dynamic logic and clock, or 3.1% and 3.6% of total power, respectively. The results in Figure 10 (b) reflect the improvement in interconnect and capacitance due to the smaller cell footprint and shorter NFET device.

Figure 10 – (a) Projected power breakdown for standard 2x2 LFET at 0.6V supply voltage and 1.1GHz. (b) Percent system power savings of stacked logic compared to standard LFET cell at 1.1GHz. Supply voltage is varied from 0.6V to 0.4V and chip area is varied from  $1 \text{mm}^2$  to  $0.7 \text{mm}^2$ . The percent power breakdown for different categories are normalized to the total power.

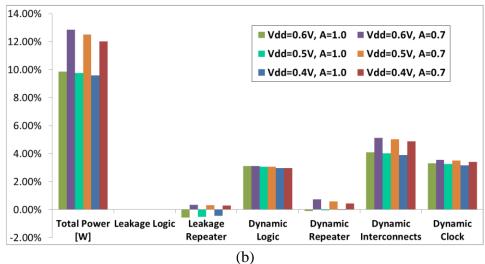

Figure 11(a) shows the maximum operating frequency of the system and the maximum operating frequency for a power density budget of 100W/cm<sup>2</sup>. The overall operating frequency of the system, determined by the critical path delay, improves for the stacked logic design. This improvement is primarily driven by the reduction in interconnect length and device input capacitance. The impact on the delay due to the increased access

resistance is more than compensated by these improvements. With thermal considerations and a power density budget of 100W/cm², the maximum operating frequency of the system becomes power limited. There is a trade-off in terms of power versus performance. When the system performance is limited by the power budget, reducing the supply voltage decreases the dynamic power of the system and allows a higher operating frequency. This is at the cost of an increased critical path delay due to lower ON currents. For supply voltages of 0.5V and 0.6V, the maximum operating frequency is power constrained. When supply voltage is reduced to 0.4V, the system becomes limited by the critical path delay.

Figure 11-(a) Maximum operating frequency (Max f) and power density constrained frequency comparison of standard and stacked cells. Stacked cell chip area is varied from 1 to  $0.7 \text{mm}^2$ . (b) Energy per clock cycle comparison for stacked and unstacked logic. Frequency is set to 1.1 GHz, supply voltage is varied from 0.6 to 0.4 V, and stacked cell chip area is varied from  $1 \text{mm}^2$  to  $0.7 \text{mm}^2$ .

When the system is power density constrained, the maximum frequency for the stacked case for a reduced chip area of 0.7mm<sup>2</sup> is lower than the unstacked case. This is primarily due to the power savings of 12.9% not scaling at the same rate as the chip area reduction of 30%.

The switching energy per clock cycle is plotted in Figure 11(b). The frequency is fixed at 1.1GHz and the supply voltage is varied from 0.6V to 0.4V. The stacked device exhibits better switching energy efficiencies due to shorter interconnects and improved device capacitance, which improves with smaller chip area. An energy reduction of 10% and 12-13% is observed for the stacked logic when chip area is 1mm<sup>2</sup> and 0.7mm<sup>2</sup>, respectively.

#### 2.5 Conclusion

Standard cells using stacked logic layout are presented for an inverter and a 2-input NAND gate. The new layout enables a 30% reduction in chip area for a given gate density. The new device structure also enables a shorter NFET, leading to a smaller input capacitance. Both the reduction in cell area and input capacitance allows the new structure to have up to 12.9% reduction in total power and 12-13% reduction in switching energy. In addition, creating a 3D structure as a standard cell and characterizing the parasitic of the cell allows compatibility with existing placement and routing tools.

While the new design structures offer potential improvements in both power and area, additional work is required to determine fabrication feasibility and cost concerns. A standard cell library can be generated to give a more complete and accurate analysis and benchmarking regarding the potential area savings from the stacked cell structure. Thermal considerations are required to evaluate the impact to the system performance, especially for a power density limited situation.

## CHAPTER 3. GENERIC SYSTEM-LEVEL MODELING AND OPTIMIZATION FOR BEYOND CMOS DEVICE APPLICATIONS

Recent efforts in benchmarking new devices have evaluated the potential performance of the energy and delay for 32-bit adders and Arithmetic Logic Unit (ALU) for Beyond CMOS Benchmarking (BCB) [14, 29]. Current benchmarking models are good for 32-bit ALU, but it is architecture and circuit specific and does not consider area constraints and power budgets. A system level approach will extend this study to evaluate and optimize system performance for a single logic core. A more general system model is useful to uniformly compare various technologies with different architecture and complexity, allowing the benchmarking to scale to more complex logic cores where these devices will ultimately be used. With a flexible system model, throughput can be optimized by finding optimal supply voltage and number of gates, which represents a system architecture complexity and functionality. Using this optimization process, the impact of various power budgets on the optimized throughput performance in terms of energy-delay product (EDP) can be evaluated.

Using the generic system model approach, this chapter uniformly models and optimizes three promising TFET devices, GaN Heterojunction TFET, WTe<sub>2</sub> Two-dimensional heterojunction interlayer TFET (ThinTFET), and WTe<sub>2</sub> Transition Metal Dichalcogenide TFET (TMD TFET), and compares their system performance with ITRS projections for CMOS high performance (CMOSHP) and low voltage (CMOSLV) devices.

#### 3.1 Generic System Model

A generic system model is used to quickly estimate the system level performance of various technology nodes. Existing system model IntSim is modified and used to model the power performance for each device technology. Intsim is an interconnect CAD tool that estimates the optimal interconnect pitch for each wiring level, co-optimizes signal, power, and clock interconnects based on stochastically derived wiring distributions. It also provides estimates for the system level power consumption for a given set of system parameters [28]. For a given operating frequency target, interconnect networks are optimized to obtain metal pitches on each metal level for a set of system parameters.

The advantage of using such a model is that it is a fast, generic model, captures system parameters and power, and has been validated with commercially available CPUs. While it is not as accurate as physical design models, it provides insightful trends and starting design parameters.

#### 3.1.1 Empirical CPI Model

For this work, an empirical cycles per instruction (CPI) model is used in conjunction with the generic system model to calculate the system throughput based on the number of transistors used in the system. The empirical CPI is based on the observations that a power law relation exists between CPI and the number of logic transistors. Previous works have shown a power-law relationship between number of logic gates and cycles per instructions. This has been verified based on 8 Intel processors using data extraction from existing CPU and CPU benchmarking specification SPECint. An updated CPI model is used in this study for the Intel microprocessor family [30].

$$CPI_{logic} = 2.466(N_{transistor})^{-0.420} \tag{1}$$

where  $N_{transistor}$  is the number of logic transistors in millions.

The functionality of the system can be improved by increasing the number of transistors, leading to a smaller CPI; however, a more complex system requires more interconnects, which imposes more constraints on the maximum frequency at which the system can operate. Therefore, when the empirical CPI model is combined with a clock frequency model and the area is fixed, there is a trade-off between system's operating frequency and CPI that gives an optimal throughput.

#### 3.1.2 Optimization Methodology Flow

As mentioned before, for the system model in this study, IntSim is used to predict the optimal operating frequency for a given supply voltage  $(V_{dd})$  and number of gates  $(N_{gates})$ . The maximum frequency that can be successfully acheived while staying within power budget is estimated and the maximum throughput is calculated using the empirical CPI model.

At the core of the parameter optimization is supply voltage and the number of logic gates. Supply voltage controls the on-current for the device and governs the system operating frequency, while the number of gates impacts our CPI. For a fixed supply voltage and number of gates, the highest operating frequency will give us the highest throughput for these two design points. The goal is to find a valid system-level model that operates at the highest frequency within a given power budget.

By sweeping  $V_{dd}$  and  $N_{gates}$ , the parameters that maximize the processor throughput for a given power budget and design space can be found. When looking at various power budgets, the different constraints impact the performance, and a comparison is made with different device technologies.

#### 3.1.3 Input Data and Device Technologies

The system model requires input data for on-current, off-current and input capacitance for different device inputs. This work evaluates sidewall-gated GaN/InN heterojunction TFET (GaNTFET) [31, 32], WTe<sub>2</sub> Two-dimensional heterojunction interlayer TFET (ThinTFET) [33], and WTe<sub>2</sub> Transition Metal Dichalcogenide TFET (TMDTFET) [34, 35] and compares system performance with conventional CMOSHP and CMOSLV devices. All data are kept consistent with the physical dimensions presented in previous Beyond CMOS Benchmarking (BCB) works [14, 29] and ITRS Roadmap for the 2018 node [36].

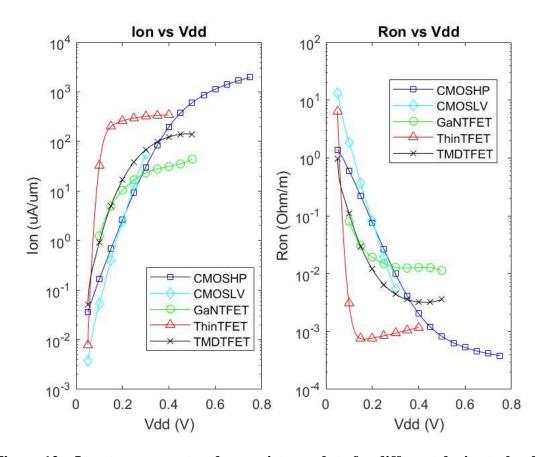

The IV curves (Figure 12) and input capacitances for the evaluated devices are taken from published sources [31-35]. To optimize  $V_{dd}$  for a given power budget, the full IV curve for  $I_{on}$  and  $I_{off}$  along with voltage dependent input capacitance for multiple supply voltage data points are extracted from these works.

Figure 12 – Input on-current and on-resistance data for different device technologies

#### 3.2 Simulation Results

#### 3.2.1 System Model Comparison of ALU and Single Logic Core

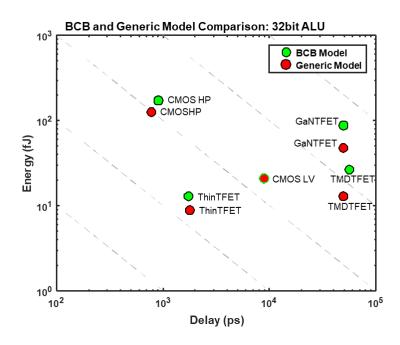

A comparison between the BCB 3.0 simulator [37] and the generic system model is made for a 32-bit ALU. See Figure 13 for the comparison of energy and delay between the two models. In general, the two models show similar trends, with the generic system models more optimistic in energy for less complex systems.

Figure 13 – Trend comparison of Energy vs Delay between BCB model with Generic System model for a 32-bit ALU.

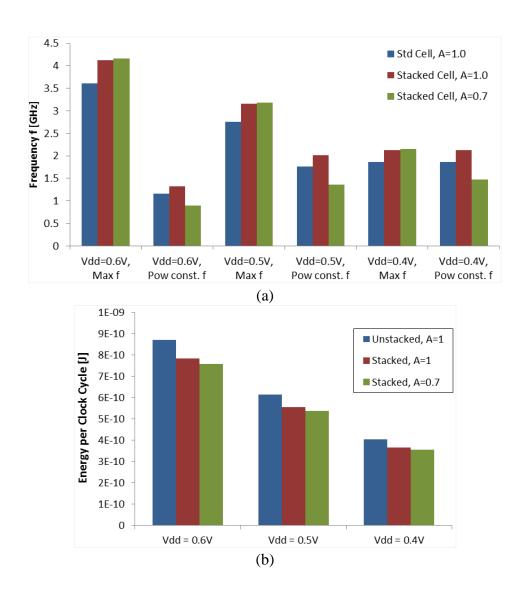

#### 3.2.2 Power Breakdown

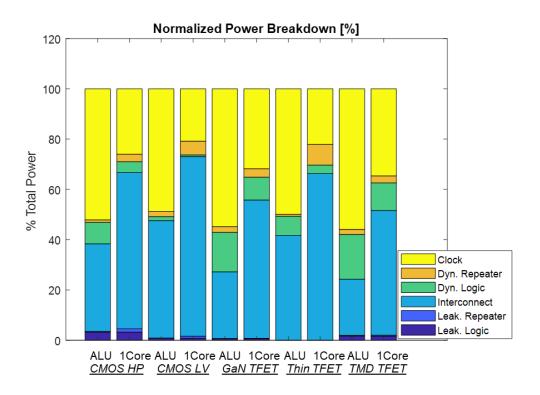

The power breakdown for a 32-bit ALU and single logic core is evaluated and shown in Figure 14. For evaluating the system model extension of the ALU to a single logic core, the same device input is used. The key parameters used in the model are shown in Table 1. The normalized power breakdown shows that as the circuit becomes larger and more complicated, system overhead starts to take a larger proportion of the power. Interconnect power doubles in proportion compared to the rest of the power breakdown. This comparison using the system model highlights the more critical role of interconnects and repeaters in more complex systems. Having a more flexible model that captures the interconnect network and optimizes it for different design points is important when looking at more complex systems.

$\begin{tabular}{ll} Table 4-Table of Input Parameters for System Model Comparison of ALU and Single Logic Core \end{tabular}$

| Key Parameters                            | Values                 |

|-------------------------------------------|------------------------|

| ALU Ngates                                | 1500                   |

| ALU Area [mm²]                            | 3.6 × 10 <sup>-4</sup> |

| Single Logic Core Ngates (Million)        | 16.3                   |

| Single Logic Core Area [mm²]              | 3.9                    |

| Logic Depth                               | 10                     |

| Power Budget Density [W/cm <sup>2</sup> ] | 90                     |

| Activity Factor                           | 0.1                    |

Figure 14 – Power breakdown comparison for 32-bit ALU and single core processor (1Core) for different device technologies.

#### 3.2.3 Throughput Optimization

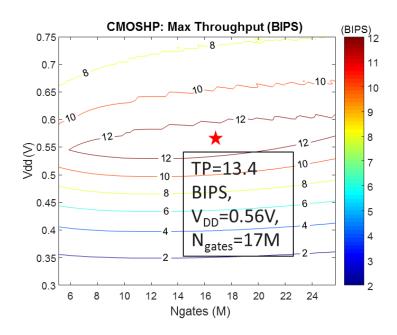

By using the empirical CPI model, there is a tradeoff between number of gates and higher operating frequency due to large gate widths for a fixed area. This leads to an optimal number of gates. A fixed chip area of  $5 \text{mm}^2$  is used for the single logic core optimization. Throughput is limited at higher supply voltages due to power budget constraints, and an optimal  $V_{dd}$  can also be found for a given power budget. The optimization algorithm finds the highest throughput for a given  $V_{dd}$  and  $N_{gates}$  pair based on the empirical CPI model. This is done by finding the highest operating frequency that meets the power budget constraint for a given  $N_{gates}$  and  $V_{dd}$ . See Figure 15 for a typical optimization result for CMOSHP.

Figure 15 - CMOS HP optimal throughput contour plot. Area is fixed at  $5mm^2$ . Power budget is set to 4.6 W, with a power density of  $93W/cm^2$

#### 3.2.4 Throughput vs Power Budget

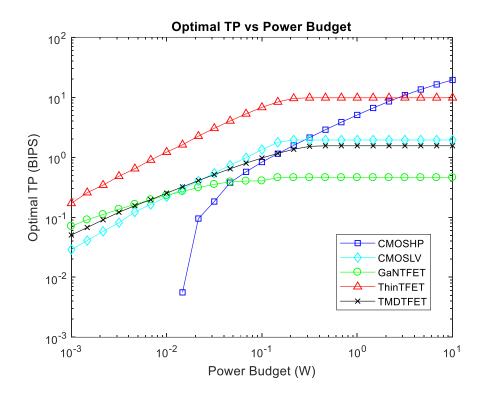

The results of optimizing throughput for a range of power budgets are show in Figure 16. The power budget limits the supply voltage and frequency the system can operate. Low-power TFET devices perform better in terms of throughput when compared to CMOS LV for low power applications (<0.1W, 2W/cm<sup>2</sup>). For high performance applications, CMOSHP still performs the best in terms of throughput at high power budgets (>2.5W, 50W/cm<sup>2</sup>). The optimal  $V_{dd}$  and  $N_{gates}$  at each point will be shown in the next subsection.

Figure 16 – Optimal throughput result versus power budget for different device technologies

#### 3.2.5 System Optimization Trends for $V_{dd}$ and $N_{gates}$

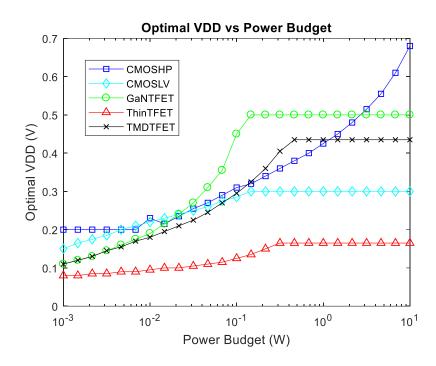

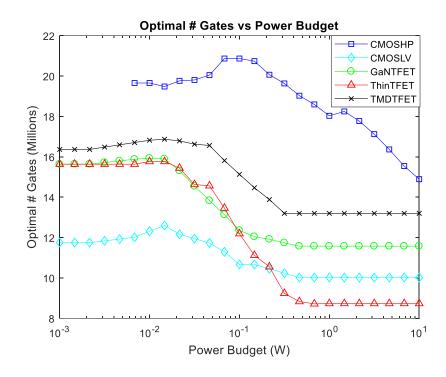

When optimizing for throughput for various power budgets, a trend for  $V_{dd}$  and  $N_{gates}$  emerges. Figure 17 shows the  $V_{dd}$  trend as power budget increases. At low power budgets, the system power is constrained and requires lower supply voltages to satisfy the requirement. As power budget increases, the optimal supply voltage also increases to allow for higher on-currents and operating frequency. For the lower power TFET and CMOS devices,  $V_{dd}$  quickly saturates to the maximum value as throughput saturates. CMOSHP; however, continues to increase due to its larger  $V_{dd}$  range and higher on-currents. For all cases, the optimal supply voltage settles to a  $V_{dd}$  that corresponds to its minimum  $R_{on}$ .

Figure 17 – Optimal  $V_{dd}$  trends for different device technologies and power budgets

A trend for the optimal number of  $N_{gates}$  is shown in Figure 18. At low power budgets, the system model favors more gates for lower CPI, which allows throughput to increase by increasing the functionality of the system without increasing power significantly. As power budget increases,  $N_{gates}$  approaches the optimal value associated with the preferred  $V_{dd}$  for maximum throughput due to the tradeoff between higher  $N_{gates}$  and lower CPI versus lower  $N_{gates}$  and higher frequency.

Figure 18 – Optimal number of gates (Ngates) trend for different device technologies and power budgets.

#### 3.2.6 Optimization with minimum EDP: Single Core vs Optimized Single Core

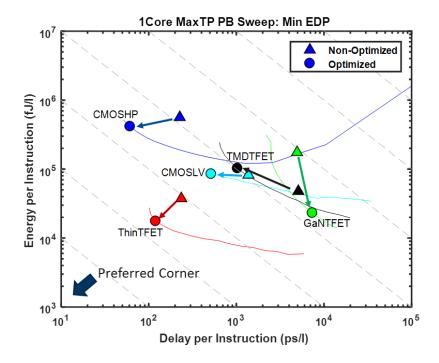

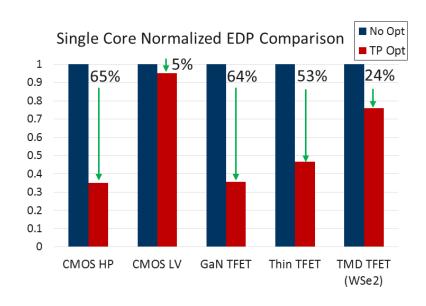

Using the system-level modeling approach in conjunction with the empirical CPI, the number of gates is optimized to maximize throughput for a range of power budgets. As the number of gates increases, the device width decreases when the area and gate density is fixed. This decreases the on-current and maximum frequency at which the system can operate. However, if larger devices are used to increase the system operating frequency, the number of gates is reduced, increasing the number of cycles per instruction. This tradeoff leads to an optimal number of gates to maximize system throughput. The results of the optimization in terms of energy and delay are shown in Figure 19 and Figure 20. The minimum EDP is evaluated for a range of power budgets and the results are tabulated in

Table 5. Overall improvements are made in terms of EDP due to the optimization of number of gates and supply voltage. For TFET devices, GaN TFET benefitted the most from the optimization of the single core with an improvement of 64% in EDP. This is primarily driven by reducing the power budget and operating at a lower frequency and supply voltage.

Figure 19 – Energy vs Delay per instruction results for different device technologies. The solid lines represent the optimized results for a range of power budget. The circle indicates the optimized results that correspond to the minimum energy delay product for that range of power budgets. The lower left-hand is the preferred corner that corresponds to a lower energy delay product.

Figure 20 – Normalized energy delay product comparison between the non-optimized case and the optimized case from a range of power budgets.

$\begin{tabular}{ll} Table 5-Optimized Minimum EDP Results for a Range of Power Budgets for Different Device Technologies \\ \end{tabular}$

| Technology                   | Optimal PD [W/cm²] | Optimal V <sub>dd</sub> [V] | Optimal Ngates [M] |

|------------------------------|--------------------|-----------------------------|--------------------|

| CMOS HP                      | 92.83              | 0.56                        | 16.9               |

| CMOS LV                      | 6.32               | 0.3                         | 9.3                |

| GaN TFET                     | 0.06               | 0.15                        | 19.1               |

| Thin TFET                    | 2.94               | 0.14                        | 13.1               |

| TMD TFET (WSe <sub>2</sub> ) | 2                  | 0.3                         | 18.4               |

#### 3.3 Conclusion

In this study, a fast system-level model is applied to three beyond CMOS devices and the system level performance is evaluated. The system model is compared with the beyond CMOS benchmarking approach and shows good agreement for the 32-bit ALU. The system level approach is applied for a single logic core evaluation, and the interconnect bottleneck is shown through the doubling in power in proportion to overall system. Optimization is performed for a single logic core analysis, and EDP is shown to improve up to 64% in the case for the sidewall-gated GaN/InN heterojunction TFET. In optimizing throughput for a range of power budgets, a trend in  $V_{\rm dd}$  shows an increase as the optimal point becomes less constrained by the power density limits. Higher  $N_{\rm gates}$  is favored at lower power budgets before decreasing in favor of high frequency at higher power budgets.

## CHAPTER 4. MODELING AND BENCHMARKING BACK END OF THE LINE TECHNOLOGIES ON CIRCUIT DESIGNS AT ADVANCED NODES

As IC scaling continues to 7nm semiconductor technology node and beyond, interconnects present a grand challenge to circuit and system performance. When wire dimensions are scaled to narrow pitches at local metal-levels to accommodate dense logic and memory on chip, the percentage of interconnect cross-sectional area occupied by the highly-resistive barrier liner (Ta/TaN) for copper can be as much as 50% [19, 20]. This has motivated industry to explore advanced metallization options like Ru and Co that do not require a barrier and are less prone to size-effects that are observed in copper. However, these advanced interconnect options require further integration efforts to compete with copper wires at an 18nm width [23]. Here we present a quantitative analysis of the impact of barrier liner thickness on circuit-level Power-Performance-Area (PPA) metrics. We define the BEOL stack technology and design Advanced Encryption Standard (AES) and Low Density Parity Check (LDPC) circuit blocks by using the state-of-the-art physical design methodologies.

#### 4.1 Design Flow and Methodology

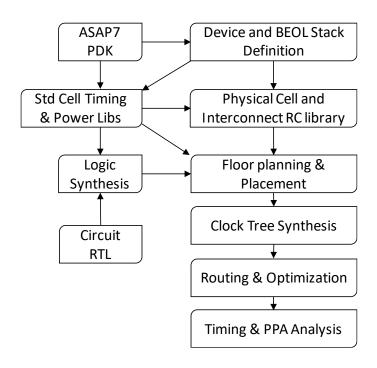

#### 4.1.1 Design Flow Overview

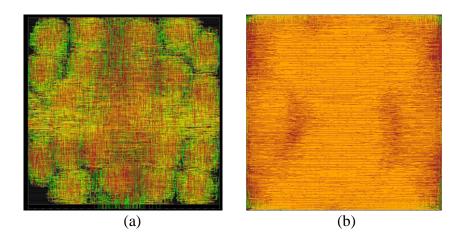

The modeling framework follows the general design flow shown in Figure 21. For our circuit RTL definition, we use an AES and LDPC circuits available online from OpenCores. The AES circuit has random logic and moderate routing demand while the

LDPC circuit has high routing demand [19]. The AES and LDPC circuit RTL is synthesized using Synopsys Design Compiler and ASAP7 PDK standard cell libraries [38]. We then create and calibrate our own BEOL parameter files based on published resistance and via models and extract the RC parasitics using Quantus QRC extraction. Using the synthesized netlist and parasitic extraction from our custom BEOL files, we perform placement and routing using the commercial EDA tool Innovus from Cadence. At this stage, floorplanning, placement, pre-route optimization, routing, and post route optimization are completed within Innovus. After placement and routing (P&R), timing and power analysis reports are generated using tools built into the EDA tools and Tempus Timing Signoff Solution.

#### 4.1.2 ASAP7 PDK

This work uses the ASAP7 PDK for the 7nm node, which is released and openly available from Arizona State University (ASU). This PDK has libraries for 4 different threshold voltage ( $V_t$ ), SLVT, LVT, RVT, and SRAM. In the case studies presented in this work, only the typical threshold libraries (RVT) are used [38-40].

Figure 21 – General Design Flow and Modeling framework for circuit-based analysis.

### 4.2 BEOL Modeling, Technology Development and Metal Barrier Scaling Case Study

#### 4.2.1 ICT Development and Wire and Via Resistance Models

The BEOL stack dimensions for ASAP7 PDK and resistance parameters used in this work are given in Table 6. These values are used to create the interconnect files (ICT) used in this chapter for RC extraction. The metal thickness to width aspect ratio is 2 for each level in the stack. Resistance values are based on IMEC's published semi-empirical models that consider grain and sidewall scattering effects along with line edge roughness (LER) effects [41]. The self-aligned via resistance values are based on Coventor

SEMulator3D simulations similar to those done in [8] and published IMEC papers [9]. A description of different metal barrier/liner cases is given in the next section.

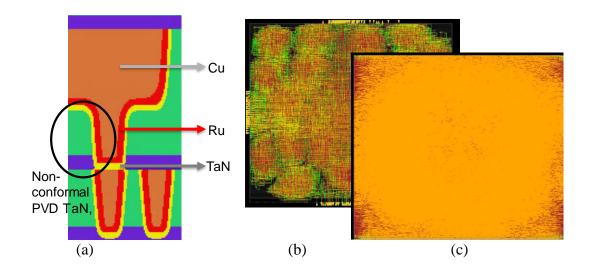

#### 4.2.2 Metal Barrier Engineering

Cu interconnects require a barrier/liner bi-layer material to prevent the diffusion of Cu into the surrounding dielectric and to ensure a void-free Cu fill. The original ASAP7 PDK assumes self-forming barriers are available and can result in very optimistic copper resistances. In this work we present a metal barrier/liner engineering case study based on more realistic assumptions for the barrier/liner material and experimentally calibrated resistance models where we examine the impact of scaling the thickness of TaN metal barrier and Ruthenium liner. TaN is typically deposited using PVD, and Ruthenium is deposited using CVD. Directional PVD of TaN results in thinner sidewall and thicker bottom coverage [42, 43]. In this work we assume 50% sidewall coverage for the PVD TaN as shown in Figure 22 a).

Metal barrier scaling presents many challenges and consumes a large portion of Cu cross-sectional area at the local levels. In section IV of this work, we compare the performances of 3 case studies for different metal barrier engineering scenarios. The first case represents the current industry best known method (BKM) that passes most reliability tests with 2nm TaN/2nm Ru bottom coverage. The second case is called the Thin scenario and represents one of the projected lower limits of barrier engineering with 1nm TaN/1nm Ru bottom coverage [22]. The third case (ImpVia) assumes current BKM barrier engineering for line resistances with advances in via resistance, either through near

barrierless via fill using ALD, prefill, or other proposed technologies. The resistance for each metal level for the three cases are given in Table 6.

**Table 6 – BEOL Key Layer Parameters and Resistances**

| Metal /<br>Via | Width/Pitch (nm) | BKM<br>MB/Liner | Thin<br>MB/Liner | ImpVia             |

|----------------|------------------|-----------------|------------------|--------------------|

| M1-M3          | 18/36            | 244 Ω/μm        | 164 Ω/μm         | $244~\Omega/\mu m$ |

| V1-V3          | 18/36            | 116 Ω           | 59 Ω             | 39 Ω               |

| M4-M5          | 24/48            | 92 Ω/μm         | 69 Ω/μm          | 92 Ω/μm            |

| V4-V5          | 24/48            | 29 Ω            | 17 Ω             | 13 Ω               |

| M6-M7          | 32/64            | 37 Ω/μm         | 30 Ω/μm          | $37~\Omega/\mu m$  |

| V6-V7          | 32/64            | 9.6 Ω           | 6.7 Ω            | 5.0 Ω              |

| M8-M9          | 40/80            | 19 Ω/μm         | 17 Ω/μm          | 19 Ω/μm            |

| V8             | 40/80            | 3.2 Ω           | 2.6 Ω            | 2.3 Ω              |

#### 4.3 Experimental Setup and Results Comparison

#### 4.3.1 Experimental Setup

In our circuit benchmarking, we analyze the Power, Performance, and Area (PPA) results of two circuits: AES and LDPC. Comparing the results of two circuits provides a more diverse analysis on the impact of BEOL parameters on the two different circuit design groups.

For the circuit optimization and P&R, the initial footprint area targets 45% core utilization based on the synthesized netlist to allow headroom for P&R repeater insertion and optimization. For our results comparison, the target frequency and area are fixed for all cases. The final GDS layouts for the two different circuits are shown in Figure 22 (b) and (c).

Figure 22 - (a) Local interconnect model cross-section and GDS layout of case BKM for (b) AES and (c) LDPC Circuit.

#### 4.3.2 Metal Barrier BKM vs Thin Scaling Results

In the first experimental setup, we compare the updated BEOL technology file that is developed for the current industry BKM with the Thin case where the bottom MB liner thickness can be scaled down by 50%. The local interconnects line resistance improves by 33% and via resistance by 49%. This has a direct impact on the effective frequency of the AES circuit as seen in our benchmarking results shown in Table 7. We see an 9.49% improvement in effective clock frequency and 6.75% reduction in the number of repeaters. When we adjust total power to the effective frequency and calculate the Power Delay Product (PDP), an overall 4.18% improvement is observed. We see this is primarily driven by the overall decrease in net resistance of the circuit.

For a much more interconnect dominant circuit like the LDPC, the impact on the effective frequency is much more pronounced. We see in Figure 22 (c) the routing congestion for the LDPC circuit is much denser in the GDS layout compared to the AES

circuit. We observe a much higher 25.74% improvement in effective frequency and a better PDP of 8.29%. Much of the PDP efficiency gain is driven by the 18.2% reduction in the required number of repeaters for the Thin case.

#### 4.3.3 Metal Barrier Thin vs ImpVia Results

Using the same optimization and P&R process described in the previous section, we analyze the PPA results comparing the impact of BKM and improved via case on the circuit performance. For the AES circuit, there is a 7.1% improvement in effective clock frequency and 3.37% improvement in PDP. While the total net resistance improves by 40%, the AES circuit is a more cell dominated design and is less sensitive to the improvement of the wire and via resistances.

For a more routing demanding LDPC design, we observe a higher (15.36%) improvement in effective clock frequency and a 6.49% improvement in PDP. The improved via case has better timing while requiring fewer repeaters and a lower total wire length.

Table 7 – Iso-Area Performance Results Comparison between current industry BKM, Thin Scaled MB, and Improved Via BEOL RC Extraction

| AES Circuit            |             |               | LDPC Circuit  |                    |               |                    |               |               |                |               |                    |

|------------------------|-------------|---------------|---------------|--------------------|---------------|--------------------|---------------|---------------|----------------|---------------|--------------------|

|                        |             | ВКМ           | Thin          | Iso-<br>Area<br>1% | ImpVia        | Iso-<br>Area<br>∆% | BKM           | Thin          | Iso-Area<br>4% | ImpVia        | Iso-<br>Area<br>∆% |

| Target freq. (GHz)     |             | 3             | 3             |                    | 3             |                    | 1.8           | 1.8           |                | 1.8           |                    |

| Cell count (           | (#)         | 17,735        | 17,017        | -4.05%             | 17,089        | -3.64%             | 88,779        | 80,597        | -9.22%         | 85,223        | -4.01%             |

| Inv / Buffer Count (#) |             | 6,934         | 6,466         | -6.75%             | 6,502         | -6.23%             | 39,753        | 32,518        | -18.20%        | 36,344        | -8.58%             |

| Worst slack            | k (ns)      | -0.059        | -0.025        | -57.63%            | -0.033        | -<br>44.07%        | -0.436        | -0.233        | -46.56%        | -0.304        | 30.28%             |

| Effective fr           | eq. (GHz) * | 2.55          | 2.79          | 9.49%              | 2.73          | 7.10%              | 1.01          | 1.27          | 25.74%         | 1.16          | 15.36%             |

| Down                   | Total       | 5.70          | 5.98          | 4.91%              | 5.90          | 3.48%              | 47.93         | 55.27         | 15.32%         | 51.70         | 7.87%              |

| Power (mW) @           | Internal    | 2.69          | 2.83          | 5.11%              | 2.78          | 3.38%              | 13.34         | 14.89         | 11.60%         | 13.89         | 4.06%              |

| eff.                   | Switching   | 3.01          | 3.15          | 4.74%              | 3.12          | 3.58%              | 34.58         | 40.37         | 16.76%         | 37.81         | 9.34%              |

| frequency              | Leakage     | 0.002         | 0.002         | -0.51%             | 0.002         | 0.74%              | 0.010         | 0.009         | -13.48%        | 0.010         | -8.14%             |