# METHODOLOGY AND ANALYSIS FOR EFFICIENT CUSTOM ARCHITECTURE DESIGN USING MACHINE LEARNING

A Dissertation Presented to The Academic Faculty

By

Ananda Samajdar

In Partial Fulfillment

of the Requirements for the Degree

Doctor of Philosophy in the

School of Electrical and Computer Engineering

College of Engineering

Georgia Institute of Technology

December 2021

# METHODOLOGY AND ANALYSIS FOR EFFICIENT CUSTOM ARCHITECTURE DESIGN USING MACHINE LEARNING

# Thesis committee:

Dr. Tushar Krishna, Advisor School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Saibal Mukhopadhyay School of Electrical and Computer Engineering Georgia Institute of Technology Dr. Hyesoon Kim School of Computer Science Georgia Institute of Technology

Dr. Vijay Janapa Reddi John A Paulson School of Engineering and Applied Sciences *Harvard University*

Dr. Vivek Sarkar School of Computer Science Georgia Institute of Technology

Date approved: October 26, 2021

# **ACKNOWLEDGMENTS**

The last five years have been a roller coaster ride with a string of many news. I am thankful for so many people and lucky co-incidences that I do not think I will be able to accurately articulate in this section. Nevertheless, I will try my best in the following paragraphs to express my gratitude to the numerous people who have touched my life, and made this journey truly memorable.

First I would like to thank my family. My father who devoted his entire life and made countless sacrifices so that I can obtain the best possible education. My mother, who to me is the human embodiment of strength. Never faltered to keep me motivated and looking forward, even in the darkest of time. My younger brother, who has been a constant source of moral support. My fiance, who never lost faith in me, and has worked equally hard and made sacrifices so that I can fulfil my dreams.

I consider myself to be fortunate to have Dr. Tushar Krishna as my advisor. Tushar has been a constant source of positive will power and motivation. Not only he is an excellent scientist and a highly effective researcher, he is also an excellent mentor, compassionate friend and an inspiring leader. I would like to thank him for being patient with me both personally and professionally and helping me grow as researcher. I hope one day I can pay forward to my mentees.

I also want to extend my deepest gratitude to my thesis committee members, Prof. Saibal Mukhopadhyay, Prof. Hyesoon Kim, Prof. Vivek Sarkar, Prof. Vijay Janapa Reddi. I am grateful for their suggestions and support for my work. Their encouragements and constructive feedback has helped me immensely to improve my thesis.

I would like to specially mention Prof. Moin Qureshi for his support and encouragement over the years. I remember reaching out to Prof. Qureshi even before starting my studies at Georgia Tech. Over the years discussions with him and his insighful advice has helped me a lot in navigating the grad life.

My research work has been greatly shaped by discussions and exchange of ideas among my brilliant collaborators. Dr. Paul Whatmough, Dr. Yuhao Zhu, and Matt Mattina have motivated and supported me with development and increasing the reach of SCALE-Sim. In many ways, I owe it to Paul and Yuhao for showing me the direction in thinking about system design with custom architectures. Dr. Micheal Pellauer, Dr. Anshuman Parashar, Prof. Joel Emer are not only shining stars in the Machine learning accelerator design community, whose work greatly shaped my thought and understanding, but also have been great mentors who helped me multiple times along my PhD journey. I am thankful to Prof. Nachiket Kapre for helping me dip my hand in FPGA based acceleration. I am yet to meet another person who is so energetic and hands-on with actual development while also actively managing a research lab with multiple students. I am grateful to Mrs. Amrita Mathuriya and Dr. Sasi Manipatruni for having me over at Kepler and providing me with the glimpse of the entrepreneur life. I had the unique experience of working at their home during the early phase of Kepler. Thank you guys for treating me as an integral part of the Kepler family.

I have also had the good fortune to work with exceptionally brilliant student collaborators. Jun (Dr. Hyoukjun Kown) has practically mentored me to ramp up on the life of a PhD student. The Genesys project have been much harder to complete without the late night discussion and tremendous research inputs from Kartikay and Parth. Moritz (Dr. Jan Mortiz Joseph) is not only a brilliant scientist who I was fortunate to have as a team mate, but is also a very dear friend. I think I owe an apology to Eric to make him sit through my ranting sessions. You are one of the most patient people I know. Matthew and Geonhwa, thank you for helping me out so many times with my papers and endless discussions.

Thank you Divya, Guru, Poulami, Moumita, Prithayan. You guys are my family in the US and responsible for so many happy memory away from home. Also a big thanks to former and current members of the Synergy lab, Hyoukjun, Saeed, Felix, Mayank, Vineet, Yehowshua, William, Geonhowa, Raveesh, Abhimanyu, Parth, Aniruddh, Matthew. You

| guys are some of the most wholesome people that I know | of and made my our lab a second |

|--------------------------------------------------------|---------------------------------|

| home.                                                  |                                 |

# **TABLE OF CONTENTS**

| Ackno   | wledgments                                                                 | v  |

|---------|----------------------------------------------------------------------------|----|

| List of | Tables                                                                     | ii |

| List of | Figures                                                                    | V  |

| Summa   | ary                                                                        | ii |

| Chapte  | er 1: Introduction                                                         | 1  |

| 1.1     | Thesis Contribution                                                        | 2  |

|         | 1.1.1 Systematic design decisions using analytical modeling and simulation | 4  |

|         | 1.1.2 Scalable and flexible DNN accelerator design                         | 4  |

|         | 1.1.3 Learning the accelerator design space using machine learning (ML)    | 5  |

| 1.2     | Thesis Impact                                                              | 7  |

| 1.3     | Thesis Statement                                                           | 8  |

| 1.4     | Thesis Overview                                                            | 8  |

| Chapte  | er 2: Background and Related Works                                         | 0  |

| 2.1     | Background                                                                 | 0  |

|         | 2.1.1 Computation in Deep Neural Network                                   | 0  |

| 2.2     | Related Works                                                              | .2 |

|        | 2.2.1    | DNN Accelerator proposals                                                                               | 12 |

|--------|----------|---------------------------------------------------------------------------------------------------------|----|

|        | 2.2.2    | Simulation and Analytical Infrastructure for DNN accelerator Design                                     | 16 |

|        | 2.2.3    | Machine learning for assisting system design                                                            | 17 |

| Chapte |          | nalytical modeling and simulation infrastructure for system-<br>c characterization and DNN accelerators | 19 |

| 3.1    | Introd   | luction                                                                                                 | 19 |

| 3.2    | SCAL     | E-Sim: Systolic Accelerator Simulator                                                                   | 20 |

|        | 3.2.1    | Background: Systolic Arrays and Dataflows                                                               | 20 |

|        | 3.2.2    | System Integration                                                                                      | 24 |

|        | 3.2.3    | Implementation                                                                                          | 25 |

|        | 3.2.4    | Validation of the tool                                                                                  | 26 |

|        | 3.2.5    | User Interface                                                                                          | 27 |

| 3.3    | Analy    | tical model for runtime                                                                                 | 28 |

|        | 3.3.1    | Mapping across Space and Time                                                                           | 29 |

|        | 3.3.2    | Runtime for Scale-Up                                                                                    | 30 |

|        | 3.3.3    | Optimal Partitioning for Scale-Out                                                                      | 33 |

| 3.4    | Analy    | sis of Scaling                                                                                          | 35 |

|        | 3.4.1    | Cost of scaling out                                                                                     | 39 |

|        | 3.4.2    | Optimizing for multiple workloads                                                                       | 41 |

| 3.5    | Chapt    | er Summary                                                                                              | 42 |

| Chapte |          | terconnect aware scalable DNN accelerator implementation ing hardware cascades in Xilinx FPGAs          | 44 |

| 11     | Internal | lunation.                                                                                               | 11 |

| 4.2    | Backg  | round                                                                  | 47 |

|--------|--------|------------------------------------------------------------------------|----|

|        | 4.2.1  | Dedicated Cascade Interconnect in Xilinx Ultrascale FPGAs              | 47 |

| 4.3    | High-l | Frequency FPGA Cascades                                                | 48 |

|        | 4.3.1  | Building Block: Convolution                                            | 48 |

|        | 4.3.2  | Building Block: Matrix-Vector Multiply                                 | 50 |

|        | 4.3.3  | Scaling And Tiling                                                     | 51 |

|        | 4.3.4  | System Design Strategy                                                 | 53 |

|        | 4.3.5  | Overall FPGA Architecture                                              | 54 |

| 4.4    | Metho  | dology                                                                 | 54 |

|        | 4.4.1  | FPGA Mapping                                                           | 54 |

|        | 4.4.2  | Performance Analysis Of MLPerf Benchmarks                              | 55 |

| 4.5    | Evalua | ation                                                                  | 56 |

|        | 4.5.1  | Frequency Trends                                                       | 58 |

|        | 4.5.2  | Performance Trends                                                     | 59 |

| 4.6    | Lesson | ıs                                                                     | 61 |

| 4.7    | Chapt  | er Summary                                                             | 62 |

| Chapte |        | rchitect: Learning design and mapping space for custom artectures      | 64 |

| 5.1    | Introd | uction                                                                 | 64 |

| 5.2    | Case S | tudies                                                                 | 65 |

|        | 5.2.1  | Case 1: Optimal Architecture and Mapping for Monolithic Systolic Array | 66 |

|        | 5.2.2  | Case 2: Optimal Memory Partitioning for Monolithic Systolic Array      | 70 |

|                   | 5.2.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Case 3: Optimal Compute Scheduling for Multi-Array System                                                                                                                                                        | 73                               |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 5.3               | Desig                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | n Aware Analysis                                                                                                                                                                                                 | 76                               |

|                   | 5.3.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Array Shape and Dataflow                                                                                                                                                                                         | 76                               |

|                   | 5.3.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | SRAM buffer Sizing                                                                                                                                                                                               | 80                               |

| 5.4               | Learn                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ing Architecture and Mapping Space                                                                                                                                                                               | 81                               |

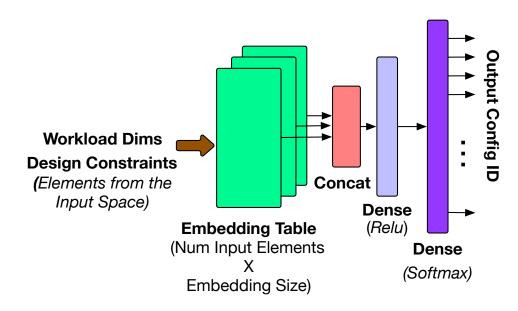

|                   | 5.4.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Design Optimization as Learning Problem                                                                                                                                                                          | 81                               |

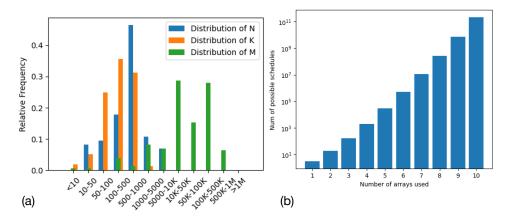

|                   | 5.4.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Dataset Generation                                                                                                                                                                                               | 82                               |

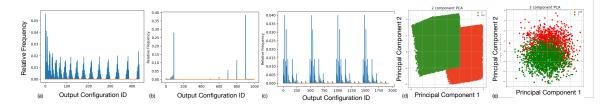

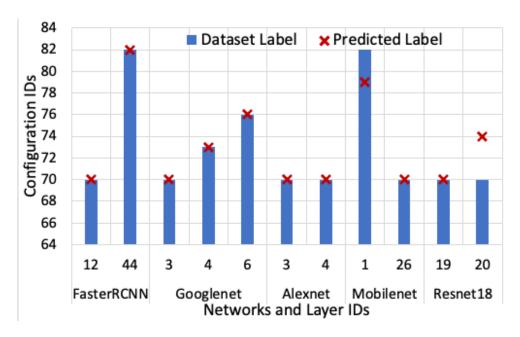

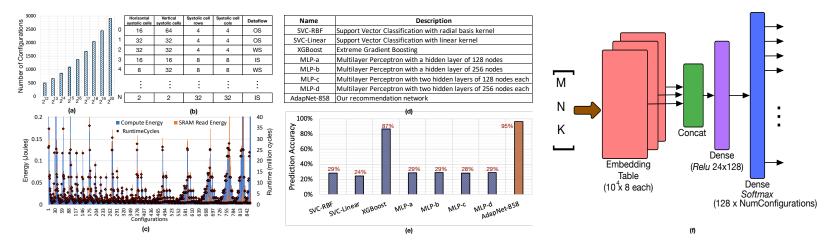

|                   | 5.4.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Statistical analysis                                                                                                                                                                                             | 85                               |

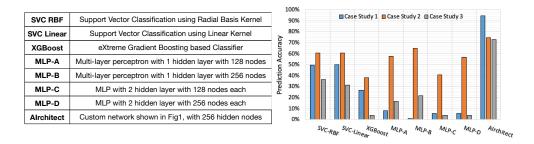

|                   | 5.4.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Learning with Existing Classifiers                                                                                                                                                                               | 87                               |

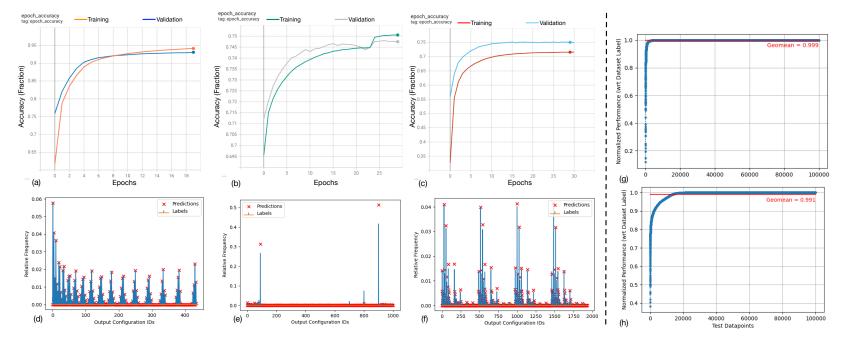

| 5.5               | AIrc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | итест: Design and Analysis                                                                                                                                                                                       | 90                               |

| 5.6               | Chapt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | er Summary                                                                                                                                                                                                       | 93                               |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                  |                                  |

| Chapte            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | f-Adaptive Reconfigurable Arrays (SARA): Learning GEMM celerator Configuration Space Using ML                                                                                                                    | 94                               |

| Chapte            | Ac                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                  |                                  |

| •                 | Ac                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | celerator Configuration Space Using ML                                                                                                                                                                           | 94                               |

| 6.1               | Ac<br>Introd<br>Backg                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | uction                                                                                                                                                                                                           | 94<br>98                         |

| 6.1               | Ac<br>Introd<br>Backg                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | celerator Configuration Space Using ML                                                                                                                                                                           | 94<br>98<br>00                   |

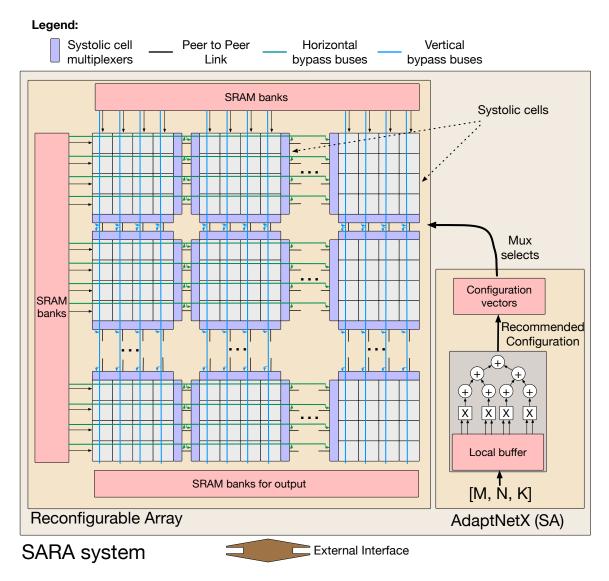

| 6.1               | Ac<br>Introd<br>Backg<br>Recon                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | celerator Configuration Space Using ML                                                                                                                                                                           | 94<br>98<br>00                   |

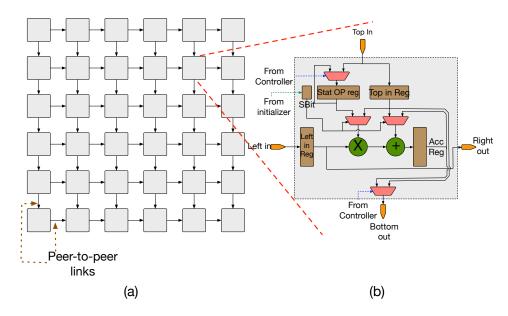

| 6.1               | Accordance  | celerator Configuration Space Using ML       9         cuction       9         round and Motivation       9         figurable Array Design       10         Compute array       10                               | 94<br>98<br>00<br>00             |

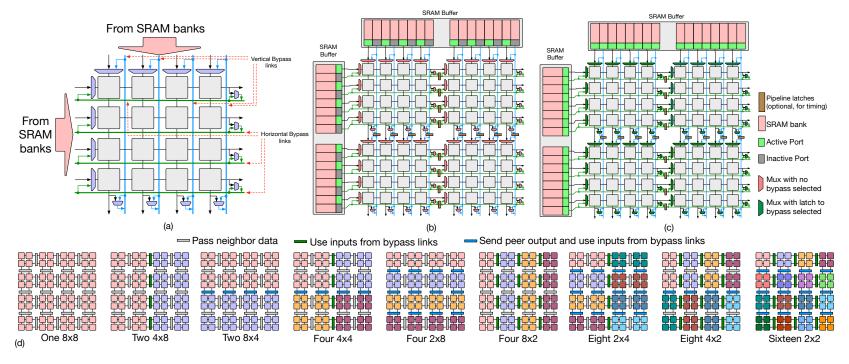

| 6.1               | Accommendation Accomm | celerator Configuration Space Using ML       9         cuction       9         round and Motivation       9         figurable Array Design       10         Compute array       10         Bypass links       10 | 94<br>98<br>00<br>03<br>04       |

| 6.1               | Accordance   Introduction   Backgrand   Recordance   6.3.1   6.3.2   6.3.3   6.3.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | celerator Configuration Space Using ML 9   uction 9   round and Motivation 9   figurable Array Design 10   Compute array 10   Bypass links 10   Scratch pad memory 10                                            | 94<br>98<br>00<br>03<br>04       |

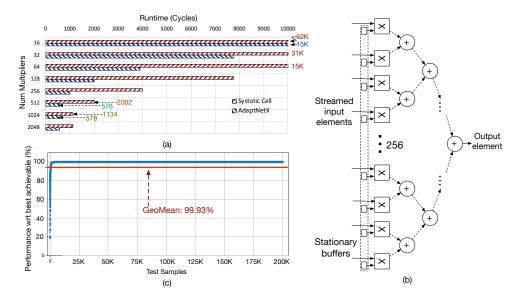

| 6.1<br>6.2<br>6.3 | Accordance   Introduction   Backgrand   Recordance   6.3.1   6.3.2   6.3.3   6.3.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | celerator Configuration Space Using ML 9   cuction 9   round and Motivation 9   figurable Array Design 10   Compute array 10   Bypass links 10   Scratch pad memory 10   Control 10                              | 94<br>98<br>00<br>03<br>04<br>05 |

|              | 6.4.3   | Alternatives to AdaptNet                                                             | 111 |

|--------------|---------|--------------------------------------------------------------------------------------|-----|

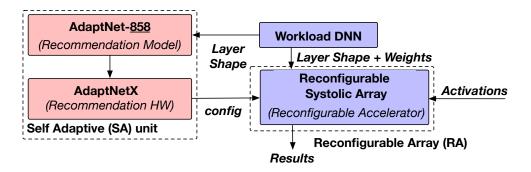

| 6.5          | SELF A  | Adaptive Reconfigurable Arrays                                                       | 112 |

|              | 6.5.1   | Hardware to run AdaptNet                                                             | 113 |

|              | 6.5.2   | SAGAR Accelerator                                                                    | 114 |

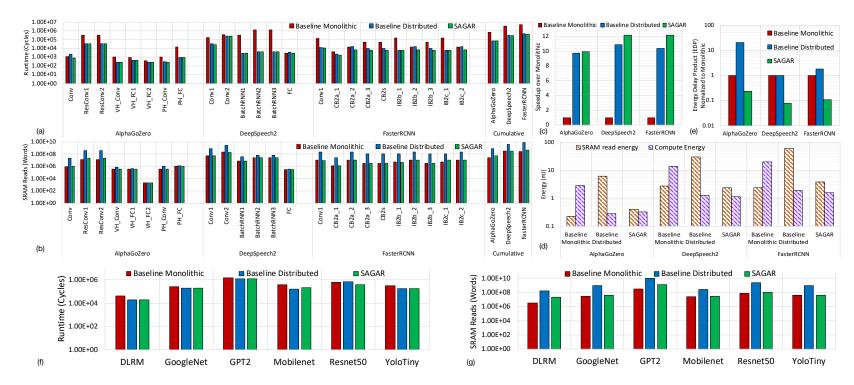

| 6.6          | Evalua  | ations                                                                               | 117 |

|              | 6.6.1   | Architectural evaluations                                                            | 117 |

|              | 6.6.2   | Implementation evaluations                                                           | 122 |

|              | 6.6.3   | Comparison with SIGMA                                                                | 124 |

| 6.7          | Relate  | d Works                                                                              | 126 |

| 6.8          | Chapte  | er Summary                                                                           | 127 |

| Chapte       | r 7: Co | nclusions                                                                            | 128 |

| 7.1          | Overv   | iew of Insights                                                                      | 128 |

| 7.2          | Discus  | ssions                                                                               | 133 |

| 7.3          | Future  | Work                                                                                 | 135 |

| Append       | dices . |                                                                                      | 137 |

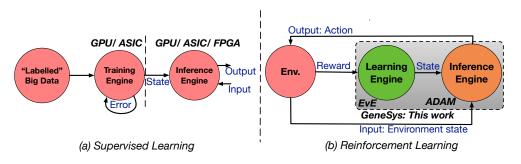

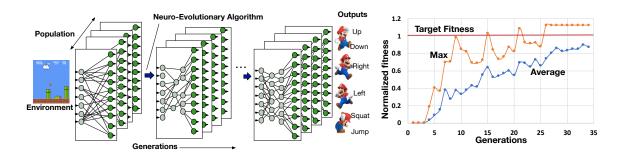

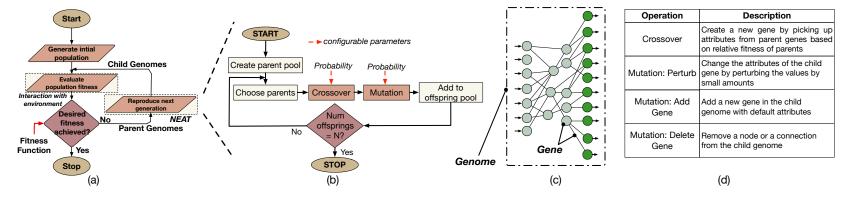

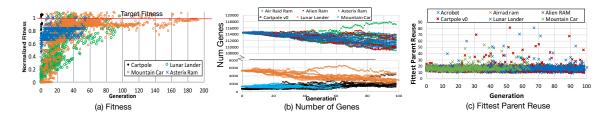

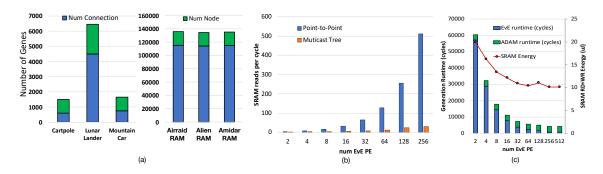

| Арр          | endix A | : GeneSys: Enabling Continuous Learning through Neural Network Evolution in Hardware | 138 |

| Refere       | nces    |                                                                                      | 169 |

| <b>T</b> 7'4 |         |                                                                                      | 101 |

# LIST OF TABLES

| 3.1 | SCALE-SIM config description                                                                                                                                                                                                                                               | 27  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.2 | SCALE-Sim Topology file description                                                                                                                                                                                                                                        | 28  |

| 3.3 | Spatio-Temporal Allocation of DNN Dimensions                                                                                                                                                                                                                               | 29  |

| 3.4 | Matrix dimensions of our language model workloads. mapped to $S_R$ , $S_C$ , and $T$                                                                                                                                                                                       | 35  |

| 4.1 | MLPerf and GoogLeNet benchmark characteristics                                                                                                                                                                                                                             | 54  |

| 4.2 | Resource and Frequency Trends for Convolution and Matrix-Multiplication blocks, tiles, and full-chip layouts                                                                                                                                                               | 57  |

| 4.3 | Xilinx VU37P FPGA inference latency (ms) and throughput (inf/s) for MLPerf benchmarks and GoogLeNet                                                                                                                                                                        | 60  |

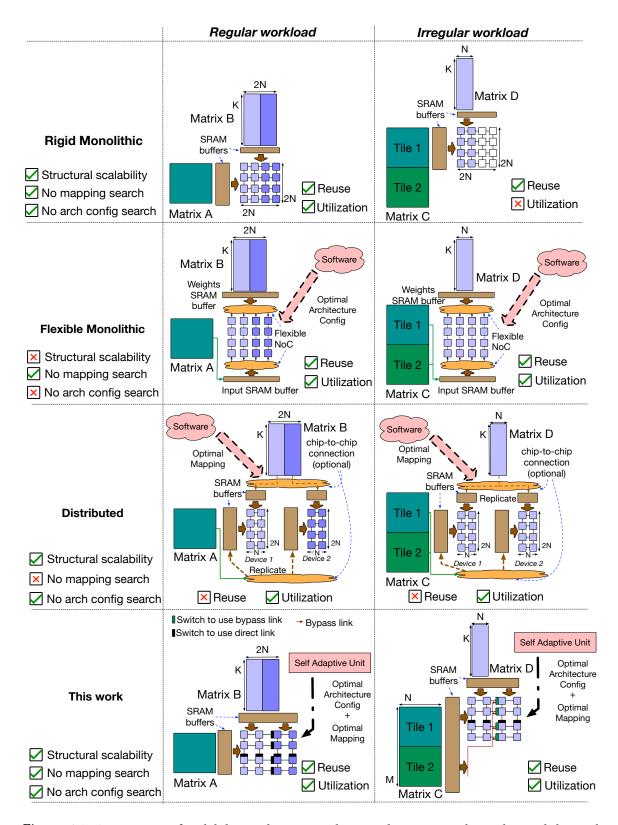

| 6.1 | Previous accelerator proposals categorized in terms of computation support, and flexibility of hardware and mapping. Accelerators are categorized into various types introduced in Figure 6.1 viz. Rigid Monolithic (RM), Flexible Monolithic (FM), and Distributed (Dist) | 99  |

| 6.2 | Bandwidth requirements for the bypass links for various dataflows, contrasted to the requirements of operands (names in parenthesis reflects the corresponding operands in 2D convolutions)                                                                                | 104 |

| 6.3 | Table depicting the architectural configuration of distributed systolic array based systems, monolithic systolic array baseline, and <i>SAGAR</i>                                                                                                                          | 117 |

| 6.4 | Dimensions for the synthetic GEMM workloads                                                                                                                                                                                                                                | 118 |

| A.1 | Open AI Gym [85] environments for our experiments                                                                                                                                                                                                                          | 146 |

| A.2 | Comparing DQN with EA        | 152 |

|-----|------------------------------|-----|

| A.3 | Target System Configurations | 162 |

# LIST OF FIGURES

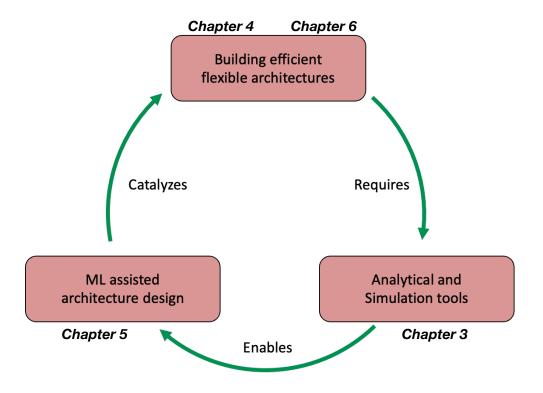

| 1.1 | The three main directions of research which build up this thesis                                                                                                       | 3  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

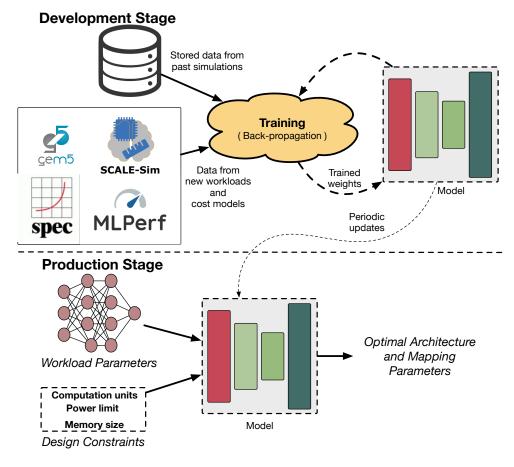

| 1.2 | Schematic of a reference implementation scenario for deployment of a learnt model for aiding optimization of architecture and mapping parameters                       | 6  |

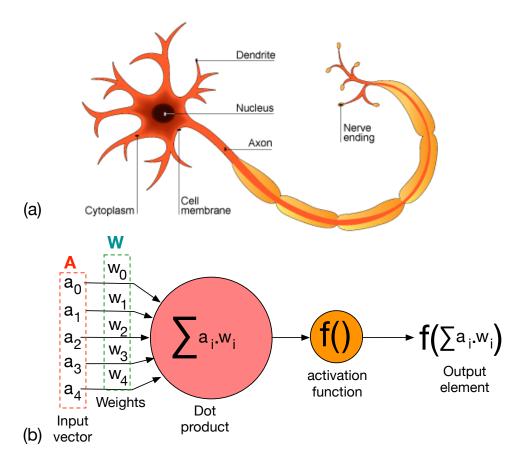

| 2.1 | (a)Schematic of biological neural adapted from [3], (b) Logical structure of an artificial neuron                                                                      | 11 |

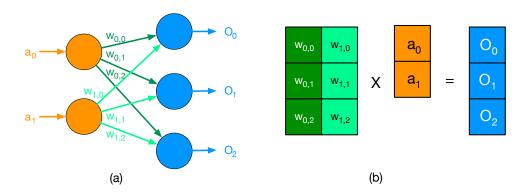

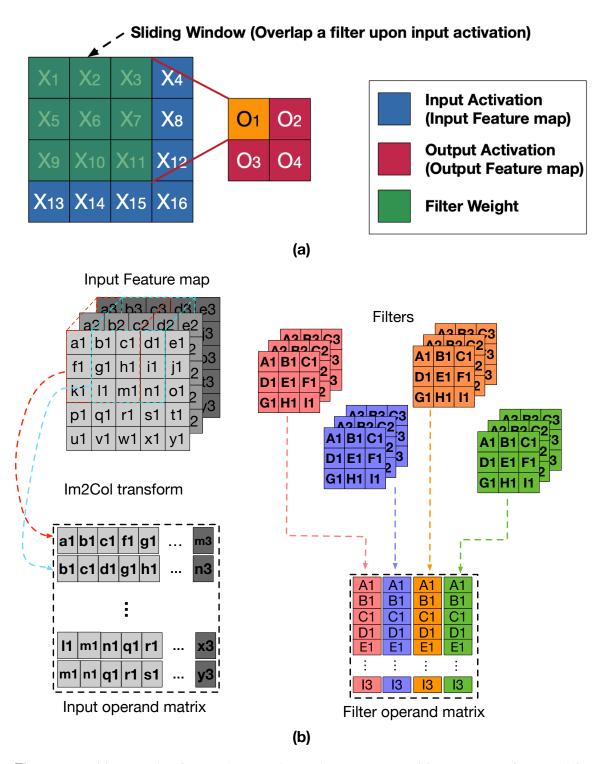

| 2.2 | (a) Example of a simple MLP network with inputs, outputs, and weights (b) Equivalent matrix-vector multiplication                                                      | 12 |

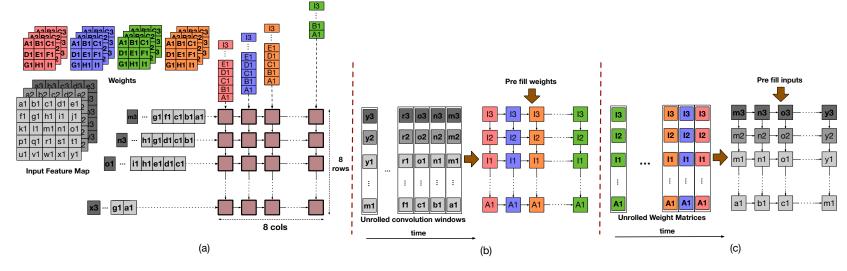

| 2.3 | (a) Example of a simple convolution layer in a CNN (b) Formation of operand for equivalent matrix-matrix multiplications in a Conv2D layer using Im2Col transformation | 13 |

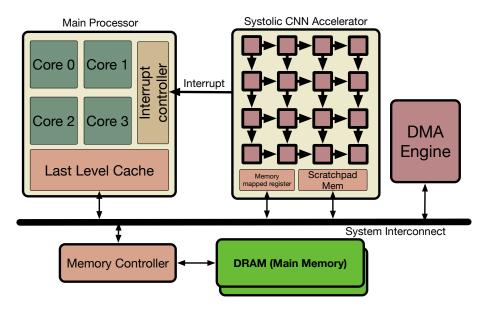

| 3.1 | Schematic showing the integration model of accelerator in a systems context                                                                                            | 20 |

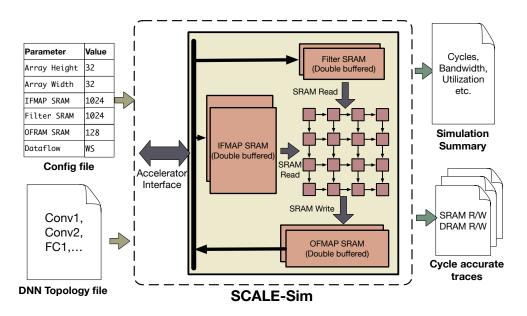

| 3.2 | Schematic depicting the inputs needed and the outputs generated by SCALE-SIM                                                                                           | 21 |

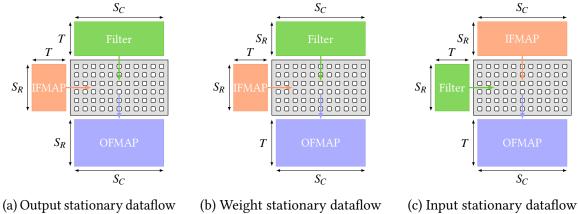

| 3.3 | Schematic showing the mapping in various dataflows (a) Output stationary; (b) Weight stationary; (c) Input stationary                                                  | 22 |

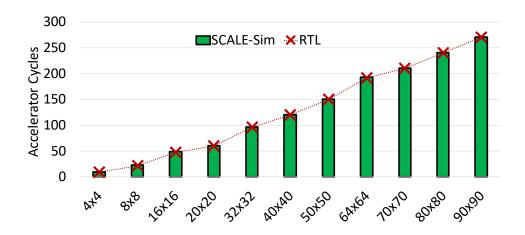

| 3.4 | Figure depicting the cycles obtained by RTL implementation and SCALE-Sim simulation for varying array sizes under full utilization                                     | 26 |

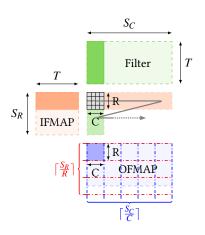

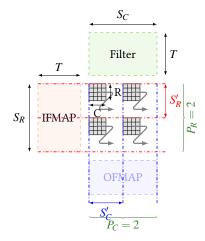

| 3.5 | Data Flow Mapping                                                                                                                                                      | 28 |

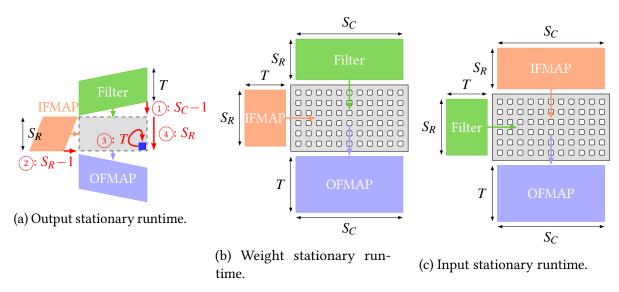

| 3.6 | Schematic depicting steps to model runtime for dataflows in systolic array.                                                                                            | 31 |

| 3.7 | Scale Up                                                                                                                                                               | 34 |

| 3.8 | Scale Out                                                                                                                                                              | 34 |

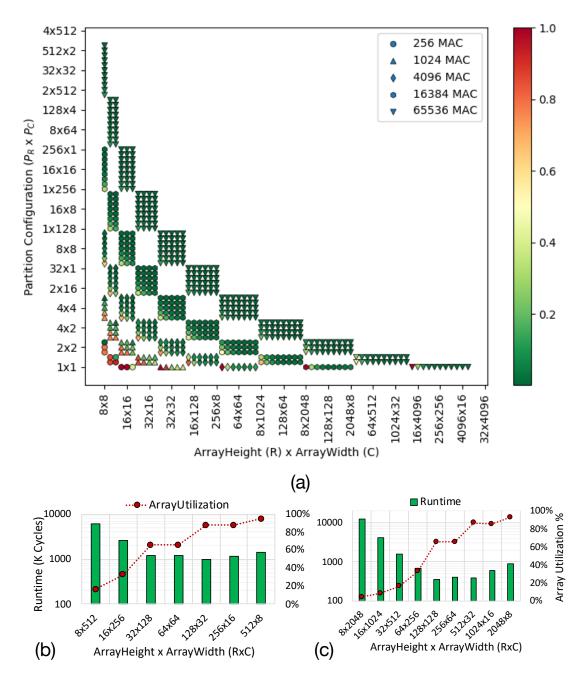

| 3.9  | (a) The search space of all possible scale-up (monolithic) and scale-out (partitioned) configurations, with different array sizes; the color represents runtime for TF0 layer of the Transformer model, normalized to max runtime across configurations for a given array size. The variation in runtime and array utilization for all scaled-up configurations when running TF0 layer for (b) 2 <sup>14</sup> MACs, (c) 2 <sup>16</sup> MACs | 36 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

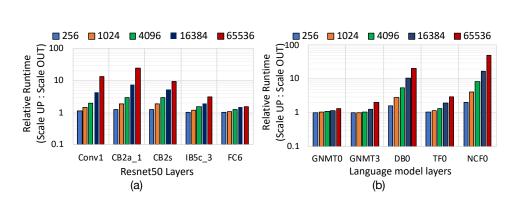

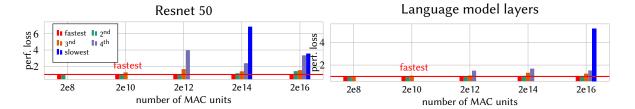

| 3.10 | Ratio of no stall runtimes obtained in best scaled-up array configuration vs best scaled-out (partitioned) configuration for a few layers in (a) Resnet50 and (b) Language models, for different MAC units                                                                                                                                                                                                                                    | 38 |

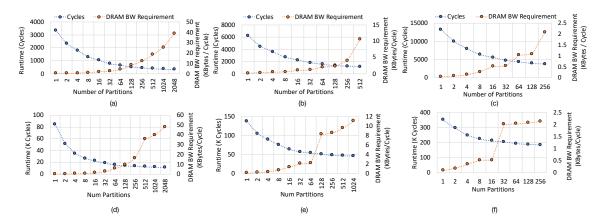

| 3.11 | Trends for best possible stall free runtime and DRAM bandwidth requirements when the number of partitions are increased from monolithic array in CBa_3 layer in Resnet50 for (a) $2^{18}$ MAC units, (b) $2^{16}$ MAC units, and (c) $2^{14}$ MAC units; and TF0 layer in Transformer for (d) $2^{18}$ MAC units, (e) $2^{16}$ MAC units, and (f) $2^{14}$ MAC units                                                                          | 39 |

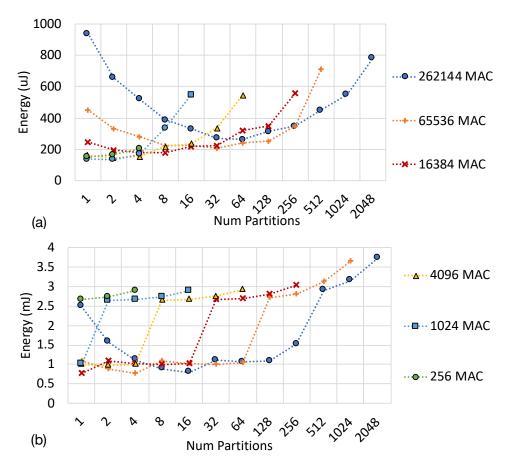

| 3.12 | Energy consumption in running (a) Layer CBa_3 from Resnet50 and (b) layer TB0 from Transformer, when scaling-up and scaling out with different MAC units                                                                                                                                                                                                                                                                                      | 40 |

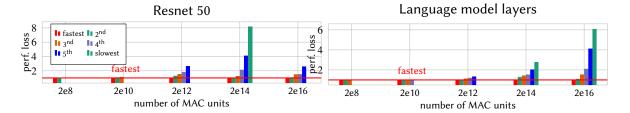

| 3.13 | Total runtime loss vs. best configuration for <i>scale-up</i> ie. aspect ratio (R:C). Colors differentiate configurations ordered by runtime                                                                                                                                                                                                                                                                                                  | 42 |

| 3.14 | Total runtime loss vs. best configuration for <i>scale-out</i> . ie part order $(P_R, P_C)$ and aspect ratio (R:C). Colors differentiate configurations ordered by runtime.                                                                                                                                                                                                                                                                   | 43 |

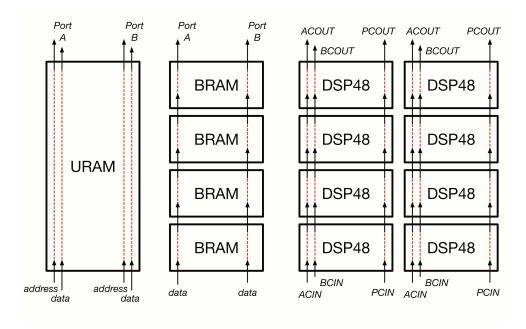

| 4.1  | High level view of cascades connections between DSP48, RAMB18, and URAM288 blocks                                                                                                                                                                                                                                                                                                                                                             | 45 |

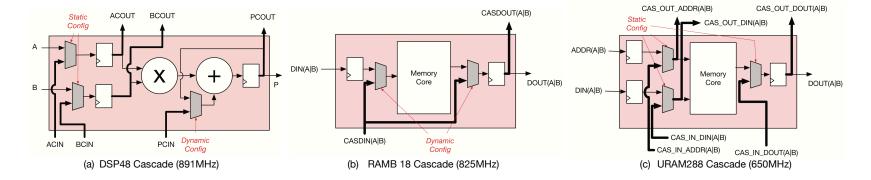

| 4.2  | Hard cascades structures embedded in Xilinx hard blocks                                                                                                                                                                                                                                                                                                                                                                                       | 46 |

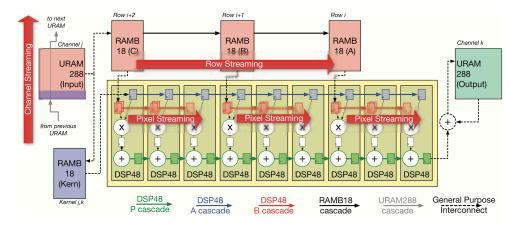

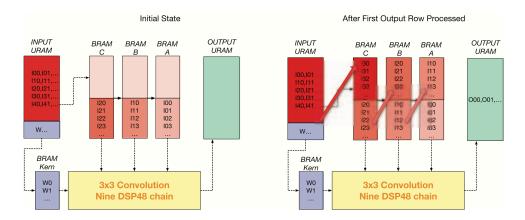

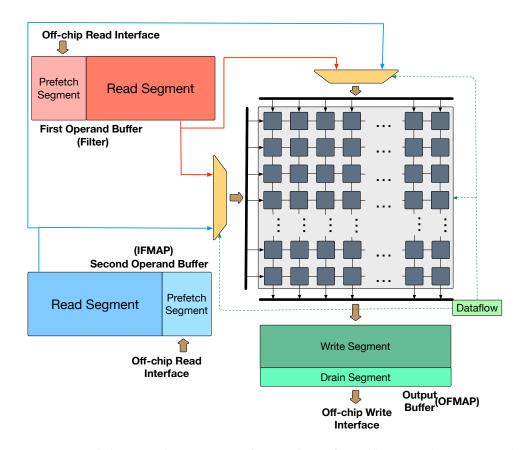

| 4.3  | Design of a $3 \times 3$ convolution block. DSPs configured in SIMD=2 mode, a set of 8bit weights are shifted into the B cascade. One stream of $2 \times 8b = 16b$ data streamed in B cascades from different rows. BRAM cascades also configured to exploit row reuse                                                                                                                                                                       | 49 |

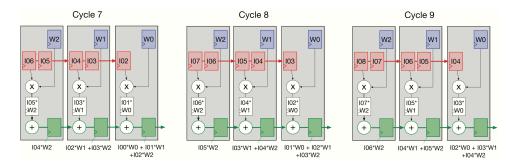

| 4.4  | The state of the DSP48 blocks in steady operation for $1 \times 3$ filter slice using 3 DSP48 units                                                                                                                                                                                                                                                                                                                                           | 49 |

| 4.5  | Data movement between URAM and BRAM to support $3 \times 3$ convolution while exploiting data reuse                                                                                                                                                                                                                                                                                                                                           | 50 |

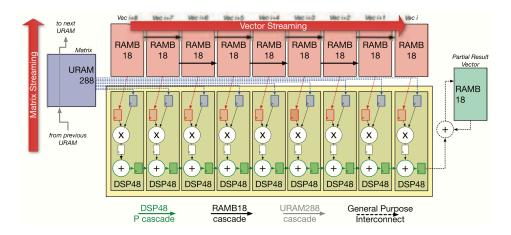

| 4.6  | matrix-vector multiplications. The DSP-48 chain is configured with SIMD=1 mode to perform matrix-vector product of 8b inputs. A chain of 9 DSPS is configured to perform length-9 dot products. URAM distributes 9 chunks of 8b values from the matrix in a row-wise fashion. The bank of 9 BRAMs distributes 8b values                                                | 51 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

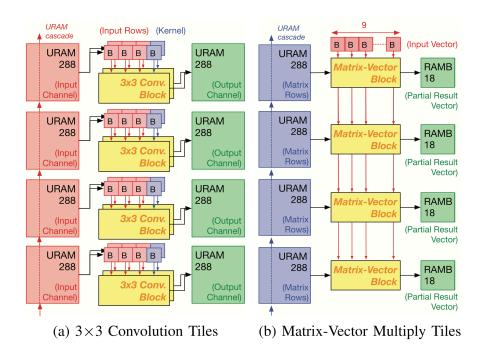

| 4.7  | Repeating tiles of the ML accelerator that obey Xilinx VU37P resource, capacity bandwidth constraints: Two Convolution tiles sharing the weight memory, while 4 tiles of Matrix-Vector multiplication block share the vector RAM                                                                                                                                       | 52 |

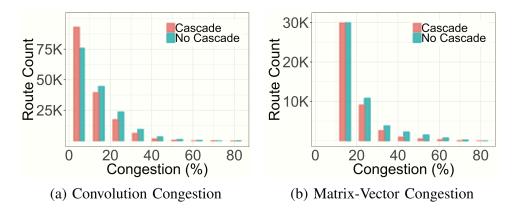

| 4.8  | Histogram of congestion of routes for full-chip Convolution and Matrix-Vector multiplication hardware                                                                                                                                                                                                                                                                  | 56 |

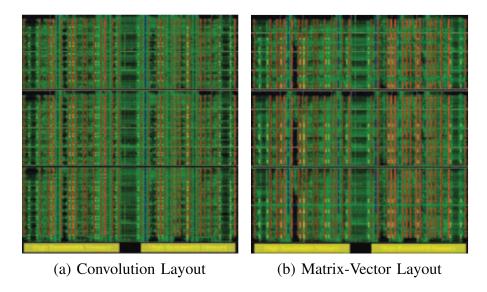

| 4.9  | Full chip VU37P layout of Convolution and Matrix-Vector multiplication hardware                                                                                                                                                                                                                                                                                        | 58 |

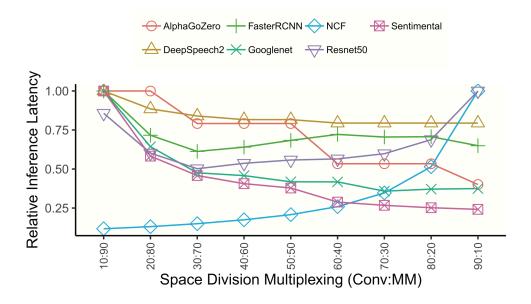

| 4.10 | Optimizing resource allocation for MLPerf Workloads                                                                                                                                                                                                                                                                                                                    | 61 |

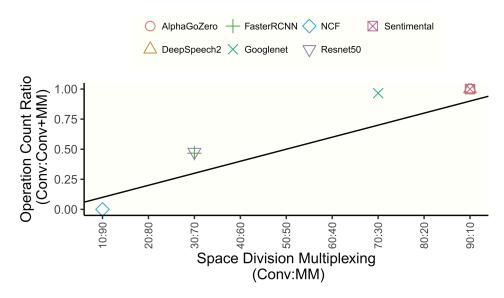

| 4.11 | Correlating MLPerf benchmark characteristics to Space Division Multiplexing arrangement                                                                                                                                                                                                                                                                                | 62 |

| 5.1  | Monolithic systolic array template with configurable array dimensions, choice of dataflow, and configurable buffer sizes                                                                                                                                                                                                                                               | 66 |

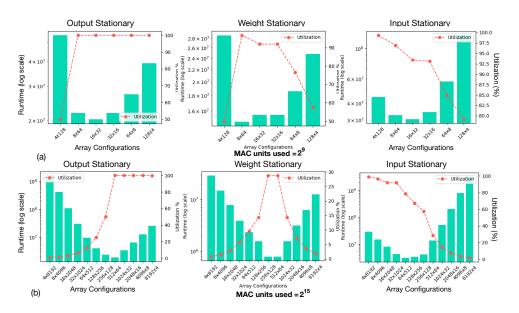

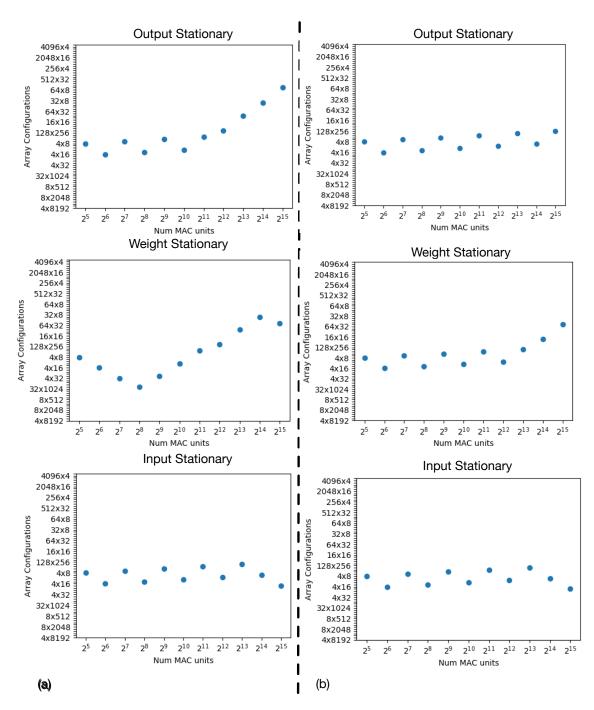

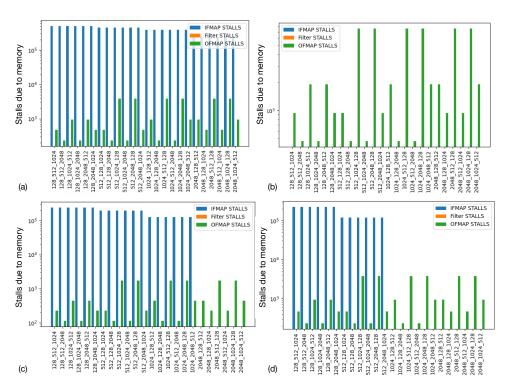

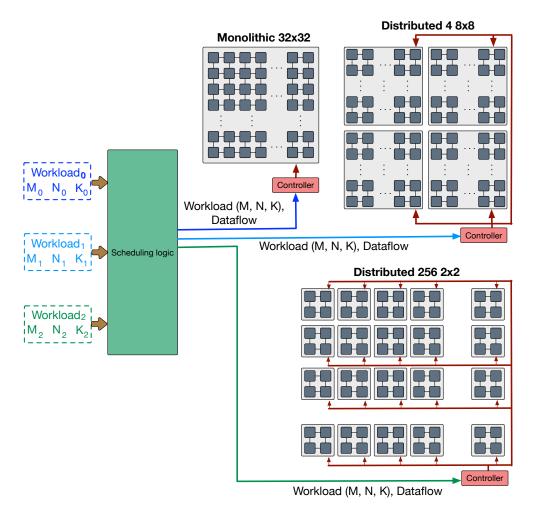

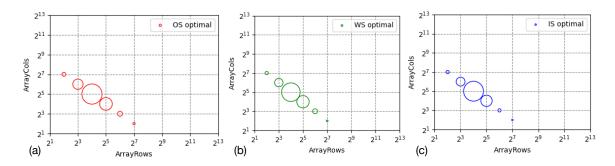

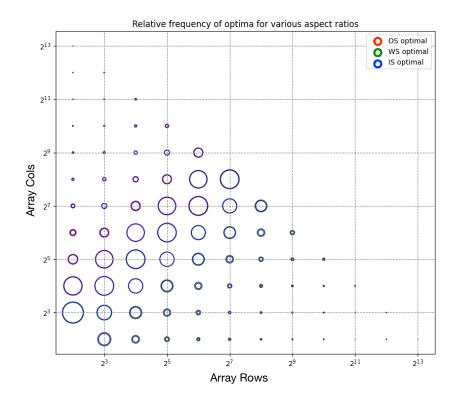

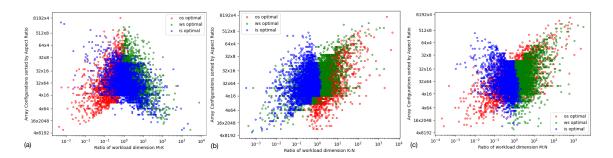

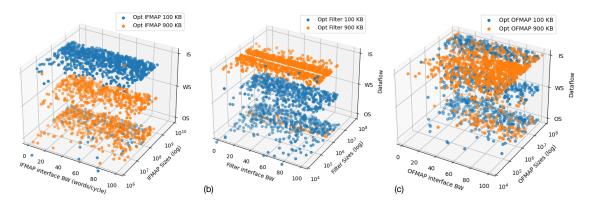

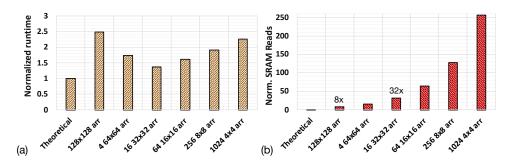

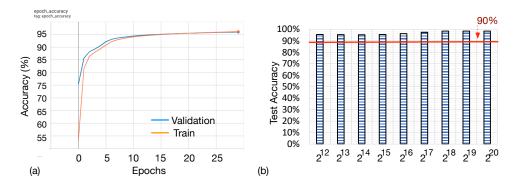

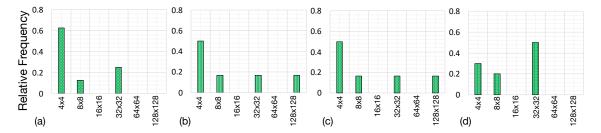

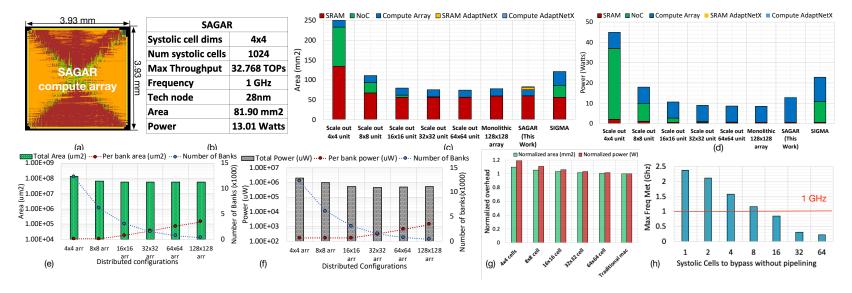

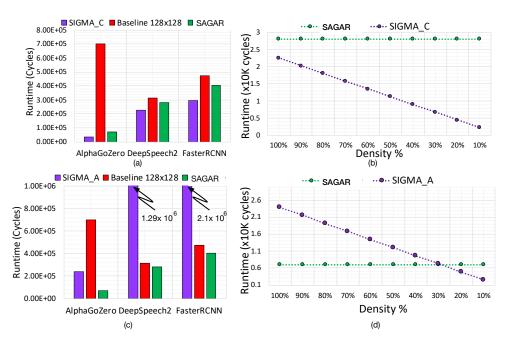

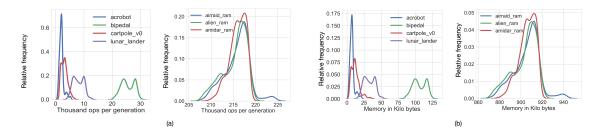

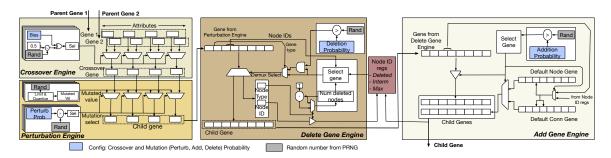

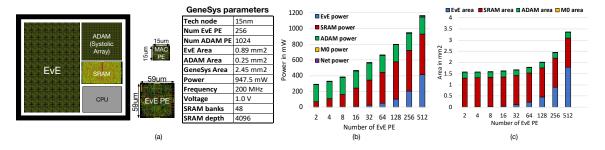

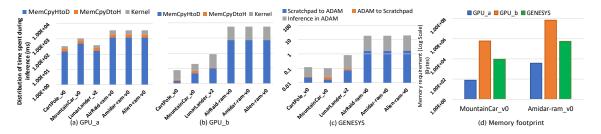

| 5.2  | Variation of runtime and utilization (red dotted line) when using different array shapes and dataflows for (a) $2^9$ MAC units, and (b) $2^{15}$ MAC units for first layer in ResNet18                                                                                                                                                                                 | 67 |