# Power Quality Improvement of Electrical Power Systems within More Electric Aircraft

Cheng Wang (M.Eng)

Thesis submitted to the University of Nottingham for the degree of Doctor of Philosophy, February 2021

# Acknowledgements

First of all, I would like to thank my supervisors Dr. Tao Yang and Prof. Serhiy Bozhko for enabling all my research activities and their great support. Also, my thanks go to Dr. Alan Watson for acting as my internal examiner and Prof. Fei Gao for acting as my external examiner.

I also would like to express my sincere gratitude to China Scholarship Council (CSC) for funding my PhD study.

In addition, many thanks for a lot of help and support from the research fellows and PhD students in the PEMC group, Dr. Zhen Huang, Xiaoyu Lang, Dr. Zhenyu Wang, Dr. Chen Li, Linhui Fan, Feng Guo, Habibu Hussaini, Dr. Shaohong Zhu, Zhuang Wen, Dr. Ponggorn Kulsangcharoen, Dr. Seang Yeoh and all other friends I met in these four years.

Last but not least, I would like to express my heartfelt appreciation to my parents for their understanding and support throughout my life. Also, I would like to thank my wife Lidan Zhao and daughter Nuoning Wang. You are always my biggest motivation during the tough time.

### Abstract

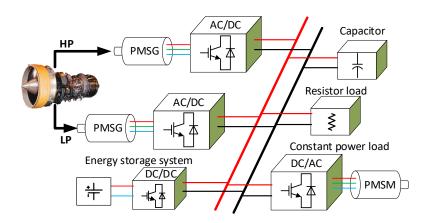

The application of more-electric aircraft concept will see a significant increase of electrical power demands with newly developed electrical loads. This will make it essential to extract electrical power from both high-pressure and lowpressure shafts of an aircraft engine for future aircraft. With each shaft driving one electrical generation subsystem, an advanced dual-channel power generation system can be formed. The dual-generation architecture can significantly reduce the fuel assumption of aircraft engines through power transfer between different engine shafts. In such a system, two permanent magnet synchronisation generators (PMSGs) will supply a common DC bus through their dedicated AC-DC converters.

On the load side, a significant penetration of power electronics is foreseen as they are essential elements to interface load and the DC bus. With an increased number of power electronic converters, harmonics from these converters will impose significant power quality challenges to the electric grid. A capacitor is required to filter the switching harmonics in the DC bus to ensure that its voltage is within the required range. However, due to a high current rating, this capacitor will be bulky and heavy.

This thesis aims to address the power quality issues for the common DC bus electrical power system architecture considering a dual-channel power generation system. To improve the power quality on the DC bus, switching harmonic component cancellation schemes are proposed for different cases. In the first case, two PMSGs are considered to supply the DC bus through AC/DC converters. In this case, the modulation scheme (either SPWM or SVPWM) of one AC-DC converter is controlled to actively cancel one specific harmonic component on the DC bus. After the first case study, the use of a bidirectional buck-boost DC-DC converter as a harmonic absorber with the proposed equal-gate-width (EGW) modulation scheme is considered. The proposed method allows for the active control of the magnitude and phase angle of some specific

harmonic component and thus can be used to suppress the required harmonic component on the DC bus. Simulation and experimental results have demonstrated the high robustness and effectiveness of the proposed methods.

# Contents

| Chapter 1  | Introduction1                                                  |

|------------|----------------------------------------------------------------|

| 1.1 N      | More Electric Aircraft1                                        |

| 1.2 E      | Electrical Power Generation Onboard Aircraft                   |

| 1.2.1      | Constant speed constant frequency4                             |

| 1.2.2      | Variable speed constant frequency4                             |

| 1.2.3      | Variable speed variable frequency5                             |

| 1.2.4      | DC Power Generation                                            |

| 1.2.5      | Dual-Channel Power Generation7                                 |

| 1.3 A      | Active Switching Harmonic Suppression of the DC-Link Capacitor |

| Current    | s10                                                            |

| 1.3.1      | Power quality improvement10                                    |

| 1.3.2      | Harmonics suppression using additional DC-DC converters11      |

| 1.3.3      | Harmonic suppression for single AC-DC converters12             |

| 1.3.4      | Harmonic suppression for multi-converter systems13             |

| 1.4 0      | Dbjectives of Thesis and Thesis Structure15                    |

| 1.4.1      | Objectives15                                                   |

| 1.4.2      | Thesis structure                                               |

| Chapter 2  | Fundamental Models and Operation of a Dual-channel Power       |

| Generation | n System19                                                     |

| 2.1 I      | ntroduction                                                    |

| 2.2 F      | Permanent Magnet Synchronised Generator (PMSG) System20        |

| 2.2.1      | PMSG modelling20                                               |

| 2.2.2      | Control of the PMSG system                                     |

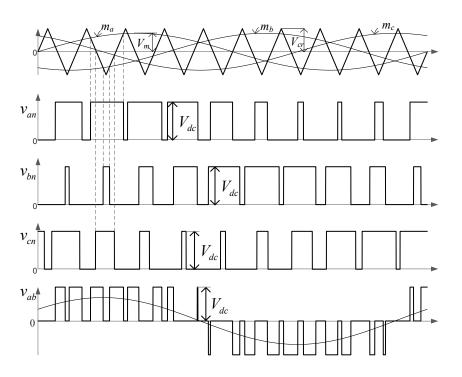

| 2.2.3      | PWM Methods for the Two-Level AC-DC Converter24                |

| 2.3 E      | Energy Storage System (ESS)                                    |

| 2.3.1      | Battery and the DC-DC converter                                |

| 2.3.     | 2 ESS Control                                                      |

|----------|--------------------------------------------------------------------|

| 2.4      | Power Sharing Control                                              |

| 2.4.     | 1 Centralised control                                              |

| 2.4.     | 2 Distributed control                                              |

| 2.4.     | 3 Decentralised control (droop control)                            |

| 2.5      | Load Model                                                         |

| 2.6      | DC Link Model for Capacitor Bank41                                 |

| 2.7      | Chapter Summary                                                    |

| Chapter  | 3 Harmonic Cancellation of Two AC/DC Converters Under              |

| Carrier- | Based PWM Operations                                               |

| 3.1      | Introduction                                                       |

| 3.2      | Second Carrier Harmonics Analysis of Single Converter44            |

| 3.2.     | 1 Mathematical Analysis on DC-Bus Second Carrier Harmonic          |

| 3.2.     | 2 Simplified Model on Second Carrier Harmonic                      |

| 3.2.     | 3 Comparison Between the Simplified and Original Model51           |

| 3.3      | Proposed Cancellation Method                                       |

| 3.3.     | 1 Method for 1:1 Power Sharing Ratio                               |

| 3.3.     | 2 Method for Unequal Power Sharing Ratios                          |

| 3.3.     | 3 First-Band Harmonic                                              |

| 3.4      | Simulation Results                                                 |

| 3.5      | Chapter Summary                                                    |

| Chapter  | 4 Harmonic Cancellation of Two AC/DC Converters Under Space        |

| Vector I | PWM Operations66                                                   |

| 4.1      | Introduction                                                       |

| 4.2      | Mathematical Model of DC-Bus Current Harmonics of Two-Level        |

| Conv     | erters under SVPWM Operation                                       |

| 4.3      | Mathematical Analysis of The First and Second carrier Harmonics 71 |

| 4.3.     | 1 Harmonic component of $f_c$                                      |

|          | 5                                                                  |

| 4.3.    | B.2 Harmonic component of $2f_c$                           | 76      |

|---------|------------------------------------------------------------|---------|

| 4.4     | Capacitor Harmonic Minimisation Method                     | 79      |

| 4.5     | Simulation Results                                         | 84      |

| 4.6     | Chapter Summary                                            | 88      |

| Chapter | r 5 Using DC-DC Converters as Harmonic Suppression Devic   | e90     |

| 5.1     | Introduction                                               | 90      |

| 5.2     | Harmonic Analysis of Two-Level AC-DC Converter in Th       | e First |

| Order   | er Side Band                                               | 91      |

| 5.2.    | 2.1 Harmonics on $f_c \pm 3f_0$                            | 92      |

| 5.2.    | 2.2 Component selection for suppression                    | 96      |

| 5.3     | Equal Gate Width (EGW) PWM of a Bi-Directional Buck        | -Boost  |

| Conv    | verter                                                     | 98      |

| 5.3.    | B.1 Conventional DC-DC converter control and PWM operation | 00      |

|         | -                                                          |         |

| 5.3.    | 1                                                          |         |

| 5.4     | Proposed Harmonics Cancellation Method                     | 104     |

| 5.5     | PWM Compensation Technique                                 | 109     |

| 5.5.    | 5.1 Impact of measured fundamental frequency Errors        | 109     |

| 5.5.    | 5.2 Applying compensation to avoid the accumulated error   | 111     |

| 5.6     | Simulation Studies                                         | 114     |

| 5.7     | Chapter Summary                                            | 118     |

| Chapter | r 6 Harmonic Cancellation of Both The First Sideband an    | nd The  |

| Second  | Harmonics within A Dual-Channel Power Generation System    | 119     |

| 6.1     | Introduction                                               | 119     |

| 6.2     | Proposed Harmonics Cancellation Scheme                     | 120     |

| 6.3     | Simulation Study                                           | 122     |

| 6.4     | Chapter Summary                                            | 126     |

| Chapter | r 7 Experimental Rig Setup and Validation                  | 128     |

| 7.1 Experimental Setup                                                |           |

|-----------------------------------------------------------------------|-----------|

| 7.1.1 Control Platform                                                | 130       |

| 7.1.2 Power Electronic Converters                                     | 131       |

| 7.1.3 Sensor Board                                                    |           |

| 7.1.4 Power Load                                                      | 134       |

| 7.2 Power Quality Improvement of Dual-Generator System un             | nder SPWM |

| Operation                                                             | 135       |

| 7.2.1 Single generator operation                                      |           |

| 7.2.2 Dual-generator operation                                        | 141       |

| 7.3 Power Quality Improvement of Dual-Generator Sys                   | tem under |

| SVPWM Operation                                                       | 145       |

| 7.3.1 Single generator operation                                      | 145       |

| 7.3.2 Dual-generator operation                                        | 149       |

| 7.4 Power Quality Improvement of Dual-Generator System                | m with an |

| Energy Storage System Involved                                        | 152       |

| 7.4.1 One AC-DC converter and one DC-DC converter                     |           |

| 7.4.2 Two AC-DC converters and one DC-DC converter                    |           |

| 7.5 Chapter Summary                                                   | 161       |

| Chapter 8 Conclusion and Future Work                                  | 162       |

| 8.1 Conclusion and Discussion                                         | 162       |

| 8.2 Future Work                                                       | 164       |

| 8.3 Publications                                                      | 166       |

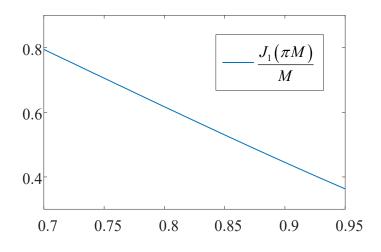

| Appendix A Mathematical Proof of The Decreasing Trend of $I_{dc,1,0}$ | 167       |

| References                                                            | 170       |

|                                                                       |           |

# **List of Figures**

| Figure 1.1: Change in non-propulsive power in conventional aircraft and more                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| electric aircraft. a) Conventional aircraft. b) More electric aircraft2                                                                               |

| Table 1-1: AC electric power system in recent civil and military aircraft[31]3                                                                        |

| Figure 1.2: Constant speed constant frequency generation system4                                                                                      |

| Figure 1.3: Variable speed constant frequency generation system5                                                                                      |

| Figure 1.4: Variable speed variable frequency generation system                                                                                       |

| Figure 1.5: DC-voltage generation system                                                                                                              |

| Figure 1.6: "Single bus" EPS structure7                                                                                                               |

| Figure 1.7: Schematic of a twin-spool, high-bypass turbofan engine                                                                                    |

| Figure 1.8: Concept diagram of the dual-channel power generation system [18].                                                                         |

|                                                                                                                                                       |

| Figure 1.9: Harmonic suppression using additional switches [49]11                                                                                     |

| Figure 1.10: DC-DC converter connecting with a three-phase inverter [64]12                                                                            |

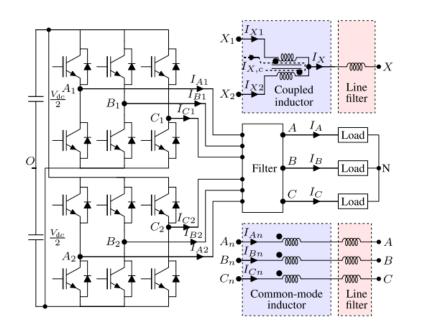

| Figure 1.11: Multi-converter system with the same fundamental frequency. a) parallel interleaved converters[67]. b) Triple three-phase machine [76]14 |

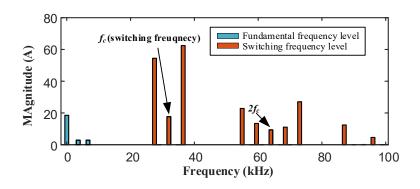

| Figure 1.12: Spectrum of DC-side current15                                                                                                            |

| Figure 2.1: Typical dual-generation power system20                                                                                                    |

| Figure 2.2: Diagram of PMSG system                                                                                                                    |

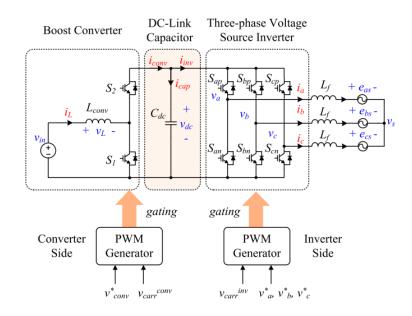

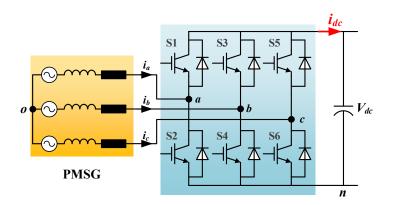

| Figure 2.3: PMSG and two-level AC-DC converter25                                                                                                      |

| Figure 2.4: Sinusoidal pulse-width modulation (SPWM)26                                                                                                |

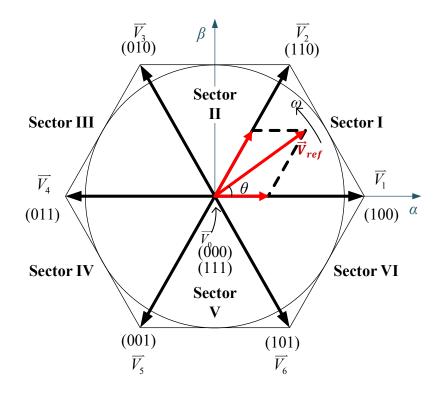

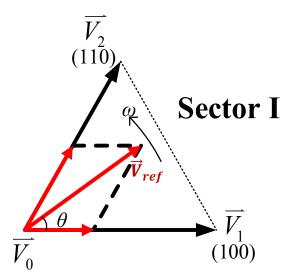

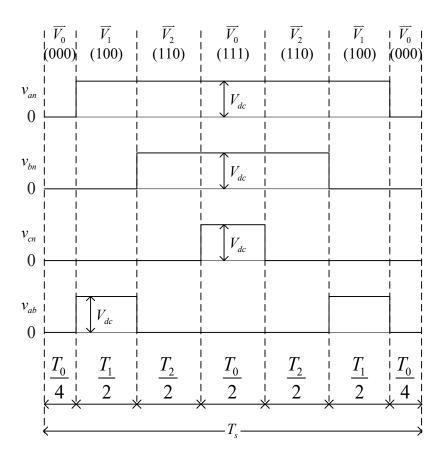

| Figure 2.5: Space vector diagram for the two-level converter27                                                                                        |

| Table 2-1: Space Vectors, Switching States, and On-State Switches                                                                                     |

| Figure 2.6: Vector synthesisation in Sector I                                                                                                         |

| Figure 2.7: Seven-segment switching sequence in Sector I                           |

|------------------------------------------------------------------------------------|

| Table 2-2: Switching sequence of SVPWM    31                                       |

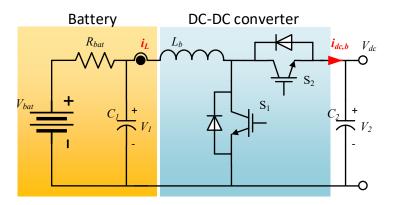

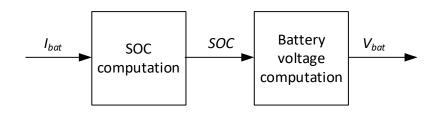

| Figure 2.8: Energy storage system                                                  |

| Figure 2.9: Battery model overview                                                 |

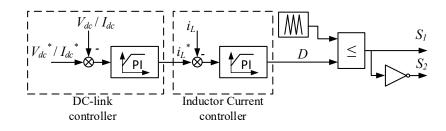

| Figure 2.10: Controller of the DC-DC converter                                     |

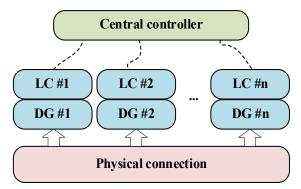

| Figure 2.11: Operation principle of centralised control                            |

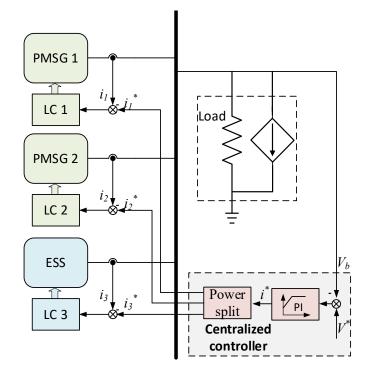

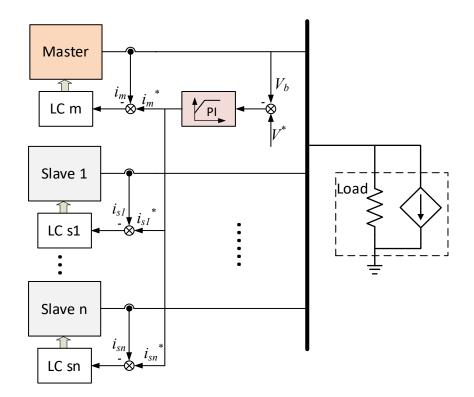

| Figure 2.12: Control scheme of centralised control35                               |

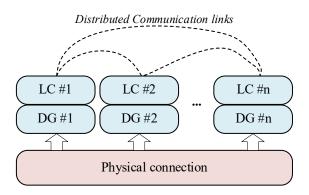

| Figure 2.13: Control scheme of master-slave control                                |

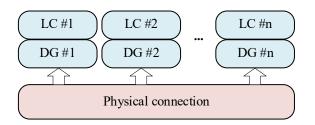

| Figure 2.14: Operation principle of distributed control                            |

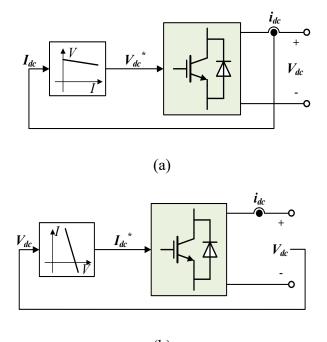

| Figure 2.15: Operation principle of decentralised control                          |

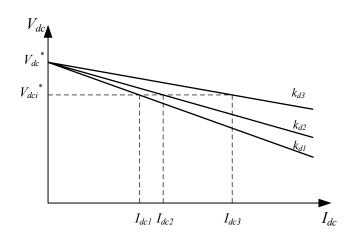

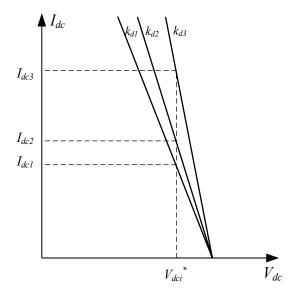

| Figure 2.16: Droop characteristic. a) V-I droop. b) I-V droop                      |

| Figure 2.17: Power sharing characters of V-I droop control curve                   |

| Figure 2.18: Power sharing characters of I-V droop control curve40                 |

| Figure 2.19: Load model41                                                          |

| Figure 3.1: Dual-channel enhanced power generation system44                        |

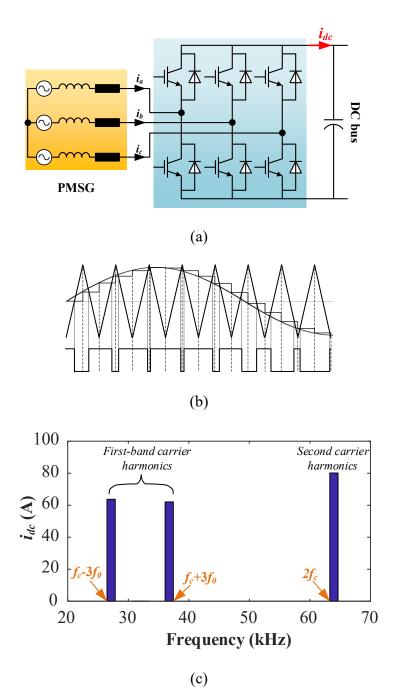

| Figure 3.2: Two-level three-phase converter. a) PMSG and two-level converter,      |

| b) asymmetric regular sampling PWM, c) spectrum of $i_{dc}$ ( $f_c$ : switching    |

| frequency, $f_0$ : fundamental frequency)45                                        |

| Table 3-1: Simulation Parameters                                                   |

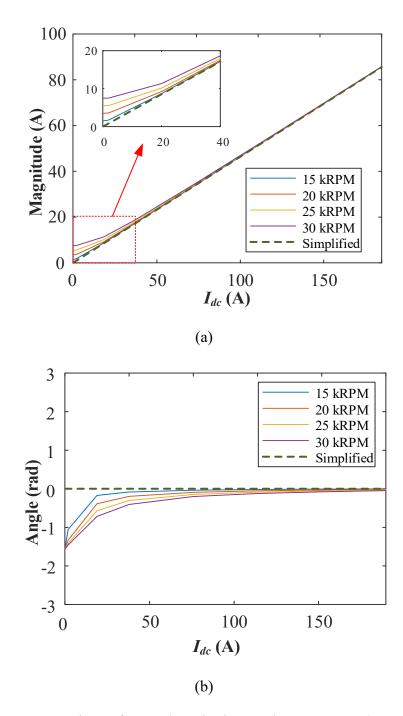

| Figure 3.3: Comparison of second carrier harmonic component $(I_{dc,2,0}(t))$ from |

| original and simplified models with increased generator power and speed. a)        |

| Magnitude. b) Phase angle                                                          |

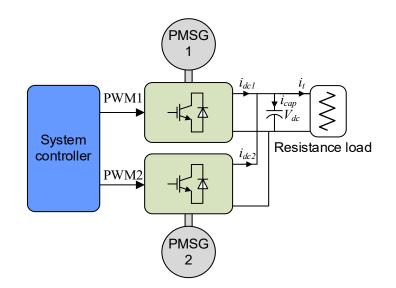

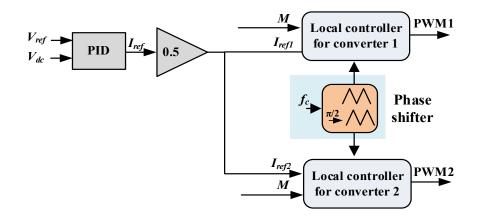

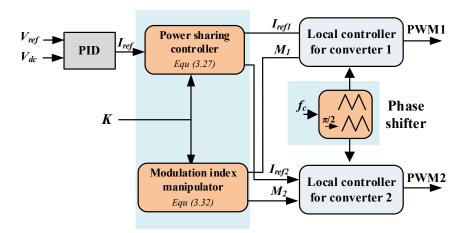

| Figure 3.4: System diagram                                                         |

| Figure 3.5: System controller when the power sharing ratio between the PMSG1       |

| and the PMSG2 is 1:155                                                             |

| Figure 3.6: System controller when the power sharing ratio between the PMSG1                                                                                                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| and the PMSG2 is unequal56                                                                                                                                                                        |

| Figure 3.7: Term $J_l(\pi M)/M$ versus $M$                                                                                                                                                        |

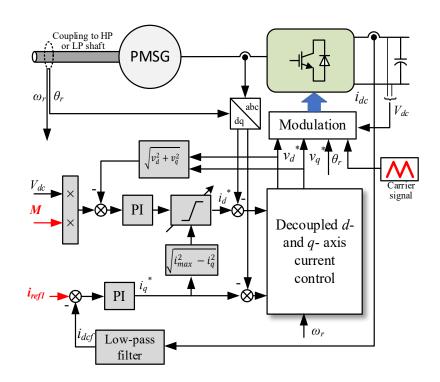

| Figure 3.8: Local controller                                                                                                                                                                      |

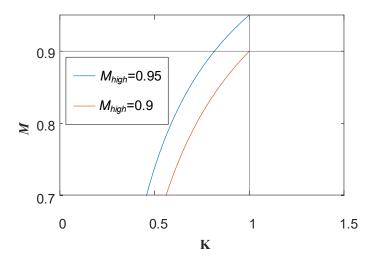

| Figure 3.9: <i>M-K</i> diagram                                                                                                                                                                    |

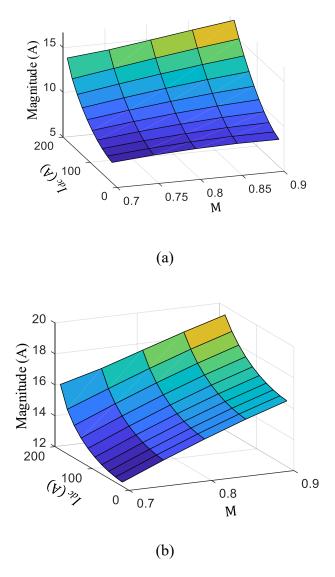

| Figure 3.10: Magnitudes of first band harmonics related to the modulation and dc-link current. a) $f_c$ -3 $f_0$ , b) $f_c$ +3 $f_0$ 61                                                           |

| Figure 3.11: Simulation result of the proposed cancellation method                                                                                                                                |

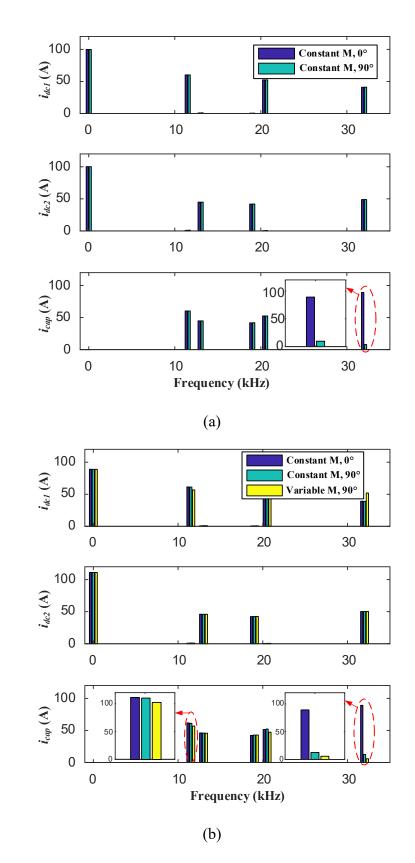

| Figure 3.12: Current spectrums when power sharing ratio changes from 1:1 to 0.8:1. a) Current spectrum when K=1:1. b) Current spectrum when K=0.8:1.64                                            |

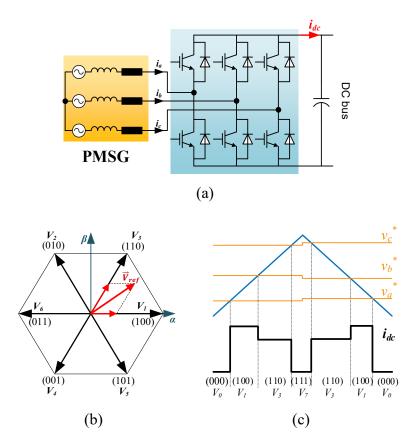

| Figure 4.1: Two-level three-phase converter and SVPWM operation. a)<br>Topology, b) Switching vectors and voltage reference, c) Modulation<br>waveform                                            |

| Figure 4.2: <i>i</i> <sub><i>dc</i></sub> spectrum                                                                                                                                                |

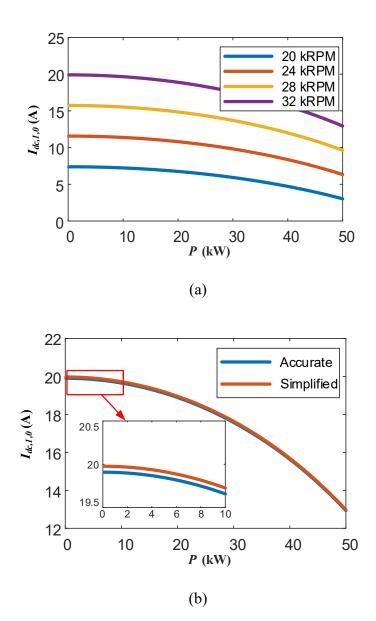

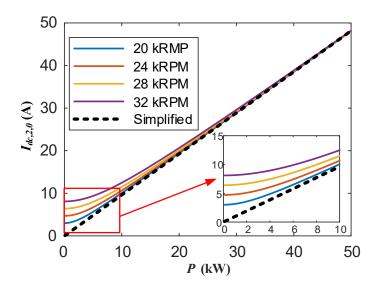

| Figure 4.3: Magnitude of first switching harmonic. a) Magnitudes under different rotor speeds, b) Comparison between simplified model (4.22) and accurate model (4.10) when rotor speed is 32kRPM |

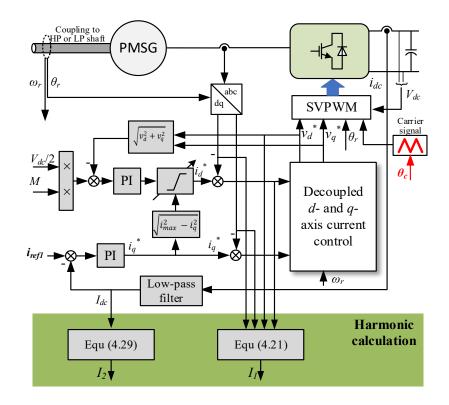

| Figure 4.4: Control diagram and harmonic calculation scheme of single PMSG system                                                                                                                 |

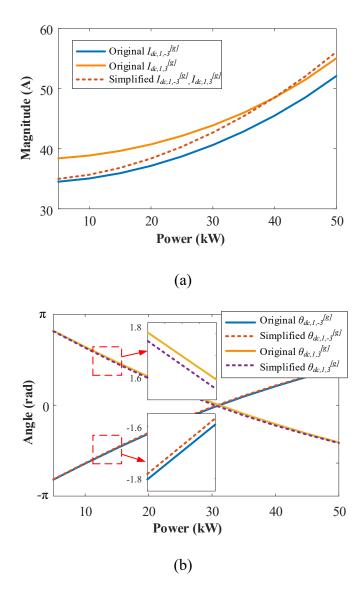

| Figure 4.5: Comparison of second carrier harmonic component from accurate (4.24) and simplified (4.29) models with increased generator power and speed.                                           |

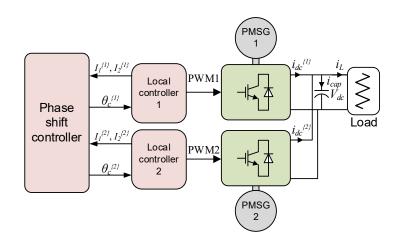

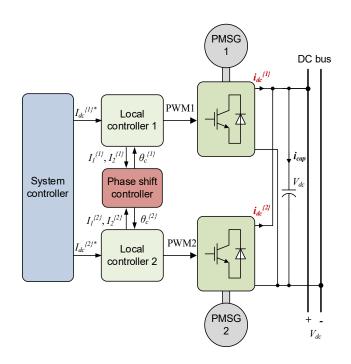

| Figure 4.6: Control diagram of a dual-generator power system80                                                                                                                                    |

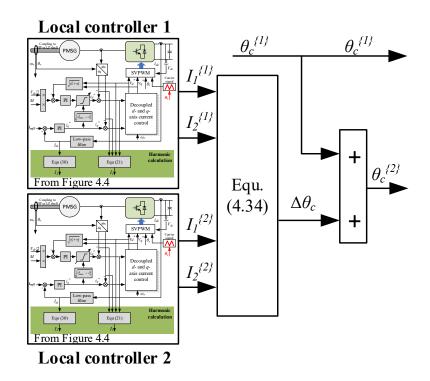

| Figure 4.7: Phase-shift controller                                                                                                                                                                |

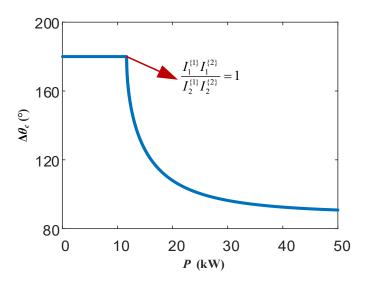

| Figure 4.8: Optimised $\Delta \theta_c$ when power sharing ratio between two converters is 1:1                                                                                                    |

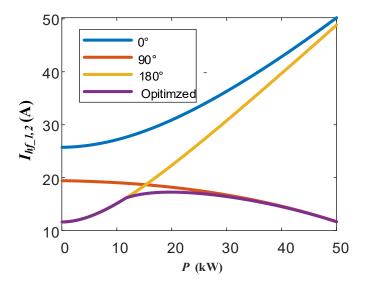

| Figure 4.9: $I_{hf_{-}l,2}$ versus output power of single converter                                                                                                                               |

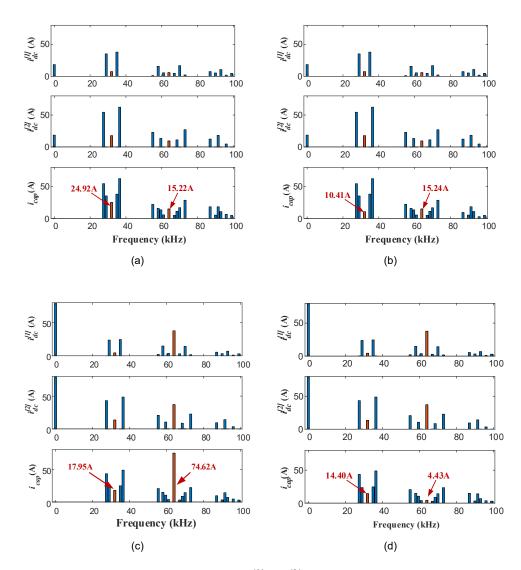

| Figure 4.11: Current spectrums of $i_{dc}^{\{1\}}$ , $i_{dc}^{\{2\}}$ , and $i_{cap}$ . a) 5kW, no phase shift,                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| b) 5kW, optimised phase shift, c) 40kW, no phase shift, d) 40kW, optimised                                                                                   |

| phase shift                                                                                                                                                  |

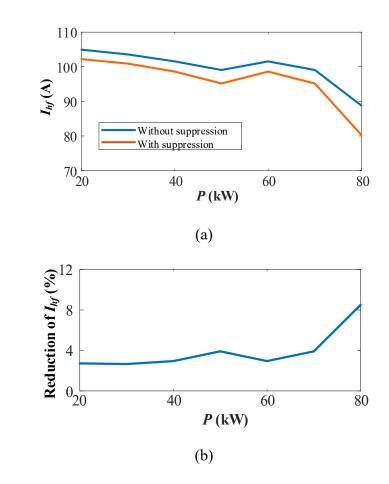

| Figure 4.12: <i>I</i> <sub>hf</sub> variation after applying the proposed method                                                                             |

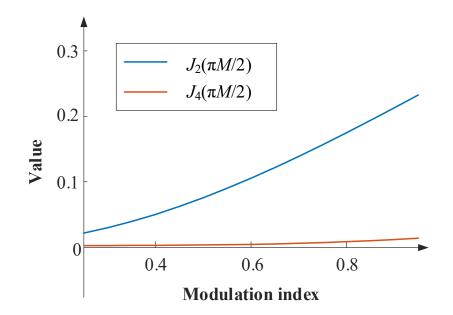

| Figure 5.1: Comparison between $J_2(\pi M/2)$ and $J_4(\pi M/2)$ with increased modulation index                                                             |

| Figure 5.2: Comparison between magnitudes of the simplified and original model on $f_c$ -3 $f_0$ and $f_c$ +3 $f_0$ . a) Magnitudes. b) Angles95             |

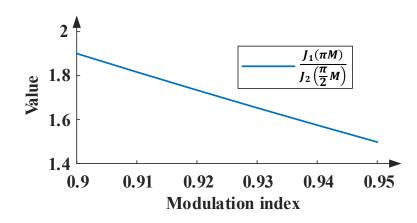

| Figure 5.3: $J_2(\pi M)/J_2(\pi M/2)$ with modulation index increases                                                                                        |

| Figure 5.4: Bidirectional buck-boost converter                                                                                                               |

| Figure 5.5: Conventional PWM strategy                                                                                                                        |

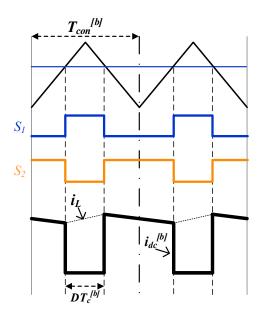

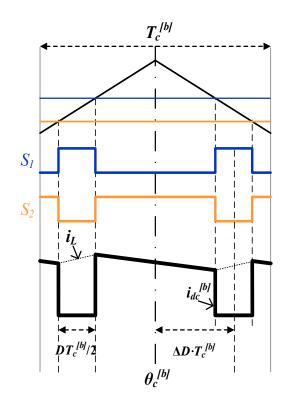

| Figure 5.6: Equal-Gate-Width (EGW) PWM101                                                                                                                    |

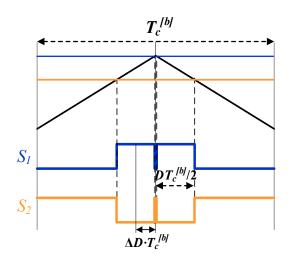

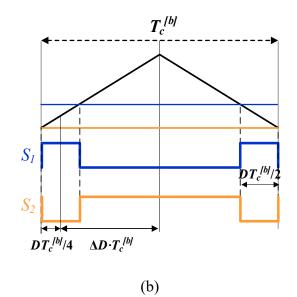

| Figure 5.7: EGW operation when the two gate signal pulses of S <sub>1</sub> are going to overlap each other. a) $\Delta D = D/4$ . b) $\Delta D = 1/2 - D/4$ |

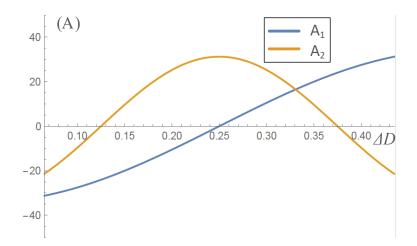

| Figure 5.8: Magnitudes of the first and second carrier harmonic with $\Delta D$ changing $(f_c^{[b]} \text{ and } 2f_c^{[b]})$                               |

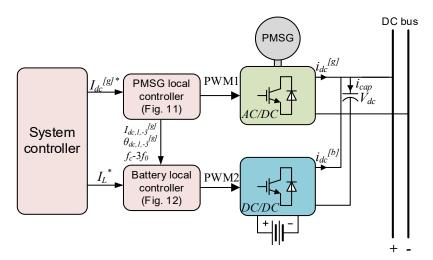

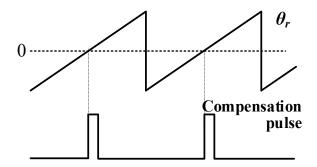

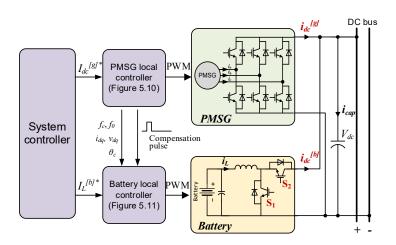

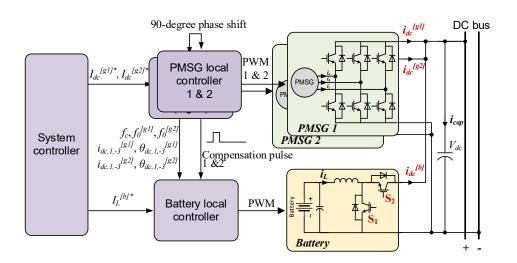

| Figure 5.9: Control architecture of the hybrid generation system105                                                                                          |

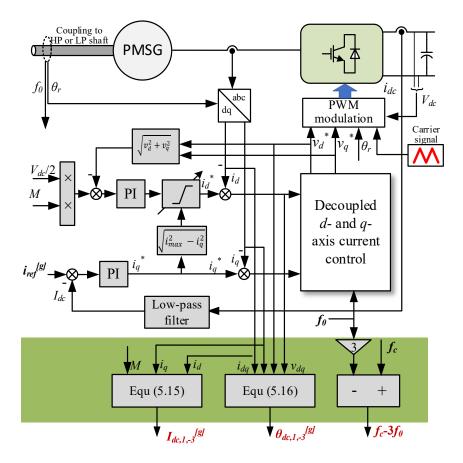

| Figure 5.10: Control diagram of the PMSG system106                                                                                                           |

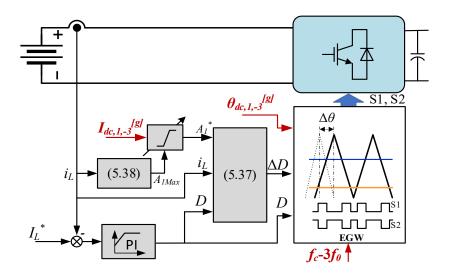

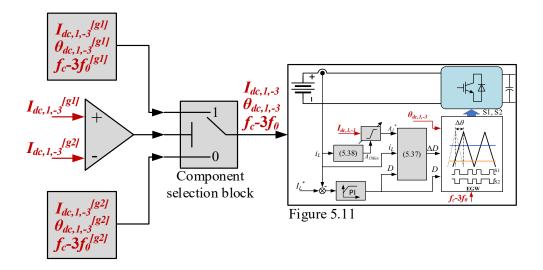

| Figure 5.11: Control diagram of battery system                                                                                                               |

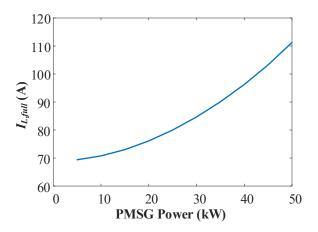

| Figure 5.12: <i>I<sub>L,full</sub></i> when the output power of PMSG varies                                                                                  |

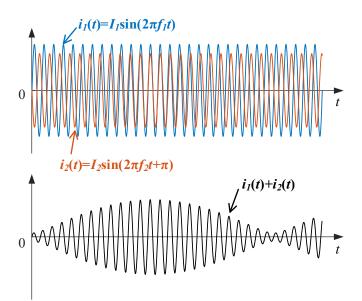

| Figure 5.13: Sum up of two un-synchronised components110                                                                                                     |

| Figure 5.14: Compensation actions on accumulated errors111                                                                                                   |

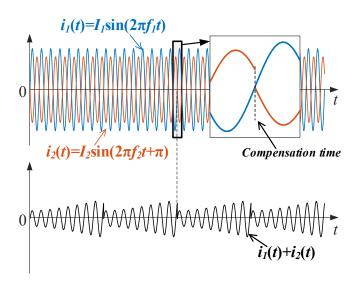

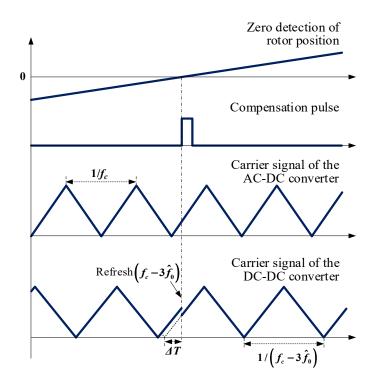

| Figure 5.15: Compensation pulse generation112                                                                                                                |

| Figure 5.16: Control architecture of the hybrid generation system considering                                                                                |

| PWM compensation113                                                                                                                                          |

| Figure 5.17: Compensation actions on carrier signals from PMSG and battery.                                                |

|----------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                            |

| Table 5-1: Simulation parameters for AC-DC and DC-DC converters115                                                         |

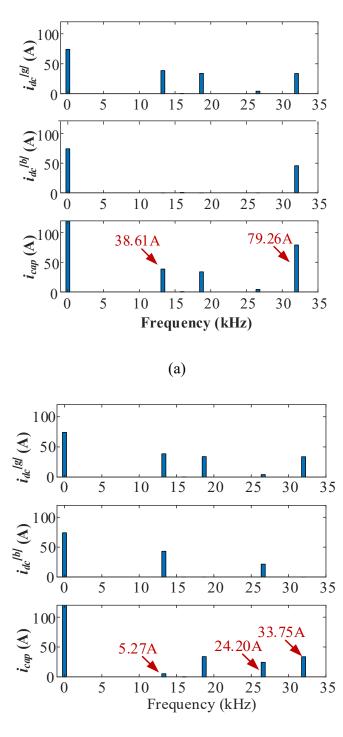

| Figure 5.18: Current spectrums of $i_{dc}{}^{[g]}$ , $i_{dc}{}^{[b]}$ , and $i_{cap}$ . When $P^{[g]}=P^{[b]}=20$ kW.      |

| a) No optimisation, b) With the EGW PWM operation116                                                                       |

| Figure 5.19: Simulation results of EGW PWM operation117                                                                    |

| Figure 6.1: Typical dual-generation power system120                                                                        |

| Figure 6.2: Control diagram of the dual-generator system together with a battery                                           |

| system                                                                                                                     |

| Figure 6.3: Modified local controller of the DC-DC converter121                                                            |

| Table 6-1: Simulation parameters for AC-DC and DC-DC converters123                                                         |

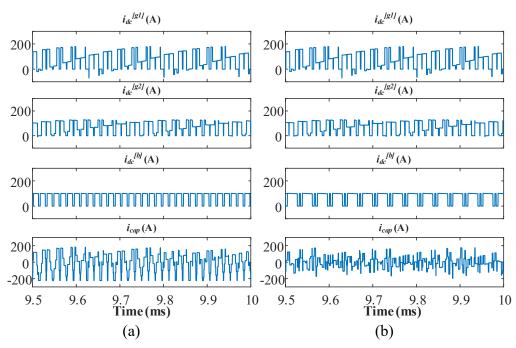

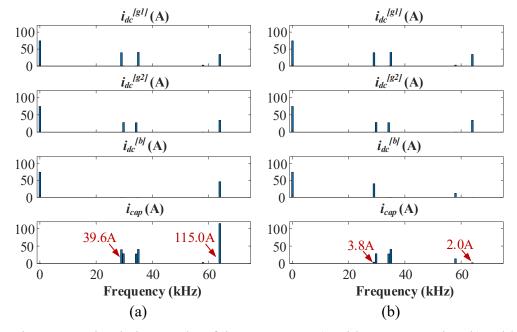

| Figure 6.4: Simulation results of $i_{dc}^{[g1]}$ , $i_{dc}^{[g2]}$ , $i_{dc}^{[b]}$ , $i_{cap}$ . a) Without suppression. |

| b) With suppression                                                                                                        |

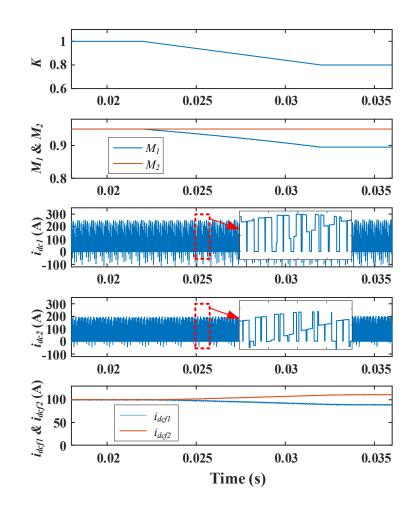

| Figure 6.5: Simulation results of the spectrums. a) Without suppression. b) With suppression                               |

|                                                                                                                            |

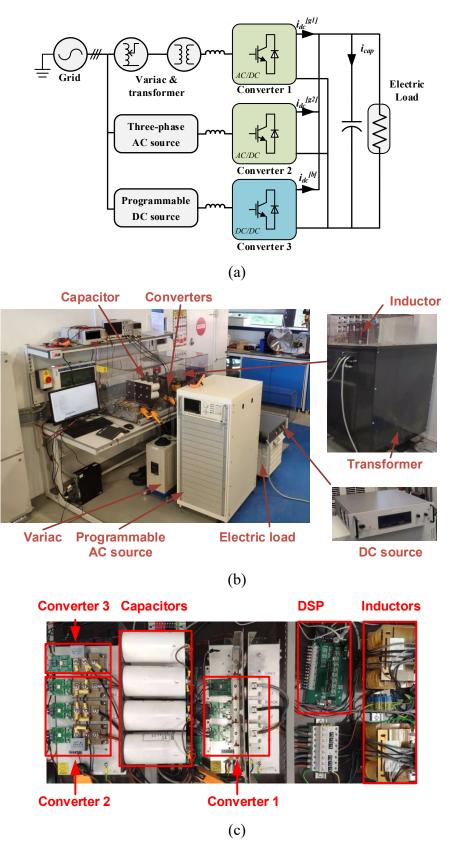

| Figure 7.1: Experiment setup. a) Experiment diagram. b) Test rig. c) Converters and the controller                         |

|                                                                                                                            |

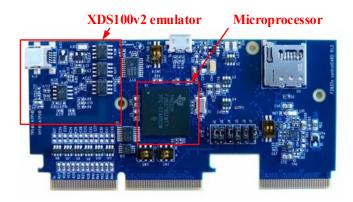

| Figure 7.2: Texas Instruments F28379D controlCARD130                                                                       |

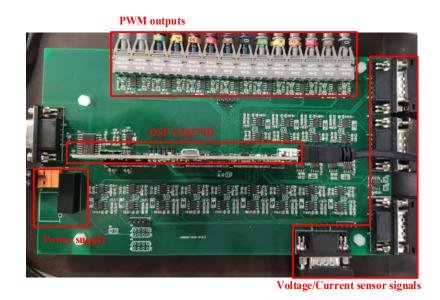

| Figure 7.3: DSP Interface board                                                                                            |

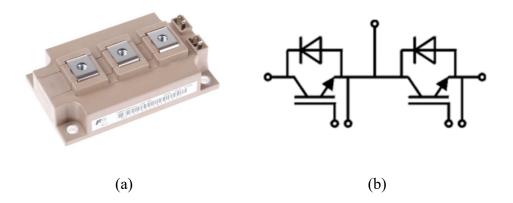

| Figure 7.4: IGBT module (2MBI200VH-120-50). a) Prototype. b) Schematic.                                                    |

|                                                                                                                            |

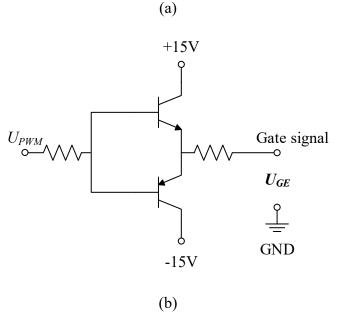

| Figure 7.5: Driver board. a) PCB board. b) Push-pull circuit132                                                            |

| Figure 7.6: Voltage sensor board133                                                                                        |

| Figure 7.7: Current sensor board                                                                                           |

| Figure 7.8: Programmable DC electronic load (EL600VDC19800W)134                                                            |

| Table 7-1: Experiment parameters for single generator under SPWM operation. |

|-----------------------------------------------------------------------------|

|                                                                             |

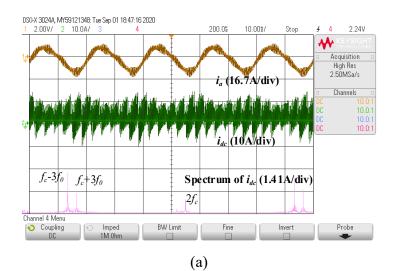

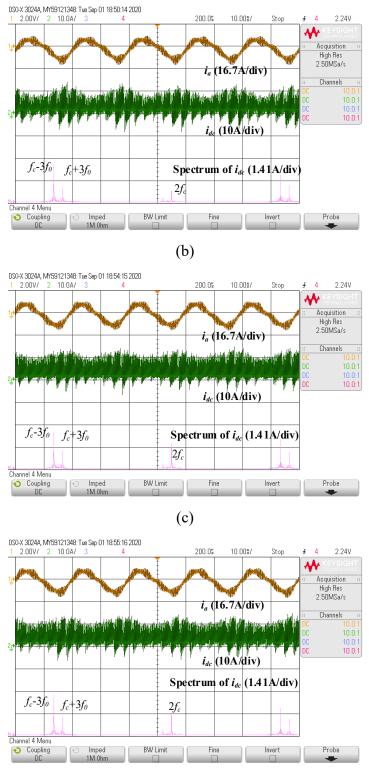

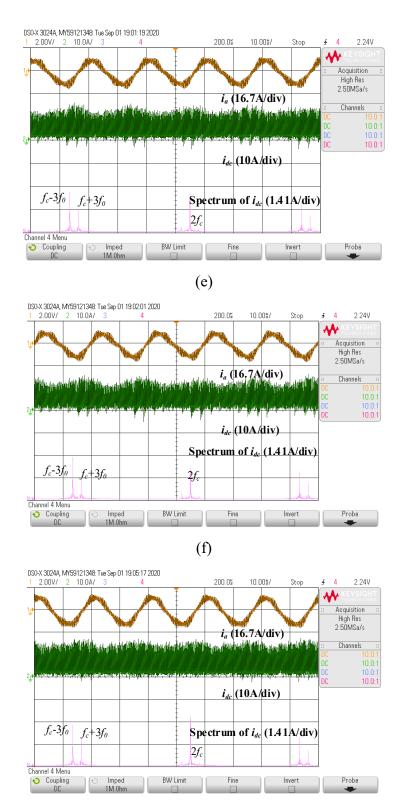

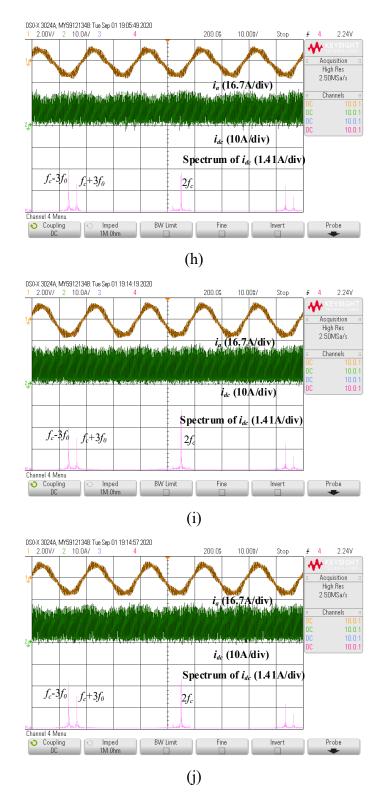

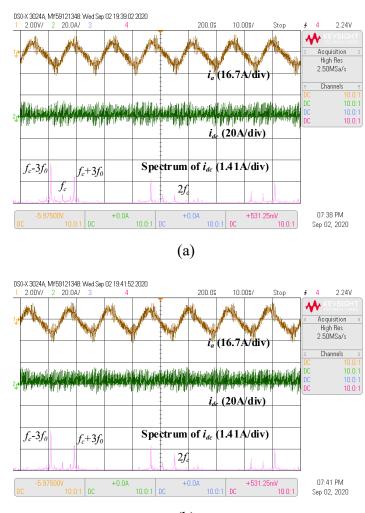

| Figure 7.9: Phase current, DC bus current and its spectrum under different power ( <i>P</i> ) and modulation index ( <i>M</i> ). a) <i>P</i> =400W, M=0.9. b) <i>P</i> =400W, M=0.95. c) <i>P</i> =800W, M=0.9. d) <i>P</i> =800W, M=0.95. e) <i>P</i> =1200W, M=0.9. f) <i>P</i> =1200W, M=0.95. g) <i>P</i> =1600W, M=0.9. h) <i>P</i> =1600W, M=0.95. i) <i>P</i> =2000W, M=0.95 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 7-2: Experiment results of second order harmonics under SPWM      operation.                                                                                                                                                                                                                                                                                                  |

| Figure 7.11: Experiment diagram of the dual-generator system under SPWM operation                                                                                                                                                                                                                                                                                                   |

| Table 7-3: Experiment parameters for dual-generator under SPWM operation.                                                                                                                                                                                                                                                                                                           |

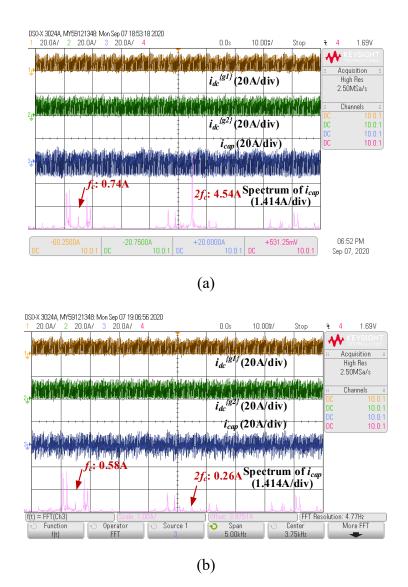

| Figure 7.12: DC-bus and capacitor current when power sharing ratio is 1:1. a)<br>Without phase shift. b) With 90-degree phase shift143                                                                                                                                                                                                                                              |

| Figure 7.13: DC-bus and capacitor currents when power sharing ratio is 0.8:1.<br>a) No phase shift and no optimised modulation index. b) With 90-degree phase<br>shift without optimised modulation index. c) 90-degree phase shift together with<br>optimised modulation index. 144                                                                                                |

| Table 7-4: Experiment parameters for single generator under SPWM operation.                                                                                                                                                                                                                                                                                                         |

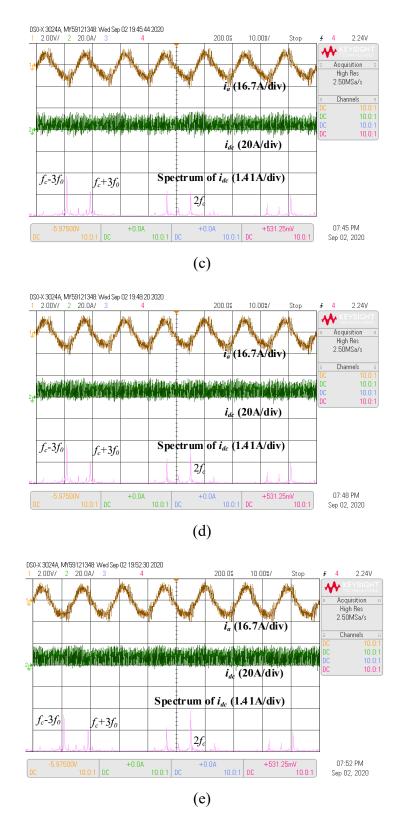

| Figure 7.14: Phase current, DC bus current and its spectrum under different power (P) and fixed modulation index ( $M$ =1.04). a) P=400W. b) P=800W. c) P=1200W. d) P=1600W. e) P=2000W148                                                                                                                                                                                          |

| Table 7-5: Experiment results of harmonic magnitudes under SVPWM      operation      149                                                                                                                                                                                                                                                                                            |

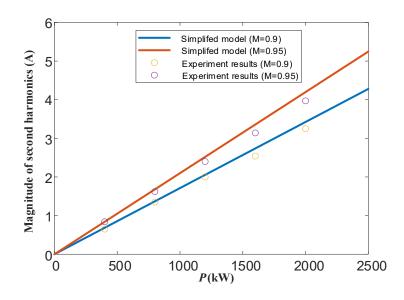

| Figure 7.15: Comparison between simplified model and experiment                                                                                                                                                                                                                                                                                                                     |

| Table 7-6: Experiment parameters for single generator under SPWM operation.                                                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 7.16: DC-bus and capacitor current when output power is 400W. a) Without phase shift. b) With an optimised phase shift angle (180°)  |

| Figure 7.17: DC-bus and capacitor current when output power is 4kW. a) Without phase shift. b) With optimised phase shift angle (93°)152    |

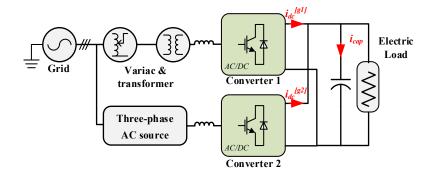

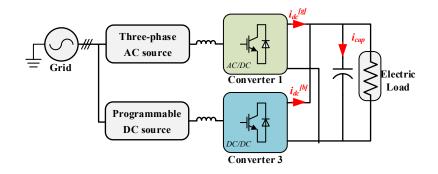

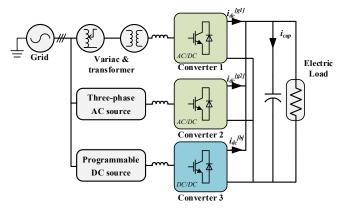

| Figure 7.18: Experimental diagram when only one AC-DC converter and one DC-DC converter are involved in the system                          |

| Table 7-7: Experiment parameters for AC-DC and DC-DC converters154                                                                          |

| 18154                                                                                                                                       |

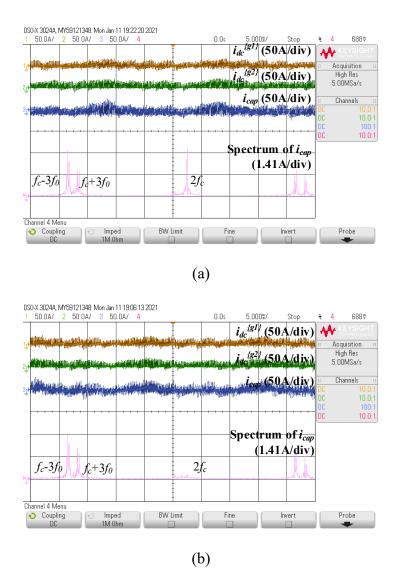

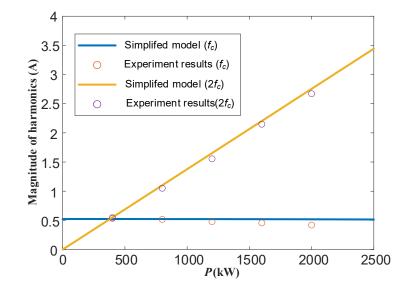

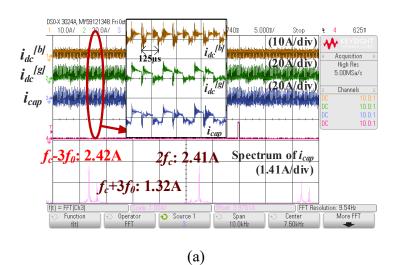

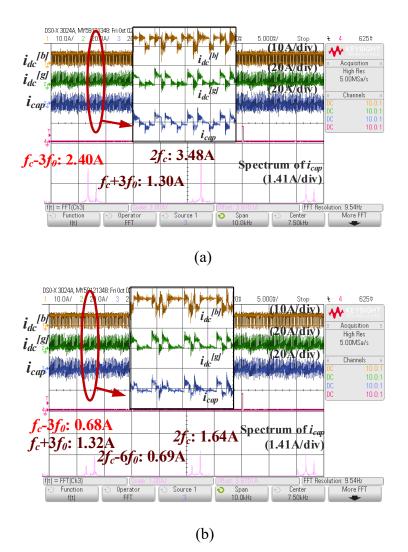

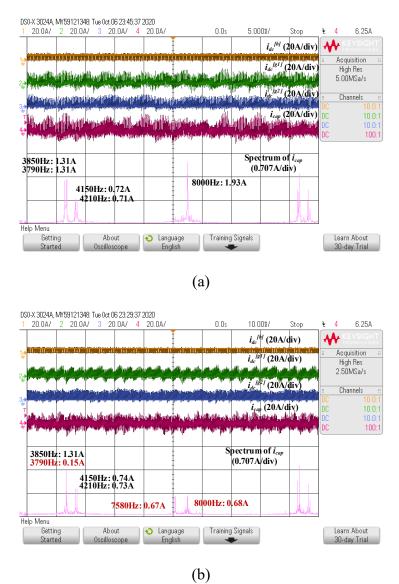

| Figure 7.19: Harmonic suppression when $P^{[g]}=1$ kW, $P^{[b]}=0.5$ kW. a) Without suppression. b) With EGW suppression                    |

| Figure 7.20: Harmonic suppression with EGW suppression when $P^{[g]}=1$ kW, $P^{[b]}=1$ kW. a) Without suppression. b) With EGW suppression |

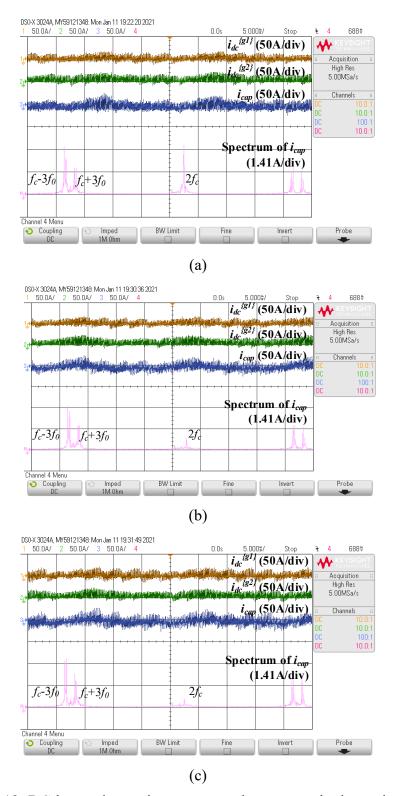

| Figure 7.21: Harmonic suppression with EGW suppression when $P^{[g]}=1$ kW, $P^{[b]}=1$ kW, $V_{bat}=180$ V                                 |

| Figure 7.22: Harmonic suppression on $f_c+3f_0$ with EGW suppression when $P^{[g]}=1$ kW, $P^{[b]}=1$ kW                                    |

| Figure 7.23: Experiment diagram                                                                                                             |

| Table 7-8: Experiment parameters for AC-DC and DC-DC converters159                                                                          |

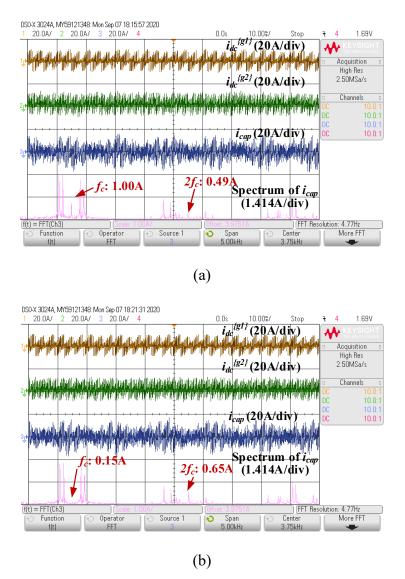

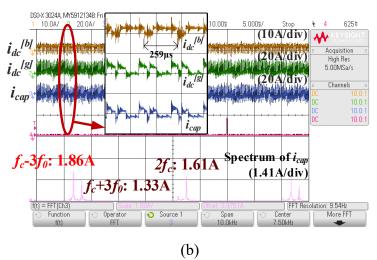

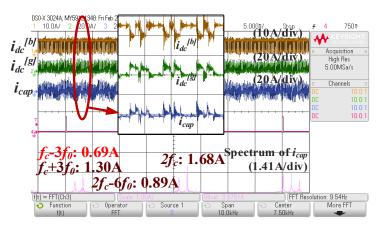

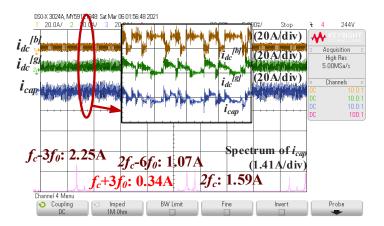

| Figure 7.24: Experimental results when $P^{[b]}=1$ kW, $P^{[g_1]}=1$ kW, $P^{[g_2]}=1$ kW. a) Without optimisation. b) With optimisation    |

|                                                                                                                                             |

# List of Terms

| $A_k$                  | Fourier coefficients of $i_{dc}^{[b]}$                      |  |

|------------------------|-------------------------------------------------------------|--|

| $C_b$                  | DC-link capacitance                                         |  |

| D                      | Duty cycle                                                  |  |

| $\Delta D$             | Bias duty cycle in EGW PWM                                  |  |

| $f_0$                  | Fundamental frequency from PMSG                             |  |

| $\hat{f}_0$            | Measured fundamental frequency from PMSG                    |  |

| $f_c$                  | Switching frequency                                         |  |

| $f_c^{[b]}$            | Carrier frequency of the DC-DC converter                    |  |

| f <sub>kf</sub>        | Frequency of <i>kf</i> th order harmonic                    |  |

| i, j                   | Switching and band side orders of DC-side current harmonics |  |

| <i>i</i> <sub>d</sub>  | <i>d</i> -axis current                                      |  |

| $i_q$                  | q-axis current                                              |  |

| $i_c^{max}$            | Maximal phase current                                       |  |

| <i>i</i> <sub>dc</sub> | DC-side current                                             |  |

| $i_{dc,i,j}(t)$        | DC-side current in the frequency of $if_c + jf_0$           |  |

| $i_{dc}^{[b]}$         | DC-side current from the ESS system                         |  |

| $i_{dc}^{[g]}$         | DC-side current from the PMSG system                        |  |

| <i>i</i> <sub>o</sub>  | Output current for loads                                    |  |

| $I_{l}^{\{l\}}$        | Magnitude of the first DC-side switching harmonic from      |  |

| 11                     | Converter 1                                                 |  |

| $I_{l}^{\{2\}}$        | Magnitude of the first DC-side switching harmonic from      |  |

|                        | Converter 2                                                 |  |

| $I_2^{\{1\}}$          | Magnitude of the second DC-side switching harmonic from     |  |

|                        | Converter 1                                                 |  |

| $I_2^{\{2\}}$          | Magnitude of the second DC-side switching harmonic from     |  |

|                        | Converter 2                                                 |  |

| Iac                    | Amplitude of the fundamental component of AC current        |  |

| $I_{dc}$                                 | DC component of the current $i_{dc}$ on DC-bus             |  |  |

|------------------------------------------|------------------------------------------------------------|--|--|

| I                                        | Magnitude of DC-side current harmonics in the frequency of |  |  |

| I <sub>dc,i,j</sub>                      | $if_c + jf_0$                                              |  |  |

| $I_{dc,i,j}^{[g]}$                       | Magnitude of DC-side current harmonics in the frequency of |  |  |

| $I_{dc,i,j}$                             | $if_c + jf_0$                                              |  |  |

| Idc,i,j <sup>[g1]</sup>                  | Magnitude of DC-side current harmonics from PMSG 1 in the  |  |  |

| <b>1</b> <i>ac</i> , <i>l</i> , <i>j</i> | frequency of $if_c + jf_0$                                 |  |  |

| $I_{dc,i,j}^{[g2]}$                      | Magnitude of DC-side current harmonics from PMSG 2 in the  |  |  |

| <b>1</b> <i>ac</i> , <i>l</i> , <i>j</i> | frequency of $if_c + jf_0$                                 |  |  |

| Idci                                     | Output current of the converter $#i$                       |  |  |

| Ihf                                      | Total harmonics on DC capacitor                            |  |  |

| I <sub>kf</sub>                          | Magnitudes of summed kfth order harmonic from all          |  |  |

| 1 KJ                                     | converters connected to the common dc bus                  |  |  |

| $I_L$                                    | DC component of the inductor current                       |  |  |

| k                                        | k=0, 1 and 2 represent phase A, B and C respectively       |  |  |

| <i>k</i> <sub>di</sub>                   | Droop coefficients of the converter $\#i$                  |  |  |

| kic                                      | Integral gain of the current regulator                     |  |  |

| $k_{pc}$                                 | Proportional gain of the current regulator                 |  |  |

| Κ                                        | Power sharing ratio between the two AC-DC converter        |  |  |

| $K_{m,n}$                                | Harmonic amplitude of switching function                   |  |  |

| $L_d$                                    | <i>d</i> -axis inductance                                  |  |  |

| $L_q$                                    | <i>q</i> -axis inductance                                  |  |  |

| $M_{high}$                               | Maximum modulation index                                   |  |  |

| Р                                        | Converter power                                            |  |  |

| $P_{cpl}$                                | Total power of the CPL                                     |  |  |

| Pres                                     | Total power of the resistive load                          |  |  |

| R                                        | Stator resistance                                          |  |  |

| R <sub>bat</sub>                         | Output resistance of battery                               |  |  |

| $R_i$                                    | Cable resistance of converter # <i>i</i>                   |  |  |

| Rres                                     | Resistance of the resistive load                           |  |  |

| sf(t)                                    | Switching function of the AC-DC converter                  |  |  |

| $T_{0}$                                 | Dwell time for vector $\overrightarrow{V_0}$              |  |  |

|-----------------------------------------|-----------------------------------------------------------|--|--|

| $T_{I}$                                 | Dwell time for vector $\overrightarrow{V_1}$              |  |  |

| $T_2$                                   | Dwell time for vector $\overrightarrow{V_2}$              |  |  |

| $T_c^{[b]}$                             | Carrier cycle time of EGW PWM                             |  |  |

| $T_{con}^{[b]}$                         | Carrier cycle time of conventional PWM                    |  |  |

| $\Delta T$                              | Phase-shift time                                          |  |  |

| $T_s$                                   | Switching cycle                                           |  |  |

| Vab                                     | Line-to-line voltage                                      |  |  |

| Vac                                     | Magnitude of converter phase voltage                      |  |  |

| $V_b$                                   | Voltage of common DC bus                                  |  |  |

| Vbat                                    | Open-circuit voltage of the battery                       |  |  |

| $v_c^{max}$                             | Maximal phase voltage amplitude at the fundamental        |  |  |

| Vc                                      | frequency                                                 |  |  |

| Vcr                                     | Peak values of carrier waves                              |  |  |

| $v_d$                                   | d-axis stator voltage                                     |  |  |

| $v_q$                                   | q-axis stator voltage                                     |  |  |

| $V_{dci}^{*}$                           | Calculated voltage reference for converter #i             |  |  |

| $V_o$                                   | Rated voltage                                             |  |  |

| $\overrightarrow{V_{ref}}$              | Reference vector                                          |  |  |

| α                                       | Power factor angle                                        |  |  |

| β                                       | Angle between phase current and its AC side voltage       |  |  |

| ζ                                       | Damping ratio                                             |  |  |

| $	heta_c$                               | Angle of the carrier signal                               |  |  |

| $\Delta 	heta_c$                        | Phase-shift angle between the two AC-DC converters        |  |  |

| $	heta_c^{[b]}$                         | Carrier angle of EGW PWM                                  |  |  |

| $	heta_c^{[k]}$                         | Phase angle of the triangular carrier signal for each leg |  |  |

| $	heta_c^{\{l\}}$                       | Phase angle of carrier signals on converter {1}           |  |  |

| $	heta_c^{\{2\}}$                       | Phase angle of carrier signal on converter {2}            |  |  |

| $\sigma_{m,n}^{[k]}, arphi_{m,n}^{[k]}$ | Phase angles of components in switching function (3.2)    |  |  |

| $\varphi_m$                             | Flux linkage of the permanent magnet                      |  |  |

|                                         |                                                           |  |  |

$\omega_e$ Electrical rotor angular velocity $\omega_n$ Natural bandwidth

# **Chapter 1**

# Introduction

#### **1.1 More Electric Aircraft**

In recent years, aircraft have been widely accepted as a convenient way to travel, as they allow long-distance, high-speed and in some circumstances more fuelefficient travel compared with other commuting methods. Therefore, the aerospace industry is growing at a phenomenal pace. It is estimated that by 2030, approximately 27,000 new aircraft will be in the air. The aerospace industry is therefore considered vital to today's world community, enabling strong annual economic growth worth \$425bn in GDP worldwide [1].

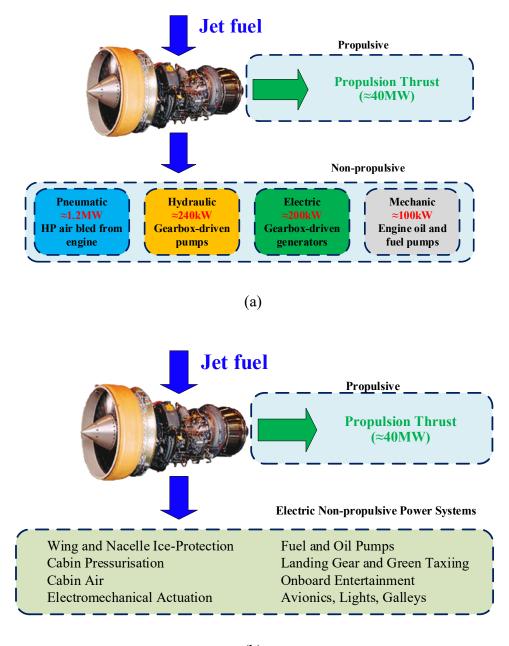

The impact of aircraft on the environment and climate is not negligible, especially the aviation industry is one of the fastest growing sources of greenhouse gas emissions. If expansion trends in the aviation industry progress at the current pace, aircraft will be a big source of pollution for years to come [2]. As a result, the aerospace industry has started to pay more attention to the use of technology to achieve more efficient and environmentally friendly solutions. Due to the rapid development of power electronics, electrical machines and advanced control, the more electric aircraft (MEA) has become the dominant trend in the aerospace industry [3]-[9]. Compared with conventional aircraft, MEA has great potential to reduce fuel burn and CO<sub>2</sub> emissions. Within an MEA, subsystems that used to be driven by hydraulic, mechanical, and pneumatic power are replaced by electrical ones [3], as shown in Figure 1.1a and Figure 1.1b.

Compared with conventional aircraft, the MEA offers significant cost benefits due to fewer parts, integration of key subsystems, and multi-use of components.

It also reduces the overall cost of operation and ownership because its moreelectric architecture helps reduce fuel consumption per passenger per mile, increasing overall aircraft performance and energy usage.

(b)

Figure 1.1: Change in non-propulsive power in conventional aircraft and more electric aircraft. a) Conventional aircraft. b) More electric aircraft.

In conclusion, the implementation of the MEA concept has revolutionised the aerospace industry. With this concept, a significant reduction of weight, cost, and fuel consumption can be achieved.

#### **1.2 Electrical Power Generation Onboard Aircraft**

Nowadays, there are three typical generation systems for electrical power onboard aircraft, which are:

- Constant speed constant frequency (CSCF)

- Variable speed constant frequency (VSCF)

- Variable speed variable frequency (VSVF)

The usage of these three types of electrical power generation systems in recent aircraft is listed in Table 1-1.

| Type of power system | Civil aircraft      | Military aircraft  |

|----------------------|---------------------|--------------------|

| CSCF                 | B777 2*120kVA       | Eurofighter        |

|                      | A340 4*90kVA        | Typhoon            |

|                      | MD-12 4*120kVA      |                    |

|                      | B747-X 4*120kVA     |                    |

|                      | B717 2*40kVA        |                    |

|                      | B737NG 2*90kVA      |                    |

|                      | B767-400 2*120kVA   |                    |

| VSCF                 | B777 2*20kVA        | F-18C/D 2*40/45kVA |

| 115VAC               | MD-90 2*75kVA       | F-18E/F 2*60/65kVA |

| VSVF                 | Horizon 2*20/25 kVA | Boeing JSF 2*50kVA |

| 115VAC               | A380 4*150kVA       |                    |

| VSVF                 | B787 4*250kVA       |                    |

| 230VAC               | A350 4*100kVA       |                    |

Table 1-1: AC electric power system in recent civil and military aircraft[31].

#### 1.2.1 Constant speed constant frequency

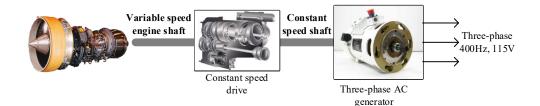

A constant speed constant frequency (CSCF) generation system is shown in Figure 1.2. There, a constant speed drive (CSD) is used between an engine shaft and an electrical generator. The CSD converts a time-varying rotating speed of an engine shaft to a constant speed and drive a three-phase generator. A fixed frequency of the three-phase generator is thus achieved.

Figure 1.2: Constant speed constant frequency generation system.

The CSCF system provides high reliability and has been well developed over the decades. As shown in Table 1-1, it is still employed in modern aircraft such as the Boeing 777. However, the cost of purchase and maintenance of the CSD can be high due to the complexity of the hydro-mechanical drive system [11]. Besides, the use of CSD reduces the reliability of the system. Hence, this topology is not the best choice for future aircraft.

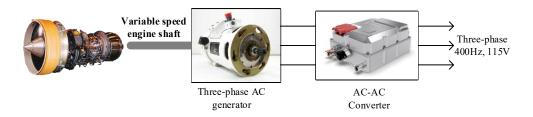

#### 1.2.2 Variable speed constant frequency

Variable speed constant frequency (VSCF) is shown in Figure 1.3. An AC electrical generator is directly driven by the engine gearbox which produces three-phase AC voltage at variable frequencies. The variable frequency is due to the variable speed of the engine shaft. Three-phase voltages are then fed into an AC-AC converter that converts the variable-frequency power to a constant frequency of 400 Hz.

Figure 1.3: Variable speed constant frequency generation system.

In such a VSCF generation system, no CSD is needed between the engine gearbox and the generator. However, the drawback is that this power converter must process all the generated power. Therefore, it must have a full power rating and high reliability to get the required level of safety from the aircraft design.

#### 1.2.3 Variable speed variable frequency

To avoid the reliability issue of the VSCF solution, the power converter can be taken out of the generation system. This results in the variable speed variable frequency (VSVF) configuration as shown in Figure 1.4. The engine shaft directly drives the AC generator and supply to the downstream loads. As the engine speed is not constant, the AC frequency from the generator will thus be changing in the range of 320–800 Hz [12].

Figure 1.4: Variable speed variable frequency generation system.

To connect this AC power with a variable frequency, nearly all aircraft loads will require power converter based interfaces. As a result, power electronic converters are required locally.

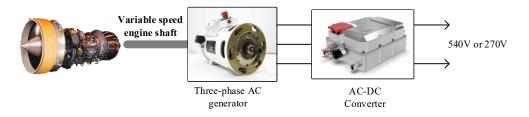

#### 1.2.4 DC Power Generation

Due to the recent development of power electronics, the DC power system has become a potential solution for future aircraft. Indeed, the DC power has been used on military aircraft (F35) and part of the electric power system on Boeing 787. Figure 1.5 shows a DC power generation system with a variable frequency generator supplying an AC-DC converter. The AC electrical power from the generator is rectified to a DC power of 270 V or 540 V [13].

Figure 1.5: DC-voltage generation system

The benefits of such a DC power generation system can be summarised as follows:

- Lower losses in the power transmission cables. This is due to the fact that only two conductors (positive and negative) are required in DC distribution, whereas three conductors (three phases) are required in AC distributions [14].

- The reduction of the skin effect in DC can reduce power loss and also significantly reduce the dielectric losses in the power cables.

- No need for any reactive power compensation equipment: the capacity of wires and devices can be reduced because it does not need to distribute/process the reactive power [14].

- Convenient for parallel power supplying and integrating energy storage system (ESS).

With these potential benefits, the DC power system has attracted great attention in recent years. In addition, such DC generation systems have been widely considered not only for MEA, but also for hybrid vehicles [15], ships [16] and microgrids [17].

The DC systems are applied in a large variety of applications, and consequently, different architectures have been proposed such as single bus, multi-bus, ring bus configurations. Due to its simplicity, as shown in Figure 1.6, the "single bus" EPS architecture is one of the promising candidates for future MEA.

Figure 1.6: "Single bus" EPS structure.

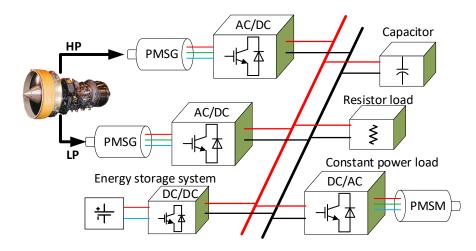

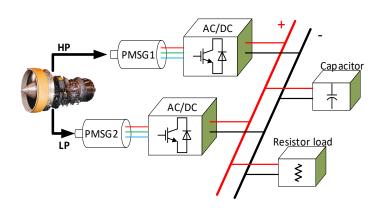

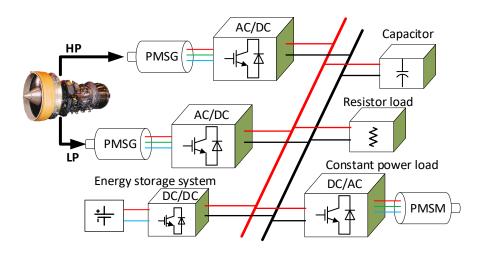

In Figure 1.6, two permanent magnet synchronised generators (PMSGs) supply power to a DC bus through AC/DC converters. An energy storage system (ESS) is connected to the DC bus through a bi-directional DC-DC converter. All kinds of load, i.e., resistive loads and electrical drive loads etc, are supplied by the DC bus. With this structure, the EPS readily permits the paralleling of multiple sources and enables the application of variable-frequency power to be more convenient.

#### 1.2.5 Dual-Channel Power Generation

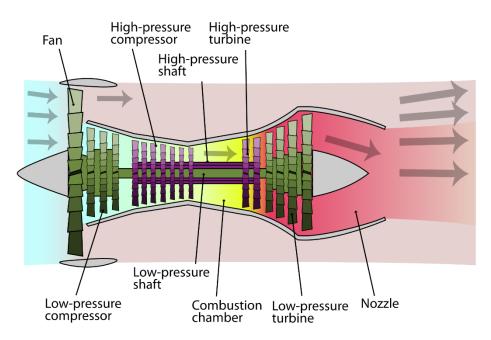

In recent decades, the turbofan engines are widely used for civil aircraft. In such engines, as shown in Figure 1.7, the air sucked by the turbofan is divided into two parts. Most of the air will go through the bypass channel and the rest will go through the engine core. The air passing through the engine core will be compressed by a low-pressure compressor and a high-pressure compressor. After two-stage compression, this high-pressure air will be mixed with fuel in the combustion chamber. With ignition, the produced hot air will pass through a high-pressure turbine and then a low-pressure turbine. The high-pressure turbine (HPT) in return will drive the high-pressure compressor (HPC) through the high-pressure (HP) shaft, and the low-pressure turbine (LPT) will drive the fan and low-pressure compressor (LPC) on the low-pressure (LP) shaft [26].

Figure 1.7: Schematic of a twin-spool, high-bypass turbofan engine.

Conventionally, the electric power on an aircraft is extracted from the aircraft high-pressure engine shaft. With increased load onboard the MEA, extracting electrical power from the high-pressure shaft only is not viable as too much power extracted from the high-pressure shaft may result in compressor surges. A compressor surge happens when a downstream blade row cannot utilise the flow delivered by the upstream ones. Surges can lead to mechanical damage to the compressor blades and the thrust bearings due to large fluctuations of airflow and the direction of forces on the rotor [19]. To extract more electrical power from an engine core whist avoiding a compressor surge, it is essential to extract power from both high-pressure and low-pressure shafts. By doing so,

power transfer between the two engine shafts in an electrical way will become feasible and this will improve engine efficiency and further increase engine operation regimes.

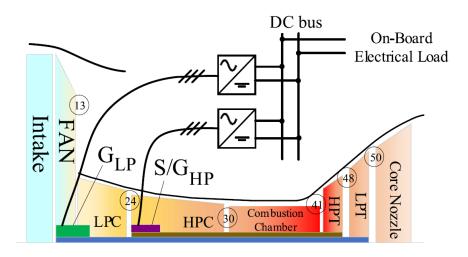

Figure 1.8: Concept diagram of the dual-channel power generation system [18].

In [27], authors proposed an advanced dual-channel electric power generation architecture, as shown in Figure 1.8. In the proposed system, two electrical generators are driven by two engine shafts, i.e., high-pressure shaft and lowpressure shaft, respectively. These two generators supply one common DC bus through the power electronic converters. The authors have concluded that this architecture enables dual-channel power generation and power transferring between two engine shafts. The enabled power transfer between two engine shafts results in improved engine efficiency and stability, as well as compatible thrust with flight mission [27]. At last, the fuel consumption and maintenance cost can be significantly reduced for the aircraft.

### **1.3** Active Switching Harmonic Suppression of the DC-Link Capacitor Currents

#### 1.3.1 Power quality improvement

One aspect that needs to be considered for the dual-channel generation system is its power quality. In conjunction with a growing number of power electronics devices, more current harmonics will be injected into the DC bus. These harmonics will have short-term and long-term effects on both grids and gridconnected equipment [30].

In a DC power system, capacitors are normally used to filter most of the voltage fluctuations. Capacitors are critical components for power quality improvement. Nowadays, electrolytic capacitors, film capacitors, and ceramic capacitors are widely used as dc-link capacitors. For aircraft applications, the weight and volume are critical design factors and should be minimised during the design process. Moreover, reducing harmonics on a DC bus can potentially extend the lifetime of capacitorsand thus improve the reliability of the entire system [31]-[37].

There are numerous methods proposed recently to actively minimise the current ripple on the capacitors [42]-[48]. However, these papers focused on ripple in the range of the fundamental frequencies and essentially to improve system stabilities when a dc-link is supplying an or multiple electric drive loads. Some of these techniques proved their efficiency in stabilising the dc-link variables even for large disturbances. However, the control bandwidth of these methods is mostly far below the switching frequency. This means that current harmonics due to the switching behaviour of converters are filtered out in the control loop, and these algorithms are not able to mitigate such current harmonics flowing into the DC-bus capacitor. Therefore, this thesis aims to contribute to knowledge in this area and propose simple methods which can suppress the switching harmonics of a dc bus with connected multiple power converters.

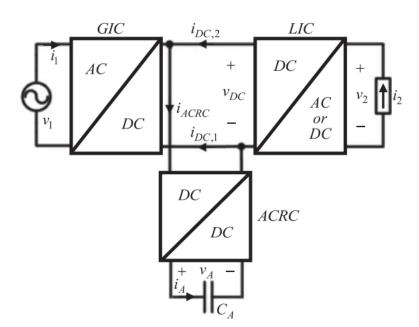

#### 1.3.2 Harmonics suppression using additional DC-DC converters

Adding additional circuits is straightforward solution for reducing capacitor harmonics at switching frequencies [49]-[56]. Having the switching frequencies of additional power devices been higher than those of the main converters, the harmonics on the capacitors can be suppressed. Existing methods by using additional switching devices can be classified into two topologies as follows.

- A parallel-connected bidirectional dc-dc converter, terminated by small auxiliary capacitance, replaces the bulk dc-link capacitance, as shown in Figure 1.9. The system reduces the dc-link ripple by diverting the pulsating portion of instantaneous power into the auxiliary capacitance.

- A series-connected bidirectional dc-dc converter, terminated by small auxiliary capacitance, replaces the bulk dc-link capacitance [57][58], utilising the same principle as the previous subgroup.

Figure 1.9: Harmonic suppression using additional switches [49].

This concept of suppressing harmonics can be implemented in either AC or DC power system with power electronic devices. However, it requires extra elements and thus increases the cost and complexity of systems.

#### 1.3.3 Harmonic suppression for single AC-DC converters

In recent years, researchers have published several papers on the reduction of switching harmonics for single two-level converter dc-link capacitors [59]-[64]. In [59], a mathematical model of DC-link currents is developed using a Double Fourier solution. It gives researchers an analytical starting point to the current harmonics for a two-level AC/DC converter. In [61], the capacitor current ripple is reduced by applying nonadjacent switching vectors.

Some researchers have investigated suppression methods when one or more DC-DC converter is connected with an AC-DC converter. Modifying switching actions on the DC-DC converter is the critical thought in these papers. In [60], suppressed capacitor harmonics are achieved by implementing a high modulation index on the DC-AC inverter and using an additional DC-DC converter. However, the DC-link voltage becomes variable, which is not the case in the DC power system (The voltage should be controlled at a certain level). In [62]-[64], the researchers investigated minimising harmonics when a boost converter is connected with a two-level DC-AC inverter using time-domain analysis. There, switching actions of the DC-DC converter need to be adjusted in every switching cycle, and this comes with high calculation efforts

Figure 1.10: DC-DC converter connecting with a three-phase inverter [64].

and thus long calculation times. Hence, they are not suitable for AC-DC converters which are connected to high-speed PMSGs in MEA applications.

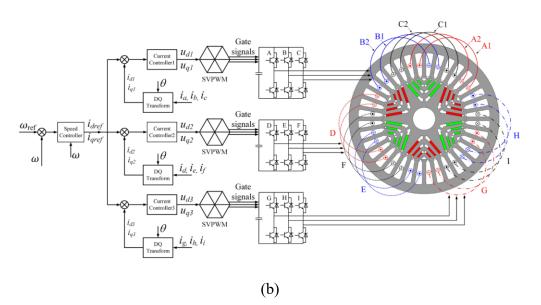

#### 1.3.4 Harmonic suppression for multi-converter systems

For DC electrical power systems with two or more AC-DC converters, the fundamental frequencies of generators are always assumed to be the same in recent publications[65]-[72]. Figure 1.11a and b show two typical systems in these publications. Phase-shift actions among the converters always achieve the switching harmonic minimisation. In Figure 1.11a, the three-phase load is supplied by two parallel-connected converters. The dc-link capacitor-current ripple reduction can be achieved applying a phase shift between the two PWM carriers of the converters, either 0° or 90° depending on the modulation scheme. In Figure 1.11b, windings in the PMSM are split into three channels, and the phase shift methods can also be used to reduce dc-link harmonics where the phase shift angle is dependent on the topology of the multiphase machine.

These two cases in Figure 1.11a and b are different from the dual-channel power generation architecture of the type considered in this thesis. In the dual-channel power generation architecture, the electrical generators are driven by different shafts, thus with different fundamental frequencies. For such a system, shown in Figure 1.8, different fundamental frequencies are applied to their dedicated AC/DC converters. To the best of the authors' knowledge, there are so far very limited publications addressing this issue and illustrating how to minimise the switching harmonics when the fundamental frequencies are different. Although this thesis focuses on the dc-bus supplied by two generators through AC-DC converters, the proposed method and analysing technique can be extended to back-to-back converters or any microgrid with multiple AC-DC or DC-DC converters.

(a)

Figure 1.11: Multi-converter system with the same fundamental frequency. a) parallel interleaved converters[67]. b) Triple three-phase machine [76].

#### **1.4** Objectives of Thesis and Thesis Structure

#### 1.4.1 Objectives

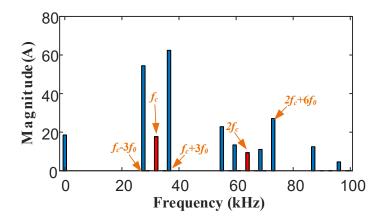

Following a literature review of the active harmonic suppression methods, this work aims to improve the power quality of DC systems in MEA by suppression of harmonic components at switching frequency levels, as shown in the orange bars in Figure 1.12. In Figure 1.12,  $f_c$  is the switching frequency of converters. The harmonics components selected for suppression in this work are those around or above the switching frequency.

Figure 1.12: Spectrum of DC-side current.

Objectives of this work are listed as follows:

- A. Proposal of a method to suppress harmonic component as twice the switching frequency when two PMSG-fed AC/DC converters work under SPWM operation (Chapter 3). harmonic suppression method is proposed based on a simplified mathematical model of the second carrier harmonic from a two-level AC-DC converter developed in Chapter 3. The proposed method can work under any rotor speed and power sharing ratio.

- B. Proposal of a method to suppress capacitor harmonics when two PMSGfed AC/DC converters operate with SVPWM scheme (Chapter 4). The proposed method can suppress both the first and the second order harmonics based on an optimised phase-shift angle.

- C. Proposal of a method to suppress first-band switching harmonics when the system augmented with a DC-DC converter (Chapter 5 and Chapter 6). An adjustable PWM method for the DC-DC converter is proposed. Using an optimised phase-shift angle together with a synchronisation approach, the first band switching harmonics are suppressed.

- D. Built a new test rig for the experiment (Chapter 7). Develop an interface board based on TI DSP 28379D. Using Matlab/Simulink to generate C code for the controller.

Although the context of the work is based on a dual-channel power generation system, it can be also considered to be a challenging case of multi-converter system with common DC bus, such as back-to-back converters, electric vehicles. Thus, the analysis presented afterwards can further be applied to optimise these applications as well.

#### 1.4.2 Thesis structure

To describe the objectives in this thesis with a logical way, this thesis will be arranged as follows:

**Chapter 2** provides the fundamentals of the dual-channel power generation architecture. Models of individual components are introduced, including the PMSG(s), batteries, AC-DC converters, DC-DC converter. Then, this chapter presents the basic control schemes for both local and system-level controller. Finally, the basic theory of SPWM and SVPWM methods are introduced and compared.

**Chapter 3** develops a method to suppress capacitor harmonic when two PMSGs works under carrier based PWM operation. A mathematical model to estimate the second carrier current harmonic on the DC-link harmonic of the two-level AC-DC converter is presented. The results show that the magnitude of the harmonic component was only determined by the value of the DC current and modulation index of the converter, while the carrier phase angle results in the phase angle of the DC-side harmonics. Based on a simplified model, a second

carrier harmonic cancellation method was proposed by actively controlling modulation index together with a phase shift angle on the carrier signal. Finally, simulation is implemented to verify the validity of the proposed second carrier harmonic model and cancellation method.

**Chapter 4.** extends the work from Chapter3 to suppress the current harmonics on DC-link when the PMSGs works under SVPWM operation. SVPWM gives the AC-DC converters higher voltage utilisation ratios. Hence it is suitable for PMSGs operating at high speed. Unlike the proposed method in Chapter 3, in which only the second carrier harmonic is analysed, this chapter will present simplified mathematical models for both the first and second carrier harmonics on capacitors. Based on the simplified models, the active phase-shift angle will be generated to suppress the total harmonic on the DC-link capacitor. The analysis shows that the method will mostly suppress the first switching harmonic under a low output power range but mostly suppress the second carrier harmonic more as the output power increases. Lastly, this chapter validates the proposed mathematical models and suppression method with simulation results.

**Chapter 5** describes suppression methods when the system incorporated a battery and a DC-DC converter. Firstly, this chapter presents a harmonic analysis of a two-level AC-DC converter. Harmonics in the first band switching frequency is selected for suppression based on a mathematical comparison. Then, this chapter proposes a new PWM method of a DC-DC converter for adjusting the magnitudes of harmonics. Based on the harmonic analysis of both the AC-DC and the DC-DC converter, a harmonic suppression method is proposed. In this method, synchronsisation action is also considered.

**Chapter 6** combines the suppression methods in Chapters 3 and 5 altogether to suppress the first sideband and the second carrier harmonics at the same time. To efficiently suppress the most significant component, a component selection block is designed in the controller of the DC-DC converter.

Chapter 7 deals with the experimental support of the analytical results of the previous chapters. The chapter presents the experimental platform and lab

prototype setup. Experimental results are shown to support the analytical results of previous chapters.

**Chapter 8** contains the conclusion of the thesis. It summarises the work and the primary outcome of the PhD research work. It also provides possible future research that can be developed from the work of the thesis. The publications from the research are also given.

## Chapter 2

# Fundamental Models and OperationofaDual-ChannelPowerGeneration System

As discussed in Chapter 1, this thesis focuses on power quality improvement of the dual-channel power generation system. Consequently, this chapter will provide the fundamental operation theories for the dual-channel power generation architecture in the MEA. Control methods for permanent magnet synchronised generators (PMSGs) and the energy storage system (ESS) are also discussed. Furthermore, the content of this chapter will serve as the basis for the proposed methods of power quality improvement.

#### 2.1 Introduction

An example architecture of a dual-channel generation system used for the initial study is shown in Figure 2.1. It consists of several components, which are

- Generators: The power on the DC power system is mainly supplied by two permanent magnetic synchronised generators (PMSGs) which extract power from the HP and LP shafts of the engine. Depending on the flight scenario, the system can be operated with only one active source, or with multiple sources feeding the same DC bus.

- 2) Energy storage system (ESS): Energy storage system is also integrated for emergency status operation. To achieve a flexible power flow in the

system, a bi-directional DC-DC converter is also implemented. Therefore, the battery can operate under either discharging or charging mode depending on supervision control.

- DC-bus capacitor: With a capacitor bank, high-frequency fluctuation of current can be filtered, which helps flatten the DC-bus voltage.

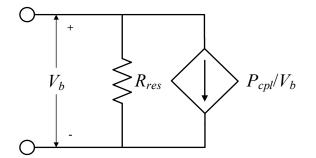

- 4) Power load: The onboard loads are represented by a combination of conventional resistive loads and by constant power load (CPL) typically driven by tightly controlled power electronics. Here, a permanent magnetic synchronised machine (PMSM) is given as an example.

Figure 2.1: Typical dual-generation power system

It is necessary to introduce the characteristics of each part of the electrical power system (EPS) to have a complete understanding of the system.

### 2.2 Permanent Magnet Synchronised Generator (PMSG) System

#### 2.2.1 PMSG modelling

Three-phase PMSG has been widely used in power generation in recent decades. To avoid the complexity associated with the calculation of three phases, it is widely adopted that PMSG are modelled in synchronously rotating

reference frame (i.e., dq frame) [1]. The dynamic equations for PMSG in the dq frame are as expressed in (2.1).

$$\begin{cases} v_d = Ri_d + L_d \frac{di_d}{dt} - \omega_e L_q i_q \\ v_q = Ri_q + L_q \frac{di_q}{dt} + \omega_e L_d i_d + \omega_e \varphi_m \end{cases}$$

(2.1)

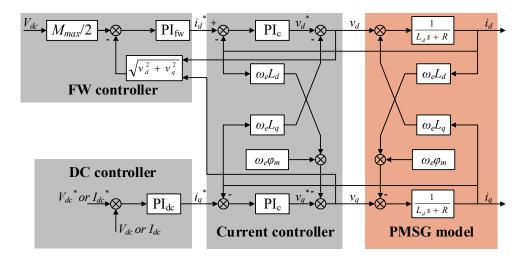

where  $v_d$ ,  $v_q$ ,  $i_d$ ,  $i_q$ ,  $L_d$ ,  $L_q$ , R,  $\varphi_m$ ,  $\omega_e$  represent *d*-axis stator voltage, *q*-axis stator voltage, *d*-axis current, *q*-axis current, *d*-axis inductance, *q*-axis inductance, stator resistance, flux linkage of the permanent magnet, and electrical rotor angular velocity respectively. Model diagram based on (2.1) is shown in Figure 2.2 within the orange block.

In this study of the dual-channel power generation system, surface mounted PMSG is assumed to be used because of its mechanical benefit for high-speed operation [1]. Furthermore, the *d*- and *q*-axis inductance are considered to be identical ( $L_d=L_q=L_s$ ) in the case of the surface-mounted PMSG. Hence, the equation (2.1) can be re-written as the expression in (2.2).

$$\begin{cases} v_d = Ri_d + L_s \frac{di_d}{dt} - \omega_e L_s i_q \\ v_q = Ri_q + L_s \frac{di_q}{dt} + \omega_e L_s i_d + \omega_e \varphi_m \end{cases}$$

(2.2)

Figure 2.2: Diagram of PMSG system.

Maximum allowable phase currents are determined by the designed rated parameters of the converter and machine. The maximum voltage is dependent on the available DC-link voltage and modulation method. The voltage and current limitations can be written as in (2.3) by neglecting stator resistance and the transient terms.

$$\begin{cases} \sqrt{v_d^2 + v_q^2} \le v_c^{max} \\ \sqrt{i_d^2 + i_q^2} \le i_c^{max} \end{cases}$$

(2.3)

where  $v_c^{max}$  and  $i_c^{max}$  are the maximal phase voltage amplitude at the fundamental frequency and maximal phase current, respectively.

#### 2.2.2 Control of the PMSG system

This section will detail the control design for a single generation system (a single source is considered for simplification) based on models illustrated in the previous subsection. The detailed control scheme for generator mode is also shown in Figure 2.2. The flux-weakening controller and DC controller generate the dq-current references which are fed to the current controller.

#### i Current Control

The first stage is to design the current controllers of the starter generator (S/G) power system. It controls dq-current ( $i_d$  and  $i_q$ ) following their reference ( $i_d$ <sup>\*</sup> and  $i_q$ <sup>\*</sup>). Figure 2.2 shows the dq current loops and their respective control plant. The feedforward terms within the current control plant are used for compensating coupling terms in the PMSG model. Then the transfer function between the dq-current and dq-voltage can be reduced to a first-order transfer function as expressed in (2.4) and (2.5) for the d-axis and q-axis current respectively.

$$\frac{i_d}{v_d^*} = \frac{1}{L_s s + R}$$

(2.4)

$$\frac{i_q}{v_q^*} = \frac{1}{L_s s + R}$$

(2.5)

Applying a PI controller with feedforward elements [80], a closed-loop transfer function can be derived as

$$\frac{i_d}{i_d^*} = \frac{k_{pc}s + k_{ic}}{L_s s^2 + (R + k_{pc})s + k_{ic}}$$

(2.6)

$$\frac{i_q}{i_q^*} = \frac{k_{pc}s + k_{ic}}{L_s s^2 + (R + k_{pc})s + k_{ic}}$$

(2.7)

Where  $k_{pc}$  and  $k_{ic}$  are the proportional and integral gains of the current regulator. The transfer function is similar to an ideal second-order response G(s), which can be written as

$$G(s) = \frac{\omega_n^2}{s^2 + 2\xi\omega_n s + \omega_n^2}$$

(2.8)

Where  $\zeta$  is the damping ratio, and  $\omega_n$  is natural bandwidth. For the current regulator,  $\zeta$  and  $\omega_n$  can be expressed as in (2.9) and (2.10) respectively.

$$\omega_n = \sqrt{\frac{k_{ic}}{k_{pc}}} \tag{2.9}$$

$$\xi = \frac{R + k_{pc}}{2L_s \omega_p} \tag{2.10}$$

To achieve the desired dynamic and statistic response, the values of  $\zeta$  and  $\omega_n$  are always set according to fundamental frequency and switching frequency. Then proportional and integral gain of the current regulator can be calculated.

#### ii DC-Link Control and flux-weakening control

After designing the current controller, the *dq*-current references are discussed here which are generated from flux weakening controller and DC-link controller as mentioned earlier.

The flux-weakening controller remains active during generator mode in order to maintain the stator voltage ( $\sqrt{v_d^2 + v_q^2}$ ) at the required level and avoid overmodulation of the converter. Here,

$$\sqrt{v_d^2 + v_q^2} \le \frac{M_{\max} V_{dc}}{2}$$

(2.11)

Where  $M_{max}$  is the maximum modulation index of the converter. This value depends on the modulation scheme, which will be discussed later in Section 2.2.3.

When the machine is rotating beyond the base speed, the flux-weakening operation is activated, and a negative *d*-axis current  $(i_d^*)$  is injected. The *q*-axis current reference is set by the outer DC power loop when the system operates in the generation mode. During the flight, the system operates in the generation mode and the *q*-axis current reference  $(i_q^*)$  is set by the dc-link current or voltage demands dictated by the specific power sharing method. For instance, current reference should be implemented when the power sharing method is voltage feedback-based droop control (current-mode droop control method), while voltage reference should be implemented when the power sharing method is current feedback-based droop control (voltage-mode droop control method).

#### 2.2.3 PWM Methods for the Two-Level AC-DC Converter