# THE UNIVERSITY OF CHICAGO

# MAXIMIZING PERFORMANCE IN POWER-CONSTRAINED COMPUTING SYSTEMS

# A DISSERTATION SUBMITTED TO THE FACULTY OF THE DIVISION OF THE PHYSICAL SCIENCES IN CANDIDACY FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

# DEPARTMENT OF COMPUTER SCIENCE

BY

# HUAZHE ZHANG

CHICAGO, ILLINOIS JUNE 2019

Copyright © 2019 by Huazhe Zhang All Rights Reserved

# TABLE OF CONTENTS

| LI | ST O     | F FIGU         | TRES                                                                                                                             | vi |

|----|----------|----------------|----------------------------------------------------------------------------------------------------------------------------------|----|

| LI | ST O     | F TABI         | LES                                                                                                                              | ii |

| A  | CKNC     | OWLED          | GMENTS                                                                                                                           | ii |

| AI | BSTR     | ACT .          |                                                                                                                                  | х  |

| 1  | INT      | RODUC          | CTION                                                                                                                            | 1  |

|    | 1.1      | Thesis         | Statement                                                                                                                        | 1  |

|    | 1.2      | Challer        | nges                                                                                                                             | 1  |

|    |          | 1.2.1          | 0                                                                                                                                | 2  |

|    |          | 1.2.2          |                                                                                                                                  | 3  |

|    | 1.3      | Contri         |                                                                                                                                  | 4  |

|    |          | 1.3.1          |                                                                                                                                  | 5  |

|    |          | 1.3.2          |                                                                                                                                  | 7  |

|    |          | 1.3.3          | J.                                                                                                                               | 8  |

|    |          |                |                                                                                                                                  |    |

| 2  | PUF      |                | XIMIZING PERFORMANCE UNDER A POWER CAP AT NODE-                                                                                  |    |

|    | LEV      | ΈL             |                                                                                                                                  | 0  |

|    | 2.1      | Relate         | d Work                                                                                                                           | 1  |

|    | 2.2      | Motiva         | tional Example                                                                                                                   | 3  |

|    | 2.3      | Power          | Capping Methodologies                                                                                                            | 5  |

|    |          | 2.3.1          | Software Power Capping 1                                                                                                         | 6  |

|    |          | 2.3.2          | Hardware Power Capping                                                                                                           | 1  |

|    |          | 2.3.3          |                                                                                                                                  | 2  |

|    | 2.4      | Experi         | mental Setup $\ldots \ldots 2$ | 4  |

|    |          | 2.4.1          | -                                                                                                                                | 4  |

|    |          | 2.4.2          |                                                                                                                                  | 4  |

|    |          | 2.4.3          | Evaluation Metrics                                                                                                               | 5  |

|    |          | 2.4.4          |                                                                                                                                  | 6  |

|    | 2.5      | Experi         | mental Evaluation                                                                                                                |    |

|    |          | 2.5.1          |                                                                                                                                  | 7  |

|    |          | 2.5.2          | Performance                                                                                                                      |    |

|    |          | 2.5.3          |                                                                                                                                  | 0  |

|    |          | 2.5.4          | Multi-Application Workloads                                                                                                      |    |

|    |          | 2.5.4<br>2.5.5 | Energy Efficiency                                                                                                                |    |

|    |          | 2.5.6          |                                                                                                                                  | 7  |

|    | 2.6      |                | $sion \dots \dots$         |    |

|    | $_{2.0}$ | Conciu         | 0.00                                                                                                                             | 0  |

| 3 | PO         | WERSH          | <i>HFT</i> : PERFORMANCE & ENERGY TRADEOFFS FOR DEPENDENT |          |

|---|------------|----------------|-----------------------------------------------------------|----------|

|   | DIS        | TRIBU          | TED APPLICATIONS UNDER SYSTEM-WIDE POWER CAPS             | 39       |

|   | 3.1        | Relate         | ed Work                                                   | 40       |

|   | 3.2        | Motiva         | ational Example                                           | 42       |

|   |            | 3.2.1          | Static Power Shifting                                     | 43       |

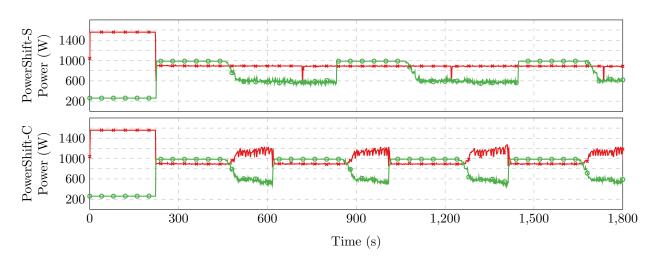

|   |            | 3.2.2          | Dynamically Shifting Unused Power                         | 45       |

|   |            | 3.2.3          | Dynamically Shifting Power to Tail Nodes                  | 45       |

|   | 3.3        | Power          | Management Approaches                                     | 47       |

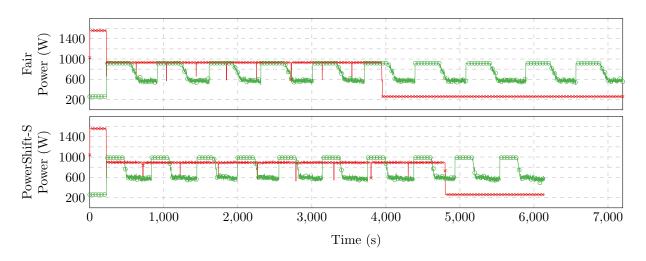

|   |            | 3.3.1          | Fair Power Allocation and SLURM                           | 47       |

|   |            | 3.3.2          | PowerShift-S: Static Power Allocation                     | 48       |

|   |            | 3.3.3          | Dynamic Power Shifting                                    | 50       |

|   |            | 3.3.4          | Extension Beyond Two Applications                         | 55       |

|   |            | 3.3.5          | Complexity, Guarantees, and Discussion                    | 56       |

|   | 3.4        | Exper          | imental Evaluation                                        | 57       |

|   |            | 3.4.1          | Experimental Setup                                        | 58       |

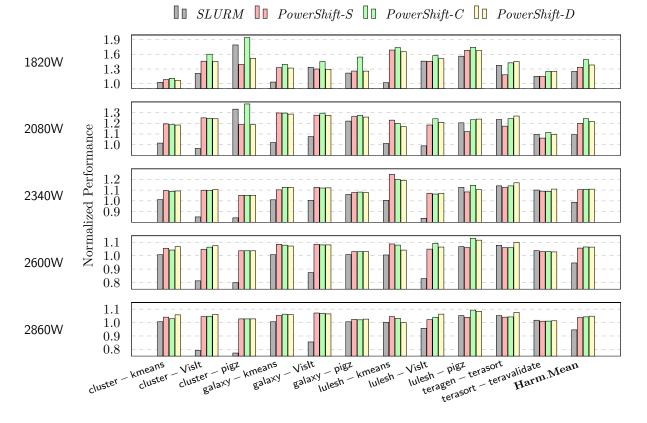

|   |            | 3.4.2          | Performance                                               | 59       |

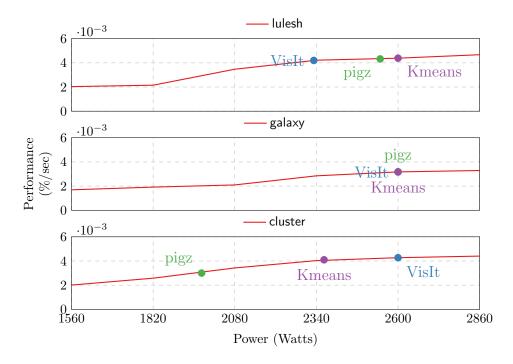

|   |            | 3.4.3          | Coupling's Effects on Optimal Power                       | 62       |

|   |            | 3.4.4          | Results with Co-located Front and Backends                | 62       |

|   |            | 3.4.5          | Considering Three Dependent Applications                  | 63       |

|   |            | 3.4.6          | Energy Savings with High Power Budgets                    | 64       |

|   |            | 3.4.7          | PowerShift's Resilience to System Noise                   | 66       |

|   |            | 3.4.8          | Overhead and Scalability analysis                         | 67       |

|   | 3.5        | Conclu         | usion                                                     | 68       |

| 4 | POI        | ס הח           | WER-CAPPING DEPENDENT DISTRIBUTED APPLICATIONS .          | 69       |

| 4 | 4.1        |                | luction                                                   | 09<br>70 |

|   | 4.1<br>4.2 |                | round and Motivation                                      | 70<br>73 |

|   | 4.2        | 4.2.1          | Prior Power Capping Approaches                            | 73       |

|   |            | 4.2.1<br>4.2.2 | Major Limitations and Solutions                           | 75       |

|   | 4.3        |                | ework                                                     | 78       |

|   | 4.0        | 4.3.1          | Phase 1: Configuration Classification                     | 80       |

|   |            | 4.3.2          | Phase 2: Online Model Building                            | 84       |

|   |            | 4.3.2          | Phase 3: Dynamic Power Shifting                           | 86       |

|   | 4.4        |                | imental Evaluation                                        | 88       |

|   | 7.7        | 4.4.1          | Experimental Setup                                        | 89       |

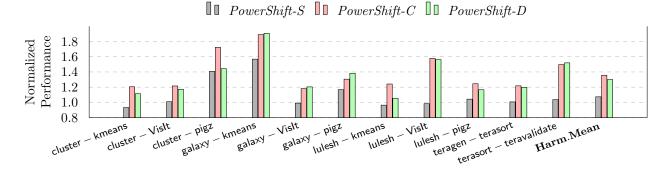

|   |            | 4.4.2          | Performance                                               | 90       |

|   |            | 4.4.3          | Running with Offline Profiles                             | 92       |

|   |            | 4.4.4          | Resilience to Tail Effects                                | 93       |

|   |            | 4.4.5          | Topology-obliviousness                                    | 95       |

|   |            | 4.4.6          | Online Model Builder                                      | 96       |

|   |            | 4.4.7          | Scalability analysis                                      | 97       |

|   | 4.5        |                | ed Work                                                   | 97       |

|   | 4.6        |                | usion                                                     | 99       |

|   | 1.0        | Control        |                                                           | 00       |

| 5  | CON  | ICLUSI | ON                                    | ) |

|----|------|--------|---------------------------------------|---|

|    | 5.1  | Future | Work                                  | 2 |

|    |      | 5.1.1  | Node-level Challenge                  | 2 |

|    |      | 5.1.2  | Large-scale Challenge                 | 3 |

|    |      | 5.1.3  | Large-scale Reliability Challenge 104 | 4 |

|    |      | 5.1.4  | Performance Model                     | 4 |

|    |      |        |                                       |   |

| BI | BLIO | GRAPH  | HY                                    | 5 |

# LIST OF FIGURES

| 2.1  | Tradeoff between timeliness and efficiency from hardware and software power                               |    |

|------|-----------------------------------------------------------------------------------------------------------|----|

|      | capping, running x264                                                                                     | 14 |

| 2.2  | PUPiL's approach to hybrid hardware/software power capping                                                | 22 |

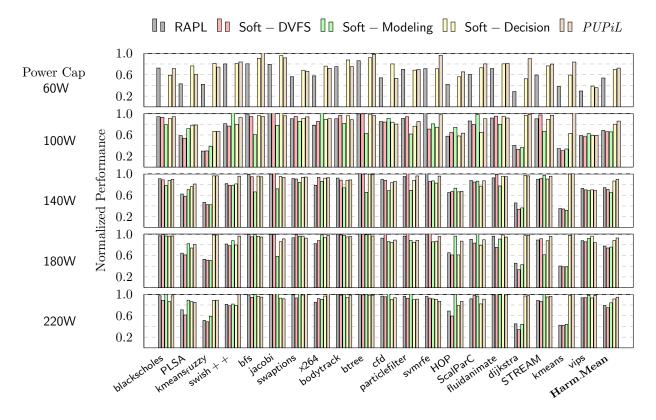

| 2.3  | Performance of several power control techniques normalized to optimal                                     | 28 |

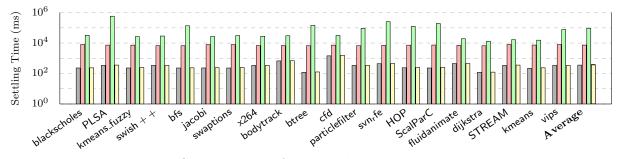

| 2.4  | Settling times for several power control techniques.                                                      | 29 |

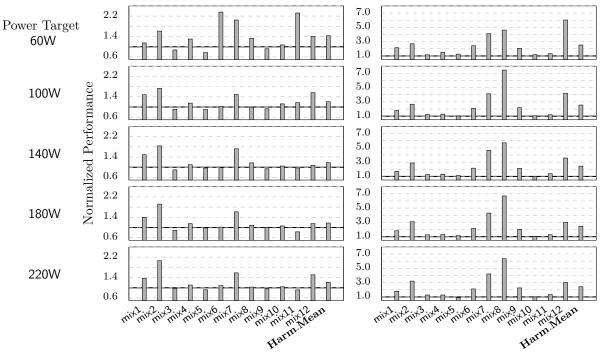

| 2.5  | Benchmark characteristics.                                                                                | 30 |

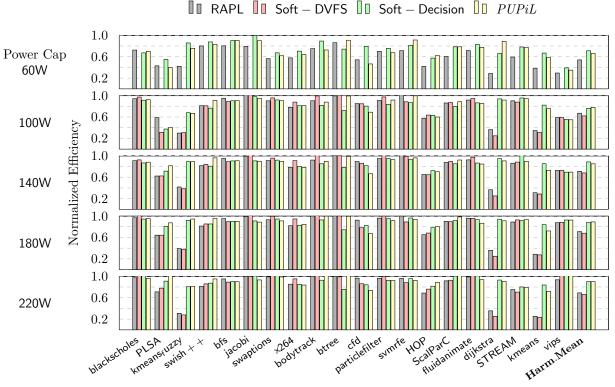

| 2.6  | Ratio of <i>PUPiL</i> to RAPL performance in cooperative (left) and oblivious (right) multiapp scenarios. | 33 |

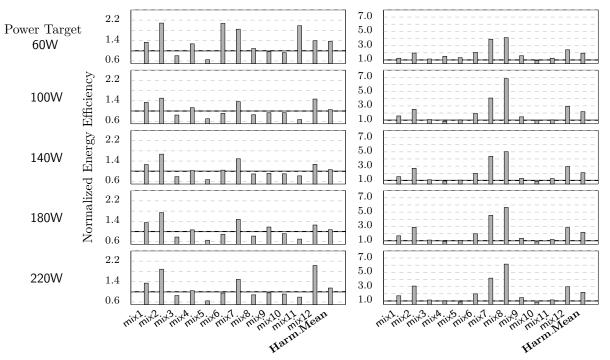

| 2.7  | Energy efficiency of several power control techniques normalized to optimal.                              | 36 |

| 2.8  | Ratio of <i>PUPiL</i> to RAPL energy efficiency in cooperative (left) and oblivious                       | 00 |

| 2.0  | (right) multiapp scenarios                                                                                | 37 |

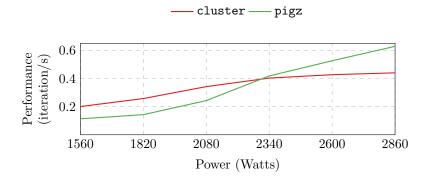

| 3.1  | Performance/power for cluster and pigz                                                                    | 42 |

| 3.2  | Fair (top) vs. PowerShift-S (bottom). $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$               | 43 |

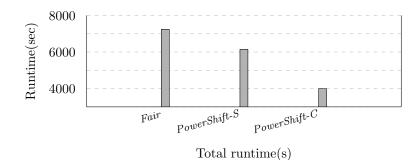

| 3.3  | Runtimes for different approaches.                                                                        | 44 |

| 3.4  | PowerShift-S (top) vs. PowerShift-C (bottom). $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$          | 44 |

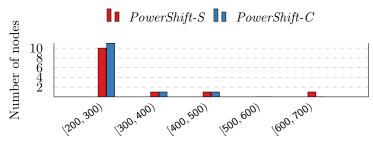

| 3.5  | Tail distribution under static and dynamic power shifting. The static approach                            |    |

|      | has a long tail, but the dynamic approach has a much shorter tail                                         | 46 |

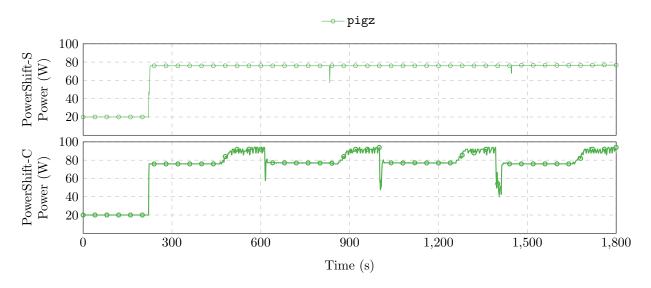

| 3.6  | Tail node power time series comparing PowerShift-S (top), to PowerShift-C (bot-                           |    |

|      | tom)                                                                                                      | 46 |

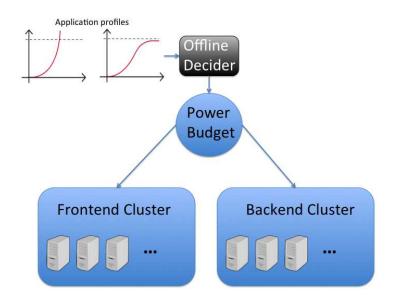

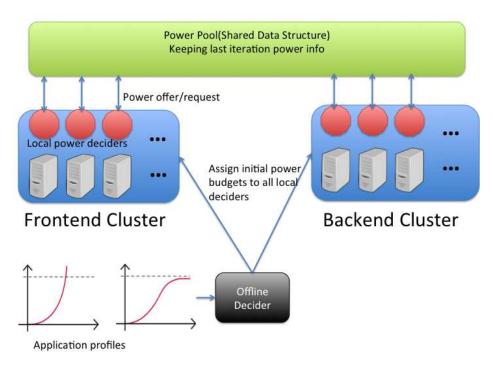

| 3.7  | PowerShift-S overview.                                                                                    | 48 |

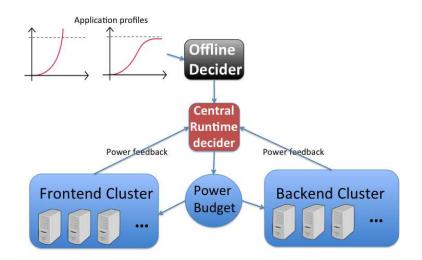

| 3.8  | PowerShift-C overview                                                                                     | 51 |

| 3.9  | PowerShift-D overview.                                                                                    | 55 |

| 3.10 | 0 1 1                                                                                                     | 58 |

|      | Power distribution of different backends paired with the three scientific frontends.                      | 63 |

| 3.12 | Performance under system noise.                                                                           | 65 |

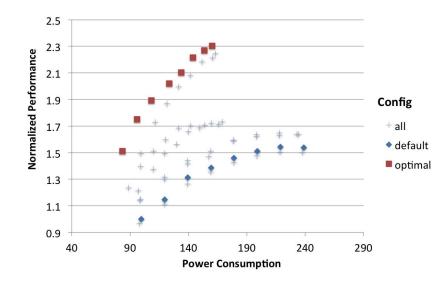

| 4.1  | Performance of different node configurations.                                                             | 77 |

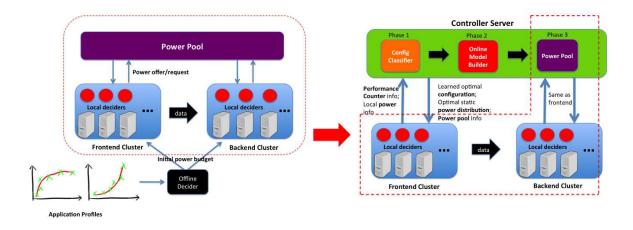

| 4.2  | Overview and comparison of <i>PowerShift-D</i> (left) and <i>PoDD</i> (right)                             | 79 |

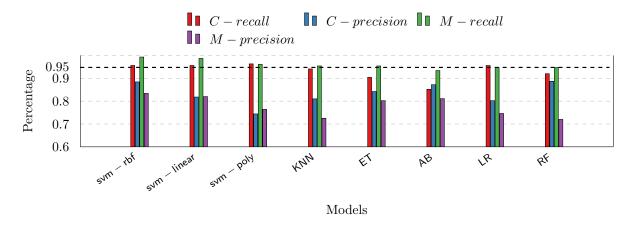

| 4.3  | Recall and precision of 8 learners for classifying computing and memory resources.                        | 83 |

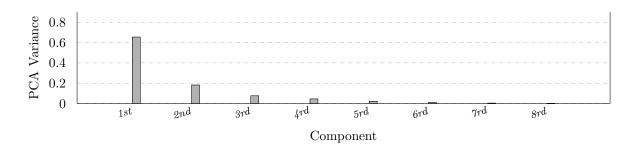

| 4.4  | Eight features explain more than 99.8% of variance                                                        | 84 |

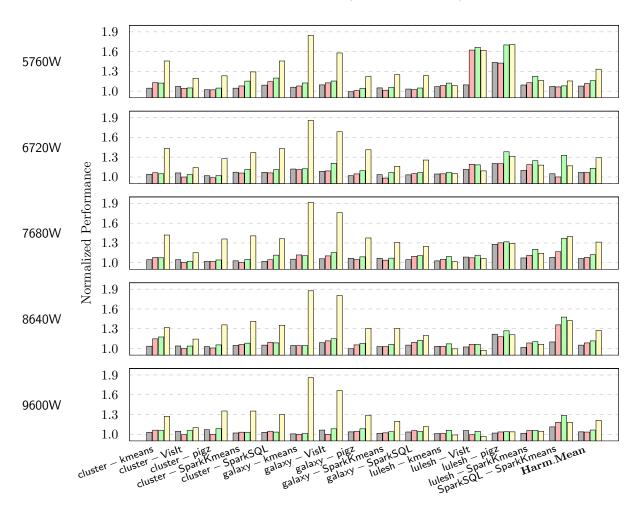

| 4.5  | Performance for different power management systems under different power caps.                            | 88 |

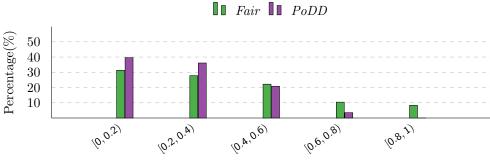

| 4.6  | Runtime distribution with work imbalance                                                                  | 93 |

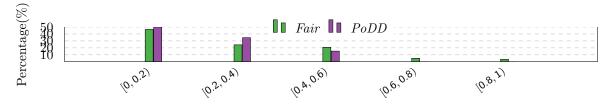

| 4.7  | Runtime distribution with system noise.                                                                   | 94 |

# LIST OF TABLES

| 2.1 | Server resources                                   | 3  |

|-----|----------------------------------------------------|----|

| 2.2 | System configurations                              | 25 |

| 2.3 |                                                    | 29 |

| 2.4 |                                                    | 31 |

| 2.5 |                                                    | 3  |

| 2.6 |                                                    | 5  |

| 3.1 | Comparison of performance under power caps         | 50 |

| 3.2 | Performance with co-located couples                | 53 |

| 3.3 | Performance of three dependent applications        | 54 |

| 3.4 |                                                    | 55 |

| 3.5 |                                                    | 57 |

| 4.1 | Overview of performance counters monitored         | 80 |

| 4.2 | Classifier models explored                         | 31 |

| 4.3 | Accuracy comparison of using top X components      | 34 |

| 4.4 | Comparison of performance under power caps         | 0  |

| 4.5 | Comparison of <i>PoDD</i> with or without profiles | )3 |

| 4.6 | Comparison with different topology mapping         | )4 |

| 4.7 | Comparison of online profiling techniques          | )5 |

| 4.8 |                                                    | 95 |

| 4.9 |                                                    | 6  |

# ACKNOWLEDGMENTS

It has been a wonderful journey exploring the unknown world for last 6 years! I am extremely grateful to all those who have helped to make it special to me, without any of you, this thesis would never be the same or even finished. I can only hope to list all of you here.

The world's BEST advisor, Professor Henry(Hank) Hoffmann. From years of studying science, I learned that an extreme statement is rarely true, but I believe "BEST" here is one of the rare cases. Thank you for patiently teaching all the basics of research and communication in English when I just started in Chicago, for always pointing out the right way to go, for motivating and cheering while I am down, for all the care along the way for not only my research but my life... And this list goes on. You have been way more than a research advisor to me, but role model and great friend!

My wife, Jiayi Liu. Your unconditional love and support mean the world to me. Time has been very long before you came to Chicago and it flies afterwards. You gave up job opportunities for supporting me, you closed the distance of tens of thousands of miles, you made everything, every day easier for me, you are the true hero.

My parents and parents-in-law, Kaiwang Zhang, Yanjun Wang, Xiulin Liu and YongQing Yu. Your unwavering support and love is always with me before and during grad school. You made every effort that parents can make to help and support Jiayi and me. We appreciate for everything you have given us.

Professor Zhihui Du, who aided me getting to Chicago. You gave the initial opportunity to me to get into research and that opened up the amazing world to me and all these followed. I cannot thank you enough for giving me the chance to do research with you when I am an undergrad. I would not be where I am without your kind help.

My master thesis committee members, Andrew Chien and Haryadi Gunawi. My doctoral dissertation committee members, Ian Foster and Haryadi Gunawi. Thank you for dropping wisdom to me and this work. This thesis can not be as good without your great advice.

My great friends in University of Chicago. Zhao Zhang, for so much help on getting me settling down and blending in the life here and for your great companionship. Fan Yang, for your kind support on helping me to configure RIVER machines time after time. Your kindness will keep inspiring me, even you are not around. Jason Lui, one of my best buddies, for everything unrelated to work we have done here, I miss all the lifting, balling, fishing, eating, gaming. Connor Imes and Nikita Mishra, for the strong collaboration and share of life in school and conferences. All my lab mates and peers, Saeid Barati, Zhixuan Zhou, Roselyne Tchoua, Will Kong, Anne Farrell, Bernard Dickens, Ivana Marinčić Tong Hu, Yuanwei(Kevin) Fang, Liwen Zhang, Jialei Wang, for creating this great atmosphere to study and live, for all the valuable inputs into my life.

The department technical and administrative staff, especially Bob Bartlett, Margaret Jaffey. You have done a great job to all students, thank you for make our life easier.

My mentor/managers during internships. Leonardo Piga, for your kind mentoring at AMD research. Qingyuan Deng, for your outstanding management and help at Facebook and for helping me get return offer which saves me tons of time job hunting. Look forward to working with you in the near future.

Special thanks to great research platforms for supporting my research: RIVER – Research Infrastructure to explore Volatility, Energy-efficiency, and Resilience at University of Chicago, administried by Andrew Chien and Fan Yang. Chameleon, a configurable experimental environment for large-scale cloud research.

Finally, for those not mentioned here, I apologize if I miss your name. I appreciate the knowledge, help, and laughters you brought to my life. I appreciate each and every interaction with you and that I believe takes me where I am today. So thank you! I am definitely looking forward to our path crossed in the future.

# ABSTRACT

Power constraints have become arguably the biggest obstacle for the performance scaling of computing machines. No matter what scale of computing system – A mobile phone or supercomputer – they are all power restricted in one way or another to ensure normal operation. While various computing systems may require different power management techniques, the goal of such systems is invariant and contains two folds of requirement: (1) guarantee computing system operates under a certain power budget/cap, and (2) efficiently make use of the limited power to deliver high performance. Thus, the challenge can be formalized to a classic constrained optimization problem – given power consumption constraints, maximize the performance of computing systems. In this dissertation, we focus on solving this problem for server systems from single-node level to large-scale. More specifically, this dissertation contains 3 projects addressing power capping challenge at different scales.

First, we propose PUPiL, a hardware/software hybrid power control system to address the power challenge at the node level. It makes the key observations of tradeoffs between existing software-based and hardware-based approaches: (1) hardware techniques provide significantly faster response time – quickly enforcing power limits and, (2) software provides much greater flexibility – by tailoring resource usage to the current application workload – leading to high performance efficiency. PUPiL combines the best of software and hardware approaches, achieving significantly higher performance with nearly same response time as hardware approach.

Second, we propose *PowerShift*, a distributed power management system to address the emerging challenge of power capping dependent applications in large-scale systems. *PowerShift*, to our knowledge, is the first work to identify the unique challenge of dependent distributed workloads and presents a family of three techniques for this scenario, demonstrating improved performance, reduced energy, and dynamic adjustment to tail behavior and system noise.

Last, *PoDD*, a hierarchical distributed power control system inspired by both *PUPiL* and *PowerShift*, is proposed to further overcome major limitations in power capping dependent applications. It incorporates learning/hardware hybrid node-level power capping with system-level power shifting to deliver significantly higher performance than prior works and no longer requires offline application profiles because of building power models online, greatly improving practicality and performance efficiency.

The 3 power management frameworks systematically study the problem of maximizing performance in power constrained systems. The key ideas and insights are highly general to guide the design of real world power control systems for a wide range of workloads and platforms. All implemented systems are open-source and evaluated to be practical, scalable, reliable and also not limited to particular applications and systems, which hopefully will serve as a base model/system to future research on power capping.

# CHAPTER 1 INTRODUCTION

## 1.1 Thesis Statement

This dissertation address the indispensable need for power budgeting/capping techniques in computing systems focusing on server systems from single-node scale (a server) to large-scale computing system (datacenter or supercomputer consists of tens of thousands of servers). The challenge of the power constraint problem are two folds: (1) how to enforce the system respecting power limit, and (2) more challengingly, how to achieve optimal performance under power caps. At node level, we propose using adaptive feedback control system that coordinates software and hardware power capping technique for high performance efficiency and timely system response. At large-scale level, we introduce a hierarchical power management framework to coordinate node-level power optimization and system-level power shifting. The node-level power optimization involves learning optimal resource allocation from hardware performance counter, which requires no code instrumentation nor application profiles. The power shifting involves an original 3-group power shifting mechanism to address the unique challenge of dependent distributed applications.

### **1.2** Challenges

Power constraints have become first-class concerns in computing systems. From a single processor on our phone to gigantic million-node supercomputers, they are all restricted with power budgets. Thus, there is an increasing need for power control systems to help computing systems running within budget while delivering high performance. Since power constraint problems are different for systems of different size, following paragraphs break the problem down into single node power capping and distributed power capping.

# 1.2.1 Node-level Power Capping Challenge

At node-level, modern processors are constrained by *dark silicon* – their abundance of transistors enables them to draw more power than they can safely sustain [25, 98]. For example, the Exynos 5 processor (in the Samsung Galaxy S4 phone) has a 5.5W peak power – nearly  $2\times$  its sustainable heat dissipation, limiting peak speed to less than 1 second [87]. At the other end of the spectrum, future exascale supercomputers have a predicted operating budget of 20 MW [6], making power management a central challenge of supercomputer operating systems [95].

These physical constraints create a need for *power control systems* which guarantee the processor operates within a strict *power cap*. Research power capping systems have been implemented in software [13, 15, 29, 54, 76, 77, 79, 103]. The need for power capping has become so great, however, that Intel processors now support power capping in hardware with their Running Average Power Limit (RAPL) interface [16].

Whether implemented in hardware or software, there are two essential properties for a power capping system. The first is **timeliness** – the speed with which a new cap can be enforced. The second is **efficiency** – the performance delivered under the cap. Without timeliness, critical operating bounds can be violated, damaging the hardware. Without efficiency, application performance suffers unnecessarily. It is, of course, trivial to implement a power cap while ignoring performance – simply turn the machine off.

In general, hardware approaches provide superior timeliness – hardware reacts much faster than software – while software approaches have superior efficiency – they find the highest performance set of resources to activate within the power cap. Hardware's timeliness is due to the relatively simple circuits that control key power indicators like processor voltage and frequency. Software's efficiency derives from its ability to consider the complex interactions between multiple resources, allowing it to solve the constrained optimization problem of scheduling the highest performance resource configuration which obeys the power cap. However, none of the software-only or hardware-only approaches achieves both satisfying efficiency and timeliness.

# 1.2.2 Distributed Power Capping Challenge

At the distributed level, next generation *exascale* supercomputers are predicted to have a strict operating budget of approximately 20 MW, but the total power dissipation at full utilization would far exceed this budget [6]. These systems require sophisticated, distributed *power-capping* mechanisms to assure their power budget will not be exceeded; the United States Department of Energy (DoE) has therefore declared power management a key challenge for exascale [95].

While power concerns create new problems, exascale's increased capacity creates new opportunities. Specifically, instead of sequentially running dependent jobs that communicate through disk, the size of exascale supercomputers allows these jobs to be *coupled* [2, 6, 12, 51, 95]. That is, two formerly independent jobs can now be run simultaneously and communicate at runtime. For example, scientific simulations can now be run with *in situ* data analysis or visualization providing scientists the insight needed to alter the simulation as it runs [2, 12]. Additionally, separately developed physics simulations can now be run together, sharing their results to provide much greater fidelity [51]. In fact, the DoE has declared resource management for coupled application workloads an additional concern for exascale [6, 95]. There are three challenges to maximizing performance for coupled applications under a power cap:

1. The coupled applications have distinct power and performance tradeoffs. Thus, optimal performance requires imbalanced power allocation and finding the highest performance power allocation is not trivial. Specifically, the couple's performance is dependent on the slowest job, so a power allocation that provides good performance for an application in one couple may be sub-optimal when that application is part of a different couple.

- 2. Such coupled applications almost invariably go through distinct phases of communication and computation and a power manager should adapt to these phases.

- 3. For some couples and power budgets, performance improvement is not possible due to diminishing returns in one application's power/performance trade-off space. The challenge here is tp recognize when performance cannot be improved and reallocating power to save energy.

Unfortunately, existing work on enforcing power caps across large scale systems does not account for coupled applications. For example, several approaches increase overall system performance with unbalanced power allocations [45, 49, 89]. Other approaches shift power as independent applications transition through compute and IO phases [84]. While unbalanced allocation and phase-adaptation are important for coupled applications they are not sufficient. In brief, coupled applications obey the basic principles of pipeline parallelism: the couple's speed is determined by the slowest application. Thus, *optimizing coupled application performance under a power cap often requires slowing down the faster application to shift more power to the slower.* This requirement to slowdown a fast application is unique to coupled application at a time [45, 82], or optimize for multiple, independent applications [49, 84, 89]. Furthermore, due to the couple's interaction, sometimes it is not possible to increase performance through any amount of power shifting. Here, the couple scheduler should reduce total power usage to save energy.

# **1.3** Contributions

This dissertation studies two major problems in the spectrum of optimizing performance under power caps: (1) the efficiency and timeliness tradeoffs in power capping single node server system, (2) maximizing performance of dependent workloads in power-constrained distributed systems. For each problem, we propose and implement original power management systems to address its unique challenges. All systems are designed to work for various real world applications and platforms. Evaluations on real computing systems with a number of important applications show great advantages of performance efficiency and other properties of our systems. The key idea and insights in the thesis, hopefully, can offer help to or be built upon by future research in this area. More specifically, we tackle these two problems with three distinct, yet continuous projects:

- *PUPiL*, maximizes performance under a power cap for single node server. By observing the tradeoffs between software-only and hardware-only power capping techniques in terms of performance efficiency and timeliness, it proposes a hybrid software/hardware approach to take advantage of the benefits from both worlds.

- *PowerShift*, optimizes performance for dependent distributed applications under systemwide power caps. To the best of our knowledge, *PowerShift* is the first work to consider coupled applications in distributed power capping. We point out the fundamental principle to optimize for coupled applications: to keep each application running at even speed. Following this idea, *PowerShift* offers 3 different power capping frameworks to handle dependent workloads.

- *PoDD*, further optimizes for dependent distributed applications for performance and practicality in two major aspects: (1) hierachical power capping system to coordinate advanced node-level power capping (inspired by *PUPiL*) with system-level power shifting (inspired by *PowerShift*), (2) requires no prior knowledge of application profiles by online model building.

This following sections detail each of the 3 contributions.

### 1.3.1 PUPiL

In this project, we explore the node-level power capping techniques. A key observation is: in general, hardware approaches provide superior timeliness –hardware reacts much faster than software – while software approaches have superior efficiency – they find the highest performance set of resources to activate within the power cap. We explore the tradeoff between timeliness and efficiency in power capping approaches. Specifically, we advocate a hybrid approach that includes both software and hardware components, using each to address the challenge to which it is best suited. PUPiL's hybrid approach provides the timeliness of hardware with significantly greater efficiency. The performance gains are particularly high when enforcing power caps in the oblivious multi-application scenario. In both single and cooperative multi-application workloads, PUPiL provides at least 18% greater mean performance compared to RAPL (the state-of-the art hardware power capping technique). In oblivious multi-application workloads, PUPiL provides at least 2.4x the mean performance.

The fundamental contribution of *PUPiL* is an empirical demonstration of the need for software and hardware to work together to maximize performance under power caps. The combined software/hardware approach proposed in this project demonstrates it is possible to achieve significant performance gains over Intel's state-of-the-art, commercial hardware approach – especially for multi-application workloads.

Besides contribution mentioned above, this project makes the following contributions:

- Develops a decision framework to maximize performance under a power cap.

- Evaluates this implementation on a real system in multiple usage scenarios.

- Identifies workload properties where Intel's RAPL power capping system fails to deliver the best performance.

- Makes all scripts, code, and data collection tools from this evaluation available as open source, so others can test or extend these results<sup>1</sup>.

<sup>1.</sup> All source code, scripts, inputs, and patches are available at: https://github.com/PUPiL2015/PUPIL.git.

#### 1.3.2 PowerShift

This project addresses the emerging challenge of coupled workloads running under a systemwide power cap in distributed computing scenario. The unique performance characteristics of coupled applications – that the couple's speed is determined by the slowest application - throws off the prior works in this area, which either optimize for single application or independent applications [4, 9, 24, 33, 45, 49, 82, 84, 89]. PowerShift is the first work, to our knowledge, to address the unique challenges of coupled applications with *PowerShift*, a family of three techniques for shifting power between dependent applications in a distributed system. All three respect the system-wide power cap and maximize the couple's performance by shifting power from the faster application to the slower one, until both run at the same rate. All techniques rely on existing node-local power cap enforcement (e.g., [52, 54, 79,109) PowerShift-S is a static technique that sets power caps based on individual application profiles. PowerShift-C is a centralized dynamic approach in which a single decision maker dynamically shifts power. *PowerShift-D* is a *distributed dynamic approach* where nodes put surplus power into a shared pool, and nodes that need more power take from the pool. These techniques provide different tradeoffs in overhead, flexibility, and adaptability. We implement *PowerShift* on a real 26 node system. We compare SLURM, a state-of-the-art, power-aware job scheduler [89] and *PowerShift* to a *Fair* approach that evenly divides power among all nodes. Results show that *PowerShift* improves mean performance up to 17% over Fair approach and up to 14% over SLURM. Additional results demonstrate that PowerShift detects when no performance improvement is possible and instead reduces energy. Furthermore, PowerShift  $D \ \mathcal{C}$  adapt to system noise and tail behavior, automatically shifting power to nodes that have unexpected extra load or long tails, improving performance by 36% and 30%, respectively. Finally, we show that *PowerShift* is topology-oblivious and works equally well if the coupled applications are physically separate or mapped to different power domains on the same node. In summary, *PowerShift* makes the following contributions:

- First work to identify the unique challenge of coupled applications.

- Proposes *PowerShift*, a family of power capping frameworks for coupled applications.

- Evaluaton shows *PowerShift* achieves 7-14% performance gain over SLURM, 18% energy saving for 5% performance loss, 30-36% performance gain in noisy environment

- Evaluation and comparison between 3 power capping frameworks offer insights of fundamental design tradeoffs on overhead, flexibility, and adaptability.

- Open-source all scripts, code, and data collection tools for future research to be built on <sup>2</sup>.

### 1.3.3 PoDD

Coupled applications are predicted to be one of the most important workloads in exscale supercomputer [95], and the system power budget is predicted to be 20MW [6]. While *PowerShift* has started to address this problem, *PoDD* further addresses two major challenges to significantly improve performance efficiency and practicality. Specifically, 2 major limitations in *PowerShift* are:

- Dependence on offline application profile greatly makes it less practical in real life systems.

- Hardware-only power capping at node-level results in sub-optimal performance.

We propose *PoDD*, a dynamic power management system addressing the challenge of coupled applications. It delivers high performance by incorporating advanced original nodelevel power capping technique to coupled-workloads-aware system-level dynamic shifting. It no longer requires prior knowledge of application profiles by building power performance model online. Furthermore, it does not need any code instrumentation. Finally, it greatly mitigates tail effect in distributed environment, is resilient to system noise and scales well

<sup>2.</sup> All source code, scripts, inputs, and patches are available at: https://github.com/huazhe/powershift.git.

large number of nodes. We implement PoDD on a 49 node distributed system and evaluate it against 4 widely-used/state-of-the-art power control systems: *Fair*, *SLURM*, *PowerShift-S* and *PowerShift-D*. The evaluation shows PoDD improves mean performance over emphFair by 28%, which outperforms *SLURM* by 21%, outperform *PowerShift-S* by 19%, and outperform *PowerShift-D* by 14%. Our evaluation on noisy environment and scalability also shows *PoDD* is resilient to system noise and predicted to have a 20X scalability over current 49-node system. Evaluations show great flexibility of *PoDD*, that it is topology-oblivious and works well whether coupled applications are physically separate or co-located.

To sum up, *PoDD* makes following contributions:

- Proposes an original machine learning classifier and hardware hybrid node-level power capping technique.

- Deploys a hierarchical power control system that coordinates advanced node-level power capping with system-level power shifting.

- Builds performance power model online to derive optimal power distribution for coupled applications, releasing the dependence on prior application profiles.

- Evaluation shows an average 14% speedup over the state-of-the-art approach *Power-Shift*, flexible topology-oblivious, scalable at least 20x scale potential, reliable resilient to system noise.

- Open-source <sup>3</sup>.

<sup>3.</sup> All source code, scripts, inputs, and patches are available at: https://github.com/podd2019/podd.git.

# CHAPTER 2

# PUPIL: MAXIMIZING PERFORMANCE UNDER A POWER CAP AT NODE-LEVEL

This chapter introduces *PUPiL*, a software and hardware hybrid power capping approach for single node systems.

Power and thermal dissipation constrain multicore performance scaling. Modern processors are built such that they could sustain damaging levels of power dissipation, creating a need for systems that can implement processor *power caps*. A particular challenge is developing systems that can maximize performance within a power cap, and approaches have been proposed in both software and hardware. Software approaches are flexible, allowing multiple hardware resources to be coordinated for maximum performance, but software is slow, requiring a long time to converge to the power target. In contrast, hardware power capping quickly converges to the power cap, but only manages voltage and frequency, limiting its potential performance.

We propose PUPiL, a hybrid software/hardware power capping system. Unlike previous approaches, PUPiL combines hardware's fast reaction time with software's flexibility. We implement PUPiL on real Linux/x86 platform and compare it to Intel's commercial hardware power capping system for both single and multi-application workloads. We find PUPiLprovides the same reaction time as Intel's hardware with significantly higher performance. On average, PUPiL outperforms hardware by from 1.18–2.4× depending on workload and power target. Thus, PUPiL provides a promising way to enforce power caps with greater performance than current state-of-the-art hardware-only approaches.

The rest of this chapter are organized as follows: First, Chapter 2.1 discusses the related works in this domain. Next, Chapter 2.2 introduces motivational examples. Then, Chapter 2.3 demonstrate the system design and algorithms. After that, Chapter 2.4 and Chapter 2.5 shows the experimental setup, results, and discuss its reason and insight. Finally, Chapter 2.6 concludes this work.

### 2.1 Related Work

As power and energy become first order concerns of computing systems, a number of approaches have been proposed for managing these critical issues. Some approaches focus on minimizing energy, which can reduce costs in data centers and servers [42, 63, 85, 99, 104] or increase battery life in mobile and embedded platforms [30, 37, 44, 53, 70, 83, 97, 106]. These techniques provide performance guarantees (*e.g.*, for meeting quality-of-service or real-time requirements) and minimize power consumption or energy, but they do not provide power guarantees and cannot implement power caps.

To help facilitate energy management, several OS projects have added operating system support for monitoring and allocated energy. The Quanto project facilitates tracking energy usage in networked embedded devices [31]. The Cinder OS allows energy usage to be tracked and allocated across multiple applications in a system [81]. The Koala project also allows energy to be tracked and allocated while supporting several different policies for optimizing energy and performance [90]. Similarly, *power containers* support fine-grain tailoring of heterogeneous resources to varying workloads [86]. LEO is a hierarchical Bayesian learning framework that produces extremely accurate estimates of an application's performance and power consumption [69]. The Coop-I/O project allows applications to coordinate with the operating system to schedule I/O operations in the most energy efficient manner possible [102]. The GRACE OS meets performance requirements for media while minimizing energy [97, 106]. None of these projects, however, explicitly support maximizing performance under a power constraint, which is the subject of this paper. JouleGuard provides energy guarantees (but not power) by coordinating application behavior with system resource usage [37].

While energy reduction can decrease costs and increase battery life, it is a separate concern from meeting power limits. Operating within power limits has become essential as multicore scalability is increasingly limited by power and thermal management [25, 98]. The physical realities of power dissipation in modern processors have led to hardware designs characterized by *dark silicon*. That is, modern processors cannot physically power all transistors at their maximum speed without damage. Thus, some of those transistors are kept dark (meaning they are not powered at all) or dim (meaning they are powered at less than full speed) [94].

These physical realities create a need to limit processor power dissipation. This concern is important enough that Intel's SandyBridge and later processors support power management in hardware [16, 0]. A number software systems have also been proposed to perform power control or *capping*.

Cluster level solutions which guarantee power consumption include those proposed by Wang et al. [100] and Raghavendra et al. [76]. These approaches require some node-level power capper and node-level systems have been developed to manage different individual components including DVFS for a processor (the Soft-DVFS approach in our evaluation) [54], per-core DVFS in a multicore [48], processor idle-time [32, 111], and DRAM [23].

Several researchers have noted that coordinating multiple components provides greater performance under a power cap than management of a single component in isolation [3, 36, 39, 59, 63, 72]. Thus, approaches have been proposed which provide power guarantees while increasing performance through coordinated management of multiple components, including processor and DRAM [13, 21, 22, 29, 57, 83], processors speed and core allocation [15, 79], combining DVFS and scheduling [77, 103], memory and disk speed [58] and combining DVFS and process placement [64]. The VirtualPower project coordinates power management, virtual machine placement, and server consolidation to meet power constraints in a virtualized data center [72]. Despite differences in mechanisms, these techniques all solve a common problem: select the highest performance set of resources that respect a given power limit. All of these projects found higher performance is available through the coordination of multiple resources. With these results, it is not surprising that a hardware solution alone would not achieve high efficiency for some applications.

We take the position that power management should not solely be the domain of hardware, but must be supported by both hardware and software coordinated through the operating system. The different resources required by different application workloads are simply too complicated for hardware to handle alone [26]. Hardware should be used to quickly enforce power limits, as hardware can simply act faster than software. Software techniques, however, should be used to determine the set of resources to activate that achieve the best performance under the power limit, considering the current workload. This paper has presented a general, decision-based approach for performing this coordination.

PUPiL complements other approaches which schedule applications to minimize energy [40, 65, 101, 112]. PUPiL determines what set of resources to activate, but it does not explicitly assign those resources to applications. Instead, it lets the underlying operating system scheduler perform that work. In this paper, that scheduler was simply the default Linux scheduler. It is likely that further performance gains could be achieved by coupling PUPiL with advanced energy-aware schedulers.

# 2.2 Motivational Example

| Processor    | Cores              | Sockets        | Speeds (GHz)   | TurboBoost |

|--------------|--------------------|----------------|----------------|------------|

| Xeon E5-2690 | 8                  | 2              | 1.2 - 2.9      | yes        |

| HyperThreads | Memory Controllers | Socket TDP (W) | Configurations |            |

| yes          | 2                  | 135            | 1024           |            |

Table 2.1: Server resources.

This example highlights the different tradeoffs in hardware and software power capping approaches and motivates the need for a hybrid design. We run the x264 video encoder on an Intel Linux/x86 system. We compare the timeliness and efficiency of both Intel's RAPL hardware and a software approach that can adjust many settings (presented in Chapter 2.3).

#### — RAPL - - - Soft — Decision

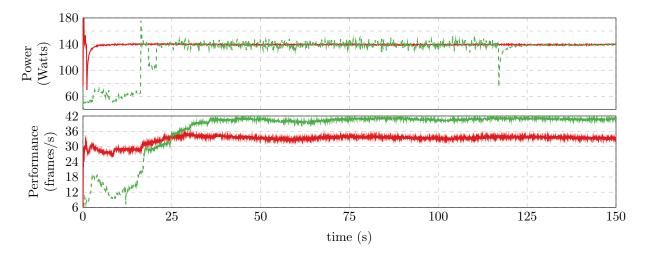

Figure 2.1: Tradeoff between timeliness and efficiency from hardware and software power capping, running x264.

Our test system is a dual-socket server with two Intel SandyBridge Xeon E5-2690 processors and 64GB of RAM. These processors support RAPL, but also have a number of configurable resources which affect power and performance tradeoffs, listed in Table 2.1. Each processor supports 15 frequency settings plus TurboBoost. Each is 8 cores, with hyperthreading, giving a total of 32 virtual cores across both sockets. These processors have a thermal design power (TDP) of 135 Watts, but experimentally we find it extremely rare for any workload to sustain that power consumption.

To illustrate the difference between hardware and software power capping, we set a 140 Watt power cap total for both sockets. RAPL must achieve this power consumption by driving each socket to 70 Watts (this is the optimal solution without thread migration, over which RAPL has no control). In contrast, the software approach configures a range of parameters: 1) how many sockets to use, 2) how many cores to use on each socket, 3) whether to use hyperthreads or not, 4) how many memory controllers to use, and 5) the frequency of each socket. For both the hardware and software approaches we measure power and performance (in frames encoded per second) as a function of time.

Figure 2.1 illustrates the results, with power shown in the top chart and performance shown on the bottom. Each chart shows time on the x-axis. The hardware approach is represented by the solid line, and the dashed line represents the software approach. Clearly, both approaches meet the power cap – RAPL hits the cap quickly while the software approach operates below the cap for approximately 20 seconds, briefly exceeds it, and finally settles at 140 Watts.

The performance results, however, show that once the software approach converges, it delivers 20% more performance than RAPL. Specifically, after convergence, the software approach averages approximately 41 frames per second while RAPL averages approximately 33.5 frames per second. Software outperforms hardware because it recognizes that hyperthreads do not help this application on this system. Using hyperthreads results in greater power consumption and a small performance loss. The software approach recognizes that it should not make use of hyperthreads and instead it increases the speed of the cores it is using without hyperthreads. Of course, it takes software a long time to recognize and adjust.

These results demonstrate the need for a hybrid approach that enforces power caps with hardware's speed, but has software's flexibility to adapt resource usage to the particular application (or applications) running on the system.

### 2.3 Power Capping Methodologies

This section introduces the different power capping approaches we explore in this paper. It first discusses our software approach. It then describes RAPL, a state-of-the-art hardware power capping system. Finally, it introduces *PUPiL*, a hybrid of software and hardware approaches.

We assume that a computer system is *configurable*; *i.e.*, it has resources or other parameters whose usage can be tuned to navigate performance/power tradeoffs. For each approach, the goal is to configure these resources to meet a power cap in a timely and efficient manner. Timeliness means the cap is quickly enforced. Efficiency means the system delivers maximum performance under the cap.

All three power capping approaches (software, hardware, and *PUPiL*) operate based on *feedback*. These approaches *observe* their environment, *decide* on a response, and *act* to implement their decisions. This feedback loop is repeated continually, allowing the power capping system to react to application phase changes or other environmental fluctuations. We use this *observe-decide-act* framework as a basis for understanding the methodologies of the three different power capping approaches addressed in this paper.

# 2.3.1 Software Power Capping

This section discusses how the software system implements observation, decision, and action.

#### Observe

In the observation phase, the software collects power and performance feedback.

Power feedback can come from any number of power monitoring mechanisms. For example, external power meters such as a WattsUp device can be used. Other alternatives include on-board power monitoring devices, such as the INA231 [46], or on-chip power monitoring, which is available commercially from Intel [16] and through research prototypes [88].

Performance feedback can also come from a number of sources. High-level performance feedback can come directly from appropriately instrumented applications [38]. It could also come from any number of other sources, including hardware counters that measure floating point computation rate or simply instructions per second [92, 96]. While the methodologies in this paper will work with any metric, the authors personally advocate the use of high-level application-specific feedback, if available as such allows a power capping system to ensure efficiency in terms of real application progress.

One issue with feedback is that real systems are noisy. To meet the efficiency challenge,

a power capping system should ensure that it is reacting to persistent phenomena and not some transient effect that momentarily disturbs performance. That is, the system should distinguish between a fundamental change in application workload and a temporary timing fluctuation (*e.g.*, due to a page fault). The power capper should adjust in the first case, but ignore the second case.

To address noise and ensure that the system acts on meaningful feedback, the software approach employs a deviation based filter to remove outliers. Specifically, the software approach measures performance over a window, filters any data that falls more than 3standard deviations from the mean, and averages the rest. Assuming, X is the list of performance measurements collected,  $\mu$  is the average of unfiltered X,  $\sigma$  is the standard deviation of unfiltered X, then  $X_{feedback}$  is the performance feedback used by the system to make decisions:

$$\mu = \frac{\sum_i X_i}{N} \tag{2.1}$$

$$\sigma = \sqrt{\frac{\sum_{i} \left(X^{i} - \mu^{2}\right)}{N}} \tag{2.2}$$

$$X_{feedback} = \frac{\sum_{j \in A} X_j}{size(A)}$$

(2.3)

$$A = \{ j \mid |X_j - \mu| < 3\sigma \}$$

(2.4)

### Decide

In the decide phase, the software selects a resource configuration. One way to select the best configuration would be to simply walk through all configurations until we find the highest performance configuration that respects the power cap. This approach has the twin drawbacks that it fails to meet the timeliness challenge and it may fail to respect the power cap. In general, the number of possible resource configurations will grow exponentially as we add more resources. Thus exhaustive search is simply not feasible.

Algorithm 1 Walking the decision framework.

| <b>Require:</b> Set of ordered resources $R$                     |                                                                      |

|------------------------------------------------------------------|----------------------------------------------------------------------|

| <b>Require:</b> Power cap $P$                                    |                                                                      |

| Put system in minimal resource configuration                     |                                                                      |

| $U \leftarrow R$                                                 | $\triangleright$ the set of untested resources                       |

| while $U \neq \emptyset$ do                                      | $\triangleright$ While untested resources                            |

| $\langle perf_{old}, pow_{old} \rangle \leftarrow GetFeedback()$ |                                                                      |

| $r \leftarrow RemoveNext(U)$                                     | $\triangleright$ next resource in order                              |

| set $r$ to highest setting                                       |                                                                      |

| wait $r.d$ time units                                            | $\triangleright$ Account for resource delay                          |

| $\langle perf_{cur}, pow_{cur} \rangle \leftarrow GetFeedback()$ |                                                                      |

| $\mathbf{if} \ perf_{cur} < perf_{old} \mathbf{then}$            |                                                                      |

| return $r$ to lowest setting                                     |                                                                      |

| else                                                             |                                                                      |

| $\mathbf{if} \ pow_{cur} > P \ \mathbf{then}$                    |                                                                      |

| $s \leftarrow BinarySearchResourceSettings(r)$                   |                                                                      |

| set $r$ to $s$                                                   |                                                                      |

|                                                                  | $\triangleright$ This may return the resource to its lowest setting. |

| end if                                                           |                                                                      |

| end if                                                           |                                                                      |

| end while                                                        |                                                                      |

Any software approach must find a more intelligent way to explore the configuration space. In this paper, we propose a novel *decision framework*. To begin, the system orders the available resources (the ordering process is described below). It then starts in the lowest resource configuration. Proceeding through resources in order, the approach puts the next resource into its highest setting. Feedback is measured in this new configuration. The software compares the performance feedback of the current configuration to that of last configuration to decide whether 1) performance has improved by using this new resource and 2) the resource usage respects the power cap. Algorithm 1 specifies the decision making process.

Algorithm 1 requires an ordered set of resources. The order is determined by Order() (detailed in Algorithm 2). The algorithm first sets the system to the smallest resource configuration. It then puts the resources into a set of untested resources. While this ordered set of untested resources is non-empty, the algorithm measures power and performance (using the helper function GetFeedback()). It then takes the next resource in order and sets it to its highest configuration setting (using the Set() helper function), waits a resource-specific

amount of time, and then measures the feedback again. If this resource provided higher performance, then the algorithm fine tunes the resource setting, otherwise it returns to the lowest setting for this resource. The fine tuning process involves performing a binary search on resource settings to find the highest performance setting that is under the power cap (the BinarySearchResourceSettings() helper function).

We use binary search on a resource-by-resource basis to avoid exhaustive search's overhead. This is an engineering tradeoff. Component-wise binary search is fast, but can get stuck in local extrema and miss the global optimal solution. In exchange, however, it scales well even as the number of configurable resources grows. In practice, this approach works well because resources tend to have a single peak. For example, not all applications can use all cores, but there tends to be a single best core count with no local extrema.

There are four helper functions for this approach. Three are straightforward and their detailed descriptions are omitted for space. We provide a brief overview here. The GetFeedback() function simply measures and returns power and performance data. The *Set*() function is used to configure the resource. The BinarySearchResourceSettings() function simply does a binary search on the available configurations for a resource. Its goal is to find the highest performance setting that respects the power cap. The ordering function is the fourth helper and it is described below.

The ordering function is essential to Algorithm 1. The software approach establishes the ordering based on the potential impact of each resource. Higher impact resources have precedence over lower impact resources. Algorithm 2 shows the algorithm used for establishing this order. The intuition is to allocate power first to higher impact resources so that we can tune the performance from coarse-grained knobs to fine-grained knobs. We evaluate impact of a resource by the performance improvement that it delivers when activated individually. The one exception is DVFS, which is used at the end to fine-tune power within the cap. To determine impact, we calibrate the system using a well-understood, embarrassingly parallel

| Algorithm 2 Ordering Resources | in | Calibration. |

|--------------------------------|----|--------------|

|--------------------------------|----|--------------|

| <u> </u>                                                                   |                                                  |

|----------------------------------------------------------------------------|--------------------------------------------------|

| <b>Require:</b> Set of resources $R$ excluding DVFS                        |                                                  |

| <b>Require:</b> a calibration benchmark without inter-thread communication |                                                  |

| Put system in minimal resource configuration                               |                                                  |

| $U \leftarrow R$                                                           | $\triangleright$ the set of disordered resources |

| $\mathbf{while} \ U \neq \emptyset \ \mathbf{do}$                          | $\triangleright$ While disordered resources      |

| $r \leftarrow RemoveNext(U)$                                               | $\triangleright$ next resource in random order   |

| set $r$ to highest setting                                                 |                                                  |

| wait $r.d$ time units                                                      | $\triangleright$ Account for resource delay      |

| $perf_r \leftarrow GetFeedback()$                                          |                                                  |

| return r to lowest setting                                                 |                                                  |

| add $r$ to $O$                                                             |                                                  |

| end while                                                                  |                                                  |

| Sort $r$ in $O$ by $perf_r$                                                |                                                  |

| Add DVFS to the last in $O$ return $O$                                     | $\triangleright$ The set of ordered resources    |

application. Based on our results, the ordering is insensitive to different applications; *i.e.*, the decision tree finds a near-optimal configuration using the same calibrated ordering for all applications. The detailed process for establishing the order is shown in Algorithm 2.

### Act

In the act phase, the software implements the resource allocation proposed by the decision phase. For example, if the decision phase decides to test a resource, the act phase is responsible for actually assigning that resource to the active applications. To implement the act phase, the software requires two pieces of external information. The first is a timing information about how long to expect from when the resource is allocated to when its effects can be observed. This information is required so that the software does not take a new observation before the resources have actually had an effect. The second piece of information is a function that implements the resource allocation. As most resources are allocated in system-specific ways, this function is necessary to maintain the generality of the approach and let it work on multiple systems.

Given this information, the action phase simply consists of setting the resource configuration to that specified by the decision phase and then putting the decision framework to sleep for the time it will take to see the resource effects. To increase efficiency, the software keeps track of the previous resource allocation and only changes those resource settings which changed since the last decision.

# 2.3.2 Hardware Power Capping

We briefly outline the approach taken by Intel's RAPL system [16], in terms of observation, decision, and action. RAPL receives a power cap and a time interval through a machine specific register (MSR). RAPL observes various low-level hardware events and estimates power consumption from those event counts. RAPL determines an energy budget that would meet the desired power cap during the specified time interval. For example, if the time interval is 0.5 seconds and the power cap is 100 Watts, the energy budget is 50 Joules.

RAPL sub-divides the user-specified time interval into a set of smaller intervals. For each of these fine-grained intervals, RAPL calculates the remaining energy budget for the remaining time in the user-specified interval and decides the best possible processor speed and voltage. Given this decision, RAPL sets DVFS to the decided state and waits for the next fine-grained interval. More detail on RAPL operation is available in the literature [16].

It is instructive at this point to compare the hardware and software approaches. Software is clearly flexible, the approach in Algorithm 1 will work with any set of available resources – the only requirement is that we must be able to establish an order on these resources. The drawback of software is that configuring the system requires executing Algorithm 1, which can be costly (as shown in Figure 2.1). In contrast, RAPL observes only power feedback (not performance), makes decisions by solving a linear equation, and acts by only tuning voltage and frequency only. All three steps can be done within milliseconds and this ensures the timeliness of hardware approach. However, because RAPL lacks performance feedback and considers only DVFS, this hardware approach cannot deliver the highest performance for many applications.

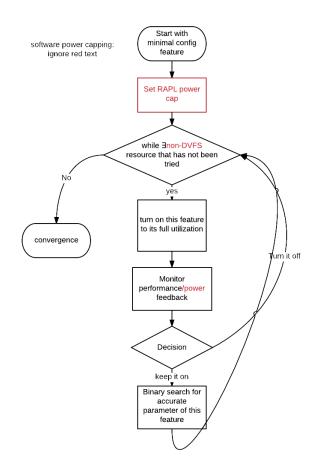

Figure 2.2: *PUPiL*'s approach to hybrid hardware/software power capping.

# 2.3.3 PUPiL's Hybrid Power Capping

Our goal is to obtain the efficiency of the software approach and the timeliness of hardware approach. Thus, we propose *PUPiL*, a hybrid power capping system that incorporates software and hardware to achieve the benefits of both.

# Timeliness

We need the system to respect the power cap as soon as the cap is set. To achieve this timeliness, hardware power capping approach has to be in charge of capping the power instead of the much slower control loop of software approach. Thus, we set the power cap in hardware first, before exploring other resources. Meanwhile, to avoid interference with the hardware approach, we remove processor speed and voltage from the set of resources controlled by software. Leaving hardware in charge of voltage and speed ensures timeliness and reduces the configuration space software much search.

Figure 2.2 illustrates *PUPiL*'s hybrid decision framework. The major difference between the software-only approach and Figure 2.2's is that the hybrid approach explicitly sets RAPL before exploring the configuration space determined by the non-DVFS resources. To achieve this in practice, we modify Algorithm 1 so that it first sets the RAPL power cap.

### Efficiency

We need to find the optimal configuration for the running application. This requires two modifications to the decision algorithm shown in Algorithm 1.

First, the power cap is now met by hardware so PUPiL need only manage performance. Thus, the hybrid approach excludes all the power condition checks in Algorithm 1 - PUPiL assumes RAPL ensures the power cap.

Second, power distribution among different chips in a multi-socket environment has to be reconsidered. Hardware power capping caps power on a per-socket manner. However, when we consider thread migration as a tunable parameter, the optimal configuration for an application or workload is often asymmetric, so it is necessary to distribute power accordingly instead of using a default even distribution. *PUPiL*, therefore, uses a core-number based power distribution across different chips. More specifically, *PUPiL* distributes the dynamic power (power cap minus static power) proportional to the core number being used by each chip. *PUPiL* achieves this by setting corresponding hardware power cap to each chip. Thus, whenever there is core number configuration adjustment, power distribution adjusts with it.

### 2.4 Experimental Setup

This section describes benchmarks, system, metrics, and points of comparison we use to evaluate *PUPiL*.

# 2.4.1 Benchmarks

We use 20 benchmark applications from three different suites including PARSEC (x264, swaptions, vips, fluidanimate, blackscholes, bodytrack) [7], Minebench (ScalParC, kmeans, HOP, PLSA, svmfe, btree, kmeans\_fuzzy) [71], and Rodinia (cfd, nn, lud, particle-filter)[11]. We also use a partial differential equation solver (jacobi) and the swish++ search web-server [41] and dijkstra [47]. These benchmarks test a range of important modern applications, both compute-intensive and memory-intensive. All applications run with up to 32 threads (the maximum supported in hardware on our test machine). In addition, all workloads are long running, taking at least 10 seconds to complete. This duration gives us plenty of time to take measurements of system performance and power.

# 2.4.2 Platform

We use a dual-socket Intel/Linux system with a SuperMICRO X9DRL-iF motherboard and two Xeon E5-2690 processors (see Table 2.1). This motherboard supports setting RAPL's power capping feature. The system runs Linux 3.2.0. We use the msr module, to access the model specific registers that implement RAPL. We use the cpufrequtils package to set the processor's clock speed. These processors have eight cores, fifteen DVFS settings (from 1.2 – 2.9 GHz), hyper-threading, and TurboBoost. In addition, each chip has its own memory controller, and we use the numact1 library to manage memory controller use. In total, the system supports 1024 user-accessible configurations, each with its own power/performance

#### Table 2.2: System configurations.

| Configuration    | Settings | Max Speedup | Max Powerup |

|------------------|----------|-------------|-------------|

| cores per socket | 8        | 7.9         | 2.1         |

| sockets          | 2        | 2.0         | 1.7         |

| hyperthreading   | 2        | 1.9         | 1.2         |

| mem controllers  | 2        | 1.8         | 1.1         |

| clock speeds     | 16       | 3.2         | 3.4         |

tradeoffs<sup>1</sup>. The thermal design power for these processors is 135 Watts.

Given those specifications, the following resources are configurable: the clock speed of each socket, core use per socket, hyperthreading, the number of sockets in use, and the number of memory controllers in use. Manipulating thread affinities allows us to change the cores per socket, the active sockets and the use of hyperthreading.

As described in Chapter 2.3, implementing the software decision system requires ordering the set of resources under consideration. Table 2.2 lists these resources in the order established by Algorithm 2. For each resource in the table, it lists the speedup and power up (increase in power, analogous to speedup) measured during the ordering process.

# 2.4.3 Evaluation Metrics

Our goal is to evaluate the timeliness and efficiency of various power capping approaches. To compare approaches, we must quantify these properties. We evaluate timeliness by measuring settling time. We evaluate efficiency by measuring the performance achieved by a workload under a power cap.

$<sup>1.\ 16</sup>$  cores, 2 hyperthreads, 2 memory controllers, and 16 speed settings (15 DVFS settings plus Turbo-Boost)

#### Timeliness

Settling time is a standard metric for a control system [35]. Given a power cap, it may take some amount of time for the controller to stabilize the system at that power. We call the period after which the system stabilizes the *steady state* and we denote the time at which the system enters steady state as  $t_{ss}$ . If the controller begins work at time  $t_0$ , then the settling time is simply:

$$settle = t_{ss} - t_0 \tag{2.5}$$

#### Efficiency

Efficiency is the performance delivered under a power cap. We evaluate efficiency using *weighted speedup*. This is a standard metric for multi-application workloads that weights the performance each application achieves in a multi-application scenario by the performance it would achieve in isolation. This metric has been demonstrated to be both consistent and fair [27].

## 2.4.4 Points of Comparison

To evaluate *PUPiL*, we compare it to several other techniques:

- **RAPL**: The primary approach with which we compare.

- Soft-DVFS: This is a software approach that sets the DVFS settings using the cpufrequtils package. Our implementation is modeled on a prior approach proposing a software-based DVFS control system [54].

- Soft-Modeling: This is a software approach that models the power for different configurations in an offline manner. That is, it uses multiple regression to estimate the power and performance of an application as a function of assigned resources (in this case, clockspeed, memory controllers, sockets, cores per socket and hyperthreads). This approach is an extreme case of a predictive model that needs no feedback information

at runtime.

- **Soft-Decision:** This is the software-only decision framework described in Chapter 2.3.1.

- **Optimal:** This is determined by running each application in every possible system configuration and measuring its performance. The optimal configuration achieves the best speed for a given power cap.

#### 2.5 Experimental Evaluation

This section evaluates *PUPiL*'s timeliness and efficiency. To enable others to perform similar evaluations, we have made the software and scripts used to perform this evaluation available online. We begin by evaluating single application workloads and then address multi-application workloads.

## 2.5.1 Single Application

To evaluate power control methods for single application workloads, we launch each application under a power cap and measure both its performance and settling time. We evaluate 5 different processor power caps: 60, 100, 140, 180, and 220 Watts. When setting the caps for both RAPL and Soft-DVFS, we split the power budget between both sockets evenly as this is the optimal allocation when no other resource is considered. Soft-Decision and *PUPiL* are free to divide the power cap among the sockets as they see fit when they migrate threads.