Aalborg Universitet

## Demonstration of 10 kV Silicon Carbide Power Semiconductor Technology in Medium Voltage Power Conversion

Dalal, Dipen Narendra

DOI (link to publication from Publisher): 10.54337/aau456353023

Publication date: 2021

Document Version Publisher's PDF, also known as Version of record

Link to publication from Aalborg University

Citation for published version (APA):

Dalal, D. N. (2021). Demonstration of 10 kV Silicon Carbide Power Semiconductor Technology in Medium Voltage Power Conversion. Aalborg Universitetsforlag. Ph.d.-serien for Det Ingeniør- og Naturvidenskabelige Fakultet, Aalborg Universitet https://doi.org/10.54337/aau456353023

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

Take down policy If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

## DEMONSTRATION OF 10 KV SILICON CARBIDE POWER SEMICONDUCTOR TECHNOLOGY IN MEDIUM VOLTAGE POWER CONVERSION

BY DIPEN NARENDRA DALAL

**DISSERTATION SUBMITTED 2021**

AALBORG UNIVERSITY DENMARK

Demonstration of 10 kV Silicon Carbide Power Semiconductor Technology in Medium Voltage Power Conversion

Ph.D. Thesis Dipen Narendra Dalal

Thesis submitted October 2021

| Dissertation submitted:    | October, 2021                                                                               |

|----------------------------|---------------------------------------------------------------------------------------------|

| PhD supervisor:            | Prof. Stig Munk-Nielsen<br>Aalborg University                                               |

| Assistant PhD supervisors: | Assoc. Prof. Christian Uhrenfeldt<br>Aalborg University                                     |

|                            | Assoc. Prof. Szymon Beczkowski<br>Aalborg University                                        |

|                            | Assoc. Prof. Michael Møller Bech<br>Aalborg University                                      |

| PhD committee:             | Associate Professor Pooya Davari (chair)<br>Aalborg University                              |

|                            | Professor Hans-Peter Nee<br>KTH Royal Institute of Technology                               |

|                            | Associate Professor Dimosthenis Peftitsis<br>Norwegian University of Science and Technology |

| PhD Series:                | Faculty of Engineering and Science, Aalborg University                                      |

| Department:                | Department of Energy Technology                                                             |

| ISSN (online): 2446-1636   |                                                                                             |

ISBN (online): 978-87-7573-998-1

Published by: Aalborg University Press Kroghstræde 3 DK – 9220 Aalborg Ø Phone: +45 99407140 aauf@forlag.aau.dk forlag.aau.dk

© Copyright: Dipen Narendra Dalal The thesis is typeset using  $IAT_EX 2_{\mathcal{E}}$

Printed in Denmark by Rosendahls, 2021

To my parents...

## Abstract

In present-day electricity networks, power electronics is widely employed or one can say "omnipresent" as an enabling technology for the conversion and control of electric power at generation, transmission, distribution and consumer end. At the consumer end, industrial sector constitutes the single largest share in the global electric energy consumption. A significant portion of electric energy in the industrial sector is consumed by medium voltage motor drive systems, that often utilize high power (375 kW – 10,000 kW), medium voltage (1 kV – 10 kV) power electronic converters. At the distribution end, high power medium voltage converters are used for grid support functionalities. At generation end, penetration of renewable energy sources such as photovoltaics and wind with their increasing power generation capabilities, demand for medium voltage power electronics which can offer potential benefits in terms of system level efficiency gains and reduced levelized cost of energy production.

Power semiconductor devices constitute the key building block of modern power electronic converters. Commercial high power medium voltage converters utilize Silicon (Si) based power semiconductor devices, which has evolved as a mature technology and dominated power electronics industry for the past years. With Si based power semiconductor devices reaching their theoretical limits of performance, newly emerging Silicon Carbide (SiC) based wide band gap (WBG) devices are foreseen as a likely alternative to Si based devices. The SiC based power semiconductor devices, with their smaller size, high blocking voltage capability, faster switching speed and high temperature withstand capability offer significant benefits to power electronic converters in terms of simplification of power converter topology with increased efficiency and power density.

This PhD thesis demonstrates 10 kV SiC power semiconductor devices in medium voltage power conversion applications. The high rate of change of voltage (dv/dt) in case of SiC Metal Oxide Field Effect Transistor (MOSFET) due to the medium voltage levels and fast switching transient requires careful consideration of electrical parasitics. Especially parasitic capacitive couplings to limit the displacement currents during the switching transients that can adversely impact electromagnetic interference and compatibility as well as switching performance for the power electronic converter. In particular, parasitic capacitive couplings within the power modules, as well as external interfacing circuits such as gate drivers and passive components. The PhD thesis begins with introducing state of the art and 10 kV half-bridge SiC MOSFET power modules utilised in this research work. Thereafter, a gate driver with high voltage isolation and a very low coupling capacitance (< 3 pF) is presented. The main contribution of the PhD thesis lays in investigating the power module parasitic capacitance induced displacement current path and its impact on the switching energy dissipation. By solving scientific challenges and implementing mitigation techniques, to lessen the impact of high dv/dt induced displacement currents on the half-bridge power module and circuits interfacing power modules, a 50 kVA, 4.16 kV rated medium voltage power stack demonstrator is designed. built and experimentally validated close to its intended operating condition. For designed medium voltage power stack, efficiency higher than 99% is inferred from the converter measurements in a DC fed three phase back-to-back regenerative test setup. The PhD thesis concludes by summarizing the research and the contemplated future work.

## Dansk resumé

Effektelektronik er brugt i vid udstrækning i det moderne elektriske system. Man kan endda sige det er en allestedsnærværende teknologi der muliggør omdannelse og kontrol af elektrisk energi ved produktion, transmission, distribution og slutbrug. Ved slutbrug står den industrielle sektor for den største del af det globale elektriske energiforbrug. En betydelig del af elektrisk energi brugt i den industrielle sektor er brugt i mellemspændings motordrev systemer, på høj effekt (375 kW – 10,000 kW), mellemspændings (1 kV – 10 kV) effektelektronik konvertere. På distributionssiden bruger man højeffekts effektelektronik mellemspændings konvertere til elektrisk net støttefunktioner. På produktionssiden er der efterspørgsel på mellemspændings effektelektronik på grund af forøgelsen af vedvarende energi så som solceller og vind turbiner da det har potentielle fordele ved øget effektivitet på system-niveau og kan reducere "levelized cost of energy" for disse energi-kilder. Halvleder komponenter til effektelektronik udgør en central byggesten af moderne effektelektronik konverterer. I dag er kommercielle højeffekts mellemspændings konverterer baseret på silicium (Si) halvleder komponenter som har udviklet sig til en moden teknologi og har domineret effektelektronik industrien i mange år. Da halvleder komponenter baseret på silicium har nået deres teoretiske grænse for vdeevne spås det at de relativt nyligt fremkomne siliciumkarbid (SiC) baseret, "wide band gap" (WBG), komponenter vil være et fremtidigt alternativ til Si-baseret komponenter. SiC-baserede komponenter giver signifikante fordele til effektelektronik konvertere da de kan simplificere konverter topologi og samtidigt øge effektiviteten og effekttætheden. Dette kan de på grund af deres mindre størrelse, højere spændingsblokeringsevne, hurtigere skiftehastighed og evne til at modstå høje temperaturer. Dette PhD speciale vil demonstrere brugen af 10 kV SiC effektelektronik komponenter i mellemspændings effektelektronik. Den hurtige spændingsændring (dv/dt) som kommer fra kombinationen af mellemspænding og hurtig skiftehastighed i en SiC "Metal Oxide Field Effect Transistor" (MOSFET) kræver nøje betragtning af elektriske parasitter. Især parasitisk kapacitans koblinger kan negativt påvirke elektrisk interferens og kompatibilitet men også influere skifte-transienterne i en effektelektronik konverter. Særligt parasitisk kapacitans koblinger fra effekt-moduler er vigtige, såvel som eksterne

kredsløb så som "gate-drivers" og passive komponenter. Dette PhD speciale begynder med en introduktion af "State of the art" og 10 kV SiC MOSFET effekt-moduler som er brugt i dette speciale. Derefter vil der blive præsenteret en "gate-driver" med høj spændingsisoleringsevne og meget lav koblings-kapacitans (< 3 pF). Hovedbidraget af dette PhD speciale ligger i en undersøgelse af de strømme som opstår fra effekt-modulers parasitiske kapacitanser og deres påvirkning af energien brugt på at tænde og slukke halvleder-komponenterne i effekt-modulerne. Ved at løse diverse videnskabelige udfordringer og implementere mitigeringsstrategier for at minimere høje dv/dt inducerede strømme på effekt-modulerne og deres kredsløb er det lykkedes at designe og bygge et 50 kVA, 4.16 kV mellemspændings effekt-modul demonstrator som er eksperimentelt valideret tæt på dets tiltænkte driftstilstand. Fra konverter målinger kan det udledes at den designede mellemspændings effekt har en effektivitet på mere end 99% i en jævnstrømsinjiceret 3-fase "back-to-back" regenerativ test opstilling. Dette PhD speciale vil ende med en opsummering af forskningen udført og kommer med overvejelser om fremtidigt arbejde.

## Contents

| A        | bstra                    | $\operatorname{ct}$                                                           | $\mathbf{v}$ |

|----------|--------------------------|-------------------------------------------------------------------------------|--------------|

| D        | ansk                     | resumé                                                                        | vii          |

| P        | reface                   | e                                                                             | xiii         |

| I        | $\mathbf{E}\mathbf{x}$   | tended summary                                                                | 1            |

| 1        | Intr                     | oduction                                                                      | 3            |

|          | 1.1                      | Background and motivation                                                     | 3            |

|          | 1.2                      | State of the art                                                              | 6            |

|          | 1.3                      | Thesis hypotheses and objectives                                              | 9            |

|          |                          | 1.3.1 Thesis hypotheses $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 9            |

|          |                          | 1.3.2 Thesis objectives                                                       | 10           |

|          | 1.4                      | Thesis outline and contributions $\ldots \ldots \ldots \ldots \ldots \ldots$  | 10           |

|          | 1.5                      | List of publications                                                          | 11           |

| <b>2</b> | $\mathbf{SiC}$           | MOSFET power modules                                                          | 15           |

|          | 2.1                      | Introduction                                                                  | 15           |

|          | 2.2                      | 10 kV half-bridge SiC MOSFET power modules                                    | 15           |

|          | 2.3                      | Static characterisation of 10 kV SiC MOSFET and JBS diode .                   | 17           |

|          | 2.4                      | Summary                                                                       | 19           |

| 3        | $\operatorname{Gal}^{1}$ | vanically isolated low-isolation capacitance gate driver                      | <b>21</b>    |

|          | 3.1                      | Introduction                                                                  | 21           |

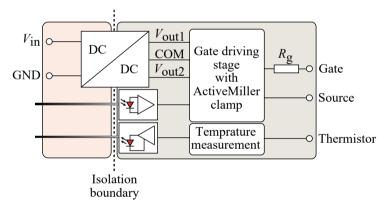

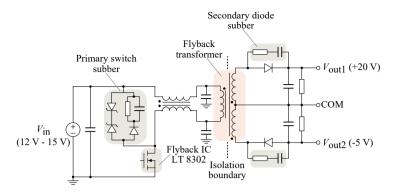

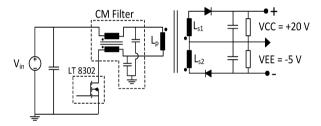

|          | 3.2                      | DC-DC isolated power supply                                                   | 26           |

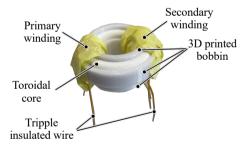

|          |                          | 3.2.1 Transformer design                                                      | 27           |

|          | 3.3                      | Gate driving stage                                                            | 30           |

|          | 3.4                      | Experimental validation                                                       | 31           |

|          | 3.5                      | Summary                                                                       | 33           |

#### Contents

| <b>4</b>                                               | Dynamic switching characterisation of SiC MOSFET power            |         |                                                             |           |  |  |

|--------------------------------------------------------|-------------------------------------------------------------------|---------|-------------------------------------------------------------|-----------|--|--|

|                                                        | mod                                                               | dules   |                                                             | <b>35</b> |  |  |

|                                                        | 4.1                                                               | Intro   | luction                                                     | 35        |  |  |

|                                                        | 4.2 Impact of power module parasitic capacitances on the SiC MOS- |         |                                                             |           |  |  |

|                                                        |                                                                   | FET     | switching transients                                        | 36        |  |  |

|                                                        |                                                                   | 4.2.1   | Device under test                                           | 36        |  |  |

|                                                        |                                                                   | 4.2.2   | Impedance network between the power module and heatsink     | 38        |  |  |

|                                                        |                                                                   | 4.2.3   | Experimental test bench                                     | 39        |  |  |

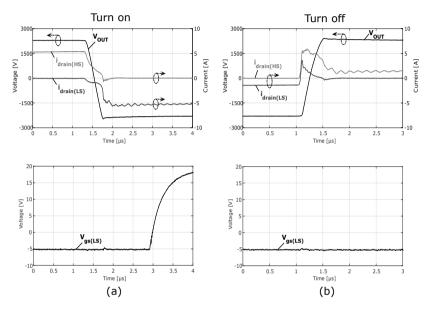

|                                                        |                                                                   | 4.2.4   | Analysis of SiC MOSFET turn-on and turn-off switching       |           |  |  |

|                                                        |                                                                   |         | transients                                                  | 41        |  |  |

|                                                        |                                                                   | 4.2.5   | Discussion on an indirect measurement method utilized       |           |  |  |

|                                                        |                                                                   |         | to obtain the power module parasitic capacitance related    |           |  |  |

|                                                        |                                                                   |         | displacement current                                        | 44        |  |  |

|                                                        |                                                                   | 4.2.6   | Analysis of power module parasitic capacitance impact       |           |  |  |

|                                                        |                                                                   |         | on the turn-on and turn-off switching energy dissipation    | 47        |  |  |

| 4.3 Assessment on the impact of SiC JBS diode on SiC M |                                                                   |         |                                                             |           |  |  |

|                                                        |                                                                   | switch  | ning transient                                              | 54        |  |  |

|                                                        |                                                                   | 4.3.1   | Device under test                                           | 54        |  |  |

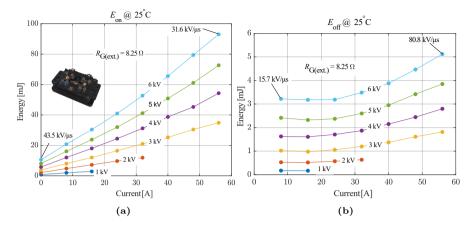

|                                                        |                                                                   | 4.3.2   | Analysis of turn-on and turn-off switching energy dis-      |           |  |  |

|                                                        |                                                                   |         | sipation for power module with and without SiC JBS          |           |  |  |

|                                                        |                                                                   |         | diode                                                       | 54        |  |  |

|                                                        | 4.4                                                               | Impac   | ct of power module design change in terms of reduced module |           |  |  |

|                                                        |                                                                   |         | itance and elimination of SiC JBS diode                     | 62        |  |  |

|                                                        | 4.5                                                               | Sumn    | nary                                                        | 64        |  |  |

|                                                        |                                                                   |         | ·                                                           |           |  |  |

| <b>5</b>                                               |                                                                   |         | C MOSFET enabled medium voltage power stack                 | 65        |  |  |

|                                                        | 5.1                                                               |         | duction                                                     | 65        |  |  |

|                                                        | 5.2                                                               |         | logy and system specification                               | 66        |  |  |

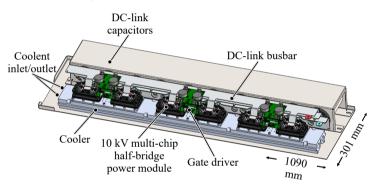

|                                                        | 5.3                                                               | MV p    | ower stack assembly                                         | 67        |  |  |

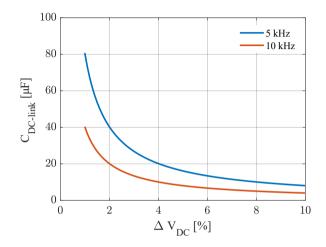

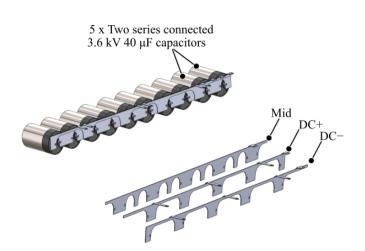

|                                                        |                                                                   | 5.3.1   | DC-link and busbar design                                   | 67        |  |  |

|                                                        |                                                                   | 5.3.2   | Thermal management                                          | 70        |  |  |

|                                                        | 5.4                                                               |         | rimental setup and results                                  | 75        |  |  |

|                                                        | 5.5                                                               | Sumn    | nary                                                        | 78        |  |  |

| 6                                                      | Con                                                               | nclusio | on: Summary and future work                                 | 81        |  |  |

|                                                        | 6.1                                                               |         | nary and main contributions                                 | 81        |  |  |

|                                                        | 6.2                                                               | Futur   | e work                                                      | 83        |  |  |

|                                                        | Refe                                                              | erences |                                                             | 86        |  |  |

99

## II Appended papers

| A |      | e driver with high common mode rejection and self turn-or                                                            |      |

|---|------|----------------------------------------------------------------------------------------------------------------------|------|

|   |      | igation for a 10 kV SiC MOSFET enabled MV converter                                                                  | 101  |

|   | A.1  | Introduction                                                                                                         | 103  |

|   |      | <ul><li>A.1.1 Transformer design</li></ul>                                                                           | 106  |

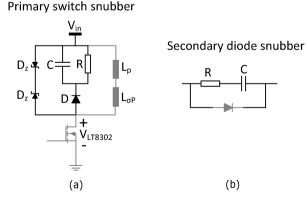

|   | 1.0  | secondary snubber                                                                                                    | 107  |

|   | A.2  | Design of a gate driving stage with active Miller clamp functionality                                                |      |

|   | A.3  | Device under test                                                                                                    | 109  |

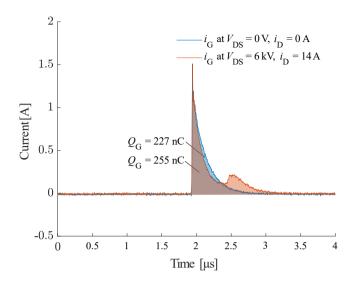

|   |      | <ul><li>A.3.1 Continuous switching operation</li></ul>                                                               | 111  |

|   |      | transition                                                                                                           | 112  |

|   |      | Conclusion                                                                                                           | 115  |

|   | Refe | rences                                                                                                               | 115  |

| в |      | oact of Power Module Parasitic Capacitances on Medium                                                                | n    |

|   | Volt | age SiC MOSFETs Switching Transients                                                                                 | 119  |

|   | B.1  | Introduction                                                                                                         | 121  |

|   | B.2  | Device under test - 10 kV half bridge SiC MOSFET power modul                                                         | e123 |

|   |      | B.2.1 Equivalent impedance network between power module                                                              |      |

|   |      | and the heatsink                                                                                                     | 126  |

|   | B.3  | Experimental test bench                                                                                              | 127  |

|   | B.4  | Understanding Impact of power module parasitic capacitance                                                           |      |

|   |      | on MOSFET turn-on and turn-off switching transients based on                                                         |      |

|   |      | experimental results                                                                                                 | 129  |

|   |      | B.4.1 Analysis for the turn-on switching transient                                                                   | 129  |

|   | B.5  | B.4.2 Analysis for the turn-off switching transient Indirect methodology utilized to obtain module parasitic capaci- | 131  |

|   | B.6  | tance related displacement currents                                                                                  | 132  |

|   |      | turn-on switching energy dissipation                                                                                 | 137  |

|   | B.7  | Analysis of module parasitic capacitance impact on turn-off<br>switching energy dissipation                          | 144  |

|   | B.8  | Conclusion                                                                                                           | 146  |

|   | Refe | rences                                                                                                               | 147  |

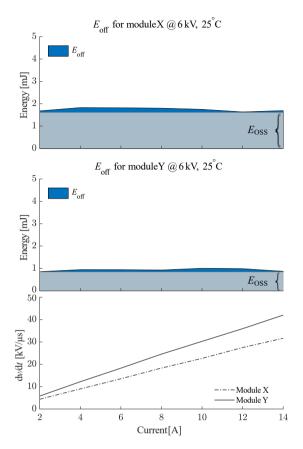

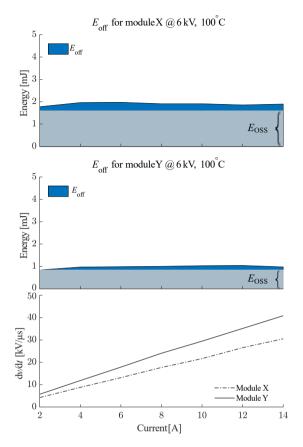

| С |      | tching Performance Assessment of 10 kV Half-Bridge Si<br>SFET Power Modules With and Without Anti-Parallel Si        |      |

|   |      | Diode                                                                                                                | 151  |

|   | C.1  | Introduction                                                                                                         | 153  |

|   | C.2  | Device under test - 10 kV half-bridge SiC MOSFET power modul                                                         |      |

|   | C.3  | Experimental test setup                                                                                              |      |

#### Contents

|                                     | C.4                                                  | .4 Impact of the anti-parallel SiC JBS diode on the SiC MOSFET           |              |  |  |

|-------------------------------------|------------------------------------------------------|--------------------------------------------------------------------------|--------------|--|--|

|                                     |                                                      | switching transient                                                      | 158          |  |  |

|                                     |                                                      | C.4.1 Analysis of the turn-on switching transient                        | 159          |  |  |

|                                     |                                                      | C.4.2 Analysis of the turn-off switching transient                       | 162          |  |  |

|                                     | C.5                                                  | Comparison of the switching energy dissipation for the module            |              |  |  |

|                                     |                                                      | with and without anti-parallel SiC JBS diode                             | 164          |  |  |

|                                     |                                                      | C.5.1 Analysis of the turn-on switching energy dissipation               | 164          |  |  |

|                                     |                                                      | C.5.2 Analysis of the turn-off switching energy dissipation $\therefore$ | 171          |  |  |

|                                     | C.6                                                  | Conclusion                                                               | 173          |  |  |

| D                                   | D Demonstration of a 10 kV SiC MOSFET based Medium V |                                                                          |              |  |  |

|                                     | age                                                  | Power Stack                                                              | 175          |  |  |

|                                     | D.1                                                  | Introduction                                                             | 177          |  |  |

|                                     | D.2                                                  | Medium voltage power stack                                               | 178          |  |  |

|                                     |                                                      | D.2.1 Half bridge 10 kV SiC MOSFET power module                          | 178          |  |  |

|                                     |                                                      | D.2.2 Isolated power supply and gate driver                              | 179          |  |  |

|                                     |                                                      | D.2.3 DC-link and busbar design                                          | 180          |  |  |

|                                     |                                                      | D.2.4 Thermal management                                                 | 182          |  |  |

|                                     |                                                      | D.2.5 Power stack assembly                                               | 183          |  |  |

|                                     | D.3                                                  | Experimental results                                                     | 184          |  |  |

|                                     |                                                      | D.3.1 On-sate and switching characteristics of the half bridge           |              |  |  |

|                                     |                                                      | 10 kV SiC MOSFET power module                                            | 184          |  |  |

|                                     |                                                      | D.3.2 Experimental setup and test results                                | 186          |  |  |

|                                     |                                                      | Conclusion                                                               | 188          |  |  |

|                                     | Refe                                                 | rences                                                                   | 189          |  |  |

| $\mathbf{E}$                        |                                                      | ti-chip Medium Voltage SiC MOSFET Power Module with                      | h            |  |  |

| Focus on Low Parasitic Capacitance. |                                                      |                                                                          | 193          |  |  |

|                                     | E.1                                                  | Introduction                                                             | 195          |  |  |

|                                     | E.2                                                  | Medium Voltage Design Considerations                                     | 196          |  |  |

|                                     | E.3                                                  | Design of 10 kV, 80 A SiC MOSFET Power Module $\ \ldots \ \ldots$ .      | 197          |  |  |

|                                     | E.4                                                  | Parasitics and Simulation                                                | 200          |  |  |

|                                     | E.5                                                  | Double Pulse Setup                                                       | 201          |  |  |

|                                     | E.6                                                  | Experimental Results and discussion                                      | 201          |  |  |

|                                     | E.7                                                  | Conclusion                                                               | $206 \\ 207$ |  |  |

|                                     | References                                           |                                                                          |              |  |  |

## Preface

As I am writing this dissertation towards the fulfillment of Doctor of Philosophy degree, I would like to express my sincere appreciation to the individuals who have made important contributions in my professional and personal development to grow as an independent researcher and a better human being.

I would like to express my utmost appreciation to Prof. Stig Munk-Nielsen for giving me the opportunity to work within the field of medium voltage Wide Band Gap power semiconductor devices and their applications. His enthusiasm for research, optimism and expertise within the field of power electronics has been a source of inspiration for me. I would like to thank him for his constant availability and many technical as well as professional guidance during my PhD, more importantly for introducing me to this exciting field of research during my Master's studies at Aalborg University, which culminated my interest in continuing further research.

At the same time, my sincere appreciation goes to my co-supervisors; Assoc. Prof. Christian Uhrenfeldt for his constant encouragement, constructive feedback on my research work and sharing his broad knowledge within the area of power semiconductor devices and its packaging, Assoc. Prof. Szymon Bęczkowski for stimulating creative technical ideas and providing technical guidance that helped solve practical challenges in my experimental laboratory work, Assoc. Prof. Michael Møller Bech for his technical advice with CPLD programming and implementation of control and protection circuit for medium voltage power stack.

Also, my acknowledgements to Prof. Hans-Peter Nee, Assoc. Prof. Dimosthenis Peftisis and Assoc. Prof. Pooya Davari for accepting to be a member of the assessment committee and taking their time to read my PhD thesis.

Furthermore, I would like to acknowledge Department of Energy Technology, Innovation Fund Denmark, KK Wind Solutions, Siemens Gamesa Renewable Energy and Vestas Wind Systems that co-funded MV-BASIC (Medium Voltage Converters Based on SiC) / MVolt (Medium voltage Power Electronics for Wind Systems) research projects, through which this PhD project has been supported.

I would like to thank my colleagues, office mates and fellow MVolt / MV-BASIC members Nicklas Christensen, Jannick Kjær Jørgensen, Hognbo Zhao,

#### Preface

Asger Bjørn Jørgensen and Thore Stig Aunsburg for their contributions in offering learnings with their diverse technical skill sets, inspiring technical discussions, research collaborations, help in laboratory and creating an enjoyable research environment throughout this journey. I would also like to thank Faheem Ahmed for his good company in the Power Electronics Laboratory and willingness in participating technical discussions. I am thankful to my friend Harsh Parikh for the good time, from the very first day I arrived in Denmark.

Furthermore, I would like to acknowledge Dr. Bjørn Rannestad from KK Wind Solutions and Assoc. Prof. Cristian Vasile Lascu for their valuable technical inputs through our weekly project co-ordination meetings.

My special thanks to Jan Christensen as well as staff members at Aalborg University workshop for manufacturing of hardware assemblies and Walter Neumar for his help with procurement of electronic components. Same goes for, Bonnie Steffensen, Corina Busk Gregersen and Mette Lindrup Skov Jensen for their help and time in making the process smooth with all the administrative work and procurement of laboratory equipments.

Many thanks to my friends back at home in India, in Aalborg and abroad. Finally, I would like to acknowledge my family, parent in-law, sister in-law and relatives for their support and blessings. I would like to express my deepest gratitude to my father Narendra Dalal for his constant support, motivation and offering me an industrial exposure at an early age of my life that introduced me to the field of power electronics, my mother Asha Dalal and sister Vibha for their endless love and care. Most importantly, my wife Hardi Gosalia for her unconditional love, constant support and for sharing with me a beautiful journey called life.

> Aalborg, September 2021 Dipen Narendra Dalal

## Part I

# **Extended summary**

## Chapter 1

## Introduction

## 1.1 Background and motivation

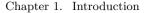

The electric energy consumption of the world reached 22,847 TWh in 2019, out of which 41.9 % of the total consumed electric energy accounts for the industrial sector [1]. To meet the growing demand electric energy production has accelerated over the past few years. The global push towards green energy transition to tackle the climate change and economies of scale has lead to a rapid deployment of renewable energy sources, in particular wind and solar, increasing their share to almost 7.8 % in the 26,936 TWh global electric energy production in 2019 [1]. Global electric energy consumption and electricity generation by different sources over the years 2010 – 2018 is presented in Fig. 1.1. Along with the decarbonization of electric energy sources, significant improvements in energy efficiency by means of implementation of the available technology is necessary [2]. In present-day electricity network, power electronics is utilized at power generation, transmission, distribution and consumer end as the enabling technology for the conversion and control of power. At the consumer end, electric motor drive systems hold the single largest share, accounting for 43 % -50 % of the global electric energy consumption [4]. Of these, high power (375 kW -10,000 kW) medium voltage (MV) (1 kV -10 kV) drive systems constitute the smallest portion of total electric drive systems in terms of number of installations. However, medium voltage drive systems are of great interest from the energy efficiency point of view due to their enormous energy consumption [4]. In 2019. European Union (EU) Commission laid down regulation 2019/178 for energy efficiency eco-design requirements for motors and variable speed drive systems with rated power of 0.12 kW - 1000 kW and voltages up to 1 kV with an aim to reduce 10 TWh of energy savings in EU that corresponds to 2030 goal of 3 Mt equivalent of annual  $CO_2$  emission reduction [5]. The Silicon Carbide (SiC) Metal Oxide Semiconductor Field Effect Transistor (MOSFET) technology is

**Fig. 1.1:** (a) Electricity consumption by sector and (b) electric energy production by sources during the years 2010 – 2018. Source: [1], [3]

classified as the best available technology for the energy efficiency improvements by means of reducing the semiconductor losses in the variable speed drive systems compared to an existing solution [5]. Electric motors and variable speed drive systems with voltages above 1 kV are relevant but have been excluded for the time being as no classification exists for the energy efficiency of motors for this voltage class [5].

At the generation end, high power MV power electronic converters are finding its application in the wind industry, as the increasing turbine power levels in range of tens of megawatts exemplify requirements for the MV generators. Since adapting MV solutions at increased power levels can provide benefits in terms of reduced ohmic losses and levelized cost of energy (LCoE) [6]. Recently announced offshore wind turbine Haliade - X from General Electric Renewable Energy utilizes 12 MW - 13 MW, 3.3 kV synchronous generator with PCS 6000 MV power electronic converter from ABB [7]–[9].

Another application of the high power MV converter is found for grid support functionalities. An emerging application and widely discussed alternative to the low frequency transformer, the solid state transformer (SST) utilizes the power electronics converter with medium frequency transformer for direct interfacing of the MV and low voltage (LV) grid [10]. Solid state transformers have been proposed for variety of applications such as traction, data center power supplies, MV high power electric vehicle (EV) battery chargers and interconnection of renewable energy sources to the distribution grid [11].

In 2011 SiC MOSFETs in 1.2 kV - 1.7 kV voltage class were first introduced commercially, since then there has been significant improvements in SiC MOSFET technology in terms of lower on-state resistance, increase in wafer diameters and improved reliability [12]–[14]. In recent years, SiC MOSFETs in 3.3 kV, 6.5 kV and 10 kV voltage class have been demonstrated by Wolfspeed and are available as an engineering sample [15], [16]. SiC MOSFETs in 3.3 kV – 15 kV voltage class have gained significant interest from industry and academia for a broad range of applications including active filters for MV distribution grids [17], motor drives [18], [19], shore-to-ship power supply [20], renewable energy [21] and SST based applications i.e, MV connected distribution systems [22]–[24], data center power supply [25], grid support [26], EV fast charger [27], railway traction drives [28] and high-voltage direct current transmission [29].

Considering the high power MV converters rated for 4.16 kV - 7.2 kV line-line voltages, MV SiC MOSFETs in 10 kV voltage class are of particular interest as an alternative to Silicon (Si) power semiconductor based solution, since higher blocking voltage capability, relatively low on-state resistance, smaller device capacitance and higher thermal conductivity of SiC MOSFET offer numerous benefits [30], [31], such as: simplification of the power converter topology and control complexity by eliminating the need of series connection of semiconductor devices and multi-level converter topologies. Thereby reduced component count, lower switching losses, increased power density and efficiency [16]. At present, the cost of MV SiC MOSFETs is significantly higher than their Si counterparts, however SiC MOSFET due to its technological benefits is seen as the enabling technology for EV drive trains [32]. Lately, the EV market is experiencing a rapid growth as a result of the global push for environment friendly policies in terms of  $CO_2$  emission standards [33]. With higher penetration of the SiC MOSFETs in EV drive trains as well as charging infrastructure and success in fabrication of the relatively large diameter (150 mm - 200 mm) SiC wafer is expected to bring down the cost of these devices [32], [34]. As a possible alternative to the Si based power semiconductor technology, SiC semiconductor devices exhibit potential to push the limits of attainable power density, efficiency and thermal performance.

With superior performance characteristics of MV SiC power semiconductor

technology comes new challenges in terms of utilizing these power semiconductor devices in practical applications. The medium voltage levels and the fast switching characteristics of MV SiC devices introduce new design challenges with regards to their application in power electronic converter as it imposes different design considerations in terms of electrical parasitics for the power module, interfacing auxiliary circuits and passive components when compared to their Si counterparts. The PhD thesis aims to unfold these key electrical parasitics and their impact on utilizing MV SiC MOSFETs in 10 kV voltage class for its intended use in MV high power conversion applications.

## 1.2 State of the art

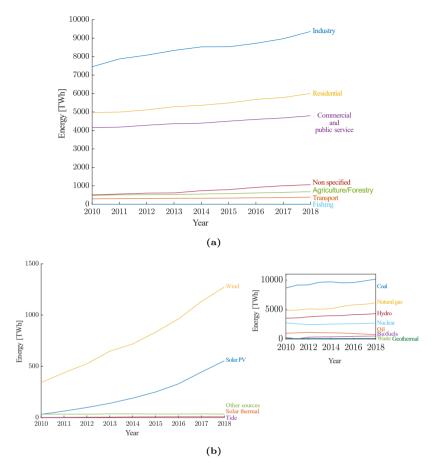

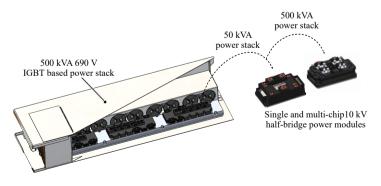

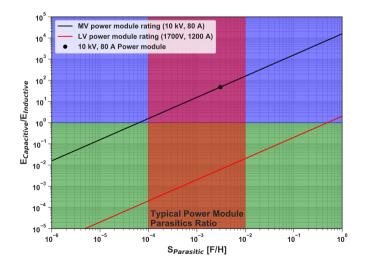

Generally, power electronic converters rated at high power utilize MV in comparison to the LV as it offers benefits in terms of lower ohmic i<sup>2</sup>R losses for similarly rated power level. Currently, the peak blocking voltage capability of the commercially available modern power semiconductor devices is limited up to 6.5 kV. The choice of power semiconductor devices in this voltage class is primarily dominated by Si based bipolar devices such as: insulated-gate bipolar transistor (IGBT) [35]–[38], injection enhanced gate transistor (IEGT) [39], integrated-gate commutated thyristor (IGCT) [40], symmetric gate-controlled thyristor (SGCT) [41] and gate turn-off thyristor (GTO) [41]–[43] for the power converters utilizing voltage source converter (VSC) topology and thyristors or phase controlled thyristor (PCT) for current source converter (CSC) topology. Commercially available MV Si and recently announced noncommercial SiC based wire bonded or press pack power modules from major manufacturers in 3.3 kV or higher voltage class are presented in Fig. 1.2a, based on their maximum Volt Ampere (VA) ratings in their respective voltage class [28], [35]–[40], [44], [45].

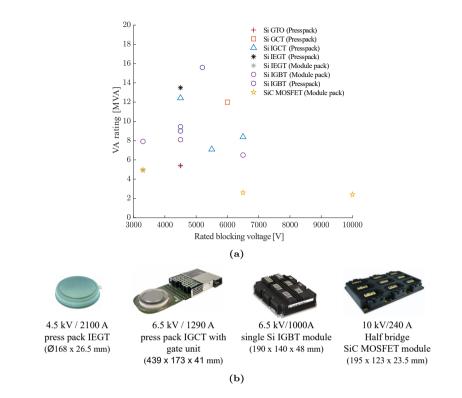

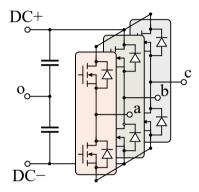

The high power MV power electronic converters can be broadly classified into current source and voltage source topologies as presented in Fig. 1.3. The VSCs have become dominant in the high power MV applications up to few tens of MW, due to their versatility, continuous development of power semiconductor technology and ease of integration. Commercial high power MV converters cover wide power range from a few hundreds of kilowatts to tens of megawatts with rated line-line output voltage between 1.2 kV to 13.8 kV with most common voltage ratings being: 2.4 kV, 3.3 kV, 4 kV, 4.16 kV, 6 kV, 6.6 kV, 10 kV, 11 kV or 13.8 kV [46], [47]. To attain improved power quality with lower filtering requirements at medium voltages, multi-level converter topologies or series connection of power semiconductor devices is adopted due to practical limitation of the prevailing power semiconductor devices in terms of their peak blocking voltage capability and maximum operating switching frequency [46]. These topologies are three level neutral point clamped (3L-NPC)

Fig. 1.2: (a) Overview of medium voltage Si and SiC power modules (b) Image of the modern Si and SiC based press pack or power module packages. Source: [28], [35]–[45]

Fig. 1.3: Overview and classification of high power MV converter topologies.

#### Chapter 1. Introduction

[48]–[51], five level H-bridge neutral point clamped (5L-NPC) [52], cascaded H-bridge (CHB) [53] and modular multi-level converter (MMC) [54], [55]. In spite of offering numerous advantages, multi-level converter topologies suffer from several drawbacks due to their higher component counts, converter design and control complexity. A brief overview and comparative evaluation of the most commonly used topologies in commercial high power MV converters is presented in Table 1.1.

Table 1.1: Performance characteristics comparison of the most commonly implemented power converter topologies in commercial high power MV converters [47].

| Performance characteristics              | 3L-NPC  | 5L-NPC  | CHB     | MMC                  |

|------------------------------------------|---------|---------|---------|----------------------|

| Power quality                            |         |         |         |                      |

| Output current total                     | +       | ++      | +++     | +++                  |

| harmonic distortion                      |         |         |         |                      |

| (THD)                                    |         |         |         |                      |

| Output voltage THD                       | +       | ++      | +++     | +++                  |

| Max. output voltage                      | +       | ++      | +++     | +++                  |

| step                                     |         |         |         |                      |

| Output voltage $\mathrm{d}v/\mathrm{d}t$ | +       | ++      | +++     | +++                  |

| Filter requirements                      | +       | ++      | +++     | +++                  |

| Controllability                          |         |         |         |                      |

| Ease of control imple-                   | ++      | +       | +       | +                    |

| mentation                                |         |         |         |                      |

| Control or design chal-                  | DC-link | DC-link | Voltage | Submodule            |

| lenges                                   | voltage | voltage | and     | capaci-              |

|                                          | balanc- | balanc- | current | $\operatorname{tor}$ |

|                                          | ing     | ing     | sharing | voltage              |

|                                          |         |         | within  | balanc-              |

|                                          |         |         | cas-    | ing                  |

|                                          |         |         | caded H |                      |

|                                          |         |         | bridge  |                      |

| Converter topology                       |         |         |         |                      |

| Semiconductor compo-                     | ++      | +       | +       | +                    |

| nent count                               |         |         |         |                      |

| Power loss distribution                  | +       | ++      | +++     | +++                  |

| Modularity & redun-                      | +       | +       | +++     | +++                  |

| dancy                                    |         |         |         |                      |

| Input transformer de-                    | +++     | +       | +       | +++                  |

| sign complexity                          |         |         |         |                      |

From the literature survey it has been identified that no commercial MV converters (rated for line-line voltage  $\geq 3.3$  kV) exist that utilize the two-level VSC topology. Lately, the MV SiC power semiconductor devices are getting attention in high power MV application since there is very little or no room for converter performance improvements with prevalent Si based technology as they seem to have attained their theoretical performance limits [30], [31].

## 1.3 Thesis hypotheses and objectives

This section presents the thesis hypotheses and objectives for the research work.

## 1.3.1 Thesis hypotheses

Increased voltage level and very high rate of change of voltage (dv/dt) during switching transients that can approach the values as high as 250 kV/µs for SiC MOSFETs, are order of magnitudes higher than their Si counter parts [22], [56]. Medium voltage levels combined with high dv/dt switching transients of SiC MOSFET introduce new challenges in terms of their practical application in power electronic converters. This leads to the formulation of the following hypotheses:

- The high dv/dt switching transient of MV SiC MOSFETs combined with their relatively lower current ratings, impose new design considerations in terms of reduced parasitic capacitance for the SiC MOSFET power modules and circuits or components interfacing the power modules such as gate drivers and filter inductors. Due to fast switching transient, the parasitic capacitances that experience high dv/dt can introduce displacement currents during switching transients. The magnitude of this displacement current can be significantly higher, which may result in worsening the electromagnetic interference and compatibility (EMI/EMC) performance, increased power loss and difficulties in achieving reliable operation for a power electronic converter.

- Due to medium voltage levels and high dv/dt switching transient, the impact of power module parasitic capacitance on SiC MOSFET switching transient and switching energy dissipation can be significant, which may not be neglected in the case of MV SiC MOSFET power modules.

- With implementing key design considerations in terms of low coupling capacitance for power modules and interfacing circuits, MV SiC MOSFET enabled power electronic converter based on simple two-level voltage source converter topology can be demonstrated.

## 1.3.2 Thesis objectives

Based on the hypotheses presented in the previous section, the main objectives of the PhD thesis are formulated as follows:

- To design and experimentally validate the low coupling capacitance and MV isolated gate driver, with a high common mode noise immunity for 10 kV half-bridge SiC MOSFET power module.

- To analyse the impact of power module parasitic capacitance on SiC MOSFET switching transient and switching energy dissipation.

- To design a kVA rated MV power stack, utilizing 10 kV half-bridge SiC MOSFET power modules and demonstrate experimental validation of power stack close to its rated operating point, with feasible efficiency estimation based on measured power loss data.

## 1.4 Thesis outline and contributions

This PhD dissertation is presented in the form of article based thesis and consists of six chapters. The chapters are based on journal and conference publications [A]–[E], as listed in Section 1.5.

### Chapter 1

### Introduction

This chapter introduces background and motivation for the PhD thesis and presents state of the art.

#### Chapter 2

### SiC MOSFET power modules

The chapter introduces custom-packaged 10 kV half-bridge SiC MOSFET power modules utilized in this research project. Furthermore, it presents key static characterisation data for 10 kV SiC MOSFET and 10 kV SiC Junction Barrier Schottky (JBS) diode.

### Chapter 3

### Galvanically isolated low-isolation capacitance gate driver

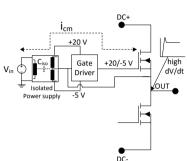

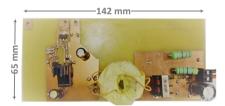

This chapter presents 10 kV SiC MOSFET gate driver design with MV isolation and very low coupling capacitance (< 3 pF) for a high common-mode (CM) noise immunity. The experimental validation of the designed gate driver in terms of DC voltage withstand capability, overall gate driving functionality and CM current measurements when subjected to high dv/dt switching transient is presented. The design and experimental validation of the gate driver is published in article [A].

### Chapter 4

Dynamic switching characterisation of SiC MOSFET power modules

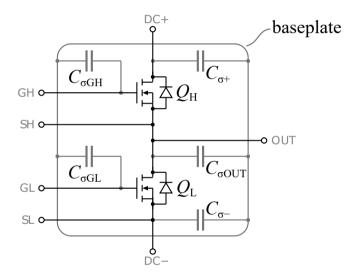

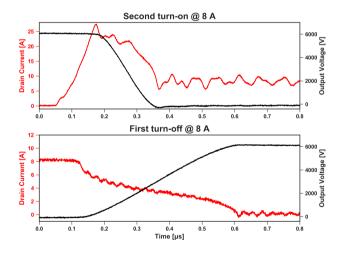

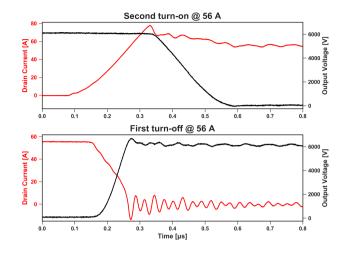

This chapter presents an in-depth analysis regarding the impact of power module

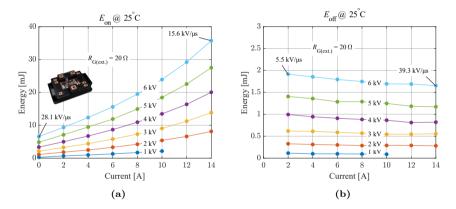

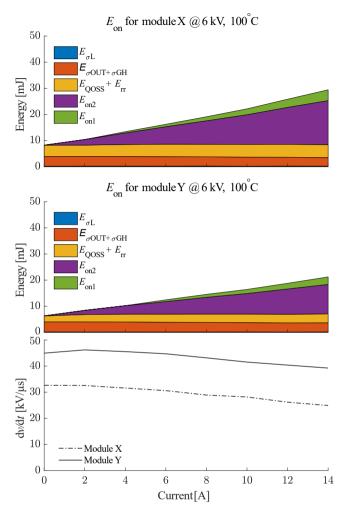

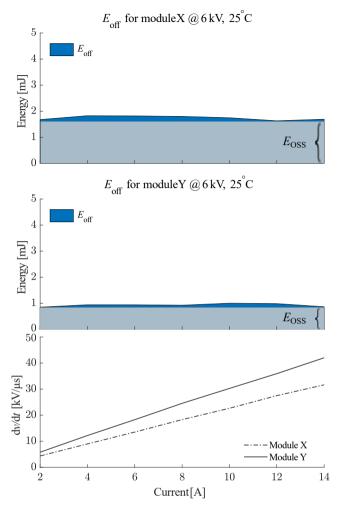

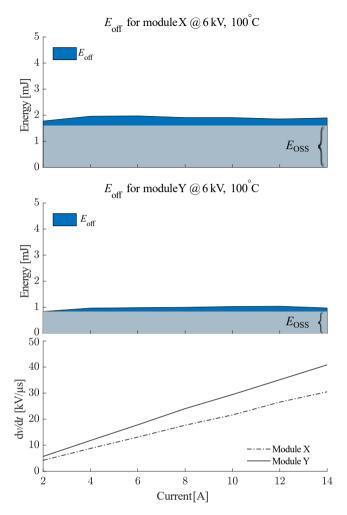

parasitic capacitance on SiC MOSFET switching transient and switching energy dissipation by utilizing two custom-made 10 kV SiC MOSFET half-bridge power modules, that differ in terms of their direct bonded copper (DBC) layouts. The contribution of module parasitic capacitance in terms of added switching energy dissipation is analysed with proposed switching energy dissection method. This work is published in article [B]. In another case study, the assessment of 10 kV half-bridge power modules with and without anti-parallel SiC JBS diode in terms of their switching performance is carried out, using switching energy dissection method proposed in article [B]. The work is summarised in article [C]. Furthermore, the dynamic switching characterisation for a reduced parasitic capacitance 10 kV multi-chip power module is presented, which is based on article [E].

### Chapter 5

### 10 kV SiC MOSFET enabled medium voltage power stack

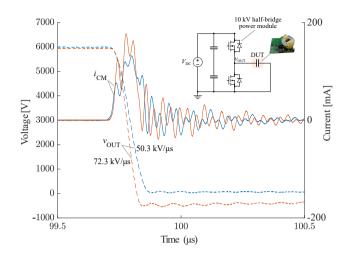

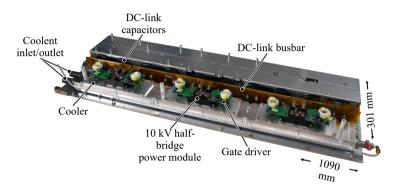

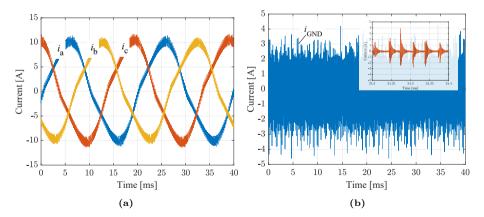

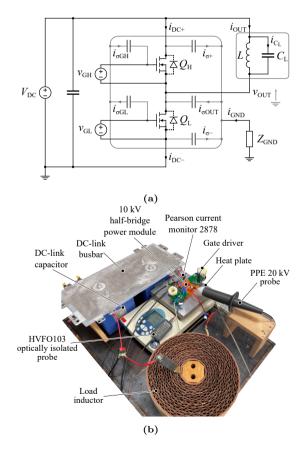

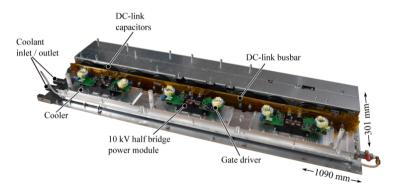

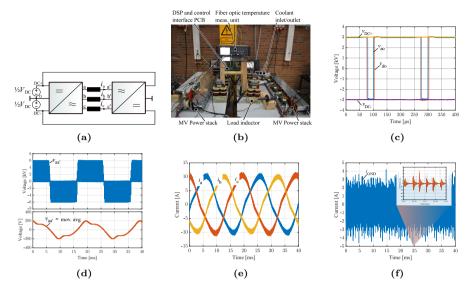

This chapter presents the design of a 50 kVA, 4.16 kV rated MV power stack utilizing 10 kV half-bridge SiC MOSFET power modules in a simple two-level voltage source converter topology. Experimental validation of the designed power stack is performed in a DC-fed three phase back-to-back regenerative test setup and key electrical measurements for the converter close to its rated operating point are demonstrated. This work is published in article [D].

#### Chapter 6

#### Conclusion: Summary and future work

The PhD thesis is concluded in this chapter with a summary highlighting main research contributions and propounded future work.

## 1.5 List of publications

The PhD Thesis is based on the following publications which have been published or submitted in international conferences or scientific journals in the field of power electronics.

- [A] D. N. Dalal, N. Christensen, A. B. Jørgensen, S. D. Sønderskov, S. Bęczkowski, C. Uhrenfeldt, S. Munk-Nielsen, "Gate driver with high common mode rejection and self turn-on mitigation for a 10 kV SiC MOSFET enabled MV converter," 2017 19th European Conference on Power Electronics and Applications (EPE'17 ECCE Europe), 2017, pp. P.1-P.10

- [B] D. N. Dalal, N. Christensen, A. B. Jørgensen, J. K. Jørgensen, S. Bęczkowski, S. Munk-Nielsen, C. Uhrenfeldt, "Impact of Power Module Parasitic Capacitances on Medium-Voltage SiC MOSFETs Switching Transients," in IEEE Journal of Emerging and Selected Topics in Power Electronics, vol. 8, no. 1, pp. 298-310, March 2020

- [C] D. N. Dalal, J. K. Jørgensen, H. Zhao, M. M Bech, S. Bęczkowski, C. Uhrenfeldt and S. Munk-Nielsen, "Switching Performance Assessment of 10 kV Half-Bridge SiC MOSFET Power Modules With and Without Anti-Parallel SiC JBS Diode," submitted to IEEE Open Journal of Power Electronics, 2021. [Submitted]

- [D] D. N. Dalal, H. Zhao, J. K. Jørgensen, N. Christensen, A. B. Jørgensen, A. B. Jørgensen, S. Bęczkowski, C. Uhrenfeldt, S. Munk-Nielsen, "Demonstration of a 10 kV SiC MOSFET based Medium Voltage Power Stack,"2020 IEEE Applied Power Electronics Conference and Exposition (APEC), 2020, pp. 2751-2757

- [E] J. K. Jørgensen, D. N. Dalal, S. Bęczkowski, S. Munk-Nielsen and C. Uhrenfeldt, "Multi-chip Medium Voltage SiC MOSFET Power Module with Focus on Low Parasitic Capacitance," CIPS 2020; 11th International Conference on Integrated Power Electronics Systems, 2020, pp. 1-6.

The co-authored conference and journal publications pertinent to the medium voltage SiC MOSFETs and its applications are listed below:

- H. Zhao, D. Dalal, J. K. Jørgensen, M. M. Bech, X. Wang, S. Munk-Nielsen, "Behavioral Modeling and Analysis of Ground Current in Medium-Voltage Inductors," in IEEE Transactions on Power Electronics, vol. 36, no. 2, pp. 1236-1241, Feb. 2021

- H. Zhao, D. N. Dalal, J. K. Jørgensen, A. B. Jørgensen, X. Wang, B. Rannestad, S. Munk-Nielsen, "Identification of the Terminal-to-Core Couplings in Filter Inductors by Using Double-Pulse-Test Setup," 2020 IEEE 21st Workshop on Control and Modeling for Power Electronics (COMPEL), 2020, pp. 1-6

- J. K. Jørgensen, N. Christensen, D. N. Dalal, A. B Jørgensen, H. Zhao, S. Munk-Nielsen, C. Uhrenfeldt, "Loss Prediction of Medium Voltage Power Modules: Trade-offs between Accuracy and Complexity," 2019 IEEE Energy Conversion Congress and Exposition (ECCE), 2019, pp. 4102-4108

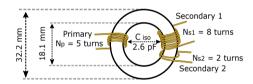

- H. Zhao, D. N. Dalal, X. Wang, J. K. Jørgensen, C. Uhrenfeldt, S. Beczkowski, S. Munk-Nielsen, "Modeling and Design of a 1.2 pF Common-Mode Capacitance Transformer for Powering MV SiC MOSFETs Gate Drivers," IECON 2019 45th Annual Conference of the IEEE Industrial Electronics Society, 2019, pp. 5147-5153

- A. B. Jørgensen, N. Christensen, D. N. Dalal, "Reduction of parasitic capacitance in 10 kV SiC MOSFET power modules using 3D FEM," 2017 19th European Conference on Power Electronics and Applications (EPE'17 ECCE Europe), 2017, pp. P.1-P.8

#### 1.5. List of publications

N. Christensen, A. B. Jørgensen, D. Dalal, S. D. Sønderskov, S. Bęczkowski, C. Uhrenfeldt, S. Munk-Nielsen, "Common mode current mitigation for medium voltage half bridge SiC modules," 2017 19th European Conference on Power Electronics and Applications (EPE'17 ECCE Europe), 2017, pp. P.1-P.8 Chapter 1. Introduction

## Chapter 2

## SiC MOSFET power modules

## 2.1 Introduction

It was only recently that the first manufacturer of 10 kV SiC devices Wolfspeed Inc., announced the 10 kV/240 A SiC MOSFET power modules [45]. However until then, the 10 kV SiC semiconductor devices were only available in the form of bare dies as an engineering samples from the manufacturer.

To utilize these semiconductor devices in a MV power electronic converter, packaging of these devices in the form of power module is a necessary requirement. The 10 kV SiC MOSFET power modules utilized in this research work are custom packaged at the Packaging Laboratory, Aalborg University [57], [58]. To provide an overview, the 10 kV SiC MOSFET power modules together with key static characteristics for a 10 kV SiC MOSFET and JBS diode dies are presented in this chapter.

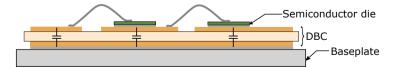

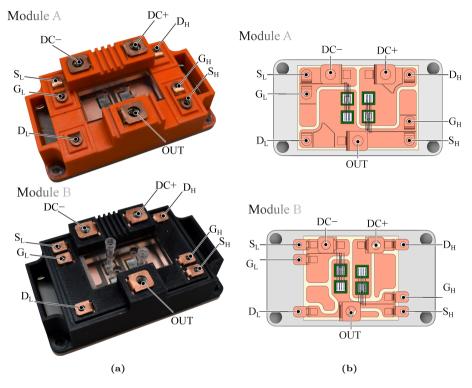

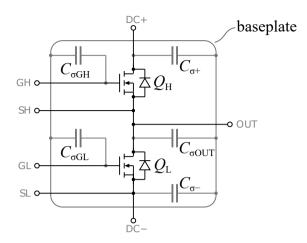

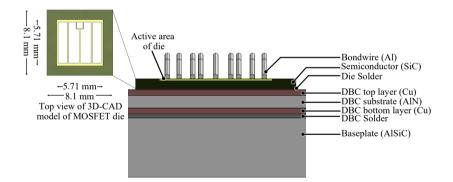

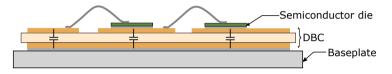

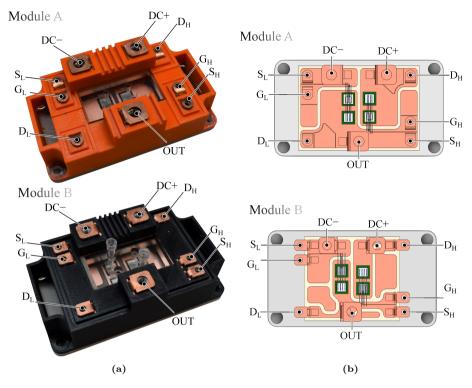

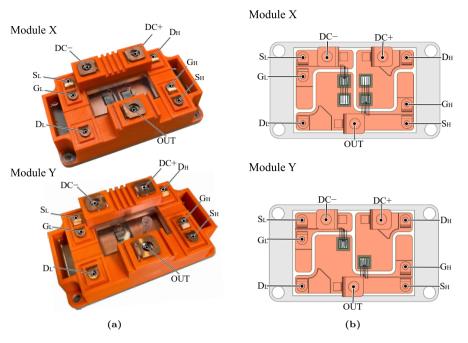

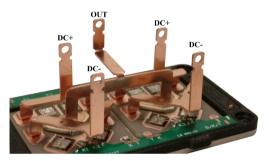

## 2.2 10 kV half-bridge SiC MOSFET power modules

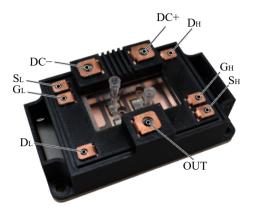

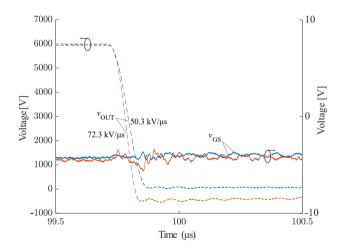

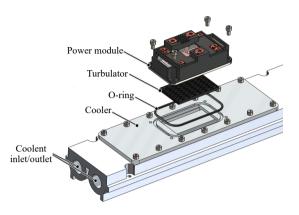

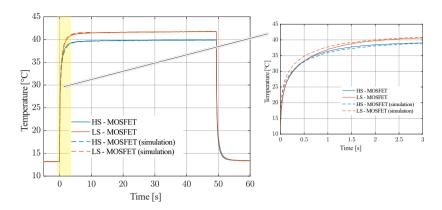

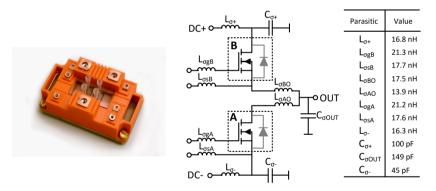

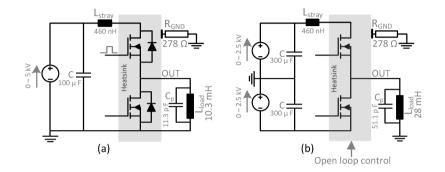

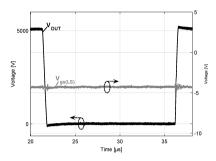

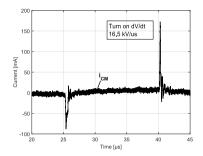

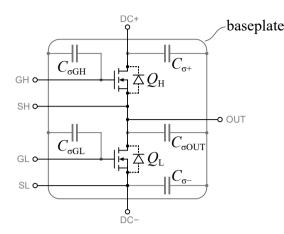

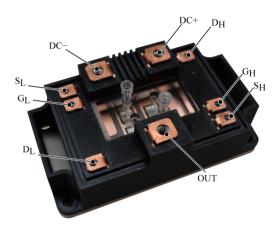

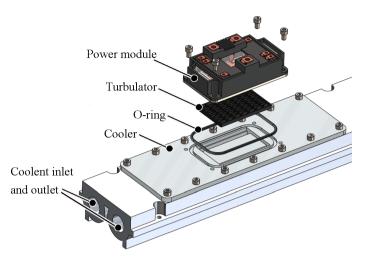

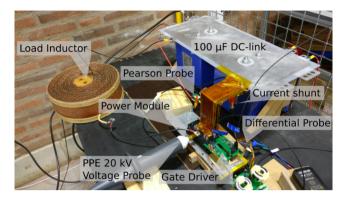

The custom packaged single-chip 10 kV half-bridge SiC MOSFET power module is shown in Fig. 2.1 with markers labeling the terminals. The power module is populated with 8.1 mm x 8.1 mm third generation 10 kV 350 m $\Omega$  SiC MOSFETs and an anti-parallel SiC JBS diode dies (from Wolfspeed [16], [59]) per switch position. The 10 kV SiC MOSFETs and diode dies are rated for the continuous drain current of 20 A as per their preliminary datasheet. The dies are soldered on a 0.63 mm Aluminium Nitride (AlN) direct bonded copper (DBC) substrate with a 3 mm thick 104 mm x 59 mm Aluminium Silicon-Carbide (AlSiC) baseplate [57]. There is an access to the die surface through a pipette, which allows insertion of fiber optic temperature sensors for monitoring purpose. This single-chip 10 kV power module is utilized in a MV three phase power stack demonstrator, which is presented in Chapter 5.

Fig. 2.1: Picture of a 10 kV single-chip half-bridge SiC MOSFET power module. (Letters D, G, H indicate drain, gate and source respectively. Subscripts H and L stands for the high side and low side devices, respectively.) [D]

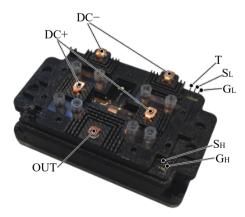

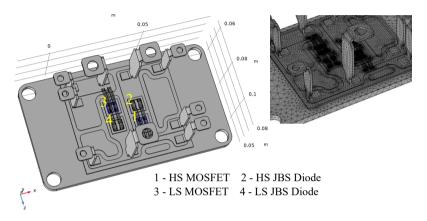

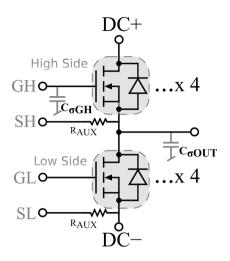

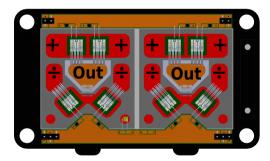

The custom packaged multi-chip half-bridge power module is shown in Fig. 2.2. The multi-chip power modules is populated with four third generation 10 kV 350 m $\Omega$  dies per switch position. The dies are soldered on two separate 1 mm AlN DBC substrates with 3 mm thick 104 mm x 59 mm AlSiC baseplate [58]. The module has a power loop inductance of 21.1 nH and a maximum gate loop inductance of 31 nH [58].

**Fig. 2.2:** Picture of a multi-chip 10 kV half-bridge SiC MOSFET power module. (Letters G, H, T indicate drain, gate and thermistor, respectively. Subscripts H and L stands for the high side and low side devices respectively.)

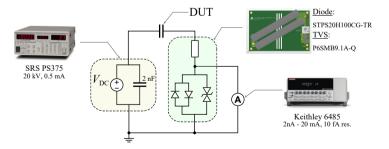

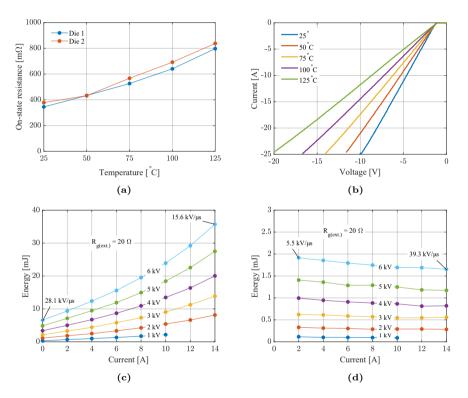

## 2.3 Static characterisation of 10 kV SiC MOS-FET and JBS diode

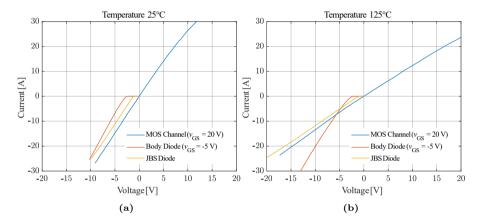

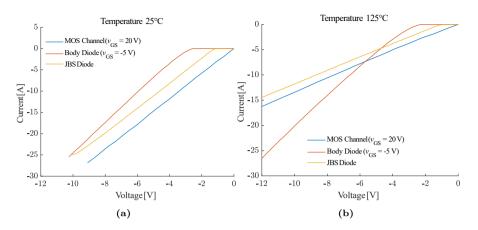

The first quadrant I–V characteristics at gate bias of 20 V as well as third quadrant characteristics at gate bias of 20 V and -5 V for a SiC MOSFET bare dies together with the forward characteristics for a 10 kV SiC JBS diode at 25°C and 125°C temperatures are presented in Fig. 2.3. The I–V characteristics are obtained from the static measurements utilizing Tektronix B371A curve tracer [60].

Fig. 2.3: Measured I–V characteristics for 10 kV SiC MOSFET and 10 kV SiC JBS diode at (a)  $25^{\circ}$ C (b)  $125^{\circ}$ C.

As can be seen from Fig. 2.3, 10 kV SiC MOSFET exhibits symmetric first quadrant and third quadrant I–V characteristics for a positive gate bias of 20 V. Based on the measured I–V characteristics of a 10 kV SiC MOSFET die, on-state resistance which exhibits positive temperature coefficient is identified to be 364 m $\Omega$  and 817 m $\Omega$  at 25°C and 125°C, respectively. Whereas, the gate-source threshold voltage is identified to be 7.0 V and 5.2 V at drain current of 100 mA from measured transfer characteristics at drain-source voltage of 30 V and temperatures of 25°C and 125°C, respectively.

The forward voltage drop of body diode decreases with temperature and is measured to be 2.6 V and 2.4 V at 100 mA forward current for temperatures of  $25^{\circ}$ C and  $125^{\circ}$ C, respectively. In case of the 10 KV SiC JBS diode the forward voltage is within 1.1 V – 1.2 V at forward current of 100 mA, with similar on-resistance as 10 kV SiC MOSFET for temperature range of  $25^{\circ}$ C –  $125^{\circ}$ C. It is worth to mention that, for a 10 kV SiC MOSFET in a third quadrant operation with a positive gate bias of 20 V, the body diode turn-on is not identified and current is primarily conducting through a MOSFET channel [61], [62]. This is attributed to the increase in body diode turn-on voltage when MOSFET channel is on [62]. Such behaviour is reported for SiC MOSFETs in 3.3 kV or higher voltage class, where ratio of drift layer resistance to total on-state resistance for the MOSFET increases [62]. At 125°C temperature, with increased current levels (>7.5 A) the body diode conduction provides lower on-state voltage drop in comparison to the JBS diode. For the intended application of a 10 kV SiC MOSFET in AC-DC or DC-AC converters where a MOSFET is turned on with a positive gate bias during reverse conduction, the current will primarily conduct through the MOSFET channel or will be shared between the MOSFET channel and anti-parallel JBS diode if present. Although, inclusion of anti-parallel SiC JBS diode may provide lower conduction losses by providing a parallel path to the SiC MOSFET channel during reverse conduction, eliminating a SiC JBS diode is beneficial from a cost and power density point of view for the power module. This can be considered if 10 kV SiC MOSFET body diode performs as good as SiC JBS diode in terms of reverse recovery.

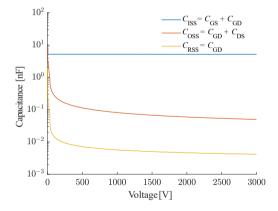

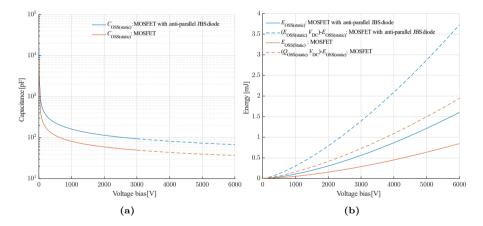

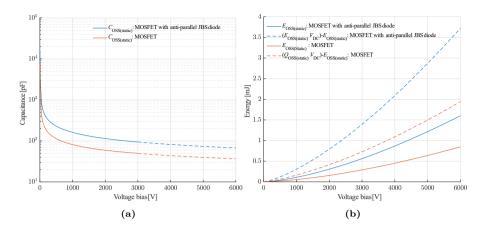

Measured input, output and reverse transfer parasitic capacitances for a 10 kV SiC MOSFET with drain-source voltage bias of up to 3 kV utilizing Keysight B1506 curve tracer [63], is shown in Fig. 2.4. Here, the input capacitance ( $C_{\rm ISS}$ ) is equal to the sum of MOSFET gate-source capacitance ( $C_{\rm GS}$ ) and drain-source capacitance ( $C_{\rm DS}$ ). Whereas, the output capacitance ( $C_{\rm OSS}$ ) is equal to the sum of MOSFET gate-drain capacitance ( $C_{\rm GD}$ ) and drain-source capacitance ( $C_{\rm DS}$ ). The reverse transfer capacitance ( $C_{\rm GS}$ ) often referred to as a Miller capacitance is equal to the gate-drain capacitance ( $C_{\rm GD}$ ). The gate-source capacitance ( $C_{\rm GS}$ ) of a MOSFET, which is almost constant with

Fig. 2.4: Measured input, output and reverse transfer capacitances with drain-source voltage bias of up to 3 kV for a 10 kV SiC MOSFET.

respect to the applied drain-source voltage bias is measured to be 5.2 nF. The gate-drain capacitance  $(C_{\text{GD}})$  and drain-source capacitance  $(C_{\text{DS}})$  are highly non-linear, where major drop in capacitance (nF to tens or hundreds of pF)

#### 2.4. Summary

occurs within the first few hundred volts of the applied drain-source bias voltage as can be seen in Fig. 2.4. The drive power or gate charge requirement for a gate driver along with the switching transition times of a SiC MOSFET are primarily determined by the MOSFET input capacitance. The output capacitance of the MOSFET is of a great importance as this gets charged or discharged during the switching event, which incurs losses. From, this point of view, smaller power device input and output capacitance of SiC MOSFETs compared to their Si counter parts is desirable to achieve faster switching transition time and lower switching energy dissipation [30], [64], [65].

### 2.4 Summary

In this chapter, the 10 kV half-bridge SiC MOSFET power modules to be utilized in the research work are introduced. The key data from static I–V characterisation at 25°C and 125°C and capacitance measurements for 10 kV SiC power semiconductor devices are presented.

Chapter 2. SiC MOSFET power modules

# Chapter 3

# Galvanically isolated low-isolation capacitance gate driver

### 3.1 Introduction

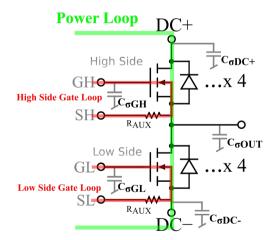

In the case of MV half-bridge SiC MOSFET power modules, dv/dt at the output terminal of a half-bridge during switching transient can be as high as up to 250 kV/µs [22], [56], [66]. The fast switching transient, introduces displacement current through the isolation barrier of the gate driver power supply as well as signal path that appear as common mode (CM). The magnitude of CM current  $i_{\rm CM}$  is related to the dv/dt and the value of isolation capacitance  $C_{\rm iso}$ as presented in (3.1),

$$i_{\rm CM} = C_{\rm iso} \cdot \frac{\mathrm{d}v}{\mathrm{d}t} \tag{3.1}$$

The magnitude of CM current needs to be limited to sufficiently lower value in order to ensure reliable operation of the half-bridge power module, since increased CM noise may negatively impact the gate drive control signal fidelity [67]. This impose a requirement of a high isolation voltage with a very low coupling capacitance, typically less than 5 pF for the gate driver [67]. Commercially available DC-DC power supplies with the isolation voltage rating in the range of 10 kV are unregulated or exhibit high isolation capacitance (10 pF – 20 pF) [68]–[70]. Furthermore, the fast switching transient can lead to a shoot-through due to Miller induced false turn-on of either high side (HS) or low side (LS) device in a half-bridge power module during the turn-on of the complementary device [71], [72]. This can be mitigated by the integration of the active Miller clamp (AMC) circuitry, which limits the complementary device gate-source Chapter 3. Galvanically isolated low-isolation capacitance gate driver

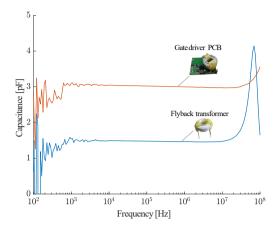

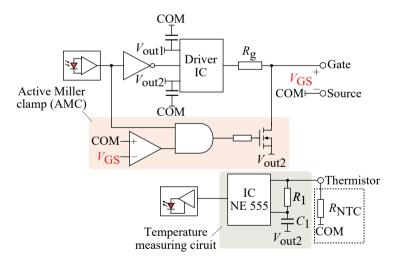

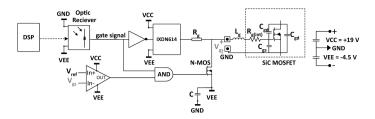

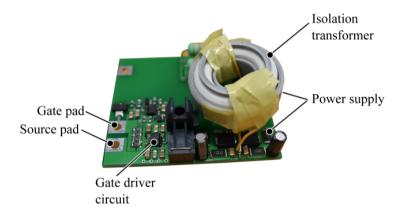

voltage ( $v_{\rm GS}$ ) below its threshold by providing a low impedance path to the high dv/dt induced Miller current [73]. Above mentioned considerations, require a design of the MV isolated, low isolation capacitance gate driver customized for the 10 kV half-bridge SiC MOSFET power modules. Various designs for the MV SiC MOSFET gate driver has been reported in literature, which are summarized in Table 3.1 with details on the DC-DC power supply and gate drive architecture including list of additional functionalities.

Table 3.1: Summary from the literature review of MV SiC MOSFET gate drivers.

| DC-DC power supply and gate driver                                                                                                                                                                                                                                                                                                                                                                                               | Additional functionality |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| [67]                                                                                                                                                                                                                                                                                                                                                                                                                             |                          |

| DC-DC: Single output voltage, primary side full-                                                                                                                                                                                                                                                                                                                                                                                 | -                        |

| bridge and secondary side diode rectifier with a                                                                                                                                                                                                                                                                                                                                                                                 |                          |

| toroidal core transformer with windings enclosed in-                                                                                                                                                                                                                                                                                                                                                                             |                          |

| side Polyvinyl chloride (PVC) tube. Voltage regula-                                                                                                                                                                                                                                                                                                                                                                              |                          |

| tion with a regulator on a secondary side. $(C_{iso} =$                                                                                                                                                                                                                                                                                                                                                                          |                          |

| 5 pF)                                                                                                                                                                                                                                                                                                                                                                                                                            |                          |

| Gate driver: Driver IC DEIC 420 from IXYS. Signal                                                                                                                                                                                                                                                                                                                                                                                |                          |

| isolation using a pulse transformer.                                                                                                                                                                                                                                                                                                                                                                                             |                          |

| [66]                                                                                                                                                                                                                                                                                                                                                                                                                             |                          |

| DC-DC: Dual output voltage, single active bridge                                                                                                                                                                                                                                                                                                                                                                                 | -                        |

| topology with primary side full-bridge and secondary                                                                                                                                                                                                                                                                                                                                                                             |                          |

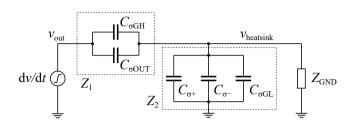

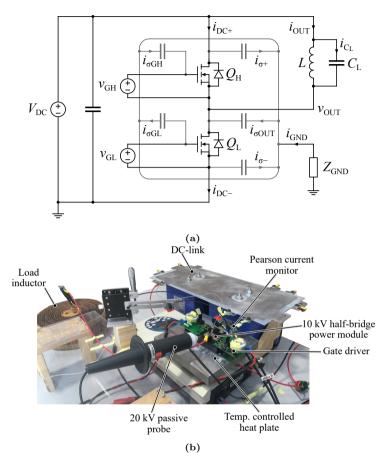

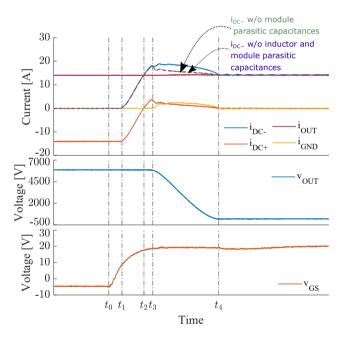

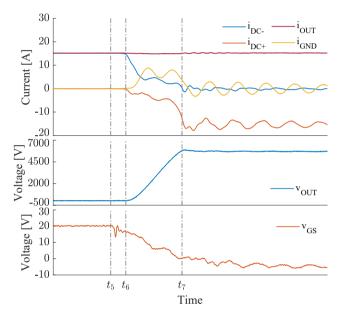

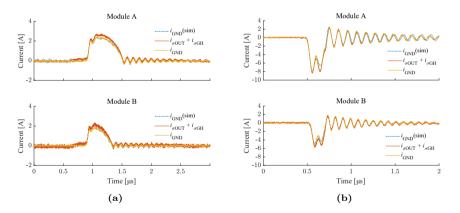

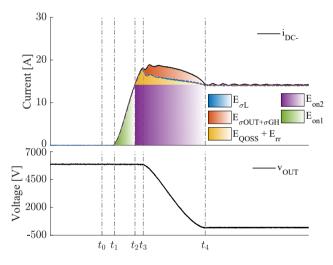

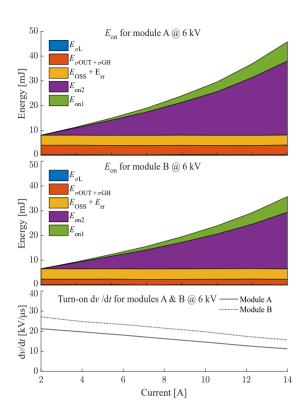

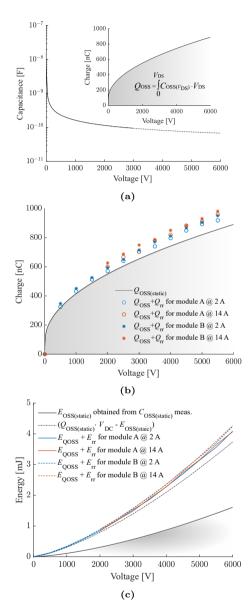

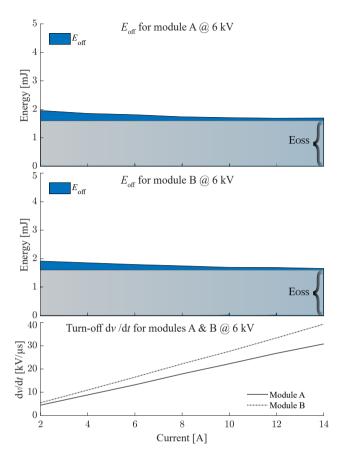

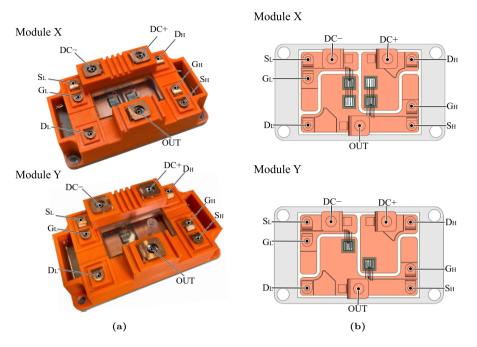

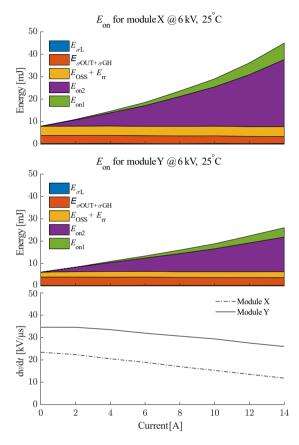

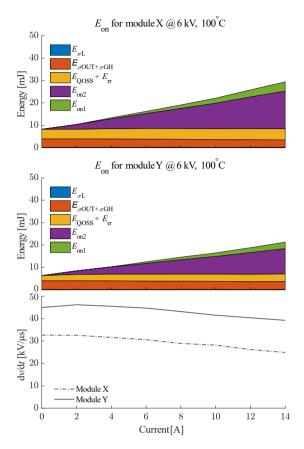

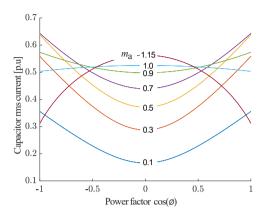

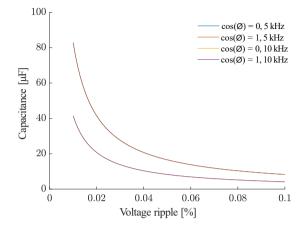

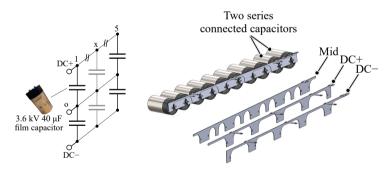

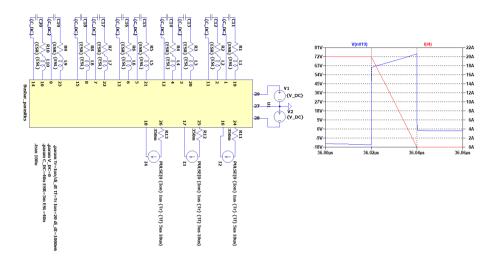

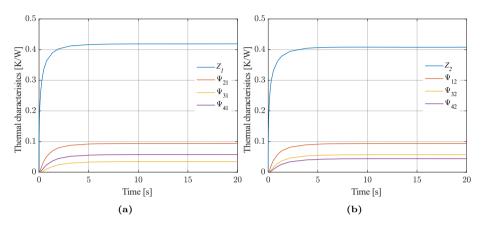

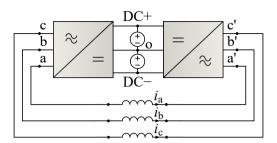

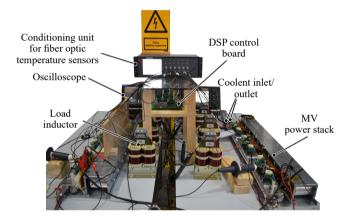

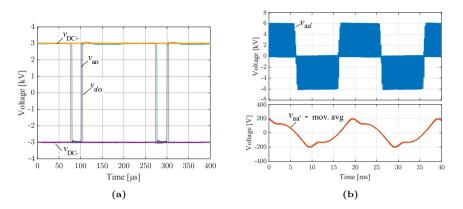

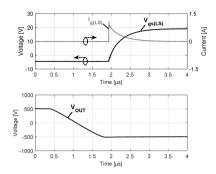

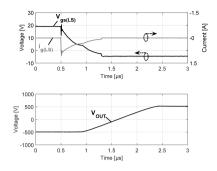

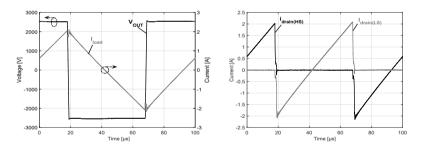

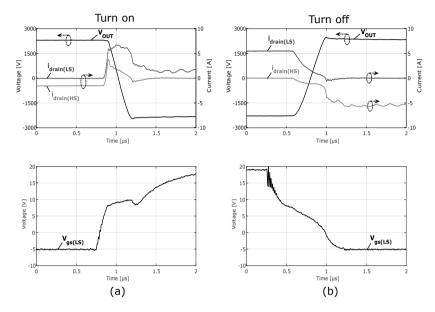

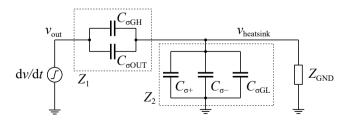

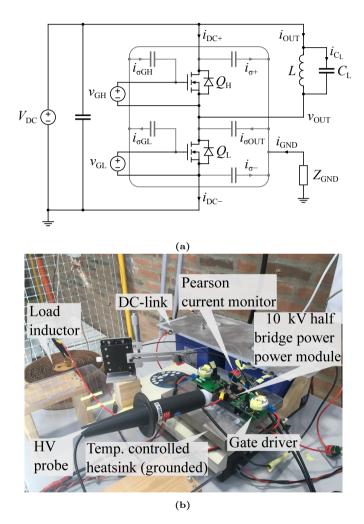

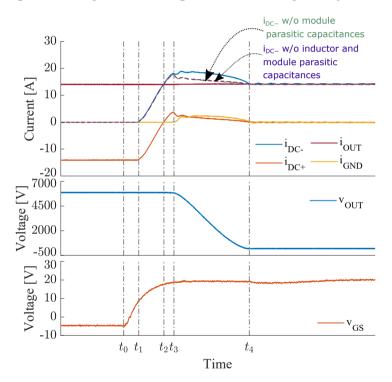

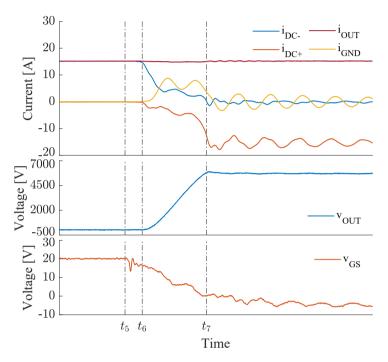

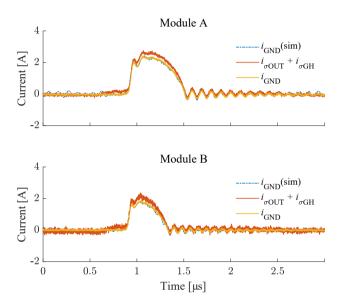

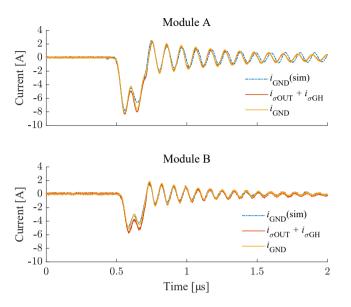

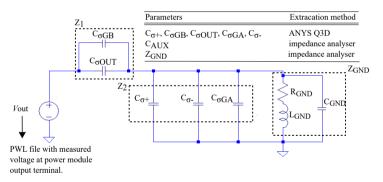

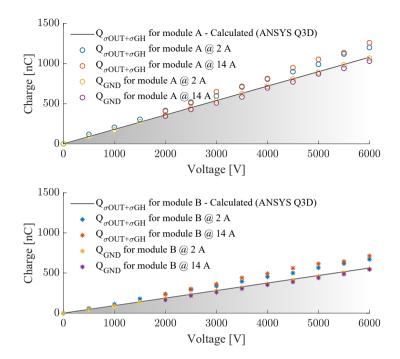

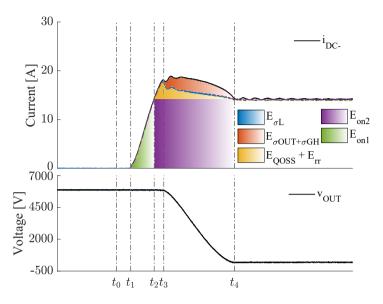

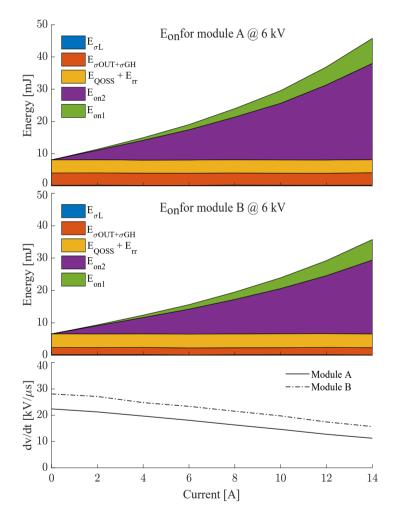

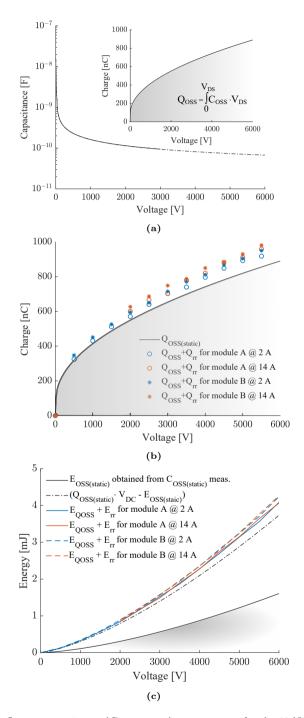

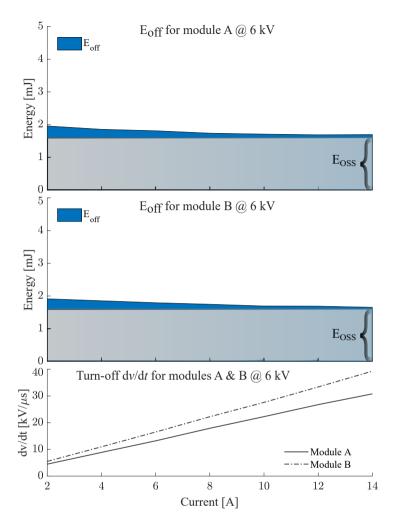

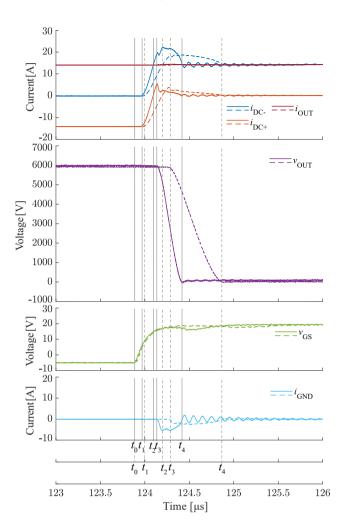

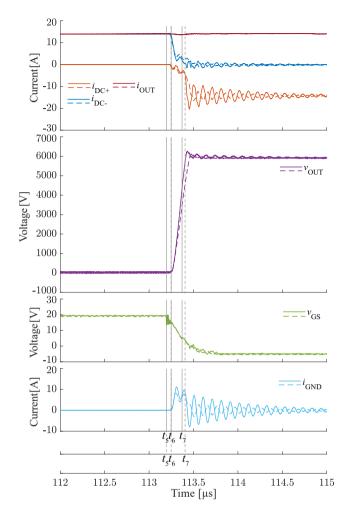

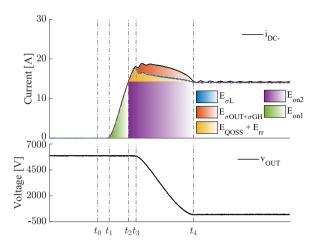

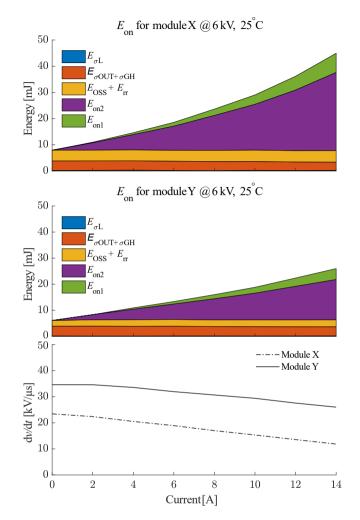

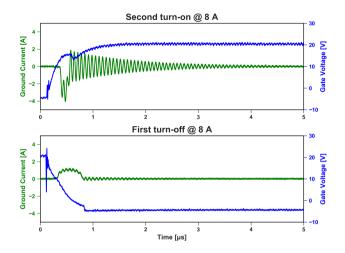

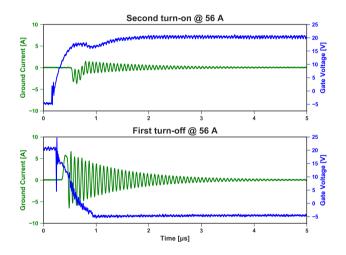

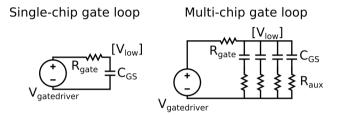

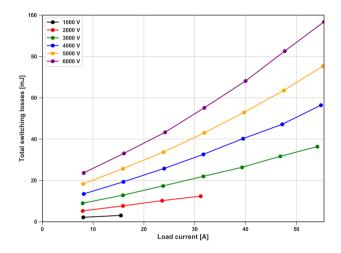

| side diode rectifier with a toroidal core transformer.                                                                                                                                                                                                                                                                                                                                                                           |                          |