Aalborg Universitet

## A Current Limiting Method for Single-Loop Voltage-Magnitude Controlled Grid-Forming **Converters During Symmetrical Faults**

Liu, Teng; Wang, Xiongfei; Liu, Fangcheng; Xin, Kai; Liu, Yunfeng

Published in: **IEEE Transactions on Power Electronics**

DOI (link to publication from Publisher): 10.1109/TPEL.2021.3122744

Publication date: 2022

Document Version Accepted author manuscript, peer reviewed version

Link to publication from Aalborg University

Citation for published version (APA):

Liu, T., Wang, X., Liu, F., Xin, K., & Liu, Y. (2022). A Current Limiting Method for Single-Loop Voltage-Magnitude Controlled Grid-Forming Converters During Symmetrical Faults. *IEEE Transactions on Power Electronics*, 37(4), 4751-4763. https://doi.org/10.1109/TPEL.2021.3122744

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

#### Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

IEEE POWER ELECTRONICS REGULAR PAPER

# A Current Limiting Method for Single-Loop Voltage-Magnitude Controlled Grid-Forming Converters During Symmetrical Faults

Teng Liu, Member, IEEE, Xiongfei Wang, Senior Member, IEEE, Fangcheng Liu, Senior Member, IEEE, Kai Xin, and Yunfeng Liu

Abstract- This paper proposes a current limiting method for single-loop voltage-magnitude controlled grid-forming (GFM) converters to avoid overcurrent during symmetrical faults. The proposed method consists of two parts, which are the outer power reference adjustment to limit the steady-state fault current, and a transient virtual resistor, implemented by directly modifying the modulation voltage reference, to limit the transient fault current during fault-inception and -clearing periods. Further, a nonlinear dynamic model for the GFM converter with the proposed control is developed, and the phase portrait is plotted to reveal the influences of power reference adjustment and of transient virtual resistor control on the transient stability. Finally, experimental tests confirm that the proposed method can effectively limit the fault current to an admissible value while simultaneously keeping the GFM mode during fault ride-through.

*Index Terms-* Grid-forming converters, fault ride-through, current limitation, transient stability.

#### I. INTRODUCTION

GRID-forming (GFM) converters have been widely deemed as a promising substitute for synchronous generators (SGs) in the future power-electronic-based power systems [1]. However, in contrast to the short-circuit capacity (5 p.u. - 8 p.u.) of SGs, GFM converters has limited overcurrent capacity (1.5 p.u. - 2 p.u.) [2]. Consequently, GFM converters are more sensitive to the short-circuit faults than SGs [3]. Furthermore, to ensure a continuous electricity supply, GFM converters are required to ride through grid faults without losing the synchronism with grid. Hence, the current limiting control and its interaction with the power grid become critical for reliable operations of GFM converters.

The existing current limitation schemes for GFM converters are generally categorized into two types. The first type is to employ an inner current control loop and to directly limit the current reference during grid faults, which usually switches the GFM converter to grid-following (GFL) control mode [4]-[6]. While this type of methods can precisely limit fault current, the latch-up and wind-up issues may happen, which challenge the fault-recovery process [7]. Further, due to the transfer from the

Manuscript received January 25, 2021; revised May 13, 2021 and August 15, 2021; accepted October 15, 2021. (Corresponding author: Xiongfei Wang)

T. Liu and X. Wang are with the AAU Energy, Aalborg University, 9220 Aalborg, Denmark (e-mail: teli@energy.aau.dk; xwa@energy.aau.dk).

F. Liu, K. Xin, and Y. Liu are with Huawei Digital Power Technologies Company, Ltd., Shanghai 201206, China (e-mail: formula.liu@huawei.com; kai.xin@huawei.com; yf.liu@huawei.com). GFM to the GFL control mode, a backup phase-locked loop (PLL) is generally needed to keep the synchronism of converter with the grid during grid fault ride-through (FRT) [8]. Yet, the PLL can induce instability issue in weak grids [9]. Alternatively, the current reference limiting can also be applied while keeping the GFM control structure during the fault. Nevertheless, such methods suffer from possible transient instability due to the current saturation during grid faults [10].

To circumvent these drawbacks, the virtual impedance-based current limitation is introduced as the second type of solutions, where the general idea is to increase the output impedance of GFM converter by a virtual impedance (VI) for limiting output current. One way to realize the VI is to modify the reference for the vector voltage control, where a voltage drop emulated by the VI is subtracted from the voltage reference dictated by outer power control loops [11]-[14]. However, the effectiveness of such VI realization is limited by the control bandwidth of vector voltage loop. Further, the inductive VI, when it is implemented by the derivative controllers, tends to amplify the measurement noise [12]. To tackle these challenges, the VI is realized by multiplying the difference between reference and output voltages with a virtual admittance, and the output is used as the current reference for the inner current loop [15]-[17]. In this way, the inductive VI can be readily synthesized by a low-pass filter, and the transient fault current can be effectively limited by the faster current loop. Yet, this virtual admittance is in cascade with the current loop, which has to be adaptively tuned for transient and steady-state operations. Another point to be noted is that the existing virtual impedance-based methods keep the emulated VI working during the whole fault period [11]-[18]. The presence of a large virtual resistor leads to the high R/X ratio of line impedance during grid faults, which may aggravate the power coupling and deteriorate the system stability [19].

Recently, a detailed comparative analysis between the current reference limitation and the VI-based current limitation is conducted in [20]. The advantages and disadvantages of these two types of schemes are evaluated from the aspects of current limiting capacity and their impacts on the transient stability. Then, the hybrid current limiting methods that combine the current reference limitation with the VI control are proposed [3], [20]. Such methods not only ensure an accurate current limitation but also keep the GFM operation during FRT. Yet, since the VI is still realized by modifying the reference of voltage control loop, the current limiting performance can be

## IEEE POWER ELECTRONICS REGULAR PAPER

deteriorated during the fault-inception and -clearing instants due to the limited control bandwidth of voltage loop [21]. Alternatively, another hybrid method that combines the current reference limitation with the outer power reference adjustment is introduced in [22]. Based on the power reference adjustment, the saturation of the current controller can be avoided. However, as the bandwidth of the outer power loop is generally designed much lower than that of the inner current loop, this method may not guarantee the GFM control mode in the initial stage of fault. Another critical point to be noted is that all these approaches were used with the dual-loop vector-voltage control (VVC), i.e., the cascaded vector-voltage and current control, where a fast closed-loop vector-current control is indispensable for the current limitation, which may induce the harmonic instability issue due to the converter-grid interactions [23].

As an alternative to VVC schemes, the single-loop voltagemagnitude (SLVM) control has drawn more attention and been used with the GFM converters. Practical applications of SLVM control have been found in the CERTS microgrid [24] and the high-voltage direct-current transmission systems [25]. Unlike the VVC, the SLVM control merely regulates the magnitude of the point-of-connection (PoC) voltage, whereas the phase angle generated by the *P*-*f* droop is directly used with the converter modulation reference. Therefore, the SLVM control essentially regulates the phase angle of the converter-bridge voltage before the output filter rather than that of the PoC voltage. As a result, the filter inductor softens the dynamic coupling between GFM converters and the grid, compared to that of VVC, which leads to a better small-signal stability performance [26]. Further, it has recently been revealed that the SLVM control has a critical impact on the transient stability of GFM converters [27]. Hence, compared to the VVC which has negligible effect on the transient stability, the SLVM control can provide a degree of freedom to enhance the system transient stability. However, few studies have been reported on the current limitation of the SLVM-controlled GFM converter. Most of the existing current limiting methods used with the VVC cannot be directly extended to the SLVM control due to the absence of inner current control loop. One existing solution to limit the fault current of SLVM-controlled GFM converters is to switch the control system to the vector-current control during fault, and it requires using a back-up PLL [25]. Thus, the GFM control mode cannot be preserved.

To achieve the effective overcurrent limitation while keeping the GFM control mode during FRT, this paper proposes a current limiting method for GFM converters with the SLVM control. The main contributions of this paper are highlighted as follows.

- To prevent steady-state overcurrent during the fault period, the outer power control reference is modified during FRT. The magnitude of steady-state fault current is theoretically derived to prove the effectiveness of such reference change. It is worth noting that the usage of this power reference adjustment is essentially different from that in [22], which aims at avoiding the saturation of inner current controller.

- To limit the transient fault currents during fault-inception and -clearing periods, an adaptive proportional feedback

of the converter output current added to the converter modulation reference is introduced to emulate a transient virtual resistor. The effectiveness of the transient virtual resistor will not be limited by the bandwidth of inner voltage control loops as those reported in [11]-[14], [18]. Besides, the negative effect of virtual resistor on the power coupling can be avoided in the proposed method, since the transient virtual resistor is only activated in the first few cycles of fault-inception and fault-clearing periods, while the power reference adjustment is used to limit the fault current in the steady state. Such unique feature can also avoid the risk of harmonic instability issues caused by embedding the vector-current control loop.

A nonlinear dynamic model of GFM converter with the proposed control is developed, based on which, the phase portrait is plotted to reveal the influences of power reference adjustment and of transient virtual resistor control, respectively, on the transient stability of SLVMcontrolled GFM converters. It turns out that the outer power reference adjustment can keep the GFM converter synchronized with the grid during the entire process of symmetrical faults, while the transient virtual resistor has negligible effect on the system transient stability.

Finally, the effectiveness of the current limiting method and the transient stability analysis are confirmed by experimental tests.

#### II. PROPOSED CURRENT LIMITING METHOD

## A. System Description

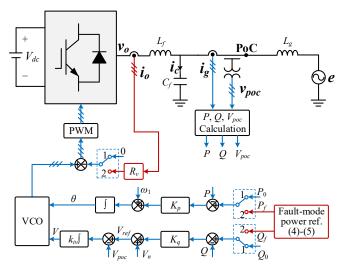

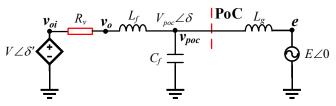

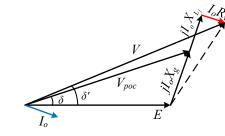

Fig. 1 shows the single-line diagram of a grid-connected three-phase GFM converter which employs the SLVM control and the proposed current limiting method.  $L_f$  and  $C_f$  denote the output *LC* filter of the converter.  $L_g$  is the grid-side inductor.  $v_o$  is the converter-bridge voltage.  $i_o$  is the converter output current, which is detected for the current limitation.  $i_c$  is the filter capacitor current.  $v_{poc}$  and e are the PoC voltage and the grid

Fig. 1 Single-line diagram of a grid-connected three-phase GFM converter with the SLVM control and the proposed current limiting method. The control signals selection is switched to 1 during normal operation period, and switched to 2 during the fault ride-through.

## IEEE POWER ELECTRONICS REGULAR PAPER

voltage, respectively.  $i_g$  denotes the grid-side current injected into the grid.  $v_{poc}$  and  $i_g$  are used to calculate the output active power *P*, the reactive power *Q*, and PoC voltage magnitude  $V_{poc}$ . In GFM converters, the dc-side voltage control is usually taken over by either a front-end converter [25] or an energy storage unit [28] connected to the dc-link. A constant dc-link voltage  $V_{dc}$  is thus assumed in this study.

The conventional *P*-*f* and *Q*-*V* droop control is adopted as the outer power control in this work. It should be noted that, in the SLVM-controlled GFM converters, the phase angle  $\theta$  generated by the *P*-*f* droop controller dictates the phase angle of  $v_o$  rather than that of  $v_{poc}$ , which is different from the VVC. The control law is given by

$$\theta = K_p \int (P_0 - P) \cdot dt + \omega_1 t \tag{1}$$

where  $K_p$  is the *P*-*f* droop coefficient,  $\omega_1$  is the grid fundamental angular frequency, and  $P_0$  denotes the reference value of the active power in the normal operating state.

The output of the Q-V droop controller is used as the voltage magnitude reference  $V_{ref}$  for the SLVM control, which is given by

$$V_{ref} = K_q \left( Q_0 - Q \right) + V_n \tag{2}$$

where  $K_q$  is the Q-V droop coefficient,  $V_n$  is the rated voltage magnitude, and  $Q_0$  is the reference value of the reactive power in the normal operating state.

Then, the PoC voltage magnitude is regulated by the SLVM control to generate the magnitude reference V of the converterbridge voltage  $v_o$ , whose control law can be expressed as

$$V = k_{iv} \int \left( V_{ref} - V_{poc} \right) \cdot dt \tag{3}$$

where  $k_{iv}$  is the integral gain of the SLVM control. Combining V and  $\theta$ , the modulation voltage is generated by the voltagecontrolled oscillator (VCO) as shown in Fig. 1.

From Fig. 1, it is seen that the GFM converter with the SLVM control is constrained to implement a closed-loop vector-current control. Consequently, the overcurrent limitation cannot be achieved by setting threshold value for the current reference. Moreover, since the SLVM loop usually has a low control bandwidth, the virtual impedance scheme that modifies the voltage magnitude reference  $V_{ref}$  fails to fast limit the transient overcurrent.

Considering these limitations, the proposed current limiting method is composed of two parts. The first part is to adjust the power references of droop controllers, which is to limit the steady-state fault current. The second part is to implement a transient virtual resistor  $R_{\nu}$  for the limitation of the transient overcurrent during fault-inception and -clearing periods, and  $R_{\nu}$ is realized by directly modifying the converter modulation reference. The detailed analysis of these two parts will be given in the following parts.

## B. Outer Power Reference Adjustment

Instead of limiting the current reference, the steady-state converter output current during the grid fault can be limited by changing the active and reactive power references [22]. Inspired by the grid code requirement for the reactive current during FRT [2], [22], the fault-mode reactive power reference  $Q_f$  can be computed as

$$Q_{f} = \begin{cases} Q_{0} & \text{if } E_{pu} > 0.9\\ 2E_{pu}S \cdot (1 - E_{pu}) & \text{if } 0.5 < E_{pu} \le 0.9\\ E_{pu} \cdot S & \text{if } E_{pu} \le 0.5 \end{cases}$$

(4)

where  $E_{pu}$  is the per unit value of the grid voltage, S is the rated apparent power of the GFM converter. Once  $Q_f$  is determined based on the depth of voltage sag, the fault-mode active power reference  $P_f$  can then be calculated as

$$P_f = \sqrt{\left(E_{pu} \cdot S\right)^2 - Q_f^2} \tag{5}$$

From (4), it is known that the power control reference is adjusted based on the voltage magnitude. It should be noted that the purpose of the power reference adjustment in our work differs from that of the existing ones applied to the GFL converters [2], [29]. In the case of GFL converters, the power reference adjustment is equivalent to the current reference modification due to their current-control characteristic. Such equivalence is guaranteed by the closed-loop vector-current control with high control bandwidth. However, this equivalence is no longer valid for the GFM converters due to their voltagecontrol characteristic. Hence, although the similar form of power reference adjustment is applied in the presented work, its effect on the fault current limitation is fundamentally different from that of GFL converters, and the actual output currents with such power reference adjustment during the faults need to be investigated.

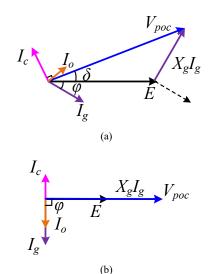

To analyze the effect of the power reference adjustment on the steady-state overcurrent, the magnitude of the converter steady-state output currents during FRT can be calculated based on the phasor diagrams of the system under different grid voltage sags, which are illustrated in Fig. 2. The power angle  $\delta$ is the phase angle difference between  $v_{poc}$  and e,  $\varphi$  is the phase angle difference between e and  $i_g$ , and  $X_g = \omega_1 L_g$  is the grid impedance. According to the IEEE Std. 1159-2019 [30], the typical range of grid voltage sag, which is between 0.1 and 0.9 p.u., is selected in the presented work.

Fig. 2 Steady-state phasor diagrams of the GFM converter during fault ridethrough when (a)  $0.5 < E_{pu} \le 0.9$ , (b)  $0.1 \le E_{pu} \le 0.5$ .

## IEEE POWER ELECTRONICS REGULAR PAPER

Based on (4) and (5), when the depth of grid voltage sag is within the range of (0.5, 0.9), the GFM converter will inject both active and reactive power during FRT, where the steadystate phasor diagram is shown in Fig. 2(a). In this case, the power transfer between PoC and the grid can be calculated as

$$P = \frac{3}{2} \cdot \frac{E \cdot V_{poc}}{X_g} \cdot \sin \delta \tag{6}$$

$$Q = \frac{3}{2} \cdot \frac{V_{poc}^2 - EV_{poc} \cos \delta}{X_g}$$

(7)

During the grid fault, P is equal to its reference value  $P_f$ .  $V_{poc}$  is also equal to its reference value due to the regulation of the SLVM control, which is given by

$$V_{poc} = K_q \left( Q_f - Q \right) + V_n \tag{8}$$

Thus, with a certain grid voltage sag, the steady-state operating point ( $V_{poc}$ ,  $\delta$ ) can be solved from (6), (7), and (8). Then, based on Fig. 2(a), the magnitude of grid-side current  $I_g$  and filter capacitor current  $I_c$  are obtained as

$$I_g = \frac{\sqrt{V_{poc}^2 + E^2 - 2EV_{poc}\cos\delta}}{X_g} \tag{9}$$

$$I_c = \omega_{\rm l} C_f V_{poc} \tag{10}$$

Further,  $\varphi$  can be calculated based on the output active power, which is expressed as

$$\varphi = \arccos\left(\frac{2}{3} \cdot \frac{P_f}{V_{poc} \cdot I_g}\right) - \delta \tag{11}$$

Finally, the magnitude of the steady-state converter output current  $I_o$  can be calculated based on Fig. 2(a), which is given by

$$I_o = \sqrt{I_g^2 + I_c^2 - 2I_g I_c \cos\left(\frac{\pi}{2} - \delta - \varphi\right)}$$

(12)

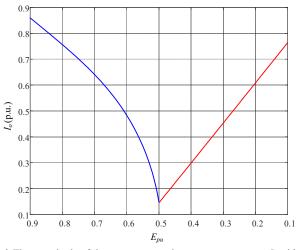

Following the above procedure, the steady-state converter output current magnitude  $I_o$  under different grid voltage sags can be derived, and the corresponding results are shown in Fig.

Fig. 3 The magnitude of the converter steady-state output current  $I_o$  with the outer power reference adjustment under different depths of grid voltage sag.

3, where the short circuit ratio SCR = 2.3 is taken as an example. It is interesting to be noted that, when  $E_{pu}$  falls into the range of (0.5, 0.9), the outer power reference adjustment will make  $I_o$  decrease with the increase of the depth of grid voltage sag. Specifically,  $I_o$  is always below the admissible value of the current limitation  $I_{lim}$  ( $I_{lim}$  = 1.2 p.u. is set in this study), which confirms the effectiveness of the proposed method in this fault range.

Similarly, when the depth of grid voltage sag is within the range of (0.1, 0.5),  $I_o$  can also be calculated based on the phasor diagram shown in Fig. 2(b). According to (4), the GFM converter only provides the reactive power to the grid for supporting the PoC voltage, while the output active power is zero. Consequently,  $v_{poc}$  and e will be in the same phase leading to  $\delta = 0$  and  $\varphi = \pi/2$ . Based on (7) and (8),  $V_{poc}$  is solved as

$$V_{poc} = \frac{1.5K_q E - X_g + \sqrt{\left(X_g - 1.5K_q E\right)^2 + 6K_q X_g \left(V_n + K_q Q_f\right)}}{3K_q}$$

(13)

Then, according to Fig. 2(b),  $I_o$  can be readily obtained as

$$I_o = \left| \frac{V_{poc} - E}{X_g} - \omega_{\rm l} C_f V_{poc} \right| \tag{14}$$

The corresponding results are also shown in Fig. 3. Differing from the previous situation,  $I_o$  will increase with the increase of the depth of grid voltage sag when  $E_{pu}$  is within the range of (0.1, 0.5).  $I_o$  will reach to the maximum value when  $E_{pu} = 0.1$ p.u. Thanks to the power reference adjustment, even when  $E_{pu}$ falls to 0.1 p.u.,  $I_o$  will not exceed  $I_{lim}$  either. Therefore, the power reference adjustment can effectively limit the steadystate converter output current during FRT no matter what the depth of grid voltage sag is. It is worth noting that the resulted steady-state current magnitudes presented in Fig. 3 may not fulfill the requirement of current injection with the maximum allowable amplitude during a fault, e.g., 1.0 p.u. reactive current injection when the voltage drops below 0.5 p.u. Besides, the low magnitude of fault current may bring challenges to the protection systems in the power grids. Such current magnitude characteristics are due to the prioritization of voltage source behavior of GFM converter during grid faults, which makes its output current dependent on the fault impedance [31]. As a result, the magnitude of the output currents cannot be controlled to the maximum value, which is one limitation of the proposed current limiting method. How to inject the fault currents with the maximum allowable magnitude while simultaneously keeping the converter in the GFM control mode still remains an open issue.

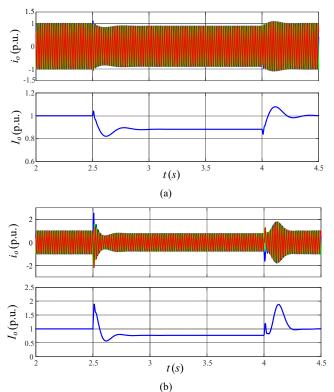

This method is tested by the PSCAD/EMTDC simulation to further demonstrate its effectiveness. The simulated results with two different grid voltage sags (i.e.,  $E_{pu}$  drops from 1.0 p.u. to 0.9 p.u. or 0.1 p.u.) are presented in Fig. 4, where the grid voltage sag occurs at 2.5s and is cleared at 4.0s. The main system parameters used for simulation tests are listed in Table I, where the nominal grid voltage and rated power of the GFM converter are chosen based on the voltage and power levels of the distributed generation systems. The parameters of the *LC*

#### IEEE POWER ELECTRONICS REGULAR PAPER

Fig. 4 Simulated fault response of the GFM converter with proposed power reference adjustment under different depths of grid voltage sag. (a)  $E_{pu}$  drops to 0.9 p.u., (b)  $E_{pu}$  drops to 0.1 p.u.

TABLE I

MAIN SYSTEM PARAMETERS FOR SIMULATION TESTS

| Item                             | Symbol   | Value                          |

|----------------------------------|----------|--------------------------------|

| Grid voltage ( <i>l-g</i> , rms) | е        | 2kV (1.0 p.u.)                 |

| Grid fundamental frequency       | $f_1$    | 50Hz                           |

| Switching frequency              | $f_{sw}$ | 10kHz                          |

| Filter inductor                  | $L_{f}$  | 0.05H (0.13 p.u.)              |

| Filter capacitor                 | $C_{f}$  | 1.06µF (0.04 p.u.)             |

| Grid impedance                   | $L_g$    | 0.16H (0.42 p.u.)              |

| Rated active power               | $P_0$    | 100kW (1.0 p.u.)               |

| Rated reactive power             | $Q_0$    | 0Var                           |

| P-f droop coefficient            | $K_p$    | $0.05\omega_1/P_0$ (0.05 p.u.) |

| Q-V droop coefficient            | $K_q$    | $0.10V_n/P_0$ (0.10 p.u.)      |

| Short-circuit ratio              | SCR      | 2.3                            |

filter are designed based on the guideline in [32] to achieve a satisfied attenuation of high-order switching ripples.  $L_g$  is selected to emulate a relatively weak grid, where SCR = 2.3. To analyze the impact of the proposed current limiting method on the system transient stability, two droop coefficients are selected to ensure the existence of a stable equilibrium point (EP), i.e., the system is stable when small disturbances are imposed around the EP, which is the necessary condition for the transient stability [10]. The selection of  $K_p$  and  $K_q$  can be readily done based on the well-documented small-signal model and eigenvalue analysis [26].

Both the three-phase instantaneous converter output current  $i_o$  and its magnitude  $I_o$  are illustrated. From the simulated waveforms of two cases, it is clear that the fault steady-state  $I_o$

can both be well restrained below 1.2 p.u. by the power reference adjustment during FRT. However, it is found from Fig. 4(b), that during fault-inception and fault-clearing periods,  $I_o$  will exceed  $I_{lim}$ , which means that the power reference adjustment fails to limit the overcurrent during these two transient periods. This is due to the low bandwidth of outer power control loops. Hence, the power reference adjustment is mainly responsible for limiting the fault current at steady state, which is a unique feature compared to the existing studies. In addition to the power reference adjustment, a proper method is necessary to fast restrain the transient fault current, which will be discussed in the following part.

## C. Transient Virtual Resistor

To effectively limit the transient fault current, the mechanism of transient overcurrent during fault-inception and -clearing periods is revealed first. At the fault-inception instant, since  $v_o$ cannot change instantaneously, there will be a large voltage difference between the converter output terminal and the grid when the grid voltage sag occurs. Such large voltage difference will impose on the output filter and grid-side inductor. Due to the inherent characteristic of the inductors, the currents flowing through the inductors contain two parts: a periodic component, which is the fault ac current, and a dc-bias component, which will decrease exponentially because of the parasitic resistance of the inductors [33]. Since the filter capacitor blocks this dc component, it flows through the inductors, which contributes to the converter output current. Hence, the overcurrent during this transient period is mainly caused by such dc-bias component. The similar mechanism can also be found in the transient current during fault-clearing period, where the large voltage difference is caused by the recovered grid voltage.

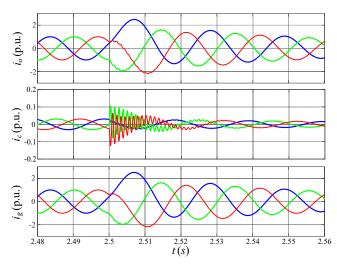

To intuitively illustrate the characteristic of fault current during these two transient periods, a simulated case during the fault-inception period is illustrated in Fig. 5 as an example, where the grid voltage sag (1.0 p.u.  $\rightarrow$  0.1 p.u.) happens at 2.5s. According to the three-phase waveforms of  $i_o$  and  $i_g$ , the fault overcurrent is mainly caused by the dc-bias component. Hence,

Fig. 5 Simulated fault currents response of the GFM converter with proposed power reference adjustment during fault-inception period. ( $E_{pu}$  drops from 1.0 p.u. to 0.1 p.u.)

IEEE POWER ELECTRONICS REGULAR PAPER

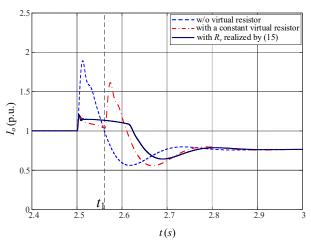

Fig. 6 When  $E_{pu}$  drops from 1.0 p.u. to 0.1 p.u. at t = 2.5s, the simulated output current magnitude of the GFM converter with and without the transient virtual resistor  $R_v$  during fault-inception period. The power reference adjustment is implemented for all the three cases.

Fig. 7 When  $E_{\rho u}$  drops from 1.0 p.u. to 0.1 p.u. at t = 2.5s, the simulation waveforms of the transient virtual resistor  $R_v$  realized by (15) and the resultant output current magnitude  $I_o$  during fault-inception period. The power reference adjustment is also implemented.

the transient overcurrent can be effectively limited by fast minimizing this dc-bias component. The decay rate of this dc component is related with the resistance between the converter output terminal and the grid. The larger resistance leads to the faster decay rate, which means a better limitation on the transient overcurrent. Consequently, the implementation of a transient virtual resistor  $R_{\nu}$  in series with the filter inductor is expected to effectively restrain the transient overcurrent.

To achieve a fast overcurrent limitation,  $R_{\nu}$  is realized by directly modifying the converter modulation voltage reference as shown in Fig. 1, which is different from conventional virtual impedance-based current limiting methods. By doing so, the response speed of  $R_{\nu}$  will not be constrained by the bandwidth of power and voltage control loops, which can thus realize a relatively fast overcurrent limitation. Taking the fault-inception period as an example, the simulated output current magnitudes with and without a constant  $R_{\nu}$  are presented in Fig. 6, where the same fault with that in Fig. 5 is emulated. Compared to the case without the virtual resistor,  $R_{\nu}$  can effectively constrain the overcurrent in the first few fundamental cycles. When  $I_o$  is limited below the threshold value,  $R_{\nu}$  is intentionally disabled at  $t_1$  to avoid its adverse effect on the steady-state performance during FRT. However, an undesired transient dynamic caused by the bypass of  $R_v$  can be observed in Fig. 6, where the GFM converter output current would exceed  $I_{lim}$  again.

To solve the above issue, instead of a constant  $R_{\nu}$ , the virtual resistance can be set to be in proportional to the overcurrent, which is expressed by

$$R_{v} = \begin{cases} k \cdot (I_{o} - I_{th}) & \text{if } I_{o} \ge I_{th} \\ 0 & \text{if } I_{o} < I_{th} \end{cases}$$

(15)

where  $I_{th}$  is the threshold value of the current limitation.  $I_{th}$  is intentionally set slightly smaller than  $I_{lim}$  to ensure a robust performance of the overcurrent limitation. In this paper,  $I_{th} = 1.1$  p.u. is selected. *k* is the proportional gain.

Based on (15), the activation of  $R_{\nu}$  is based on the converter output current magnitude  $I_o$ . When  $I_o \ge I_{th}$ , the value of  $R_v$  is proportional to the difference between  $I_o$  and  $I_{th}$ . Otherwise,  $R_v$ equals to 0. Since  $I_{th}$  is set to be larger than the nominal value,  $R_{\nu}$  will not be activated in the normal operating condition. The value of k is determined in the worst-case scenario of a threephase bolted fault. To illustrate its effectiveness, the simulation waveforms of  $R_{\nu}$  and the resulted output current magnitude during the fault-inception are shown in Fig. 7. It is observed that, once  $I_o$  exceeds  $I_{th}$ ,  $R_v$  is activated to constrain the fault current. With the decrease of  $I_o$ ,  $R_v$  will decrease, and continuously reduces to 0 when  $I_o = I_{th}$  causing the disable of  $R_v$ . Afterwards, the power reference adjustment will make  $I_o$  further decrease below  $I_{th}$  to reach its steady-state value, and  $R_v$  will not be activated again since  $I_o < I_{th}$ . As a result, there is no oscillations between operation with and without  $R_{\nu}$ .

To clearly compare the performance of such adaptive  $R_v$  with that of the constant one, the simulation waveform of  $I_o$  in Fig. 7 is also presented in Fig. 6. It is clear that, compared to the case with a constant  $R_v$ , the implementation of  $R_v$  by (15) can effectively restrain the transient fault current while having a much smoother dynamic process.

It is noted that only the symmetrical faults have been considered in the above-mentioned analysis. As the essence of the transient virtual resistor is to increase the output impedance of the GFM converter for limiting the overcurrent, and  $R_v$  is adaptively adjusted based on the output current magnitude, its effectiveness is independent of the fault types and faulted phase. Hence,  $R_v$  can also be used to constrain the transient overcurrent in the presence of asymmetrical faults. The only adaptation is to replace  $I_o$  in (15) with the maximum current magnitude  $I_{pk}$  among the three phases, which can be calculated based on the sequence component decomposition of the measured three-phase output currents [18].

However, if only the positive-sequence current is injected during asymmetrical faults, the voltage will be boosted in the non-faulty phases, which tends to cause the overvoltage [34]. Moreover, the lack of negative-sequence current injection will lead to power oscillations during the fault [29]. Hence, differing from symmetrical faults, the accurate control of negativesequence current is necessary during asymmetrical faults. Since the objective of the proposed method is to preserve the voltage source behavior of GFM converter during symmetrical faults, the power reference adjustment cannot be directly applied to

#### IEEE POWER ELECTRONICS REGULAR PAPER

asymmetrical faults for the steady-state current limitation. More research work is needed to precisely control the negativesequence current while simultaneously keeping the voltage source behavior during asymmetrical faults.

#### III. IMPACT OF PROPOSED METHOD ON TRANSIENT STABILITY

The transient stability of GFM converters, i.e., the ability of converters to maintain synchronism with the power grid when subjected to large disturbances, is critical to resilient operation of power system [35], [36]. However, it has been reported in [3] and [10] that the current limitation may make the GFM converter more prone to lose the synchronism with the grid. Hence, it is important to investigate the impact of the proposed current limiting method on the system transient stability.

## A. Dynamic Representation of the SLVM-Controlled GFM Converter with Proposed Current Limiting Method

Since the *P*-*f* droop controller dictates the phase angle of  $v_o$ , rather than that of filter capacitor voltage, the output *LC* filter should be considered in the transient stability analysis [27]. Besides, the proposed transient virtual resistor is in series with  $L_f$ . Hence, based on Fig. 1, the system equivalent circuit can be obtained in Fig. 8, where the phase angle of the grid voltage is taken as the reference angle.  $v_{oi}$  is the converter terminal voltage before the transient virtual resistor.  $\delta'$  is the phase angle difference between  $v_{oi}$  and *e*. It has been proved that the filter capacitor has little effect on the transient stability due to the integrator of the SLVM control [27]. The filter capacitor is thus neglected in the following analysis.

GFM converter achieves its synchronism with grid through the *P-f* droop controller. Hence, the system transient stability during FRT is determined by the dynamic response of  $\delta'$ , whose dynamic behavior with the proposed current limiting method can be modeled as

$$\delta' = \frac{K_p}{s} \cdot \frac{\omega_p}{s + \omega_p} \cdot \left( P_f - \frac{3}{2} \cdot \frac{E \cdot V_{poc}}{X_g} \cdot \sin \delta \right)$$

(16)

where  $\omega_p$  is the cutoff frequency of the first-order low-pass filter (LPF). Differing from the GFM converter with VVC [36],  $V_{poc}$  cannot be regarded as a constant value. On the contrary, its dynamic is governed by the *Q-V* droop and the SLVM control. Based on (2), (4), and (7), and considering the LPF for the power measurement filtering, the voltage magnitude reference  $V_{ref}$  for the SLVM control during the fault can be derived as

$$V_{ref} = \frac{K_q \omega_p}{s + \omega_p} \cdot \left( Q_f - \frac{3}{2} \frac{V_{poc}^2 - EV_{poc} \cos \delta}{X_g} \right) + V_n \tag{17}$$

Then, by substituting (17) into (3), the dynamic of the voltage magnitudes is given by

$$V = \frac{k_{iv}}{s} \cdot \left[ \frac{K_q \omega_p}{s + \omega_p} \cdot \left( Q_f - \frac{3}{2} \frac{V_{poc}^2 - EV_{poc} \cos \delta}{X_g} \right) + V_n - V_{poc} \right]$$

(18)

Consequently, the dynamic of  $V_{poc}$  will be coupled with that of  $\delta'$  leading to a more complex system dynamic behavior. By applying the derivation on both sides of (16) and (18), the

Fig. 8 The equivalent circuit of the SLVM-controlled GFM converter with the proposed current limiting method.

Fig. 9 Phasor diagram of the SLVM-controlled GFM converter with the proposed current limiting method when neglecting the filter capacitor.

system dynamic behavior can be represented by the following two differential equations:

$$\ddot{\delta}' = -\omega_p \dot{\delta}' + \omega_p K_p \cdot \left( P_f - \frac{3}{2} \cdot \frac{E \cdot V_{poc}}{X_g} \cdot \sin \delta \right)$$

(19)

$$\ddot{V} = -\omega_p \dot{V} + k_{iv} K_q \omega_p \left( Q_f - \frac{3}{2} \frac{V_{poc}^2 - EV_{poc} \cos \delta}{X_g} \right)$$

$$+ k_{iv} \omega_p \cdot \left( V_n - V_{poc} \right) - k_{iv} \dot{V}_{poc}$$

(20)

It is clear from (19) and (20) that the relationships between  $\delta'$  and  $\delta$ , V and  $V_{poc}$  should be determined first to obtain the dynamic trajectory of  $\delta'$  during fault-inception and -clearing periods.

According to Fig. 8, when the effect of the filter capacitor is neglected, the phasor diagram of the GFM converter with the proposed current limiting method can be obtained in Fig. 9. By using trigonometric operations, their dynamic relationships can be readily solved from the phasor diagram. Since the obtained analytical expressions are relatively complex, only the compact forms are presented in (21), where  $\delta$  and  $V_{poc}$  can be represented by the functions of  $\delta'$  and V, respectively.

$$\begin{cases} \delta = f(\delta', V) \\ V_{poc} = g(\delta', V) \end{cases}$$

(21)

By substituting (21) into (19) and (20), the dynamic behavior of the SLVM-controlled GFM converter with the proposed current limiting method can be fully expressed by these two differential equations consisting of two state variables  $\delta'$  and V. Then, the phase portrait [38], which is an effective tool in the non-linear system analysis, is adopted in the following part to investigate the impact of the current limiting method on system transient stability.

## B. Phase Portrait-Based Transient Stability Analysis

#### IEEE POWER ELECTRONICS REGULAR PAPER

ς.

$$\begin{aligned} \dot{x}_{1} &= x_{2} \\ \dot{x}_{2} &= -\omega_{p}x_{2} + \omega_{p}K_{p} \cdot \left(P_{f} - \frac{3}{2} \cdot \frac{E \cdot g(x_{1}, x_{2})}{X_{g}} \cdot \sin[f(x_{1}, x_{2})]\right) \\ \dot{x}_{3} &= x_{4} \\ \dot{x}_{4} &= -\omega_{p}x_{4} + k_{iv}K_{q}\omega_{p} \left(Q_{f} - \frac{3}{2} \cdot \frac{g^{2}(x_{1}, x_{2}) - E \cdot g(x_{1}, x_{2}) \cdot \cos[f(x_{1}, x_{2})]}{X_{g}}\right) + k_{iv}\omega_{p} \cdot \left[V_{n} - g(x_{1}, x_{2})\right] - k_{iv}\dot{g}(x_{1}, x_{2}) \end{aligned}$$

(22)

It is known that the dynamic response of  $\delta'$  under a grid fault, which determines system transient stability, can be reflected by the phase portrait showing  $\dot{\delta}' - \delta'$  curve. The changing trend of  $\delta'$  can be readily observed from the phase portrait, where  $\delta'$  will increase when  $\dot{\delta}' > 0$  and decrease when  $\dot{\delta}' < 0$ . The points at which  $\dot{\delta}' = 0$  are the EPs. The transient stability will be achieved only when  $\delta'$  converges to a stable EP during the grid fault. Otherwise,  $\delta'$  will diverge leading to the transient instability of the GFM converter.

To obtain the phase portrait from (19) and (20), four state variables, i.e.,  $x_1 = \delta'$ ,  $x_2 = \delta'$ ,  $x_3 = V$ ,  $x_4 = \dot{V}$ , are defined. Then, combined with (21), the differential equations in (19) and (20) can be rewritten in (22) (shown at the top of this page).

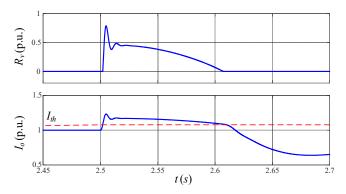

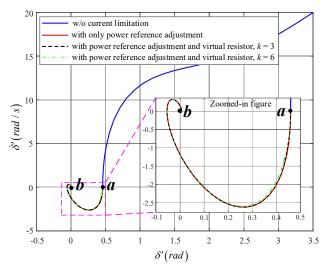

Further, the Matlab command "ode45" is applied to solve (22), and the phase portraits of the GFM converter with the proposed current limiting method are plotted in Fig. 10, where the grid voltage drops from 1.0 p.u. to 0.1 p.u. To have a direct comparison, the phase portraits without the proposed current limiting method and with only power reference adjustment are also presented in Fig. 10. Point *a* denotes the stable EP of the system before the fault. It is observed that, without the proposed current limiting method, the GFM converter cannot keep synchronism with the grid since  $\delta'$  shows a diverging trajectory when the fault occurs. On the contrary, when the outer power reference adjustment is implemented, the transient stability of the GFM converter can be assured with  $\delta'$  converging to a new

Fig. 10 Phase portraits of the SLVM-controlled GFM converter with and without the proposed current limiting method. ( $E_{pu}$  drops from 1 p.u. to 0.1 p.u.)

stable EP b after the fault. Since the output active power of the GFM converter is regulated to be zero, the EP b is expected to locate at the origin (0, 0), which is exactly matched with the phase portrait.

In addition, when the proposed current limiting method is implemented, i.e., both the outer power reference adjustment and transient virtual resistor are enabled, the phase portraits are almost the same as that with only power reference adjustment. It can also be seen from Fig. 10 that different virtual resistances have little effect on the phase portrait. This is because that the outer power control and the SLVM control loops dominate the system dynamics in the timescale of transient instability, while the transient virtual resistor in merely activated at the instants of the fault-inception and -clearing period, which is switched to zero after the current magnitude is below the threshold value. The timescale of transient virtual resistor is much faster than that of transient stability. This can be checked from Fig. 7 that the time duration with the activation of virtual resistor only lasts for about 0.1s. The same result can also be observed from the following experimental waveforms shown in Fig. 19.

Therefore, the proposed current limiting method can not only restrain possible overcurrent during FRT, but also enhance the system transient stability through the adjustment of power reference. The converter is capable of keeping the GFM control mode during FRT.

## IV. EXPERIMENTAL RESULTS

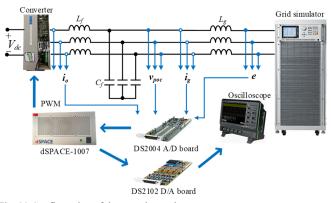

To further verify the effectiveness of the proposed current limiting method, the downscaled experimental tests are conducted. The configuration of the experimental setup is shown in Fig. 11, where the main system parameters are listed in Table II. The per unit values of these parameters are kept the

Fig. 11 Configuration of the experimental setup.

#### IEEE POWER ELECTRONICS REGULAR PAPER

TABLE II

MAIN SYSTEM PARAMETERS FOR EXPERIMENTAL TESTS

| Item                         | Symbol   | Value                          |

|------------------------------|----------|--------------------------------|

| Grid voltage (l-g, rms)      | е        | 50V (1.0 p.u.)                 |

| Grid fundamental frequency   | $f_1$    | 50Hz                           |

| Switching frequency          | $f_{sw}$ | 10kHz                          |

| Filter inductor              | $L_{f}$  | 3mH (0.13 p.u.)                |

| Filter capacitor             | $C_{f}$  | 15µF (0.04 p.u.)               |

| Grid impedance               | $L_g$    | 10mH (0.42 p.u.)               |

| Rated active power           | $P_0$    | 1kW (1.0 p.u.)                 |

| Rated reactive power         | $Q_0$    | 0Var                           |

| <i>P-f</i> droop coefficient | $K_p$    | $0.05\omega_1/P_0$ (0.05 p.u.) |

| Q-V droop coefficient        | $K_q$    | $0.10V_n/P_0$ (0.10 p.u.)      |

| Short-circuit ratio          | SCR      | 2.3                            |

same with those in the simulation tests. The control algorithm is implemented in the DS1007 dSPACE system. A constant dc voltage supply is used to power the dc-side. The power grid is emulated by a *Chroma Grid Simulator* 61845, which can be programmed to emulate different types of grid faults.

## A. Verification of Outer Power Reference Adjustment

The effectiveness of the power reference adjustment on the steady-state fault currents limitation is examined first. Based on Fig. 3, when the depth of grid voltage sag is within the range of (0.1, 0.9), it is found that  $E_{pu} = 0.1$  and 0.9 p.u. are two critical cases with the largest magnitude of steady-state output currents. Besides, another critical scenario is the case with the smallest current magnitude when  $E_{pu} = 0.5$  p.u. Hence, these three cases are selected and tested, respectively.

Fig. 12 shows the experimental waveforms with only the power reference adjustment when the grid voltage drops from 1.0 to 0.9 p.u. From Fig. 12(a), it can be observed that the output active and reactive power will follow their new reference values determined by (4) and (5) when the grid fault happens. Hence, the steady-state output current magnitude  $I_0$  is limited below 1.2 p.u. (1 p.u. = 9.43 A in the experimental tests). Besides, the steady-state value of I<sub>o</sub> during FRT is in accordance with the theoretical calculation in Fig. 3. Once the fault is cleared, the converter output power will return back to their nominal values as shown in Fig. 12(b). A slight overshoot is observed in Io during this transient period, and the peak value does not exceed 1.2 p.u. due to the relatively small depth of grid voltage sag. To clearly demonstrate the dynamic response of the output currents, the experimental waveforms of the three-phase output currents during fault-inception and -clearing periods are also presented in Fig. 13.

Next, the case when the grid voltage drops to 0.5 p.u. is tested. For simplicity, only the experimental results during the fault-inception period are presented in Fig. 14 to demonstrate the effectiveness of the power reference adjustment. It is observed that the steady-state  $I_o$  during the fault is also in accordance with the theoretical result shown in Fig. 3, which is well below the admissible value of current limitation.

Finally, the situation becomes much challenging when the grid voltage drops to 0.1 p.u., where the experimental results are shown in Fig. 15. It is observed that the GFM converter will output zero active power during FRT. Thanks to the power

Fig. 12 When the grid voltage  $E_{pu}$  drops from 1.0 p.u. to 0.9 p.u., the experimental results of the SLVM-controlled GFM converter with only power reference adjustment during (a) fault-inception period, (b) fault-clearing period.

Fig. 13 When the grid voltage  $E_{pu}$  drops from 1.0 p.u. to 0.9 p.u., the experimental waveforms of the three-phase converter output currents and its magnitude with only power reference adjustment during (a) fault-inception period, (b) fault-clearing period.

IEEE POWER ELECTRONICS REGULAR PAPER

Fig. 14 When the grid voltage  $E_{pu}$  drops from 1.0 p.u. to 0.5 p.u., the experimental results of the SLVM-controlled GFM converter with only power reference adjustment during fault-inception period.

reference adjustment, the steady-state fault current  $I_o$  is also limited well below the admissible value. The corresponding experimental waveforms of the three-phase output currents during these two transient periods are presented in Fig. 16. Hence, the power reference adjustment is verified to effectively constrain the steady-state output current during FRT.

However, from Figs. 15 and 16, during the fault-inception and -clearing periods, the transient-state  $I_{\rho}$  will almost reach to 20A (i.e., 2.1 p.u.), which is far beyond the admissible value. The reason that the converter can withstand such large transient overcurrent without tripping is the intentional adoption of the oversized switching devices. The purpose of doing so is to demonstrate the complete dynamic responses of the GFM converter during fault-inception and -clearing periods without tripping the converter. Consequently, the characteristic of the fault currents during these two transient periods can be clearly revealed. Moreover, the experimental results in Figs. 15 and 16 can thus match well with the simulation waveforms in Fig. 4(b). From Fig. 16(b), it is observed that there exist two peaks in the transient-state  $I_{o}$  after fault clearance. The transient overcurrent during the first-peak period is caused by the recovered grid voltage. During this period, due to the slow dynamic of the outer power control loops, the power reference adjustment will not take effect on the dynamic responses of the converter output current. Meanwhile, since  $E_{pu}$  recovers to its nominal value at the fault-clearing instant, there will be a large voltage difference between the converter output terminal and grid, which leads to the first peak of the transient overcurrent. After that, the power reference adjustment starts to take effect on  $i_0$ . Hence, the transient overcurrent during the second-peak period can be attributed to the power reference adjustment.

Based on the above observations, the incapability of the outer power reference adjustment to limit the fault current during these two transient periods is confirmed, which necessitates the use of transient virtual resistor for limiting the transient overcurrent.

## B. Verification of Transient Virtual Resistor

Since the larger depth of grid voltage sag leads to the more severe overcurrent during fault-inception and -clearing periods, only the worst scenario where the grid voltage drops to 0.1 p.u. is tested to verify effectiveness of the transient virtual resistor.

Fig. 15 When the grid voltage  $E_{pu}$  drops from 1.0 p.u. to 0.1 p.u., the experimental results of the SLVM-controlled GFM converter with only power reference adjustment during (a) fault-inception period, (b) fault-clearing period.

Fig. 16 When the grid voltage  $E_{pu}$  drops from 1.0 p.u. to 0.1 p.u., the experimental waveforms of the three-phase converter output currents and the magnitude with only power reference adjustment during (a) fault-inception period, (b) fault-clearing period.

Fig. 17 When the grid voltage  $E_{pu}$  drops from 1.0 p.u. to 0.1 p.u., the experimental results of the SLVM-controlled GFM converter with both power reference adjustment and transient virtual resistor during (a) fault-inception period, (b) fault-clearing period.

Fig. 18 When the grid voltage  $E_{pu}$  drops from 1.0 p.u. to 0.1 p.u., the experimental waveforms of the three-phase converter output currents and the magnitude with both power reference adjustment and transient virtual resistor during (a) fault-inception period, (b) fault-clearing period.

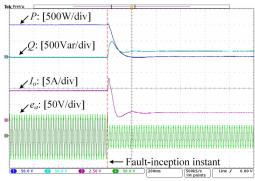

Fig. 17 shows the experimental results when the GFM converter employs both outer power reference adjustment and transient virtual resistor control. Comparing Fig. 17(a) with Fig. 15(a), it is clear that  $I_o$  during the fault-inception period is well limited below 1.2 p.u. by the transient virtual resistor. The effective overcurrent attenuation is also observed during the fault-clearing period in Fig. 17(b). Such satisfied overcurrent limiting performance can be further confirmed by comparing the three-phase output currents presented in Fig. 18 with those in Fig. 16. In summary, it is proved that the transient virtual resistor can effectively limit the transient fault current.

## *C. Verification of the Impact of Proposed Current Limiting Method on System Transient Stability*

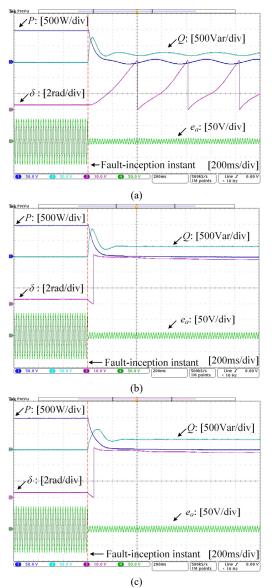

Finally, the impact of the proposed current limiting method on the system transient stability is tested. Fig. 19 shows the

Fig. 19 When the grid voltage  $E_{pu}$  drops from 1.0 p.u. to 0.1 p.u., the experimental results of the SLVM-controlled GFM converter (a) without the proposed current limiting method, (b) with only the outer power reference adjustment, (c) with the proposed current limiting method.

### IEEE POWER ELECTRONICS REGULAR PAPER

experimental results when the grid voltage drops to 0.1 p.u., where the transient stability can be observed from the waveform of  $\delta$ . It is clearly seen from Fig. 19(a) that the GFM converter without using the proposed method loses the synchronism with the grid when the fault happens. In contrast, when the GFM converter is equipped with the power reference adjustment, the system transient stability can be guaranteed even with such a severe grid voltage sag, which is shown in Fig. 19(b). In this circumstance,  $\delta$  will first decrease from its pre-fault value to 0 rad and continuously decrease below 0 rad to a negative value. Finally, it is stabilized at about 0 rad, which is in accordance with the phase portrait shown in Fig. 10. It should be noted that the "phase jump" in Fig. 19(b) is not a real phase jump. The reason for this "phase jump" is because the range of  $\delta$  is set within  $(0, 2\pi)$ . Hence, when  $\delta$  is smaller than 0 rad, its value is flipped to  $\delta + 2\pi$  in the measured waveforms.

Further, when the transient virtual resistor is deployed, the corresponding experimental waveforms are shown in Fig. 19(c). Compared to Fig. 19(b), it is found that the dynamic response of  $\delta$  in Fig. 19(c) is almost the same with that in Fig. 19(b), which also coincides with the phase portraits presented in Fig. 10. Therefore, it is verified that the power reference adjustment can enhance the system transient stability, while the transient virtual resistor has little effect on it.

## V. CONCLUSIONS

This paper presents an effective current limiting method for the SLVM-controlled GFM converters during symmetrical grid faults. Through the power reference adjustment, the converter steady-state output current can be restrained, while the transient overcurrent is limited by the transient virtual resistor. Further, the transient stability analysis based on the phase portrait turns out that the outer power reference adjustment can keep the GFM converter synchronized with the grid during grid faults, while the transient virtual resistor has negligible impact on the transient stability. The experimental results validate that the proposed method can not only achieve the effective fault current limitation, but also keep the converter working in the GFM mode during the FRT.

#### References

- R. H. Lasseter, Z. Chen and D. Pattabiraman, "Grid-Forming Inverters: A Critical Asset for the Power Grid," *IEEE J. Emerg. Select. Topics Power Electron.*, vol. 8, no. 2, pp. 925-935, Jun. 2020.

- [2] E. Afshari, G. R. Moradi, R. Rahimi, B. Farhangi, et al., "Control Strategy for Three-Phase Grid-Connected PV Inverters Enabling Current Limitation Under Unbalanced Faults," *IEEE Trans. Ind. Electron.*, vol. 64, no. 11, pp. 8908-8918, Nov. 2017.

- [3] T. Qoria, F. Gruson, F. Colas, X. Kestelyn, and X. Guillaud, "Current Limiting Algorithms and Transient Stability Analysis of Grid-Forming VSCs", *Electric Power System Research*, vol. 189, Dec. 2020, 106726.

- [4] I. Sadeghkhani, M. E. H. Golshan, J. M. Guerrero, and A. M. Sani, "A Current Limiting Strategy to Improve Fault Ride-Through of Inverter Interfaced Autonomous Microgrids," *IEEE Trans. Smart Grid*, vol. 8, no. 5, pp. 2138-2148, Sept. 2017.

- [5] K. O. Oureilidis and C. S. Demoulias, "A Fault Clearing Method in Converter-Dominated Microgrids With Conventional Protection Means," *IEEE Trans. Power Electron.*, vol. 31, no. 6, pp. 4628-4640, June 2016.

- [6] A. Camacho, M. Castilla, J. Miret, A. Borrell, and L. G. de Vicuña, "Active and Reactive Power Strategies with Peak Current Limitation for Distributed Generation Inverters During Unbalanced Grid Faults," *IEEE*

Trans. Ind. Electron., vol. 62, no. 3, pp. 1515-1525, Mar. 2015.

- [7] N. Bottrell and T. C. Green, "Comparison of Current-Limiting Strategies During Fault Ride-Through of Inverters to Prevent Latch-Up and Wind-Up," *IEEE Trans. Power Electron.*, vol. 29, no. 7, pp. 3786-3797, July 2014.

- [8] H. Wu and X. Wang, "Design-Oriented Transient Stability Analysis of Grid-Connected Converters with Power Synchronization Control," *IEEE Trans. Ind. Electron.*, vol. 66, no. 8, pp. 6473-6482, Aug. 2019.

- [9] D. Zhu, S. Zhou, X. Zou, and Y. Kang, "Improved Design of PLL Controller for LCL-Type Grid-Connected Converter in Weak Grid," *IEEE Trans. Power Electron.*, vol. 35, no. 5, pp. 4715-4727, May 2020.

- [10] L. Huang, H. Xin, Z. Wang, L. Zhang, K. Wu, and J. Hu, "Transient Stability Analysis and Control Design of Droop-Controlled Voltage Source Converters Considering Current Limitation," *IEEE Trans. Smart Grid*, vol. 10, no. 1, pp. 578-591, Jan. 2019.

- [11] C. Glöckler, D. Duckwitz, and F. Welck, "Virtual Synchronous Machine Control with Virtual Resistor for Enhanced Short Circuit Capability," in *Proc. 2017 IEEE PES ISGT-Europe*, Italy, Sep. 2017, pp. 1-6.

- [12] A. D. Paquette and D. M. Divan, "Virtual Impedance Current Limiting for Inverters in Microgrids With Synchronous Generators," *IEEE Trans. Ind. Appl.*, vol. 51, no. 2, pp. 1630-1638, March-April 2015.

- [13] T. Qoria, F. Gruson, F. Colas, G. Denis, T. Prevost, and X. Guillaud, "Critical Clearing Time Determination and Enhancement of Grid-Forming Converters Embedding Virtual Impedance as Current Limitation Algorithm," *IEEE J. Emerg. Select. Topics Power Electron.*, vol. 8, no. 2, pp. 1050-1061, Jun. 2020.

- [14] X. Lu, J. Wang, J. M. Guerrero, and D. Zhao, "Virtual-Impedance-Based Fault Current Limiters for Inverter Dominated AC Microgrids," *IEEE Trans. Smart Grid*, vol. 9, no. 3, pp. 1599-1612, May 2018.

- [15] P. Rodriguez, I. Candela, and A. Luna, "Control of PV Generation Systems Using the Synchronous Power Controller," in *Proc. 2013 IEEE*-ECCE, Denver, CO, 2013, pp. 993-998.

- [16] W. Zhang, A. M. Cantarellas, J. Rocabert, A. Luna, and P. Rodriguez, "Synchronous Power Controller with Flexible Droop Characteristics for Renewable Power Generation Systems," *IEEE Trans. Sustainable Energy*, vol. 7, no. 4, pp. 1572-1582, Oct. 2016.

- [17] R. Rosso, S. Engelken, and M. Liserre, "Current Limitation Strategy for Grid-Forming Converters Under Symmetrical and Asymmetrical Grid Faults," in *Proc. 2020 IEEE Energy Convers. Congr. Expo.*, Detroit, MI, USA, 2020, pp. 3746-3753.

- [18] S. F. Zarei, H. Mokhtari, M. A. Ghasemi, and F. Blaabjerg, "Reinforcing Fault Ride Through Capability of Grid Forming Voltage Source Converters Using an Enhanced Voltage Control Scheme," *IEEE Trans. Power Del.*, vol. 34, no. 5, pp. 1827-1842, Oct. 2019.

- [19] Y. W. Li and C. Kao, "An Accurate Power Control Strategy for Power-Electronics-Interfaced Distributed Generation Units Operating in a Low-Voltage Multibus Microgrid," *IEEE Trans. Power Electron.*, vol. 24, no. 12, pp. 2977-2988, Dec. 2009.

- [20] T. Qoria, "Grid-Forming Control to Achieve 100% Power Electronics Interfaced Power Transmission Systems," Ph.D. dissertation, ENSAM, Paris, France, 2020.

- [21] G. Denis, T. Prevost, M. Debry, F. Xavier, X. Guillaud, and A. Menze, "The Migrate Project: The Challenges of Operating A Transmission Grid with Only Inverter-Based Generation. A Grid-Forming Control Improvement with Transient Current-Limiting Control," *IET Renewable Power Generation*, vol. 12, no. 5, pp. 523-529, Sep. 2018.

- [22] M. G. Taul, X. Wang, P. Davari, and F. Blaabjerg, "Current Limiting Control with Enhanced Dynamics of Grid-Forming Converters During Fault Conditions," *IEEE J. Emerg. Select. Topics Power Electron.*, vol. 8, no. 2, pp. 1062-1073, June 2020.

- [23] X. Wang and F. Blaabjerg, "Harmonic Stability in Power Electronic-Based Power Systems: Concept, Modeling, and Analysis," *IEEE Trans. Smart Grid*, vol. 10, no. 3, pp. 2858-2870, May 2019.

- [24] E. Alegria, T. Brown, E. Minear and R. H. Lasseter, "CERTS Microgrid Demonstration with Large-Scale Energy Storage and Renewable Generation," *IEEE Trans. Smart Grid*, vol. 5, no. 2, pp. 937-943, Mar. 2014.

- [25] L. Zhang, L. Harnefors, and H. Nee, "Power-Synchronization Control of Grid-Connected Voltage-Source Converters," *IEEE Trans. Power Syst.*, vol. 25, no. 2, pp. 809-820, May 2010.

- [26] W. Du, Z. Chen, K. P. Schnerider, R. H. Lasseter et al., "A Comparative Study of Two Widely Used Grid-Forming Droop Controls on Microgrid

#### IEEE POWER ELECTRONICS REGULAR PAPER

Small-Signal Stability," *IEEE J. Emerg. Select. Topics Power Electron.*, vol. 8, no. 2, pp. 963-975, Jun. 2020.

- [27] T. Liu and X. Wang, "Transient Stability of Single-Loop Voltage-Magnitude Controlled Grid-Forming Converters," *IEEE Trans. Power Electron.*, vol. 36, no. 6, pp. 6158-6162, June 2021.

- [28] Q. Zhong, P. Nguyen, Z. Ma and W. Sheng, "Self-Synchronized Synchronverters: Inverters Without a Dedicated Synchronization Unit," *IEEE Trans. Power Electron.*, vol. 29, no. 2, pp. 617-630, Feb. 2014.

- [29] M. A. Garnica López, J. L. García de Vicuña, J. Miret, M. Castilla, and R. Guzmán, "Control Strategy for Grid-Connected Three-Phase Inverters During Voltage Sags to Meet Grid Codes and to Maximize Power Delivery Capability," *IEEE Trans. Power Electron.*, vol. 33, no. 11, pp. 9360-9374, Nov. 2018.

- [30] "IEEE Recommended Practice for Monitoring Electric Power Quality," IEEE Std 1159-2019 (Revision of IEEE Std 1159-2009), Aug. 2019.

- [31] European Network of Transmission System Operators for Electricity (ENTSO-E), "High Penetration of Power Electronic Interfaced Power Sources and the Potential Contribution of Grid Forming Converters," Report, [available Online]

- [32] G. Lo Calzo, A. Lidozzi, L. Solero, and F. Crescimbini, "LC Filter Design for On-Grid and Off-Grid Distributed Generating Units," *IEEE Trans. Ind. Appl.*, vol. 51, no. 2, pp. 1639-1650, Mar. 2015.

- [33] Z. Shuai, W. Huang, C. Shen, J. Ge and Z. J. Shen, "Characteristics and Restraining Method of Fast Transient Inrush Fault Currents in Synchronverters," *IEEE Trans. Ind. Electron.*, vol. 64, no. 9, pp. 7487-7497, Sept. 2017.

- [34] M. Graungaard Taul, X. Wang, P. Davari, and F. Blaabjerg, "Current Reference Generation Based on Next-Generation Grid Code Requirements of Grid-Tied Converters During Asymmetrical Faults," *IEEE J. Emerg. Select. Topics Power Electron.*, vol. 8, no. 4, pp. 3784-3797, Dec. 2020.

- [35] P. Kundur, *Power System Stability and Control*. New York, NY, USA: Perseus Books, 1994.

- [36] X. Wang, M. G. Taul, H. Wu, Y. Liao, F. Blaabjerg, and L. Harnefors, "Grid-Synchronization Stability of Converter-Based Resources—An Overview," *IEEE Open J. Ind. Appl.*, vol. 1, pp. 115-134, 2020.

- [37] H. Wu and X. Wang, "Design-Oriented Transient Stability Analysis of Grid-Connected Converters with Power Synchronization Control," *IEEE Trans. Ind. Electron.*, vol. 66, no. 8, pp. 6473-6482, Aug. 2019.

- [38] S. H. Strogatz. Nonlinear Dynamics and Chaos: With Applications to Physics, Biology, Chemistry, and Engineering. New York, NY, USA: Perseus Books, 1994.

**Teng Liu** (Member, IEEE) received the B.S. and Ph.D. degrees in electrical engineering from Xi'an Jiaotong University (XJTU), Xi'an, China, in 2012 and 2019, respectively.

He is currently a Postdoc with the AAU Energy, Aalborg University. His current research interests include modeling, control, and stability analysis of grid-connected converters.

Dr. Liu was a recipient of the MPCE Excellent Reviewer Award in 2020.

Xiongfei Wang (Senior Member, IEEE) received the B.S. degree from Yanshan University, Qinhuangdao, China, in 2006, the M.S. degree from Harbin Institute of Technology, Harbin, China, in 2008, both in electrical engineering, and the Ph.D. degree in energy technology from Aalborg University, Aalborg, Denmark, in 2013.

From 2009 he has been with the Department of Energy Technology, Aalborg University, where he became an Assistant Professor in 2014, an Associate

Professor in 2016, a Professor and Leader of Electronic Power Grid (eGRID) Research Group in 2018. He has also been a part-time Professor at KTH Royal Institute of Technology, Stockholm, Sweden, from 2020. His current research interests include modeling and control of power electronic converters and systems, stability and power quality of power-electronics-dominated power systems, high-power converters. Dr. Wang serves as a Member-at-Large of Administrative Committee for the IEEE Power Electronics Society (PELS) in 2020-2022, a Co-Editor-in-Chief for the IEEE Transactions on Power Electronics Letters, and as an Associate Editor for the IEEE Journal of Emerging and Selected Topics in Power Electronics (JESTPE). He was selected into Aalborg University Strategic Talent Management Program in 2016. He has received six Prize Paper Awards in the IEEE Transactions and conferences, the 2018 Richard M. Bass Outstanding Young Power Electronics Engineer Award, the 2019 IEEE PELS Sustainable Energy Systems Technical Achievement Award, the 2020 IEEE Power & Energy Society Prize Paper Award, the 2020 JESTPE Star Associate Editor Award, and the Highly Cited Researcher in the Web of Science in 2019-2021.

**Fangcheng Liu** (Senior Member, IEEE) received the B.S. degree from Huazhong University of Science and Technology, Wuhan, China, in 2007, the Ph.D. degree from Xi'an Jiaotong University, Xi'an, China, in 2014, both in electrical engineering.

Since 2014, he has been with Huawei, where he is currently a Principal Engineer at Digital Power Technology & Strategy Dept (Part of Huawei Digital Power Technologies). His main research interests include modeling and control of grid-connected

converters, and stability of power electronic based power systems.

Kai Xin received the Ph.D. degree in electrical engineering from Huazhong University of Science and Technology, Wuhan, China in 2007.

He was a Researcher at Power Conversion System Control Lab in General Electric Global Research Center, Shanghai, China, from 2007 to 2011. Since 2011, he has been with Huawei, where he is currently a Technical Expert of Power Electronics Technology Lab (Part of Huawei Digital Power Technologies).

PV/wind power generation system, and Energy conversion techniques and applications.

Yunfeng Liu received the Ph.D. degree in electronic engineering from Southeast University, Nanjing, China, in 1999.

He was a Postdoctoral Researcher in the Department of Electrical Engineering of Tsinghua University, Beijing, China, from 1999 to 2001. He was a Visiting Scholar at Virginia Tech-CPES, Virginia, US, from 2001 to 2003. He was the Senior Researcher at General Electric Global Research Center (GE GRC), Shanghai, China and later as

Manager of Power Conversion System Control Lab of GE GRC, from 2003 to 2011. Since 2011, he has been with Huawei, where he is currently the Chief Scientist of Huawei Digital Power Technologies Co., Ltd. His main research interests include High power semiconductor devices, converter and application in power system, and Energy conversion techniques and applications.