FACULDADE DE ENGENHARIA DA UNIVERSIDADE DO PORTO

# **Field-Configurable GPU**

Pedro Rodrigues de Castro

Mestrado Integrado em Engenharia Eletrotécnica e de Computadores

Supervisor: Professor José Carlos Alves

July 20, 2021

### Abstract

This thesis proposes a solution on the topic of high performance computing and the field of study of accelerated data processing.

One well known platform that targets this issue is the GPU. These devices present a SIMT (Single Instruction, Multiple Data) architecture which are ideal to process high amounts of data in parallelizable processes.

So, using them as an inspiration, a GPU micro-architecture was implemented on an FPGA in order to test if the performance would be promising.

In order to optimize as much of the resources of the FPGA (Field Programmable Gate Array) and the performance of the application, this micro-architecture can be reconfigured with different parameters and hardware modules using a software tool created for this project.

This software includes a compiler that interprets an assembly-like program and implements it according to the developed architecture. This way, only the resources needed to execute the application are allocated to the architecture.

To end the design process of this tool, the program constructs the Hardware Description Language (HDL) files with the reconfigured architecture for the given user specification.

The combination of the architecture with the program provides a reconfigurable and flexible platform that enables writing programs for a specific application, while still being easier to program and modify compared to manual HDL instantiating.

To test the design, an FCNN (Fully Connected Neural Network) was implemented using the project's design process and tools. Its performance was compared to other processors, as to obtain a baseline for the benchmark. The results showed a speedup of up to 80 and 7 times compared to an ARM and Intel processor, respectively.

Even though further optimizations could be done to this example in terms of performance, these results showed potential benefits in process acceleration, specially in the embedded systems area.

The tools developed also allow the use cases to scale up depending on the size of the application. ii

### Resumo

Esta tese propõe uma solução no tópico de computação de alta performance e o campo de estudo de processamento de dados acelerado.

Um dos dispositivos mais conhecidos atualmente que é usado nesta área é a Unidade de Processamento Gráfico (GPU). Este é ideal para a aceleração de computações em tarefas que envolvem o processamento de muitos dados em paralelo. Isto é possível devido à sua microarquitectura SIMT (Instrução Única, Múltiplos Dados).

É por este motivo que este projeto toma esta plataforma como inspiração e tenta implementá-la num FPGA (*Field Programmable Gate Array*).

Tirando partido do poder de reconfiguração dos FPGAs, o projeto remove as partes de hardware que não serão usadas na aplicação do utilizador. Isto otimiza os recursos disponíveis do circuito integrado, tal como reduz os tempos de transmissão de dados entre registos.

A ferramenta desenvolvida no contexto da tese compila um programa, escrito de forma semelhante a *Assembly*, para a arquitetura proposta.

No fim do processo de design, a ferramenta constrói os ficheiros HDL (*Hardware Description Language*) que contêm os módulos necessários para a arquitetura conforme os detalhes dados pelo utilizador.

A combinação da arquitetura com o programa disponibiliza ao utilizador uma maior facilidade de modificações e de reconfiguração à sua aplicação comparado com o instanciamento manual.

O design foi testado com a implementação de uma Rede Neuronal Completamente Conectada (FCNN). Para ter uma referência de comparação de resultados, o mesmo algoritmo foi executado em dois processadores. A implementação em FPGA demonstrou uma aceleração do processo 80 e 7 vezes maior do que um processador ARM e Intel, respetivamente.

Apesar deste exemplo ter alguma margem para mais otimizações, os resultados obtidos já são promissores, especialmente na área de sistemas embebidos.

As ferramentas desenvolvidas também permitem o escalamento da aplicação, dependendo do seu tamanho.

iv

## Acknowledgements

I would like to thank my supervisor Prof. José Carlos Alves for his guidance and curiosity throughout all the thesis. I would also like to acknowledge the constant support and advises of my family and my colleagues.

Pedro Rodrigues de Castro

vi

"What I cannot create, I do not understand"

Richard Feynman

viii

## Contents

| 1 | Intr  | oduction                                      | 1 |

|---|-------|-----------------------------------------------|---|

|   | 1.1   | Context                                       | 1 |

|   | 1.2   | Objectives                                    | 1 |

|   | 1.3   | Motivation                                    | 2 |

| 2 | State | e of the Art                                  | 3 |

|   | 2.1   | Accelerated Computing                         | 3 |

|   |       |                                               | 8 |

|   | 2.2   |                                               | 9 |

|   | 2.3   | A Brief History of the GPU                    | 2 |

|   | 2.4   | The modern GPU Architecure                    | 4 |

|   |       | 2.4.1 Memory                                  | 5 |

|   |       | 2.4.2 The GPGPU                               | 7 |

|   | 2.5   | Hardware Improvement Techniques               | 7 |

|   |       | 2.5.1 Speed improvements                      | 7 |

|   |       | 2.5.2 Pre-processing                          | 7 |

|   |       | 2.5.3 SIMD                                    | 8 |

|   |       | 2.5.4 SMT                                     | 9 |

|   |       | 2.5.5 SIMT                                    | 9 |

|   |       | 2.5.6 Superscalar Processors                  | 9 |

|   |       | 2.5.7 DSP in the FPGA                         | 0 |

|   | 2.6   | Power Consumption Improvements                | 1 |

|   |       | 2.6.1 Design/Fabrication low-power techniques | 1 |

|   |       | 2.6.2 Run-time low-power techniques           |   |

| 3 | Arcl  | itecture 2                                    | 5 |

| 5 | 3.1   | First iteration                               |   |

|   | 3.2   | Final version                                 |   |

|   | 3.3   | Branching                                     |   |

|   | 3.4   | Subroutine execution                          |   |

|   | 3.5   | Instructions                                  |   |

|   | 5.5   | 3.5.1 Decoding                                |   |

|   |       | 3.5.2 Instructions and Instruction types      |   |

|   |       |                                               |   |

| 4 |       | generation program 3                          |   |

|   | 4.1   | Program parsing                               |   |

|   | 4.2   | RTL generation                                |   |

|   |       | 4.2.1 Module generation                       | 2 |

|    | 4.3   | Creating | g instructions              | . 42 |

|----|-------|----------|-----------------------------|------|

| 5  | Resu  | ılts     |                             | 45   |

|    | 5.1   | Archited | cture and Program generator | . 45 |

|    | 5.2   | CUDA     | Comparison                  | . 46 |

|    |       | 5.2.1    | Kernel programming          | . 46 |

|    |       | 5.2.2    | Memory management           | . 47 |

|    | 5.3   | Example  | e use case                  | . 48 |

|    |       | _        | The FCNN                    |      |

|    |       | 5.3.2    | Program implementation      | . 51 |

|    |       | 5.3.3    | Resource usage              | . 53 |

|    |       |          | Performance                 |      |

|    |       | 5.3.5    | Optimizations               | . 54 |

|    |       |          | Scalability                 |      |

| 6  | Con   | clusions | and future work             | 57   |

|    | 6.1   |          | ve's fulfilment             | . 57 |

|    | 6.2   |          | work                        |      |

| A  | NVI   | DIA Ter  | ms                          | 59   |

| Re | feren | ces      |                             | 63   |

# **List of Figures**

| 2.1                                                                           | Simplified overview of the FPGA architecture [1]                                       |  |  |  |

|-------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--|--|--|

| 2.2                                                                           | 42 Years of Microprocessor Trend Data [2]                                              |  |  |  |

| 2.3 Left: Homogeneous sixteex 1-BCE cores. Right: Homogeneous four 4-BCE core |                                                                                        |  |  |  |

|                                                                               | [3]                                                                                    |  |  |  |

| 2.4                                                                           | Example of the speedup achieved when distributing sixteen BCEs over the <i>R</i> value |  |  |  |

|                                                                               | with different parallelization values [3]                                              |  |  |  |

| 2.5                                                                           | Heterogeneous one 4-BCE core and 12 1-BCE cores (Total of 16 BCEs) [3] 7               |  |  |  |

| 2.6                                                                           | Example of the speedup achieved when splitting the sixteen BCEs over a larger          |  |  |  |

|                                                                               | core and several 1-BCE cores [3]                                                       |  |  |  |

| 2.7                                                                           | Processor-Memory performance gap [4]                                                   |  |  |  |

| 2.8                                                                           | Example of the roofline model for 3 applications. $App_1$ is bounded by the mem-       |  |  |  |

|                                                                               | ory bandwidth while the other two apps are bound by the processor's peak perfor-       |  |  |  |

|                                                                               | mance [5]                                                                              |  |  |  |

| 2.9                                                                           | Harvard architecture overview 10                                                       |  |  |  |

|                                                                               | Abstract view of the implementation of the MIPS subset [6]                             |  |  |  |

|                                                                               | The traditional fixed-function graphics pipeline (Modified from [7]) 13                |  |  |  |

|                                                                               | Unified hardware shader design (Modified from [7])                                     |  |  |  |

|                                                                               | NVIDIA®'s Streaming Multiprocessor [8]                                                 |  |  |  |

|                                                                               | CUDA Memory hierarchy [9]                                                              |  |  |  |

|                                                                               | Branching effect [8]                                                                   |  |  |  |

|                                                                               | Intel® AVX and Intel® SSE data types [8]                                               |  |  |  |

|                                                                               | SIMD versus scalar operations [8]                                                      |  |  |  |

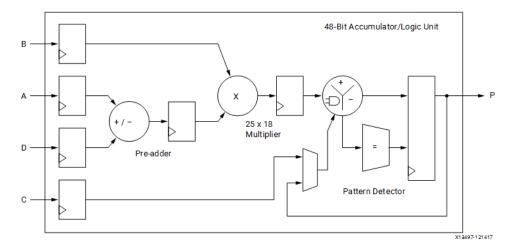

| 2.18                                                                          | Xilinx® DSP48 block [1]         20                                                     |  |  |  |

|                                                                               | Two lines switching states in an adiabatic bus [10]                                    |  |  |  |

| 2.20                                                                          | The EPO (Energy per Operation) in function of the ratio of the power supply            |  |  |  |

|                                                                               | voltage and the technology's threshold voltage 24                                      |  |  |  |

| 0.1                                                                           |                                                                                        |  |  |  |

| 3.1                                                                           | Streaming Multiprocessor schematic, first iteration                                    |  |  |  |

| 3.2                                                                           | Streaming Multiprocessor schematic                                                     |  |  |  |

| 3.3                                                                           | Control flow interactions with the Core                                                |  |  |  |

| 3.4                                                                           | Data flow of a Core   29                                                               |  |  |  |

| 3.5                                                                           | ALU schematic                                                                          |  |  |  |

| 3.6                                                                           | Branching stack                                                                        |  |  |  |

| 3.7                                                                           | Subroutine stack                                                                       |  |  |  |

| 3.8                                                                           | ROM instruction storage. Example of an instruction that takes 2 ROM addresses. 33      |  |  |  |

| 3.9                                                                           | Decoding state machine. The example instr_1 only takes a single ROM address,           |  |  |  |

|                                                                               | and as such, doesn't need a new state, contrary to instr_2, which occupies 3 ROM       |  |  |  |

|                                                                               | addresses                                                                              |  |  |  |

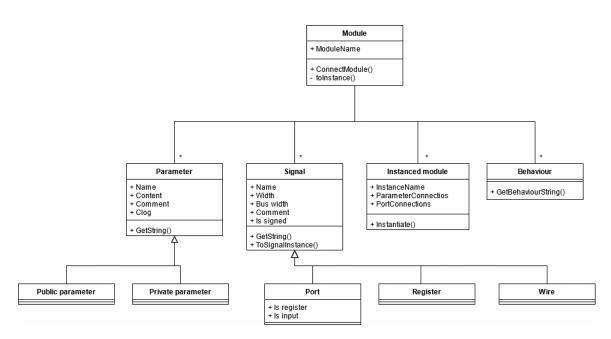

| 4.1 | Module class diagram                                                           | 41 |

|-----|--------------------------------------------------------------------------------|----|

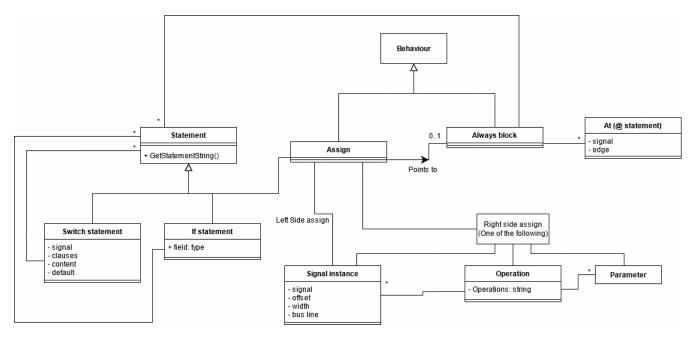

| 4.2 | Behaviour class diagram                                                        | 42 |

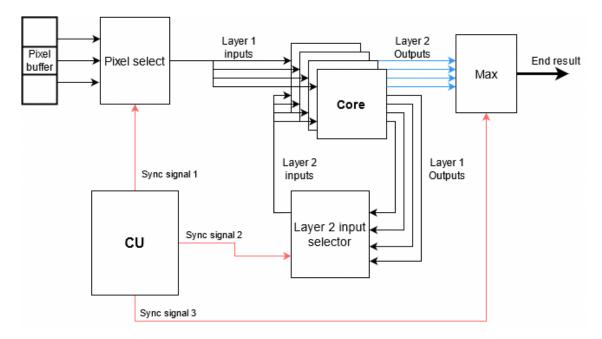

| 5.1 | FCNN Hardware implementation                                                   | 49 |

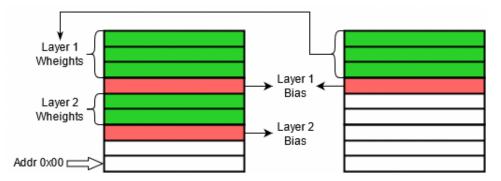

| 5.2 | RAM content. The right stack is the content of a core that only implements the |    |

|     | first layer, while the left one executes in all layers                         | 51 |

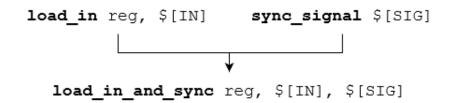

| 5.3 | Fixed ROM address overflow.                                                    | 55 |

| 5.4 | New instruction created by merging two existent instructions                   | 55 |

# **List of Tables**

| 2.1        | Example of the $C = A + B$ operation                                                        | 12 |

|------------|---------------------------------------------------------------------------------------------|----|

| 3.1<br>3.2 | Opmode values and respective outputs for the DSP48E1[11]                                    | 30 |

|            | lating in the warp                                                                          | 36 |

| 4.1        | Adjustable parameters in the configuration file.                                            | 37 |

| 5.1        | Implementation resource usage of the FCNN in the FPGA of the Zynq-7000 (Device name Z-7010) | 53 |

| A.1        | Conversion from terms used in [12] to official NVIDIA/CUDA and AMD jargon                   | 60 |

| A.2        | Conversion from terms used in [12] to official NVIDIA/CUDA and AMD jargon                   |    |

|            | (cont. 1)                                                                                   | 61 |

| A.3        | Conversion from terms used in [12] to official NVIDIA/CUDA and AMD jargon                   |    |

|            | (cont. 2)                                                                                   | 62 |

# **Abbreviations and Symbols**

| ALU   | Arithmetic Logic Unit                                   |

|-------|---------------------------------------------------------|

| ASIC  | Application Specific Integrated Circuit                 |

| AVX   | Advanced Vector Extension                               |

| BCE   | Basic Computing Element                                 |

| CPU   | Central Processing Unit                                 |

| CUDA  | Compute Unified Device Architecture                     |

| FCNN  | Fully Connected Neural Network                          |

| FPGA  | Field-Programmable Gate Array                           |

| GPGPU | General Purpose Graphical Processing Unit               |

| GPU   | Graphical Processing Unit                               |

| HDL   | Hardware Description Language                           |

| IC    | Integrated Circuit                                      |

| ISA   | Instruction Set Architecture                            |

| LUT   | Look Up Table                                           |

| MIPS  | Microprocessor without Interlocked Pipelined Stages     |

| MMU   | Memory Management Unit                                  |

| MNIST | Modified National Institute of Standards and Technology |

| PC    | Program Counter                                         |

| RAM   | Random Access Memory                                    |

| ROM   | Read Only Memory                                        |

| RTL   | Register Transfer Level                                 |

| SIMD  | Single Instruction, Multiple Data                       |

| SIMT  | Single Instruction, Multiple Threads                    |

| SM    | Streaming Multiprocessor                                |

| SMT   | Simultaneous Multi-threading                            |

|       |                                                         |

### Chapter 1

### Introduction

### 1.1 Context

Modern computing has come a long way since its foundation and, more then ever, depends on speed and reliability. As larger and more complex programs are created, the need to keep up with the performance requirements tighten. For this purpose, a area known as accelerated computing has become a topic more refined and complex to rival the constantly increasing demands of data processing.

Not only does this field of study investigate application acceleration through software, but it also contemplates new, or purpose specific, hardware implementations.

Such an implementation is the GPU (Graphical Processing Unit). This device is designed for the purpose of processing large amounts of graphical data. However, it is also possible to use it's power to compute other tasks that also require parallel data computations. In recent years, this gave rise to a new and dedicated device for this motive, the GPGPU (General Purpose GPU), where the graphic pipeline hardware was removed and some types of data processing was optimized.

Another well known devices for application acceleration are the FPGAs or the ASICs. These two make full use of the hardware configuration to output the intended results. Although, in terms of raw performance, the ASIC is superior to the FPGA, the price of fabrication is much larger if the desired batch size is small. Therefore, in this thesis, the main focus will be turned to the FPGA, as it is a cheaper platform for prototyping and testing.

The FPGA allows the reconfiguration of its own hardware structure. Meaning, the device may be reconfigured, fine tuned or re-purposed for other implementations, in contrast to the ASIC, which after fabrication cannot be rewired.

### **1.2** Objectives

The FPGA is a versatile device and the GPU is a well known architecture which enables the parallelization of calculations for large sums of data. Having mentioned these two devices, the aim of this thesis is to implement and evaluate the performance of a GPU architecture on an FPGA.

More specifically, as the intention is not to focus on graphic rendering, the micro-architecture in mind is the GPGPU, which removes the unnecessary graphical processing hardware.

However, this project also has the purpose of allowing for a more flexible execution of the GPGPU architecture. This could have an impact from adaptable data sizes, to reduced instruction sets for the ALUs (Arithmetic Logic Unit).

A program will interconnect the user's application program and the architecture, abstracting him from the the instruction set and the lower level implications.

### **1.3 Motivation**

Having a reconfigurable architecture may tackle a few problems in computation and embedded systems. Making purpose specific architectures can improve significantly in terms of used area of the IC, speed and/or power consumption.

In applications where speed is key, the space available in the chip can be managed to enable the fastest performance possible. From creating an operation that would normally be unavailable in normal CPUs or GPUs, to repeating the same physical blocks to increment the data throughput.

Certain devices are more limited in area, being the available number of logic units or having to share space with another digital system in the same FPGA or ASIC. Having full control over the sizes of the physical blocks or the memory and bus sizes can help improve space efficiency.

Regarding the power consumption, most embedded systems have a tight restriction on battery life. Furthermore, with IoT (Internet of Things) devices being widely used for more, and more demanding, applications (such as edge computing) this should be kept in mind.

All these factors must be taken into account while implementing accelerated computing applications. However, the convenience and the comfort of a high level overview, much like the programming of a normal CPU application, must still be present in the tools to be developed.

### Chapter 2

### **State of the Art**

### 2.1 Accelerated Computing

With the rise of machine learning, computer vision and other big data applications, computation speed with high data throughput is a great concern. A small list of alternatives to tackle this subject will follow.

For specific applications, the best solution could always be considered the implementation of an ASIC. These are tailored to solve a specific problem that raises from a specific application. Its hardware is, in the best case, fully optimized for speed, space, power or all of those. However, once designed and fabricated, there is no way of adapting its configuration. This can even cause bugs to be deployed without having a way to fix them without replacing the component with a newly designed one.

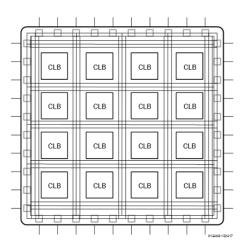

Much like an ASIC, the FPGA can be configured for the specific task. Yet, it can be reconfigured and re-purposed, contrary to the ASIC. The structure of the FPGA is a grid of Configurable Logic Blocks (CLB), containing Look Up Tables, Flip-Flops and other components, that can be rewired to a specific pattern. Although it may not be able to achieve such a good performance compared to its counterpart, due to the overhead in chip area, it allows for a good prototyping platform.

Figure 2.1: Simplified overview of the FPGA architecture [1]

The DSP (Digital Signal Processor) is a microprocessor that sees usage in audio and image processing, besides other communication tasks. It is a processor with hard-wired signal processing algorithms, optimizing the transistor use and clock cycles for the required operations. Nonetheless, it trades this optimizations for flexibility. In most cases, it is used as a pre/post-processor for other connected ICs.

In the specific area of machine learning and computer vision, a few solutions for have emerged recently, the TPU (Tensor Processing Unit) and the VPU (Visual Processing Unit), respectively. Both enable the implementation of some AI (Artificial Intelligence) algorithms and techniques to enhance the speed of the task. These units can present a similar micro-architecture to the GPU, as they are both SIMD (more on this topic will be presented latter on, 2.3). However, the way they are implemented may be restrictive for the algorithm needed. This is due to the hardware design of the devices, which might only be capable of performing a set of algorithms. Besides, the network parameters need to be quantized when compiling the program to the hardware, which may reduce the precision of the implementation [13, 14].

The GPU (or the GPGPU) is another platform with an architecture capable of performing data processing acceleration. The output bandwidth is very high for the same operation compared to a CPU. Its disadvantage is that, even though it has a programmable interface, it can't run purely sequential tasks without loosing its strength in performance.

Last but not least is the CPU. Up until a certain point in history, the CPU's speed was bound by the operations per clock cycle. This would mean that the speed would improve by decreasing the clock cycles taken to perform operations and by increasing the clock frequency, depending on both architectural and technological improvements.

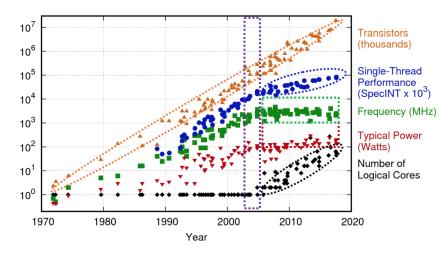

Over the years, as Moore's law dictates, the speed was increasing. However, the speed of the CPUs were reaching their limits with only a single core due to the power wall problem. The heat dissipation of the chip could not keep up with the heating of the system, ending up damaging it, or even burning the IC. The industry resisted implementing multi-core systems, as it required a lot of effort, not only in terms of hardware, but also on more complex compilers.

Figure 2.2: 42 Years of Microprocessor Trend Data [2]

Ultimately, the power wall was hit around 2004, which forced the trend of multi-core CPUs. The CPU became a generic processing unit with several cores to execute parallel tasks. This multi-core architecture can also be seen in modern GPUs and even DSPs.

The speedup gained from this multi-core system, however, is bounded by the executed program. The Amdahl's law, stated in Equation 2.1, bounds the maximum speedup gained in a multicore system depending on the parallelizable execution time of a program, being N the number of cores and F the parallelizable part of the program (between 0 and 1, being 1 a fully parallelizable program).

$$Speedup = \frac{1}{(1-F) + \frac{F}{N}}$$

(2.1)

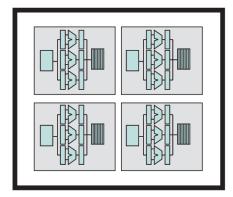

In modern computing, the cores themselves can have different computation powers. So, each chip is bounded by a *N* Base Core Equivalents (BCE) for all cores, having each core consuming *R* BCEs. Therefore, there are N/R physical cores per chip [3].

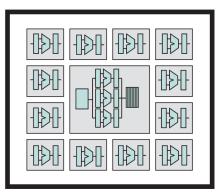

Figure 2.3: Left: Homogeneous sixteex 1-BCE cores. Right: Homogeneous four 4-BCE cores [3] Note: This is a simplified schematic and assumes the area as the limiting resource.

In this case, the serial fraction of the program uses a core at rate Perf(R). Typically,  $Perf(R) = \sqrt{R}$  [3]. The parallelizable segment of the program uses N/R cores at rate Perf(R) each. For now it is being considered that the BCEs are equally distributed amongst the physical cores, making them homogeneous (or symmetric) cores.

Serial time =

$$\frac{1-F}{Perf(R)}$$

(2.2)

$$Parallel time = \frac{F}{Perf(R) \times \frac{N}{R}} = \frac{F \times R}{Perf(R) \times N}$$

(2.3)

With these new factors, Amdahl's law becomes:

$$Homogeneous Speedup = \frac{1}{\frac{1-F}{Perf(R)} + \frac{F \times R}{Perf(R) \times N}}$$

(2.4)

This is what makes the distinction between the GPU and the CPU processing power. Even though the GPU has more cores than the CPU, each has less power compared to the CPU cores.

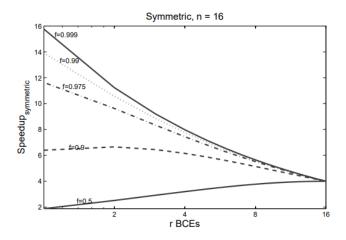

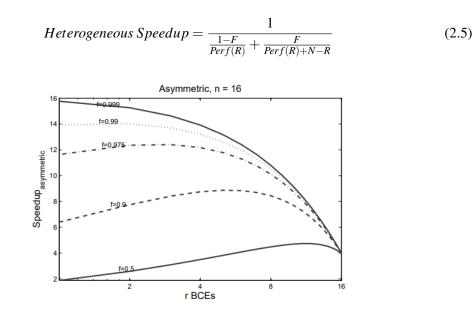

Figure 2.4: Example of the speedup achieved when distributing sixteen BCEs over the R value with different parallelization values [3]

The more parallelizable the program is, the more it benefits from having multiple cores. In contrast, the performance is degraded in programs with a serial execution compared to processors with fewer cores.

An alternative to the homogeneous multi-core chip is the heterogeneous (or asymmetric) architecture. This has a bigger core that performs the serial operation and distributes the remaining BCEs between other smaller cores with one BCE each.

Figure 2.5: Heterogeneous one 4-BCE core and 12 1-BCE cores (Total of 16 BCEs) [3]

Figure 2.6: Example of the speedup achieved when splitting the sixteen BCEs over a larger core and several 1-BCE cores [3]

Depending on the BCE count and the parallelizable section of the program, a sweet spot in the distribution of the BCEs becomes apparent (for example, with F = 0.9 and N = 16, the optimized distribution is around R = 7). Furthermore, the overall performance of the heterogeneous architecture is better in comparison to the homogeneous.

More on this topic, there is a technique named dynamic multi-core chips, that bundles the BCEs in groups at run-time, in order to take full advantage of all the available cores at every scenario. With this, the speedup achievable is:

$$Dynamic Speedup = \frac{1}{\frac{1-F}{Perf(R)} + \frac{F}{N}}$$

(2.6)

If the hardware was ideal, this would be the most optimized case of all described above, as the own architecture can change in accordance to the current needs of the application.

#### 2.1.1 Final remarks on Accelerated Computing

All the devices covered until now can be merged together, on the one hand, to cover up their disadvantages, and on the other hand, to make the most out of their strengths. In fact, this is common in High Performance Computing (HPC).

However, distributing different devices has a cost. As a matter of fact, one of the current major bottlenecks that is being faced is the memory bandwidth limitation. In other words, some applications' speed is not actually bound by the computation power, but by the memory transmission speed.

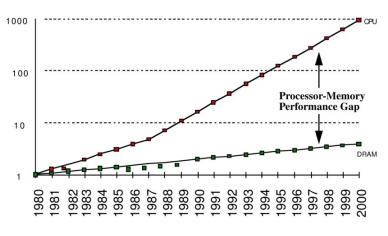

Figure 2.7: Processor-Memory performance gap [4]

This problem affects all memory transmissions within the same IC and becomes even more evident when integrating different chips communicating to each other. For this reason, in most accelerated computing applications, the constant exchange of information is generally avoided, and whenever possible, the memory closest to the processing units is used (namely the lower level caches and registers).

Technologies like the 2.5D or 3D packaging emerged to try to mitigate this issue, by implementing the different ICs in the same packaging [15]. This method reduces the time of data exchanges and increases bandwidth.

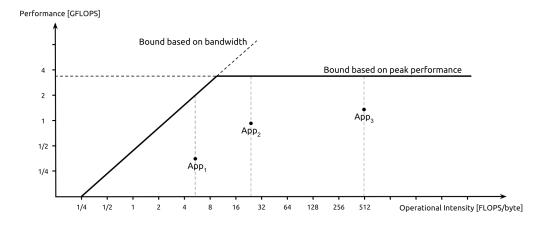

The roofline model attempts to specify if the application's speed limitation comes from memory bandwidth or the program's complexity [16, 17, 5]. In this model, the application is quantified into an arithmetic intensity in flops (floating point operations per second) per byte (Gflop/B). The bandwidth of the memory is given in gigabytes per second (GB/s) and the processing performance in Gflops. With this information, the plotted graphic (exemplified in Figure 2.8) shows that if the arithmetic intensity is lower than the intersection of the two lines, the program's performance is being bounded by the memory's bandwidth. If the arithmetic intensity is beyond that point, the program's limitation is the processor's speed.

Figure 2.8: Example of the roofline model for 3 applications.  $App_1$  is bounded by the memory bandwidth while the other two apps are bound by the processor's peak performance [5]

### 2.2 Processor Architecture

Before diving deeper in the GPU architecture, it should be made clearer how a processor functions and its core components. The contemplated architecture that will follow is the Harvard processor architecture due to it's simplicity. Furthermore, this type of design can be found in a traditional DSP architecture and other micro-controllers, which, considering the topic at hand, shows some relevance. Modern computers are based on a derived version of this architecture, using the some properties of the Von Neumann architecture, named modified Harvard architecture, which allows instruction memory to be accessed as data [18, 19].

The Harvard architecture distinguishes itself owing to its physical separation of instruction memory and data memory. This way, the program instructions are located in ROM (Read-Only Memory) while the data memory is located in RAM (Random Access Memory). This way, it is less likely that the program will suffer memory corruption due to the incorrect usage of the data memory. Furthermore, and more importantly, this distinction forces the existence of two separate buses, making it possible for the processor to fetch instructions and read/write data at the same time.

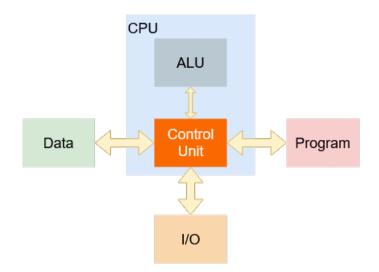

Figure 2.9: Harvard architecture overview

The control of the system is performed by a central unit, which performs the data or instruction fetches and stores/loads the needed information from/to the respective register. This registers reside in the ALU and are used by it to perform the operations or store the results. There are also special registers that store other information regarding the operation performed, such as the result of a conditional statement or the overflow of a mathematical operation. If the programmed application checks the state of this flags, it is the control unit's task to jump to the correct instruction address depending on the boolean value.

The jump operation is performed over the Program Counter (PC) register, which resides inside the control unit. In the normal operation of the program, at the execution of each instruction the PC is incremented to the next address. However, if the jump instruction is being performed, an address offset is added to the PC. This may depend on the architecture itself, as the PC might be set to a specific address instead of being added as an offset.

Besides the control flow instructions, such as the jump, performed in the control unit, the majority of the operations execute in the ALU. All these mentioned instructions are part of the ISA (Instruction Set Architecture). The instructions are decoded and only executed by the intended modules. This selection is normally done by multiplexers that enable the block which must perform the operation [6].

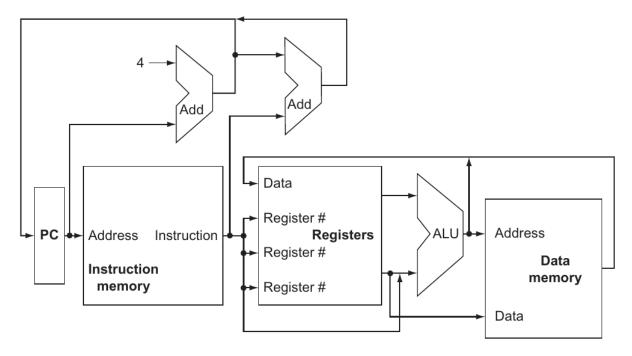

Figure 2.10: Abstract view of the implementation of the MIPS subset [6]

The ISA may have several classifications based on the implementation [12, 20, 21]:

- **Stack machines 0-Operand**: The operations are performed on the elements on top of the stack.

- Accumulator machines 1-Operand: The operations are performed on the top element of the stack and are implicitly accumulated on a special register.

- General Purpose Registers (GPR):

- Register-Register (or Load-Store) 3-Operand: The data is moved from memory to the registers before the operation.

- Register-Memory 2-Operand: One operand is in memory when performing the operation while the other is already loaded to the register.

- Memory-Memory 3-Operand: The operation has to fetch all data when performing the instruction.

These implementations affect the performance or the program size. The example in Table 2.1 shows the program size depending on the implementation used, being the Memory-Memory the lowest in program memory usage. However, the Mem-Mem has to fetch instructions from memory, making it slower. The Reg-Reg has a bigger program size, but all data is in register when operating, making it faster than the previous. The Reg-Mem is the middle ground between those two. It should be noted that not all ISA classifications have only *n* number of operands in its instructions, as there are some operations that might need another number of operands. Besides, a computer architecture is not limited to only one of these types of instruction sets. It may be relevant to add different variants of operations to have programs aimed for various optimizations.

| Stack  | Accumulator | Reg-Reg        | Reg-Mem     | Mem-Mem     |

|--------|-------------|----------------|-------------|-------------|

| Push A | Load A      | Load R1, A     | Load R1, A  | Add C, A, B |

| Push B | Add B       | Load R2, B     | Add R1, B   |             |

| Add    | Store C     | Add R3, R1, R2 | Store C, R1 |             |

| Pop C  |             | Store C, R3    |             |             |

Table 2.1: Example of the C = A + B operation

The usual instructions found in most ISAs include:

- Load/Store instructions: Move data between memory and registers.

- Jump or branch instructions: Jump to an address in the instruction memory. They can be unconditional jumps or a jump instruction that is only performed if a flag is set or if the operands check the condition.

- **Comparison instructions**: These instructions perform comparisons between registers and normally write to a flag register.

- **Boolean logic instructions**: These can be bitwise comparators, comparisons between registers or shift registers.

- **Mathematical instructions**: Such as additions, subtractions, multiplications, etc. The ISA may have different sets of instructions for different data types and sizes.

### **2.3** A Brief History of the GPU

As the name implies, the GPU's main purpose is for graphics processing and rendering. This processor is normally integrated in a graphics card. However, the first graphics cards were not the processing units of today.

Before having a dedicated device for graphic processing, this task was performed in a software pipeline (Figure 2.11) by the CPU. Not only would this generate lesser quality graphics, but also cause a heavier workload and potentially slowing the other processes down. For the hardware interface, the image display would resort to transistor-transistor logic (TTL) chips [22, 7].

Figure 2.11: The traditional fixed-function graphics pipeline (Modified from [7])

To keep up with the demand for higher quality graphics, the pixel count was increasing. Moreover, the graphics pipeline would also evolve, adding new calculations to the already existing ones. These factors would increase the workload of the CPU even further.

It was in the '90s that a dedicated devices started appearing. Some of the latter stages of the pipeline were transferred to hardware. However, the CPU was still required for the first stages.

As the evolution continued, some segments of the pipeline started to be divided into smaller sections, taking advantage of parallelizable calculations such as the texture [7].

It was not until 1999 that the pipeline was fully implemented in hardware. From this point onward, the pipeline itself started evolving, adding new stages and parallelizations to the process.

In 2001, the pipeline was made programmable. In conjunction with the graphics hardware, the programmers had the option to program segments of the pipeline. Only one year latter, the first true programmable GPU was created. This featured per pixel operations, allowing fine grain customization of the image processing [7]. Nonetheless, the tools to program this devices were crude and unrefined, often resorting to modified graphical APIs for the specific application. Needless to mention that this tools made it hard to take full advantage of the board.

### 2.4 The modern GPU Architecure

**Note**: Before proceeding with this section, the terms regarding the GPU micro-architecture components will normally be expressions coined by NVIDIA. This is due to the fact that they are the most commonly found idioms when referring to the subject. More can be found in the Appendix A.

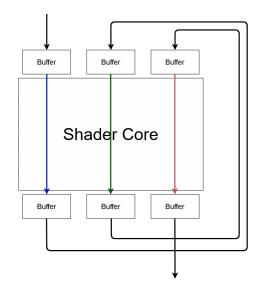

Finally, in 2006, the last step towards the architecture of the modern GPU was done. The featured Unified Shader Design (Figure 2.12) transformed the device into a new and more generic micro-architecture.

Figure 2.12: Unified hardware shader design (Modified from [7])

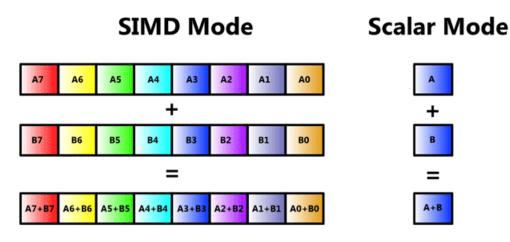

The main feature that allows the modern GPUs to achieve such high throughput is the SIMD (Single Instruction, Multiple Data) micro-architecture. As the name implies, a single instruction of the program executes in several ALUs concurrently, outputting the same number of data elements as ALUs. These processing cores, called CUDA cores by NVIDIA, are capable of generic calculations similar to the instructions commonly found in an CPU.

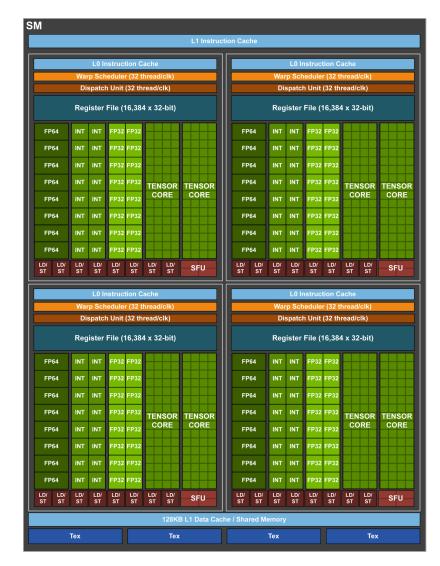

Figure 2.13: NVIDIA®'s Streaming Multiprocessor [8]

The Unified Shader Architecture groups several CUDA cores in lots. These lots are called streaming multiprocessors (SM), and the cores inside it share the same SIMD instruction. A program, or thread, that executes inside the SM is called a warp (or wave front in AMD's terms [23, 24]). The GPU has several SMs, enabling it to have multiple programs independent of each other, or segments of the same program.

In the Figure 3.2, the tensor cores shown are proprietary hardware that performs certain operations faster to the detriment of precision and is used in modern NVIDIA GPUs.

#### 2.4.1 Memory

The GPU has several levels of memory. This has two reasons, the first being the scope of the layer(s) that should have access to it. The second is due to speed limitations caused by the distance between the memory and the component accessing it.

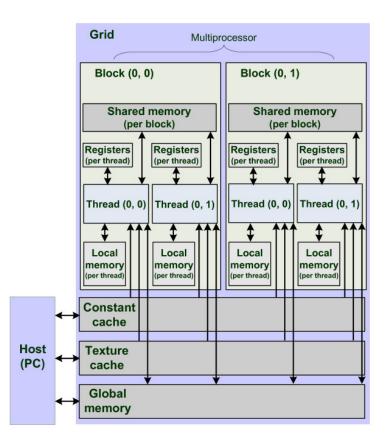

Figure 2.14: CUDA Memory hierarchy [9]

The memory levels ordered by access speed (from faster to slower) in a GPU are the following:

- Registers: Only available for the individual core.

- Shared memory or level 1 (L1) cache: Accessible by all cores within a SM.

- Local memory: Memory accessible by a single thread (or core). However, it is not on chip memory, making it slower than shared memory.

- Constant memory: Read-only memory, resides in device memory.

- **Texture memory**: Read-only memory, resides in device memory and is optimized for 2D spacial locality.

- Global memory: Shared by all the Streaming Multiprocessors.

It is worthy to mention that there are differences in bandwidth between layers. The order of bandwidth from larger to smallest is: Shared memory/L1 cache, Texture/constant memory, Global memory, Local memory, Registers. The throughput of the global memory may vary depending on the device capabilities, however, making it less precise to order the bandwidth [25].

#### 2.4.2 The GPGPU

The final transition specialized in accelerated computation was done in 2010 with the advancement of the GPGPU. Now, the platform was set for big data applications, without the graphical specific hardware. This modification alleviated some chip space, allowing the placement of more cores for more data processing or more memory.

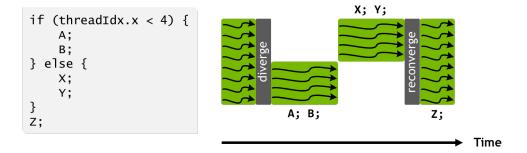

More importantly, the cores of the GPGPU (and the GPU) evolved from a SIMD microarchitecture to a SIMT (Single Instruction, Multiple Threads). This meant that the cores are more developed, and don't need to run the exact same instructions. However, the execution of branching instructions may aggravate the performance of the device.

Figure 2.15: Branching effect [8]

If a program has a conditional statement that would cause the threads within a warp to branch, some of the cores will have to remain inactive until the other cores finish executing their conditional statement. This may cause a considerable slow down in the program execution. This is the reason why it should be avoided to use conditional statements in GPU programs.

### 2.5 Hardware Improvement Techniques

#### 2.5.1 Speed improvements

This section will discuss some methods to improve the speed in applications data show a lot of Data-Level Parallelism (DLP).

#### 2.5.2 Pre-processing

A simple but very effective technique is to pre-process the incoming data with dedicated hardware. This may very from application to application, and the computations performed may range from simple signal processing, to more complex data paths.

As this is just a method, it can be implemented as purely combinational circuits to sequential circuits, as shown with the DSP. The task of this component is not to process the data completely, but to simplify part of the input into more digestible data for the rest of the hardware.

#### 2.5.3 SIMD

The SIMD architecture previously mentioned when discussing the GPU's architecture was one of its variations. There are two variations in regards to this topic [12].

The first one, is an execution pipeline of data operations. It is easier to compile and understand then its counterparts. However, when conceived, it was considered too expensive for microprocessors due to the cost of sufficient DRAM bandwidth.

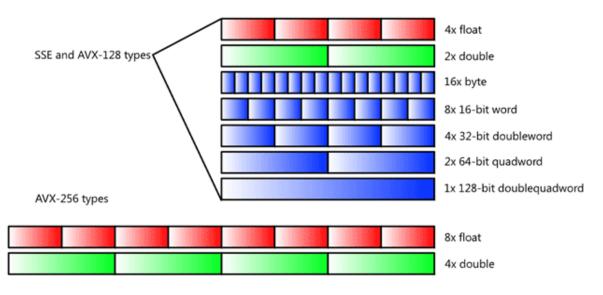

The second variation is called a Vector Extension. Nowadays, it is found in most instruction sets of devices which support multimedia applications. Currently more known as AVX (Advanced Vector Extension) in the x86 architecture, it started as MMX (Multimedia Extensions) in 1996, and was followed by SSE (Streaming SIMD Extensions) shown on Figure 2.16. Other architectures like ARM or RISC-V present their own version of vector extension as SVE (Scalable Vector Extension) and RVV (RISC-V Vector Extension), respectively [12, 8, 26, 27].

Figure 2.16: Intel® AVX and Intel® SSE data types [8]

This method takes advantage of the already implemented registers of the ALU. It creates an array in said register with smaller sized data types. It performs the operation needed, generating an output register that will also contain the results in an array (Figure 2.17).

Figure 2.17: SIMD versus scalar operations [8]

This method is implemented with its own set of instructions, and cannot be performed in unsupported hardware. This means that the hardware used for the array calculations is not the same as with the scalar operations. This certainly adds performance in regards to speed, but it trades it for chip area.

It should be kept in mind that this technique is not mutually exclusive with SIMT and SMT, as it can complement them depending on the hardware design and further improve data-level parallelism processing.

### 2.5.4 SMT

The SMT (Simultaneous Multi-Threading) provides self-contained cores that can run independently from each other and separate the tasks of each executing thread. Not only can this bring faster processing speeds for data-level parallelism, but also for tasks. This is currently seen in most CPU's. Even though it requires more complex operative systems (with complex and, preferably, scalable schedulers) and compilers, it has improved the speedup of computation in the past few decades, with this topic still in development [28].

#### 2.5.5 SIMT

The SIMT (Single Instruction, Multiple Threads) can be considered an hybrid of the SIMD and the SMT. Although the cores execute the same instruction, they may be able to branch and halt execution while the other threads execute the necessary branching program. Although this might be more inefficient in resource usage, it makes the system more adaptable.

This type of implementation can be seen in modern GPGPU's as previously mentioned in 2.4.2.

#### 2.5.6 Superscalar Processors

The superscalar processor enables the execution of several instructions at a time, accelerating the execution of the program. This also enables the Out-of-Order execution (also know as OoO) which

mitigates the slower memory speeds. As shown in Figure 2.7, the major bottleneck in computing is the memory speed compared to processing speed [29, 30].

With In-Order execution, this would mean the ALU would have to wait while the registers did not have the new data.

In contrast, the Out-of-Order execution executes instructions if the memory is available, and only has to wait in cases where the needed memory is still being fetched and no operation can be done in the mean time. This can be achieved through a combination of the organization of the instructions made at compile time and the supporting hardware, which must be able to execute more than one instruction in parallel.

In modern CPUs, this OoO execution is also achieved by making the CPU itself reorganize the execution of the instructions, making it less dependent on the compiler and more reliable when having several processes running in the same machine.

#### 2.5.7 DSP in the FPGA

Most FPGA's already have built in DSPs to speedup some very common applications. As a matter of fact, most neural networks and computer vision applications need the addition and multiplication operations. To accelerate the process and reduce consumed area of the application in the FPGA, the designers of these chips integrate a set number of DSPs, depending on the model. The operation of the DSP is translated to the following equation:

$$P = B \times (A+B) + C \tag{2.7}$$

However, this can also be reconfigured, depending on the FPGA, replacing additions with subtractions or a self feeding loop, with C = P. This is better visualized in Figure 2.18.

Figure 2.18: Xilinx® DSP48 block [1]

### 2.6 Power Consumption Improvements

There are two approaches when dealing with power consumption. The first is when designing the architecture, and the second is performed at run-time. The run-time solutions also need supporting hardware in order to operate, but change dynamically depending on the run-time conditions.

Some of the techniques presented next are basic techniques used in digital design overall, while others are more complex and specific for sequential processing units.

#### 2.6.1 Design/Fabrication low-power techniques

#### 2.6.1.1 Module based power reduction

A very common method is to pipeline the processing in several stages. In this context of processing units, there can be two types of pipelining at different levels of abstraction. At the lower level, the instructions or the pre-computation can be pipelined, meaning part of the operation is performed at each clock cycle until the final stage is reached. At the higher level of abstraction, the SIMD (or SIMT/SMT) cores can perform the operations like previously, passing the data from core to core.

The pipeline method has several advantages. Firstly, it can allow a higher clock speed in instructions where the propagation delay was a bottleneck. And second, it can improve the power consumption, as their will be less dynamic power consumption from the switching transistors.

Pipelines in processors have a disadvantage, however. Modern pipelines use speculative execution to attempt to predict the branching in the execution. In addition to the increase in complexity, if the prediction result is incorrect, the pipeline stalls and energy is wasted [31].

Another method is the parallel replication of a block and the desynchronization of each. This means that each block takes turns when processing the data at every clock cycle, allowing to greatly reduce the clock frequency. By copying several similar blocks, the occupied area is increased. This technique can also be implemented in conjunction with the pipeline, creating a hybrid. However, when dealing with multi-core architectures, this can be achieved at a higher level of implementation with scheduling of the warp execution, making it less relevant in this specific field of study.

Either integrated in the same IC or connected to the main chip with an interconnection, the pre-computation of incoming (or outgoing) data, using combinational or sequential logic, not only reduces the power consumption, but also the processing speed.

Most circuits, and especially processors, don't have all parts of circuit operating at all times. So, a method to reduce the power consumed is gating the clock, that is, turning of the clock to the components that are inactive, reducing the energy lost in switching the clock line [32]. Lastly, when executing a program, the ALU might not need the result of an operation immediately after dispatching the instruction. As such, the ALU could have what is called slack scheduling, allowing some instructions to take more than a clock cycle to perform while it runs other instructions of the program. There can be several ways to achieve this, including a smaller frequency for the hardware executing the slower operation or a pipeline, as previously discussed [33, 34, 35].

#### 2.6.1.2 Interconnect power reduction

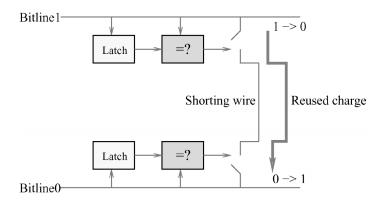

The transmission of data across a chip is also a factor to consider when optimizing the energy efficiency of the system [10].

Normally, the transmission of data is done in buses that have components attached and listening to it. But, most data exchanges are done from one component to another, meaning, there is no need for the other components to listen for data in the bus if it is not addressed to them. By segmenting the bus into several parts and disconnecting the lines, if the transmission is not needed beyond to a certain point of the line, energy consumption can be reduced.

Another alternative is to create hardware interfaces between communicating modules that splits the signal into two lines, each with a complementary differential voltage compared to one another. This voltage is also considerably lower than the rest of the chip, hence the better results in power consumption. This technique is called a low-swing bus. Still, when considering its implementation in an FPGA, there is no control over this component, being the fabricator's decision to add such a feature.

When a line on the bus switches states, the line's capacity needs to be charged/discharged. In common implementations, the line is connected to the source or ground. However, with the adiabatic bus, some charge can be recycled by redirecting the charge from a line that is transitioning from 1 to 0, to a line that is transitioning from 0 to 1. Even if not all charge can be reused, the improvement is significant. The most energy is saved when an equal number of lines rise and fall at the same time.

Figure 2.19: Two lines switching states in an adiabatic bus [10]

#### 2.6.2 Run-time low-power techniques

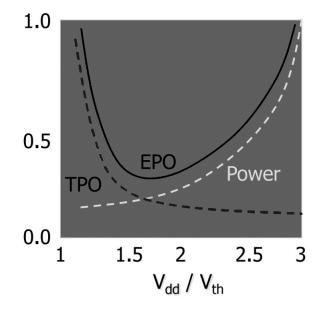

Depending on the current executing program in a processor, it may not be justifiable to run at maximum processing power. In order to improve this, power management units can be implemented [10, 36, 37].

One way of doing this is to simply turn off any component that is not being used, (much like clock gating, but this time completely blocking the power). This could bring an additional delay whenever the turned off module would need to be repowered.

Another approach is to scale the frequency and the voltage supply of the component. There are three types of power losses in the CMOS technology.

- Energy lost through leakage currents: Highly dependent on the specific CMOS technology and size

- **Power lost through short circuit**: When the transistors in a logic gate are switching from one state to another, due to the ON/OFF time of the transistors, a short circuit happens.

- **Dissipated power from switching**: Energy lost when charging or discharging the load's capacitance.

The last two mentioned power losses happen dynamically, meaning it depends on how many logic transitions the systems has overall. The approximate and simplified equation for the power lost from dynamic operation is:

Dynamic Power

$$\approx V_{DD}^2 \times f_{CLK} \times C_{Load}$$

(2.8)

So, the system depends on both the clock frequency and the supply voltage. There is however a limitation on the modification of these two parameters. First and foremost, the voltage cannot be lower than the threshold of the given technology. Then, if the voltage is lowered, it should be noted that the clock frequency also needs to lower. This happens because voltage reduction increases the delay [38, 39].

Because of this, as the supply voltage decreases, the power decreases as well, with the increase in the time per operation (TOP).

Figure 2.20: The EPO (Energy per Operation) in function of the ratio of the power supply voltage and the technology's threshold voltage

These types of run-time power management can be inserted at different levels. At a lower level, a local management unit can be used to control the specific operation of a single module. At a higher layer, a global management unit can regulate or send information to the local management units to control groups (or individual) cores, processors or cluster of processors.

## **Chapter 3**

## Architecture

Inspecting the problem at hand the steps to create a solution should be the following

- 1. Create and test a sample architecture for the intended purpose of the project

- 2. Generate RTL architecture files from a user's program and parameters

As in any computer architecture, the first step should be to create the basic structure while having into consideration the instruction set that will be implemented in it. This allows to better organize what should be needed from the hardware, and better adapt the resources demanded to perform those operations.

As the context of the thesis is to implement the architecture into an FPGA, it should also be noted that the resources used in the architecture include already implemented blocks, such as DSPs and RAM/ROM. These help improve the speed of the architecture, as purpose specific components already integrated into FPGA's board are more performant than replicating them with the Look Up Tables (LUT).

In order to achieve a more flexible design capable of being as generic as possible, the intended architecture for this project was SIMT. This makes it possible to have branching executions of the different threads running in the cores. Although this is more convenient and advantageous in certain cases, the general rule of branching in SIMT architecture still applies, being that branching should be used as little as possible.

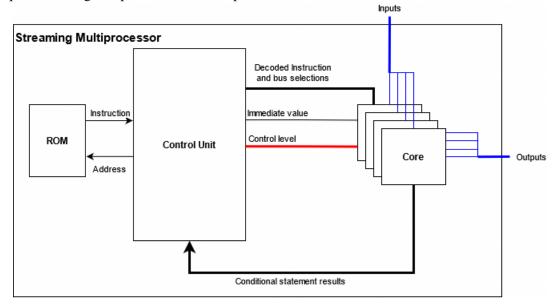

In the first iteration of the project, a few basic blocks were defined. These include the main control unit, that decodes the instruction, and the core itself.

## 3.1 First iteration

In the first iteration there were a few flaws that would limit the architecture in terms of performance.

The main focus of the control unit was to decode the instructions from ROM and to handle the program counter, being just increment it or loading it with and address to jump to.

This would mean that the core activation management was made inside each core. In comparison to a centralized management, sharing information between each core and the control unit will need more wiring. This is not the best solution in order to make the project scalable, as it will require more logic to perform the same operations.

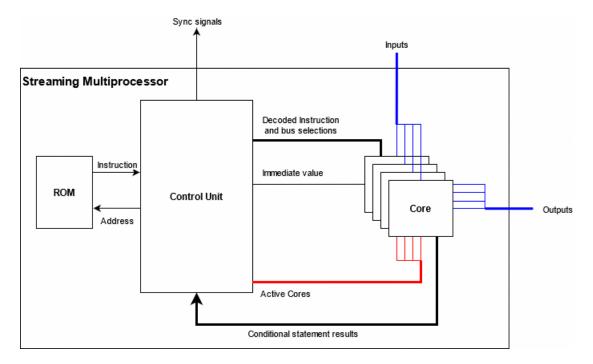

Figure 3.1: Streaming Multiprocessor schematic, first iteration

The branch control was performed with a level counter. For each new branch, the level would increase in the control unit. Each core would keep track of its own branching level. For example, if a core stopped executing in the level 4, it would remain inactive while the level in the control unit was higher than 4. Each core would also communicate to the control unit if it was available to perform a jump. That way, if every core agreed to perform the jump, no unnecessary branch would be read, avoiding wasted time reading instructions that would not be used.

The branching implementation, however, had a major flaw. When returning to a previous branch, the progress that a core had already executed within that branch was lost. This would mean constant repetition of conditional statements to verify the same conditions tested for the previous branches and slow down the execution.

The first iteration was also intended to be used mostly with 3 operands in the instructions (2 for the operands and 1 for the register to store the result). However, this restricts the usage of some operations in the present DSP unit of the FPGA. In case any MACC operations should be required, the last register of the DSP needs to be active . Instead of using external registers to the DSP for this purpose, it is more performant and convenient to use the internal register at the output signal.

### **3.2** Final version

From the first iteration, a few points were improved. Firstly, the cores had to be made as lightweight as possible. This turns the project easier to scale up, as doing this would only involve increasing the number of cores (of course, still taking into account the resources for the target FPGA). So,

by removing the branching from the core, the central control unit has the information associated with every core to decide if a branch is necessary or if a jump should occur. This topic will be discussed in further detail in the subsection 3.3.

Figure 3.2: Streaming Multiprocessor schematic

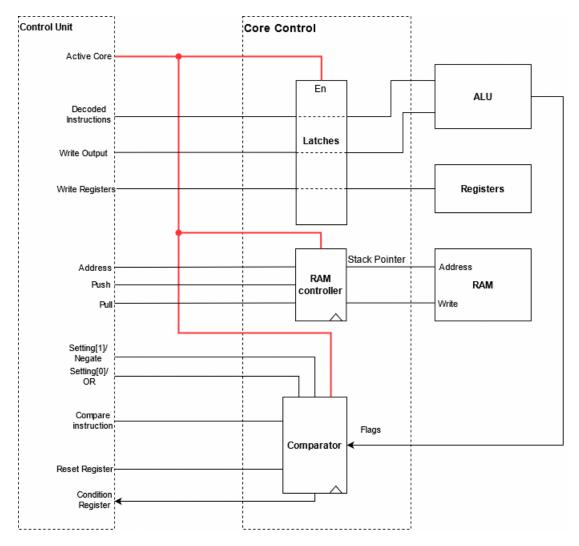

When a core is inactive, the instructions and the write enable signals are turned off. This is the effect of having transparent latches, which are enabled simply by the active core signal corresponding to the thread. Moreover, when a core is also inactive, the comparator signals the control unit has if the core is available to jump, has it would not perform any operation either way.

To have a method of synchronization between outside structures and the Streaming Multiprocessor (SM), a signal of N bits were created. With the current instructions available, only one bit is active per instruction, and the bit remains in a high state for exactly one clock cycle.

Figure 3.3: Control flow interactions with the Core

It was also important to have more than one memory type. In this new iteration, a RAM was added to each core. The individual RAM control is provided through the Core Control Unit, instead of the main one. This way, the core only inserts or modifies its RAM content if it is active. The stack pointer is also individual to each core, meaning that when a branch occurs, the stack may increase/decrease differently to each core. It should be noted however, when using this, stack consistency should be kept in check when writing a program. Otherwise, it may lead to the stack overflowing.

More on this point, as the implementation is application specific and the parameters are fine tuned by the user, no memory protection was implemented. So, elements can be pushed onto the stack when it is completely full. This will cause the stack pointer to return to beginning of the stack, which may lead to the impossibility to pop previous elements. However, if the right stack size is specified by the user the given application, and with the right memory consistency program, this should not pose a problem. Besides, this reduces the amount of logic per core, ever so slightly.

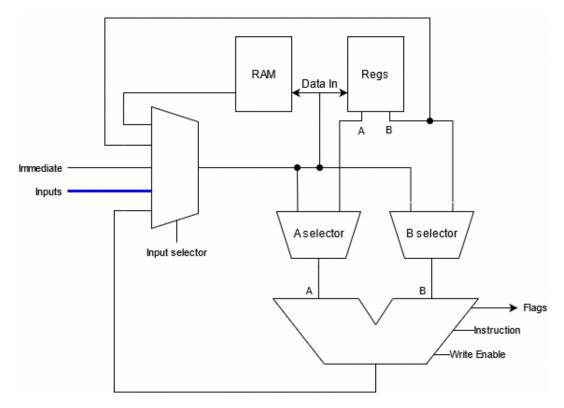

Figure 3.4: Data flow of a Core

With this design, the core consists of components like memories, multiplexers, a few control logic and the ALU. In conjunction with the generator program, the unused memory types are also removed or reduced to save as much space per core as possible.

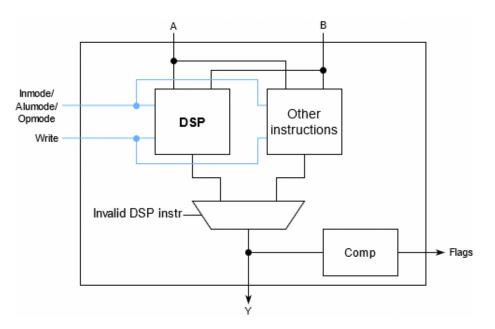

Figure 3.5: ALU schematic

Another stronger point for this architecture's flexibility is the input multiplexer configuration. There is a multiplexer that selects a data source to the data bus. With this, operations can be performed with input or RAM data, sparing a few clock cycles to load the data into registers. The line is defaulted to the ALU output, as it should be one of the most important data.

| Opmode                                        |                                              |                                                    |                                                                                            |

|-----------------------------------------------|----------------------------------------------|----------------------------------------------------|--------------------------------------------------------------------------------------------|

| 6 5 4                                         | 3 2                                          | 1 0                                                | Output                                                                                     |

| Z                                             | Y                                            | Х                                                  |                                                                                            |

| XXX                                           | XX                                           | 00                                                 | 0                                                                                          |

| XXX                                           | 01                                           | 01                                                 | Mult                                                                                       |

| XXX                                           | XX                                           | 10                                                 | Output (P)                                                                                 |

| XXX                                           | XX                                           | 11                                                 | A:B                                                                                        |

| XXX                                           | 00                                           | XX                                                 | 0                                                                                          |

| XXX                                           | 01                                           | 01                                                 | Mult                                                                                       |

| XXX                                           | 10                                           | XX                                                 | All bits to 1                                                                              |

| XXX                                           | 11                                           | XX                                                 | С                                                                                          |

| 000                                           | XX                                           | XX                                                 | 0                                                                                          |

| 001                                           | XX                                           | XX                                                 | PCIN                                                                                       |

| 010                                           | XX                                           | XX                                                 | Output (P)                                                                                 |

| 011                                           | XX                                           | XX                                                 | С                                                                                          |

| 100                                           | 10                                           | 00                                                 | Output (P)                                                                                 |

| 101                                           | XX                                           | XX                                                 | 17-bit shift (PCIN)                                                                        |

| 110                                           | XX                                           | XX                                                 | 17-bit shift (Output)                                                                      |

| 111                                           | XX                                           | XX                                                 | XX                                                                                         |

| 000<br>001<br>010<br>011<br>100<br>101<br>110 | xx<br>xx<br>xx<br>xx<br>10<br>xx<br>xx<br>xx | xx<br>xx<br>xx<br>xx<br>xx<br>00<br>xx<br>xx<br>xx | 0<br>PCIN<br>Output (P)<br>C<br>Output (P)<br>17-bit shift (PCIN)<br>17-bit shift (Output) |

Table 3.1: Opmode values and respective outputs for the DSP48E1[11]

Note: Some operations require specific conditions to be met.

Looking at the DSP operation mode codes in Table 3.1, there is one case where the behaviour is undefined (Opmode[6:3]=111). As such, it is possible to take advantage of this extra unused instructions to provide more operations to the ALU without using extra signals. This is why the DSP is a component of the overall ALU. It is now possible to insert new and custom operations to the ALU in a separate file.

Another product of this decision is the usage of a single register in the control unit for the Inmode, Opmode and Alumode. Although the DSP has available registers to store these signals, they were disabled in order to use all the instructions available in the ALU, and to create consistency across the cores and the ALU.

## 3.3 Branching

One of the main features of this design is the integration of a SIMT architecture. This enables the usage of conditionals and execution of different instructions depending on the information of each core altogether.

It should be noted that compared to the case of a single core architecture, the branching doesn't have the same implications as in a SMT architecture. While in a single core architecture, a branch would mean the program counter would jump to an address in case a condition was met, in a SIMT, this would only occur if all the cores are in an agreement. If not, the cores that signaled they were available to jump would need to be turned off, while the others execute the instructions.

To optimize the FPGA resources as much as possible, an individual stack was made for the branching and to jump to subroutines. As the width of the addresses and the number of cores are very likely to be different, it is better to save memory space by separating them. It is also simpler to implement the control for such a structure.

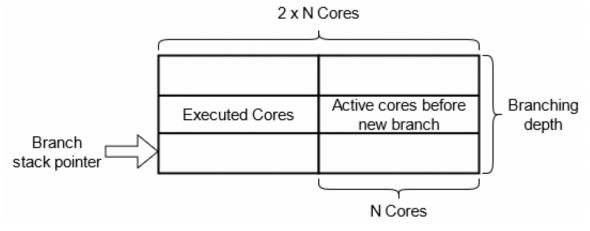

Before performing the branching, a setup instruction necessitates to be performed, initializing the branching stack. The width of the stack corresponds to 2 times the number of cores present in the design.

Figure 3.6: Branching stack

On the right side, the currently active cores are pushed onto it when setting up the procedure. With this information, it is possible to have nested branches, as the information before the branch began is now available.

On the left side of the stack, are the cores that have already executed a segment of the branch. This emulates an if/else statement. If the first conditions to jump have not been met by a certain core, this core executes the following instructions. This core then becomes inactive, ignoring any other execution of the subsequent branches.

Any time there is an update on the branching, it is checked if the left side of the top of stack is the same as the right side. This case means that all the cores that branched have do not need to perform any other operation. If this condition is met, a jump is performed to the end of the branching were a final instructions pops the stack, and decrements the pointer (if the address is already at the end of the stack it sets the empty register). At this point, the active cores are the same as the ones before the branching.

A program segment that would use the branching would look something like the Listing 3.1. The syntax will be detailed in a latter point, but this is presented here to show the functionality of the branches.

```

new_branch

add

reg_0, reg_1

2

$0, !negative

compare

3

4

add

reg_2, reg_3

$0, !negative

compare

5

Branch 2

branch

6

7 Branch_1:

8

. . .

update_branch End_of_branch

9

compare

$0, !zero

10

branch

Branch_3

11

12 Branch_2:

. . .

update_branch End_of_branch

14

15 Branch_3:

16

...

17 End_of_branch:

18

end_branch

```

Listing 3.1: Example of a program with 3 branches

The previous program has 3 branches and acts similarly to an "if"/"else if"/"else" statement. When performing the compare instructions, it is possible to mix normal instructions as the conditional register will hold its value until a branch is executed.

After a branch is executed, an update instruction checks if all the cores are available to jump to the end of the branching, closing it and resuming the program. The last branch should not need to run this instruction.

The conditions for the "else if" should be written after the update instruction, followed by another branch to the next "else" address.

## 3.4 Subroutine execution

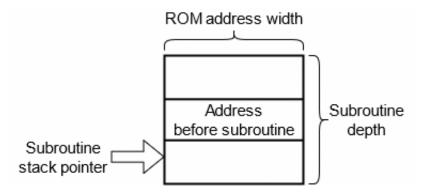

A common occurrence in computer programming is a repetition of the same structure of code. To avoid this, and to save some ROM space, a subroutine system was implemented.

Figure 3.7: Subroutine stack

The subroutine jump is a simpler stack implementation compared to the branching one. Its respective stack stores the address where a subroutine was called. Every subroutine should have a return from subroutine instruction at the end, which pops the address that it needs to return to. By having a stack, a subroutine can call another subroutine, allowing for nested statements.

## 3.5 Instructions

The architecture and the generator program were designed to make it easier to create new instructions. With this in mind, the instruction decoding was made automatic.

When referring to the instructions, however, it should be emphasized that the architecture considers the application's reconfiguration and exact memory utilization. This means that the instructions may not be very efficient in terms of addressing space. In common CPU architectures, for example, the addressing space and the instruction composition are very coherent with each other. So, in this case, the configuration of every instruction needs to be mapped to the exact parameters and usage of the current application, which will be discussed in a latter chapter.

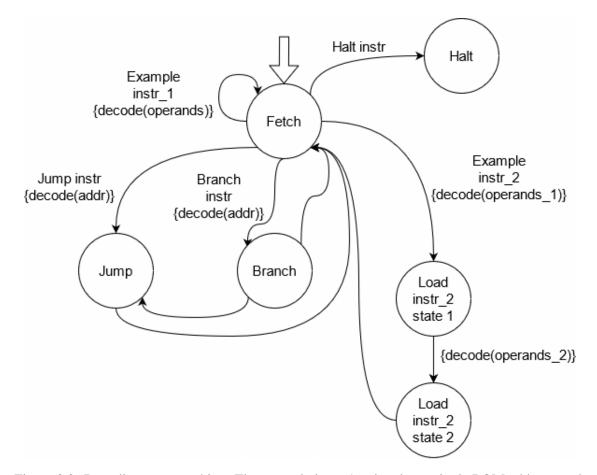

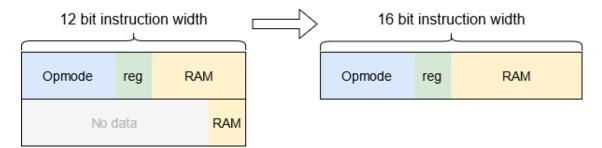

#### 3.5.1 Decoding

From the architecture side, new states need to be added to the state machine in order to correctly decode the operands depending on the instruction, as shown in Figure 3.9. In case the whole operation code and arguments fit inside the instruction width, the state remains in the Fetch state. If the instruction does not fit in a single memory cell, then it needs to change to a new state to continue with the decoding. A new state is used for every new type of decoding the program requires, until every operand is completely decoded. The last state of the decoding process can then redirect the state machine to another state, instead of going to the default Fetch, redirecting the flow to a Jump or Branch state, depending on the purpose of the instruction.

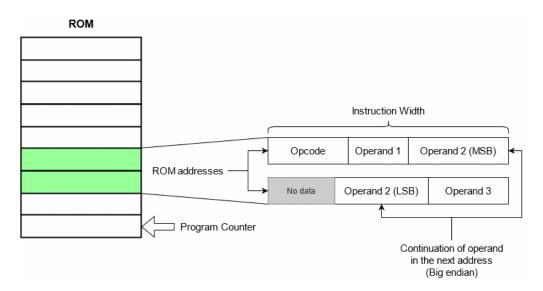

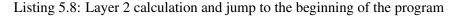

Figure 3.8: ROM instruction storage. Example of an instruction that takes 2 ROM addresses.

This process has a disadvantage however. Even if the two instructions share exactly the same operands, they will need individual decoding states for each, as the final state transition may be different. This may cause a bigger state machine, then a manually created one.

Figure 3.9: Decoding state machine. The example instr\_1 only takes a single ROM address, and as such, doesn't need a new state, contrary to instr\_2, which occupies 3 ROM addresses.

The decoding itself is simply a matter of filling the right registers with the right information. The operands in the ROM are organized as big endian. When an instruction does not fit in a memory address, and an operand breaks in chunks, its continuation goes to the leftmost side of the next address line, and so on for every other operand.

This is shown in Figure 3.8, where the *Operand 2* is divided into two, and is inserted into the address line on the side of the *Operand 3*.

The number of address lines taken for an instruction depends on the size of its operands, the instruction width set by the user and the total number of instructions used (which translates to the operation code width).

#### **3.5.2** Instructions and Instruction types

As the architecture is somewhat flexible to different types of instructions, these can take a different number and types of arguments.

From Table 3.2 a few more details should be given about some registers.