# INSTITUT FÜR INFORMATIK

# Sequentially Constructive Concurrency A Conservative Extension of the Synchronous Model of Computation

Reinhard von Hanxleden, Michael Mendler, Joaquin Aguado, Björn Duderstadt, Insa Fuhrmann, Christian Motika, Stephen Mercer, Owen O'Brien and Partha Roop

> Bericht Nr. 1308 August 2013 ISSN 2192-6247

# CHRISTIAN-ALBRECHTS-UNIVERSITÄT ZU KIEL

### Institut für Informatik der Christian-Albrechts-Universität zu Kiel Olshausenstr. 40 D – 24098 Kiel

## Sequentially Constructive Concurrency A Conservative Extension of the Synchronous Model of Computation

Reinhard von Hanxleden, Michael Mendler, Joaquin Aguado, Björn Duderstadt, Insa Fuhrmann, Christian Motika, Stephen Mercer, Owen O'Brien and Partha Roop

> Bericht Nr. 1308 August 2013 ISSN 2192-6247

R. von Hanxleden, B. Duderstadt, I. Fuhrmann, and C. Motika are with the Department of Computer Science, Kiel University, Kiel, Germany.

E-mail: {rvh, bdu, ima, cmot}@informatik.uni-kiel.de

M. Mendler and J. Aguado are with Bamberg University, Germany.

E-mail: {michael.mendler, joaquin.aguado}@uni-bamberg.de

S. Mercer and O. O'Brien are with National Instruments, Austin, TX, USA.

E-mail: {stephen.mercer,owen.o'brien}@ni.com

P. Roop is with Auckland University, Auckland, New Zealand.

E-mail: p.roop@auckland.ac.nz

Parts of this report have appeared in the *Proceedings of the Design*, *Automation and Test in Europe Conference (DATE'13)*, Grenoble, France, March 2013

#### Abstract

Synchronous languages ensure deterministic concurrency, but at the price of heavy restrictions on what programs are considered valid, or *constructive*. Meanwhile, sequential languages such as C and Java offer an intuitive, familiar programming paradigm but provide no guarantees with regard to deterministic concurrency. The *sequentially constructive* model of computation (SC MoC) presented here harnesses the synchronous execution model to achieve deterministic concurrency while addressing concerns that synchronous languages are unnecessarily restrictive and difficult to adopt.

In essence, the SC MoC extends the classical synchronous MoC by allowing variables to be read and written in any order as long as sequentiality expressed in the program provides sufficient scheduling information to rule out race conditions. This allows to use programming patterns familiar from sequential programming, such as testing and later setting the value of a variable, which are forbidden in the standard synchronous MoC. The SC MoC is a conservative extension in that programs considered constructive in the common synchronous MoC are also SC and retain the same semantics. In this paper, we identify classes of variable accesses, define sequential constructiveness based on the concept of SC-admissible scheduling, and present a priority-based scheduling algorithm for analyzing and compiling SC programs.

**Keywords:** Concurrency, synchronous languages, determinism, constructiveness.

# Contents

| 1        | Introduction                                                                                                             | 1                                                        |

|----------|--------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| <b>2</b> | Related Work                                                                                                             | 2                                                        |

| 3        | The SC Language and the SC Graph  3.1 The SC Language                                                                    | 4<br>4<br>6<br>8<br>8<br>9<br>10<br>11<br>11<br>12<br>14 |

| 4        | "Free" Scheduling of SCGs 4.1 Continuations and Continuation Pool                                                        | 14<br>15<br>16<br>20                                     |

| 5        | Sequential Constructiveness5.1 Types of writes5.2 SC-Admissible Scheduling                                               | 21<br>21<br>23                                           |

| 6        | Analyzing Sequential Constructiveness6.1 Conservative approximations6.2 Determining SC schedules6.3 Computing priorities | 27<br>35<br>37<br>37                                     |

| 7        | Variables vs. Signals 7.1 Emulating pure signals                                                                         | 38<br>38<br>39<br>39                                     |

| 8        | SCCharts — Sequentially Constructive Statecharts                                                                         | 40                                                       |

| 9        | Alternative Notions of Constructiveness                                                                                  | 41                                                       |

| 10       | Summary and Outlook                                                                                                      | 47                                                       |

# List of Figures

| 1  | The mapping between SCL statements and SCG subgraphs                             | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2  | The Control example                                                              | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3  | The syntactical elements of the SC Graph (SCG)                                   | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4  |                                                                                  | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 5  |                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|    | reincarnation                                                                    | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 6  | The InstLoop example, with an instantaneous loop that leads to statement rein-   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|    | • • •                                                                            | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 7  |                                                                                  | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 8  |                                                                                  | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 9  |                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|    |                                                                                  | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 10 |                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|    | outcome                                                                          | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 11 | The SCL program Fail, which has a deterministic outcome, but no SC-admissible    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|    | schedule                                                                         | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

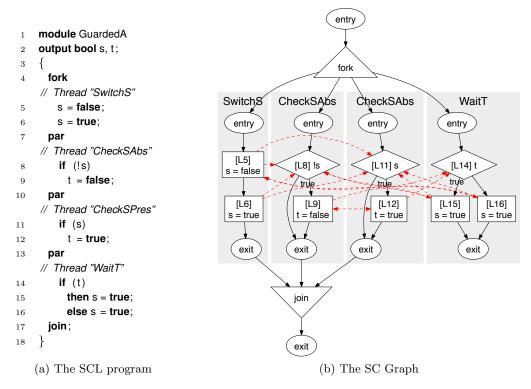

| 12 | The GuardedA example, illustrating the data-dependent nature of SC-constructive- |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|    | ness                                                                             | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 13 | SCL program SCDet                                                                | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 14 |                                                                                  | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

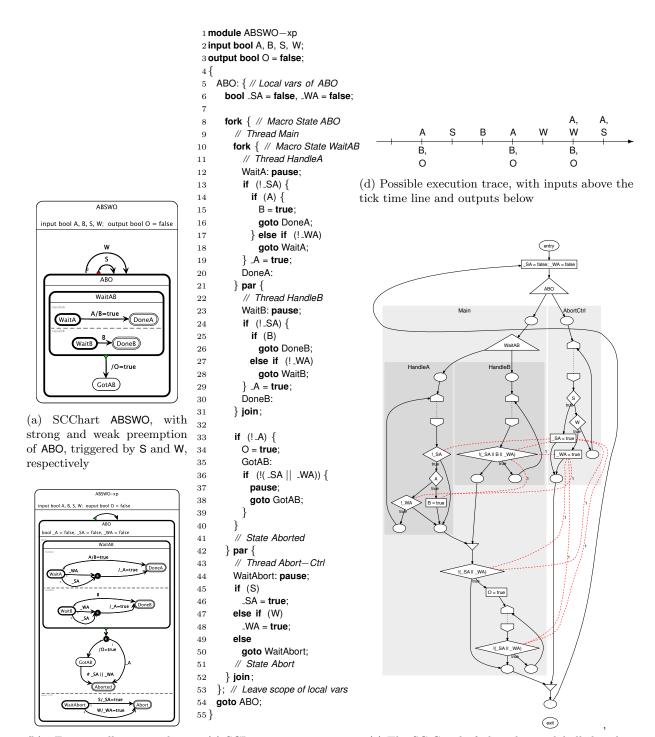

| 15 | The ABSWO example, illustrating strong and weak preemption, and the function-    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|    | ally equivalent ABSWO-xp ("expanded") example                                    | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 16 | Relationships of Statecharts classes                                             | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|    | 2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15         | The Control example The syntactical elements of the SC Graph (SCG) The Reinc example, illustrating thread reincarnation The Reinc2 example, a more elaborate example of thread concurrency and thread reincarnation The InstLoop example, with an instantaneous loop that leads to statement reincarnation within a tick Execution states of a thread The XY example The InEffective examples illustrating non-deterministic responses despite ineffective out-of-order write accesses The NonDet example, illustrating multiple admissible runs and non-deterministic outcome The SCL program Fail, which has a deterministic outcome, but no SC-admissible schedule The GuardedA example, illustrating the data-dependent nature of SC-constructiveness SCL program SCDet Overview of SCCharts The ABSWO example, illustrating strong and weak preemption, and the functionally equivalent ABSWO-xp ("expanded") example |

# List of definitions, propositions and theorems

| 1  | Definition (SCG subgraphs)                                      | 8  |

|----|-----------------------------------------------------------------|----|

| 2  | Definition (Ancestor/Subordinate/Concurrent Threads)            | 10 |

| 3  | Definition (Ticks)                                              | 13 |

| 4  | Definition (Concurrent Node Instances)                          | 14 |

| 1  | Proposition (Active continuations have sequential predecessors) | 18 |

| 2  | Proposition (Active and pausing continuations are concurrent)   | 18 |

| 5  | Definition (Combination functions)                              | 21 |

| 6  | Definition (Absolute/relative writes and reads)                 | 22 |

| 7  | Definition (Confluence of Nodes)                                | 23 |

| 8  | Definition (Confluence of Node Instances)                       | 24 |

| 9  | Definition (Scheduling Relation on Node Instances)              | 24 |

| 10 | Definition (SC-Admissibility)                                   | 25 |

| 11 | Definition (Sequential Constructiveness)                        | 26 |

| 12 | Definition (Valid SC-Schedule.)                                 | 27 |

| 13 | Definition (ASC Schedulability)                                 | 28 |

| 1  | Theorem (Sequential Constructiveness)                           | 28 |

| 14 | Definition (Priorities)                                         | 37 |

| 2  | Theorem (Finite Priorities)                                     | 37 |

#### 1 Introduction

One of the challenges of embedded system design is the deterministic handling of concurrency. The concurrent programming paradigm exemplified by languages such as Java and C with Posix threads essentially adds unordered concurrent threads to a fundamentally sequential model of computation. Combined with a shared address space, concurrent threads may generate write/write and write/read race conditions, which are problematic with regard to ensuring deterministic behavior [1], as the run-time order of execution of a multi-threaded program depends both on the actual time that each computation takes to execute and on the behavior of an external scheduler beyond the programmer's control .

As an alternative to this non-deterministic approach, the *synchronous* model of computation (MoC), exemplified by languages such as Esterel, Lustre, Signal and SyncCharts [2], approaches the matter from the concurrency side. The synchronous MoC divides time into discrete *macroticks*, or *ticks* for short. Within each tick, a synchronous program reads in inputs and calculates outputs. The inputs to a synchronous program are assumed to be in synchrony with their outputs, and the time that computations take is abstracted away. Simultaneous threads still share variables, where we use the term "variable" in a generic sense that also encompasses streams and signals. However, race conditions are resolved by a deterministic, statically-determined scheduling regime, which ensures that within a tick, a) reads occur after writes and b) each variable is written only once. A program that cannot be scheduled according to these rules is rejected at compile time as being *not causal*, or *not constructive*. This approach ensures that within each tick, all variables can be assigned a unique value. This provides a sufficient condition for a deterministic semantics, though, as we argue here, not a necessary condition.

Introducing global synchronization barriers and sequences of reaction cycles is a sound basis for deterministic concurrency and applicable also for general programming languages commonly used for embedded systems. Demanding unique variable values per tick not only limits expressiveness but also runs against the intuition of programmers versed in sequential programming, and makes the task of producing a program free of "causality errors" more difficult than it needs to be. For example, a simple programming pattern such as if (!done) { ...; done = true} cannot be expressed in a synchronous tick because done must first be written to within the cycle before it can be read. Another issue that prevents this program from compiling under a synchronous interpretation is that done would possibly be both false and true within the same tick. However, in this example, there is no race condition, nor even any concurrency that calls for a scheduler in the first place. Thus, there is no reason to reject such a program in the interest of ensuring deterministic concurrency.

Contributions. We propose the sequentially constructive model of computation (SC MoC), a conservative extension to the synchronous MoC that accepts a strictly larger class of programs. Specifically, the SC MoC permits variables to have multiple values per tick as long as these values are either explicitly ordered by sequential statements within the source code or the compiler can statically determine that the final value at the end of the tick is insensitive to the order of operations. This extension still ensures deterministic concurrency, and is conservative in the sense that programs that are accepted under the existing synchronous MoC have the same meaning under the SC MoC. For example, all constructive Esterel programs are also sequentially constructive (SC). However, there exist Esterel programs that are SC, but not constructive in Berry's sense [3]. E. g., all programs that do not use the concurrency operator are SC, though they may be non-constructive in Esterel.

Outline. The next section discusses related work. Sec. 3 presents the SC language (SCL) and the SC graph (SCG), which we use as a basis for the concept of sequential constructiveness.

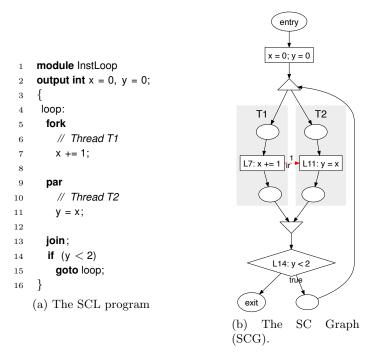

| Statement | Program | Assignment | Sequence      | Conditional                | Label / Goto           | Parallel                              | Pause |

|-----------|---------|------------|---------------|----------------------------|------------------------|---------------------------------------|-------|

| SCL       | s       | x = ex     | $s_1$ ; $s_2$ | if $(ex)$ $s_1$ else $s_2$ | goto $l \dots l$ : $s$ | fork $s_1$ par $s_2$ join             | pause |

| SCG       | entry   | x = ex     | s1<br>s2      | if ex                      | goto                   | fork entry entry s1 s2 exit exit ioin | surf  |

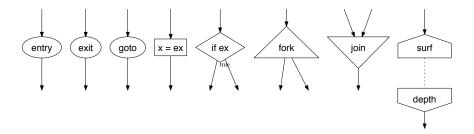

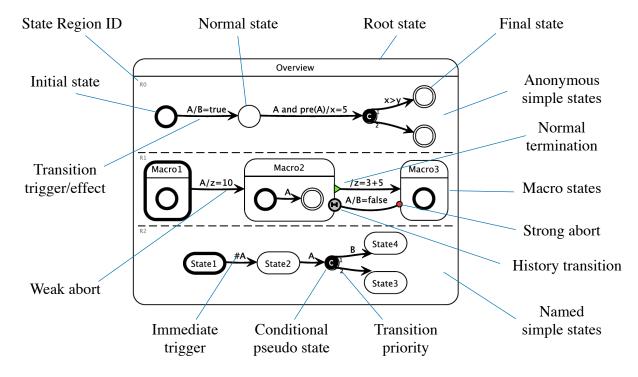

Figure 1: The mapping between SCL statements and SCG subgraphs. Double circles are place holders for SCG subgraphs. Solid arrows depict *seq* (sequential) edges, the dotted line indicates a *tick* edge.

Sec. 4 presents the general scheduling problem, on which Sec. 5 builds to define sequential constructiveness. Sec. 6 presents an approach to analyze whether programs are SC and to compute a schedule for them. Sec. 7 discusses how Esterel/SyncChart-style signals can be emulated with plain shared variables under the SC MoC. Sec. 8 presents SCCharts, a dialect of Statecharts [4] that is inspired by SyncCharts [5] but harnesses the SC MoC to provide a deterministic semantics to a larger class of Statecharts. Sec. 9 relates SC to other MoCs, such as Pnueli and Shalev [6]. We summarize in Sec. 10.

#### 2 Related Work

Edwards [7] and Potop-Butucaru et al. [8] provide good overviews of compilation challenges and approaches for concurrent languages, including synchronous languages and classical work such as Ferrante et al.'s Program Dependence Graph (PDG) [9]. The SC Graph introduced here can be viewed as a traditional control flow graph enriched with data dependence information akin to the PDG for analysis and scheduling purposes.

Esterel [10, 11] provides deterministic concurrency with shared signals. Signals can be written ("emitted") and read ("tested for presence") concurrently. They are absent per default, and become present in a tick whenever any thread chooses to emit them in the current tick. In this sense, signals can be written to concurrently, but there is no write-write race, because any signal emission just sets the signal present, and it does not matter which thread performs this signal emission first or last. Furthermore, within each tick, any signal emissions must be performed before any signal presence tests. Causal Esterel programs on pure signals satisfy a strong scheduling invariant: they can be translated into constructive circuits which are delayinsensitive [12] under the non-inertial delay model [13], which can be fully decided using ternary Kleene algebra [14, 13]. The algebraic transformations proposed by Schneider et al. [15] increase the class of programs considered constructive, but do not permit sequential writes within a tick. The notion of sequential constructiveness introduced here is weaker regarding schedule insensitivity, but more adequate for the sequential memory models available for imperative languages.

Signals in Esterel may also be *valued*, in which case they do not only carry a presence status, but also a value of some type. The emission of a valued signal sets a signal present and assigns it a value. Concurrent emissions of a valued signal are allowed if the signal is associated with a *combination function*. This function must be associative and commutative, which allows to resolve write-write races and ensures a deterministic outcome irrespective of the order in which

the signal emissions are performed. E. g., consider a valued signal x of type int with combination function + and some initial value  $x_0$ ; if at some tick two concurrent signal emissions  $\operatorname{emit} \mathsf{x}(ex_1)$  and  $\operatorname{emit} \mathsf{x}(ex_2)$  are performed, which emit x with the values of the expressions  $ex_1$ ,  $ex_2$ , respectively, the resulting value for x will be  $x_0 + ex_1 + ex_2$ , irrespective of the order in which the additions (signal emissions) are performed. The SC MoC adopts this concept of a combination function, and considers such assignments via a combination function as a relative write.

Finally, Esterel also has the concept of *variables* that can be modified sequentially within a tick. However, they cannot be used for communication among threads, only concurrent reads are allowed. The variable access mechanism of the SC MoC proposed here can be viewed as a combination of Esterel's signals and variables that is more liberal than either one, without compromising determinism.

Lustre [16], like Signal [17], is a data-flow oriented language that uses a declarative, equation-based style to perform variable (stream of values) assignments. Write-write races are ruled out by the restriction to just one defining equation per variable. Write-read races are addressed by the requirement that, within a tick, an expression is only computed after all variables referenced by that expression have been computed. This requires that the write-read dependencies form a partial order from which a schedule can be derived [18]. I. e., there must be no cyclic write-read dependencies. A clock calculus takes account of the fact that not every stream variable is evaluated in every tick. From the result of this schedulability analysis [19] imperative C or Java code can be obtained. To generate this target code, an SC MoC semantics such as presented here is needed.

Caspi et al. [20] have extended Lustre with a shared memory model. Similar to the admissibility concept used in this paper, they defined a *soundness* criterion for scheduling policies that rules out race conditions. However, they adhere to the current synchronous model of execution in that they forbid multiple writes even when they are sequentially ordered.

Synchronous C, a.k.a. SyncCharts in C [21], augments C with synchronous, deterministic concurrency and preemption. It provides a coroutine-like thread scheduling mechanism, with thread priorities that have to be explicitly set by the programmer. The algorithm presented in Sec. 6.2 can be used to automatically synthesize priorities for Synchronous C. PRET-C [22] also provides deterministic reactive control flow, with static thread priorities.

SHIM [23] provides concurrent Kahn process networks with CSP-like rendezvous communication [24] and exception handling. SHIM has also been inspired by synchronous languages, but it does not use the synchronous programming model, instead relying on communication channels for synchronization.

The concept of sequential constructiveness not only applies to textual C/Java-like languages, but also to a graphical formalism such as Statecharts [4]. In fact, the development of a semantically sound, yet flexible and intuitive Statechart dialect was the original motivation for developing the SC MoC. We have developed such a Statechart dialect, named Sequentially Constructive Statecharts (SCCharts) [25], to be used for the development of safety-critical embedded systems in an industrial setting.

The core semantic concepts of SCCharts are analogous to André's SyncCharts [5], which can be viewed as a graphical variant of the synchronous language Esterel [10, 11]. In Esterel Studio, SyncCharts were introduced as Safe State Machines. The Safety Critical Application Development Environment (SCADE) uses a variant of SyncCharts elements to augment dataflow diagrams with reactive behavior, by extending boolean Clocks towards clocks that express state [26, 27]. The main differences between SCCharts and SyncCharts (including those present in SCADE) are:

1. SCCharts are not restricted to constructiveness in Berry's sense [3], but relax this require-

ment to sequential constructiveness. This makes a significantly larger class of Statecharts acceptable without compromising determinism.

2. SCCharts do not introduce signals, but use shared variables. However signals can be fully emulated with variables under SC scheduling. I. e., one can implement signal initialization to "absent" as absolute write with *false*, potentially followed in the same tick by a signal emission implemented as relative write that performs disjunction with *true*.

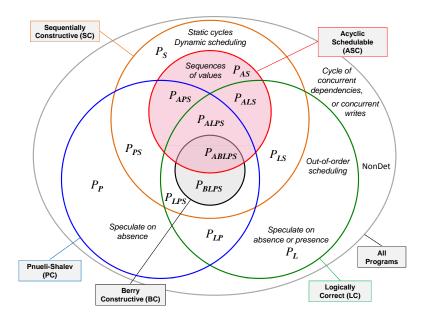

An interesting question is how SCCharts and the SC MoC domain relate to other Statecharts dialects with respect to what class of programs are considered admissible. This opens up a further line of investigations that we plan to persue in the future. Briefly, SC-scheduling is not the only way to interpret the Synchrony Hypothesis, i. e., to execute concurrent threads in a clock-synchronous fashion. What is considered constructively executable depends a lot on the target execution architecture. The more scheduling choices there remain admissible in the target, and thus out of control of the compiler, the more restrictive the compiler has to be in admitting programs, in order to guarantee a deterministic and bounded macro-tick response. If the compiler is permitted to resolve scheduling choices, by sequentializing statements in certain coherent ways, e.g., as we do here, then fewer schedules are admissible. Thus, more programs can execute constructively.

Various other approaches with their own admissible scheduling schemes have been considered for Statecharts. Some are more restricted, some more generous and yet others incomparable with SC admissibility and sequential constructiveness (S-constructiveness). The three most prominent approaches are due to Pnueli and Shalev [6], Boussinot [28] and Berry and Shiple [29], which we refer to as P, L, and B-constructiveness, respectively. We find that B-constructiveness is most restrictive and strictly included in all the notions of {S, P, L}-constructiveness, while the latter are incomparable with each other. We believe that S-constructive programs are more practical than either P- and L-constructive programs. This gains substantial extra ground for programming synchronous interactions compared to the existing imperative synchronous code which is based on B-constructiveness. None of them considers sequential control flow as SC does.

## 3 The SC Language and the SC Graph

To illustrate the SC MoC, we introduce a minimal *SC Language* (SCL), adopted from C/Java and Esterel. The concurrent and sequential control flow of an SCL program is given by an *SC Graph* (SCG), which acts as an internal representation for elaboration, analysis and code generation. Fig. 1 presents an overview of the SCL and SCG elements and the mapping between them.

#### 3.1 The SC Language

SCL program constructs have the following abstract syntax of statements

$$s ::= x = ex \mid s$$

;  $s \mid \text{if } (ex) s \text{ else } s \mid l : s \mid \text{goto } l \mid \text{fork } s \text{ par } s \text{ join } \mid \text{pause}$

where x is a variable, ex is an expression and  $l \in L$  is a program label. The statements s comprise the standard operations assignment, the sequence operator, conditional statements, labelled commands and jumps. As a syntactical detail on the conditional, this, as is the practice in C-like languages, does not use a then keyword, but we will still refer to the two branches as then and else branches. In addition, the two statements introducing synchrony and concurrency

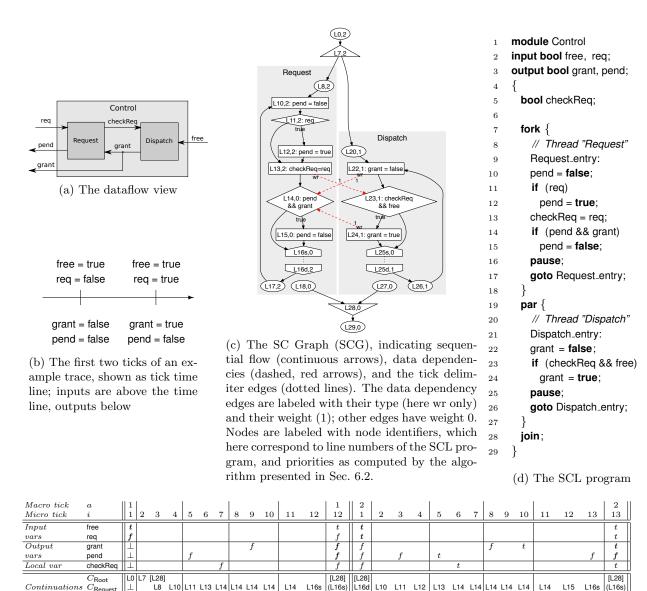

Figure 2: The Control example.

pausing (parentheses).

next, as further explained in Sec. 4.1. Threads may be disabled (denoted  $\perp$ ), active, waiting (square brackets), or

are the pause statement, which deactivates a thread until the next tick commences, and parallel composition, which forks off two threads and terminates (joins) when both threads have terminated. In Esterel, parallel composition is denoted  $\parallel$ ; we here use fork/par/join instead, to provide additional structure and to avoid confusion with the logical or used in expressions. For simplicity, we here only consider parallelism of degree two; larger numbers of concurrent threads can be accommodated by nesting of parallel compositions, or by a straightforward extension of syntax and semantics to support arbitrary numbers of concurrent threads directly.

A well-formed SCL program is one in which (i) expressions and variable assignments are type correct, (ii) there are no duplicate or missing program labels and (iii) no goto jumps into or out of a parallel composition.

To present SCL examples in *concrete textual* as opposed to abstract syntax, more syntactic information is needed. E.g., we typically add braces for structuring the code, subject to conventions regarding the binding strength of the operators (the conditional binds weaker than the sequence). We may also omit empty else branches, or enhance the unstructured goto with structured loops (for, while, etc.). Also, there may be comments and local variable declarations, including their data types, initial values and input/output assignations. However, as our formal development will be based on the internal representation of SCL programs as SC Graphs, we may leave the concrete SCL syntax informal. An illustration of the concrete SCL syntax is the Control example program shown in Fig. 2d and elaborated below.

SCL is a concurrent imperative language with shared variable communication. Variables can be both written to and read from by concurrent threads. Reads and writes are collectively referred to as variable accesses. The sublanguage of expressions ex used in assignments and conditionals is not restricted. All we assume is a function eval to evaluate ex in a given memory  $\rho$  and return a value  $v = eval(e, \rho)$  of the appropriate data type. However, we rule out side effects when evaluating ex.

Esterel *signals* can be coded in SCL using variable accesses as described in Sec. 7. We are also omitting Esterel's abortions and traps, which can be emulated with variables, too; see the ABSWO example discussed in Sec. 8.

#### 3.2 The Control Example

Turning our attention again to the Control example from Fig. 2, we see that this program executes two concurrent *threads*, named Request, and Dispatch. Together with the Root thread, which always runs at the top level, this program thus consists of three threads. Strictly speaking, we must distinguish threads and run-time *thread instances*, since in general one (static) thread can be instantiated multiple times, even within one tick. But for now, this distinction is not important, as in Control there is exactly one run-time instance of each thread.

The functionality of Control is inspired by Programmable Logic Controller software used in the railway domain. It processes requests (as indicated by the input flag req) to a resource, which may be free or not. As indicated in the dataflow/actor view in Fig. 2a, there are two separate functional units, corresponding to the Request and Dispatch threads, which process the requests and dispatch the resource. The output variables indicate whether the resource has been granted or is still pending.

The execution of Control is broken into discrete reactions, the aforementioned (macro) ticks. During each tick, the following sequence is performed:

- 1. read input variables from the environment,

- 2. execute all active (currently instantiated) threads until they either terminate or reach a pause statement,

- 3. write output variables to the environment.

Only the output values emitted at the end of each macro tick are visible to the outside world. The internal progression of variable values within a tick, i. e., while performing a sequence of *micro ticks* (cf. Sec. 3.9), is not externally observable. Hence, when reasoning about deterministic behavior, we only consider the outputs emitted at the end of each macro tick.

(a) Node types, with control flow and tick boundary edges (weight 0)

Figure 3: The syntactical elements of the SC Graph (SCG)

The execution of Control begins with a fork that spawns off Request and Dispatch. These two threads then progress on their own. Were they Java threads, a scheduler of some run time system could now switch back and forth between them arbitrarily, until both of them had finished. Under the SC MoC, their progression and the context switches between them are disciplined by a scheduling regime that prohibits race conditions. Determinism in Control is achieved by demanding that in any pair of *concurrent* write/read accesses to a shared variable, the write must be scheduled before the read. For example, the write to checkReq in node L13 of the SCG (Fig. 2c), corresponding to line 13 of the SCL program (Fig. 2d), is in a different concurrent thread, relative to the read of checkReq (L23). Hence thread Request must be scheduled such that it executes L13 before Dispatch executes L23.

A common means to visualize program traces in synchronous languages is a *tick time line*, as shown in Fig. 2b. As can be seen there, in the first tick, the inputs free = true, req = false produce the outputs grant = pend = false, under the concurrent write-before-read scheduling sketched above.

An interesting characteristic of Control is that the concurrent threads not only share variables, but also modify them sequentially. E.g., Dispatch first initializes grant with false, and then, in the same tick, might set it to true. Similarly, Request might assign to pend the sequence false/true/false. Due to the prescribed sequential ordering of these assignments, this does not induce any non-determinism. However, this would not be permitted under the strict synchronous model of computation, which requires unique variable values per tick. Similarly, pend is read (L14) and subsequently written to (L15); this (sequential) write-after-read is again harmless, although forbidden under the existing synchronous MoC. However, because it is possible to schedule Control such that all concurrent write-before-read requirements are met and all such schedules lead to the same result, we consider Control sequentially constructive. The rest of this paper consists of making this notion precise, and describing a practical strategy to analyze sequential constructiveness and to implement schedules that adhere to the SC model of computation. One building block is the graph abstraction presented in the next section.

#### 3.3 The SC Graph

The SCG syntactical elements are presented in Fig. 3. The SCG for the Control example is shown in Fig. 2c. An SCG is a labelled graph G = (N, E) whose statement nodes N correspond to the statements of the program, and whose edges E reflect the sequential execution ordering and data dependencies between the statements. Every edge  $e \in E$  connects a source  $e.src \in N$  with a target node  $e.tgt \in N$ . Nodes and edges are further described by various attributes.

A node n is labelled by the statement type n.st that it represents, viz.  $n.st \in \{\text{entry, exit, goto}, x = ex$ , if (ex), fork, join, surf, depth $\}$ , where x is some variable and ex is some expression. Nodes labelled with x = ex are referred to as assignment nodes, those with if ex as condition nodes, those with surf as surface nodes; all other nodes are referred by their statement type  $(entry\ nodes,\ exit\ nodes,\ etc.)$ . As illustrated in Fig. 3, in the graphical representations of the SCG the shape of a node indicates the statement type, except for entry/exit/goto nodes, which all are shown as ovals; they share the characteristic that they mainly serve to structure the SCG and could be eliminated without changing the meaning of an SCG. The statement types of SCG nodes are closely related, but not identical to the primitive statements of the SCL language presented in Sec. 3.1; how these statements relate to each other is elaborated in Sec. 3.4.

Every edge e has a type  $e.type \in \{seq, tick, wr, wi, ir, ww\}$  that specifies the nature of the particular ordering constraint expressed by e. We write  $e.src \rightarrow_{\alpha} e.tgt$ , pronounced "e.src  $\alpha$ -precedes e.tgt," if  $e.type = \alpha$ .

Edges of the form  $n_1 \to_{seq} n_2$  and  $n_1 \to_{tick} n_2$  are induced directly from the source program. In the former case the two nodes  $n_1$  and  $n_2$  are sequential successors, and in the latter case tick successors. Collectively they are referred to as flow successors, and edges of type seq or tick are referred to as flow edges. A path consisting exclusively of flow edges is referred to as flow path. We use  $\to_{seq}$  for the reflexive and transitive closure of  $\to_{seq}$ .

Informally,  $n_1 \to_{seq} n_2$  holds if the statements may execute in the same tick, and a sequential control flow enforces  $n_1$  to be executed immediately before  $n_2$ . In other words, the program order never generates a situation in which the scheduler is free to choose between  $n_1$  or  $n_2$ . Note that  $n_1 \to_{seq} n_2$  does not necessarily mean that there is a fixed run-time ordering between  $n_1$  and  $n_2$ . For example, when  $n_1$  and  $n_2$  are enclosed in a loop, there might be an execution sequence  $n_1, n_2, n_1, n_2$  within the same tick.

The relationship  $n_1 \to_{tick} n_2$  says that there is a tick border between  $n_1$  and  $n_2$ , i.e., the control flow passes from  $n_1$  to  $n_2$  not instantaneously in the same tick, as with  $n_1 \to_{seq} n_2$ , but only upon a global clock tick. All other types of edges  $n_1 \to_{\alpha} n_2$  for  $\alpha \in \{wr, wi, ir, ww\}$  are derived for the purpose of scheduling analysis and discussed later in Sec. 6.

#### 3.4 Mapping SCL to an SCG

Fig. 1 gives a schematic overview of how the SCL statements introduced in Sec. 3.1 correspond to an SCG. This is formally described in the following.

To handle compound statements, we need the concept of an SCG subgraph.

**Definition 1** (SCG subgraphs). For an SCG G = (N, E), an SCG subgraph  $G_{sub} = (N_{sub}, E_{sub}, in, Out)$  consists of a set of statement nodes  $N_{sub} \subseteq N$ , a set of edges  $E_{sub} \subseteq N \times N$ , an incoming

<sup>&</sup>lt;sup>1</sup>Strictly speaking, "x = ex" and "if (ex)" each denote a multitude of statements, ranging over all variables x and expressions ex. However, to not make the notation unnecessarily heavy, we here treat them like the other statements that are not parameterized.

node  $in \in N_{sub}$ , and a set of outgoing nodes  $Out \subseteq N_{sub}$ . These elements are also referred to as  $G_{sub}.N_{sub}$ , etc.

The SCG subgraph corresponding to an SCL statement s is denoted SCG(s).

- An SCL program s corresponds to an SCG consisting of the nodes and edges of SCG(s), plus an entry node  $n_e$ , an exit node  $n_x$ , a seq-edge from  $n_e$  to SCG(s).in, and seq-edges from all  $n \in SCG(s).Out$  to  $n_x$ .

- For s being an assignment x = ex, we stipulate  $SCG(s) = (\{n\}, \emptyset, n, \{n\})$ , where n is an assignment node with n.st = "x = ex."

- For s being a sequence  $s_1$ ;  $s_2$ , we have  $SCG(s) = \{SCG(s_1).N_{sub} \uplus SCG(s_2).N_{sub}, SCG(s_1).E_{sub} \uplus SCG(s_2).E_{sub} \uplus E', SCG(s_1).in, SCG(s_2).Out\}$ , where  $\uplus$  is disjoint union and E' consists of seq-edges from the nodes in  $SCG(s_1).Out$  to  $SCG(s_2).in$ .

- If s is a conditional if (ex)  $s_1$  else  $s_2$ , then  $SCG(s) = \{SCG(s_1).N_{sub} \uplus SCG(s_2).N_{sub} \uplus \{n\}, SCG(s_1).E_{sub} \uplus SCG(s_2).E_{sub} \uplus E', n, SCG(s_1).Out \cup SCG(s_2).Out\}$ , where n is a conditional node with n.st = "if ex," and E' contains edges  $n \to_{seq} true(n)$  and  $n \to_{seq} false(n)$ , in which  $true(n) := SCG(s_1).in$  and  $false(n) := SCG(s_2).in$  are the two uniquely defined true and false branch nodes of the conditional.

- For s being a goto l statement that jumps to a labeled statement l: s', it is  $SCG(s) = \{\{n\}, \{e\}, n, \emptyset\}\}$ , where n is a goto node, i. e., n.st = goto, and e an edge  $n \to_{seq} SCG(s').in$ .

- For s being a parallel statement fork  $s_1$  par  $s_2$  join, it is  $SCG(s) = \{SCG(s_1).N_{sub} \uplus SCG(s_2).N_{sub} \uplus \{n_f,n_j,n_{e1},n_{e2},n_{x1},n_{x2}\},SCG(s_1).E_{sub} \uplus SCG(s_2).E_{sub} \uplus E',n_f,\{n_j\}\},$  where  $n_f$  is a fork node and  $n_j$  a join node; furthermore,  $n_{e1}$ ,  $n_{e2}$  are entry nodes and  $n_{x1}$ ,  $n_{x2}$  exit nodes for each created thread that are connected to the fork and join node, respectively, and to  $SCG(s_1)$  and  $SCG(s_2)$  as indicated in Fig. 1. Observe that the join node  $n_j$  is uniquely associated with the fork  $n_f$ , which can be expressed by writing  $n_j = join(n_f)$ . As noted earlier, for simplicity we here only consider parallelism of degree two, but an extension to higher degrees would be straightforward.

- For s being a pause statement, it is  $SCG(s) = \{\{n_s, n_d\}, \{e\}, n_s, \{n_d\}\}\}$ , where  $n_s$  is a surface node and  $n_d$  a depth node, and e is a tick-edge from  $n_s$  to  $n_d$ . This models the fact that the statement can be active at the end of a tick and at the beginning of the subsequent tick. In a well-formed SCG  $n_d$  is the unique tick successor  $tick(n_s) = n_d$  of  $n_s$ . i. e., whenever n.st = surf then  $n \to_{tick} tick(n)$  and tick(n).st = depth.

#### 3.5 Thread Terminology

We distinguish the concept of a static *thread*, which relates to the structure of a program, from a dynamic *thread instance* (see Sec. 3.10), which relates to a program in execution. We here define our notion of (static) threads, building on the SCG program representation G = (N, E) with statement nodes N and control flow edges E.

Let T denote the set of threads of G. Each thread  $t \in T$ , including the top-level Root thread, is associated with unique entry and exit nodes t.en,  $t.ex \in N$  with  $statement\ types\ t.en.st = entry$  and t.ex.st = exit.

Each  $n \in N$  belongs to a thread th(n), defined as the immediately enclosing thread  $t \in T$  such that there is a flow path to n (as defined in Sec. 3.3) that originates in t.en and that does

```

entry

module Reinc

1

output int x, y;

2

3

loop:

4

fork

5

6

// Thread T1

7

x = 1;

8

9

par

10

// Thread T2

11

pause;

x = 2;

12

13

ioin:

14

goto loop;

15

16

exit

(a) The SCL program

(b) The SCG

```

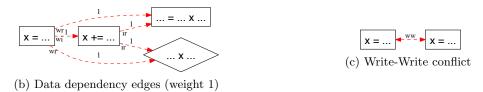

Figure 4: The Reinc example, illustrating thread reincarnation. The assignments to x are both executed in the same tick, yet are sequentialized.

not traverse any other entry node t'.en, unless that flow path subsequently traverses t'.ex also. For each thread t we define sts(t) as the set of statement nodes  $n \in N$  such that th(n) = t. For example, the Control program (Fig. 2) consists of the threads  $T = \{\text{Root}, \text{Request}, \text{Dispatch}\}$ , and the Root thread consists of the statement nodes  $sts(\text{Root}) = \{\text{L0}, \text{L7}, \text{L28}, \text{L29}\}$ . The remaining statement nodes of N are partitioned into sts(Dispatch) and sts(Request), as indicated in Fig. 2c.

We define fork(t) to be the fork node that immediately precedes t.en. Every thread  $t \neq \mathsf{Root}$  has an immediate  $parent\ thread\ p(t)$ , defined as th(fork(t)). In the Control example,  $p(\mathsf{Request}) = p(\mathsf{Dispatch}) = \mathsf{Root}$ .

We are now ready to define (static) thread concurrency and subordination:

**Definition 2** (Ancestor/Subordinate/Concurrent Threads). Let  $t, t_1, t_2$  be threads in T.

- 1. The set of ancestor threads of t is recursively defined as  $p^*(t) = \{t, p(t), p(p(t)), \dots, Root\}$ .

- 2.  $t_1$  is subordinate to  $t_2$ , written  $t_1 \prec t_2$ , if  $t_1 \neq t_2$  and  $t_1 \in p^*(t_2)$ .

- 3.  $t_1$  and  $t_2$  are concurrent, denoted  $t_1 \mid\mid t_2$ , iff they are descendants of distinct threads sharing a common fork node, i. e., iff there exist  $t'_1 \in p^*(t_1)$ ,  $t'_2 \in p^*(t_2)$  with  $t'_1 \neq t'_2$  and  $fork(t'_1) = fork(t'_2)$ . We then refer to this fork node as the least common ancestor fork, denoted lcafork $(t_1, t_2)$ . This is lifted to nodes, i. e., if  $th(n_1) \mid\mid th(n_2)$  then  $lcafork(n_1, n_2) = lcafork(th(n_1), th(n_2))$ .

In Control, it is Root  $\prec$  Request and Root  $\prec$  Dispatch. It is also Request || Dispatch, whereas Root is not concurrent with any thread. Note that concurrency on threads, in contrast to concurrency on node instances (Def. 4), is purely static and can be checked with a simple, syntactic analysis of the program structure.

#### 3.6 Thread Reincarnation—The Reinc Example

The Reinc example shown in Fig. 4 illustrates that *static* thread concurrency is not sufficient to capture whether individual statements are *run-time concurrent*, in the sense that it would be

up to the discretion of a scheduler how they should be ordered. Consider the assignments x = 1 (L7) and x = 2 (L12). These are in the concurrent threads T1 and T2, and can be activated in the same tick, but they are still sequentially ordered and thus not run-time concurrent. This is due to the *reincarnation* of T2, which takes place as follows.

In the initial tick, T1 executes L7 and terminates, and T2 rests at L11 (pause). Thus there is one instance of each thread that executes in the initial tick. In subsequent ticks, first T2 continues with L12 and terminates, which enables the join (L14) and, after the loop, both T1 and T2 get started again, in a second instance during the same tick, and as in the initial tick, T1 executes L7 and terminates, and T2 rests at L11. Thus, L12 gets executed in the *first* instance of T2, but it is the *second* instance of T2 that is concurrent to the execution of L7. As a result, the concurrent writes to x in L12 and L7 are cleanly separated through the sequential loop, and the deterministic result for x at the end of each tick is the value 1.

The definition of the least common ancestor fork (Def. 2) helps to capture this. The fact that L12 and L7 are not run-time concurrent is because their executions go back to different executions of lcafork(L12, L7) = L5. L12 is executed in an instance of T2 that was forked off by an execution of L5 in the previous tick, whereas L7 is executed in an instance of T1 forked off by an execution of L5 in the current tick. Thus our definition of run-time concurrency of two statements  $n_1, n_2$ , provided in the following, also refers to instances (executions) of  $lcafork(n_1, n_2)$ .

#### 3.7 Thread Trees—The Reinc2 Example

The Reinc2 example shown in Fig. 5 is a more elaborate variant of Reinc that illustrates a more complex thread structure. Specifically, we have T21 || T22, T23 || T24, and T1 || t for all  $t \in \{T2, T21, T22, T23, T24\}$ .

The thread tree, shown in Fig. 5c, is a means to visualize the thread relationships. It contains a subset of the SCG nodes, namely the thread entry nodes, labeled with the names of their threads, and the fork nodes, which are attached to the entry nodes of their threads. Threads are concurrent iff their least common ancestor (lca) in the thread tree is a fork node. E.g., T21 and T23 are not concurrent, because their lca is the thread entry node T2, meaning that T21 and T23 are sequential within T2. The thread tree is conceptually similar to the AND/OR tree used to illustrate state relationships in Statecharts [4]; fork nodes correspond to AND states, denoting concurrency, whereas the thread entry nodes correspond to OR states, denoting exclusive/sequential behavior.

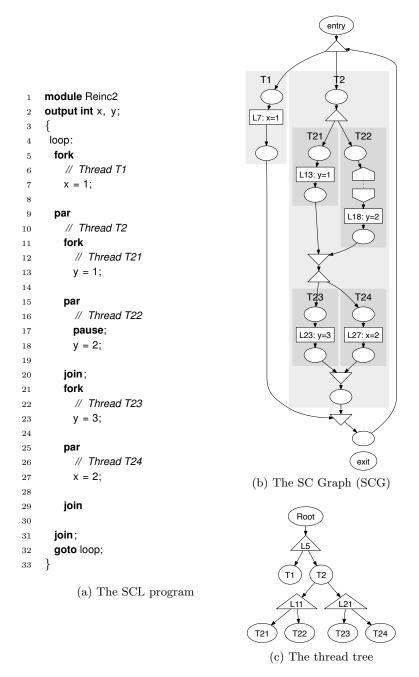

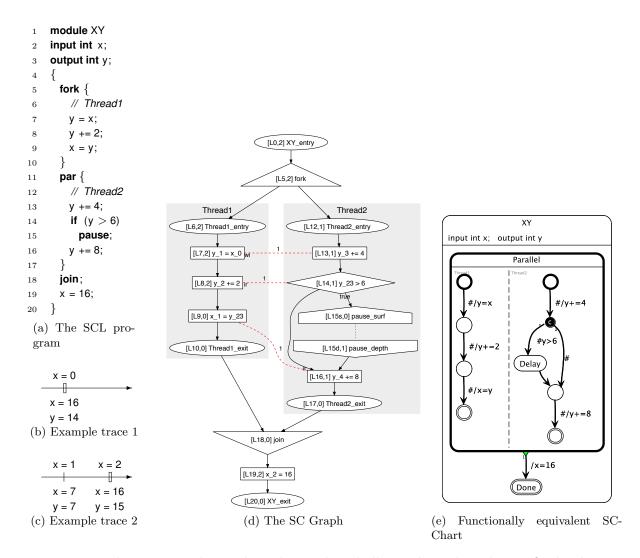

#### 3.8 Statement Reincarnation—The InstLoop Example

The InstLoop example shown in Fig. 6 illustrates the issue of statement reincarnation. In particular, the statically concurrent accesses to x in L7 and L11 are executed twice within a tick, because the loop iterates two times. Because of the data dependency on x, L7 must be scheduled before L11—but only within the same loop iteration.

Traditional synchronous programming would consider such a loop that does not separate iterations by pause statements to be *instantaneous*, and hence reject this program, on the justification that the instantaneous loop might potentially run forever. However, the SC MoC does not have a problem with this program, as it is still deterministic. The loop in InstLoop also happens to be executed only two times. Of course, one might still want to ensure that a program always terminates, but this issue is orthogonal to determinism and having a well-defined semantics.

As this example highlights, it is not enough to impose an order on the program statements. To capture precisely the concept of sequential constructiveness, we need to distinguish statement

Figure 5: The Reinc2 example, a more elaborate example of thread concurrency and thread reincarnation

instances. The key here is again the least common ancestor fork; the specific executions of L7 and L11 that go back to the same execution of lcafork(L7, L11) = L5 must be ordered.

#### 3.9 Macro Ticks, Micro Ticks, and the Thread Status

As already described, the externally observable execution of a synchronous program consists of a sequence of macro ticks. Internally, however, one typically breaks down a macro tick into a series of *micro ticks*, both for describing the semantics and for a concrete implementation. We call this series of micro ticks a *run*, whereas a *trace* describes only the externally visible output

Figure 6: The InstLoop example, with an instantaneous loop that leads to statement reincarnation within a tick

values emitted at each macro tick.

**Definition 3** (Ticks). For an SCG G = (N, E), a (macro) tick R, of length  $len(R) \in \mathbb{N}_{\geq 1}$ , is a mapping from micro tick indices  $1 \leq j \leq len(R)$ , to nodes  $R(j) \in N$ . A run of G is a sequence of macro ticks  $R^a$ , indexed by  $a \in \mathbb{N}_{\geq 1}$ .

Another way to look at a macro tick is as a linearly ordered set of node instances, viz. pairs ni = (n, i) consisting of a statement node  $n \in N$  and a micro tick count  $i \in \mathbb{N}$ . Concretely, each R can be identified with the set  $\{(n, i) \mid 1 \le i \le len(R), n = R(i)\}$ . A special case is the empty macro tick with len(R) = 0 and  $R = \emptyset$ . Sometimes it is convenient to view macro ticks as sequences of nodes  $R = n_1, n_2, \ldots, n_k$  where k = len(R) and  $n_i = R(i)$  for all  $1 \le i \le k$ .

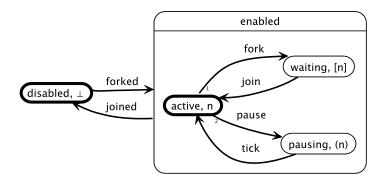

One possible run of the Control example is illustrated in Fig. 2e. We also see for each micro tick the node that is scheduled next for execution. An assignment results in an update of the written variable, reflected by the variable values of the subsequent micro tick. The continuations, explained further in Sec. 4, denote the current state of each thread, i. e., the node (statement) that should be executed next, similar to a program counter. In addition, a continuation denotes what execution state a thread is in. Fig. 7 illustrates the possible states using a SyncChart notation. Threads other than the Root thread are initially disabled, with a status denoted by  $\bot$ . When a thread gets forked by its parent, it becomes enabled. Enabled threads are initially active, i. e., eligible for execution, with a status denoted by the node to be executed next. When an active thread forks off some child threads, it becomes waiting, denoted by the node to be executed next in square brackets, until the child threads join and the parent becomes active again. An active thread that executes a pause statement and thus finishes its current tick becomes pausing, denoted in parentheses, until the next tick is started and it becomes active again.

Figure 7: Execution states of a thread

#### 3.10 Concurrency of Node Instances

For a macro tick R, an index  $1 \le i \le len(R)$ , and a node  $n \in N$ ,  $last(n,i) = max\{j \mid j \le i, R(j) = n\}$  retrieves the last occurrence of n in R at or before index i. If it does not exist,  $last(n,i) = 0.^2$  The function last(n,i) is instrumental to define concurrency of node instances as discussed above in Secs. 3.6 and 3.8.

**Definition 4** (Concurrent Node Instances). For a macro tick R,  $i_1, i_2 \in \mathbb{N}_{\leq len(R)}$ , and  $n_1, n_2 \in \mathbb{N}$ , two node instances  $ni_1 = (n_1, i_1)$  and  $ni_2 = (n_2, i_2)$  are concurrent in R, denoted  $ni_1 \mid_R ni_2$ , iff

- 1. they appear in the micro ticks of R, i. e.,  $n_1 = R(i_1)$  and  $n_2 = R(i_2)$ ,

- 2. they belong to statically concurrent threads, i. e.,  $th(n_1) || th(n_2)$ , and

- 3. their threads have been instantiated by the same instance of the associated least common ancestor fork, i. e.,  $last(n, i_1) = last(n, i_2)$  where  $n = lcafork(n_1, n_2)$ .

In the Control example of Fig. 2e, the variable accesses that are *concurrent* involve checkReq and grant. We call this particular run *admissible* because all concurrent variable accesses follow certain admissibility rules, defined in detail later (Sec. 5.2, pages 5.2 ff). The run here is admissible because the write to checkReq (L13) is scheduled before the corresponding read (L23), and similarly the writes to grant (L22 and potentially L24) are scheduled before the read (L14).

## 4 "Free" Scheduling of SCGs

With the above preliminaries in place, we now come to discuss the semantics of SCL. We do this by looking at the execution and scheduling of a fixed SCG G = (N, E) associated with some arbitrary program. We begin by considering the "free execution" of G based on the program orders  $\rightarrow_{seq}$  and  $\rightarrow_{tick}$ . Our notion of sequential constructiveness will then arise from a further restriction of the "free" schedules guided by additional sequentiality orders  $\rightarrow_{\alpha}$  for  $\alpha \in \{wr, wi, ir, ww\}$ .

Traditional schedulers work at machine instruction granularity. This means that thread context switches can basically occur anywhere within any statement. In principle, we could

<sup>&</sup>lt;sup>2</sup>Strictly, last(n, i) should be written last(R, n, i) as it depends on the macro tick R, not only on n and i. For notational compactness, we leave this implicit, however.

allow this flexibility also for the SC MoC. For simplicity, we restrict ourselves to scheduling at the statement level. In particular, the evaluation of expressions and the update of variables in assignments happens atomically. On the other hand, a conditional statement if (ex)  $s_1$  else  $s_2$  sequentially separates the decision based on the (atomic) evaluation of ex from the execution of the appropriate branching command  $s_i$ .

#### 4.1 Continuations and Continuation Pool

Our simulation semantics is based on *continuations* which are instances of program nodes from the SCG enriched with information about the run-time context in which the nodes are executed. In general imperative languages this may comprise explicit thread identification, instance numbers, local memory, reference to stack frames and other scheduling information. For the simple SCL language considered in this paper and for the "free" scheduling to be defined in this section, only few data are needed. It suffices to let continuations contain the currently running node in the SCG and a *scheduling status* to indicate whether the continuation is *active*, *waiting* or *pausing*.

Formally, a continuation c has a node  $c.node \in N$  and a status  $c.status \in \{active, waiting, pausing\}$ . We refrain from identifying continuations with the pairs (c.node, c.status) in order to allow for other attributes in enriched versions of the semantics. Instead, we write c[s::n] when s=c.status and n=c.node, or to express that the status and node of a continuation c are updated to be s and n, respectively. The waiting status is derivable from subordination of threads: If  $th(c'.node) \prec th(c.node)$ , then c' runs in a proper ancestor thread of c and thus c' must wait for c. We overload notation and write  $c' \prec c$  in this case.

The statuses of continuations (defined here) and threads (introduced in Sec. 3.9) are closely related, but not identical concepts. For a thread that is enabled and hence has a continuation, the status of the thread is the status of its continuation; however, there is no disabled status for continuations, and disabled threads do not have a continuation associated with them.

At every micro tick of an execution run, the scheduler picks an active continuation from a pool of continuations and executes it. A  $continuation\ pool$  may be modelled simply as a finite set C of continuations, subject to some constraints outlined below, since all information is contained in the attributes of its elements.

Initially, C only contains the main program Root activated at its entry node Root.en. Then, every time an active fork node is executed the corresponding join node is installed in the same thread as the fork. This thread is subordinate to the threads of the children spawned by the fork which thus block the execution of the continuation in the parent thread. In this fashion, the join node of the parent thread starts with status waiting until the children are terminated, at which point its status becomes active. The switching between active and pausing happens in the execution of the pause statement. When an active surf node is scheduled, its status changes to pausing, thereby suspending it for the current macro tick. When the execution switches to the next macro tick, the thread is re-activated at the uniquely associated depth node.

Looking back at the execution run of Fig. 2b we can see the thread pool  $C_i^a$  in micro tick i of macro tick i being made up of the entries in the rows  $C_{\mathsf{Root}}$ ,  $C_{\mathsf{Request}}$  and  $C_{\mathsf{Dispatch}}$  at column index i. The entries show the continuations' nodes and status. Nodes in square brackets [n] are waiting, those in brackets (n) are pausing and all othere are active.

Continuation pools satisfy some coherence properties. The waiting continuations  $c[\text{waiting} :: n] \in C$  are precisely those continuations in C that are not  $\prec$ -maximal in C and they must always be join nodes, i.e., n.st = join. All  $\prec$ -maximal continuations have status active or

pausing. Of those, the pausing continuations  $c[\text{pausing} :: n] \in C$  must be surface nodes, i.e., n.st = surf. Moreover, the threads appearing in a continuation pool preserve the tree structure. For each  $c \in C$  such that  $th(c.node) \neq \text{Root}$ , there is a unique parent  $c' \in C$  such that p(th(c.node)) = th(c'.node). By construction, the parent continuation always corresponds to a waiting join statement, i.e., c'.node.st = join and c'.status = waiting. A continuation pool satisfying these constraints is called valid.

#### 4.2 Configurations, Micro Step and Macro Step Scheduling

A configuration is a pair  $(C, \rho)$  where C is a pool of continuations and  $\rho$  is a memory assigning values to the variables accessed by G. A configuration is called valid if C is valid. We wish to perform a single scheduling step to move from the current configuration  $(C_{cur}, \rho_{cur})$  to the next configuration  $(C_{nxt}, \rho_{nxt})$ . In general, this involves the execution of one or more continuations from  $C_{cur}$ . Our "free" schedule is restricted (i) to execute only  $\prec$ -maximal threads and (ii) to do so in an interleaving fashion: