## ENERGY-TIME PERFORMANCE OF HETEROGENEOUS COMPUTING SYSTEMS: MODELS AND ANALYSIS

## Lavanya Ramapantulu

M.S. Microelectronics, Birla Institute of Technology and Science

A THESIS SUBMITTED FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

DEPARTMENT OF COMPUTER SCIENCE NATIONAL UNIVERSITY OF SINGAPORE

2016

#### DECLARATION

I hereby declare that the thesis is my original work and it has been written by me in its entirety.

I have duly acknowledged all the sources of information which have been used in the thesis.

No portion of the work referred to in this thesis has been submitted in support of an application for another degree of qualification at this or any other university or institution of learning.

R. Lavanya

Lavanya Ramapantulu 12 May 2016

# Abstract

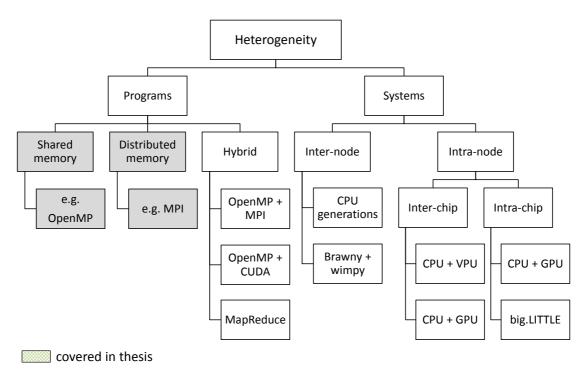

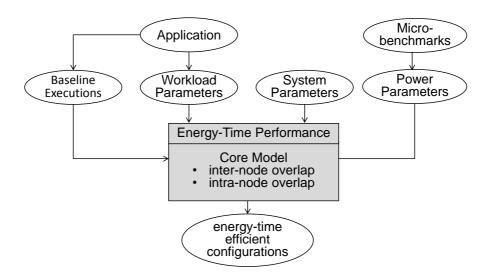

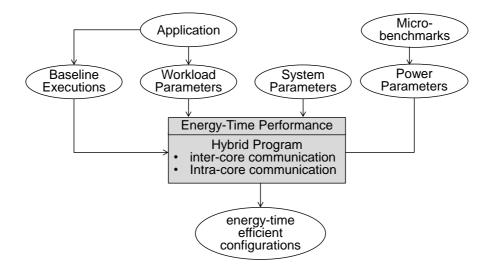

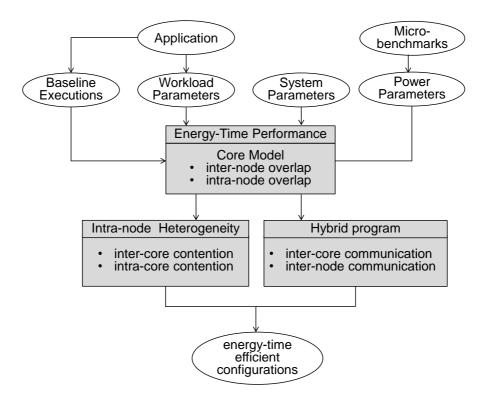

While heterogeneity is increasingly becoming the norm in most computing platforms today, one of the key challenges is to determine the set of energy-time efficient system configurations among the large system configuration space to execute a parallel application. This large configuration space offers a new opportunity to improve the match between parallel application demands and system resources to achieve efficient energy-time performance. This thesis presents an approach to address this challenge using a *measurement-driven analytical model* that determines both time and energy efficient system configurations. Based on our taxonomy of heterogeneous computing systems, we first propose a core analytical model for a baseline heterogeneous system representing *inter-node heterogeneity* and consisting of brawny and wimpy nodes. The proposed core model is scalable for different types of heterogeneity and is formulated using parametric values obtained from baseline measurements of the application for better accuracy. The key novelties of our approach include modeling both inter and intra-node resource overlaps and resource contention.

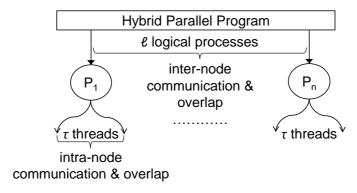

Among heterogeneous systems, intra-node heterogeneous systems with Vector Processing Units (VPUs) are increasingly being adopted in the Top500 supercomputers as they offer accelerated performance gains. Secondly, the impact of heterogeneity in parallel programs leads to the wider adoption of hybrid programming models for scientific applications. Hybrid programming models are gaining traction as they exploit system resources and parallelism at both inter- and intranode levels. The scalability of our proposed core model is shown by extending it to both *intra-node heterogeneous system* and *hybrid programs*. Key model extensions include (i) inter- and intra-core contentions for VPUs in a Many Integrated Core (MIC) architecture system, and (ii) inter- and intra-node communication for hybrid programs.

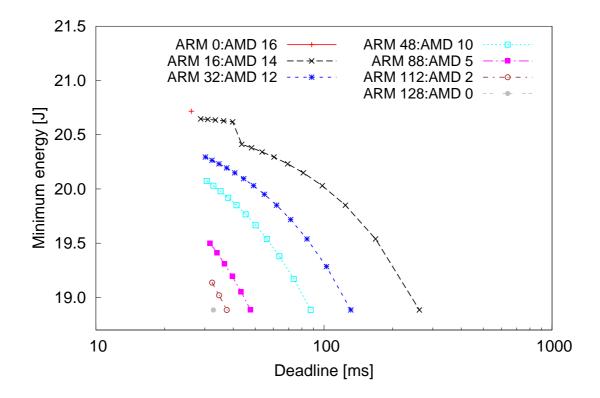

With the advent of heterogeneity at both program and system level, it is nontrivial for application developers or users to choose an energy and time optimal configuration from the large configuration space. The proposed core model and its extensions are applied to determine energy-time efficient system configurations for inter-node heterogeneous system, intra-node heterogeneity with VPUs and hybrid programs. In determining these efficient system configurations, we exposed a number of insights. Firstly, there are *multiple Pareto-optimal "sweet-spot" configurations* that can be approximated using a distinct energy-deadline *Pareto-frontier*. These configurations facilitate energy-time trade-offs such as to minimize energy used for a given execution-time deadline and/or to minimize execution time for a given energy budget. Our analysis shows that for inter-node heterogeneous clusters and hybrid programs, energy savings of up to 75% can be achieved by selecting Pareto-optimal configurations as opposed to non-optimal configurations. Furthermore, among the Pareto-optimal configurations hybrid programs reduces the energy used by up to 65% at the expense of 18% increase in execution time.

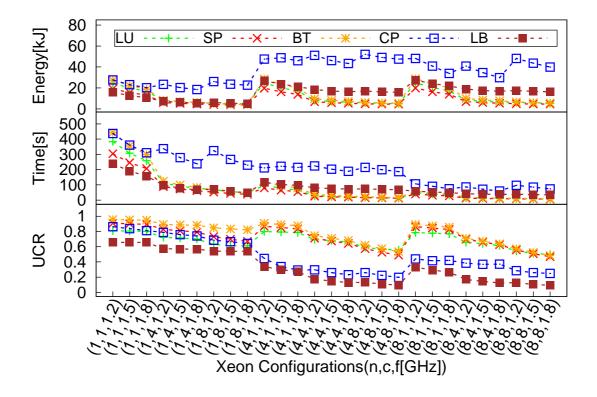

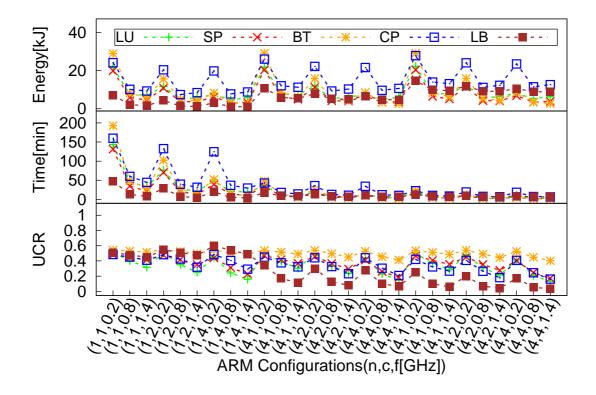

With the explosion of the configuration space, we show that the Pareto-frontier can be analytically established using the node *performance-to-power ratios (PPR)*. We show that the Pareto-frontier can be further improved by replacing low PPR nodes with higher PPR nodes using our power substitution ratio. Additionally, our energy proportionality analysis reveals that inter-node heterogeneous clusters enable the scaling of the energy-proportionality wall by exposing sub-linear energyproportional configurations. To further optimize the Pareto-frontier, we introduce a new metric called *useful computation ratio (UCR)* to quantify the degree of resource contentions and communication overheads in an execution. Lastly, we show how UCR and Pareto-optimal configurations can be used in conjunction by system designers to gain further insights into system resource imbalances, and how application developers can further fine-tune their hybrid programs. Science is bound, by the everlasting vow of honour, to face fearlessly every problem which can be fairly presented to it. – Lord Kelvin

## Acknowledgments

I would like to express my sincere gratitude to my thesis advisor Professor Teo Yong Meng. The door to Professor Teo's office was always open whenever I needed help or had a question about my research or writing. He has taught me the nuances of research by asking the right questions to help me think clearly and present my thoughts in a coherent manner. His guidance struck the right balance between giving me the freedom to follow my ideas and steering me in the right direction whenever he thought I needed it. His teaching style of asking the right questions inspires me to embark on an academic career. Thank you, Professor Teo for your advice and support during my PhD studies.

I would like to take this opportunity to thank my thesis advisory committee, Professor Ooi Wei-Tsang and Professor Wong Weng-Fai for their comments, feedback and support during the various milestones of my candidature. I would like to thank Professor Chin Wei Ngan, Professor Ooi Beng Chin, Professor Ananda and Professor Lakshminarayanan for being supportive and lending their systems for my research. My heartfelt gratitude to Madam Loo Line Fong for her continuous support both before joining and during my PhD candidature. I thank the staff in the graduate office for their support in administrative matters and enabling me to attend conferences to present my research. I recognize that this research would not have been possible without financial assistance and express my sincere gratitude to the Ministry of Education, Singapore.

A special acknowledgement to my mentors in the lab, Dr. Bogdan Marius Tudor and Dr. Cristina Carbunaru, from whom I have learnt the nitty-gritty details involved in writing technical research papers. A special thank you to my wonderful colleague and collaborator Dumitrel Loghin for discussing my research and reviewing my work. I would like to thank my lab mates over the years Khanh, Linh, Trang, Saeid, Thy, Oana, Sunimal, Suman, Irvan for making the work place enjoyable.

I thank all my friends who made my stay in Singapore such a wonderful experience. Marcel, Pooja, Sreetama, Subhasree, Sudipta, Shuang Liu for their advice during the different milestones of my PhD studies; Akshay, Asha, Parvathy, Neha, Sanat for making me feel at home; Prasanta, Anirudh, Abhra, Bhargava, Yang Yi for the discussions on life philosophies; Mahsa, Maryam, Huping, Chundong, Yamilet, Anh and the NUS Buddhist society for enhancing my cultural experience; Peichu, Sergey, Shin Hwei for company to play table-tennis; Kuldeep, Rajiv for being wonderful cohort mates; and many more friends who made this journey an enjoyable one.

Last but not the least, I would like to thank my family and friends for being a source of strength, love and encouragement despite being thousands of miles away from me. Finally, I thank my friend, philosopher and life-guide Anshoo Tandon without whom I would not have embarked on this defining chapter of my life.

I am sure that there are many more to thank and sincerely apologize to those that are overlooked.

## List of Publications

- L. Ramapantulu, B.M. Tudor, D. Loghin, T. Vu and Y.M. Teo, *Modeling the Energy Efficiency of Heterogeneous Clusters*, Proceedings of 43rd International Conference on Parallel Processing, pp 321-330, Minneapolis, USA, Sep 9-12, 2014. [Inter-node Heterogeneity]

- L. Ramapantulu, D. Loghin and Y.M. Teo, An Approach for Energy Efficient Execution of Hybrid Parallel Programs, Proceedings of 29th IEEE International Parallel and Distributed Processing Symposium, pp 1000-1009, Hyderabad, INDIA, May 25-29, 2015. [Hybrid Programs]

- D. Loghin, L. Ramapantulu, O. Barbu and Y.M. Teo, A Time-Energy Performance Analysis of MapReduce on Heterogeneous Systems with GPUs, Performance Evaluation - An International Journal, Vol 91, pp 255-269, Elsevier, 33rd International Symposium on Computer Performance, Modeling, Measurement and Evaluation (IFIP WG 7.3 Performance 2015), Sydney, AUSTRALIA, Oct 19-21, 2015. [Inter-chip and Intra-chip Heterogeneity]

- 4. L. Ramapantulu, D. Loghin and Y.M. Teo, On Energy Proportionality and Time-Energy Performance of Heterogeneous Clusters, Proceedings of 18th IEEE Cluster Conference, Taipei, Taiwan, Sep 12-16, 2016. (accepted) [Inter-node Heterogeneity]

- L. Ramapantulu, T. Dao, D. Loghin, N. Thoai and Y.M. Teo, Modeling the Energy-Time Performance of MIC Architecture System, Proceedings of 24th IEEE Conference on Modeling, Analysis and Simulation of Computer and Telecommunication Systems, London, UK, Sep 19-21, 2016. (accepted) [Intra-node Heterogeneity]

# **Table of Contents**

| Al            | bstra | i i                                       | ii       |

|---------------|-------|-------------------------------------------|----------|

| A             | cknov | vledgements v                             | ii       |

| $\mathbf{Li}$ | st of | Publications i                            | x        |

| Li            | st of | Figures x                                 | v        |

| $\mathbf{Li}$ | st of | Tables xi                                 | x        |

| 1             | Intr  | oduction                                  | 1        |

|               | 1.1   | Motivation                                | 3        |

|               | 1.2   | Challenges and Research Questions         | 4        |

|               | 1.3   | Objective and Contributions               | 8        |

|               | 1.4   | Thesis Organization                       | 1        |

| <b>2</b>      | Rela  | ted Work 1                                | 5        |

|               | 2.1   | Heterogeneous Computing Systems           | 5        |

|               |       | 2.1.1 Systems                             | 8        |

|               |       | 2.1.2 Programs                            | 5        |

|               | 2.2   | Approaches                                | 8        |

|               |       | 2.2.1 Energy Efficiency                   | 9        |

|               |       | 2.2.2 Energy Proportionality              | 1        |

|               |       | 2.2.3 Time Performance                    | 6        |

|               | 2.3   | Heterogeneity and Energy-time Performance | 2        |

|               | 2.4   | Summary                                   | 3        |

| 3             | App   | roach and Core Model 4                    | <b>5</b> |

|               | 3.1   | Overview                                  | 5        |

|   | 3.2               | Core 1   | Model                                                                                                                                        | 48  |

|---|-------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------|-----|

|   |                   | 3.2.1    | Model Inputs                                                                                                                                 | 48  |

|   |                   | 3.2.2    | Execution Time Model                                                                                                                         | 50  |

|   |                   | 3.2.3    | Matching Technique                                                                                                                           | 54  |

|   |                   | 3.2.4    | Energy Model                                                                                                                                 | 56  |

|   | 3.3               | Valida   | $ation \ldots \ldots$ | 57  |

|   |                   | 3.3.1    | Workloads and Setup                                                                                                                          | 58  |

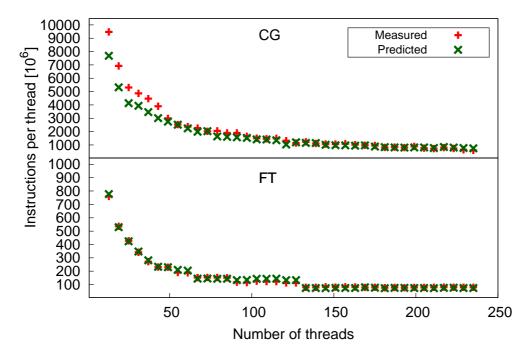

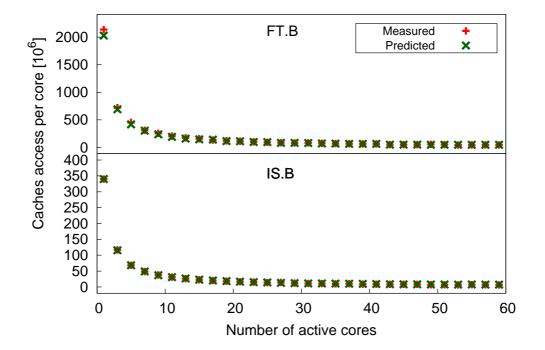

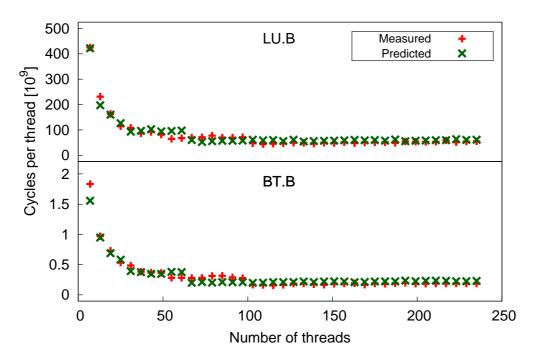

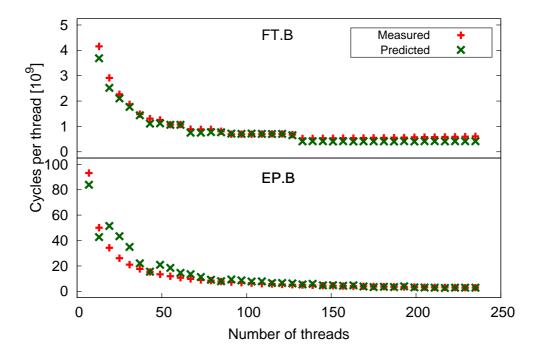

|   |                   | 3.3.2    | $WPI$ and $SPI_{core}$                                                                                                                       | 60  |

|   |                   | 3.3.3    | $SPI_{mem}$ Regression over Core Frequency $f$                                                                                               | 60  |

|   |                   | 3.3.4    | Execution Time and Energy                                                                                                                    | 62  |

|   |                   | 3.3.5    | Sources of Inaccuracy                                                                                                                        | 62  |

|   |                   | 3.3.6    | Accuracy of Related Work                                                                                                                     | 63  |

|   | 3.4               | Summ     | nary                                                                                                                                         | 63  |

| 4 | 1                 | levaia a | ef Inten no de Histonemenous Sustans                                                                                                         | 65  |

| 4 | <b>Ana</b><br>4.1 | Ũ        | of Inter-node Heterogeneous Systems<br>o-optimal Configurations                                                                              |     |

|   | 4.2               |          | et of Performance-to-Power Ratio                                                                                                             |     |

|   | 4.2               | 4.2.1    | Performance-to-Power Ratio (PPR)                                                                                                             |     |

|   |                   | 4.2.1    | Analytical Analysis of PPR on Sweet Region                                                                                                   |     |

|   | 4.3               |          | et of Power Substitution Ratio                                                                                                               |     |

|   | 1.0               | 4.3.1    | Power Substitution Ratio (PSR)                                                                                                               |     |

|   |                   | 4.3.2    | Impact of Heterogeneous Mixes on the Sweet Region                                                                                            |     |

|   |                   | 4.3.3    | Analytical Analysis of PSR on Sweet Region                                                                                                   |     |

|   | 4.4               |          | y Proportionality Analysis                                                                                                                   |     |

|   |                   | 4.4.1    | Brawny versus Wimpy Node                                                                                                                     |     |

|   |                   | 4.4.2    | Cluster-wide Energy Proportionality                                                                                                          |     |

|   |                   | 4.4.3    | Does Heterogeneity Scale the Energy Proportionality Wall? .                                                                                  |     |

|   | 4.5               | Summ     | nary                                                                                                                                         | 92  |

|   |                   |          |                                                                                                                                              |     |

| 5 |                   |          | to Intra-node Heterogeneity with VPU                                                                                                         | 95  |

|   | 5.1               |          | iew                                                                                                                                          |     |

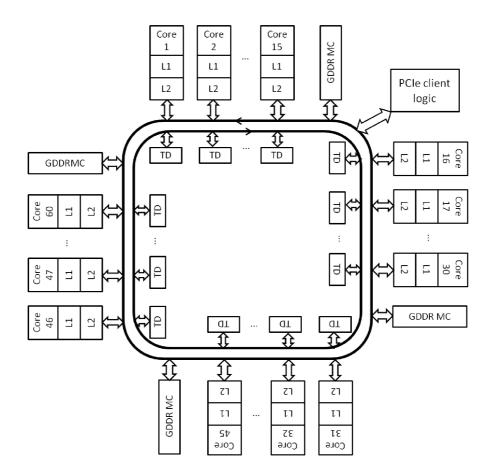

|   |                   | 5.1.1    | MIC Architecture                                                                                                                             |     |

|   | 5.2               |          | Performance Model                                                                                                                            |     |

|   |                   | 5.2.1    | Intra-core contention                                                                                                                        |     |

|   | <b>_</b> .        | 5.2.2    | Inter-core contention                                                                                                                        |     |

|   | 5.3               | Model    | l Parameterization and Validation                                                                                                            | 107 |

|    |                                                 | 5.3.4                                                                                                                                                       | Power Characterization                                                                                                                                                                                                                                                                 | 4                                                                                                                                              |

|----|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

|    | 5.4                                             | Analy                                                                                                                                                       | sis $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $11$                                                                                                                                                                                                                                  | 4                                                                                                                                              |

|    |                                                 | 5.4.1                                                                                                                                                       | Pareto-optimal Configurations                                                                                                                                                                                                                                                          | 5                                                                                                                                              |

|    |                                                 | 5.4.2                                                                                                                                                       | Performance-to-power Ratio                                                                                                                                                                                                                                                             | 7                                                                                                                                              |

|    | 5.5                                             | Summ                                                                                                                                                        | ary                                                                                                                                                                                                                                                                                    | 21                                                                                                                                             |

| 6  | $\mathbf{Ext}$                                  | ension                                                                                                                                                      | to Hybrid Programs with Communication 12                                                                                                                                                                                                                                               | 23                                                                                                                                             |

|    | 6.1                                             | Overv                                                                                                                                                       | iew                                                                                                                                                                                                                                                                                    | 24                                                                                                                                             |

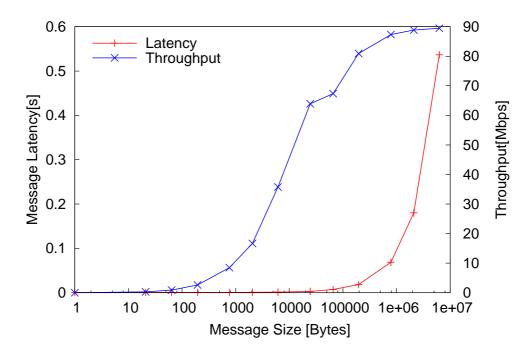

|    | 6.2                                             | Comm                                                                                                                                                        | nunication Model                                                                                                                                                                                                                                                                       | 28                                                                                                                                             |

|    |                                                 | 6.2.1                                                                                                                                                       | Model Inputs                                                                                                                                                                                                                                                                           | 28                                                                                                                                             |

|    |                                                 | 6.2.2                                                                                                                                                       | Time Model                                                                                                                                                                                                                                                                             | 80                                                                                                                                             |

|    |                                                 | 6.2.3                                                                                                                                                       | Energy Model                                                                                                                                                                                                                                                                           | 33                                                                                                                                             |

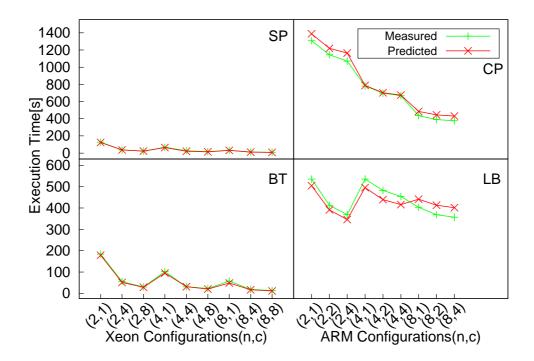

|    |                                                 | 6.2.4                                                                                                                                                       | Validation                                                                                                                                                                                                                                                                             |                                                                                                                                                |

|    | 6.3                                             | v                                                                                                                                                           | sis                                                                                                                                                                                                                                                                                    |                                                                                                                                                |

|    |                                                 | 6.3.1                                                                                                                                                       | Pareto-optimal Configurations                                                                                                                                                                                                                                                          |                                                                                                                                                |

|    |                                                 | 6.3.2                                                                                                                                                       | Useful Computation Ratio                                                                                                                                                                                                                                                               | 12                                                                                                                                             |

|    |                                                 | ~                                                                                                                                                           |                                                                                                                                                                                                                                                                                        |                                                                                                                                                |

|    | 6.4                                             | Summ                                                                                                                                                        | nary                                                                                                                                                                                                                                                                                   | 15                                                                                                                                             |

| 7  |                                                 | Summ<br>clusio                                                                                                                                              | ·                                                                                                                                                                                                                                                                                      | 15<br>19                                                                                                                                       |

| 7  |                                                 | clusio                                                                                                                                                      | ·                                                                                                                                                                                                                                                                                      | 19                                                                                                                                             |

| 7  | Cor                                             | clusio                                                                                                                                                      | n 14                                                                                                                                                                                                                                                                                   | <b>19</b><br>19                                                                                                                                |

| 7  | Cor                                             | <b>iclusio</b><br>Thesis                                                                                                                                    | <b>n 1</b> 4<br>s Summary                                                                                                                                                                                                                                                              | <b>19</b><br>19<br>50                                                                                                                          |

| 7  | Cor                                             | nclusio<br>Thesis<br>7.1.1                                                                                                                                  | n 14<br>s Summary                                                                                                                                                                                                                                                                      | <b>19</b><br>19<br>50<br>54                                                                                                                    |

| 7  | Cor                                             | Thesis<br>7.1.1<br>7.1.2<br>7.1.3                                                                                                                           | n 14<br>s Summary                                                                                                                                                                                                                                                                      | <b>19</b><br>19<br>50<br>54<br>57                                                                                                              |

| 7  | Cor<br>7.1                                      | Thesis<br>7.1.1<br>7.1.2<br>7.1.3<br>Future<br>7.2.1                                                                                                        | n       14         s Summary       14         Measurement-based Analytical Model       15         Insights from Energy-Time Performance Analysis       15         Limitations       15         e Directions       15         Dynamic Adaptation of Configurations at Run-time       15 | <b>19</b><br>49<br>50<br>54<br>57<br>57                                                                                                        |

| 7  | Cor<br>7.1                                      | Thesis<br>7.1.1<br>7.1.2<br>7.1.3<br>Future                                                                                                                 | n 14<br>s Summary                                                                                                                                                                                                                                                                      | <b>19</b><br>49<br>50<br>54<br>57<br>57                                                                                                        |

|    | Cor<br>7.1                                      | Thesis<br>7.1.1<br>7.1.2<br>7.1.3<br>Future<br>7.2.1<br>7.2.2                                                                                               | n       14         s Summary       14         Measurement-based Analytical Model       15         Insights from Energy-Time Performance Analysis       15         Limitations       15         e Directions       15         Dynamic Adaptation of Configurations at Run-time       15 | <b>19</b><br>50<br>54<br>57<br>57<br>57                                                                                                        |

| Re | Con<br>7.1<br>7.2                               | Thesis<br>7.1.1<br>7.1.2<br>7.1.3<br>Future<br>7.2.1<br>7.2.2<br>nces                                                                                       | n 14<br>s Summary                                                                                                                                                                                                                                                                      | <b>19</b><br>50<br>54<br>57<br>57<br>57                                                                                                        |

| Re | Con<br>7.1<br>7.2                               | Thesis<br>7.1.1<br>7.1.2<br>7.1.3<br>Future<br>7.2.1<br>7.2.2<br>nces                                                                                       | n 14<br>s Summary                                                                                                                                                                                                                                                                      | <ol> <li>49</li> <li>50</li> <li>54</li> <li>57</li> <li>57</li> <li>58</li> <li>51</li> <li>35</li> </ol>                                     |

| Re | Con<br>7.1<br>7.2                               | aclusion         Thesis         7.1.1         7.1.2         7.1.3         Future         7.2.1         7.2.2         ances         periment         Program | n 14<br>s Summary                                                                                                                                                                                                                                                                      | <ol> <li>49</li> <li>50</li> <li>54</li> <li>57</li> <li>57</li> <li>58</li> <li>51</li> <li>35</li> <li>35</li> </ol>                         |

| Re | Cor<br>7.1<br>7.2<br>efere<br>Exp<br>A.1        | Thesis<br>7.1.1<br>7.1.2<br>7.1.3<br>Future<br>7.2.1<br>7.2.2<br>nces<br>Progra<br>System                                                                   | n 14<br>S Summary                                                                                                                                                                                                                                                                      | <ol> <li>49</li> <li>50</li> <li>54</li> <li>57</li> <li>57</li> <li>58</li> <li>51</li> <li>35</li> <li>35</li> <li>37</li> </ol>             |

| Re | Con<br>7.1<br>7.2<br>efere<br>Exp<br>A.1<br>A.2 | Thesis<br>7.1.1<br>7.1.2<br>7.1.3<br>Future<br>7.2.1<br>7.2.2<br>nces<br>Progra<br>System<br>Softwa                                                         | n 14<br>s Summary                                                                                                                                                                                                                                                                      | <ol> <li>49</li> <li>50</li> <li>54</li> <li>57</li> <li>57</li> <li>58</li> <li>51</li> <li>35</li> <li>35</li> <li>37</li> <li>38</li> </ol> |

### **B** Model Parameters

| $\mathbf{C}$ | Sens | sitivity Analysis                                          | 195   |

|--------------|------|------------------------------------------------------------|-------|

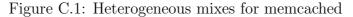

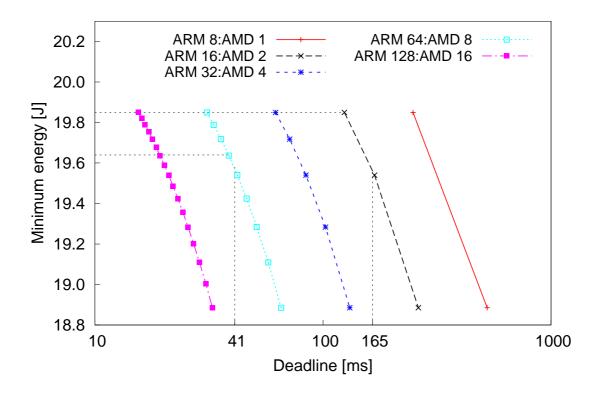

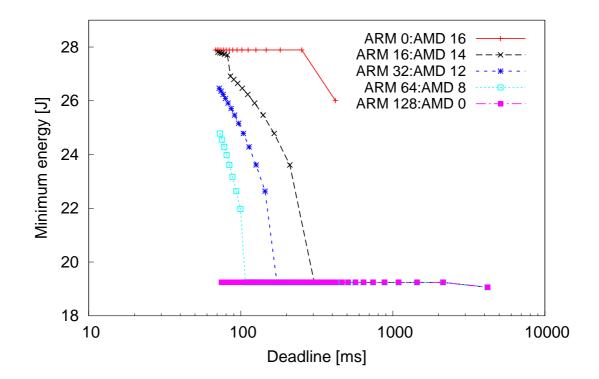

|              | C.1  | What is a Good Mix of High-performance to Low-power Nodes? | . 195 |

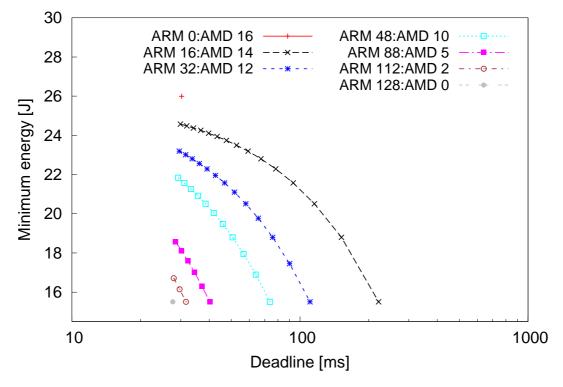

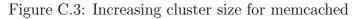

|              | C.2  | Are Larger Mixes of Heterogeneous Nodes Better?            | . 197 |

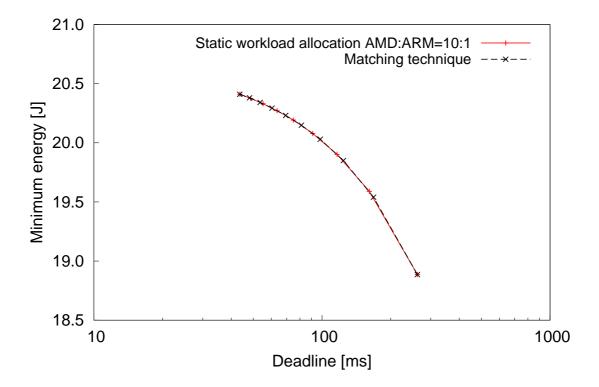

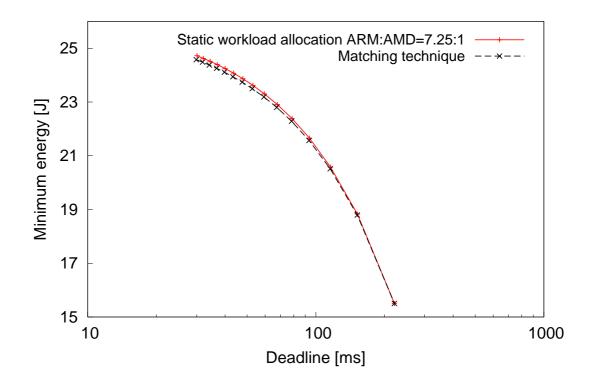

|              | C.3  | Does Static Workload Allocation Suffice?                   | . 199 |

|              | C.4  | Impact of Realistic Workloads on Heterogeneity             | . 202 |

|              | C.5  | Impact of Jobs Queueing Delay                              | . 207 |

# List of Figures

| A classification of heterogeneous computing systems                        | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

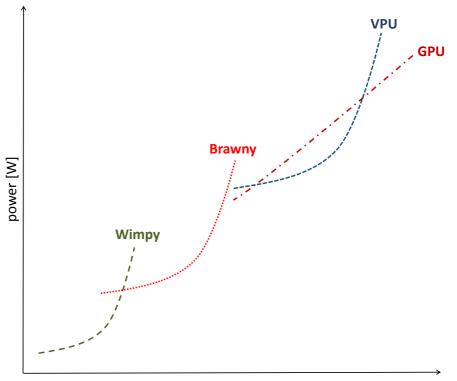

| Power-performance of processors                                            | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

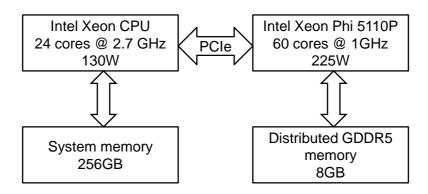

| Example system with inter-chip heterogeneity, Intel Xeon Phi 2             | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

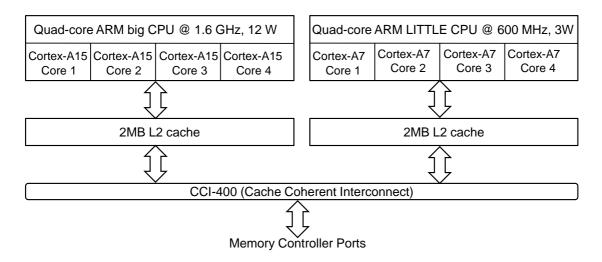

| Example system with intra-chip heterogeneity, ARM big.<br>LITTLE $$ . $$ 2 | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

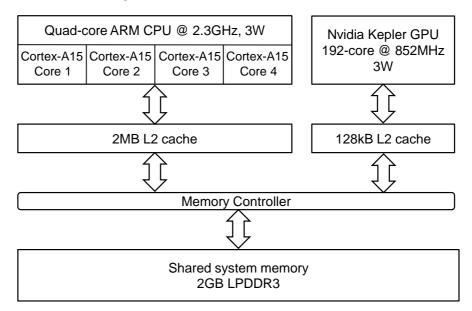

| Example system with intra-chip heterogeneity, Nvidia Jetson TK1 . $\ 2$    | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

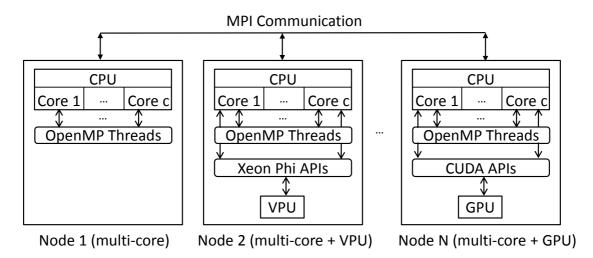

| Hybrid program with MPI, OpenMP, Xeon Phi<br>API and CUDA $\ .$ . 2        | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

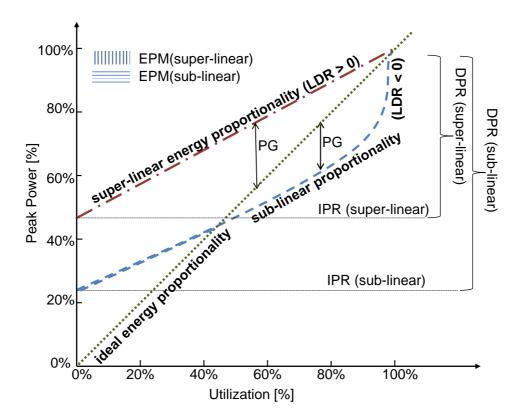

| Energy proportionality metric relationships                                | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

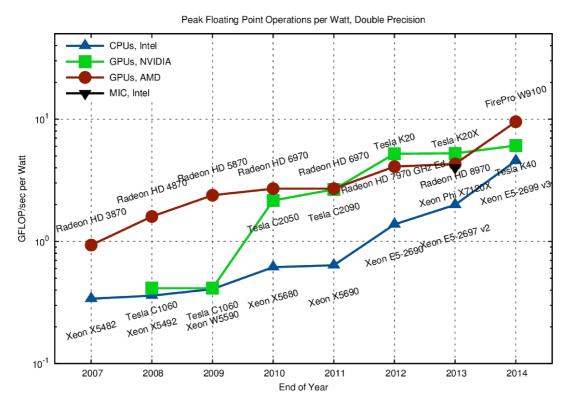

| Energy-performance of CPU, GPU and MIC [140]                               | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

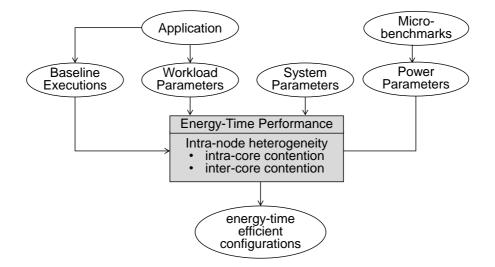

| Methodology for core model                                                 | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

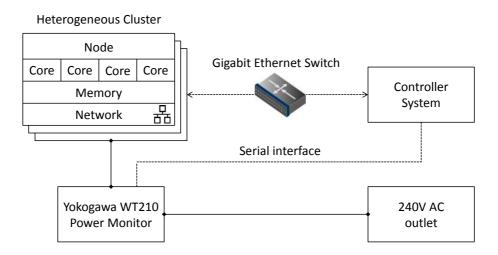

| Validation setup                                                           | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

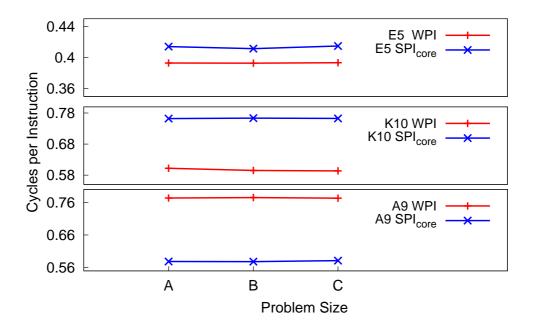

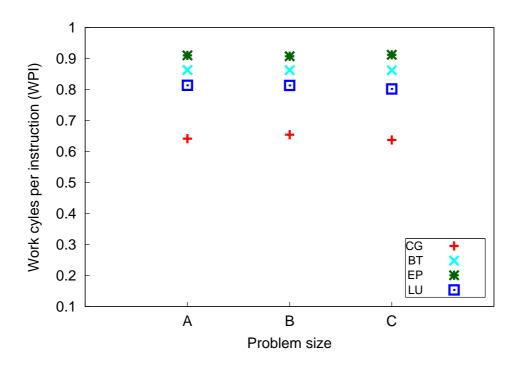

| $WPI$ and $SPI_{core}$ across problem size                                 | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

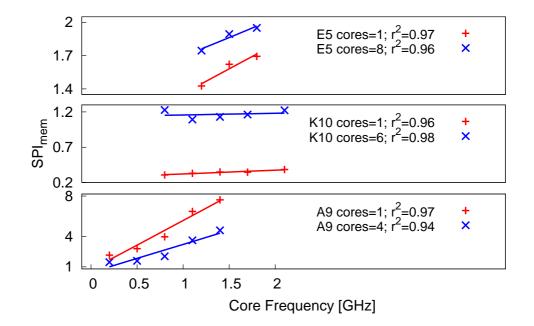

| Effect of frequency and number of cores on $SPI_{mem}$ 6                   | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

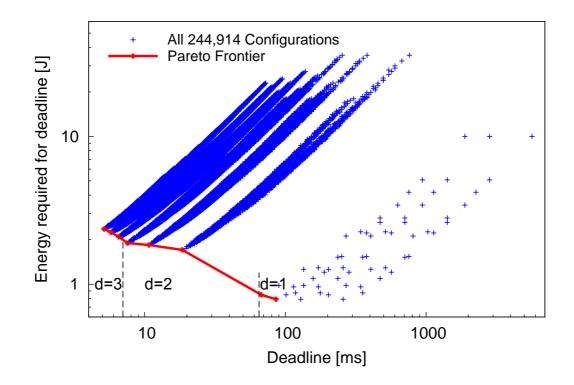

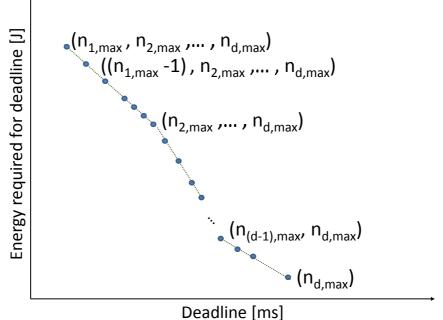

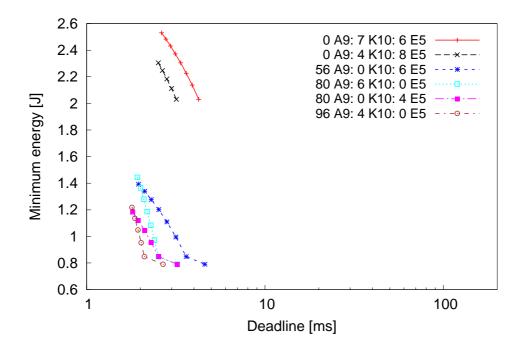

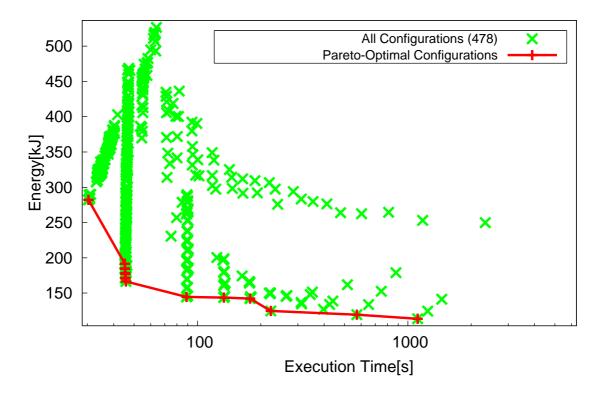

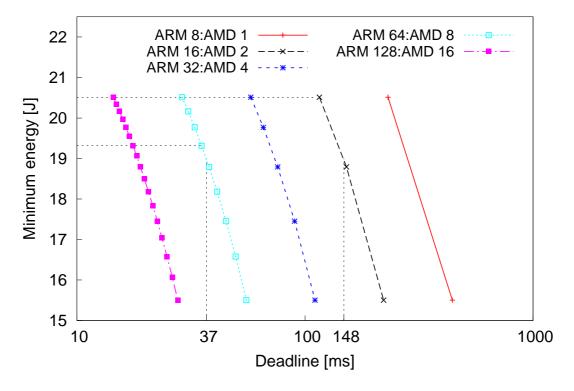

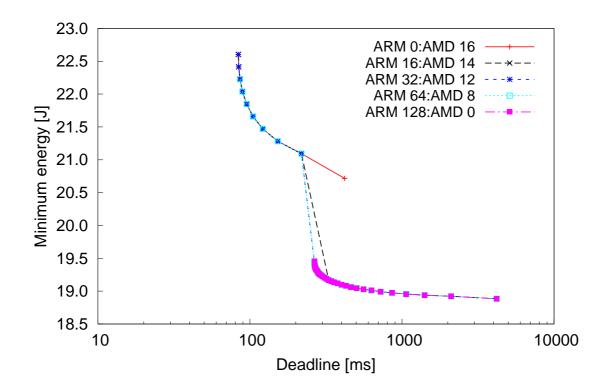

| Pareto frontier for EP with $d_{max} = 3$                                  | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

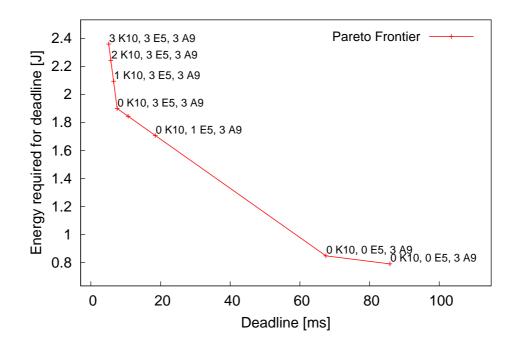

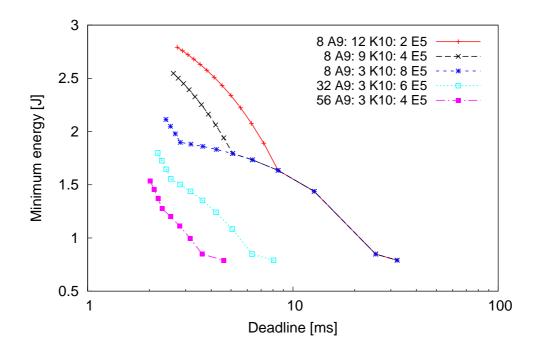

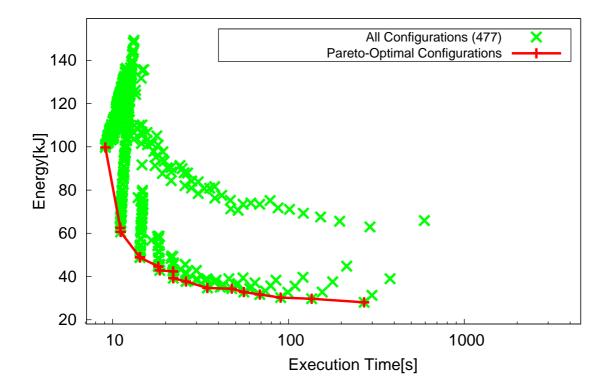

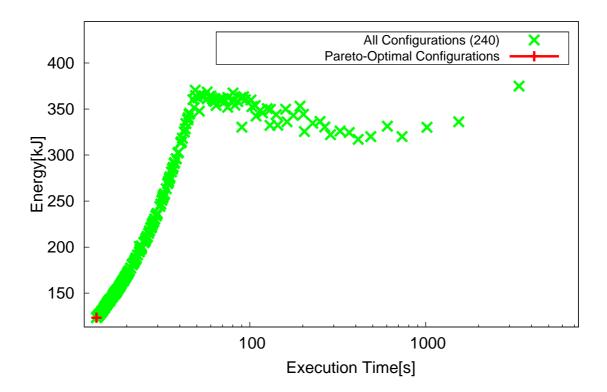

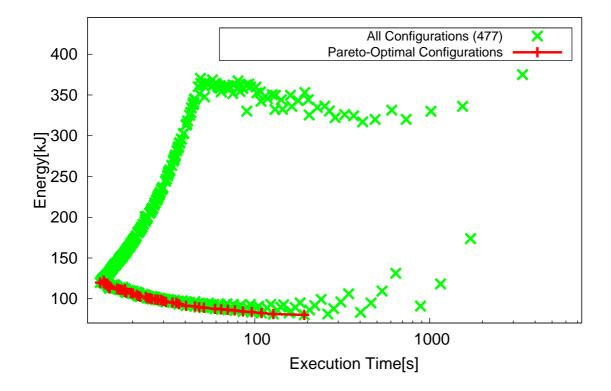

| Pareto frontier configurations for EP                                      | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

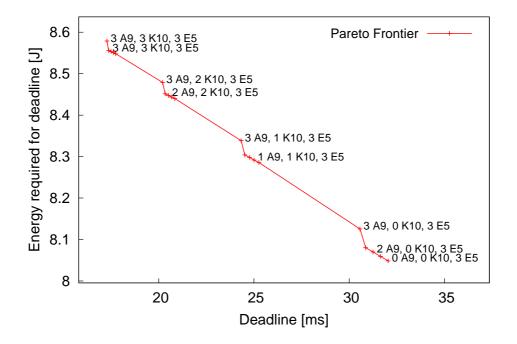

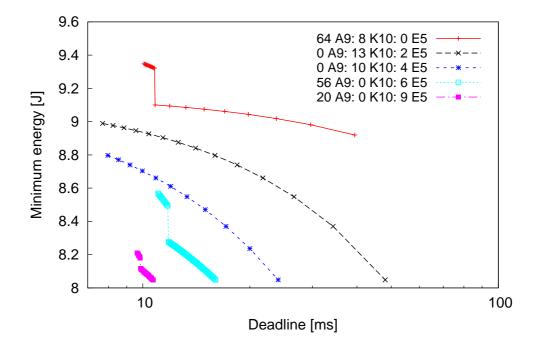

| Pareto frontier configurations for RSA-2048                                | 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Configurations on the sweet-spot region                                    | 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Pareto frontier for EP with $d = 2$                                        | 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

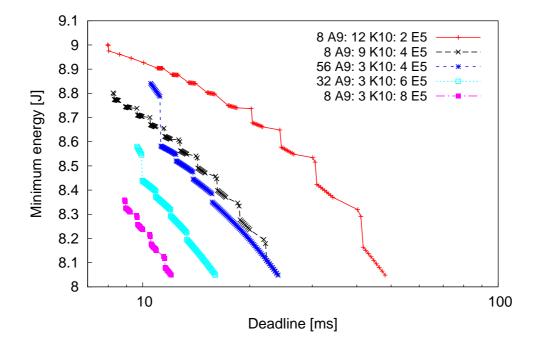

| Pareto frontier for EP with $d = 3$                                        | 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Pareto frontier for RSA-2048 with $d = 2$                                  | 76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Pareto frontier for RSA-2048 with $d = 3$                                  | 77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

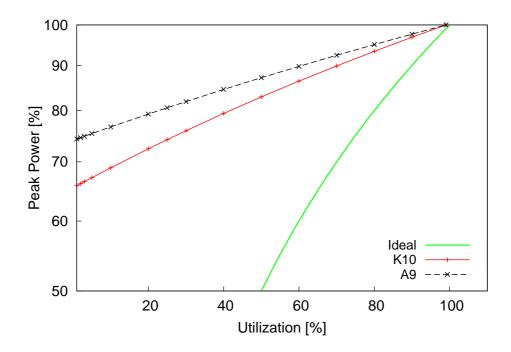

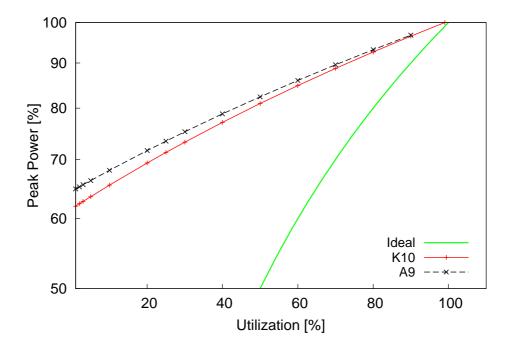

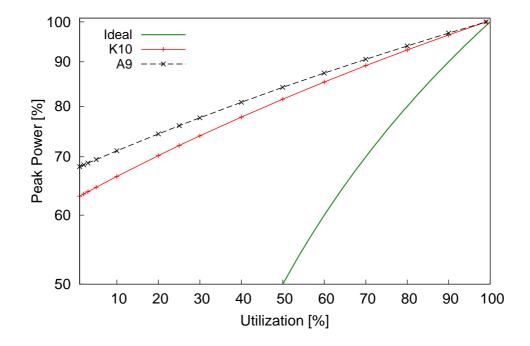

| Energy proportionality of EP                                               | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Energy proportionality of $x2648$                                          | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Energy proportionality of blackscholes                                     | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

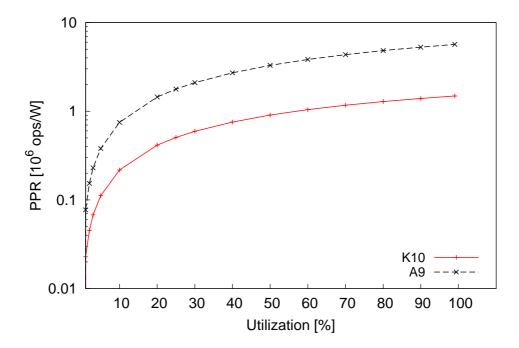

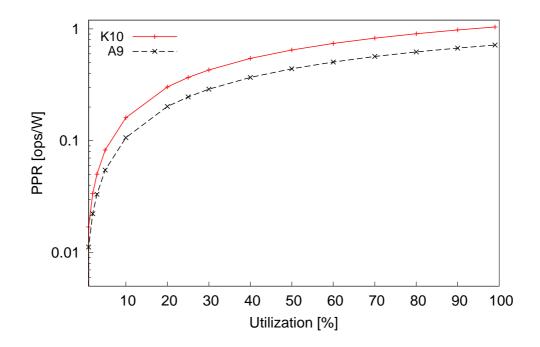

| PPR of EP                                                                  | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

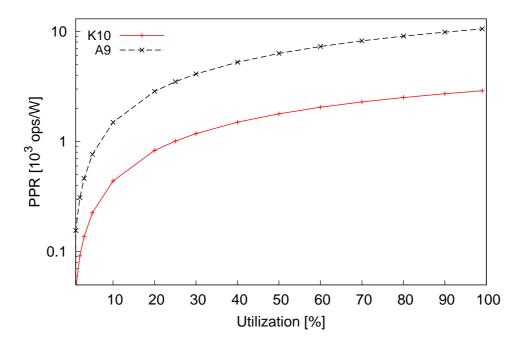

| PPR of x264                                                                | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| PPR of blackscholes                                                        | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                            | Power-performance of processors1Example system with inter-chip heterogeneity, Intel Xeon Phi2Example system with intra-chip heterogeneity, ARM big.LITTLE2Example system with intra-chip heterogeneity, Nvidia Jetson TK12Example system with MPI, OpenMP, Xeon Phi API and CUDA2Energy proportionality metric relationships3Energy-performance of CPU, GPU and MIC [140]3Methodology for core model4Validation setup6WPI and SPIcore across problem size6Effect of frequency and number of cores on SPImem6Pareto frontier for EP with $d_{max} = 3$ 6Pareto frontier configurations for RSA-20487Configurations on the sweet-spot region7Pareto frontier for EP with $d = 2$ 7Pareto frontier for RSA-2048 with $d = 3$ 7Pare |

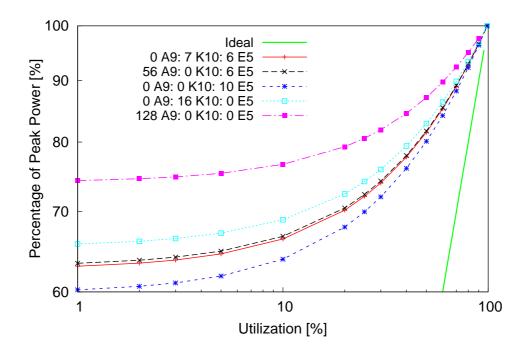

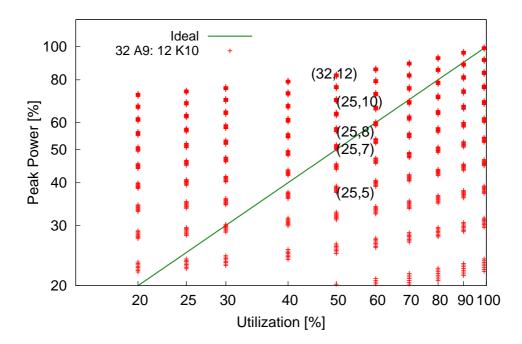

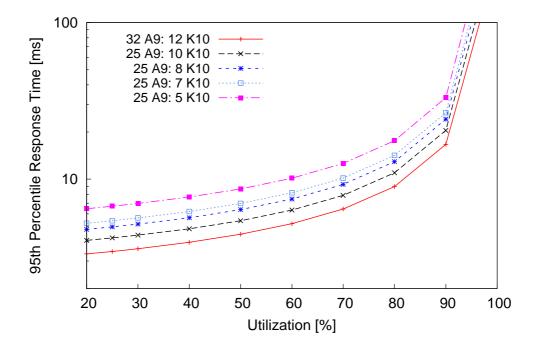

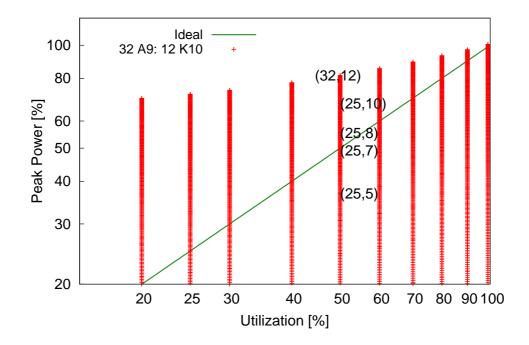

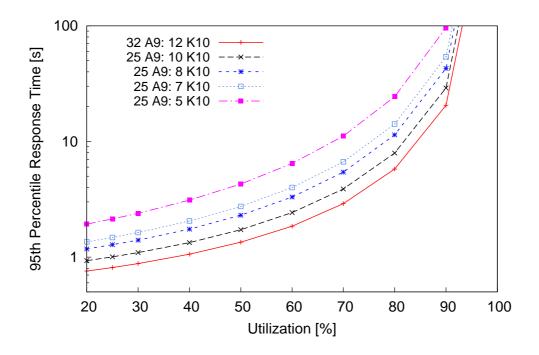

| 4.15                                                                                       | Cluster-wide energy proportionality $d = 1$ and $d = 2 \dots 87$                                                                                                                                                                                                                                                           |

|--------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.16                                                                                       | Cluster-wide energy proportionality $d = 3$                                                                                                                                                                                                                                                                                |

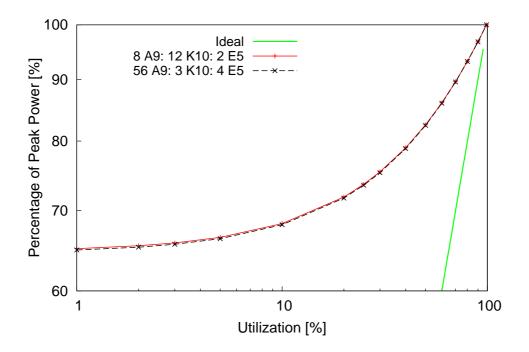

| 4.17                                                                                       | Energy proportionality of Pareto-optimal configurations for EP $90$                                                                                                                                                                                                                                                        |

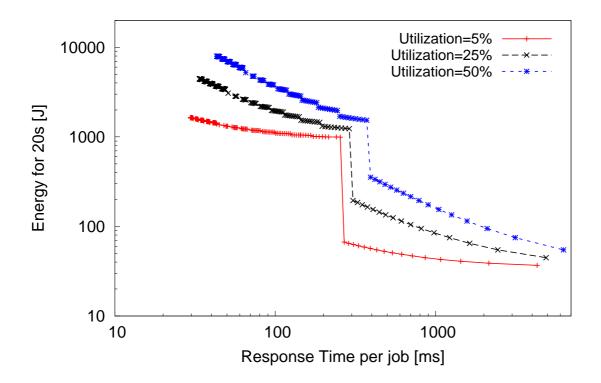

| 4.18                                                                                       | Response time of sub-linear heterogeneous mixes for EP 91                                                                                                                                                                                                                                                                  |

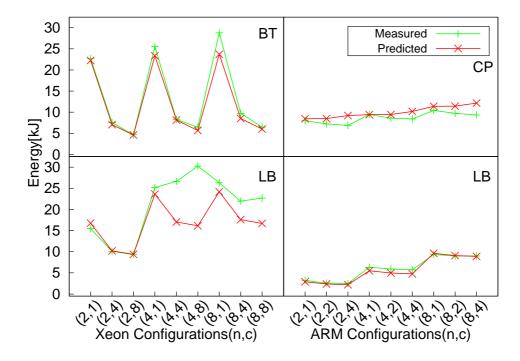

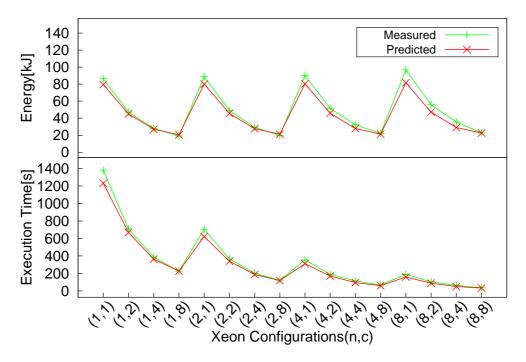

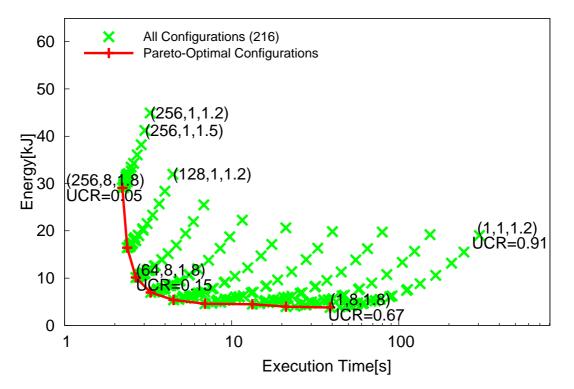

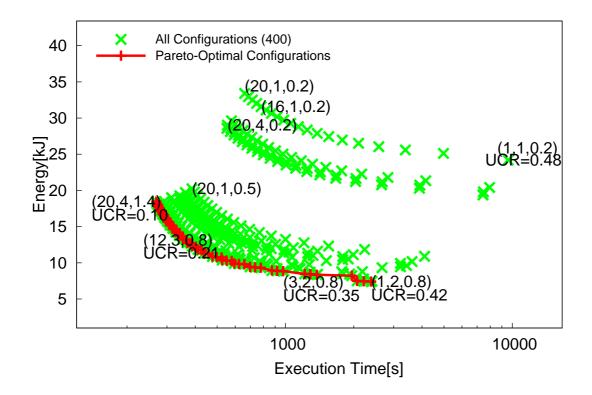

| 4.19                                                                                       | Energy proportionality of Pareto-optimal configurations for $\mathbf{x}264$ 91                                                                                                                                                                                                                                             |