# A TRANSCEIVER DESIGN FOR IMPLANTABLE MEDICAL DEVICES

LI CHONG (M.Eng.(Hons), KMUST)

## A THESIS SUBMITTED

FOR THE DEGREE OF MASTER OF ENGINEERING DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING NATIONAL UNIVERSITY OF SINGAPORE

2015

# DECLARATION

I hereby declare that the thesis is my original work and it has been written by me in its entirety. I have duly acknowledged all the sources of information which have been used in the thesis.

This thesis has also not been submitted for any degree in any university previously.

LI CHONG 20 October 2015

# Acknowledgements

I would like to take the opportunity to express my deepest gratitude to Asst. Prof. Yang Zhi who had led me to the academic research area and the field of biomedical microelectronics devices. His researches are so appealing and attract me into the fascinating electronic world of hardware. He enlightened me about the beauty of solid-state electric circuits and the implantable medical devices. He gave me the opportunity to start the study and research of the analog circuit design from a project which enable me to have both overall and part views of an implantable device design. He strengthened me on the will to pursuit of wisdom.

I would also like to express my deep gratitude to Dr. Xu Jian who had provided me with sufficient advices in analog integrated circuits (IC) design. Since the beginning his offering me the opportunity to involve in some particular design works which make myself familiar with the software and hardware environment for design, till the designing phase his guidance, all his help enable me to finish all my study so fast.

I would like to thanks my peer Anh Tuan Nguyen who had also given a lot of helps in my study and research of analog IC design. I would also like to thanks my peers Luo Yuxuan, Wu Tong, Wang Baitong, Zhao Wenfeng, Kuldeep Singh Rajput, Lim Sheng Tong, Cai Lei, Tam Wing Kin, Kafiul Islam, Mohammad Reza Keshtkaran, etc. for their technical helps. I am deeply indebted to my parents, my wife and my brother, as well as my teacher Prof. Zhou Yanling. For their eternal love, unwavering supports especially in this two years. Without them, I cannot accomplish my study and achieve everything I have for today.

# Contents

| Acknowledgements II                                        |

|------------------------------------------------------------|

| ContentsIV                                                 |

| Summary                                                    |

| List of Tables                                             |

| List of Figures IX                                         |

| List of AcronymsXI                                         |

| Chapter 1 Introduction                                     |

| 1.1 Introduction                                           |

| 1.2 Medical Implants                                       |

| 1.2.1 Wireless Medical Implantable Devices                 |

| 1.2.2 Wireless Telemetry                                   |

| 1.2.3 Requirements of Wireless Implantable Medical Devices |

| 1.2.4 Power Link of Implantable Devices                    |

| 1.2.5 Data Link of Implantable Devices                     |

| 1.2.6 Architecture of the Proposed Medical Device          |

| Chapter 2 Power Amplifier                                  |

| 2.1 Power Amplifier                                        |

| 2.1.1 Introduction                                         |

| 2.1.2 Principle of Class E Power Amplifiers                |

| 2.1.3 Design Procedure                                     |

| 2.1.4 The Proposed Class E Amplifier                       |

| Chapter 3 Load Shift Keying                                |

| 3.1 Introduction                                           |

| 3.2 Principle of LSK [58]                                  |

| 3.3 The Proposed LSK Demodulator                           |

| Chapter 4 Envelope Detector                                |

| 4.1 Introduction                                           |

| 4.2 Principle of Envelope Detector                         |

| 4.2.1 Diode Capacitor Envelope Detector                    |

| 4.2.2 Detector Using Op-amp                                |

| 4.2.3 Envelope Detector with MOS Transistor                |

| 4.2.4 Positive Peak Detector Using Current Mirror          |

| 4.3 The Proposed Envelope Detector        |

|-------------------------------------------|

| Chapter 5 Filters                         |

| 5.1 Introduction                          |

| 5.2 Principles of Filters                 |

| 5.2.1 Passive Filters                     |

| 5.2.2 Active Filters                      |

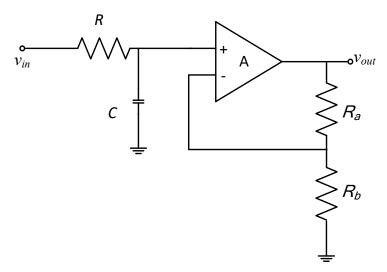

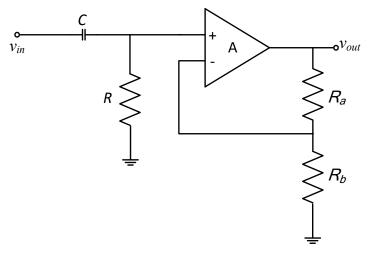

| 5.3 The Proposed Band Pass Filter         |

| Chapter 6 ADC                             |

| 6.1 Introduction                          |

| 6.2 Principle of ADCs                     |

| 6.2.1 Principle of SAR ADC                |

| 6.2.2 Charge Redistribution SAR ADC       |

| 6.3 The Proposed SAR ADC                  |

| Chapter 7 Measurement and Result          |

| 7.1 Introduction                          |

| 7.2 Class E amplifier measurement         |

| 7.3 Envelope Detector and LSK Measurement |

| Chapter 8 Conclusion                      |

| Bibliography                              |

# **Summary**

In recent years, implantable devices and wearable devices are extensively applied in clinic to assist patients either to substitute the missing function of a damaged organ or to alleviate and remedy the disease progression of a malfunctioning part in the body. It has become one of the hottest topic in the intersection of electronic and medical. A number of products and applications such as brain pacemakers, retinal implants, wearable blood pressure monitors and blood glucose detectors have been released into healthcare markets. They are often used with operational software applets installed on smart phones/ tablets in order to monitor or assist the therapy of epilepsy, amblyopia, and even heart diseases. One of the key challenges of developing these devices is to reduce both the device size and power consumption while improving data rate and power efficiency. These two requirements are difficult to be simultaneously achieved because increasing data transfer rate normally increases the power consumption and enlarges the device size.

In this research, we propose a transceiver design for an implantable medical device that utilizes inductive coupling coils for data and power transmission. A Class E power amplifier was employed to amplify and transfer power from the transceiver side (external device) to the receiver side (internal implant). And then with a Load Shift Keying (LSK) demodulator --- a particular scheme of Amplitude Shift Keying (ASK) which has a higher data recovery efficiency compared to Frequency Shift Keying (FSK) structure for digital signal transmission --- the biological data captured by the implant were transmitted back to the transceiver. The LSK demodulation technique allowed power and data to be transferred simultaneously through one single inductive link. It could work under a variety

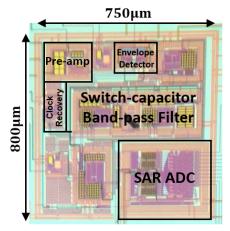

of modulation indexes and different coding/decoding protocols. Furthermore, it enables us to reduce both the power consumption and the device size of the transceiver. The circuits were fabricated in 180nm CMOS process technology and a prototype was designed to demonstrate the performance of the proposed demodulator. Measurement results indicated that the circuit could support the power carrier signal of different frequencies and data rates. The core area of the chip was 750µm x 800µm and the achievable minimum modulation index of the prototype was 5%, whereas the supported data rate was 1 Mbps. With a 1.65V power supply the total current consumption was 3.6 mA.

# List of Tables

| Table 1.1 Power and data transmit status from recent research reports | . 9 |

|-----------------------------------------------------------------------|-----|

| Table 6.1 Simulation result of the proposed SAR ADC.                  | 66  |

| Table 7.1 Designed transceiver performance                            | 74  |

# **List of Figures**

| Figure 1.1 Retinal implant with wireless interface [10]                                           | 5    |

|---------------------------------------------------------------------------------------------------|------|

| Figure 1.2 Middle ear implantable device powered via inductive couple coils [15]                  | 5    |

| Figure 1.3 Architecture of the proposed implantable device and external device                    |      |

| Figure 2.1 Structure of Class E power amplifier                                                   | . 19 |

| Figure 2.2 Class E amplifier circuit                                                              |      |

| Figure 2.3 The coupling coils of the proposed Class E power amplifier                             | 23   |

| Figure 2.4 Proposed Class E amplifier prototype                                                   | 23   |

| Figure 3.1 Circuit for analysis of LSK principle                                                  |      |

| Figure 3.2 LSK demodulator circuit schematic                                                      |      |

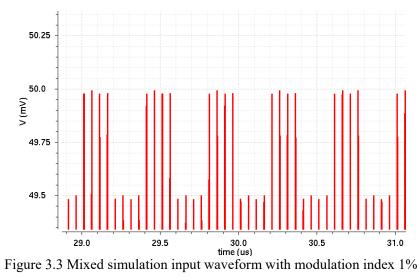

| Figure 3.3 Mixed simulation input waveform with modulation index 1%                               |      |

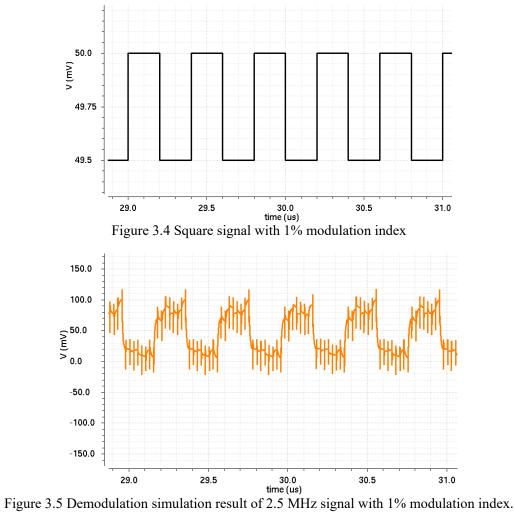

| Figure 3.4 Square signal with 1% modulation index                                                 |      |

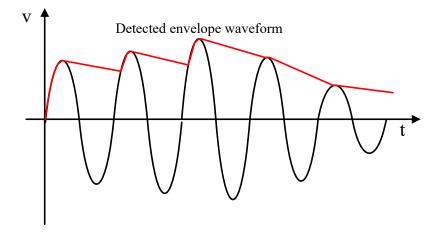

| Figure 3.5 Demodulation simulation result of 2.5 MHz signal with 1% modulation index              |      |

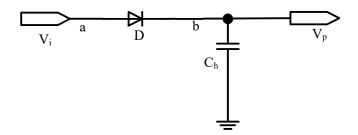

| Figure 4.1 Ideal envelop detector output waveform                                                 |      |

| Figure 4.2 Diode capacitor envelop detector                                                       |      |

| Figure 4.3 Output waveform of diode capacitor envelop detector                                    |      |

| Figure 4.4 Envelop detector output failed to detect a quick and distinct input voltage drop       |      |

| Figure 4.5 Envelop detector with op-amp                                                           |      |

| Figure 4.6 Positive envelop detector with MOS transistor and buffer                               |      |

| Figure 4.7 Positive envelop detector with current mirror                                          |      |

| Figure 4.8 Multi-phase envelop detector with current mirror                                       |      |

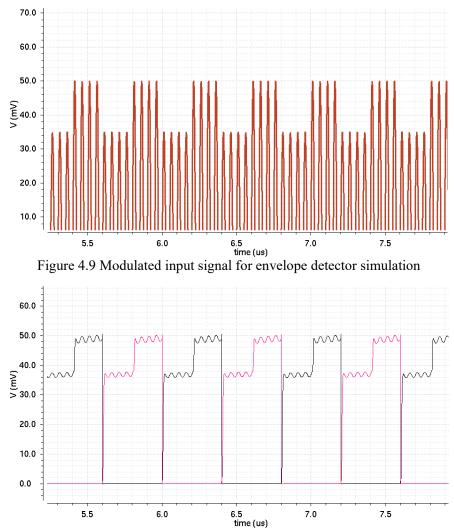

| Figure 4.9 Modulated input signal for envelop detector simulation                                 |      |

| Figure 4.10 Simulate result regarding the input signal of Figure 4.9, two different color plots a |      |

| the two phase of outputs, which are $V_1$ and $V_p$ in Figure 4.8                                 |      |

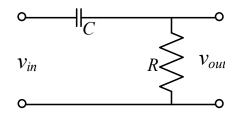

| Figure 5.1 RC low-pass filter                                                                     |      |

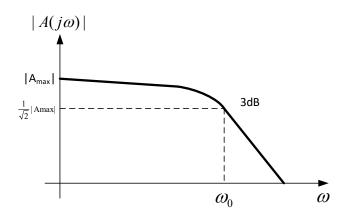

| Figure 5.2 Magnitude versus frequency of RC low-pass filter                                       | 48   |

| Figure 5.3 RC high-pass filter                                                                    | 48   |

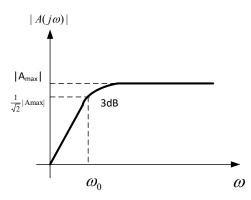

| Figure 5.4 Magnitude versus frequency of RC high-pass filter                                      | 49   |

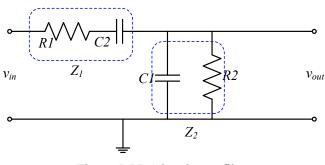

| Figure 5.5 RC band-pass filter                                                                    |      |

| Figure 5.6 Magnitude versus frequency of RC band-pass filter                                      |      |

| Figure 5.7 Low-pass filter with an operational ampifier                                           |      |

| Figure 5.8 High-pass filter with an operational amplifier                                         |      |

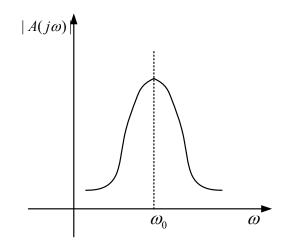

| Figure 5.9 The proposed switched capacitor band-pass filter circuit                               |      |

| Figure 6.1 Structure of conventional SAR ADC [78]                                                 |      |

| Figure 6.2 Operation flow of SAR ADC                                                              |      |

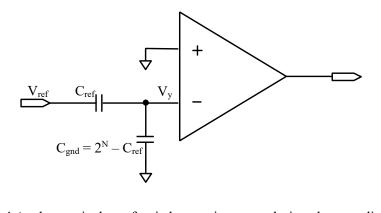

| Figure 6.3 Switch-capacitor array scheme in CR SAR ADC [79]                                       | 60   |

| Figure 6.4 Analog equivalent of switch-capacitor array during charge redistribution               |      |

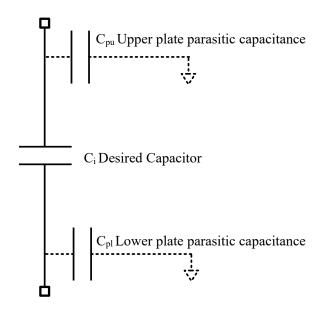

| Figure 6.5 The parasitic capacitance of integrated capacitor                                      | 63   |

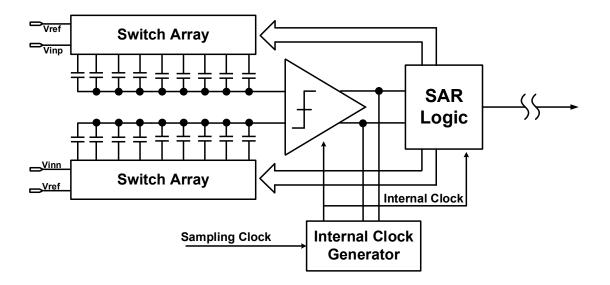

| Figure 6.6 SAR ADC architecture in this research                                                  | 64   |

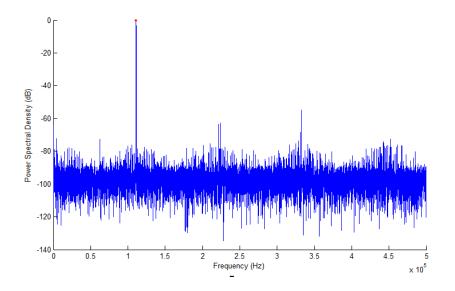

| Figure 6.7 Measured 32,658 point FFT spectrum                                                     |      |

| Figure 7.1 Prototype of the Class E power amplifier                                               | 67   |

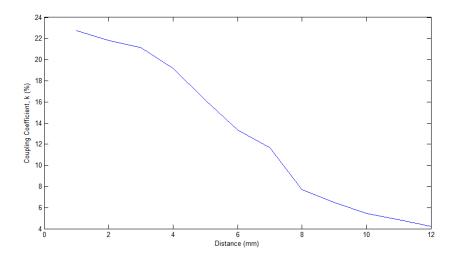

| Figure 7.2 Coupling coefficient versus coils distance                                             | 68   |

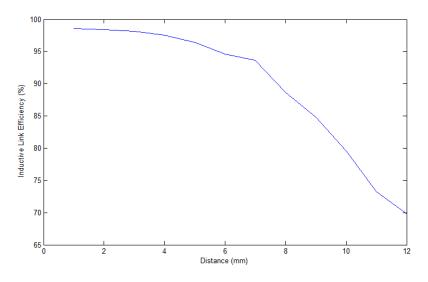

| Figure 7.3 Inductive Link Efficiency versus coils distance                                        |      |

| Figure 7.4 Prototype chip micrograph                                                              |      |

| Figure 7.5 Prototype PCB board of the proposed transceiver                                        | 70   |

| Figure 7.6 Extracted envelope of square wave modulated input signal (carrier frequency            |      |

|                                                                                                   |      |

| =10MHz, data rate =20 KHz, modulation index = 50%                                      | 71 |

|----------------------------------------------------------------------------------------|----|

| Figure 7.7 Demodulated output of a 1 MHz signal with carrier frequency of 10 MHz in 6% |    |

| modulation index                                                                       | 72 |

| Figure 7.8 (a) Zoom-in of the output in Figure 7.5, (b) SAR ADC output                 | 72 |

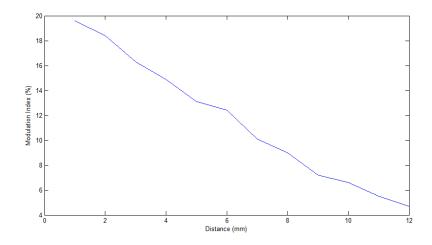

| Figure 7.9 Minimum modulation index versus inductive link distance                     | 73 |

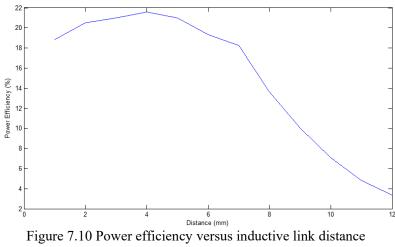

| Figure 7.10 Power efficiency versus inductive link distance                            | 74 |

# List of Acronyms

| AC         | Alternating Current                                           |  |  |  |  |

|------------|---------------------------------------------------------------|--|--|--|--|

| ADC        | Analog to Digital converter                                   |  |  |  |  |

| ASK        | Amplitude-Shift Keying                                        |  |  |  |  |

| BMJ        | British Medical Journal                                       |  |  |  |  |

| CMOS       | Complementary Metal-Oxide Semiconductor                       |  |  |  |  |

| CR SAR ADC | Charge Redistribution Successive Approximation Register ADC   |  |  |  |  |

| DAC        | Digital to Analog Converter                                   |  |  |  |  |

| DC         | Direct Current                                                |  |  |  |  |

| DNL        | Frequency Shift Keying                                        |  |  |  |  |

| ECG        | Electrocardiogram                                             |  |  |  |  |

| EEG        | Electroencephalogram                                          |  |  |  |  |

| EMG        | Electromyography                                              |  |  |  |  |

| FCC        | Federal Communication Committee                               |  |  |  |  |

| FDA        | Food and Drug Administration                                  |  |  |  |  |

| FPGA       | Field-Programmable Gate Array                                 |  |  |  |  |

| FSK        | Frequency Shift Keying                                        |  |  |  |  |

| GBW        | Gain-bandwidth                                                |  |  |  |  |

| INL        | Integral Nonlinearity                                         |  |  |  |  |

| IC         | Integrated Circuits                                           |  |  |  |  |

| IT         | Information Technology                                        |  |  |  |  |

| LSB        | Lest Significant Bit                                          |  |  |  |  |

| LSK        | Load Shift Keying                                             |  |  |  |  |

| Mbps       | Megabits per second                                           |  |  |  |  |

| MICS       | Medical Implant Communication Services                        |  |  |  |  |

| MOS        | Metal Oxide Semiconductor                                     |  |  |  |  |

| MS         | Mega Samples                                                  |  |  |  |  |

| MSB        | Most Significant Bit                                          |  |  |  |  |

| NASA       | National Aeronautics and Space Administration                 |  |  |  |  |

| Op amp     | Operational Amplifier                                         |  |  |  |  |

| OTA        | Operational Transconductance Amplifier                        |  |  |  |  |

| PCB        | Printed Circuit Board                                         |  |  |  |  |

| PSK        | Phase-Shift Keying                                            |  |  |  |  |

| RC         | Resistor-Capacitor                                            |  |  |  |  |

| RF         | Radio Frequency                                               |  |  |  |  |

| SAR        | Successive Approximation Register                             |  |  |  |  |

| SAR ADC    | Successive Approximation Register Analog to Digital Converter |  |  |  |  |

| SFDR       | Spurious-Free Dynamic Range                                   |  |  |  |  |

| SNDR       | Signal-to-noise + Distortion Ratio                            |  |  |  |  |

| SNR        | Signal-to-Noise Ratio                                         |  |  |  |  |

| USA        | United States of America                                      |  |  |  |  |

| USD        | US Dollar                                                     |  |  |  |  |

|            |                                                               |  |  |  |  |

# **Chapter 1 Introduction**

## **1.1 Introduction**

With the development of science and engineering, IT (information technology) is changing the modern lifestyle. In particular, wireless communication technology has revolutionized the way people communicate and acquire knowledge. It is ubiquitously employed in personal mobile products, and it is also gradually applied in healthcare appliances and services. Implementations of wireless technologies in wearable and portable healthcare devices have become some of the hottest topics in the intersection of electronic and medical. A vast array of products and applications such as wireless step monitors, wearable blood oxygen saturation monitors and heart rate detectors, etc., which often accompanied by some applets on smart phones/tablets have been employed to diagnose the epilepsy, muscle problems, heart diseases, etc. With these healthcare devices, both patients and hospitals may significantly reduce their expenses, for example, the United States saved around 1.9 trillion USD every year which might otherwise be spent on chronic diseases and their management in the past half-decade [1]. This huge potential of resource saving is attracting more and more researchers to work on this area. Among all the applications in this area, implantable medical device is one of the most promising outcome. Implantable medical device is normally implanted and operated within human body in order to diagnose diseases or process treatments, and it can be more focused on the trauma of a patient.

In the past half century, one of the most widely used implantable medical devices is microelectronic biosensor. It has a large amount of applications such as measurement devices on heart-rate, ECG, EEG, temperature, oxygen saturation of blood and neurosignal [2], etc.; also, some therapy devices, for example, with a bi-directional telemetry developed by NASA [3], Siemens-Pacesetter Inc., Sylmar, California implemented a Synchrony pacemaker and obtained approval from Food and Drug Administration (FDA) for general marketing in August 1989. Around a decade later, a deep-brain stimulator [4] was developed to send electrical impulses to specific brain nuclei for the treatment of movement and affective disorders. Now, with the advancements of science and technology, clinical markets require the implantable medical devices to have higher efficiencies and smaller form factors. Two things, therefore, become critical under such a demand: one is to achieve a high speed wireless data transmission channel between implants (in-body devices) and transceivers (off-body devices) with a high accuracy; the other one is to create a high efficiency wireless power recharging channel between implants and transceivers.

In this thesis, we propose a transceiver design of an implantable medical device utilizing inductive coupling coils for power and data transmission. A Class E power amplifier is employed to amplify and transfer power from the transceiver to the internal implanted device. And then by designing a Load Shift Keying (LSK) demodulator --- a special scheme of Amplitude Shift Keying (ASK) which has a higher data recovery efficiency compared to Frequency Shift Keying (FSK) structure for digital signal transmission --- the biology data captured by the implant are transmitted back to the off-body transceiver (external device). The LSK demodulation technique allows power and data transmission through one single inductive link simultaneously. It can work under a variety of modulation indexes and different coding/decoding protocols. Therefore, it can achieve a high data rate

and a high power transfer efficiency. Furthermore, it is also able to scale down the whole microelectronic system in terms of power consumption and volume.

## **1.2 Medical Implants**

A medical implant is a man-made device implanted inside the human body. It is different from a transplant, which is an organ or tissue of natural origin [5]. A medical implant is implanted inside a human body to replace a missing biological structure or rectify a deforming structure of the body and eventually to re-implement the lost functionalities or to compensate for the abnormalities. Implants are not only passive biomedical materials such as silicone or apatite, they can also be active devices that contain electronic circuits so that to help people actively fulfil some particular functionalities. And these active devices are normally called implantable devices. One appealing technique for implantable devices is integrated solid-state circuit because of its higher integration density which enables its physical size to be smaller and its power consumption to be lower. Coupled with modern biomaterials, more and more implantable devices are developed with solidstate circuits integrated on them.

#### **1.2.1 Wireless Medical Implantable Devices**

In 1889, John Alexander MacWilliam reported his experiment about using electrical impulse to evoke a heart of asystole so that to achieve a rhythm of 60-70 beats per minute in the British Medical Journal (BMJ) [6]. Since then, a lot of researchers worked on pacemakers, which is a kind of device that uses electrical stimulation to drive heart beating. A pacemaker is primarily designed to aid a heart to maintain in an adequate beating rate

for a patient whose natural heart rate is not fast enough or there is disease in the heart's natural electrical conduction system [7]. In 1958, the first implantable artificial cardiac pacemaker was successfully implanted into Arne Larsson who is the world's first implantable pacemaker patient through thoracotomy at the Karolinska Institute in Solna, Sweden [8]. Recently, with wireless technique, modern pacemakers can inter-transfer data with the off-body device, and also be recharged or powered wirelessly.

Figure 1.1 and Figure 1.2 show us a couple of implant examples that have been clinically used. Both of them have been commercially launched in the healthcare market. The retinal implant as shown in Figure 1.1 was approved by the FDA in 2013, which was designed to enhance vision in patients who have been progressively blinded by the condition retinitis pigmentosa [9]. A miniature video camera is mounted on a patient's glasses to capture images, then the images are converted into electrical pulses and transmitted into the electrode array implanted on the retina of the patient through wireless channels. The electrode array will then stimulate the healthy cells on the retina and eventually create visual patterns in the brain [10]. Figure 1.2 shows a middle ear implantable device which has been approved by both European CE-mark in 1998 and FDA in 2000 [11] [12] [13]. Similar to the retinal implant, a microphone and an audio processor are worn by a patient on his or her ear to capture sounds, and then the sounds are converted into electrical signals and transmitted to a device implanted in the middle ear of the patient through wireless channels. The implanted device will transfer "the sounds" to the inner ear where auditory neurons will be activated to generate the sense of hearing [14]. Both of these two implantable devices are capable of being wirelessly recharged and transferring data.

Figure 1.1 Retinal implant with wireless interface [10]

Figure 1.2 Middle ear implantable device powered via inductive couple coils [15]

It is expected that more and more sophisticated implantable devices to be developed and launched in the healthcare market. These devices may need more power supply and wider bandwidth communication channel; meanwhile, to be integrated within a tiny package and should be easily implanted and maintained inside the human body. The requirements of wireless recharging and data transfer are therefore becoming more critical.

#### **1.2.2 Wireless Telemetry**

Telemetry generally means a device or the technique that fulfills automatic measurement and data transmission from remote locations or inaccessible sources through wire, radio or other methods, etc. [16]. The telemetry instrumentations that are employed in implantable medical devices are called biomedical telemetries or biotelemetries. With biomedical telemetries, the off-body devices of implantable medical devices can transmit data and power to the implanted internal devices. This transmission of data can be unidirectional or bidirectional. Unidirectional biotelemetries can be divided into two types: one is to transmit the biological data from the implanted device to the external body device where the data will be processed and monitored, such as electrocardiograph (ECG), neural signal or blood oxygen saturation; the other is to transmit commanding data or manipulating data from the external body devices to the implanted device so that to configure the internal device or control the internal device, for example, to stimulate the body tissue in a desired pattern [17] [18]. Normally, the biotelemetry which is used to transmit data is called data telemetry, whereas, the one which is used to transmit power is called power telemetry.

Telemetry has become a research topic for more than a century. How to wirelessly transmit power and data in a high efficiency is still challenging researchers. Especially, some applications (e.g. implants) even pose additional constraints on form factors and this increases the difficulty of research and development. At the same time, technology on biosensors are also becoming more advanced, which result in that higher and higher communication rate to be achieved between the external body device and the internal implanted device. All these requirements bring about higher difficulties in designing both the power link and the data link. In the next section we will discuss some general requirements regarding the implantable medical devices.

#### **1.2.3 Requirements of Wireless Implantable Medical Devices**

Surgeries and some particular diseases require that the implantable medical devices to be as small as possible. For example, retinal implants and some cochlear implants are expected to be less than one centimeter in size. Some particular devices that are designed to process disease cells or to flow through the human circulatory system should be even smaller. If a medical device is similar to a blood cell in size (in couple of micro-meters), blood vessels can take the medical device to almost everywhere of a human body to cure diseases. Therefore, in modern micro-electronics research, it is expected to scale down the implantable device in physical size by a few orders of magnitudes.

A pivotal problem of designing such a tiny wireless implantable electronic device is to ensure enough power supply while the device is tiny. As we know, the power sources normally provide less power supply when its size is reduced. Another problem is that the micro-electronic devices are required to communicate wirelessly with external devices in order to transmit and receive biosignals and commands. Similar to the power source, antennas or inductive coils also perform worse when their physical sizes are diminished. Moreover, when a micro-electronic device is implanted inside a human body, the human tissue surrounding the device will reduce the inductance or radiation of the inductive coils or antennas. Hence, signal penetration through human tissue becomes the third problem in designing an implantable electronic device, which dictates that the device have to work in a proper frequency and with enough power density. Therefore, there is a trade-off in designing implantable devices between size and power/data transmission.

## **1.2.4 Power Link of Implantable Devices**

Since implantable micro-electronic devices are designed for specific diseases, the requirements on power also vary from application to application. Normally, devices with a higher data communication rate such as multi-channel neural recorders require relatively higher power density to support the wireless data link. Some other implantable devices, for instance, the retinal implants or the cochlear implants may consume a very large amounts of current in order to stimulate the target nerves, and therefore they consume even more power.

Table 1.1 lists the range of power consumptions of different implantable devices regarding the range of data rates in the former published research reports. The contents in this table are adapted from [19]. Even though different applications of implantable devices require different amounts of power, a trend can still be observed from the table. In Table 1.1, we can find that devices with higher data communication rates usually consume more power. It also can be seen in Table 1.1 that most of the devices or systems consume about 1 mW, and there are only three devices that consume less than 10<sup>-1</sup> mW. Also most of the devices are in one centimeter size scale. And for a smaller device, its power consumption also tends to be lower.

|                                     | Data Rate (Mbps)                       |                                                                           |                          |               |  |

|-------------------------------------|----------------------------------------|---------------------------------------------------------------------------|--------------------------|---------------|--|

| Power (mW)                          | $10^{-3} - 10^{-2}$                    | $10^{-2} - 10^{0}$                                                        | $10^{0} - 10^{2}$        | $10^2 - 10^3$ |  |

| $10^2 - 10^3$                       |                                        |                                                                           | Emira 04<br>Khorram 05   | Aytur 06      |  |

| $10^1 - 10^2$                       |                                        | Choi 03 Dong 05<br>Parramon 06 Ryckaert 06<br>Cojocaru 06<br>Verma 05     |                          |               |  |

| 10 <sup>0</sup> - 10 <sup>1</sup>   | Philp 04<br>Peiris 05<br>Solzbacher 07 | Najafi 98<br>Melly 01<br>Molnar 04<br>Jarvinen 05<br>Chen 06<br>Dawson 07 | Daly06                   |               |  |

| 10 <sup>-1</sup> - 10 <sup>0</sup>  | Otis 05                                | Cook 06<br>Dawson 09<br>Guermandi 07                                      | Ghovanloo 04<br>Sawan 05 |               |  |

| 10 <sup>-2</sup> - 10 <sup>-1</sup> |                                        | Pletercher 07<br>Pletercher 09<br>Bashirullah 09                          |                          |               |  |

Table 1.1 Power and data transmit status from recent research reports

Nowadays, researchers are very interested in designing ultra-low power consumption circuits for implantable devices by optimizing analog circuits. The idea is to improve the analog circuit performance through different approaches such as high integration density, integrating fewer components and balancing different trade-offs, etc. as well as reducing the entire circuit power consumption. On the other hand, in digital circuit design, researchers are also attempting to miniaturize the whole circuit by lowering the data communication rate through better algorithms [20]. Recently, a lot of researchers have published studies on devices and systems with ultra-low power consumption [19]. They reported a large array of implantable devices that may consume from 10s to 100s of nW

through optimized circuit design and advance fabrication techniques. For example, in [21], the author reported a system with its amplifier, band-pass filter, and SAR-ADC integrated in a single chip and consumes just 450 nW. In fact, there are also some implantable devices which do not need to transmit data which may consume even less power.

To deliver enough energy to the implanted internal device from the external device as discussed above, many methods have been studied, for example, electro-magnetic wave, pure magnetic field, light or even sound. We will briefly analyze them below.

Radio frequency (RF) is a particular kind of electromagnetic wave with frequencies lies in a range of 3 kHz to 300 GHz [22]. It is widely used in wireless telemetries for industry applications, it can also be found in satellites, mobile phones, televisions and even radar systems. It is actually one of the most common and the most widely utilized technique to achieve wireless power and data transmission. However, because of its high frequency, RF may cause body tissue damage, e.g. ionizing tissue [23], it is rarely used in implantable device researches. In addition, radio frequency can be significantly attenuated when it passes through the human body tissue.

Another medium that is used to transmit signals is light, which is quite common in navigation applications. Sailors use a series of flash to communicate with each other from remote locations. In telemetry studies, researchers employ laser or diode to emit light from a source device, and then harvest and convert the optical signal into energy or data with a receiver device. One limitation of optical transmission is that the substance between the source device and the receiver device may block or attenuate the optical signal. To penetrate the tissues of human body, researchers also attempted to use light of different wavelengths, e.g. infrared light to implement the optical link [24]. In [25], light was used to penetrate cornea and lens of a patient to transmit power and data for a retinal prosthesis implant. However, long time exposure under strong light may result in fatigue or even damage to human tissue.

One more technique which is used to transfer energy is acoustic wave. It is a commonly employed method in industry applications, especially in submarine applications. The reason behind is that other media source can be absorbed under water, yet sound wave can propagate faraway. However, with sound wave, the achievable data rate is very low. Hence, in implantable devices, researchers are attracted more by some media source such as inductive link which has no absorption issue and can also accomplish high data rate.

Inductive link is a kind of media source to implement telemetry, especially for biotelemetry. By placing two coupled coils in a proper distance, the coupling magnetic field generated in one coil will be transformed into electric current in the other coil. Then energy and data will be inter-transmitted between two coils simultaneously. Inductive link is one of the most widely used techniques to accomplish energy and data transmission in implantable devices. Compare with other media sources, inductive link can achieve a very high power transmission efficiency. Furthermore, data signal can also be transmitted through different modulation methods in an inductive link with power carrier signal. One critical limitation of the inductive link is its limited coil distance. Large distance may cause the transmission efficiency to greatly decrease, which means the external body inductive coil has to be placed in a proper distance (normally one to few centimeters) from the implanted inductive coil.

#### **1.2.5 Data Link of Implantable Devices**

For centuries, scientists were interested in transmitting data or signals into the bodies of living beings. A century ago, a series of experiments were conducted by Maurey to record the bird's muscle movements, in which a flying bird was studied by having wires attached on it and a hose lead to a smoked drum [26]. These experiments boosted most of the data transmission topics till even today for implantable device research. It is obvious that using wire is not a good choice for implantable devices. Not to mention that the wires will limited the movements of a human body; the wires penetrating skin surface can also easily cause skin infections. Furthermore, friction of the percutaneous wires may also lead to the muscle tissue damage. Hence, there are few researchers working on percutaneous wires that are used to connect implantable devices for clinical patients.

Advance of modern physical science enables engineering researchers to utilize various methods to implement data transmission without contact cables or wires. For implantable medical devices, similar to the power transmission, there are also several techniques including magnetic field, electro-magnetic wave and even light, etc. that have been employed or under research investigation for data links. Inductive link, which is a typical application of electro-magnetic induction has been widely used for implantable implementations, for example, the aforementioned mid-ear implantable device. The implanted device (receiver) and the external device (transceiver) communicate across the patient's skin in a distance of few centimeters' range. The transceiver and the receiver cannot be separated too far away because the further the distance between the transceiver coil and the receiver coil the more attenuation the electro-magnetic wave will experience.

On the contrary, shorter distance can help to enhance the strength of the inductive coupling. Recently, some of the implantable devices are designed to transmit power and data simultaneously through one coupling coil pair [27] [28]. However, for this type of designs or applications, the carrier frequencies cannot exceed tens of MHz because human tissue may absorb the high frequency signals and may also be damaged by them [29]. The most common frequency for these devices is 13.56 MHz. Meanwhile, the bandwidth of the transmitted signals may also be relatively small. For some particular implementations, which are not critical in data rate, this single coil pair solution is the best choice, because it can achieve high power efficiency and it takes less space than solutions of multi antennas/coil pairs.

There are also some researchers exploring the capability of radio frequency (RF) in transmitting a higher data rate because the carrier frequencies of RF signals can be hundreds of MHz or even higher as GHz. Another merit of RF technique is that the distance between transceiver and receiver can be meters away which is very competitive compared to inductive coupling coils. In [30], the author just employed RF as the data transmission method to fulfill the high data rate requirements of a neural recording. But also, as we have mentioned, because of the high carrier frequency, RF may be harmful to human body, and it is quite difficult to obtain approval from medical device regulation agency. For instance, the bandwidth is limited to 300 kHz for MICS (Medical Implant Communication Services) by FCC (Federal Communication Committee) standards in the USA. Hence, a lot of researchers are still concentrating on the inductive link systems. It can be found that quite many publications about the innovations on the inductive link were reported such as [31] - [34].

For modulation scheme of inductive links, considering the generic data transmission, frequency modulation is widely used for analog signal transmission because it is resilient to noise. Meanwhile, it can also be found that several different modulation schemes are used for inductive links, such as amplitude-shift keying (ASK) and phase-shift keying (PSK) are mostly employed for digital signal transmission. Also, considered the power transmission, there were some previous reports by means of multi-channels or multi coil pairs [35] [36] [37] to implement both the data and power transmission. However, including more physical components may result in a bigger implant device. Therefore, for implantable biomedical devices, because of the low power requirement and the limited physical size, the amplitude-shift keying (ASK) scheme is particularly appealing. In addition, an ASK scheme is normally a simple modulation circuit, which has low energy dissipation, adequate modulation index and reasonable signal-to-noise ratio (SNR) [38]. Furthermore, it enables the data transmission and power delivery to be achieved simultaneously.

### 1.2.6 Architecture of the Proposed Medical Device

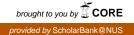

Figure 1.3 shows the architecture of the proposed biomedical system which includes the external device and the implantable device. We propose to develop this as a neurosensory system to acquire sub-scalp EEG data so that to provide long-term, neurological health monitoring for epilepsy patients. As can be seen in Figure 1.3, the whole microsystem has two parts. The internal part on the right side in the figure is a microchip which is implanted under the skin of a patient and connected to a well-designed thin electrode array that is also implanted in the body but separated from the microchip. The electrons array is located in

the sub-galeal beneath the patient's scalp yet in the outside of the patient's skull. The other part on the left is the external body device which is a wearable device. It is the so called transceiver which can be a small piece of device integrated with power amplifier, data receiver and signal processor. In this design, the implant device on the right side of the figure is wirelessly powered through the coupling coils by the transceiver on the left. After detecting EEG data from the sub-scalp, the implant device can transmit the biological signal to the transceiver through the same coupling coils. In this thesis, we will concentrate on the transceiver part (the left part of Figure 1.3).

Figure 1.3 Architecture of the proposed implantable device and external device

Based on the discussions above, in the following contents, we will present a transceiver design of the implantable system by means of inductive coupling coils for power and data transmission. An E type power amplifier is employed to amplify and transfer power from the external transceiver to the internal implantable device. At the same time, by designing a load-shift keying (LSK) demodulator --- a special scheme of ASK --- the data signal from the implanted device is transmitted to the external transceiver. The LSK demodulation

technique allows power and data to be transmitted through one single inductive link simultaneously. It can work under a variety of modulation indexes and different coding/decoding protocol. Meanwhile, it enables us to reduce the power consumption and body size of the whole microelectronic system.

# **Chapter 2 Power Amplifier**

This chapter conveys the analysis and design of power amplifiers for inductive data and power transceivers. First, we will discuss different topologies of power amplifiers. Then, state-of-the-art power amplifier designs are reviewed and analyzed. At last, we propose a novel Class-E amplifier for the proposed inductive transceiver device.

## 2.1 Power Amplifier

### 2.1.1 Introduction

Considering that the external transceiver part of a biomedical device is normally designed as a wearable/portable equipment so that it can be easily carried around by patients, and battery is normally the best option for its power supply. While, to extend the duration of a battery after a single recharge and also to prolong the lifetime of a battery, power amplifiers are widely employed to overcome the power issue in the external transceiver design. There are several topologies of power amplifiers. Based on the output stages for analog designs, they are categorized as A, B, AB and C, and based on the proportion of each input cycle for switching designs, they are categorized as D and E [39]. The D and E power amplifiers performance is significantly better than A to C [40] - [47]. Class E power amplifiers are generally one single-transistor solution, whereas two or more transistors are commonly required for Class D power amplifier. The transistors in power amplifiers are utilized as switches, which are expected to be non-power consumption components. Theoretically, a Class E power amplifier can achieve peak energy efficiency of 100%, whereas the values of Class A and Class B amplifier are 50% and 78% respectively. [48] reports a Class E power amplifier design with power efficiency of 96%. Hence, a Class E amplifier is the more advantageous topology compared to the rest types of power amplifiers in terms of power efficiency. Furthermore, to drive a Class E amplifier is also simpler than the other power amplifiers [49]. Therefore, for power amplifications, Class E amplifier is particularly appealing among all the other amplifier architectures, especially for implantable device or short distance wireless communication applications.

## 2.1.2 Principle of Class E Power Amplifiers

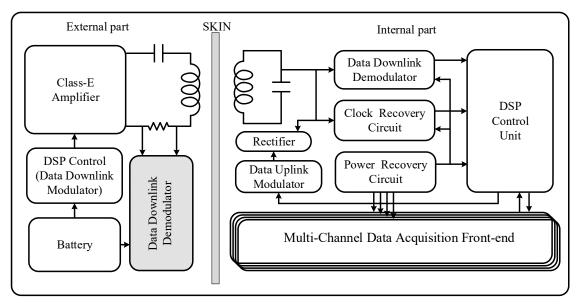

Figure 2.1 shows a typical conventional basic architecture of Class E power amplifiers. As can be found in Figure 2.1, there is an RF choke, a MOS transistor M and a load network that includes two capacitors  $C_p$  and  $C_0$  and an inductor  $L_p$ . The MOS transistor M is utilized as a switch. Controlled by the driver voltage at a specific work frequency, it will be switched between stages of "on" and "off" regularly. The inductance of RF choke should be large enough such that the DC current can dominate the AC components in the current. Therefore, the RF choke acts as a DC current source. In the load network, the capacitors  $C_0$ ,  $C_p$  and the inductor  $L_p$  work together to generate sinusoidal waveforms, and eventually enable the MOS transistor M to be switched between on and off smoothly. And, the current that flows across M during the operations is quite a small value. In this circuit, the load of the circuit is Rp.

As mentioned above, to extend the battery life, we should try to reduce the energy dissipation in the circuit at the utmost. In another word, we need to endeavor to maximize the power efficiency while designing the whole circuit. The power efficiency is a parameter,

which is used to assess the proportion of power that is converted and delivered to the load. Regarding the definition, we can have the equation to calculate power efficiency:

$$\eta = \frac{\text{power that is converted and delivered to the load } R_p}{\text{DC power supply of } V_{cc}}$$

From the equation, it can be found that the ideal efficiency is 100%.

Figure 2.1 Structure of Class E power amplifier

## 2.1.3 Design Procedure

Since the concept of Class E power amplifier was introduced in 1964 by Ewing [50], there have been a lot of researches published on this type of power amplifier. Some introduces circuits that can support different quality factors, as well as the different duty ratios, and some introduces the analytical solutions for Class E power amplifier [51] [52].

From the previous designs, researchers were attempting to find out how the components affect each other, and what is the optimum setting value for each component, and eventually minimize the switching loss. Ideally, for conventional applications, by neglecting the parasitic resistance of all the components, the total power that is delivered to the load resistor  $R_p$  can be 100%. But, this efficiency can never be achieved in practice. For wireless implantable devices, Class E power amplifiers are also widely employed to amplify and deliver power [53]. However, it can be found that the conventional applications are different from the wireless implantable devices. In the conventional applications, the output power of the circuit is the total power consumption of the load resistor  $R_p$ . While, for wireless implantable devices, the delivered power is expected to be the electromagnetic energy generated by the inductor  $L_p$ , and the power dissipated in the load resistor  $R_p$  should be as small as possible. But the design methods and procedures for the conventional applications are still applicable for the wireless implantable devices, because the optimizing aims are the same, which is to reduce the loss on the MOS transistor switch.

According to the optimizing design procedures introduced in [54], we will initially determine a starting parameter. What we need to consider in designing the circuit including: first, how much power we need to generate and deliver to the inductor  $L_p$  in the external device which is denoted as  $P_L$ . This is actually a requirement of the implanted device; second, the quality factor of the entire circuit, which is denoted as  $Q_p$  is determined by the requirement of the data transfer rate; last, the voltage source that is used to supply the power amplifier is denoted as  $V_{cc}$ . This voltage source value is normally the starting parameter. But it is adjustable in case that parameters of  $P_L$  and  $Q_p$  cannot meet the desired requirements. The power which is dissipated in the load resistor  $R_p$  and the power delivered in the inductor  $L_p$  can be calculated by

$$P_L = \frac{1}{2} L_p \omega_c |I_p|^2$$

(2.1)

$$P_R = \frac{1}{2} R_p |I_p|^2 \tag{2.2}$$

Where  $I_P$  is the current that flow through  $R_P$  and  $L_P$ . With (2.1) and (2.2) and the quality factor equation of (2.3),

$$Q_P = \frac{P_L}{P_R} \tag{2.3}$$

we can have:

$$Q_p = \frac{L_p \omega_c}{R_p} \tag{2.4}$$

Then, P<sub>R</sub>, which is the power consumed by R<sub>P</sub> can be calculated by:

$$P_R = \frac{V_{cc}^2}{kR_p} \tag{2.5}$$

Where k is a constant parameter that is determined by  $Q_P$  and the duty ratio. Combining the equation above, we can derive the equation of  $L_P$ :

$$L_p = \frac{Q^2 V_{cc}^2}{k P_L \omega_C} \tag{2.6}$$

The equation of  $R_p$  is also achievable given  $Q_{p}$ ,

$$R_p = \frac{L_p \omega_c}{Q_p} \tag{2.7}$$

After the calculation of the resistor  $R_p$  and the inductor  $L_p$ , we can then determine the remaining parameters of the whole circuit, for example, the values of the capacitors. However, considering the parasitic capacitance, we connected more capacitors and inductors in the circuit so that the values can be adjustable.

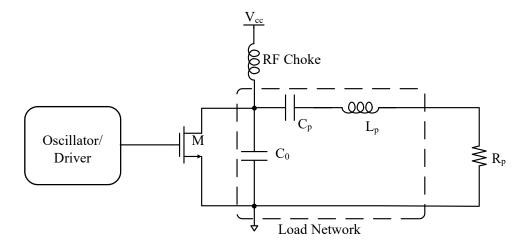

### 2.1.4 The Proposed Class E Amplifier

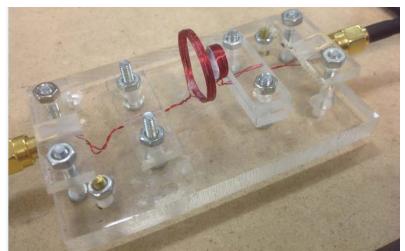

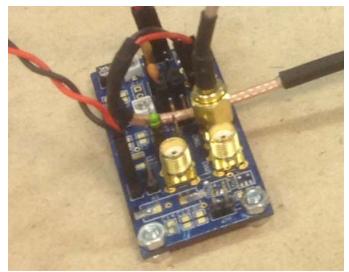

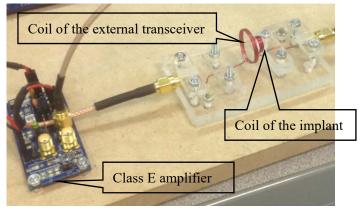

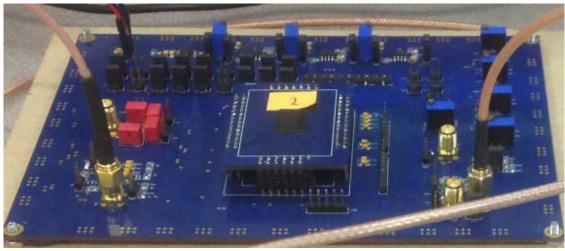

In this research, the power amplifier is required to deliver 1 mW to the secondary coil. And the power carrier frequency should be from 10 to 20 MHz. Based on these requirements, we designed the circuit as shown in Figure 2.2. The coil on the transceiver side is 19.8 mm and the size of the secondary side is 9.3 mm as shown in Figure 2.3 and the transceiver PCB prototype is shown in Figure 2.4. Measurement results will be discussed in chapter 7.

Figure 2.2 Class E amplifier circuit

Figure 2.3 The coupling coils of the proposed Class E power amplifier

Figure 2.4 Proposed Class E amplifier prototype

# **Chapter 3 Load Shift Keying**

## 3.1 Introduction

It is commonly seen that inductive coupling coils are employed to power implanted devices. However, most of the coupling coils suffer from transmitting enough power because of their limited physical sizes. Hence, to mitigate this limitation, Load Shift Keying (LSK) modulation scheme is adopted because it can support small modulation index signals which enhance the power transfer efficiency.

LSK, is also called "reflectance modulation" [55] [56], which is a particular implementation of passive impedance reflection, and also a primary method used in designing implantable medical devices for retrieving biological data. LSK is also considered as a special topology of amplitude-shift keying (ASK) in terms of the circuit design [56]. As we have discussed, the LSK is a bi-functional modulation technique, which allows transmissions of power and data to be accomplished simultaneously through one single inductive coupling link. A common inductive coupling link includes two basic inductive coil components. One property of an inductive coupling link is that when the loading impedance of one side is changed, the loading impedance in the coupled side reflects the change. This is actually the change of the reflected impedance. LSK modulation topology is just an application of this property. By detecting the reflected impedance changes that happened in the secondary side, and eventually decode the signal. This signal is just the digital data transmitted by the secondary circuit. This working

scheme is different from a common topology of ASK scheme because in a common ASK modulation device the power efficiency may suffer more decrease when data is also transmitted in the same inductive link. For example, in the common ASK design of [57], the primary side was used to detect the amplitude changes of the input waveform, which was a reflection against the resonant capacitance changes or the inductance changes appeared on the secondary coil. However, while the primary side was working on the reflection, the changes from the secondary coil might conduct a resonant frequency change in the primary side, and this change could greatly affect the power transmission efficiency.

To realize the LSK modulation topology, a particular functional circuit is required to modulate the load impedance changes on the secondary side related to the transmitted digital data. This modulating procedure should affect as small as possible on the resonant capacitance or the inductance of the secondary side circuit; otherwise, the power transmission from the primary side to the secondary side will be affected. In this particular functional circuit design, the AC loading impedance on the secondary side is determined by both the inductive power recovery circuit and the DC loading impedance [58]. Therefore, through varying the power recovery circuit appropriately, which may adjust the DC load impedance of this circuit to a desire value, the AC loading impedance can be eventually modulated. In practice, a data-driven switch will be adopted to configure the circuit from one stage to another, and to change the DC loading impedance from one value to another. This configuration can eventually shift the AC loading impedance between two values according to the binary digital data. When the voltage potential crossing the primary coil reflects the AC loading impedance changes on its own amplitude, the changes will be recognized as data bits "0" and "1". Through such a procedure, the data signal is thus

transmitted from the secondary side circuit to the primary side circuit. In this research, we focus on the development of the transceiver device, which is the primary side circuit. To test the entire working procedure, we utilized an FPGA to simulate the AC load impedance changes.

Even though the LSK is one of the most common ways to implement power and data transmission link, to design and realize a LSK with a high efficiency and high-speed transmission is still a challenging task.

The first challenge is to make sure that the waveform amplitude on the primary side circuit (the external body circuit) can reflect an immediate and distinct change when the AC load impedance on the secondary side circuit (the implanted device circuit) changes. To overcome this challenge, the AC load impedance change on the secondary coil have to be distinguishable as much as possible, which means the total amount of the load value should be changed as large as possible. Because the maximum achievable change on the load impedance is to reduce the amount from an initial value to zero, many reported designs chose either to shut down the load completely which means to keep the circuit open or to bypass the load which means to short the circuit. However, both of these two methods may disturb the secondary circuit on the resonance, and eventually reduce the total efficiency of power transmission from the primary circuit to the secondary circuit.

The second challenge is to achieve a high data rate. In the former discussed working procedure of LSK topology, to achieve a reliable recovery of the data signal on the primary circuit, the power carrier frequency ought to be separated away from the data bandwidth as much as possible. Meanwhile, the power carrier frequency cannot be too high as

discussed in chapter 1, because the high frequency signals can be absorbed by human tissue and may result in cell damage [59]. Hence, the carrier frequency have to be set to less than tens of MHz, for example, the most commonly used carrier frequency is 13.56MHz. This may ultimately affect the data rate of a LSK link by limiting it to a few Mbps. The achievable ratio of data rate to carrier frequency is normally very small.

The last challenge is to reduce the sensitivity of a LSK data link against the interferences of the surrounding environment. The media source that a LSK data link applied is electromagnetic wave. Hence, when the relative position or the orientation of the inductive coupling coils is changed, the density of the electromagnetic wave may also be modified, and this will lead to reduction on the efficiency of the wireless link. At the same time, other electronic devices around may also emit electromagnetic wave, and the unresolved electromagnetic wave may also affect a LSK inductive link by generating some unexpected amplitude variations on the power carrier waveform. All these changes or interferences may substantially reduce the demodulation accuracy of the LSK link. And it could be even more severe when the design is required to achieve a higher power transmission efficiency because this means the modulation index have to be small.

### 3.2 Principle of LSK [58]

Figure 3.1 Circuit for analysis of LSK principle

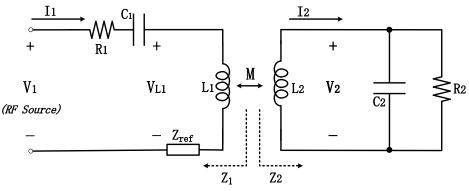

Figure 3.1 shows the circuit, which is used to analyze the principle of LSK. It can be seen in the figure that M is the mutual inductance of the inductive coils;  $Z_2$  is the secondary coil load impedance and reflected impedance in the primary side is  $Z_{ref}$ . If we define the RF power carrier's angular frequency as  $\omega$ , according to [58] then we can have:

$$Z_{ref} = \frac{\omega^2 M^2}{Z_2} \tag{3.1}$$

And the primary coil load impedance is:

$$Z_{1} = \frac{V_{1}}{I_{1}} = R_{1} + Z_{ref} + j\left(\omega L_{1} - \frac{1}{\omega C_{1}}\right)$$

(3.2)

If we take L<sub>2</sub> as a voltage source V<sub>2</sub>, and the impedance in series with L<sub>2</sub> is  $j\omega L_2$ . Then we can calculate the secondary coil's impedance by the following equation:

$$Z_{2} = \frac{V_{2}}{I_{2}} = j\omega L_{2} + \frac{1}{\left(j\omega C_{2} + \frac{1}{R_{2}}\right)}$$

$$= \frac{R_{2}}{1 + \omega^{2}R_{2}^{2}C_{2}^{2}} + j\left(\omega L_{2} - \frac{\omega C_{2}R_{2}^{2}}{1 + \omega^{2}R_{2}^{2}C_{2}^{2}}\right)$$

(3.3)

As can be seen, both of the two circuits in the primary and the secondary sides work in frequency  $\omega$ , which is a common resonant frequency. Therefore, if the imaginary parts of the impedance for both  $Z_1$  and  $Z_2$  are equal to zero, we can have:

$$\omega L_2 - \frac{\omega C_2 R_2^2}{1 + \omega^2 R_2^2 C_2^2} = 0 \tag{3.4}$$

$$C_2^2(\omega^2 R_2^2 L_2) - C_2(R_2^2) + L_2 = 0$$

(3.5)

With (3.5) and (3.3), we obtain:

$$Z_2 = \frac{R_2}{1 + \omega^2 R_2^2 C_2^2} = \frac{L_2}{R_2 C_2}$$

(3.6)

According to [60], the mutual inductance can be calculate by the following equation:

$$M = k\sqrt{L_1 L_2} \tag{3.7}$$

Where k is the parameter of coupling-coefficient, which is determined by geometrical parameters. Then with the equations above, we can derive  $Z_1$  as:

$$Z_1 = R_1 + k^2 \omega^2 L_1 C_2 R_2 \tag{3.8}$$

If we define V<sub>L1</sub> as the potential difference between the two terminals of L<sub>1</sub>, then,

$$V_{L1} = \frac{\omega Z_1 V_1}{Z_1} = \frac{V_1}{\omega C_1 (R_1 + k^2 \omega^2 L_1 C_2 R_2)}$$

(3.9)

From the equation, if the resistance of the receiver circuit is changed from  $R_2$  to  $R'_2$ , then the voltage  $V_{L1}$  will become:

$$V_{L1}' = \frac{V_1}{\omega C_1 (R_1 + k^2 \omega^2 L_1 C_2 R_2')}$$

(3.10)

The equation of (3.9) and (3.10) complied with our discussion in the former section. And based on this equation, the LSK modulation is designed in the following section.

### 3.3 The Proposed LSK Demodulator

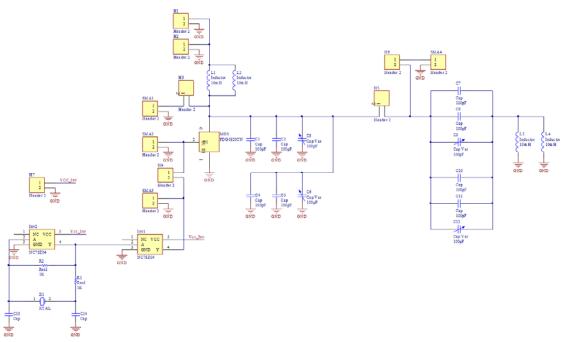

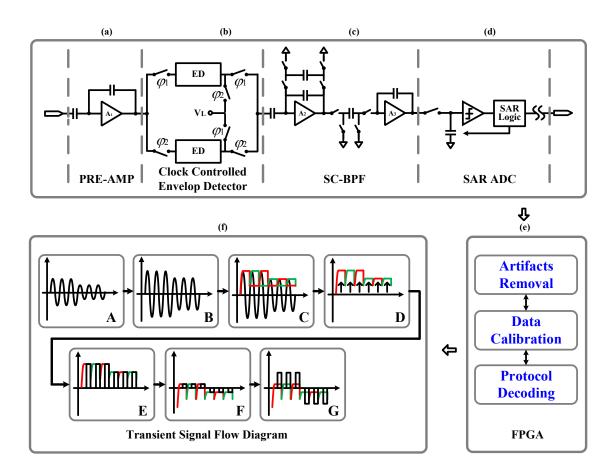

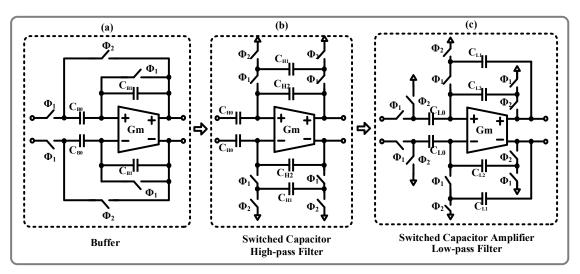

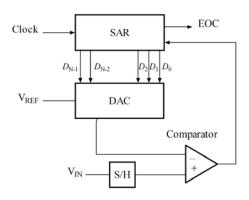

Based on the discussion above, a LSK demodulator is designed and portrayed in Figure 3.2. This LSK demodulator is employed in the transceiver device to demodulate the received data from the reflected power carrier signal, process the demodulated signal and finally output a digitized waveform. It can be seen in Figure 3.2 that there are 6 modules in the whole circuit. The demodulator consists of a pre-amplifier (a), an envelope detector (b), a switched-capacitor band-pass filter (c) and an asynchronous 10-bit SAR ADC (d). Figure 3.2(e) and Figure 3.2(f) are two independent modules, which are an FPGA and a signal indicator.

Figure 3.2 LSK demodulator circuit schematic

The pre-amplifier is a two stage Operational Transconductance Amplifier (OTA) that supports 600MHz GBW and serves as a buffer of the signal. Its output is directly fed to the next module, an envelope detector.

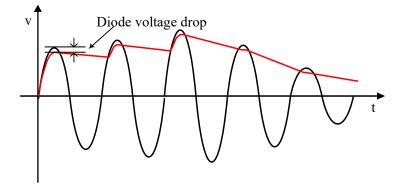

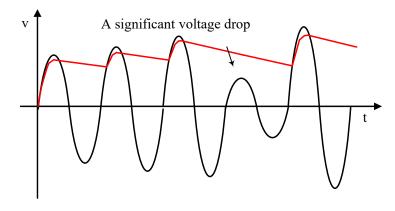

The envelope detector is designed to realize the spectral analysis following the preamplifier. A simple conventional envelope detector usually includes a diode and a capacitor, which has a diode voltage drop and a trade-off between slew rate and droop rate [61]. Some more practical designs may utilize an op-amp and either a diode or a CMOS transistor with a feedback path so that to reduce the diode voltage drop. However, the limited slew rate of op-amp increases the droop rate of the circuit [61]. And an increased droop rate means a faster speed of discharge. When the input voltage drops very fast, it is very hard for the detector to follow the input signal and accurately detect the peak value. In addition, most of the conventional designs discharge through a RC filter or a current source [61] - [64]. With these discharge branches, ripples may be introduced in the extracted envelope and they require a substantial bit-to-bit interval to avoid decoding errors. As a comparison, the envelope detector design in this thesis inherently suppresses the mentioned defects: as shown in Figure 3.2(b). More details about the design and the working flow will be discussed in chapter 4.

The switched-capacitor band-pass filter is cascaded following the envelope detector to get rid of the large DC component from the extracted envelope and amplify the envelope. This is because that the extracted envelope contains some unresolved interferences, which should be removed subsequently for a reliable data transmission. Detailed content will be discussed in chapter 5 In addition, the 10-bit asynchronous SAR ADC with 10 MHz sampling rate is designed to digitize the output signal of the filter. In this ADC design, both split-capacitor array and  $V_{CM}$ -based switching topology are employed to reduce power and area. More discussion can be found in chapter 6.

Compared to the previous research reports, the performance of this design is improved in the following two aspects: firstly, it achieves a higher sensitivity of modulation based on the simulation, which is less than 1% in modulation index without sacrificing the power transmission efficiency. Secondly the multi-phase envelope detector overcomes the trade-off between envelope ripples and the detector speed which increases the achievable data rate significantly [65] [66]. Thirdly, this design is an integrated circuit that included analog and digital components, which can reject some artifacts and interferences while processing and transmitting signals.

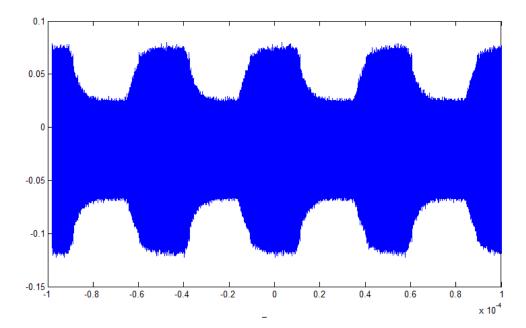

The schematic is implemented and simulated in Cadence 6.1. To test the simulation performance of the envelope detector, we generated an input signal in 20 MHz frequency and the modulation index was 1%, the signal was shown in Figure 3.3. This signal was generated by multiplying two signal sources, one was sinusoidal signal with a 20 MHz frequency and 1.0 V amplitude, and it was used to simulate the power carrier signal; the other signal was a square signal in a frequency of 2.5 MHz and amplitudes are 50 mV and 49.5 mV. Figure 3.4 shows the squire signal and it can be found that the modulation index is 1%. The demodulation result is shown in Figure 3.5. The result was captured before SAR ADC module. Measurement result of the prototype will be discussed in chapter 7.

# **Chapter 4 Envelope Detector**

### **4.1 Introduction**

Envelope detector is also called peak detector, which is widely utilized as a core component by the transceiver side of a wireless communication link. It is usually employed to build up a closed-loop, which is also called automatic voltage gain circuit [67]. Normally, in analog circuit design, an envelope detector is used to detect either the positive peak value or the negative peak value of a signal, and also to track the values along with the change of time. Figure 4.1 shows the ideal output waveform of a positive envelope detector [68]. In this chapter, we will discuss a few envelope detector designs and the circuit we implemented for this thesis.

Figure 4.1 Ideal envelope detector output waveform

### 4.2 Principle of Envelope Detector

#### 4.2.1 Diode Capacitor Envelope Detector

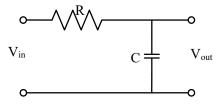

Figure 4.2 shows the principle schematics of a positive envelope detector [69]. From the schematic, this circuit contains two components only, which are a diode and a capacitor. We take this positive envelope detector as an example to illustrate the working principle of the envelop detector. As we can see in Figure 4.2, when the input voltage  $V_i$  is greater than the detected value  $V_p$  plus the voltage drop across the forward-biased diode D, then the diode D will be "turned on" and current will pass through the diode D and charge the capacitor  $C_h$  until the voltage of  $V_b$  is equal to or greater than  $V_a$ , then the diode will be "turned off" and the capacitor holds the  $V_b$  at the maximum value of the input signal, which means the output voltage follows input peak value. Even when  $V_i$  drop, the maximum value  $V_p$  will still be held at the maximum value of the input signal by capacitor  $C_h$ . Hence, if the capacitance of  $C_h$  is appropriate, the output signal will the waveform as shown in Figure 4.3.

Figure 4.2 Diode capacitor envelope detector

Figure 4.3 Output waveform of diode capacitor envelop detector

By analyzing the circuit shown in Figure 4.2 we can find that there are a few problems with this envelope detector circuit. First, the detected value  $V_p$  cannot be accurately equal to the maximum value of the input signal because there is a voltage drop across the diode D. Thus, if the input signal is similar to the diode voltage drop, the circuit may not able to detect the input. Second, the input impedance is almost zero which is too small because the diode is operated in forward-biased condition. Third, normally for a diode, the voltage drop is sensitive to the change of environmental temperature, as well as the current. This may be another severe effect on the accuracy of the envelope detector circuit. Fourth, there is no discharge path in the circuit. If there is a quick and distinct drop happens in the input signal, this envelope detector may not able to follow the drop, as shown in Figure 4.4. Fifth, there is also a tradeoff on how to set up the capacitor value. For a small capacitor, it is easy to hold the peak value, however, need longer time to charge up and discharge [69].

Figure 4.4 Envelope detector output failed to detect a quick and distinct input voltage drop

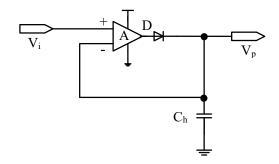

#### 4.2.2 Detector Using Op-amp

Figure 4.5 shows a positive envelope detector with an op-amp in the loop. In this circuit, the voltage  $V_p$  is fed as a feedback to the negative input terminal of an op-amp A. With this configuration,  $V_p$  can closely follow the positive input  $V_i$  when  $V_i$  is larger than negative inputs of the op-amp A, which is  $V_p$ . Meanwhile, we can solve the first problem of the diode voltage drop discussed in section 4.2.1. While, when the input voltage  $V_i$  drops till less than  $V_p$ , which means the op-amp A operates in negative saturation condition, then the diode D is switched off, and the capacitor  $C_h$  will hold  $V_p$  at the previous maximum value.

Figure 4.5 Envelope detector with op-amp

Compared with the diode capacitor envelope detector, an extra power supply is required to drive the op-amp A. At the same time, the slew rate of the op-amp will restrict the operation speed of the whole circuit.

#### **4.2.3 Envelope Detector with MOS Transistor**

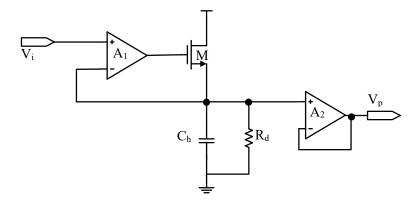

Figure 4.6 demonstrates another envelope detector scheme, which is more practical. Its difference from the scheme shown in Figure 4.2 is that the diode is replaced by a source follower, and a buffer  $A_2$  is cascaded. In this circuit, when the input  $V_i$  is greater than  $V_p$ , the MOS transistor M will be "turned on", which means the current can flow through M to charge up the capacitor  $C_h$ . In contrast, when  $V_i$  drops till less than  $V_p$ , which means that the negative input of op-amp  $A_1$  is greater than the positive input, the MOS transistor will be "turned off" and the capacitor  $C_h$  will hold the output voltage at the former detected peak value. To improve the performance of following a falling input signal, the output is grounded through the resistor  $R_d$  to discharge  $C_h$ . With this discharge path, the circuit can achieve a higher droop rate. In some designs, the resistor  $R_d$  may also be replaced by a current source. Generally, to improve the loading capacity, a buffer  $A_2$  may be implemented to isolate the detected voltage  $V_p$  from the following load circuit.

Figure 4.6 Positive envelope detector with MOS transistor and buffer

With this schematic, we can found that the first four problems mentioned in section 4.2.1 are somehow resolved. This circuit can have a more accurate trace in terms of a quick drop of the input signal because there is a special path to discharge the hold capacitor. However, we have to design the discharge path carefully. Because if the droop rate is too high or too low, the detector may not be able to detect the neighboring peak value if the input signal fluctuates too fast.

#### **4.2.4 Positive Peak Detector Using Current Mirror**

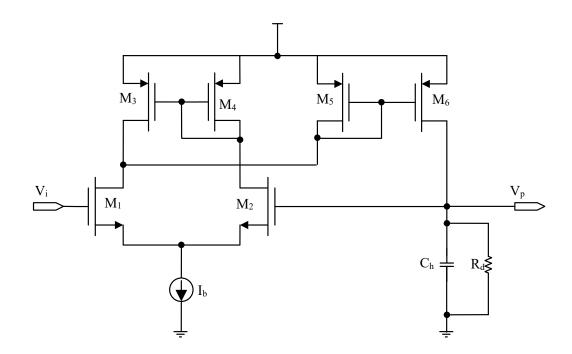

One more method to enhance the speed and accuracy of an envelope detector is to use a current mirror as the displacement of the diode in Figure 4.6. Figure 4.7 shows the schematic designed by this method. It can be seen that this positive envelope detector consists of a differential amplifier (CMOS transistor  $M_1$  to  $M_4$ ), a current mirror (CMOS transistor  $M_5/M_6$ ) and a discharge path ( $R_d$ ). In this circuit, the function of the differential amplifier is same as the op-amp in section 4.2.3. When  $V_i$  is greater than  $V_p$ , then transistor  $M_5$  and  $M_6$  will be "turned on", the current can flow through. The current through transistor  $M_5$  will be mirrored by transistor M6 and charge up the hold capacitor  $C_h$ .

Figure 4.7 Positive envelope detector with current mirror

## 4.3 The Proposed Envelope Detector

In this work, the envelope detector is applied to accomplish spectral analysis following the pre-amplifier as shown in Figure 3.2. A simple conventional envelope detector as shown in Figure 4.2 is usually a diode-capacitor circuit, which has a diode voltage drop, and the droop rate conflict with the slew rate. Some more practical designs discussed above may utilize an op-amp and a diode or a MOS transistor with a feedback path so that to reduce the diode voltage drop or solve other problems discussed in section 4.2.1. However, the restricted slew rate of the operation amplifier may increase the droop rate. A higher droop rate means the discharge is faster. When the input peak value falls very fast, it may be very hard for the detector to accurately chase the input peak values. Furthermore, many of the conventional designs discharge through a RC filter or a current source [70] - [73] as

discussed in section 4.2.3 - 4.2.4. And this may contribute to the ripples in the output, which may need a substantial bit-to-bit interval to correct the decoding errors. As a comparison, the envelope detector design in this research inherently overcome the mentioned defects.

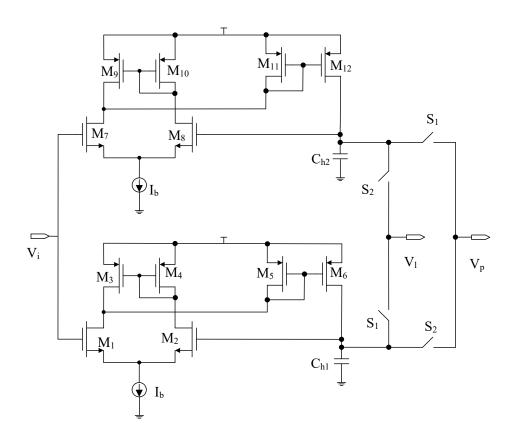

Firstly, as shown in Figure 4.8, to remove the diode voltage drop, a unidirectional current mirror ( $M_5$  and  $M_6$  or  $M_{11}$  and  $M_{12}$ ) is constructed to replace the ideal diode of a conventional circuit. When the input voltages are greater than the maximum detected values, the OTA will produce a voltage amplitude on the drain and gate of  $M_5$  or  $M_{11}$  which will "turn on" the current mirror, the excess current will flow through  $M_5$  or  $M_{11}$ , and will be mirrored by  $M_6$  or  $M_{12}$  and eventually to charge up the hold capacitor  $C_{h1}/C_{h2}$  and force  $V_1/V_p$  to track the peak values of  $V_i$ . On the contrary, as  $V_1$  or  $V_p$  approaches  $V_i$  or while the input signal drop till less than the output peak value, the output of OTAs which are built-up by  $M_1$  -  $M_4$  and  $M_7$  -  $M_{10}$  will drop to zero or even below, and the current mirrors will be cut off.

Secondly, to overcome the detecting issue due to low droop rate, we employ a configuration of non-overlapping clock and switched-capacitor to control two sets of envelope detectors to work in turns. With such a mechanism, through resetting each peak detector periodically, each envelope detector will be distributed more time to discharge itself. And after the reset, each one will work more precisely. The work procedure is stated here. When  $S_1$  is switched on, then the upper envelope detector ( $M_7$  to  $M_{12}$ ) will work, and the lower detector ( $M_1$  to  $M_6$ ) will be reset. This is phase one. In reverse, when  $S_2$  is switched on, then the lower envelope detector ( $M_1$  to  $M_6$ ) will work, and the upper detector ( $M_7$  to  $M_{12}$ ) will be reset. This is phase two. The holding capacitors  $C_{h1}$  and  $C_{h2}$  will work

in turns for these two envelope detectors to hold and output the detected peak values phase by phase. Through this mechanism, both of the two envelope detectors can have enough time to discharge itself, which eventually diminish the ripples and the distortions on the output waveform while the data rate is maintained the same.

We utilize a top clock to generate several non-overlapped clocks through digital standard cells. Also, the output signals of the proposed envelop detector are sampled by the subsequent filter or the ADC with a <sup>1</sup>/<sub>4</sub>-delayed sampling clock signal, which allows that the proposed system architecture has enough time for signal processing and settling.

This circuit can suppress the effect of switching glitches with three methods: first, the values of hold capacitors  $C_{h1}$  and  $C_{h2}$  are larger enough to suppress the switching glitches compared with conventional circuits; second, Switches  $S_1$  and  $S_2$  are controlled by non-overlapping clock signals, and dummy transistors are also used in the switches to remove glitches; third, the input signal has already been amplified before it is sent to the envelop detector, so the effect on amplitude introduced by glitches can be neglected here.

Figure 4.8 Multi-phase envelope detector with current mirror

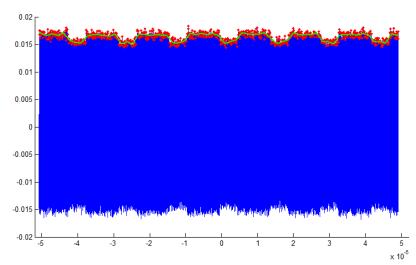

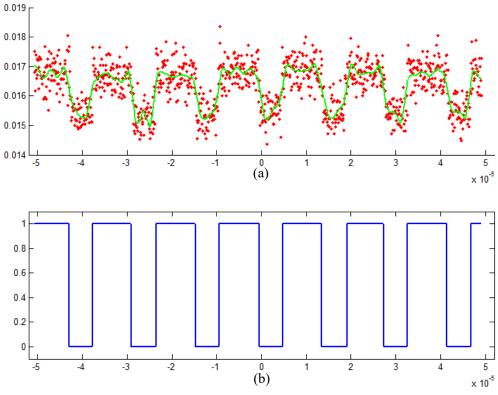

The schematic is simulated in Cadence 6.1. To test the performance of the envelope detector, we generate an input signal in 20 MHz frequency and 50 mV amplitude as shown in Figure 4.9. This input is a multiplied signal by two sources, one is sinusoidal signal with a 20 MHz frequency and 1 V amplitude, and it is used to simulate the power carrier signal; the other one is a square signal in a frequency of 2.5 MHz and amplitudes of 50 mV and 35 mV. The simulation result is shown in Figure 4.10. Because the bit error rate is generally higher when the transmission signal is in a higher frequency compared with the signal in a lower frequency, so we provided the simulated results of the signal in a high frequency only and take them as reference.

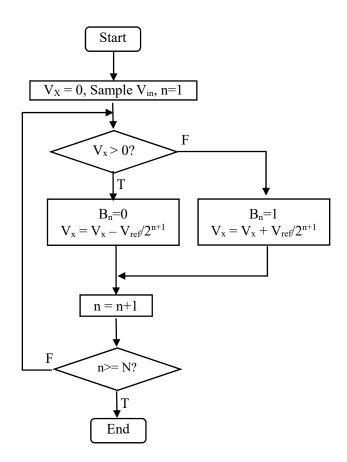

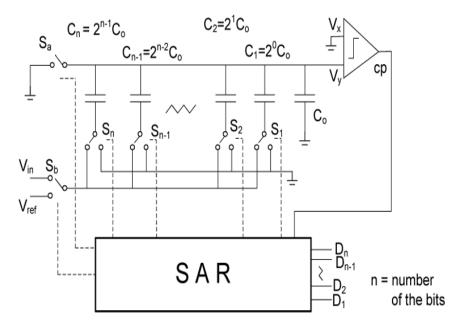

Figure 4.10 Simulate result regarding the input signal of Figure 4.9, two different color plots are the two phase of outputs, which are  $V_1$  and  $V_p$  in Figure 4.8