## OPTIMAL PULSE WIDTH MODULATION OF MULTILEVEL INVERTERS FOR MEDIUM VOLTAGE DRIVES

AMARENDRA EDPUGANTI

NATIONAL UNIVERSITY OF SINGAPORE

2015

### OPTIMAL PULSE WIDTH MODULATION OF MULTILEVEL INVERTERS FOR MEDIUM VOLTAGE DRIVES

AMARENDRA EDPUGANTI (M.Tech, IIT Kanpur, India)

### A THESIS SUBMITTED

FOR THE DEGREE OF DOCTOR OF PHILOSOPHY DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING NATIONAL UNIVERSITY OF SINGAPORE

### DECLARATION

I hereby declare that this thesis is my original work and it has been written by me in its entirety. I have duly acknowledged all the sources of information which have been used in the thesis.

This thesis has also not been submitted for any degree in any university previously.

R. Amarendra

Amarendra Edpuganti September 7, 2015

## Acknowledgements

It is my great pleasure to remember and appreciate all those directly or indirectly involved in successful completion of the thesis. First of all, I would like to express my sincere gratitude to my thesis supervisor Dr. Akshay Kumar Rathore for his esteemed guidance, encouragement and trust in my ability throughout study. His subject expertise, perfect planning and vision has been greatly instrumental in completing the thesis within three years. I am also grateful for his kind support in obtaining internship position at Rolls-Royce, Singapore and part-time research job in university.

I would like to thank National University of Singapore for giving me the opportunity to pursue doctoral studies and awarding research scholarship. I would also like to thank lab officers Mr. Y.C. Woo, Mr. M. Chandra, Mr. Seow, Mr. Abdul Jalil, and Mr. Teo for their support in doing experimental work. I would like to thank Dr. Amit Gupta for giving me the internship opportunity at Rolls-Royce, Singapore and Michael Zagrodnik for deep technical discussions during internship.

I am also grateful to my colleagues Pan Xuewei, Radha, Ravi, Gnana, Debjani, Satarupa, Devendra, Anirban, Suvendu, Dorai babu, Kanakesh, Divya, Anurag, Siva, Prasanna, Jeevan, and Kalpani for their support and interactions during studies. I am also indebted to my friends Rajasekhar, Ashok, Suvendu, Himanshu Singh, Arjun, Vishal, Gopal, Manish Kanjikar, Shiva, Lalan Kumar, Santosh, Kamesh, Virendra, and Bala Kumar for their support in having peaceful stay in Singapore.

I am obliged to my parents for showing me the path to pursue doctoral studies. I am specially grateful to my wife Maheswari for her unconditional love and support throughout my thesis. I owe a huge gratitude to my spiritual master H.H. Radhanath Swami for giving me the vedic wisdom to pursue a meaningful life and also for inspiring his disciples to become an ideal example in the society. I am specially grateful to H.G Devaki Nandan prabhu for his valuable guidance through out my stay in Singapore. I am also grateful to H.G Shankar Pandit Pr for his maturity and wisdom. Most of all, I thank their lordships Sri Sri Jagannath Baladeva Subhadra for giving me the opportunity and intelligence to carry out the research work.

# Contents

| A             | cknov | wledgements                                          | i   |

|---------------|-------|------------------------------------------------------|-----|

| Ta            | ble o | of Contents                                          | iii |

| Su            | ımma  | ary                                                  | vi  |

| $\mathbf{Li}$ | st of | Tables v                                             | iii |

| $\mathbf{Li}$ | st of | Figures                                              | x   |

| Li            | st of | Acronyms x                                           | ix  |

|               |       |                                                      | xi  |

|               |       | ·                                                    |     |

| 1             | Intr  | roduction                                            | 1   |

|               | 1.1   | Background                                           | 1   |

|               | 1.2   | Literature Survey                                    | 5   |

|               |       | 1.2.1 LDSF modulation techniques                     | 5   |

|               |       | 1.2.2 Emerging MLC topologies                        | 20  |

|               | 1.3   | Performance comparison of LDSF modulation techniques | 25  |

|               | 1.4   | Research Problem and Objectives                      | 27  |

|               | 1.5   | Thesis Contributions                                 | 28  |

|               | 1.6   | Thesis Outline                                       | 29  |

|               | 1.7   | Concluding Remarks                                   | 30  |

| <b>2</b>      | Gen   | neralized SOP Technique                              | 31  |

|               | 2.1   | Introduction                                         | 31  |

|               | 2.2   | Basics of SOP                                        | 32  |

|               | 2.3   | Estimation of pulse number, $N$                      | 33  |

|               | 2.4   | Optimization of switching angles                     | 35  |

|               |       | 2.4.1 Multilevel Structures                          | 37  |

|               |       | 2.4.2 Optimization Algorithm                         | 38  |

|   |     | 2.4.3 Optimization Results                                                                                                                 | 1 |

|---|-----|--------------------------------------------------------------------------------------------------------------------------------------------|---|

|   | 2.5 | Allocation of Optimal Switching Angles                                                                                                     | 3 |

|   | 2.6 | SOP of Cascaded 7L MLC                                                                                                                     | 4 |

|   |     | 2.6.1 Circuit Topology and Operation                                                                                                       | 4 |

|   |     | 2.6.2 Implementation of SOP technique                                                                                                      | 3 |

|   |     | 2.6.3 Experimental results                                                                                                                 | 2 |

|   | 2.7 | SOP of Cascaded 9L MLC                                                                                                                     | 2 |

|   |     | 2.7.1 Circuit topology and Operation                                                                                                       | 3 |

|   |     | 2.7.2 Implementation of SOP Technique                                                                                                      | 3 |

|   |     | 2.7.3 Experimental Results                                                                                                                 | 1 |

|   |     | 2.7.4 Performance Comparison                                                                                                               | 3 |

|   | 2.8 | Summary and Conclusions                                                                                                                    | 4 |

| 3 | Mo  | dified Generalized SOP Technique 83                                                                                                        | 5 |

|   | 3.1 | Introduction                                                                                                                               | 5 |

|   | 3.2 | Modified Generalized SOP                                                                                                                   | 7 |

|   |     | 3.2.1 New method for estimation of $N$                                                                                                     | 7 |

|   |     | 3.2.2 Optimization Results                                                                                                                 | ) |

|   | 3.3 | Experimental Results for 7L MLC                                                                                                            | 2 |

|   | 3.4 | Experimental Results for 9L MLC                                                                                                            | 2 |

|   | 3.5 | Summary and Conclusions                                                                                                                    | 5 |

| 4 | Mo  | dified SOP Technique for MMC Topology 114                                                                                                  | 1 |

|   | 4.1 | Introduction $\ldots \ldots 11^4$ | 4 |

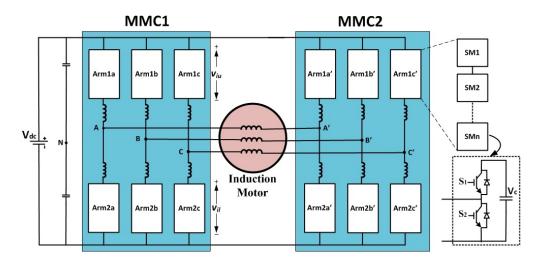

|   | 4.2 | Circuit Topology and Operation                                                                                                             | 5 |

|   | 4.3 | Modified SOP Technique                                                                                                                     | 3 |

|   |     | 4.3.1 Calculation of $N$                                                                                                                   | 7 |

|   |     | 4.3.2 Optimization of switching angles                                                                                                     | 9 |

|   |     | 4.3.3 Allocation of Optimal Switching Angles                                                                                               | ) |

|   | 4.4 | Experimental results                                                                                                                       | 2 |

|   | 4.5 | Summary and Conclusions                                                                                                                    | 7 |

| 5 |     | anced SOP Technique for Dual Inverter Based MLC<br>ologies 128                                                                             | 3 |

|   | 5.1 | Introduction                                                                                                                               | 3 |

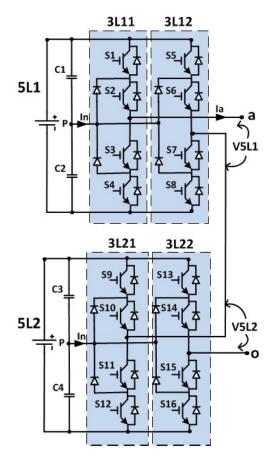

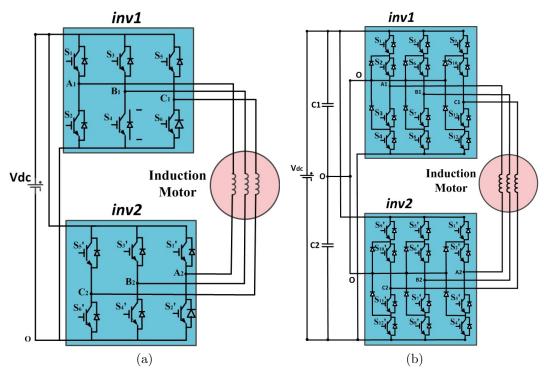

|                      | 5.2   | Circuit topologies and Operation             |

|----------------------|-------|----------------------------------------------|

|                      | 5.3   | Enhanced SOP technique                       |

|                      |       | 5.3.1 Computation of pulse number $N$        |

|                      |       | 5.3.2 Optimization of Switching Angles       |

|                      |       | 5.3.3 Allocation of Optimal Switching Angles |

|                      | 5.4   | Experimental results                         |

|                      |       | 5.4.1 D2L Inverter                           |

|                      |       | 5.4.2 D3L Inverter                           |

|                      |       | 5.4.3 Dual 3L-MMC                            |

|                      | 5.5   | Summary and Conclusions                      |

| 6                    | Con   | clusions and Future Work 155                 |

|                      | 6.1   | Summary and Conclusions                      |

|                      | 6.2   | Summary of thesis contributions              |

|                      | 6.3   | Scope of Future Work                         |

| Bil                  | oliog | raphy 161                                    |

| $\operatorname{Lis}$ | t of  | Publications 184                             |

## Summary

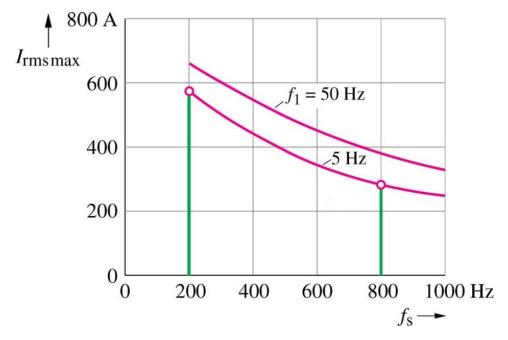

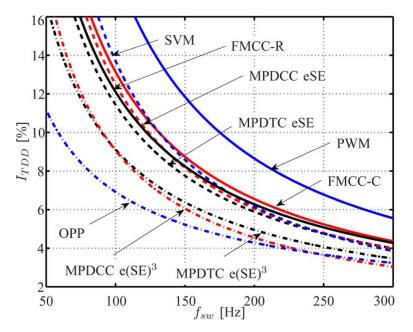

Low device switching frequency modulation of multilevel inverters (MLIs) for medium voltage drives is essential to increase semiconductor device utilization, minimize cooling requirements and achieve higher overall system efficiency. However, there exists a trade-off between device switching frequency and harmonic distortion of machine stator currents. Therefore, classical modulation techniques such as sinusoidal pulsewidth modulation and space vector modulation techniques utilize higher device switching frequency (around 1 kHz) to generate good quality of machine stator currents. Based on the literature survey of several low device switching frequency modulation techniques, it has been identified that synchronous optimal pulsewidth modulation (SOP) is an effective and emerging modulation technique to achieve better quality of machine stator currents.

Till now, SOP has been demonstrated for classical three-level and fivelevel MLIs. On the other hand, the present trend in MV high power drives is to use MLIs with higher number of voltage levels to achieve better quality of output voltage waveforms. Also, several new topologies have been proposed as an alternative to classical MLI topologies and some of them found industrial relevance as well. Therefore, there is a need to analyze and propose modifications to the state-of-the-art SOP technique in order to modulate MLIs with any number of voltage levels and also emerging MLI topologies.

One of the main goal of the thesis is to develop systematic analysis to implement state-of-the-art SOP technique for MLIs with any number of voltage levels. The developed analysis has been utilized to modulate cascaded seven-level and nine-level MLIs with peak device switching frequency limited to rated fundamental frequency (50 Hz). However, it has been noticed that power semiconductor devices operate at unequal device switching frequency and peak device switching frequency is not limited to desired value. Subsequently, modified SOP technique has been proposed to overcome these issues. The proposed technique has been utilized to modulate seven or higher-level MLIs with peak device switching frequency set at rated fundamental frequency (50 Hz).

Also, the thesis has explored the feasibility of implementing SOP technique for one of the emerging topology known as modular multilevel converter (MMC). One of the main challenges for modulation of MMC is to achieve balanced floating capacitor voltages. Based on the study, a systematic algorithm has been developed to implement SOP for MMC topology. The proposed technique has been demonstrated for five-level MMC with peak device switching frequency set at 2000 Hz.

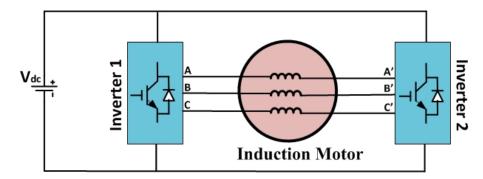

In addition, the thesis has investigated the issue of common-mode currents in machine stator windings for the dual inverter based MLI fed openend stator winding induction motor drives. An enhanced SOP technique has been proposed to achieve high quality stator currents with elimination of common-mode currents, while operating power semiconductor devices at few hundred Hertz. Finally, dual nL-MMC topology has been proposed for open-end stator winding induction motor drives, which can be operated from a single dc source and generates any number of voltage levels. The proposed technique has been demonstrated experimentally with low power prototypes of dual two-level, dual three-level and dual three-level MMC topologies.

# List of Tables

| <ol> <li>Specifications of commercialized higher level MLCs</li> <li>Number of structures for 3L, 5L, 7L and 9L waveforms</li> <li>Structures of 3L, 5L, 7L and 9L waveforms with N = 5</li> <li>Switching states and synthesized output voltage levels of cascaded 7L MLC</li></ol> | 26<br>38<br>38 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| <ul> <li>2.2 Structures of 3L, 5L, 7L and 9L waveforms with N = 5</li> <li>2.3 Switching states and synthesized output voltage levels of cascaded 7L MLC</li></ul>                                                                                                                   |                |

| 2.3 Switching states and synthesized output voltage levels of cas-<br>caded 7L MLC                                                                                                                                                                                                   | 38             |

| caded 7L MLC                                                                                                                                                                                                                                                                         |                |

|                                                                                                                                                                                                                                                                                      |                |

| 2.4 SOP of 7L-MLC at $f = -f_{in}$ : Estimated values of $N_{-r}$                                                                                                                                                                                                                    | 46             |

| 2.1 Solution (1) will at $J_{s,max} - J_{1R}$ . Estimated values of $N_{7L}$                                                                                                                                                                                                         |                |

| and $f_s$ for a given $m$                                                                                                                                                                                                                                                            | 46             |

| 2.5 $$ Distribution of switching transitions for cascaded 7L MLC $$ .                                                                                                                                                                                                                | 48             |

| 2.6 Allocation of optimal switching angles for 7L MLC. (a) $(m=0.92)$                                                                                                                                                                                                                | 225,           |

| N=3) (b)( $m=0.4667$ , $N=6$ ) (c) ( $m=0.3412$ , $N=8$ )                                                                                                                                                                                                                            | 51             |

| 2.7 Allocation of optimal switching angles of 7L MLC for $(m=0.466)$                                                                                                                                                                                                                 | 37,            |

| N=6). (a) Combination 1 (b) Combination 2                                                                                                                                                                                                                                            | 52             |

| 2.8 Parameters of major components in 7L MLC prototype                                                                                                                                                                                                                               | 53             |

| 2.9 Estimated values of N and $f_s$ for 7L MLC: (a) ( $m=0.9225$ ,                                                                                                                                                                                                                   |                |

| N=3) (b) ( $m=0.4667$ , $N=6$ ) (c) ( $m=0.3412$ , $N=8$ )                                                                                                                                                                                                                           | 53             |

| 2.10 Operation of cascade 9L MLC                                                                                                                                                                                                                                                     | 63             |

| 2.11 SOP of 9L MLC at $f_{s,max} = f_{1R}$ : Estimated values of $N_{9L}$                                                                                                                                                                                                            |                |

| and $f_s$ for a given $m$                                                                                                                                                                                                                                                            | 64             |

| 2.12 Distribution of switching commutations for cascaded 9L MLC                                                                                                                                                                                                                      | C 65           |

| 2.13 Analysis of dc-link capacitor voltages of 5L-HNPC                                                                                                                                                                                                                               | 67             |

| 2.14 Allocation of optimal switching angles for 9L MLC. (a)( $m=0.92$                                                                                                                                                                                                                | 216,           |

| N=4) (b)( $m=0.5804$ , $N=6$ ) (c)( $m=0.4706$ , $N=8$ )                                                                                                                                                                                                                             | 70             |

| 2.15 List of components and their rated parameters for 9L MLC .                                                                                                                                                                                                                      | 72             |

| 2.16 Performance comparison between proposed SOP and level-                                                                                                                                                                                                                          |                |

| 2.10 renormance compansion between proposed SOF and level-                                                                                                                                                                                                                           |                |

| 3.1 | $N_{3L}$ and $f_s$ for a given $m$ to achieve $f_{s,max} = f_{1R}$ 88                                                                                       |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.2 | $N_{7L}$ and $f_s$ for a given $m$ to achieve $f_{s,max} = f_{1R}$ 88                                                                                       |

| 3.3 | $N_{9L}$ and $f_s$ for a given $m$ to achieve $f_{s,max} = f_{1R}$ 88                                                                                       |

| 3.4 | Optimal switching angles and distribution of $N$ for 7L-MLC.                                                                                                |

|     | (a) $(m=0.9294, N=3)$ (b) $(m=0.6824, N=3)$ (c) $(m=0.4824, N=3)$                                                                                           |

|     | N=6 (d) ( $m=0.3294$ , $N=9$ )                                                                                                                              |

| 3.5 | Optimal switching angles and division of $N$ for 9L-MLC. (a)                                                                                                |

|     | (m=0.9176, N=4) (b) $(m=0.7020, N=4)$ (c) $(m=0.4980, N=4)$                                                                                                 |

|     | N=8) (d) ( $m=0.3333$ , $N=12$ )                                                                                                                            |

| 4.1 | Synthesis of output voltage levels of 5L-MMC                                                                                                                |

| 4.2 | SOP of 5L-MMC at $f_{s,max} = 200$ Hz: Computed N and $f_s$                                                                                                 |

|     | for a given $m$                                                                                                                                             |

| 4.3 | List of components and their parameters in 5L-MMC exper-                                                                                                    |

|     | imental setup                                                                                                                                               |

| 5.1 | Synthesis of output voltage levels in phase A of Dual 3L-MMC131                                                                                             |

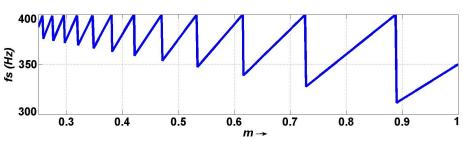

| 5.2 | SOP of D2L inverter at $f_{s,max} = 400$ Hz : Computed pulse                                                                                                |

|     | number and corresponding $f_s$ for a given value of $m$ 135                                                                                                 |

| 5.3 | SOP of D3L inverter at $f_{s,max} = 400$ Hz : Computed pulse                                                                                                |

|     | number and corresponding $f_s$ for a given $m \dots $ |

| 5.4 | SOP of 3L-MMC with $f_{s,max} = 400$ Hz : Estimated value of                                                                                                |

|     | $N_{3LM}$ and corresponding $f_s$ for a given $m \ldots \ldots \ldots \ldots \ldots 138$                                                                    |

| 5.5 | List of components and their parameters in the experimental                                                                                                 |

|     |                                                                                                                                                             |

|     | set-up of D2L and D3L inverters                                                                                                                             |

| 5.6 | set-up of D2L and D3L inverters                                                                                                                             |

# List of Figures

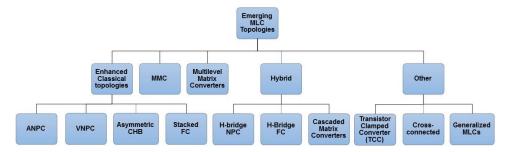

| 1.1  | Emerging MLC topologies                                                                  | 2  |

|------|------------------------------------------------------------------------------------------|----|

| 1.2  | Maximum device rms current versus $f_s$ for EUPEC 6.5-kV                                 |    |

|      | 600-A IGBT module. (Courtesy of J. Holtz and X. Qi) $\ . \ .$ .                          | 4  |

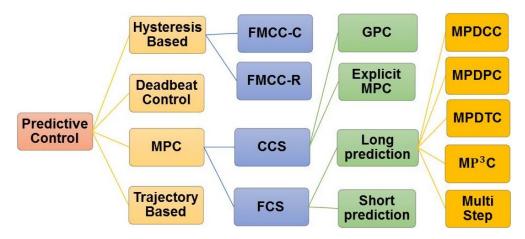

| 1.3  | Classification of predictive control techniques                                          | 7  |

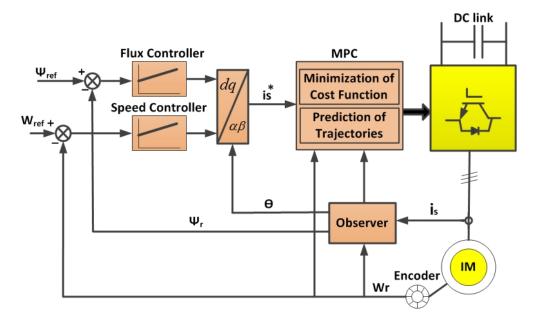

| 1.4  | MPDCC control scheme                                                                     | 10 |

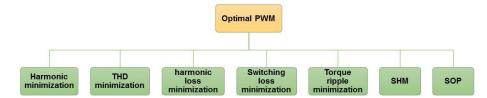

| 1.5  | Classification of optimal PWM techniques                                                 | 15 |

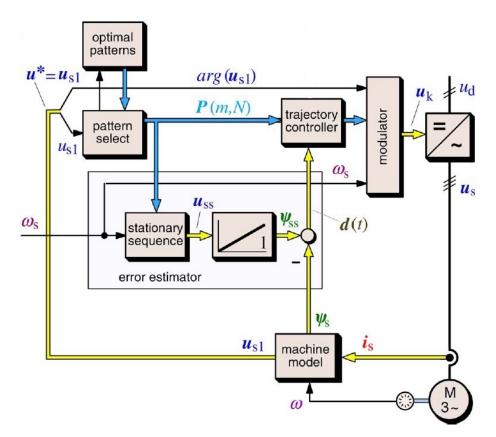

| 1.6  | Signal flow diagram of stator flux trajectory control system [1]                         | 17 |

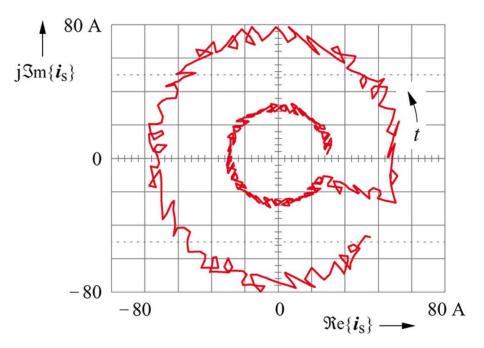

| 1.7  | Trajectory of the stator current vector with a step transition                           |    |

|      | from no-load operation to nominal load $[1]$                                             | 18 |

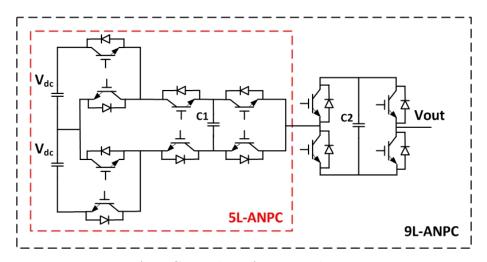

| 1.8  | ANPC topology for 5L and 9L operation                                                    | 20 |

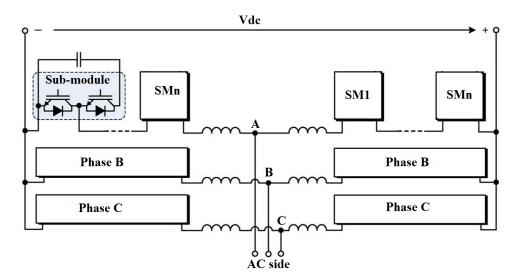

| 1.9  | MMC topology                                                                             | 21 |

| 1.10 | Dual inverter based MLC topology for open-end stator wind-                               |    |

|      | ing induction motor drive $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 23 |

| 1.11 | Performance comparison between SPWM, SVM, MPC and                                        |    |

|      | SOP techniques : current TDD versus $f_s$ (Note: SOP is                                  |    |

|      | referred as OPP in the figure). (Courtesy of J. Scoltock, T.                             |    |

|      | Geyer, and U. Madawala)                                                                  | 25 |

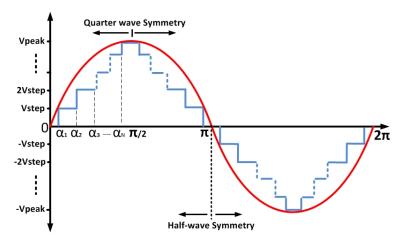

| 2.1  | A typical $nL$ phase output voltage waveform                                             | 32 |

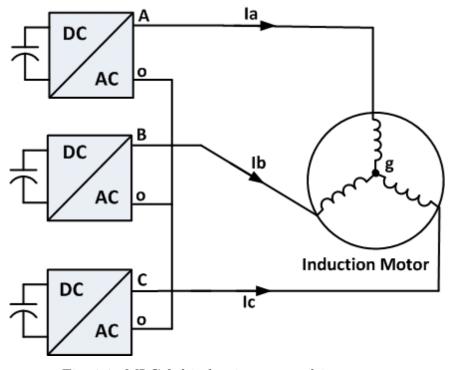

| 2.2  | MLC fed induction motor drive system                                                     | 34 |

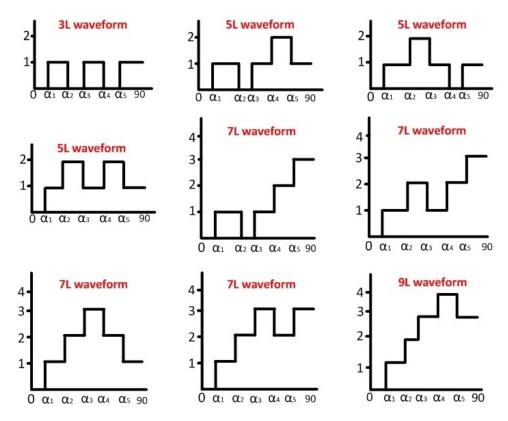

| 2.3  | Structures of 3L, 5L, 7L and 9L waveforms with $N=5$                                     | 37 |

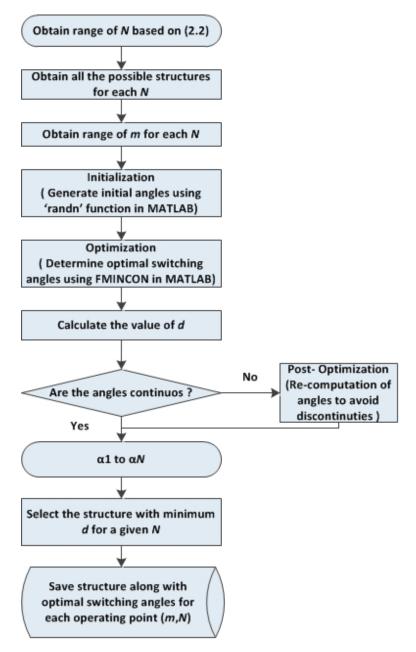

| 2.4  | Flowchart of optimization algorithm                                                      | 39 |

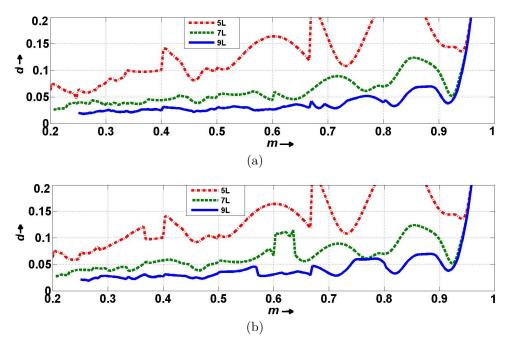

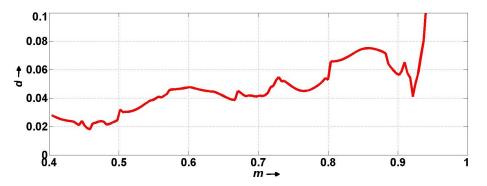

| 2.5  | Performance of SOP in terms of $d$ for 5L, 7L and 9L wave-                               |    |

|      | forms with $f_{s,max} = f_{1R}$ . (a) Before post-optimization (b) Af-                   |    |

|      | ter post-optimization                                                                    | 42 |

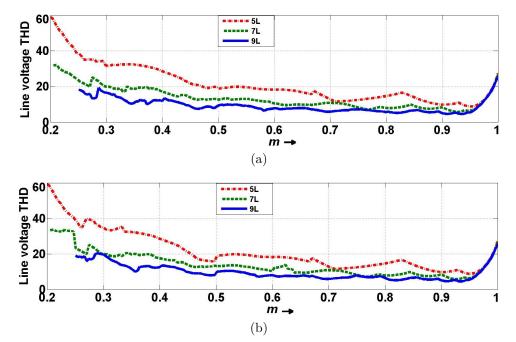

| 2.6  | Performance of SOP in terms of line voltage THD for 5L,                                           |    |

|------|---------------------------------------------------------------------------------------------------|----|

|      | 7L and 9L waveforms with $f_{s,max}=f_{1R}$ . (a) Before post-                                    |    |

|      | optimization (b) After post-optimization                                                          | 43 |

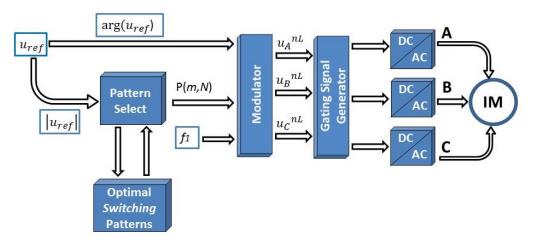

| 2.7  | Signal flow graph of SOP technique for an $n$ L-MLC                                               | 43 |

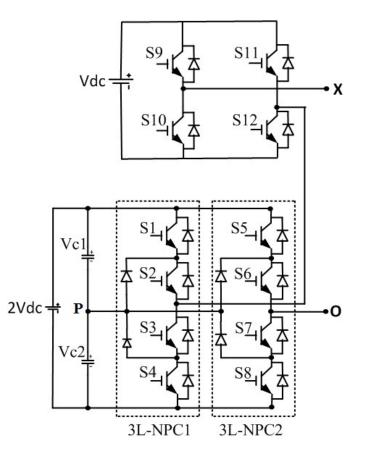

| 2.8  | Cascaded 7L inverter topology                                                                     | 45 |

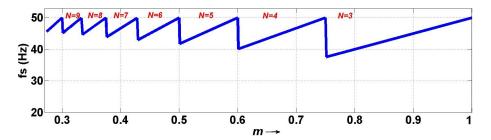

| 2.9  | SOP of 7L-MLC at $f_{s,max} = f_{1R}$ : Estimated values of N and                                 |    |

|      | $f_s$ for a given $m$                                                                             | 47 |

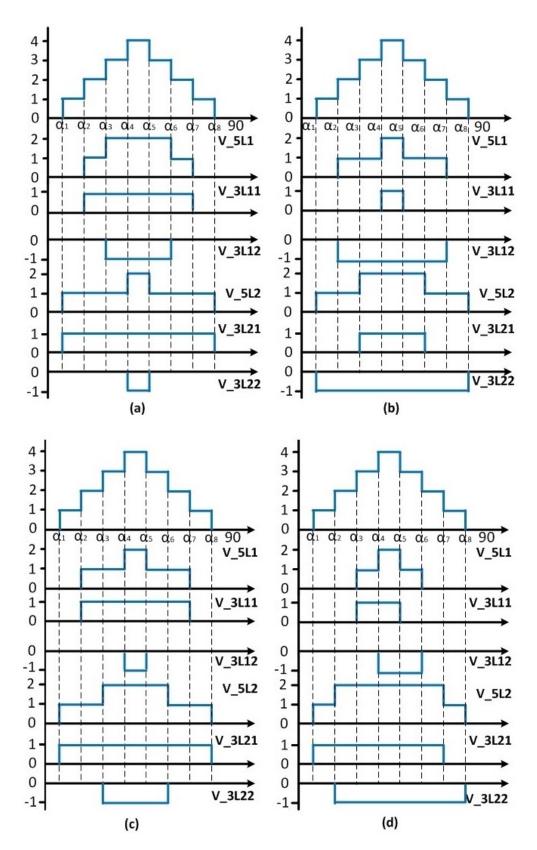

| 2.10 | Operation of 5L-HNPC inverter for different switching patterns $% \left( \frac{1}{2} \right) = 0$ | 50 |

| 2.11 | Experimental setup of 7L MLC                                                                      | 52 |

| 2.12 | Gating signals of power semiconductor devices for $(m=0.4667, m=0.4667)$                          |    |

|      | $N{=}6$ ). (a) 3L-NPC1 (b) 3L-NPC2 (c) H-Bridge $\ldots$                                          | 54 |

| 2.13 | Swapping technique for operating point ( $m=0.3412$ , $N=8$ ).                                    |    |

|      | (a) Gating signals of S1, S5 and S9 (b) Output voltage of                                         |    |

|      | 3L-NPC1, 3L-NPC2, H-Bridge and 7L-MLC                                                             | 55 |

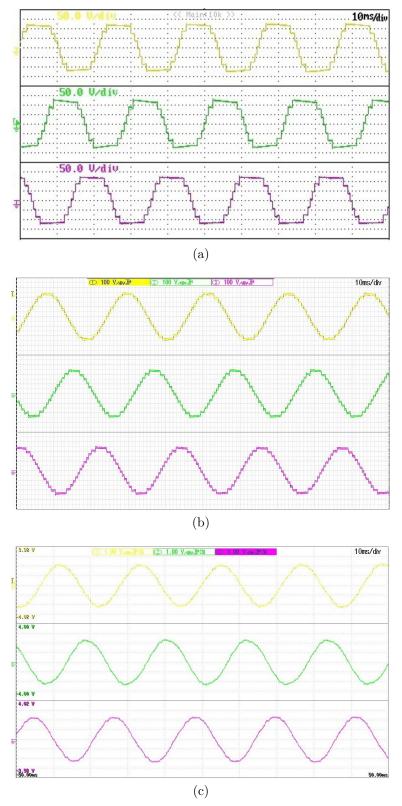

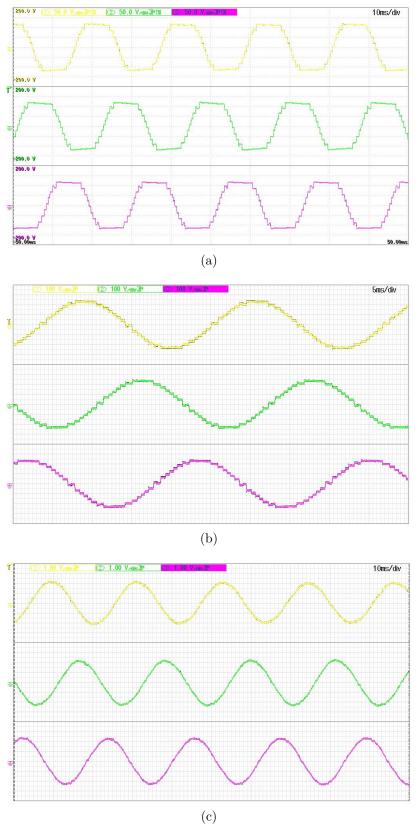

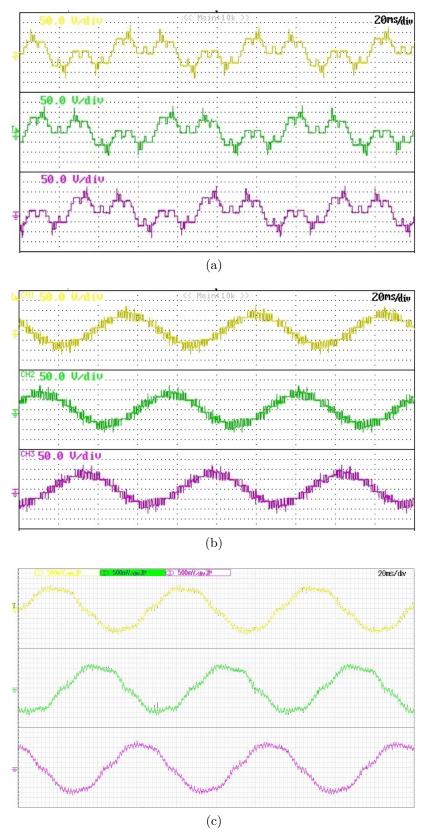

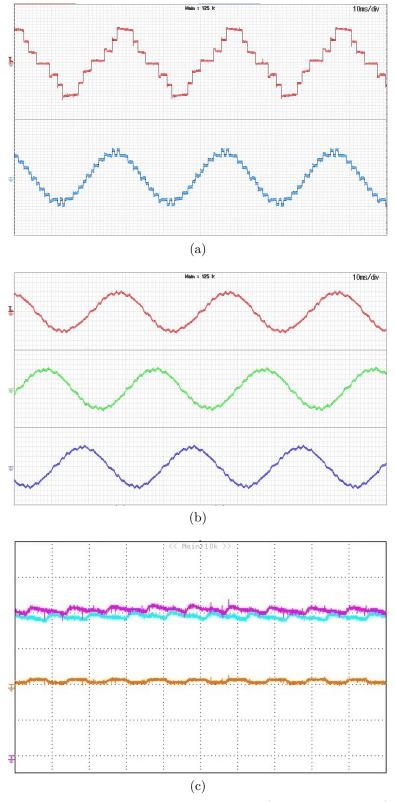

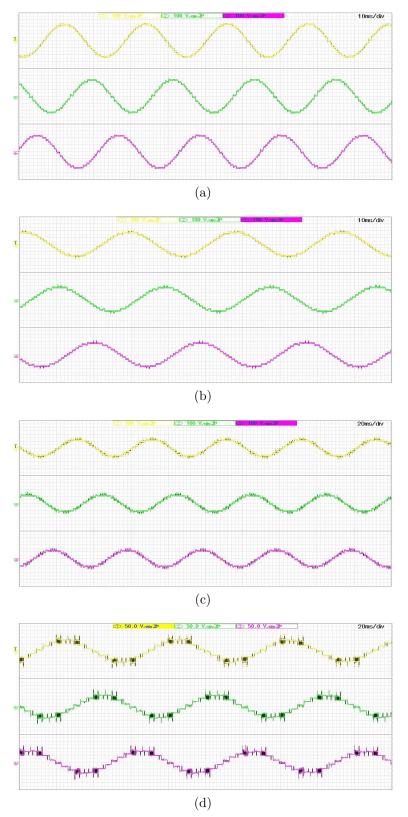

| 2.14 | Experimental results for $(m=0.9225, N=3)$ . X-axis:10 ms/div                                     |    |

|      | (a) Phase voltages of 7L inverter (Y-axis:50 V/div) (b) In-                                       |    |

|      | put line voltages of induction motor (Y-axis:100 V/div) (c) $$                                    |    |

|      | Stator currents of induction motor (Y-axis:1 A/div)                                               | 57 |

| 2.15 | Experimental results for ( $m=0.4667$ , $N=6$ ). X-axis:10 ms/div                                 |    |

|      | (a) Phase voltages of 7L inverter (Y-axis:50 V/div) (b) In-                                       |    |

|      | put line voltages of induction motor (Y-axis:50 V/div) (c) $$                                     |    |

|      | Stator currents of induction motor (Y-axis:0.5 A/div)                                             | 58 |

| 2.16 | Experimental results for $(m=0.3412, N=8)$ . (a) Phase volt-                                      |    |

|      | ages of 7L inverter (X-axis:10 ms/div, Y-axis:50 V/div) (b)                                       |    |

|      | Input line voltages of induction motor (X-axis:20 ms/div,                                         |    |

|      | Y-axis:50 V/div) (c) Stator currents of induction motor (X-                                       |    |

|      | axis:20 ms/div, Y-axis:0.5 A/div)                                                                 | 59 |

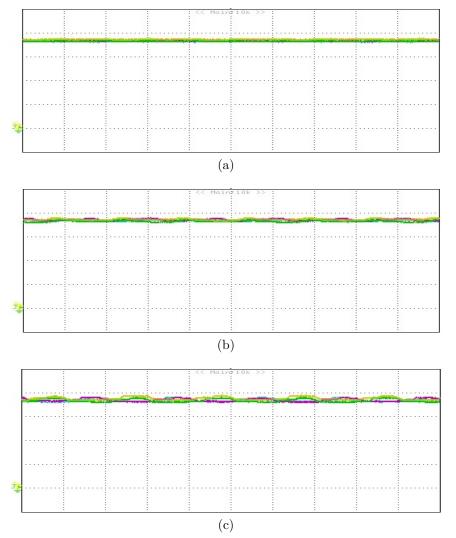

| 2.17 | Dc-link voltages of 5L-HNPC inverter. X-axis:10 ms/div, Y-                                        |    |

|      | axis:10 V/div. (a) ( $m=0.9225$ , $N=3$ ) (b) ( $m=0.4667$ , $N=6$ )                              |    |

|      | (c) $(m=0.3412, N=8)$                                                                             | 60 |

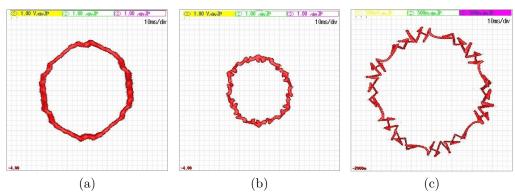

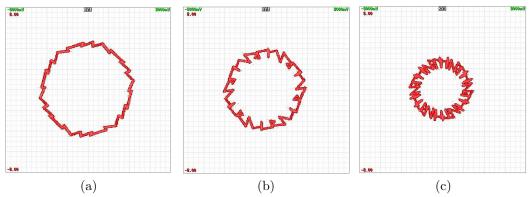

| 2.18 | Space vector trajectory of machine stator currents. X,Y-                        |    |

|------|---------------------------------------------------------------------------------|----|

|      | axes:1 A/div. (a) ( $m$ =0.9225, $N$ =3) (b) ( $m$ =0.4667, $N$ =6)             |    |

|      | (c) $(m=0.3412, N=8)$                                                           | 60 |

| 2.19 | Harmonic spectrum of stator currents. (a) $(m=0.9225, N=3)$                     |    |

|      | (b) $(m=0.4667, N=6)$ (c) $(m=0.3412, N=8)$                                     | 61 |

| 2.20 | Cascade 9L MLC topology                                                         | 62 |

| 2.21 | SOP of 9L MLC at $f_{s,max} = f_{1R}$ : Estimated values of $N_{9L}$            |    |

|      | and $f_s$ for a given $m$                                                       | 64 |

| 2.22 | Different possible realizations of 9L waveform                                  | 68 |

| 2.23 | PCB of cascade 9L MLC for one of the three phases                               | 71 |

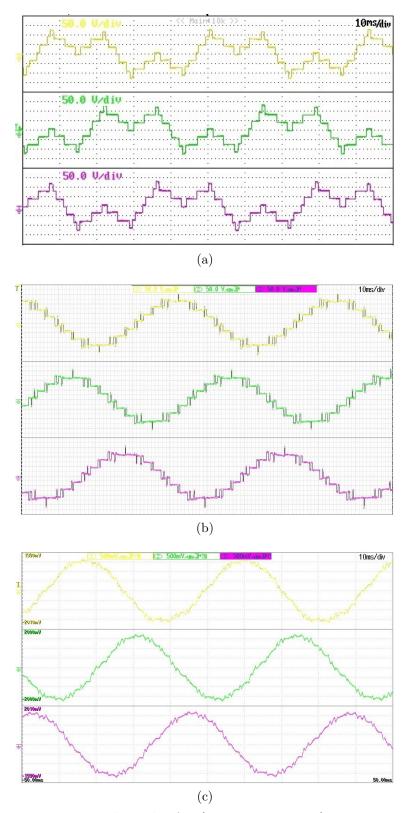

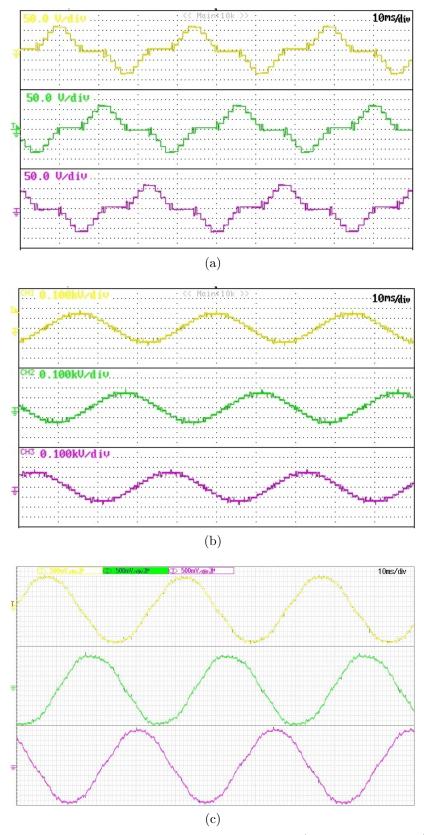

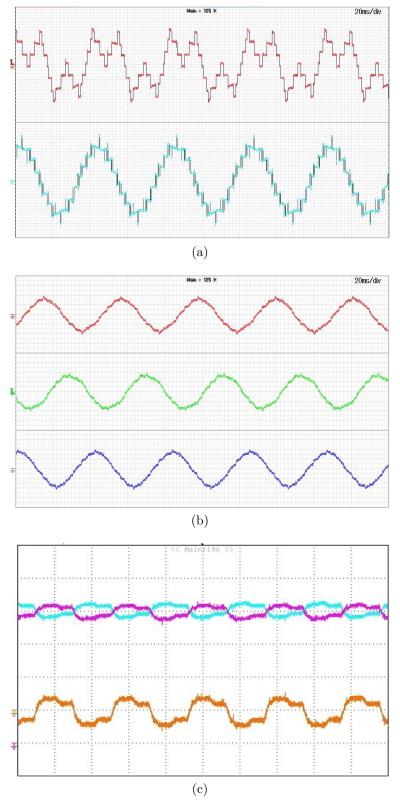

| 2.24 | Experimental results of 9L MLC for $(m=0.9216, N=4)$ . (a)                      |    |

|      | Output phase-voltage (b) Output line-voltage (c) Machine                        |    |

|      | stator currents                                                                 | 73 |

| 2.25 | Experimental results of 9L MLC for $(m=0.5804, N=6)$ . (a)                      |    |

|      | Output phase-voltage (b) Output line-voltage (c) Machine                        |    |

|      | stator currents                                                                 | 74 |

| 2.26 | Experimental results of 9L MLC for $(m=0.4706, N=8)$ . (a)                      |    |

|      | Output phase-voltage (b) Output line-voltage (c) Machine                        |    |

|      | stator currents                                                                 | 75 |

| 2.27 | Experimental results of 9L MLC for $(m=0.3059, N=13)$ . (a)                     |    |

|      | Output phase-voltage (b) Output line-voltage (c) Machine                        |    |

|      | stator currents                                                                 | 76 |

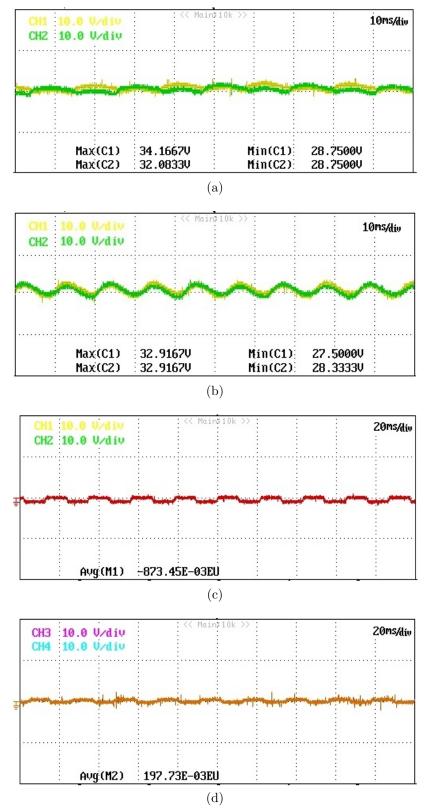

| 2.28 | Dc-link capacitor voltages and NPP error of 9L-MLC for                          |    |

|      | $(m=0.9216, N=4)$ . (a) $V_{C1}$ and $V_{C2}$ (b) $V_{C3}$ and $V_{C4}$ (c) NPP |    |

|      | error of top 5L-HNPC inverter (d) NPP error of bottom 5L-                       |    |

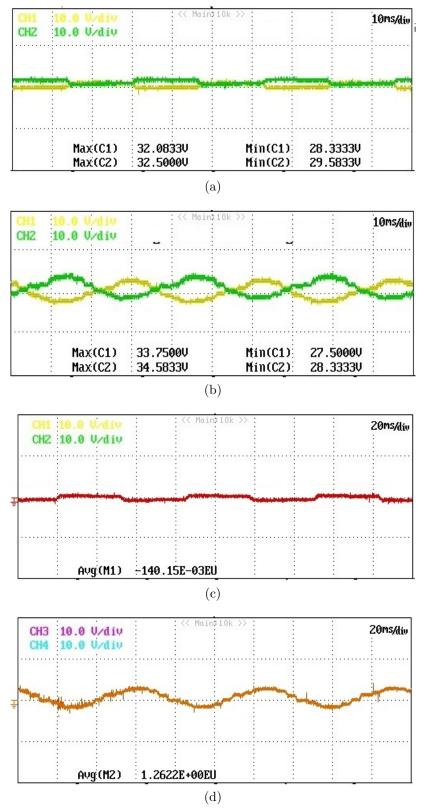

|      | HNPC inverter                                                                   | 77 |

| 2.29 | Dc-link capacitor voltages and NPP error of 9L-MLC for                          |    |

|      | $(m=0.5804, N=6)$ . (a) $V_{C1}$ and $V_{C2}$ (b) $V_{C3}$ and $V_{C4}$ (c)     |    |

|      | NPP error of top 5L-HNPC inverter (d) NPP error of bottom                       |    |

|      | 5L-HNPC inverter                                                                | 78 |

|      |                                                                                 |    |

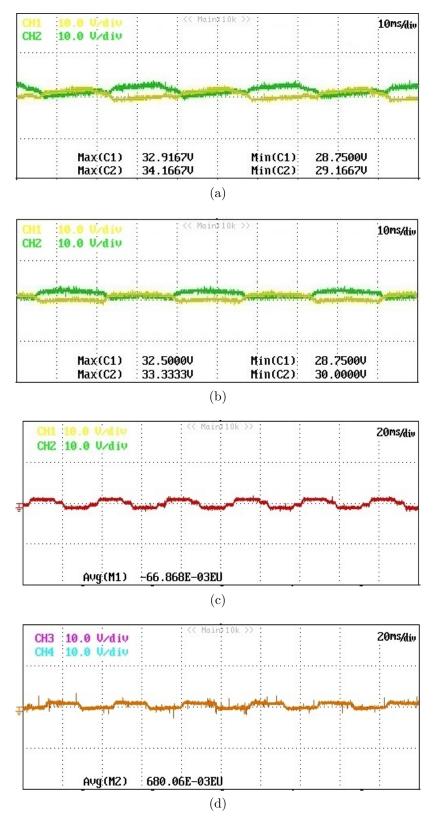

| 2.30       | Dc-link capacitor voltages and NPP error of 9L-MLC for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

|            | $(m=0.4706, N=8)$ . (a) $V_{C1}$ and $V_{C2}$ (b) $V_{C3}$ and $V_{C4}$ (c)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                |

|            | NPP error of top 5L-HNPC inverter (d) NPP error of bottom                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                |

|            | 5L-HNPC inverter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 79             |

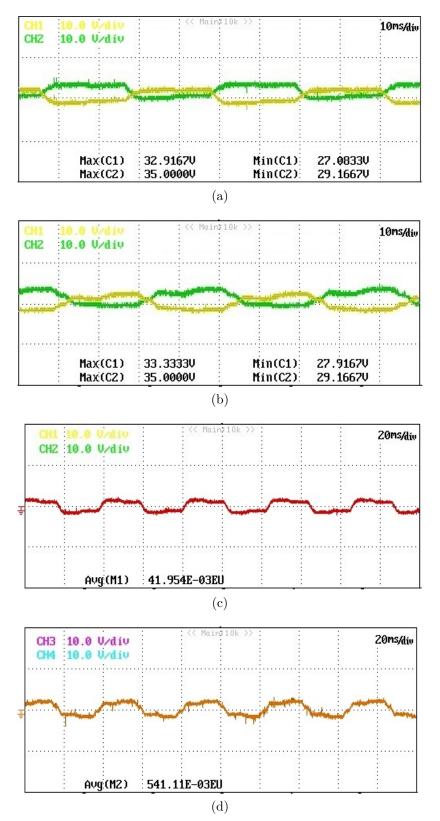

| 2.31       | Dc-link capacitor voltages and NPP error of 9L-MLC for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                |

|            | $(m=0.3059, N=13)$ . (a) $V_{C1}$ and $V_{C2}$ (b) $V_{C3}$ and $V_{C4}$ (c)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |

|            | NPP error of top 5L-HNPC inverter (d) NPP error of bottom                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                |

|            | 5L-HNPC inverter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 80             |

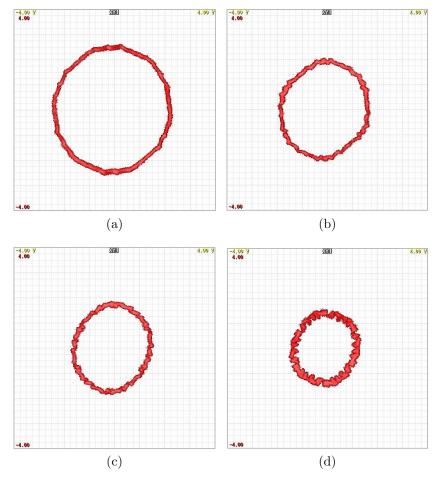

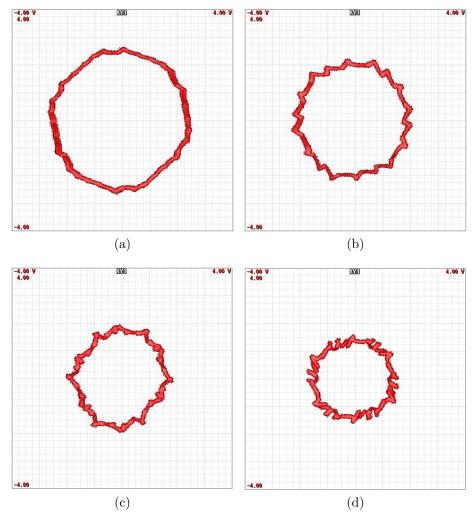

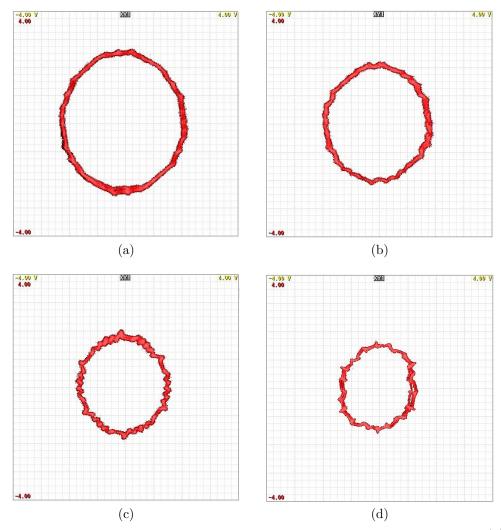

| 2.32       | Space vector trajectory of stator currents. (a) $(m=0.9216, N=4)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                |

|            | (b) $(m=0.5804, N=6)$ (c) $(m=0.4706, N=8)$ (c) $(m=0.3059, N=6)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                |

|            | N=13)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 81             |

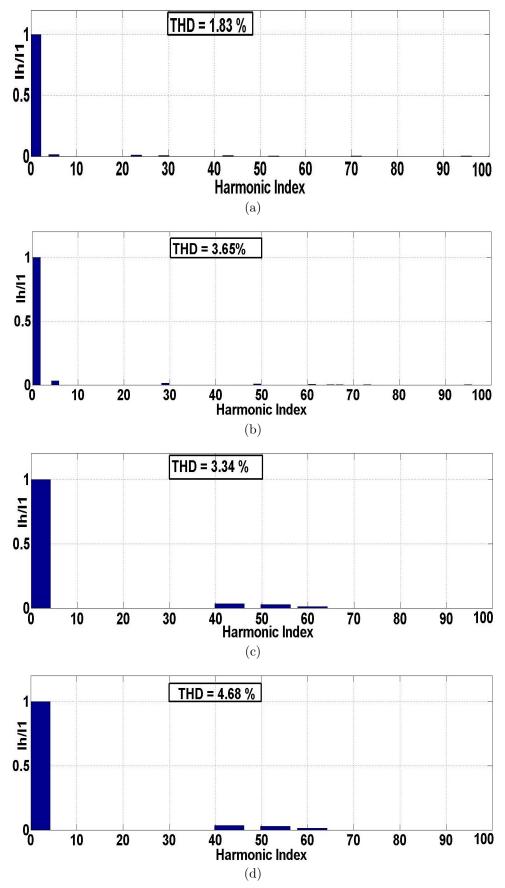

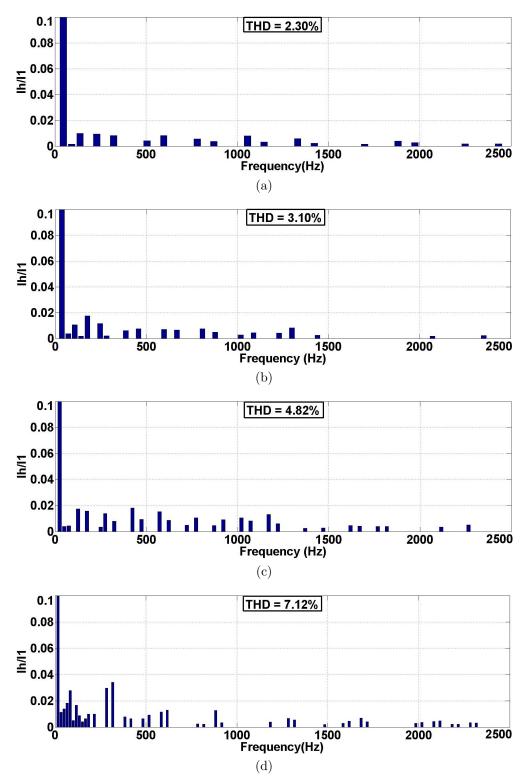

| 2.33       | FFT harmonic spectrum of machine stator current of phase A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 82             |

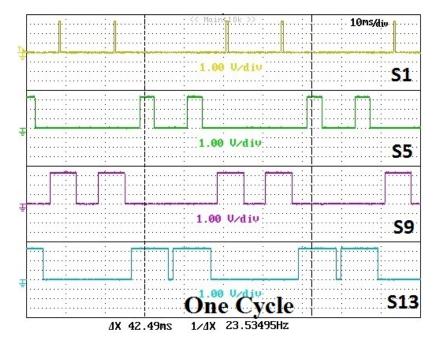

| 2.34       | Gating signals of semiconductor devices S1, S5, S9 and S13 $.$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 83             |

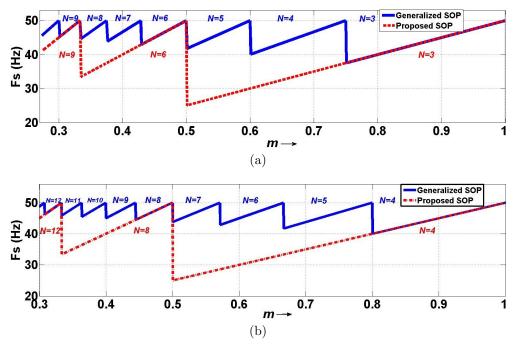

| 3.1        | Performance comparison between proposed and generalized                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                |

|            | SOP methods in terms of f with $f = -f \cdot (a)$ 7 MIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                |

|            | SOP methods in terms of $f_s$ with $f_{s,max} = f_{1R}$ : (a) 7L MLC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                |

|            | (b) 9L MLC $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 89             |

| 3.2        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 89             |

| 3.2        | (b) 9L MLC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 89             |

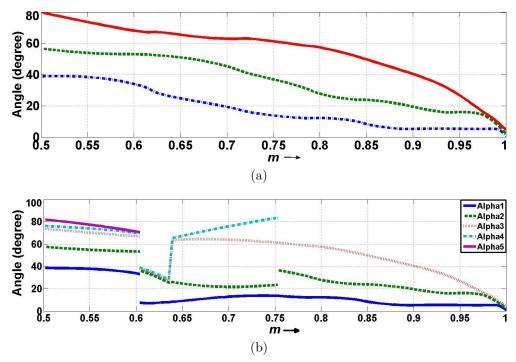

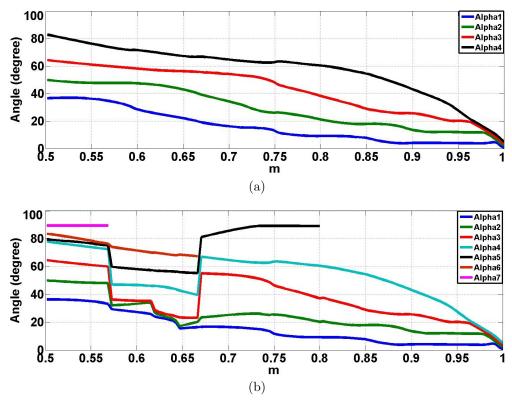

| 3.2        | (b) 9L MLC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 89<br>90       |

| 3.2<br>3.3 | (b) 9L MLC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                |

|            | (b) 9L MLC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 90             |

|            | (b) 9L MLC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 90             |

| 3.3        | (b) 9L MLC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 90<br>91       |

| 3.3        | (b) 9L MLC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 90<br>91       |

| 3.3<br>3.4 | (b) 9L MLC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 90<br>91       |

| 3.3<br>3.4 | (b) 9L MLC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 90<br>91       |

| 3.3<br>3.4 | (b) 9L MLC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 90<br>91       |

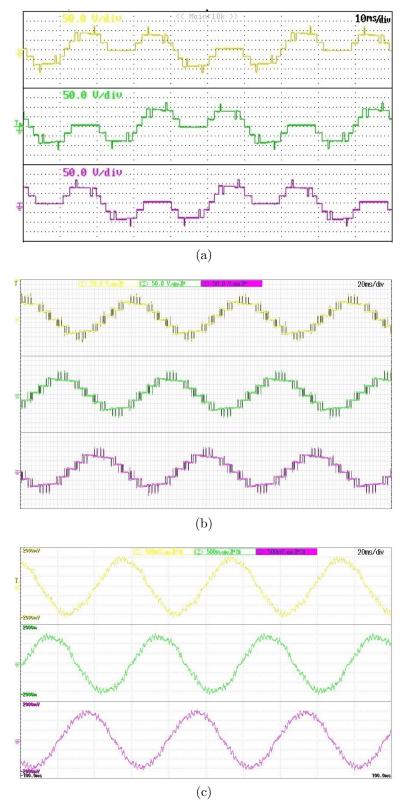

| 3.3<br>3.4 | (b) 9L MLC<br>Performance comparison between generalized and proposed<br>SOP techniques in terms of $d$ with $f_{s,max}=f_{1R}$ : (a) 7L MLC<br>(b) 9L MLC<br>Optimal switching angles of 7L MLC with $f_{s,max}=f_{1R}$ . (a)<br>proposed SOP method (b) generalized SOP method<br>Optimal switching angles of 9L MLC with $f_{s,max}=f_{1R}$ . (a)<br>proposed SOP method (b) generalized SOP method<br>Experimental results of 7L MLC for $(m=0.9294, N=3)$ . X-<br>axis: 10 ms/div. (a) phase and line voltages (Y-axis: 50<br>V/div, 100 V/div) (b) machine stator currents (Y-axis: 1 | 90<br>91<br>91 |

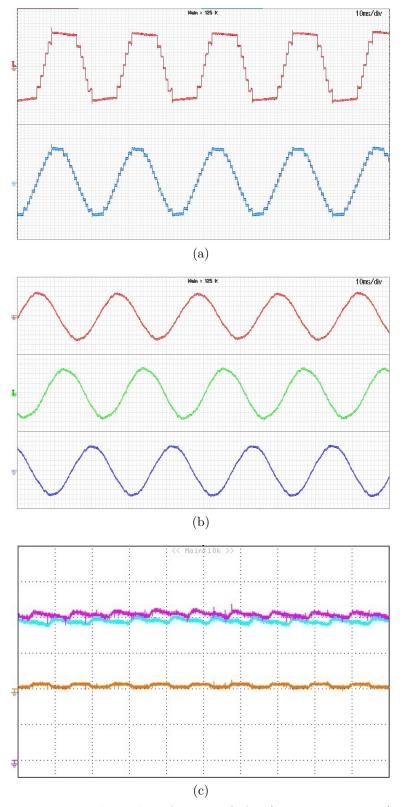

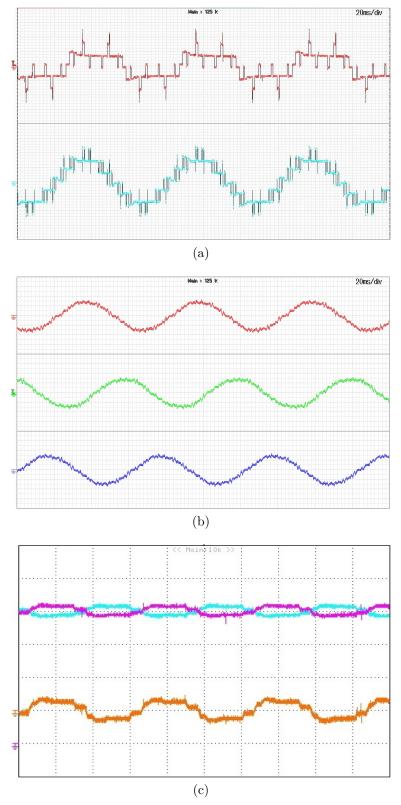

| 3.6  | Experimental results of 7L MLC for ( $m=0.6824$ , $N=3$ ). X-          |

|------|------------------------------------------------------------------------|

|      | axis: 10 ms/div. (a) phase and line voltages (Y-axis: 50               |

|      | V/div, 100 V/div) (b) machine stator currents (Y-axis: 1 $$            |

|      | A/div) (c) DC-link capacitor voltages and NPP error of 5L-             |

|      | HNPC inverter (X-axis:20 ms/div, Y-axis:10 V/div) 95                   |

| 3.7  | Experimental results of 7L MLC for ( $m=0.4824$ , $N=6$ ). X-          |

|      | axis: 10 ms/div. (a) phase and line voltages (Y-axis: 50               |

|      | V/div) (b) machine stator currents (Y-axis: $1 \text{ A/div}$ ) (c)    |

|      | DC-link capacitor voltages and NPP error of 5L-HNPC in-                |

|      | verter (X-axis:20 ms/div, Y-axis:10 V/div)                             |

| 3.8  | Experimental results of 7L MLC for ( $m=0.3294$ , $N=9$ ). X-          |

|      | axis: 10 ms/div. (a) phase and line voltages (Y-axis: $50$             |

|      | V/div) (b) machine stator currents (Y-axis: $1 \text{ A/div}$ ) (c)    |

|      | DC-link capacitor voltages and NPP error of 5L-HNPC in-                |

|      | verter (X-axis:20 ms/div, Y-axis:10 V/div)                             |

| 3.9  | Machine stator current space vector trajectories of 7L MLC $$          |

|      | (a) $(m=0.9294, N=3)$ (b) $(m=0.6824, N=3)$ (c) $(m=0.4824, N=3)$      |

|      | N=6 (d) ( $m=0.3294$ , $N=9$ )                                         |

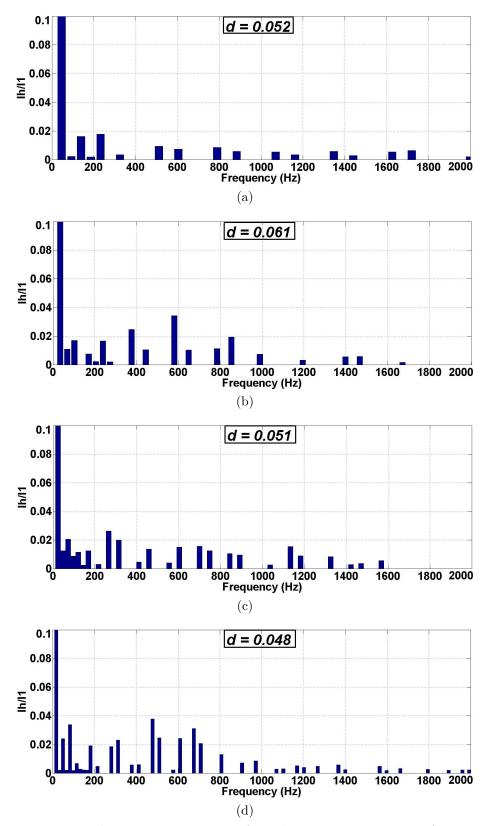

| 3.10 | FFT harmonic spectrum of machine stator currents of 7L                 |

|      | MLC (enlarged view to show dominant harmonics). (a)                    |

|      | (m=0.9294, N=3) (b) $(m=0.6824, N=3)$ (c) $(m=0.4824, N=3)$            |

|      | N=6 (d) ( $m=0.3294$ , $N=9$ )                                         |

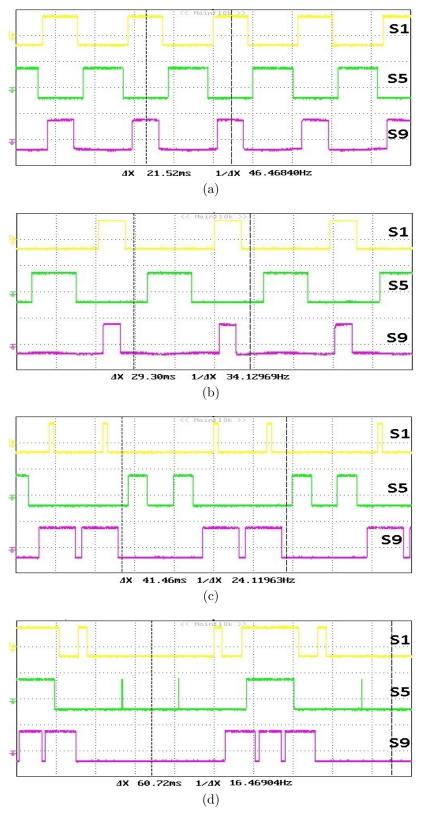

| 3.11 | Gating signals of semiconductor devices in 7L MLC. X-axis:             |

|      | 10 ms/div, Y-axis: 20 V/div (a)( $m$ =0.9294, $N$ =3)(b)( $m$ =0.6824, |

|      | N=3)(c)( $m=0.4824$ , $N=6$ )(d)( $m=0.3294$ , $N=9$ )                 |

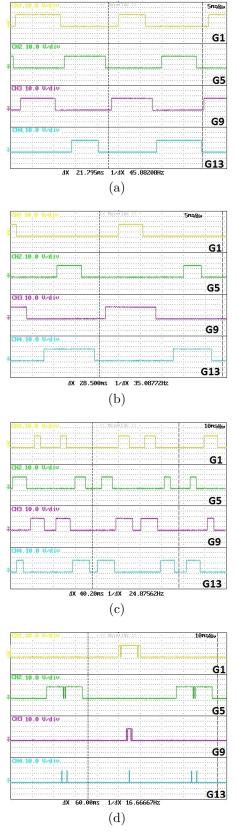

| 3.12 | Gating signals for IGBTs S1, S5, S9 and S13 in phase A of              |

|      | 9L MLC. (a) $(m=0.9176, N=4)$ (b) $(m=0.7020, N=4)$ (c)                |

|      | (m=0.4980, N=8) (d) $(m=0.3333, N=12)$                                 |

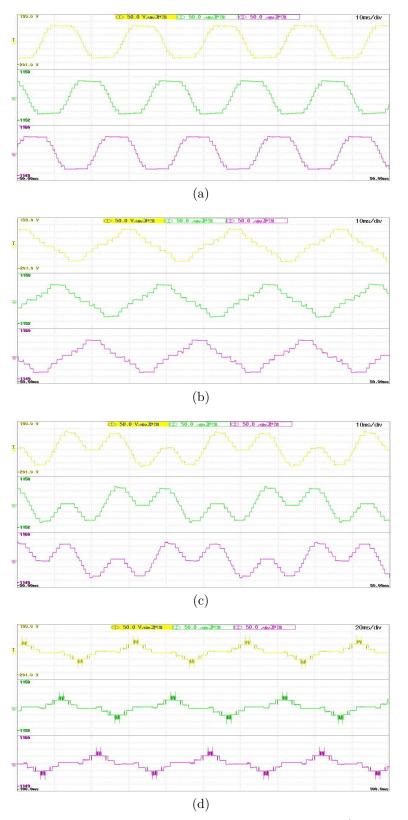

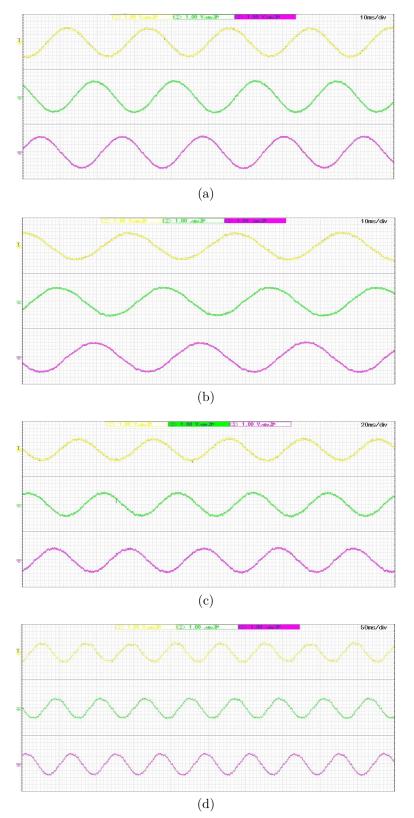

| 3.13 | Output phase-voltage of 9L MLC. X-axis:10 ms/div. Y-axis:              |

|      | 50 V/div. (a) ( $m$ =0.9176, $N$ =4) (b) ( $m$ =0.7020, $N$ =4) (c)    |

|      | (m=0.4980, N=8) (d) $(m=0.3333, N=12)$                                 |

|      |                                                                        |

| 3.14 | Output line-voltage of 9L MLC. (a) ( $m=0.9176$ , $N=4$ ) (X-                                                                                                     |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | axis:10 ms/div, Y-axis: 100 V/div) (b) ( $m$ =0.7020, $N$ =4)                                                                                                     |

|      | (X-axis:10 ms/div, Y-axis: 100 V/div)(c) ( $m=0.4980$ , $N=8$ )                                                                                                   |

|      | (X-axis:20 ms/div, Y-axis: $100 \text{ V/div}$ )(d) (m=0.3333, N=12)                                                                                              |

|      | (X-axis:20 ms/div, Y-axis: 50 V/div) $\dots \dots \dots$          |

| 3.15 | Machine stator currents. Y-axis: 1 A/div. (a) ( $m=0.9176$ ,                                                                                                      |

|      | $N{=}4$ ) (X-axis:10 ms/div) (b) ( $m{=}0.7020$ , $N{=}4$ ) (X-axis:10                                                                                            |

|      | ms/div)(c) (m=0.4980, N=8) (X-axis:20 ms/div)(d) (m=0.3333, ms/div)(d) (m=0.3333)                                                                                 |

|      | N=12) (X-axis:50 ms/div)                                                                                                                                          |

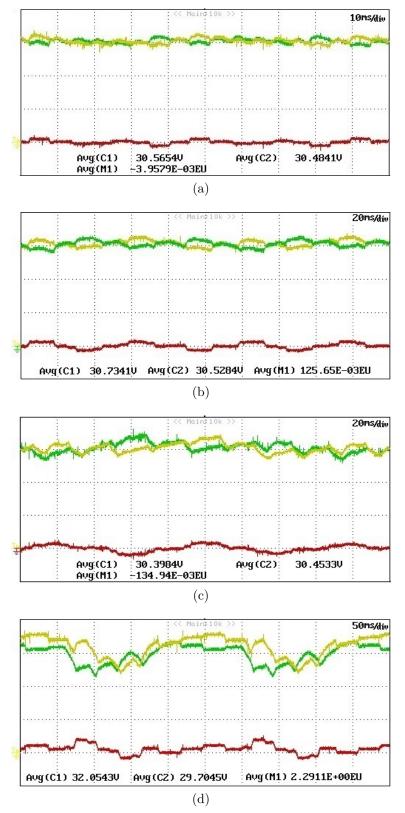

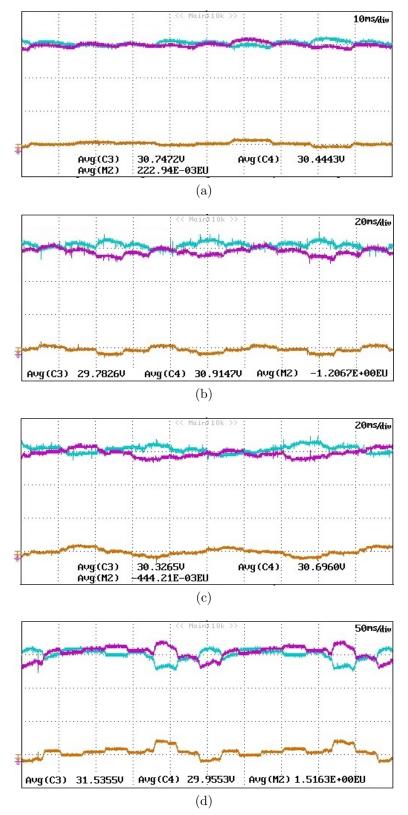

| 3.16 | Dc-link capacitor voltages and NPP error of 5L-HNPC1 in-                                                                                                          |

|      | verter (Vc1,Vc2). Y-axis: 10 V/div (a) ( $m$ =0.9176, $N$ =4)                                                                                                     |

|      | (b) $(m=0.7020, N=4)$ (c) $(m=0.4980, N=8)$ (d) $(m=0.3333, N=10)$                                                                                                |

|      | N=12)                                                                                                                                                             |

| 3.17 | Dc-link capacitor voltages and NPP error of 5L-HNPC2 in-                                                                                                          |

|      | verter (Vc3,Vc4).<br>Y-axis: 10 V/div. (a) ( $m=0.9176$ , $N=4$ )                                                                                                 |

|      | (b) $(m=0.7020, N=4)$ (c) $(m=0.4980, N=8)$ (d) $(m=0.3333, N=10)$                                                                                                |

|      | N=12)                                                                                                                                                             |

| 3.18 | Space vector trajectory of stator currents of 9L MLC. (a)                                                                                                         |

|      | (m=0.9176, N=4) (b) $(m=0.7020, N=4)$ (c) $(m=0.4980, N=4)$                                                                                                       |

|      | N=8) (d) ( $m=0.3333$ , $N=12$ )                                                                                                                                  |

| 3.19 | Harmonic spectrum of machine stator currents for 9L MLC $$                                                                                                        |

|      | (enlarged view for showing dominant harmonics and their                                                                                                           |

|      | magnitude). (a) $(m=0.9176, N=4)$ (b) $(m=0.7020, N=4)$                                                                                                           |

|      | (c) $(m=0.4980, N=8)$ (d) $(m=0.3333, N=12)$                                                                                                                      |

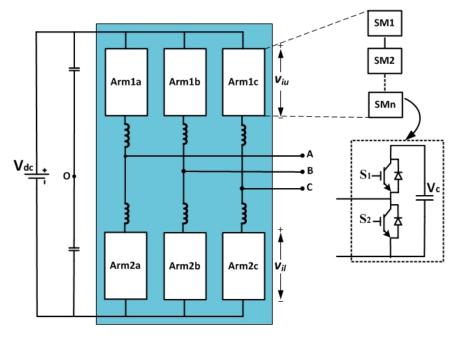

| 4.1  | MMC topology                                                                                                                                                      |

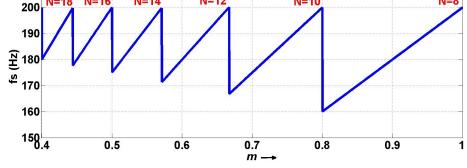

| 4.2  | SOP of 5L-MMC at $f_{s,max} = 200$ Hz: Computed N and $f_s$                                                                                                       |

|      | for a given $m$                                                                                                                                                   |

| 4.3  | Results of optimization for operating 5L-MMC at $f_{s,max} =$                                                                                                     |

|      | $200 \text{ Hz}: d \text{ versus } m \qquad \dots \qquad$ |

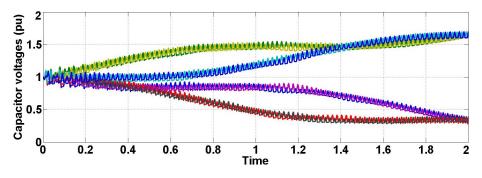

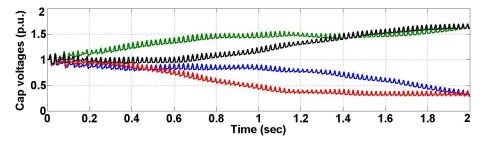

| 4.4  | Submodule capacitor voltages (p.u.) of one phase leg of 5L-                                                                                                       |

|      | MMC with pre-assigned switching angles for insertion/bypass                                                                                                       |

|      | of submodules                                                                                                                                                     |

|      |                                                                                                                                                                   |

| 4.5  | Prototype of 5L-MMC phase leg                                                          |

|------|----------------------------------------------------------------------------------------|

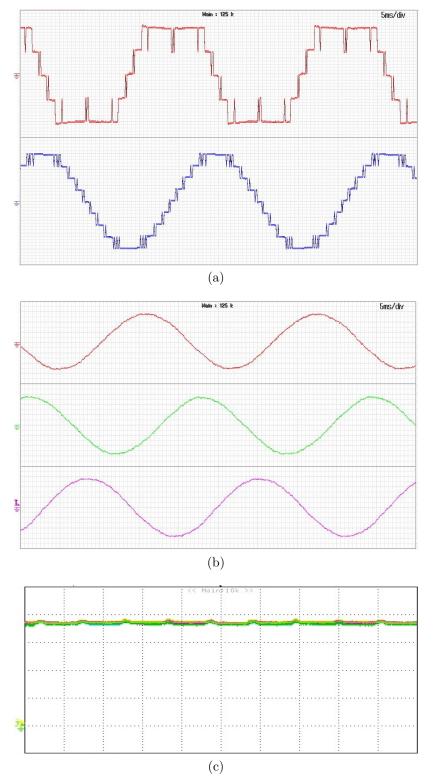

| 4.6  | Experimental results of 5L-MMC for $(m=0.9216, N=8)$ . X-                              |

|      | axis: 5 ms/div. (a) Output phase and line-to-line voltage                              |

|      | (Y-axis: 50 V/div, 100 V/div) (b) three-phase stator cur-                              |

|      | rents (Y-axis: 1 A/div). (c) submodule capacitor voltages                              |

|      | of upper arm of phase A (X-Axis: 20 ms/div, Y-axis: 20                                 |

|      | $V/{\rm div})$                                                                         |

| 4.7  | Experimental results of 5L-MMC for $(m=0.6667, N=12)$ .                                |

|      | X-axis: 10 ms/div. (a) Output phase and line-to-line volt-                             |

|      | age (Y-axis: 50 V/div, 100 V/div) (b) three-phase stator                               |

|      | currents (Y-axis: $1 \text{ A/div}$ ) (c) submodule capacitor voltages                 |

|      | of upper arm of phase A (X-Axis: 20 ms/div, Y-axis: 20                                 |

|      | V/div)                                                                                 |

| 4.8  | Experimental results of 5L-MMC for $(m=0.4431, N=18)$ . X-                             |

|      | axis: 20 ms/div. (a) Output phase and line-to-line voltage                             |

|      | (Y-axis: 50 V/div) (b) three-phase stator currents (Y-axis:                            |

|      | $1~\mathrm{A/div})(\mathrm{c})$ submodule capacitor voltages of upper arm of           |

|      | phase A (X-Axis: 20 ms/div, Y-axis: 20 V/div) $\ . \ . \ . \ . \ . \ . \ . \ . \ . \ $ |

| 4.9  | Space vector trajectories of machine stator currents. X,Y-                             |

|      | axis: 1 A/div (a) ( $m=0.9216$ , $N=8$ ). (b) ( $m=0.6667$ , $N=12$ ).                 |

|      | (c) $(m=0.4431, N=18)$                                                                 |

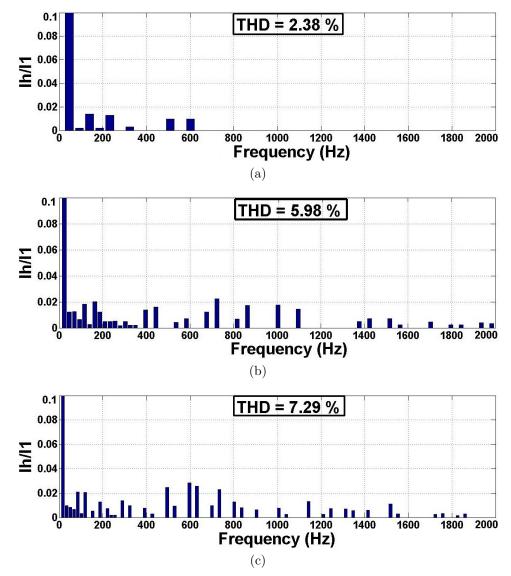

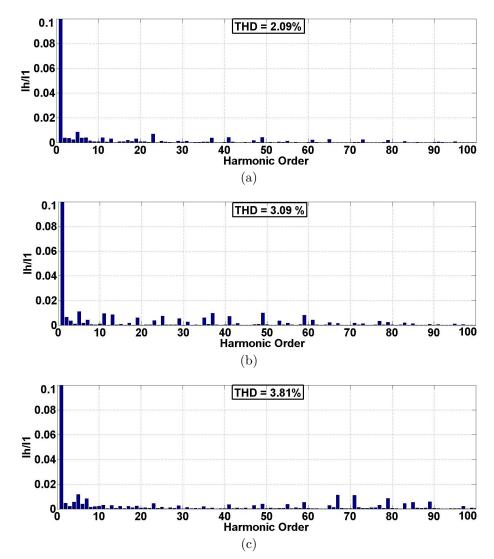

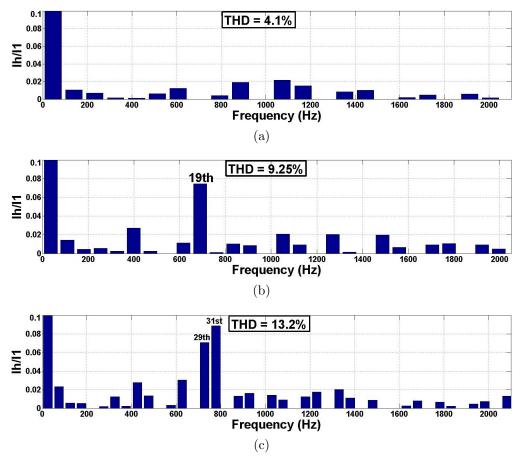

| 4.10 | Harmonic spectrum of stator currents (enlarged view to show                            |

|      | the dominant harmonic components). X-axis: Harmonic                                    |

|      | Order. Y-axis: $\frac{I_h}{I_1}$ . (a) (m=0.9216, N=8). (b) (m=0.6667,                 |

|      | N=12). (c) ( $m=0.4431$ , $N=18$ )                                                     |

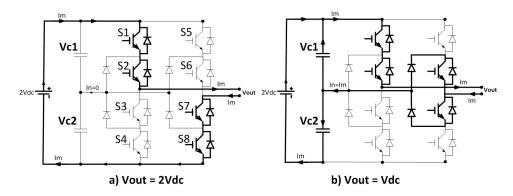

| 5.1  | Single dc-link dual inverter fed open-end stator winding in-                           |

|      | duction motor drive. (a) D2L inverter (b) D3L inverter 129                             |

| 5.2  | Dual <i>n</i> L-MMC fed open-end stator winding IM drive $\ldots$ 130                  |

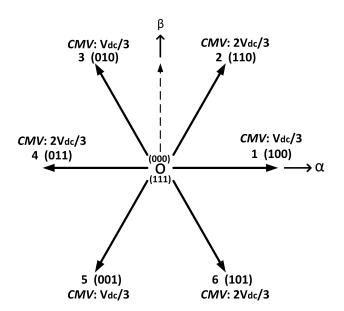

| 5.3  | Voltage space vectors for 2L inverter                                                  |

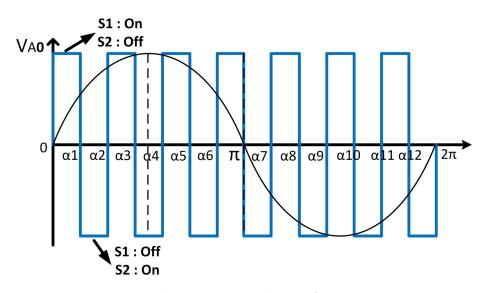

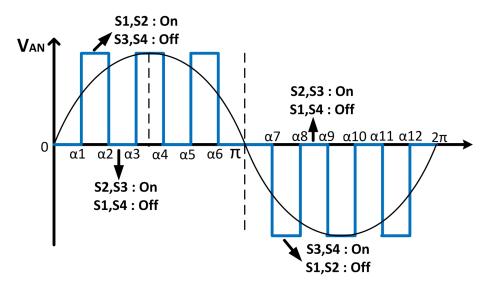

| 5.4  | Phase output voltage of 2L inverter                                                    |

| 5.5  | SOP of D2L inverter at $f_{s,max} = 400$ Hz : $f_s$ versus $m \dots 135$               |

| 5.6  | Phase output voltage of 3L-NPC inverter                                                |

|      |                                                                                        |

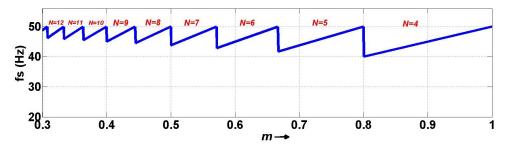

| 5.7  | SOP of D3L inverter at $f_{s,max} = 200$ Hz : $f_s$ versus $m \dots 137$   |

|------|----------------------------------------------------------------------------|

| 5.8  | SOP of 3L-MMC with $f_{s,max} = 400$ Hz : Estimated pulse                  |

|      | number N and corresponding $f_s$ for a given $m$                           |

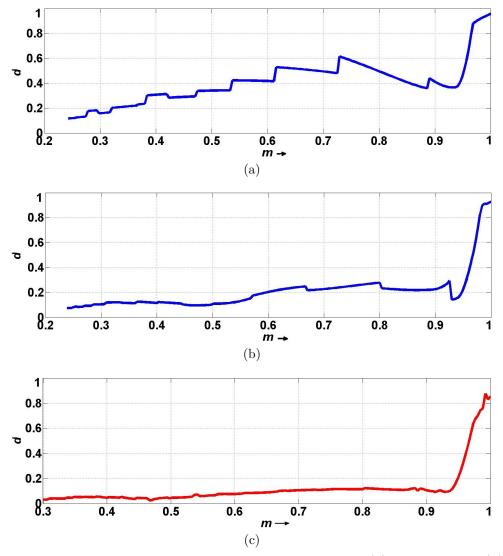

| 5.9  | Optimization results in terms of $d$ versus $m$ : (a) D2L inverter         |

|      | (b) D3L inverter (c) Dual 3L-MMC                                           |

| 5.10 | Submodule capacitor voltages (p.u.) of 3L-MMC phase leg                    |

|      | with pre-assigned switching angles                                         |

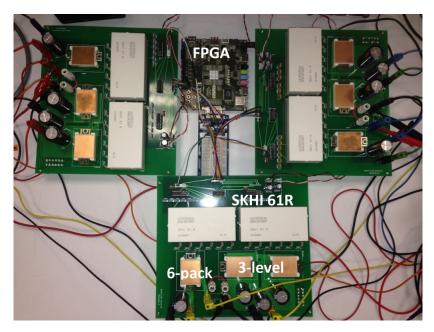

| 5.11 | Prototype of D2L and D3L inverters for one of the three-phases 143         |

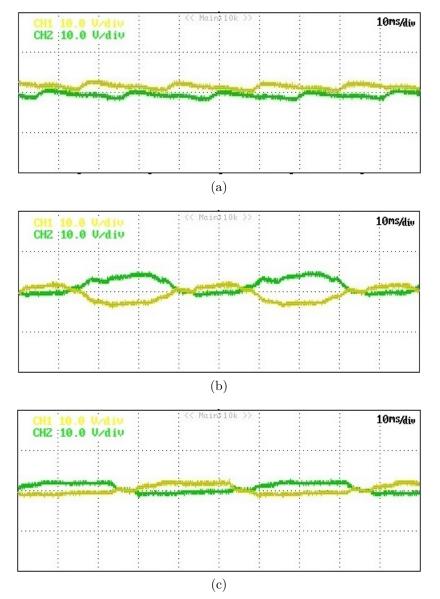

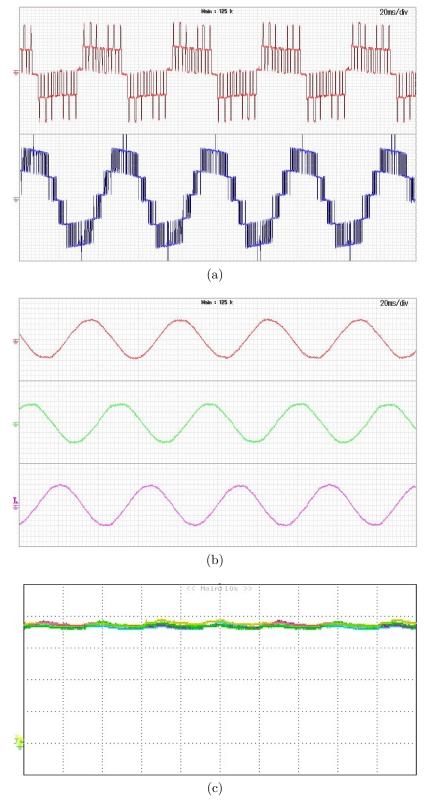

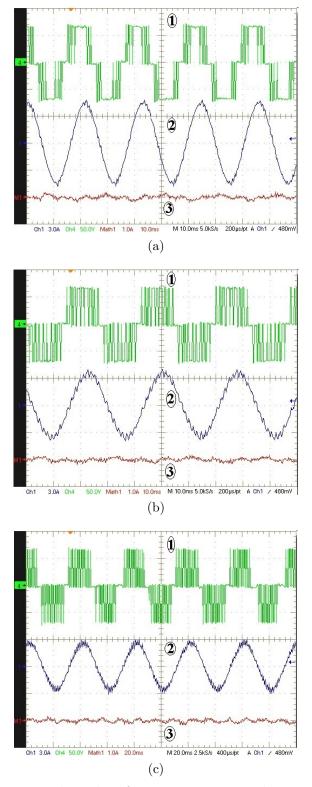

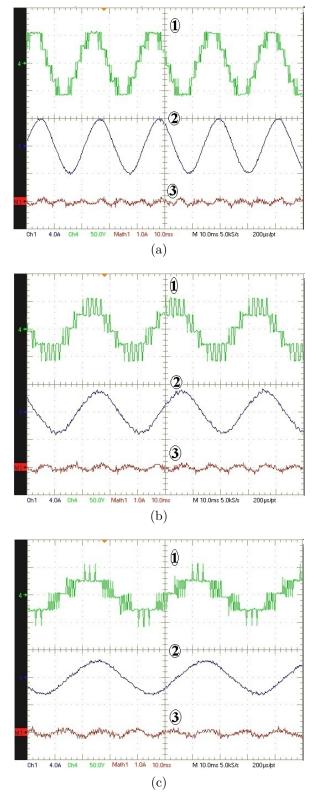

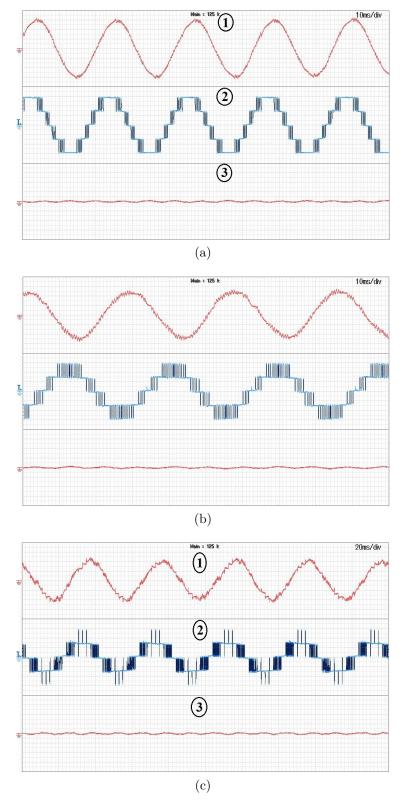

| 5.12 | Experimental results of D2L inverter : machine stator volt-                |

|      | age (1) (Y-axis:50 V/div), stator current (2) (Y-axis:4 A/div),            |

|      | and zero-sequence current (3) (Y-axis:1 A/div). (a) ( $m=0.9333$ ,         |

|      | N=6). X-axis:10 ms/div. (b)( $m=0.7255$ , $N=10$ ). X-axis:10              |

|      | ms/div. (c) ( $m=0.5020$ , $N=14$ ). X-axis:20 ms/div 144                  |

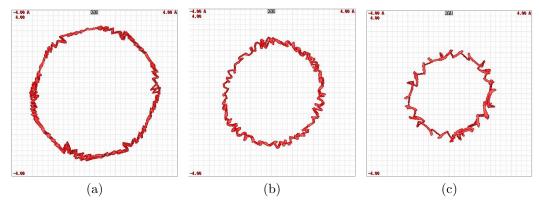

| 5.13 | Experimental results of D2L inverter : Stator current space                |

|      | vector trajectories. X-axis, Y-axis: 2 A/div (a) ( $m=0.9333$ ,            |

|      | N=6) (b) (m=0.7255, N=10) (c) (m=0.5020, N=14) 145                         |

| 5.14 | Experimental results of D2L inverter : Harmonic spectrum                   |

|      | of stator currents (enlarged view to show the dominant har-                |

|      | monic components). X-axis: Frequency (Hz). Y-axis: $\frac{I_h}{I_1}$ . (a) |

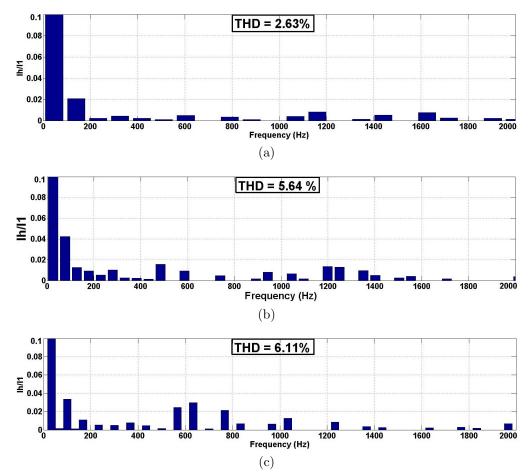

|      | (m=0.9333, N=6) (b) $(m=0.7255, N=10)$ (c) $(m=0.502, N=10)$               |

|      | N=14)                                                                      |

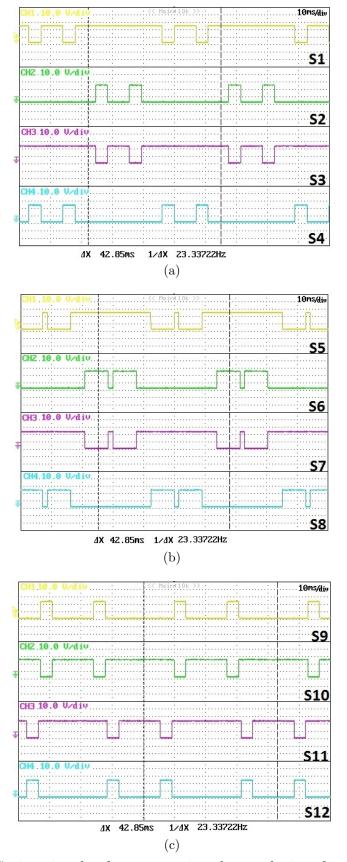

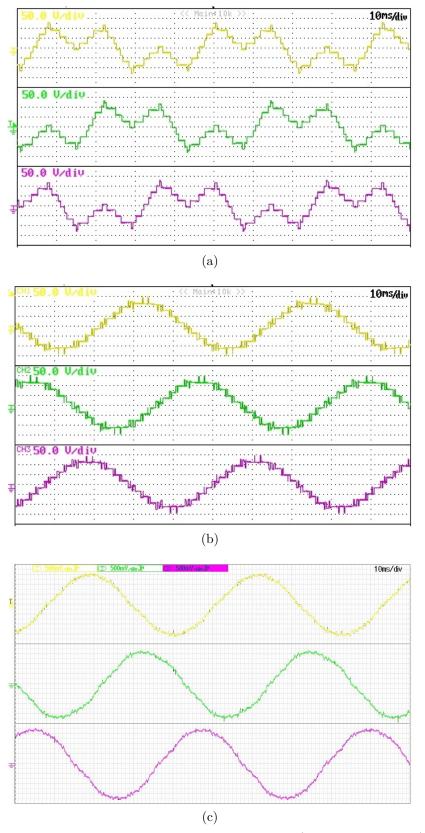

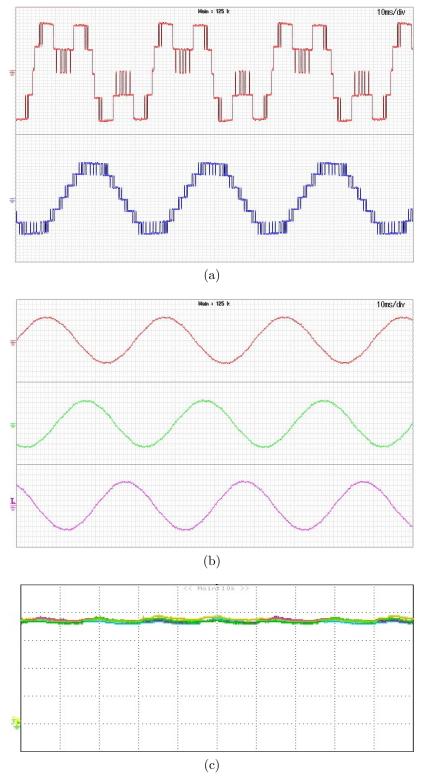

| 5.15 | Experimental results of D3L inverter : machine stator volt-                |

|      | age (1) (Y-axis:50 V/div), stator current (2) (Y-axis:4 A/div),            |

|      | and zero-sequence current $\textcircled{3}$ (Y-axis:1 A/div). X-axis:10    |

|      | ms/div. (a) ( $m=0.9294$ , $N=8$ ). (b)( $m=0.6667$ , $N=12$ ). (c)        |

|      | (m=0.5098, N=14)147                                                        |

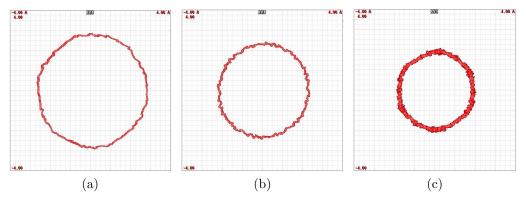

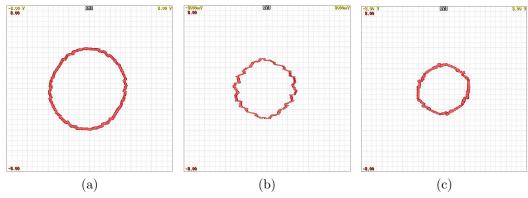

| 5.16 | Experimental results of D3L inverter : Stator current space                |

|      | vector trajectories. X-axis, Y-axis: 2 A/div (a) ( $m=0.9294$ ,            |

|      | N=8) (b) (m=0.667, N=12) (c) (m=0.5098, N=14)                              |

|      |                                                                            |

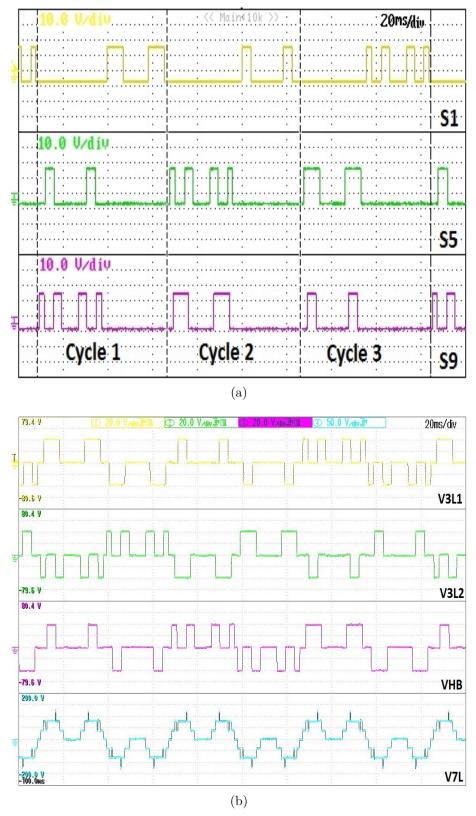

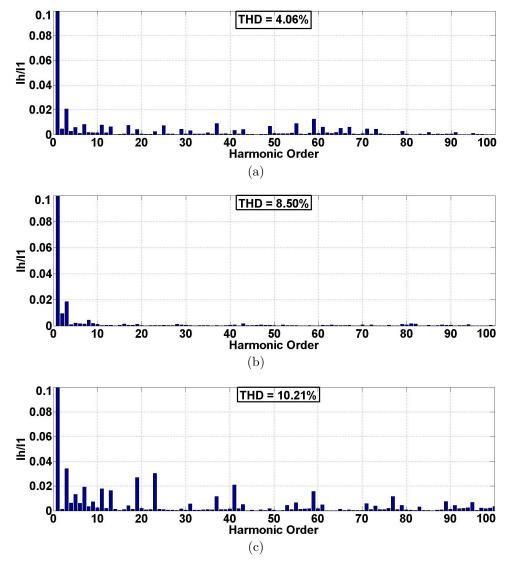

5.17 Experimental results of D3L inverter : Harmonic spectrum of stator currents (enlarged view to show the dominant harmonic components). X-axis: Frequency (Hz). Y-axis:  $\frac{I_h}{I_1}$ . (a) (m=0.9294, N=8) (b) (m=0.667, N=12) (c) (m=0.5098, N=12)5.18 Prototype of dual 3L-MMC for one of the three-phases . . . 150 5.19 Experimental results of dual 3L-MMC inverter : machine stator current (1)(Y-axis:50 V/div), stator voltage (2) (Yaxis:1 A/div), and zero-sequence current (3) (Y-axis:1 A/div). (a) (m=0.9294, N=8). X-axis:10 ms/div. (b)(m=0.7020, m=0.7020)N=11). X-axis:10 ms/div. (c) (m=0.5020, N=15). Xaxis:20 ms/div.  $\ldots$   $\ldots$   $\ldots$   $\ldots$   $\ldots$   $\ldots$   $\ldots$  1515.20 Experimental results of dual 3L-MMC inverter : Stator current space vector trajectories. X,Y-axis:1 A/div (a) (m=0.9294,N=8) (b) (m=7020, N=11) (c)(m=0.5020, N=15) . . . . . 152 5.21 Experimental results of dual 3L-MMC inverter : Harmonic spectrum of stator currents (enlarged view to show the dominant harmonic components). X-axis: Harmonic Order. Yaxis:  $\frac{I_h}{I_1}$ . a) (m=0.9294, N=8) (b) (m=7020, N=11) (c)(m=0.5020, N=11) 5.22 Experimental results of dual 3L-MMC inverter : Submodule capacitor voltages of phase A. X-axis: 20 ms/div, Yaxis:20 V/div (a) (m=0.9294, N=8) (b) (m=7020, N=11)

# List of Acronyms

- AFE Active-front end

- ANPC Active neutral-point-clamped

- CCS Continuous control set

- CHB Cascaded H-Bridge

- CMV Common-mode voltage

- D2L Dual two-level

- D3L Dual three-level

- DTC Direct torque control

- EMI Electromagnetic interference

- FC Flying capacitor

- FCS Finite control set

- FMCC Forced machine current control

- GPC Generalized predictive control

- GTO Gate turn-off thyristor

- HNPC H-Bridge with neutral-point-clamped phase leg

- HV High voltage

- HVDC High voltage direct current

- IGBT Insulated-gate bipolar transistor

- IGCT Integrated-gate commutated thyristor

- LDSF Low device switching frequency

- LV Low voltage

- MLC Multilevel converter

- MLI Multilevel inverter

- MMC Modular multilevel converter

- MPC Model predictive control

- MPDCC Model predictive direct current control

- MPDTC Model predictive direct torque control

- MP<sup>3</sup>C Model predictive pulse pattern control

- MV Medium voltage

- NLC Nearest level control

- NPC Neutral-point-clamped

- NPP Neutral-point-potential

- NVC Nearest vector control

- OPP Optimized Pulse Pattern

- PMSG Permanent magnet synchronous generator

- PWM Pulsewidth modulation

- ${\rm SPWM} \ \, {\rm Sinusoidal} \ \, {\rm pulsewidth} \ {\rm modulation}$

- SHE Selective harmonic elimination

- SHM Selective harmonic mitigation

- SVC Space vector control

- SVM Space vector modulation

- SOP Synchronous optimal pulsewidth modulation

- TCC Transistor clamped converter

- TDD Total demand distortion

- THD Total harmonic distortion

- VNPC Vienna neutral-point-clamped

# List of Symbols

| $\alpha_i$       | Switching angles or instants $(i=1,2,N)$                       |

|------------------|----------------------------------------------------------------|

| d                | Distortion factor                                              |

| $f_1$            | Fundamental frequency                                          |

| $f_{1R}$         | Rated fundamental frequency                                    |

| $f_s$            | Device switching frequency                                     |

| $f_{s,avg}$      | Average device switching frequency                             |

| $f_{s,max}$      | Maximum device switching frequency                             |

| $i_h$            | Harmonic rms current                                           |

| $i_{h,six-step}$ | Harmonic rms current at six-step operation $(m = 1)$           |

| k                | $k^{th}$ order harmonic component                              |

| $i_k$            | Amplitude of $k^{th}$ order harmonic component of              |

|                  | converter output current                                       |

| $l_{\sigma}$     | Leakage inductance of induction motor                          |

| m                | Modulation index                                               |

| N                | Pulse number                                                   |

| nL               | <i>n</i> -level $(n=2,3,4,5,\dots)$                            |

| s(i)             | Slope of switching transition at                               |

|                  | switching angle $\alpha_i$ ( $i = 1, 2, 3, \ldots, N$ )        |

| $u_k$            | Amplitude of $k^{th}$ order harmonic component of              |

|                  | converter phase output voltage                                 |

| $u_{k,six-step}$ | Amplitude of $k^{th}$ order harmonic component of              |

|                  | converter phase output voltage at six-step operation $(m = 1)$ |

| $V_{peak}$       | Peak value of converter output voltage                         |

| $w_1$            | Fundamental frequency of stator current                        |

# Chapter 1 Introduction

This Chapter presents the introduction of the thesis. The background behind motivation of this thesis is given in Section 1.1. The literature review of LDSF modulation techniques and emerging MLC topologies is presented in Section 1.2. Comparison of several LDSF modulation techniques is done in Section 1.3. The research problem and research objectives of the thesis are discussed in Section 1.4. The research contributions and outline of the thesis are given in Sections 1.5, and 1.6, respectively. This Chapter is concluded in Section 1.7.

### 1.1 Background

Development of novel converter topologies, new semiconductor devices, and innovative modulation techniques are essential to produce advanced power electronics technologies for modern applications. For high power applications, better efficiency can be obtained by increasing the voltage rating rather than current rating of power conversion system. There are two ways to handle increased voltage rating : (1) develop HV semiconductor devices, (2) develop new converter topologies with LV/MV semiconductor devices. Out of the two, development of new converter topologies known as MLCs have emerged as an attractive solution for MV/HV high power applications. The merits of MLCs over classical 2L converters are: higher operating voltage capability with matured LV/MV semiconductor devices, better output voltage waveform quality, lower harmonic distortion of input and output currents, reduced filters size, less  $\frac{dv}{dt}$  stress, lower common-mode voltages, reduced electromagnetic interference, reduced torque ripple, and feasible fault-tolerant operation [2–10].

MLCs consist of an array of semiconductor devices and capacitive voltage sources, which can generate output voltage waveforms with multiple steps by appropriate switching. With increase in number of voltage levels or steps, the staircase output waveform approaches sinusoidal waveform. The classical multilevel topologies are NPC [11], FC [12] and CHB converters [13]. The topology of 3L-NPC has become popular due to its simple structure, but it has not been extended to higher level operation due to excessive losses of clamping diodes, uneven distribution of losses in inner and outer devices and unachievable dc-link capacitor voltage balance [14]. FC multilevel topologies are not suitable for high power applications due to requirement of higher device switching frequency to achieve capacitor voltage balance [15].

The CHB topology can achieve higher operating voltage by utilizing LV semiconductor devices. Due to modularity and scalability, the CHB topology has become industrial standard for high power and high quality demanding applications. However, the main disadvantage of CHB topology is the requirement of expensive and bulky phase-shifting multi-winding isolation transformer to provide large number of isolated dc sources [3].

Fig. 1.1: Emerging MLC topologies