### THEORETICAL STUDY OF ADVANCED FIELD-EFFECT TRANSISTORS BASED ON ALTERNATIVE CHANNEL MATERIALS FOR SUPPLY VOLTAGE REDUCTION

### LOW KAIN LU

B.S., Purdue University M.S., Purdue University

## A THESIS SUBMITTED FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

## DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING

NATIONAL UNIVERSITY OF SINGAPORE

2015

## DECLARATION

I hereby declare that the thesis is my original work and it has been written by me in its entirety. I have duly acknowledged all the sources of information that have been used in the thesis.

This thesis has also not been submitted for any degree in any university previously.

ľ . l

Low Kain Lu 8 December 2015

## Acknowledgements

First and foremost, I wish to thank my main supervisor, Assoc. Prof. Liang Gengchiau, and co-supervisor, Prof. Yeo Yee-Chia, for their continuous support during my Ph.D. study. I have benefited greatly from their strong technical expertise and knowledge. Their ideas, feedback, and willingness of making time for discussions are greatly appreciated. Without their careful supervision and encouragement, this research work would not have been possible.

I would like to thank Prof. Fan Weijun (from Nanyang Technological University) for his great help and advice in my work on the band structure calculations of germanium-tin alloy. In addition, I would like to express my gratitude to Dr. Yang Yue and Dr. Lam Kai-Tak for all the technical supports I received throughout my PhD. study. Next, I would like to thank Dr. Huang Wen for her guidance on the ab-initio calculations. I would like to thank Zhang Xiaoyi and Guo Yan for their help in the tight binding and semi-classical transport calculations. I am also grateful to Gaurav Gupta for his assistance on the quantum transport calculation based on NEGF. My gratitude goes to Dr. Gong Xiao for all the fruitful discussions.

My special thanks to all my other colleagues: Kian Hui, Ashvini, Sujith, Ivana, Guo Cheng, Pengfei, Chunlei, Eugene, Samuel, Vijay, Lanxiang, Tong Yi, Yinjie, Liu Bin, Zhou Qian, Wang Wei, Sachin, Dong Yuan, Lei Dian, Annie, and Xu Xin. I am thankful that our paths have crossed. It has truly been an honor to work with you all.

Last but not least, I would like to extend my deepest and sincere gratitude to my family members who have supported and encouraged me throughout the years in all my endeavors.

# **Table of Contents**

| DECLARATION                                                        | ii   |

|--------------------------------------------------------------------|------|

| Acknowledgements                                                   | iii  |

| Table of Contents                                                  | iv   |

| Abstract                                                           | vii  |

| List of Tables                                                     | X    |

| List of Figures                                                    | xii  |

| List of Symbols                                                    | XX   |

| List of Abbreviation                                               | xxii |

| Chapter 1 Introduction                                             | 1    |

| 1.1 Background                                                     | 1    |

| 1.2 Transistors with Alternative Channel Material                  | 3    |

| 1.2.1 Group IV and III-V Semiconductors                            | 6    |

| 1.2.2 Two-Dimensional Materials                                    | 7    |

| 1.3 Transistor with Steep Switching Behavior                       | 8    |

| 1.3.1 Working Principles of TFET                                   | 11   |

| 1.3.2 Development and Designs of TFET Technology                   | 13   |

| 1.4 Objectives of Thesis                                           | 15   |

| 1.5 Organization of Thesis                                         | 16   |

| Chapter 2 GeSn Alloy as Channel Material for Metal-Oxide-Semicondu |      |

| Field-Effect Transistors                                           | 18   |

| 2.1 Introduction                                                   | 18   |

| 2.2 Electronic Band Structure Analysis of GeSn Alloy               | 20   |

| 2.2.1 The empirical pseudopotential method                         | 20   |

| 2.2.2 $Ge_{1-x}Sn_x$ band structure calculations approach          | 22   |

| 2.2.3 Results and Discussions of $Ge_{1-x}Sn_x$ band structure      | 24 |

|---------------------------------------------------------------------|----|

| 2.3 Derivation of Effective Mass Parameters                         |    |

| 2.3.1 Effective Mass Approximation                                  |    |

| 2.3.2 Discussions and Results of Numerical Fitting                  |    |

| 2.4 Device Performance of GeSn based Transistor                     | 42 |

| 2.4.1 Methodology and Device Model                                  | 42 |

| 2.4.2 Results and Discussions of <i>I</i> <sub>ON</sub> Performance | 44 |

| 2.5 Conclusions                                                     | 50 |

| Chapter 3 Drive Current of Silicane and Germanane Metal-Oxide              | e-  |

|----------------------------------------------------------------------------|-----|

| Semiconductor Field-Effect Transistors in the Ballistic Transport Regime:  | A   |

| Simulation Study                                                           | .52 |

|                                                                            |     |

| 3.1 Introduction                                                           |     |

| 3.2 Approach                                                               | .55 |

| 3.2.1 Electronic band structure calculations                               | .55 |

| 3.2.2 Ballistic transport performance calculations                         | .55 |

| 3.3 Results and Discussions                                                | .56 |

| 3.3.1 Electronic band structure                                            | .56 |

| 3.3.2 Electrical Performance                                               | .60 |

| 3.4 Conclusions                                                            | .76 |

|                                                                            |     |

| Chapter 4 Voltage Scalability of Group IV, III-V, and 2D-Materials Ultra   | a-  |

| Thin-Body Transistor based on ITRS metrics                                 | .77 |

| 4.1 Introduction                                                           | 77  |

| 4.2 Methodology                                                            |     |

| 4.3 Results and Discussions                                                |     |

|                                                                            |     |

| 4.3.1 $I_{ON}$ Performance of MOSFET for HP Technology Targeting Year 2018 |     |

| 2022, and 2026                                                             |     |

| 4.3.2 $I_{ON}$ Performance of MOSFET for LP Technology Targeting Year 2018 | 8,  |

| 2022, and 2026                                                             | .85 |

| 4.3.3 Detailed Performance Evaluation Based on 2026 ITRS Metrics           | .87 |

| 4.4 Conclusions                                                            | .96 |

| Chapter 5 Tunneling Field-Effect Transistor: Device Physics a  | and Design of a     |

|----------------------------------------------------------------|---------------------|

| L-Shaped Germanium Source Tunneling Transistor                 | 97                  |

| 5.1 Introduction                                               | 97                  |

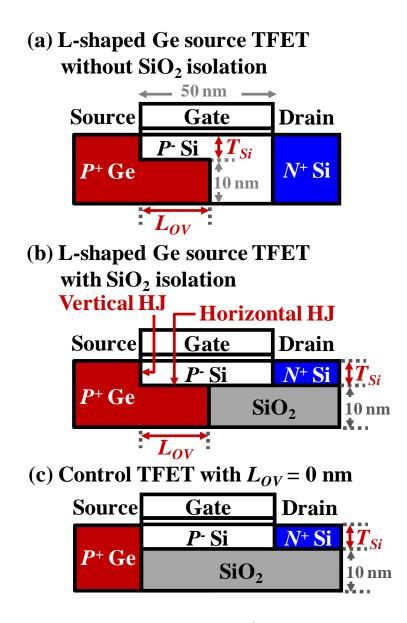

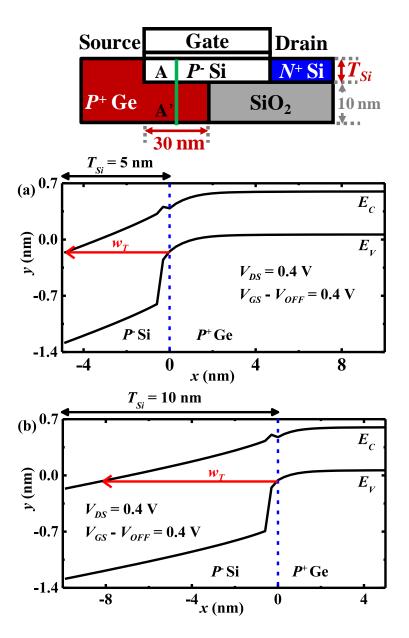

| 5.2 Proposed Structure and Simulation Approach                 |                     |

| 5.2.1 Device structure and design                              |                     |

| 5.2.2 Methodology and Device Parameters                        |                     |

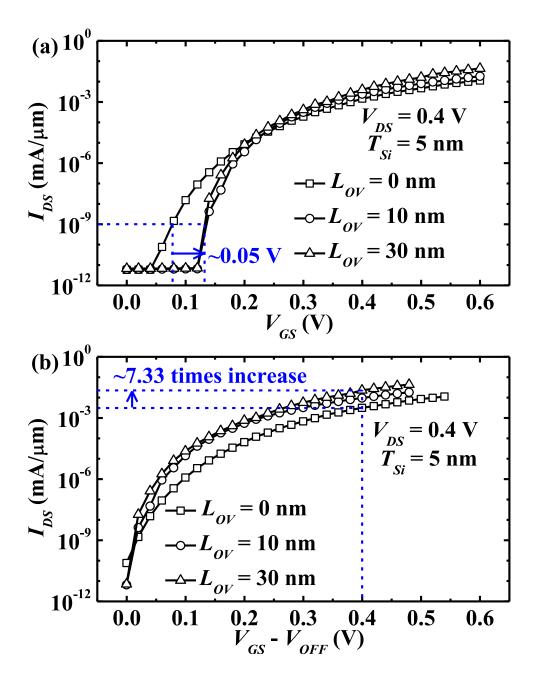

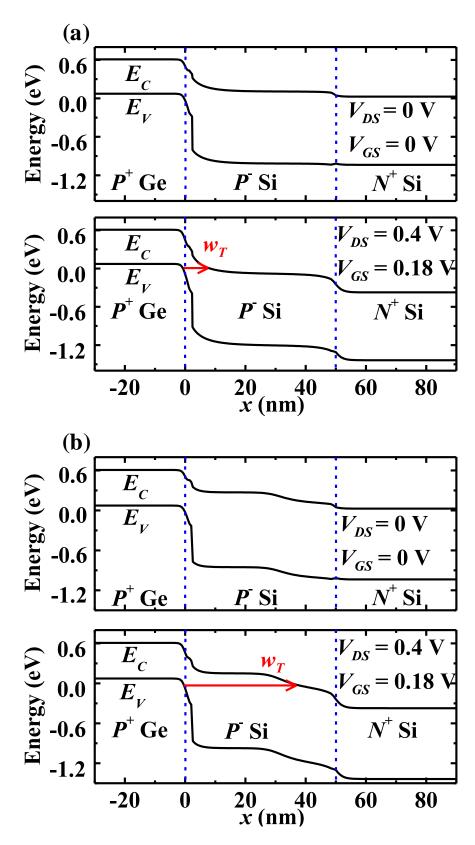

| 5.3 Results and Discussions                                    |                     |

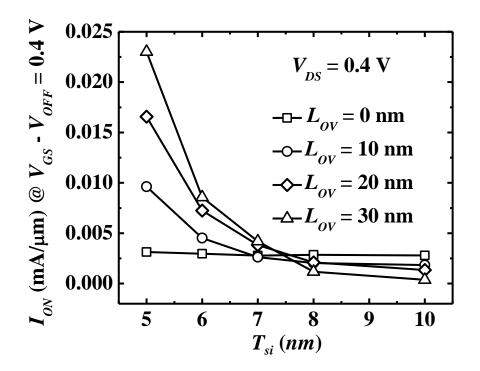

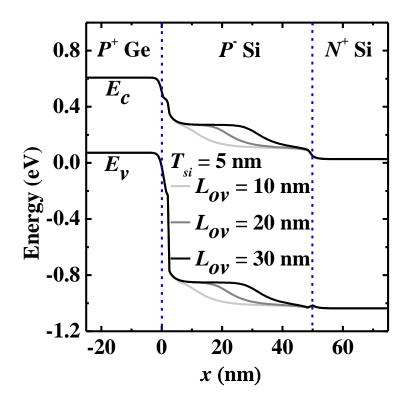

| 5.3.1 Impact of $T_{Si}$ and $L_{OV}$ on ON-state current:     |                     |

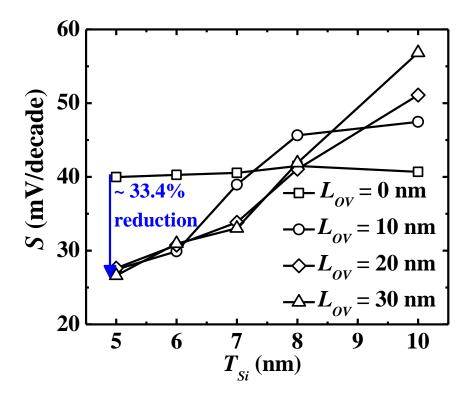

| 5.3.2 Impact of $T_{Si}$ and $L_{OV}$ on subthreshold swing S: | 111                 |

| 5.4 Design guidelines for optimal L-shaped Ge source TFETs:    |                     |

| 5.5 Conclusions                                                | 114                 |

| Chapter 6 Conclusion and Future Directions                     | 115                 |

| 6.1 Conclusion                                                 | 115                 |

| 6.2 Contribution of This Thesis                                | 116                 |

| 6.2.1 Theoretical Study of the Electronic Properties of GeSn A | lloy as Channel     |

| Material for MOSFETs                                           | 116                 |

| 6.2.2 Ballistic Transport Performance of Group IV 2D Material  | ls: Silicane and    |

| Germanane MOSFETs                                              | 117                 |

| 6.2.3 Voltage Scalability of Ultra-Thin Body MOSFETs based o   | n Group IV, III-    |

| V, and 2-Dimensional Materials                                 | 118                 |

| 6.2.4 Design and Physics of L-shaped Germanium Source Tunnel   | ling Transistor 119 |

| 6.3 Future Directions                                          | 119                 |

| 6.3.1 GeSn-based Transistors                                   | 119                 |

| 6.3.2 Transistors based on 2D Materials from Group IV          |                     |

| 6.3.3 Tunneling Field-Effect Transistors                       | 121                 |

| References                                                     | 122                 |

| Appendix                                                       | 147                 |

| List of Publications                                           | 147                 |

## Abstract

### Theoretical Study of Advanced Field-Effect Transistors based on Alternative Channel Materials for Supply Voltage Reduction

By

Low, Kain Lu

### Doctor of Philosophy – Electrical and Computer Engineering National University of Singapore

Complementary-metal-oxide-semiconductor (CMOS) transistors have been commonly employed in the electronics for the past decades due to their excellent scalability, low cost, and high performance. Higher packing density per unit chip area and enhanced circuit performance can be achieved via the scaling of CMOS transistors. However, with the scaling of CMOS devices into the nanometer regime, the issues associated with the adverse short channel effects (SCEs) arise, leading to high leakage current which increases the static power of a transistor. Furthermore, exponential growth of the number of transistors per integrated circuit (IC) chip causes drastic increase of power density. All these contribute to high power consumption in an IC chip, which has become a serious problem as the technology advances.

In order to reduce the power consumption, power supply voltage ( $V_{DD}$ ) needs to be lowered. Nevertheless, reduction of  $V_{DD}$  should not compromise the ON-current ( $I_{ON}$ ) so that the switching speed of transistors can be sustained. In this context, metaloxide-semiconductor field-effect transistors (MOSFETs) based on alternative channel materials with high product of carrier velocity and density of states (DOS) and tunneling field-effect transistor (TFET) with steeper subthreshold slope (S) are promising candidates to enable the reduction of  $V_{DD}$ . In this thesis, MOSFETs with alternative potential channel materials and TFET are explored.

From the perspective of alternative channel materials, semiconductor alloys based on group IV materials, such as Ge and Sn, appear to be of great interest due to their tunable direct band gap and process or materials compatibility with the Si-based platform. We evaluate the electronic properties of  $Ge_{1-x}Sn_x$  alloys using empirical pseudopotential method (EPM) for Sn composition varying from 0 to 20%. The effective masses of  $Ge_{1-x}Sn_x$  alloys are subsequently extracted from the band edges along high symmetry lines. Based on the extracted effective masses of bulk GeSn, the transverse, longitudinal, and confinement effective masses are projected for the double-gate ultra-thin body (DG-UTB) n-MOSFET based on GeSn. The ballistic  $I_{ON}$  of GeSn-based DG-UTB n-MOSFET is investigated in order to assess its  $I_{ON}$  performance.

In addition to the conventional bulk and ultra-thin body channel materials from group IV and III-V, 2-dimensional (2D) monolayer materials, such as transition metal dichalcogenides (TMDs), with extremely thin body allow an excellent electrostatic control. This is desirable for the ultimately scaled CMOS to reduce the SCEs. We examine the electronic properties and the upper limit of the ballistic  $I_{ON}$  of MOSFETs based on hydrogenated silicene and germanene, so-called silicane and germanane, respectively. Their ON-current performances are compared with those of the TMDs based transistors. Silicane n-MOSFET outperforms the rest of n-channel transistors studied while silicane and germanane p-MOSFETs offer higher  $I_{ON}$  than 2D-TMDs p-MOSFETs.

In order to identify the potential channel materials with better voltage scalability for the reduction of the power consumption, the ultimate voltage scalability of a double-gate ultra-thin body MOSFET employing channel materials from group IV, III-V, and 2D materials is studied. The key performance metrics, including the voltage scalability and power delay product (PDP), are assessed based on the device specifications projected by the International Technology Roadmap for Semiconductors (ITRS) for high performance (HP) and low power (LP) applications. Channel materials from group IV, III-V, and black phosphorus (BP) are assessed based on the requirements for HP technology while 2D materials are evaluated according to LP technology requirements. It is found that Ge and GaSb transistors show good voltage scalability for HP application. For LP application, good voltage scalability and low PDP are attained in silicon, black phosphorus (BP), and silicane transistors.

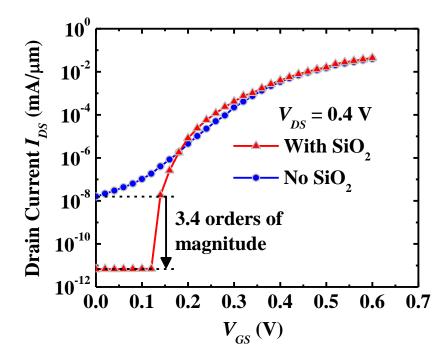

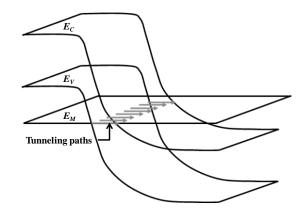

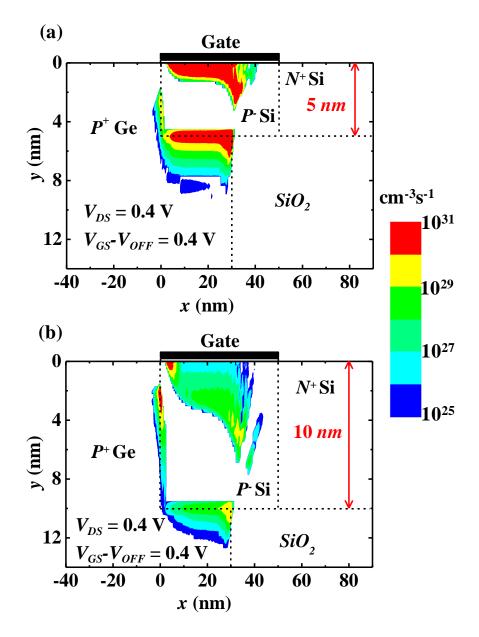

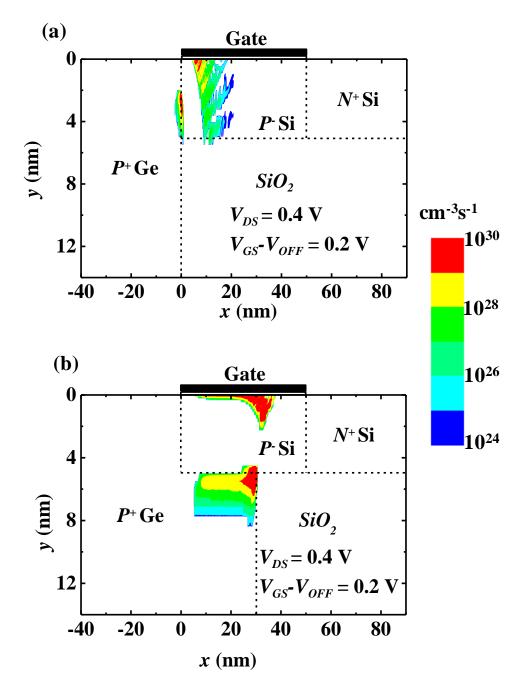

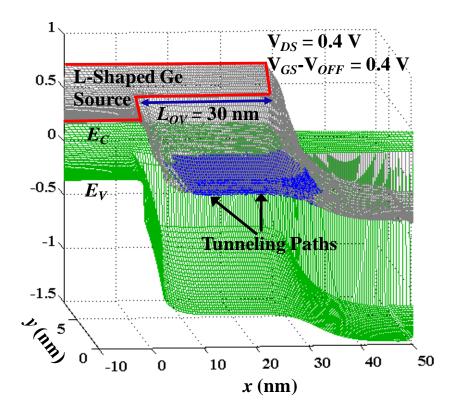

For the transistor with steep subthreshold swing, we demonstrate a novel device structure for TFET with its source region extending into the channel region toward the drain. The proposed structure also exploits heterostructure with staggered (or type II) band alignment at the tunneling junction to enhance the  $I_{ON}$  of TFET. The horizontal heterostructure tunneling junction formed by the P<sup>+</sup> Ge source region underneath the P<sup>-</sup> Si channel region enhances the  $I_{ON}$  by increasing the tunneling area which is scalable with the gate length. A more uniformly distributed electrostatic potential along the horizontal tunneling junction gives rise to steeper subthreshold characteristics.

# **List of Tables**

| Table 1.1.        | Bulk electron and hole mobility of various alternative channel materials [8].                                                                                                                                                                                                                                                                                            | .6 |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Table 2.1.        | The fitted form factors for $Ge_{1-x}Sn_x$ with various Sn compositions used in EPM. The calculated band gap energies are in good agreement with the reported data [120].                                                                                                                                                                                                | 26 |

| <b>Table 2.2.</b> | Effective masses of conduction band at symmetry valleys (L, $\Gamma$ , and $\Delta$ ) in the Brillouin zone.                                                                                                                                                                                                                                                             | 28 |

| Table 2.3.        | Effective masses of heavy-hole, light-hole and split-off bands along symmetry lines [(100), (110), and (111)] in the Brillouin zone                                                                                                                                                                                                                                      | 28 |

| Table 2.4.        | The bowing equations for light-hole and electron effective masses fitted with a quadratic polynomial for $0 \le x \le 0.20$ .                                                                                                                                                                                                                                            | 29 |

| Table 2.5.        | The fitted Luttinger-like parameters, including Kane energy $(E_p)$ ,<br>band gap energy at the $\Gamma$ valley $(E_g^{\Gamma})$ , and spin-orbit splitting $\Delta$ for                                                                                                                                                                                                 |    |

| Table 2.6.        | $0.05 \le x \le 0.20$ .<br>The effective masses of the LH and HH bands of $\text{Ge}_{1-x}\text{Sn}_x$ (in unit of $m_0$ ) obtained using a simple parabolic line fit using 8-band k.p method and EPM for $0.05 \le x \le 0.20$ .                                                                                                                                        |    |

| Table 2.7.        | The effective masses of the conduction and split-orbit bands of Ge <sub>1</sub> .<br><sub>x</sub> Sn <sub>x</sub> (in unit of $m_0$ ) obtained using a simple parabolic line fit using<br>8-band k.p method and EPM for $0.05 \le x \le 0.20$                                                                                                                            | 41 |

| Table 2.8.        | The longitudinal $(m_x)$ , transverse $(m_y)$ , confinement $(m_z)$ effective<br>masses, subband degeneracy $(g_v)$ , and energy separation $(\Delta E)$<br>between L and $\Gamma$ valley $(\Delta E)$ for 2D GeSn material system for $0 \le x$<br>$\le 0.20$ . The units for the effective mass and $\Delta E$ are $m_0$ (free electron<br>mass) and eV, respectively. | 43 |

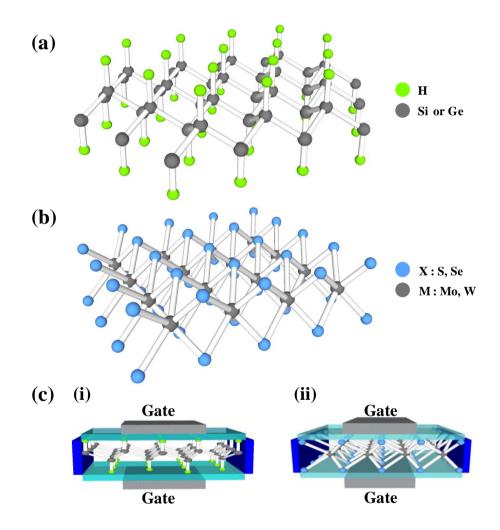

| Table 3.1.        | Optimized structural and electronic parameters of silicane and germanane. $a$ , $\Delta z$ , and $d$ represent the lattice constant, buckling distance, and bond length, respectively. $X =$ Silicon or Germanium and $H =$ Hydrogen.                                                                                                                                    | 57 |

# **Table 4.1.** $T_{body}$ , EOT, $R_{SD}$ , $V_{DD}$ , and $L_G$ for production years of 2018, 2022,and 2026, as projected by the 2013 ITRS.81

## **List of Figures**

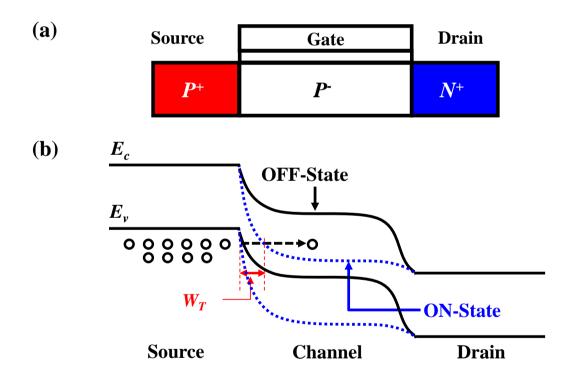

- Fig. 1.5. (a) Schematic of P-I-N TFET, (b) Energy band along source to drain for OFF and ON-state. At the OFF-state, the tunneling barrier width  $(W_T)$  is large which prohibits the carriers from the source to tunnel

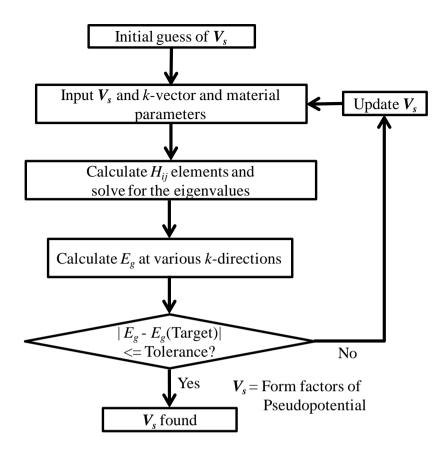

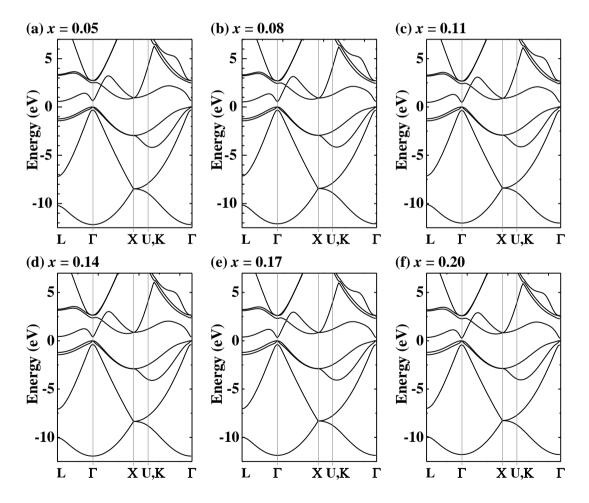

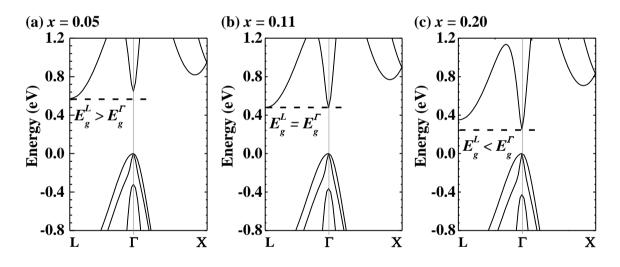

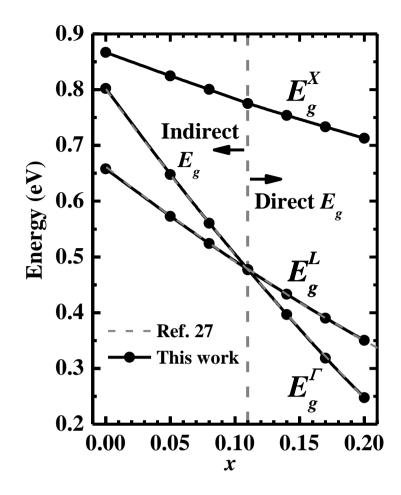

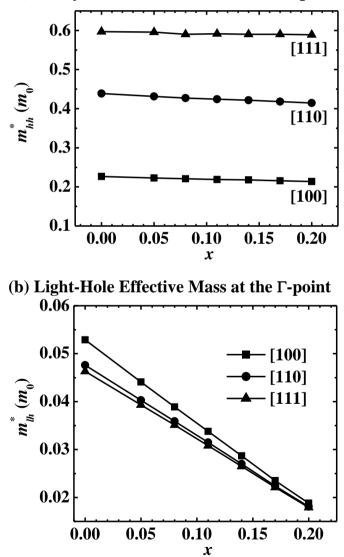

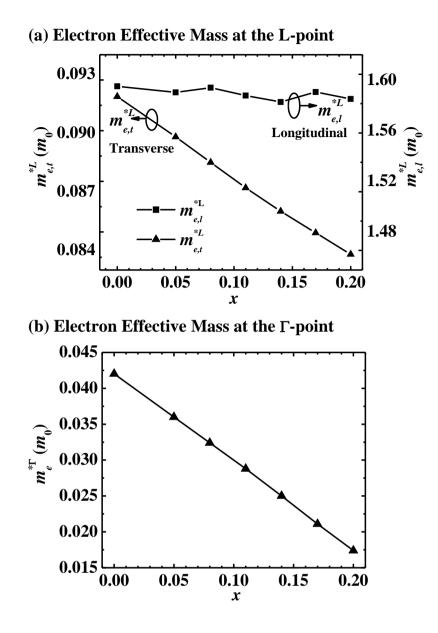

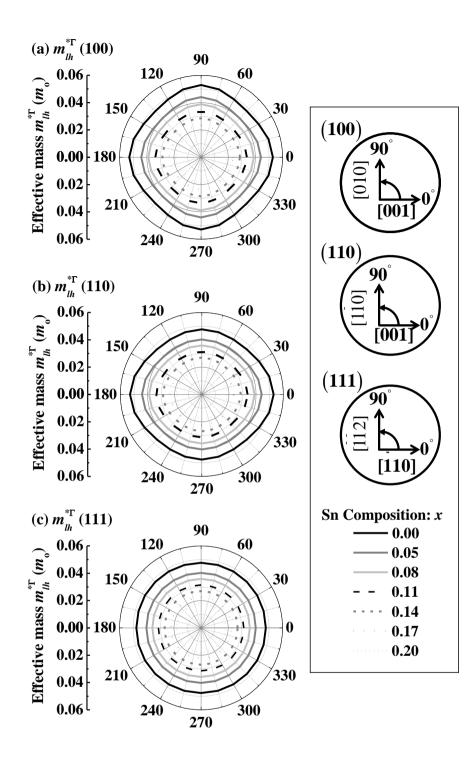

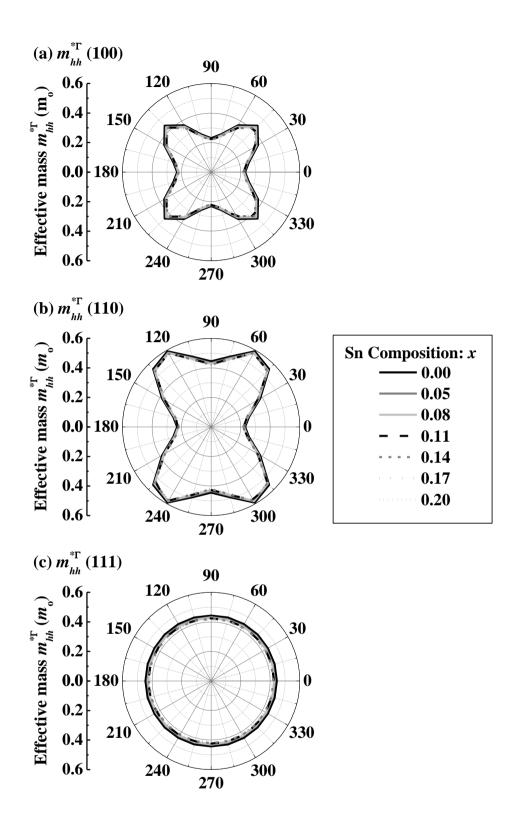

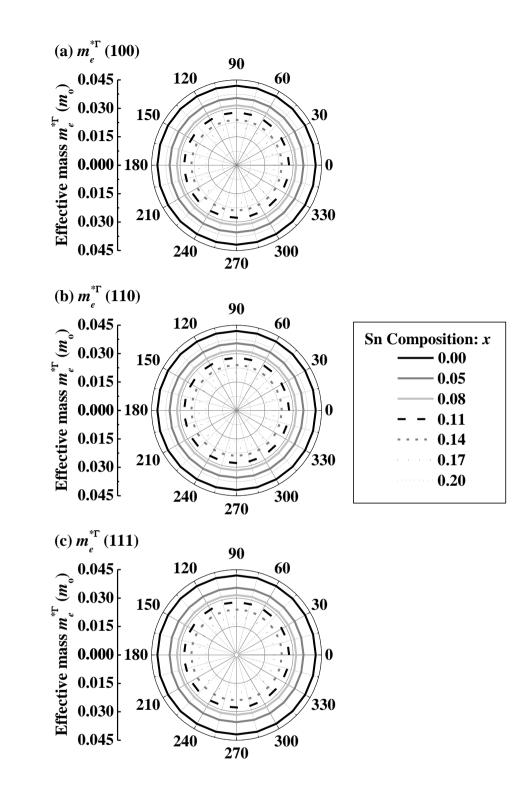

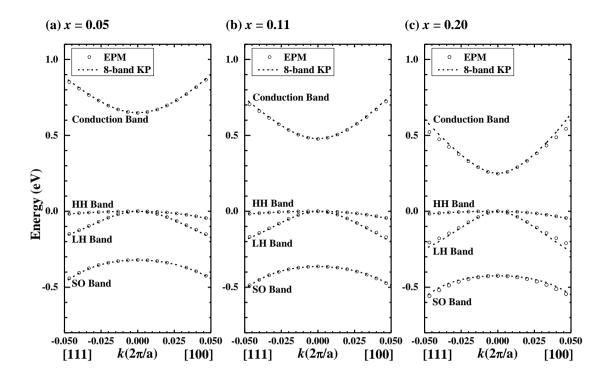

to the channel region and the high energy carriers are filtered out by the band gap. Thus, the leakage current of TFET is expected to be lower. At the ON-state,  $W_T$  is reduced by the gate potential which permits band-to-band tunneling to occur, giving rise to an ON-state Key points for the design considerations of TFET......13 **Fig. 1.6**. Flow chart of the iterative process used in finding sets of Fig. 2.1. pseudopotential form factors yielding band gap energies in good agreements with the experimental values......24 **Fig. 2.2.** Full band structure of  $Ge_{1-x}Sn_x$  along high symmetry lines in the Brillouin zone for (a) x = 0.05, (b) x = 0.08, (c) x = 0.11, (d) x =Fig. 2.3. Zoomed-in view of the electronic band structures of  $Ge_{1-x}Sn_x$  along high symmetry lines for (a) x = 0.05, (b) x = 0.11, and (c) x = 0.20, showing the transition from indirect [Fig. 2.3(a)] to direct band gap [Fig. 2.3(c)] of  $Ge_{1-x}Sn_x$ . Fig. 2.3(b) illustrates the critical composition of 11% where the band gap energies of L and  $\Gamma$  valley The calculated band gap energies of X, L, and  $\Gamma$  valley at various Sn **Fig. 2.4**. compositions. The band gap energies of L and  $\Gamma$  valley agree well Fig. 2.5. (a) Heavy-hole (HH) and (b) light-hole (LH) effective masses of  $Ge_{1-x}Sn_x$  along high symmetry lines in the Brillouin zone for x Fig. 2.6. Electron effective masses of  $Ge_{1-x}Sn_x$  along high symmetry lines in the Brillouin zone for x ranging from 0.0 to 0.20: (a) Longitudinal and transverse electron effective mass at L valley, (b) Electron Fig. 2.7. The effective masses for light-hole, heavy-hole, and conduction band at  $\Gamma$ - valley of Ge<sub>1-x</sub>Sn<sub>x</sub> for three common plane orientations [(100), (110), and (111)] and various in-plane directions. The LH

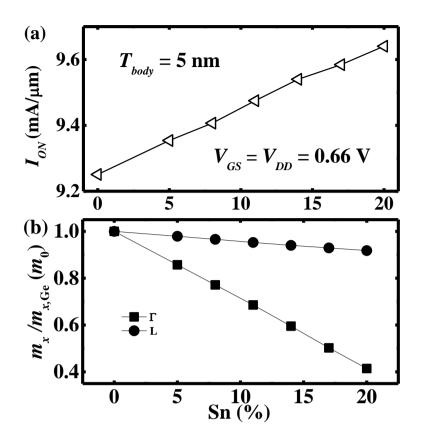

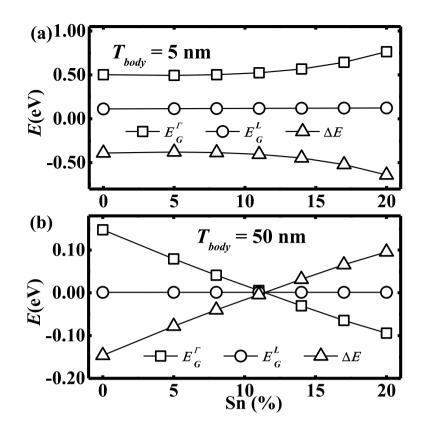

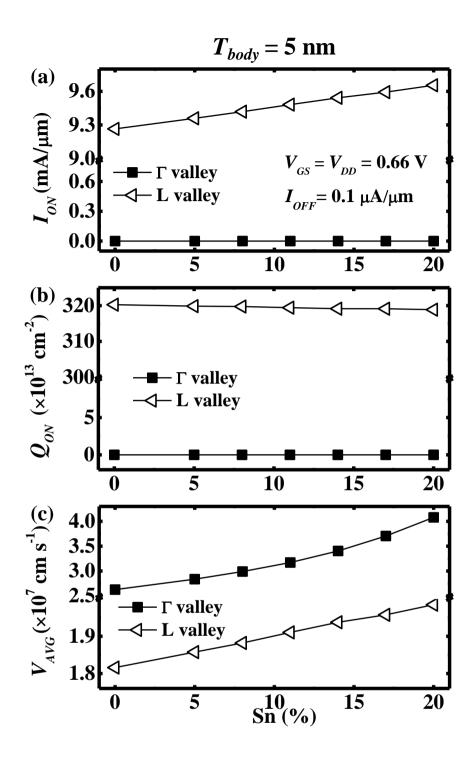

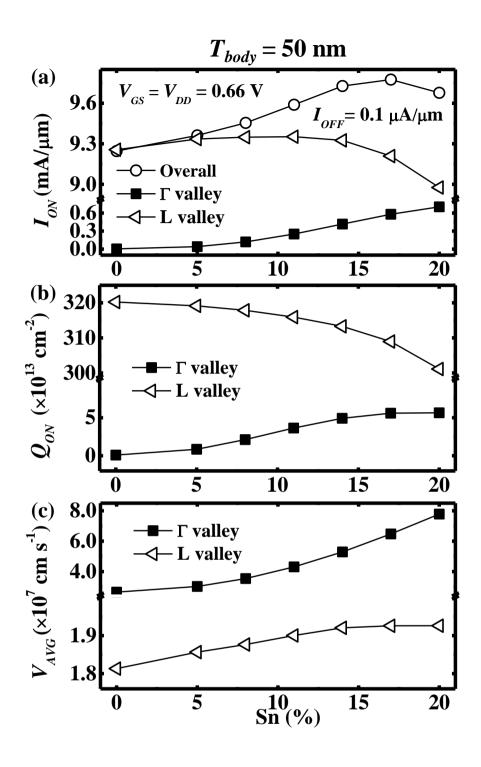

- **Fig. 2.13.**  $E_g^{\Gamma}$ ,  $E_g^L$ , and energy separation ( $\Delta E$ ) between L and  $\Gamma$  valley for (a) 5 nm and (b) 50 nm  $T_{body}$ . Due to the quantum confinement and relatively smaller  $m_z$  of  $\Gamma$  valley, the subband of  $\Gamma$  valley is higher

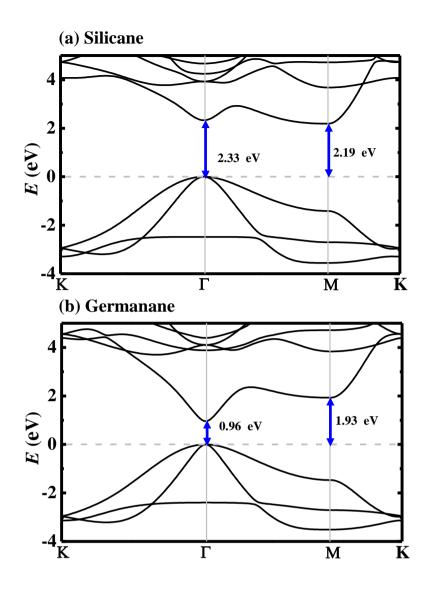

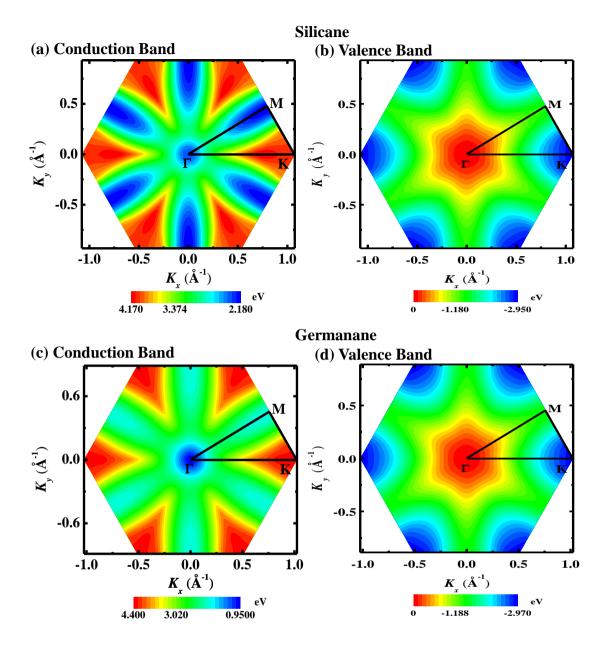

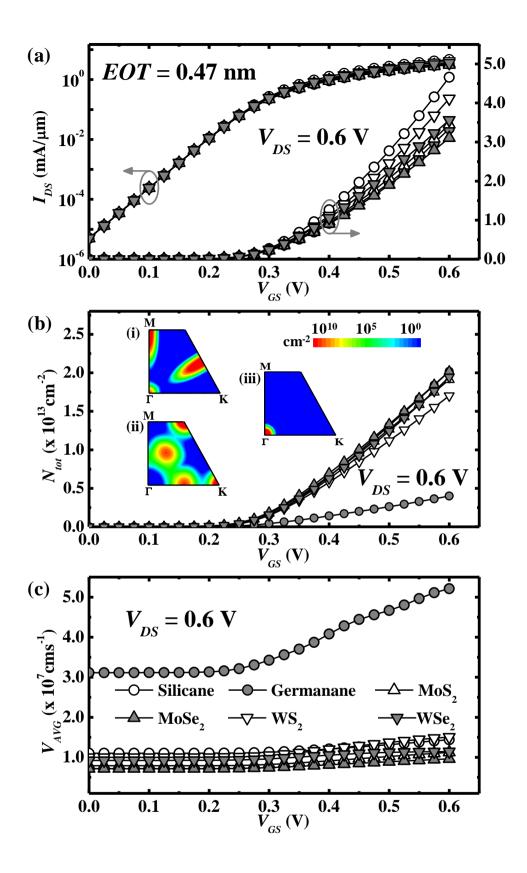

- Fig. 3.2. Electronic band structures of (a) Silicane and (b) Germanane......58

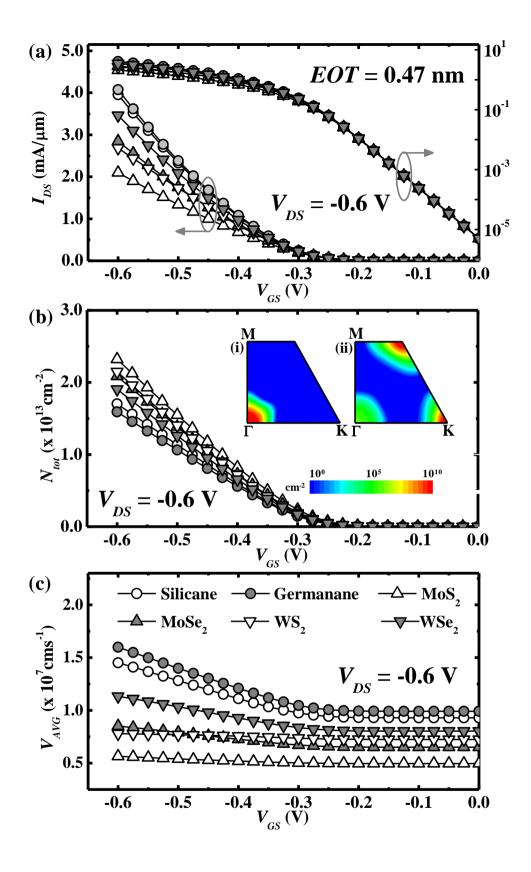

| Fig. 3.5. | p-MOSFET: (a) Ballistic $I_{DS} - V_{GS}$ for different 2D materials at $V_{DD}$<br>= -0.6 V. (b) Average hole density. Insets showing the distribution<br>of hole density in the positive quadrant of the first Brillouin zone<br>(BZ) ( $k_x - k_y$ plane) at ON-state (i) Germanane and (ii) WSe <sub>2</sub> . (c) |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | Average hole velocity                                                                                                                                                                                                                                                                                                  |

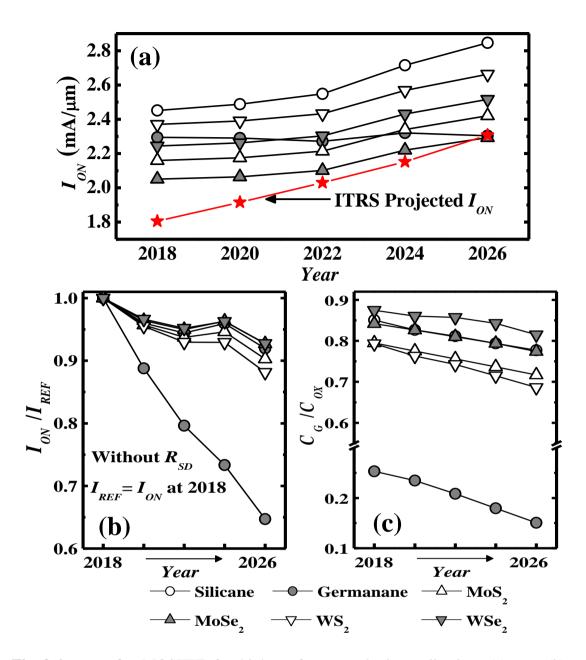

| Fig. 3.6. | $I_{ON}$ of n-MOSFET for high performance logic application: (a) $I_{ON}$ ,                                                                                                                                                                                                                                            |

|           | (b) Ballistic $I_{ON}/I_{REF}$ without considering $R_{SD}$ , where $I_{REF}$ is the $I_{ON}$                                                                                                                                                                                                                          |

|           | of year 2018, and (c) $C_G/C_{OX}$ at different years of production                                                                                                                                                                                                                                                    |

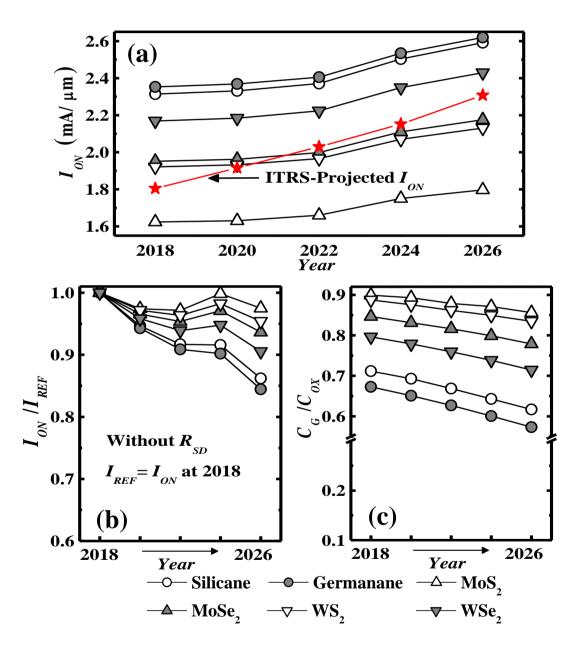

| Fig. 3.7. | $I_{ON}$ of p-MOSFET for high performance logic application: (a) $I_{ON}$ ,                                                                                                                                                                                                                                            |

|           | (b) Ballistic $I_{ON}/I_{REF}$ without considering $R_{SD}$ , where $I_{REF}$ is the $I_{ON}$                                                                                                                                                                                                                          |

|           | of year 2018, (c) $C_G/C_{OX}$ at different years of production                                                                                                                                                                                                                                                        |

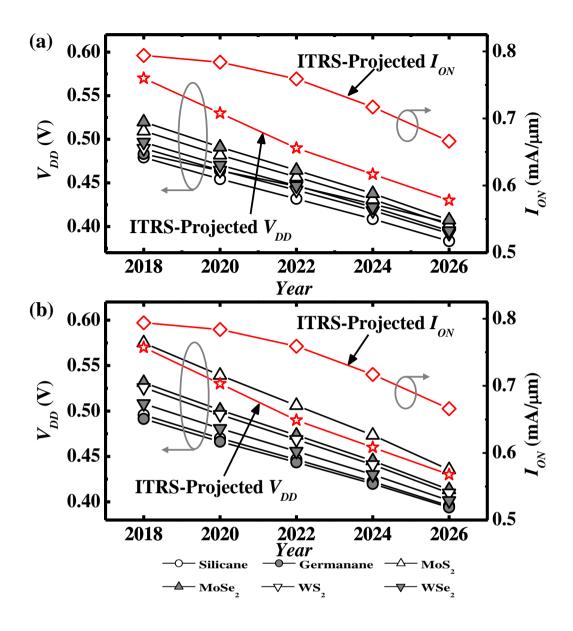

| Fig. 3.8. | Minimum scalable $V_{DD}$ ( $V_{DD,min}$ ) at different production years for<br>low operating power logic applications: (a) n-MOSFET (b) p-                                                                                                                                                                            |

|           | MOSFET. $V_{DD,min}$ is defined to be the smallest $V_{DD}$ required by the                                                                                                                                                                                                                                            |

|           | MOSFET to deliver the ITRS-projected <i>I</i> <sub>ON</sub> 74                                                                                                                                                                                                                                                         |

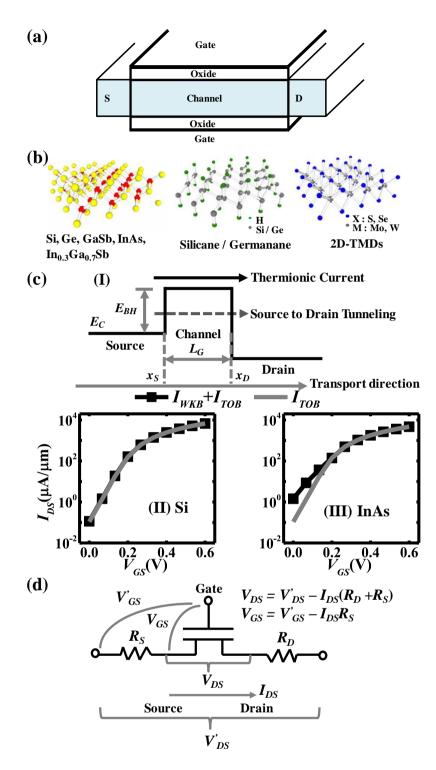

| Fig. 4.1. | (a) Double-Gate Ultra-Thin Body (DG-UTB) device structure. (b)<br>Crystal structures of the channel materials considered in this work                                                                                                                                                                                  |

|           | (c) (I) Conduction band profile across source, channel, and drain                                                                                                                                                                                                                                                      |

|           | region. The barrier height is denoted as $E_{BH}$ . Gate transfer                                                                                                                                                                                                                                                      |

|           | characteristic of Si (II) and InAs (III) UTB n-MOSFETs based on                                                                                                                                                                                                                                                        |

|           | ITRS specification for year 2026. Leakage current of InAs n-                                                                                                                                                                                                                                                           |

|           | MOSFET increases after including the direct source-to-drain                                                                                                                                                                                                                                                            |

|           | tunneling current $(I_{WKB})$ in addition to the thermionic current $(I_{TOB})$ .                                                                                                                                                                                                                                      |

|           | (d) Circuit diagram of the simulated DG-UTB transistor with                                                                                                                                                                                                                                                            |

|           | extrinsic source / drain resistance component ( $R_{SD}$ ). A higher $R_{SD}$                                                                                                                                                                                                                                          |

|           | reduces the voltage drop across the intrinsic terminals of MOSFET 79                                                                                                                                                                                                                                                   |

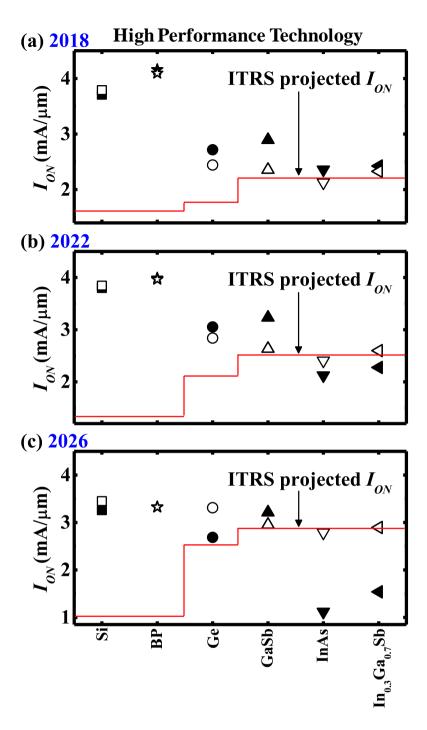

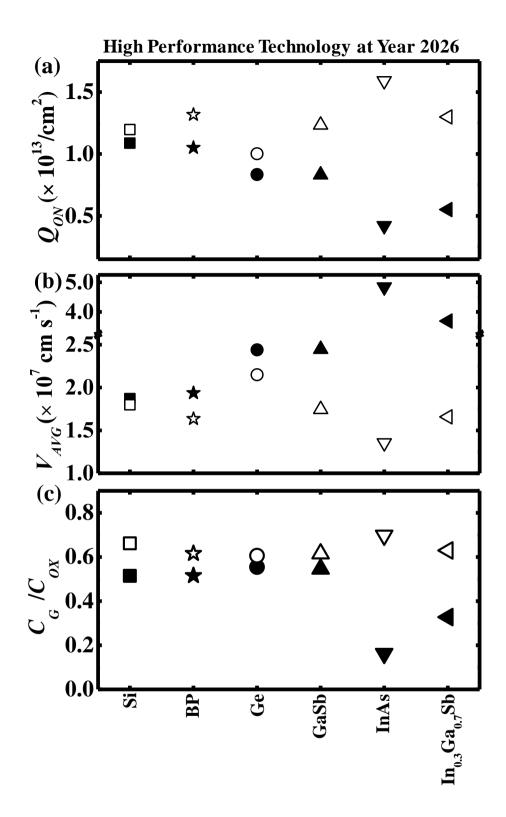

**Fig. 4.2.** HP technology: Comparison of ballistic  $I_{ON}$  of n-MOSFET (filled) and p-MOSFET (open) for HP technology for production year of (a) 2018; (b) 2022; and (c) 2026. BP and Si n-MOSFETs provide higher  $I_{ON}$  than the rest for all the production years. For all production years studied, the  $I_{ON}$  values of InAs and In<sub>0.3</sub>Ga<sub>0.7</sub>Sb for both n-MOSFETs and p-MOSFETs are lower compared to those of

|           | other n-MOSFETs and p-MOSFETs. Higher $I_{ON}$ observed in Si and BP n-MOSFET and p-MOSFET in the production years of 2018 and                                                                                                                                                                                                                                                                                                                                                                 |    |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|           | 2022 is mostly due to larger $V_{DD}$ and smaller EOT projected by the 2013 ITRS                                                                                                                                                                                                                                                                                                                                                                                                               | 84 |

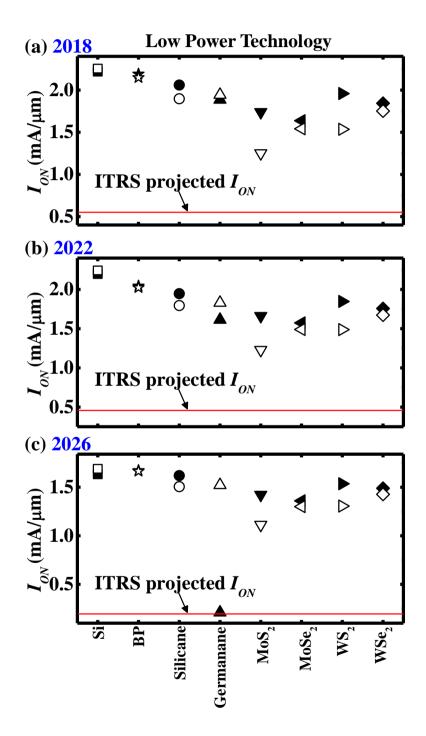

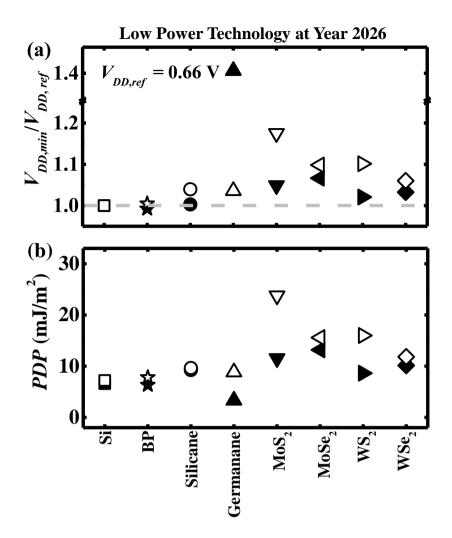

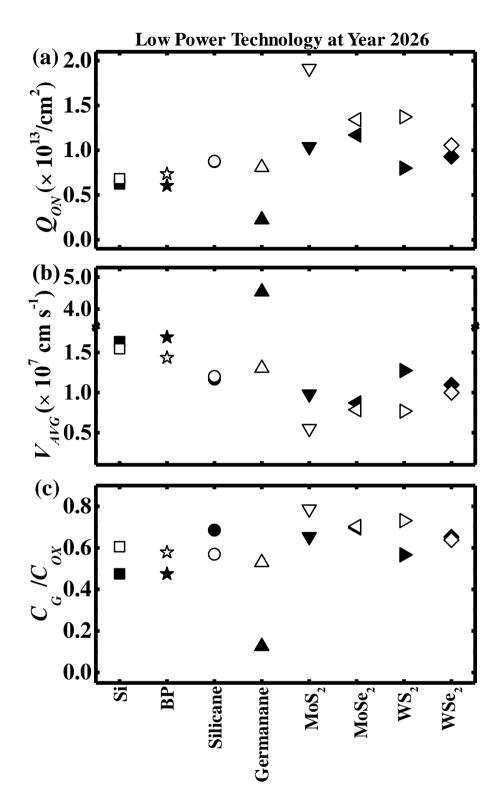

| Fig. 4.3. | LP technology: Comparison of ballistic <i>I</i> <sub>ON</sub> of n-MOSFET (filled)<br>and p-MOSFET (open) for LP technology for production year of (a)<br>2018; (b) 2022; and (c) 2026.                                                                                                                                                                                                                                                                                                        | 86 |

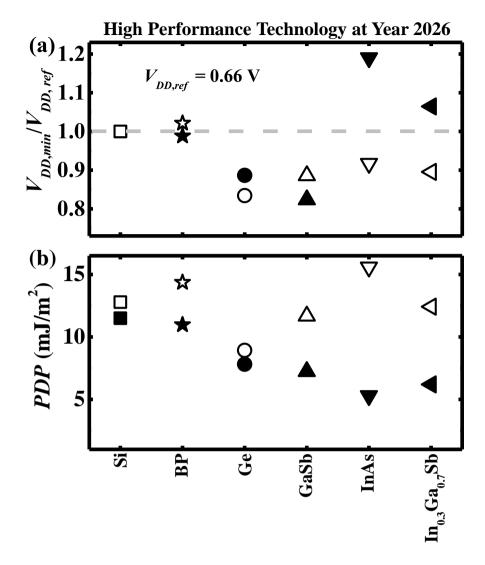

| Fig. 4.4. | HP technology at year 2026: (a) $V_{DD,min}/V_{DD,ref}$ of n-MOSFET (filled)<br>and p-MOSFET (open), where $V_{DD}$ , ref is the $V_{DD,min}$ of Si MOSFET.<br>$V_{DD,min}$ is defined to be the smallest value of $V_{DD}$ required to deliver<br>the $I_{ON}$ of Si n-MOSFET and p-MOSFET, respectively at the<br>production year of 2026. (b) Power delay product (PDP) across<br>different channel materials                                                                               | 88 |

| Fig. 4.5. | HP technology at year 2026: (a) Carrier density in the channel of n-<br>MOSFET (filled) and p-MOSFET (open) at the ON state. (b)<br>Average carrier velocity of n-MOSFET and p-MOSFET at the ON<br>state. (c) $C_G/C_{OX}$ at the ON state. InAs and In <sub>0.3</sub> Ga <sub>0.7</sub> Sb n-MOSFETs<br>with smaller electron effective mass at $\Gamma$ valley have the ratio of $C_G$<br>to $C_{OX}$ smaller than 0.4, indicating that they are operating in<br>quantum capacitance regime. | 89 |

| Fig. 4.6. | LP technology at year 2026: (a) $V_{DD,min}/V_{DD,ref}$ of n-MOSFET (filled) and p-MOSFET (open). BP exhibits the smallest $V_{DD,min}$ for both n-MOSFET and p-MOSFET among the MOSFETs based on 2D materials. (b) Power delay product (PDP) across different channel materials.                                                                                                                                                                                                              | 93 |

| Fig. 4.7. | LP technology at year 2026: (a) Carrier density in the channel of n-<br>MOSFET (filled) and p-MOSFET (open) at the ON state. (b)<br>Average carrier velocity of n-MOSFET and p-MOSFET at the ON<br>state. (c) $C_G/C_{OX}$ at the ON state. All n-MOSFETs and p-MOSFETs<br>for LP technology operate at classical regime except for germanane<br>n-MOSFET with its $C_G/C_{OX}$ being smaller than 0.2.                                                                                        | 94 |

- **Fig. 5.9.** Energy band diagram along source-to-drain of device with  $T_{Si} = 5$ nm in OFF-state for  $L_{OV} = 10$ , 20, and 30 nm. The trend of increased lateral tunneling width,  $W_T$ , with increasing  $L_{OV}$  is observed......109

- Fig. 5.11. 3D surface plot of energy band ( $E_C$  and  $E_V$ ) with superimposed tunneling paths at allowed energy levels as extracted from simulation confirms that vertical tunneling indeed is the dominant current component for the device with  $T_{Si} = 5$  nm and  $L_{OV} = 30$  nm.....111

# **List of Symbols**

| а                    | Lattice parameters                                      | nm                |

|----------------------|---------------------------------------------------------|-------------------|

| $C_D$                | Gate-to-drain capacitance                               | F/cm <sup>2</sup> |

| $C_S$                | Gate-to-source capacitance                              | F/cm <sup>2</sup> |

| $C_G$                | Total gate capacitance                                  | F/cm <sup>2</sup> |

| $C_{it}$             | Interface trap capacitance                              | F/cm <sup>2</sup> |

| $C_{OX}$             | Gate oxide capacitance                                  | F/cm <sup>2</sup> |

| $C_Q$                | Quantum capacitance                                     | F/cm <sup>2</sup> |

| $E_{\mathrm{C}}$     | Conduction band energy                                  | eV                |

| $E_g$                | Energy band gap                                         | eV                |

| $E_g^{\Gamma}$       | Energy band gap at $\Gamma$ valley                      | eV                |

| $E_g^L$              | Energy band gap at L valley                             | eV                |

| $E_{f,d}$            | Drain fermi energy                                      | eV                |

| $E_{f,s}$            | Source fermi energy                                     | eV                |

| $E_p$                | Kane energy                                             | eV                |

| $E_{ m V}$           | Valence band energy                                     | eV                |

| f                    | Frequency                                               | Hz                |

| $I_{DS}$             | Source to drain current                                 | A/µm              |

| I <sub>D,sat</sub>   | Saturation drain current                                | A/µm              |

| I <sub>LEAK,SD</sub> | Leakage current                                         | A/µm              |

| I <sub>OFF</sub>     | OFF-state current                                       | A/µm              |

| $I_{ON}$             | ON-state current                                        | A/µm              |

| k                    | Boltzmann constant                                      | eV/K              |

| $L_{ m G}$           | Gate length                                             | m                 |

| $m_0$                | Free electron effective mass                            | kg                |

| $m_{e,l}^{*L}$       | Longitudinal electron effective mass at L valley        | kg                |

| $m_{e,t}^{*L}$       | Transverse electron effective mass at L valley          | kg                |

| $m_{e,l}^{*\Gamma}$  | Longitudinal electron effective mass at $\Gamma$ valley | kg                |

| <i>,</i>             |                                                         |                   |

| $m_{e,t}^{*\Gamma}$  | Transverse electron effective mass at $\Gamma$ valley   | kg               |

|----------------------|---------------------------------------------------------|------------------|

| $m_{e,l}^{*\Delta}$  | Longitudinal electron effective mass at $\Delta$ valley | kg               |

| $m_{e,t}^{*\Delta}$  | Transverse electron effective mass at $\Delta$ valley   | kg               |

| $m_{lh}^{*\Gamma}$   | Light hole effective mass                               | kg               |

| $m_{hh}^{*\Gamma}$   | Heavy hole effective mass                               | kg               |

| $m_x$                | Longitudinal effective mass                             | kg               |

| $m_{v}$              | Transverse effective mass                               | kg               |

| $m_{_{7}}$           | Confinement effective mass                              | kg               |

| $Q_n$                | Electron density                                        | cm <sup>-2</sup> |

| $Q_p$                | Hole density                                            | cm <sup>-2</sup> |

| P <sub>Active</sub>  | Active power consumption                                | W                |

| P <sub>Passive</sub> | Passive power consumption                               | W                |

| q                    | Elementary charge                                       | С                |

| $R_{SD}$             | Source-drain series resistance                          | $\Omega.\mu m$   |

| S                    | Subthreshold swing                                      | mV/decade        |

| Т                    | Temperature                                             | K                |

| $T_{body}$           | Body thickness                                          | nm               |

| $	au_d$              | Time delay                                              | S                |

| $V_{DS}$             | Drain voltage                                           | V                |

| $V_{DD}$             | Power supply voltage                                    | V                |

| $V_{GS}$             | Gate voltage                                            | V                |

| V <sub>inj</sub>     | Thermal injection velocity                              | $ms^{-1}$        |

| $V_{TH}$             | Threshold voltage                                       | V                |

| μ                    | Carrier mobility                                        | $cm^2/V \cdot s$ |

| W                    | Width of the transistor                                 | m                |

| <i>Y1, Y2, Y3</i>    | Luttinger parameters                                    |                  |

|                      |                                                         |                  |

# **List of Abbreviation**

| 2D                                     | Two-dimensional                                             |

|----------------------------------------|-------------------------------------------------------------|

| BP                                     | Black phosphorus                                            |

| BTBT                                   | Band-to-band tunneling                                      |

| CMOS                                   | Complementary metal-oxide-semiconductor                     |

| CB                                     | Conduction band                                             |

| CBM                                    | Conduction band minimum                                     |

| CVD                                    | Chemical vapor deposition                                   |

| DFT-GGA                                | Density functional theory in general gradient approximation |

| VBM                                    | Valence band maximum                                        |

| E-k                                    | Energy dispersion                                           |

| EOT                                    | Equivalent oxide thickness                                  |

| EPM                                    | Empirical pseudopotential method                            |

| DG                                     | Double-gate                                                 |

| DOS                                    | Density of states                                           |

| FB-FET                                 | Feedback field-effect transistor                            |

| GaSb                                   | Gallium antimonide                                          |

| Ge                                     | Germanium                                                   |

| GeSn                                   | Germanium-tin                                               |

| HL                                     | Heavy hole                                                  |

| HP                                     | High performance                                            |

| I-V                                    | Current-voltage                                             |

| IC                                     | Integrated circuit                                          |

| IMOS                                   | Impact-ionization metal-oxide-semiconductor                 |

| ITRS                                   | International Technology Roadmap for Semiconductors         |

| InAs                                   | Indium arsenide                                             |

| In <sub>0.3</sub> Ga <sub>0.7</sub> Sb | Indium gallium antimonide                                   |

| LH                                     | Light hole                                                  |

| $L_{OV}$          | Overlap length of the extended source                       |

|-------------------|-------------------------------------------------------------|

| LP                | Low power                                                   |

| MBE               | Molecular beam epitaxy                                      |

| $MoS_2$           | Molybdenum disulfide                                        |

| MoSe <sub>2</sub> | Molybdenum diselenide                                       |

| MOSFET            | Metal-oxide-semiconductor field effect transistor           |

| n-MOSFET          | n-channel metal-oxide-semiconductor field-effect transistor |

| OPW               | Orthogonalized plane wave                                   |

| PAW               | Projector-augmented plane wave                              |

| PBE               | Perdew-Burke-Ernzerhof                                      |

| p-MOSFET          | p-channel metal-oxide-semiconductor field-effect transistor |

| SCEs              | Short channel effects                                       |

| S/D               | Source / drain                                              |

| Si                | Silicon                                                     |

| SiO <sub>2</sub>  | Silicon dioxide                                             |

| Sn                | Tin                                                         |

| SO                | Split-off                                                   |

| TCAD              | Technology computer-aided design                            |

| TFET              | Tunneling field-effect transistor                           |

| TMD               | Transition metal dichalcogenides                            |

| $T_{Si}$          | Silicon body thickness                                      |

| UTB               | Ultra-thin body                                             |

| VASP              | Vienna ab-initio simulation package                         |

| VB                | Valance band                                                |

| VCA               | Virtual Crystal Approximation                               |

| $WS_2$            | Tungsten disulfide                                          |

| WSe <sub>2</sub>  | Tungsten diselenide                                         |

| WKB               | Wentzel-Kramers-Brillouin                                   |

# Chapter 1

## Introduction

### 1.1 Background

In complementary metal-oxide semiconductor (CMOS) technology, the logic functions in the integrated circuits (IC) are realized using n-channel and p-channel metal-oxide-semiconductor field effect transistors (n-MOSFETs and p-MOSFETs, respectively). Moore's law [1] predicts that the number of transistors in an IC approximately doubles every two years. The semiconductor industry follows the Moore's law for the past few decades. Continued scaling of CMOS devices enables the number of transistors on IC chips to increase at an exponential rate. Higher packing density allows more logic circuits to be fabricated on a given IC chip area which in turn reduces the cost per function.

The saturation drain current ( $I_{D,sat}$ ) of an idealized long-channel MOSFET is inversely proportional to the gate length. Thus, the downscaling of gate length is beneficial for achieving higher  $I_{D,sat}$ , leading to enhancement in circuit speed performance. However, as transistor dimensions are aggressively scaled to the deep sub-micrometer regime and beyond, several serious challenges arise which make the downscaling of transistors extremely difficult. Among severe challenges include short-channel effects (SCEs) and reliability issue. Short channel effects, such as drain induced barrier lowering (DIBL),  $V_{TH}$  roll-off, and punch-through, significantly increase the OFF-state current ( $I_{OFF}$ ) of highly scaled MOSFETs.

While higher packing density and improved circuit speed can be achieved via the scaling of CMOS devices, it also causes high power consumption issue. Basically, power consumption of an IC can be categorized into two components: active power  $(P_{Active})$  and passive power  $(P_{Passive})$ , as given by:

$$P_{Active} \propto C_L V_{DD}^2 f , \qquad (1.1)$$

$$P_{Passive} \propto I_{OFF} V_{DD}, \qquad (1.2)$$

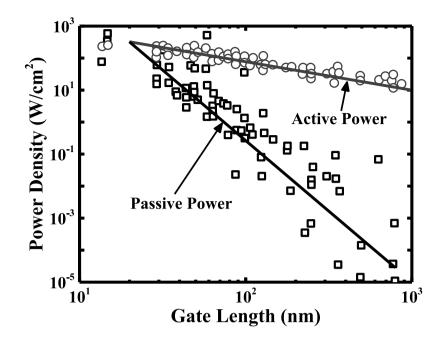

where  $C_L$  is the load capacitance,  $V_{DD}$  is the power supply voltage, f is the switching frequency of the circuit, and  $I_{OFF}$  is the OFF-state current. Fig. 1.1 shows that both active and static power density increase with reduction of gate length. Power consumption has become a more serious issue for advanced technology nodes [2]-[4].

Equation 1.1 and 1.2 show that both  $P_{Active}$  and  $P_{Passive}$  are strongly dependent on  $V_{DD}$ . Hence,  $V_{DD}$  reduction is one of the effective approaches to reduce the power consumption. Nonetheless, the downscaling of  $V_{DD}$  requires careful considerations. The switching speed of the circuit is inversely proportional to the time delay  $(\tau_d)$ , which is given by

$$\tau_d \propto \frac{V_{DD}}{I_{ON}}.$$

(1.3)

To ensure faster switching speed of circuits, the change in  $I_{ON}$  with  $V_{DD}$  downscaling needs to be smaller than the change in  $V_{DD}$ .

To address the power consumption issue in CMOS technology through  $V_{DD}$  reduction, two promising methods are focused in this thesis. The first approach is to explore MOSFETs with alternative channel materials which offer a higher product of carrier injection velocity and density of states (DOS) than Silicon. The second one is the use of novel transistors with steep switching characteristic. In the next two sections, the technological background and development of these two approaches are detailed.

**Fig. 1.1.** Active power and static power versus gate length collected from literature. Both active and static power show increasing trend with the reduction of gate length. The contribution of static power to the overall power density increases and eventually becomes dominant at the highly scaled gate length. This figure is reproduced from Ref. [2].

### **1.2 Transistors with Alternative Channel Material**

As transistor dimensions progress to the nanometer regime, quasi-ballistic transport dominates the drive current. The  $I_{D,sat}$  equation of a MOSFET in quasi-ballistic regime is given by [5]:

$$I_{D,sat} = C_G W v_{inj} \left( \frac{1 - r_c}{1 + r_c} \right) (V_{GS} - V_{TH}), \qquad (1.4)$$

where  $C_G$  is the gate capacitance, W is the channel width,  $v_{inj}$  is the thermal injection velocity, and  $r_c$  is the backscattering coefficient. From 1.4, one of the key parameters affecting the  $I_{D,sat}$  of highly scaled transistors is the  $v_{inj}$ . It was found that  $v_{inj}$  is dependent on low-field mobility while  $r_c$  is inversely proportional to low-field mobility [6]-[7]. In addition,  $I_{D,sat}$  is also a function of gate capacitance ( $C_G$ ) whose value is determined by the series connection of the gate oxide capacitance ( $C_{OX}$ ) and the quantum capacitance ( $C_Q$ ).  $C_{OX}$  is determined by the thickness and the dielectric constant of gate oxide while  $C_Q$  depends on the DOS of the channel material. The downscaling of equivalent oxide thickness (EOT) with technology nodes and introduction of high mobility channel materials can result in the value of  $C_{OX}$  being comparable or even larger than that of  $C_Q$ . Under this condition, the charge in the channel is limited by the DOS which degrades the  $I_{ON}$ . Thus, it is crucial to utilize channel materials with reasonably high DOS in order to have a condition of  $C_Q >>$  $C_{OX}$  such that  $C_G$  is mainly determined by  $C_{OX}$  for achieving higher current.

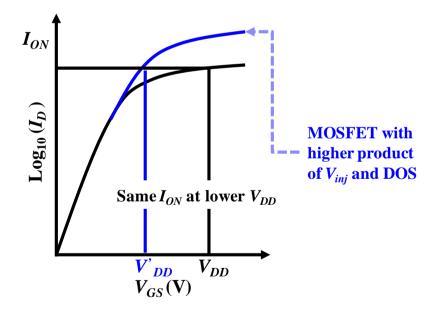

For extremely scaled transistors, the channel length can be comparable or even smaller than the carrier mean free path. This leads to the operation in the ballistic regime where  $r_c$  is equal to zero. Fig. 1.2 shows the  $I_{DS}$ - $V_{GS}$  characteristics of two transistors employing different channel materials with the same subthreshold swing. It is observed that material with higher product of injection velocity and DOS exhibits higher  $I_{ON}$  at the same gate overdrive. In other words, the same  $I_{ON}$  can be obtained at a lower  $V_{DD}$ , enabling the downscaling of  $V_{DD}$  without compromising  $I_{ON}$ . Therefore, it is desirable to employ materials with high  $v_{inj}$  and large DOS in the extremely scaled transistor to achieve higher  $I_{ON}$  at reduced  $V_{DD}$ - $V_{TH}$ .

For the past few decades, silicon (Si) semiconductor material is primarily employed in CMOS technology. However, silicon being the mainstream semiconductor in the ICs is expected to eventually reach its scaling limit. Therefore, instead of depending on the conventional scaling approach, a variety of other techniques have been used to improve the performance of Si-based CMOS technology. In semiconductor industry, strain techniques have been used to enhance the  $I_{ON}$  of Si-MOSFETs by boosting the mobility [9]-[20]. For instance, at the 90 nm technology node [9], SiGe liner stressor and SiN source/drain (S/D) stressors were employed by Intel Corporation to induce beneficial strains in the Si-based p-MOSFETs and n-MOSFET, respectively. The induced strain enhances the  $I_{ON}$  of Si-based MOSFETs via the modification of the electronic band structures.

However, the required improvement in current density and other device parameters, such as intrinsic delay, could no longer be satisfied by solely straining the conventional Si-based MOSFET. Due to the mobility limitation faced in Si MOSFETs, various alternative channel materials have been researched extensively in order to identify potential materials which exhibit superior performance than Si MOSFETs.

**Fig. 1.2.**  $I_{DS} - V_{GS}$  of MOSFETs with different carrier injection velocity and density of states. Under the same  $I_{ON}$  and subthreshold swing, MOSFET with higher product of injection velocity and DOS (blue solid line) delivers the required  $I_{ON}$  at a lower  $V_{DD}$  as compared to the MOSFETs with lower injection velocity and DOS (black solid curve). In other words, MOSFETs with higher product of injection velocity and DOS can achieve higher  $I_{ON}$  at the same  $V_{DD}$ .

#### **1.2.1 Group IV and III-V Semiconductors**

The carrier injection velocities of channel materials can be indicated by their mobility since the carrier injection velocity is related to the low field mobility. Table 1.1 lists the bulk mobilities of some of the potential channel materials. Among promising alternative materials with high mobility for n-channel MOSFETs are III-V compound semiconductors due to their light electron effective mass. At a given  $I_{OFF}$ , III-V n-MOSFETs with higher carrier injection velocity owing to their smaller electron effective mass allow higher  $I_{ON}$  to be delivered. Hence, III-V n-MOSFETs are promising for achieving high speed at lower operating  $V_{DD}$  [21]-[31]. However, low electron DOS in III-V semiconductors may counteract the benefit of high injection velocity, limiting their  $I_{ON}$  in technology nodes with extremely scaled EOT.

For the group IV semiconductors, germanium (Ge) offers the highest hole mobility among the materials listed in Table 1.1. Apart from the elemental semiconductors of group IV, semiconductor alloys have been extensively used for altering material properties through tuning the alloy composition. The Si/Ge material system of group IV has been widely studied for applications in optoelectronics and electronics. However, the indirect nature of the band gap of the Si/Ge material system is a fundamental limitation for its application in optoelectronics.

**Table 1.1.**Bulk electron and hole mobility of various alternative channelmaterials [8].

|                                      | Si   | Ge   | GaAs | InP  | InAs  | InSb  |

|--------------------------------------|------|------|------|------|-------|-------|

| Electron mobility $(cm^2/V \cdot s)$ | 1350 | 3900 | 8500 | 5400 | 40000 | 77000 |

| Hole mobility (cm <sup>2</sup> /V·s) | 480  | 1900 | 400  | 200  | 500   | 850   |

Recently,  $Ge_{1-x}Sn_x$  alloy has attracted immense interest as a promising alternative alloy to achieve tunable direct band gaps in group IV diamond-cubic materials. With the incorporation of substitutional tin (Sn),  $Ge_{1-x}Sn_x$  shows higher carrier mobility than Ge. By tuning the Sn composition, the band gap of  $Ge_{1-x}Sn_x$ alloys exhibits a transition from indirect to direct. Very good progress has been made in realizing high-performance Ge P-MOSFETs [32]-[39]. Recently, GeSn channel P-MOSFETs were experimentally demonstrated to have higher hole mobility than Ge channel P-MOSFETs [40]-[42]. As compared to III-V semiconductors,  $Ge_{1-x}Sn_x$ material systems make possible the fabrication of optical and electronic devices with group IV materials using a CMOS compatible process flow. As a result, the manufacturing cost can be reduced due to easier integration of  $Ge_{1-x}Sn_x$  into current Si platform as compared to III-V materials.

### **1.2.2 Two-Dimensional Materials**

Lower dimensional materials, such as 2D monolayer materials, are currently of much interest due to their superior electronic properties. One of the beneficial features of 2D monolayer materials is the extremely small body thickness which allows excellent electrostatic control of the channel potential by the gate electrode. The excellent electrostatic integrity inherent in the 2D material is desirable for the ultimately scaled CMOS to minimize the short channel effects arising from the downscaling of the transistors dimensions. Graphene, a 2D honeycomb network of carbon atoms, has attracted much attention because of its unique material properties [43]-[44]. The high mobility makes graphene highly attractive for nanoelectronic applications [45]. Despite the superior electronic properties of graphene, it has its own shortcomings, such as high leakage current originated from the zero band gap characteristic. This has sparked tremendous interest toward the exploration of other 2D materials. Among the possible 2D material systems are those from the family of transition metal dichalcogenides (TMD) (MoS<sub>2</sub>, MoSe<sub>2</sub> WS<sub>2</sub>, WSe<sub>2</sub> etc.) [46]-[48]. Unlike graphene, monolayer 2D-TMDs have intrinsic band gaps (1–2 eV) which make them possible as alternative channel materials for CMOS devices. The theoretical and experimental studies show that 2D-TMDs transistors are good for low power applications due to their large band gap and good electrostatic control [49]-[52].

### **1.3 Transistor with Steep Switching Behavior**

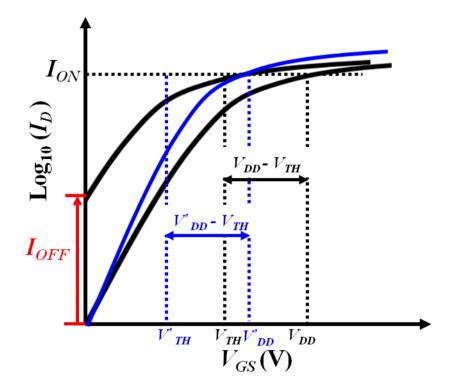

The aggressive downscaling of CMOS transistors has to be accompanied with the reduction of  $V_{DD}$  so that constant electric fields in the transistors can be maintained. In order to sustain the same  $I_{ON}$  at reduced  $V_{DD}$ , the  $V_{TH}$  of the conventional MOSFETs needs to be reduced. However, decreasing  $V_{TH}$  without scaling the subthreshold swing (*S*) will result in a high  $I_{OFF}$  as depicted in Fig. 1.3. This leads to higher passive power consumption which is proportional to  $I_{OFF}$ . Thus, a steeper switching characteristic is required in order to retain the same  $I_{ON}$  and  $I_{OFF}$ when  $V_{DD}$  is reduced.

**Fig. 1.3.**  $I_{DS} - V_{GS}$  of a conventional MOSFET (solid black curve) and steep-slope transistor (solid blue curve). When the power supply voltage is reduced from  $V_{DD}$  to  $V_{DD}$ , the threshold voltage needs to be scaled down as well in order to maintain the same current drivability. However, an increase in the  $I_{OFF}$  is observed in the MOSFET with the  $V_{DD}$  reduction. Hence, transistor with steeper subthreshold characteristic is required in order to keep the same  $I_{OFF}$  at a reduced  $V_{DD}$ , as shown by the blue curve.

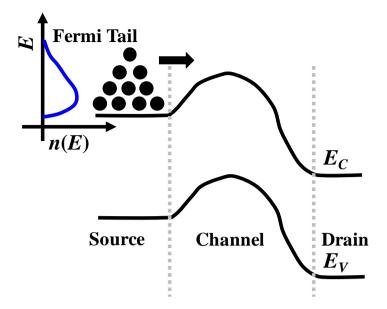

The operating mechanism of MOSFET is based on the injection of carrier from the source side over the potential barrier to the channel region with the potential barrier being modulated by the gate potential. As illustrated in Fig. 1.4, carriers at the source have a thermal energy distribution which follows the Fermi-Dirac distribution. Hence, there are always a finite number of high energy electrons that can surmount the potential barrier at the subthreshold operation region. These high energy electrons contribute to the subthreshold current which sets the lower limit of the MOSFETs subthreshold swing. The S of the MOSFETs can be mathematically described by

$$S = \ln 10 \frac{kT}{q} \left( 1 + \frac{C_D + C_{it}}{C_{OX}} \right) > \ln 10 \frac{kT}{q}, \qquad (1.5)$$

where *k* is the Boltzmann constant, *T* is the temperature, *q* is the electronic charge,  $C_D$  is the depletion capacitance,  $C_{OX}$  is the gate oxide capacitance, and  $C_{it}$  is the capacitance due to the interface traps. Based on equation 1.5, the lowest *S* that can be achieved by the conventional MOSFETs at room temperature is 60 mV/decade.

Due to this fundamental limit,  $I_{OFF}$  of MOSFETs will eventually reach an unacceptable level with the  $V_{DD}$  scaling (which requires reduction of  $V_{TH}$ ). This calls for novel transistors that can achieve *S* smaller than 60 mV/decade at room temperature, so-called steep-slope transistors. Among the potential steep-slope transistors are impact-ionization metal-oxide-semiconductor (I-MOS) device [53]-[56], feedback field-effect transistor (FB-FET) [57]-[58], mechanical gate field-effect transistor [59]-[60], and tunneling field-effect transistor (TFET) [61]-[67].

The operating mechanism of IMOS is based on avalanche breakdown in the reverse biased p-i-n diode. In spite of having steeper *S* in I-MOS, a larger gate voltage is required to induce high electric field for the impact ionization to occur. This translates to higher power consumption due to larger bias required. In addition, I-MOS suffers from reliability issues due to the carrier trapping and the creation of interface states caused by the hot carriers. In FB-FET, the static power consumption is high as the p+-i-n+ diode works in the forward bias regime. For mechanical gate field-effect transistor, the high operating voltage and intrinsic delay limit its potential applications.

**Fig. 1.4.** Energy band diagram along source, channel, and drain region of a MOSFET. The energy distribution of carriers at the source region follows the Fermi Dirac distribution, resulting in finite amount of carriers available at high energy levels. Carriers in the tail of the Fermi distribution can surpass the potential barriers and contribute to the subthreshold current. This subthreshold current sets a lower limit for the switching characteristic of a conventional MOSFET.

### **1.3.1 Working Principles of TFET**

Unlike the steep-slope transistors mentioned above, TFET utilizes the gatecontrolled band-to-band tunneling (BTBT) mechanism to give rise to *S* less than 60 mV/decade at room temperature. The general structure of a TFET is shown in Fig. 1.5(a). It shares the same device structure as the typical MOSFET. However, the drain and source doping are complementary of each other. TFET is basically a gated P-I-N structure which makes use of the BTBT mechanism to give rise to the ON-state current. Fig. 1.5(b) shows the energy band along the source to drain in order to illustrate the operating mechanism of TFET. At the OFF-state, the tunneling barrier width ( $W_T$ ) is substantially large which prevents the carriers in the source from tunneling to the channel. The leakage current of TFET is expected to be smaller than that of MOSFETs since the high energy tail electrons are cut off by the band gap in the source. To switch on n-TFETs, a positive gate voltage is applied across the channel region which pulls the energy band down as shown by blue line in Fig. 1.5(b). The tunneling barrier is reduced exponentially which allows the carriers to tunnel from the source to the channel contributing to the ON-state current.

Recent theoretical research reports on TFETs reveal that TFET has the potential for the low power application with the  $V_{DD}$  operation below 0.5 V thanks to its steeper switching behavior and low OFF-state current. In this thesis, TFET is explored as a steep-slope transistor to address the power consumption issue.

**Fig. 1.5.** (a) Schematic of P-I-N TFET, (b) Energy band along source to drain for OFF and ON-state. At the OFF-state, the tunneling barrier width  $(W_T)$  is large which prohibits the carriers from the source to tunnel to the channel region and the high energy carriers are filtered out by the band gap. Thus, the leakage current of TFET is expected to be lower. At the ON-state,  $W_T$  is reduced by the gate potential which permits band-to-band tunneling to occur, giving rise to an ON-state current.

#### **1.3.2 Development and Designs of TFET Technology**

In 1992, the first lateral surface tunnel transistors (STTs) based on III-V compound semiconductors [68]-[69] were proposed by Baba and Uemura after the discovery of the BTBT phenomenon by Leo Esaki in 1957 [70]. Since then, there have been extensive experimental research works conducted on improving the performance of TFETs based on Si [61]-[62], germanium (Ge) [71]-[73], and III-V [74]-[76]. In addition, various theoretical and simulation works with the aim of understanding the physical insights for device design of TFET have been carried out [64], [77]-[88].

Although a steeper switching characteristic can be achieved in TFETs, the  $I_{ON}$  of TFETs is still too low to satisfy the drive current requirement for low power application projected by the International Technology Roadmap for Semiconductors (ITRS) [89]. This calls for innovations and designs to enhance the  $I_{ON}$  of TFETs. Fig. 1.6 shows the main design considerations of TFET.

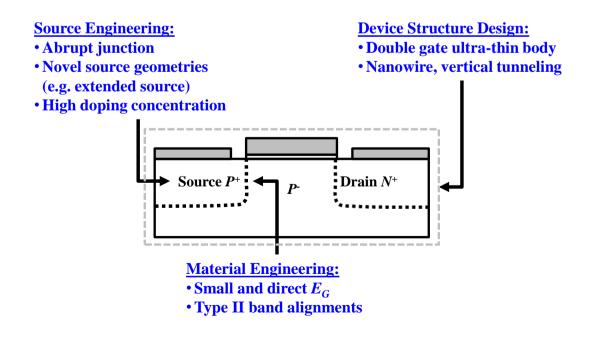

Fig. 1.6. Key points for the design considerations of TFET.

The BTBT rate of TFETs can be further improved by engineering the source junction. A highly doped and abrupt junction is desired for achieving high electric field and narrow depletion width at the tunneling junction. High electric field and narrow depletion region reduce the tunneling barrier width which in turn increases the BTBT rate exponentially. Specially-designed source structures, such as extended source structures, have been proposed to improve the *S* and drive currents of TFETs [61], [90].

Since the BTBT rate is inversely dependent on the band gap, materials with smaller and direct band gap are preferred. Ge and III-V semiconductors are potential materials due to their larger BTBT rate resulted from the smaller and direct band gaps. Another way of increasing the tunneling rate is the use of heterojunction with type II staggered band alignment [91]-[99]. The conduction band offset in the type II heterojunction reduces the effective band gap (energy difference between conduction band (CB) in the channel and valence band (VB) in the source). Thus, higher tunneling current can be obtained from the well-designed type II heterojunction.

Similar to the conventional MOSFETs, the current of TFETs is also modulated by the gate potential. Hence, it is important to enhance the gate control over the tunneling junction for the current improvement. This can be achieved by using the same device structures employed in the MOSFETs, such as multigate structure with ultra-thin body [100]-[101]. In addition, novel device structures have been proposed, including vertical TFETs and TFETs with source tunneling junction extending into the channel region.

## **1.4 Objectives of Thesis**

The main objective of this thesis is to address the power consumption issue faced by the current CMOS technology via the reduction of power supply voltage. Two technology approaches are explored. The first option is to employ MOSFETs with alternative channel materials which offer higher product of carrier injection velocity and DOS. The second approach is to use TFET. For MOSFETs with high carrier injection velocity and DOS, various channel materials across group IV, III-V, and 2D atomically thin materials are explored to assess their potentials as alternative channel materials beyond silicon. For group IV semiconductors, Ge<sub>1-x</sub>Sn<sub>x</sub> alloy is investigated by examining its electronic properties and ballistic  $I_{ON}$  at different tin (Sn) compositions. 2D materials can be an attractive alternative for low power applications due to their larger band gap and the excellent electrostatic integrity inherent in a two-dimensional system. In this context, 2D materials from group IV (hydrogenated silicene and germanene) are evaluated and compared to the 2Dtransition metal dichalcogenides (2D-TMDs) in terms of their ballistic  $I_{ON}$ . Subsequently, the voltage scalability of ultra-thin body transistor employing channel materials from group IV, III-V, and 2D materials is assessed based on the ITRSprojected device specifications for high performance (HP) and low power (LP) technologies. For the  $V_{DD}$  reduction by employing TFET, a novel TFET device structure based on type II tunneling junction is proposed, aiming at improving the ON-current and the subthreshold swing. The findings from this thesis are part of the research efforts in scaling down the  $V_{DD}$  to mitigate the power consumption issues for highly scaled technology nodes.

## **1.5 Organization of Thesis**

This thesis comprises 6 chapters. Chapter 1 covers the introduction of this research work, including the background information on the power consumption problems faced in the semiconductor industry and the possible solutions for the  $V_{DD}$  reduction to reduce the power consumption in IC chips.

In Chapter 2, the electronic properties of  $Ge_{1-x}Sn_x$  alloy are studied by theoretically calculating its electronic band structures (*E-k*) at different Sn compositions. The *E-k* dispersion is obtained from the empirical pseudopotential method (EPM) where the fitting parameters are adjusted such that the band gaps from the calculated *E-k* dispersion match with those from the experimental results. The effective masses for both electron and hole are subsequently extracted along various high symmetry lines using a parabolic line fit. In addition, employing the effectivemass Hamiltonian for diamond semiconductor, the band edge dispersion at the  $\Gamma$ valley calculated by 8-band k.p. method is fitted to that obtained from the EPM approach. This is to derive the Luttinger-like parameters for  $Ge_{1-x}Sn_x$  alloys. Using the extracted effective mass from the bulk GeSn material system, the equivalent effective masses of GeSn in the 2-dimensional system are projected. Subsequently, the ballistic  $I_{ON}$  of double-gate ultra-thin body n-MOSFET based on GeSn is calculated in order to assess their ultimate ON-current performance.

In Chapter 3, the ballistic  $I_{ON}$  of double-gate ultra-thin body (DG-UTB) transistors based 2D materials are investigated. The 2D materials studied consist of hydrogenated silicene and germanene, i.e., silicane and germanane, respectively. The electronic band structures of silicane and germanane are calculated using the first-principles density functional theory. Subsequently, the ballistic performance of MOSFETs is evaluated via the semi-classical ballistic transport model. The  $I_{ON}$  of

silicane and germanane are compared with those of 2D-transistion metal dichalcogenides (2D-TMDs) based on the ITRS projected requirements for HP and LOP technologies.

In Chapter 4, the ultimate voltage scalability of double-gate ultra-thin body (DG-UTB) MOSFETs employing materials from group IV, III-V, and 2D materials are examined based on the requirements for high performance (HP) and low power (LP) logic applications. The device specifications for HP and LP technologies are obtained from the 2013 edition of the International Technology Roadmap for Semiconductors (ITRS). The channel materials considered are composed of Ge, GaSb, InAs,  $In_{0.3}Ga_{0.7}Sb$ , and 2D materials [black phosphorus (BP), silicane, germanane,  $MoS_2$ ,  $MoSe_2$ ,  $WS_2$ ,  $WSe_2$ ]. The performance metrics (minimum scalable  $V_{DD}$ , power delay product (PDP)) are benchmarked based on the ones of Si MOSFET.

In Chapter 5, a novel TFET structure with an L-shaped Ge source is proposed. The device consists of a Ge source that extends underneath a Si-channel region and it is separated from the drain region by an insulator (SiO<sub>2</sub>). By optimizing the overlap length of the extended source ( $L_{OV}$ ) and the Si body thickness ( $T_{Si}$ ), the current due to vertical band-to-band tunneling (BTBT) of the Ge–Si hetero-junction could be increased significantly and is scalable with  $L_{OV}$ . In addition, a steeper subthreshold swing can be achieved due to a more uniformly distributed electrostatic potential along the tunneling heterojunction.

Chapter 6 summarizes the key findings of this thesis and provides possible future directions based on the works carried out.

## **Chapter 2**

# GeSn Alloy as Channel Material for Metal-Oxide-Semiconductor Field-Effect Transistors

## **2.1 Introduction**

As discussed in Chapter 1, GeSn alloys can be used in transistors and its material properties can be engineered by tuning the Sn composition. By tuning the Sn composition, the band gap of  $Ge_{1-x}Sn_x$  alloys exhibits a transition from indirect to direct. The tunable direct band gap of  $Ge_{1-x}Sn_x$  makes possible the fabrication of optical and electronic devices with group IV materials using a complementary-metal-oxide-semiconductor (CMOS) compatible process flow.

The GeSn material system can be grown epitaxially using various growth techniques such as molecular beam epitaxy (MBE) [102]-[114] and chemical vapor deposition (CVD) [115]-[120]. Pulsed UV laser annealing of amorphous Ge-Sn film has been used to synthesize the metastable crystalline  $Ge_{1-x}Sn_x$  alloys [121]. Other techniques used to grow crystalline  $Ge_{1-x}Sn_x$  are dc-diode sputtering [122] and RF sputtering [123]-[125]. An optical absorption measurement for diamond cubic  $Ge_1$ .  $_xSn_x$  alloys performed by He *et al.* [108] has shown that the range of direct energy gap of  $Ge_{1-x}Sn_x$  to be  $0.35 < E_g < 0.80$  eV for 0.15 < x < 0. Later, Guevara *et al.* [125] reported that the critical Sn composition ( $x_c$ ) corresponding to the transition from indirect to direct band gap is experimentally observed to lie between  $0.10 < x_c < 0.13$  determined from transmittance measurements using a fast-Fourier-transform infrared interferometer. D<sup>'</sup>.Costa *et al.* [120] and R. Chen *et al.* [113] reported the critical

concentration to be 0.11 and 0.071, respectively. First-principles and empirical methods have been used for the calculations of  $\text{Ge}_{1-x}\text{Sn}_x$  alloys physical parameters. From first-principles calculations, the optical band gap bowing parameter (*b*) is reported to be 2.06 [126], 2.75 [127], 2.49 [128], and 1.90 [129] while calculations based on Virtual Crystal Approximation (VCA) generally give a smaller optical band gap bowing (0.94 [130], 0.25 [131], 0.4 [132], and 0.30 [133]).

The important parameters associated with the band structure of  $Ge_{1-x}Sn_x$  have not been fully examined to date. One of the important fundamental parameters used in the design of electronic and optical devices is the effective mass. Most of the studies of  $Ge_{1-x}Sn_x$  alloys have focused on band gaps and critical composition. However, the present lack of investigation on the effective mass parameters of  $Ge_{1-x}Sn_x$  alloys has accentuated the need for theoretical calculation of  $Ge_{1-x}Sn_x$  effective mass parameters.

In this Chapter, the empirical pseudopotential method (EPM) is adopted for calculating the band structures of  $\text{Ge}_{1-x}\text{Sn}_x$  alloys along high symmetry lines in the Brillouin zone for Sn composition varying from 5% to 20%. The effective masses of electron and hole are extracted from the band edges using a parabolic line fit. Based on the band gap energies at L valley and  $\Gamma$  valley obtained from fitting the experimental data, the adjustable parameters of EPM are tuned in order to reproduce the band features that are in good agreement with experimental data.

This Chapter is organized as follows: A brief background of GeSn alloy research progress is discussed in section 2.1. Empirical pseudopotential method (EPM) and  $Ge_{1-x}Sn_x$  band structure calculations approaches using EPM are described in Section 2.2.1 and 2.2.2, respectively. In Section 2.2.3, the results of  $Ge_{1-x}Sn_x$  band structures calculations and effective masses are presented and discussed. In Section 2.3, we review the 8-band k.p model and the derivation of the Luttinger parameters

for  $\text{Ge}_{1-x}\text{Sn}_x$  at different Sn composition. The ballistic  $I_{ON}$  of double-gate ultra-thin body n-channel metal-oxide-semiconductor field-effect transistor (n-MOSFET) based on GeSn alloy is discussed in Section 2.4. Section 2.5 summarizes the key points of this chapter.

## 2.2 Electronic Band Structure Analysis of GeSn Alloy

#### 2.2.1 The empirical pseudopotential method

The EPM method [134] is employed for the calculation of the electronic band structure of  $\text{Ge}_{1-x}\text{Sn}_x$  with the diamond cubic structure. The EPM is based on the orthogonalized plane wave (OPW) [135] method where the crystal wavefunction is constructed to be orthogonal to the core states. The pseudopotential Hamiltonian of semiconductors is given by:

$$H = -\frac{\hbar^2}{2m} \nabla^2 + V_p(\mathbf{r}), \qquad (2.1)$$

where  $V_p$  is the pseudopotential of the crystal that can be expanded into a Fourier series over the reciprocal lattice *G* as:

$$V_{p}(\boldsymbol{r}) = \sum_{\boldsymbol{G}} \left( V^{S}(\boldsymbol{G}) S^{S}(\boldsymbol{G}) + i V^{A}(\boldsymbol{G}) S^{A}(\boldsymbol{G}) \right) e^{i \boldsymbol{G} \cdot \boldsymbol{r}}.$$

(2.2)

In Eq. 2.2,  $S^{S}(G)$  and  $S^{A}(G)$  are the symmetric and asymmetric structural factors, respectively while  $V^{S}(G)$  and  $V^{A}(G)$  are the symmetric and asymmetric pseudopotential form factors, respectively. They are related to the cation atomic potential  $V_{1}(G)$  and anion atomic potential  $V_{2}(G)$  in the unit cell by:

$$V^{s}(\boldsymbol{G}) = \frac{1}{2} \left[ V_{1}(\boldsymbol{G}) + V_{2}(\boldsymbol{G}) \right], \qquad (2.3)$$

$$V^{A}(\boldsymbol{G}) = \frac{1}{2} \Big[ V_{1}(\boldsymbol{G}) - V_{2}(\boldsymbol{G}) \Big].$$

(2.4)