# STUDY OF CMOS COMPATIBLE RUTHENIUM OXIDE SCHOTTKY CONTACTS FOR ALGAN/GAN AND INALN/GAN DIODES AND HIGH MOBILITY TRANSISTORS GROWN ON SILICON (111) SUBSTRATES

LWIN MIN KYAW

NATIONAL UNIVERSITY OF SINGAPORE

2015

## STUDY OF CMOS COMPATIBLE RUTHENIUM OXIDE SCHOTTKY CONTACTS FOR ALGAN/GAN AND INALN/GAN DIODES AND HIGH MOBILITY TRANSISTORS GROWN ON SILICON (111) SUBSTRATES

LWIN MIN KYAW

(B.Eng. NUS)

## A THESIS SUBMITTED

## FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

## DEPARTMENT OF ELECTRICAL AND COMPUTER

## ENGINEERING

### NATIONAL UNIVERSITY OF SINGAPORE

2015

## DECLARATION

I hereby declare that this thesis is my original work and it has been written by me in its entirety.

I have duly acknowledged all the sources of information which have been used in the thesis.

This thesis has also not been submitted for any degree in any university previously.

LWIN MIN KYAW

30 July 2015

## ACKNOWLEDGEMENTS

I sincerely express my deepest sense of thanks and gratitude to my supervisors, Associate Prof. Chor Eng Fong and Dr. Sudhiranjan Tripathy. Prof. Chor Eng Fong's dedication and keen interest above all her great attitude to help me had been solely and mainly responsible for my work. Her timely advice, detailed analysis, scholarly suggestion and scientific approach have assisted me to a very great extent to complete this task. I do appreciate her altruism for working on revising my manuscripts and reports even in weekends and public holidays. As my co-supervisor, Dr.Sudhiranjan Tripathy also helped, advised and taught me through my PhD life in addition to providing the necessary resources and training in the Institute of Materials Research, and Engineering (IMRE).

I would also like to thank Dr. Milan Kumar Bera (Research Fellow), Dr. Liu Yi (my senior, a fellow PhD student), Mr. Aju Abraham Saju (an undergraduate final year project student), Mr. Ngoo Yi Jie (Research Engineer), and Dr. Sarab Preet Singh (Research Fellow) for their dedicated help and support to this work. Without them, I could not complete this task..

Special thanks also go to the Lab Officers in Centre for Optoelectronics (COE), Ms. Musni bte Hussain and Mr. Tan Beng Hwee, for their dedicated maintenance of clean room and their help in dealing with administrative matters. I would also give my appreciation to the staff members from IMRE, Dr. Thirumaleshwara Bhat, Mr. Surani Bin Dolmanan, Dr. Lakshmi Kanta Bera, Mr. Neo Kiam Peng, Ms. Teo Siew Lang, Dr. Tan Hui Ru, Ms. Doreen Lai, Dr. Tang Xiaosong, Mr. Lim Po Chong, Mr. Wang Weide and Dr. Zhang Zheng. My sincere thanks also extend to friends and colleagues in COE.

Last but not least, I would like to deeply express my thanks to my parents, sisters and girlfriend for their endless love, support, encouragement and patience throughout my life. Without them, I would not have become the man I am Today.

## Table of Contents

| Chapter 1: Introduction1                                                                                                               |                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| 1.1 Properties of Gallium Nitride                                                                                                      | 1                                                        |

| 1.2 GaN based High Electron Mobility Transistors                                                                                       | 4                                                        |

| 1.2.1 GaN HEMT heterostructure growth                                                                                                  | 4                                                        |

| 1.2.2 Development of GaN based HEMTs                                                                                                   | 7                                                        |

| 1.2.3 AlGaN/GaN HEMTs technology                                                                                                       | 11                                                       |

| 1.2.4 InAlN/GaN HEMTs technology                                                                                                       | 12                                                       |

| 1.2.5 Advantages of GaN HEMTs over Si LDMOSFETs                                                                                        | 13                                                       |

| 1.3 Challenges and motivations                                                                                                         | 15                                                       |

| 1.3.1 Cost                                                                                                                             | 15                                                       |

| 1.3.2 Gate Leakage and Thermal Stability                                                                                               | 16                                                       |

| 1.3.3 Self heating and thermal conductivities of GaN based HEMTs                                                                       | 22                                                       |

| 1.4 Synopsis of the thesis                                                                                                             | 23                                                       |

| Chapter 2: Physics in GaN-based devices, fabrication and characterization techniques                                                   |                                                          |

|                                                                                                                                        |                                                          |

|                                                                                                                                        |                                                          |

| 2.1 Physics in GaN-based devices                                                                                                       | 25                                                       |

| <ul><li>2.1 Physics in GaN-based devices</li><li>2.1.1 Schottky contacts</li></ul>                                                     |                                                          |

| -                                                                                                                                      | 25                                                       |

| 2.1.1 Schottky contacts                                                                                                                | 25<br>27                                                 |

| 2.1.1 Schottky contacts<br>2.1.2 Operation principle of GaN HEMTs                                                                      | 25<br>27<br>29                                           |

| <ul> <li>2.1.1 Schottky contacts</li> <li>2.1.2 Operation principle of GaN HEMTs</li> <li>2.2 Device fabrication techniques</li> </ul> | 25<br>27<br>29<br>35                                     |

| <ul> <li>2.1.1 Schottky contacts</li></ul>                                                                                             | 25<br>27<br>29<br>35                                     |

| <ul> <li>2.1.1 Schottky contacts</li></ul>                                                                                             | 25<br>27<br>29<br>35<br>35                               |

| <ul> <li>2.1.1 Schottky contacts</li></ul>                                                                                             | 25<br>27<br>29<br>35<br>35<br>35                         |

| <ul> <li>2.1.1 Schottky contacts</li> <li>2.1.2 Operation principle of GaN HEMTs</li> <li>2.2 Device fabrication techniques</li></ul>  | 25<br>27<br>29<br>35<br>35<br>38<br>38                   |

| <ul> <li>2.1.1 Schottky contacts</li></ul>                                                                                             | 25<br>27<br>29<br>35<br>35<br>38<br>38<br>38<br>42       |

| <ul> <li>2.1.1 Schottky contacts</li></ul>                                                                                             | 25<br>27<br>29<br>35<br>35<br>38<br>38<br>38<br>42<br>44 |

| <ul> <li>2.1.1 Schottky contacts</li> <li>2.1.2 Operation principle of GaN HEMTs</li> <li>2.2 Device fabrication techniques</li></ul>  | 25<br>27<br>29<br>35<br>35<br>38<br>38<br>42<br>44<br>45 |

| 2.3.9 Atomic Force Microscope (AFM)                                              |

|----------------------------------------------------------------------------------|

| Chapter 3: Preliminary explorations of cost effective CMOS compatible, gold-free |

| Schottky contacts on InAlN/GaN grown on Si (111)                                 |

| 3.1 Introduction                                                                 |

| 3.2 Experimental Procedures                                                      |

| 3.3 Results and Discussion55                                                     |

| 3.4 Conclusion                                                                   |

| Chapter 4: Thermally robust RuOx Schottky diodes and HEMTs on n-GaN and          |

| InAlN/GaN heterostructure grown on 100 mm Si(111)69                              |

| 4.1 Introduction69                                                               |

| 4.2 Experimental Procedures                                                      |

| 4.3 Results and Discussions73                                                    |

| 4.4 Conclusion                                                                   |

| Chapter 5: Thermally robust RuOx based AlxGa1-xN/GaN Schottky HEMTs on 200       |

| mm diameter Si(111) substrates81                                                 |

| 5.1 Introduction                                                                 |

| 5.2 Experimental Procedures                                                      |

| 5.3 Results and Discussions                                                      |

| 5.4 Conclusion                                                                   |

| Chapter 6: Probing channel temperature profiles of semitransparent RuOx based    |

| Schottky contacts on InAlN/GaN HEMTs and AlGaN/GaN HEMTs on 200 mm               |

| diameter Si(111) by optical spectroscopy94                                       |

| 6.1 Introduction94                                                               |

| 6.2 Experimental Procedures95                                                    |

| 6.3 Results and Discussions                                                      |

| 6.4 Conclusion                                                                   |

| Chapter 7: Effects of annealing pressure and ambient on thermally robust RuOx    |

| Schottky Contacts on InAlN/AlN/GaN-on-Si(111) Heterostructure115                 |

| 7.1 Introduction115                                                              |

| 7.2 Experimental Procedures                                                      |

| 7.3 Results and Discussions117                                                   |

| 7.4 Conclusion                                                                   |

| Chapter 8: Single Contact Annealing Process for Both Gate-First and G                                                                                                | ate-Last RuO <sub>x</sub> |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| Gate In <sub>x</sub> Al <sub>1-x</sub> N/GaN HEMTs                                                                                                                   | 130                       |

| 8.1 Introduction                                                                                                                                                     | 130                       |

| 8.2 Experimental Procedures                                                                                                                                          | 130                       |

| 8.3 Results and Discussions                                                                                                                                          | 133                       |

| 8.4 Conclusion                                                                                                                                                       | 136                       |

| Chapter 9: Summary and suggested future work                                                                                                                         |                           |

| 9.1 Summary                                                                                                                                                          | 137                       |

| 9.1.1 Pre-RuO <sub>x</sub> investigations of CMOS compatible, gold-free Sch<br>on InAlN/GaN grown on Si (111)                                                        | •                         |

| 9.1.2 Thermally robust RuO <sub>x</sub> Schottky diodes and HEMTs or<br>InAlN/GaN heterostructure grown on 100 mm Si(111)                                            |                           |

| 9.1.3 Thermally robust RuO <sub>x</sub> based Al <sub>x</sub> Ga <sub>1-x</sub> N/GaN Schottky HEM diameter Si(111) substrates                                       |                           |

| 9.1.4 Probing channel temperature profiles of semitransparent<br>Schottky contacts on InAlN/GaN HEMTs and AlGaN/GaN H<br>mm diameter Si(111) by optical spectroscopy | IEMTs on 200              |

| 9.1.5 Effects of annealing pressure and ambient on thermally Schottky contacts on InAlN/AlN/GaN-on-Si(111) heterostructu                                             |                           |

| 9.1.6 Single Contact Annealing Process for Both Gate-First and G<br>Gate In <sub>x</sub> Al <sub>1-x</sub> N/GaN HEMTs                                               |                           |

| 9.2 Suggested future work                                                                                                                                            | 141                       |

| 9.2.1 Further developments of SCAP                                                                                                                                   | 142                       |

| 9.2.2 Reduction of $RuO_x$ gate resistance for RF performance                                                                                                        |                           |

#### LIST OF FIGURES

| Figure 1.1 Schematic drawing of cross sectional view of AlGaN/GaN (left)                |

|-----------------------------------------------------------------------------------------|

| and InAlN/GaN (right) heterostructure grown on Si(111) substrate7                       |

| Figure 1.2 Schematic cross-sections of (a) Schottky gate HEMT (b) p-GaN                 |

| gate HEMT or MIS gate HEMT8                                                             |

| Figure 1.3 The conventional gate-last fabrication process of HEMT9                      |

| Figure 1.4 Gate-first fabrication process of HEMT10                                     |

| Figure 1.5 Typical $I_D$ - $V_{GS}$ and $I_G$ - $V_{GS}$ curves of Schottky gate HEMT17 |

| Figure 1.6 Schematics of self-aligned gate first process flow20                         |

| Figure 1.7 Schematics of self-aligned gate-last process using dummy gate21              |

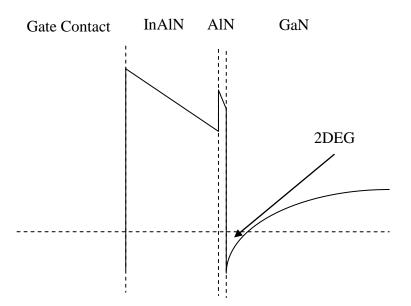

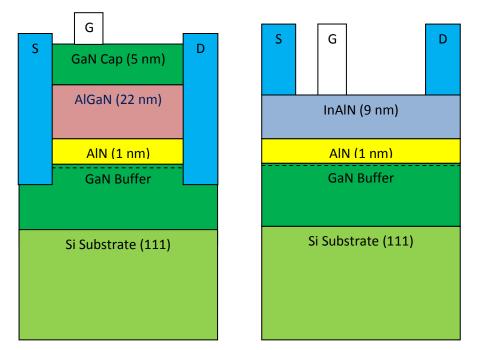

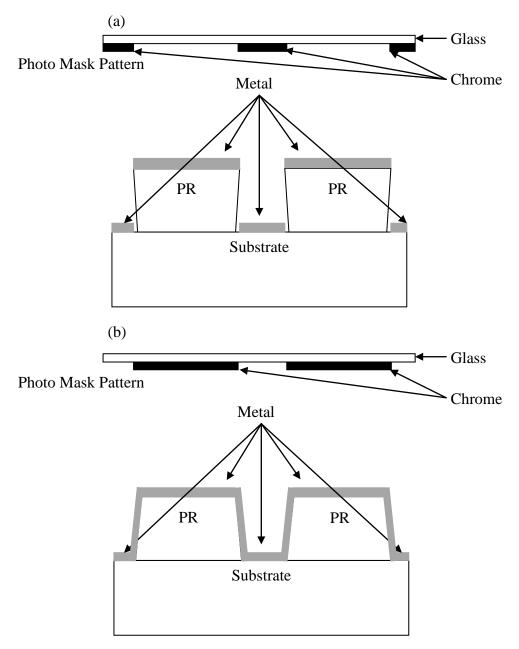

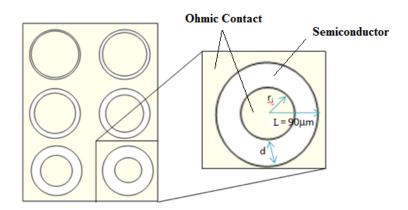

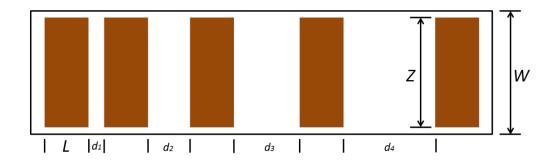

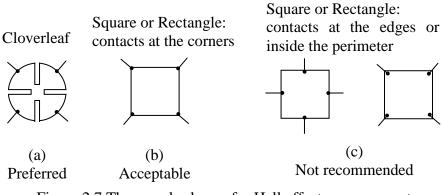

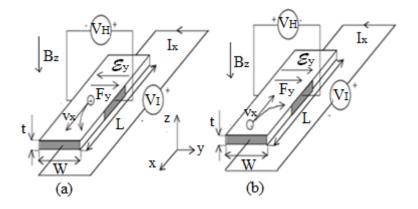

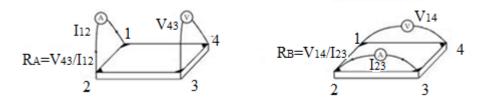

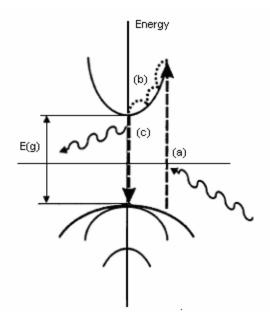

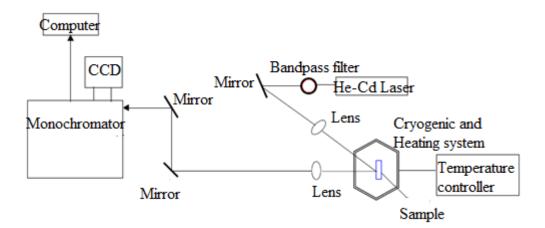

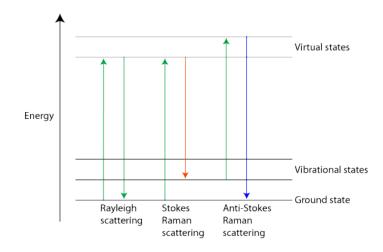

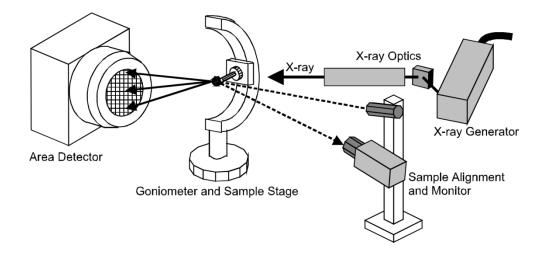

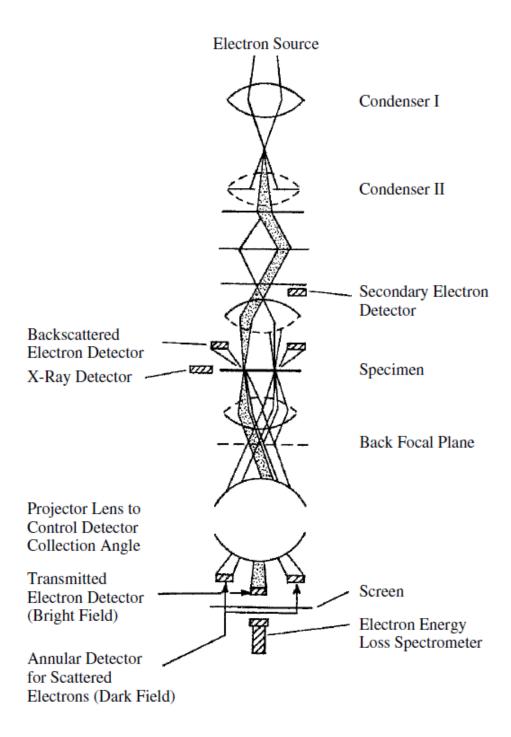

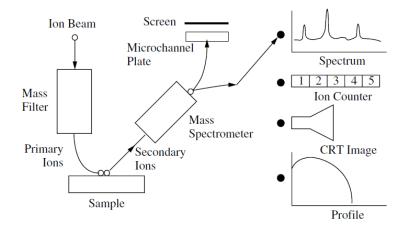

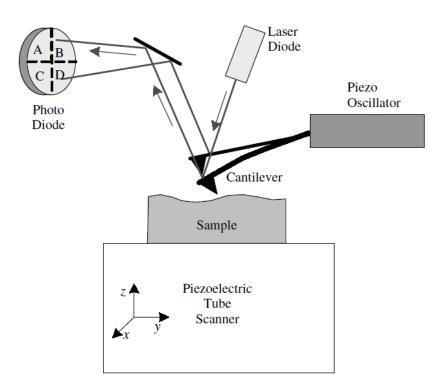

Figure 2.1 Index of interface behavior of various semiconductors versus the difference in electronegativity of their constituent elements [65]......26 Figure 2.2 Conduction band diagram of InAlN/GaN heterostructure with an Figure 2.3 Cross-section of the typical AlGaN/GaN (left) and InAlN/GaN (right) HEMTs. S, D and G means source, drain and gate contact respectively. Recessed source and drain contacts are used in AlGaN/GaN HEMTs......29 Figure 2.4 Schematic drawing showing the comparison of metal lift off process between (a) negative pattern (image reversal process) and (b) positive pattern. It is to be noted that in order to obtain the same pattern on the Figure 2.6 Linear transmission line methodtest structure with various spacing d. Z is the width of the contact pad and W is the width of the mesa isolation.37 Figure 2.8 Hall voltage  $(V_H)$  owing the presence of current flow and a perpendicular magnetic field across (a) p-type semiconductor, and (b) n-type semiconductor......41 Figure 2.9 Van der Pauw resistance measurement[85]......41 Figure 2.10 Photoluminescence process schematic. (a) Excitation. (b)

| Figure   | 2.11    | The       | schemati    | c rep    | resentation  | of     | simpl    | ified  | micro-  |

|----------|---------|-----------|-------------|----------|--------------|--------|----------|--------|---------|

| Photolu  | mines   | cence set | -up[90]     |          |              |        |          | •••••  | 43      |

| Figure 2 | 2.12 S  | cattering | mechanisr   | ns in m  | aterials     |        |          | •••••  | 44      |

| Figure 2 | 2.13Br  | uker D8   | Discover v  | with GA  | ADDS X-ray   | diffr  | action s | system | ı46     |

| Figure 2 | 2.14 T  | he princi | ple of tran | smissio  | n electron m | nicros | сору (Т  | TEM)   | [81]48  |

| Figure   | 2.15    | Schemat   | ic of a     | typical  | Secondary    | Ion    | Mass     | Spect  | rometry |

| (SIMS)   | [81]    | •••••     |             |          |              |        |          |        | 49      |

| Figure 2 | 2.16 Se | chematic  | of an aton  | nic forc | e microscop  | e[81]  |          |        | 51      |

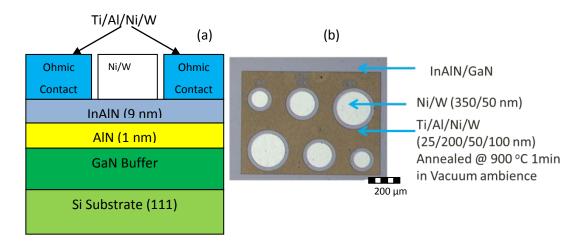

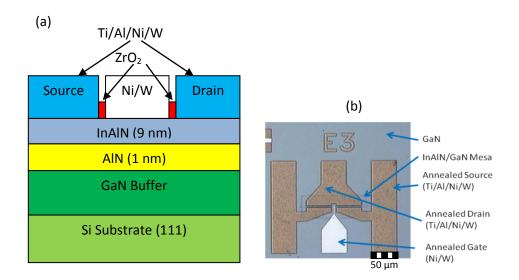

| Figure 3.1 (a) Schematic cross-section and (b) morphology of InAlN/GaN-on-                          |

|-----------------------------------------------------------------------------------------------------|

| Si(111) Schottky diodes                                                                             |

| Figure 3.2 (a) Schematic cross-section and (b) surface morphology of the                            |

| Schottky gate InAlN/GaN-on-Si(111) HEMTs55                                                          |

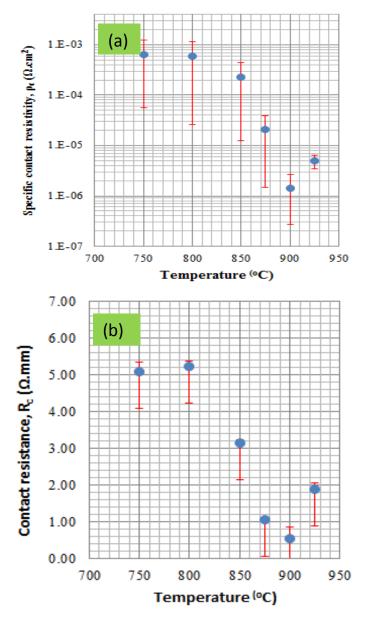

| Figure 3.3 Annealing temperature variation of (a) specific contact resistivity                      |

| and (b) contact resistance with an optimized Ti/Al/Ni/W (25/200/40/50 nm)                           |

| layer combination on InAlN/GaN-on-Si(111)56                                                         |

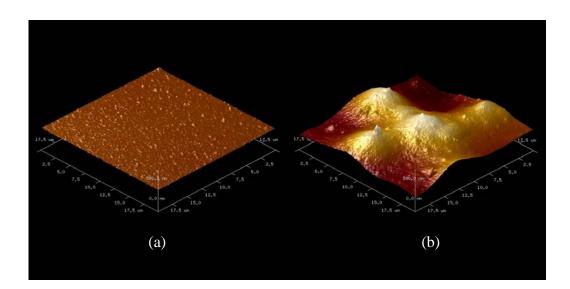

| Figure 3.4 AFM images of (a) Ti/Al/Ni/W (25/200/40/100 nm) contact                                  |

| annealed at 900 °C 1 min in vacuum, and (b) Ti/Al/Ni/Au (25/200/40/100 nm)                          |

| contact annealed at 850 °C 30 sec in vacuum                                                         |

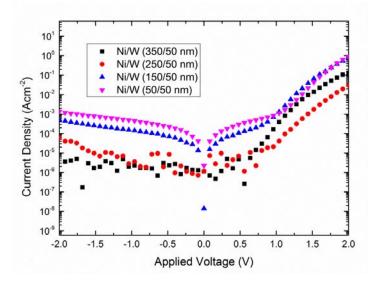

| Figure 3.5 I-V characteristics of Ni/W Schottky diodes as a function of Ni/W                        |

| thickness ratios. The contacts are under as-deposited condition (i.e., without                      |

| annealing)                                                                                          |

| Figure 3.6 I-V characteristics of Ni/W (350/50 nm) Schottky diodes as a                             |

| function of annealing temperature. The contact was annealed for 1 minute in                         |

| vacuum ambient60                                                                                    |

| Figure 3.7 Effects of Ni/W thickness ratio and annealing temperature on SBH                         |

| and ideality factor. The annealing was conducted in vacuum for 1 minute60                           |

| Figure 3.8 Operating temperature dependency of the Ni/W (350/50 nm)                                 |

| Schottky contact on InAlN/GaN. The contact has been annealed at 400 $^{\circ}C$ in                  |

| vacuum for 1 minute62                                                                               |

| Figure 3.9 I <sub>D</sub> -V <sub>DS</sub> characteristics of InAlN/GaN-on-Si HEMT with and without |

| $ZrO_2$ passivation. The threshold voltage, $V_{th}$ , with and without passivation                 |

| $ZrO_2$ is about -1.7 V and -1 V, respectively. The gate overdrive, $V_{OVERDRIVE}$ (=            |

|---------------------------------------------------------------------------------------------------|

| $V_{GS}$ - $V_{th}$ ), was increased in steps of 1 V63                                            |

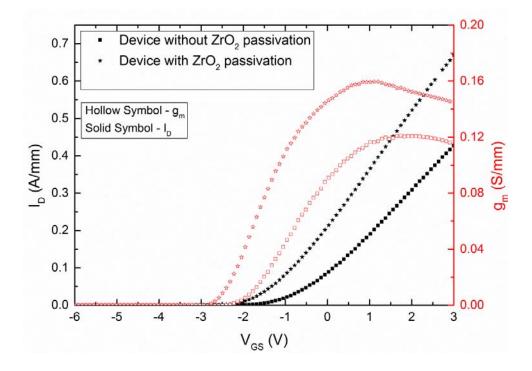

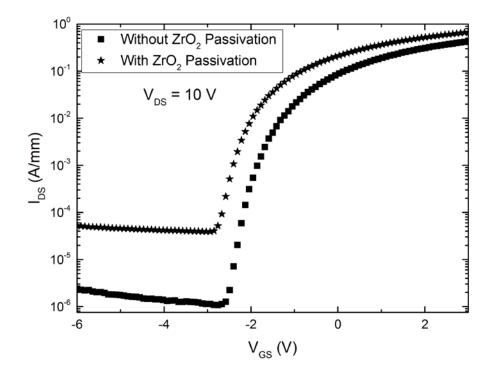

| Figure 3.10 ID-VGS characteristics of InAlN/GaN-on-Si HEMT with and                               |

| without $ZrO_2$ passivation at $V_{DS} = 10$ V64                                                  |

| Figure 3.11 The transfer characteristics of InAlN/GaN-on-Si(111) HEMTs                            |

| with and without $ZrO_2$ passivation at $V_{DS} = 10$ V64                                         |

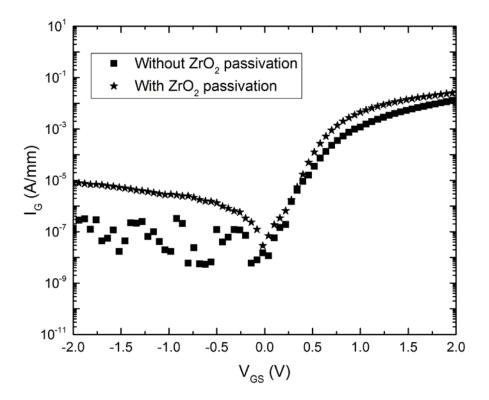

| Figure 3.12 $I_G$ - $V_{GS}$ characteristics of InAlN/GaN-on-Si(111) HEMTs with and               |

| without ZrO <sub>2</sub> passivation65                                                            |

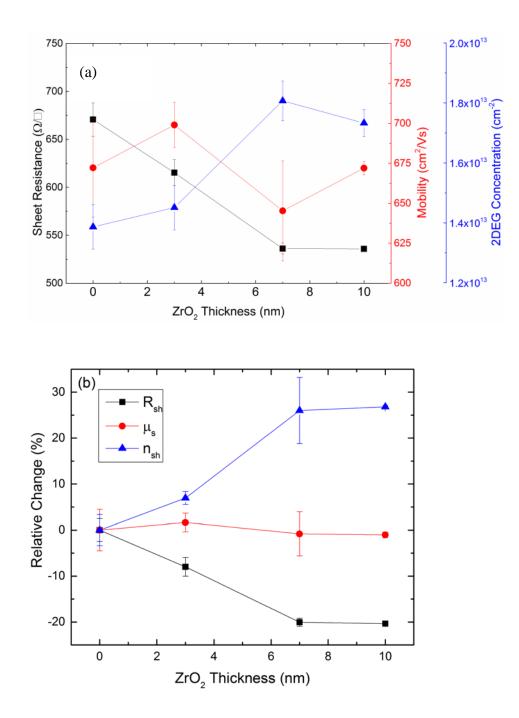

| Figure 3.13 Effects of $ZrO_2$ thickness on (a) absolute value and (b) relative                   |

| change of sheet resistance ( $R_{sh}$ , square), carrier mobility ( $\mu_s$ , circle) and carrier |

| concentration ( <i>n<sub>sh</sub></i> , triangle)67                                               |

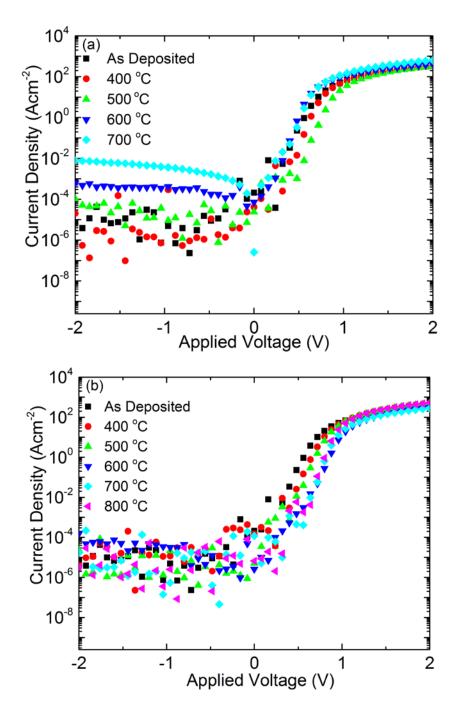

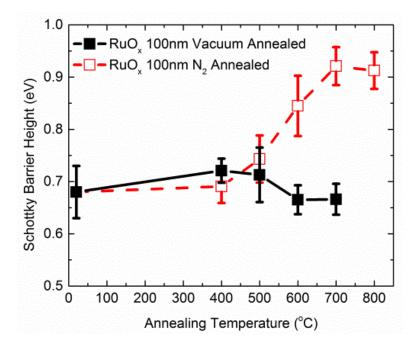

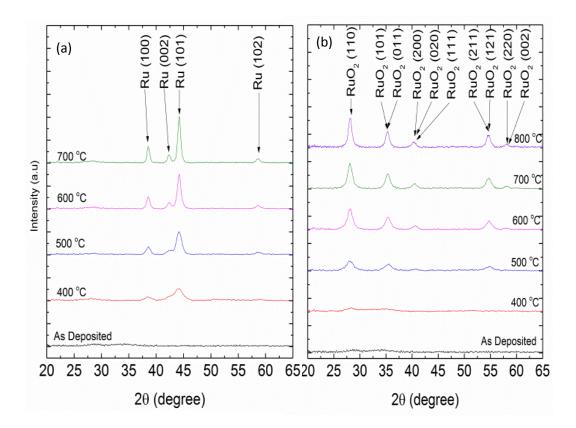

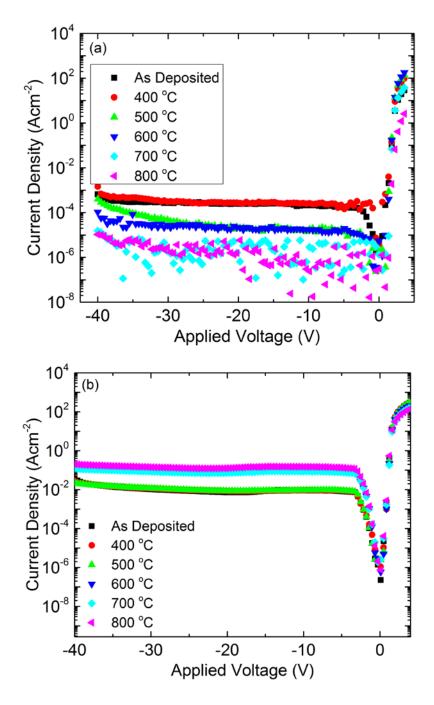

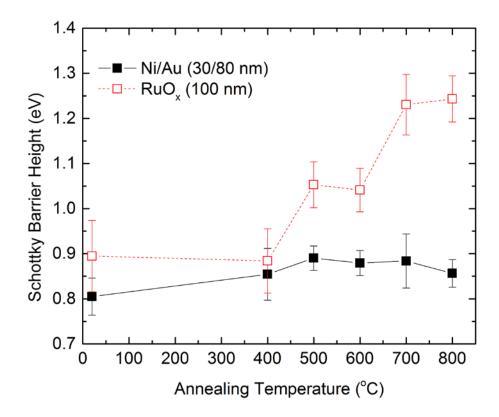

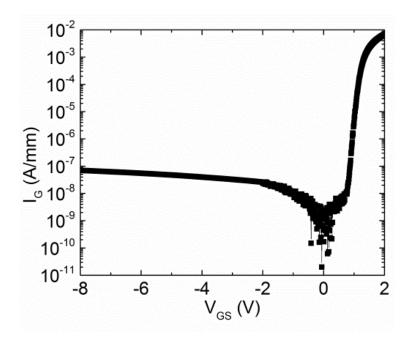

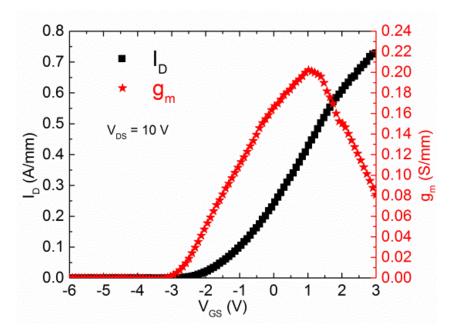

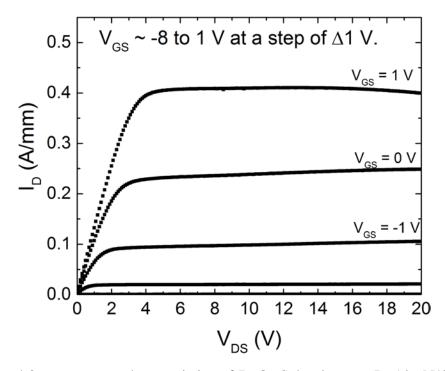

Figure 4.1 *I-V* characteristics of RuO<sub>x</sub> Schottky diodes on n-GaN-on-Si(111) substrate, annealed at various temperatures in (a) vacuum and (b) N<sub>2</sub> for 1 Figure 4.2 The effects of annealing temperatures on Schottky Barrier Height (SBH) of  $RuO_x$  Schottky diodes on n-GaN-on-Si(111) substrate, annealed in N<sub>2</sub> and vacuum for 1 minute......73 Figure 4.3 XRD spectra of RuOx annealed in (a) vacuum and (b) N<sub>2</sub> at 400, Figure 4.4 I-V characteristics of (a) RuOx and (b) Ni/Au Schottky diodes on In<sub>0.17</sub>Al<sub>0.83</sub>N/GaN-on-Si(111) HEMTs, for various annealing temperatures in N<sub>2</sub>. The annealing duration is 1 minute and the Ohmic contacts are Ti/Al/Ni/W Figure 4.5 The effect of annealing temperature on Schottky Barrier Height (SBH) of RuOx and Ni/Au on InxAl1-xN/GaN /Si (111) Schottky diodes annealed in N<sub>2</sub> for 1 minute.....77 Figure 4.6  $I_G$ - $V_{GS}$  characteristics (with floating drain) of RuO<sub>x</sub> Schottky gate  $In_xAl_{1-x}N/GaN$ -on-Si (111) HEMT, with the gate annealing at 700 °C in N<sub>2</sub>. 78 Figure 4.7 The  $I_D$  and  $g_m$  versus  $V_{GS}$  characteristics of RuO<sub>x</sub> Schottky gate In<sub>x</sub>Al<sub>1-x</sub>N/GaN-on-Si (111) HEMT, with gate annealing at 700 °C in N<sub>2</sub>......79 Figure 4.8 I<sub>D</sub>-V<sub>DS(pulsed)</sub> characteristics of RuO<sub>x</sub> Schottky gate In<sub>x</sub>Al<sub>1-x</sub>N/GaNon-Si(111) HEMTs, annealed at 700 °C. .....79

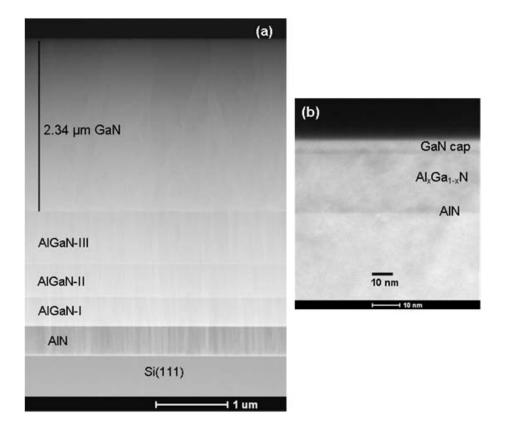

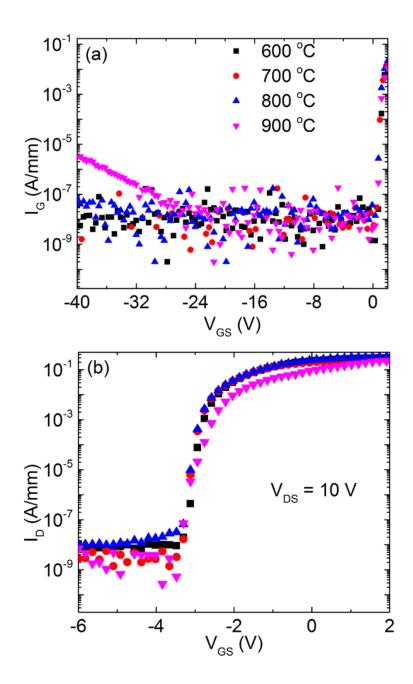

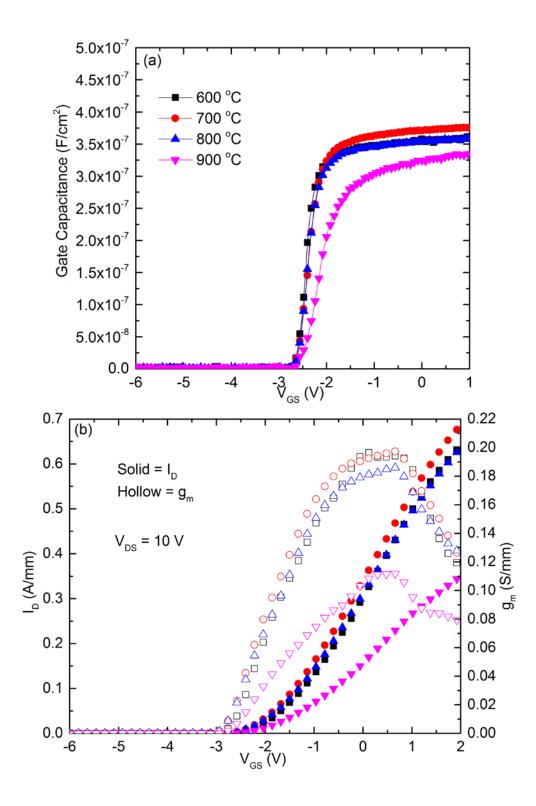

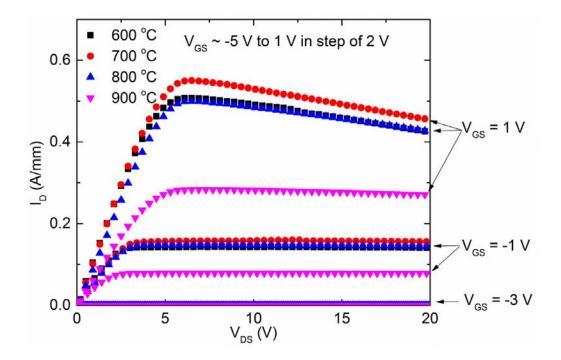

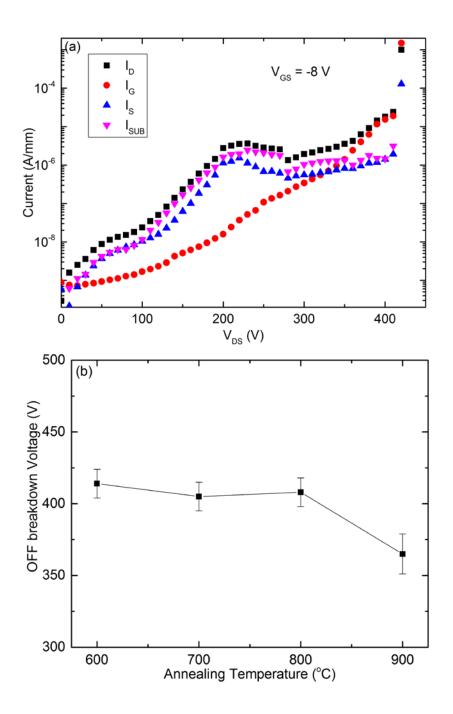

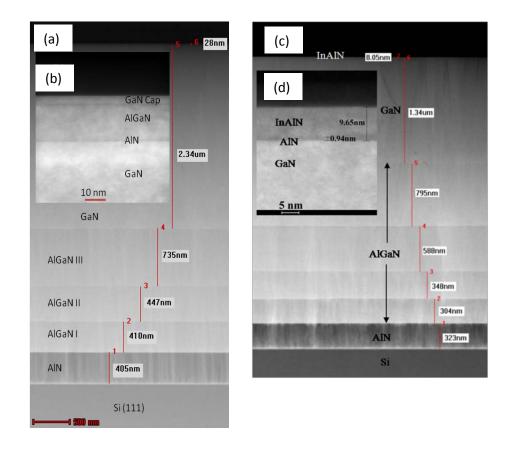

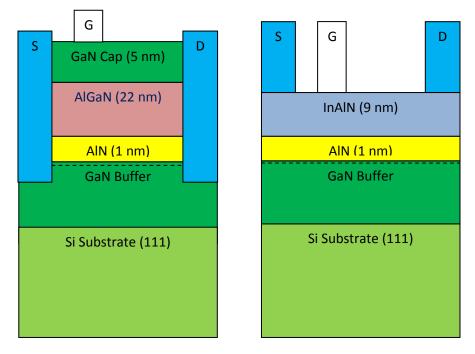

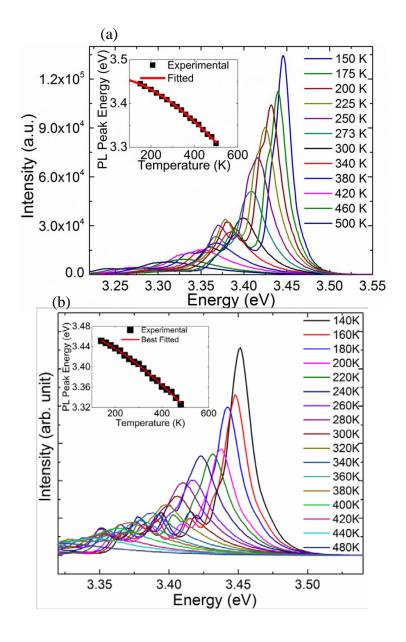

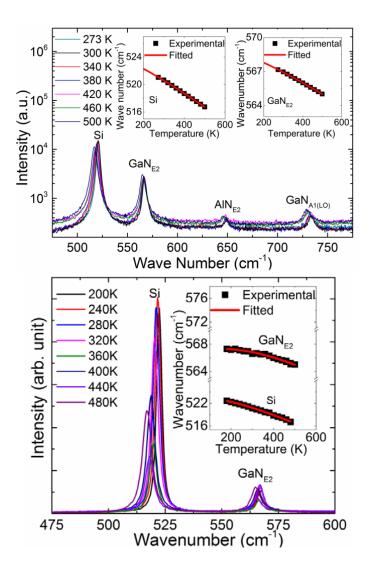

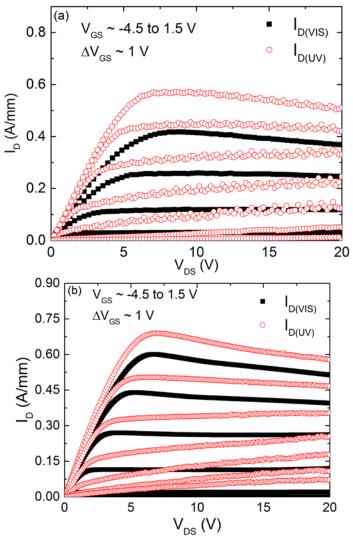

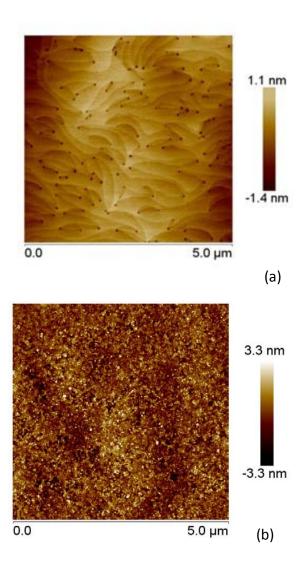

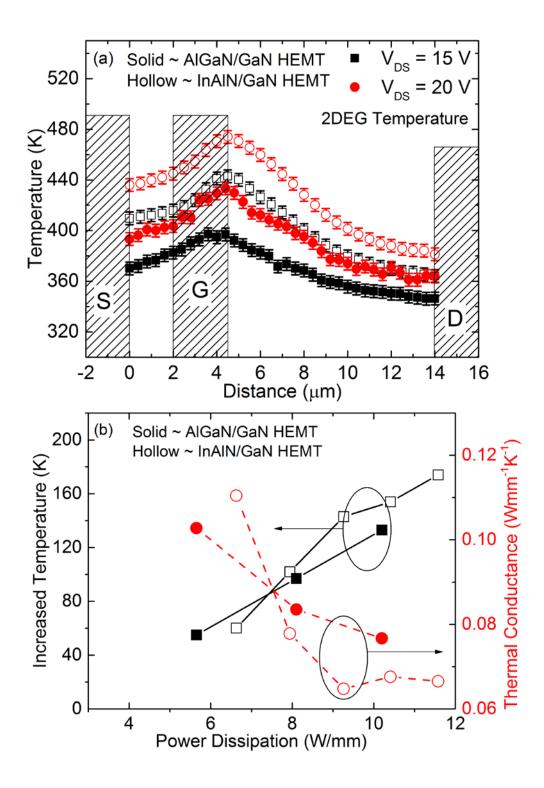

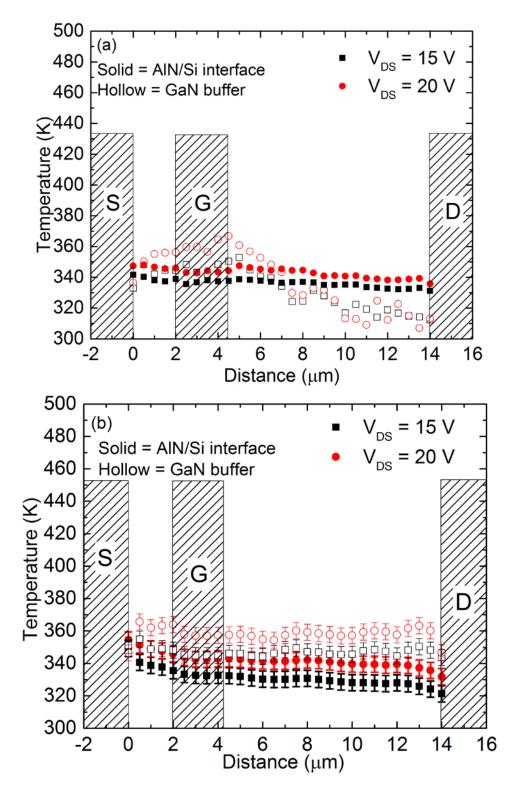

Figure 6.1 (a) The STEM image of the full Al<sub>x</sub>Ga<sub>1-x</sub>N HEMT structure showing the detailed configurations of epilayers used in this study. The inset (b) shows the STEM image of the top interfaces with  $Al_xGa_{1-x}N$  barrier and thin GaN cap. (c) The STEM image of the full In<sub>x</sub>Al<sub>1-x</sub>N HEMT structure showing the detailed configurations of epilayers used in this study. The inset (d) shows the STEM image of the top interfaces with  $In_xAl_{1-x}N$  barrier.......97 Figure 6.2 Schematics showing the cross section of AlGaN/GaN HEMTs (left) and InAlN/GaN HEMTs (right). The Source and Drain contacts (S & D symbols) of both HEMTs are Ti/Al/Ni/W with the same thickness (25/200/40/50 nm). AlGaN/GaN has ~ 50 nm recess etched Ohmic contact while InAlN/GaN has non recess etched Ohmic contact. The gate contact (G Figure 6.3 Micro-PL spectra of (a) AlGaN/GaN HEMT on Si substrate and (b)InAlN/GaN HEMT on Si substrate recorded at different temperatures from the device area used for optical temperature probing with 325 nm He-Cd laser line excitation. The inset shows the change in band edge PL peak energy as a function of sample temperature where the black square symbols represent the experimental results while the red line represents the best-fitted data using the Figure 6.4 Micro-Raman spectra of (a) AlGaN/GaN HEMT and (b) InAlN/GaN HEMT on Si substrate at different temperatures with 488 nm Arion laser line excitation. The insets show phonon peak shifts at different sample temperature for optical phonon of Si, and  $E_2$ -high of GaN. The black square symbols are the experimental results while the red lines are the fitted data using the phonon peak shifts and temperature relationship in Equation Figure 6.5  $I_D$ - $V_{DS}$  characteristics of (a) AlGaN/GaN HEMT and (b) InAlN/GaN HEMT under visible light illumination (solid symbols) and 325 nm UV PL illumination condition (hollow symbols). The dimensions of both HEMTs are as follows:  $L_{\rm gd} \sim 9.5 \ \mu {\rm m}$ ;  $L_{\rm gs} \sim 2 \ \mu {\rm m}$ ;  $L_{\rm g} \sim 2.5 \ \mu {\rm m}$ ; and  $W_{\rm g} = 2 \times$ Figure 6.6 AFM images of (a) AlGaN/GaN and (b) InAlN/GaN Figure 6.7 (a) The temperature profiles of 2DEG GaN channel region from 325 nm PL probing across source to drain regions of AlGaN/GaN HEMT and InAlN/GaN HEMT stack on 200 mm Si (111) at  $V_{DS} = 15$  and 20 V. (b) Temperature rise (square symbols) at the gate edge region between gate and drain and thermal conductance (circle symbols) of AlGaN/GaN HEMT and InAlN/GaN HEMT as a function of DC power dissipation......109 Figure 6.8 The average temperature profiles of GaN buffer layer and AlN/Si(111) interface measured between source and drain on the same (a) AlGaN/GaN HEMT and (b) InAlN/GaN HEMT device on Si by using optical phonon shift of Si and  $E_2$ -high phonon peak shift of GaN from 488 nm Raman

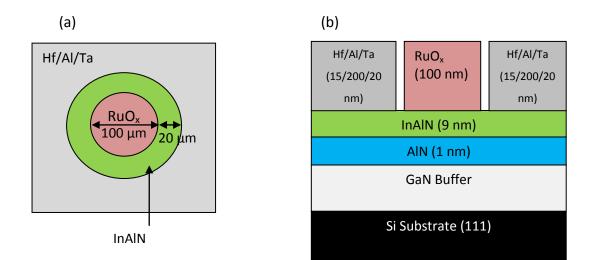

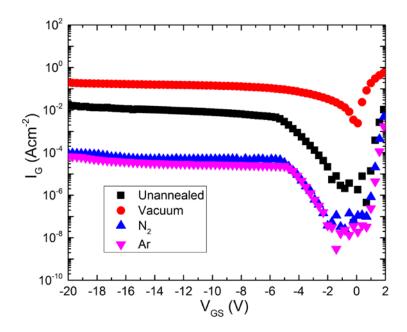

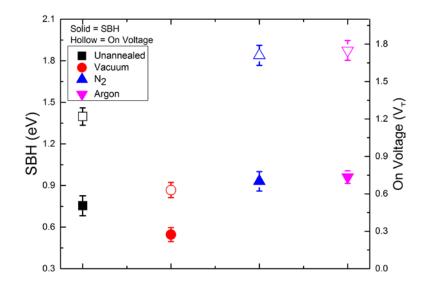

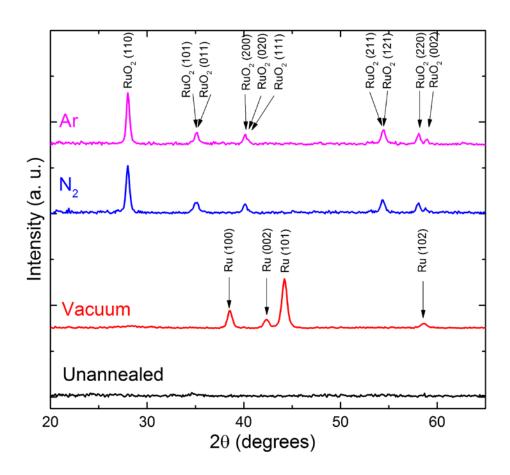

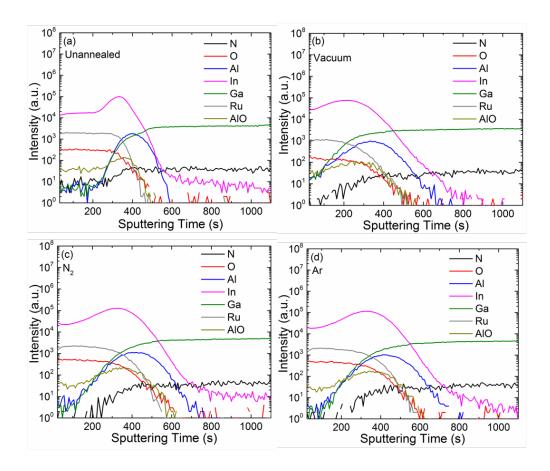

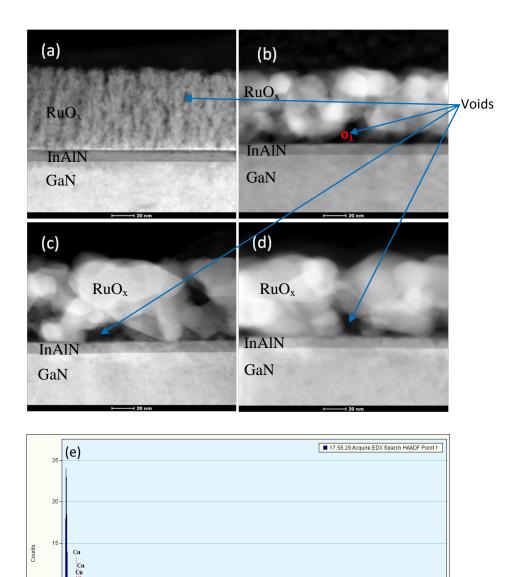

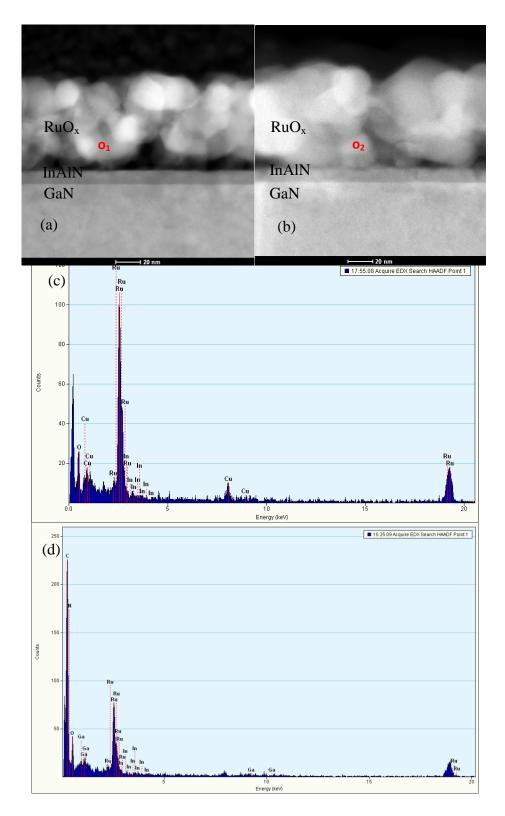

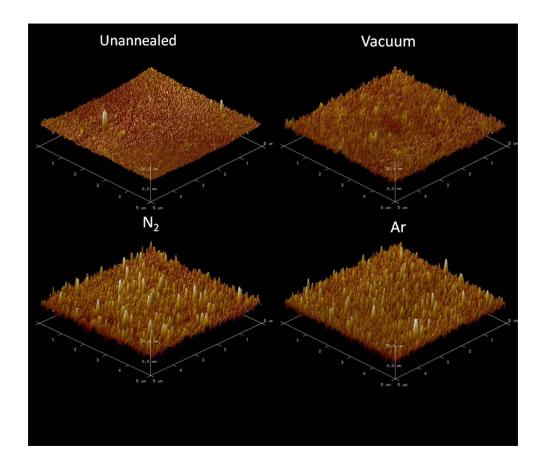

Figure 7.1 Schematic (a) top view and (b) cross sectional view of Schottky diodes with  $RuO_x$  (100 nm) as the anode and Hf/Al/Ta(15/200/20 nm) as the cathode. 116 Figure 7.2 Typical*I-V* characteristics of  $RuO_x$ Schottky diodes under different annealing conditions. Figure 7.3 The extracted SBHs (Solid Symbol) and On Voltages (Hollow Symbol) of RuO<sub>x</sub> Schottky diodes under different annealing conditions. The annealing temperature and duration are 800 °C and 1 minute, respectively..118 Figure 7.4 XRD spectra of RuOx Schottky diodes under different annealing conditions. (unannealed ~ Black, annealed in vacuum ~ Red, in N2 ~ Blue, and in Ar ~ Purple) at 800 °C for 1 minute......121 Figure 7.5 SIMS Profiles of RuO<sub>x</sub> Schottky diodes under different annealing conditions: (a) Unannealed, (b) annealed in vacuum, (c) annealed in N<sub>2</sub>, and (d) annealed in Ar. The annealing temperature and duration are 800 °C and 1 Figure 7.6 The HADDF-STEM images of RuOx Schottky diodes under different annealing conditions: (a) unannealed, (b) annealed in vacuum, (c) annealed in N<sub>2</sub> and (d) annealed in Ar. The annealing temperature and duration are 800 °C and 1 minute, respectively. The magnification is 710k. (e) The spot EDX spectrum at O<sub>1</sub> (void) indicated in (b). Cu and C are observed due to contamination during TEM sample preparation. Similar EDX spectra of voids are observed in unannealed, N2 annealed and Ar annealed samples....125 Figure 7.7 The HADDF-STEM images of RuOx Schottky diodes (a) annealed in vacuum and (b) annealed in Ar.. (c) The spot EDX spectrum at  $O_1$  indicated in (a) and (d) The spot EDX spectrum at O2 indicated in (b). Cu and C are observed due to contamination during TEM sample preparation......126 Figure 7.8 AFM images of RuO<sub>x</sub> Schottky diodes under different annealing conditions. The sample surface area  $(x \times y)$  is 5  $\mu$ m  $\times$  5  $\mu$ m. The minimum and maximum color scale for the z axis is -30 nm and 30 nm respectively. .128

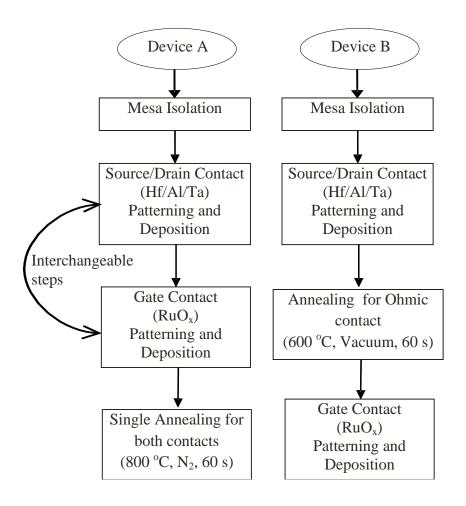

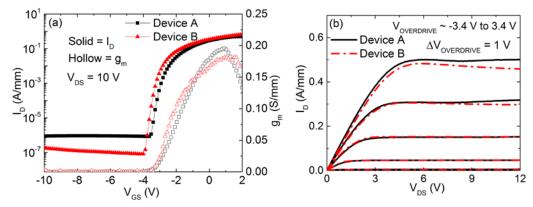

| Figure 8.1 The Fabrication Process flows of Device A and Device B. Device                        |

|--------------------------------------------------------------------------------------------------|

| A is made using the Single Contact Annealing Process (SCAP), while Device                        |

| B using the conventional gate-last process132                                                    |

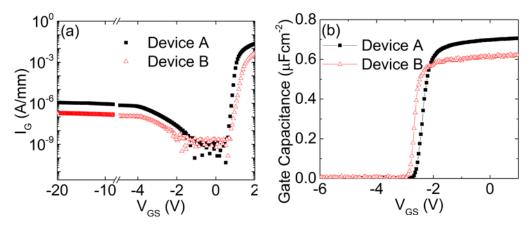

| Figure 8.2 (a) $I_G$ and (b) $C_{GS}$ as a function of $V_{GS}$ of Device A (black square)       |

| and Device B (red triangle)134                                                                   |

| Figure 8.3 (a) $I_{D(LOG)}$ and transconductance $(g_m)$ as a function of $V_{GS}$ at $V_{DS}$ = |

| 10 V and (b) $I_D$ - $V_{DS}$ at different $V_{OVERDRIVE}$ of Device A (black square, solid      |

| line) and Device B (red triangle, dash-dot line)136                                              |

#### LIST OF TABLES

| Table 1.1 Material parameters for Si, GaAs, SiC and GaN [2]2                                                  |

|---------------------------------------------------------------------------------------------------------------|

| Table 1.2 Figures of merit (FOMs) for various semiconductors at 300K for                                      |

| microwave power device applications. All FOMs are normalized with respect                                     |

| to those of silicon                                                                                           |

| Table 1.3Comparison of substrates available for GaN epitaxial growth[13, 14].                                 |

|                                                                                                               |

| Table 1.4 Spontaneous polarization ( $\mathbf{P}_{SP}$ ) and piezoelectric polarization ( $\mathbf{P}_{EP}$ ) |

| and theoretical calculation of the free electron density $(\boldsymbol{n}_s)$ in InAlN/GaN and                |

| AlGaN/GaN HEMTs[23]13                                                                                         |

| Table 1.5 Metal and alloy Schottky contacts to AlGaN/GaN Heterostructure 19                                   |

Table 7.1 Leakage current @ -20 V and SBH of RuO<sub>x</sub> Schottky diodes under different conditions. The annealing duration is 1 minute......120

## LIST OF ABBREVIATIONS

| 2DEG             | 2 Dimensional Electron Gas                        |

|------------------|---------------------------------------------------|

| AFM              | Atomic Force Microscopy                           |

| Al               | Aluminium                                         |

| ALD              | Atomic Layer Deposition                           |

| AlGaAs/InGaAs    | Aluminum Gallium Arsenide/Indium Gallium Arsenide |

| AlGaN/GaN        | Aluminum Gallium Nitride/Gallium Nitride          |

| Au               | Gold                                              |

| BCl <sub>3</sub> | Bromine trichloride                               |

| Cl <sub>2</sub>  | Chlorine                                          |

| CMOS             | Complementary Metal-Oxide-Semiconductor           |

| CTLM             | Circular Transmission Line Method                 |

| DC               | Direct Current                                    |

| DI               | De-Ionized                                        |

| EDS              | Energy-Dispersive X-ray Spectroscopy              |

| FE               | Field Emission                                    |

| FOM              | Figure Of Merit                                   |

| Ga               | Gallium                                           |

| GaAs             | Gallium Arsenide                                  |

| GaAs             | Gallium Arsenide                                  |

| HAADF            | High-Angle Annular Dark Field                     |

| HEMT             | High Electron Mobility Transistor                 |

| ICP              | Inductively Coupled Plasma                        |

| InAlN/GaN        | Indium Aluminum Nitride/Gallium Nitride           |

| IPA              | Iso-Propyl Alcohol                                                   |

|------------------|----------------------------------------------------------------------|

| Ir               | Iridium                                                              |

| LDMOSFET         | Laterally Diffused Metal Oxide Semiconductor Field Effect Transistor |

| LTLM             | Linear Transmission Line Method                                      |

| MIS              | Metal Insulator Semiconductor                                        |

| MOCVD            | Metal Organic Chemical Vapor Deposition                              |

| MOS              | Metal Oxide Semiconductor                                            |

| Ν                | Nitrogen                                                             |

| Ni               | Nickel                                                               |

| 0                | Oxygen                                                               |

| PA               | Power Amplifier                                                      |

| Pd               | Paladium                                                             |

| Pt               | Platinum                                                             |

| RF               | Radio Frequency                                                      |

| RIE              | Reactive Ion Etch                                                    |

| RTA              | Rapid Thermal Annealing                                              |

| Ru               | Ruthenium                                                            |

| RuO <sub>2</sub> | Ruthenium Dioxide                                                    |

| RuO <sub>x</sub> | Ruthenium Oxide                                                      |

| SBH              | Schottky barrier height                                              |

| Si               | Silicon                                                              |

| SiC              | Silicon Carbide                                                      |

| SIMS             | Secondary Ion Mass Spectroscopy                                      |

| STEM             | Scanning Transmission Electron Microscopy                            |

| TEM              | Transmission Electron Microscopy                                     |

|                  |                                                                      |

| Ti              | Titanium                                       |

|-----------------|------------------------------------------------|

| ToF-SIMS        | Time of Flight Secondary Ion Mass Spectroscopy |

| UV              | Ultra-Violet                                   |

| W               | Tungsten                                       |

| W-CDMA          | Wide Band Code Division Multiple Access        |

| WN <sub>x</sub> | Tungsten Nitride                               |

| XRD             | X-ray Diffraction                              |

| µ-PL            | Micro-Photo-Luminicence                        |

## LIST OF SYMBOLS

| Symbol                     | Property                                                                     | Unit                 |

|----------------------------|------------------------------------------------------------------------------|----------------------|

| $E_g$                      | bandgap                                                                      | eV                   |

| ε <sub>r</sub>             | relative permittivity                                                        | -                    |

| $E_c$                      | critical breakdown field                                                     | MV/cm                |

| $\mu_n$                    | electron mobility                                                            | $cm^2/V \cdot s$     |

| $\sigma_{th}$              | thermal conductivity                                                         | W/cm·K               |

| <i>v</i> <sub>t</sub>      | electron saturation velocity                                                 | cm/s                 |

| $\mathbf{P}_{\mathrm{SP}}$ | spontaneous polarization                                                     | cm <sup>-2</sup>     |

| $\mathbf{P}_{\mathrm{PE}}$ | piezoelectric polarization                                                   | cm <sup>-2</sup>     |

| $f_T$                      | unity current gain cut off frequency                                         | Hz                   |

| fmax                       | unity power gain cut off frequency                                           | Hz                   |

| $R_c$                      | contact resistance                                                           | Ω                    |

| $R_{sh}$                   | sheet resistance                                                             | $\Omega/\square$     |

| $ ho_c$                    | contact resistivity                                                          | $\Omega \cdot cm^2$  |

| $\phi_b$                   | Schottky barrier height                                                      | eV                   |

| $\phi_{m}$                 | metal work function                                                          | eV                   |

| Xs                         | electron affinity of the semiconductor                                       | eV                   |

| S                          | fermi level pinning factor                                                   | -                    |

| ΔΧ                         | the difference in electronegativity of constituent elements in semiconductor | eV                   |

| $m^*$                      | effective mass of carrier                                                    | kg                   |

| q                          | electron charge                                                              | С                    |

| h                          | planck constant                                                              | m <sup>2</sup> ·kg/s |

| λ                          | de Broglie wavelength                                                        | m                    |

| $k_B$                  | Boltzmann's constant                                                   | $m^2 \cdot kg \cdot s^{-2} \cdot K^{-1}$ |

|------------------------|------------------------------------------------------------------------|------------------------------------------|

| Т                      | temperature                                                            | °C or K                                  |

| $R_T$                  | total resistance                                                       | Ω                                        |

| $L_T$                  | transfer length                                                        | cm                                       |

| J                      | current density                                                        | Acm <sup>-2</sup>                        |

| $A^*$                  | Richardson's constant                                                  | Acm <sup>-2</sup> K <sup>-2</sup>        |

| n                      | ideality factor                                                        | -                                        |

| SBH                    | Schottky Barrier Height                                                | eV                                       |

| Ι                      | current                                                                | A/mm                                     |

| F                      | Lorentz force                                                          | Ν                                        |

| $B_z$                  | magnetic field in z direction                                          | Т                                        |

| $\mathcal{V}_X$        | velocity in x direction                                                | m/s                                      |

| $\epsilon_y$           | electromotive force in y direction                                     | V                                        |

| $J_x$                  | current density in x direction                                         | Acm <sup>-2</sup>                        |

| $n_s$                  | carrier density                                                        | cm <sup>-3</sup>                         |

| <i>n</i> <sub>sh</sub> | sheet carrier density                                                  | cm <sup>-2</sup>                         |

| $\mu_s$                | carrier mobility                                                       | $cm^2/V \cdot s$                         |

| $V_H$                  | Hall voltage                                                           | V                                        |

| $d_{hkl}$              | inter-planar spacing of any lattice planes with Miller indices {h k l} | -                                        |

| θ                      | Bragg's angle                                                          | degree                                   |

| $V_{GS}$               | gate to source voltage                                                 | V                                        |

| $V_{DS}$               | drain to source voltage                                                | V                                        |

| $V_{GD}$               | gate to drain voltage                                                  | V                                        |

| $V_{TH}$               | threshold voltage                                                      | V                                        |

| Voverdrive             | overdrive voltage                                                      | V                                        |

| I <sub>DSAT(max)</sub> | maximum drain current                                                  | A/mm                                     |

| $I_D$         | drain current                         | A/mm              |

|---------------|---------------------------------------|-------------------|

| $I_{OFF}$     | OFF State current                     | A/mm              |

| $I_{ON}$      | ON State current                      | A/mm              |

| IDSAT         | drain saturation current              | A/mm              |

| $I_G$         | gate current                          | A/mm              |

| $I_{SUB}$     | substrate current                     | A/mm              |

| SS            | sub-threshold swing                   | mV/decade         |

| $C_G$         | gate capacitance                      | Fcm <sup>-2</sup> |

| $C_{GA}$      | maximum accumulation gate capacitance | Fcm <sup>-2</sup> |

| $R_{on}$      | static on state resistance            | $\Omega$ ·mm      |

| $L_{gd}$      | gate to drain distance                | μm                |

| $L_{gs}$      | gate to source distance               | μm                |

| $L_g$         | gate length                           | μm                |

| $W_g$         | gate width                            | μm                |

| $E_{g0-2DEG}$ | bandgap of the GaN near 2DEG          | eV                |

| $T_{0}$       | Debye temperature                     | Κ                 |

| $\omega_0$    | phonon frequency at 0 K               | $cm^{-1}$         |

| С             | speed of light                        | m/s               |

| $R_a$         | average roughness                     | nm                |

| $R_q$         | root mean square roughness            | nm                |

#### LIST OF PUBLICATIONS

Journal Publications Directly Related to this Thesis

- L. M. Kyaw, A. A. Saju, Y. Liu, M. K. Bera, S. P. Singh, S. Tripathy, and E. F. Chor, "Thermally Robust RuO<sub>x</sub> Schottky Diodes and HEMTs on III-Nitrides", *Phys. Status Solidi C*, 11 (2014) 1–4.

- L. M. Kyaw, S. B. Dolmanan, M. K. Bera, Y. Liu, H. R. Tan, T. N. Bhat, Y. Dikme, E. F. Chor and S. Tripathy, "Influence of RuO<sub>x</sub> Gate Thermal Annealing on Electrical Characteristics of Al<sub>x</sub>Ga<sub>1-x</sub>N/GaN HEMTs on 200mm Silicon", *ECS Solid State Letters*, 3(2), (2014) Q5-Q8.

- S. Tripathy, L. M. Kyaw, S. B. Dolmanan, Y. J. Ngoo, Y. Liu, M. K. Bera,

S. P. Singh, H. R. Tan, T. N. Bhat, and E. F. Chor, "In<sub>x</sub>Al<sub>1-x</sub>N/AlN/GaN High Electron Mobility Transistor Structures on 200 mm Diameter Si(111) Substrates with Au-free Device Processing", *ECS Journal of Solid State Science and Technology*, 3(5), (2014) Q84-Q88.

- L. M. Kyaw, L. K. Bera, Y. Liu, M. K. Bera, S. P. Singh, S. B. Dolmanan, H. R. Tan, T. N. Bhat, E. F. Chor, and S. Tripathy, "Probing channel temperature profiles in Al<sub>x</sub>Ga<sub>1-x</sub>N/GaN high electron mobility transistors on 200 mm diameter Si(111) by optical spectroscopy", *Applied Physics Letters*, 105 (2014) 073504.

- L. M. Kyaw, L. K. Bera, T. N. Bhat, Y. Liu, H. R. Tan, S. B. Dolmanan, E. F. Chor, and S. Tripathy, "Channel temperature measurements in In<sub>x</sub>Al<sub>1</sub>. xN/GaN high electron mobility transistors on Si(111) using optical spectroscopy", *Journal of Vacuum Science & Technology B*, 33 (2015) 051203.

L. M. Kyaw, Y. Liu, M. Y. Lai, T. N. Bhat, H. R. Tan, P. C. Lim, S. Tripathy, and E. F. Chor, "Annealing Pressure Dependent RuO<sub>x</sub> Schottky Contacts on InAlN/AlN/GaN-on-Si(111) Heterostructure", *ECS Journal of Solid State Science and Technology*, 5 (2016) Q17.

#### **Other Journal Publications**

- Y. Liu, S. P. Singh, Y. J. Ngoo, L. M. Kyaw, M. K. Bera, G. Q. Lo, and E. F. Chor, "Low thermal budget Hf/Al/Ta ohmic contacts for InAlN/GaN-on-Si HEMTs with enhanced breakdown voltage", *Journal of Vacuum Science &Technology B*, 32 (2014) 032201.

- Y. Liu, S. P. Singh, L. M. Kyaw, M. K. Bera, Y. J. Ngoo, H. R. Tan, S. Tripathy, G. Q. Lo, and E. F. Chor, "Mechanisms of Ohmic Contact Formation and Carrier Transport of Low Temperature Annealed Hf/Al/Ta on In<sub>0.18</sub>Al<sub>0.82</sub>N/GaN-on-Si", *ECS Journal of Solid State Science and Technology*, 4(2), (2015) P30-P35.

- M. K. Bera, Y. Liu, L. M. Kyaw, Y. J. Ngoo, S. P. Singh, and E. F. Chor, "Positive Threshold-Voltage Shift of Y<sub>2</sub>O<sub>3</sub> Gate Dielectric InAlN/GaN-on-Si (111) MOSHEMTs with respect to HEMTs", *ECS Journal of Solid State Science and Technology*, 3(6), (2014) Q120-Q126.

- S. P. Singh, Y. Liu, Y. J. Ngoo, L. M. Kyaw, M. K. Bera, S. B. Dolmanan,

S. Tripathy and E. F. Chor, "Influence of PECVD deposited SiN<sub>x</sub> passivation layer thickness on In<sub>0.18</sub>Al<sub>0.82</sub>N/GaN/Si HEMT", *Journal of Physics D: Applied Physics,* (in press).

Conference Publications and Presentations Directly Related to this Thesis

- L. M. Kyaw, Y. Liu, M.K. Bera, Y. J. Ngoo, S. Tripathy, E. F. Chor, "Gold-free InAlN/GaN Schottky Gate HEMT on Si(111) Substrate with ZrO<sub>2</sub> Passivation", *ECS Transactions*, 53(2), (2013) 75-83.

- L. M. Kyaw, L. K. Bera, Y. Liu, M. K. Bera, S. P. Singh, S. B. Dolmanan, T. N. Bhat, E. F. Chor, and S. Tripathy, "Micro-Raman and Photoluminescence Thermography of AlGaN/GaN HEMTs Grown on 200 mm Si(111)", presented at the International Workshop on Nitride Semiconductors (IWN 2014), Wroclaw, Poland, August 24-29, 2014.

- L. M. Kyaw, Y. Liu, M. K. Bera, S. P. Singh, S. Tripathy, and E. F. Chor, "Electrical Characteristics of Au-free In<sub>x</sub>Al<sub>1-x</sub>N/GaN HEMTs Fabricated Using A Single Contact Annealing Process", presented at the International Workshop on Nitride Semiconductors (IWN 2014), Wroclaw, Poland, August 24-29, 2014.

- L. M. Kyaw, Y. Liu, M. Y. Lai, T. N. Bhat, H. R. Tan, P. C. Lim, S. Tripathy, and E. F. Chor, "Effect of Annealing Pressure and Ambient on Thermally Robust RuO<sub>x</sub> Schottky Contacts on InAlN/AlN/GaN-on-Si(111) Heterostructure", *ECS Transactions*, 66(1), (2015) 249-257.

#### Other Conference Publications and Presentations

- Y. Liu, M. K. Bera, L. M. Kyaw, G. Q. Lo, E. F. Chor, "Low resistivity Hf/Al/Ni/Au Ohmic Contact Scheme ton-Type GaN", World Academy of Science, Engineering and Technology 69, (2012) 602

- 6. M. K. Bera, Y. Liu, L. M. Kyaw, Y. J. Ngoo, and E. F. Chor, "Thickness Dependent Electrical Characteristics of InAlN/GaN-on-Si MOSHEMTs

with  $Y_2O_3$  Gate Dielectric and Au-free Ohmic Contact", *ECS Transactions*, 53(2), (2013) 65-74

- M. K. Bera, Y. Liu, L. M. Kyaw, Y. J. Ngoo, S. P. Singh, and E. F. Chor, "Fabrication and performance of InAlN/GaN-on-Si MOSHEMTs with LaAlO<sub>3</sub> gate dielectric using gate-first CMOS compatible process at low thermal budget", ECS Transactions, 61(4), (2014) 271.

- Y. Liu, L. M. Kyaw, M.K. Bera, S. P. Singh, Y. J. Ngoo, G.Q. Lo, and E.

F. Chor, "Low thermal budget Au-Free Hf-based ohmic contacts on InAlN/GaN heterostructure", *ECS Transactions*, 61(4), (2014) 319.

- S. P. Singh, Y. Liu, L. M. Kyaw, Y. J. Ngoo, M. K. Bera, S. Tripathy, and E. F. Chor, "Silicon nitride thickness dependence electrical properties of InAlN/GaN heterostructures", ECS Transactions, 61(4), (2014) 215.

#### SUMMARY

In this thesis, the study focuses on the development of gold-free, CMOS compatible Schottky contact for low cost, low leakage current and high performance GaN based diodes and high mobility transistors (HEMTs). Our preliminary investigations show that although Ni/W Schottky contact is cheaper than conventional Ni/Au Schottky contact (as W is lower cost than Au), the leakage current and thermal stability are only comparable to that of Ni/Au. Our further studies have demonstrated that RuO<sub>x</sub> Schottky contact yields lower leakage current and better thermal stability than Ni/Au Schottky contact on InAlN/GaN HEMTs. RuOx Schottky contact is more thermally stable up to 800°C compared to the latter at 600°C. In addition, RuO<sub>x</sub> Schottky contact exhitibts approximately 4 orders of magnitude lower leakage current than that of Ni/Au Schottky contact on InAlN/GaN HEMTs. Moreover, it has been found that the material and electrical characteristics of RuO<sub>x</sub> Schottky contact depend on the annealing ambient and pressure (vacuum, N2 and Ar; with  $N_2$  and Ar at the same pressure). Annealing pressure has been shown to play a vital role, while ambient has minimal effect, in changing the material and electrical characteristics of RuOx Schottky contact. With RuOx thin film being semitransparent to optical excitation wavelengths, accurate thermal investigations underneath the gate of both AlGaN/GaN HEMTs and InAlN/GaN HEMTs have been made possible by means of micro-Raman and Photoluminescence (PL) techniques. This is not achievable with conventional Ni/Au gate. The maximum temperatures of both AlGaN/GaN HEMTs and InAlN/GaN HEMTs occur at the gate edge between gate and drain and their values are 435 K and 475 K respectively. Lastly, with thermally robust  $RuO_x$  Schottky contact, we have demonstrated that the performance of InAlN/GaN HEMTs using a single contact annealing process is comparable to that of HEMTs using a conventional gate-last process. In conclusion, employing RuO<sub>x</sub> Schottky contact in GaN based HEMTs could realize CMOS compatibility, high thermal budget and low leakage HEMTs for low cost, high temperature, high speed and high power applications.

### Chapter 1: Introduction

#### 1.1 Properties of Gallium Nitride

Gallium nitride (GaN) based devices have been attractive to researchers since the deomonstration of successful GaN synthesis demonstrated by Johnson et al. in 1932 [1] for more than eight decades. They are promising for hightemperature, high-speed and high-power electronic applications due to the superior material properties of GaN and also that of related III-nitrides over silicon (Si), gallium arsenide (GaAs) and silicon carbide (SiC). These material properties are listed in Table 1.1, which highlights the material parameter comparison among Si, GaAs, SiC, and GaN[2]. It can be observed in Table 1.1 that GaN has the widest bandgap (3.4 eV) among these materials. This indicates that GaN has high resistance to thermally generated leakage current; hence, it is suitable for high temperature applications. In addition, owing to its high critical breakdown field (around 4 MV/cm), GaN-based electronic devices such as diodes and transistors would be able to operate in high power applications. In addition, excellent electron transport characteristics of GaN including high electron mobility of 1300  $\text{cm}^2/\text{V}$ 's and high electron saturation velocity of  $3 \times 10^7$  cm·s<sup>-1</sup> mean that it is also suitable for high speed and high frequency electron devices.

| Material                                                   | Si   | GaAs | SiC  | GaN  |

|------------------------------------------------------------|------|------|------|------|

| Bandgap, $E_g(eV)$                                         | 1.12 | 1.42 | 3.25 | 3.40 |

| Relative permittivity, $\varepsilon_r$                     | 11.8 | 12.8 | 9.7  | 9.0  |

| Breakdown field, $E_c$ (MV/cm)                             | 0.25 | 0.4  | 3    | 4.0  |

| Electron saturation velocity, $v_t$ (10 <sup>7</sup> cm/s) | 1.0  | 2.0  | 2.0  | 3.0  |

| Electron mobility, $\mu_n$ (cm <sup>2</sup> /V·s)          | 1300 | 6000 | 800  | 1350 |

| Thermal conductivity, $\sigma_{th}(W/cm \cdot K)$          | 1.5  | 0.5  | 4.9  | 1.3  |

Table 1.1 Material parameters for Si, GaAs, SiC and GaN [2].

Table 1.2 shows the figures of merit (FOMs) for Si, GaAs, SiC, and GaN[3], where Chow and Tyagi theoretically highlighted the advantages of GaN over Si, GaAs, and SiC for high frequency and high power applications by means of Johnson, Keyes and Baliga figures of merit. These figures are related to the material parameters such as the critical breakdown field ( $E_c$ ), the dielectric permittivity ( $\epsilon$ ), the carrier mobility ( $\mu$ ), the thermal conductivity ( $\sigma_{th}$ ), and the saturated electron velocity ( $v_t$ ). These FOMs are used to evaluate the ability of power handling and thermal dissipation for electron devices. As observed in Table 1.2, FOMs of GaN are the best among these materials; hence, it is well suited for high speed, high-power and high-temperature applications.

| Figures of merit | Johnson                                     | Keyes                                                            | Baliga-low<br>frequencies                  | Baliga-high<br>frequencies                  |

|------------------|---------------------------------------------|------------------------------------------------------------------|--------------------------------------------|---------------------------------------------|

| Equation         | $\propto (E_c v_t)^2$                       | $\propto \sigma_{th} \left(\frac{v_t}{\varepsilon}\right)^{1/2}$ | $\propto ε \mu E_c^3$                      | $\propto \mu E_c^3$                         |

| Description      | Power<br>handling<br>at high<br>frequencies | Thermal dissipation                                              | Power<br>handling<br>at low<br>frequencies | Power<br>handling<br>at high<br>frequencies |

| Si               | 1                                           | 1                                                                | 1                                          | 1                                           |

| GaAs             | 11                                          | 11 0.45                                                          | 28                                         | 16                                          |

| SiC              | 37                                          | 0.73 16                                                          |                                            | 3.8                                         |

| GaN              | 790                                         | 1.8                                                              | 910                                        | 100                                         |

Table 1.2 Figures of merit (FOMs) for various semiconductors at 300K for microwave power device applications. All FOMs are normalized with respect to those of silicon.

In addition, GaN based heterostructure technologies are available which allow quantum well and hetero-junction in GaN material system to span new operation areas for GaN based high mobility electron transistors (HEMTs). In GaN based HEMTs, two dimension electron gas (2DEG) results when a barrier layer (e.g., AlGaN or InAlN) is in contact with a buffer layer (e.g., GaN). This 2DEG has high electron density and high mobility without intentional doping in the barrier layer due to large spontaneous and piezoelectric polarizations[4, 5]. This reduces the coulombic scattering in GaN based heterostructure resulting in increased mobility [6]. For example, an electron mobility in excess of 2000  $\text{cm}^2/\text{V}$ 's at room temperature and 11000  $\text{cm}^2/\text{V}$ 's at 4.2 K have been reported in the 2DEG channel in AlGaN/GaN HEMT grown on 6H-SiC substrate [7].

In addition to its excellent electrical properties mentioned above, GaN has a high hardness, thermal conductivity and excellent chemical inertness. This allows GaN-based devices to operate well in harsh environments [8]. Furthermore, with robustness against radiation, GaN could be used in military and space applications[9].

#### 1.2 GaN based High Electron Mobility Transistors

#### 1.2.1 GaN HEMT heterostructure growth

Due to the lack of native GaN substrates in large quantities, researchers had tried nearly most of the crystal-growth technologies on different substrates and orientations to grow high quality GaN materials. With the great progress achieved in the past several decades, GaN based heterostructures have been epitaxially grown in both metal organic chemical vapor deposition (MOCVD) [10] and molecular beam epitaxy (MBE) systems[11]. Compared to the latter, the former growth system is more popular for the epitaxial growth of GaN based heterostructures due to higher growth rate capability, multi-wafer growth capability leading to lower process cost and, similar quality of heterostructures and HEMTs [12].

Traditionally, GaN-based heterostructures have been grown on SiC and sapphire [15]. SiC substrate has a low lattice mismatch (3.5%) to GaN and a good thermal conductivity (4.9 W/cm.K), and good quality GaN HEMT epi-

layer structure on 4 inch SiC substrate have been demonstrated [16, 17, 18]. However, SiC substrate is expensive and large size 200 mm diameter SiC substrate is not available yet. On the other hand, sapphire substrate is less costly than SiC substrate. However, sapphire has a poor lattice mismatch (16.1%) to GaN and poor thermal conductivity (0.32 W/cm.K) [16]. More recently, researchers have become interested in growing GaN on Si substrate. Even though Si substrate has a large lattice mismatch (16%) to GaN, it is attractive due to the large wafer size availability (> 200 mm diameter), low wafer cost, and its relatively high thermal conductivity. Much research is being performed in order to overcome the challenges to obtain a good quality nitride based heterostructure on large Si wafers (specifically 200 mm diameter and above). With the capability of growing GaN based heterostructure on large size silicon substrate, it is one step closer to achieve economical GaNon-silicon high power and high speed devices.

Table 1.3 summarizes the properties of various substrates for GaN epitaxial growth.

There are mainly two GaN based heterostructures used for the fabrication of HEMTs. One is the AlGaN/GaN heterostructure and another is the InAlN/GaN heterostructure. When a thin AlGaN epilayer is grown on a GaN buffer layer, a tensile strain is introduced in the top thin barrier layer resulting from lattice mismatch between the AlGaN barrier layer and GaN buffer layer. Both the piezoelectric polarization due to the presence of strain and the spontaneous polarization for nitride barriers are in the same direction. Furthermore, these 2 polarization fields are large enough to produce 2DEGs confined in the heterostructure without any dopant introduced in the barrier

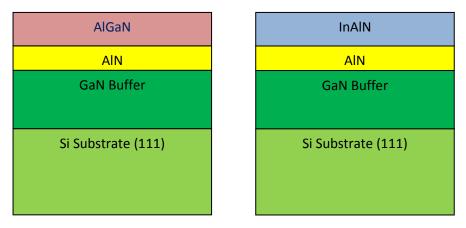

layer. Normally, the sheet carrier concentration of 2DEG at the AlGaN/GaN heterostructure is in the range of ~ $10^{13}$  carriers per cm<sup>2</sup> and the mobility of carriers is as high as 1600 cm<sup>2</sup>/Vs, owing to less scattering from ionized dopants and the interfaces resulted from having smoother surface at hetero interface compared to the surface of Si-SiO<sub>2</sub> interface in MOSFET. On the other hand, lattice matched In<sub>0.17</sub>Al<sub>0.83</sub>N/GaN heterostructure is strain free, thus resulting in reduced defects due to lattice mismatch and better reliability [8]. Moreover, the strong spontaneous polarization of the InAlN barrier layer induces a high sheet carrier density > 2 x 10<sup>13</sup> cm<sup>-2</sup> in 2DEG [9]. However, the carrier mobility in the InAlN/GaN 2DEG is not as high as that of AlGaN/GaN due to higher alloy disorder scattering compared to AlGaN/GaN heterostructure and InAlN/GaN heterostructure grown on Si(111) substrate.

| Substrate                            | SiC              | Sapphire         | Si               |

|--------------------------------------|------------------|------------------|------------------|

| Thermal Conductivity<br>(W/cm·K)     | 3                | 0.5              | 1.5              |

| Resistivity<br>(Ω·cm)                | >10 <sup>4</sup> | >10 <sup>8</sup> | >10 <sup>4</sup> |

| Diameter used for Epitaxy<br>(in)    | 2-3              | 2-4              | 2-8              |

| Lattice mismatch to GaN (%)          | 3.5              | 16               | 16.9             |

| Thermal expansion mismatch<br>to GaN | 18.9             | -25.4            | 116              |

| Cost                                 | high             | low              | low              |

Table 1.3 Comparison of substrates available for GaN epitaxial growth[13, 14].

Figure 1.1 Schematic drawing of cross sectional view of AlGaN/GaN (left) and InAlN/GaN (right) heterostructure grown on Si(111) substrate.

#### 1.2.2 Development of GaN based HEMTs

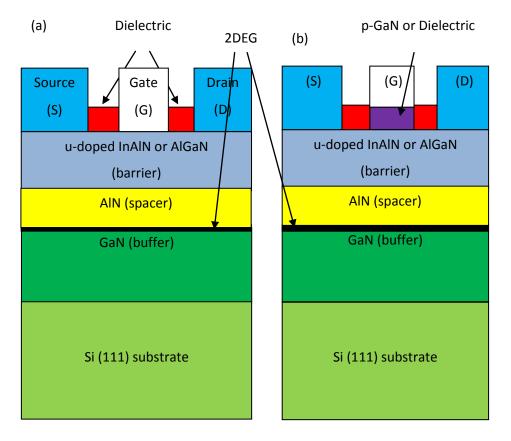

GaN based HEMTs can be divided into three groups depending on their gate stack structure namely Schottky (metal-semiconductor) gate HEMT, p-GaN gate HEMT and metal-insulator-semiconductor (MIS) gate HEMT. The cross sections of the HEMTs based on these three structures are shown in Figure 1.2. The p-GaN [11, 12] and MIS gate HEMTs are widely used for high power applications where the low leakage current and high breakdown voltage are desired. For high frequency applications, Schottky and MIS gate HEMTs are widely used. On the other hand, p-GaN gate is not a good candidate to be used in high frequency application due to its high Ohmic and access resistance which would increase the gate delay, hence, reducing the frequency performance compared to Schottky and MIS gate. Since our main focus is high frequency and high power HEMTs, we will focus on Schottky gate HEMT and MIS gate HEMT. The focus of my project is on Schottky gate HEMTs, while MIS gate HEMTs is carried out by another researcher in our research group.

Figure 1.2 Schematic cross-sections of (a) Schottky gate HEMT (b) p-GaN gate HEMT or MIS gate HEMT.

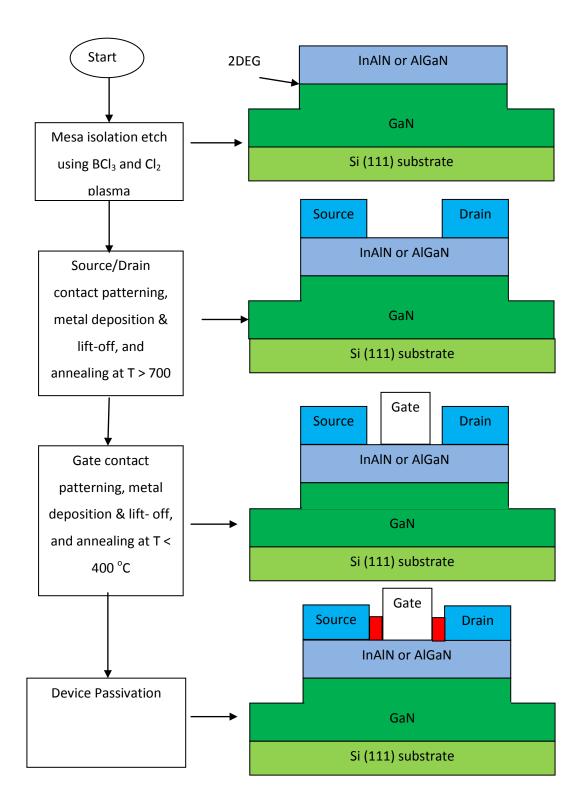

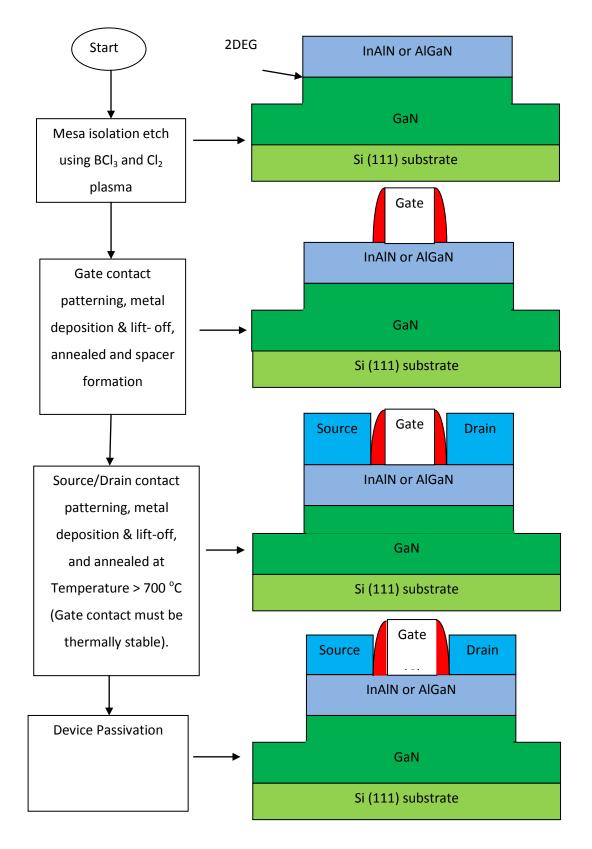

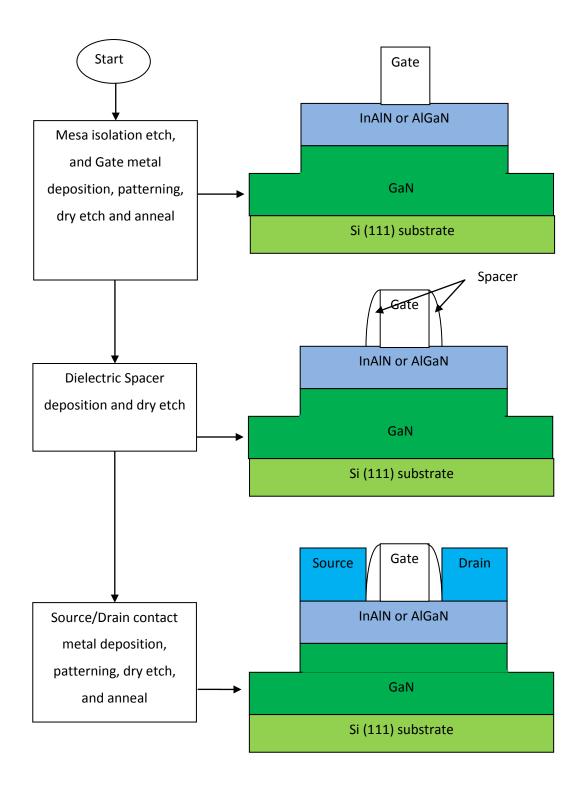

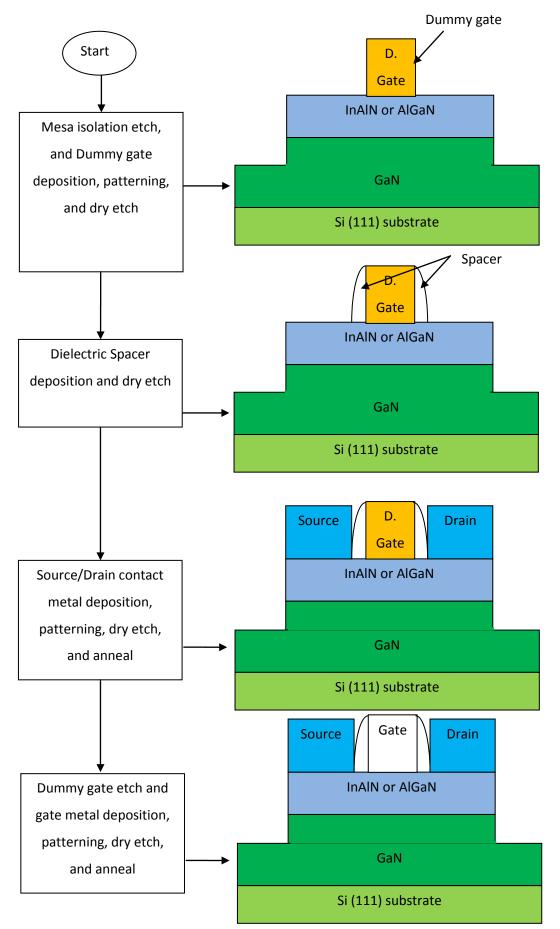

The conventional fabrication of GaN HEMT uses a gate-last process, meaning the gate is made after the source/drain contact annealing, and this is shown in Figure 1.3. The gate-last process is commonly used because the traditional gold-based gate contact (e.g., Ni/Au) is not thermally robust to withstand the high temperature annealing (> 700°C) required for the formation of low contact resistance of gold-based source/drain Ohmic contacts (e.g., Ti/Al/Ni/Au) to GaN based HEMTs. Annealing at such temperature could lead to high gate leakage due to Ni/Au thermal instability. More recently, a gatefirst process has been proposed and this is shown in Figure 1.4. It should be noted that Si MOSFET process is typically a gate-first process.

Figure 1.3 The conventional gate-last fabrication process of HEMT

Figure 1.4 Gate-first fabrication process of HEMT

The gate-last process, as shown in Figure 1.3, starts with mesa isolation etch using inductively coupled plasma (ICP) with the gas mixture of BCl<sub>3</sub> and Cl<sub>2</sub>, as shown in Figure 1.3. Following which, the source/drain contacts are patterned, and the metals are deposited using reactive sputtering or e-beam evaporation system. The contacts are defined after metal lift-off and are annealed at very high temperature (> 700°C) to achieve Ohmic properties. The gate contact is subsequently patterned, and the gate metal is deposited using reactive sputtering or e-beam evaporation system. The gate contact is again defined after metal lift-off and is annealed at a moderate temperature (typically below 400°C). The passivation dielectric layer is then deposited to complete the device fabrications.

#### 1.2.3 AlGaN/GaN HEMTs technology

Owing to the excellent material properties of GaN and the benefits of heterojunctions, AlGaN/GaN HEMTs have been showing great prospective for high-power and high-frequency operations since the first demonstration in 1993 [15] in which Khan et al. reported that the AlGaN/GaN HEMTs with a 250 nm gate length exhibited maximum transconductance,  $g_{m(max)}$ , of 23 mS/mm, a maximum drain current,  $I_{DSAT(max)}$ , of 180 mA/mm, and an electron mobility of 563 cm<sup>2</sup>/V·s at 300 K. Since the quality of AlGaN/GaN wafer and device processing technology is continuously enhanced from the first demonstration, the current AlGaN/GaN HEMTs exhibit great improvement in performance and could be comparable or better than other contending materials such as Si, GaAs, and SiC. Chung et al. [16] reported that  $I_{DSAT(max)}$

of 1.2 A/mm and  $g_{m(max)}$  of 410 mS/mm, an unity current gain cut off frequency,  $f_T$  of 70 GHz and a unity power gain cut off frequency,  $f_{max}$ , of 300 GHz were obtained in AlGaN/GaN-on-SiC HEMTs. For low cost and high performance GaN HEMTs on Si, Bouzid-Driad et al. [17] demonstrated that  $I_{DSAT(max)}$  of 820 mA/mm,  $g_{m(max)}$  of 440 mS/mm, and a  $f_T$  of 100 GHz and a high  $f_{max}$  of 206 GHz were achieved in AlGaN/GaN-on-Si HEMTs. Medjoub et al. [18] have demonstrated 100 nm gate GaN HEMT on 100 mm Si with a output power density of 2.5 W/mm at 40 GHz. Therefore, AlGaN/GaN HEMTs grown on Si are suitable for high frequency applications. In addition, lkeda et al. [19] reported that 1.8 kV of three-terminal off-state breakdown voltage with ~15 µm gate to drain distance was achieved in AlGaN/GaN HEMTs grown on Si are also suitable for high power applications.

#### 1.2.4 InAlN/GaN HEMTs technology

Another GaN based heterostructure, InAlN/GaN, becomes popular for microwave power electronic technology [20]. In  $In_{0.18}Al_{0.82}N/GaN$  heterostructure, strain and piezoelectric polarization resulted from lattice mismatch do not exist. As shown in Table 1.4, InAlN/GaN heterostructure can provide higher 2DEG carrier concentration due to ~ 3 times higher spontaneous polarization than that of AlGaN/GaN, which means that a higher output current density can be achieved if the breakdown conditions can be maintained [21]. InAlN/GaN HEMTs have been shown experimentally to have

higher polarization charges without the drawback of high strain that resulted

from lattice mismatch[22].

Table 1.4 Spontaneous polarization ( $\mathbf{P}_{SP}$ ) and piezoelectric polarization ( $\mathbf{P}_{EP}$ ) and theoretical calculation of the free electron density ( $\mathbf{n}_s$ ) in InAlN/GaN and AlGaN/GaN HEMTs[23].

| Structure                                  | $\Delta \mathbf{P}_{SP}(cm^{-2})$ | $\mathbf{P}_{\mathrm{EP}}(\mathrm{cm}^{-2})$ | $\mathbf{n}_{s}$ (cm <sup>-2</sup> ) |

|--------------------------------------------|-----------------------------------|----------------------------------------------|--------------------------------------|

| Al <sub>0.3</sub> Ga <sub>0.7</sub> N/GaN  | $-1.56 \times 10^{-2}$            | $-9.8 \times 10^{-3}$                        | $1.58 \times 10^{13}$                |

| In <sub>0.17</sub> Al <sub>0.83</sub> /GaN | $-4.37 \times 10^{-2}$            | 0                                            | $2.73\times10^{13}$                  |

The outstanding device performances have been reported[23-26] for InAlN/GaN HEMTs grown on SiC. Yue et al. [27] achieved  $I_{DSAT(max)}$  of 1.9 A/mm,  $g_{m(max)}$  of 653 m/mm and  $f_T$  of 400 GHz in InAlN/GaN-on-SiC HEMTs. Sun et al [28] reported that InAlN/GaN HEMTs grown on Si (111) has  $I_{DSAT(max)}$  of 1.3 A/mm,  $g_{m(max)}$  of 330 m/mm and  $f_T$  of 102 GHz which is the highest value achieved for InAlN/GaN HEMTs grown on Si(111). These results clearly demonstrate that InAlN/GaN HEMTs grown on Si(111) has not reached the potential yet. Further development of InAlN/GaN HEMTs depends on the improvement of material quality, the optimization of device structures and device processing technology.

#### 1.2.5 Advantages of GaN HEMTs over Si LDMOSFETs

Owing to superior material properties, GaN based HEMT has many advantages over Si laterally diffused metal oxide semiconductor field effect transistor, LDMOSFET. Lee et. al has studied the comparison of GaN based HEMT and Si LDMOS power amplifiers (PAs) for wide band code division multiple access (W-CDMA) applications [13]. In the study, they reported that GaN HEMT based class AB PA has 8.7 % higher efficiency compared to Si LDMOS counterpart. Furthermore, GaN HEMT PA is less sensitive to changes in temperature and can be controlled by the adaptive control of Pre distorter (a device used to improve the linearity of RF PA) to achieve fixed efficiency and gain. On the other hand, Si LDMOS is very sensitive to the changes in temperature and even with PD adaptive control, the gain and output efficiency of Si LDMOS varies by about 2.6 dB and 3 %, respectively. Hence, GaN HEMT is good candidate for use in high efficiency Radio Frequency (RF) PA.

Furthermore, owing to high breakdown voltage, GaN HEMTs can operate at high drain bias voltage [14]. For the same amount of the output power, the power,  $I^2R$ , wasted on parasitic resistance would be lowered in PA with higher drain bias voltage compared to PA with lower drain bias voltage. Hence, it increases efficiency and simplifies the cooling system which is an important advantage since the cost and weight of cooling system has very high impact on the cost of high power RF transmitter [14]. With high efficiency, GaN HEMT based PA would operate at lower temperature, hence, reducing power consumption, increasing reliability and life expectancy.

## 1.3 Challenges and motivations

Even though GaN based HEMTs have superior quality over Si based LDMOS, there are challenges that need to be addressed for HEMTs before they can replace MOSFET. The important challenges are related to cost, high gate leakage current and thermal stability, and device performance improvement.

# 1.3.1 Cost

Firstly, cost is the challenge for GaN based HEMTs to compete with other semiconductor devices (e.g., Si-based). However, with the availability of GaN based heterostructures grown on Si(111) wafer with excellent quality, low cost and high performance GaN based HEMTs become feasible. If the fabrication of GaN-on-Si HEMTs can be processed in existing Si fabrication foundries, the making of GaN-on-Si HEMTs can be made more cost competitive. Furthermore, with the availability of large Si substrate (> 100 mm diameter), Hahn et al. [29] have reported the enhancement mode 1.0  $\mu$ m gate Al<sub>x</sub>Ga<sub>1</sub>. <sub>x</sub>N/GaN HEMT on 150 mm diameter Si substrate with the extrinsic transconductance of 366 mS/mm using a recessed gate process. In addition, a few groups have recently reported on the realization of Al<sub>x</sub>Ga<sub>1-x</sub>N/GaN heterostructures on Si(111) using Au-based contacts or Au-free contacts [30-36]. Therefore, with larger substrate (200 mm diameter), the fabrication cost per transistor could be further reduced. However, the conventional Au-based contacts is widely used in GaN based HEMT while gold acts as a deep level trap and fast diffuser in silicon which can degrade the Si based device performance; hence, it is strictly forbidden in Si CMOS foundries. In addition, gold is an expensive material which would add cost to the fabrication of HEMT.

Therefore, we aim to develop non-gold based Schottky contacts for GaNbased HEMTs on Si (111) substrate to make them CMOS compatible to reduce the fabrication cost.

#### 1.3.2 Gate Leakage and Thermal Stability

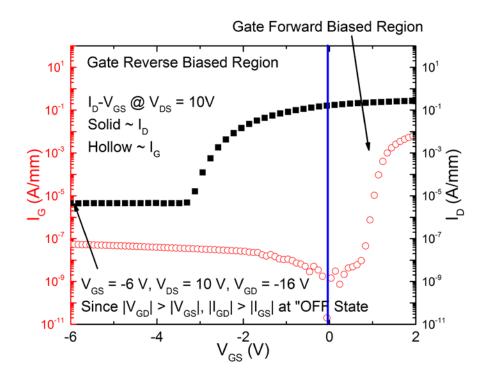

Another major factor that limits HEMT performance is the high Schottky gate leakage current ( $I_G$ ) [37-39]. When a Schottky diode is forward biased, the current flowing through it depends exponentially on the forward biased voltage. Therefore, if a Schottky contact is used as the gate in HEMTs, the leakage current from the gate,  $I_G$ , will depend exponentially on the gate to source voltage,  $V_{GS}$ . This is depicted by a typical  $I_G$ - $V_{GS}$  curve (at a fixed  $V_{DS}$ ) of a Schottky gate HEMT shown in Figure 1.5. Hence, there is a maximum  $V_{GS}$  voltage (typically 2 to 3 V) above which the gate leakage will be too high and will increase the leakage loss and power consumption. Hence, the drain current,  $I_D$ , will be limited due to the constraint on  $V_{GS}$ .

A typical  $I_D$ - $V_{GS}$  (at a fixed  $V_{DS}$ ) curve is also shown in Figure 1.5. In the 'OFF" state of HEMT, the drain current,  $I_{OFF}$ , is mostly dominated by  $I_G$ , where  $I_G$  is the sum of gate to drain current,  $I_{GD}$  and gate to source current,  $I_{GS}$ . Since  $|V_{GD}|$  $> |V_{GS}|$  in the OFF state,  $I_G$  is dominated by  $I_{GD}$ . Hence, the gate reverse breakdown voltage is mainly determined by  $V_{GD}$ . Therefore, this limits the maximum drain bias voltage[40]. In addition to the limitation of drain and gate voltages, the large Schottky gate leakage current can lead to a higher power consumption, smaller gate voltage swing and reduced device lifetime.

Figure 1.5 Typical  $I_D$ - $V_{GS}$  and  $I_G$ - $V_{GS}$  curves of Schottky gate HEMT.

Chen et al. [41] reported that the leakage current of the Schottky gate contact was due to the combination of several contributing components such as thermionic emission, generation recombination current, and tunneling current. At low bias voltage, the contribution of tunneling current dominates. This tunneling current resulted from the presence of dislocations in AlGaN/GaN and InAlN/GaN heterostructures [42, 43].

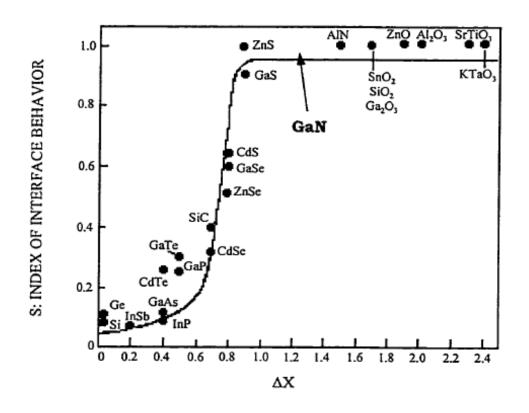

Many methods have been explored to reduce the gate leakage current of HEMTs. One of them is to use a high work function Schottky gate. To date, a number of high work function Schottky contacts to AlGaN/GaN heterostructure have been studied. Table 1.5 summarizes the properties of a

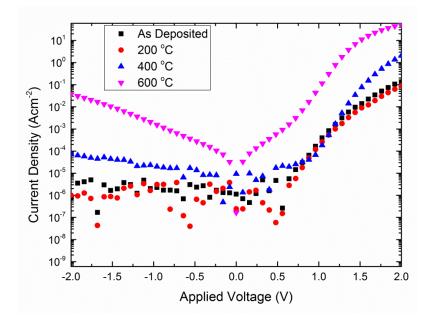

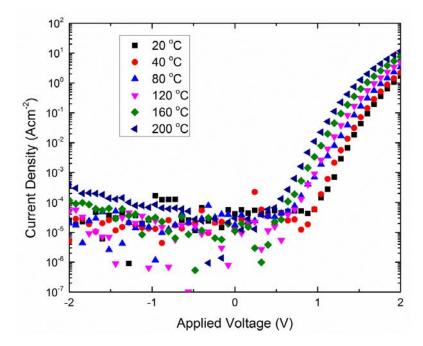

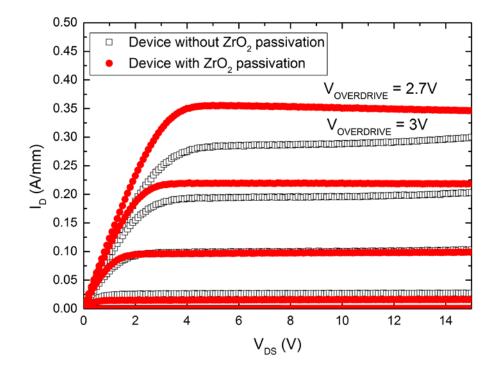

selection of commonly used Schottky contacts to AlGaN/GaN heterostructure. As shown in Table 1.5, high work function elemental metals such as Pt, Ni, Ir, and Pd can yield Schottky Barrier Height (SBH) higher than 0.85 eV after annealing at a temperature (typically less than 500°C). However, their leakage current was reported to increase upon high temperature heat treatment (above 500°C). Furthermore, the reverse leakage current of these contacts increased above  $10^{-4}$  Acm<sup>-2</sup> when annealed at above 500°C which made them not suitable for use in high temperature applications. Most Schottky contacts listed in Table 1.5, except RuO<sub>2</sub>, suffer from degradation of leakage current after annealing above  $600^{\circ}$ C. Hence, RuO<sub>2</sub> may be a good Schottky gate candidate for high temperature applications.