# DEVELOPMENT OF NANO/MICROELECTROMECHANICAL SYSTEM (N/MEMS) SWITCHES

**QIAN YOU**

(*M.Sc.*, *NUS*)

## A THESIS SUBMITTED FOR THE DEGREE OF DOCTOR OF PHILOSOPHY DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING

NATIONAL UNIVERSITY OF SINGAPORE

2015

## **DECLARATION**

I hereby declare that this thesis is my original work and it has been written by me in its entirety. I have duly acknowledged all the sources of information which have been used in the thesis.

This thesis has also not been submitted for any degree in any university previously.

酸抗

Qian You

15 Jan 2015

## Acknowledgements

I would like to express my deepest and most sincere gratitude to my supervisors Prof. Lee Chengkuo for his consistent supports, guidance and encouragement during my Ph.D. study. Without his support, this thesis can never be completed. I would like to thank Prof. Liang Gengchiau, for giving me opportunity entering the world of research, and supportive supervision during my whole candidature. I also deeply appreciate Dr. Humberto Campanella for offering attachment opportunity in Institute Microelectronics (IME) and his continuous support of me. I really could not have imagined the possibility of this dissertation without gracious concerns and kind helps from all of my supervisors.

Meanwhile, I am very grateful to Dr. Julius Tsai, Dr. Vincent Pott and Dr. Pushpapraj Singh for their continuous support and guidance during my attachment period. Without their help, I would not able to complete the fabrication and characterization successfully.

In addition, I must express my sincere gratitude to all my past and present colleagues and friends in CICFAR and CNNL lab: Mr. Bo Woon Soon, Mr. Prakash Pitchappa, Dr. Huang Wen, Dr. Lam Kai Tak, Prof. Liu Huicong, Dr. Li Bo, Dr. Wang Nan, Dr. Lou Liang, Dr. Zhang Songsong, Mr. Lokesh Dhakar, Mr. Xiang Zhuolin, Mr. Ho Chong Pei, Mr. Wang Tao, Mr. Wang Hao, Mr. Lee Sanghoon, Ms Wang Jiahui and so on.

## **Table of Contents**

| ECLARATIONi                                        |

|----------------------------------------------------|

| cknowledgements iii                                |

| ible of Contentsiv                                 |

| ımmaryvii                                          |

| st of Tablesix                                     |

| st of Figuresx                                     |

| st of Acronymsxvi                                  |

| st of Symbolsxix                                   |

| napter 1 Introduction of N/MEMS Switches           |

| 1.1 Power-Efficiency Limitation of CMOS            |

| 1.2 The Call of New Applications                   |

| 1.3 Mechanical Switches                            |

| 1.4 Actuation Mechanism                            |

| 1.4.1 Electrostatic Actuation                      |

| 1.4.2 Piezoelectric Actuation                      |

| 1.4.3 Electrothermal Actuation10                   |

| 1.4.4 Electromagnetic Actuation 11                 |

| 1.4.5 Comparison of Different Actuation Mechanisms |

| 1.5 Recent Prototypes of N/MEMS Switches           |

| 1.5.1 Folded- Flexure Beams Switches               |

| 1.5.2 Platinum Coated Polysilicon Switches         |

| 1.5.3 Laterally Actuated Ruthenium Switches        |

| 1.5.4 TiN Based Vertically Actuated Switches       |

|      | 1.5.5    | Comparison of the Four Prototypes                         | 21 |

|------|----------|-----------------------------------------------------------|----|

|      | 1.6      | N/MEMS Switches Applications                              | 22 |

|      | 1.6.1    | Pure N/MEMS Switches Circuit                              | 22 |

|      | 1.6.2    | NVM                                                       | 24 |

|      | 1.6.3    | Hybrid N/MEMS-CMOS Circuit                                | 25 |

|      | 1.7      | Thesis organization.                                      | 29 |

| Chap | pter 2   | Design Consideration of N/MEMS Switches                   | 31 |

|      | 2.1      | Pull-In Voltage                                           | 32 |

|      | 2.2      | Contact Material                                          | 34 |

|      | 2.3      | Laterally and Vertically Actuated                         | 36 |

|      | 2.4      | Fixed-Fixed Beam and Cantilever                           | 38 |

|      | 2.5      | Scalability of N/MEMS Switches                            | 41 |

| Chap | pter 3   | U-Shaped NEMS Switches with Low Actuation Voltage         | 45 |

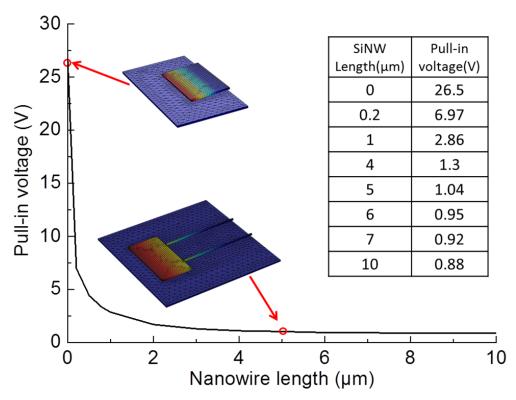

|      | 3.1      | Silicon Nanowire                                          | 46 |

|      | 3.2      | Simulation                                                | 48 |

|      | 3.3      | Fabrication Process                                       | 50 |

|      | 3.4      | Electrical Measurement                                    | 53 |

|      | 3.5      | Suggestion for Performance Improvement                    | 57 |

| Chap | pter 4   | All Metal Based NEMS Switches                             | 63 |

|      | 4.1      | All-Metal-Based Laterally Actuated Switches for NEMS-CMOS |    |

| int  | tegratio | n                                                         | 65 |

|      | 4.2      | The Desire of High Temperature NEMS Switches              | 69 |

|      | 4.3      | Fabrication Process                                       | 71 |

|      | 4.4      | Electrical Measurement with Limited Current               | 84 |

|      | 4.5      | Electrical Measurement with High Current                  | 88 |

|      | 4.6      | High Temperature Measurement                              | 91 |

|      | 4.7      | Conclusion                                                | 98 |

### Table of Contents

| Chapter 5 | Dimension Optimization of All Metal Based NEMS Swi       | tches.101 |

|-----------|----------------------------------------------------------|-----------|

| 5.1       | Dimensions                                               | 102       |

| 5.2       | Pull-In Voltage                                          | 103       |

| 5.3       | Failure Mode and Process Yield                           | 114       |

| 5.4       | Conclusion                                               | 120       |

| Chapter 6 | Conclusions                                              | 123       |

| 6.1       | Contributions of This Works                              | 123       |

| 6.2       | Future Directions                                        | 125       |

| 6.2.      | 1 Further scaling                                        | 125       |

| 6.2.      | 2 Devices with different functions                       | 126       |

| 6.2.      | 3 Encapsulation                                          | 127       |

| Bibliogra | phy                                                      | 131       |

| Appendix  | I: Process Flow of U-Shaped NEMS Switches                | 153       |

| Appendix  | II: Process Flow of All Metal Based NEMS Switches        | 155       |

| Appendix  | III: Process Flow of Encapsulated All Metal Based NEMS S | witches   |

|           |                                                          | 156       |

| Appendix  | IV: List of Publication                                  | 159       |

## **Summary**

Power management is a daunting challenge for continuous MOSFET scaling-down due to leakage current issue. To avoid this power crisis, alternative switching devices have been proposed. Nano/Micro Electromechanical System (N/MEMS) switches have been attracting attention for their excellent switching properties such as zero-leakage current, abrupt switch behavior and potential to operate at high temperature. These unique properties make the N/MEMS switches a strong candidate for ultra-low power electronics and harsh environment integrated circuits. This thesis begins with a general overview of the existing N/MEMS switches prototypes and several proposed applications. It then presents the design considerations of N/MEMS switches in various aspects.

This work concentrates on further miniaturizing the size of the devices and clarifying the main issues on the successful implementation of N/MEMS switch technology. The state-of-the-art research shows two major constraints: very high actuation voltage and very limited process successful rate. Notable improvement works need to be done to address these issues including investigation of new device structures, development of advanced fabrication process and implementation of new materials. It is remarkably challenging when the mechanical switches have been reducing their dimensions from MEMS to NEMS (MEMS with sub-micrometer features).

To address the high actuation voltage issue of N/MEMS switches, U-shaped Si nanowire based NEMS switch has been developed. With the help of

#### Summary

U-shaped structure and ultra-small Si nanowire, the actuation voltage of the NEMS switch has been reduced from conventionally more than 5V to only 1V.

Prior demonstrations of NEMS switches normally demonstrate the operation of a single switching element which was mostly fabricated by a process with very low success rate. Therefore, extensive studies of NEMS switches design and properties associated with fabrication issues are difficult to be carried out. To address this problem, an all-metal-based NEMS switch has been developed in a systematical approach to fulfill a few technical requirements at the same time, mainly targeting on reliable fabrication process with high yield throughput. Molybdenum, as a new material for NEMS switches, has been used as the structural layer. The devices are fabricated with low temperature CMOS compatible process with a single mask layer. The electrical measurement shows sound high temperature operation characteristics with good reliability, e.g., survived after 28 hours continuous cycling testing at 300 °C environments. The devices also show low contact resistance of 2.5 k $\Omega$  and an on/off ratio as high as  $10^8$ . The basic design rules to obtain high process output are determined. With optimized dimensions, the achieved process yield is as high as 100 %.

## **List of Tables**

| Table 1-1 Comparison of four actuation mechanisms                            | 12  |

|------------------------------------------------------------------------------|-----|

| Table 1-2 Summary of devices described above                                 | 21  |

| Table 1-3 Switch property versus application                                 | 22  |

| Table 2-1 Properties of contact material at room temperature [156]           | 35  |

| Table 2-2 The scaling properties of N/MEMS technology                        | 42  |

| Table 3-1 Pull-in voltage of N/MEMS switches.                                | 45  |

| Table 4-1 Process Differences between this work and conventional work        | 75  |

| Table 4-2 Comparison of metal based NEMS switch                              | 99  |

| Table 5-1 Design Parameter                                                   | 102 |

| Table 6-1 The scaling properties of N/MEMS technology with constant <i>w</i> | 126 |

## **List of Figures**

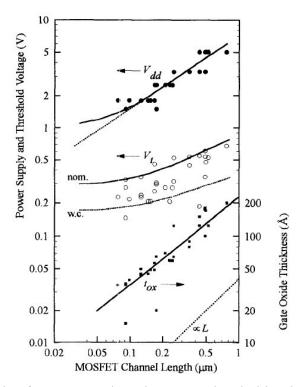

| Figure | 1-1 Trends of power supply voltage $V_{dd}$ , threshold voltage $V_t$ , and gate oxide thickness $t_{ox}$ versus channel length for CMOS logic technologies. Adapted from [2]                                                                                                                                                                                                                                                                                                                                                                                                                                | 2  |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

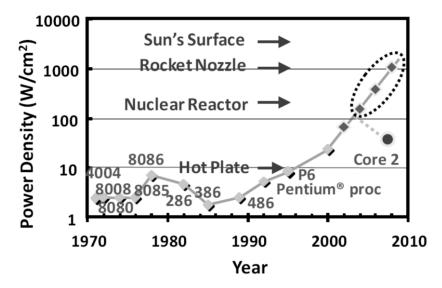

| Figure | 1-2 Power density versus minimum feature size as reported in [5]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3  |

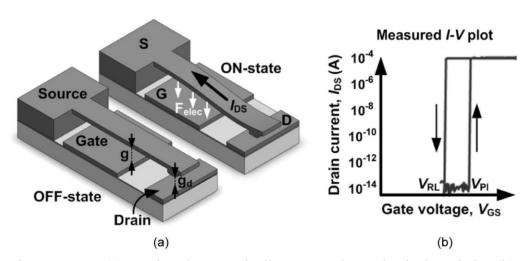

| Figure | 1-3 (a) Basic electrostatically actuated mechanical switch. (b) Measured current versus gate voltage characteristics for a mechanical switch. Adapted from [19].                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5  |

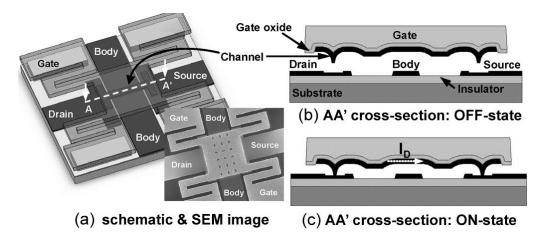

| Figure | 1-4 Schematic illustrations of an electrostatic actuated switch.  (a) Isometric view. (b) Cross sectional view along the channel (AA') in the off-state. (c) Cross-sectional view in the on-state. In the off state, an air gap separates the channel from the metallic source and drain electrodes so that no current can flow. In the on state, electrostatic force between the gate and the body electrode causes the gate to be deflected downward sufficiently to bring the channel into contact with the source and drain electrodes, to form a conductive path for current to flow. Adapted from [41] | 8  |

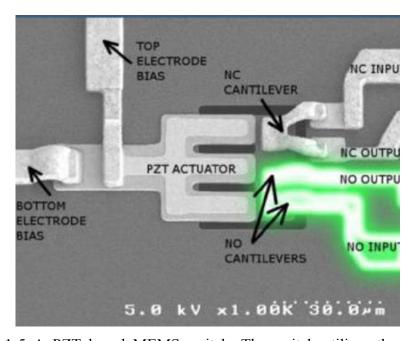

| Figure | 1-5 A PZT based MEMS switch. The switch utilizes the converse piezoelectric effect to generate movement. Two electrodes on the left (Top and bottom) provide the necessary electric field to bending down the contact. Output current flow is highlighted in green where the physical contact is formed. Adapted from [58, 59]                                                                                                                                                                                                                                                                               | 9  |

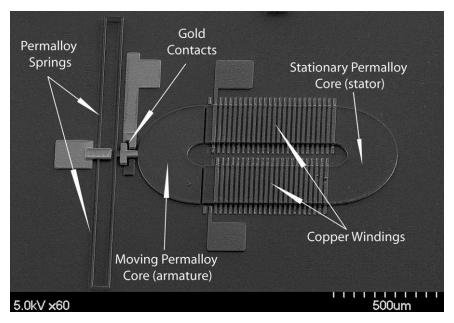

| Figure | 1-6 SEM image of a fully fabricated single-pole single-throw electromagnetic MEMS switch. When current applied to the coils, the magnetic force generated by the stationary permalloy overcomes the return spring force and closes the switch. Adapted from [71]                                                                                                                                                                                                                                                                                                                                             | 10 |

| Figure | 1-7 SEM image of a fully fabricated single-pole single-throw electromagnetic MEMS switch. When current applied to the coils, the magnetic force overcomes the return spring force and closes the switch. Adapted from [79]                                                                                                                                                                                                                                                                                                                                                                                   | 11 |

| Figure | 1-8 Top view a Folded-beam Switch, adapted from [99]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 14 |

| Figure | 1-9 Process flow of the folded-flexure switch, adapted from [99]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 15 |

| Figure | 1-10 (a) I-V curve of switch turn on. (b) On-state resistance with cycling for different applied body bias, adapted from [41]                                                                         | 16 |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure | 1-11 (a) SEM cross section of non-released platinum-coated beams. (b) SEM images showing actuation of a five terminal polysilicon switch coated with platinum. Adapted from [112]                     | 17 |

| Figure | 1-12 Laterally actuated ruthenium switches (a) SEM photo (b) process flow. Adapted from [116]                                                                                                         | 18 |

| Figure | 1-13 I-V curve of laterally actuated Ru switches, adapted from [116]                                                                                                                                  | 19 |

| Figure | 1-14 An SEM image of TiN Switch, adapted from [118]                                                                                                                                                   | 20 |

| Figure | 1-15 Measured I-V curve for TiN devices, adapted from [118]                                                                                                                                           | 20 |

| Figure | 1-16 Experimental results of the MEMS switch circuit, adapted from [87]                                                                                                                               | 23 |

| Figure | 1-17 Schematic of NVM operation. Adapted from [123]                                                                                                                                                   | 24 |

| Figure | 1-18 NVM I-V curve, adapted from [123].                                                                                                                                                               | 25 |

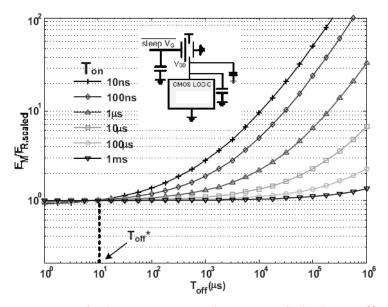

| Figure | 1-19 Energy ratio (MOSFETs to N/MEMS switches) vs. off-<br>period for various on-period, for designs power gated with 90<br>nm MOSFETs and N/MEMS switches. Adapter from [21].                        | 26 |

| Figure | 1-20 CMOS-NEMS FPGA using NEMS switches as routing                                                                                                                                                    | 27 |

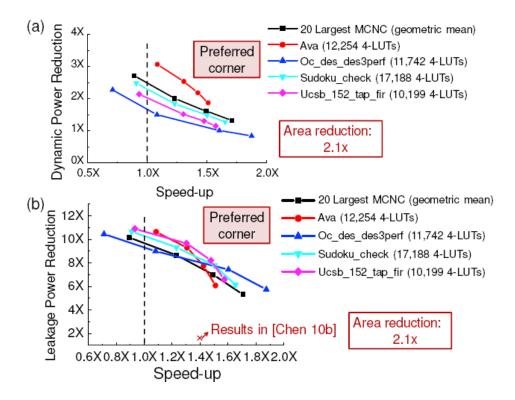

| Figure | 1-21 Power-speed trade-offs comparing CMOS-NEM FPGAs to a CMOS-only FPGA. (a) Dynamic power reduction vs. speed-up; (b) Leakage power reduction vs. speed-up, adapted from [128].                     | 28 |

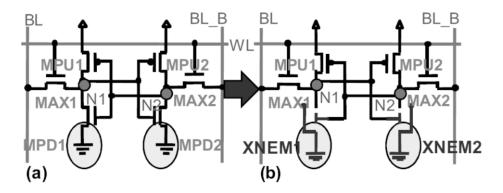

| Figure | 1-22 Schematic of (a) a conventional CMOS SRAM cell and (b) a NEMS/CMOS hybrid SRAM cell with NEMS Switches replacing the pull-down MOSFETs, adapted from [29]                                        | 29 |

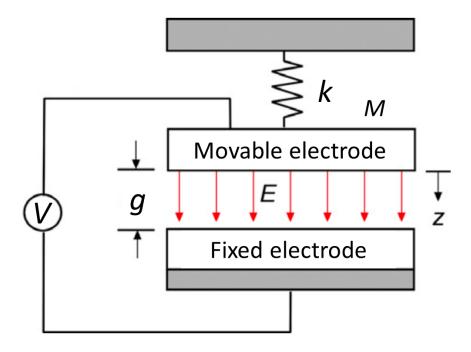

| Figure | 2-1 Schematic diagram of a N/MEMS switch                                                                                                                                                              | 33 |

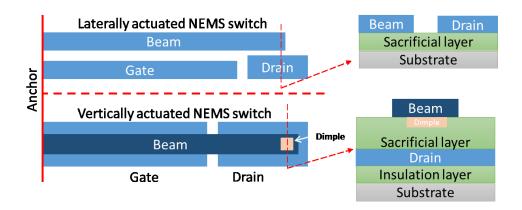

| Figure | 2-2 Schematic of laterally and vertically actuated switches. The drain terminal is closer to the beam to ensure no gate to beam pull-in. The cross-section views of each type are shown on the right. | 37 |

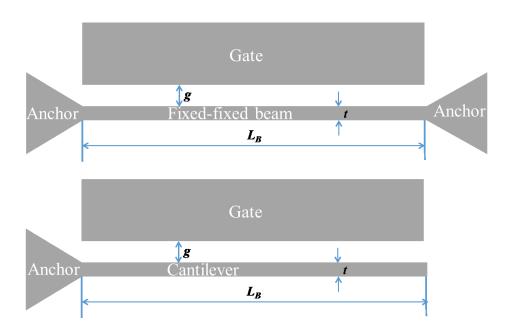

| Figure | 2-3 Fixed-fixed beam and cantilever                                                                                                                                                                   | 38 |

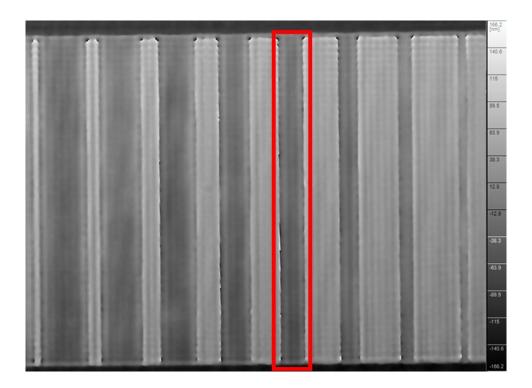

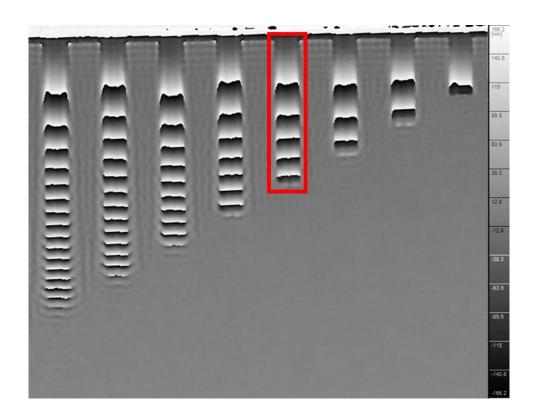

| Figure | 2-4 Phase pattern of a fixed-fixed beam in holography microscope, phase change for one period (white to black) represents deformation of 332.4 nm. The red rectangle enclosed                         |    |

## List of Figures

|        | one of the beams. No severe color change represents a flat topography of the beam. the beam length: $80~\mu m$ .                                                                                                                                                                                              | 40 |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure | 2-5 Phase pattern of cantilever beam in holography microscope, phase change for one period (white to black) represents deformation of 332.4 nm. The red rectangle enclosed one of the beams. More than 5 times of phase change can be found on the beam represents more than 1.5 μm bending. beam width: 4 μm | 41 |

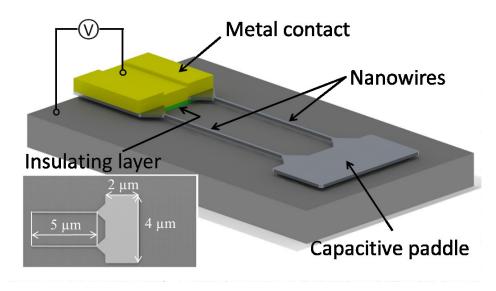

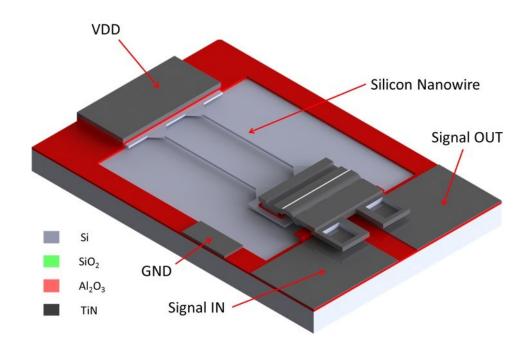

| Figure | 3-1 A schematic illustration of the U-shaped NEMS switch                                                                                                                                                                                                                                                      | 47 |

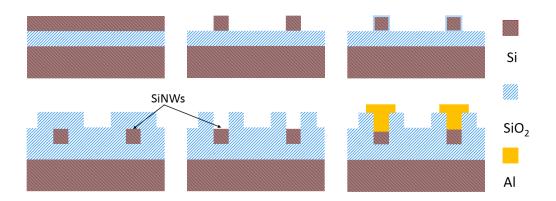

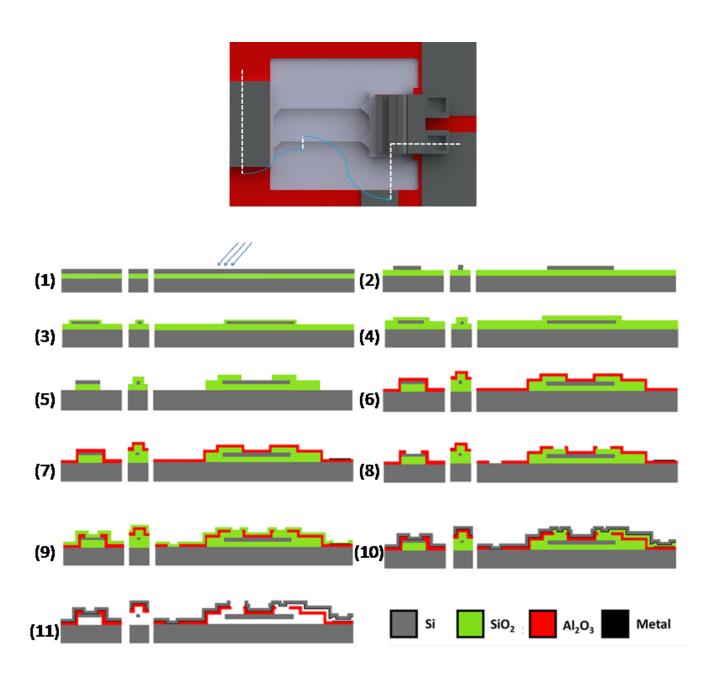

| Figure | 3-2 Process Flow for SiNW based NEMS switch                                                                                                                                                                                                                                                                   | 50 |

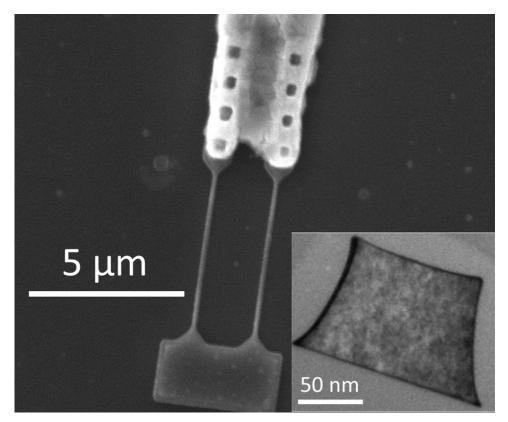

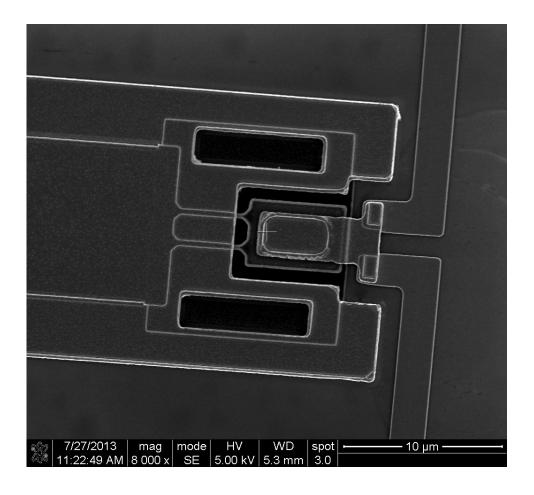

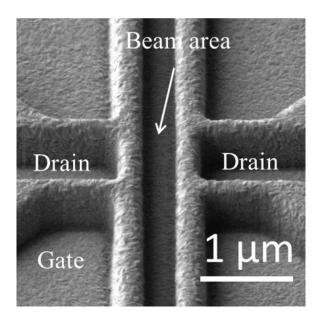

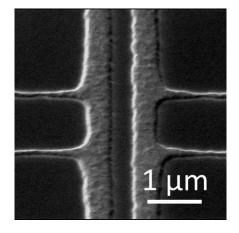

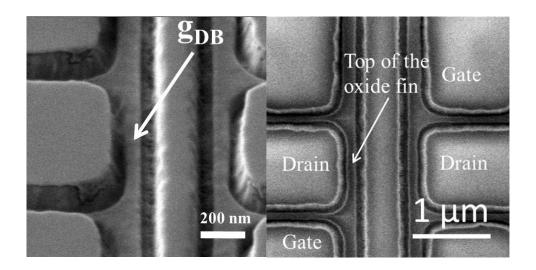

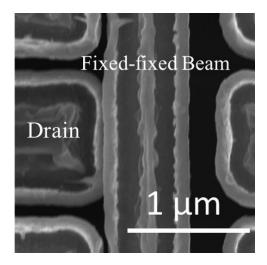

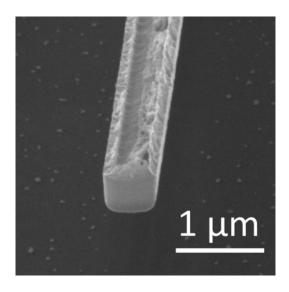

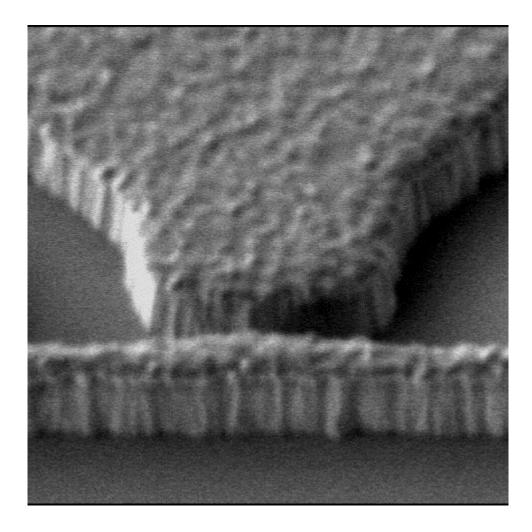

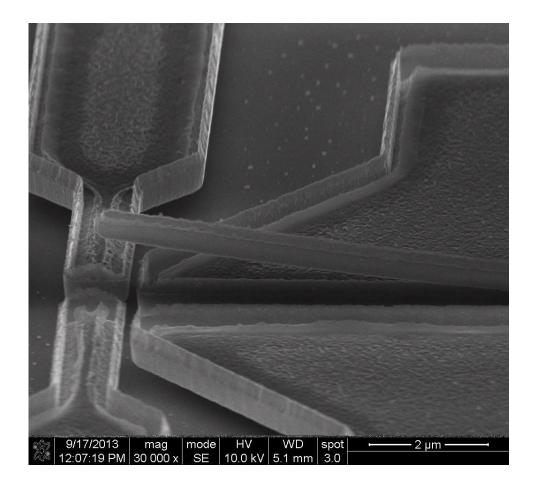

| Figure | 3-3 SEM photo of a U-shaped NEMS switch after HF vapor releasing, Inset: TEM image of a SiNW cross-section                                                                                                                                                                                                    | 52 |

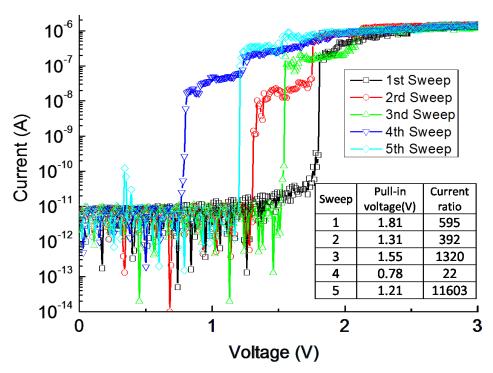

| Figure | 3-4 I-V characteristic of the device shown in Figure 3-3 for the first five switching cycles. The current ratio indicates the change in current that occurs within 10 mV of the pull-in voltage.                                                                                                              | 54 |

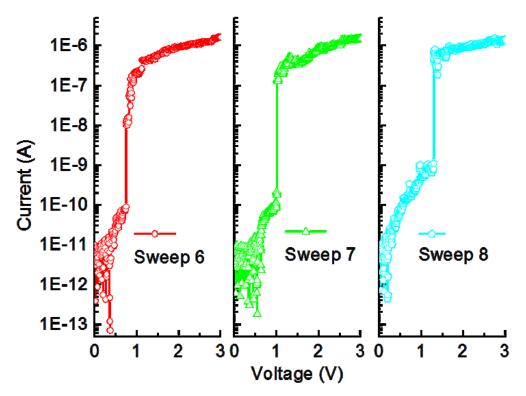

| Figure | 3-5 I-V characteristic of the device, with deterioration in off-<br>state current during the 6 to 8 switching cycles.                                                                                                                                                                                         | 56 |

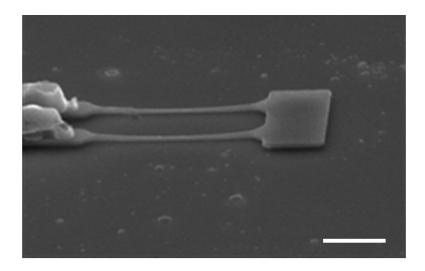

| Figure | 3-6 SiNWs NEMS switch welded on substrate, scale bar: 2 μm                                                                                                                                                                                                                                                    | 57 |

| Figure | 3-7 A schematic illustration of the U-shaped NEMS switch with metal contact.                                                                                                                                                                                                                                  | 58 |

| Figure | 3-8 Process flow of Metal based SiNWs Switches, the cross-section is made along the white dash line above.                                                                                                                                                                                                    | 59 |

| Figure | 3-9 A released U-Shaped SiNW NEMS switch with metal contact                                                                                                                                                                                                                                                   | 60 |

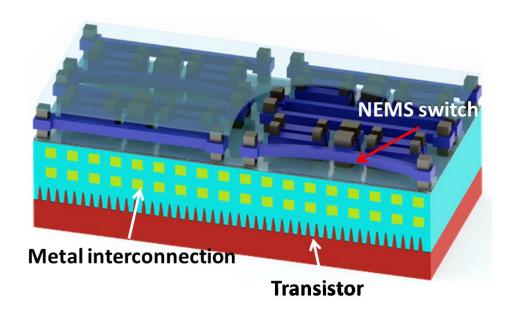

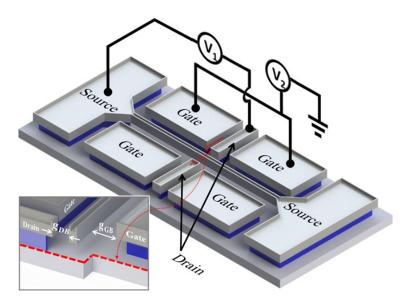

| Figure | 4-1 Schematic of building laterally actuated NEMS switches above CMOS. The NEMS switches are fabricated after transistor and interconnection process for NEMS-CMOS integration.                                                                                                                               | 66 |

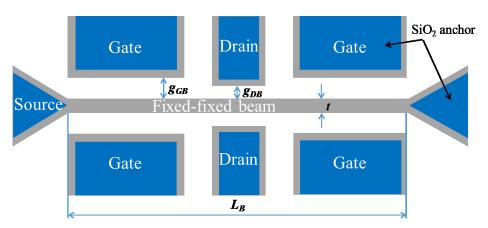

| Figure | 4-2 The schematic drawing of a laterally actuated all metal NEMS switch.                                                                                                                                                                                                                                      | 67 |

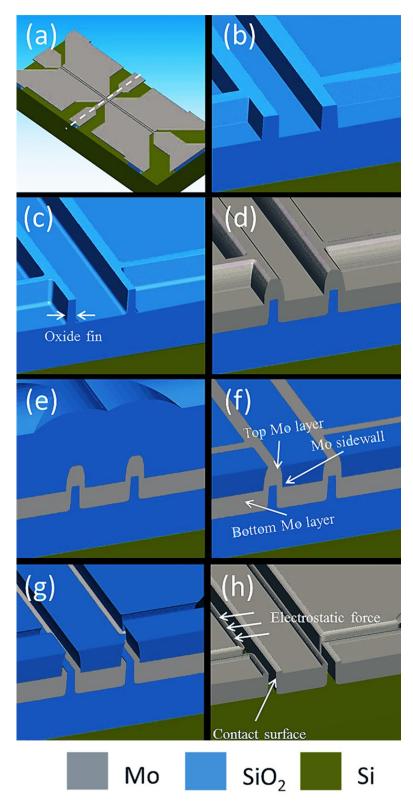

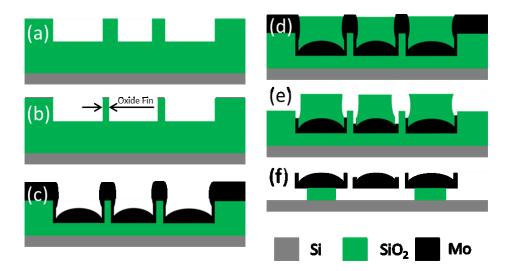

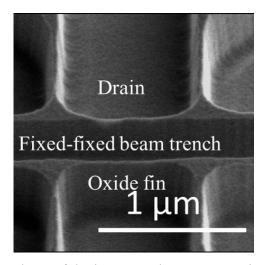

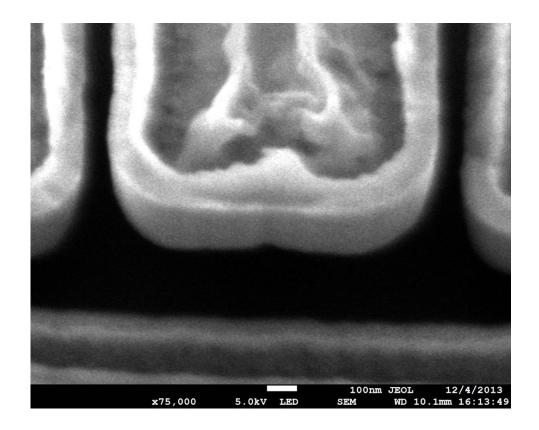

| Figure | 4-3 (a) The white dash line indicates the cross-section used in the following figures (b) SiO2 RIE forming the trench (c) Wet etch reducing the oxide fin thickness (d) 300nm Mo PVD (e) 500nm HDP CVD SiO2 (f) SiO2 CMP (g) Mo RIE (h) VHF release                                                           | 72 |

| Figure | 4-4 the cross-section view of process for all-metal-based NEMS Switch                                                                                                                                                                                                                                         | 74 |

| 76 |

|----|

| 77 |

| 77 |

| 78 |

| 79 |

| 80 |

| 80 |

| 81 |

| 82 |

| 83 |

| 84 |

| 85 |

| 86 |

| 87 |

| 88 |

| 89 |

| 89 |

|    |

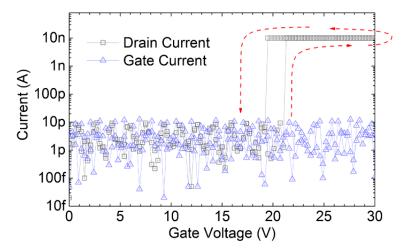

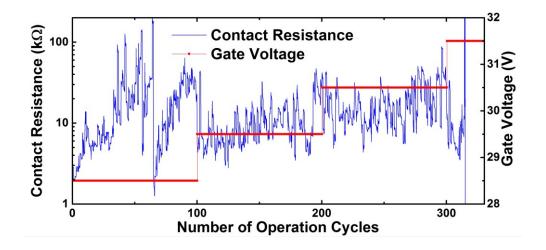

| Figure | 4-22 Contact resistance change over the cycling test                                                                                                                            | 90  |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

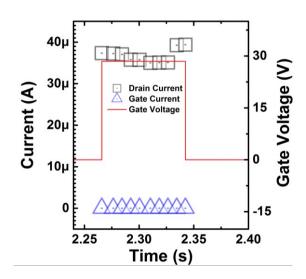

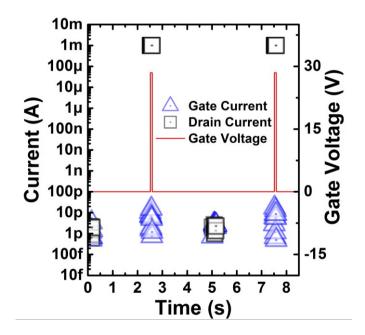

| Figure | 4-23 Electrical tests for a fixed-fixed beam device with dimension of $L_B$ =28 $\mu$ m, t=700 nm and $g_{GB}$ =150 nm Cycling test with 1mA current applied on drain terminal. | 91  |

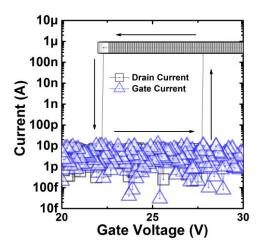

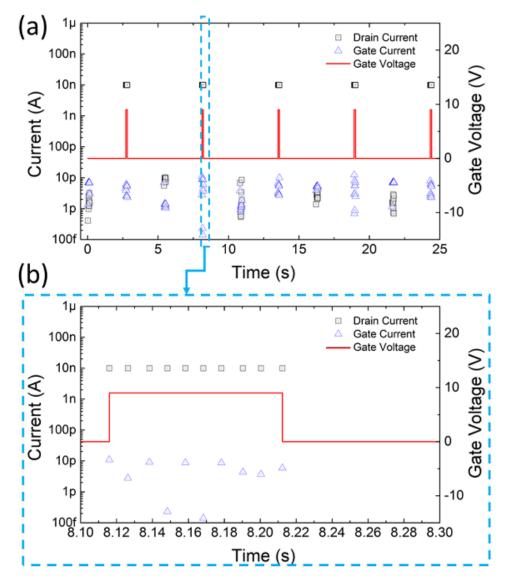

| Figure | 4-24 (a) First 25s of cycling test at 300 °C, (b) zoom-in view from 8.1s to 8.3s of the cycling test. Current displace in the figures uses absolute value.                      | 92  |

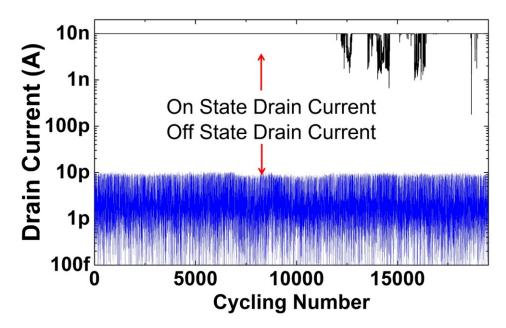

| Figure | 4-25 Cycling test data of drain current recorded at 300 °C                                                                                                                      | 93  |

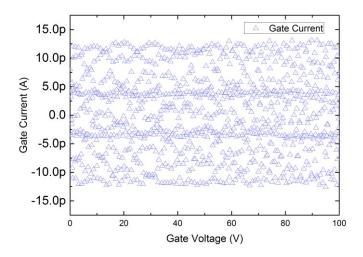

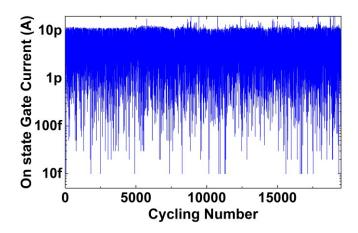

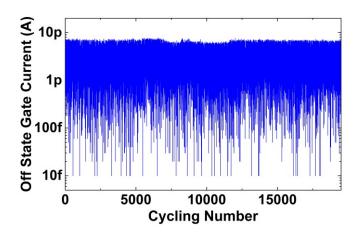

| Figure | 4-26 Cycling test data of on state gate current recorded at 300 °C.                                                                                                             | 94  |

| Figure | 4-27 Cycling test data of off state gate current recorded at 300 °C.                                                                                                            | 94  |

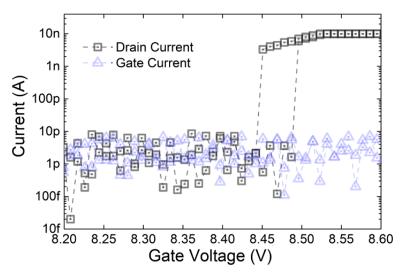

| Figure | 4-28 I-V sweep performed after cycling test at 300 °C. Current displace in the figures uses absolute value. Drain terminal voltage is 1V during this measurement.               | 95  |

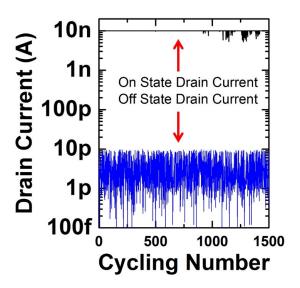

| Figure | 4-29 Cycling test data of drain current recorded at room temperature.                                                                                                           | 96  |

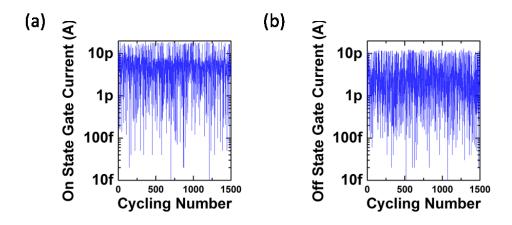

| Figure | 4-30 Cycling test data of (a) on state gate current, (b) off state gate current recorded for room temperature.                                                                  | 97  |

| Figure | 4-31 Drain contact area after cycling test, the beam is attracted by electron charging to another side                                                                          | 98  |

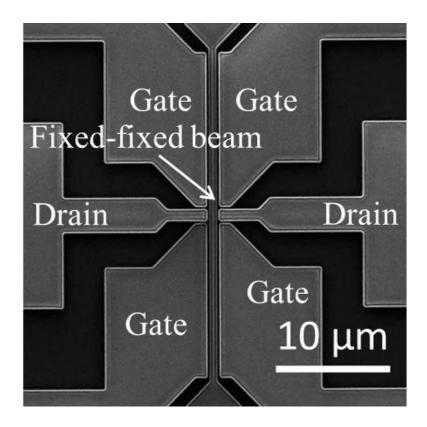

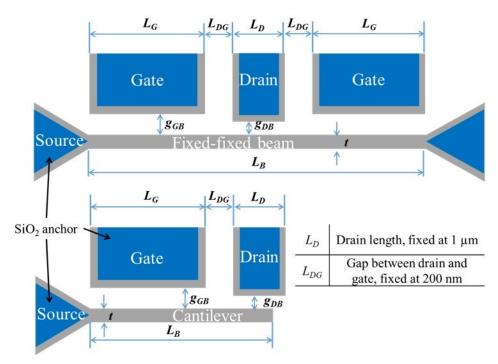

| Figure | 5-1 Schematic drawing of a fixed-fixed beam switch and a cantilever switch                                                                                                      | 102 |

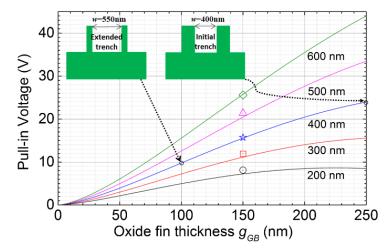

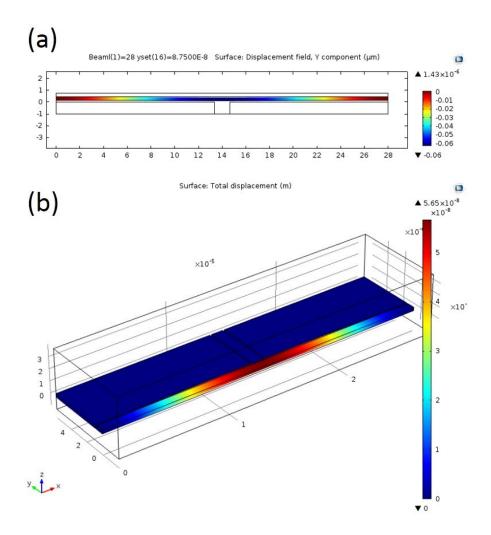

| Figure | 5-2 (a) 2D simulation of a fixed-fixed beam NEMS switch. (b) 3D simulation of a fixed-fixed beam NEMS switch                                                                    | 105 |

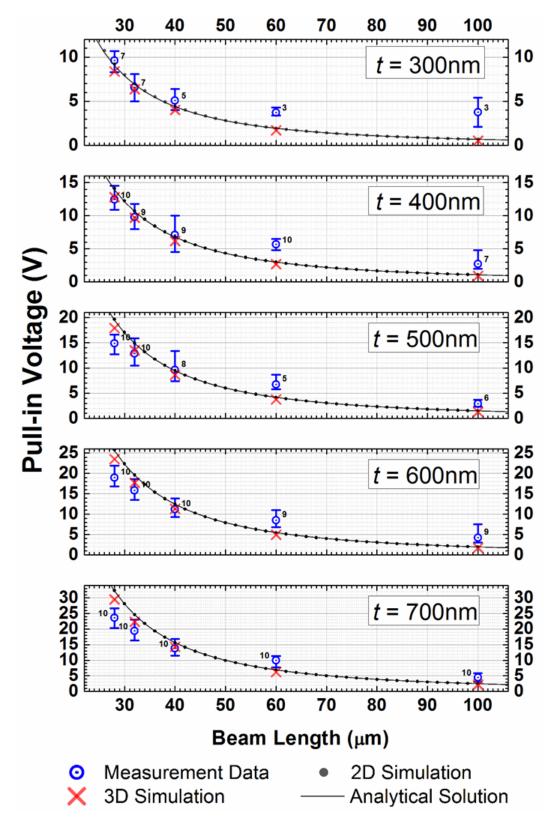

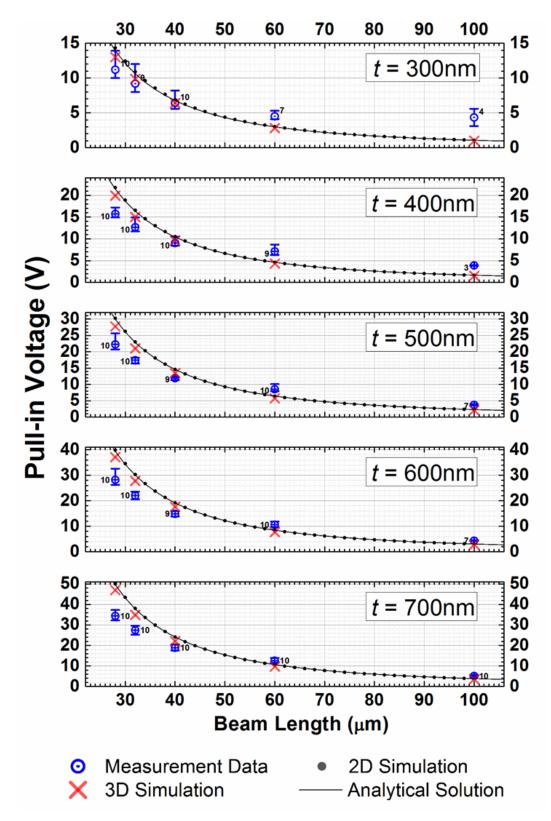

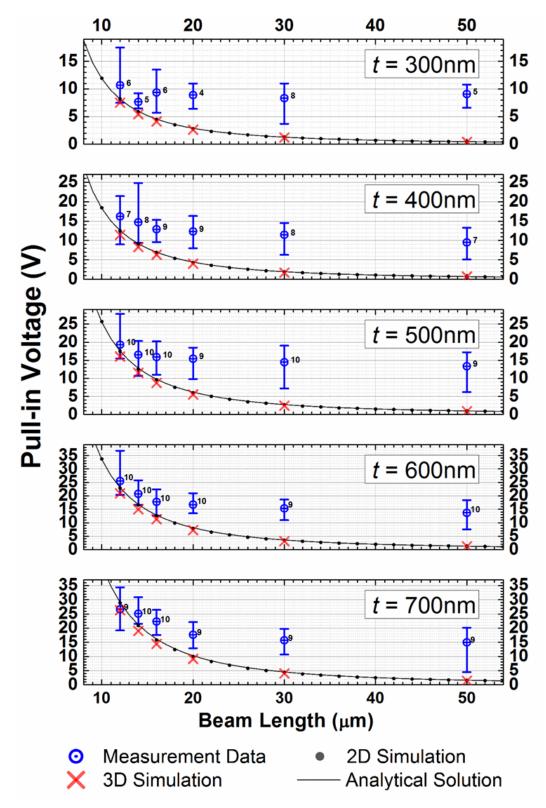

| Figure | 5-3 Pull-in voltage summary of fixed-fixed beam devices with $g_{GB} = 150$ nm, and $g_{DB} = 100$ nm, with beam length $L_B$ , beam width t varies.                            | 107 |

| Figure | 5-4 Pull-in voltage summary of fixed-fixed beam devices with $g_{GB} = 200$ nm, and $g_{DB} = 150$ nm, with beam length $L_B$ , beam width t varies.                            | 108 |

| Figure | 5-5 Pull-in voltage summary of cantilever beam devices with $g_{GB} = 150$ nm, and $g_{DB} = 100$ nm, with beam length $L_B$ , beam width t varies.                             | 109 |

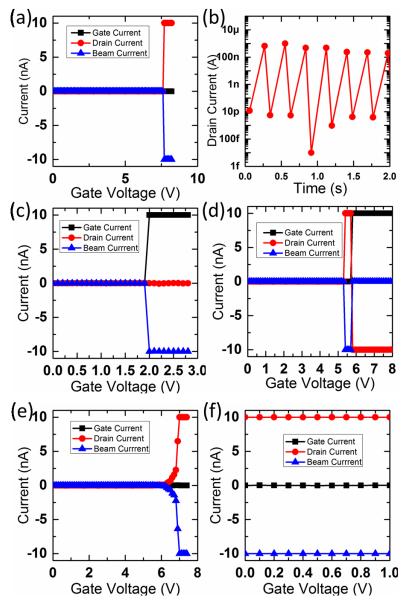

| Figure | 5-6 (a) I-V curve of a repeatable device (b) cycling measurement of a repeatable device. (c) I-V curve of a gate to beam pull-in device. (d) I-V curve of a device to secondary |     |

|        | pull-in. (e) First round I-V curve of a device with stiction (f) Second round I-V curve of a device with stiction                                                                                                    | 112 |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

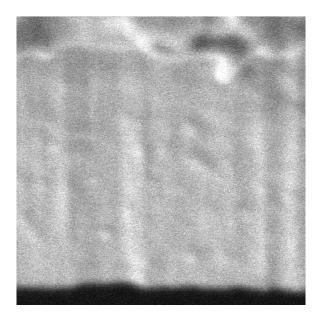

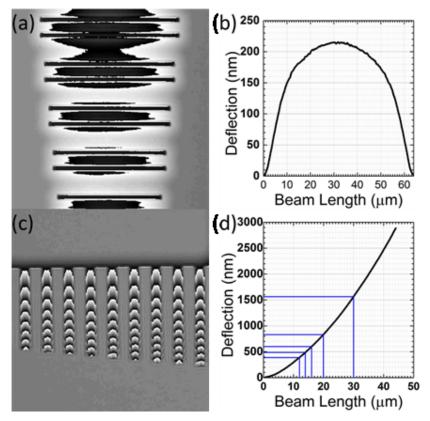

| Figure | 5-7 (a) The phase pattern of the fixed-fixed beams. (b) Beam deflection of a 60 $\mu$ m fixed-fixed beam. (c) The phase pattern of cantilever beams (d) beam deflection of a 50 $\mu$ m cantilever                   | 113 |

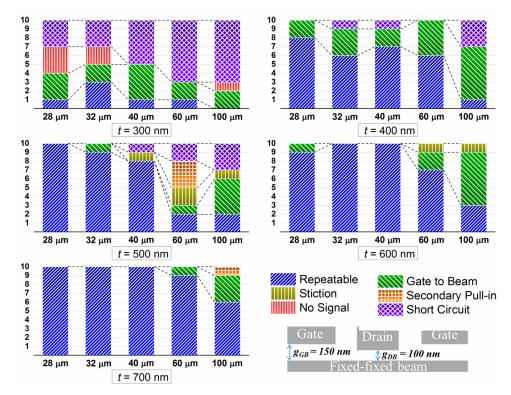

| Figure | 5-8 Failure analysis of fixed-fixed beam devices with $g_{GB}$ = 150 nm, and $g_{DB}$ = 100 nm, with beam length $L_B$ (x-axis), beam width t varies. Number on y-axis indicate the count of different failure mode. | 115 |

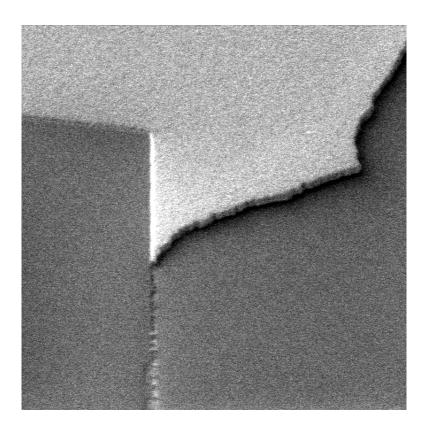

| Figure | 5-9 Gate to beam pull-in devices                                                                                                                                                                                     | 116 |

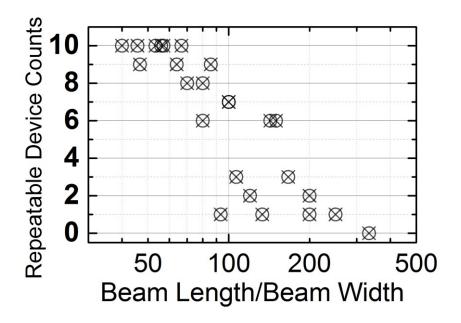

| Figure | 5-10 Counts of repeatable device versus beam length to width ratio                                                                                                                                                   | 117 |

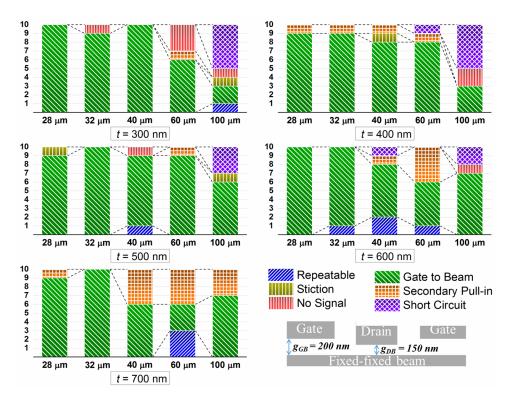

| Figure | 5-11 Failure analysis of fixed-fixed beam devices with $g_{GB}$ = 200 nm and $g_{DB}$ = 150 nm, with beam length $L_B$ (x-axis), beam width t varies. Number on y-axis indicate the count of different failure mode. | 118 |

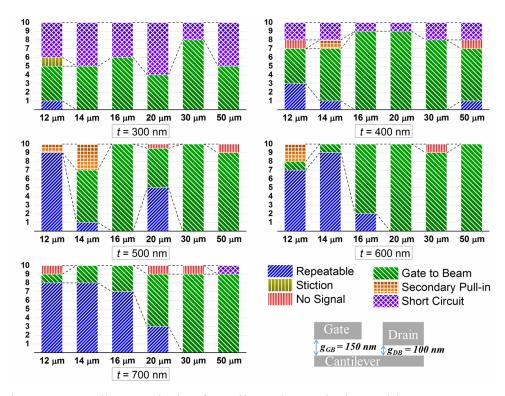

| Figure | 5-12 Failure analysis of cantilever beam devices with $g_{GB}$ = 150 nm, and $g_{DB}$ = 100 nm, with beam length $L_B$ (x-axis), beam width t varies. Number on y-axis indicate the count of different failure mode. | 119 |

| Figure | 5-13 Cantilever in NEMS switch with severe bending.                                                                                                                                                                  | 120 |

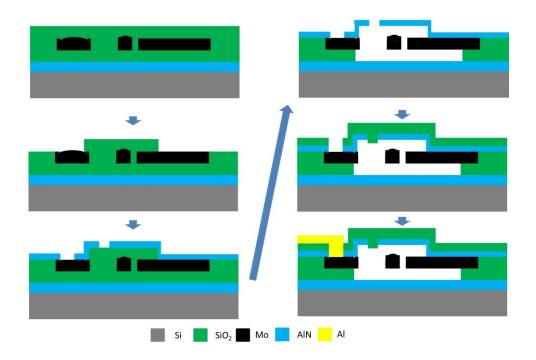

| Figure | 6-1 Proposed Process flow for wafer level encapsulated NEMS switch                                                                                                                                                   | 128 |

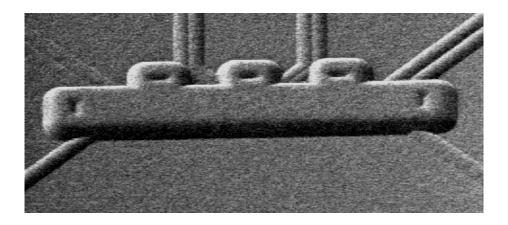

| Figure | 6-2 SEM image of an encapsulated NEMS switch                                                                                                                                                                         | 129 |

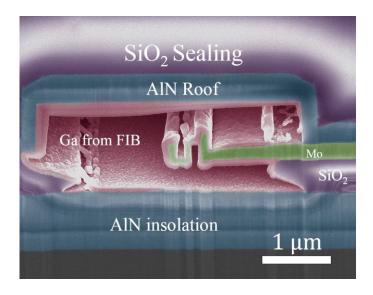

| Figure | 6-3 Cross-section of an encapsulated NEMS switch                                                                                                                                                                     | 129 |

## List of Acronyms

| Al                             | Aluminum                                |

|--------------------------------|-----------------------------------------|

| Al <sub>2</sub> O <sub>3</sub> | Aluminum Oxide                          |

| ALD                            | Atomic Layer Deposition                 |

| AlN                            | Aluminum Nitride                        |

| Ar                             | Argon                                   |

| BEOL                           | Back-End-Of-Line                        |

| BOX                            | Buried-Oxide                            |

| CMOS                           | Complementary Metal–Oxide–Semiconductor |

| СМР                            | Chemical Mechanical Polishing           |

| CNT                            | Carbon Nanotube                         |

| CPD                            | Critical Point Dryer                    |

| DHF                            | Dilute Hydrochloric Acid                |

| DI water                       | Deionized Water                         |

| DRIE                           | Deep Reactive Ion Etching               |

| EBL                            | Electron-Beam Lithography               |

| FEM                                      | Finite Element Method                             |  |  |

|------------------------------------------|---------------------------------------------------|--|--|

| FPGA                                     | Field-Programmable Gate Array                     |  |  |

| HDP CVD                                  | High-Density Plasma Chemical Vapor Deposition     |  |  |

| HF                                       | Hydrofluoric Acid                                 |  |  |

| IC                                       | Integrated Circuit                                |  |  |

| LPCVD                                    | Low-Pressure Chemical Vapor Deposition            |  |  |

| Mo                                       | Molybdenum                                        |  |  |

| MOCVD                                    | Metal-Organic Chemical Vapour Deposition          |  |  |

| MOSFET                                   | Metal-Oxide-Semiconductor Field-Effect Transistor |  |  |

| N/MEMS                                   | Nano / Micro -Electro-Mechanical System           |  |  |

| NEMS                                     | Nano -Electro-Mechanical System                   |  |  |

| NVM                                      | Non-Volatized Memory                              |  |  |

| PECVD                                    | Plasma-Enhanced Chemical Vapor Deposition         |  |  |

| poly-Si <sub>0.4</sub> Ge <sub>0.6</sub> | Polycrystalline Silicon-Germanium                 |  |  |

| Pt                                       | Platinum                                          |  |  |

| PVD                                      | Physical Vapor Deposition                         |  |  |

| PZT                                      | Lead Zirconate Titanate                           |  |  |

| RTA                            | Rapid Thermal Annealing       |  |  |

|--------------------------------|-------------------------------|--|--|

| Ru                             | Ruthenium                     |  |  |

| SEM                            | Scanning Electron Microscope  |  |  |

| Si                             | Silicon                       |  |  |

| Si <sub>3</sub> N <sub>4</sub> | Silicon Nitride               |  |  |

| SiC                            | Silicon Carbide               |  |  |

| SiNW                           | Silicon Nanowire              |  |  |

| SiO <sub>2</sub>               | Silicon Dioxide               |  |  |

| SOI                            | Silicon-On-Insulator          |  |  |

| SRAM                           | Static Random-Access Memory   |  |  |

| TaN                            | Tantalum nitride              |  |  |

| TiN                            | Titanium Nitride              |  |  |

| TiO <sub>2</sub>               | Titanium Dioxide              |  |  |

| UV                             | Ultraviolet                   |  |  |

| VHF                            | Vapor Phase Hydrofluoric Acid |  |  |

| W                              | Tungsten                      |  |  |

| ZnO                            | Zinc Oxide                    |  |  |

## **List of Symbols**

| A                      | Actuation area                                      |  |  |  |

|------------------------|-----------------------------------------------------|--|--|--|

| $a_c$                  | Coefficient for pull-in voltage of cantilever       |  |  |  |

| $a_{ff}$               | Coefficient for pull-in voltage of fixed-fixed beam |  |  |  |

| С                      | Capacitance                                         |  |  |  |

| Е                      | Young's modulus                                     |  |  |  |

| f                      | Natural frequency of the beam                       |  |  |  |

| g                      | Initial gap                                         |  |  |  |

| <b>g</b> <sub>DB</sub> | Gap between beam to drain terminal                  |  |  |  |

| <b>G</b> GB            | Gap between beam to gate terminal                   |  |  |  |

| $I_{ds}$               | Drain to source current                             |  |  |  |

| $I_{off}$              | Off-state leakage current                           |  |  |  |

| k                      | Spring constant                                     |  |  |  |

| $k_B$                  | Boltzmann's constant                                |  |  |  |

| k <sub>eff</sub>       | Effective spring constant of the beam               |  |  |  |

| $L_B$    | Beam length.                                           |  |  |  |

|----------|--------------------------------------------------------|--|--|--|

| $L_D$    | Drain terminal width                                   |  |  |  |

| $L_{DG}$ | Distant between drain terminal and gate terminal       |  |  |  |

| $L_G$    | Gate terminal width                                    |  |  |  |

| m        | Mass of the beam                                       |  |  |  |

| q        | The magnitude of the electrical charge on the electron |  |  |  |

| S        | Subthreshold slope                                     |  |  |  |

| T        | Temperature                                            |  |  |  |

| t        | Width of the beam                                      |  |  |  |

| U        | Dimensional scaling factor                             |  |  |  |

| V        | Voltage                                                |  |  |  |

| $V_{dd}$ | Supply voltage                                         |  |  |  |

| $V_{GS}$ | Gate to source voltage                                 |  |  |  |

| $V_{pi}$ | Pull-in voltage                                        |  |  |  |

| $V_t$    | Threshold voltage                                      |  |  |  |

| W        | Out-of plane thickness of the beam                     |  |  |  |

| Z        | The movable structure with displacement                |  |  |  |

| $Z_{pi}$          | Maximum stable displacement |

|-------------------|-----------------------------|

| $\mathcal{E}_{0}$ | Permittivity of the vacuum  |

## Chapter 1 Introduction of N/MEMS Switches

### 1.1 Power-Efficiency Limitation of CMOS

Since the invention of complementary metal-oxide-semiconductor (CMOS), the integrated circuit (IC) based on CMOS technology virtually dominates every aspect of computation and communication. Two key advantages that have driven the ICs to the success from day one are low-cost and high-performance. As all the components of the ICs are projected on silicon (Si) wafers by photolithography rather than being assembled discretely, the cost of the ICs is essentially reduced with a smaller footprint. The aggressive dimension scale-down allows ICs, consisting of billions of transistors, to be produced cost-effectively.

The better performance of IC is attributed to the faster switch, less power consumption and more functionality of the transistors. As a result, the major motivation for the semiconductor industry is to keep scaling down the dimension and climbing the performance. Traditionally, dimensional scaling has been sufficient to deliver these aforementioned performance merits, but it reaches its bottleneck over the past few years. For metal–oxide–semiconductor field-effect transistor (MOSFET), the drain to source current ( $I_{ds}$ ) will never be zero, instead it decreases exponentially at a rate of subthreshold slope S. In the best case,  $I_{ds}$  will decrease by a factor of 10 for every 60mV below the threshold voltage ( $V_t$ ). The subthreshold slope is restricted by the fundamental

limit of thermal voltage,  $k_BT/q$ , where  $k_B$  is Boltzmann's constant, T is the temperature, q is the magnitude of the electrical charge on the electron. As the supply voltage ( $V_{dd}$ ) and threshold voltage keep scaling down with the dimensions, there is less headroom below the threshold voltage. Consequently, the subthreshold leakage current increases exponentially with decreasing threshold voltage. The off-state leakage current ( $I_{off}$ ) between the drain and the source increases dramatically, which can be estimated as[1].:

$$I_{off} \propto 10^{-V_t/S}$$

Figure 1-1 Trends of power supply voltage  $V_{dd}$ , threshold voltage  $V_t$ , and gate oxide thickness  $t_{ox}$  versus channel length for CMOS logic technologies. Adapted from [2]

The threshold voltage scaling-down has significantly slowed down below 0.3V to maintain a low off-state leakage current [3]. Meanwhile, the scaling-down of supply voltage ( $V_{dd}$ ) has also slowed down, as the value of gate to source voltage  $V_{GS}$  should be maintained to achieve certain overdrive voltage

$\mid V_{GS} - V_T \mid$  (for high performance) as shown in Figure 1-1. Therefore, the active power consumption ( $\propto {V_{dd}}^2$ ) and static power consumption ( $\propto {I_{off}} \times V_{dd}$ ) become difficult to be controlled simultaneously. Furthermore, the gate to channel leakage current caused by direct tunneling through the gate oxide also worsens the problem [4].

Figure 1-2 Power density versus minimum feature size as reported in [5].

From Figure 1-2, the power density of the microprocessors reached the dangerous territory of 10W/cm<sup>2</sup> even before the release of Intel P6, higher than that of a hot plate. It was predicted to get worse for smaller critical dimensions. The traditional approach of simply scaling down the dimensions must be altered. To avoid the unreasonably high power density, the industry went from high speed single-core processors to slower multi-core processors working in parallel. However, parallelism is still only a temporary fix, the power consumption cannot be reduced indefinitely. To continually constrain the power density within a reasonable value, subthreshold leakage current needs to be eliminated.

### 1.2 The Call of New Applications

Continuous dimensional scaling-down explores a brand new field for diverse applications of computational devices. Portable and autonomous electronics have created an unexpected market in the recent years. Many researches are focusing on increased functionality of mobile devices, to make them the ultimate customer interface to the world [6].

Computational devices with limited power consumption and power resources can be embedded in almost every field. Such systems can be used to collect information with various sensor nodes, ranging from environmental monitoring [7, 8], building management [9], industrial application [10] to personal health care system[11-13] and home automation[14]. In these applications, the devices typically rely on a finite energy source like a battery or very limited power supply, such as energy harvester [15]. With limited progress in battery technology, the development of these technologies is greatly constrained. On the other hand, unlike pure computational devices, these sensor nodes or mobile devices will stay in a hibernating state for most of the time. Thus, technology which can eliminate the off-state power consumption will be favorable.

#### 1.3 Mechanical Switches

Despite of some potential optimization that can extend the life of CMOS technology, the fundamental obstacle of subthreshold slope still underlies. Alternatives have been demonstrated with subthreshold slopes below 60 mV/dec, such as: ferroelectric FETs [16], tunneling FETs [17], and impact

ionization FET[18]. In this thesis, we will focus on electromechanical devices which show most unique electrical properties.

Micro/Nano-Electro-Mechanical system (N/MEMS) switches are devices which employ mechanical force to actuate a movable structure (in most cases, beam) to make a conductive path between two electrodes as shown in Figure 1-3(a). By removing the controlling mechanical force, the mechanical spring forces will pull back the conductive path, leaving the beam suspended. Due to the nature of their operational principle, N/MEMS switches define the off state by a physical air gap. The on state of the N/MEMS switches is established only when the contact is physically closed. Thus, the N/MEMS switches feature two fundamental properties which are unavailable in MOSFETs: zero off-state current and abrupt switching. A typical I-V curve can be found in Figure 1-3 (b). Moreover, zero off-state current means zero standby power dissipation and abrupt switching behavior suggest the potential of freely reduce the turn-on voltage.

Figure 1-3 (a) Basic electrostatically actuated mechanical switch. (b) Measured current versus gate voltage characteristics for a mechanical switch. Adapted from [19].

Since N/MEMS switches can be fabricated at relatively low process temperature, and these switches do not have to be built with single crystalline semiconductor materials such as silicon (Si), they can be placed on top of CMOS routing layers using a back-end-of-line (BEOL) compatible process, which will reduce the chip footprint. Furthermore, alternative substrates such as glass or plastic can be used, which would significantly reduce the cost.

As N/MEMS switches can be fabricated directly above the CMOS wafer, possible applications for hybrid N/MEMS-CMOS technology include power gating [20-26], static random-access memory (SRAM) [27-29], field-programmable gate array (FPGA) [30-32]. The hysteresis property of the switches also makes them suitable for non-volatile memory (NVM) application [1.17]. Another advantage switches have over CMOS is robustness against temperature variations and radiation hardness, which is attractive, especially for industrial, military and space applications [33, 34].

Many issues still remain to be solved in order to apply N/MEMS switches in logic applications, among which the most critical one is contact reliability, since logic circuits would require the switches to operate over 10<sup>16</sup> hot switching cycles. Since mechanical touches need to be established for every turn-on cycle, high velocity impact of the movable beam and the fixed electrode as well as the resultant "tip bouncing" can quickly degrade the contact [35, 36].

Another significant issue for N/MEMS switches is the presence of surface adhesion force (Van der Waals force) [37, 38]. The prototypes developed so far are generally large for realistic applications. With the devices scaling down,

permanent stiction might happen if the elastic restoring force is not sufficiently high. In order to minimize stiction and maintain clean contact spots, hermetically encapsulation [39, 40] process for N/MEMS switches should be developed.

#### 1.4 Actuation Mechanism

In this section, various actuation mechanisms used in N/MEMS switches are classified into four major groups: electrostatic, piezoelectric, electrothermal, and electromagnetic actuation. These actuation mechanisms are commonly used in other MEMS devices with their own unique strength and weakness. In the following section, we will analyze these mechanisms by focusing on their power consumption and integration feasibility.

#### 1.4.1 Electrostatic Actuation

In electrostatic actuation, a typical configuration consists of a movable electrode connected to suspending mechanical springs, while a fixed electrode is anchored onto the substrate. When a voltage difference is applied between the electrodes, the electrostatic attractive force accelerates the movable electrode to the stationary electrode. Meanwhile, the spring suspending the movable electrode is deformed.

Figure 1-4 Schematic illustrations of an electrostatic actuated switch. (a) Isometric view. (b) Cross sectional view along the channel (AA') in the off-state. (c) Cross-sectional view in the on-state. In the off state, an air gap separates the channel from the metallic source and drain electrodes so that no current can flow. In the on state, electrostatic force between the gate and the body electrode causes the gate to be deflected downward sufficiently to bring the channel into contact with the source and drain electrodes, to form a conductive path for current to flow. Adapted from [41]

The electrostatic actuation gains most of the focus in the community. In principle, utilization of electrostatic actuation tolerates a wide variety of materials because it only requires conductors to be separated by a non-conductive gap. It is relatively easy to manufacture by using conventional process and material. Unlike electrothermal or electromagnetic actuation, it does not consume much active power as charging a capacitor is the only operation needed to turn on the devices [42, 43]. No continues current path exists on the actuation side. The switching speed is relatively higher with only 10 to 100 ns delay [44, 45], while the electromagnetic and electrothermal switches usually have more 1 ms delay. One major constraint for electrostatic actuation is its high actuation voltage, and early demonstrations typically require around 50V supply voltage [46-48]. Fortunately, the actuation voltage scales down quickly with the dimension. Although most of the recent study

still requires a supply voltage of more than 5 V [49-55], a few approaches have been proposed to match the supply voltage with CMOS [41, 56, 57].

#### 1.4.2 Piezoelectric Actuation

Piezoelectric effect is understood as the linear electromechanical interaction between mechanical and electrical state in crystalline materials. An applied voltage across the electrodes of a piezoelectric material will result in a net strain that is proportional to the magnitude of the electric field. Typical piezoelectric materials for MEMS application include lead zirconate titanate (PZT), aluminum nitride (AlN) and zinc oxide (ZnO).

Figure 1-5 A PZT based MEMS switch. The switch utilizes the converse piezoelectric effect to generate movement. Two electrodes on the left (Top and bottom) provide the necessary electric field to bending down the contact. Output current flow is highlighted in green where the physical contact is formed. Adapted from [58, 59]

Piezoelectric switches provide strong actuation force and large deflection [60, 61]. The actuation voltage can be controlled within 1 V [62-70]. The major hurdle for piezoelectric actuation is the material development. PZT is

considered as the traditional piezoelectric material for MEMS, but the fabrication process is not CMOS compatible. Recent progress on AlN actuator makes the piezoelectric actuation mechanism an attractive alternation, but process development of a scaled device remains to be explored.

#### 1.4.3 Electrothermal Actuation

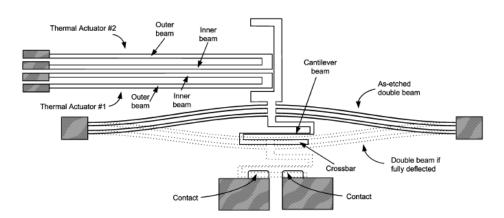

Electrothermal actuators use stacked layer of materials with different thermal expansion coefficients, or a single material with specific geometry (Figure 1-6) [42]. Two actuators have been fabricated the switch will buckle when heated and go back to original state when power is turned off.

Figure 1-6 SEM image of a fully fabricated single-pole single-throw electromagnetic MEMS switch. When current applied to the coils, the magnetic force generated by the stationary permalloy overcomes the return spring force and closes the switch. Adapted from [71]

A few advantages are shown by using electrothermal actuation, including large displacement, high contact force (which provides low contact resistance), and relatively simple fabrication process. However, unlike electrostatic or piezoelectric actuators, electrothermal actuators consume a larger amount of active power as a constant temperature needs to be maintained for deformation.

In this sense, the electrothermal actuation has a fundamental contradiction with N/MEMS switch technology.

#### 1.4.4 Electromagnetic Actuation

Reported electromagnetic switches are normally based on the deflection of NiFe permalloy cantilever which is actuated by coils [72-80]. Figure 1-7 shows an electromagnetic switch, where the permalloy serves as a movable structure and is connected to the gold contact.

Figure 1-7 SEM image of a fully fabricated single-pole single-throw electromagnetic MEMS switch. When current applied to the coils, the magnetic force overcomes the return spring force and closes the switch. Adapted from [79]

The electromagnetic switches have some excellent performance including low operating voltage, low contact resistance and good endurance. But these devices are too large and slow to be used in ICs. Furthermore, the performance does not appear to be energy-efficient, and processing of ferroelectric materials is not compatible with CMOS technology.

#### 1.4.5 Comparison of Different Actuation Mechanisms

Table 1-1 summarized the above mentioned four different actuation mechanisms. Electrostatic actuation would be the most suitable solution for N/MEMS switches. Considering the difficulty in process development and the cost of fabrication, any device targeting to replace MOSFET should be developed based on current CMOS process. Unlike piezoelectric and electromagnetic actuation, electrostatic actuation does not have specific requirement for material and can be easily fitted in the CMOS compatible process.

Table 1-1 Comparison of four actuation mechanisms

|                   | Electrostatic | Piezoelectric | Electrothermal       | Electromagnetic |

|-------------------|---------------|---------------|----------------------|-----------------|

| Power Consumption | Low           | Low           | Very High (>1<br>mW) | High(> 1 mW)    |

| Fabrication       | Easy          | Medium        | Easy                 | Difficult       |

| Speed             | Fast (~10 ns) | Fast (~10 ns) | Slow (> 1ms)         | Slow (> 1ms)    |

| Scalable          | Good          | Medium        | Medium               | Poor            |

Moreover, the simple fabrication process and structure design ensure the dimension can be scaled down easily. In the meantime, the major drawback, i.e., high actuation voltage, can be reduced by using smaller device dimension. The power consumption of the electrostatic N/MEMS switches only comes from charging the capacitor, which can be considered as very limited.

On the other hand, electrothermal actuation and electromagnetic actuation have their fundamental limitation in mechanical switch application. Electrothermal actuation requires a continued power supply, which contradicts

the merits of mechanical switches. Electromagnetic actuation needs CMOS incompatible materials as well as tedious process for the coil.

As a result, most of the studies focus on electrostatic actuation. In the next section, recent studies on electrostatic actuated N/MEMS switch prototypes will be reviewed.

# 1.5 Recent Prototypes of N/MEMS Switches

In this section, various prototypes of N/MEMS switches are summarized, mainly focused on the process integration, electrical performance and reliability.

#### 1.5.1 Folded- Flexure Beams Switches

Figure 1-8 shows the schematic view of the folded-flexure beams MEMS switches. The work is done by a joint research effort from UC Berkeley, MIT and UCLA [21, 81-110]. The switch is comprised of a movable plate (source) with four folded supporting beams at each corner. The folded-flexure beams are further extended to the anchor on the substrate. The gate and drain terminals are buried beneath the moveable plate with an air gap in between. When the gate-to-source voltage is sufficient to pull down the plate, physical contact will be established between source and drain, and then electrical signal will pass from the left side drain terminal across the movable source to the right side drain terminal.

Figure 1-8 Top view a Folded-beam Switch, adapted from [99]

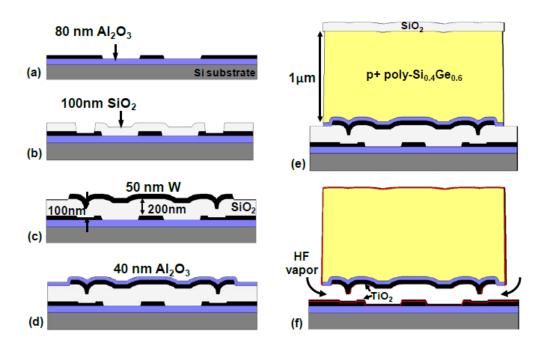

A four mask process is developed for the electrostatically actuated switches as shown in Figure 1-9. The process starts with atomic layer deposition (ALD) of 80nm aluminum oxide (Al<sub>2</sub>O<sub>3</sub>) at 300°C as bottom insulation. 50 nm tungsten (W) deposited by magnetron sputtering is used as bottom electrodes (gate and drain). Then silicon dioxide (SiO<sub>2</sub>) deposited by low-pressure chemical vapor deposition (LPCVD) at 400°C works as the sacrificial material. Two layers of W and Al<sub>2</sub>O<sub>3</sub> are then deposited and patterned as top electrode (source). *In-situ* boron-doped polycrystalline silicon-germanium (poly-Si<sub>0.4</sub>Ge<sub>0.6</sub>) deposited at 410°C by LPCVD is used as structural material. The low temperature LPCVD process is developed for post-CMOS integration. The thick poly-Si<sub>0.4</sub>Ge<sub>0.6</sub> mainly serves as supporting layer for the W and Al<sub>2</sub>O<sub>3</sub>. Lastly, an ultra-thin (3Å thick) coating of titanium dioxide (TiO<sub>2</sub>) is deposited at 300°C by ALD after the device is released by vapor phase

hydrofluoric acid (VHF). The process temperature is controlled under 410 °C, all the materials used are CMOS compatible.

Figure 1-9 Process flow of the folded-flexure switch, adapted from [99]

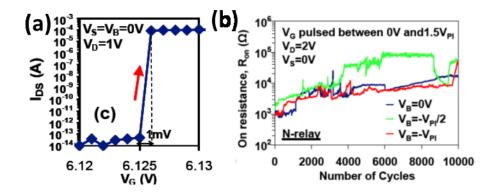

Although the device occupies quite a large area, it shows very good electrical performance. Figure 1-10 shows the switch has an S<0.1mV/dec abrupt turn on behavior at 6.12V. The contact resistance is stabilized at  $1\sim10$  k $\Omega$ . Longer endurance measurement of 1.25 billion on/off cycles in  $N_2$  ambient without stiction or failure is also demonstrated.

Device functionality is verified under a temperature range of 30° C -200°C. Radiation hardness of the devices is also achieved with alpha particles of various doses (200K rad, 2M rad, 20M rad). It is found that only switches exposed to 20M rad shows 10% jump in turn on voltage. Lower doses cause a negligible shift [99]. The typical amount of radiation encountered in space due to cosmic radiation is 50-100 rad/year. In the maximum intensity zone of inner

Van Allen belt, radiation can reach as high as 500k rad/year [111], under which it would still take 40 years to reach a level of 20M rad. Therefore, radiation is not expected to be a concern.

The 1 µm poly-Si<sub>0. 4</sub>Ge<sub>0.6</sub> deposition is vital to the success of the whole process. A thick, low stress structure material eliminates the deformation of the switches induced by the thin, high stress material below. TiO<sub>2</sub> coating is also very important as it greatly raises the endurance of the switches from a few cycles to hundreds of billions of cycles [102].

Figure 1-10 (a) I-V curve of switch turn on. (b) On-state resistance with cycling for different applied body bias, adapted from [41]

### 1.5.2 Platinum Coated Polysilicon Switches

Laterally actuated switch is an attractive solution because it allows the fixed electrodes to be patterned with the movable structure at the same time. Unlike the above mentioned vertically actuated switches, the contact surface for laterally actuated switches is on the sidewall. Thus, unless the whole structural material is metal, the movable beam needs proper coating for the contact.

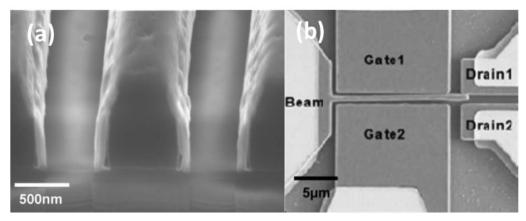

A team from Stanford University developed laterally actuated, platinum-coated polysilicon switches [54, 112-115]. A 2 μm SiO<sub>2</sub> is first deposited by LPCVD at 400 °C, which serves as both the sacrificial and the insolation layer. A 1.2-μm-thick *In-situ* doped polysilicon layer is then deposited by LPCVD at 580 °C and subsequently annealed at 1075 °C for 30s. A 300-nm oxide hard mask is used to pattern the polysilicon. The minimum gap is 600 nm. To coat the polysilicon sidewall with platinum (Pt), a 50 nm-thick Pt layer is sputtered followed by anisotropic etching to remove the Pt film from the bottom and top surfaces as shown in Figure 1-11 (a). The polysilicon structure is released by 49% hydrofluoric acid (HF) and critical point dryer (CPD) as shown in Figure 1-11(b).

Figure 1-11 (a) SEM cross section of non-released platinum-coated beams. (b) SEM images showing actuation of a five terminal polysilicon switch coated with platinum. Adapted from [112]

The device shows abrupt turn-on and turn-off behavior at 8 V and 5 V, respectively. However, the study only includes single device demonstration, the yield of the switches is not mentioned. The fabrication process needs high temperature deposition as well as very high temperature annealing, which makes it unsuitable for post-CMOS integration.

### 1.5.3 Laterally Actuated Ruthenium Switches

Pure metal structural layers usually suffer from high strain and stress, but the deposition can be done at low temperature, which enables post-CMOS switch integration. Czaplewski et al [116, 117] demonstrated a laterally actuated switch using ruthenium (Ru) as both the contacting and structural layer.

Figure 1-12 Laterally actuated ruthenium switches (a) SEM photo (b) process flow. Adapted from [116]

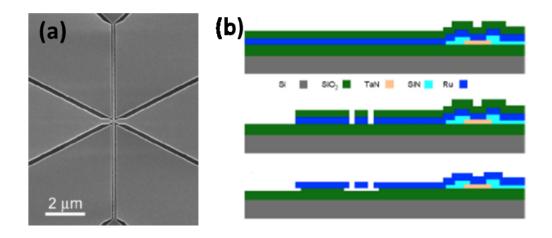

The switches are fabricated as follows (Figure 1-12 (a)). A 500 nm thick  $SiO_2$  is thermally grown on silicon wafers as isolation dielectric and sacrificial layer. Tantalum nitride (TaN) interconnect is then sputtered and patterned as on-chip resistor. 100 nm Silicon nitride ( $Si_3N_4$ ) is subsequently deposited for isolation, where via is also patterned and etched. Next, a 200 nm thick Ru and a 100 nm thick  $SiO_2$  hard mask are deposited. The Ru-layer is subsequently patterned and etched with the  $SiO_2$  hard mask. The smallest features of the switch, the actuation gaps (20-70 nm) and beam width (50-100 nm), are patterned using electron-beam lithography (EBL). Finally, the switches are

released by wet etching (1:3 HF: deionized (DI) water) for 1 minute, followed by rinsing in DI water and blown dry with N<sub>2</sub>.

Figure 1-13 I-V curve of laterally actuated Ru switches, adapted from [116]

One of the fabricated switches with a beam length of 5  $\mu$ m, beam thickness of 100 nm and gap width of 50 nm is measured for electrical properties as shown in Figure 1-13. The turn-on voltage is 13 V. However, the process yield is low, as only 12 switches are tested to be functional among 800 fabricated devices.

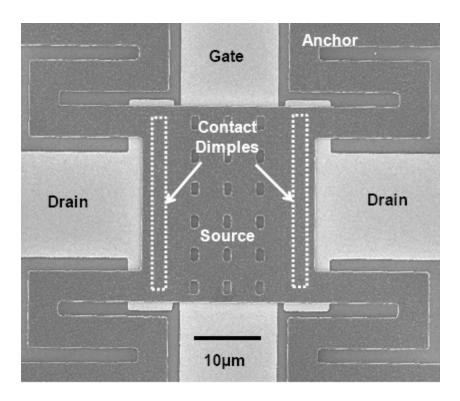

## 1.5.4 TiN Based Vertically Actuated Switches

Another example of pure metallic switches using titanium nitride (TiN) as structural and contact material is reported in [118-120]. The cantilever-type NEMS switches with 40-nm-thick suspension air gap and 50-nm-thick TiN are designed and fabricated. The bottom electrodes are fabricated with physical vapor deposition (PVD) of TiN on a Si<sub>3</sub>N<sub>4</sub> insulation layer. The sacrificial SiO<sub>2</sub> layer is deposited by plasma-enhanced chemical vapor deposition

(PECVD) with a 40 nm actuation-gap from the gate and a 20 nm dimple gap from the drain. The movable top electrode is formed with 10 nm thick PVD TiN and an additional 40 nm thick metal-organic chemical vapor deposition (MOCVD) TiN layer. The length and width of the beams range from 700 nm to 900 nm and 200 nm to 400 nm, respectively. The devices are finally released by a wet process, followed by a CPD step as shown in Figure 1-14.

Figure 1-14 An SEM image of TiN Switch, adapted from [118]

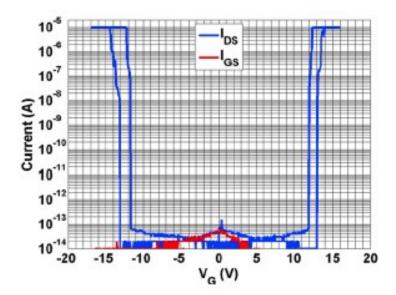

Figure 1-15 shows the drain current versus gate voltage characteristics for a switch with cantilever length of 700 nm. The devices show only few dozen on/off cycles and contact resistance close to 1  $G\Omega$ , and thus further investigation needs to be done to improve the metal-to-metal contact.

Figure 1-15 Measured I-V curve for TiN devices, adapted from [118]

## 1.5.5 Comparison of the Four Prototypes

Among the above mentioned four prototypes, the folded-flexure beams switches are proven to be the most reliable ones, with well controlled process temperature, lower turn-on voltage, good endurance and very high process yield. With the device dimension scaling down, the following three prototypes face their own problem. The platinum coated polysilicon switches require process temperature as high as 1075 °C. The laterally actuated ruthenium switches show very limited process yield. The TiN based switches have very high contact resistance which should not be observed with metallic contact surface. The turn-on voltage of the later three devices is also larger. Thus, more work should be done to achieve low temperature process integration, low pull-in voltage, low contact resistance and high process yield with scaled N/MEMS switches.

Table 1-2 Summary of devices described above

|                                     | Folded- flexure beams switches | Platinum coated polysilicon switches | Laterally actuated ruthenium switches                   | TiN based vertically actuated switch |

|-------------------------------------|--------------------------------|--------------------------------------|---------------------------------------------------------|--------------------------------------|

| Pattern method                      | Photolithography               | Photolithography                     | EBL                                                     | Photolithography                     |

| Typical movable structure dimension | 60 μm × 60 μm                  | 16 μm × 0.8 μm                       | 5 μm × 0.5 μm                                           | 0.7 μm × 0.2 μm                      |

| Highest Process temperature         | 410 °C                         | 1075 °C                              | 1200 °C (250 °C<br>after the first oxide<br>deposition) | Not mentioned                        |

| Turn-on voltage                     | 6 V                            | 8 V                                  | 13 V                                                    | 16 V                                 |

| Working<br>temperature              | Up to 200 °C                   | Room temperature                     | Room temperature Room tempe                             |                                      |

| Yield                               | >95% [99]                      | Not mentioned                        | 1.5%                                                    | Not mentioned                        |

# 1.6 N/MEMS Switches Applications

N/MEMS switches provide some unique properties which are unavailable in CMOS technology as well as most of the proposed CMOS-replacement electronics. Table 1-3 summarizes some of these features and their targeted applications. In this section, selected applications are reviewed to show the merits of introducing N/MEMS switch technology as a key component of electronics.

Table 1-3 Switch property versus application

| Property                       | Application                           |

|--------------------------------|---------------------------------------|

| Zero leakage                   | Low-power circuit, power gating, FPGA |

| Hysteresis, Stiction           | Non-volatile memories                 |

| High temperature and radiation | Industrial, Military                  |

### 1.6.1 Pure N/MEMS Switches Circuit

Although the slower switching speed induced by mechanical delay suggests that N/MEMS switches cannot match with CMOS in operational frequency, the zero leakage current properties makes N/MEMS switches a compelling technology in ultra-low power circuits. Moreover, its nature to resist high temperature and radiation opens another regime of harsh-environment electronics.

The most complex pure N/MEMS switches integrated circuit reported so far consists of 98 MEMS switches, where the single device operation has been described in section 1.5.1. [87, 106, 107, 121, 122]. It demonstrates the micro-architecture and circuit techniques for building multipliers with

switches. A 16-bit mechanical switch multiplier is shown in Figure 1-16. Experimental results indicate that pure switch technology consumes 10 times lower energy per operation when compared to an equivalent CMOS multiplier of 90 nm technology node.

The enhanced performance of the multiplier confirms that the advantage of energy-efficiency can be extended to larger arithmetic blocks, suggesting that large scale logic circuit such as microprocessors can be expected to demonstrate similar energy/performance improvements by using N/MEMS switches as the basic circuit functional elements.

Figure 1-16 Experimental results of the MEMS switch circuit, adapted from [87]

### 1.6.2 NVM

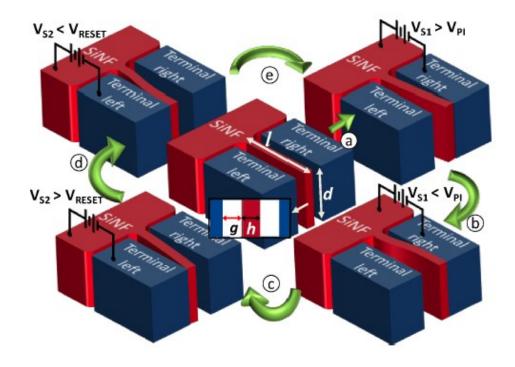

After switches are turned on, adhesion force appears between the movable structure and the fixed electrode. If the adhesion force is large enough to overcome the spring restoring force, then even without the help of the electrostatic force, the on state of the switch can be preserved without power supply. With proper design of writing and erasing function, N/MEMS switches can be applied in non-volatile memory.

Figure 1-17 Schematic of NVM operation. Adapted from [123]

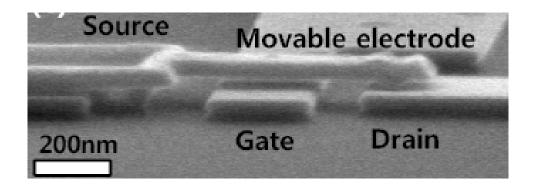

As shown in Figure 1-17, the silicon cantilever is actuated electrostatically to contact one of the two terminals when operation voltage is applied between the cantilever and either terminal [123-126]. After the cantilever is switched to one terminal, the bias voltage is turned off and the cantilever maintains its contact with this terminal due to adhesion between the surfaces of the silicon cantilever and electrode terminal. When the electrostatic potential is gradually

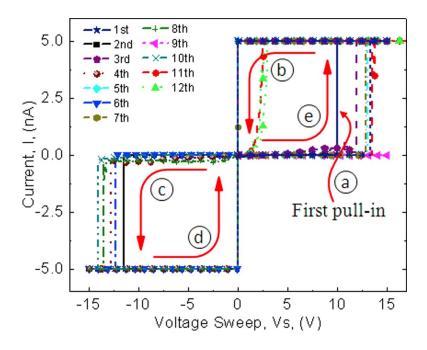

increased at the opposite terminal, the cantilever flips and switches towards the opposite lateral terminal. A silicon cantilever with dimension of 80 nm wide and 2  $\mu$ m long is demonstrated to maintain its geometrical position even after the bias voltage is turned off. Bi-stable hysteresis behavior by writing and erasing voltage as low as 8.4 and 10.1 V is measured.

In Figure 1-18, repeatable write and erase operation is demonstrated by electrical measurement. Unfortunately, the devices are proven to stop working after 12 cycles, possibly due to the melting of silicon cantilever on one of the fixed electrodes caused by the large amount of joule heating.

Figure 1-18 NVM I-V curve, adapted from [123].

### 1.6.3 Hybrid N/MEMS-CMOS Circuit

To fully utilize the zero leakage current properties of the N/MEMS switches and reduce the influence of their high mechanical delay, several

hybrid N/MEMS-CMOS circuits have been studied, such as power gating, FPGA and SRAM.

Switching off inactive CMOS logic circuit blocks by power gate is widely adopted to reduce power consumption. However, the leakage current of MOSFET power gates leads to the insufficient cutoff of the power supply. In contrast, N/MEMS switch based power gates are able to eliminate off-state leakage. Simple analysis and experimental demonstration have been made to predict the performance of MEMS switches over MOSFETs for power gates [20-23, 25, 127]. As shown in Figure 1-19, consider the off-period of CMOS logic circuit block is longer than 1 µs, N/MEMS based power gate shows significant advantages (up to 100 times less power consumption) over MOSFET power gating especially when the turn-on of the CMOS block is short.

Figure 1-19 Energy ratio (MOSFETs to N/MEMS switches) vs. off-period for various on-period, for designs power gated with 90 nm MOSFETs and N/MEMS switches. Adapter from [21].

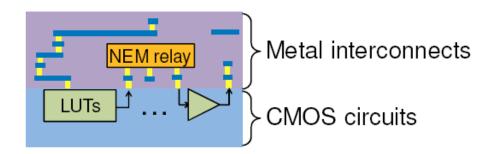

Similar principles can be applied to FPGA technology by replacing the routing switches in FPGA with N/MEMS switches as shown in Figure 1-20. Since FPGA programmable routing switches remain the same state after configuration, large mechanical delays of switches do not affect FPGA application performance. Moreover, N/MEMS switches with low on-state resistance value also contribute to improving the critical path delays in FPGA applications.

Figure 1-20 CMOS-NEMS FPGA using NEMS switches as routing Switches, adapted from [128].

Simulation results indicate that N/MEMS implemented FPGA can simultaneously achieve 10-fold leakage power reduction, 2-fold dynamic power reduction and 2-fold area reduction, without incurring any application speed penalty compared to a CMOS-only FPGA at the 22nm technology node as shown in Figure 1-21.

Figure 1-21 Power-speed trade-offs comparing CMOS-NEM FPGAs to a CMOS-only FPGA. (a) Dynamic power reduction vs. speed-up; (b) Leakage power reduction vs. speed-up, adapted from [128].

To achieve an increase in stability and decrease in leakage power dissipation, the pull-down MOSFETs in a conventional CMOS SRAM are replaced with N/MEMS switches (Figure 1-22). The zero leakage characteristic of NEMS switches results in a dramatic reduction in static power dissipation. The structure is designed so that the relatively long mechanical delay of the NEMS switches does not result in speed degradation. The read static noise margin is improved by 250%. In addition, by replacing the two transistors leaked most the current, MPD1 and MPD2, the static power dissipation decreases by 85%. The write delay decreases by 60%, and reading delay decreases by 10%.

Figure 1-22 Schematic of (a) a conventional CMOS SRAM cell and (b) a NEMS/CMOS hybrid SRAM cell with NEMS Switches replacing the pull-down MOSFETs, adapted from [29].

# 1.7 Thesis organization

This thesis summarizes the various works on N/MEMS switches that were undertaken during the course of my candidature. The contents of each chapter in the thesis are as follows:

Chapter 2 will discuss the design consideration of electrostatically actuated N/MEMS switches, including the pull-in effect, pull-in voltage and the concerns of selecting contact material. From the device structure aspect, different actuation direction and beam type are discussed. The scalability of the switch technology is explained by analyzing the key parameters with the dimension scaling-down.

Chapter 3 will present a dual-silicon-nanowires based U-shaped NEMS switch with low pull-in voltage. The device is fabricated using standard CMOS compatible processes. The switch consists of a capacitive paddle with dimension of 2  $\mu$ m by 4  $\mu$ m mechanically supported by two silicon nanowires, suspended on top of the substrate with a gap of 145 nm. The nanowires are 5  $\mu$ m long with cross-section of 90 nm by 90 nm. The average pull-in voltage is

about 1.12 V and the ratio of the on/off current is measured to be over 10000. According to the measurement results, this U-shape structure demonstrates great potential in lowering down the pull-in voltage.

Chapter 4 will provide an all metal based electrostatic NEMS switch fabricated using a one mask process. To enhance the reliability of NEMS switch and address a few issues with Si nanowire based devices, in chapter 4 and chapter 5, the main focus is to design a NEMS switch with CMOS compatible process, metal-to-metal contact, low contact resistance, good process yield and capability of harsh environment operation. The Damascene-like process is designed to ensure a clean, high aspect ratio, metal-to-metal mechanical contact. Molybdenum is used as the structural material. The devices show an abrupt switching behavior of 108 on/off ratio. High temperature cycling behavior is demonstrated in a vacuum chamber at 300 °C for more than 28 hours.

Chapter 5 will discuss the further optimization of all metal based NEMS switches. With reliable Damascene-like process, 800 devices with different dimensions have been measured with respect to the pull-in voltage and process yield. Dimensions with 100 % yield have been identified. General design rules of high yield dimension have also been proposed.

Finally, the main contributions of this thesis and suggestions for future works will be summarized in Chapter 6.

# Chapter 2 Design Consideration of

# N/MEMS Switches