# DEVELOPMENT OF NEMS RELAYS IN LOGIC COMPUTATION AND RUGGED ELECTRONICS

#### SOON BO WOON

(B.Eng.(Hons.), LJMU)

### A THESIS SUBMITTED

#### FOR THE DEGREE OF DOCTOR OF PHILOSOPHY DEPARTMENT OF ELECTRICAL & COMPUTER ENGINEERING NATIONAL UNIVERSITY OF SINGAPORE

2015

### DECLARATION

I hereby declare that this thesis is my original work and it has been written by me in its entirety. I have duly acknowledged all the sources of information which have been used in the thesis.

This thesis has also not been submitted for any degree in any university

previously.

SOON BO WOON

21 May 2015

#### ACKNOWLEDGEMENTS

There have been help, guidance and hospitality received in making this thesis possible. With that, I wish to express my sincere acknowledgement to the persons for making a difference in my doctorate degree study.

First and foremost, I would like to express my deepest gratitude to my advisor, Professor Lee Cheng Kuo, for his extraordinary guidance, knowledge sharing and selflessness understanding. The process would be detrimental and disastrous one without his enormous support. It is far more than meaningful and honour to have him as an advisor, as a chief and as a great mentor.

I want to thank my fellow MEMS group mates from The Department of Electrical and Computer Engineering, National University of Singapore (ECE, NUS), especially Qian You and Wang Nan. They worked with me hand-in-hand in countless labs and cleanroom sessions. It was my pleasure and I am glad that things work really well towards our goal.

My special thanks to Dr. Julius Tsai, Dr. Feng Han Hua, Dr. Pavel Neuzil, Dr. Julien Reboud, Dr. Wong Chee Chung, Dr. Kee Jack Sheng and Dr. Cheam Daw Don, who have been incredible friends, particularly Pavel, whom I deemed as the point-blank Dutch uncle. I felt blessed to have met them and extremely appreciative to their earnest advice. I want to extend my sincere thanks to Victor Leong, Eldwin Ng, Professor Thomas Kenny and the folks at Stanford National Nanofabrication Infrastructure Network (NNIN) for their great work and support. The Epi-Seal program had been a prominent pillar that contributed tremendously in this project.

I am very grateful to the staffs from Institute of Microelectronics (A\*STAR Singapore) especially Adrian, Dexian, Phyo, Jon, Fariz, Timothy, Jasmine, Lai Yin and Yong Wei. The cleanroom and labs seems to be a pale whitish cold place without the warmth of these helpful staff.

Thanks to my parents, Peter and Nyukyin, and in-laws, Jerry and Choonfah for being such a caring family and supportive. I am grateful to my siblings, Alan, Seong and Carmen, for seeing through things and taking good care of my parents during my work and study abroad. This thesis is dedicated to my wife, Veronica, for her unconditional support, love, kindness and time. I could not thank her enough for taking care of our lovely daughter, Haley, who is merely few months old by the time this thesis is completed.

## CONTENTS

| DECLARATIONI                                                    |

|-----------------------------------------------------------------|

| ACKNOWLEDGEMENTSII                                              |

| CONTENTS IV                                                     |

| SUMMARYX                                                        |

| LIST OF TABLES XIII                                             |

| LIST OF FIGURES XIV                                             |

| LIST OF SYMBOLS AND ABBREVIATIONSXXXI                           |

| CHAPTER 1: INTRODUCTION1                                        |

| 1.1 General introduction1                                       |

| 1.2 Background to the research                                  |

| 1.2.1 Semiconductor transistor limits in harsh environment7     |

| 1.2.2 Existing high temperature electronics devices             |

| 1.2.2.1 Silicon on insulator10                                  |

| 1.2.2.2 III-V material compound transistor and SiC technology10 |

| 1.3 State of the art N/MEMS switch                              |

| 1.3.1 Electrostatic N/MEMS switch15                             |

| 1.3.2 N/MEMS switches: Memory and logic devices                 |

| 1.3.3 N/MEMS switch: Material selection                         |

| 1.3                                                     | 3.3.1 Silicon Carbide                                                                                                                                                                                                                                                                                                                                     | 22                                                              |

|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| 1.3                                                     | 3.3.2 Metal and metal oxides                                                                                                                                                                                                                                                                                                                              | 23                                                              |

| 1.3                                                     | 3.3.3 Other materials                                                                                                                                                                                                                                                                                                                                     | 25                                                              |

| 1.4                                                     | Silicon as N/MEMS switch                                                                                                                                                                                                                                                                                                                                  | 27                                                              |

| 1.4.1                                                   | Nano-size dimension of Si based N/MEMS switch                                                                                                                                                                                                                                                                                                             | 27                                                              |

| 1.4.2                                                   | Si based N/MEMS non-volatile memory                                                                                                                                                                                                                                                                                                                       | 30                                                              |

| 1.4.3                                                   | Reliability in high temperature                                                                                                                                                                                                                                                                                                                           | 32                                                              |

| 1.4.4                                                   | Operation reliability in high acceleration                                                                                                                                                                                                                                                                                                                | 33                                                              |

| 1.4.5                                                   | Secondary pull-in phenomenon                                                                                                                                                                                                                                                                                                                              | 34                                                              |

| 1.5                                                     | Motivation and objective                                                                                                                                                                                                                                                                                                                                  | 37                                                              |

|                                                         |                                                                                                                                                                                                                                                                                                                                                           |                                                                 |

| 1.6                                                     | Organization of thesis                                                                                                                                                                                                                                                                                                                                    | 39                                                              |

| 1.6<br>CHAPTE                                           |                                                                                                                                                                                                                                                                                                                                                           |                                                                 |

| СНАРТИ                                                  |                                                                                                                                                                                                                                                                                                                                                           | N                                                               |

| CHAPTE<br>NANOFI                                        | ER 2: DESIGN AND FABRICATION OF A SILICON                                                                                                                                                                                                                                                                                                                 | N                                                               |

| CHAPTE<br>NANOFI                                        | ER 2: DESIGN AND FABRICATION OF A SILICON<br>N NON-VOLATILE MEMORY BASED ON VAN DEI                                                                                                                                                                                                                                                                       | N<br>R<br>43                                                    |

| CHAPTE<br>NANOFI<br>WAALS                               | ER 2: DESIGN AND FABRICATION OF A SILICON<br>N NON-VOLATILE MEMORY BASED ON VAN DEI<br>FORCE                                                                                                                                                                                                                                                              | N<br>R<br>43<br>43                                              |

| CHAPTE<br>NANOFI<br>WAALS<br>2.1                        | ER 2: DESIGN AND FABRICATION OF A SILICON<br>N NON-VOLATILE MEMORY BASED ON VAN DEI<br>FORCE                                                                                                                                                                                                                                                              | N<br>R<br>43<br>43<br>44                                        |

| CHAPTE<br>NANOFI<br>WAALS<br>2.1<br>2.2                 | ER 2: DESIGN AND FABRICATION OF A SILICON<br>N NON-VOLATILE MEMORY BASED ON VAN DEI<br>FORCE                                                                                                                                                                                                                                                              | <b>N</b><br><b>R</b><br><b>43</b><br>43<br>44<br>46             |

| CHAPTH<br>NANOFI<br>WAALS<br>2.1<br>2.2<br>2.3          | ER 2: DESIGN AND FABRICATION OF A SILICON<br>N NON-VOLATILE MEMORY BASED ON VAN DEI<br>FORCE                                                                                                                                                                                                                                                              | <b>R</b><br><b>43</b><br>43<br>44<br>46<br>46                   |

| CHAPTE<br>NANOFI<br>WAALS<br>2.1<br>2.2<br>2.3<br>2.3.1 | ER 2:       DESIGN AND FABRICATION OF A SILICON         N NON-VOLATILE MEMORY BASED ON VAN DEI         FORCE         Introduction         Operational NEMS switch with bi-stable states         Critical length and van der Waals force         Governing equations for beam's critical length         Finite element simulations and boundary conditions | <b>N</b><br><b>A</b><br><b>43</b><br>43<br>44<br>46<br>46<br>52 |

| 2.                                                                                                  | .4.1 La                                                                    | ayout view                                         | 55                                          |

|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|----------------------------------------------------|---------------------------------------------|

| 2.5                                                                                                 | Fabr                                                                       | ication process                                    | 57                                          |

| 2.                                                                                                  | .5.1 D                                                                     | etailed fabrication and critical steps             | 58                                          |

|                                                                                                     | 2.5.1.1                                                                    | Ultra high aspect ratio silicon nanofin definition | 60                                          |

|                                                                                                     | 2.5.1.2                                                                    | Gap definition                                     | 65                                          |

|                                                                                                     | 2.5.1.3                                                                    | Side terminal definition                           | 66                                          |

|                                                                                                     | 2.5.1.4                                                                    | Isolation and metallization                        | 68                                          |

|                                                                                                     | 2.5.1.5                                                                    | Device release                                     | 69                                          |

| 2.6                                                                                                 | Fabr                                                                       | ication outcome                                    | 70                                          |

| 2.7                                                                                                 | Conc                                                                       | clusion                                            | 71                                          |

|                                                                                                     |                                                                            |                                                    |                                             |

| CHAF                                                                                                | PTER 3                                                                     | : CHARACTERIZATION OF TWO TERM                     | IINAL                                       |

|                                                                                                     |                                                                            | CHARACTERIZATION OF TWO TERN                       |                                             |

|                                                                                                     | CON NA                                                                     |                                                    | 72                                          |

| SILIC                                                                                               | CON NA<br>Testi                                                            | NOFIN NON-VOLATILE MEMORY                          | <b>72</b>                                   |

| <b>SILIC</b><br>3.1                                                                                 | CON NA<br>Testi<br>Elect                                                   | NOFIN NON-VOLATILE MEMORY                          | <b>72</b><br>72<br>73                       |

| <ul><li>SILIC</li><li>3.1</li><li>3.2</li><li>3.3</li></ul>                                         | CON NA<br>Testi<br>Elect<br>Resu                                           | NOFIN NON-VOLATILE MEMORY                          | <b>72</b><br>72<br>73<br>74                 |

| <ul> <li>SILIC</li> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.</li> </ul>                        | CON NA<br>Testi<br>Elect<br>Resu<br>.3.1 I-                                | NOFIN NON-VOLATILE MEMORY                          | 72<br>72<br>73<br>74<br>-volatile           |

| <ul> <li>SILIC</li> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.</li> <li>m</li> </ul>             | CON NA<br>Testi<br>Elect<br>Resu<br>.3.1 I-'                               | NOFIN NON-VOLATILE MEMORY                          | 72<br>72<br>73<br>74<br>-volatile<br>74     |

| <ul> <li>SILIC</li> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.</li> <li>m</li> <li>3.</li> </ul> | CON NA<br>Testi<br>Elect<br>Resu<br>.3.1 I-`<br>nemory<br>.3.2 No          | NOFIN NON-VOLATILE MEMORY                          | 72<br>72<br>73<br>74<br>-volatile<br>74<br> |

| SILIC<br>3.1<br>3.2<br>3.3<br>3.<br>3.<br>3.<br>3.<br>3.                                            | CON NA<br>Testi<br>Elect<br>Resu<br>.3.1 I-<br>nemory<br>.3.2 No<br>.3.3 M | NOFIN NON-VOLATILE MEMORY                          | 72<br>72<br>73<br>74<br>-volatile<br>74<br> |

| 3.3.6 Reliability in high temperature and failure analysis                     |

|--------------------------------------------------------------------------------|

| 3.4 Non-volatile memory application                                            |

| 3.5 Conclusions                                                                |

| CHAPTER 4: DESIGN AND FABRICATION OF A VACUUM                                  |

| ENCAPSULATED SILICON TO SILICON CURVED BEAM LOGIC                              |

| SWITCH98                                                                       |

| 4.1 Introduction                                                               |

| 4.2 Wafer level vacuum encapsulation100                                        |

| 4.3 Robustness of a curved beam structure against secondary pull-in failure102 |

| 4.4 Curved beam stiffness and breakdown voltage tolerance103                   |

| 4.4.1 Governing equations for curved beam's stiffness                          |

| 4.4.2 Finite element simulations and boundary conditions                       |

| 4.4.3 Stopper design110                                                        |

| 4.4.4 Design of Experiment (DOE) parameter112                                  |

| 4.5 Design approach113                                                         |

| 4.5.1 Layout view113                                                           |

| 4.6 Fabrication Process114                                                     |

| 4.6.1 Detailed Fabrication and critical steps116                               |

| 4.7 Fabrication outcome118                                                     |

| 4.8 Conclusion                                                                 |

| CHAPTER 5: CHARACTERIZATION OF A VACUUM                            |

|--------------------------------------------------------------------|

| ENCAPSULATED SILICON TO SILICON CURVED BEAM LOGIC                  |

| SWITCH IN HARSH ENVIRONMENT                                        |

| 5.1 Testing set-up and procedure                                   |

| 5.2 Electrical and mechanical characterization                     |

| 5.3 Result and discussion                                          |

| 5.3.1 I-V characteristics of a three-terminal electrostatic switch |

| 5.3.2 Contact resistance                                           |

| 5.3.3 Curved beam structure robustness against secondary pull-in   |

| 5.3.4 Switching speed                                              |

| 5.3.5 Operation range from $-60$ °C to 400 °C145                   |

| 5.3.5.1 Pull-in voltage drift145                                   |

| 5.3.5.2 Contact resistance drift148                                |

| 5.3.6 Reliability of switch versus temperature                     |

| 5.3.6.1 At room temperature                                        |

| 5.3.6.2 At higher temperature up to 400 °C                         |

| 5.3.7 Reliability of curved beam switch under high acceleration    |

| 5.4 Conclusion167                                                  |

| CHAPTER 6: FAILURE MECHANISM AND ANALYSIS169                       |

| 6.1 Joule heating phenomenon at contact interface                  |

6.1.1 Failure in N/MEMS Si-to-Si switch......169

| 6.1.2   | Contact temperature                                   |     |

|---------|-------------------------------------------------------|-----|

| 6.1.3   | Failure mechanism                                     |     |

| 6.2     | Conclusion                                            |     |

| CHAPTI  | ER 7: CONCLUSIONS AND FUTURE WORK                     |     |

| 7.1     | Conclusions on current work                           |     |

| 7.2     | Recommendations for future work                       |     |

| 7.3     | Refractory metal as possible higher reliable material |     |

| 7.3.1   | Material selection                                    |     |

| 7.3.2   | A vacuum encapsulated Mo curved beam switch           |     |

| 7.3.3   | Fabrication process flow                              |     |

| 7.3.4   | Fabrication results                                   |     |

| 7.3.5   | Towards high density all mechanical logic computation |     |

| BIBLIO  | GRAPHY                                                | 194 |

| LIST OF | PUBLICATIONS                                          | 212 |

| APPENI  | DICES                                                 | 215 |

| A1. AN  | SYS CODE – Simulation of bi-stable hysteresis curve   |     |

| A2. AN  | SYS CODE – Temperature simulation of contact resistor |     |

#### SUMMARY

The physical limitation in silicon bandgap hinders the development of rugged electronics. In the case of harsh environment operation such as down-hole operation where ambient temperature can rise beyond 300 °C, the electronic peripherals are disrupted due to substantial surge in the off-state current. Meanwhile, technology such as silicon-on-insulator (SOI) device, silicon carbide (SiC) and III-V semiconductors are explored by others. But these platforms are usually temperature range limited and difficult to be fabricated. Therefore an all mechanical complementary-metal-oxide-semiconductor (CMOS) compatible architecture is attractive to be implemented in high temperature logic computation and rugged electronics.

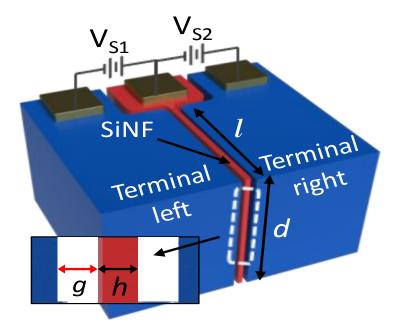

This thesis aims to explore and develop high temperature logic computation and rugged electronic leveraging on nano/microelectromechanical (N/MEMS) switches. First, a non-volatile memory (NVM) is demonstrated using an ultra-high aspect ratio two-terminal silicon nanofin (SiNF) switch. The SiNF switch is fabricated on a silicon-on-insulator (SOI) wafer with aspect ratio of 1:35 and minute size of 80 nm width (w) × 3.5 µm height (h) × 2 µm length (l). This nano-scale dimension is favourable for high density application. The two-terminal switch is designed to demonstrate non-volatile memory's hysteresis behaviour based on the novel idea of van der Waals (VDW) force latching mechanism. This bi-stable mechanism leveraging on surface adhesion demonstrated is the first of its kind in nano-scale switches. Set and reset operation can be configured by electrostatically actuating the SiNF between one of two terminals, with pull-in voltage ranging from 10 to 20 V. The off-state leakage current in hundreds of pA range while the on/off is in the order of  $10^2$ . Low voltage drift of -24mV/K is demonstrated from 50 °C to 150 °C with switching speed of approximately ~70ns.

Next, a logic switch that demonstrates logic computation function is designed and encapsulated in vacuum to enhance the lifetime in high temperature. This three-terminal micro switch relies on a curved beam (source) that actuates toward the contact terminal (drain) by charging the control terminal (gate). The curved beam design also increases the spring stiffness thus providing better reliability. Meanwhile, three independent terminals are designed to provide uninterrupted gate control and drain-source signals. The micro switch demonstrated high sub-threshold slope of 120  $\mu$ V/decade and pull-in voltage ranges from 15 to 25 V. In extreme temperature environment, operation range of the micro switch from -60 °C to 400 °C is verified and demonstrated, which yields a resistance drift of approximately -200  $\Omega$ /K. Meanwhile, lifetime of more than 10<sup>7</sup> cycles at room temperature and 10<sup>6</sup> cycles in high temperature of 400 °C are successfully verified. Subsequently, investigation using a shaker test from 1 g to 10 g is performed to show that the switch's operation is unaffected by high acceleration. Such study is important for application in high acceleration environment such as satellite deployment or rocket launch. Failure analysis of both devices are performed and further studied. The study of such Si-to-Si contact-based micro switches provides a crucial guideline and paves the path to the future of mechanical computing and failure mechanisms in harsh environment applications.

# LIST OF TABLES

| Table 1.1 Technologies available for HTE market [6, 79]                         |

|---------------------------------------------------------------------------------|

| Table 1.2 Summary of technology in high temperature electronics [27, 92, 134]15 |

| Table 1.3 Comparison of N/MEMS actuation mechanisms [135-153], [154-157]17      |

| Table 1.4 Comparison of lifetime and temperature study of different N/MEMS      |

| switches                                                                        |

| Table 2.1 SiNF parameters in design of experiment (DOE)                         |

| Table 3.1 Comparison of Switching speed between different NEMS switch           |

| Table 4.1 Curve beam parameters in design of experiment (DOE)    112            |

| Table 5.1 Parameter Settings for On-Off Cycle                                   |

| Table 6.1 Comparison of specification of different N/MEMS switches for high     |

| temperature environment                                                         |

| Table 7.1 Material Property of different candidate for switch [210]             |

# LIST OF FIGURES

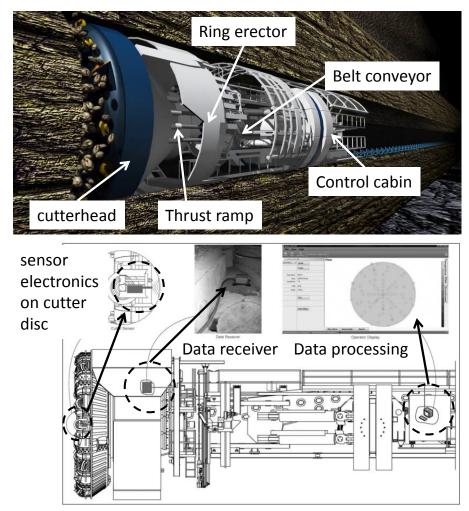

| Figure 1.1: Example of rugged electronics application: Tunnel boring machine's     |

|------------------------------------------------------------------------------------|

| (TBM) sensor network showing the position of different electrical modules [1, 2]2  |

| Figure 1.2: High temperature electronics requirement in different industry sector  |

| [6]6                                                                               |

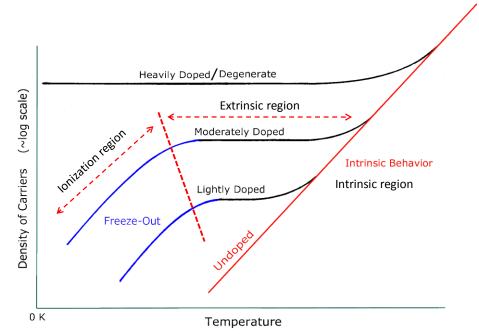

| Figure 1.3: Semiconductor carrier's density change with respect to temperature. At |

| high temperature, intrinsic carriers dominate and device's behaviour becomes       |

| unstable [79-81]                                                                   |

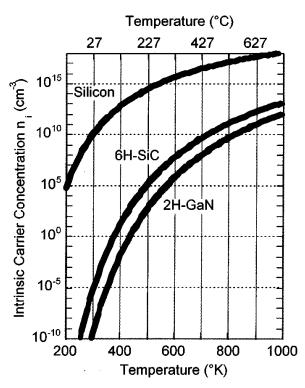

| Figure 1.4: Comparison of silicon, 6H-SiC, and 2H-GaN intrinsic carrier            |

| concentration $(n_i)$ versus temperature [79]11                                    |

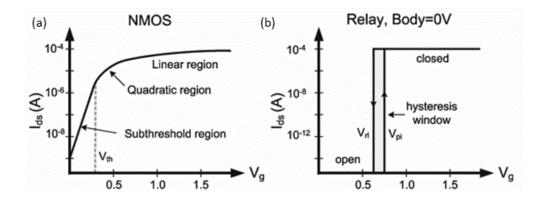

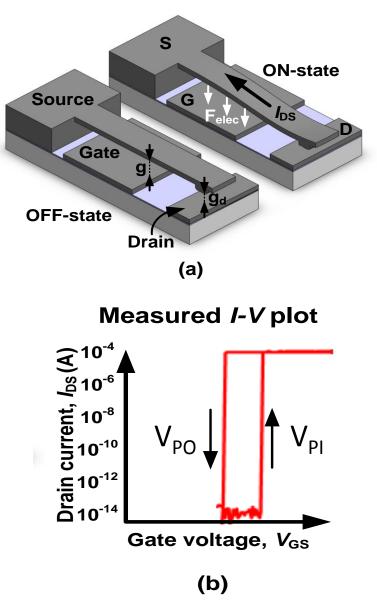

| Figure 1.5: (a) Switching characteristics of a NMOS with sub-threshold swing. (b)  |

| Steep sub-threshold rise and fall of a micro switch                                |

| Figure 1.6: Operation of electrostatic switches. (a) Operation of electrostatic    |

| switches in OFF and ON states. (b) Typical voltage sweeping curve of electrostatic |

| switches                                                                           |

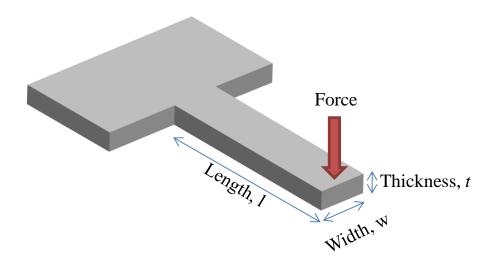

| Figure 1.7: Dimension parameter of a typical cantilever beam                       |

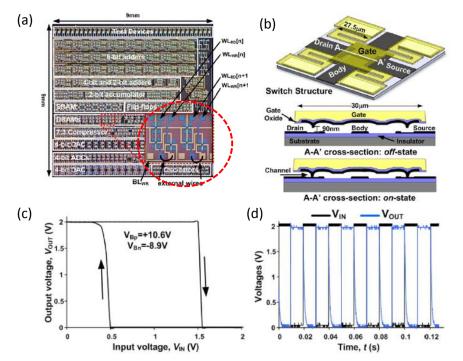

| Figure 1.8: (a) Die photo of the hybrid N/MEMS-CMOS chip. (b) layout and           |

| cross-section of the N/MEMS switch. (c) Voltage transfer characteristic showing    |

| hyper abrupt transitions between logic states. (d) Timing diagrams for 2-V, 50-Hz  |

| operation [41, 160]20                                                              |

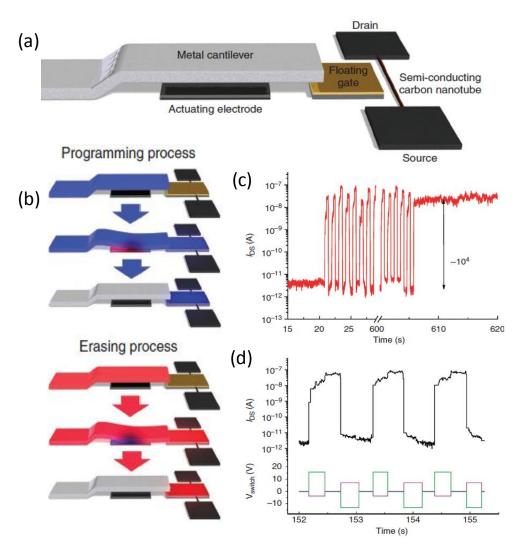

| Figure 1.9: (a) Schematic diagram of the MEMS-based non-volatile memory                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| device. The CNT is used for the source/drain channel and a MEM cantilever is                                                                                                                                                                                                                                                                                                                                                                                                           |

| added to transfer charges to the floating gate. (b) Diagrams demonstrating the                                                                                                                                                                                                                                                                                                                                                                                                         |

| programming (upper three panels)/erasing (lower three panels) processes. Blue/red                                                                                                                                                                                                                                                                                                                                                                                                      |

| colours indicate the polarities $\pm$ of the applied voltages. (c) Memory endurance                                                                                                                                                                                                                                                                                                                                                                                                    |

| operation under repeated programming/erasing cycles for the side-floating gate                                                                                                                                                                                                                                                                                                                                                                                                         |

| device. The test was performed over 500 cycles for $600 \text{ s}$ with Vds = 100 mV. (d)                                                                                                                                                                                                                                                                                                                                                                                              |

| Expanded section of (c) also showing the voltages applied to the cantilever (purple                                                                                                                                                                                                                                                                                                                                                                                                    |

| line) and activating electrode (green line) [41, 160]21                                                                                                                                                                                                                                                                                                                                                                                                                                |

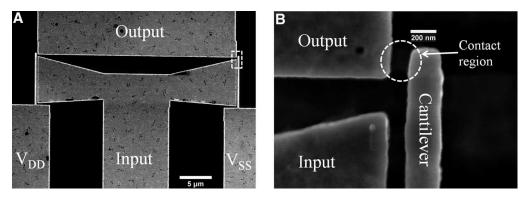

| Figure 1.10: (a) SEM of an inverter device. (b) zoom-in of the highlighted contact                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| [39]23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| [39]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

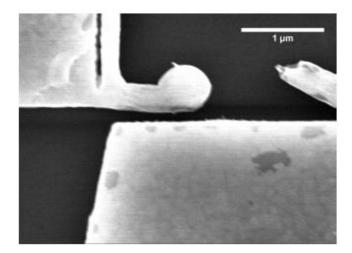

| Figure 1.11: Localized Joule heating resulting in melting of SiC [39]23                                                                                                                                                                                                                                                                                                                                                                                                                |

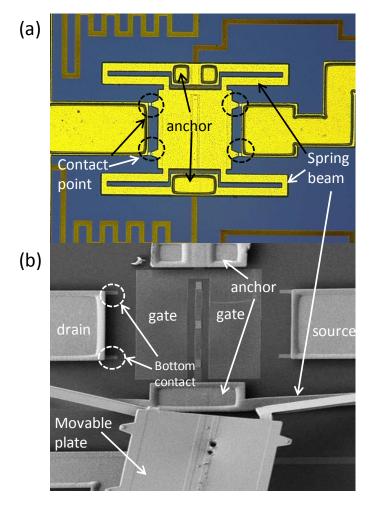

| Figure 1.11: Localized Joule heating resulting in melting of SiC [39]23<br>Figure 1.12: (a) SEM images showing actuation of a five terminal polysilicon                                                                                                                                                                                                                                                                                                                                |

| Figure 1.11: Localized Joule heating resulting in melting of SiC [39]23<br>Figure 1.12: (a) SEM images showing actuation of a five terminal polysilicon<br>switch coated with platinum on the sidewalls and selected top surfaces. (b) SEM                                                                                                                                                                                                                                             |

| Figure 1.11: Localized Joule heating resulting in melting of SiC [39]23<br>Figure 1.12: (a) SEM images showing actuation of a five terminal polysilicon<br>switch coated with platinum on the sidewalls and selected top surfaces. (b) SEM<br>cross section of unreleased platinum-coated beams [171]24                                                                                                                                                                                |

| Figure 1.11: Localized Joule heating resulting in melting of SiC [39]23<br>Figure 1.12: (a) SEM images showing actuation of a five terminal polysilicon<br>switch coated with platinum on the sidewalls and selected top surfaces. (b) SEM<br>cross section of unreleased platinum-coated beams [171]24<br>Figure 1.13: (a) Optical micrograph showing the switch design. Four folded springs                                                                                          |

| Figure 1.11: Localized Joule heating resulting in melting of SiC [39]23<br>Figure 1.12: (a) SEM images showing actuation of a five terminal polysilicon<br>switch coated with platinum on the sidewalls and selected top surfaces. (b) SEM<br>cross section of unreleased platinum-coated beams [171]24<br>Figure 1.13: (a) Optical micrograph showing the switch design. Four folded springs<br>are attached to an anchor point on the wafer, and the opposite sides are connected to |

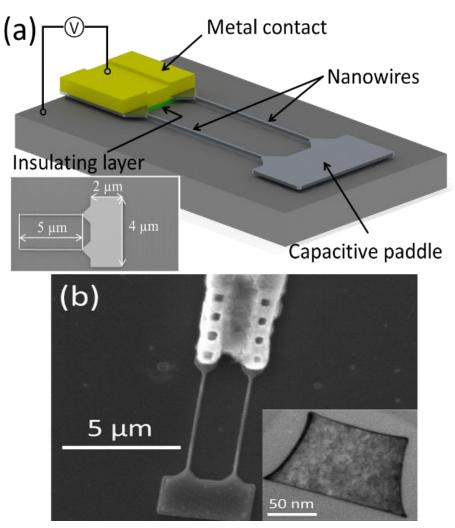

| Figure 1.11: Localized Joule heating resulting in melting of SiC [39]                                                                                                                                                                                                                                                                                                                                                                                                                  |

| photo of a U-shape NEMS switch after HF vapor releasing, Inset: TEM image of a                        |

|-------------------------------------------------------------------------------------------------------|

| SiNW cross-section [133]                                                                              |

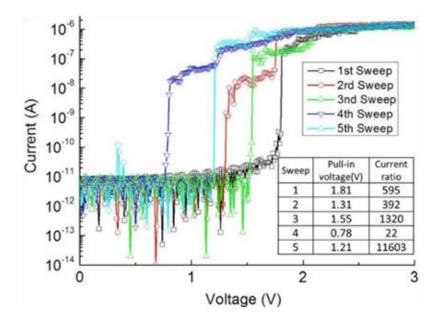

| Figure 1.15: I-V characteristic of the device. For the first five switching cycles, the               |

| current ratio indicates the change in current that occurs within 10 mV of the pull-in                 |

| voltage                                                                                               |

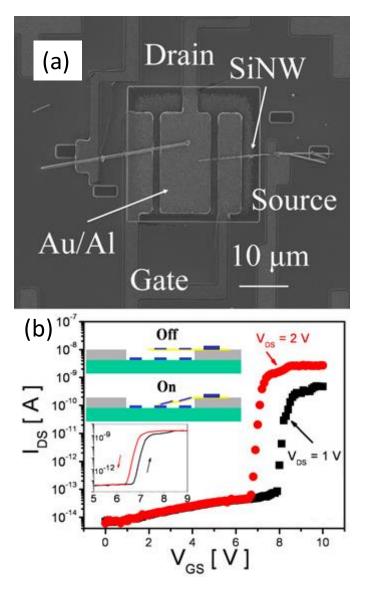

| Figure 1.16: (a) SEM image of two 3T switch; (b) The typical switching current-                       |

| voltage characteristics of the 3T switch. The inset shows the switch on/off diagram                   |

| and the hysteresis of $I_{DS}$ - $V_{GS}$ as the gate voltage is swept from $V_{GS} = 0$ to 9.0 V and |

| then back to 0 V at $V_{DS} = 2.0$ V [81]                                                             |

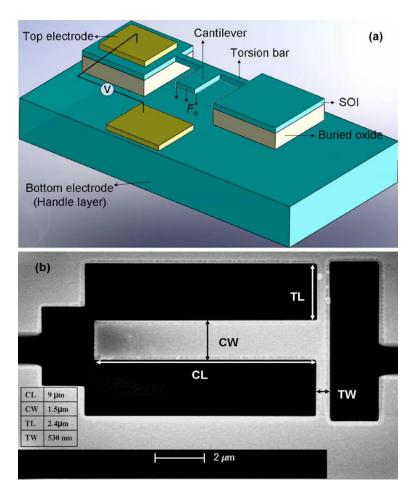

| Figure 1.17: A schematic illustration of the NEMS torsion switch device. (b) SEM                      |

| photo of a NEMS torsion switch after HF vapour releasing. The dimension: CL,                          |

| CW, TL, and TW of device are 9 $\mu m,$ 1.5 $\mu m,$ 2.4 $\mu m,$ and 530 nm respectively             |

| [18]                                                                                                  |

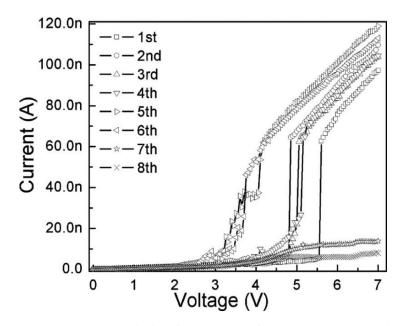

| Figure 1.18: I-V characteristic of the device for multiple operations [18]                            |

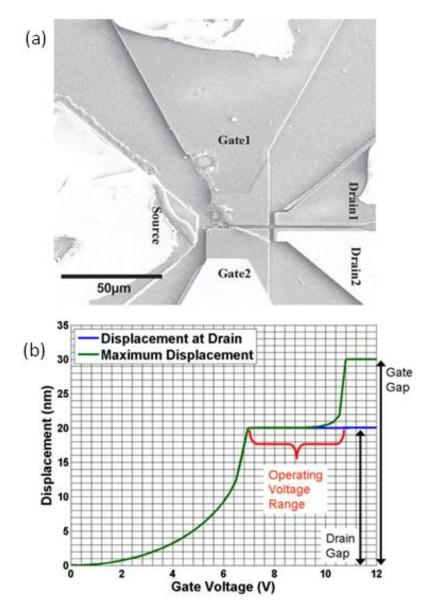

| Figure 1.19: (a) SEM image of a five-terminal switch after electrostatic actuation.                   |

| High current flow between the beam and the gate after shorting causes irreversible                    |

| damage. (b) Plot of the displacement of the source at the gate and the maximum                        |

| displacement of the source as a function of gate voltage for a N/MEMS switch. The                     |

| source pulls in to the drain at approximately 7 V. As the voltage is increased, the                   |

| source Shorts to the gate at approximately 11 V. The difference between these two                     |

| voltages is the operating voltage [189]                                                               |

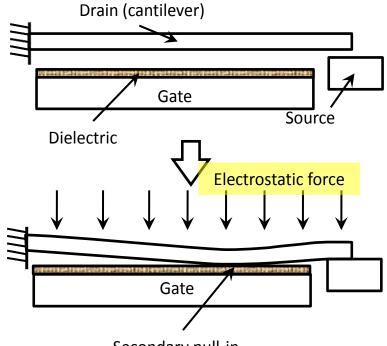

| Figure 1.20: Illustration of secondary pull-in for free-end cantilever beam,              |

|-------------------------------------------------------------------------------------------|

| double-clamped beam                                                                       |

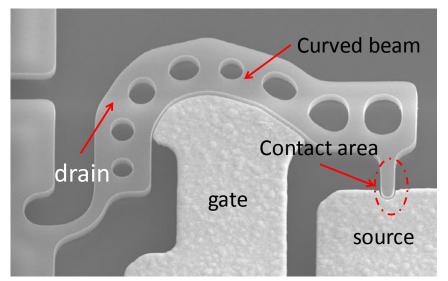

| Figure 1.21: SEM image of the curved beam switch showing three terminals: drain,          |

| gate and source. The contact area is depicted by dashed line [194]                        |

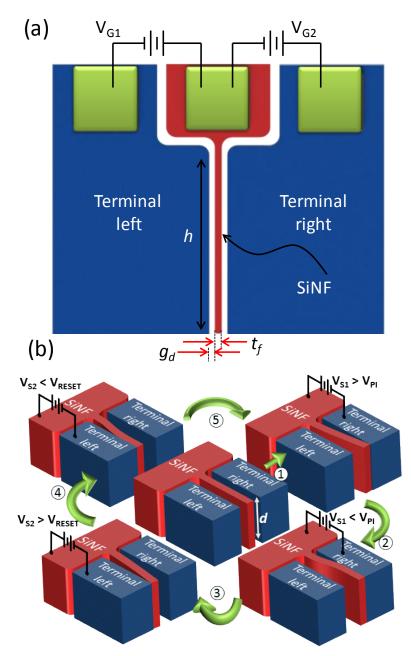

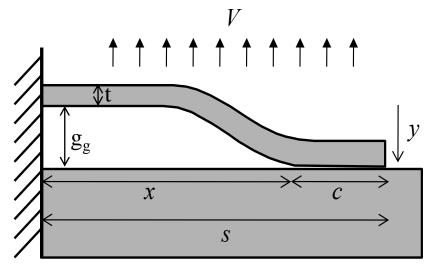

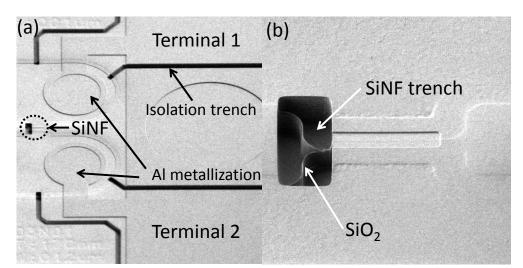

| Figure 2.1: (a) Top view schematic of the NEMS memory with SiNF as the actuator           |

| that can switch between two terminals (b) Structure and operation of a bi-stable          |

| NEMS switch. (1) SiNF is pulled-in to the right terminal by $V_{SI}$ . (2) VDW force      |

| holds the SiNF in contact position even after the electrostatic force is removed (3)      |

| As bias is applied opposite, SiNF flips towards the other terminal. (4) VDW force         |

| holds the switch in left terminal. (5) The switch cycles between two terminals,           |

| resulting in bi-stable state device45                                                     |

| Figure 2.2: Side view of cantilever structure stick to bottom substrate with              |

| dimensional parameters                                                                    |

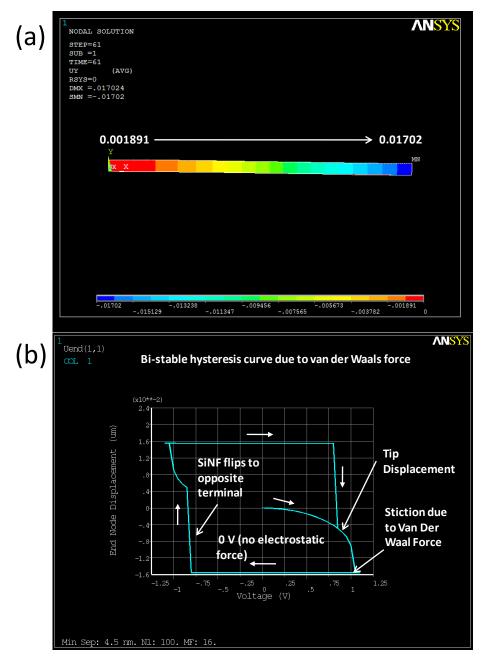

| Figure 2.3: (a) FEM simulation model of a SiNF in ANSYS with displacement (in             |

| $\mu$ MKS) denoted. (b) The result of simulation for a successful non-volatile hysteresis |

| curve due to van der Waals force. As the voltage sweep from starting from 0 V, tip        |

| displacement of the SiNF is simulated. Pull-in is detected after that and the stiction    |

| due to van der Waals force is consider as a load that holds the SiNF tip in closed        |

| contact position. The contact remains closed as voltage sweep return to zero. The         |

| same phenomenon repeats on the other side of the switch terminal, forming a               |

| non-volatile hysteresis curve                                                             |

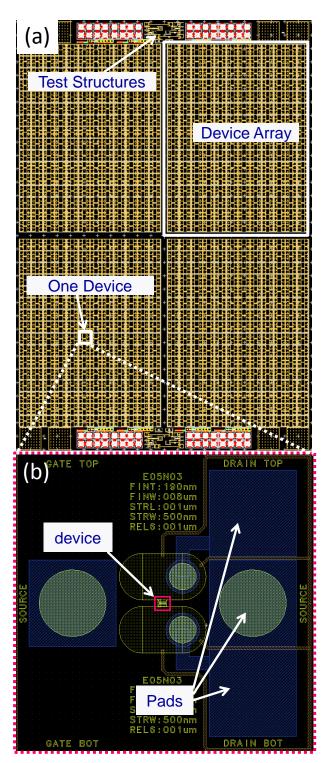

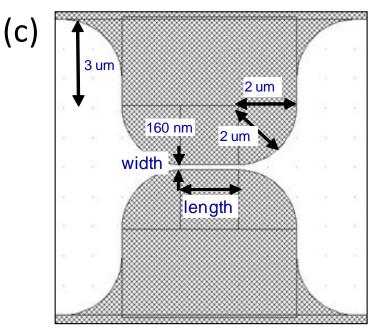

| Figure 2.4: (a) Reticle $(25 \times 35 \text{ mm})$ top layout. (b) Single device cell layout with |

|----------------------------------------------------------------------------------------------------|

| top metallization pads                                                                             |

| Figure 2.5: Zoom-in view of the SiNF with specific dimensions                                      |

| Figure 2.6: A 3D schematic of the NEMS memory with SiNF as the actuator that                       |

| switches between the terminals. The entire structure is made from Si except the                    |

| metallization using Al                                                                             |

| Figure 2.7: CMOS front end of the line (FEOL) process flow for SiNF switch a.)                     |

| SOI wafer – 3.5 $\mu$ m device layer, 1 $\mu$ m BOX. b.) 3.5 $\mu$ m Si DRIE. c.) Dry oxidation.   |

| d.) 5 µm poly-Si deposition and planarization till flat. e.) Al metallization. f.)                 |

| Device release in VHF60                                                                            |

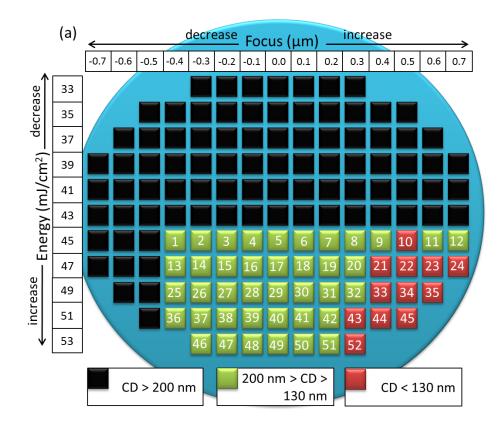

| Figure 2.8: (a) Wafer exposure map and measurement location of the available die                   |

| area. (b) FEM result of SiNF exposure optimization. Bossung's plot shows                           |

| optimized window of target SiNF's CD62                                                             |

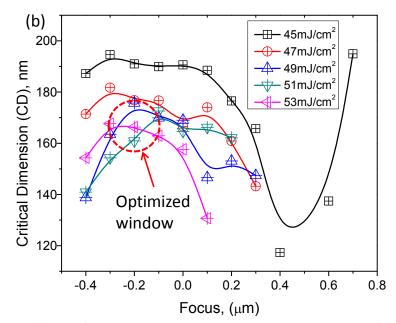

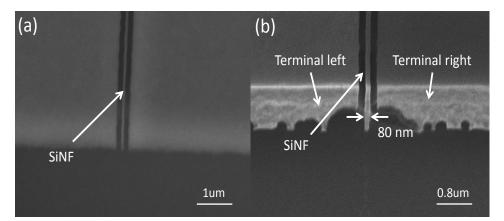

| Figure 2.9: (a) Overall SiNF definition with DRIE. (b) Zoom-in of one SiNF with                    |

| open end with very straight sidewall. (c) Sideview of SiNF shows etched surface                    |

| profile                                                                                            |

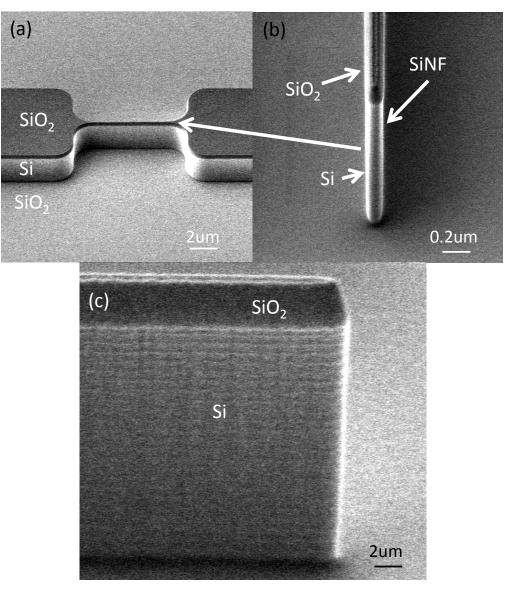

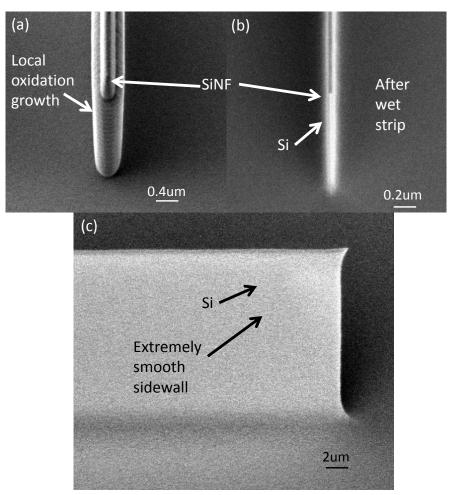

| Figure 2.10: (a) Local oxidation (wet) of SiNF to reduce surface roughness and                     |

| overall SiNF width. (b) SiNF width of 80 nm after removing surface oxide. (c)                      |

| Side view of SiNF shows extremely smooth sidewall                                                  |

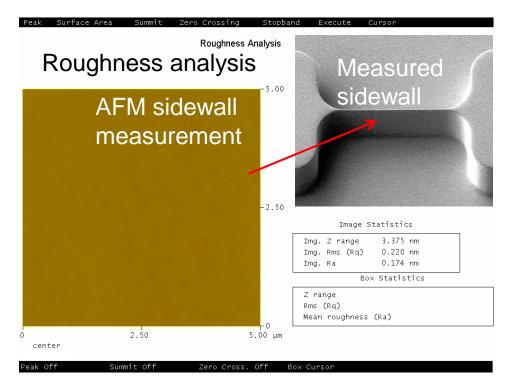

| Figure 2.11: AFM result of sidewall of SiNF                                                        |

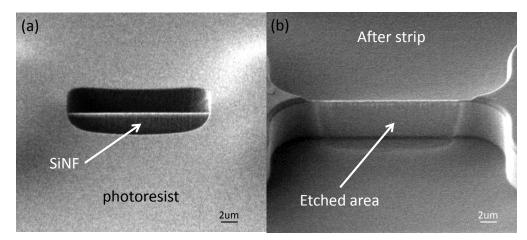

| Figure 2.12: (a) Photoresist opening of the SiNF area for gap definition. (b) $SiO_2$              |

| sacrificial reduction etches using HF acids around the SiNF actuation area to create      |

|-------------------------------------------------------------------------------------------|

| 80nm gap                                                                                  |

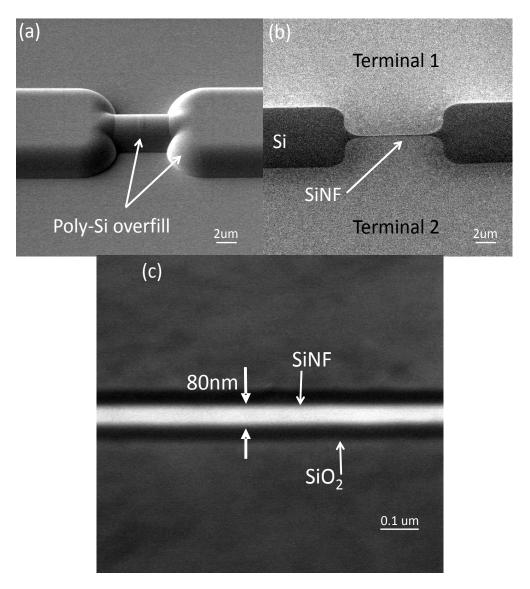

| Figure 2.13: (a) Thick poly silicon deposition overfilling all trenches and forming       |

| side terminal of the SiNF. (b) After CMP, SiNF is exposed and the terminals are           |

| self-aligned to side. (c) Zoom-in of the SiNF67                                           |

| Figure 2.14: (a) Isolation trench stop on buried oxide layer (BOX) to isolate the         |

| SiNF and the gate-electrodes. (b) SiNF is etched to become a cantilever, $\text{SiO}_2$   |

| sidewall remains due to higher selectivity                                                |

| Figure 2.15 (a) Top view of the released SiNF. (b) Tilted view of the SiNF with 80        |

| nm width69                                                                                |

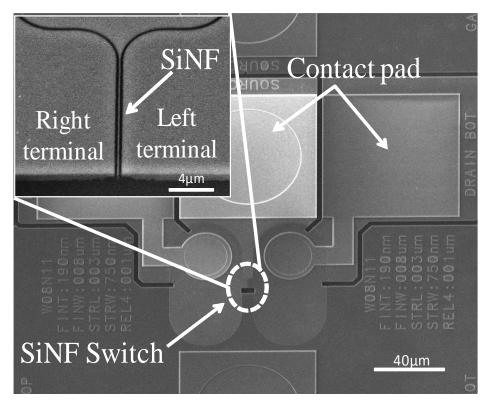

| Figure 2.16: SEM of a switch device of 8 $\mu m$ length $\times$ 90nm thick SiNF. (Inset) |

| Zoom in view of the SiNF in the centre of the device70                                    |

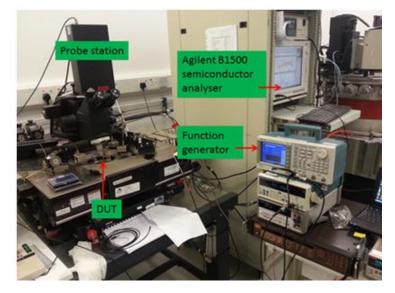

| Figure 3.1: Testing set-up of the SiNF electrical characterization. Probe station with    |

| microchamber (Cascade RBL-6100) equipped with semiconductor analyser (Agilent             |

| B1500) and function generator (Tektronix AFG 3102)72                                      |

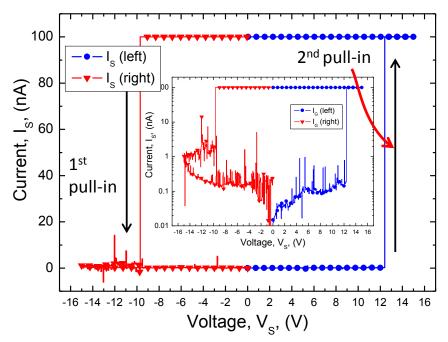

| Figure 3.2: Measured hysteresis curve of a 2 $\mu$ m long fin showing two pull-in         |

| voltage (-10 V and 12 V) of a SiNF device. (Inset) log scale curve. 0V point omitted      |

| for illustration purpose. The on/off ratio of the SiNF is approximately 2~3 orders of     |

| magnitude75                                                                               |

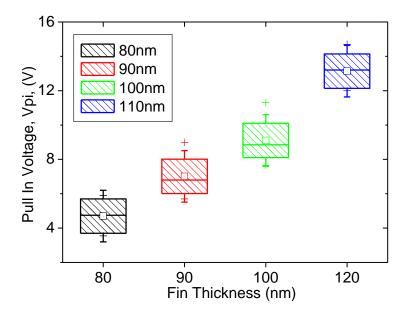

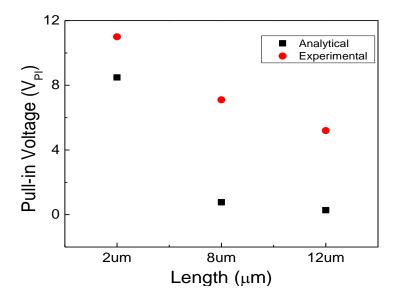

| Figure 3.3: Pull-in voltage, $V_{PI}$ versus different thickness of switch of 80 – 120 nm |

| (measured). Constant error bar for twenty switching devices and median of each            |

| thickness are measured. Pull-in voltage, $V_{Pl}$ increases with the thickness of SiNF76                     |

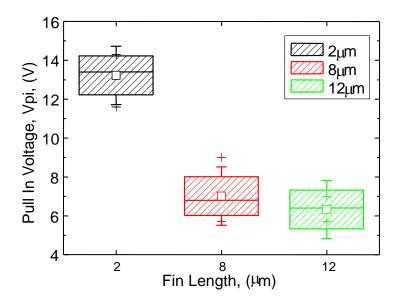

|--------------------------------------------------------------------------------------------------------------|

| Figure 3.4: Pull-in voltage, $V_{Pl}$ versus different switching length of 2µm, 8µm and                      |

| 12µm. Constant error bar for twenty switching devices and median of each length                              |

| are measured. Pull-in voltage, $V_{PI}$ reduces with the length of SiNF                                      |

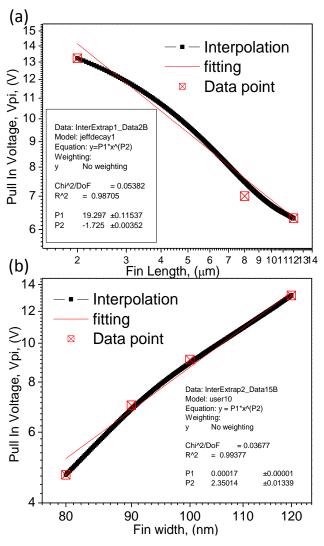

| Figure 3.5: (a) Pull-in voltage line fitting with respect to SiNF length on a log-log                        |

| scale. (b) ) Pull-in voltage line fitting with respect to SiNF width on a log-log scale.77                   |

| Figure 3.6: Comparison of pull-in voltage for analytical model and experimental                              |

| value. Mean value is taken from experimental value. Overall the experimental value                           |

| is higher than then analytical value, where the analytical model is a standard parallel                      |

| capacitor model79                                                                                            |

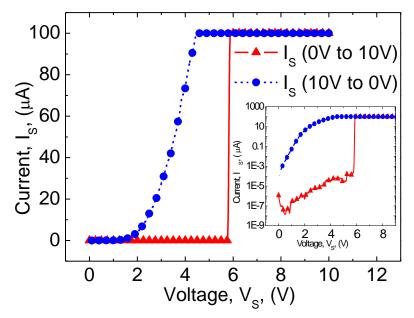

| Figure 3.7: Measured $I_s - V_s$ curve of an 8 µm length SiNF device. The current                            |

| compliance of the measurement is limited up to 100 $\mu$ A. From 0V to 10V, measured                         |

| $V_{PI}$ is 5.95 V at 25m V/decade. The measured $I_{ON}/I_{OFF}$ is 10 <sup>5</sup> . From 10 V to 0 V, the |

| pull out is not abrupt but shows charging relation                                                           |

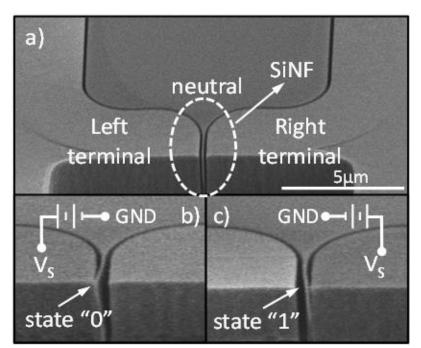

| Figure 3.8: SEM diagram showing a 2 $\mu m$ length $\times$ 80 nm width SiNF in operation.                   |

| (a) SiNF remains at neutral position. (b) SiNF contact remains on hold to the left                           |

| terminal, depicting state "0". (c) SiNF flips to the right terminal and on hold to the                       |

| right terminal, depicting state "1"                                                                          |

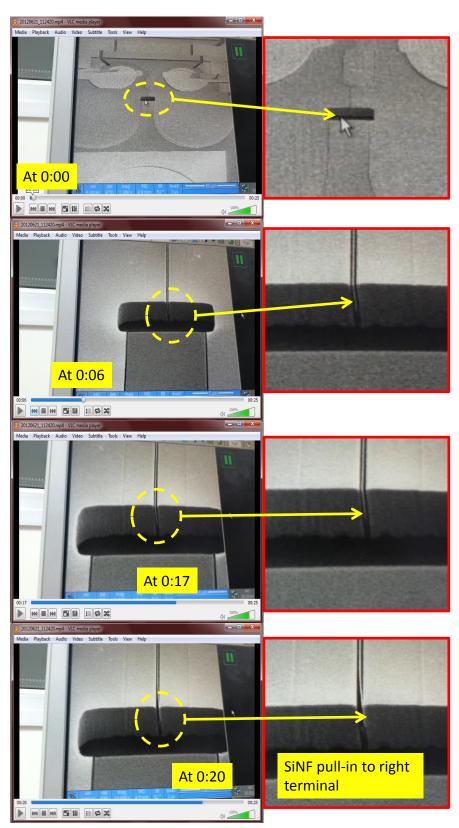

| Figure 3.9: Live video of the SiNF switching in real time, captured under SEM. The                           |

| SiNF switch is activated and makes contact with the right terminal during operation.83                       |

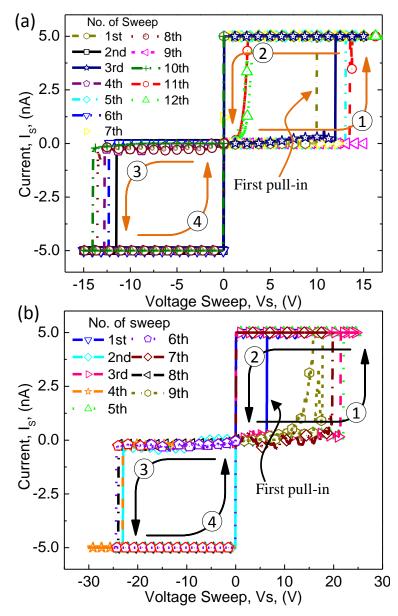

| Figure 3.10: Measured bi-stable I-V Characteristic of the NEMS memory. (a) 2 $\mu$ m                         |

| SiNF device (b) 8 $\mu$ m SiNF device. The bi-stable operation is shown in a following            |

|---------------------------------------------------------------------------------------------------|

| sequence. (1) First the SiNF is pulled in to the left terminal. (2) Left terminal                 |

| contact holding by the VDW. (3) SiNF flips to the right terminal. (4) Right terminal              |

| contact holding by the VDW. Note that the current in continuous when voltage                      |

| sweep returns to 0V                                                                               |

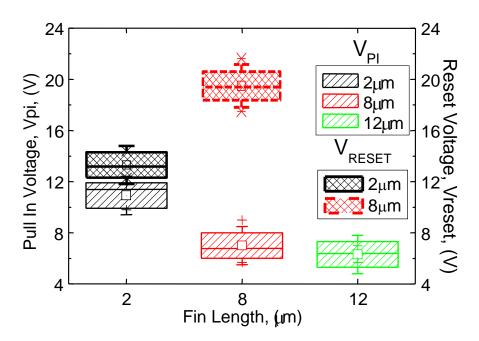

| Figure 3.11: Constant error bar of $V_{PI}$ and $V_{RESET}$ versus 2, 8, and 12 µm long SiNF      |

| of twenty devices. $V_{PI}$ reduced while $V_{RESET}$ increases sharply, while device with fin    |

| length of 12 $\mu$ m cannot be reset due to permanent adhesion                                    |

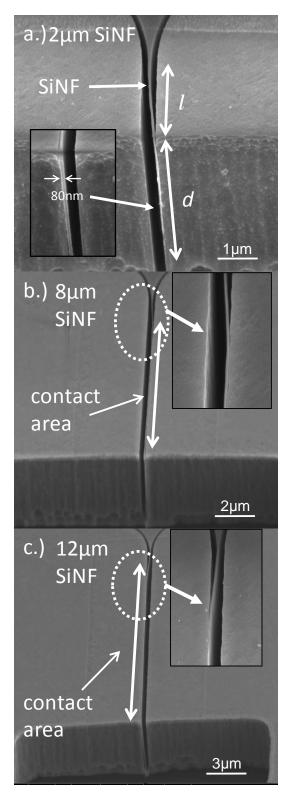

| Figure 3.12: SEM images of SiNF. (a) 2 $\mu m$ SiNF. Inset: Zoom-in of contact                    |

| between SiNF and terminal. (b,c) 8,12 $\mu m$ SiNF device. Insets: Zoom in view of                |

| SiNF bending and in contact with either terminal                                                  |

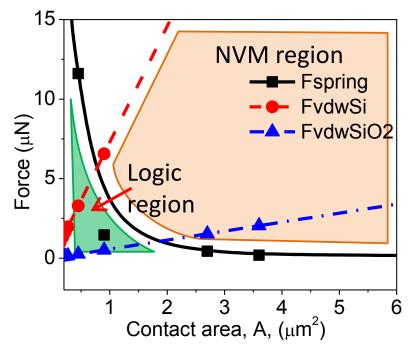

| Figure 3.13: Force of spring and van der Waals of silicon beam and contact surfaces               |

| of Si and SiO <sub>2</sub> versus measured contact area of SiNF. Non-volatile memory region is    |

| defined as the van der Waals force is larger than the spring restoration force of the             |

| SiNF. The logic region is vice versa90                                                            |

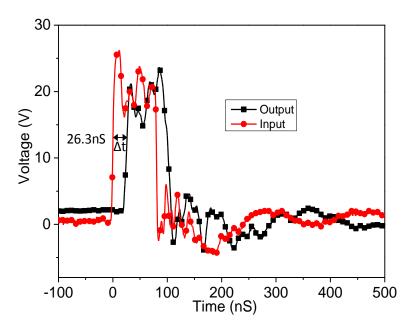

| Figure 3.14: Switching speed of an 80 nm $\times$ 2 $\mu m$ SiNF. The time difference, $\Delta t$ |

| given by the delay is measured to be 26.3 ns                                                      |

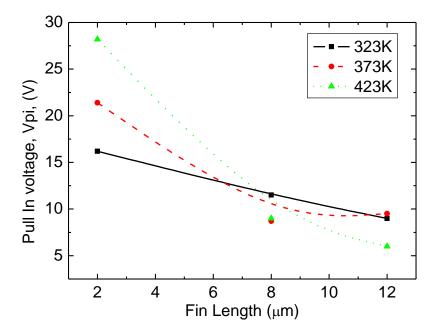

| Figure 3.15: $V_{PI}$ at temperature of 50 °C, 100 °C and 150 °C of 2 µm long switch of           |

| thickness 90 nm. Low voltage drift of 24mV/K is measured                                          |

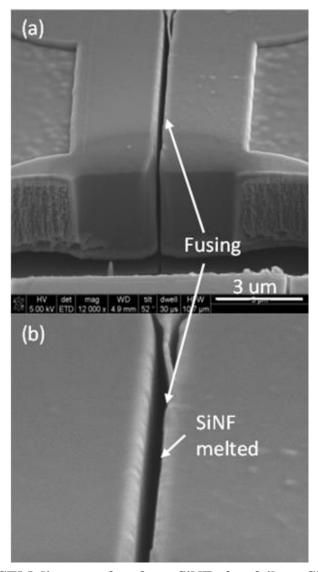

| Figure 3.16: SEM diagram of an 8 $\mu$ m SiNF after failure. SiNF is melted and fused             |

| to the actuating terminal                                                                         |

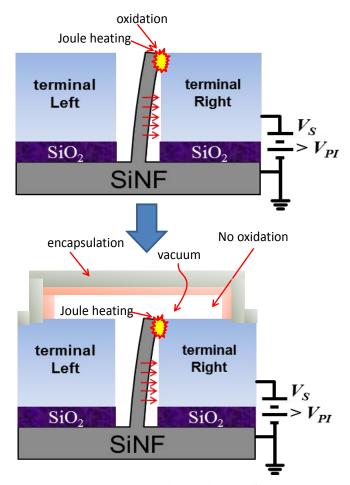

| Figure: 3.17 Vacuum encapsulation of the SiNF switch can prevent oxidation of the           |

|---------------------------------------------------------------------------------------------|

| contact interface. Meanwhile, Joule heating needs to be reduced to enhance the              |

| lifetime of the device                                                                      |

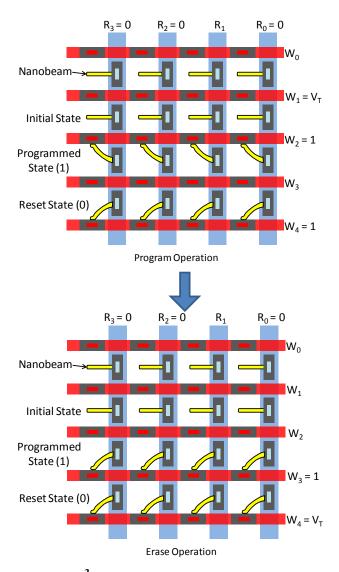

| Figure 3.18: Proposed $2^3$ bit memory array implemented by two-terminal SiNF               |

| switch. Each device consists of two states, namely Reset State '0' and                      |

| Programmed State '1'. Write and reset operation can be executed by turning on both          |

| read and write line. Meanwhile, read operation is performed by low current                  |

| measurement where device are subjected to a read potential ( $V_{read} < V_{PI}$ )          |

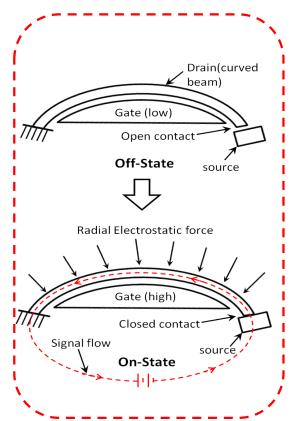

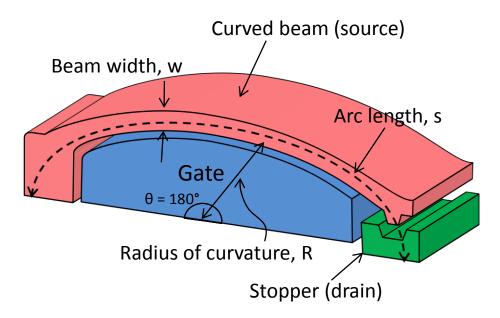

| Figure 4.1: Illustration of radial electrostatic force exerted on the curved beam when      |

| gate potential is changed from high to low. (Condition for pull-in: $V_{GATE} \ge V_{PI}$ ) |

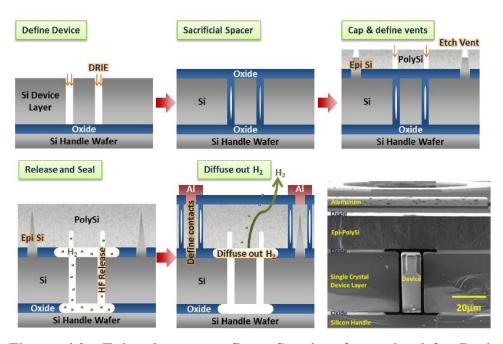

| Figure 4.2: Epi-seal process flow. Starting from the left: Device definition,               |

| sacrificial and spacer deposition, cap and release hole patterning, poly-silicon            |

| sealing and interconnect redistribution [184]101                                            |

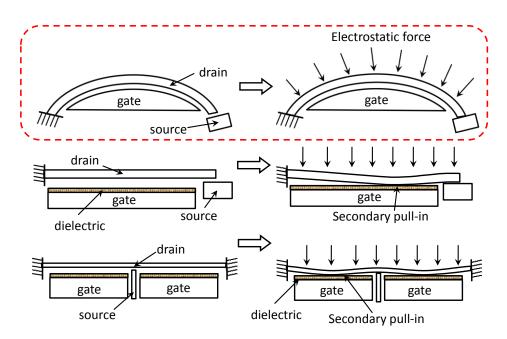

| Figure 4.3: Illustration of secondary pull-in comparison between electrostatic switch       |

| for curve beam, free-end cantilever beam, double-clamped beam. The curved beam              |

| structure offers robust gate voltage overdrive and prevention from secondary pull-in        |

| due to the enhanced mechanical strength after pull-in happens                               |

| Figure 4.4: Cross-section layout of the semi-circular curved beam electrostatic             |

| switch design107                                                                            |

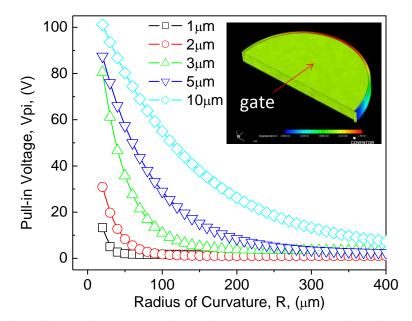

| Figure 4.5: Simulation result of pull-in voltage versus radius of curvature for curved      |

| beam with varying widths. Inset: 3D model of curved switch (Displacement: $0$ -             |

| 0.86 μm)                                                                                           |

|----------------------------------------------------------------------------------------------------|

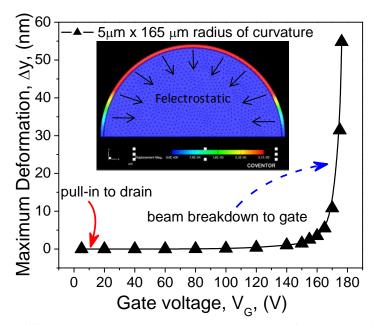

| Figure 4.6: Simulated high breakdown voltage of 174 V with initial pull-in and                     |

| contacted drain at approximately 11 V. Inset: Pull-in of drain to gate during                      |

| breakdown. (Displacement: $0 - 3.1 \times 10^{-3} \mu\text{m}$ )                                   |

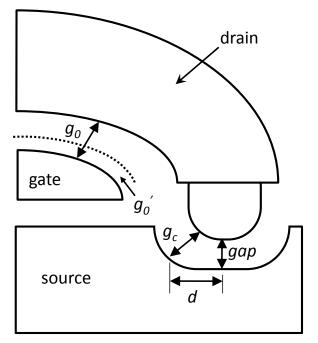

| Figure 4.7: Contact dimple stopper and contact distance requirement for curved                     |

| beam switch112                                                                                     |

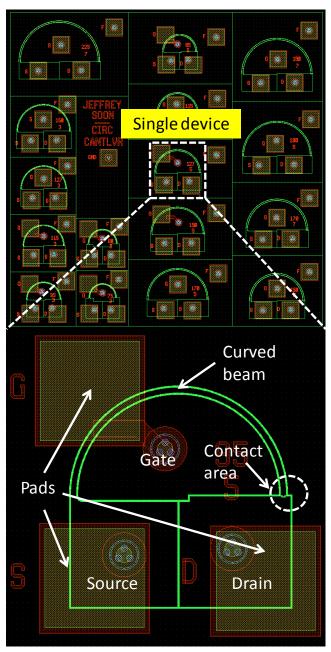

| Figure 4.8: Layout view of one $3 \times 3 \text{ mm}^2$ die. A single device cell is shown at the |

| bottom. One device comprised of a curved beam, gate and drain                                      |

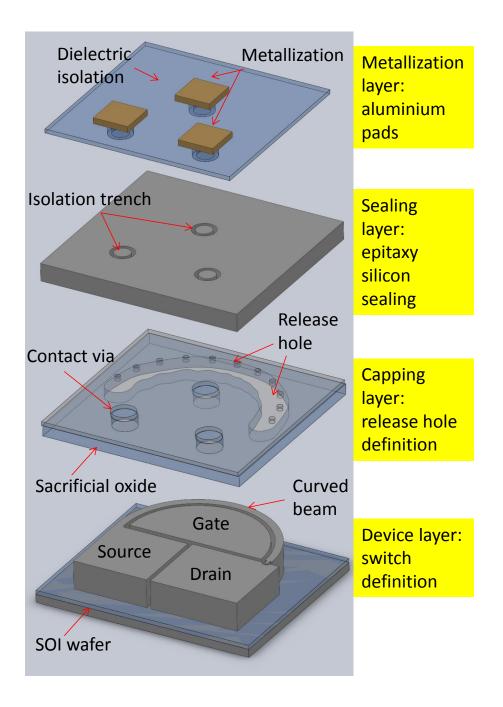

| Figure 4.9: Exploded view of the Si-to-Si MEMS switch with encapsulation layers                    |

| consist of device layer, capping layer, sealing layer and metallization layer with                 |

| different function                                                                                 |

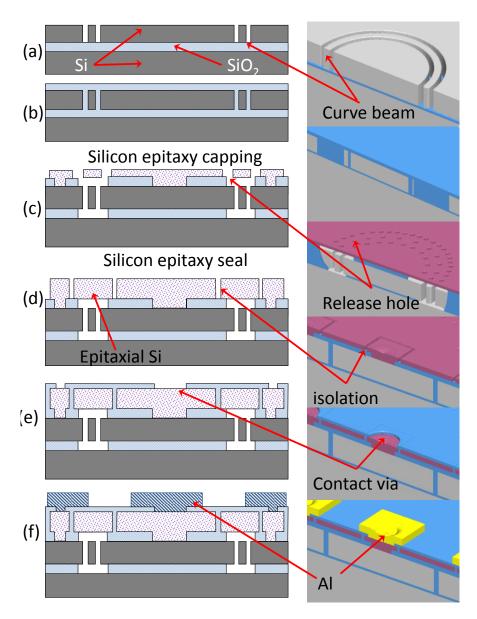

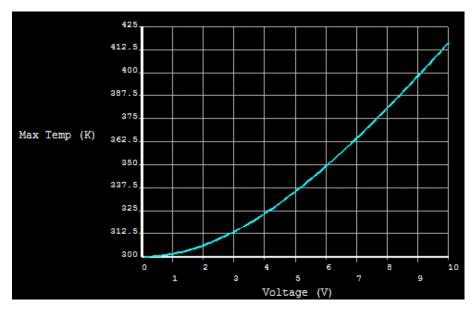

| Figure 4.10: Fabrication process flow of encapsulated curve switch. (a) Si deep                    |

| trench etching. (b) $SiO_2$ overfills to seal trench. (c) Via definition with device               |

| release. (d) Si epitaxy sealing and electrode isolation. (e) Passivation opening. (f) Al           |

| metallization117                                                                                   |

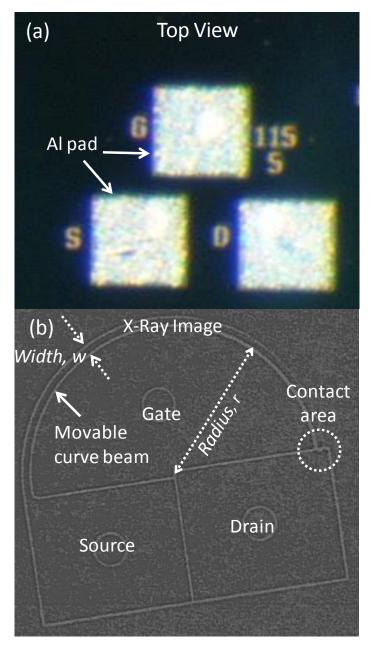

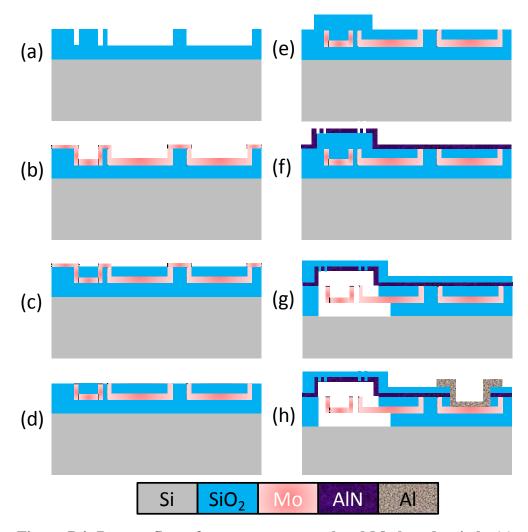

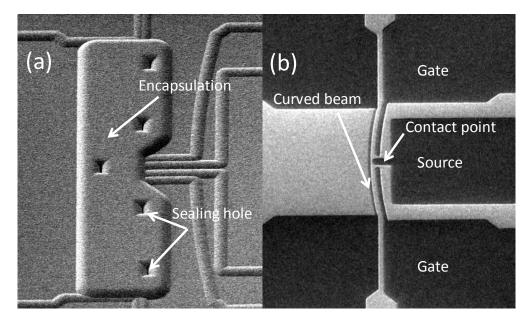

| Figure 4.11: (a) Top view of the finished chip with metalized aluminium pad. (b.)                  |

| X-Ray image showing the encapsulated three-terminal switch comprised of a                          |

| movable curve beam (Source), control terminal (Gate) and contact terminal (Drain).119              |

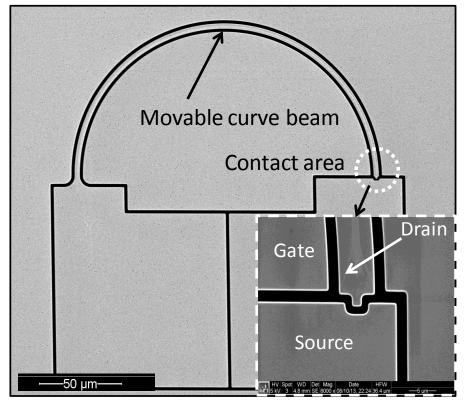

| Figure 4.12: SEM image of a 3 $\mu m$ $\times$ 85 $\mu m$ radius curved switch before              |

| encapsulation is performed. The image is captured after the DRIE process. (Inset)                  |

| Zoom-in of the contact region                                                                      |

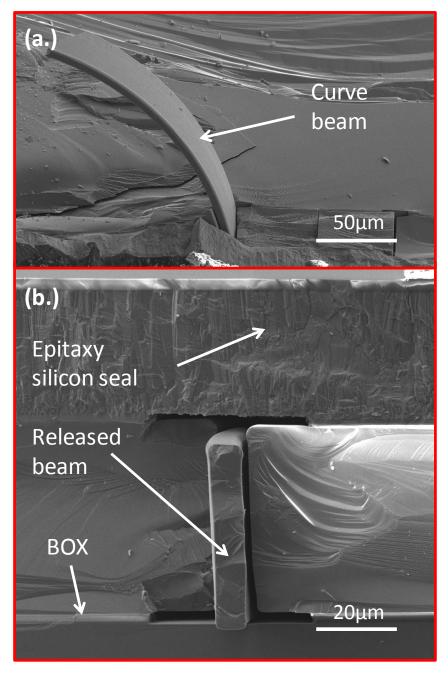

| Figure 4.13: SEM cross-section of a curved switch device showing the released                                                                                                                                                                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| curved beam with a poly-silicon encapsulation seal. (a.) Encapsulated curved beam.                                                                                                                                                                                                         |

| (b.) Epi-Seal process with encapsulated beam                                                                                                                                                                                                                                               |

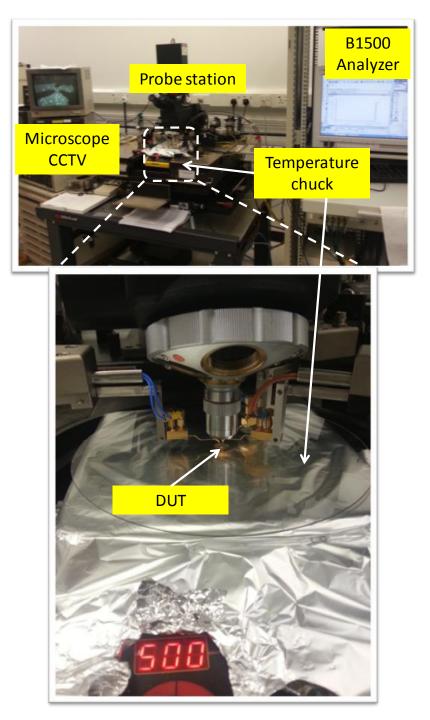

| Figure 5.1: Testing set up of the vacuum encapsulated curved beam switch. The set                                                                                                                                                                                                          |

| up includes a probe station (Cascade RBL-6100) equipped with CCTV, a                                                                                                                                                                                                                       |

| semiconductor analyser (Agilent B1500), the probe station stage modified with a                                                                                                                                                                                                            |

| hot plate (Thermo Scientific HP131225Q Cimarec). The Zoom-in image shows the                                                                                                                                                                                                               |

| DUT placed under hot plate with temperature setting 500 °C                                                                                                                                                                                                                                 |

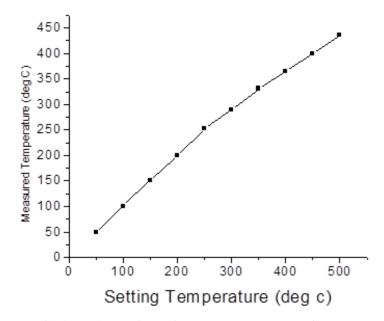

| Figure 5.2: Calibration of surface temperature of the curved beam switch. The                                                                                                                                                                                                              |

| measured temperature is regulated to its setting temperature for more accurate                                                                                                                                                                                                             |

| 100                                                                                                                                                                                                                                                                                        |

| temperature setting purpose                                                                                                                                                                                                                                                                |

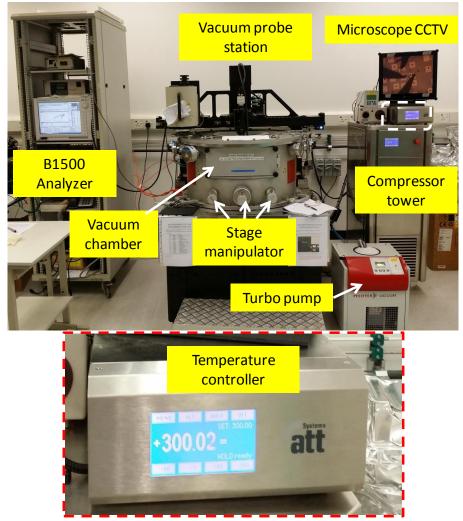

| Figure 5.3: Vacuum probe station (Cascade Microtech vacuum probe station,                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                            |

| Figure 5.3: Vacuum probe station (Cascade Microtech vacuum probe station,                                                                                                                                                                                                                  |

| Figure 5.3: Vacuum probe station (Cascade Microtech vacuum probe station, PMV200) equipped with an 8" wafer vacuum test chamber, turbo pump and a                                                                                                                                          |

| Figure 5.3: Vacuum probe station (Cascade Microtech vacuum probe station, PMV200) equipped with an 8" wafer vacuum test chamber, turbo pump and a compressor tower for cooling. Bottom image shows the detail of the temperature                                                           |

| Figure 5.3: Vacuum probe station (Cascade Microtech vacuum probe station, PMV200) equipped with an 8" wafer vacuum test chamber, turbo pump and a compressor tower for cooling. Bottom image shows the detail of the temperature controller that can be set from -60 °C to 300 °C          |

| Figure 5.3: Vacuum probe station (Cascade Microtech vacuum probe station,<br>PMV200) equipped with an 8" wafer vacuum test chamber, turbo pump and a<br>compressor tower for cooling. Bottom image shows the detail of the temperature<br>controller that can be set from -60 °C to 300 °C |

| Figure 5.3: Vacuum probe station (Cascade Microtech vacuum probe station,<br>PMV200) equipped with an 8" wafer vacuum test chamber, turbo pump and a<br>compressor tower for cooling. Bottom image shows the detail of the temperature<br>controller that can be set from -60 °C to 300 °C |

| Figure 5.3: Vacuum probe station (Cascade Microtech vacuum probe station,<br>PMV200) equipped with an 8" wafer vacuum test chamber, turbo pump and a<br>compressor tower for cooling. Bottom image shows the detail of the temperature<br>controller that can be set from -60 °C to 300 °C |

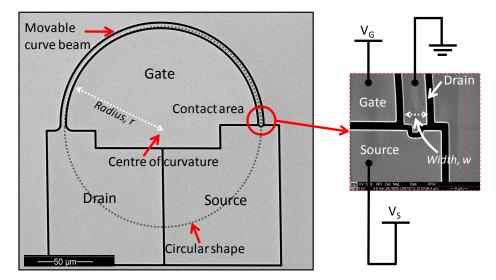

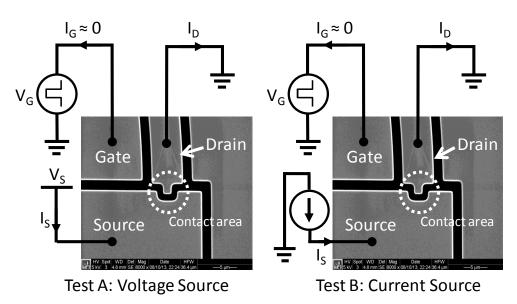

| actuation with gate terminal and $V_s$ is used to detect signal from source to drain.                  |

|--------------------------------------------------------------------------------------------------------|

| Parameter radius, r and width, w of beam is shown                                                      |

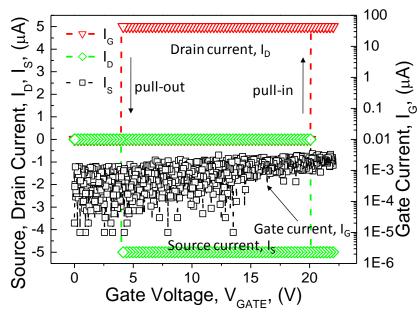

| Figure 5.6: Three terminal testing of $I_D$ , $I_S$ , $I_G - V_G$ . Pull-in and pull-out of the curved |

| beam is shown by the near ideal abrupt on-off characteristics at 20 V and 3.8 V                        |

| respectively. Low noise and power is demonstrate by the low gate current $(I_G)$ at pA                 |

| range at all time during entire sweep                                                                  |

| Figure 5.7: Cycling test set-up for Si-to-Si reliability test. Test A based on voltage                 |

| source $(V_S)$ and current measurement $(I_S)$ while Test B based on current source $(I_S)$            |

| and voltage measurement $(V_S)$                                                                        |

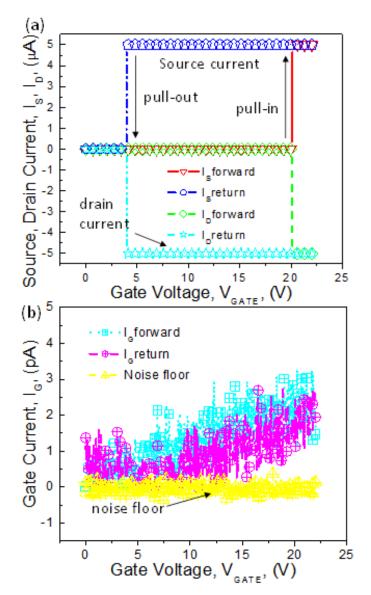

| Figure 5.8: Three-terminal testing of $I_D$ , $I_S$ , $I_G - V_G$ . (a) Switch turns on during         |

| forward $V_G$ sweep and turns off during return $V_G$ sweep. (b) $I_G$ remains low with                |

| measured noise floor of the semiconductor analyzer                                                     |

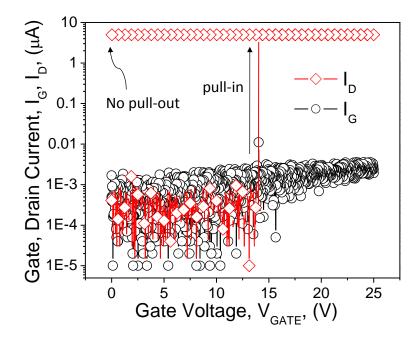

| Figure 5.9: $I_D$ , $I_G - V_G$ of 5 µm wide × 165 µm radius curved beam. Permanent                    |

| non-resettable contact is obtained as $V_G$ sweeps returns to zero, indicating switch                  |

| remains in contact136                                                                                  |

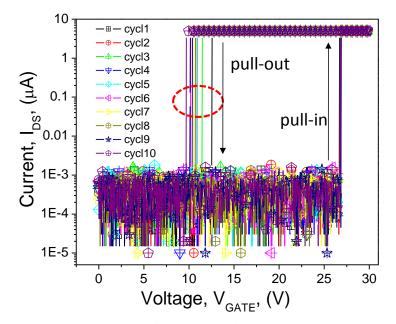

| Figure 5.10: Measurement of ten sweeping cycles. $I_{DS}$ - $V_G$ sweeping cycles within               |

| same device. Pull-out variation is highlighted137                                                      |

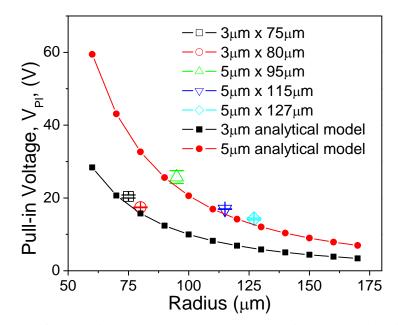

| Figure 5.11: Comparison between measured pull-in voltages $(V_{PI})$ of 3, 5 µm                        |

| (width) curved beam with various radius versus analytical model. Absolute error 1 –                    |

| 3 V measured from 15 devices of the same dimension                                                     |

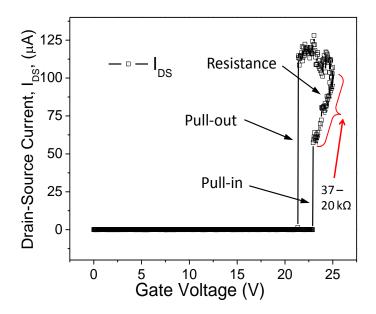

| Figure 5.12: Pull-in and pull-out characteristics of a 5 $\mu m \times 95 \ \mu m$ curved beam         |

| switch showing a contact resistance measurement without current compliance 140                     |

|----------------------------------------------------------------------------------------------------|

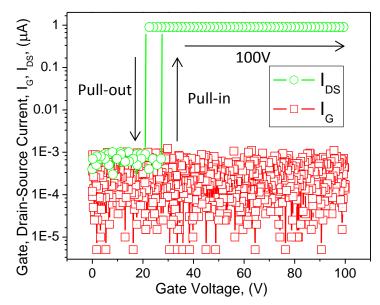

| Figure 5.13: Pull-in and pull-out characteristics of a 5 $\mu m$ $\times$ 95 $\mu m$ device with   |

| voltage over drive from 0 to 100V. Gate current $(I_G)$ remain low at pA level during              |

| the sweep141                                                                                       |

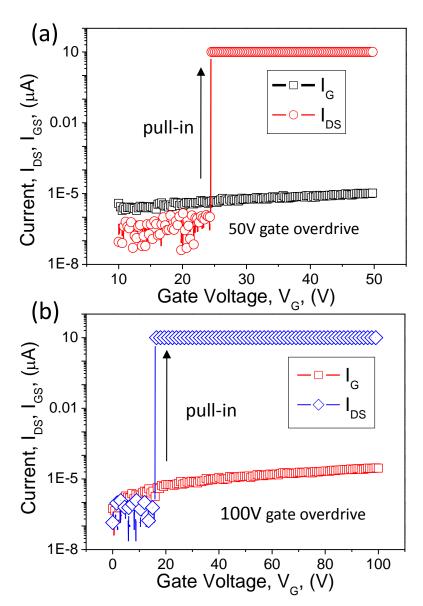

| Figure 5.14: High voltage breakdown endurance. (a) $V_{Pl}$ at 24.5 V of 5 $\mu$ m × 95 $\mu$ m    |

| radius beam, $V_G$ until 50 V (b) $V_{PI}$ at 15.5 V of 5 $\mu$ m × 115 $\mu$ m radius beam, $V_G$ |

| until 100 V                                                                                        |

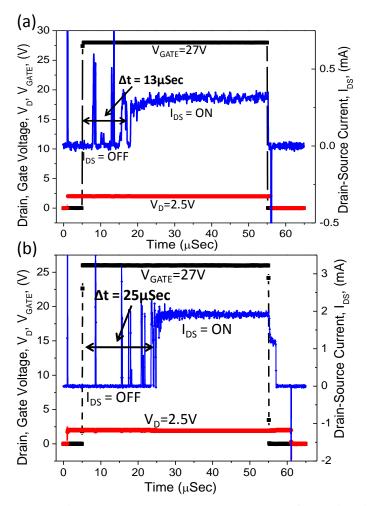

| Figure 5.15: Ultra high speed pulse I-V measurement for switching delay. (a) 5 $\mu$ m             |

| $\times75~\mu m$ radius switch (b) 5 $\mu m \times 95~\mu m$ radius switch144                      |

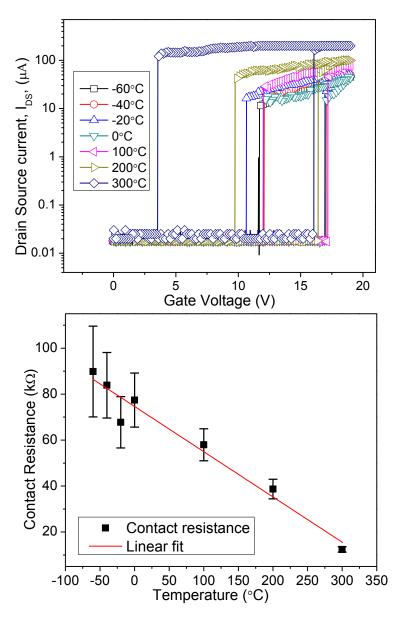

| Figure 5.16: I-V measurement of a 5 $\mu m \times 150 \ \mu m$ radius curved beam switch. (a)      |

| Pull-in and pull-out characteristics from room temperature to 400 °C. (b) Linear fit               |

| of the extracted pull-in voltage yields a $V_{PI}$ drift of 1.04mV/K                               |

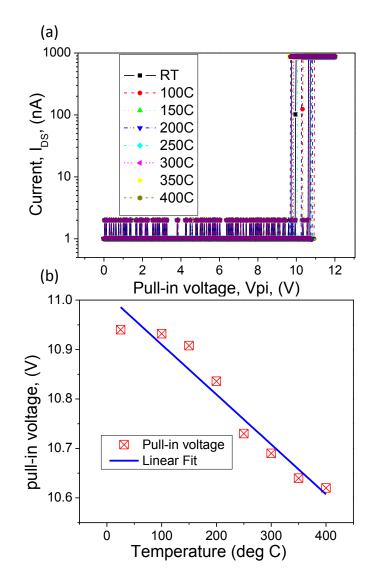

| Figure 5.17: I-V measurement of a 5 $\mu m \times$ 95 $\mu m$ radius curved beam switch. (a)       |

| Pull-in and pull-out characteristics from room temperature to 400 °C. (b) Linear fit               |

| of the extracted pull-in voltage yields a $V_{PI}$ drift of 1.36mV/K                               |

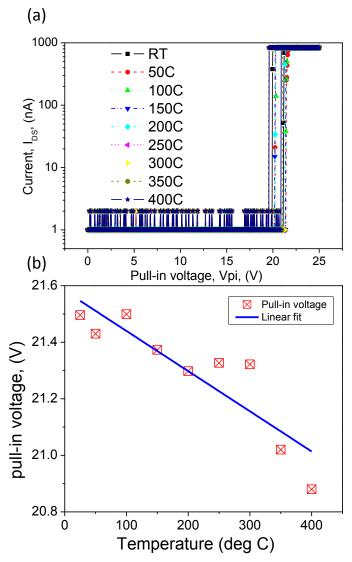

| Figure 5.18: Contact resistance of a 5 $\times$ 127 $\mu m$ curved beam from -60 °C to 300         |

| °C. (a.) Multiple pull-in $I_{DS}$ - $V_G$ at different temperatures. (b.) Extracted contact       |

| resistance drift (35 measurements) of -196Ω/K150                                                   |

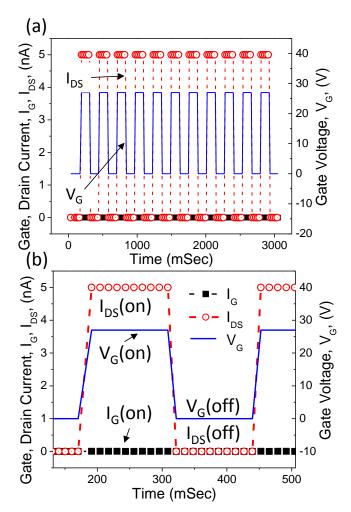

| Figure 5.19: Real time measurement set-up for on-off cycling test up to $10^5$ cycles              |

| under ambient condition of 5 $\mu m$ $\times$ 95 $\mu m$ radius beam. (a) Real time                |

| measurement of multiple cycles. (b) zoom-in of one cycle                                           |

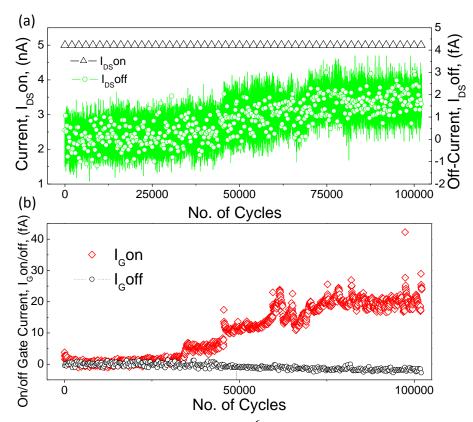

| Figure 5.20: I-V characteristics for $10^6$ cycles under ambient condition. (a) On-off            |

|---------------------------------------------------------------------------------------------------|

| drain source current $(I_{DS})$ with respect to every cycle. (b) On-off gate current $(I_G)$      |

| with respect to every cycle                                                                       |

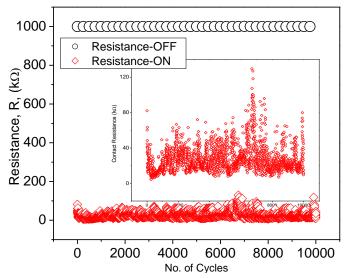

| Figure 5.21: Contact resistance versus no. of cycles under 300 °C elevated                        |

| temperature. (Inset) Zoom in on the contact resistance during on cycle156                         |

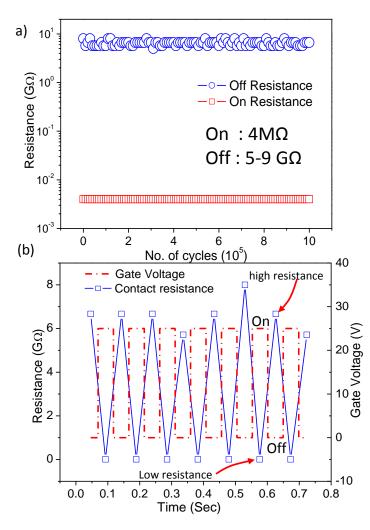

| Figure 5.22: (a) One million cycles at 400 °C verified with $I_{DS}$ current limited to 0.5       |

| $\mu A$ in log scale. (b) Zoomed-in of device showing seven repeated on-off cycle with            |

| respect to gate voltage                                                                           |

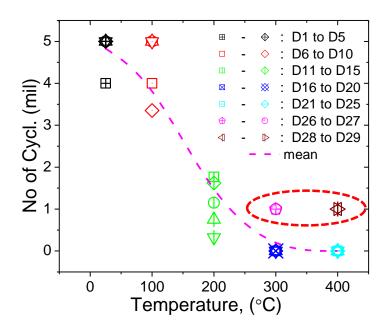

| Figure 5.23: Reliability statistics of twenty-five devices with maximum current flow              |

| (1A). By limiting the current to 0.5 $\mu$ A (highlighted), the reliability is enhanced – a       |

| lifetime of one million cycles is achieved at 300 °C and 400 °C158                                |

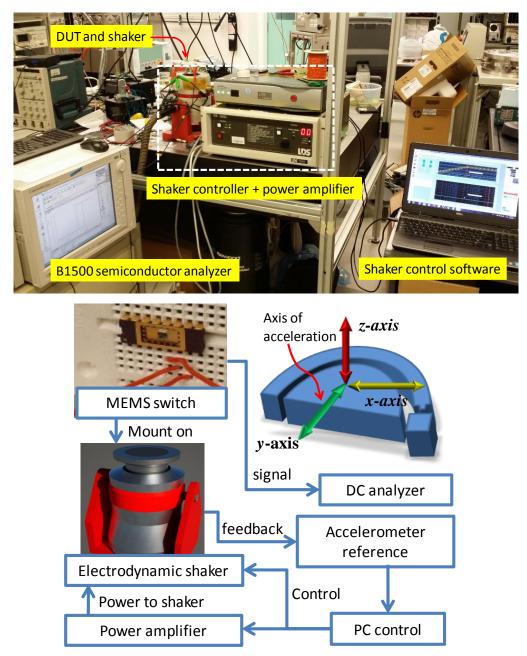

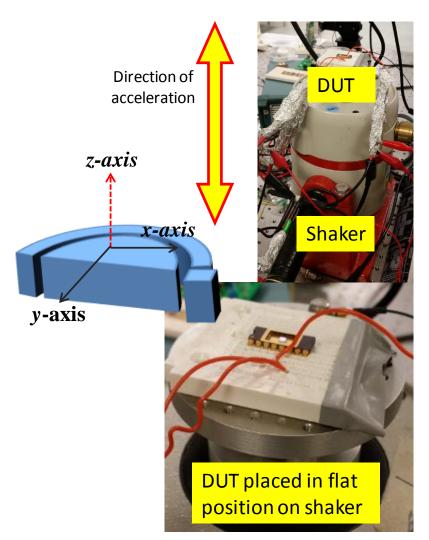

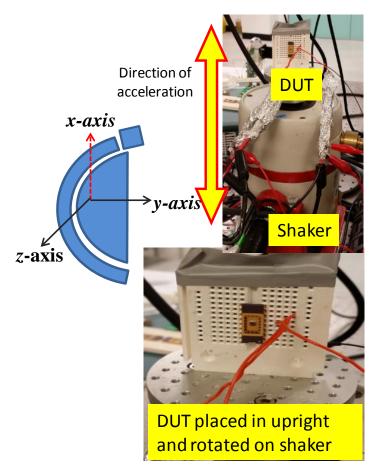

| Figure 5.24: Operation under acceleration shock test with device placed flat on the               |

| shaker. The direction of acceleration is along the $z$ -axis, as represented by the red           |

| dash arrow. The electrical connection for gate, drain and source is connected to the              |

| semiconductor analyser                                                                            |

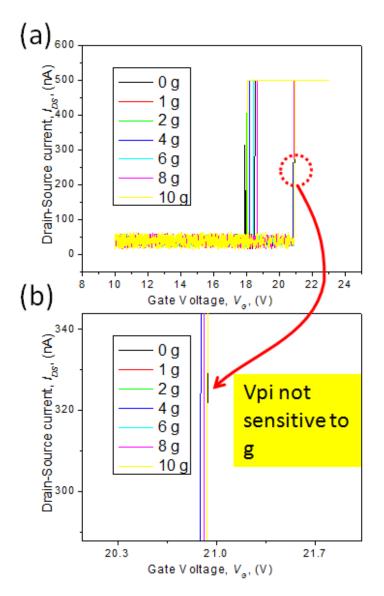

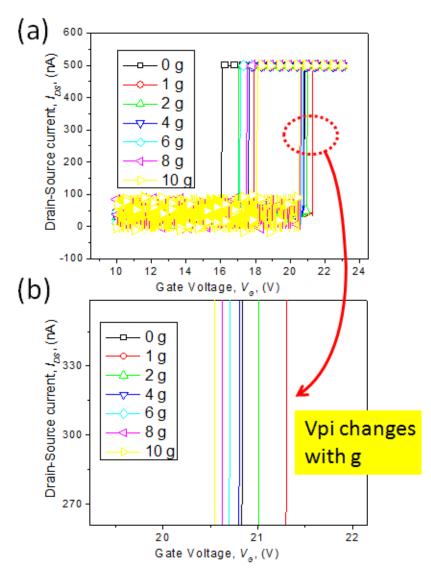

| Figure 5.25: I-V characteristics of a 3 $\mu m \times 80 \ \mu m$ radius curved beam device under |

| z-axis acceleration. (a) Consistent pull-in voltage of approximately 22 V at                      |

| incremental acceleration from 1 g to 10 g @ 2kHz. (b) Zoom-in of the pull-in                      |

| voltage162                                                                                        |

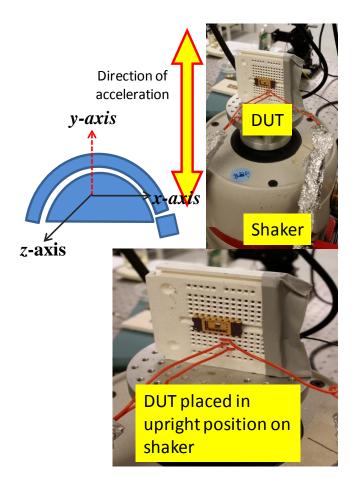

| Figure 5.26: Operation under acceleration shock test with device placed in upright                |

| position on the shaker. The direction of acceleration is along the y-axis, as                     |

| represented by the red dash arrow. The electrical connection for gate, drain and                  |

|---------------------------------------------------------------------------------------------------|

| source is connected to the semiconductor analyzer                                                 |

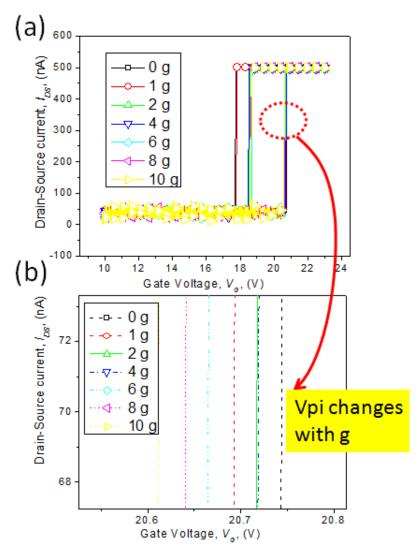

| Figure 5.27: I-V characteristics of a 3 $\mu m \times 80~\mu m$ radius curved beam device under   |

| y-axis acceleration (a) Pull-in voltage decreases with increases of acceleration from             |

| 1 g to 10 g @ 2 kHz. (b) Zoom-in of the pull-in voltage164                                        |

| Figure 5.28: Operation under acceleration shock test with device placed in upright                |

| position on the shaker. The direction of acceleration is along the x-axis, as                     |

| represented by the red dash arrow. The electrical connection for gate, drain and                  |

| source is connected to the semiconductor analyzer                                                 |

| Figure 5.29: I-V characteristics of a 3 $\mu m \times 80 \ \mu m$ radius curved beam device under |

| x-axis acceleration (a) Pull-in voltage decreases with increases of acceleration from             |

| 1 g to 10 g. (b) Zoom-in of the pull-in voltage                                                   |

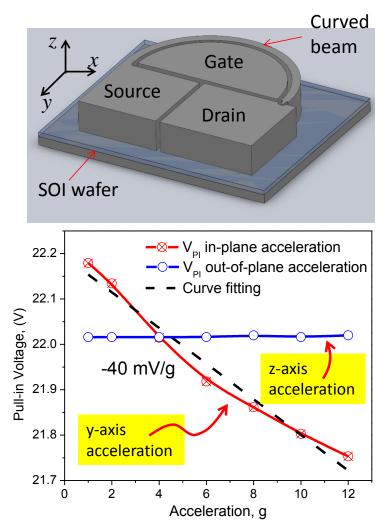

| Figure 5.30: Pull-in voltage $(V_{Pl})$ stability with respect to acceleration at z-axis and      |

| y-axis. $V_{PI}$ drift in y-axis acceleration of -40 mV/g is extracted from curve fitting         |

| using measurement result while no drift is observed in z-axis acceleration167                     |

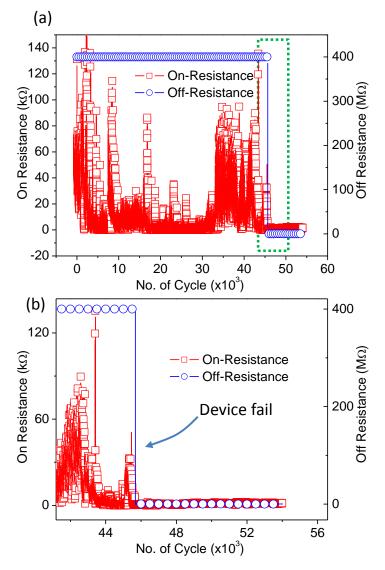

| Figure 6.1: Contact resistance versus number of cycles at 300 °C with maximum                     |

| current compliance (1 A) (a) Approximately 47 thousand cycles achieved for                        |

| Si-to-Si switch encapsulated in vacuum. (b) Zoom-in to the last few cycles showing                |

| that device fail170                                                                               |

| Figure 6.2: Contact resistance versus number of cycles at 400 °C with maximum                     |

| current compliance (1 A) (a) Merely 923 cycles achieved for Si-to-Si switch                       |

| encapsulated in vacuum. (b) Zoomed-in view of device that failed abruptly at 923                               |

|----------------------------------------------------------------------------------------------------------------|

| cycles                                                                                                         |

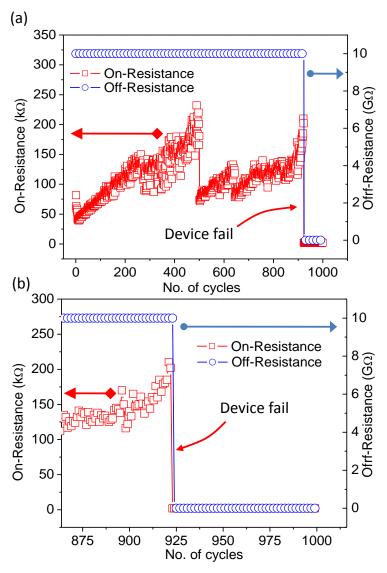

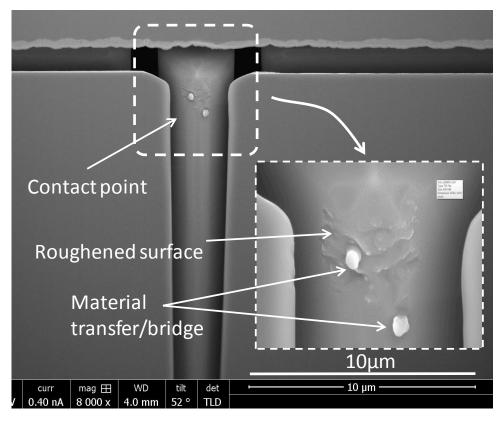

| Figure 6.3: Focus ion beam milling reveals cross-sectional view of a failed device                             |

| after sudden failure at high temperature cycling                                                               |

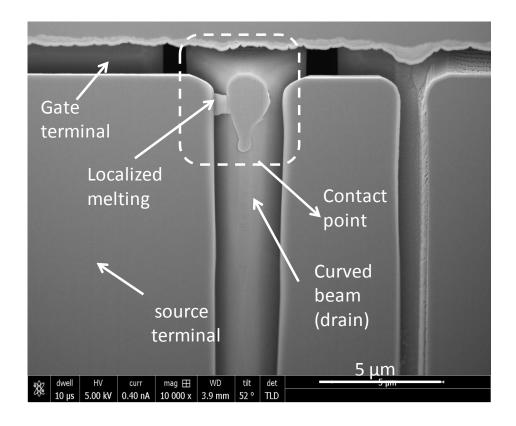

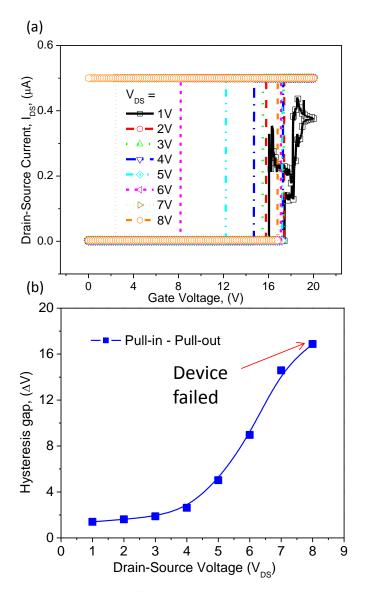

| Figure 6.4: Dependency of the contact resistance on $V_{DS}$ bias from 0.5 V to 4.5 V (a)                      |

| $I_{DS}$ - $V_G$ at different $V_{DS}$ where device failed at $V_{DS}$ = 4.5V. (b) Contact resistance (45      |

| measurements) and calculated contact temperature versus drain source voltage, $R_C$ -                          |

| V <sub>DS.</sub>                                                                                               |

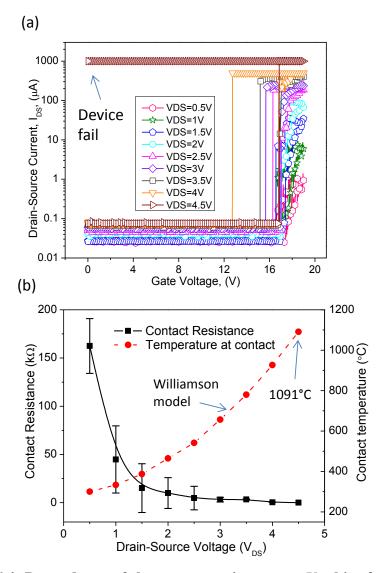

| Figure 6.5: (a.) $I_{DS}$ - $V_G$ at different $V_{DS}$ with $I_{DS}$ limited to 0.5 $\mu$ A. The device fails |

| to pull out at $V_{DS} = 8$ V. (b.) The hysteresis gap increases as drain-source voltage                       |

| increases177                                                                                                   |

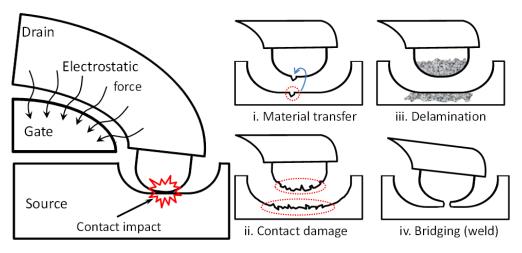

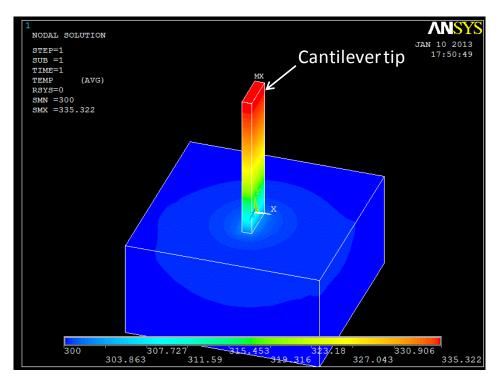

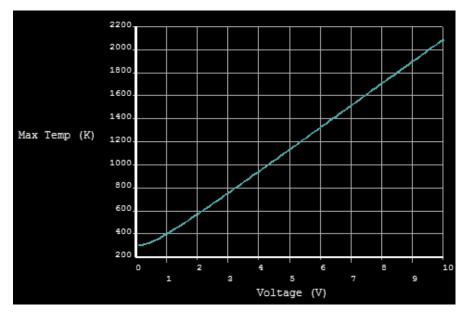

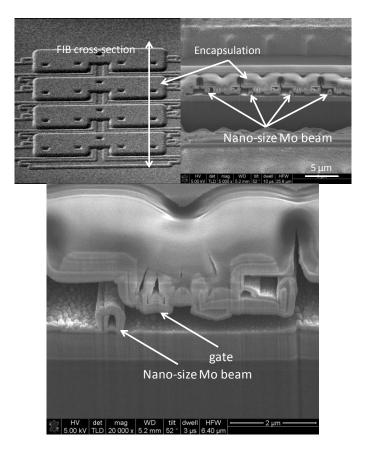

| Figure 6.6: Failure mechanisms of contact switches. Repeated push and pull by                                  |