Software Techniques for Energy Efficient Memories

Pooja Roy (M.S., University of Calcutta, 2010)

#### A THESIS SUBMITTED FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

DEPARTMENT OF COMPUTER SCIENCE SCHOOL OF COMPUTING NATIONAL UNIVERSITY OF SINGAPORE December 2014

# Declaration

I hereby declare that this thesis is my original work and it has been written by me in its entirety. I have duly acknowledged all the sources of information which have been used in the thesis. This thesis has also not been submitted for any degree in any university previously.

(POOJA ROY)

### Abstract

The recent times are known as the *dark silicon era*. *Dark* implies the percentage of the chip that cannot be switched-on at a given time to keep the power consumption in budget. As a consequence, researchers are innovating energy efficient systems. Memory subsystem consumes a major part of energy and so it is imperative to evolve them into energy-efficient memories. In the past few years, new memories such as resistive memories or non-volatile memories have emerged. They are inherently energy efficient and are promising candidates for the future memory devices. However, the application and program layer is not aware of the new memory and new architectural designs. Thus, the application layer is not specifically optimized for energy efficiency.

In this thesis, we propose compiler optimization and software testing methods to optimize programs for energy efficiency. Our techniques provide cross-layer support to fully utilize the advantages of the energy-efficient memories. In most of our works, we assume a resistive technology based hybrid memories as L1 data cache, L2, L3 and main memory level. In hybrid memory designs, data placement is critical as the resistive memories are sensitive to write operations. Therefore, it is common to place a smaller SRAM or DRAM alongside to filter the write accesses. However, caches are transparent to the application layer and so it is challenging to influence the data traffic to the caches at runtime. Our solution is a new virtual memory design (EnVM) that is aware of resistive technology based hybrid caches. EnVM is based on the memory access behaviour of a program and can control the data allocation to the caches. The merits of EnVM diminish at the main memory level, as the size of basic data unit differs from caches. Caches address cache line size data where as main memory addresses a page which is much larger. We propose a new operating system assisted page addressing mechanism that accounts for cache line size data even in the main memory level. Thus, we can magnify the effects of hybrid memory at the main memory level.

The next challenge is a characteristic of the energy-efficient memories that makes them prone to errors (bit-flips). This is not only true for the resistive memories, undervolted memories also exhibit such characteristics. Adapting error detection and correction mechanisms often offsets the gain in power consumption. We propose a framework that exploits the inherent error resiliency of some application to solve this issue. Instead of mitigating, it allows errors if the final output is within a given Quality of Service (QoS) range. Thus, it is possible to run such applications on the energy-efficient memories without having to provide error-correction support. In addition, the gain in energy efficiency is magnified. The above framework, based on a dynamic program testing accrues a large search space to find an optimal approximation configuration for a given program. The running time of the analysis and book-keeping overheads of such techniques scales linearly with increase in program size (lines of code). In out next work, we propose a static code analysis which deduces accuracy measures for program variables to achieve a given QoS. This compile-time framework complements the dynamic testing schemes and can improve their efficiency by reducing the search space.

In this thesis, we show that with proper support from the software stack, it is possible deploy energy efficient memories in the current memory hierarchy and achieve remarkable reduction in power consumption without compromising performance.

### Acknowledgments

"You need the willingness to fail all the time. You have to generate many ideas and then you have to work very hard only to discover that they don't work. And you keep doing that over and over until you find one that does work." – John Backus

I thank my advisor Professor Weng Fai Wong, who placed his trust in me, and without whom this thesis would not be real. Prof. Wong has taught me all I know about research and the art of solving problems. I learnt from him the kind of rigor, focus and precision that is imperative in research. Not only he encouraged me to generate new ideas, to work hard on them till it comes to fruition, he is also the person I have always turned to regarding basics of compiler optimizations. I am especially thankful for his patience and his faith in me during the most difficult times of my research. I am always inspired by his integrity and sincerity. I hope to be a researcher and a professor of brilliance as his.

I thank Professor Tulika Mitra, for her constant support, valuable guidance and feedback. She has always been my inspiration since I joined the School of Computing. I thank Professors Siau Cheng Khoo and Wei Ngan Chin for their precious time and guidance. I thank Professors Debabrata Ghosh Dastidar and Nabendu Chaki, for their support throughout my undergraduate and graduate studies in India. I thank Dr. Rajarshi Ray and Dr. Chundong Wang for their support as seniors, Manmohan and Jianxing for being amazing colleagues. I thank my friends in Singapore for making this city a home away from home. I am deeply thankful my wonderful roommates Damteii, Sreetama, Sreeja and Priti for taking care of me everyday. I thank my friends in Kolkata, especially Debajyoti, for their assurance and love in the times I needed the most. I thank all my seniors and friends of Soka Gakkai, especially Dr. M. Sudarshan, for their constant prayers and encouragements.

I thank all the staffs in Dean's office and the graduate department for helping me in administrative matters and for making it possible for me to attend conferences and present my work.

Finally, I thank my grandmother for she is my first friend and my first teacher, my uncle for his constant encouragements, my little cousins and my late aunt, who has a place next to my mother's in my life. I also thank all my close relatives for always making me feel pampered and loved. I thank Avik for his patience, love and for making my dreams his priority.

I thank my parents, who instilled in me the passion to study and provided me with all the faculties to pursue my dreams. Without their love and support, I would not have been anything near to what I am today. Lastly, I thank my mentor in life Dr. Daisaku Ikeda, whose words of encouragement kept me going through the roller coaster ride of my doctoral studies and to whom I dedicate my thesis.

To Sensei.

# Contents

|          | Dec  | elaration                                  | i            |

|----------|------|--------------------------------------------|--------------|

|          | Abs  | stract                                     | iii          |

|          | Ack  | knowledgements                             | $\mathbf{v}$ |

|          | List | of Figures                                 | xiv          |

|          | List | of Tables                                  | xvi          |

|          | List | of Algorithms                              | xvii         |

|          | Puł  | olications                                 | xix          |

| 1        | Inti | roduction                                  | 1            |

|          | 1.1  | Energy Efficient Memories                  | 1            |

|          | 1.2  | Motivation & Goal                          | 5            |

|          | 1.3  | Contributions                              | 8            |

|          |      | 1.3.1 Write Sensitivity of Hybrid Memories | 8            |

|          |      | 1.3.2 Error Management of Hybrid Memories  | 10           |

|          | 1.4  | Thesis Outline                             | 12           |

| <b>2</b> | Bac  | kground & Related Works                    | 13           |

|          | 2.1  | Resistive Memories                         | 13           |

|          | 2.2  | Write Sensitivity of Hybrid Memories       | 14           |

|   |     | 2.2.1   | Hybrid Caches                                  | 15 |

|---|-----|---------|------------------------------------------------|----|

|   |     | 2.2.2   | Hybrid Main Memories                           | 17 |

|   | 2.3 | Error   | Susceptibility of Hybrid Memories              | 19 |

|   | 2.4 | Appro   | eximate Computing                              | 20 |

|   |     | 2.4.1   | Approximation in Programs                      | 20 |

|   |     | 2.4.2   | Approximation in Hardware Devices              | 21 |

| 3 | Cor | npilati | on Framework for Resistive Hybrid Caches       | 23 |

|   | 3.1 | Motiva  | ation                                          | 23 |

|   | 3.2 | Our P   | Proposal                                       | 25 |

|   | 3.3 | EnVM    | f                                              | 27 |

|   |     | 3.3.1   | Statically Allocated Data                      | 29 |

|   |     | 3.3.2   | Dynamically Allocated Data                     | 35 |

|   | 3.4 | Puttin  | ng It All Together                             | 39 |

|   | 3.5 | Archit  | cectural Support                               | 40 |

|   |     | 3.5.1   | Boundary Registers                             | 40 |

|   |     | 3.5.2   | Cache Properties                               | 40 |

|   | 3.6 | Evalua  | ation                                          | 42 |

|   |     | 3.6.1   | Tools & Benchmark                              | 42 |

|   |     | 3.6.2   | Results                                        | 43 |

|   | 3.7 | Chapt   | er Summary                                     | 49 |

| 4 | Ope | erating | s System Assisted Resistive Hybrid Main Memory | 51 |

|   | 4.1 | Motiva  | ation                                          | 51 |

|   | 4.2 | Our P   | Proposal                                       | 56 |

|   | 4.3 | Fine-C  | Grain Writes                                   | 57 |

|   |     | 4.3.1   | Shadow Page Management                         | 57 |

|   |     | 4.3.2   | Extended LLC                                   | 59 |

|   |     | 4.3.3   | Shadow Table Cache                             | 60 |

|   | 4.4 | Fine-Grain Page Reclamation                                                 | 60  |

|---|-----|-----------------------------------------------------------------------------|-----|

|   | 4.5 | Evaluation Methodology                                                      | 65  |

|   | 4.6 | Experimental Results                                                        | 69  |

|   |     | 4.6.1 Write Reduction to PCM                                                | 69  |

|   |     | 4.6.2 Memory Utilization                                                    | 70  |

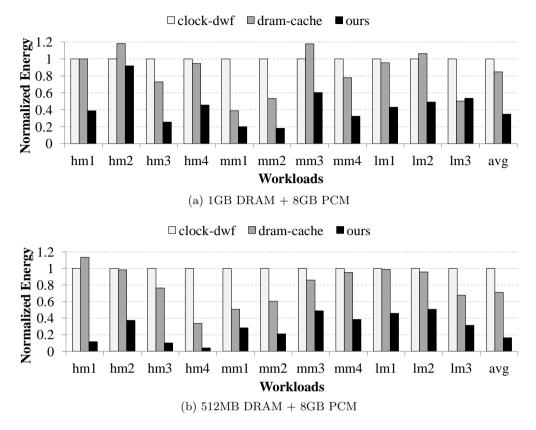

|   |     | 4.6.3 Energy Consumption                                                    | 71  |

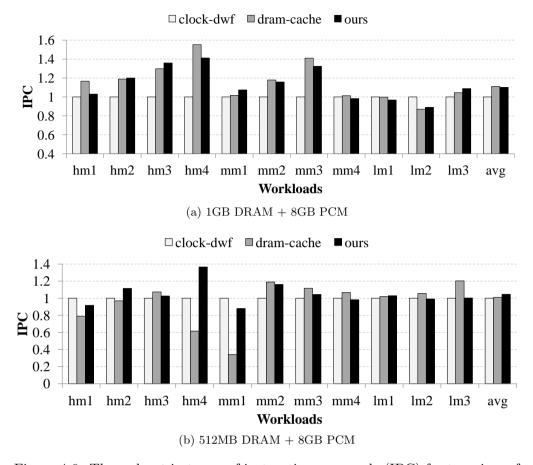

|   |     | 4.6.4 Performance                                                           | 73  |

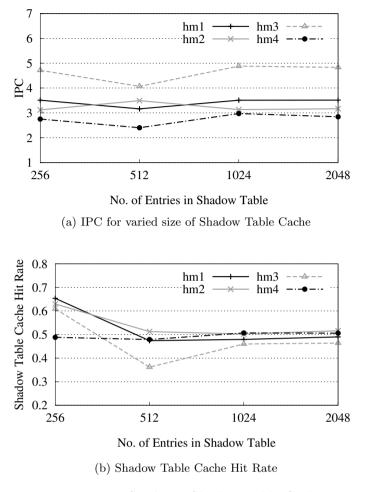

|   |     | 4.6.5 Shadow Table Cache                                                    | 74  |

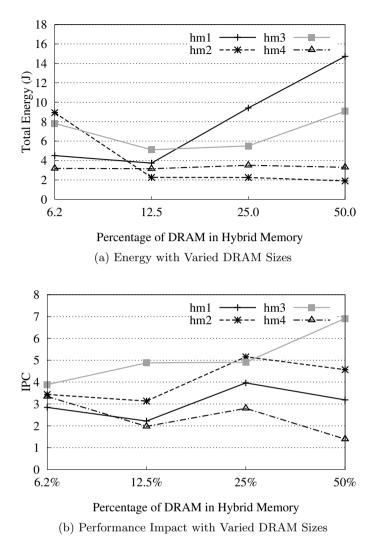

|   |     | 4.6.6 DRAM Sizes                                                            | 74  |

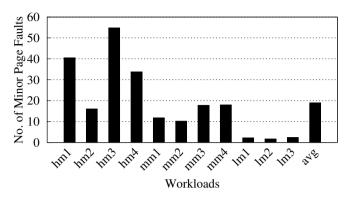

|   |     | 4.6.7 Page Reclamation                                                      | 77  |

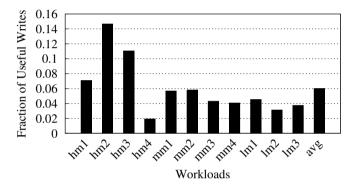

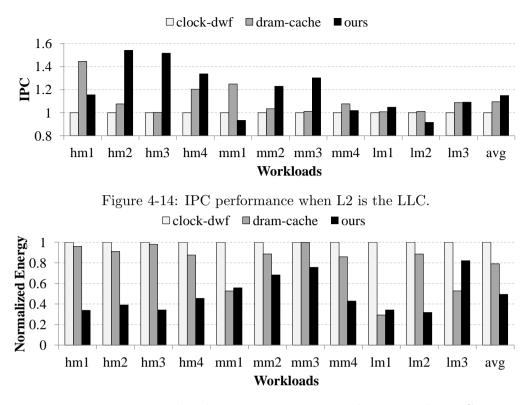

|   |     | 4.6.8 L2 as Last Level Cache                                                | 78  |

|   | 4.7 | Chapter Summary                                                             | 80  |

| 5 | Err | or Management through Approximate Computing                                 | 81  |

|   | 5.1 | Motivation                                                                  | 82  |

|   | 5.2 | Our Proposal                                                                | 83  |

|   | 5.3 | Automated Analysis                                                          | 86  |

|   | 5.4 | Optimizations                                                               | 93  |

|   |     | 5.4.1 Discretization Constant                                               | 93  |

|   |     | 5.4.2 Perturbation Points                                                   | 95  |

|   |     | 5.4.3 Instrumentation & Testing $\ldots \ldots \ldots \ldots \ldots \ldots$ | 96  |

|   | 5.5 | Evaluation                                                                  | 96  |

|   | 5.6 | Chapter Summary                                                             | 103 |

| 6 | Cor | npilation Framework for Approximate Computing                               | 105 |

|   | 6.1 | Overview                                                                    | 105 |

|   | 6.2 | PAC Framework                                                               | 108 |

|   |     | 6.2.1 Component Influence Graph (CIG)                                       | 109 |

|   |     | 6.2.2 Accuracy Equations                                                    | 111 |

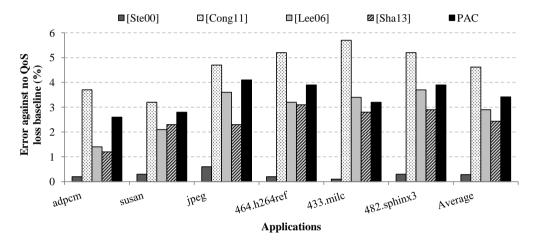

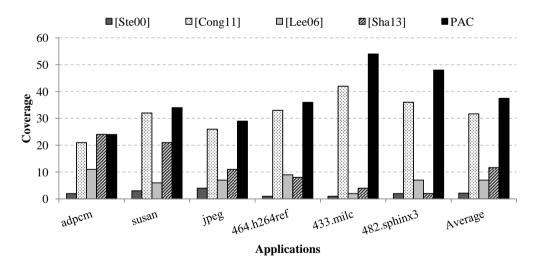

|   |     | 6.3.1   | Comparison with approximation techniques        | 119 |

|---|-----|---------|-------------------------------------------------|-----|

|   |     | 6.3.2   | Comparison with software reliability techniques | 121 |

|   |     | 6.3.3   | Impact of Errors                                | 124 |

|   |     | 6.3.4   | Impact of Approximating Conditions              | 126 |

|   | 6.4 | Chapt   | er Summary                                      | 126 |

| 7 | Con | clusio  | n                                               | 129 |

|   | 7.1 | Thesis  | Summary                                         | 129 |

|   | 7.2 | Future  | e Research                                      | 131 |

|   | Bib | liograp | bhy                                             | 132 |

# List of Figures

| Broad classification of energy efficient memories                   | 2                                                                                                                               |

|---------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| A comprehensive illustration of the scope of this thesis. $\ . \ .$ | 8                                                                                                                               |

| Simple hybrid memory hierarchy                                      | 15                                                                                                                              |

| Different designs of hybrid main memory                             | 17                                                                                                                              |

| Existing and proposed virtual memory design for hybrid mem-         |                                                                                                                                 |

| ories                                                               | 28                                                                                                                              |

| Percentage of variables in a program with certain memory ac-        |                                                                                                                                 |

| cess affinity.                                                      | 29                                                                                                                              |

| Example of modified code in the benchmarks with new malloc          |                                                                                                                                 |

| calls                                                               | 36                                                                                                                              |

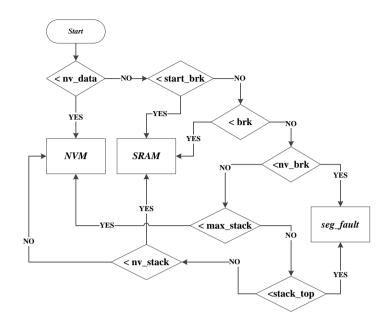

| Overall framework of EnVM                                           | 39                                                                                                                              |

| Cache Selection Logic.                                              | 41                                                                                                                              |

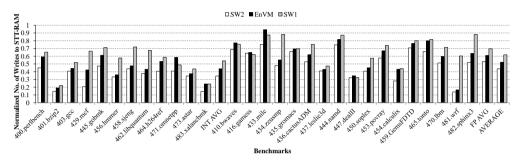

| Total writes to STT-RAM in a hybrid cache design normalized         |                                                                                                                                 |

| to the total number of writes to a $pure\ STT\text{-}RAM$ cache     | 43                                                                                                                              |

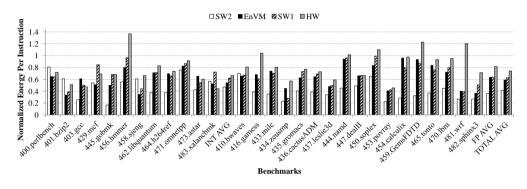

| Energy per instruction normalized against <i>pure SRAM</i> cache.   | 45                                                                                                                              |

| Energy (joules/instruction) consumed by the additional hard-        |                                                                                                                                 |

| ware units for HW and EnVM                                          | 46                                                                                                                              |

| Total energy consumption by additional hardware components.         | 46                                                                                                                              |

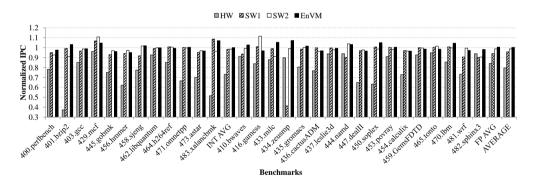

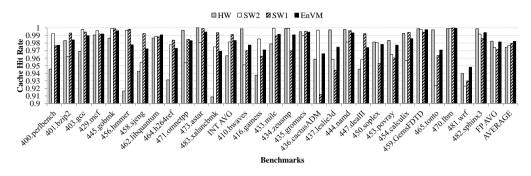

| Instructions Per Cycle (IPC) normalized to pure SRAM based          |                                                                                                                                 |

| cache design.                                                       | 47                                                                                                                              |

| Cache hit rate for the hybrid L1 cache design                       | 48                                                                                                                              |

|                                                                     | A comprehensive illustration of the scope of this thesis Simple hybrid memory hierarchy Different designs of hybrid main memory |

| 3-12 | Summary of state-of-the-art methods and EnVM                            | 48 |

|------|-------------------------------------------------------------------------|----|

| 4-1  | Different designs of hybrid main memory                                 | 52 |

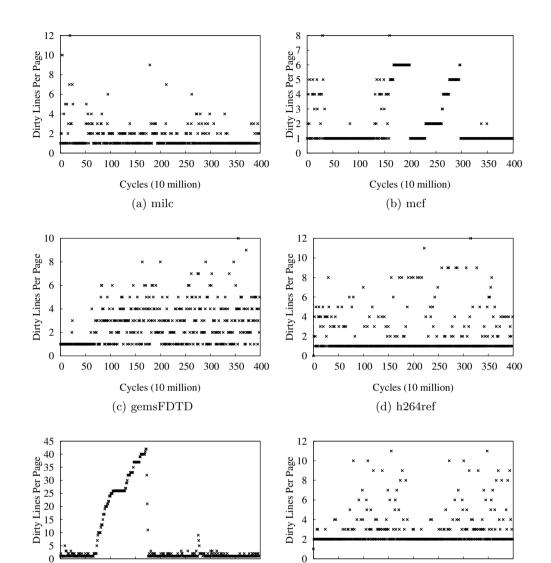

| 4-2  | An example showing the extra amount of dirty data in main               |    |

|      | memory due to cache line size writebacks                                | 53 |

| 4-3  | Average number of dirty cache line per main memory page of              |    |

|      | six memory intensive applications                                       | 55 |

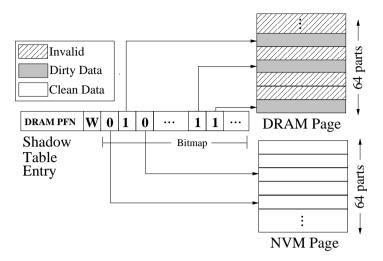

| 4-4  | Shadow page and shadow table entry                                      | 58 |

| 4-5  | PCM to shadow page physical address translation                         | 59 |

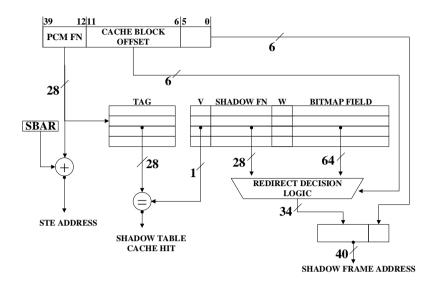

| 4-6  | Example of dirtiness aware page reclamation with an overlook            |    |

|      | value of 8                                                              | 63 |

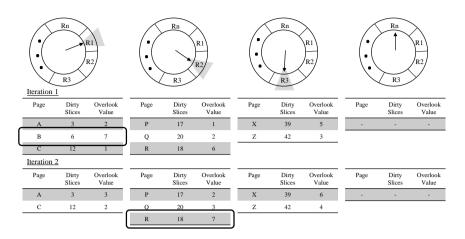

| 4-7  | Overview of our proposed framework                                      | 64 |

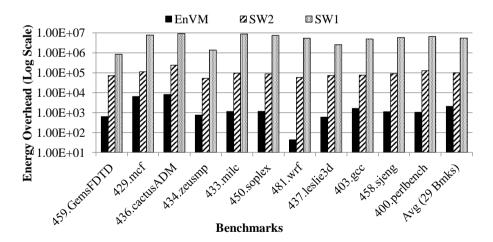

| 4-8  | Dynamic energy of hybrid memory (DRAM+PCM) for two                      |    |

|      | sizes of DRAM, normalized to energy consumption of $\verb"clock-dwf"$ . | 72 |

| 4-9  | Throughput in terms of instructions per cycle (IPC) for two             |    |

|      | sizes of DRAM, normalized to the IPC of $clock-dwf$                     | 73 |

| 4-10 | Study on Shadow Table Cache.                                            | 75 |

| 4-11 | Study on varied DRAM sizes                                              | 76 |

| 4-12 | Total number of minor page faults                                       | 77 |

| 4-13 | Amount of useful writes to PCM                                          | 77 |

| 4-14 | IPC performance when L2 is the LLC                                      | 78 |

| 4-15 | Normalized energy consumption when L2 is the LLC. $\ldots$              | 78 |

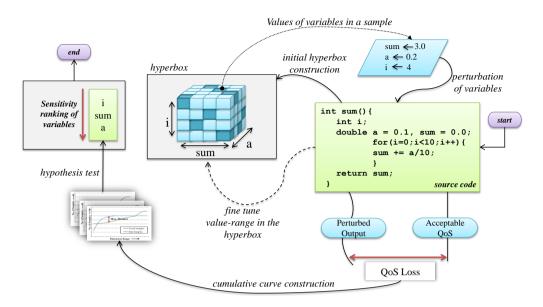

| 5-1  | Overview of "ASAC" framework. Each box represents a step                |    |

| -    | and the arrows are the dataflow between them. There is an               |    |

|      | information flow from Sampler back to the Hyperbox Con-                 |    |

|      | struction to facilitate further optimization in range analysis.         | 85 |

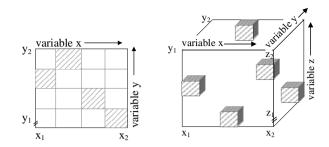

| 5-2  | Example of 2 dimensional and 3 dimensional hyperboxes                   | 88 |

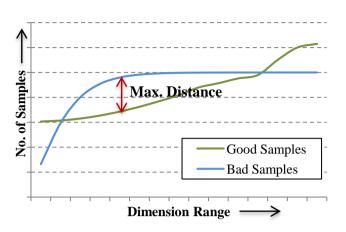

| 5 - 3 | Example CDFs of "good" and "bad" samples based on the                       |     |

|-------|-----------------------------------------------------------------------------|-----|

|       | QoS and distance metric.                                                    | 91  |

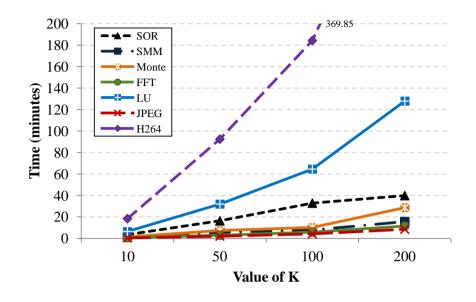

| 5-4   | Total runtime (minutes) of ASAC with values of $k$ while $m = 2$ .          | 94  |

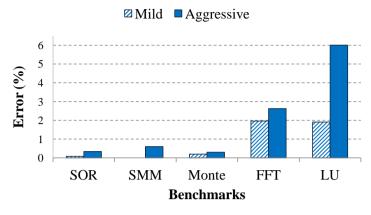

| 5 - 5 | Percentage of error after approximating program data. The                   |     |

|       | two bars are different error percentage after approximating                 |     |

|       | either one-third or all the data that are classified as approx-             |     |

|       | imable by ASAC                                                              | 99  |

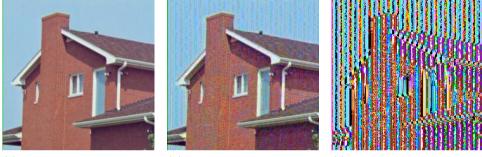

| 5-6   | JPEG benchmark with various levels of approximations sepa-                  |     |

|       | rately in <i>Encode</i> and <i>Decode</i> stages. Image (a) is the original |     |

|       | image. Images (b) and (c) are result of introducing mild ap-                |     |

|       | proximation (in $30\%$ of the variables). Images (d) and (e)                |     |

|       | are result of introducing aggressive approximation (in all the              |     |

|       | variables that are approximable)                                            | 101 |

| 5-7   | JPEG benchmark with errors in data that are marked as "Pre-                 |     |

|       | cise" by ASAC                                                               | 101 |

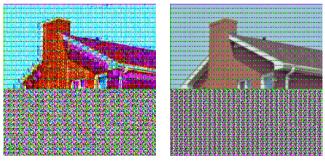

| 6-1   | A kernel and corresponding CIG from fft.c (MiBench) $\ . \ . \ .$           | 109 |

| 6-2   | An example of a CIG showing the 'Error Independence' relations.             | 112 |

| 6-3   | DoA propagation for branching statements in a CFG. $\ . \ . \ .$            | 114 |

| 6-4   | Transformation for approximate comparison. $\ldots$                         | 117 |

| 6-5   | Error Percentage (error injected in approximable variables)                 | 125 |

| 6-6   | Impact of errors injection in approximable variables character-             |     |

|       | ized by different methods                                                   | 125 |

# List of Tables

| 1.1 | Comparison of features of different memory technologies     | 4   |

|-----|-------------------------------------------------------------|-----|

| 3.1 | Simulation Configuration                                    | 42  |

| 4.1 | Simulation Configuration                                    | 66  |

| 4.2 | SPEC2006 and PARSEC benchmarks and their working set sizes  | 67  |

| 4.3 | Workloads                                                   | 68  |

| 4.4 | Detailed memory access counts for clock-dwf                 | 69  |

| 4.5 | Detailed memory access counts for dram-cache                | 69  |

| 4.6 | Detailed memory access counts for our framework             | 70  |

| 5.1 | Ranges of some variables in H.264                           | 87  |

| 5.2 | Percentage of variables marked as approximable by ASAC with |     |

|     | different values of $k$ and $m$                             | 95  |

| 5.3 | Description of all the benchmarks used for evaluation       | 97  |

| 5.4 | Comparison of $ASAC$ with "EnerJ" [1]                       | 98  |

| 5.5 | H.264 Approximation Results                                 | 100 |

| 6.1 | Comparison with EnerJ to show PAC's accuracy.               | 119 |

| 6.2 | Comparison with ASAC to show PAC's accuracy                 | 120 |

| 6.3 | Runtime of PAC as compared to standard $-03$ optimization   |     |

|     | flag in GCC and ASAC                                        | 120 |

| 6.4 | Description of the applications                             | 122 |

| 6.5 | Comparison with bitwidth analysis with no. of variables for |     |

|-----|-------------------------------------------------------------|-----|

|     | all cases (above paragraph) and ratio of code coverage      | 123 |

| 6.6 | Comparison with PDG based scheme with no. of matches        |     |

|     | identified by both methods and PAC's accuracy. $\hdots$     | 123 |

| 6.7 | Overhead of conditional transformation                      | 126 |

# List of Algorithms

| 3.1 | Address Generation for Global and Stack Data (Partial) $\ . \ .$ | 34  |

|-----|------------------------------------------------------------------|-----|

| 3.2 | Dual Heap Management                                             | 37  |

| 4.1 | Write Aware Page Reclamation                                     | 61  |

| 5.1 | Range Analysis                                                   | 87  |

| 5.2 | Hyperbox Construction & Sampling                                 | 90  |

| 5.3 | Sensitivity Ranking                                              | 92  |

| 6.1 | CIG Construction                                                 | 110 |

| 6.2 | Branching Statements' Accuracy Propagation                       | 115 |

| 6.3 | PAC dataflow Analysis (Partial)                                  | 116 |

## List of Publications

- 1. Pooja Roy, Manmohan Manoharan, Weng Fai Wong. *Fine Grain Management of Non-Volatile Hybrid Main Memories*, Manuscript in preparation.

- Pooja Roy, Jianxing Wang, Weng Fai Wong. PAC: Program Analysis for Approximation-aware Compilation, Working Paper.

- Pooja Roy, Manmohan Manoharan, Weng Fai Wong. EnVM : Virtual Memory Design for New Memory Architectures, In Proceedings of the 2014 International Conference on Compilers, Architectures and Synthesis of Embedded Systems (CASES 2014), Article No. 12, New Delhi, India, October 12 - 17, 2014, ACM.

- Pooja Roy, Rajarshi Ray, Chundong Wang, Weng Fai Wong. ASAC: Automatic Sensitivity Analysis for Approximate Computing, In Proceedings of the 2014 SIGPLAN/SIGBED Conference on Languages, Compilers and Tools for Embedded Systems, LCTES '14, pages 95 - 104, Edinburgh, UK, June 12 - 13, 2014, ACM.

- Pooja Roy, Manmohan Manoharan, Weng Fai Wong. Write Sensitive Variable Partitioning for Resistive Technology Caches, 51<sup>st</sup> Design Automation Conference (DAC), poster, San Francisco, USA, June 1 - 5, 2014.

### Chapter 1

# Introduction

The evolution of computer systems has reached a juncture where the percentage of chips that can be utilized, keeping the power consumption within a budget, is decreasing exponentially. This is commonly known as the *utilization wall* or the *power wall*. As memory devices are the primary consumers of power, it is imperative to evolve them into energy efficient memories. Architectural innovations have been explored and applied extensively to make the memory devices energy efficient. Dynamic voltage/frequency scaling (DVS/DVFS) based memories, non-volatile memories (NVMs, Flash), reconfigurable memories are some of the widely accepted examples. In this thesis, we attempt to explore software techniques to enable improved utilization of the energy efficient memories.

#### **1.1** Energy Efficient Memories

There are broadly two kinds of energy efficient memories. First, memories that are built with low power consuming devices or materials. Non-volatile memories such as flash, NAND flash, magnetoresitive random access memory (MRAM), spin transfer torque random access memory (STT-RAM), phase change memory (PCM), racetrack or domain-wall memory (DWM) are some of the examples.

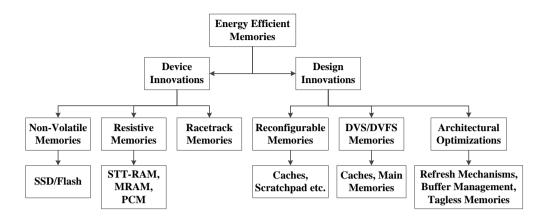

Figure 1-1: Broad classification of energy efficient memories

Second class energy efficient memories are the ones that are operated in an optimized fashion to reduce their power consumption. These are essentially architectural designs that apply to any type of memory device. However, such optimization techniques depend on the level of the memory device in the memory hierarchy. For example, refresh mechanisms for DRAM based main memories reduces the number of times a DRAM bank is periodically recharged and this is one of the earliest attempts to reduce power consumption. Operating memory devices at different voltage and frequency levels is another way of optimizing them for power, often known as DVS/DVFS based memories. Recently, reconfigurable caches, where the number of sets and ways can be dynamically controlled depending on some constraints are also being extensively researched for energy efficiency of the memories. Figure 1-1 illustrates the classification of the energy efficient memories that will aid in understanding the perspective of this thesis.

#### **Limitations of Conventional Memories**

In a discussion on energy efficient memories, it is important to describe the limitations of the conventional memory devices and architectures. First, let us examine the SRAM devices. SRAM is widely used to build processor caches. SRAM is fast, which makes it suitable to be placed very close to the performance critical pipeline. However, SRAM suffers a power penalty in terms of leakage current. As the technology node scales and capacity increases, the leakage current of SRAM becomes a more serious concern. Therefore, for higher capacity off-chip memories, DRAM is the usual choice. DRAMs are denser and cheaper compared to SRAMs. Though they do not exhibit leakage current component, the power ditch is the refresh energy. DRAM cells discharge with time and thus need to be refreshed to keep the data alive. This refresh mechanism constitutes the majority of the power consumption in DRAMs.

Multi-core systems demand larger memory on and off-chip to be able to provide higher compute power and functionality. On the other hand, low-power embedded devices such as smartphones and tablets, though do not demand huge compute capabilities, poses higher power constraints in terms of battery provision. In both scenarios, the demerits with respect to power consumption, makes it difficult to put more SRAM and DRAM to suffice the requirements and constraints. Therefore, the gradual shift from conventional memory designs and devices to energy efficient memories is inevitable.

#### **Resistive Memory Devices**

Resistive memory devices are essentially non-volatile memories that are capable of retaining data independent of the power supply. Therefore, they are free from leakage current or refreshes. Resistive memories such as MRAM, STT-RAM and PCM are well studied and considered for on-chip and off-chip memory levels. Specifically, STT-RAM is considered as a suitable device for processor caches. They are 4x denser than SRAM, which either provides bigger caches or reduces the silicon area budget of the chips. At the main memory level, PCM is considered to be the next alternative of DRAM providing faster and bigger offchip memories. However, these memories have few drawbacks. First, the access latencies of load (read) and store (write) are asymmetric. The memory write access is usually 3x longer than memory read. Secondly, the write endurance of the resistive memories is much lower than their conventional counterparts. Write endurance is defined as the maximum number of write operations a memory cell can endure before failing permanently. Moreover, the write current is also higher and so, the resistive memories are also known as write-sensitive memories.

Therefore, if the resistive memories receive a large amount of write operations without any control, the lifetime of the entire chip will be reduced. The non-volatility of the resistive memories could be relaxed to gain lower access latency for memory read and write. The time period for which it can preserve memory content without a refresh is known as the *Retention Time*. However, beyond the retention time, these memories are susceptible to stochastic error in terms of single or multiple bit-flips. This characteristic is similar to that of soft errors in the conventional memory devices. Such errors are inherently a part of dynamic voltage and frequency scaled memories, which is described in the following section. We will refer to this issue as error susceptibility. Table 1.1

| Features                | SRAM      | DRAM      | MRAM       | PCM      | STT-RAM    |

|-------------------------|-----------|-----------|------------|----------|------------|

| Non-Volatile            | No        | No        | Yes        | Yes      | Yes        |

| Cell-Size $(F^2)$       | 5-120     | 6-10      | 16-40      | 6-12     | 6-20       |

| Read Latency (ns)       | 1-100     | 30        | 3-20       | 20-50    | 2-20       |

| Write Latency (ns)      | 1-100     | 15        | 3-20       | 50/120   | 2-20       |

| Endurance               | $10^{16}$ | $10^{16}$ | $>10^{15}$ | $10^{8}$ | $>10^{15}$ |

| Write Power             | Low       | Low       | High       | Low      | Low        |

| Other Power Consumption | Leakage   | Refresh   | None       | None     | None       |

Table 1.1: Comparison of features of different memory technologies

shows a comprehensive comparison of all the memory technologies mentioned above.

#### **DVS/DVFS** Based Memory Designs

In a DVS or DVFS based memory, the voltage or frequency is dynamically changed to reduce power consumption. Decreasing the operating voltage of a memory is also known as *undervolting*. Together with reducing power consumption, undervolting also reduces reliability and renders the memory prone to errors. DVS/DVFS is a popular energy controlling mechanism at all levels of memory hierarchy. Beginning from instruction and data L1 caches, it can be applied to all cache levels and aptly to main memories too. Researchers have explored many novel architectures and policies to utilize DVS/DVFS based memories. However, the error handling and book-keeping involved in all such techniques, always negates the energy gain to an extent.

#### 1.2 Motivation & Goal

In this thesis, we would explore the various possibilities of deploying energy efficient memories at various levels of the memory hierarchy. Specifically, we would propose compiler and software assisted techniques that unleash the full potential of these memories. We base our works on *hybrid memory* architectures. In hybrid memory systems, a resistive memory is supported by a conventional SRAM/DRAM memory with a smaller capacity to filter out write accesses. Summarizing the scope and attempt of this thesis in a comprehensive way -

- We assume an energy-efficient memory hierarchy consisting of resistive technology based hybrid memories at each level. Though these memories will exhibit similar properties, the implications are different when they are placed at different levels of the memory hierarchy.

- Specifically, we will focus on compilation and software techniques and how such methods can be applied to aid the energy-efficient memories.

- Finally, we would engage our efforts to deal with two specific challenges, namely, **write sensitivity** and **error susceptibility** of energy efficient memories.

Overall, we attempt to answer the following question -How to optimize programs so that they can alleviate the weaknesses of the energy-efficient memories in the underlying hardware architecture?

#### Software Support for Memory Hierarchy

Usually, it is a common practice to analyze and optimize program code based on the underlying hardware on which it is expected to be executed. Information on the program code is used to optimize and compile it so that it gains maximum in terms of performance and correctness at runtime.

For example, *Registers* are one of the very limited, yet important hardware resources. Registers play a key role in the performance, as they are situated closest to the processor. *Register Allocation*, therefore, is a very significant step in the compilation process that determines which variables could be allocated to registers and at what point of program execution should they be written back to the memory. As the numbers of registers are limited and in contrast, the numbers of variables in a program are much larger, it is a difficult task to sieve and allocate the variables to registers in an optimal fashion. Register allocation techniques are well-studied over decades and still it remains one of the most important research areas as it plays a significant role in the performance of systems.

However, as the power consumption has now become a threat to further evolution of computer systems, program codes are being analyzed and transformed in various new ways, so that it consumes less energy too, while it is executed. In pursuit of this, it is essential to examine if existing off-the-shelf program analysis techniques already provide such a support.

In this thesis, we are chiefly concerned with energy consumption of memory devices. When a program is analysed for its memory usage, generally the load and store instructions are of prime importance. In most of the conventional program analysis and optimization techniques, the memory accesses are considered to be symmetric i.e. a read access is equivalent to a write access in terms of latency and probe. In addition, correctness of the program output is regarded as the goal while optimizing programs for a particular underlying architecture. While the above-mentioned assumptions are no longer valid for architectures using energy efficient memories, it is therefore, imperative to design new program analyses and optimizations to perceive the advantages of energy efficient memories.

#### **1.3** Contributions

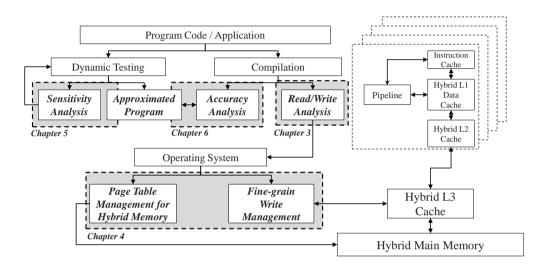

Figure 1-2: A comprehensive illustration of the scope of this thesis.

In this thesis, we would explore the various ways a program can be optimized for a completely energy efficient memory hierarchy. Figure 1-2 illustrates the possible influences of software and compiler techniques over memories at different levels of the memory hierarchy and a comprehensive illustration of the scope of this thesis. The *gray* boxes represent the works proposed in this thesis.

#### 1.3.1 Write Sensitivity of Hybrid Memories

#### **Optimizing Programs for Hybrid Caches**

Caches are the most critical memories to the performance of a system. A resistive memory based cache hierarchy as the next generation of on-chip memories is well explored. However, as mentioned before, if caches are built with resistive memory technology, they will be sensitive to write operations. Compilation techniques that are aware of this write sensitivity and access latency asymmetry are able to support the resistive memories on behalf of the software stack. Differentiating between read and write operations would not only enhance performance, reduce power consumption, it will increase the lifetime of the chips also. Unfortunately, caches are transparent to the application layer. The only way to control the data allocation to the caches is to influence the physical address of memory objects. The physical address of memory objects are strongly mapped to the virtual addresses.

Therefore, we propose a new virtual memory design, *EnVM*, which is aware of resistive memory based hybrid caches. In particular, we assume a STT-RAM and SRAM based hybrid cache, deployed at any level of cache hierarchy. Virtual addresses are generated according to memory access behaviour of the program variables. Read and write intensive data are allocated separately in the virtual memory area, introducing a data locality based on the memory access behaviour. The new virtual memory layout is implicitly used to allocate data to STT-RAM and SRAM at any level of the memory hierarchy and is not dependent on the particular arrangements of the two partitions. The proposed design successfully filters out write operations and allocates them to SRAM. Chapter 3 elaborates more on this work.

#### **Operating System Assisted Hybrid Main Memories**

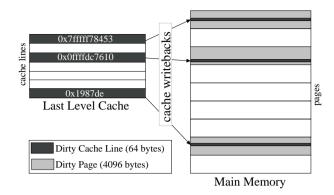

EnVM is capable of influencing data allocation to all the memories in the entire memory hierarchy from L1 caches to the main memory. As it is a virtual memory design, unique to a process, it is also applicable to multi-core and multi-tasking environments. EnVM is supported by a small hardware component which is coupled with the address translation unit. Thus, it closely monitors and intercepts cache fills and writebacks. Read and write intensive data are read and written back to the resistive and conventional SRAM/DRAM partitions respectively, in all levels of caches. However, the data exchange between the last level cache (LLC) and main memory is different in nature. The unit of data copied between the caches is the size of cache lines (say 64 bytes), generally same for different levels of caches. In case of LLC writebacks, there is a disparity between the sizes.

LLC usually maintains a cache line size writeback. On the contrary, the main memory maintains data in units of pages (say 4KB) which is much larger than the cache line size. Therefore, any read or write intensive data that is written back from the LLC under the influence of EnVM, has no guarantee to maintain the locality based on memory access intensity in the main memory too. As the page size is large, it is difficult to allocate all the read and write intensive data separately in the resistive and DRAM partitions. To achieve that, the virtual memory area should be aligned with page size containing same size chunks of read and write intensive data, which is very unlikely.

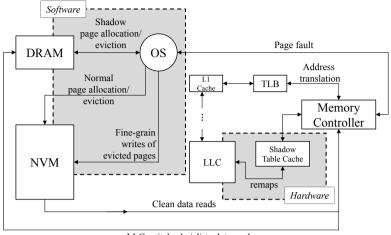

So, we propose a new operating system assisted, LLC writeback scheme to the hybrid main memory. In this technique, the main memory maintains sub-page level data and is able to differentiate between dirty and clean data at the cache line size granularity. The key mechanism is that the LLC always writes back to the DRAM partition and LLC fills are always served by the resistive memory partition. This interaction and mapping of sub-page level activity is entirely maintained by the operating system. More details on this work are included in Chapter 4.

#### 1.3.2 Error Management of Hybrid Memories

#### Dynamically Testing Programs for Approximation

With the two techniques mentioned above, the entire software stack is aware of the underlying hybrid memory system. The applications and operating system assists the memory sub-systems to achieve energy efficiency and performance. Hence, the write sensitivity problem of the resistive memories is now acknowledged. Next, would focus on error susceptibility issue of these memories. Resistive memories are exposed to stochastic errors, which are commonplace for the DVS- DVFS based memories too, commonly known as soft-errors. Many researchers have proposed error detection and error correction techniques for reliability against soft-errors. This implicitly assumes a framework that ensures correctness of a program even at the cost of power consumption. In addition, such methods demand high book-keeping overheads. On the flip side, with popularity of high configuration embedded devices such as smartphones and tablets, power constraints in terms of battery usage have become a bottleneck.

Many applications that are usually run on these devices are resilient to errors to some extent. In other words, accuracy of some applications can be relaxed i.e. approximated, if there is a reduction in power consumption as a consequence. In our third work, we propose a framework to analyse a program to extract approximable data which, even if incurs errors, will not lead to catastrophic failure of the application and will produce output within an acceptable quality of service (QoS) band. We propose a dynamic testing framework based on statistical sensitivity analysis which characterizes program data into critical and approximable classes. The approximable data are allocated to the resistive or DVS/DVFS based memories and other data to SRAM/DRAM. The apt usage of energy efficient memories to hold approximated program data reduces the power consumption required to maintain the correctness or mitigate errors. Chapter 5 elaborates on this work in details.

#### Statically Analyzing Programs for Approximation

Dynamic testing frameworks involve computationally intensive algorithms and profiling of applications to characterize approximation spaces in a program. They are based on large search spaces with a goal to find a near-optimal approximation configuration for a given application. The ideal configuration is one that would minimize the energy consumption of the application during runtime with no QoS loss. However, it is a difficult problem and thus, the state-of-the-art solution involves programmer's expertise to manually annotate the applications for possible approximations. Our previous work attempts to alleviate programmer's effort and generates approximation spaces automatically with a penalty of a complex and compute intensive analysis.

In this work, our aim is to statically analyze a program to extract approximations in program variables based on the required correctness (QoS) of the output variable. As a compile time analysis has limited knowledge about program runtime, our ulterior goal is to merely reduce the huge search spaces the dynamic testing based methods incur, by heuristically determining possible approximations. Chapter 6 elaborates on this work in details.

#### 1.4 Thesis Outline

This thesis continues with an extensive study on the related literature and stateof-the-art techniques in Chapter 2. We introduce our first proposal of a static analysis and code generation technique for the deployment of hybrid memories as processor caches in Chapter 3. Further, we propose a system-wide and operating system assisted framework to support hybrid memories at the main memory level in Chapter 4.

After the previous two proposals to solve the write sensitivity of the hybrid memories, in Chapter 5, we propose a solution to mitigate the error susceptibility issue of energy efficient memories. We continue by elaborating on the limitations of the proposed technique and thereby, proposing a complementary static analysis in Chapter 6. Finally, the thesis concludes in Chapter 7.

### Chapter 2

## **Background & Related Works**

In this chapter, we would elucidate on the existing literature and researches related to resistive memories and their usage to reduce the energy consumption of computer systems. First, we would start with a short description on the device level details of resistive memories followed by various schemes to deploy them in the current memory hierarchy.

#### 2.1 Resistive Memories

Resistive memories are *memristor* [2] based non-volatile memories. Recent studies [3–7] show that they are promising as next generation alternatives to SRAM and DRAM. Resistive memories are inherently energy efficient and provide better performance than other non-volatile memories like NAND Flash etc [8, 9]. One variety of resistive memory, namely, STT-RAM (Spin Torque Transfer Random Access Memory) is a suitable candidate for processor caches and thus, can be an alternative to SRAM [3, 4, 10–12]. STT-RAMs are denser (4x) than SRAM and do not exhibit any leakage current, thus, highly energy efficient. With the increasing demand of many cores and network-on-chip architectures, denser and power efficient caches like STT-RAMs opens a way forward for Moore's scaling. Other works [5–7, 13] suggest that a class of memories, namely PCM (Phase Change Memories) which are similar to the resistive memories and shares all the merits and demerits, are good candidates for main memory as an alternative to DRAM.

However, resistive memories disclose two main drawbacks which hinder them from being adapted in the memory hierarchy in a straight-forward fashion. First, write sensitivity, i.e. the read and write access latencies are different. A memory write requires longer (3x) than a memory read. In addition, write current is higher than read current. Thus, writes to resistive memory devices are expensive and critical to performance and lifetime. Second drawback is error susceptibility of the resistive memories. Smullen et al. reduces the write latency of the resistive memories by introducing a relaxed non-volatility design [14], which exposes the resistive memory cells to stochastic errors. The relaxed non-volatility entails these devices with a retention time - a time interval for which a memory cell can hold the content without being refreshed. Beyond the retention time, the memory cells are susceptible to errors.

#### 2.2 Write Sensitivity of Hybrid Memories

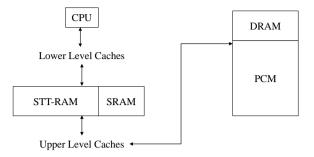

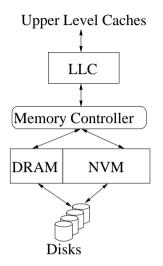

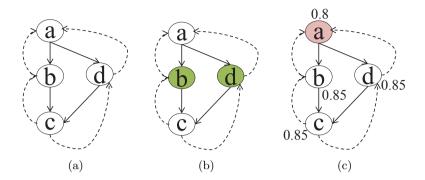

Due to the above idiosyncrasies researchers have proposed a *Hybrid Memory* design which comprises a large partition of STT-RAM/PCM assisted by a small SRAM/DRAM partition to aid the write sensitivity of their counterparts, as shown in Figure 2-1.

Figure 2-1 illustrates a simple hybrid memory hierarchy with hybrid cache(s) and hybrid main memory. There are two main challenges -

• Data Allocation - A random data allocation to the two partitions of hybrid memory may result in unaccounted write operations in the resistive memory. Therefore, it is important to allocate data to the two partitions

Figure 2-1: Simple hybrid memory hierarchy

wisely. Depending on which level of memory hierarchy the hybrid memory is placed in, the data allocation policy will have different implications.

• Write Reduction - In addition, the data allocation strategy should be such that the writes to the resistive memory are minimized. The write reduction is of prime importance as it impacts the performance, writes being 3x slower and also the lifetime of the chip, as the write endurance is lower.

#### 2.2.1 Hybrid Caches

Towards the reduction of writes in hybrid caches comprising SRAM and STT-RAM, *data migration* techniques have been proposed where cache blocks are migrated to SRAM to absorb write accesses, and then moved back to the STT-RAM from where they can service read requests [3, 15]. However, such hardware managed schemes require significant energy overhead for the additional hardware units which can offset the energy gain. Moreover, the migration traffic is a serious concern. Zhou et al. [16] suggested a method to reduce writes by performing a read operation before the write operation. This checks if the write operation is redundant i.e. rewriting the same data. Such redundant writes are terminated and the total number of writes to STT-RAM is reduced. These works require both runtime and hardware support, and thus poses significant overhead. Most of the hybrid memory management techniques are hardware controlled. A few schemes, concentrating on compiler assisted and profiling techniques have been directed at embedded system where the applications are stable and known ahead of time [17–19].

#### Hybrid L1 Cache

Deployment of STT-RAM in the L1 cache is most challenging problem as L1 cache is closest to the processor and hence is time critical [20]. Li et al. [15] introduced one of the first compiler assisted approaches for managing hybrid caches. They assumed a hybrid L1 cache architecture that allows for migration of data from STT-RAM to SRAM to reduce write operations. They presented a novel stack data placement and proposed an arrangement of memory blocks in such a way that reduces migrations because copying data from one cache to another is an expensive operation. Further, they proposed a preferential cache allocation policy that places migration intensive blocks into SRAM to further reduce write accesses to STT-RAM [17].

#### Hybrid L2 & Last Level Cache (LLC)

Mao et al. [21] proposed a novel prefetching technique for STT-RAM based LLC to reduce write accesses due to aggressive prefetching. This method demands extensive hardware support. Chen et al. [19] presented hardware and software cooptimized framework to aid STT-RAM based hybrid L2 caches. They proposed a memory-reuse distance based program analysis that allocates write intensive data in SRAM and read intensive data in STT-RAM. This analysis is supported by a runtime data migration technique using hardware counters for each cache line. Though their framework improved performance and also showed energy efficiency, they are based on the profiling of application. Profiling based methods suffer the well-known shortcomings in usability and scalability.

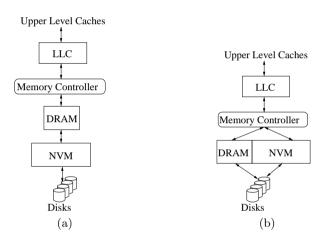

#### 2.2.2 Hybrid Main Memories

As main memories are further away from the processor and pipeline, advantages of using resistive memory (PCM) at the main memory level are enhanced. There are two types of architectures proposed for the hybrid memory as shown in 2-2. In the first type (2-2a), the DRAM is seen as a last level cache of the system. In order to do this, DRAM must be stacked on the CPU chip using 3D die stacking techniques. The second type (??) of hybrid memory has the DRAM occupying a separate address range in the physical address space of the processor. This is the architecture envisioned in our work. The main objective is to enhance the lifetime of PCM and improve the overall system write performance.

Figure 2-2: Different designs of hybrid main memory

For the first type, Qureishi et al. [7] suggested using DRAM as an LLC with a sophisticated cache controller. They also suggested a mechanism to improve the access latency of hybrid main memories that adjusts the scheduling of memory accesses using write pausing [22]. Architectures with DRAM as the LLC, requires on-chip tag stores implemented in SRAM. For very large DRAM caches, the overhead associated with storing the tag array is significant. Dong et al. [23] reduced the size of the tag stores by using very large cache line size in the DRAM cache. Though this reduces the tag store, fragmentation and increased traffic when fetching data from the PCM memory worsens memory bus contention. Loh et al. [24, 25] overcomes the issue of on-chip tag storage by storing both data and tag in the same DRAM row. The latency associated with a tag lookup from the DRAM is reduced through a parallel on chip lookup structure called Missmaps, and a technique called compound access scheduling where data and tag lookup is scheduled side by side in the same memory transaction. Zhou et al. [16] manages the DRAM cache with the aim of reducing writebacks to the PCM memory. This work also distributes writebacks among write queues evenly to spread the writes across PCM, popularly known as *wear levelling*.

Among other works that assume the second type of hybrid memory architecture with a disjoint address space and arranged linearly [5, 26–29], Dhiman et al. [5] proposed a technique based on counting the number of writes to individual PCM frames. Once the count reaches a threshold, the data is moved to a DRAM frame.

Zhang et al. [26] introduced a similar concept of recording the writebacks to individual frames of an on-chip DRAM memory. A multi-queue (MQ) algorithm is used to migrate write intensive pages from PCM to DRAM. Implementing onchip tables to store writes to individual PCM frames is not scalable. The storage overhead associated with storing these tables may not always be realizable for large scale systems with terabytes of PCM memory.

Ramos et al. [27] used another kind of memory controller that implements a modified MQ algorithm to rank page frames. The pages are migrated to DRAM on the basis of the read and write references. The memory controller performs page migration between DRAM and PCM without support from the OS.

A purely OS-based hybrid page management technique implemented in the Linux kernel was explored by Park et al. [28]. The page fault handler is modified to allocate DRAM frames to writable memory regions of the process, while nonwritable regions are allocated PCM frames. Shin et al. [29] made use of a kernel daemon to monitor the write activity to the pages by scanning through the page tables of all the processes running in the system. Energy is saved by powering down blocks of DRAM memory after migrating these pages back to PCM.

## 2.3 Error Susceptibility of Hybrid Memories

Smullen et al. [14] proposed a design of STT-RAM where the non-volatility property is relaxed and the write access is faster as a consequence. Relaxing the non-volatility of the resistive memories, introduces the concept of *Retention Time* - the maximum time period for which a memory cell can keep data alive without a refresh operation. Therefore, relaxed non-volatility designs of STT-RAM and PCM demands a regular refresh mechanism, without which, the memory cells are susceptible to stochastic errors beyond the retention time.

Various authors suggested different STT-RAM and PCM cell structures with different retention times [4, 14, 30], varying from 10ms to  $24.5\mu$ s. Li et al. [31] proposed smart refresh scheme for such STT-RAM based caches, while other works relied on error detection and correction (EDC) to ensure data integrity [32, 33]. Refresh techniques are power hungry and have performance impact. On the other hand, EDC schemes have high book-keeping and space overheads.

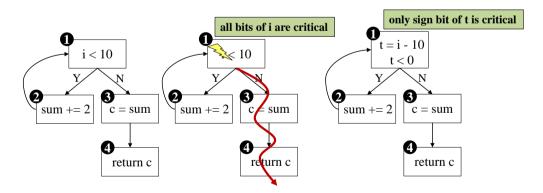

In this thesis, we approach the error susceptibility issue of the resistive memories with a perspective to allow errors resulting in a graceful degradation of application and as a consequence reduce power consumption. This would not only apply to resistive memories, but would also aid other energy-efficient memories such as DVS/DVFS based devices that are error prone. Thus, the abatement of power consumption is twofold. First, using energy-efficient memories without any refresh or EDC mechanisms saves significant overhead. Second, by trading-off accuracy of application, it is possible to achieve better performance which reduces runtime and saves power. In recent literature, such an approach is popularly known as *Approximate Computing*.

## 2.4 Approximate Computing

There are many popular applications in commercial embedded devices that do not require a strict QoS as long as they meet an acceptable threshold [34]. Building on this idea, approximate computing has gained much attention. It allows programs to relax their accuracy in order to save on energy consumption, instead of focusing on mitigating soft-errors in programs [34–36].

#### 2.4.1 Approximation in Programs

Recently there have been wide explorations on how to allow a disciplined approximation to relax the accuracy of a program and reduce energy consumption as a consequence [1, 37–41]. Approximation is achievable at different levels of abstraction such as code approximation, program approximation, approximate computer architectures and device level approximations.

Baek et al. [37] suggested the idea of this trade-off by proposing a loop and function approximation framework. In this, the programmers are expected to provide multiple versions of a function or a loop structure. The framework consists of a calibration that generates different QoS models and allows a graceful QoS loss during runtime to save energy. However, this solution places a demand on the programmer's expertise and involvement. With the popularity of open-source application development for embedded devices, it is generally not feasible to request multiple versions of a code to allow approximate computing. In addition, compiling (or re-compiling, in case of legacy software) a program with extra versions of functions and loops would result in code bloat and larger executables which is not suitable for tight budget and low power devices.

Sampson et al. [1] proposed a type-qualifier based programming paradigm, EnerJ, to facilitate approximation of program data. This ensures safety in terms of maintaining a distinction between approximate and precise computation of program data. Only with explicit programmer's endorsements, a conversion from precise to approximate or vice-versa is allowed. It provides an exclusive compiler to generate instructions for the underlying dynamic voltage scaling-based hardware called "Truffle" to switch between high and low power modes [39].

Carbin et al. [42] proposed a technique that classifies code regions into approximable and critical by a training method that uses fuzzed input data. Depending on the program path taken by different inputs, it is able to identify critical program regions and approximable regions. In other works, they propose program transformations and code generation techniques to allow approximate computation. The motivation in these works is to save computation power i.e. loop iterations, floating point operations etc. One such method is known as "loop perforation" where loop iterations are skipped in order to save computation which results in approximation in the output [43]. Misailovic et al. [44, 45] proposes probabilistic accuracy tests to allow for program level approximations. However, in most of the above mentioned works, one common drawback is the programmer's involvement, and the lack of scalability.

Shafique et al. [46] proposes a technique to discover errors that are masked by program flow and operations on data. This indicates an inherent error resilience and approximation capability of a program. However, this is based on static code analysis and thus is not accurate as a whole program optimization framework. Error concerning only statically allocated data and compile-time inferable computation is exposed to this technique. Program data that are dynamically allocated or are influenced by runtime computations are hard to analyse.

#### 2.4.2 Approximation in Hardware Devices

Approximation can be introduced in both the hardware and software stack. There are many other works investigating and designing architectural or device level approximation infrastructures [47–49]. Chippa et al. [50] presented a work on characterizing error resilience in applications based on approximate adders. They also proposed "Impact", an approximate adder circuit that saves energy by approximating addition operations [51]. Many other designs for approximate adders have been proposed thereafter [52–56]. Liu et al. [40] proposed a DRAM refresh mechanism that protects critical data and approximates non-critical data to save refresh energy. Kahng et al. [52] propose an accuracy-configurable adder which can adaptively adjust during runtime based on the required accuracy. Memories that can control power supply at the bit level are widely explored [57– 59]. For such memories, it is imperative to know how many bits of a variable are approximable. Finally, Nesenbergs et al. [60] proposed an approximate comparator that runs on low power and reduces the cost of comparisons which are otherwise highly expensive.

## Chapter 3

# Compilation Framework for Resistive Hybrid Caches

In this chapter, we introduce a compiler framework to attenuate the write impact on hybrid memories. Specifically, we would propose a new virtual memory layout which is aware of the hybrid memory architectures at the processor cache level. We propose analyses targeted towards both statically and dynamically allocated data and generate program executable with new virtual addresses according to their memory access behaviour. Such an approach is able to influence all memory devices in the memory hierarchy simultaneously.

## 3.1 Motivation

Virtual memory is the key to managing multiple processes efficiently with the limits of the physical memory of a system. Virtual memory allows programs to execute with memory footprints that are larger than the available physical memory. However, the classic virtual memory is designed with the assumption that the underlying cache hierarchy is built using fast SRAM and therefore it is not aware of write sensitivity issue of hybrid memories.

From systems' perspective, allocating data without differentiating between read and write accesses, is detrimental to the hybrid memories. Unmonitored and excessive write operations can impede performance, and reduce the lifetime of the on-chip hybrid caches and hence of the processors [9, 11]. So, it is essential to judiciously manage memory accesses based on their access patterns and access types in order to achieve a balance between energy efficiency and performance. Recent works have explored novel data allocation techniques towards efficient utilization of the hybrid caches. Chen et al. [19] proposes a hardware-software co-optimized framework to allocate data to hybrid caches. Their compile-time analysis produces hints for each instruction that influences data placement in the partitions. The hardware support ensures that write intensive data is migrated from STT-RAM to SRAM to ameliorate the write endurance issue. Li et al. [17] proposed a new stack layout to optimize data allocation to the hybrid caches. They present a specialized address generation policy that reduces data migration between the two partitions, while, at the same time, reducing write operations to STT-RAM. Their technique can be applied to global data too. However, all the techniques are specialized for a particular cache level and architecture. Most of the methods have hardware overheads. These partial approaches will result in even higher overheads when STT-RAM based hybrid caches are adapted at all levels. Worse, it would lead to mutual interference between the different cache levels, subsequently resulting in impaired efficiency.

For example, in the algorithm by Chen et al. [19], memory blocks with a large memory reuse distance are assumed to incur write operations to L2 due to L1 capacity miss. Based on such heuristics, every memory block is provided with hints to be considered while placing the cache block in L2 SRAM partition or STT-RAM partition. Suppose we also have a hybrid L1 that uses the other algorithm [15] which places read and write intensive blocks in different localities if they are in the stack region. The data locality, then, becomes a function of the type of memory access and not temporal relationships. In such a setup of L1 and L2 caches, a large memory reuse distance for a L1 cache block does not necessarily result in capacity misses. Therefore the assumption for algorithm for L2 cache management is weakening significantly. These two cache management techniques for L1 and L2 will fail to cooperate with each other, and may in fact be detrimental to one another.

## 3.2 Our Proposal

All the works proposed in literature target a specific level in the cache hierarchy. Many are profile based program analysis with hardware support to manage the cache blocks in accordance with the program behaviour obtained. Such hardware supports and program analyses are not scalable to the entire memory hierarchy. There is, therefore, a need for a holistic framework that manages the virtual memory area of a process to aid hybrid memories at any level of the memory hierarchy. The cache hierarchy is generally accessed using physical addresses that are computed from virtual addresses using specialized hardware. Virtual memory layout, therefore, influences optimized cache management. As the underlying memory technology changes, a shift in virtual memory design is essential for maintaining performance and energy efficiency.

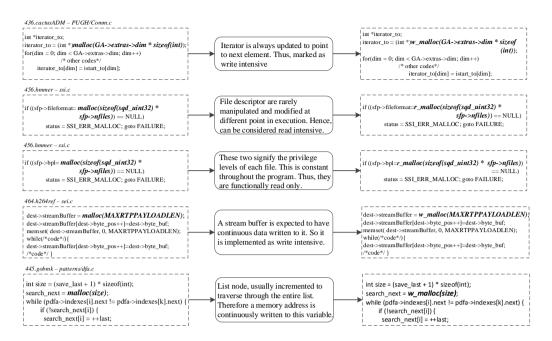

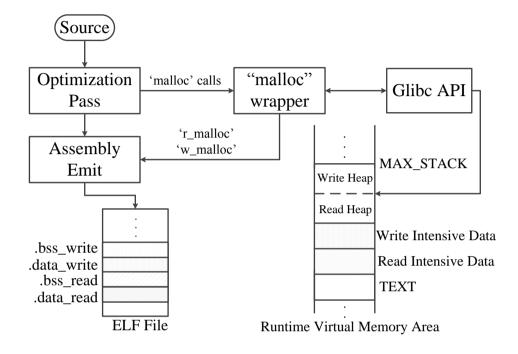

We propose a new virtual memory design EnVM, which is aware of hybrid caches. The revised virtual memory design is able to influence data allocation across all the levels of memory hierarchy seamlessly. EnVM consists of a static analysis that generates virtual addresses for statically allocated data used for virtual memory layout of the global data and stack. The static analysis is able to discern the memory access affinity for each data and generates virtual address accordingly. The key idea is to enhance locality of data based on their memory access tendency i.e. read or write intensive. For dynamically allocated memory i.e. heap area in the virtual address space, EnVM makes use of modified system libraries. Our new dynamic memory allocator interface is exposed to the programmer and provides the programmer with distinctive functions for read intensive and write intensive data structures. Virtual address generation for heap accesses is performed at runtime by the operating system. Our modified kernel supports the system libraries to manage the new heap area of virtual address space. The virtual to physical address translation is intersected by a group of conventional segment registers to facilitate data allocation to the hybrid memory partitions i.e. SRAM and STT-RAM.

There are several advantages of EnVM. First, it is able to influence the data allocation across all levels of memory hierarchy without requiring specialized hardware at each level. This helps in easier adoption and scalability to deeper cache hierarchies. Secondly, EnVM provides a holistic design for both statically allocated and dynamically allocated data, spanning the entire virtual memory address space. Finally, our experiments show that EnVM eliminates the need for data migration as the write operations are optimized and filtered out to SRAM. Although, cache management can be further optimized by some form of migration, EnVM serves as the base virtual memory for the new memory technologies. We implemented EnVM using the GCC compiler and GNU malloc library. In order to quantify the gain, we implemented a hybrid cache model [61] and compare EnVM with two existing works on software assisted data allocation for hybrid caches [17, 19]. Details of evaluation and experimental results are presented in Section 3.6.

Summarizing the contributions of this work -

- We propose EnVM, the first virtual memory design that is aware of memory hierarchies built using the new memory technologies. EnVM provides an uniform data allocation mechanism to all the levels of memory hierarchy. This is an important step towards an *all hybrid memory* based memory hierarchy.

- EnVM provides a novel static code analysis that can identify and allocate data with read and write affinity separately in the virtual address space. It enables data allocation accordingly and reduces write operations to STT-RAM.

- We propose a new programmer's interface to be able to allocate read and write intensive heap memory exclusively during runtime with the help of optimized system libraries and the operating system.

- EnVM is the only virtual memory design that enables data allocation to hybrid caches built with SRAM and STT-RAMs. It utilizes existing hardware and advocates migration-less hybrid cache design.

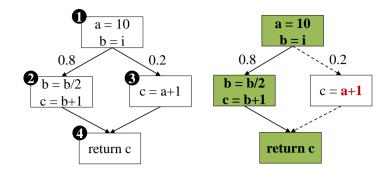

## 3.3 EnVM

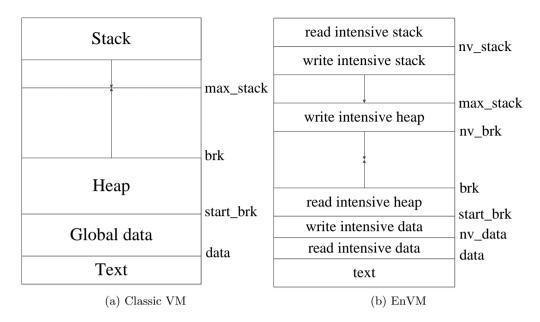

In this section, we will describe EnVM and its functionality in detail. We will first describe EnVM's new memory layout followed by the data management techniques for both statically allocated and dynamically allocated data. Traditionally, the virtual memory space is divided in logical segments as shown in Figure 3-1a. EnVM contains fine-grained logical segments that are based on the memory access affinity of the memory objects as shown in Figure 3-1b. In other words, memory objects that exhibit read affinity are placed separately from those that show write affinity.

Figure 3-1: Existing and proposed virtual memory design for hybrid memories.

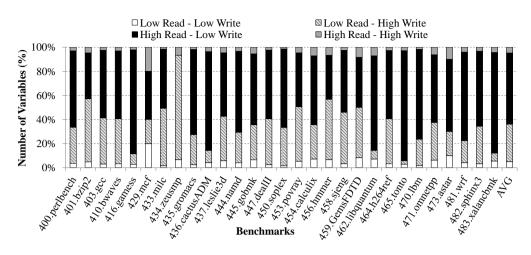

In order to examine the nature of programs, we examined benchmarks from SPEC2006 [62] for the total proportion of variables showing read and/or write affinity in each application. The results presented in Figure 3-2, shows that memory objects that shows affinity to both read and write operations are less in proportion. In most of the benchmarks, only 5% of the variables show a high read and write affinity, where as 90% variables (on average) shows affinity towards either read or write accesses. On an average, 59% of variables show read affinity over write and 31% show write affinity over read. Thus, it is viable to allocate these two classes to the STT-RAM and SRAM respectively. The premise of this work rests on this aspect.

In EnVM, the read and write intensive groups are separated by segment boundaries known to the operating system (OS). At runtime, the OS manages the data allocation to underlying hybrid memories using the segment boundaries. This is analogous to managing text segment and non-text segment for instruction caches and data caches separately.

Figure 3-2: Percentage of variables in a program with certain memory access affinity.

#### 3.3.1 Statically Allocated Data

Runtime behaviour of statically allocated data is possible to analyze at compiletime. To arrange the global and stack data in EnVM, we propose a new static code analysis for placing variables according to their memory access affinity. The analysis we present here estimates the number of reads and writes of each program variable. Unlike profiling techniques, it path insensitive, and therefore does not focus only on the frequently executed program path(s). The analysis is a dataflow analysis (DFA) problem. The DFA is applied as an interprocedural analysis on the control flow graph of the program.

**Definition 3.3.1** (Abstract Domain). The abstract domain of the analysis is a tuple containing an identifier for the variable, it's read and write count represented as (V, R, W), where  $V \in$  set of all variables in the program, R and  $W \in \mathbb{N}$ . The domain forms a lattice,  $((V, \mathbb{N}, \mathbb{N}) \cup \{\top\}, \sqsubseteq_F)$ , where  $\top$  is the top element and  $\sqsubseteq_F$  is the partial order defined as

$$(X \sqsubseteq_F Y)$$

iff  $(X(V) \sqsubseteq_{RW} Y(V))$  for each variable  $V_i \in V$  (3.1)

$$(V_i \sqsubseteq_{RW} V_j) \text{ iff } (R_i \le R_j) \land (W_i \le W_j)$$

$$(3.2)$$

where  $R_i, W_i, R_j$  and  $W_j$  denotes the read and write counts for variables  $V_i$  and  $V_j$  respectively.

The partial order defined above is significant for the termination of the dataflow analysis. It also plays an important role in analyzing branches and joins in the control flow graph. The partial ordering rule says that two variables are partially ordered if and only if both the read and write counts are in natural order. For example, if the read count of one variable is higher than that of the other but opposite for the write count, then the analysis cannot determine any partial order between the two variables.

As the DFA we propose is counting based, the partial order between different variables do not influence the outcome of the analysis. However, the partial ordering between instances of the same variable is important during branch joins. This phenomenon is described later with the discussion of *meet* operator. Each instruction i, in a basic block is passed through two *transfer functions*, F and B, for forward and back edges, respectively.

**Definition 3.3.2** (Transfer Function). At each program point, the set of tuples (V, R, W), denoted as X, and the transfer function for the current instruction i, is defined as

$$F_i(X) = Gen[i] \sqcup Probe_i(X) \tag{3.3}$$

The function Gen[i] discovers a variable from the instruction *i*, and the function  $Probe_i(X)$  examines all the elements of the set X and updates it according to the rule below -

$$\forall V' \in X, where V' = (V, R, W)$$

$$R = R + 1 \text{ if } i \text{ reads } V$$

$$W = W + 1 \text{ if } i \text{ writes } V$$

(3.4)

The key idea is to examine whether an instruction i has a read operation on variable V, then read counter is incremented, and if i has a write operation on V, the write counter is incremented. For all back edges in the CFG, most likely a loop edge back to the start of the loop, we have a transfer function  $B_i(X)$ . For an instruction i succeeding instruction j through a back edge, all variables  $V \in$  instructions between j and i, R = R + k and W = W + k, where k is a static loop bound [63]. This will have a similar effect as going through the loop instructions k times. When resolving branches and  $\phi$  functions, we apply the meet operator  $\sqcup$ .

**Definition 3.3.3** (Meet Operator). The meet operator  $\sqcup$  is applied when two basic blocks have a common successor basic block. The OUT information from the two parent basic blocks are unified using the meet operator to form the IN information of the successor. It is defined as

$$(V_{i}, R_{i}, W_{i}) \sqcup (V_{j}, R_{j}, W_{j}) = \begin{cases} \top , if(V_{i} = V_{j}) \land (V_{i} \not\sqsubseteq V_{j}) \\ (V_{i}, \max(R_{i}, R_{j}), \max(W_{i}, W_{j})) \\ , if(V_{i} = V_{j}) \land (V_{i} \sqsubseteq V_{j}) \\ \{(V_{i}, R_{i}, W_{i}) \cup (V_{j}, R_{j}, W_{j})\} \\ , if(V_{i} \neq V_{j}) \end{cases}$$

(3.5)

The above rule says that when different instances of a variable along different paths are not in partial order then it is assigned the  $\top$  element. Elaborately, for the same variable, traversing different paths, we consider the path with maximum of the read and write counts accrued among all paths. However, if the partial order is not maintained, that means, the read and write counts attains maximum value in different paths, it is marked as inconclusible. For example, if a variable has a read count that is more than the write count for one path, but it is the other way around for another path, then we assign  $\top$  to the variable. This means that