## SOFT-SWITCHING CURRENT-FED POWER CONVERTERS FOR LOW VOLTAGE HIGH CURRENT APPLICATIONS

### PAN XUEWEI

(B. Eng. UESTC, P.R. China)

### A THESIS SUBMITTED

### FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

## DEPARTMENT OF ELECTRICAL & COMPUTER ENGINEERING

NATIONAL UNIVERSITY OF SINGAPORE

2014

### DECLARATION

I hereby declare that this thesis is my original work and it has been written by me in its entirety.

I have duly acknowledged all the sources of information which have been used in the thesis.

This thesis has also not been submitted for any degree in any university previously.

Pan Xuewei

Pan Xuewei 24 June 2014

.

Acknowledgement

## Acknowledgement

I would like to express my deepest gratitude to my supervisor Dr. Akshay K. Rathore, for his invaluable guidance, continuous encouragement, support over the years of my doctoral study and research. His passion and enthusiasm for research is a source of inspiration to me. As his first PhD student, I am always appreciating the time and energy he spent on me.

I am also grateful to the lab officers Mr. Teo Thiam Teck, Mr. Woo Ying Chee, Mr.Chandra, for their kind help. Special thanks to Mr. Abdul Jalil Bin Din for his prompt PCB fabrication services

I would like to thank my colleagues and friends, Ms. Satarupa Bal, Ms. Radha Sree Krishna Moorthy, Mr. Ravi Kiran Surapaneni, Mr. Devendra Patil, Mr. Jeevan Adhikari, Dr. Huang Huolin, Dr. Li Yanlin, Dr. Yu Xiaoxiao, Dr. Hoang Duc Chinh, Dr. Souvik Dasgupta, Dr. Sangit Sasidhar, Dr. Parikshit Yadav, Ms. Li Yulin, Mr. Li Qifan, Ms. Zhang Yuan, Mr. Gong Feng, Mr. Tang Tao, Mr. Mao Zhenyu, Mr. Fan Zhen, Mr. Shen Chao, Ms. Qing He, for their friendship and accompany. The joy we have shared and the memories we have made are the gifts that will be cherished forever. My life in NUS was made pleasant by them. Special thanks to my friend, Dr. Prasanna for his patient guidance, constant encouragement, and valuable suggestions. The things I leant from him are far beyond the knowledge of power electronics. I am also deeply influenced by his wisdom, unique personality, and life attitude.

I am grateful to my parents Mr. Pan Guiyang and Ms. He Demei for supporting me to follow my dreams, encouraging, and loving me all the time.

i

## **Table of Contents**

| Ac        | knowledgementi                                                                                      |

|-----------|-----------------------------------------------------------------------------------------------------|

| Ta        | ble of Contentsii                                                                                   |

| Su        | mmaryv                                                                                              |

| Lis       | t of Tables viii                                                                                    |

| Lis       | t of Figuresiix                                                                                     |

| Lis       | t of Acronymsxvii                                                                                   |

| Chapter 1 |                                                                                                     |

| Backgrou  | nd and Problem Definition1                                                                          |

| 1.1       | Background1                                                                                         |

| 1.2       | The Opportunities and Challenges of Fuel Cell Vehicles                                              |

| 1.3       | Power Conditioning System Architecture of Fuel Cell Vehicles9                                       |

| 1.4       | Problem Definitions and Research Objectives14                                                       |

| 1.5       | Thesis Contributions                                                                                |

| 1.6       | Thesis Outline                                                                                      |

| Chapter 2 |                                                                                                     |

|           | ng Inductance Assisted Extended Range Soft-switching Three-phase<br>Current-fed DC/DC Converter     |

| 2.1       | Introduction                                                                                        |

| 2.2       | Fuel Cell Characteristics and Properties                                                            |

| 2.3       | A Brief Review of High Frequency Transformer Isolated DC/DC<br>Converter Topologies                 |

| 2         | 2.3.1 Voltage-fed PWM DC/DC Converter                                                               |

| 2         | 2.3.2 Current-fed PWM DC/DC Converter                                                               |

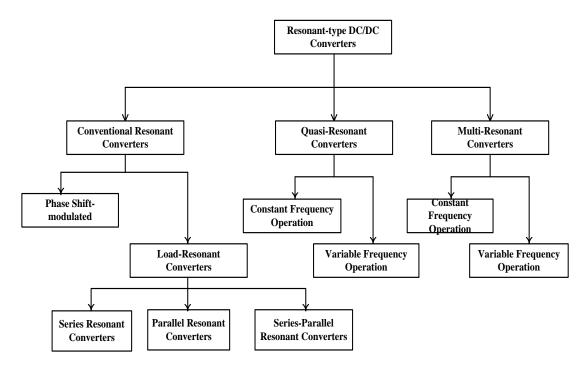

| 2         | 2.3.3 Resonant-type DC/DC Converter (Voltage-fed and Current-fed)36                                 |

| 2         | 2.3.4 Problem Definition                                                                            |

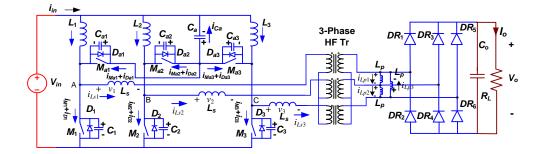

| 2.4       | Proposed Three-phase AC link Current-sharing Active-clamped<br>Current-fed Isolated DC/DC Converter |

| 2.5       | Operation and Analysis of the Converter41                                                           |

| 2         | 2.5.1 Discontinuous Auxiliary Clamp Capacitor Current                                               |

| 2         | 2.5.2 Continuous Auxiliary Clamp Capacitor Current                                                  |

| 2.6       | Design of the Converter                                                                             |

| 2.7       | Simulation and Experimental Results                                                                 |

| 2.8       | Summary and Conclusions70                                                                                    |

|-----------|--------------------------------------------------------------------------------------------------------------|

| Chapter 3 |                                                                                                              |

|           | Clamped Zero Current Commutated Soft-switching Current-fed<br>re Bridge (CFDAB) DC/DC Converter              |

| 3.1       | Introduction72                                                                                               |

| 3.2       | Survey of Bidirectional DC/DC Converter74                                                                    |

| 3.3       | Proposed Naturally Clamped Zero Current Commutated Current-fed<br>Dual Active Bridge (CFDAB) DC/DC Converter |

| 3.4       | Operation and Analysis of the Converter                                                                      |

| 3.5       | Design of the Converter                                                                                      |

| 3.6       | Simulation and Experimental Results92                                                                        |

| 3         | 8.6.1. Boost Mode (Discharging Mode)                                                                         |

| 3         | 8.6.2 Buck Mode (Charging Mode)                                                                              |

| 3.7       | Summary and Conclusions102                                                                                   |

| Chapter 4 |                                                                                                              |

|           | al Analysis and Control Design of Zero Current Commutated<br>ed Dual Active Bridge (CFDAB) DC/DC Converter   |

| 4.1       | Introduction                                                                                                 |

| 4.2       | Small Signal Modeling of the Converter Using State-space Averaging                                           |

| 4.3       | Controller Design: Two Loop Average Current Control114                                                       |

| 4         | .3.1 Design of Current Control Loop:                                                                         |

| 4         | .3.2 Voltage Control Loop:                                                                                   |

| 4.4       | Simulation and Experimental Results                                                                          |

| 4.5       | Summary and Conclusions                                                                                      |

| Chapter 5 |                                                                                                              |

|           | Multi-cell Current-fed Full-bridge Voltage Doubler (CF-FBVD)<br>nal DC/DC Converter                          |

| 5.1       | Introduction127                                                                                              |

| 5.2       | Study of Bidirectional DC/DC Converters128                                                                   |

|           | 5.2.1 Voltage-fed Dual Active Full-Bridge (VF-DAB) DC/DC Converter                                           |

| 5         | 5.2.2 Current-fed Dual Active Half-Bridge (CF-DAHB) DC/DC                                                    |

| (         | Converter                                                                                                    |

|             | 2.3 Current-fed Dual Active Full-Bridge (CF-DAFB) DC/DC converter with Active-clamp                            |

|-------------|----------------------------------------------------------------------------------------------------------------|

|             | .2.4 Secondary Modulation Based Current-fed Full-Bridge Voltage<br>Poubler (CF-FBVD)                           |

| 5           | .2.5 Comparison and Selection                                                                                  |

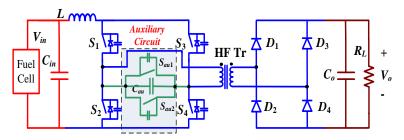

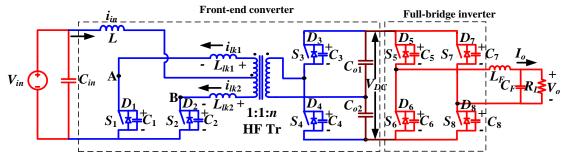

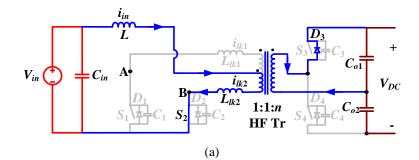

| 5.3         | Proposed Modular Multi-cell Current-fed Full-bridge Voltage Doubler<br>(CF-FBVD) Bidirectional DC/DC Converter |

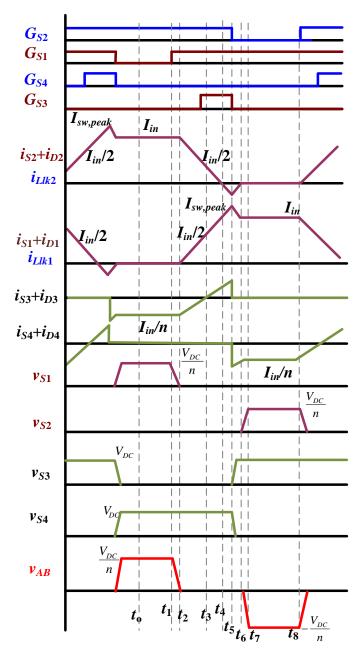

| 5.4         | Operation and Analysis of the Converter140                                                                     |

| 5.5         | Design of the Converter147                                                                                     |

| 5.6         | Simulation and Experimental Results152                                                                         |

| 5.7         | Summary and Conclusions                                                                                        |

| Chapter 6   |                                                                                                                |

|             | d Three-Phase Bidirectional DC/DC Converter with Natural<br>and Zero Current Commutation165                    |

| 6.1         | Introduction165                                                                                                |

| 6.2         | Comparison of Three Current-fed Converters                                                                     |

| 6.3         | Operation and Analysis of the Converter171                                                                     |

| 6.4         | Design of the Converter                                                                                        |

| 6.5         | Simulation and Experimental Results                                                                            |

| 6           | .5.1 Boost Mode (Discharging Mode)                                                                             |

| 6           | .5.2 Buck Mode (Charging Mode)192                                                                              |

| 6.6         | Summary and Conclusions193                                                                                     |

| Chapter 7   |                                                                                                                |

| Conclusion  | as and Suggestions for Future Work195                                                                          |

| 7.1         | Introduction195                                                                                                |

| 7.2         | Conclusions                                                                                                    |

| 7.3         | Future Work                                                                                                    |

| References  |                                                                                                                |

| Appendice   | <b>s</b> 214                                                                                                   |

| Appendix    | <b>A</b> 214                                                                                                   |

| Appendix    | <b>B</b> 233                                                                                                   |

| Appendix    | C238                                                                                                           |

| List of Pub | lications                                                                                                      |

Summary

## **Summary**

This thesis presents novel current-fed soft-switching topologies and modulation techniques for low voltage high current applications such as solar photovoltaic (PV) and fuel cell based utility interactive inverters and fuel cell vehicles (FCVs). Low voltage energy storage system (ESS) in microgrid, electric vehicles (EVs), uninterruptible power supply (UPS), and DC microgrid are also within the scope of low voltage high current applications. The main objective of this thesis is to develop high-frequency soft-switching current-fed power converters for low voltage high current applications. Fuel cell is a typical low voltage high current source of energy. Fuel cell inverters provide continuous and secured output in all seasons. FCVs offer zero emission, satisfied driving range, and short refueling time, and therefore FCVs exhibit significant potential for transportation. In this thesis, the specifications are taken for FCV but the proposed topologies, modulation techniques, control design, and the demonstrated results are suitable for any general applications of low voltage high current such as PV/fuel cell based utility interactive inverters, UPS, microgrid, V2G, and energy storage. Similar merits and performance are expected.

This thesis first analyzes various propulsion system architectures and power conditioning systems (PCS) for FCVs. Among all aspects of PCS, the main focus of the thesis is on the front-end DC/DC converter interfacing the fuel cell stack and high voltage dc bus, and bidirectional DC/DC converter connecting the energy storage system (ESS) and high voltage dc bus. High voltage dc bus is connected to traction inverter.

v

Summary

The fuel cell stack voltage and generated power vary mainly with fuel flow rate. The front-end DC/DC converter is employed to mitigate such variations, to stabilize output voltage and to control power flow. To achieve high density power converters, high frequency modulation and soft-switching of semiconductor devices is desired. However, to maintain soft-switching over wide variation in source voltage and current while expecting high performance has been a challenge. A magnetizing inductance assisted extended softswitching three-phase AC link current-fed DC/DC converter is proposed, analyzed, and designed. Simulation and experimental results of the converter are presented. The proposed converter maintained zero voltage soft-switching (ZVS) of all semiconductor devices over wide range of load (full load till 10% load) and source voltage (22V and 41V).

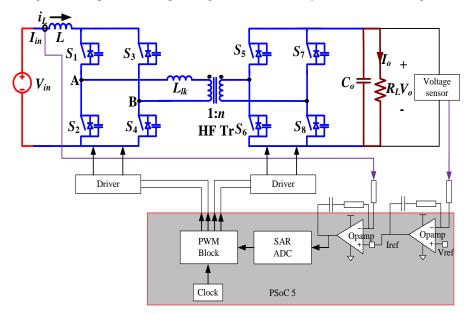

To improve the fuel economy and transient performance of FCVs, auxiliary energy storage devices such as battery or supercapacitor are usually utilized. A bidirectional DC/DC converter is needed to actively control power flow between the energy storage device and the dc bus. A novel naturally clamped zero current commutated soft-switching bidirectional current-fed dual active bridge (CFDAB) isolated DC/DC converter is proposed in this thesis. Proposed secondary modulation technique naturally clamps the voltage across the low voltage side current-fed devices with zero current commutation (ZCC) eliminating the necessity for so far traditionally adopted active-clamp circuit or passive snubbers. Soft-switching is achieved for both direction of power transfer. For the CFDAB converter, small signal model and relevant transfer functions are derived. Two-loop controller is designed and implemented on mixed signal processor Cypress PSoC 5. Simulation and experimental results

vi

#### Summary

are provided to demonstrate the dynamic performance with fast response and small voltage undershoot/overshoot.

Modular multi-cell current-fed full-bridge voltage doubler (CF-FBVD) is proposed for high power application. Parallel Input Series Output (PISO) configuration is employed for interleaving two cells with phase-shifted modulation between them. The input and output ripples were much reduced due to interleaved cells.

The proposed secondary modulation technique is also modified and applied to the current-fed three-phase topology. A trade-off among power transferring capacity, device count, cost, and efficiency is obtained. The input and output filter requirements are much reduced with the interleaved and three-phase design.

## **List of Tables**

| Table No.                                                                                                                                                           | Page No.   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Table 2.1: The comparison of three different voltage-fed DC/DC conv                                                                                                 | verters 27 |

| Table 2.2: Turn-on devices during different intervals of case B                                                                                                     | 53         |

| Table 2.3: Comparison of components' ratings.                                                                                                                       | 59         |

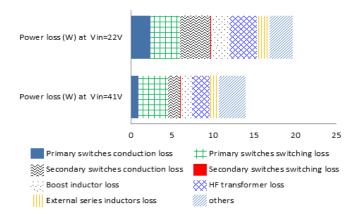

| Table 3.1: Major components' parameters of experimental prototype.                                                                                                  |            |

| Table 3.2: Loss distribution estimation from the loss model                                                                                                         | 102        |

| Table 5.1: Comparison of four bidirectional DC/DC converter topolog<br>= 12 V and full load (1 kW)                                                                  |            |

| Table 5.2: Comparison of switch voltage/current stress for the six configurations under the same output power                                                       | 139        |

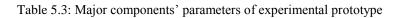

| Table 5.3: Major components' parameters of experimental prototype.                                                                                                  | 156        |

| Table 6.1: Comparison of parameters between three-phase active-clar ZVS, single-phase ZCS, and proposed ZCS current-fed topologie                                   | 1          |

| Table 6.2: Comparison of losses and efficiency between three-phase a clamped ZVS, single-phase ZCS, and proposed ZCS current-fed topologies at full load condition. |            |

| Table 6.3: Current and voltage stress of major components                                                                                                           |            |

| Figure No.                                                                                                                                                                                      | Page No. |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Fig. 1.1. World energy consumption growth [1].                                                                                                                                                  | 2        |

| Fig. 1.2. US energy consumption by sector in 2009[2-3]                                                                                                                                          | 2        |

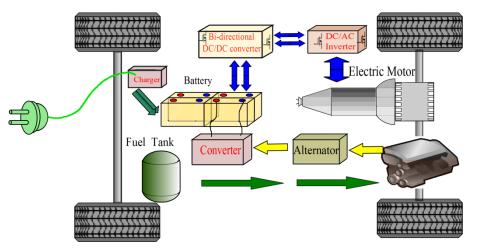

| Fig. 1.3. Architecture of a BEV.                                                                                                                                                                | 4        |

| Fig. 1.4. Architecture of a HEV                                                                                                                                                                 | 5        |

| Fig. 1.5. Architecture of a PHEV                                                                                                                                                                | 5        |

| Fig. 1.6. Architecture of a FCV.                                                                                                                                                                | 5        |

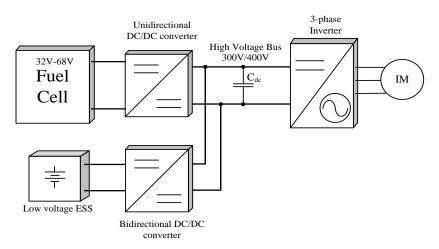

| Fig. 1.7. Type 1, power system architecture of FCV with variable high dc bus.                                                                                                                   |          |

| Fig. 1.8. Type 2, power system architecture of FCV with variable low dc bus.                                                                                                                    |          |

| Fig. 1.9. Type 3, power system architecture of FCV with fixed high vo<br>bus.                                                                                                                   | -        |

| Fig. 1.10. Type 4, power system architecture of FCV with both fixed l voltage and fixed high voltage dc bus.                                                                                    |          |

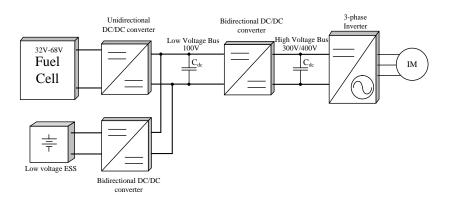

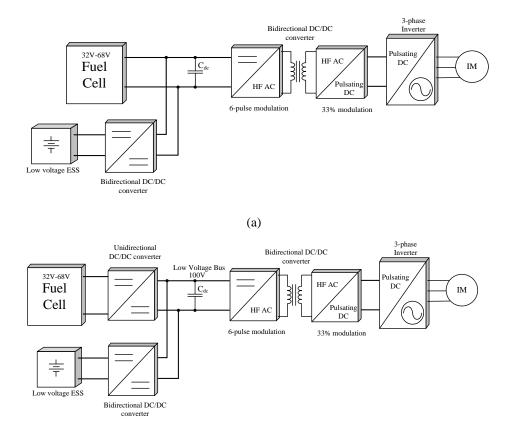

| Fig. 1.11. Type 5, modified power system architecture of FCV. (a) Va<br>low voltage dc bus and high voltage pulsating dc bus, (b) fixed lo<br>voltage dc-link and high voltage pulsating dc bus | OW       |

| Fig. 2.1. PEM fuel cell diagram.                                                                                                                                                                |          |

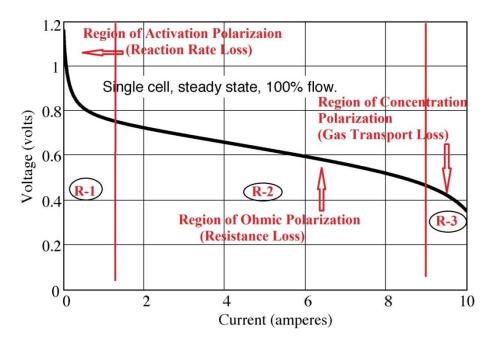

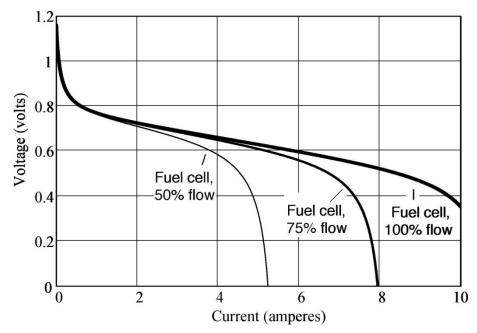

| Fig. 2.2. Fuel cell voltage-current characteristic [42]                                                                                                                                         |          |

| Fig. 2.3. Fuel cell voltage-current characteristic at different fuel flow                                                                                                                       | [42] 23  |

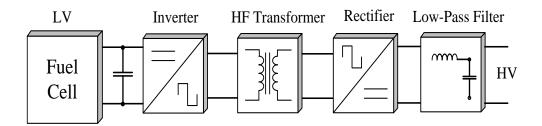

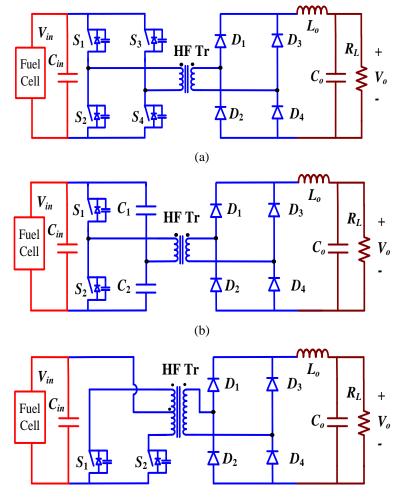

| Fig. 2.4. Configuration of voltage-fed HF transformer isolated DC/DC converter for low voltage high current applications.                                                                       |          |

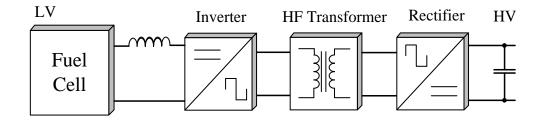

| Fig. 2.5. Configuration of current-fed HF transformer isolated DC/DC converter for low voltage high current applications                                                                        |          |

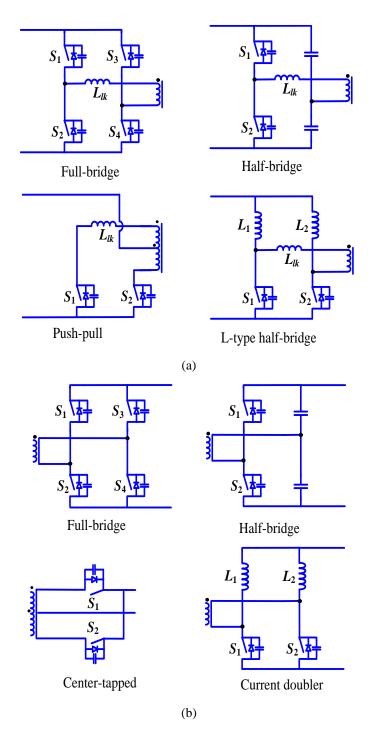

| Fig. | 2.6. Voltage-fed HF transformer isolated DC/DC converters. (a) Full-<br>bridge converter (b) half-bridge converter (c) push-pull converter                                                                  | 27 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

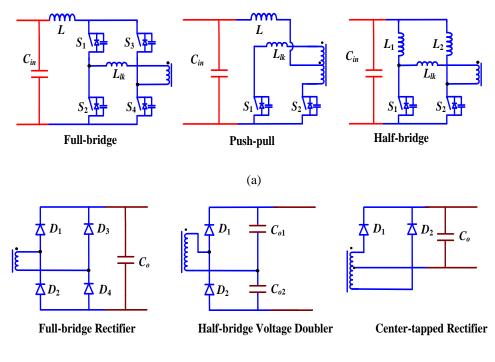

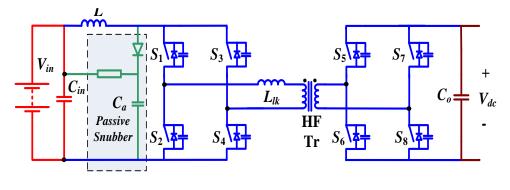

| Fig. | 2.7. Conventional current-fed PWM DC/DC converter topologies. (a)<br>Three typical topologies for the low voltage inverter stage. (b) Three<br>typical topologies for the high voltage side rectifier stage | 51 |

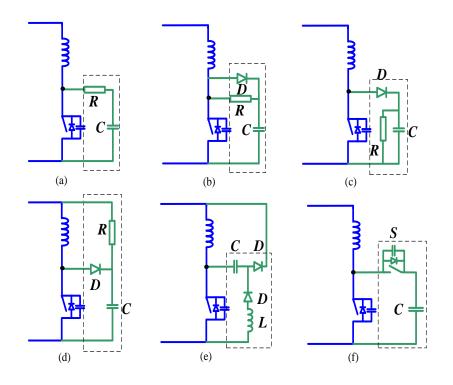

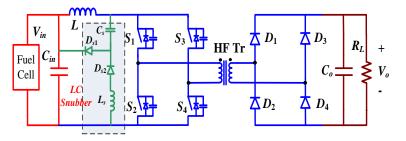

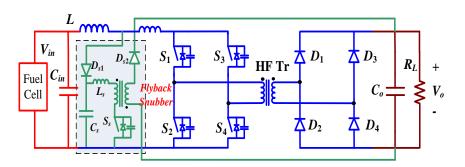

| Fig. | 2.8. Snubbers for suppressing the voltage spike: (a) Dissipative RC snubber, (b)(c)(d) Dissipative RCD snubber,(e) Non-dissipative energy recovery LC snubber, and (f) active-clamping snubber              | 51 |

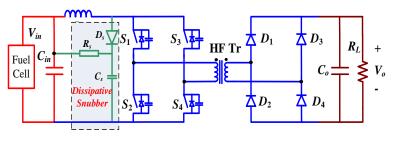

| Fig. | 2.9. Current-fed full-bridge DC/DC converter employing dissipative snubbers                                                                                                                                 | 2  |

| Fig. | 2.10. Current-fed full-bridge DC/DC converter employing non-dissipative snubbers                                                                                                                            | 52 |

| Fig. | 2.11. Current-fed full-bridge DC/DC converter with an auxiliary flyback snubber                                                                                                                             | 52 |

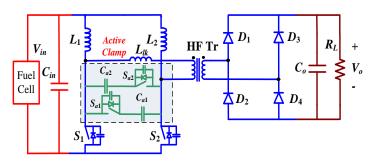

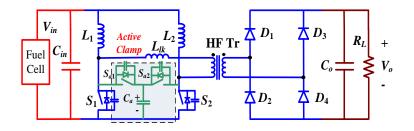

| Fig. | 2.12. Current-fed L-type half-bridge DC/DC converters with three different types of active-clamping circuits                                                                                                | 64 |

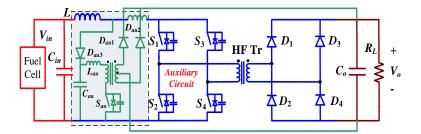

| Fig. | 2.13. Current-fed ZCS full-bridge DC/DC converter with parallel auxiliary circuit                                                                                                                           | 5  |

| Fig. | 2.14. Current-fed ZCS full-bridge DC/DC converter with current-<br>blocking diodes                                                                                                                          | 5  |

| Fig. | 2.15. Current-fed ZCS full-bridge DC/DC converter with snubber energy 3                                                                                                                                     | 6  |

| Fig. | 2.16. Current-fed ZCS full-bridge DC/DC converter with an external boost converter                                                                                                                          | 6  |

| Fig. | 2.17. Classification of resonant-type DC/DC converter [85]                                                                                                                                                  | 7  |

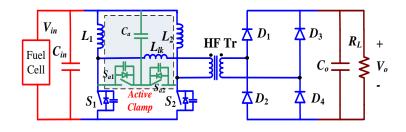

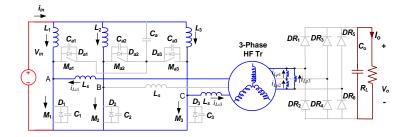

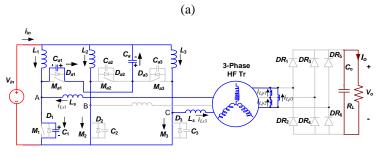

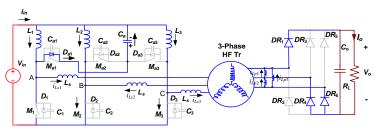

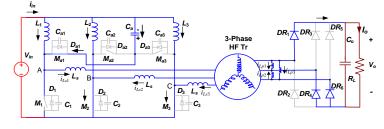

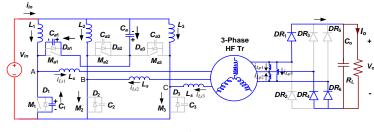

| Fig. | 2.18. Three-phase AC link current-sharing active-clamped current-fed isolated DC/DC converter                                                                                                               | -0 |

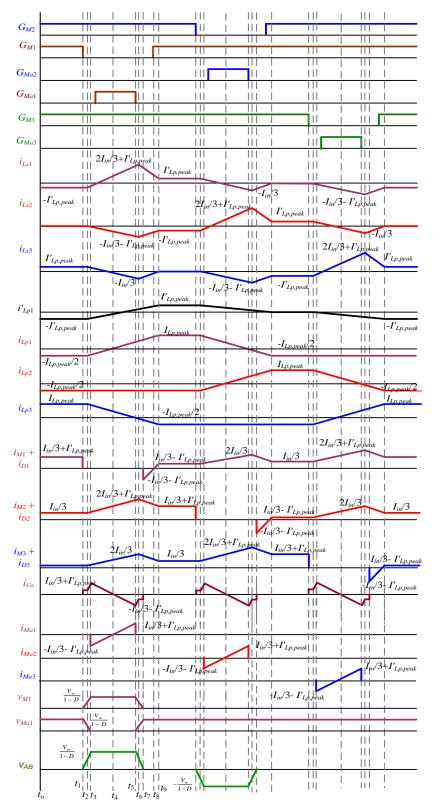

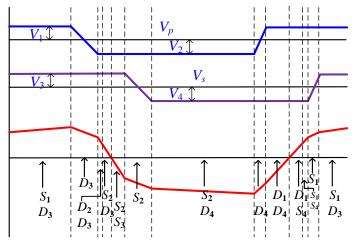

| Fig. | 2.19. Operating waveforms of the proposed converter in discontinuous auxiliary clamp capacitor current case (case A)                                                                                        | 2  |

| Fig. | 2.20. Equivalent circuits during different intervals of operation of the proposed converter                                                                                                                 | 9  |

| Fig. | 2.21 Operating waveforms of the proposed converter in continuous auxiliary clamp capacitor current case (case B).                                                                                                                                                                                          | 52 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

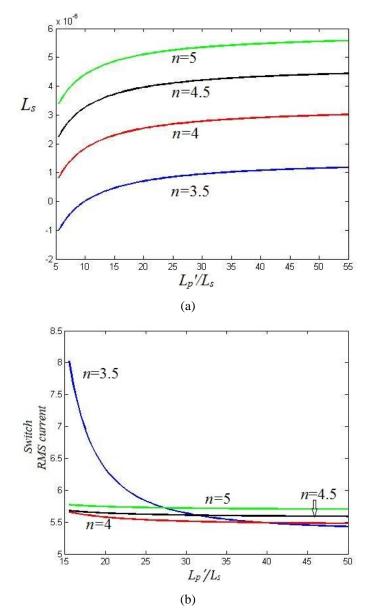

| Fig. | 2.22. Variation of (a) value of series inductance $L_s$ (H), and (b) switch RMS current (A), with respect to inductor ratio $L_p$ / / $L_s$ for various transformer turns ratio $n$ .                                                                                                                      | 56 |

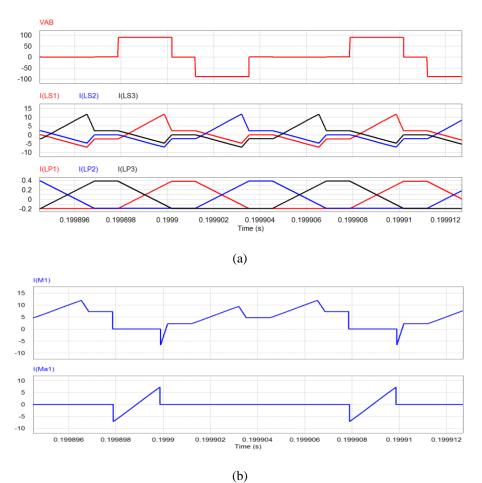

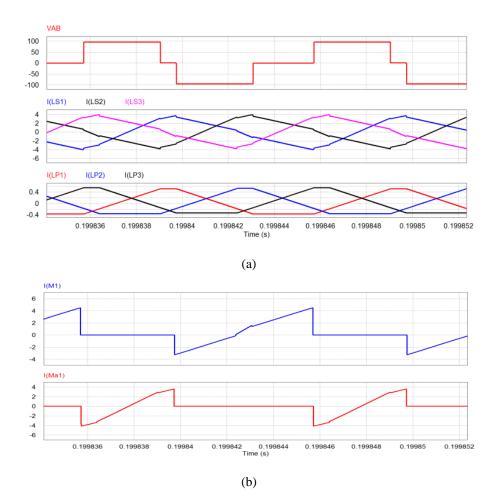

| Fig. | 2.23. Simulation waveforms at $V_{in} = 22$ V and full load: (a) voltage $v_{AB}$ , series inductor currents $i_{Ls1}$ , $i_{Ls2}$ and $i_{Ls3}$ , and parallel inductor currents $i_{Lp1}$ $i_{Lp2}$ and $i_{Lp3}$ (b) main switch $M_1$ current $i_{M1}$ , auxiliary switch $M_{a1}$ current $i_{Ma1}$ . | 61 |

| Fig. | 2.24. Simulation waveforms at $V_{in} = 41$ V and 10% load: (a) voltage $v_{AB}$ , series inductor currents $i_{Ls1}$ , $i_{Ls2}$ and $i_{Ls3}$ , and parallel inductor currents $i_{Lp1}$ $i_{Lp2}$ and $i_{Lp3}$ (b) main switch $M_1$ current $i_{M1}$ , auxiliary switch $M_{a1}$ current $i_{Ma1}$ .  | 62 |

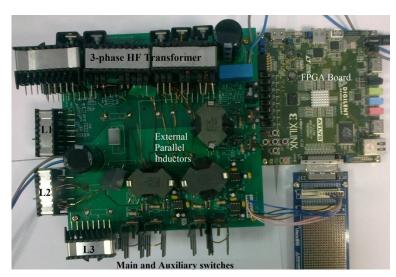

| Fig. | 2.25. 300 W laboratory prototype of current-fed three-phase DC/DC converter with active-clamp                                                                                                                                                                                                              | 62 |

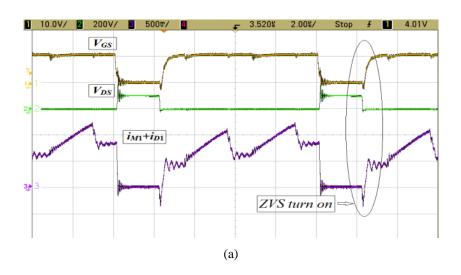

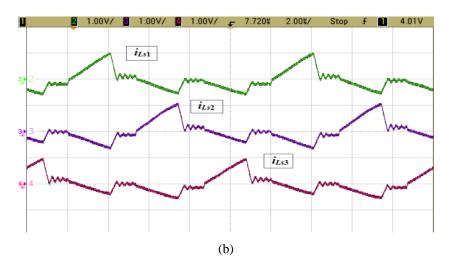

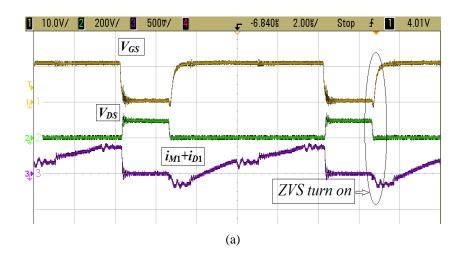

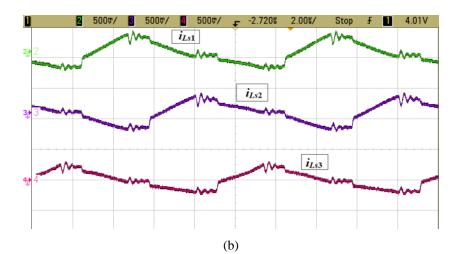

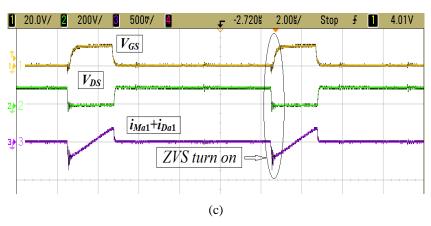

| Fig. | 2.26. Experimental waveforms at $V_{in} = 22$ V and full load (x-axis: 2 µs/div):                                                                                                                                                                                                                          | 64 |

| Fig. | 2.27. Experimental waveforms at $V_{in} = 22$ V and 10% load (x-axis: 2 µs/div):                                                                                                                                                                                                                           | 65 |

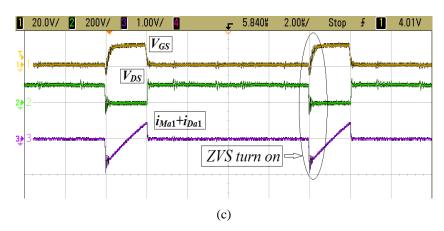

| Fig. | 2.28. Experimental waveforms at $V_{in} = 41$ V and full load (x-axis: 2 µs/div):                                                                                                                                                                                                                          | 66 |

| Fig. | 2.29. Experimental waveforms at $V_{in} = 41$ V and 10% load (x-axis: 2 µs/div):                                                                                                                                                                                                                           | 67 |

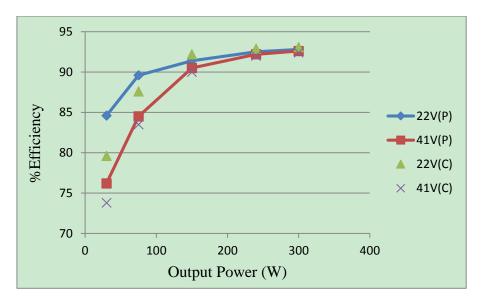

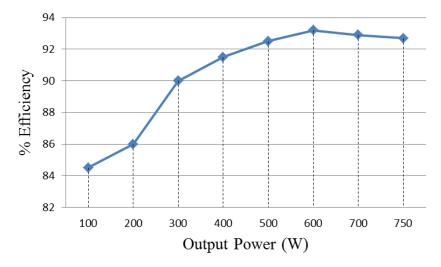

| Fig. | 2.30. Plot of efficiency versus output power for different load condition with $V_{in} = 22$ V and $V_{in} = 41$ V for the proposed converter (P) and conventional converter without external inductor (C).                                                                                                | 68 |

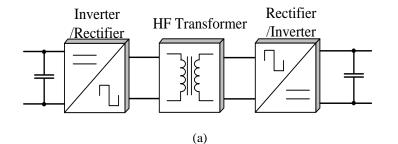

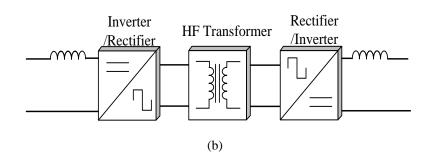

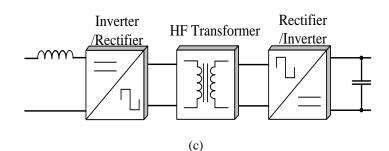

| Fig. | <ul><li>3.1. Topology categorization of bidirectional DC/DC converters based on voltage-fed and current-fed input/output: (a) Dual voltage-fed topology, (b) Dual current-fed topology, (c) Combination of voltage-fed and current-fed topologies.</li></ul>                                               | 74 |

| Fig. | 3.2. Major inverter and consequent rectifier topologies used for bidirectional DC/DC converter in Fig. 3.1. (a) Inverter topologies, (b) Rectifier topologies.                                                                                                                                             | 75 |

| Fig. | 3.3. Bidirectional Dual Active Bridge (DAB) PWM DC/DC converter                                                                                                                                                                                                                                            | 75 |

| Fig. | 3.4. Bidirectional series resonant DAB DC/DC converter                                                                                                                                                                                                                                 | 76 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

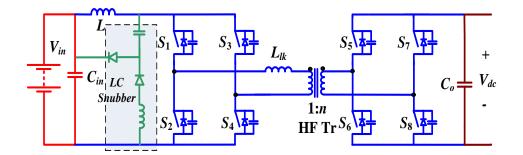

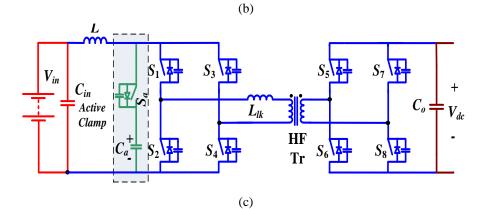

| Fig. | 3.5. Bidirectional DC/DC converter based on a current-fed full-bridge topology at the low voltage side and a voltage-fed full-bridge at the high voltage side. (a) Employing a passive RCD snubber. (b) Employing an energy recovery snubber. (c) Employing an active-clamping snubber | 78 |

| Fig. | 3.6. Bidirectional DC/DC converter based on a current-fed half-bridge topology at the low voltage side and a voltage-fed half-bridge at the high voltage side.                                                                                                                         | 80 |

| Fig. | 3.7. Asymmetrical bidirectional isolated dc-dc converter                                                                                                                                                                                                                               | 80 |

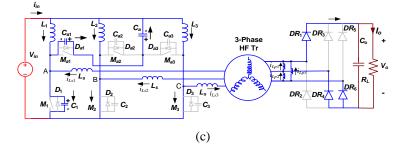

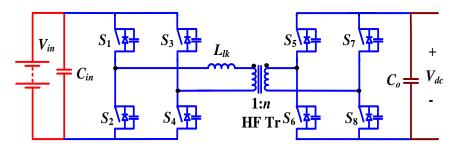

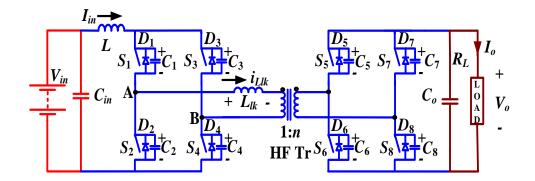

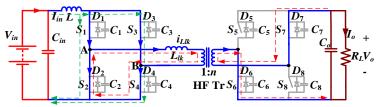

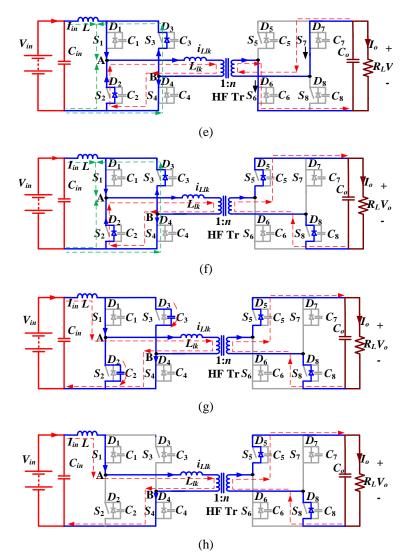

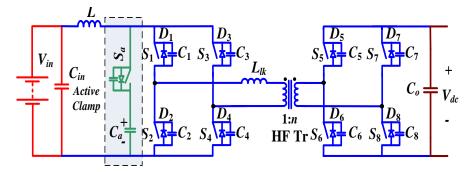

| Fig. | 3.8. Proposed ZCS current-fed dual active bridge (CFDAB) DC/DC converter                                                                                                                                                                                                               | 81 |

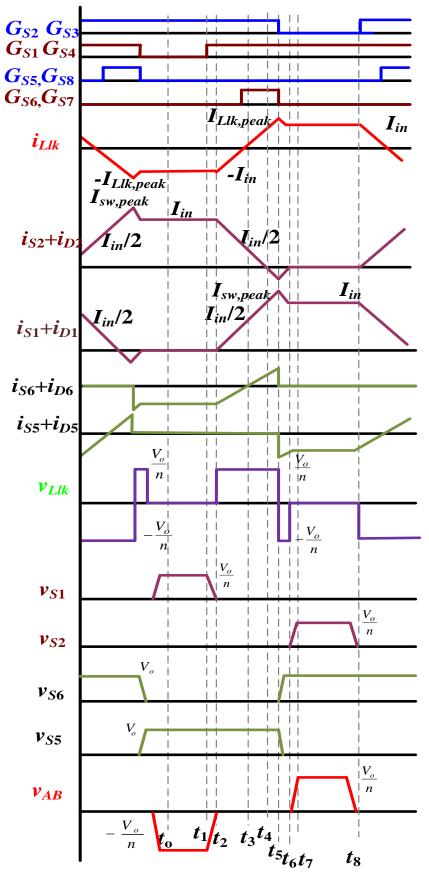

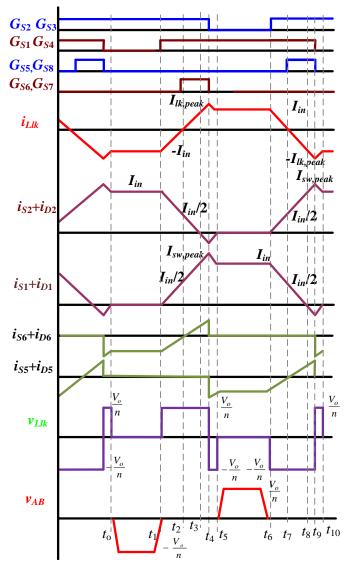

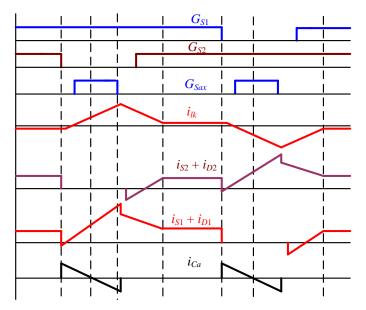

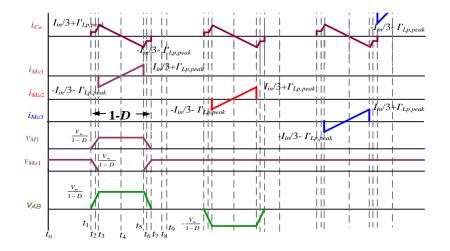

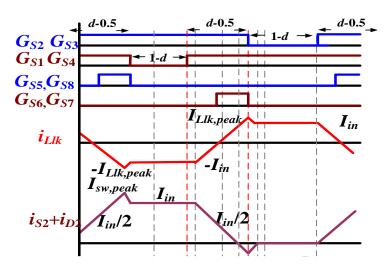

| Fig. | 3.9. Operating waveforms of the proposed ZCS CFDAB DC/DC converter.                                                                                                                                                                                                                    | 83 |

| Fig. | 3.10. Equivalent circuits during different intervals of operation of the proposed converter for the waveforms shown in Fig. 3.9.                                                                                                                                                       | 87 |

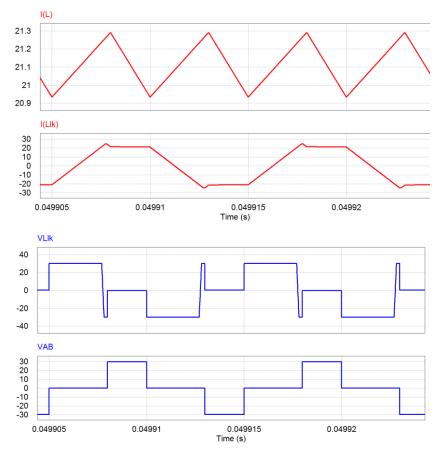

| Fig. | 3.11. Current waveforms through input inductor $I(L)$ , and leakage inductance $I(L_{lk})$ , voltage waveform across leakage inductance $V(L_{lk})$ and voltage waveform $V_{AB}$ .                                                                                                    | 92 |

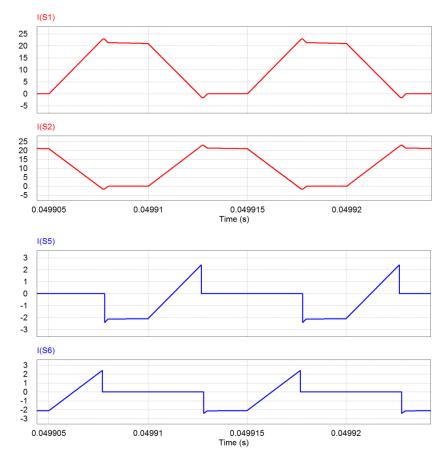

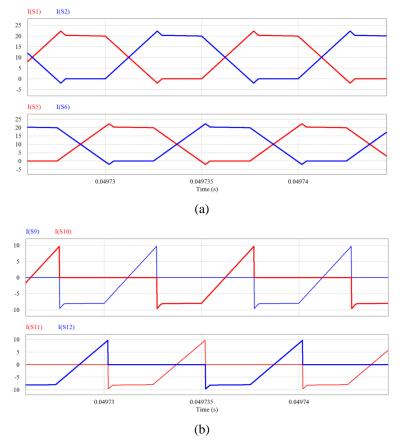

| Fig. | 3.12. Current waveforms through primary switches $I(S_1)$ and $I(S_2)$ and secondary switches $I(S_5)$ and $I(S_6)$ .                                                                                                                                                                  | 93 |

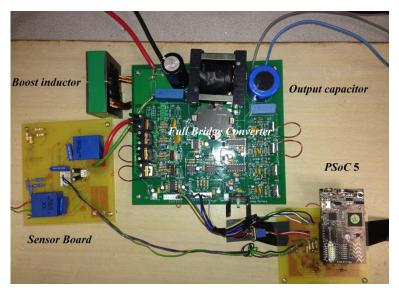

| Fig. | 3.13. Photograph of the laboratory prototype                                                                                                                                                                                                                                           | 95 |

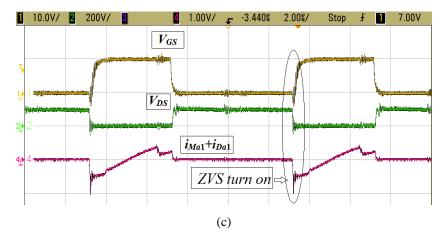

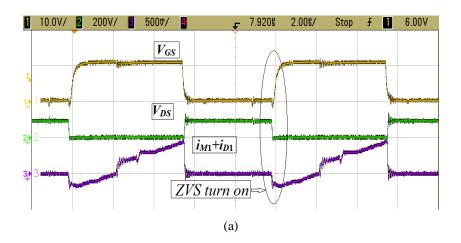

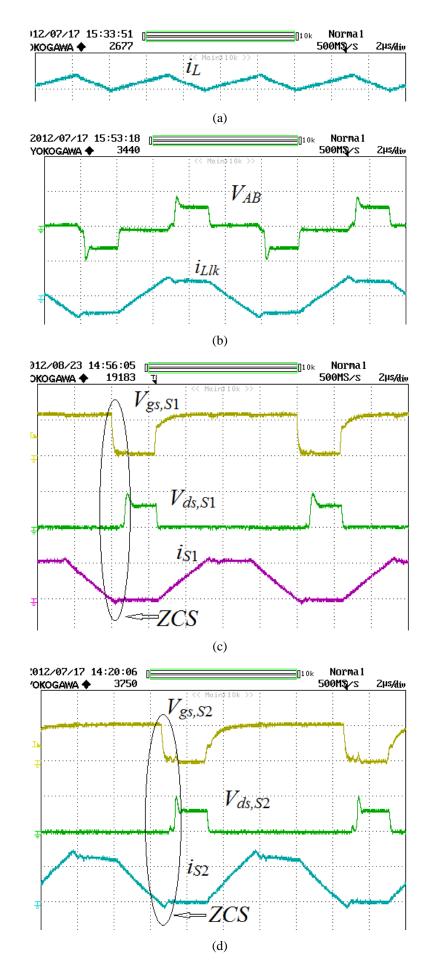

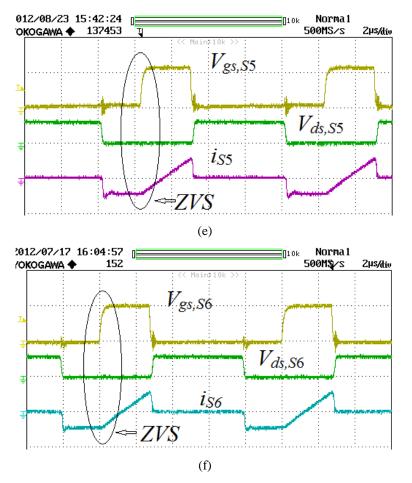

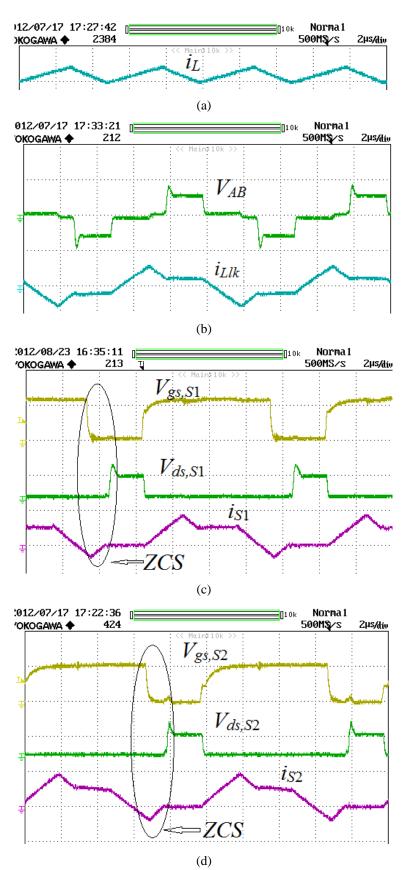

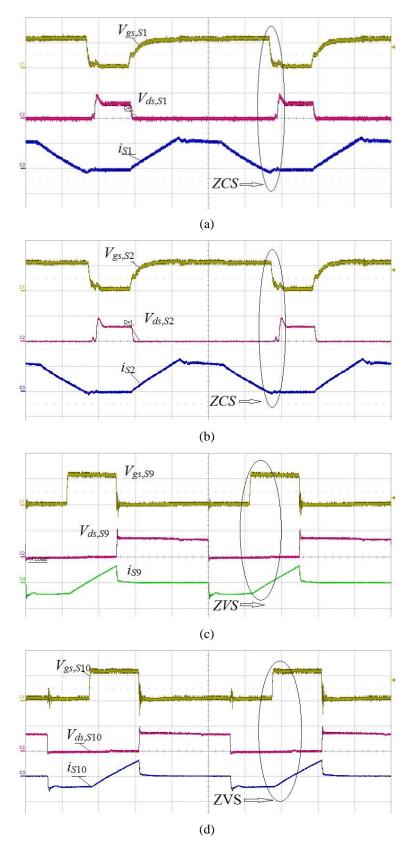

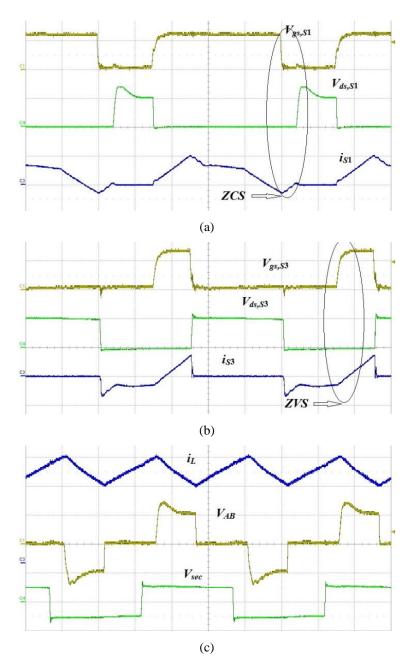

| Fig. | 3.14. Experimental results for output power of 250W at 300V in boost mode                                                                                                                                                                                                              | 98 |

| Fig. | 3.15. Experimental results for output power of 100W at 300V in boost mode                                                                                                                                                                                                              | 00 |

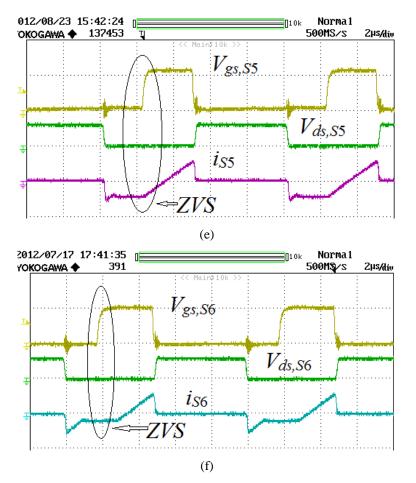

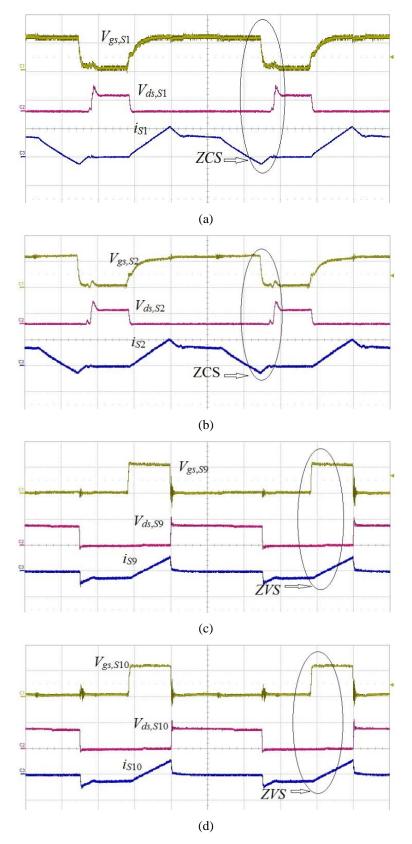

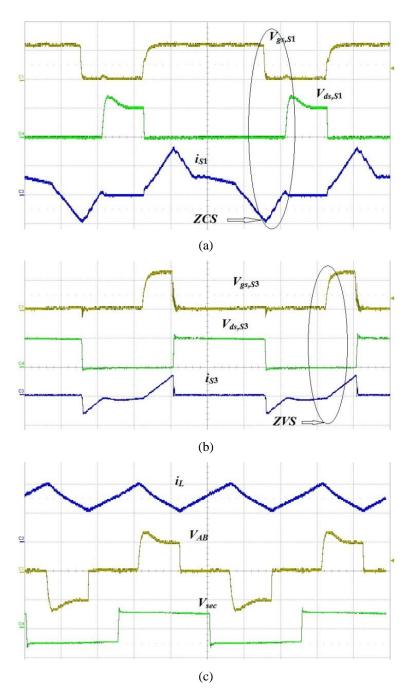

| Fig. | 3.16. Experimental results for output power of 250W at 300V in buck mode 1                                                                                                                                                                                                             | 01 |

| Fig. | 4.1. Operating waveforms of proposed zero current commutated CFDAB DC/DC converter                                                                                                                                                                                                     | 07 |

| Fig. | 4.2. Equivalent circuits during different intervals of operation for the waveforms shown in Fig. 4.1                                                                                                                                                                                   | 08 |

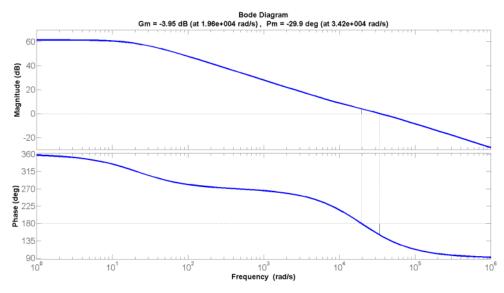

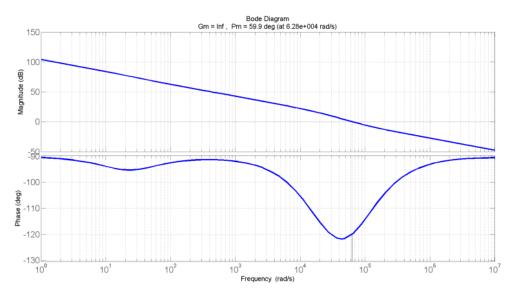

| Fig. | 4.3. Control to output voltage transfer function of the system without controller.                                                                                                                                  | 115 |

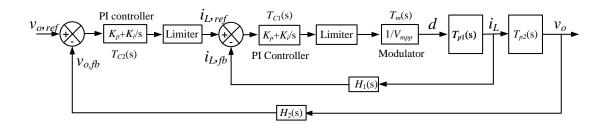

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Fig. | 4.4. Complete two-loop average current control system schematic diagram.                                                                                                                                            | 115 |

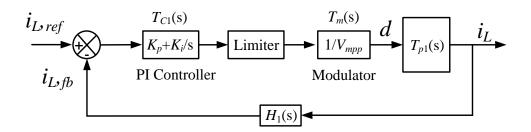

| Fig. | 4.5. Block diagram showing closed loop control system                                                                                                                                                               | 115 |

| Fig. | 4.6. Inner current control loop schematic diagram                                                                                                                                                                   | 117 |

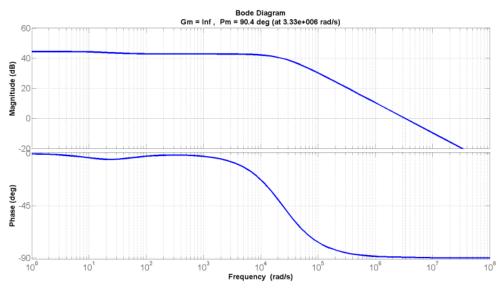

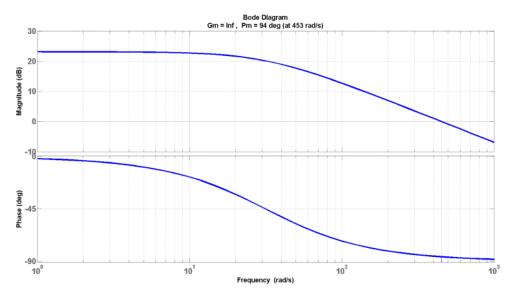

| Fig. | 4.7. Bode plot of current control loop without controller: PM=92.2 °at 628krad/s                                                                                                                                    | 118 |

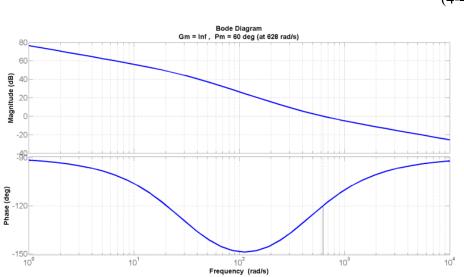

| Fig. | 4.8. Bode plot of current control loop with PI controller: PM=59.9 °at $f_c$ =62.8krad/s.                                                                                                                           | 118 |

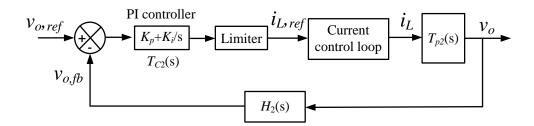

| Fig. | 4.9. Outer voltage control loop schematic diagram                                                                                                                                                                   | 119 |

| Fig. | 4.10. Bode plot of voltage control loop without controller: PM=94 °at 453 rad/s                                                                                                                                     |     |

| Fig. | 4.11. Bode plot of voltage control loop with PI controller: PM=60 °at $f_c$ =628rad/s.                                                                                                                              | 121 |

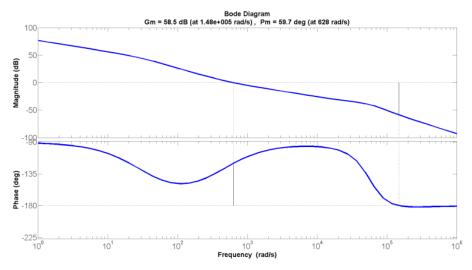

| Fig. | 4.12. Frequency response of the overall system with both the current and the voltage controllers                                                                                                                    | 121 |

| Fig. | 4.13. Pole-zero maps of: (a) control to output voltage transfer function of the system without controller (equation 4-38), (b) the overall system with both the current and the voltage controllers (equation 4-49) |     |

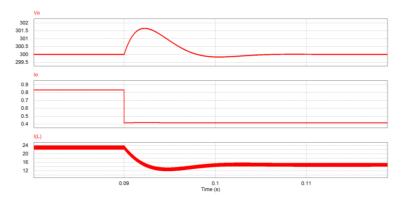

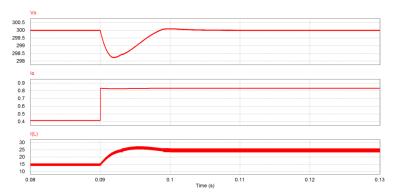

| Fig. | 4.14. Simulation waveforms for $V_{in}=12V$ with step change in load from full load to half load.                                                                                                                   | 124 |

| Fig. | 4.15. Simulation waveforms for $V_{in}$ =12V, step change in load from half load to full load.                                                                                                                      | 125 |

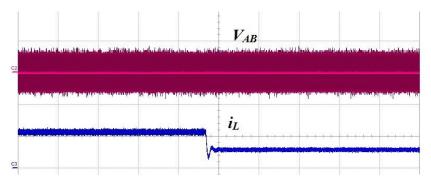

| Fig. | 4.16. Experimental results for step change in load from full load to half load (200ms/div): (1) Voltage $V_{AB}$ (50V/div), (2) Inductor current $i_L$ (20A/div)                                                    | 125 |

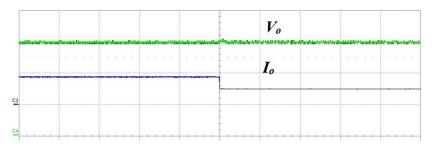

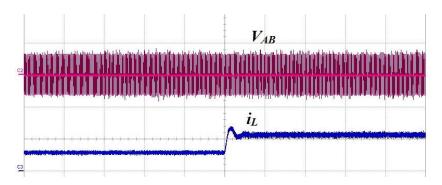

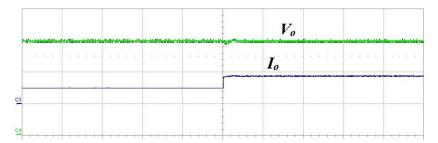

| Fig. | 4.17. Experimental results for step change in load from full load to half load (100ms/div): (1) Output voltage $V_O$ (100V/div), (2) Output current $i_O$ (1A/div)                                                  |     |

| Fig. 4.18. Experimental results for step change in load from half load to full load (100ms/div): (1) Voltage $V_{AB}$ (50V/div), (2) Inductor current $i_L$ (20A/div)                                                                                                                                                                                                                                     | 5 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| <ul> <li>Fig. 4.19. Experimental results for step change in load from half load to full load (100ms/div): (1) Output voltage V<sub>0</sub> (100V/div), (2) Output current i<sub>0</sub> (1A/div).</li> </ul>                                                                                                                                                                                              | 6 |

| Fig. 5.1. VF-DAB DC/DC converter                                                                                                                                                                                                                                                                                                                                                                          | 9 |

| Fig. 5.2. Operating waveforms of secondary controlled VF-DAB DC/DC converter                                                                                                                                                                                                                                                                                                                              | 9 |

| Fig. 5.3. CF-DAHB DC/DC converter                                                                                                                                                                                                                                                                                                                                                                         | 1 |

| Fig. 5.4. Operating waveforms of CF-DAHB DC/DC converter                                                                                                                                                                                                                                                                                                                                                  | 1 |

| Fig. 5.5. CF-DAFB DC/DC converter with active-clamp                                                                                                                                                                                                                                                                                                                                                       | 2 |

| Fig. 5.6. Operating waveforms of CF-DAFB DC/DC converter with active-<br>clamp                                                                                                                                                                                                                                                                                                                            | 2 |

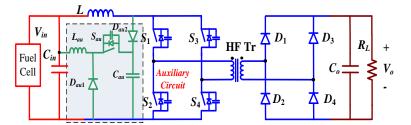

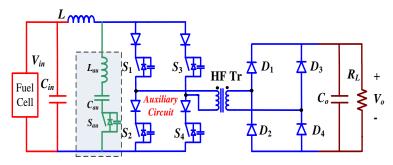

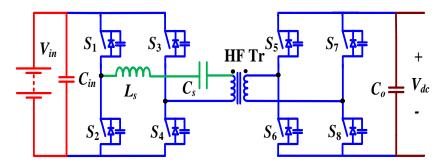

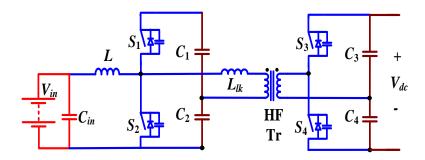

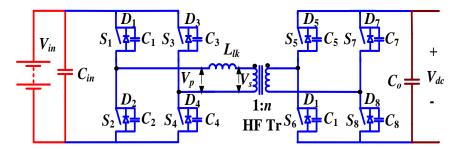

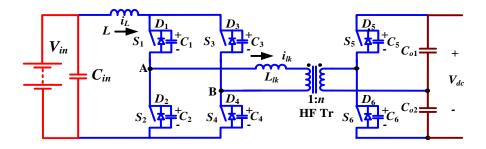

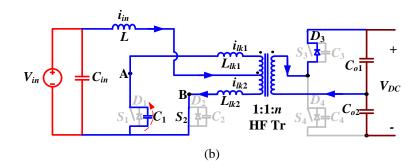

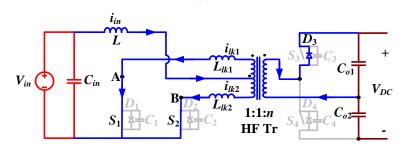

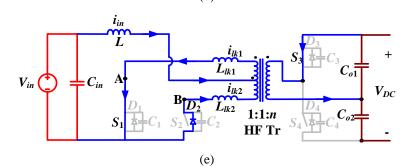

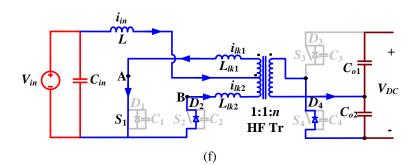

| Fig. 5.7. Proposed secondary modulation based CF-FBVD DC/DC Converter. 13                                                                                                                                                                                                                                                                                                                                 | 3 |

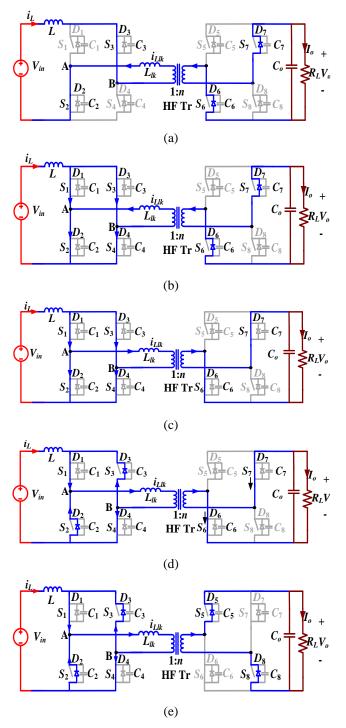

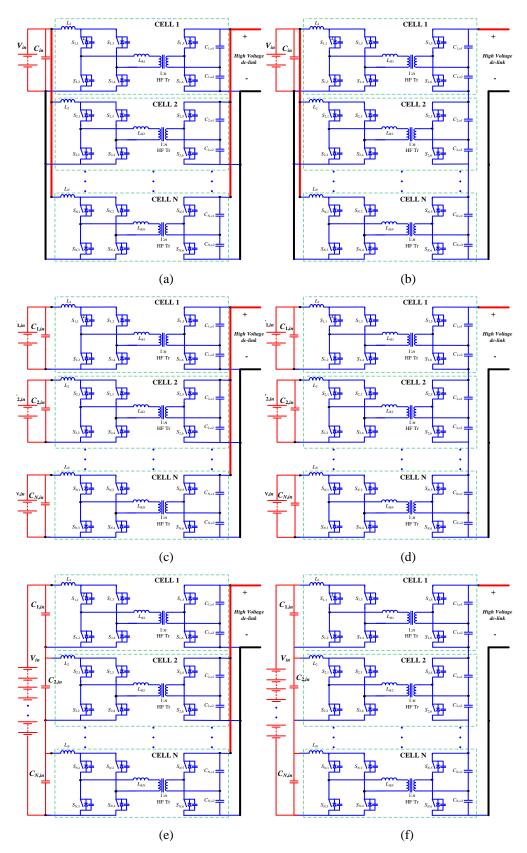

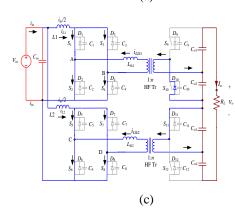

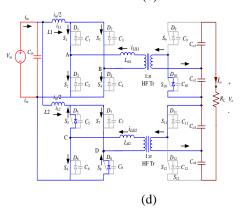

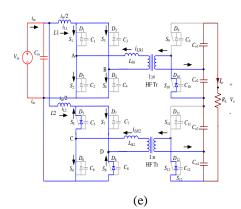

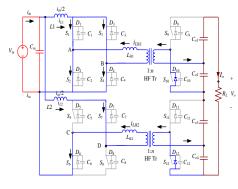

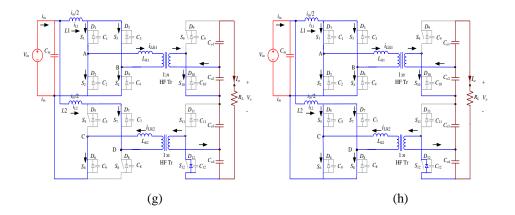

| <ul> <li>Fig. 5.8. Different possible configurations of the proposed modular CF-FBVD multi-cell DC/DC converter. (a) Parallel Input Parallel Output (PIPO); (b) Parallel Input Series Output (PISO); (c) Multiple Input Parallel Output (MIPO); (d) Multiple input Series Output (MISO); (e) Series Input Series Output (SISO); (f) Series Input Parallel Output (SIPO)</li></ul>                         | 7 |

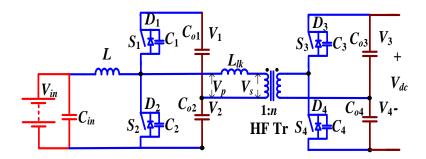

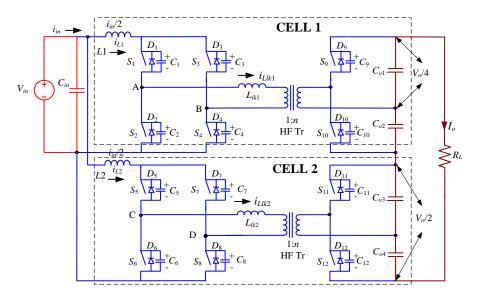

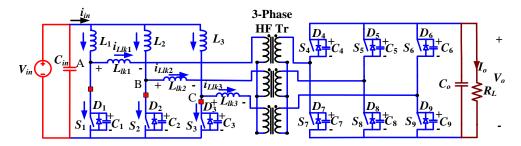

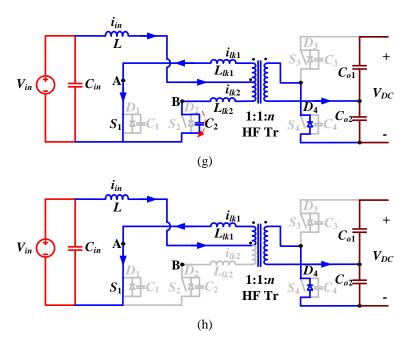

| Fig. 5.9. A design example of two cells for the PISO configuration of the proposed modular CF-FBVD multi-cell DC/DC converter                                                                                                                                                                                                                                                                             | 9 |

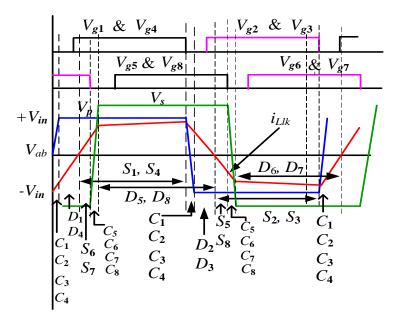

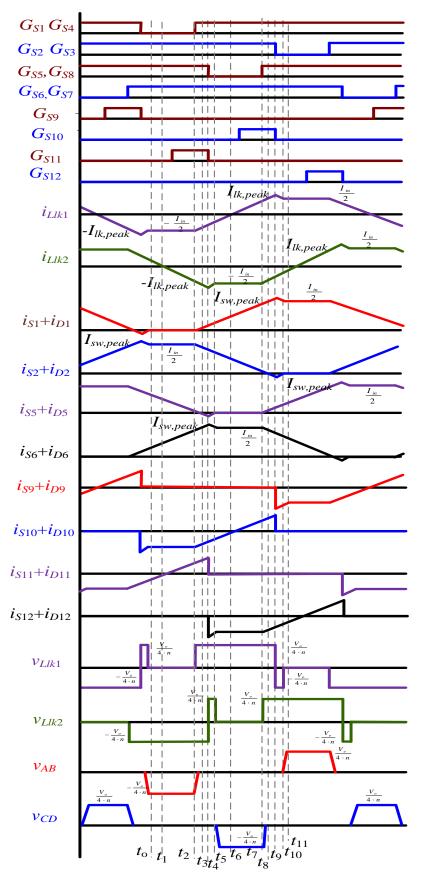

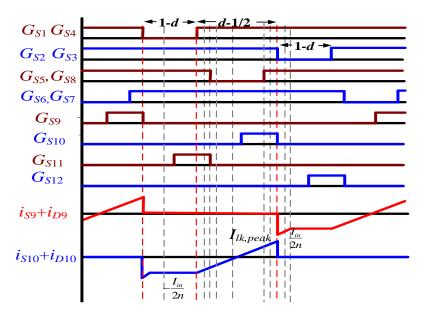

| Fig. 5.10. Operating waveforms of proposed ZCS current-fed dual active bridge converter                                                                                                                                                                                                                                                                                                                   | 1 |

| Fig. 5.11. Equivalent circuits during different intervals of operation of the proposed converter                                                                                                                                                                                                                                                                                                          | 3 |

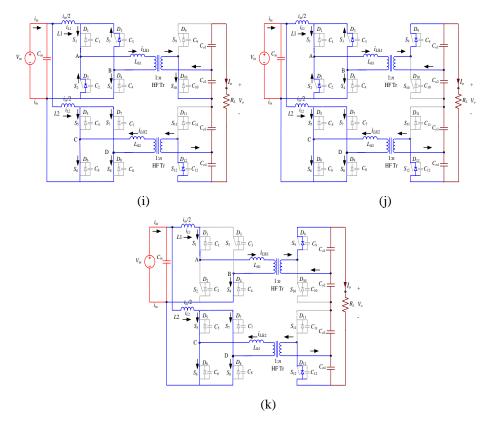

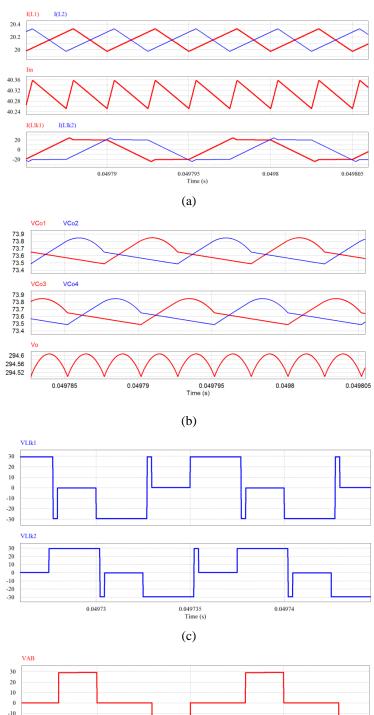

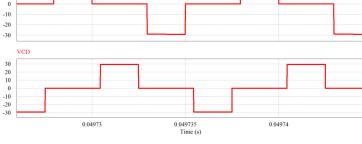

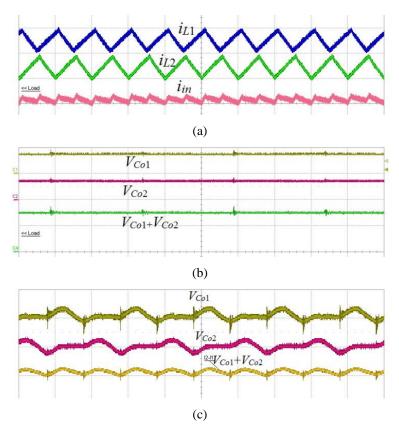

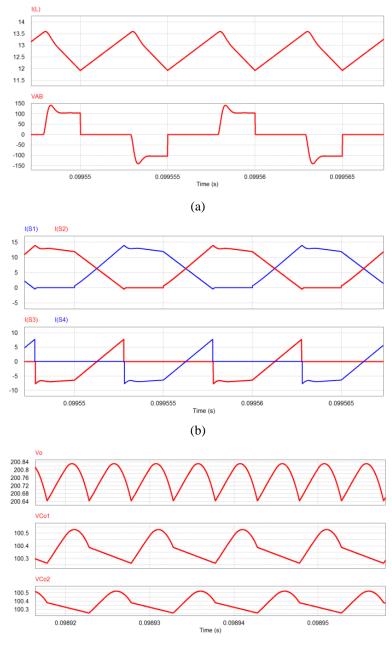

| Fig. 5.12. Simulation waveforms: (a) input boost inductor currents $I(L_1)$ , $I(L_2)$ ,<br>input current $I_{in}$ , series inductor currents $I(L_{Llk1})$ and $I(L_{Llk2})$ , (b) Voltages<br>across output capacitors $V_{Co1}$ , $V_{Co2}$ , $V_{Co3}$ , $V_{Co4}$ and output voltage $V_O$ , (c)<br>voltage waveforms $V(L_{Llk1})$ , $V(L_{Llk2})$ , (d) voltage waveforms $V_{AB}$ and $V_{CD}$ 15 | 3 |

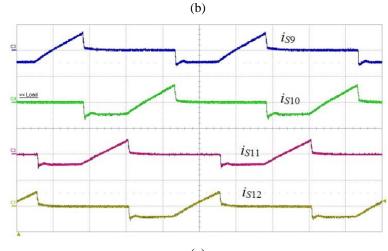

| Fig. 5.13. Simulation waveforms: (a) primary switch currents $I(S_1)$ , $I(S_2)$ , $I(S_5)$ and $I(S_6)$ , (b) secondary switch currents $I(S_9)$ , $I(S_{10})$ , $I(S_{11})$ and $I(S_{12})$ 15                                                                                                                                                                                                          | 4 |

| Fig. : | 5.14. Photograph of the laboratory prototype                                                                                                                                                                                  | 155 |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

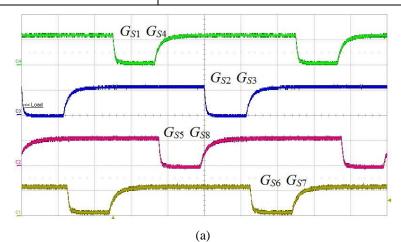

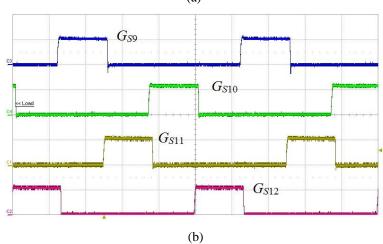

| C      | 5.15. Gating signals of all the switching devices for output power of 500W at 300V. (a) primary side switches, (b) secondary side switches (x-axis: 2 µs/div, y-axis: 10V/div)                                                |     |

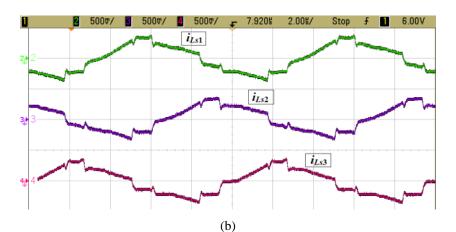

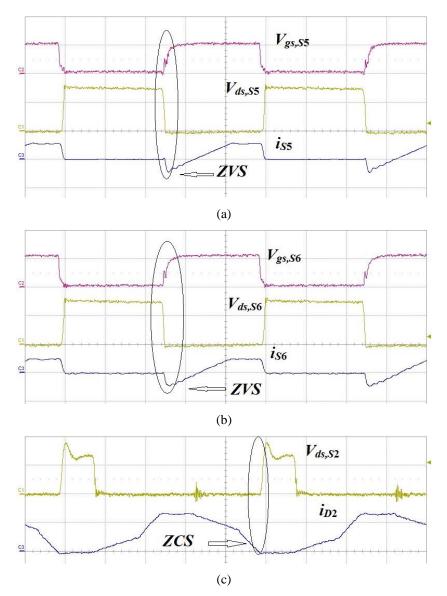

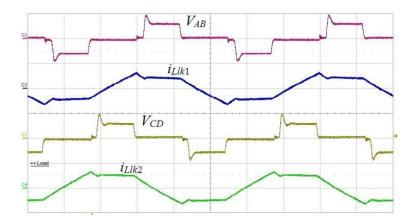

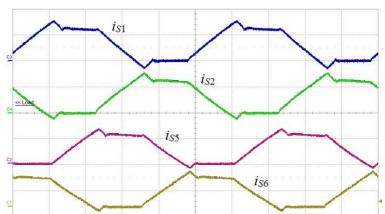

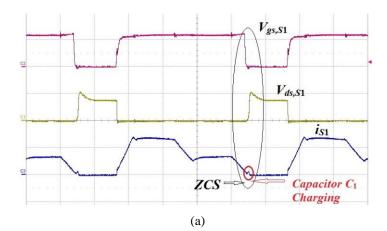

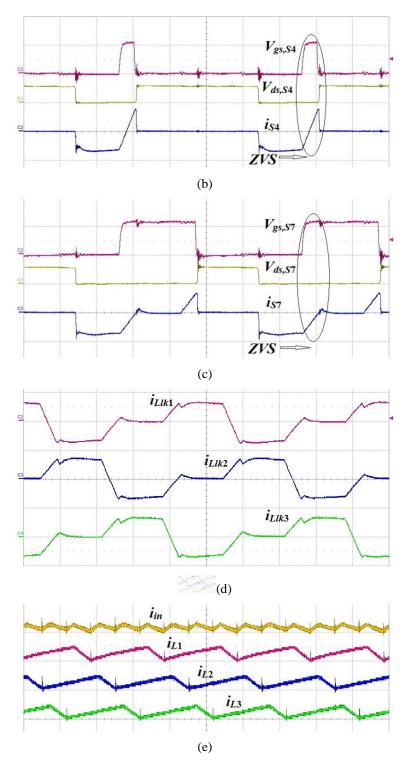

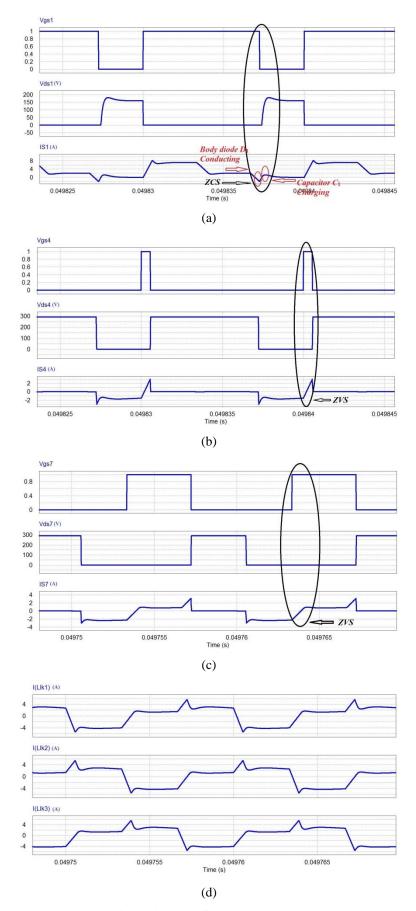

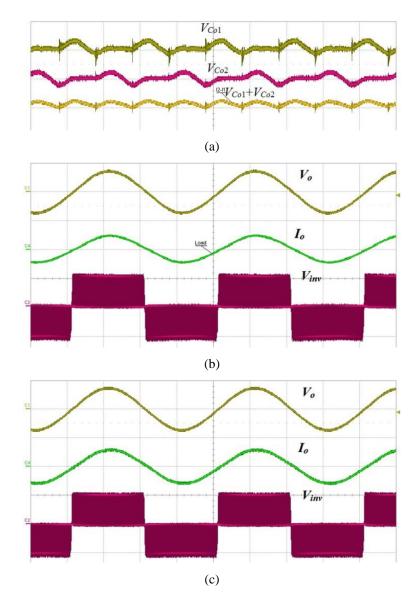

| Fig. : | 5.16. Experimental results for output power of 500W at 300V                                                                                                                                                                   | 159 |

| Fig. : | 5.17. Experimental results for output power of 250W at 300V                                                                                                                                                                   | 160 |

| Fig. : | 5.18. Experimental results for output power of 500W at 300V                                                                                                                                                                   | 161 |

| Fig. : | 5.19. Experimental results for output power of 500W at 300V                                                                                                                                                                   | 162 |

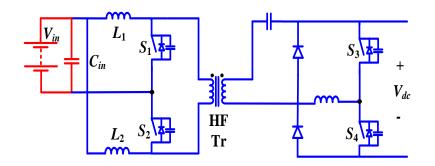

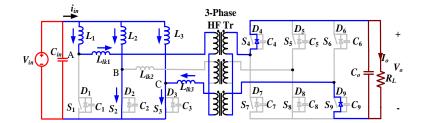

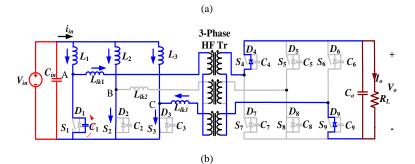

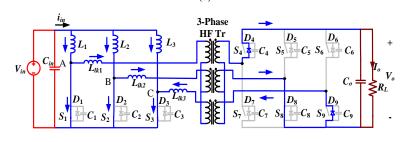

| -      | 6.1. Three-phase AC link snubberless current-fed isolated DC/DC converter.                                                                                                                                                    | 167 |

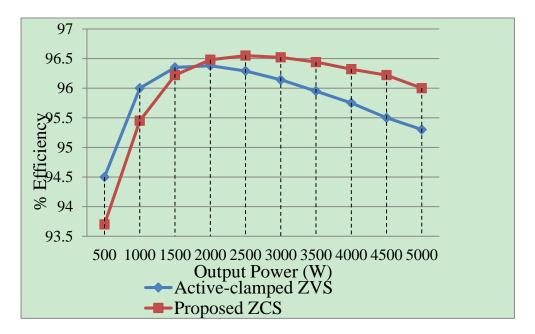

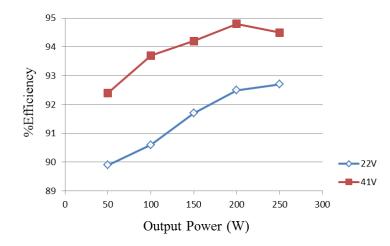

| -      | 6.2. Calculated efficiency of the proposed three-phase ZCS converter and three-phase active-clamped ZVS converter                                                                                                             | 167 |

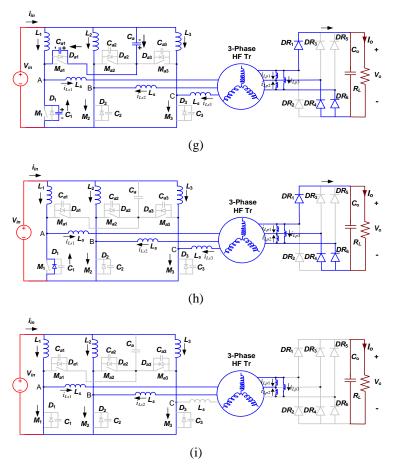

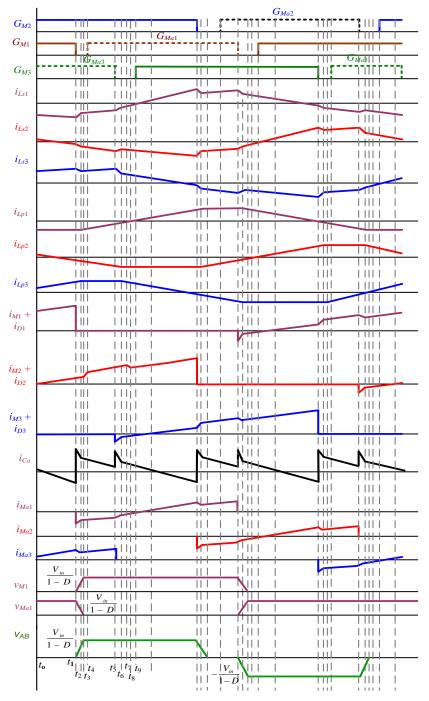

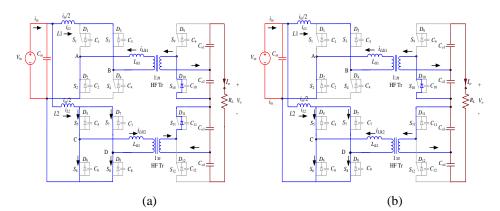

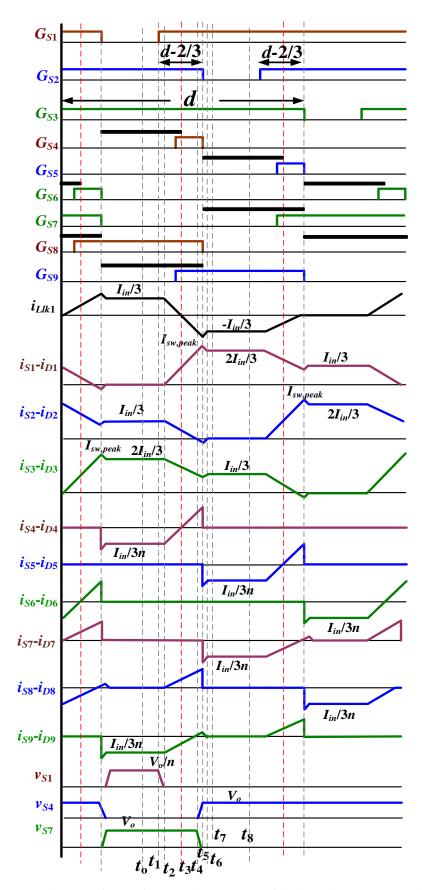

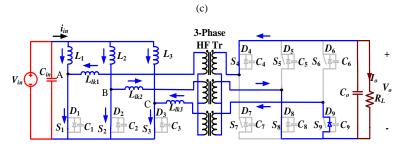

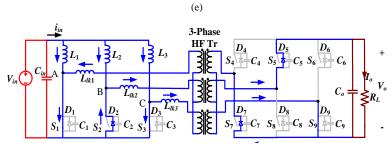

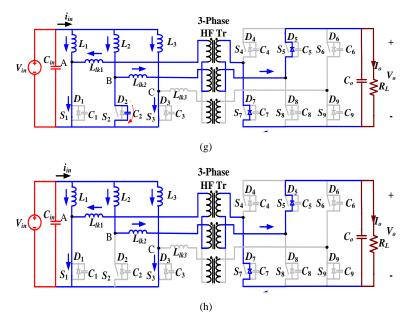

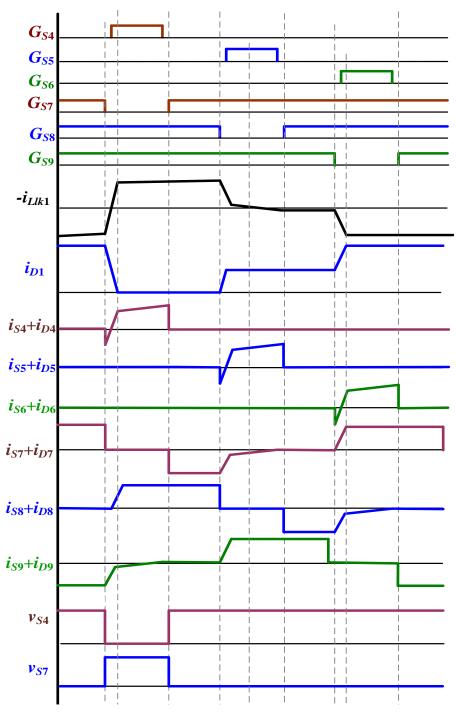

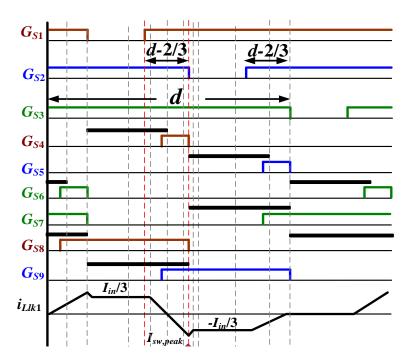

| -      | 6.3. Operating waveforms of proposed ZCS current-fed three-phase converter shown in Fig. 6.1.                                                                                                                                 | 174 |

| -      | 6.4. Equivalent circuits during different intervals of operation of the proposed converter in boost mode                                                                                                                      | 176 |

| 0      | 6.5. Operating waveforms of the proposed three-phase converter in buck mode                                                                                                                                                   | 179 |

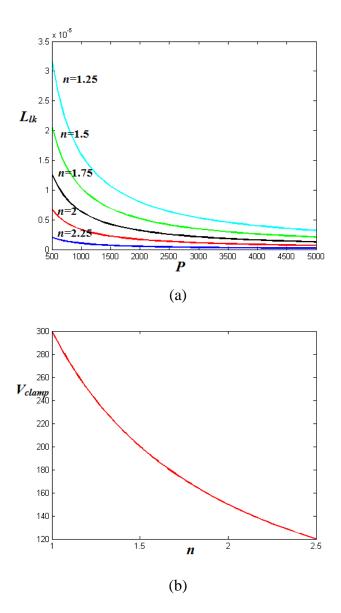

| -      | 6.6. Variation of (a) Series inductance $L_{lk}$ (H) ( $\mu$ H) with respect to power transferring ability $P$ (W), and (b) Clamped voltage across primary switches $V_{clamp}$ (V) for various transformer turns-ratio $n$ . | 182 |

| Fig. ( | 6.7. Photograph of the laboratory prototype                                                                                                                                                                                   | 185 |

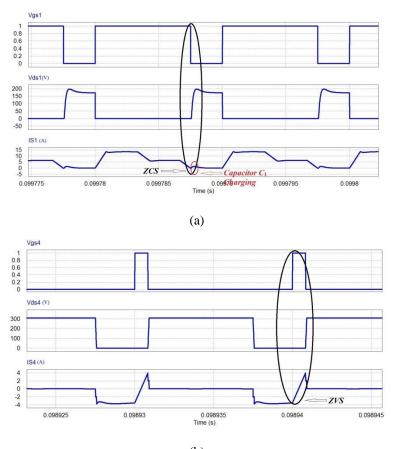

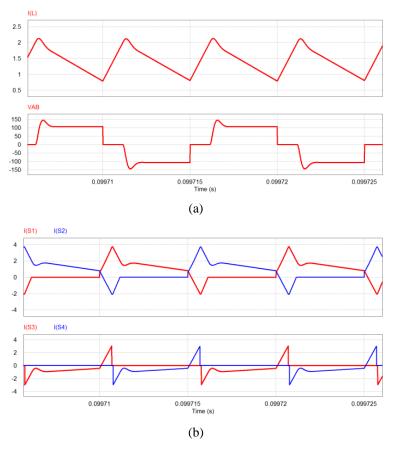

| Fig. ( | 6.8. Simulation waveforms at 750W power (boost mode)                                                                                                                                                                          | 187 |

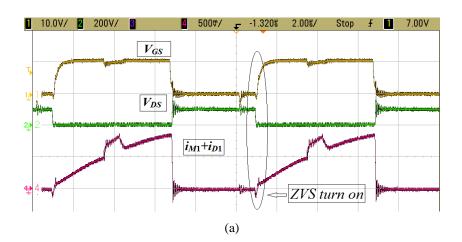

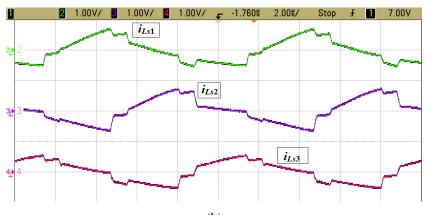

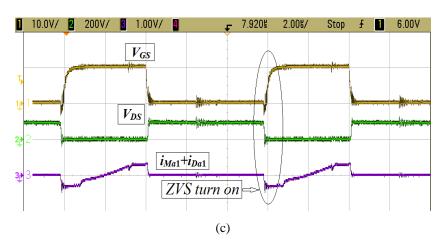

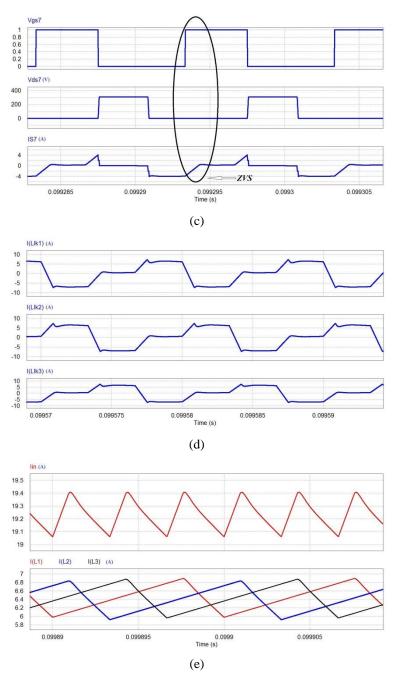

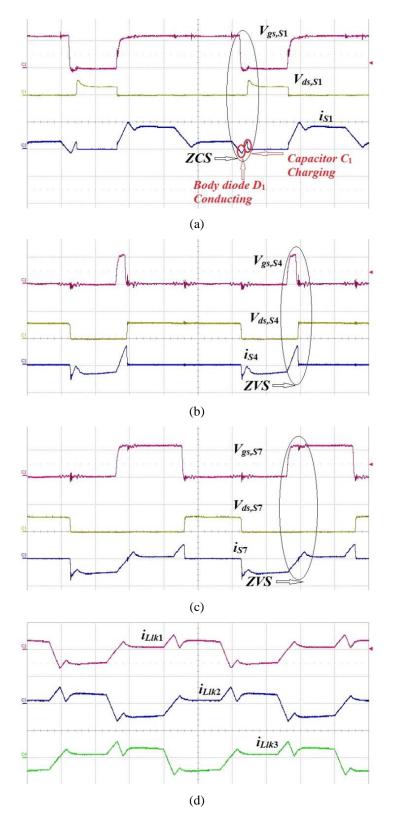

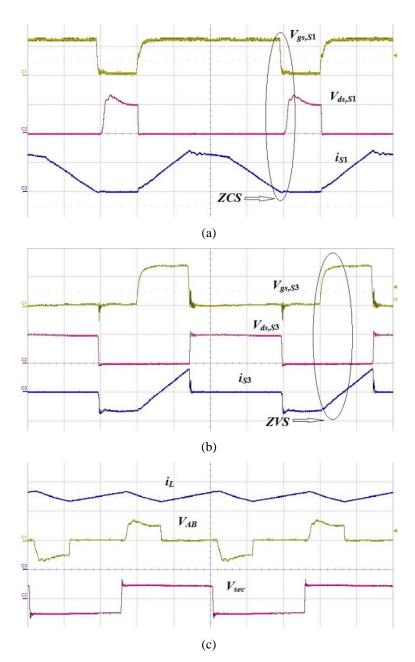

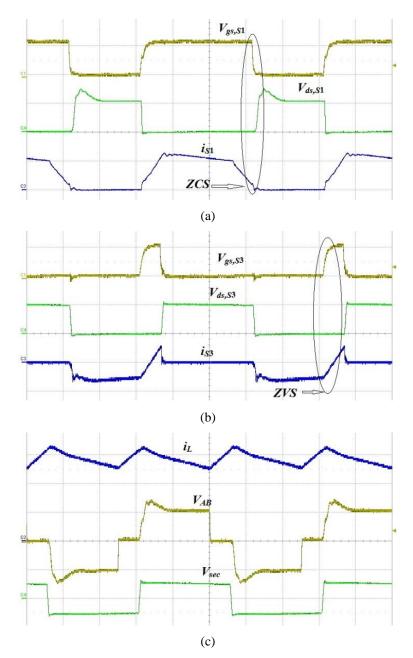

| Fig. ( | 6.9. Experimental results for output power of 750W at 300V (boost mode)                                                                                                                                                       |     |

| Fig. ( | 6.10. Simulation waveforms at 375W (boost mode)                                                                                                                                                                               | 189 |

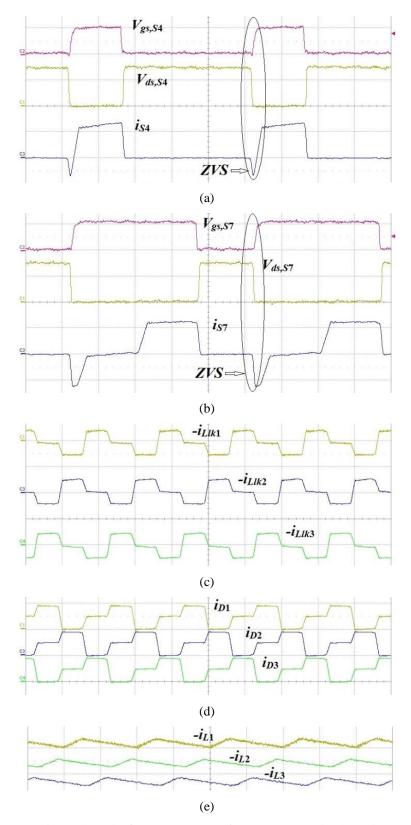

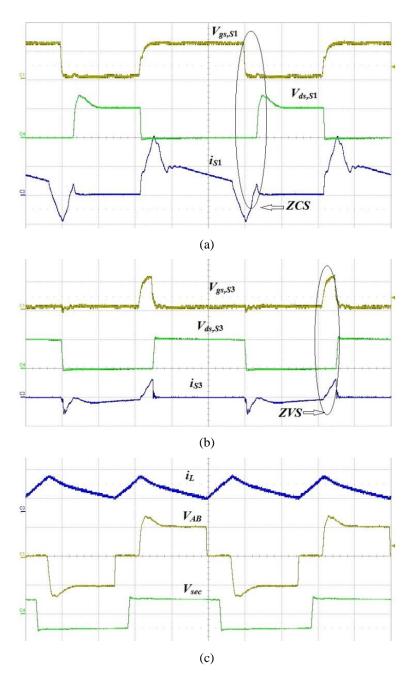

| -      | 6.11. Experimental results for output power of 375W at 300V (boost mode).                                                                                                                                                     | 190 |

| Fig. | 6.12. Experimental results for output power of 450W at 300V (buck | 101 |

|------|-------------------------------------------------------------------|-----|

|      | mode).                                                            | 191 |

|      |                                                                   |     |

| Fig. | 6.13. Efficiency of the proposed three-phase ZCS converter        | 192 |

## List of Acronyms

| EIA                                         | Energy Information Administration                                                                                                                                                                 |

|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EPA                                         | Environmental Protection Agency                                                                                                                                                                   |

| BEVs                                        | Battery Electric Vehicles                                                                                                                                                                         |

| HEVs                                        | Hybrid Electric Vehicles                                                                                                                                                                          |

| PHEVs                                       | Plug-in Hybrid Electric Vehicles                                                                                                                                                                  |

| FCVs                                        | Fuel-Cell Vehicles                                                                                                                                                                                |

| ICE                                         | Internal Combustion Engine                                                                                                                                                                        |

| ESS                                         | Energy Storage System                                                                                                                                                                             |

| DOE                                         | Department of Energy                                                                                                                                                                              |

| PEFC                                        | Polymer Electrolyte Fuel Cell                                                                                                                                                                     |

| PEMFC                                       | Proton Exchange Membrane Fuel Cell                                                                                                                                                                |

| EMI                                         | Low Electromagnetic Interference                                                                                                                                                                  |

| ZVS                                         | Zero-Voltage Switching                                                                                                                                                                            |

| ZCS                                         | Zero-Current Switching                                                                                                                                                                            |

|                                             |                                                                                                                                                                                                   |

| AFC                                         | Alkaline Fuel Cell                                                                                                                                                                                |

| AFC<br>DMFC                                 | Alkaline Fuel Cell<br>Direct Methanol Fuel Cell                                                                                                                                                   |

|                                             |                                                                                                                                                                                                   |

| DMFC                                        | Direct Methanol Fuel Cell                                                                                                                                                                         |

| DMFC<br>MCFC                                | Direct Methanol Fuel Cell<br>Molten Carbonate Fuel Cell                                                                                                                                           |

| DMFC<br>MCFC<br>PAFC                        | Direct Methanol Fuel Cell<br>Molten Carbonate Fuel Cell<br>Phosphoric Acid Fuel Cell                                                                                                              |

| DMFC<br>MCFC<br>PAFC<br>SOFC                | Direct Methanol Fuel Cell<br>Molten Carbonate Fuel Cell<br>Phosphoric Acid Fuel Cell<br>Solid Oxide Fuel Cell                                                                                     |

| DMFC<br>MCFC<br>PAFC<br>SOFC<br>ERCCs       | Direct Methanol Fuel Cell<br>Molten Carbonate Fuel Cell<br>Phosphoric Acid Fuel Cell<br>Solid Oxide Fuel Cell<br>Energy Recovery Clamp Circuits                                                   |

| DMFC<br>MCFC<br>PAFC<br>SOFC<br>ERCCs       | Direct Methanol Fuel Cell<br>Molten Carbonate Fuel Cell<br>Phosphoric Acid Fuel Cell<br>Solid Oxide Fuel Cell<br>Energy Recovery Clamp Circuits<br>Resistor-Capacitor                             |

| DMFC<br>MCFC<br>PAFC<br>SOFC<br>ERCCs<br>RC | Direct Methanol Fuel Cell<br>Molten Carbonate Fuel Cell<br>Phosphoric Acid Fuel Cell<br>Solid Oxide Fuel Cell<br>Energy Recovery Clamp Circuits<br>Resistor-Capacitor<br>Resistor-Capacitor-Diode |

| SPRC    | Series Parallel Resonant Converter      |

|---------|-----------------------------------------|

| QRCs    | Quasi-Resonant Converters               |

| MRCs    | Multi-Resonant converters               |

| CFDAB   | Current-Fed Dual Active Bridge          |

| ZCC     | Zero Current Commutation                |

| NVC     | Natural Voltage Clamping                |

| SSM     | Small Signal Modeling                   |

| РМ      | Phase Margin                            |

| GM      | Gain Margin                             |

| BW      | Bandwidth                               |

| PSoC    | Programmable System-on-Chip             |

| SAR     | Successive Approximate Register         |

| PEBB    | Power Electronics Building Block        |

| CF-FBVD | Current-Fed Full-Bridge Voltage Doubler |

| VF-DAB  | Voltage-Fed Dual Active Full-Bridge     |

| CF-DAHB | Current-Fed Dual Active Half-Bridge     |

| CF-DAFB | Current-Fed Dual Active Full-Bridge     |

| TDR     | Total Device Rating                     |

| CESS    | Composite Energy Storage System         |

| PIPO    | Parallel Input Parallel Output          |

| PISO    | Parallel Input Series Output            |

| MIPO    | Multiple Input Parallel Output          |

| MISO    | Multiple Input Series Output            |

| SISO    | Series Input Series Output              |

| SIPO    | Series Input Parallel Output            |

xviii

## Chapter 1

## **Background and Problem Definition**

#### **1.1 Background**

Renewable energy has experienced impressive growth over the past decade owing to the dwindling fossil fuel reserves, concern on global climate change, energy security, and air pollution. Non-conventional energy sources such as solar, hydrogen, and correlated energy storage are low voltage high current sources. These sources produce variable and/or discontinuous output and therefore, power electronics is necessary to condition them into regulated and useful form. The main objective of this thesis is to develop modular highfrequency soft-switching current-fed power converters for low voltage high current applications. Since fuel cell is a typical low voltage high current energy source, in this thesis, the converter are developed under the scenario of fuel cell applications. However, the proposed novel soft-switching current-fed topologies and modulation techniques are suitable for any general low voltage high current applications such as solar/fuel cell based utility interactive inverters, UPS, microgrid, V2G, and energy storage. Similar merits and performance is expected owing to similar specifications and properties.

Global consumption of fossil fuels has been increasing in gigantic proportion with the rapid development of largely populated countries like China and India. U.S. Energy Information Administration (EIA) recently

1

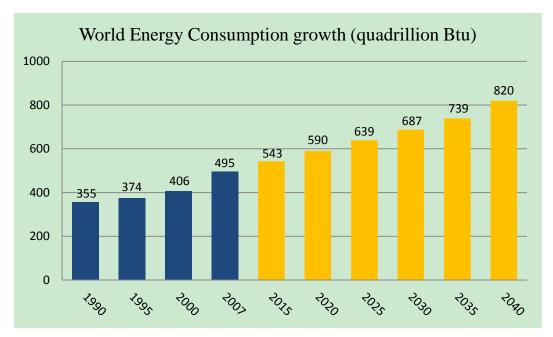

Fig. 1.1. World energy consumption growth [1].

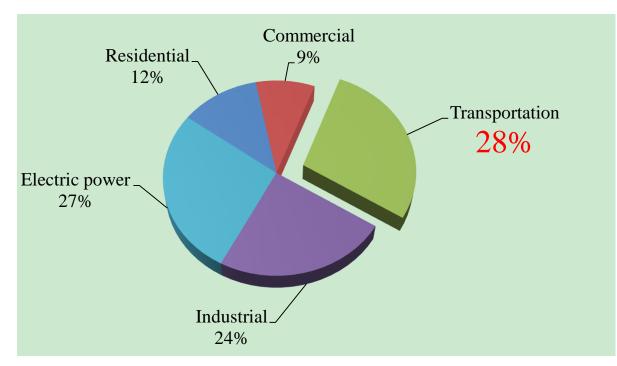

Fig. 1.2. US energy consumption by sector in 2009[2-3].

released International Energy Outlook 2013 (IEO2013) [1-2]. It projects that world's energy consumption will grow by 56% between 2010 and 2040, from 524 quadrillion British thermal units (Btu) to 820 quadrillion Btu as shown in Fig. 1.1 [1]. A major portion of the worldwide fossil fuel consumption occurs in the transportation sector. According to the EIA, the total energy consumption of United States in 2009 was 27.7 trillion kilowatt hours (kWh), with 28% in transportation sector as illustrated in Fig. 1.2 [2-3]. For transportation sector, 94% of the supply source is from petroleum and only 3% is from renewable energy. Approximately 72% of petroleum is used for transportation sector. About 63% of crude oil consumption relied on import for United States in 2009 [2-3]. Meanwhile, the global number of vehicles is expected to increase from 700 million to 2.5 billion in the next 50 years [4]. Therefore, improving vehicular fuel economy becomes a need.

On the other hand, according to the reports from the U.S. Environmental Protection Agency (EPA), a significant portion of harmful emission is from the vehicles, i.e., vehicles account for about 75% carbon monoxide (CO) emissions, about 35% carbon dioxide (CO<sub>2</sub>,) about 45% nitrous oxide (NOx) emissions, and amount for nearly 40% volatile organic compounds emissions [5]. The total carbon emission by 2030 is projected to be around 40 billion metric tons [6]. Therefore, to address the problems of dwindling fossil fuel reserves and air pollution, it is essential to develop new ways of transportation targeting high efficiency, fuel utilization, and better performance.

# **1.2** The Opportunities and Challenges of Fuel Cell Vehicles

Battery electric vehicles (BEVs), hybrid electric vehicles (HEVs), plug-in hybrid electric vehicles (PHEVs), and fuel-cell vehicles (FCVs) are the emerging means of transportation either to replace or reduce the conventional internal combustion engine (ICE), by using 3-phase electric motor for propulsion through three-phase inverter. In this Section, the characteristics and properties of different types of electric vehicles are discussed and compared.

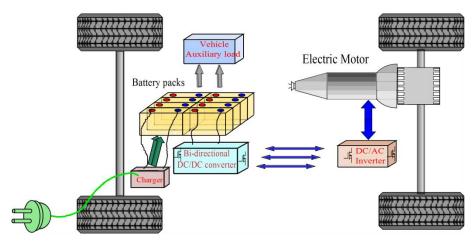

A BEV, also known as all-electric vehicle, is propelled by electric motor powered by rechargeable battery packs. ICE and fuel system are completely eliminated from the vehicle. The battery packs can be charged from renewable sources such as wind, solar, etc. or conventional AC grid utility or DC grid in a micro-grid. Therefore, BEVs provide the following merits due to the absence of ICE and fuel system [7]:

- High energy efficiency: BEVs convert about 59-62% of the electrical energy from the grid to power at the wheels.

- Zero emission.

- Independency of crude oil.

- High performance: BEVs provide quiet and smooth operation and require less maintenance.

Fig. 1.3. Architecture of a BEV.

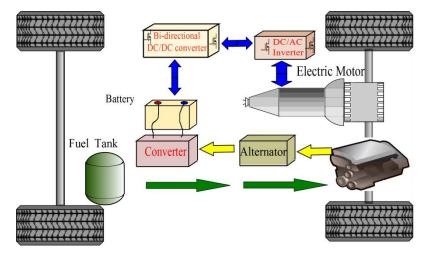

Fig. 1.4. Architecture of a HEV.

Fig. 1.5. Architecture of a PHEV.

Fig. 1.6. Architecture of a FCV

The substantial drawbacks of BEVs are short driving range (about 100-200 miles), longer charging (refueling) time (4 to 8 hours for slow charging

and 30 min for fast charging), and large volume and heavy weight of battery pack [8].

HEV combines a conventional ICE propulsion system with an electric propulsion system consisting of energy storage system (ESS) and electric motor, as shown in Fig. 1.4. The incorporation of electric propulsion system allows the use of smaller engines than conventional ICE vehicles. The engine can be turned-off during idle or low speed states by utilizing the energy stored in the ESS [9]. The ESS can also assist the ICE drivetrain operating at the most efficient range thus enormously enhancing the fuel economy and reducing the emission [3].

PHEV is a one kind of HEVs with larger rechargeable energy storage that can be charged by connecting a plug to an external electric power source, which gives PHEVs a much larger all-electric range and reduces their petroleum consumption. As illustrated in Fig. 1.5, the ESS can be recharged either from the grid by plugging into an electrical outlet or by the ICE. The PHEVs batteries are capable of powering the vehicle purely on electricity at a normal speed over significant distances (approximately 40 miles) [10].

Due to government tax incentives and high oil prices, HEVs and PHEVs have already enjoyed commercial success. Since the first groundbreaking HEVs, Toyota Prius and Honda Insight, were introduced to the automotive market, a number of automakers initiated HEVs and PHEVs research programs and subsequently developed several vehicle models worldwide [11-12]. Commercially available HEVs include Toyota Prius, Toyota Highlander Hybrid, Toyota Camry Hybrid, Lexus RX 400h, Honda Insight, Honda Civic Hybrid, Honda Accord Hybrid, and Ford Escape Hybrid [13]. In August 2013, Toyota launched the 4<sup>th</sup> generation of the Prius and the Prius family reached global cumulative sales of 3.8 million units by June 2013 [11-12].

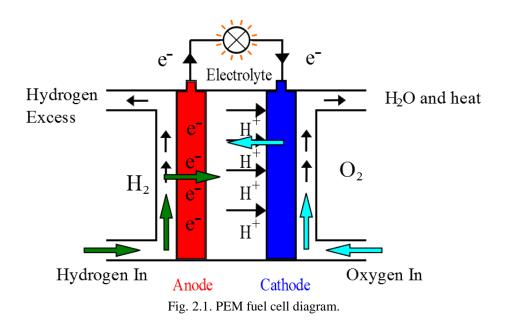

A typical architecture of a FCV is illustrated in Fig. 1.5. The hydrogen is either stored on board or obtained from reforming the hydrocarbon fuel such as gasoline, natural gas, methanol, or ethanol. This hydrogen rich gas from the reformer is fed to the anode of the fuel cell stack. The fuel cell stack generates electrical energy in dc form after reaction of hydrogen fuel and oxygen from air, i.e., oxidization. The dc output is converted to ac through a 3-phase inverter to drive electric motor. As long as continuity of the fuel supply is maintained, the electric motor can propel the vehicle quietly, smoothly, and efficiently. It requires overall less maintenance compared to ICE vehicles.

The comparison of the above-mentioned types of electric vehicles (EVs) is summarized in [14]. The predicted greenhouse gases, oil consumption and urban air pollution for different EVs scenarios over the 21<sup>st</sup> century for the US light duty vehicle fleet are compared. HEVs and PHEVs can contribute to reduce greenhouse gases emission only to very limited level. Similarly, HEVs and PHEVs powered by fuels are unlikely to reduce oil consumption considerably and remove urban air pollution completely. Overall, we can conclude that HEVs and PHEVs are not the ultimate solutions for energy crisis and emission problem. Because they still depend heavily on crude oil and emit considerable amount of greenhouse gas. To achieve the long-term goal of zero-carbon emission and substantially cut dependence on oil, BEVs and FCVs are considered as the most promising alternative powertrain technologies of future sustainable road transport system.

7

A comparison between BEVs and FCVs in terms of mass, volume, greenhouse gases, fueling time, energy efficiency, fueling infrastructure and cost is given in [14-15]. The recent advancements in battery technology still cannot satisfy BEVs with sufficient energy storage, driving range, fast charging (refueling) ability and low cost. With zero-emission, satisfied driving range, short refueling time, highest potential efficiency, and high reliability, FCVs exhibit significant potential in transportation. Although FCVs are quite promising to serve as next generation transportation system, they are still restricted by several challenges. These issues are briefly discussed below.

- Development of fuel cell stacks and related system: The polymer electrolyte fuel cell (PEFC), also known as the proton exchange membrane fuel cell (PEMFC) is the most popular for vehicle application. However, a few issues like optimal purification of hydrogen [16], components degradation, and durability [17-18], are under research and development. Fuel cell stack durability in realworld environments is currently about half of what is needed for commercialization [19]. The targets set by the US Department of Energy (DOE) for FCVs is to be 60% efficient, 30US\$/kW cost and a nominal lifetime of at least 5000h [19].

- Currently FCVs are more expensive than ICE vehicles and hybrid vehicles. According to report of US DOE, the fuel cell system cost projected to high-volume of 500,000 units per year is \$47/kW in 2012 [19]. To achieve widespread commercialization, the cost is the key bottleneck and must be reduced further to be economically competitive.

- 8

- The barriers of hydrogen production, storage, transmission and refueling infrastructures do not yet support the widespread adoption of FCVs.

- 4) Compressed hydrogen gas tank on FCVs acquires more space than a gasoline tank. Onboard hydrogen storage is challenging without sacrificing on space, weight, safety, and or cost of vehicles. New techniques like liquid storage at sub-zero temperatures or materialsbased storage are still under research [20].

Although there are currently no fuel cell cars available for commercial sale, several major automotive industries have been manufacturing and testing their FCVs. Since 2009, over 20 FCV demonstration cars such as Mazda 5 Hydrogen RE Hybrid, Volkswagen Caddy-Maxi HyMotion, Hyundai Tucsonix35 FCEV, Mercedes-Benz-F800 have been tested in labs [21-22]. USA and Canada have tested the FCVs on road too. Ballard designed fully integrated fuel cell modules delivering 75 kW and 150 kW for local bus transportation in London which operates up to 19 hours without refueling [23]. As one of the essential enabling technologies of FCVs, power electronic converters play a key role in the commercialization of FCVs, which motivated the research of this thesis.

### **1.3 Power Conditioning System Architecture of Fuel** Cell Vehicles

In FCVs, basically fuel cell stack oxidizes hydrogen gas and generates electrical energy in DC form. Power converters are responsible for conditioning the generated electrical energy to propel the vehicle smoothly and efficiently. Also, the power electronic converters should satisfy the ever growing auxiliary load demand like electrical steering, air-conditioning, information, entertainment etc. in the vehicle. Generally power electronics in FCVs need to accomplish the following tasks [13, 24]:

- Voltage conversion: Fuel cell is a typical low voltage high current source of energy. The low output voltage generated by the fuel cell needs to be boosted to suitable voltage level to drive electric motor for propulsion. In addition, voltage conversion between energy storage and traction inverter should be performed.

- Energy management: The energy flow from both fuel cell and energy storage system should be well managed to obtain optimal vehicle performance and overall reduced fuel consumption [25-26].

- Electronic control: Power electronics act as a controller for electric traction motor, fuel cell support system and ESS.

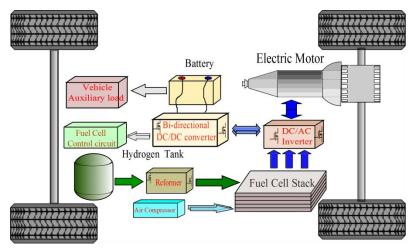

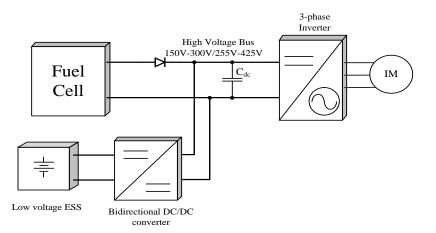

Four different power system architectures for FCVs are illustrated in Fig. 1.7 to Fig. 1.10 [27-28]. FCVs suffer from slow dynamic response to load variation due to their slow internal electrochemical and mechanical characteristics. Therefore, secondary source of energy storage that can deliver quick power is needed. As shown in Fig. 1.7 to Fig. 1.10, ESS such as battery or supercapacitor is usually utilized for cold start up, to absorb the regenerative braking energy and to achieve good transient performance.

Fig. 1.7 shows the conventional topology where fuel cell stack itself develops the variable high voltage dc bus [29-32]. High-voltage variable dc bus voltage of either 255V-425V [29-30] or 150-300V [31-32] from the fuel cell stack has

been proposed. A bidirectional DC/DC converter is used to boost low voltage ESS to match fuel cell dc bus voltage. A standard 3-phase inverter (traction inverter) is directly connected at fuel cell bus to invert the fuel cell stack voltage to drive the traction motor. This architecture is simple to realize and cost effective. The main issue with this topology is that fuel cell stack delivering high voltage needs to be selected and employed. However, the output voltage of fuel cell stack depicts a wide variation with the fuel flow, fuel pressure, and stack temperature. For example, the low fuel cell stack voltage corresponds to highest (rated) power and therefore supplies low voltage to traction inverter and motor at rated power. Design of efficient and compact bidirectional dc/dc converter to boost from low voltage ESS to higher variable voltage and maintaining high efficiency at low total harmonic distortion (THD) of three phase inverter whose dc link voltage is varying is a challenge. Besides, there is no galvanic isolation between fuel cell and the motor drive [33].

Fig. 1.7. Type 1, power system architecture of FCV with variable high voltage dc bus.

Fig. 1.8. Type 2, power system architecture of FCV with variable low voltage dc bus.

Fig. 1.9. Type 3, power system architecture of FCV with fixed high voltage dc bus.

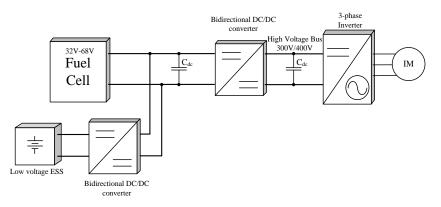

Fig. 1.8 (type 2) and Fig. 1.9 (type 3) show other two alternative architectures for FCV, where variable low voltage dc bus from fuel cell stack is adopted [27-28]. A fixed high voltage dc bus is developed. A front-end DC/DC converter is utilized to boost the low voltage from fuel cell stack to the peak value needed by the traction inverter. The difference between type 2 and 3 is that the low voltage ESS is directly connected through bidirectional DC/DC converter to the fuel cell stack for type 2 while for type 3 the ESS is connected to fixed high voltage dc bus. The challenge with type 2 is to design a bidirectional DC/DC converter which can maintain high and flat efficiency through wide variation of fuel cell stack voltage. For type 3, to design an efficient bidirectional DC/DC converter with a high boost ratio is difficult.

Fig. 1.10. Type 4, power system architecture of FCV with both fixed low voltage and fixed high voltage dc bus.

(b)

Fig. 1.11. Type 5, modified power system architecture of FCV. (a) Variable low voltage dc bus and high voltage pulsating dc bus, (b) fixed low voltage dc-link and high voltage pulsating dc bus.

In Fig. 1.10, an additional DC/DC converter is included to obtain a constant low voltage dc bus [28, 33]. The low voltage ESS is connected to fixed low voltage dc bus. Since the voltage gain of the bidirectional converter is nearly constant, it is easier to design the converter having maximum

efficiency. Constant dc voltage also simplifies control of 3-phase inverter and traction drive. However, the additional DC/DC converter may deteriorate the overall efficiency and will add to the cost and size. Pulsating high voltage dc bus without large electrolytic capacitor is proposed in [35-37] as shown by Fig. 1.11. Different hybrid modulation techniques have been introduced to control the front-end dc/pulsating dc converter and the back-end pulsating dc/ac converter, which can reduce the switching losses and increase the efficiency.

Low voltage fuel cell stack ranging from 32V-68V is more suitable for compact vehicles like fuel cell cars with power rating up 5kW. While for the high power rating (higher than 100kW) FCVs like fuel cell buses, high voltage fuel cell stack may be preferred [18]. Therefore, it is necessary to select and design a suitable architecture according to specific application requirements. Similar architectures as shown in Fig. 1.7 to Fig. 1.11 can also be employed in other low voltage high current applications such as solar and fuel cell based standalone UPS applications.

#### **1.4 Problem Definitions and Research Objectives**

As one of the essential enabling technologies, power electronics plays a vital role for low voltage high current applications. Major requirements for the power conditioning system are summarized as follows [27]:

Cost effective. Electrical and electronic system account for 20% to 30% of the total cost of a modern vehicle [13]. Power electronics is one of the essential enabling technologies that can provide an option to compensate the cost gap.

- 2) Low weight, small volume and high power density.

- High reliability and fault tolerance. Approximately 10-15 years life span is expected for the operation of power electronics.

- Modular and scalable. Modular and scalable design can help improve the manufacturability.

- 5) High efficiency.

- 6) Low electromagnetic interference (EMI). To increase the electromagnetic compatibility, soft-switching is generally preferred at high switching frequency.

- 7) Electric isolation.

Galvanic isolation is preferred to prevent electric leakage/electric shock.

Overall efficiency is of a major concern in these applications to utilize the fuel at the best and needs to be concretely addressed [38]. The overall purpose of the research is to develop low cost, high density, integrated and modular power electronics. The problems of existing research and corresponding specific objectives are pointed out as follows: