# DESIGN OF INTEGRATED NEURAL/MUSCULAR STIMULATORS

LIU XU

NATIONAL UNIVERSITY OF SINGAPORE

2014

# DESIGN OF INTEGRATED NEURAL/MUSCULAR STIMULATORS

LIU XU

(B.Eng. M.Eng. HUST, P.R.China)

## A THESIS SUBMITTED

## FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

# DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING

## NATIONAL UNIVERSITY OF SINGAPORE

2014

## DECLARATION

I hereby declare that the thesis is my original work and it has been written by me in its entirety. I have duly acknowledged all the sources of information which have been used in the thesis.

This thesis has also not been submitted for any degree in any university previously.

liuxu

Liu Xu

09 July 2014

### ACKNOWLEDGEMENT

First, I would like to thank my supervisor Associate Professor Xu Yong Ping. His wide knowledge and academic reputation, as well as his patient guidance and rigorous and industrious attitude, always inspire me during my PhD study in NUS. He has exposed me to the integrated circuit (IC) design. At later stage of my PhD study, I was attached to Institute of Microelectronics (IME) A\*Star Singapore. I would like to thank the guidance from my IME co-supervisors Dr. Je Minkyu and Dr. Yao Lei, as well as technical support from my IME colleague Mr. Li Peng, as well as other research staff.

I would like to thank Dr. Ng Kian Ann for his many suggestions and technical discussions, Mr. Teo Seow Miang and Ms. Zheng Huan Qun for their support in chip testing and design tools. I am also indebt to Assistant Professor Yen Shih-Cheng and Ms. Khadijah Yusoff for their support and assistance in the in-vivo animal experiments for chip performance validation. I would also like to thank all of my colleagues in the Signal Processing & VLSI Laboratory at NUS and colleagues in IME for their helpful discussion and knowledge sharing during the past years.

Last but not least, I want to thank my parents and wife for their selfless support throughout my studies.

## TABLE OF CONTENTS

| ACKNOWLEDGEMENTi                                                 |

|------------------------------------------------------------------|

| TABLE OF CONTENTSii                                              |

| SUMMARYv                                                         |

| LIST OF TABLES                                                   |

| LIST OF FIGURES viii                                             |

| LIST OF ABBREVIATIONSxii                                         |

| CHAPTER 1                                                        |

| INTRODUCTION1                                                    |

| 1.1 Background1                                                  |

| 1.1.1 Basic principles of Neural/Muscular Stimulation1           |

| 1.1.2 Design Consideration of Neural/Muscular Stimulation System |

| 1.2 Motivation                                                   |

| 1.3 Research Contributions                                       |

| 1.4 List of Publications10                                       |

| 1.5 Organization of the Thesis12                                 |

| CHAPTER 2                                                        |

| LITERATURE REVIEW                                                |

| 2.1 Power Efficient Neural/Muscular Stimulator13                 |

| 2.2 Stimulation-Artifact Suppressed Stimulator19                 |

| 2.2.1 Origin of Stimulation Artifact                             |

| 2.2.2 Stimulation Artifact Cancellation                                      |

|------------------------------------------------------------------------------|

| CHAPTER 3                                                                    |

| DESIGN OF NEURAL/MUSCULAR STIMULATOR FOR ENHANCED POWER                      |

| EFFICIENCY                                                                   |

| 3.1 Theoretical Analysis26                                                   |

| 3.1.1 Current Waveform for High Power Efficiency                             |

| 3.1.2 Exponentially Decaying Current Generation                              |

| 3.2 Implementation of Power-Efficient Stimulator with Exponentially Decaying |

| Current                                                                      |

| 3.2.1 DAC Design                                                             |

| 3.2.2 Current Copier and Exponentially Decaying Current Generation Circuit33 |

| 3.2.3 High-Voltage Output Stage and Active Charge Balancing Circuit42        |

| 3.2.4 Global Digital Controller                                              |

| 3.3 Measurement Results46                                                    |

| 3.3.1 Test Bench Measurement Results47                                       |

| 3.3.2 In-Vitro Measurement Results                                           |

| 3.3.3 In-Vivo Measurement Results                                            |

| 3.4 Summary                                                                  |

| CHAPTER 4                                                                    |

| DESIGN OF NEURAL/MUSCULAR STIMULATOR FOR ARTIFACT                            |

| CANCELLATION                                                                 |

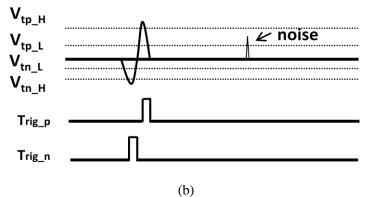

| 4.1 Proposed RTPPS for Artifact Cancellation60                               |

| 4.2 4-Channel Neural Recording and Stimulation System Implementation6 | 62 |

|-----------------------------------------------------------------------|----|

| 4.2.1 High-Voltage Artifact-Suppressed Stimulator                     | 64 |

| 4.2.2 Recording Front End and Action Potential Detector               | 64 |

| 4.2.3 Digital Control Block                                           | 66 |

| 4.3 Measurement Results                                               | 68 |

| 4.3.1 Bench-top Measurement Results                                   | 68 |

| 4.3.2 In-Vitro Test                                                   | 71 |

| 4.3.3 Animal Experiment                                               | 75 |

| 4.4 Summary                                                           | 81 |

| CHAPTER 5                                                             | 83 |

| CONCLUSION AND FUTURE WORKS                                           | 83 |

| 5.1 Conclusion                                                        | 83 |

| 5.2 Future work                                                       | 84 |

| BIBLIOGRAPHY                                                          | 86 |

### SUMMARY

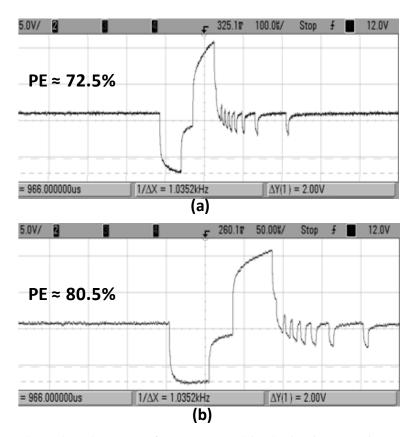

Neural/muscular stimulator has been used in medical therapies, as well as therapeutical devices. It delivers either current or voltage to the tissue through electrodes, evoking action potentials in the nerves or muscles. This thesis focuses on the power efficiency improvement of the neural/muscular stimulator and the cancellation of the artifacts introduced by the stimulation. A current-mode neural/muscular stimulator with an exponentially decaying stimulation current is first described. The use of exponentially decaying current makes the voltage on the stimulating electrode constant during the stimulation, which eliminates the headroom and increases the power efficiency. A simple exponentially decaying current generator is proposed based on Taylor series approximation and implemented in a 16-channel prototype stimulator IC. The prototype IC is fabricated in a 0.18-µm CMOS process with high-voltage LDMOS option, occupying a core area of  $1.65 \text{ mm} \times 1.65 \text{ mm}$ . The stimulator is tested with different loads, which mimics the electrode/tissue interface, and the measured results show that maximum stimulation power efficiency of 95.9% can be achieved at the output stage of the stimulator. Depending on the electrode impedance and stimulation current, the power efficiency can be improved by nearly 10% at the output stage, compared to traditional constant-current stimulators.

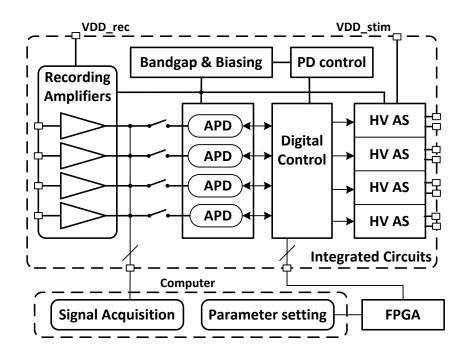

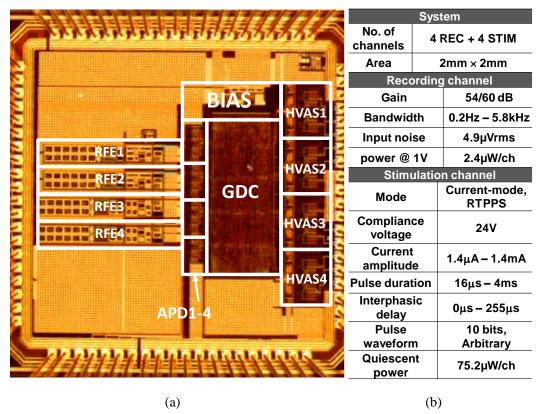

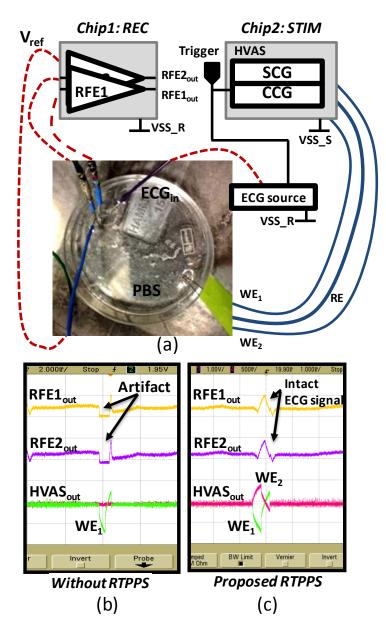

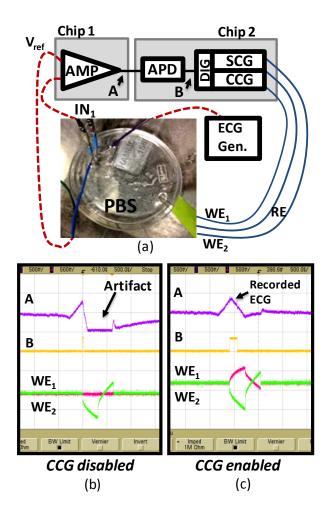

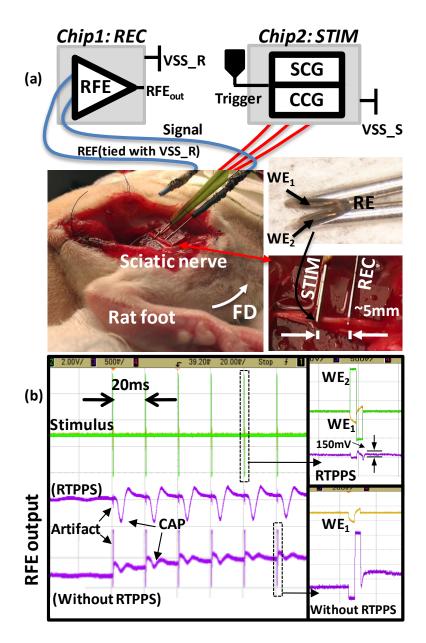

In the second part of the thesis, an artifact-suppression technique based on a referenced and tuned push-pull stimulation (RTPPS) scheme with a tri-polar electrode is presented. The stimulation pulses delivered to two working electrodes with a

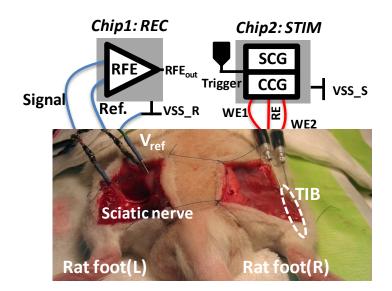

common reference electrode are complementary and thus one counteracts with the other to suppress the stimulation artifact. A prototype 4-channel integrated recording and stimulation system is designed to demonstrate the proposed artifact-suppression technique and implemented in 0.18-µm CMOS technology. The chip can be externally programmed and work in four different modes, namely, recording (REC), stimulation (STIM), closed-loop recording-stimulation (REC-STIM) and closed-loop stimulation-recording (STIM-REC). Both in-vitro and in-vivo experiments are carried out using rats as an animal model. The results show that the stimulation artifact can be greatly reduced compared to the conventional bipolar stimulation with no artifact cancellation. The amplitude of the measured stimulation artifact is suppressed to only 10%-20% of the neural spikes to be recorded in the animal experiment.

## LIST OF TABLES

| Table 1   | Efficacious stimulation properties                      | 5  |

|-----------|---------------------------------------------------------|----|

| Table 2   | Summary of stimulation-artifact cancellation techniques | 24 |

| Table 3.1 | Switched transistor array control logic                 | 41 |

| Table 3.2 | Parameters used in multi-channel stimulation test       | 50 |

| Table 3.3 | Performance comparison of current-mode stimulators      |    |

## LIST OF FIGURES

| Figure 1.1 Principle of electrical stimulation                                                                                                                                                                                                                                                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1.2 Strength-duration and charge-duration curves for initiation of an action potential                                                                                                                                                                                                                     |

| Figure 1.3 Electrical circuit models: (a) electrode-tissue interface, (b) simplified model4                                                                                                                                                                                                                       |

| Figure 1.4 Concept of (a) Bionic nerve link and (b) Epileptic seizure detection and suppression using a closed-loop neural recording and stimulation system7                                                                                                                                                      |

| Figure 2.1 Conceptual diagrams of the stimulators based on (a) voltage-mode, (b) charge-mode, and (c) current-mode stimulation                                                                                                                                                                                    |

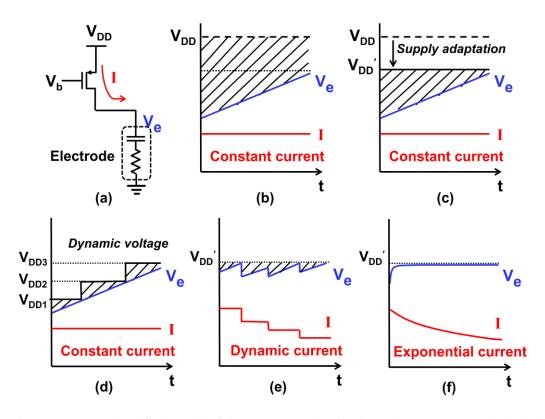

| Figure 2.2 (a) Simplified model of the current-mode stimulator, (b) Power wasted (shaded area) in conventional stimulators, (c) in supply adaptation method, (d) in dynamic voltage scaling (e) in dynamic current control, and (f) proposed time-continuous exponential current stimulation                      |

| Figure 2.3 A traditional current-mode stimulator15                                                                                                                                                                                                                                                                |

| Figure 2.4 Overall architecture of the power-efficient stimulation system using supply adaptation technique [14]                                                                                                                                                                                                  |

| Figure 2.5 Stimulator using dynamic voltage scaling technique [33]17                                                                                                                                                                                                                                              |

| Figure 2.6 Another stimulator using dynamic voltage scaling technique [39]18                                                                                                                                                                                                                                      |

| Figure 2.7 (a) Origin of the stimulation induced artifact and (b) recorded action potential with artifact                                                                                                                                                                                                         |

| Figure 2.8 Recording, stimulation, and artifact elimination system with blanking technique [22]                                                                                                                                                                                                                   |

| Figure 3.1 (a) Comparison between the ideal exponential current waveform and its $2^{nd}$ -order Taylor series approximation (exponentially decaying current waveform), (b) electrode voltage calculated by integrating the exponentially decaying current, (c) exponentially decaying current generation circuit |

| Figure 3.2 S                               | ystem archetecture of the 16-channel stimulator IC                                                                                                                                                                                                                                                           | .31        |

|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Figure 3.3 A                               | rchitecture of DAC current cells                                                                                                                                                                                                                                                                             | .32        |

| Figure 3.4 Se                              | chematic: (a) MSB current unit cell (b) LSB current unit cell                                                                                                                                                                                                                                                | .32        |

| -                                          | DAC sharing in multichannel stimulator, (b) schematic of a simplificircuit.                                                                                                                                                                                                                                  |            |

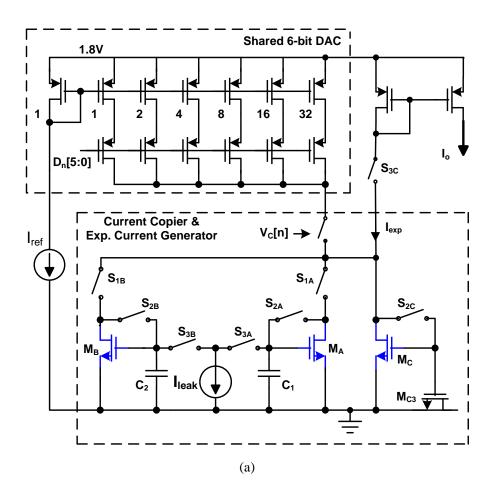

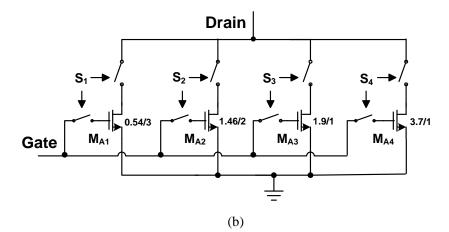

| exponentially                              | (a) Schematic of the shared 6-bit DAC and the current cop<br>decaying current generator in single-channel, (b) switched transis<br>in the current copier.                                                                                                                                                    | stor       |

| Figure 3.7 Si                              | imulation result of the required I <sub>leak</sub> vs. different loads                                                                                                                                                                                                                                       | .37        |

| Figure 3.8 U                               | Iltra low current generator                                                                                                                                                                                                                                                                                  | .37        |

| e                                          | imulation result: input current $(I_S)$ vs output current $(I_{leak})$ of current                                                                                                                                                                                                                            |            |

| generator circu                            | Operation of the current copier and exponentially decaying curruit: (a) current-replication phase, (b) cathodic stimulation phase, and ation phase.                                                                                                                                                          | l (c)      |

| Figure 3.11                                | Simulation Result: overdrive voltage vs. current                                                                                                                                                                                                                                                             | 41         |

| Figure 3.12                                | High-voltage output stage and active charge balancing circuit                                                                                                                                                                                                                                                | .42        |

|                                            | System operation: (a) digital control timing diagram, (b) comm<br>(c) and control state diagram                                                                                                                                                                                                              |            |

| Figure 3.14.                               | Die microphotograph of 16-channel stimulator IC                                                                                                                                                                                                                                                              | .46        |

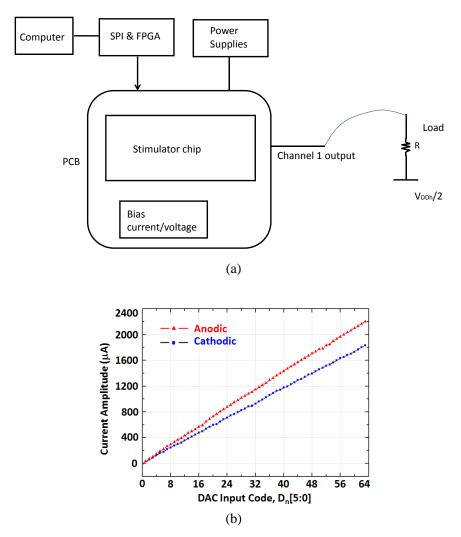

| -                                          | (a) Measurement setup. (b) Cathodic and anodic stimulation current varying the DAC input code                                                                                                                                                                                                                |            |

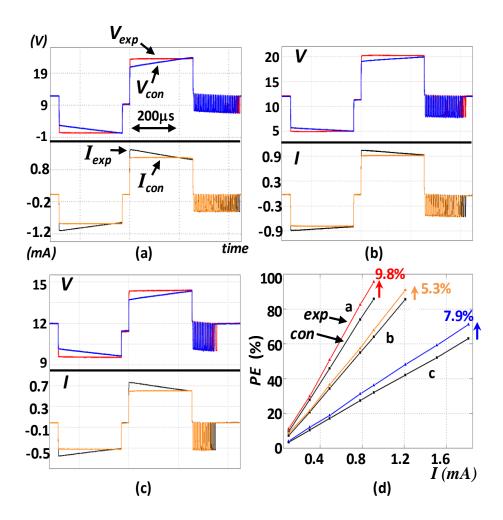

| (a) $R_L = 10 \text{ kG}$<br>impedance, (c | Measured waveforms of the stimulation currents and electrode voltage<br>and $C_L = 100 \text{ nF}$ load impedance, (b) $R_L = 8 \text{ k}\Omega$ and $C_L = 300 \text{ nF}$ l<br>c) $R_L = 3.7 \text{ k}\Omega$ and $C_L = 240 \text{ nF}$ load impedance, and (d) postimulation current at the output stage | oad<br>wer |

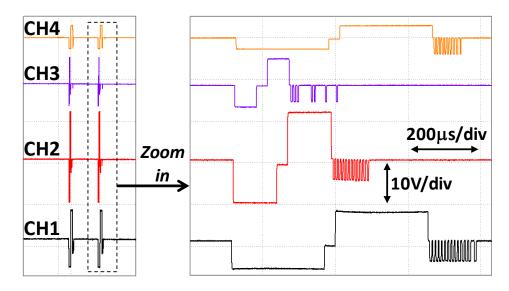

| Figure 3.17.                               | Measured multi-channel stimulation waveforms (zoomed-in plot on                                                                                                                                                                                                                                              | the        |

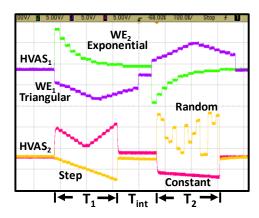

Figure 4.8 Arbitrary stimulation waveforms from two HVAS channels......70

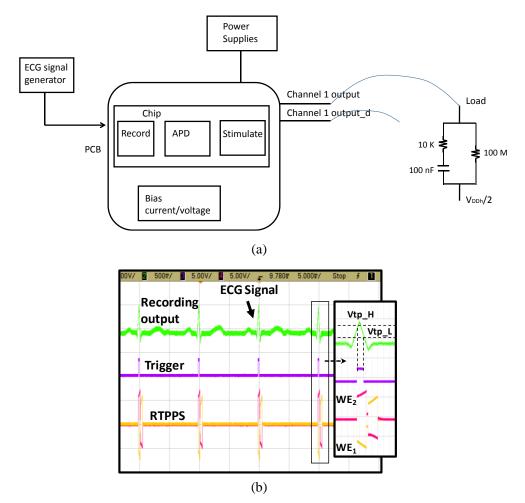

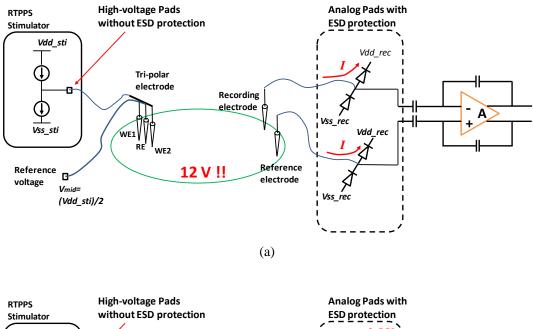

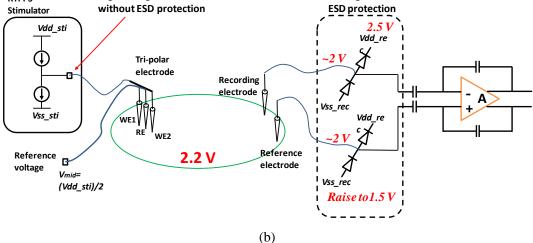

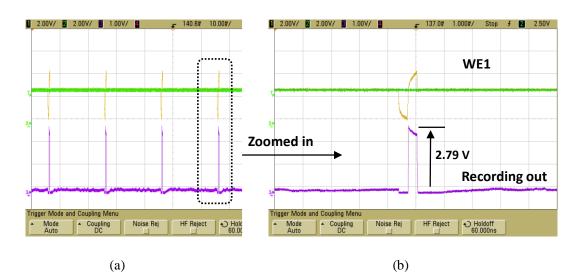

Figure 4.10 (a) ESD pad induced problem in closed-loop recording and stimulation

system. (b) Solution for experiment setup: raise ground......72

Figure 4.12 In-vitro test setup and results in REC-STIM mode. The top trace is the output signal from recording amplifier. Middle trace is APD output, and the bottom two traces are the voltages on two working stimulation electrodes......74

## LIST OF ABBREVIATIONS

| ACB  | Active Charge Balancing                     |

|------|---------------------------------------------|

| AP   | Action Potential                            |

| APD  | Action Potential Detector                   |

| BPF  | Band pass filter                            |

| САР  | Compound action potential                   |

| CCG  | Counter Current Generator                   |

| CE   | Counter Electrode                           |

| DAC  | Digital to Analog Convertor                 |

| DBS  | Deep brain stimulation                      |

| ECG  | Electrocardiogram                           |

| EEG  | Electroencephalogram                        |

| ESD  | Electro-Static Discharge                    |

| FES  | Functional Electrical Stimulation           |

| FF   | Flip-flop                                   |

| FPGA | Field Programmable Gate Array               |

| GDC  | Global digital control                      |

| HVAS | High-voltage artifact-suppressed stimulator |

| HVCD | High-Voltage Current Driver                 |

| LPF  | Low pass filter                             |

| LSB  | Least Significant Bit                       |

| MOS   | Metal-oxide semiconductor                  |

|-------|--------------------------------------------|

| MSB   | Most significant bit                       |

| PBS   | Phosphate buffered saline                  |

| PD    | Power down                                 |

| PE    | Power efficiency                           |

| RE    | Reference electrode                        |

| REC   | Recording                                  |

| RFE   | Recording front end                        |

| RTPPS | Referenced and Tuned Push-Pull Stimulation |

| SCG   | Stimulation Current Generator              |

| STIM  | Stimulation                                |

| WE    | Working Electrode                          |

# CHAPTER 1 INTRODUCTION

#### 1.1 Background

In the past few decades, driven by the increasing demands from biomedical field aiming to cure neurological diseases and improve the quality of patients' daily life, researchers began to take advantage of the semiconductor technology to develop miniaturized and power efficient stimulators for implantable applications. Examples of such applications include deep brain stimulation (DBS) [1], pain management and relief [2], retinal/cochlear/neural prosthesis [3-4], and functional electrical stimulation (FES) [5].

#### 1.1.1 Basic principles of Neural/Muscular Stimulation

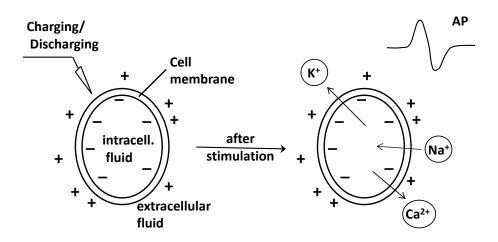

The aim of electrical stimulation of tissue (nerve or muscle) is to trigger action potentials (AP) in axons, which requires the artificial depolarization of some portion of the axon membrane to a threshold voltage [6]. As shown in Fig. 1.1, in one of a bunch of muscle cells, the membrane forms a boundary that separates fluids within and outside the cell. Ions composition in both intracellular and extracellular fluid creates a transmembrane potential of about -90 mV in normal state (the potential of extracellular fluid is taken as reference at 0V). During stimulation, electric current charges the extracellular fluid through the stimulation electrode and decrease the

Figure 1.1 Principle of electrical stimulation.

potential of the extracellular fluid. Once the transmembrane potential rises from -90 mV to a threshold voltage (around -55 mV) due to electric charging, an AP is produced. When an AP occurs, the channel on the membrane is open and  $K^+$  or  $Ca^{2+}$  ions go out of the cell until the membrane potential recovers to its rest state.

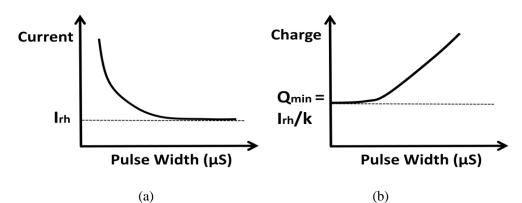

The relationship between the stimulation current sufficient for triggering an action potential and the stimulation duration is shown in Fig. 1.2(a). The threshold current  $I_{th}$ decreases with increasing stimulation pulse width. The minimum required stimulation current is called the rheobase current ( $I_{rh}$ ). The following relationship [7] has been derived experimentally to quantify the strength-duration curve:

$$I_{th} = \frac{I_{rh}}{1 - \exp(-W / \tau_m)}$$

where  $I_{th}$  is the current required to reach threshold,  $I_{rh}$  is the rheobase current, W is the stimulation pulse width, and  $\tau_m$  is the membrane time constant. Fig. 1.2(b) shows the charge-duration curve, which plots the threshold charge  $Q_{th} = I_{th}W$  versus

Figure 1.2 Strength-duration and charge-duration curves for initiation of an action potential.

stimulation pulse width. It is found that an action potential can be excited either by a minimum current with a certain pulse width or a minimum amount of charge injected.

Monophasic and biphasic rectangular waveforms are two widely used stimulation waveforms in existing stimulators. In monophasic stimulation, a negative current pulse is generated to excite the tissue and an action potential is produced. Monophasic stimulation is effective to initiate an AP but it may damage the tissue and electrodes during long period stimulation due to the accumulated residual charge and electrochemical reactions. In biphasic stimulation, the output is a negative current pulse followed by a positive one. The first pulse (negative pulse) elicits the desired physiological effect and produces an AP, and the second pulse (positive pulse) reverses the direction of electrochemical processes occurred during the cathodic stimulating phase. Compared to monophasic stimulation, the biphasic stimulation greatly reduces the chance of tissue damage. In addition to aforementioned waveforms, non-rectangular stimulus waveforms have also been proposed, which may

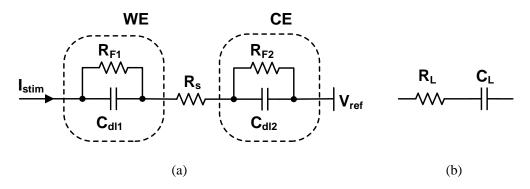

Figure 1.3 Electrical circuit models: (a) electrode-tissue interface, (b) simplified model.

offer safety benefits while maintaining stimulation efficacy [8].

Electrode materials used in neural stimulation should be biocompatible and non-toxic, and should have large charge storage capacity. Platinum (Pt), gold (Au), iridium (Ir), and palladium (Pd) have been commonly used for fabricating stimulation electrodes due to their relative resistance to corrosion. Especially, platinum and platinum-iridium alloys are common materials used for electrical stimulation of excitable tissue [6]. In general cases, two electrodes are placed in a tissue and electrical current passes from one electrode to another through the tissue. The electrode-tissue interface consists of a working electrode (WE) and a counter electrode (CE), as modeled in Fig. 1.3(a).  $R_S$  is solution resistance which exists between two electrodes.  $C_{d11}$  and  $C_{d12}$  are the double layer capacitors representing charge storage.  $R_{FI}$  and  $R_{F2}$  are Faradaic resistors which are very large and can be neglected. The double layer capacitor of counter electrode ( $C_{d12}$ ) is rather large and can also be neglected [9]. Therefore, the electrode-tissue interface can be simply modeled as a series resistor  $R_L$  and a series capacitor  $C_L$ , as shown in Fig. 1.3 (b). The value of  $R_L$  and  $C_L$  depend on the tissue impedance as well as the electrode properties.

There are two kinds of damages that could occur during stimulation: electrode corrosion and tissue damage.

$$2H_2O \rightarrow O^2 \uparrow + 4H^+ + 4e^-$$

(oxidation of water) (1-1)

$$Pt + 4Cl^{-} \rightarrow [PtCl4]^{2-} + 2e^{-}$$

(corrosion) (1-2)

In reaction (1-1), water molecules are irreversibly oxidized, forming oxygen gas and hydrogen ions, and thus lowering the pH. Reaction (1-2) is the corrosion of a platinum electrode in a chloride-containing media. Irreversible Faradaic reactions result in a net change in the chemical environment, potentially creating chemical species that are damaging to tissue or the electrode [6]. Studies have shown that both charge per phase and charge density are important factors in determining neural damage [10]. Some studies showed that charge-balanced biphasic stimulation does not cause significant tissue damage at levels up to 2  $\mu$ C/mm<sup>2</sup> per pulse. However, in order to prevent electrode corrosion, the charge-balanced waveform must not exceed 0.4  $\mu$ C/mm<sup>2</sup> per

Table 1. Efficacious stimulation properties

| Stimulation duration   | tens - hundreds μs                       |

|------------------------|------------------------------------------|

| Stimuli source         | minimum current or charge                |

| Waveform               | balanced and biphasic                    |

| Interphasic delay time | 0 - 100 μs                               |

| Electrode-tissue model | a series capacitor and a series resistor |

| Safe level             | 0.4 µC/mm <sup>2</sup> /phase            |

pulse, otherwise the electrode potential is driven to damaging positive potentials during the anodic (reversal) phase and interphasic delay time [11-12]. The electrode potential must be kept within a potential window (safety window) where irreversible electrochemical reactions do not happen at levels that are intolerable to the physiological system or the electrode [6]. Current density in each stimulation cycle also affects the damage on tissue. It is concluded that under the experimental conditions used in a reported study, the Q value (charge per phase) was the most important stimulus value in predicting neural damage. The level of 0.3 - 0.4  $\mu$ C/ph is demonstrated to be safe in long time stimulation [13]. Table I summarizes the efficacious and safe stimulation parameters.

#### **1.1.2 Design Consideration of Neural/Muscular Stimulation System**

Most neural/muscular stimulation systems consist of voltage/current generation circuit, output driver, and digital control circuit. One of the major concerns in developing implantable stimulation system is the power efficiency, which is defined as the ratio of power delivered to the load ( $P_{load}$ ) to the total power consumed by the stimulator ( $P_{tot}$ ). Stimulation power efficiency is becoming increasingly important due to the limited power budget in the implantable circuit and systems nowadays. It determines the battery lifetime or the required coil size for wireless power transfer. Stimulator with high power-efficiency also generates less heat and reduces the risk of tissue damage [14]. The techniques of improving power-efficiency of the stimulator will be discussed in chapter 2.

Another concern is the stimulation artifact. It is known that neural/muscular stimulators have been mostly applied in neural prosthesis systems, and neural recording is also involved in these applications to sense and generate trigger signal for stimulation or to provide assessment of stimulation efficacy and tissue status to enable closed-loop control for stimulator or simultaneous neural recording and stimulation

Figure 1.4 Concept of (a) Bionic neural link and (b) Epileptic seizure detection and suppression using a closed-loop neural recording and stimulation system.

[1], [15-22]. In aforementioned applications, the stimulation induced artifact usually exists and is an undesired signal recorded during stimulation. As the artifact voltage is overwhelmingly large compared with the neural signals (a few tens to several

hundreds of millivolts), the artifact could easily corrupt the neural signal and overload the recording amplifier. Consequently it affects the quality of neural recording and neural spike detection. In the applications where the stimulation is controlled by the action potential (AP), such as the peripheral nerve prosthesis in [19], when the AP is detected, it triggers the stimulator and stimulates the muscle, as shown in Fig. 1.4(a). The large stimulation pulse causes the artifact which is subsequently picked up by the recording amplifier as a false AP and a false stimulation will be triggered. The situation is even worse in multi-channel neural recording and stimulation system [23]. In the closed-loop neural recording and stimulation application, such as epileptic seizure detection and suppression, when epileptic seizure episode in EEG is detected, the stimulator is triggered and generates pulses to stimulate certain region in the brain and suppress the epileptic seizure [24-26], as shown in Fig. 1.4(b). To avoid stimulation induced artifact, the recording amplifier has to be reset when artifact is detected, and the normal recording can only be resumed after the stimulation when the stimulator is turned off [27].

### **1.2** Motivation

As mentioned before, power efficiency of the neural/muscular stimulator is an important performance and needs to be improved. While, other performances such as chip area, safety, and stimulation effectiveness of neural/muscular stimulator also need to be considered and balanced in circuit design. Besides, stimulation artifact is

always a problem existing in the applications of closed-loop neural prosthesis systems. Therefore, this work focuses on two problems, namely, the power-efficiency of the neural/muscular stimulators and the stimulation-artifact cancellation. The objectives are (1) to develop a power efficient neural/muscular stimulator, in particular, to eliminate the headroom existing in the stimulators that employ constant current pulse stimulation, without sacrificing other performance of the stimulator, and (2) to suppress the stimulation induced artifact without the need to disable the recording amplifier in recording/stimulation systems.

### **1.3** Research Contributions

A technique to further enhance the power efficiency of the output stage of the stimulator is proposed, in which an exponential stimulation current is employed. The proposed method eliminates the remaining headroom at the output stage and can also be employed together with the supply adaptation technique to obtain the maximum power efficiency. The proposed technique is demonstrated in a prototype 16-channel stimulator with a novel exponential current generator. In addition, the stimulator developed in this research integrates many functions on chip, including high voltage compliance, active charge balance, high power efficiency and small chip area. Maximum stimulation power efficiency of 95.9% can be achieved at the output stage of the stimulator, which is higher than most previous current-mode stimulators. Depending on the electrode impedance and stimulation current, the power efficiency

can be further improved by nearly 10% at the output stage, compared to traditional constant-current stimulator.

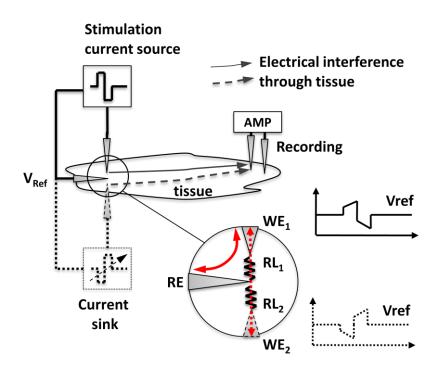

A stimulation artifact cancellation technique with a tri-polar electrode using referenced and tuned push-pull stimulation (RTPPS) scheme is also proposed to suppress the artifact with no blanking of the recording channels is needed. Unlike the previously reported artifact suppression techniques, the RTPPS cancels the artifact at the stimulation site before it propagates to the recording front-end. The RTPPS uses a tri-polar stimulation configuration with two working electrodes and one reference electrode. The stimulation currents delivered by two working electrodes are complement to each other. By doing so, the impact of large stimulation voltage fluctuation propagated to the recording site can be significantly reduced. The proposed concept is demonstrated with a prototype integrated 4-channel closed-loop neural recording/stimulation system in both in-vitro and in-vivo experiments.

### **1.4 List of Publications**

The following publications from this study have been either published or submitted.

<sup>[1] &</sup>lt;u>Xu Liu</u>, Lei Yao, et al., "A 16-channel 24-V 1.8-mA power efficiency enhanced neural/muscular Stimulator with exponentially decaying stimulation current," *IEEE Int. Symposium on Circ. and Syst.*, 2015, accepted.

[2] <u>Xu Liu</u>, Lei Yao, et al., "Stimulation artifact suppression with a referenced and tuned push-pull stimulator," submitted.

[3] <u>Xu Liu</u>, Lei Yao, Minkyu Je, Ng Kian Ann, Yong Ping Xu, "An artifact-suppressed stimulator for neural recording and stimulation system", *Singapore provisional application patent*, IME ref: PAT12-071/MMD-009, filed, Sep. 2012.

[4] Lei Yao, J. Zhao, P. Li, <u>Xu Liu</u>, Y. P. Xu, M. Je, "Implantable stimulator for biomedical applications", *IEEE MTT-S International Microwave Workshop Series on RF and Wireless Technologies for Biomedical and Healthcare Applications (IMWS-BIO)*, Dec. 2013, pp. 1-3.

[5] K.A. Ng, <u>Xu Liu</u>, Jianming Zhao, Li Xuchuan, Shih-Cheng Yen, Minkyu Je, Yong Ping Xu, Ter Chyan Tan, "An inductively powered CMOS multichannel bionic neural link for peripheral nerve function restoration," *IEEE Asian Solid State Circuits Conference (A-SSCC)*, 2012, pp. 181 – 184.

[6] Yong Ping Xu, Shih-Cheng Yen, K.A. Ng, <u>Xu Liu</u>, Ter Chyan Tan, "A bionic neural link for peripheral nerve repair," *IEEE Annu. Int. Conf. Eng. in Medicine and Biology Society (EMBC)*, 2012, pp. 1335 – 1338.

[7] J.Y.J. Tan, <u>Xu Liu</u>, K. H. Wee, Shih-Cheng Yen, Yong Ping Xu, T.C. Tan, "A monolithic programmable nerve/muscle stimulator," *IEEE Annu. Int. Conf. Eng. in Medicine and Biology Society (EMBC)*, 2011, pp. 511 – 514.

[8] J.Y.J. Tan, <u>Xu Liu</u>, K. H. Wee, Shih-Cheng Yen, Yong Ping Xu, "A programmable muscle stimulator based on dual-slope charge balance," *IEEE Asian Solid State Circuits Conference* (A-SSCC), 2011, pp. 197 – 200.

### **1.5** Organization of the Thesis

The organization of this thesis is as follows:

Chapter 2 presents the literature review on recent advances in power-efficient neural/muscular stimulator, and artifact-suppressed closed-loop stimulation and recording system. Chapter 3 deals with the design and implementation of the proposed power efficient neural/muscular stimulator and measurement results. Chapter 4 describes the design and implementation of artifact-suppressed neural/muscular stimulator, as well as the in vitro and in vivo experiment results. Conclusion and future work are presented in Chapter 5.

# CHAPTER 2 LITERATURE REVIEW

### 2.1 Power Efficient Neural/Muscular Stimulator

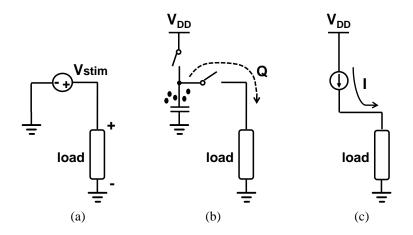

The neural or muscular stimulation can be performed in voltage, charge or current mode, as shown in Fig. 2.1. The voltage-mode stimulator shown in Fig. 2.1(a) generates a voltage directly on the tissue load. If only the output stage is considered, the power efficiency of the stimulator is given by

$$PE(t) = \frac{P_{load}(t)}{P_o(t)} = \frac{V_{load}(t) \cdot I_{load}(t)}{V_{stim}(t) \cdot I_o(t)} = \frac{V_{load}(t)}{V_{stim}(t)}$$

(2-1)

in which  $V_{load}(t)$  is the voltage over the load,  $V_{stim}(t)$  is the stimulation voltage and  $I_o(t)$ is the resultant current in the output stage, respectively. It is known that the voltage-mode stimulation provides the highest power efficiency [28-30] because ideally  $V_{load}$  equals to  $V_{stim}$  at the output stage of the stimulator. Nonetheless, its

Figure 2.1 Conceptual diagrams of the stimulators based on (a) voltage-mode, (b) charge-mode, and (c) current-mode stimulation.

Figure 2.2. (a) Simplified model of the current-mode stimulator, (b) Power wasted (shaded area) in conventional stimulators (c) in supply adaptation method, (d) in dynamic voltage scaling (e) in dynamic current control, and (f) proposed time-continuous exponential current stimulation.

uncontrolled or inaccurately controlled current and charge injection makes the voltage-mode stimulation inappropriate for clinical applications. The charge-mode stimulation as shown in Fig. 2.1(b) has accurate control over the amount of injected charge. However, it requires large capacitors ( $\sim\mu$ F), which prevents its adoption in implantable applications particularly when the multi-channel stimulation is required. The above-mentioned deficiencies of voltage-mode and charge-mode stimulation methods make the current-mode stimulation the most widely adopted method in biomedical applications [5], [31-36].

However, traditional current-mode stimulator with constant stimulation current

usually has the lowest power efficiency compared to voltage-mode and charge-mode stimulators [30], [32]. This is because the power efficiency of current-mode stimulators depends on the load (electrode) impedances and degrades dramatically when the voltage across the load  $V_{load}(t)$  is low, as illustrated in Fig. 2.2(a) and (b). The shaded headroom area indicates the power wasted by the stimulation circuit, which reduces the overall power efficiency of the stimulator.

Fig. 2.3 A traditional current-mode stimulator [23].

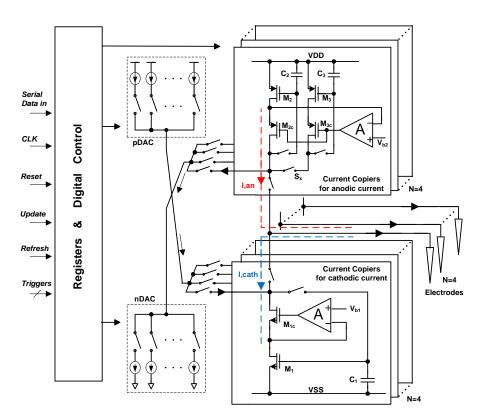

Fig. 2.3 shows a general neural/muscular stimulator [23]. It contains a digital control block, two DACs, and two groups of current copiers. Amplifiers are used at the output branch to increase the output impedance. Constant anodic and cathodic current can be generated and output to the electrodes. A single power supply of 3.3V is used for the

chip. As mentioned previously, the power efficiency of this traditional constant current stimulator is not high due to the headroom across transistors  $M_1$  and  $M_2$ .

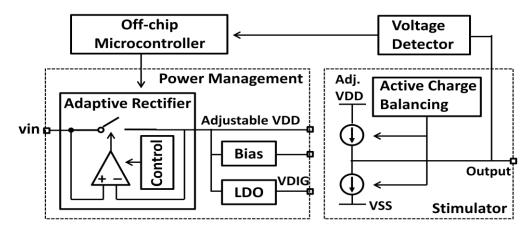

In order to overcome this drawback, that is, to eliminate the shaded area shown in Fig. 2.2(b), several techniques have been reported. A supply adaptation technique was proposed, in which the supply voltage is adjusted according to the maximum voltage on the electrode [14], [37]. Its system architecture is shown in Fig. 2.4. The adaptive rectifier in the power management circuit can output adjustable supply voltage ranging from 2.5 V to 4.6 V (at 2.8 mA loading) to power the stimulator. The desired supply voltage is determined by the load maximum voltage during stimulation

Figure 2.4 Overall architecture of the power-efficient stimulation system using supply adaptation technique [14].

through the voltage detector and controlled by an off-chip microcontroller. The active charge balancing circuit in the stimulator removes the residual charge after each stimulation pulse to prevent tissue damage. As indicated in Fig. 2.2(c), this power-efficient stimulator using supply adaptation technique reduces the shaded area, but not completely. Dynamic voltage and current scaling techniques have been proposed to further improve the PE by adjusting the supply voltage [33], [38] or the stimulation current [39] in number of steps, as shown in Fig. 2.2(d) and (e). However the shaded area still cannot be completely eliminated unless a large number of steps is used, which requires more control circuits and computation resources to achieve optimal power efficiency.

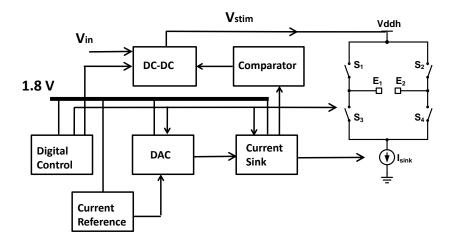

The stimulator [33] using dynamic voltage scaling techniques is shown in Fig. 2.5. A DC-DC converter providing 3V, 6V, 9V and 12V supply for stimulation is designed. During stimulation, the electrode voltage is detected and compared to different reference voltages, and meanwhile the corresponding stimulation voltage (Vstim) is chosen and applied. Power efficiency can be improved by using this dynamic voltage scaling technique. Besides non-ideal power efficiency of DC-DC converter, the

Fig. 2.5 Stimulator using dynamic voltage scaling technique [33].

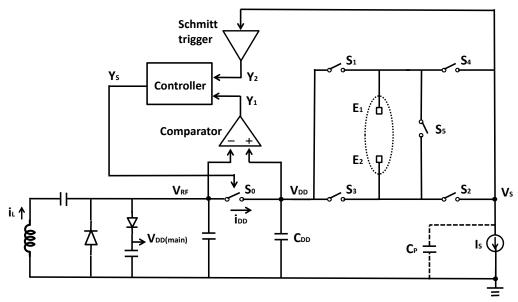

limited number of voltage steps still make the stimulator unable to completely remove the headroom, as shown in Fig. 2.2(d). Another stimulator [39] shown in Fig. 2.6 using dynamic voltage scaling technique is proposed trying to further improve the power efficiency at the output stage. The supply voltage  $V_{DD}$  of the electrode driver is generated from rectified voltage ( $V_{RF}$ ) separately by a regulation switch (S<sub>0</sub>). A capacitor ( $C_{DD}$ ) reduces the ripple on  $V_{DD}$ . A continuous-time comparator, a Schmitt trigger and a controller constitute a feedback loop, which is active throughout all RF cycles of each stimulation period. The comparator compares  $V_{RF}$  with  $V_{DD}$ . The Schmitt trigger compares Vs with an upper threshold and a lower threshold. The binary output signals  $Y_1$  and  $Y_2$  of these two units are fed into the controller, which, in turn, drives S<sub>0</sub> with a binary output signal  $Y_S$ . During stimulation, the voltage Vs is kept within a very small window similar to Ve as shown in Fig. 2.2(e). The headroom voltage across current source (Is) can be adjusted to a small value, as such, the power efficiency is improved. However, to achieve a very small ripple of Vs, capacitor CDD must be very large (1.5 nF, in their

Fig. 2.6 Another stimulator using dynamic voltage scaling technique [39].

design), making the stimulator not suitable for implantable applications. Besides, the

power efficiency is still not completely optimized due to the ripple on Vs.

In this work, a technique that uses exponentially decaying stimulation current to eliminate the headroom and improve the power efficiency of the stimulator is proposed and will be described in Chapter 3. With an exponentially decaying stimulation current, as shown in Fig. 2.2(f), the voltage on the stimulation electrode can be made relatively constant and thus minimizes the power wasted in the triangular shaded area (as in Fig. 2.2(b) and (c)) which is caused by the capacitive loading from the electrode. The proposed method can also be employed together with the supply adaptation technique (as in Fig. 2.2(c)) to obtain the maximum power efficiency.

#### 2.2 Stimulation-Artifact Suppressed Stimulator

#### **2.2.1 Origin of Stimulation Artifact**

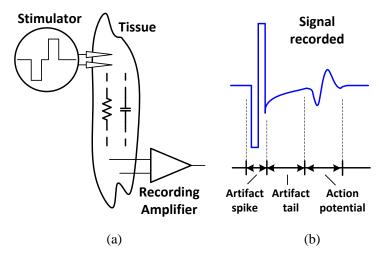

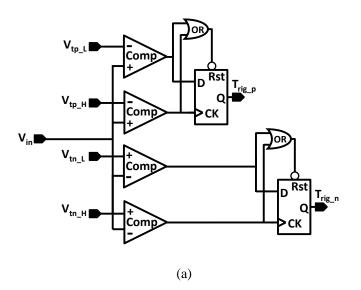

Most neural/muscular recording and stimulation systems consist of multiple recording and stimulation channels, action potential detection and data processing circuit, stimulation circuitry, and electrodes. During the operation, the large stimulation current causes the tissue potential to change and this tissue potential fluctuation will propagate to the recording site and cause artifacts [40] as illustrated in Fig. 2.7. For bipolar stimulation, there are two stimulation electrodes, namely, a working and a reference electrode. During stimulation, most of the biphasic current flows between the working and the reference electrode through the tissue being stimulated. In the cathodic phase, the electric potential near working electrode decreases since the stimulator sinks current from the reference electrode. While in the anodic phase, the electric potential near working electrode increases since the stimulator sources current to the reference electrode through the tissue-electrode interface. The amplitude of this

Figure 2.7 (a) Origin of the stimulation induced artifact and (b) recorded action potential with artifact.

voltage variation is usually from several hundred millivolts to several volts. It depends on several factors, including electrode impedance and power-supply voltage at the output stage of the stimulator. Furthermore, this large voltage variation at the stimulation site can propagate to the recording front end (RFE) through the tissue which is a volume conductor. Although the coupled voltage signal is attenuated when reaching the recording sites, it is still much larger than the neural signal to be recorded, and hence it could saturate the recording amplifier, causing the artifact [41-42].

Fig. 2.7 (b) illustrates the recorded stimulation artifact waveform in a typical neural recording and stimulation system, in which the evoked action potential (AP) is

recorded after an undesired artifact spike. The RFE is initially saturated by the large stimulation artifact, followed by a long artifact tail before the amplifier is fully recovered and ready to record next AP [40]. The RFE output becomes saturated because of its high gain (usually 500 – 1000 times) and the long recovery time is required due to the time constant of the high-pass filter in RFE, which is usually very large (2-10 ms) in order to block the DC offset without attenuating the useful low-frequency signal. As a result, the next AP can only be observed after the recording amplifier fully recovers. Such a stimulation artifact can be observed in most of the closed-loop recording and stimulation systems [19-23], [43].

Though the amplitude of the recorded artifact spike is determined by several factors such as distance between recording and stimulation sites, gain of the amplifier, and electrode impedance [41-42], [44-45] it is typically hundreds of millivolts that is ten to hundred times higher than the amplitude of the neural signals recorded.

### 2.2.2 Stimulation Artifact Cancellation

Several stimulation artifact cancellation techniques have been reported previously. Blanking technique [20], [46-51] and digital signal processing [52] have been used to cancel the artifact. In the blanking technique, the RFE is switched off or disabled (input is short to ground) during stimulation period and turned on after the stimulation is completed to continue the recording. As shown in Fig. 2.8, the recording amplifier and two capacitors ( $C_I$  and  $C_F$ ) are used to amplify nerve signals. A very large resistor R<sub>F</sub> is used in the feedback path to provide a dc current path to bias the input. The discharge amplifier helps the electrode return to its pre-stimulation voltage after stimulation. The recording amplifier is disabled during stimulation and enabled after 2 ms when the stimulation ends [22]. This method is effective in some applications, such as EMG signal observation, because the evoked neural spike usually emerges with latency causing no overlap between artifact spike and AP. But in some other applications, such as neural prosthesis or deep brain stimulation (DBS), the neural responses in the cathodic and anodic stimulation phases also need to be recorded. In such applications, if blanking technique is employed, the neural signals during the "blanking" period cannot be recorded and thus some important neural information may be missed.

Figure 2.8 Recording, stimulation, and artifact elimination system with blanking technique [22].

The artifact cancellation using digital signal processing can be divided into two categories: post-signal processing and real-time signal processing. In post-signal processing, the recorded neural signal together with artifact is acquired. The artifact is subsequently removed by specific algorithms such as subtraction, time-delayed de-correlation and adaptive filtering in digital domain, either in hardware of software [53-58]. One disadvantage of post-signal processing is that the RFE must have large dynamic range so that the artifact does not saturate the amplifier. In real-time signal processing for artifact cancellation, the artifact can be removed in real-time by using analog or digital signal processing implemented in hardware [59-61]. The merit of removing artifact using digital processing compared with blanking is that no neural spikes are missing in the recording, but they are computationally intensive.

Another artifact suppressing technique reported is the localized stimulation [62-63], where the stimulation current returns to a local ground. Although this reduces the artifact amplitude at input of the recording amplifier, and allows the amplifier to quickly recover to the normal state, the artifact is still not effectively suppressed especially when the large stimulation current is applied. Its effectiveness also depends on the distance between recording site and stimulation site.

Several other artifact cancellation methods have also been proposed. In [64], neural recording is carried out only in the mid-phase between cathodic and anodic stimulation phases to avoid the artifact. In [65-66], high-frequency short-duration

pulses or other specific patterns are adopted for stimulation. However the stimulation parameters (i.e. pulse width, amplitude, and frequency) are usually determined by the application and not by the artifact cancellation.

Aforementioned solutions for artifact suppression are mainly on the effort of recording amplifier design or data processing. To realize a bidirectional stimulation and recording system where both recording-stimulation and stimulation-recording mode can be applied, we need to suppress both artifact-spike and artifact-tail. If the stimulation artifact can be cancelled at the stimulation site, we could avoid disabling (blanking) the RFE and record all neural spikes during stimulation, and simplify the

| Artifact<br>Cancellation<br>Technique                | Advantage                                                                       | Disadvantage                                                                                                                        |

|------------------------------------------------------|---------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| Blanking                                             | Easy to implement,<br>Save computation resource.                                | No recording in blanking period.                                                                                                    |

| Localized stimulation                                | No extra circuit is used,<br>Save computation resource.                         | Effectiveness depends on current<br>amplitude and distance between<br>electrodes.<br>Require more than one reference<br>electrodes. |

| Digital signal processing                            | No data/signal missing.                                                         | Require large dynamic range in RFE<br>and extra software/ hardware<br>implementation,<br>Computationally intensive.                 |

| Special recording/<br>stimulation pattern<br>control | No extra circuit is used,<br>No data/signal miss,<br>Save computation resource. | Limited flexibility of stimulation parameters.                                                                                      |

Table 2. Summary of stimulation-artifact cancellation techniques

backend digital processing and save time/computation resource. Table 2 summarizes the advantages and disadvantages of the existing stimulation-artifact cancellation techniques.

# **CHAPTER 3**

# DESIGN OF NEURAL/MUSCULAR STIMULATOR FOR ENHANCED POWER EFFICIENCY

# **3.1 Theoretical Analysis**

### **3.1.1 Current Waveform for High Power Efficiency**

To deliver enough current to the high impedance load, the output stage of the current-mode stimulator is used to amplify the stimulation current and increase output voltage compliance. The output stage of the stimulator is usually powered under a supply from 10 V to 20 V and the rest of the circuits are operating under a low supply voltage in order to reduce the power consumption. With a current amplification ratio of 6 to 10, nearly 95% - 99% of the power is consumed at the output stage during stimulation. If only the output stage is considered, the power efficiency at the output stage can be calculated by

$$PE(t) = \frac{P_{load}(t)}{P_{a}(t)} = \frac{V_{e}(t) \cdot I_{stim}(t)}{V_{DD} \cdot I_{stim}(t)} = \frac{V_{e}(t)}{V_{DD}},$$

(3-1)

where  $I_{stim}$  is the stimulation current,  $V_{DD}$  is the supply voltage of the output stage.  $V_e(t)$  is determined by the load impedance and stimulation current, which is always smaller than  $V_{DD}$ . Thus the current-mode stimulator usually has the lowest power efficiency.

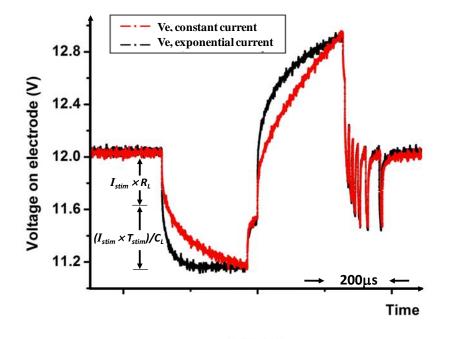

In order to maximize the power efficiency, a constant voltage close to  $V_{DD}$  is preferred on the stimulation electrode. Based on the circuit model in Fig. 2.2(a), the voltage on the load during stimulation is

$$V_{e}(t) = I(t) \times R_{L} + \int_{0}^{t} \frac{I(t)}{C_{L}} dt$$

(3-2)

where  $V_e(t)$ , I(t),  $R_L$  and  $C_L$  are the electrode voltage, stimulation current, load resistance, and load capacitance, respectively. The constant load voltage can be realized during stimulation when the following equation is fulfilled:

$$\frac{dV_e(t)}{dt} = \frac{d}{dt} \left( I(t) \times R_L + \int_0^t \frac{I(t)}{C_L} dt \right) = 0$$

(3-3)

By solving (3-3), I(t) can be expressed as

$$I(t) = I_0 \operatorname{exp}\left(\frac{t}{R_L C_L}\right)$$

(3-4)

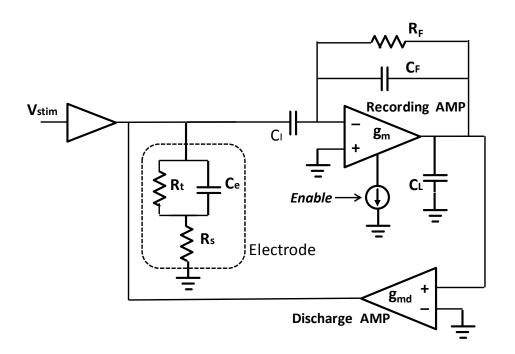

where  $I_0$  is the initial value of the stimulation current. The exponentially decaying current in (3-4) can be expressed by its Taylor Series. Considering that ( $t/R_LC_L$ ) is usually small (around 0.2) in biomedical applications [67], high order terms can be neglected and (3-4) can be approximated by the 2<sup>nd</sup>-order Taylor series as given below.

$$I(t) \approx I_0 \left( 1 + \left( -\frac{1}{R_L C_L} \right) t + \frac{1}{2} \left( \frac{1}{R_L C_L} \right)^2 t^2 \right)$$

=  $\frac{I_0}{2} \left( 1 + \left( 1 - \frac{1}{R_L C_L} t \right)^2 \right)$  (3-5)

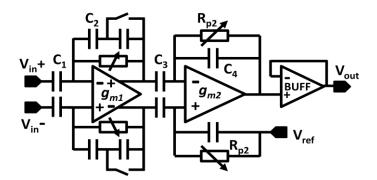

Fig. 3.1(a) shows that the error of (3-5), resulting from the approximation, is less than 0.6% at stimulation duration of 200  $\mu$ s and maximum 5.6% at 600  $\mu$ s under a typical electrode load of 10 k $\Omega$  and 100 nF [67]. Fig. 3.1(b) shows the electrode voltage  $V_e$  calculated by integrating the approximated current in (3-5). Different  $R_LC_L$  are used

for covering the range of load variation from 50% to 150% of the default  $R_L C_L$  value (1 ms) and it is found that the electrode voltage,  $V_e$ , is nearly constant (variation less than 3%) for  $t < 250 \ \mu$ s.

Figure 3.1 (a) Comparison between the ideal exponential current waveform and its 2<sup>nd</sup>-order Taylor series approximation (exponentially decaying current waveform), (b) electrode voltage calculated by integrating the exponentially decaying current, (c) exponentially decaying current generation circuit.

### **3.1.2 Exponentially Decaying Current Generation**

Fig. 3.1(c) is the proposed exponentially decaying current generation circuit according to (3-5). Transistors  $M_1$  and  $M_2$  have the identical size. Using the long-channel MOS transistor model and ignoring the channel length modulation effect [68], the output current  $I_{out}$  can be expressed as

$$I_{out}(t) = \frac{\beta}{2} (V_{gs0} - V_{thn})^2 + \frac{\beta}{2} (V_{gs0} - V_{thn} - \frac{I_{leak}}{C} t)^2$$

$$= \frac{2\beta (V_{gs0} - V_{thn})^2}{4} \left( 1 + \left( 1 - \frac{I_{leak}}{C(V_{gs0} - V_{thn})} t \right)^2 \right)$$

(3-6)

where  $\beta$  is the MOS transistor transconductance parameter,  $V_{gs0} (= V_{gs1}(0) = V_{gs2}(0))$  is the initial gate-source voltage of M<sub>1</sub> and M<sub>2</sub>, and V<sub>thn</sub> is the threshold voltage of NMOS transistors.

Comparing (3-5) and (3-6), to obtain the exponentially decaying current waveform, the following condition has to be satisfied:

$$\frac{I_{leak}}{C(V_{gs0} - V_{thn})} = \frac{1}{R_L C_L} \,. \tag{3-7}$$

the values of design parameters of the proposed circuit such as C,  $I_{leak}$  and  $\beta$ ,  $V_{gs0}$ , can be determined to produce a desired exponential current waveform, resulting in a nearly constant  $V_e$ .

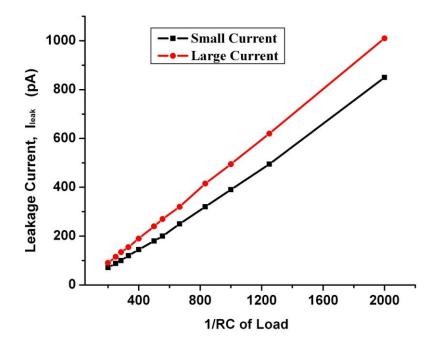

To maximize the power efficiency of the stimulator with a specific load, equation (3-7) should be satisfied. We set the value of capacitor C to be 2 pF and assume that the initial overdrive voltage ( $V_{gs0}$ - $V_{thn}$ ) of the transistor is 400 mV, and then the  $I_{leak}$  is

calculated as 800 pA when the default  $R_LC_L$  value (10K•100n  $\Omega$ •F) is used. Practically,  $R_L$  and  $C_L$  have a wide range based on the electrode shape and implantation environment [31], [67], [9]. Besides, the initial overdrive voltage ( $V_{gs0}$ - $V_{thn}$ ) also changes due to process variation. Therefore,  $I_{leak}$  needs to be tunable to satisfy (3-7).

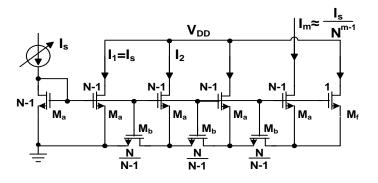

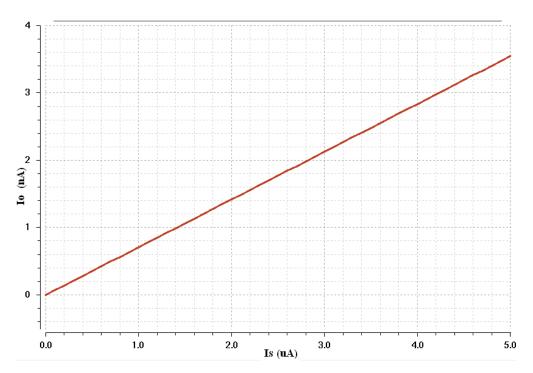

A current splitter structure [69] is used to generate  $I_{leak}$ . Controlled by an adjustable external current source Is (i.e. 200nA ~ 5µA), the current splitter can generate an output current ranging from 140 pA to 3.5 nA which can cover  $R_LC_L$  value from  $2.3 \times 10^{-4} \ \Omega \cdot F$  to  $5.7 \times 10^{-3} \ \Omega \cdot F$ . By tuning  $I_{leak}$  through the external current source  $I_S$ , (3-7) can be satisfied for the desired time constant  $(R_L'C_L')$ .

# **3.2 Implementation of Power-Efficient Stimulator with Exponentially Decaying Current**

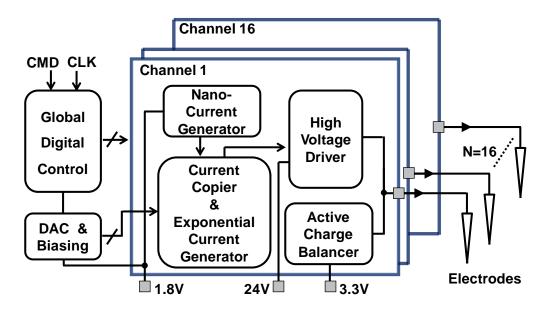

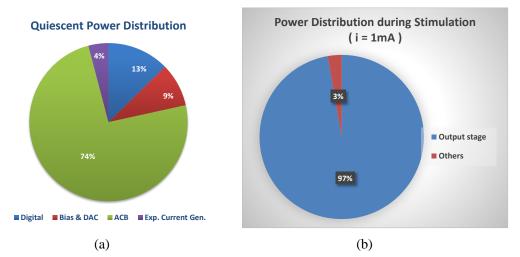

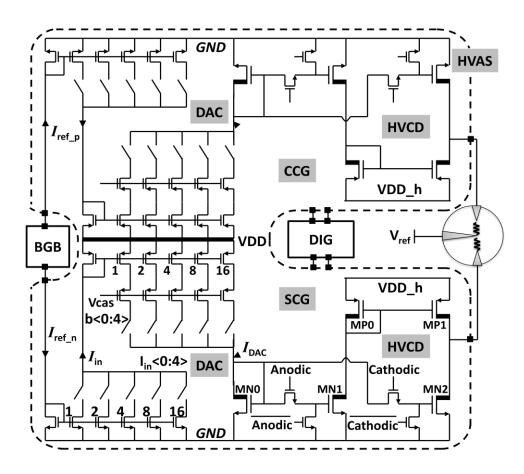

The proposed exponentially decaying current generator is integrated in a 16-channel stimulation system for proof of concept. The block diagram of the prototype stimulator with proposed exponentially decaying stimulation current is shown in Fig. 3.2. It consists of a global digital controller, a 6-bit DAC, and 16 stimulation channels. The stimulation channels can be selectively powered down to minimize the overall power consumption. Each channel consists of a current copier, an exponentially decaying current generator, a high-voltage current driver and an active charge-balancing circuit. The global digital controller is to receive and decode the commands. Especially, the 6-bit DAC is shared by 16 channels to save the total chip

Figure 3.2. System archetecture of the 16-channel stimulator IC.

area and power and is controlled by the global digital block. The DAC sequentially generates current source for the current copier in each channel. The proposed exponentially decaying current generator provides the optimized stimulation waveform for high power efficiency. The generated biphasic exponentially decaying current is amplified and delivered to the stimulation site by a high-voltage current driver with nearly 24-V compliance. The active charge-balancing circuit removes the residual charge produced by the mismatched biphasic stimulation current using a pulse insertion technique [9].

## 3.2.1 DAC Design

DAC is needed in most neural/muscular stimulators to set the stimulation current. The output current of a stimulator is usually made selectable in a wide range so that it can be used for different applications. For example, a current larger than 500  $\mu$ A may be needed to stimulate a muscle, while, a current less than 100  $\mu$ A is large enough to

excite an AP in a nerve [19]. Therefore, a current-mode DAC is suitable for providing such stimulation source current since its output current can be easily controlled and programmed. In our design, to meet the general specifications of stimulator as mentioned in Chapter 1, a 6-bit DAC circuit whose output current ranges from 4  $\mu$ A to 252  $\mu$ A with a step current of 4  $\mu$ A is designed. After going through a current copier circuit and a high-voltage output stage, the final output current of the stimulator will range from about 30  $\mu$ A to 1.6 mA.

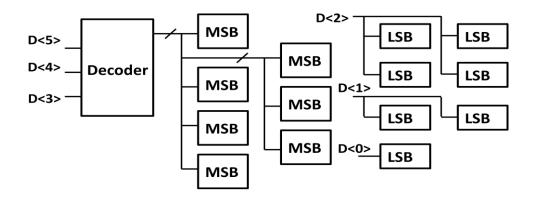

Figure 3.3 Architecture of DAC current cells.

Figure 3.4 Schematic: (a) MSB current unit cell (b) LSB current unit cell.

This 6 bit DAC circuit consists of a 3-to-7 thermometer decoder [70], 7 MSB current unit cells, and 7 LSB current unit cells, as shown in Fig. 3.3 and Fig. 3.4. These 7 LSB current unit cells are controlled by D<2:0> through direct switch control and the MSB unit cells are controlled by D<5:3> through the thermometer decoder. The output current of LSB and MSB unit cell are set to 4  $\mu$ A and 32  $\mu$ A, respectively.

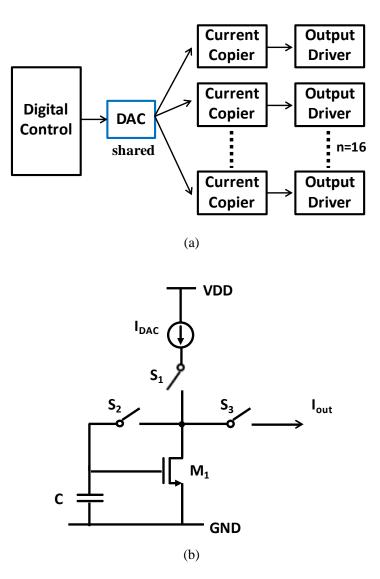

# 3.2.2 Current Copier and Exponentially Decaying Current Generation Circuit

In traditional multi-channel stimulators, each channel is driven by a local DAC circuit so that the amplitude of stimulation current can be set differently from other channels. However, in some applications, such as retinal prosthesis, where large number of channels are needed, the local DACs will occupy large chip area and increase the overall power consumption. In this design, only one global DAC is used and shared among all 16 channels, as shown in Fig. 3.5(a). Current copying technique [71-72] is therefore adopted to enable the DAC sharing.

A simplified current copier circuit [73] is shown in Fig. 3.5(b). The current copier converts the current to the gate-source voltage and stored on the gate capacitance and capacitor C. During "pre-charging" state,  $S_1$  and  $S_2$  are closed,  $S_3$  is open, the capacitor C is charged and gate-source voltage of transistor  $M_1$  will be sampled. Then,  $S_2$  will be open after pre-charging finishes, and  $V_{gs}$  of  $M_1$  holds its value. During "stimulating" state,  $S_1$  and  $S_2$  are open,  $S_3$  is closed, and the same amount of current generated by M<sub>1</sub> will flow to the output stage.

Figure 3.5 (a) DAC sharing in multichannel stimulator, (b) schematic of a simplified current copier circuit.

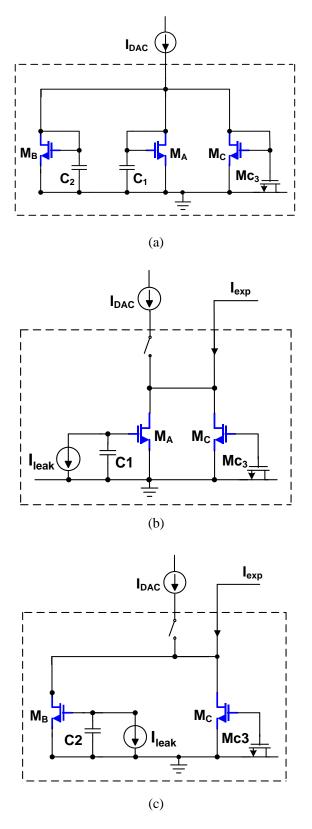

Noticed that both exponentially decaying current generator (shown in Fig. 3.1(c)) and current copier circuit (shown in Fig. 3.5) consist of transistors and capacitors and have similarity in structure, we combine these two functions together and make a new circuit featuring both current copying and exponential current generating as shown in

Fig. 3.6(a). In this combined current copier and exponentially decaying current generator, a switched transistor array  $M_C$  is used to generate the constant current term in equation (3-6) mentioned in section 3.1.2, and two identical transistor arrays  $M_A$

Figure 3.6 (a) Schematic of the shared 6-bit DAC and the current copier/exponentially decaying current generator in single-channel, (b) switched transistor array  $M_A$  used in the current copier.

and  $M_B$  are used to generate the time-dependent current term in (3-6). To determine the value of capacitors and the amplitude of current sink ( $I_{leak}$ ) in the circuit, (3-7) has to be satisfied to configure the design parameters. Consequently, assuming a constant initial overdrive voltage  $V_{gs0}$ - $V_{thn}$  = 400mV, the values of  $I_{leak}$  and C ( $C_1$  and  $C_2$  in Fig. 3.6(a)) can be derived from the values of  $R_L$  and  $C_L$ . In the design, we set the value of C to be around 2 pF. For the capacitor implementation, since the  $M_{C3}$  is used to keep the gate-source voltage of  $M_C$  constant, the MOS capacitor is used to save the chip area due to its large capacitance density. For  $C_1$  and  $C_2$ , MIM capacitors are used to provide constant capacitance for the varying voltage across the capacitors.

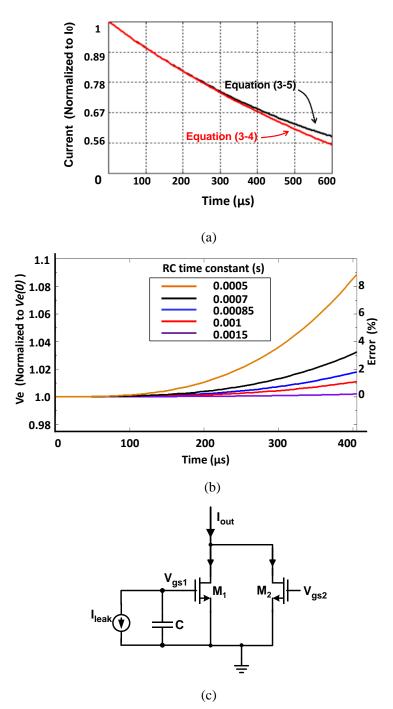

Practically,  $R_L$  and  $C_L$  have a wide range based on the electrode shape and implantation environment [31], [67], [9]. In the design, although we set a default value of  $I_{leak}$  to be 800 pA based on the typical load with  $R_L = 10 \text{ k}\Omega$  and  $C_L = 100 \text{ nF}$ [67], for different loads,  $I_{leak}$  needs to be tuned to cover a wide range of  $R_L$  and  $C_L$ , to satisfy equation (3-7). The value of required  $I_{leak}$  according to different load conditions ( $R_LC_L$ ) is presented in Fig. 3.7. The red curve shows the relationship between  $I_{leak}$  and 1/RC of the load when a large current (D=001111, 60 µA) is generated from the DAC. The black curve shows the simulation results when a small current (D=000111, 28 µA) is applied. This can be explained according to equation (3-7). Large current results in high overdrive voltage and hence a larger  $I_{leak}$  is needed in order to satisfy the condition in equation (3-7). The simulation results of the current copier and exponentially decaying circuit also reveals that the required  $I_{leak}$  has a

Figure 3.7 Simulation result of the required *I*<sub>leak</sub> vs. diffent loads.

linear relationship with the reciprocal of time constant under the fixed load. In other words, the circuit can be easily tuned to fit different loads in different applications.

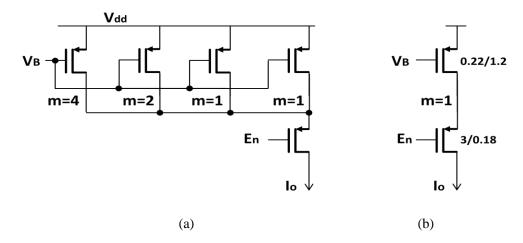

Figure 3.8 Ultra low current generator.

The schematic of current splitter [69] which generates  $I_{leak}$  is shown in Fig. 3.8. In this current splitter, the gate nodes of all transistors are connected together. In the 1<sup>st</sup>-order cell (the first branch generating current  $I_I$ ), the current  $I_1$  is equal to the reference

current  $I_s$ , and the current flowing through M<sub>b</sub> is approximately N times smaller than  $I_1$ . In this design, N is set to 10 and a 4<sup>th</sup>-order current splitting is used to generate  $I_{leak}$  of several hundred picoamperes.

Figure 3.9 Simulation result: input current (*Is*) vs output current (*I*<sub>leak</sub>) of current splitter.

Fig. 3.9 shows the relation between input and output current of the current splitter. When the input current (*Is*) is tuned from 0 to 5  $\mu$ A, the output current of the splitter ranges from 0 to 3.6 nA. The result shows good linearity which guarantees the tuning ability of the exponentially-decaying current stimulator.

The current copier and exponentially decaying current generation circuit operates in three phases. First, in the current-replication phase, the control signal from the global digital controller connects the circuit to the DAC output. The switches  $S_{1A}$ ,  $S_{2A}$ ,  $S_{1B}$ ,

Figure 3.10 Operation of the current copier and exponentially decaying current generator circuit: (a) current-replication phase, (b) cathodic stimulation phase, and (c) anodic stimulation phase.

$S_{2B}$  and  $S_{2C}$  in Fig. 3.6(a) are closed so that the DAC output current  $I_{DAC}$  can flow into transistor arrays  $M_A$ ,  $M_B$  and  $M_C$ , as shown in Fig. 3.10(a). Since these three transistor arrays have the same size, they conduct the same amount of current ( $I_{DAC}/3$ ) through each and the same gate-source voltages are stored in the capacitors  $C_1$ ,  $C_2$  and  $M_{C3}$ , respectively. As the cathodic stimulation phase starts, the circuit is disconnected from the DAC output and operates with the gate-source voltages stored in the capacitors. Since the current flowing through  $M_A$  and  $M_C$  forms the exponentially decaying current  $I_{exp}$  in the cathodic stimulation phase, the switches  $S_{1A}$  and  $S_{3A}$  are closed while all the other switches are open, as shown in Fig. 3.10(b). Similarly, during the anodic stimulation phase shown in Fig. 3.10(c), the circuit remains disconnected from the DAC output, and  $I_{exp}$  is generated from  $M_B$  and  $M_C$  using the gate-source voltages stored in  $C_2$  and  $M_{C3}$  with  $S_{1B}$  and  $S_{3B}$  closed.

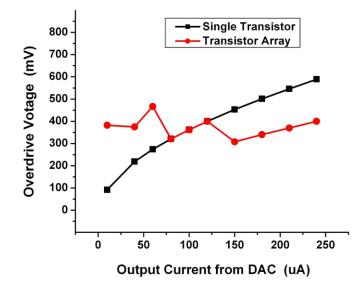

To support variable strengths of stimulation, the DAC generates  $I_{DAC}$  which varies over the range from 4 µA to 252 µA. Therefore, the initial overdrive voltage ( $V_{gs0} - V_{thn}$ ) of the transistors in current copier cells also varies with the current, which requires  $I_{leak}$  to be tuned accordingly. To reduce its required tuning range, the switched transistor arrays M<sub>A</sub>, M<sub>B</sub> and M<sub>C</sub> are implemented in the circuit shown in Fig. 3.6(b) to maintain the initial overdrive voltage relatively constant over the range of  $I_{DAC}$ .

The switches S<sub>1</sub>, S<sub>2</sub>, S<sub>3</sub> and S<sub>4</sub> in Fig. 3.6(b) are controlled using the logic shown in Table 3.1. For the  $n^{\text{th}}$  stimulation channel, as the 6-bit DAC input code  $D_n$ [5:0]

| <i>D</i> <sub>n</sub> [5:0] | $I_{DAC}$                                  | $S_1$ | $S_2$ | <b>S</b> <sub>3</sub> | <b>S</b> 4 |

|-----------------------------|--------------------------------------------|-------|-------|-----------------------|------------|

| $0 \le D_n \le 4$           | $0 \leq I_{DAC} \leq 16 \ \mu A$           | 1     | 0     | 0                     | 0          |

| $5 \leq D_n \leq 16$        | $20 \ \mu A \leq I_{DAC} \leq 64 \ \mu A$  | 0     | 1     | 0                     | 0          |

| $17 \leq D_n \leq 36$       | $68 \ \mu A \leq I_{DAC} \leq 144 \ \mu A$ | 0     | 0     | 1                     | 0          |

| $37 \leq D_n \leq 63$       | 148 $\mu A \le I_{DAC} \le 252 \ \mu A$    | 0     | 0     | 0                     | 1          |

TABLE 3.1 Switched Transistor Array Control Logic

becomes larger, the DAC output current  $I_{DAC}$  increases and the larger transistor in the array is chosen. In order to avoid taking up too much extra area and simplify the design of transistor array as well as its control circuit, only 4 transistors are used in each array. The entire  $I_{DAC}$  range is divided into 4 regions responding to these 4 transistors. For different regions, different transistors are activated. The transistors are sized proportional to the average  $I_{DAC}$  values in the corresponding regions. By doing so, the initial overdrive voltage ( $V_{gs0} - V_{thn}$ ) of the transistors can be kept within the range from 300 mV to 460 mV, as shown in Fig. 3.11. While it ranges from 100 mV

Figure 3.11 Simulation result: overdrive voltage vs. current.

to 600 mV if single transistor is used. With the transistor array, the full swing of the tunable  $I_{leak}$  can be reduced by nearly 75% and thus improves the tunability.

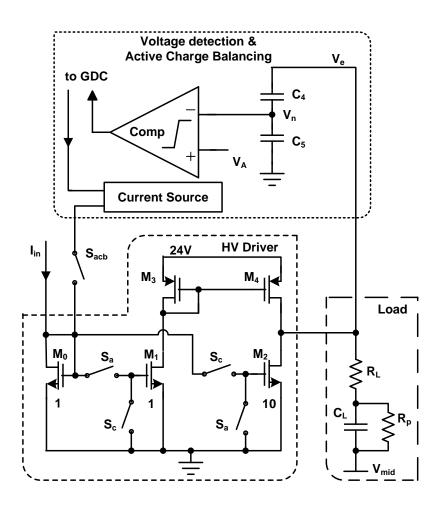

# 3.2.3 High-Voltage Output Stage and Active Charge Balancing Circuit

Output stage of the stimulator amplifies the stimulation current and provides large voltage compliance in order to deliver sufficient current to the high impedance load. In order to provide sufficient stimulation strength even when the load impedance is high, output stage is designed in a 0.18-µm 24-V high-voltage CMOS process. The

Figure 3.12 High-voltage output stage and active charge balancing circuit.

high-voltage output driver transforms the monophasic current to the biphasic current for cathodic and anodic stimulations. As shown in Fig. 3.12, the current mirror composed of  $M_0$  and  $M_2$  forms the anodic stimulation path, and the cathodic stimulation path consists of two pairs of current mirrors ( $M_0$ - $M_1$  pair and  $M_3$ - $M_4$  pair). Since  $M_0$ - $M_2$  and  $M_3$ - $M_4$  pairs mirror the current with the ratio of 1:10, nearly 90% of current is consumed in the final load-driving branch.

An active charge-balancing circuit (ACB) is added to remove the residual charge using the pulse insertion technique in [9]. First, before each stimulation cycle, electrode voltage (*Ve*) equals to the reference voltage (*V<sub>mid</sub>*), and the node voltage between capacitor C<sub>4</sub> and C<sub>5</sub> (*V<sub>n</sub>*) is initially set equal to *V<sub>A</sub>*. After each stimulation, the electrode potential (*Ve*) is sampled by a capacitive voltage divider and compared with *V<sub>A</sub>* by a comparator. If *V<sub>n</sub>* > *V<sub>A</sub>* (*Ve* > *V<sub>mid</sub>*), GDC will send a short pulse to close switches S<sub>acb</sub> and S<sub>c</sub>, delivering a sink current to absorb the excessive residual charge on the electrode. ACB keeps inserting pulses until *V<sub>n</sub>* is slightly smaller than *V<sub>A</sub>*. If *V<sub>n</sub>* < *V<sub>A</sub>* (*Ve* < *V<sub>mid</sub>*), in the similar way, the stimulator will deliver an anodic current pulse, until finally the voltage on the electrode is kept within a safety level (V<sub>mid</sub> ±50mV).

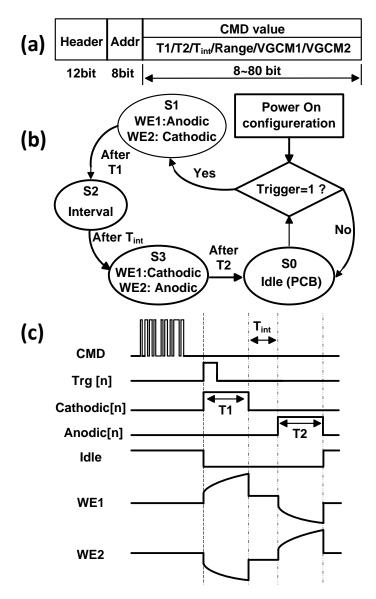

# 3.2.4 Global Digital Controller

The global digital controller (GDC) provides the control signals of switches between the shared DAC and 16 stimulation channels as well as the switches in the current

(b)

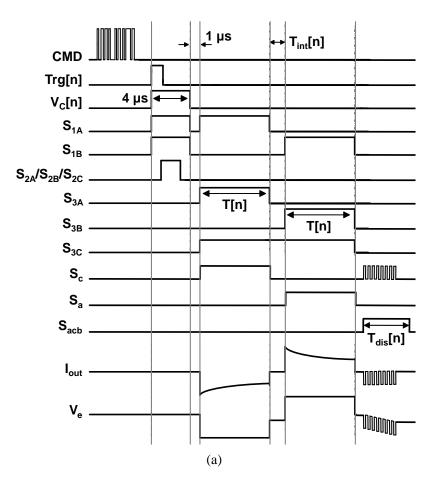

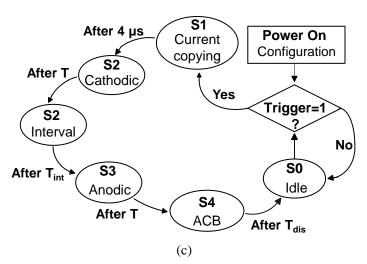

Figure 3.13 System operation: (a) digital control timing diagram, (b) command frame format, and (c) control state diagram.

copier, exponentially decaying current generator, active charge balancer, and high-voltage output driver for each channel.

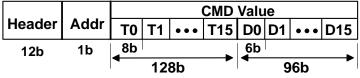

The timing diagram of control signals used for system operation is shown in Fig. 3.13(a). Firstly, the stimulation parameters such as T[n],  $T_{dis}[n]$  and  $D_n[5:0]$  for all 16 channels are set by decoding the incoming commands to configure the stimulation duration and amplitude of each channel. The command frame format is shown in Fig. 3.13(b). When the  $n^{\text{th}}$  channel is triggered, the digital code presenting the current amplitude of the selected channel goes to the DAC input through a multiplexer.  $V_C[n]$ is set to logic 1 to connect the channel with the DAC output and the switches are configured to operate the channel in the current-replication phase for 4 µs. The cathodic stimulation phase then begins 1  $\mu$ s after  $V_C[n]$  goes back to logic 0. By using the initial gate-source voltages stored during the current-replication phase, the transistor arrays  $M_A$  and  $M_C$  (in Fig. 3.6(a)) generate the exponentially decaying stimulation current during T[n]. After delivering the cathodic stimulation current, there is an interphasic delay of 30 µs before the anodic phase starts. In the anodic stimulation phase, the exponentially decaying current generated by M<sub>B</sub> and M<sub>C</sub> is steered into the high-voltage driver. The active charge balancing operation is initiated after the anodic stimulation phase and sustained for  $T_{dis}[n]$ . For multi-channel operation, as it takes 4 µs for the selected channel to copy its current from the DAC output, the multi-channel triggering signals should come in with a minimum interval of 4  $\mu$ s.

The GDC module is designed by a staff member of Institute of Microelectronics (IME) Singapore as part of the collaboration and the detail digital implementation is reported in [74].

# **3.3 Measurement Results**

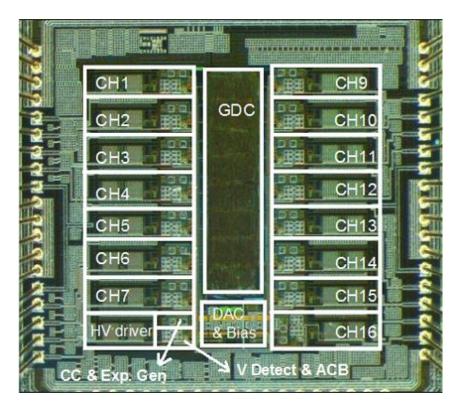

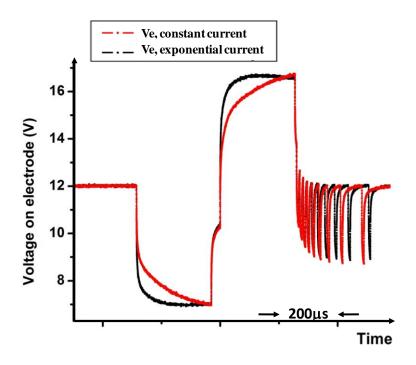

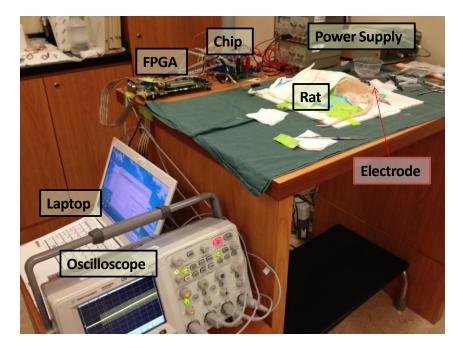

The prototype stimulator with exponentially decaying stimulation current is fabricated in a 0.18- $\mu$ m CMOS technology with 24-V high-voltage LDMOS option. The core area is 1.65 mm × 1.65 mm and the total die area including pads is 2.5 mm × 2.5 mm. The microphotograph of the fabricated stimulator IC is shown in Fig. 3.14.

Figure 3.14 Die microphotograph of 16-channel stimulator IC.

#### **3.3.1 Test Bench Measurement Results**

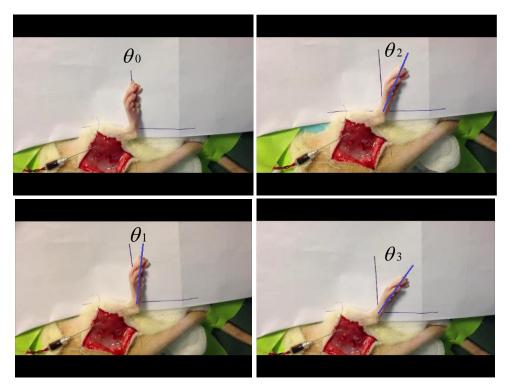

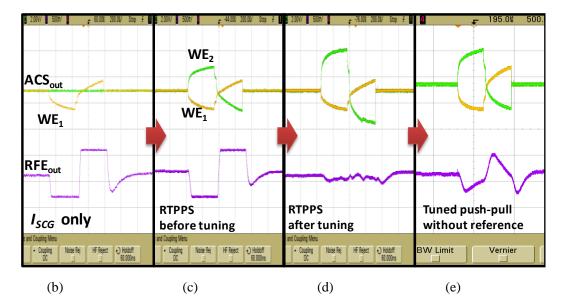

As the DAC input code increases from 1 to 63, the measured cathodic stimulation current ranges from 28  $\mu$ A to 1.8 mA while the anodic current changes from 34  $\mu$ A to 2.2 mA, as shown in Fig. 3.15. The mismatch of cathodic and anodic current is