# DESIGN OF LOW-POWER LOW-VOLTAGE SUCCESSIVE-APPROXIMATION ANALOG-TO-DIGITAL CONVERTERS

#### LI YONGFU

(Bachelor of Engineering (Hons.), National University of Singapore, Singapore)

A THESIS SUBMITTED FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING

NATIONAL UNIVERSITY OF SINGAPORE 2014

#### **Declaration**

I hereby declare that this thesis is my original work and it has been written by me in its entirety. I have duly acknowledged all the sources of information which have been used in the thesis.

This thesis has also not been submitted for any degree in any university previously.

LI YONGFU 15TH JULY 2014

# Design of Low-Power Low-Voltage Successive-Approximation Analog-to-Digital Converters

by Li Yongfu

Submitted to the Department of Electrical and Computer Engineering on 15th July 2014, in partial fulfillment of the requirements for the degree of Doctor of Philosophy

#### **Abstract**

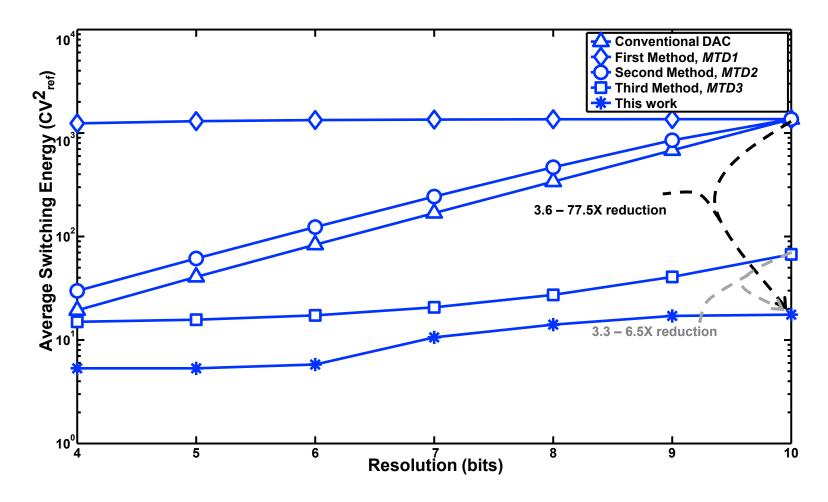

This dissertation circuit techniques for proposes new design Successive-Approximation-Register (SAR) Analog-to-Digital Converters (ADCs) and capacitive-array Digital-to-Analog Converter (DACs). A dual-channel, configurable 4-to-10-bit SAR ADC is proposed and fabricated in 130-nm CMOS technology. It operates at a supply voltage of 0.6-V and achieves a maximum sampling rate of 250-kS/s and a FOM of 24-fJ/step. To reduce the area and power consumption per channel, the ADC uses a dual-capacitive-arrays DAC architecture and reuses multiple building blocks, such as the DACs, the comparator and the SAR logic, for the dual-channel ADC. To minimize the switching power consumption across all resolution modes, an energy-efficient charge-recovery switching scheme is proposed. It achieves a 3.6-to-77.5× reduction compared to the conventional charge-redistribution scheme.

As the resolution of the ADC increases, the matching requirements for the unit capacitors (i.e., increase the area of the unit capacitor) and the number of unit capacitors in the conventional binary-weighted capacitive-array (CBW) DAC increases exponentially, thus increasing the area, the switching power consumption and the settling time in the DAC. Therefore, two methods are proposed to address these challenges in high resolution (>10-bit) capacitive-array DACs.

First, a placement strategy is proposed to address the layout's mismatches, where a matrix-adjustment method is proposed to optimize the size of the CBW DAC, different placement techniques and weighting methods are proposed for the placement of active and dummy unit capacitors. The resulting star-like placement increases the degree of dispersiveness (i.e., reduce random mismatch), reduces the first-order oxide-gradient-induced mismatches and the second-order lithographic errors and achieves a more symmetrical routing compared to existing works. A homogenization method is also proposed to reduce the asymmetrical fringing

mismatches among the capacitive-array, thus improving the systematic mismatch between the capacitive-array and the dummy capacitors.

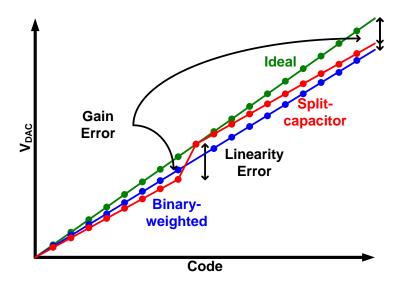

Second, two new types of split capacitive-array DAC architectures are proposed to reduce the area, the power consumption and improve the linearity compared to the CBW DAC and the conventional binary-weighted split capacitive-array with a fractional attenuation capacitor (BWA) DAC. A design methodology is proposed to determine the segmentation degree in the DAC for optimum performance. For a 12-bit SAR ADC, the proposed DACs reduce the input load capacitance and area by  $2\times$  and  $4\times$ , respectively, and the switching power by  $15\times$  and  $15.5\times$ , respectively, compared to the CBW DAC. It also improves the linearity, minimizes the mismatch variation and reduces the switching power by  $3.75\times$  and  $3.87\times$ , respectively, compared to the BWA DAC.

#### Acknowledgements

First of all, I wish to express my gratitude to my advisor, Professor Lian Yong, for giving me the opportunity to work with his group. He is always eager to share his new ideas with me. He is always encouraging us to think creatively and gives us all the freedom to do that. I am greatly indebted to his inspirations, encouragement and support. I enjoyed tremendously working under his guidance.

I would also like to thank all of my committee professors. In particular, I also would like to thank Associate Professor Heng Chun Huat for his meticulously detailed eye for circuit. I have benefited a lot from his rich knowledge in circuit design. I would also like to thank Professor Yeo Swee Ping, Associate Professor Xu Yong Ping, Associate Professor Koenraad Mouthaan, Dr. Ha Ya Jun and Dr. Moorthi s/o Palaniapan for introducing circuit design since my undergraduate years.

When I first joined Professor Lian's group, Yang Zhenglin, Zhang Jinghua, Eng Wei Jie and Mehran Mohammadi Izad welcomed and helped me to adapt myself to new circumstance. I really appreciate their extreme patience for listening and sharing their delights. In particular, I thank Zhenglin for his encouragement and discussion to keep things in perspective.

My view of the semiconductor industry would have been quite narrow without the experience gained from learning and working at Globalfoundries Singapore Pte Ltd. I therefore like to thank Professor Lap Chan, Dr. Colin Hui, Dr. Ng Chee Mang, Leong Kam Chew, Sky Yeo Wee Kwong, Ushasree Katakamsetty, Nandavaram Elisha Prashanth Sagar, Valerio Perez and Cris Magalang. Additionally, my degree would have been much more difficult without the financial support from Globalfoundries.

I would also like to thank Professor Chua Kee Kiang, Professor Adekunle Olusola Adeyeye, Associate Professor John Thong, Associate Professor Tan Leng Seow, Associate Professor Chor Eng Fong for giving us support to establish the Graduate

Student Council. I also like to thank Chen Xiao Lei, Zhang Zhe, Ganesh Iyer, Shubhanshu Goyal, Syed Rizwan and Lou Liang for establishing the council together with me. I also like to thank Nguyen Hoang Tuan Minh, Wang Yu, Liang Wenyu, Mohammadreza Keshtkaran, Kwadwo Konadu Ansah-Antwi, Ahmed Mehmood and Farshad Rassaei for improving the council together with me along the years.

I would also like to thank Chacko John Deepu, Pramod Kumar Pisharady and Nithin Salgunan for introducing me to IEEE Singapore GOLD committee and allowing me to serve and contribute to the members in Singapore. I would also like to thank them for supporting me as the chairperson for the IEEE Singapore Young Professional 2014.

The completion of this work would not have been possible without the support and encouragement of those people, including colleagues, advisors and friends. I loved talking to and learning from everyone in the VLSI and SP laboratory and Bioelectronics laboratory including Teo Seow Ming, Zheng Huan Qun, Zhang Zhe, Zhang Xiaoyang, Wang Lei, Hong Yibin, Chacko John Deepu, Zhang Da Ren, Mahmood Khayatzadeh, Tan Jun, Liew Wen Sin, Li Ti, Mao Wei, Zou Xiaodan, Niu Tianfang, Li Xuchuan, Gong Xiaohui, Zhao Jianming, Wang Xi, Jerrin Pathrose, Ng Kian Ann, Liu Xu, Nankoo Serge Georges John, Liu Xiayun, Zhou Lianhong, Yu Heng and Do Thi Thu Trang.

My sincere gratitude goes to Globalfoundries SP13 group, Wong Wei Chang, Xu Naiyun, Koh Kah How, Ding Ying Jie, Eugene Kong Yu Jin, Roger Kwok Wai Keung, Edwin Low Kim Fong, Zin Zar Lwin, Boo Ann Ann, Ong Ran Xing and Ho Hui Wen for their joyful company. Without their support, SP 2010 orientation would not have been made possible.

I thank all my master and final year students I have had the privilege of working with under Professor Lian Yong and Associate Professor Koenraad Mouthaan.

I would not have been able to achieve all I have without the support and encouragement of my family. Finally, I thank Ms. Chua Dingjuan, who has been there for me every day as we worked together to complete our PhD. Her love and guidance is more important to me than anything else.

### **Contents**

| A  | bstract                                                       | V    |

|----|---------------------------------------------------------------|------|

| A  | cknowledgements                                               | vii  |

| C  | ontents                                                       | ix   |

| Li | ist of Figures                                                | xiii |

| Li | ist of Tables                                                 | xvii |

| Li | ist of Abbreviations                                          | xix  |

| 1  | Introduction                                                  | 1    |

|    | 1.1 Development of analog-to-digital converters (ADCs)        | 1    |

|    | 1.2 Organization of the dissertation                          | 6    |

| 2  | Successive approximation analog-to-digital converters         | 11   |

|    | 2.1 Basic operation                                           | 11   |

|    | 2.1.1 Conventional charge-redistribution SAR ADC              | 15   |

|    | 2.2 Advanced techniques in SAR ADC architectures              | 17   |

|    | 2.2.1 Asynchronous SAR ADCs                                   | 17   |

|    | 2.2.2 Pipelined-SAR ADCs                                      | 18   |

|    | 2.2.3 Time-interleaved SAR ADCs                               | 18   |

|    | 2.2.4 Multi-bit per cycle (flash) SAR ADCs                    | 19   |

|    | 2.3 Type of DAC architecture                                  | 19   |

|    | 2.3.1 Resistive-string DAC                                    | 20   |

|    | 2.3.2 Conventional binary-weighted capacitive-array (CBW) DAC | 21   |

|    | 2.3.3 Binary-weighted split capacitive-array with attenuation |      |

|    | capacitor (BWA) DAC                                           | 22   |

|    | 2.3.4 Passive charge sharing capacitive-array DAC             | 23   |

|   | 2.3.5 Non-binary (sub-radix-2) capacitive-array DAC                                       | 24 |

|---|-------------------------------------------------------------------------------------------|----|

| 3 | Analytical Study Of The Capacitive-Array DAC's Switching Methods                          | 25 |

|   | 3.1 Introduction                                                                          | 25 |

|   | 3.2 Analysis of switching energy                                                          | 26 |

|   | 3.2.1 From sampling to MSB transition phase                                               | 27 |

|   | 3.2.2 Bit-cycling phase                                                                   | 30 |

|   | 3.3 Examples of switching methods                                                         | 33 |

|   | 3.3.1 Charge-redistribution switching method for the CBW DAC                              | 33 |

|   | 3.3.2 Charge-redistribution switching method for the BWA DAC                              | 35 |

|   | 3.3.3 Step-and-down switching method for the CBW DAC                                      | 37 |

|   | 3.3.4 $V_{CM}$ -based switching method for the CBW DAC                                    | 40 |

|   | 3.4 Charge-recovery switching method for the dual-capacitive-array DAC                    |    |

|   | architecture                                                                              | 44 |

|   | 3.5 Summary                                                                               | 49 |

| 4 | Dual Channel Time Interlegged December weble Desclution SAD ADC                           | 51 |

| 4 | <b>Dual-Channel, Time-Interleaved, Reconfigurable Resolution SAR ADC</b> 4.1 Introduction | 51 |

|   | 4.2 System Architecture                                                                   | 53 |

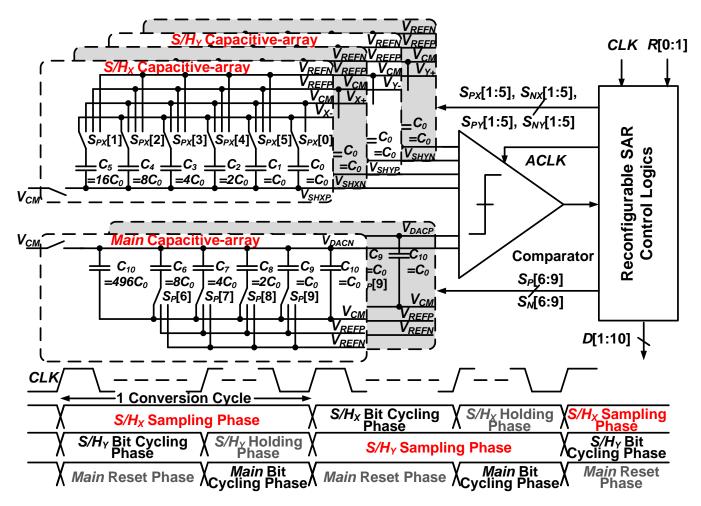

|   | 4.2.1 ADC architecture                                                                    | 55 |

|   | 4.2.2 Energy-efficient charge-recovery switching energy                                   | 57 |

|   | 4.2.3 Resolution reconfigurability in DAC architecture                                    | 58 |

|   | 4.3 Implementation of Key Building Blocks                                                 | 61 |

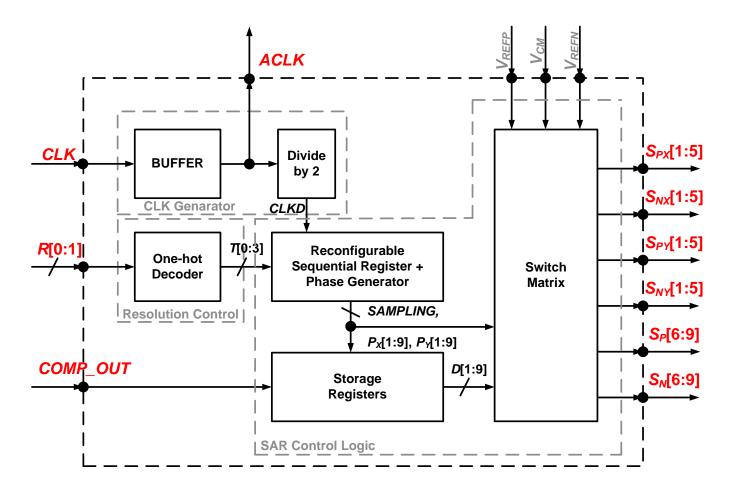

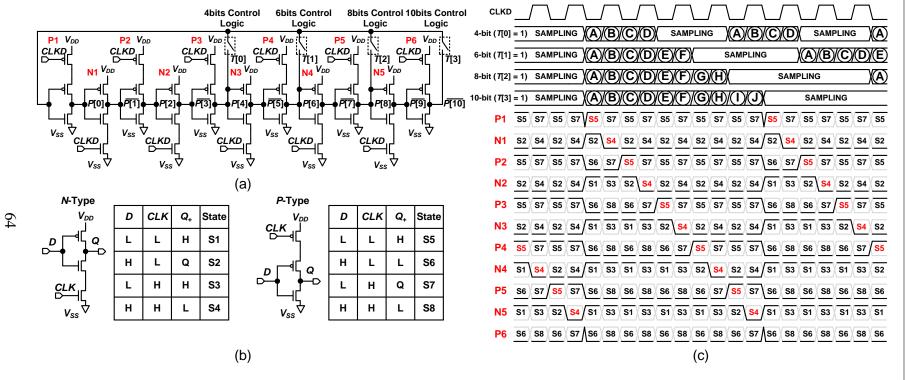

|   | 4.3.1 Reconfigurable SAR Control Logic                                                    | 61 |

|   | 4.3.1.1 Sequential Registers                                                              | 63 |

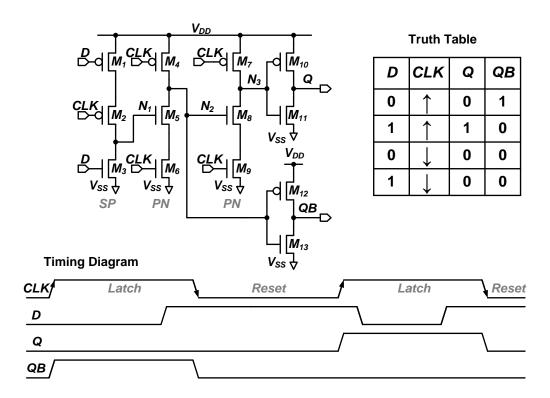

|   | 4.3.1.2 Storage registers                                                                 | 65 |

|   | 4.3.2 Switching network                                                                   | 67 |

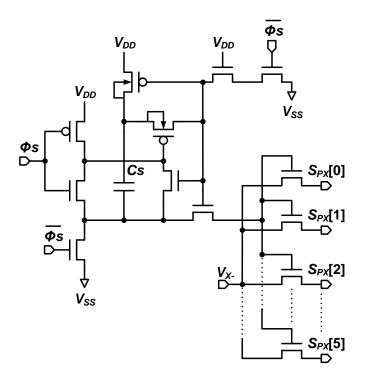

|   | 4.3.2.1 Sampling switches                                                                 | 67 |

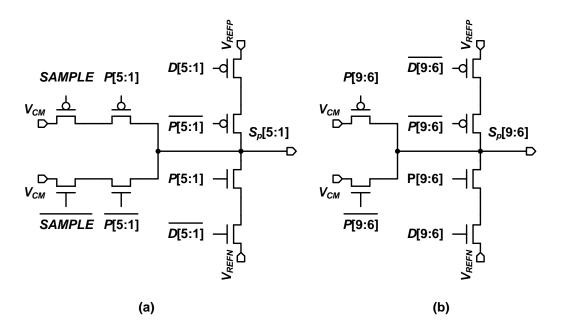

|   | 4.3.2.2 Reference switches                                                                | 67 |

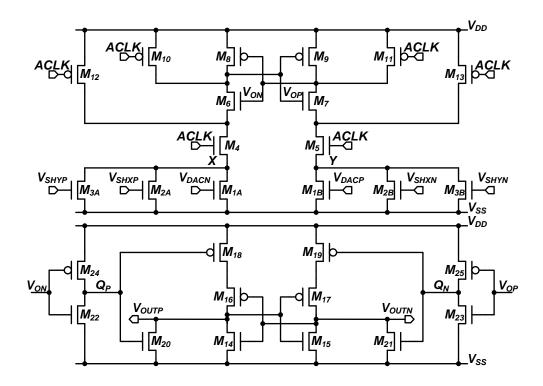

|   | 4.3.3 Multiple-input comparator design                                                    | 69 |

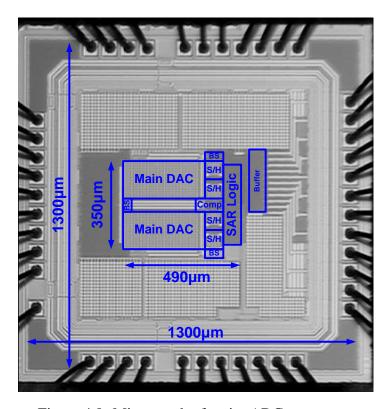

|   | 4.4 Measurement results                                                                   | 72 |

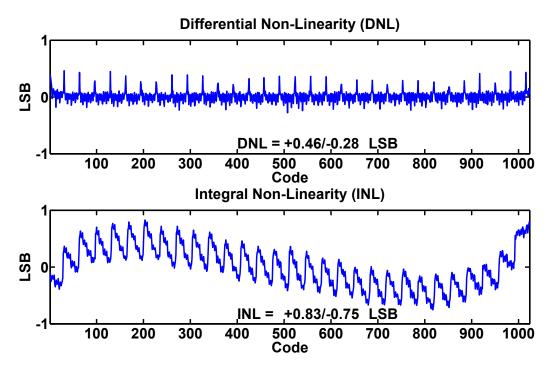

|   | 4.4.1 Static Performance                                                                  | 74 |

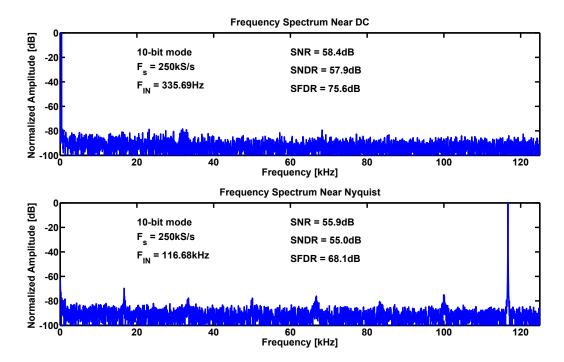

|   | 4.4.2 Dynamic Performance                                                                 | 75 |

|   | 4.4.3 Power Consumption and Figure-of-Merit                                               | 76 |

|   | 4.5 Summary                                                                               | 79 |

| 5 | Placement Strategy For The Conventional Binary-Weighted                     |     |

|---|-----------------------------------------------------------------------------|-----|

|   | Capacitive-Array DAC                                                        | 81  |

|   | 5.1 Introduction                                                            | 81  |

|   | 5.2 Terminology and review of evaluation models                             | 84  |

|   | 5.2.1 Terms and definitions for the capacitive-array DAC                    | 84  |

|   | 5.2.2 Random mismatch model - two-dimensional spatial correlation           |     |

|   | model                                                                       | 86  |

|   | 5.2.3 First-order process mismatch - oxide gradient model                   | 88  |

|   | 5.3 Placement strategy                                                      | 90  |

|   | 5.3.1 Matrix-adjustment method                                              | 92  |

|   | 5.3.2 Dummy capacitors placement using spatial weighting method .           | 96  |

|   | 5.3.3 Capacitive-array placement using diagonal weighting method .          | 99  |

|   | 5.3.4 Homogenizing algorithm with edge weighting method                     | 103 |

|   | 5.3.5 Routing                                                               | 104 |

|   | 5.3.6 Example of a 9-bit $C_{typeA}$ CBW DAC                                | 106 |

|   | 5.4 Experimental results                                                    | 108 |

|   | 5.5 Summary                                                                 | 114 |

| 6 | Capacitive-Array DAC Architectures for High Resolution SAR ADCs             | 115 |

|   | 6.1 Introduction                                                            | 115 |

|   | 6.2 CBW DAC and BWA DAC                                                     | 118 |

|   | 6.2.1 Area requirement                                                      | 120 |

|   | 6.2.2 Power consumption due to the capacitors' switching                    | 121 |

|   | 6.2.3 Linearity analysis                                                    | 122 |

|   | 6.2.3.1 CBW DAC                                                             | 123 |

|   | 6.2.3.2 BWA DAC                                                             | 124 |

|   | 6.3 Architecture I - an improved binary-weighted split capacitive-array DAC | 125 |

|   | 6.3.1 Area requirement                                                      | 127 |

|   | 6.3.2 Power consumption due to the capacitors' switching                    | 128 |

|   | 6.3.3 Linearity analysis                                                    | 129 |

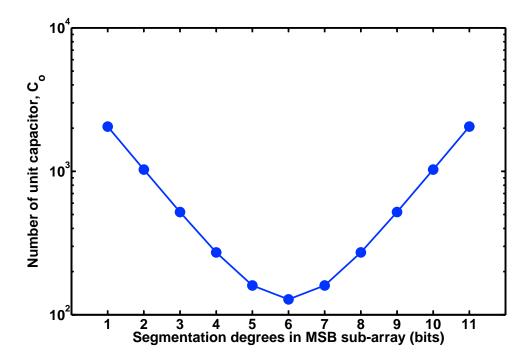

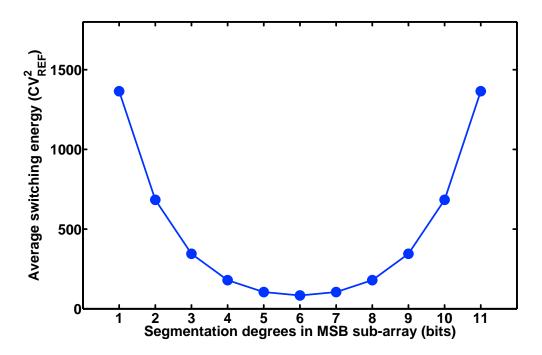

|   | 6.3.4 Optimum choice of segmentation degree                                 | 130 |

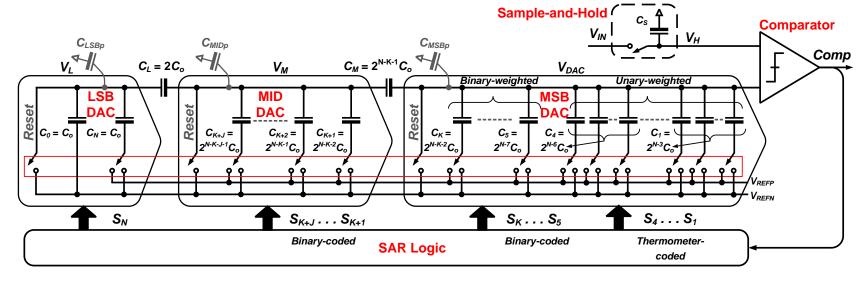

| 6.4 Architecture II - an unary-binary segmentation with multiple-split | t     |

|------------------------------------------------------------------------|-------|

| capacitive-array DAC architecture                                      | . 131 |

| 6.4.1 Area requirement                                                 | . 134 |

| 6.4.2 Power consumption due to the capacitors' switching               | . 135 |

| 6.4.3 Linearity analysis                                               | . 139 |

| 6.4.4 Optimum choice of segmentation degree                            | . 139 |

| 6.4.5 Unary-Binary Segmentation In MSB Sub-Array                       | . 140 |

| 6.5 Comparison with other structures                                   | . 141 |

| 6.6 Summary                                                            | . 141 |

| 7 Conclusion                                                           | 143   |

| 7.1 Future works                                                       | . 144 |

| 7.1.1 Low-voltage power management circuits                            | . 145 |

| 7.1.2 Comparator offset using digital calibration techniques or        | r     |

| redundancy techniques                                                  | . 145 |

| 7.1.3 Digital correction for channel mismatch                          | . 146 |

| 7.1.4 DAC calibration techniques                                       | . 146 |

| Appendix A Summary For The State-Of-The-Art SAR ADC From               | 1     |

| ISSCC and VLSI Symposium                                               | 149   |

| Appendix B PCB Design And Test Setup                                   | 159   |

| Bibliography                                                           |       |

## **List of Figures**

| Recent research trend of ADC based on Resolution and           |                                               |

|----------------------------------------------------------------|-----------------------------------------------|

| Sampling Speed [4]                                             | 3                                             |

| Recent research trend of ADC based on FOM [4]                  | 4                                             |

| Recent research trend of ADC across the years                  | 5                                             |

| Schematic diagram of a <i>N</i> -bit conventional SAR ADC      | 12                                            |

| Waveform of the conventional switching procedure for a         |                                               |

| N-bit DAC output waveform                                      | 13                                            |

| Flow Chart for a N-bit conventional SAR ADC                    | 14                                            |

| Schematic diagram of a N-bit conventional SAR ADC using        |                                               |

| the top plate sampling technique and without an explicit S/H   |                                               |

| circuit                                                        | 16                                            |

| Schematic diagram of a N-bit conventional SAR ADC using        |                                               |

| the bottom plate sampling technique without an explicit S/H    |                                               |

| circuit                                                        | 16                                            |

| Schematic diagram of a CBW DAC                                 | 21                                            |

| Schematic diagram of a BWA DAC                                 | 23                                            |

| Conventional charge-redistribution sampling technique          | 28                                            |

| Top plate sampling technique                                   | 28                                            |

| Bottom plate sampling technique                                | 29                                            |

| An example of an "up" transition in the capacitive-array DAC.  | 32                                            |

| An example of a "down" transition in the capacitive-array      |                                               |

| DAC                                                            | 32                                            |

| Switching energy versus output code                            | 33                                            |

| A 3-bit SAR ADC with the conventional switching method         | 34                                            |

| A 3-bit capacitive array with set-and-down switching method.   | 39                                            |

| A 3-bit capacitive array with $V_{CM}$ -based switching method | 42                                            |

|                                                                | Recent research trend of ADC based on FOM [4] |

| Figure 3.10 | Schematic diagram SAR ADC architecture using the                                        |    |

|-------------|-----------------------------------------------------------------------------------------|----|

|             | dual-capacitive-array DAC                                                               | 43 |

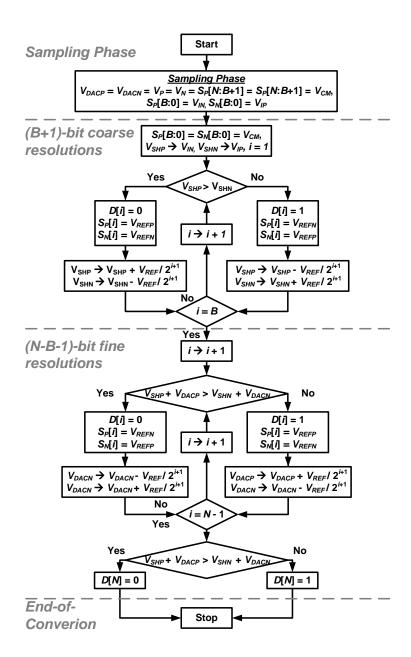

| Figure 3.11 | Flow chart of the proposed switching scheme                                             | 46 |

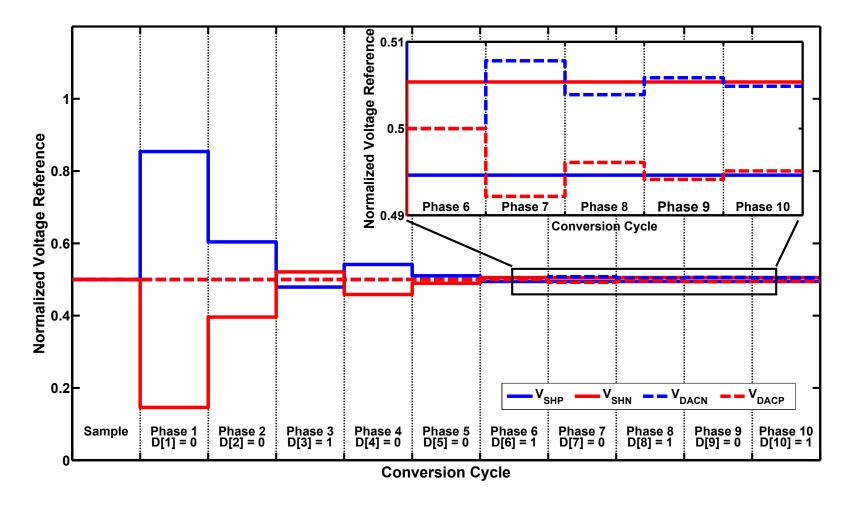

| Figure 3.12 | Waveforms of signals $V_{SHP}$ , $V_{SHN}$ , $V_{DACN}$ and $V_{DACP}$                  | 47 |

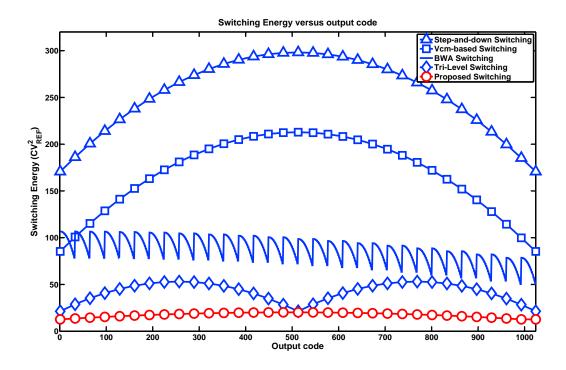

| Figure 3.13 | Switching energy versus output code                                                     | 49 |

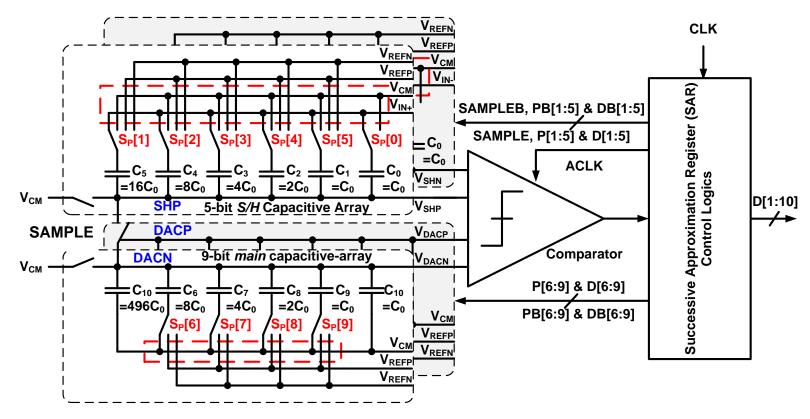

| Figure 4.1  | The proposed resolution-reconfigurable SAR ADC architecture and the ADC conversion plan | 54 |

| Figure 4.2  | Energy savings across resolution of the proposed switching                              |    |

| 8           | scheme compared to the conventional scheme                                              | 60 |

| Figure 4.3  | A 4-bit to 10-bit dual-channel SAR control logic                                        | 62 |

| Figure 4.4  | (a) Reconfigurable Shift Register built on tri-state inverter                           |    |

| _           | chain with the configurable timing sequence. (b)                                        |    |

|             | The schematic diagrams of tri-state inverter and the                                    |    |

|             | corresponding truth table and state notation. (c) Example of                            |    |

|             | a 10-bit shift register with the corresponding waveform                                 | 64 |

| Figure 4.5  | Schematic and truth table of proposed flip-flop with auto-reset.                        | 66 |

| Figure 4.6  | A schematic showing an integrated bootstrapped sampling                                 |    |

|             | switches for $S/H_X$ capacitive array                                                   | 68 |

| Figure 4.7  | Schematic of (a) a <i>S/H</i> Switch (b) a <i>main</i> Switch                           | 68 |

| Figure 4.8  | Proposed multiple-input dynamic latched comparator                                      | 69 |

| Figure 4.9  | Micrograph of entire ADC prototype                                                      | 72 |

| Figure 4.10 | Measured DNL and INL at $f_S = 250$ -kS/s in 10-bit mode                                | 74 |

| Figure 4.11 | Measured FFT with 8192-points at 250kS/s with input tone                                |    |

|             | at 335.69-Hz and 116.68-kHz, respectively                                               | 75 |

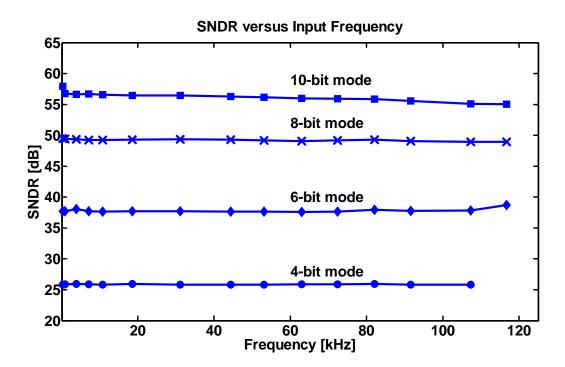

| Figure 4.12 | Measured SNDR vs. input frequency over all resolution                                   |    |

|             | modes at $f_s = 250$ kS/s at 0.6-V                                                      | 76 |

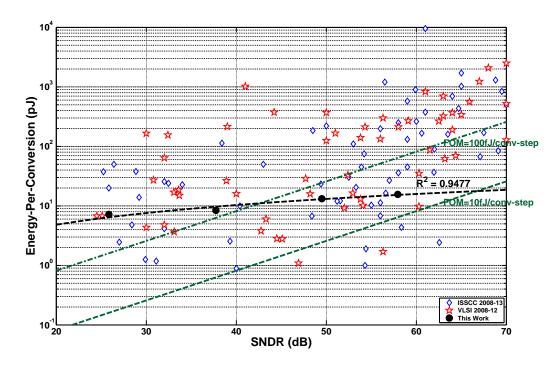

| Figure 4.13 | Comparison to State-of-The-Art works [4]                                                | 77 |

| Figure 5.1  | N-bit Conventional Binary-weighted capacitive array DAC                                 | 84 |

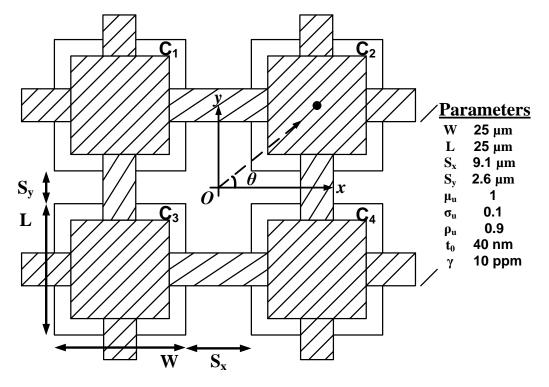

| Figure 5.2  | Experimental Setup for the geometry of unit capacitors and                              |    |

|             | mismatch parameters                                                                     | 85 |

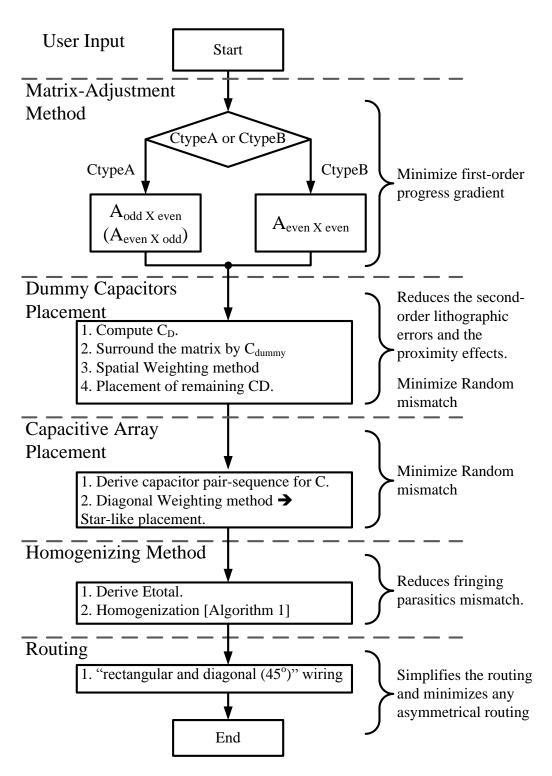

| Figure 5.3  | Flow chart illustrating the various techniques used in the                              |    |

|             | proposed placement strategy                                                             | 91 |

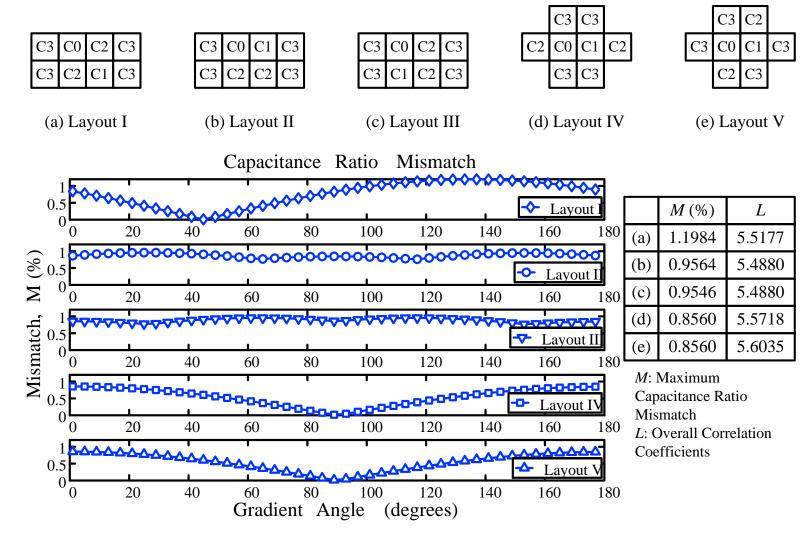

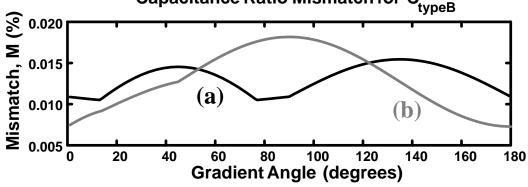

| Figure 5.4  | Experimental placements for 3-bit $C_{typeA}$ in $A_{2\times4}$ and $A_{3\times4}$ .    | 94 |

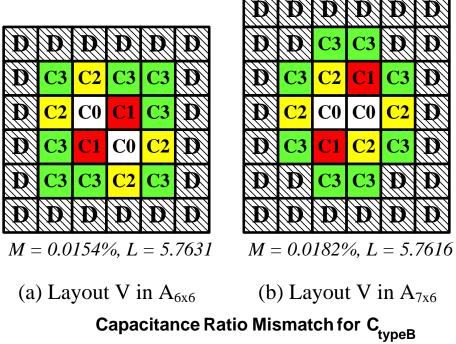

| Figure 5.5  | Experimental placements for 3-bits $C_{typeB}$ capacitive arrays    |      |

|-------------|---------------------------------------------------------------------|------|

|             | in $A_{6\times 6}$ and $A_{6\times 7}$                              | 95   |

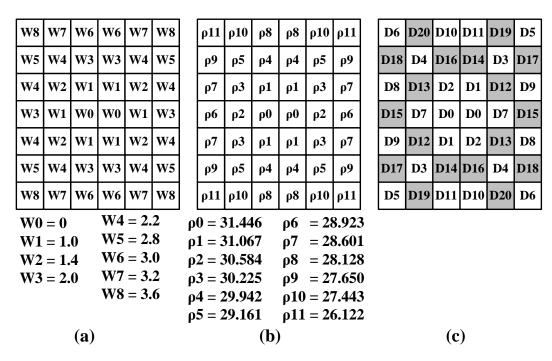

| Figure 5.6  | Illustrations of entry weight definitions (a) Distance weight       |      |

|             | (b) Spatial correlation weight (c) Diagonal weight                  | 97   |

| Figure 5.7  | Placement dummy unit capacitors and dummy edge                      |      |

|             | computation for 9-bit $C_{typeA}$ capacitive array with dummy       |      |

|             | unit capacitors in $A_{27\times26}$                                 | 98   |

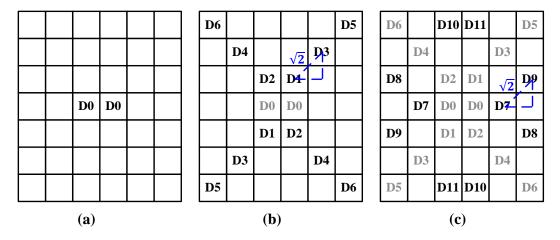

| Figure 5.8  | Illustrating the procedure of defining diagonal weights             | 100  |

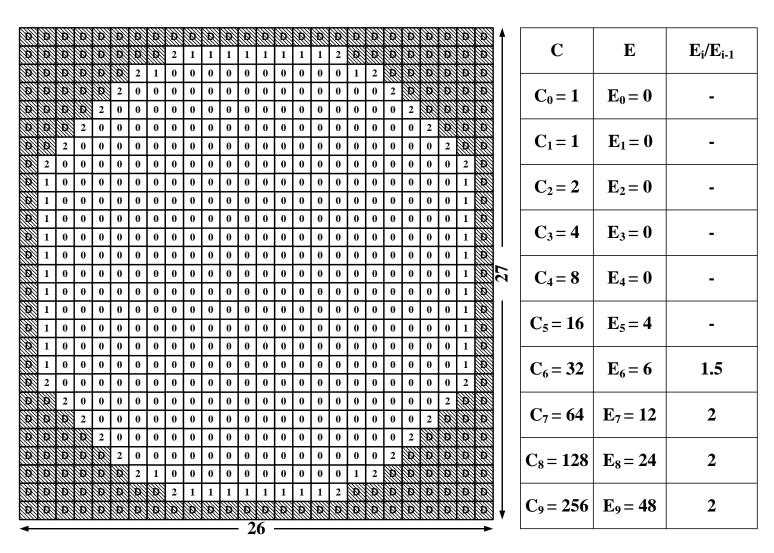

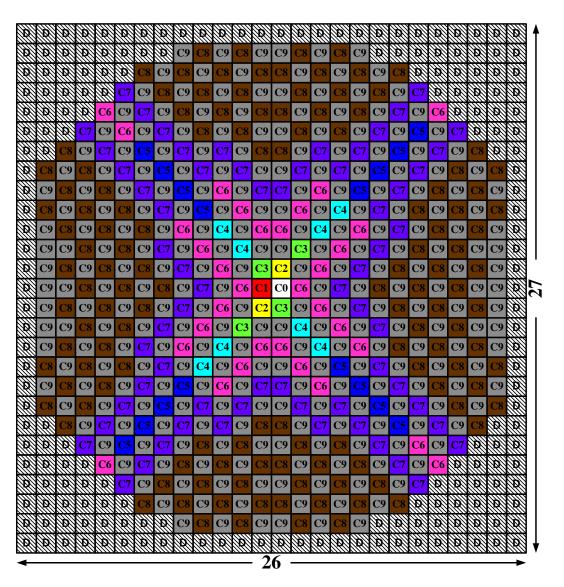

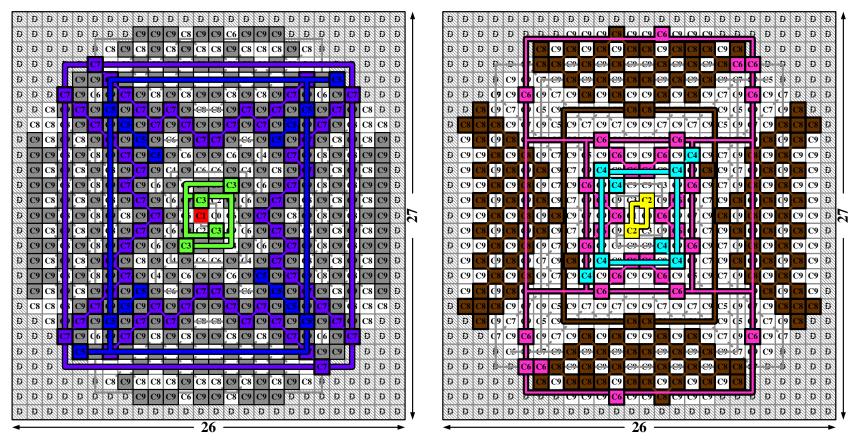

| Figure 5.9  | The placement result of 9-bit $C_{typeA}$ capacitive array with     |      |

|             | dummy unit capacitors in $A_{27\times26}$                           | 102  |

| Figure 5.10 | Layout details showing the parasitic shielding and $45^{\circ}$     |      |

|             | routing used in 3-bits $C_{typeB}$ capacitive array layout          | 105  |

| Figure 5.11 | Final placement result of 9-bit $C_{typeA}$ capacitive array with   |      |

|             | dummy unit capacitors in $A_{27\times26}$ . The coloured rectangles |      |

|             | and diagonal wires represent the routing connection of the          |      |

|             | capacitors                                                          | 107  |

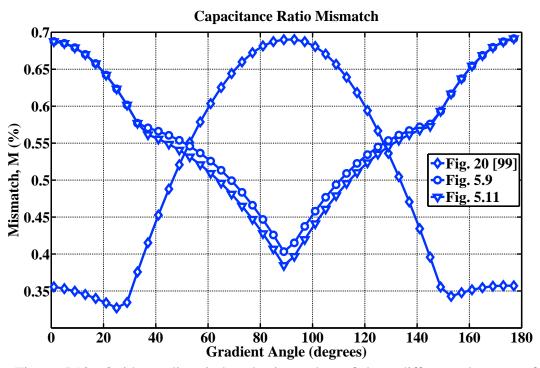

| Figure 5.12 | Oxide-gradient-induced mismatches of three different                |      |

|             | placement for 9-bit $C_{typeA}$ capacitive array                    | 109  |

| Figure 6.1  | Linearity of the CBW and BWA DACs                                   | 117  |

| Figure 6.2  | Schematic diagram of a single-ended N-bit SAR ADC using             |      |

|             | (a) the CBW DAC and (b) the BWA DAC                                 | 119  |

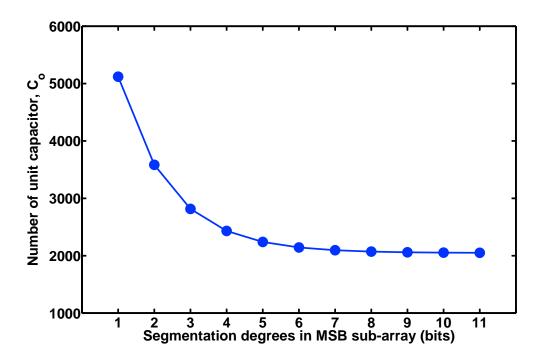

| Figure 6.3  | Total number of unit capacitor required for a 12-bit SAR            |      |

|             | ADC using the BWA DAC with different segmentation degrees           | .120 |

| Figure 6.4  | Switching energy consumption of a 12-bit charge                     |      |

|             | redistribution SAR ADC using the BWA DAC with                       |      |

|             | different segmentation degrees                                      | 121  |

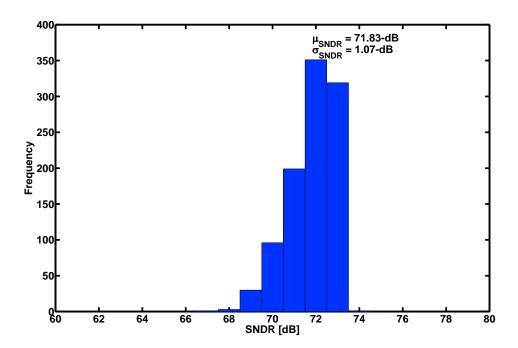

| Figure 6.5  | The histogram of the SNDR with 1000 Monte Carlo                     |      |

|             | simulations for a 12-bit charge-redistribution SAR ADC              |      |

|             | using the CBW DAC with 1% standard deviation in the unit            |      |

|             | capacitor                                                           | 123  |

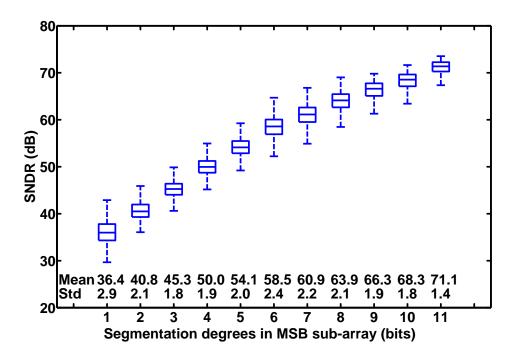

| Figure 6.6  | The histogram of the SNDR with 1000 Monte Carlo                     |      |

|             | simulations for a 12-bit charge-redistribution SAR ADC              | 10:  |

|             | using the CBW DAC with different segmentation degrees               | 124  |

| Figure 6.7  | Schematic diagram of a single-ended N-bit SAR ADC using         |     |

|-------------|-----------------------------------------------------------------|-----|

|             | the proposed 2-segmented split capacitive array DAC             | 126 |

| Figure 6.8  | Total number of unit capacitor required for a 12-bit SAR        |     |

|             | ADC using the improved split-capacitive-array DAC with          |     |

|             | different segmentation degrees                                  | 127 |

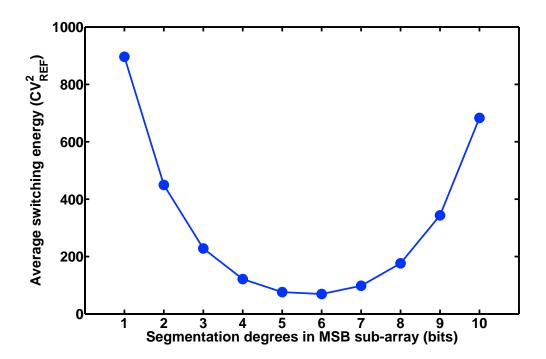

| Figure 6.9  | Switching energy consumption of a 12-bit charge                 |     |

|             | redistribution SAR ADC using the improved                       |     |

|             | split-capacitive-array DAC with different segmentation          |     |

|             | degrees                                                         | 128 |

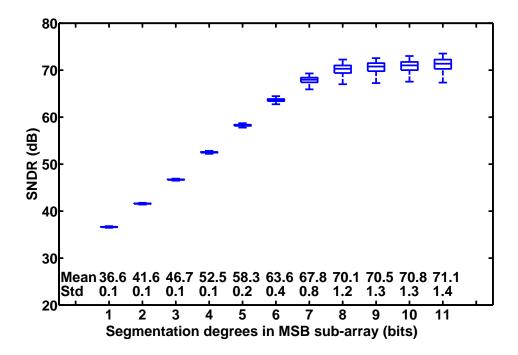

| Figure 6.10 | The histogram of the SNDR with 1000 Monte Carlo                 |     |

|             | simulations for a 12-bit charge-redistribution SAR ADC          |     |

|             | using the improved split-capacitive-array DAC with different    |     |

|             | segmentation degrees                                            | 130 |

| Figure 6.11 | Schematic diagram of a single-ended <i>N</i> -bit SAR ADC using |     |

|             | the proposed 3-segmented split capacitive array DAC             | 133 |

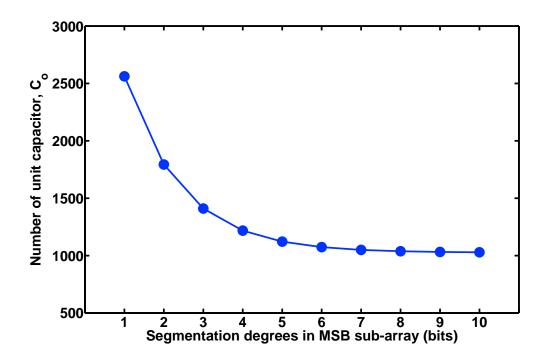

| Figure 6.12 | Total number of unit capacitor required for a 12-bit SAR        |     |

|             | ADC using the 3-segmented split-capacitive-array DAC with       |     |

|             | different segmentation degrees                                  | 134 |

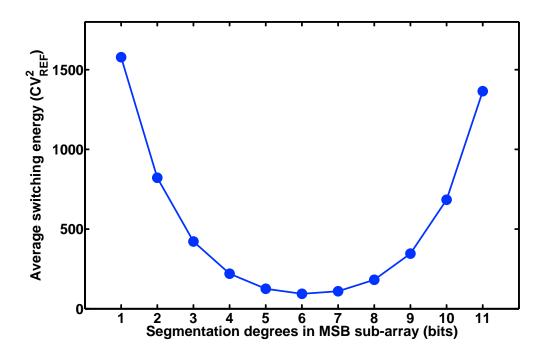

| Figure 6.13 | Switching energy consumption of a 12-bit charge                 |     |

|             | redistribution SAR ADC using the 3-segmented                    |     |

|             | split-capacitive-array DAC with different segmentation          |     |

|             | degrees                                                         | 138 |

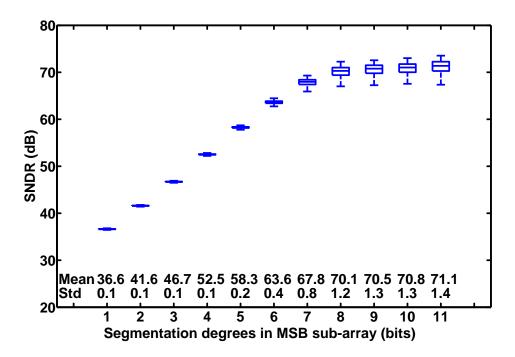

| Figure 6.14 | The histogram of the SNDR with 1000 Monte Carlo                 |     |

|             | simulations for a 12-bit charge-redistribution SAR ADC          |     |

|             | using the 3-segmented split-capacitive-array DAC with           |     |

|             | different segmentation degrees                                  | 140 |

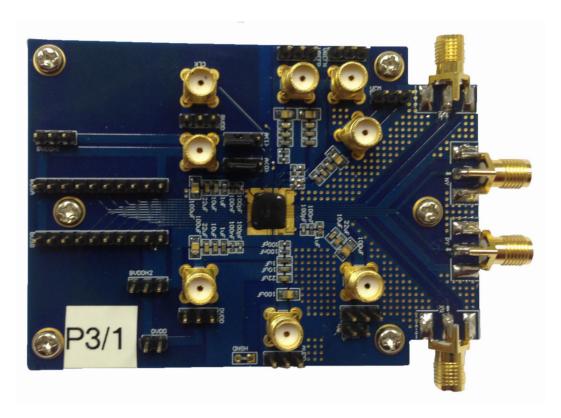

| Figure B.1  | PCB layout with COB packaging                                   | 160 |

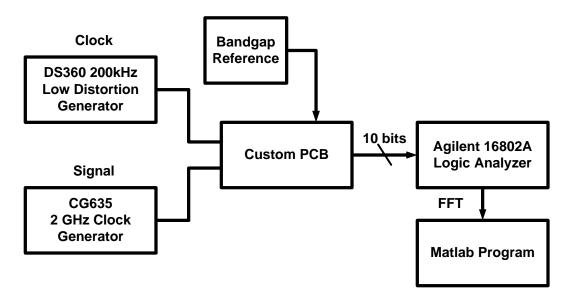

| Figure B.2  | Testing plan with listed equipment                              | 160 |

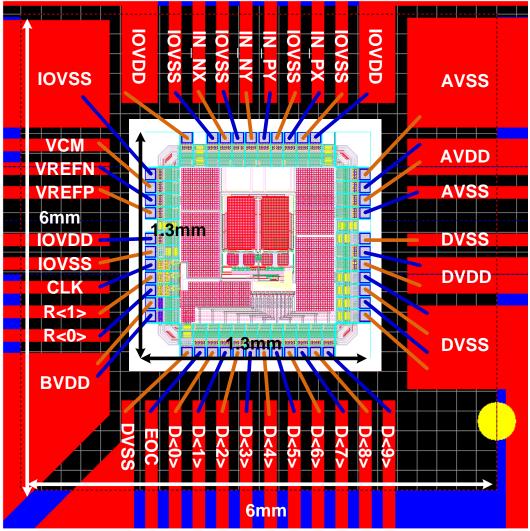

| Figure B 3  | Bonding diagram of the ADC test chin                            | 161 |

### **List of Tables**

| Table 3.1 | Comparison of various switching schemes 48                                                                                                                                        |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 4.1 | ADC Performance Summary                                                                                                                                                           |

| Table 4.2 | Comparison to State-of-The-Art SAR ADCs                                                                                                                                           |

| Table 5.1 | Experimental Results with our proposed placement and common-centroid placement in [97]. ( <i>M</i> : capacitance mismatch ratio; <i>L</i> : overall correlation coefficients) 110 |

| Table 5.2 | Study of Capacitance mismatch ratio, $M$ , on 8-to-11-bit                                                                                                                         |

|           | $C_{typeA}$ with varying oxide thickness, $t_o$ and oxide gradient,                                                                                                               |

|           | $\gamma$                                                                                                                                                                          |

| Table 5.3 | Comparisons of capacitance mismatch ratio, overall                                                                                                                                |

|           | correlation coefficients, and running time for the heuristic                                                                                                                      |

|           | algorithm [92], SA algorithm [99] and our work. (M:                                                                                                                               |

|           | capacitance mismatch ratio; L: overall correlation coefficients) 113                                                                                                              |

| Table 6.1 | Performance Comparison for a 12-bit SAR ADC 141                                                                                                                                   |

| Table A.1 | ADC Performance Summary from ISSCC paper 1997 - 2012 150                                                                                                                          |

| Table A.2 | ADC Performance Summary from VLSI paper 1997 - 2012 . 156                                                                                                                         |

|           |                                                                                                                                                                                   |

#### **List of Abbreviations**

ADC ..... Analog-to-Digital Converter

BWA ...... Conventional Binary-Weighted Split Capacitive-Array

..... with a Fractional Attenuation Capacitor

**CBW** ...... Conventional Binary-Weighted Capacitive-Array

DAC ..... Digital-to-Analog Converter

**DCA** ...... Dual-Array Capacitive-Array

DNL ..... Differential Non-Linearity

**ENOB** ..... Effective Number of Bits

FFT ..... Fast Fourier Transform

FOM ..... Figures of Merit

GHz ..... Gigahertz

**INL** ..... Integral Non-Linearity

**LSB** ..... Least Significant Bit

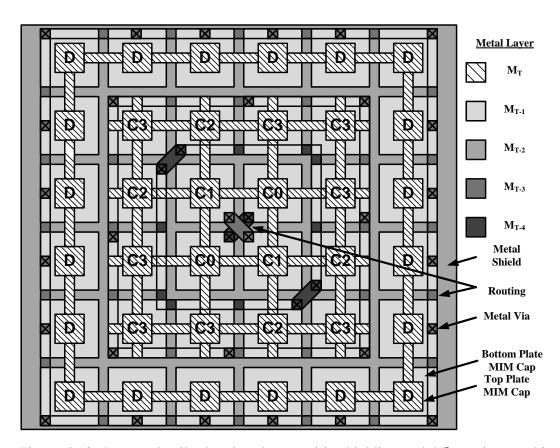

MIM ..... Metal-Insulator-Metal

MHz ..... Megahertz

MSB ..... Most Significant Bit

**NP** ...... Non-Deterministic Polynomial-Time

S/H ..... Sample-and-Hold

**SAR** ...... Successive-Approximation-Register

SA ..... Simulated-Annealing

SFDR ..... spurious-free dynamic range

**SNDR** ...... Signal-to-Noise Distortion Ratio

#### Chapter 1

#### Introduction

# 1.1 Development of analog-to-digital converters (ADCs)

For the past two decades, the rapid development of complementary metal oxide semiconductor (CMOS) technologies has decreased the power supply voltages, and along with the dynamic power. Power Supply voltages of 5-V, 3.3-V, 2.5-V, 1.8-V and 1.2-V have followed as CMOS line spacings shrank to 0.6-μm, 0.35-μm, 0.25-μm, 0.18-μm, 0.13-μm and sub-100nm. One of the keys to the success of these systems has been the advance in analog-to-digital converters (ADCs) which convert the continuous-time signals to the discrete-time, binary-coded form. ADCs are ubiquitous critical components for information processing, computing, data transmission, and control systems. Despite the large variety of ADCs for various applications, their performances can be summarized by a relatively small number of parameters: sampling rate, resolution (number of bits per sample), signal-to-noise distortion ratio (*SNDR*), spurious-free dynamic range (*SFDR*) and power dissipation [1].

A widely adopted figures of merit (*FOM*), also called *Walden's* figures of merit, can be used to benchmark all the state-of-the-art ADCs. This *FOM* is the most commonly used for Nyquist ADCs considering resolution, bandwidth and power consumption in order to provide a platform for energy efficiency comparison [2, 3].

$$FOM = \frac{P}{2^{ENOB} \times f_s} \tag{1.1}$$

where P is the power dissipation,  $f_s$  is the Nyquist sampling rate, and ENOB is the effective number of bits defined by the SNDR as:

$$ENOB = \frac{SNDR_{dB} - 1.76}{6.02} \tag{1.2}$$

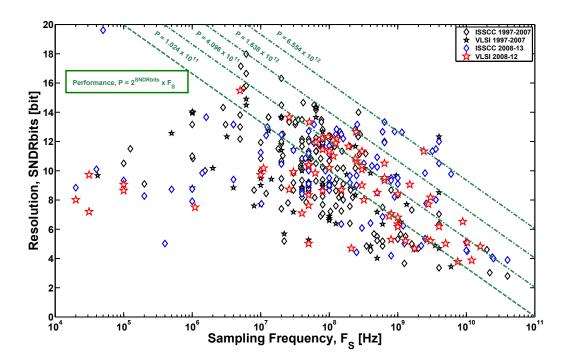

Figure 1.1 shows the developments of the state-of-the-art ADCs in the *IEEE International Solid-State Circuits Conference (ISSCC)* and *IEEE Symposium on VLSI Circuit (VLSI)* over the last decade [4]. The ADCs are arranged according to their sampling frequency and resolution. A close study of those ADCs developed over the last five years shows that there are three key areas of developments. The first key development is for the application in miniature wireless sensors, which enable remote military surveillance, environmental monitoring, chemical detection and medical monitoring, requiring 8-to-12-bits of resolution at less than 1 MHz frequency. The second key development is for the military radar, software defined radio and terrestial and satellite telecommunications, which require 8-to-14-bits resolution and sampling rates of a few tens of megahertz (MHz) to a few hundreds of MHz range. Most of the academia research have focused on these two research areas. The third development is for high speed instrumentation and optical communication applications, which require more than tens of gigahertz (GHz) sampling rate and additional dedicated on-chip peripheral circuits such as synthesizer, memory blocks

and DSP processors to accomplish the test measurement.

Figure 1.1: Recent research trend of ADC based on Resolution and Sampling Speed [4].

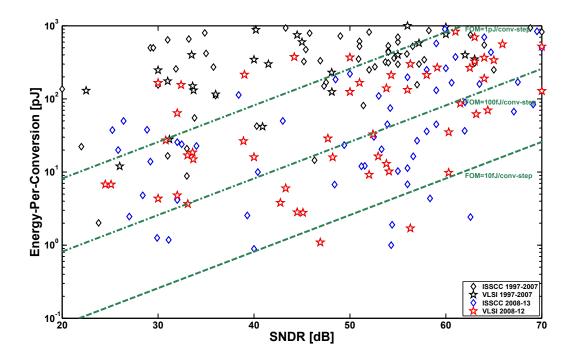

Figure 1.2 compares the energy efficiency versus resolution for the state-of-the-art ADCs. Each green line indicates different orders of magnitude of FOM. It is clearly shown that the performances of the ADCs have improved more than  $100\times$  over the last five years.

Figure 1.2: Recent research trend of ADC based on FOM [4].

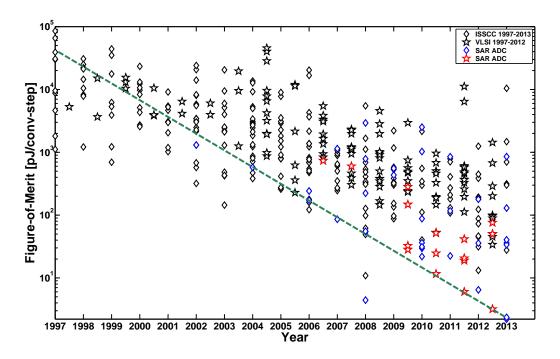

Figure 1.3 shows the FOM of the state-of-the-art ADCs across the years [4]. In particular, the successive-approximation-register (SAR) ADC (highlighted in blue and red) has become the most popular architecture over the last five years [4]. The green line indicates the improvement of SAR ADCs over the years and it is estimated that the performances of the SAR ADCs have improved by  $1000 \times$  over the last five years. Generally, the FOM of the state-of-the-art SAR ADCs are at least  $10 \times$  better than other architectures and the best FOM on record is a SAR ADC [4]. This is because the SAR ADC has a lower design complexity compared to other ADCs' architectures, such as pipelined and oversampled sigma delta converters.

Figure 1.3: Recent research trend of ADC across the years.

#### 1.2 Organization of the dissertation

This dissertation outlines the study and design of low-power SAR ADC and DAC and it is a result of the research performed at the VLSI/Signal Processing Laboratory and Bioelectronics Laboratory, Department of Electrical and Computer Engineering, National University of Singapore between August 2009 and July 2014. The research during this period has resulted in the following publications and journal submissions:

- 1. **Yongfu Li**, Yong Lian and Perez, V., "Design optimization for an 8-bit microcontroller in wireless biomedical sensors," *IEEE Biomedical Circuits and Systems Conference (BioCAS)*, Nov. 2009, pp.33-36.

- 2. **Yongfu Li**, Zhe Zhang and Yong Lian, "Energy-efficient charge-recovery switching scheme for dual-capacitive-arrays SAR ADC," *Electronics Letters*, vol. 49, no. 5, pp.330-332, 2013.

- 3. **Yongfu Li**, Zhe Zhang, Dingjuan Chua and Yong Lian, "Placement for binary-weighted capacitive-array in SAR ADC using multiple weighting methods", *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 33, no. 9, pp.1277-1287, 2014.

- 4. **Yongfu Li** and Yong Lian, "An improved binary-weighted split capacitive-array DAC for high resolution SAR ADCs," *Electronics Letters*, vol. 50, no. 17, pp.1194-1195, 2014.

- 5. Yongfu Li, Wei Mao, Zhe Zhang and Yong Lian, "An ultra-low voltage comparator with faster comparison time and reduced offset voltage," *IEEE Asia Pacific Conference on Circuits and Systems (APCCAS)*, 2014.

- 6. Yongfu Li, Zhe Zhang and Yong Lian, "A Dual-Channel 0.6-V 250-kS/s 4-to-10-bit Resolution-Reconfigurable SAR ADC for Sensor Applications," under review by *IEEE Journal of Solid-State Circuits*.

- 7. **Yongfu Li** and Yong Lian, "An unary-binary segmentation with multiple-split capacitive-array DAC architecture for high resolution SAR ADC," submitting to *IEEE Transactions on Circuits and Systems II: Express Briefs*.

- 8. **Yongfu Li**, Xiaoyang Zhang, Zhe Zhang and Yong Lian, "A 0.4-to-1.2-V fully-digital low-dropout voltage regulator with fast-transient algorithm", submitting to *IEEE Transactions on Circuits and Systems I: Regular Papers*.

- Yongfu Li, Zhe Zhang, Xiaoyang Zhang and Yong Lian, "A 726-nW, 940-mVpp, 1-kpulses/s all-digital 3-to-5-GHz impulse UWB transmitter using in 130-nm CMOS", submitting to *IEEE Transactions on Circuits and Systems II: Express Briefs*.

- 10. Zhe Zhang, Yongfu Li, Koen Mouthaan and Yong Lian, A Miniature inductorless IR-UWB transceiver for wireless short-range communication and vital-Sign, under review by IEEE Transactions on Biomedical Circuits and Systems.

- 11. Xiaoyang Zhang, Zhe Zhang, **Yongfu Li**, Changrong Liu, Yong-Xin Guo and Yong Lian, "A 2.89-μW fully integrated UWB event-driven ECG sensors for dry electrode Use", submitting to *IEEE Transactions on Biomedical Circuits and Systems*.

The contributions and the outline of this dissertation is organized as follows:

**Chapter 2:** The first chapter begins with the discussion of the fundamentals of the SAR ADC. The discussion is then further extended to various advanced architectures used in the SAR ADCs and DAC architectures. This study allows everyone to have a broader understanding of SAR ADC.

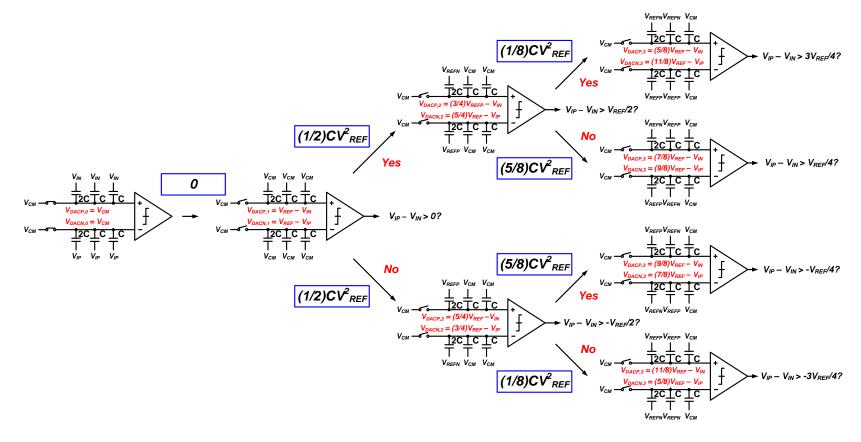

Chapter 3: In the design of a low power SAR ADC, the switching power consumption in the capacitive-array DAC constitutes a significant part of the total power consumption and it even determines the lower bound on the ADC power consumption [5]. It is instructive to have a thorough understanding of the switching power consumption of different types of switching methods. This study leads to the development of a charge-recovery switching method for the dual-capacitive-array DAC architecture. The proposed switching method achieves 98.7% and 46.9% reduction in switching energy and area respectively while maintaining the switching energy constant for different output codes. This scheme achieves the lowest switching energy among existing switching schemes [6].

Chapter 4: The miniature sensor requires multiple ADC channels to sense various telemetry readings. In order to reduce the area and power consumption per channel, the SAR ADC with the dual-capacitive-array DAC architecture, as described in Chapter 3, is extended to multiple-channel ADC, which reuses multiple building blocks, such as the DACs, the comparator and the SAR logic. It operates at a supply voltage of 0.6-V and achieves a maximum sampling rate of 250-kS/s and a FOM of 24-fJ/step. To meet various application-level constraints, the ADC is able to configure its resolution from 4-to-10-bit with a scalable SAR control logic. To minimize the switching power consumption across all resolution modes, the energy-efficient charge-recovery switching method achieves a 3.6-to-77.5× reduction compared to the conventional charge-redistribution scheme.

As the resolution of the ADC increases, the matching requirements for the unit capacitors (i.e., increase the area of the unit capacitor) and the number of unit capacitors in the conventional binary-weighted capacitive-array (CBW) DAC increase exponentially, thus increasing the area, the switching power consumption and the settling time in the DAC. Therefore, two methods are proposed to address these challenges in high resolution (>10-bit) capacitive-array DACs.

Chapter 5: First, a placement strategy is proposed to address the layout's mismatches, where a matrix-adjustment method is proposed to optimize the size of the CBW DAC and different placement techniques and weighting methods are proposed for the placement of active and dummy unit capacitors. The resulting star-like placement increases the degree of dispersiveness (i.e., reduce random mismatch), reduces the first-order oxide-gradient-induced mismatches and the second-order lithographic errors and achieves a more symmetrical routing compared to existing works. A homogenization method is also proposed to reduce the asymmetrical fringing mismatches among the capacitive-array, thus improving the systematic mismatch between the capacitive-array and the dummy capacitors.

Chapter 6: Second, two new types of split capacitive-array DAC architectures are proposed to reduce the area, the power consumption and improve the linearity compared to the CBW DAC and the conventional binary-weighted split capacitive-array with a fractional attenuation capacitor (BWA) DAC. A design methodology is proposed to determine the segmentation degree in the DAC for optimum performance. For a 12-bit SAR ADC, the proposed DACs reduce the input load capacitance and area by  $2\times$  and  $4\times$ , respectively, and the switching power by  $15\times$  and  $15.5\times$ , respectively, compared to the CBW DAC. It also improves the linearity, minimizes the mismatch variation and reduces the switching power by  $3.75\times$  and  $3.87\times$ , respectively, compared to the BWA DAC.

Finally, Chapter 7 concludes the research findings and suggests future work.

#### Chapter 2

# Successive approximation analog-to-digital converters

#### 2.1 Basic operation

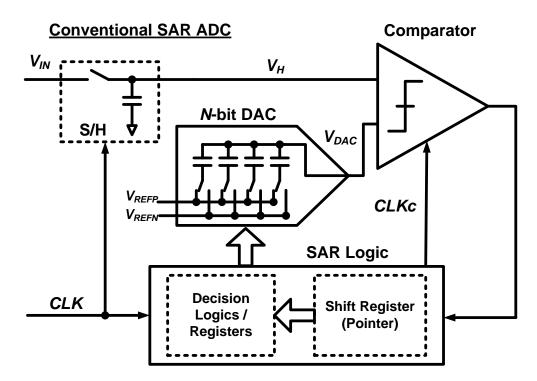

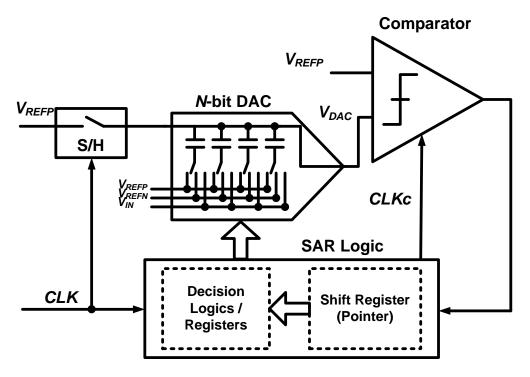

During the conversion from an analog signal to a digital code word, the ADC performs three different tasks, i.e., sampling, quantization and comparison. Similarly, for a SAR ADC, these three tasks correspond to the sample-and-hold (S/H) sampling circuit, the capacitive-array DAC and the comparator, as shown in figure 2.1. A digital finite state machine (itself called a SAR control logic) applies a binary search algorithm to the DAC and search through all possible quantization levels before converging to the final digital word, which is a digital representation of the analog input. The digital code corresponds to a voltage range defined by the reference voltages,  $V_{REFP}$  and  $V_{REFN}$ , where the analog input voltage lies.

The details of the conversion process for an *N*-bit SAR ADC are first described conceptually in [7]. Basically, the SAR ADC operates in 2 different phases: *sampling*, during which the input voltage is stored and *bit-cycling*, during which bits of the corresponding digital word are successively resolved. The entire process

Figure 2.1: Schematic diagram of a N-bit conventional SAR ADC.

requires at least N+1 clock periods to complete one conversion cycle.

A detailed switching method is described as follow:

- 1. <u>Sampling Phase</u>: The input analog signal,  $V_{IN}$  is fed through a S/H sampling circuit so that the sampled voltage,  $V_H$  does not change during the entire conversion phase. The output voltage of capacitive-array DAC,  $V_{DAC}$  is reset to  $V_{REFN}$ .

- 2. <u>Bit-cycling Phase</u>: During the first clock cycle, the MSB capacitor  $C_1$  is connected to  $V_{REFP}$  while the remaining capacitors connected to  $V_{REFN}$ . The comparator compares and determines if the sampled voltage  $V_H$  is larger or smaller than the output voltage of the capacitive-array DAC. The MSB bit (D[1]) is determined and stored in the SAR control logic.

- 3. In the next bit cycle, the capacitor  $C_2$  is connected to  $V_{REFP}$  and  $C_1$  is connected to  $V_{REFP}$  if D[1] is 1, else  $C_1$  is connected to  $V_{REFN}$ . The SAR control logic changes the output of the DAC according to comparator's output.

$V_H$  is compared to the output of the DAC and the next MSB bit (D[2]) is determined.

4. Step 3 is repeated for the next N - 1 cycle until the output of the DAC converges to the value of  $V_H$  within the resolution of the converter.

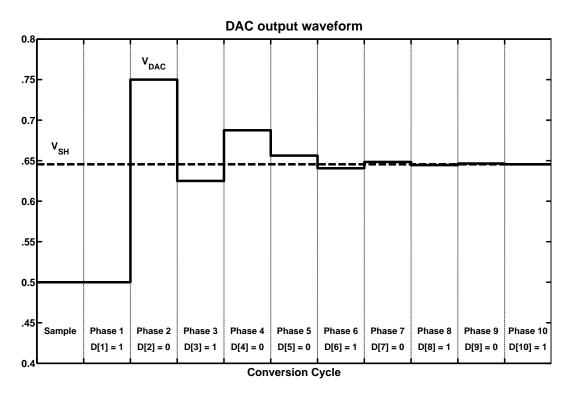

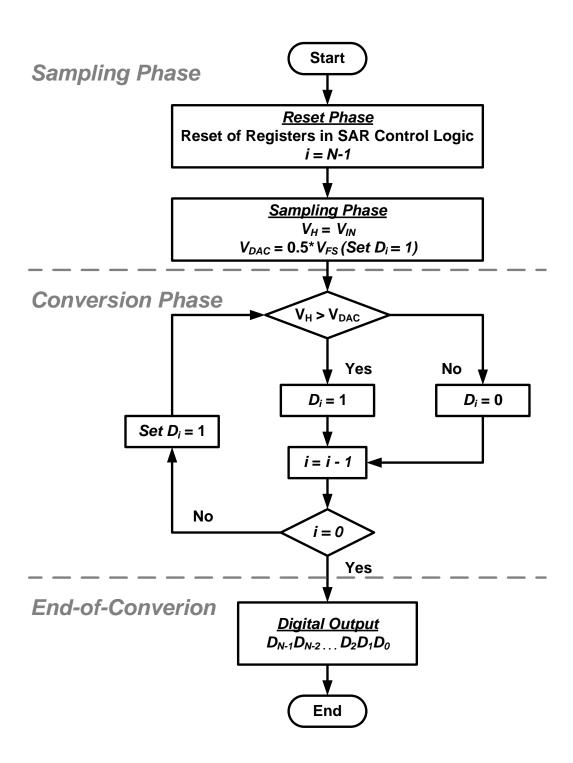

An example of the voltage waveform of the conventional switching procedure is shown in figure 2.2. The entire process can be simplified into a flow-chart, as shown in figure 2.3.

Figure 2.2: Waveform of the conventional switching procedure for a N-bit DAC output waveform.

Figure 2.3: Flow Chart for a N-bit conventional SAR ADC.

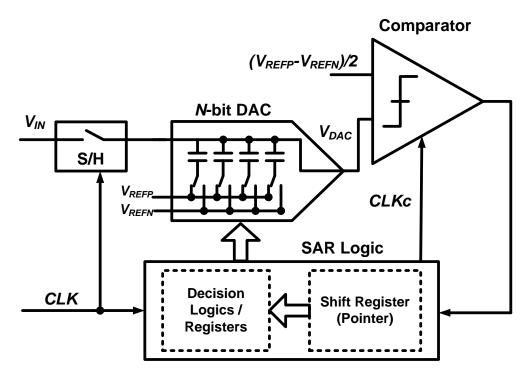

#### 2.1.1 Conventional charge-redistribution SAR ADC

Beside the architecture as shown in figure 2.1, the conventional binary-weighted SAR ADC can also be used without any additional sampling capacitor for the S/H circuit as shown in figures 2.4 and 2.5. This is one of the earliest SAR ADC architecture, which is know as "charge-redistribution" converter [7]. The sampling capacitor is realised by the capacitive-array DAC itself through the "top plate sampling" technique (figure 2.4) or the "bottom plate sampling" technique (figure 2.5) [8]. During the sampling phase, the input signal is stored on the capacitive-array DAC. During the bit cycling phase, the bottom plates of the capacitors are switched one after the other from  $V_{REFN}$  to  $V_{REFP}$  and the  $V_{DAC}$  converses to  $V_{VREFP}$ . Each technique has its own merits and flaws. For example, the "top plate sampling" technique does not requires any additional sampling switches but the S/H switches induce additional parasitic capacitances, reducing the input voltage range of the SAR ADC. On the other hand, the "bottom plate sampling" technique minimizes the effect of channel charge injection and improves the switches' linearity but it requires additional switches and non-overlapping clock circuit, increasing the design complexity and area.

Figure 2.4: Schematic diagram of a N-bit conventional SAR ADC using the top plate sampling technique and without an explicit S/H circuit.

Figure 2.5: Schematic diagram of a N-bit conventional SAR ADC using the bottom plate sampling technique without an explicit S/H circuit.

#### 2.2 Advanced techniques in SAR ADC architectures

Technology scaling continues to benefit the SAR ADCs due to the reduction of switching energy and minimum capacitor size, but the wafer cost for advanced CMOS prcoess (65-nm to 28-nm) continues to increase during the recent years, which is due to poor yield and high production cost [9, 10]. Therefore, in order to further improve the energy efficiency of the SAR ADCs, it is important to achieve architectural innovation that can be used in any technology. Recent research efforts in SAR ADCs have led to the numerous developments of different SAR ADC architectures, which improve the sampling rate and energy efficiency. A deeper understanding of these advanced SAR ADC architectures is necessary. The key techniques will be discussed in the following sections and a comprehensive summary of all the reported state-of-the-art SAR ADC architectures from *IEEE ISSCC* and *VLSI* are listed in Appendix A.

#### 2.2.1 Asynchronous SAR ADCs

In the design of a high speed SAR ADC, a phase-locked loop is needed to provide the high frequency clock but it increases the design complexity and hardware overhead. An asynchronous system provides a convenient solution by generating the fast clock internally through control signal and comparator's latching time [11–23]. Thus, the sampling rate is equal to the clock rate and it does not need any additional phase-locked loop circuit. However, one of the greatest challenge is to reduce the risk of metastability in the asynchronous SAR ADC [24]. The on-going research is to design a more robust asynchronous logic and metastable detector to address this issue.

#### 2.2.2 Pipelined-SAR ADCs

The traditional pipelined ADCs can easily achieve high sampling rate but it dissipates considerable amount of power in the amplifiers and require complex calibration schemes to achieve high accuracy. Furthermore, technology scaling has severely aggravated the design of the analog circuits. Recently research developments have demonstrated that the SAR ADCs [17, 23, 25, 26] are capable of achieving a higher energy efficiency than the traditional pipelined ADCs [27–31] for 10-to-12-bit and 50-to-100-MS/s specifications.

To take the advantage of the high-resolution property in the pipelined architecture, the two-stages pipelined-SAR ADCs were developed, which are potentially capable of achieving both high resolution and high conversion efficiency [32–36]. The first-stage of the architecture uses the capacitive-array DAC to perform residue amplification and the second stage uses the SAR ADC to replace the flash ADC in the conventional pipelined ADC and thus eliminating the need for more pipeline stages and lower the number of operational amplifiers.

#### 2.2.3 Time-interleaved SAR ADCs

Another effective way to increase the ADC's sampling rate is to use the time-interleaving SAR ADCs [22, 37–42]. To further improve the resolution, the time-interleaved technique can be incorporated into pipelined-SAR architecture [43, 44]. However, the time-interleaving ADCs introduce channel mismatch problems (i.e., channel gain and offset, bandwidth mismatches) and the *FOM* of the ADC does not improve or might even deteriorates because more power is required by the complex calibration circuits that become necessary to reduce the error between channels. Therefore, developing a low-cost high-efficiency digital calibration technique is one of the popular topics for the high-speed SAR ADCs.

#### 2.2.4 Multi-bit per cycle (flash) SAR ADCs

Comparing with the time-interleaved SAR ADC topology, another effective way to improve the ADC's sampling rate is to employ a multi-bit per cycle SAR ADC architecture [45]. He *et al* proposed a two-bit per cycle SAR ADC with interpolative resistive DACs and calibration logic to achieve an area of 0.028-*mm*<sup>2</sup> [46]. Later, Hong *et al* proposed a two-bit per cycle SAR ADC using reduced capacitive-array DACs and non-binary decision scheme to reduce the static power consumption and relax the requirement for DAC settling time [47]. Lien *et al* proposed an asynchronous subranged two-bit per cycle SAR ADC with coarse resistive DACs and fine capacitive-array DACs to reduce the number of switches and lower matching requirement of a resistive DAC [16].

This type of architecture inherently has no timing mismatch issue and thus, it is comparable to a time-interleaving SAR ADC. The ADC's sampling rate increases significantly from one to two-bit per cycle because the number of bit cycles diminishes by a factor of 2. However, more than two-bit per cycle is not recommended because a M-bit per cycle SAR ADC requires a minimum  $2^M - 1$  number of comparators and DACs, which increases the area and the power consumption. In addition, the comparators' offset induces linearity errors, which degrades the ADC accuracy.

#### 2.3 Type of DAC architecture

The DAC plays a pivotal role in the design of a SAR ADC. For a high resolution SAR ADC, the overall accuracy and linearity are primarily determined by its DAC's matching characteristics. These DACs can be broadly classified into four categories, namely switched-current DACs [48, 49], resistive R-2R DACs [50–54],

resistive-string DACs [46, 55] and capacitive-array DACs.

Early implementations used switched-current and resistive R-2R DACs, but such DACs consume static power and make them unsuitable for low power applications. Although these DACs can be made lower power by duty cycling, they require series switches to pass rail-to-rail voltages. This limits the amount of voltage scaling in the ADC, or requires a large number of bootstrapped switches [56], thus increasing power and area. Resistive-string DACs and capacitive-array DACs are the most commonly-used architectures in the current state-of-the-art SAR ADCs. A good understanding of these DACs is necessary to achieve architectural innovation in the SAR ADC and the following sections will discuss these architectures.

#### 2.3.1 Resistive-string DAC

The simplest structure of the resistive DAC is the kelvin divider or resistive-string DAC. It has recently been reconsidered for the use of high-speed multi-bit/cycle SAR ADC architectures [16, 55]. A N-bit resistive-string DAC simply consists of  $2^N$  equal resistors in series and  $2^N$  switches, one between each node of the chain and the output. This architecture is simple, and is inherently monotonic. The output is taken from the appropriate tap by closing just one of the switches. Unlike the capacitive-array DAC, a resistive-string DAC is able to provide multiple reference voltages simultaneously, which is a much more suitable choice for the multi-bit/cycle SAR ADC architecture. However, one problem with this architecture is that the output is always connected to  $2^N$  - 1 switches that are off and one switch that is on. For larger resolutions, a large parasitic capacitance appears at the output node, resulting in a slower sampling rate.

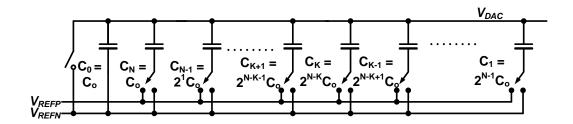

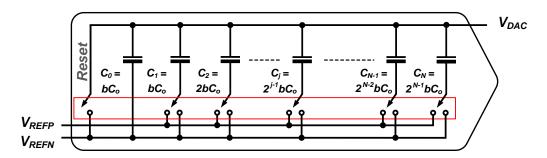

# 2.3.2 Conventional binary-weighted capacitive-array (CBW) DAC

Among all the DAC architectures, the capacitive-array DAC architecture is the most popular choice due to its zero quiescent current, which makes it appropriate for low-power applications. The charge-redistribution technique allows the *S/H* function to be realised by the capacitive-array DAC itself. The conventional way of implementing the capacitive-array DAC is the CBW DAC architecture, as shown in figure 2.6 and the value of each capacitor in the CBW DAC is given by

$$C_i = 2^{N-i}C_o, 1 \le i \le N.$$

(2.1)

As the resolution of the SAR ADC increases, the DAC requires a more stringent matching requirement for the unit capacitor (i.e. increases the area of the unit capacitor) and the total number of capacitors in the CBW DAC increase exponentially, thus increasing the area, the switching power consumption and the settling time in the DAC [57]. The capacitor matching and parasitic capacitances directly affect the non-linearity parameters of the ADC such as the INL and DNL. In this dissertation, a placement strategy is proposed to address the layout's mismatches, which will be discussed in Chapter 5.

Figure 2.6: Schematic diagram of a CBW DAC.

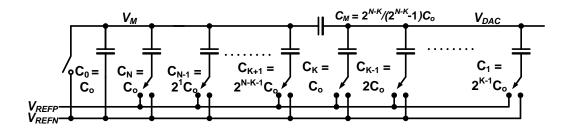

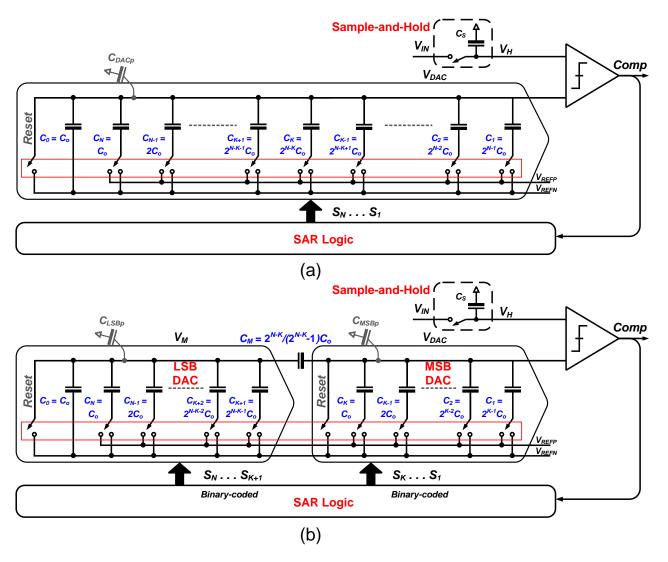

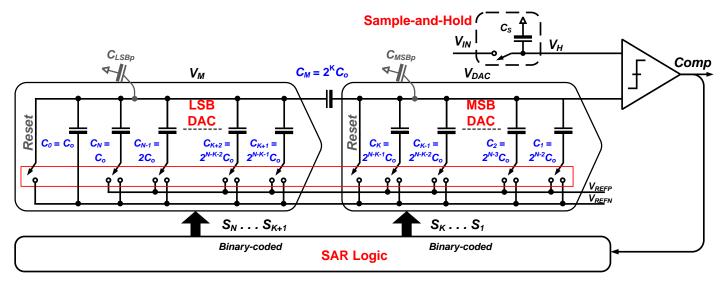

# 2.3.3 Binary-weighted split capacitive-array with attenuation capacitor (BWA) DAC

Beside the layout's mismatches, the switching power consumption and the settling time in the CBW DAC have limited the efficiency and the maximum sampling rate of the SAR ADC. The BWA DAC architecture provides an alternative solution to alleviate the performance problems in the CBW DAC [11, 23, 45, 58–62]. As shown in figure 2.7, the BWA DAC is divided into a *K*-bit MSB sub-array and a (*N-K*)-bit LSB sub-array, where the value of each capacitor is given by

$$C_{i} = \begin{cases} 2^{K-i}C_{o}, & 1 \leq i \leq K, \\ 2^{N-i}C_{o}, & K+1 \leq i \leq N, \end{cases}$$

$$C_{o}, & i = 0, \end{cases}$$

$$C_{M} = \frac{2^{N-K}}{2^{N-K}-1}C_{o}, \qquad (2.2)$$

where  $C_o$  is the capacitance of the unit capacitor,  $C_M$  is the attenuation capacitor and the total number of the capacitors are decreased by a factor of  $2^K$ . The total capacitance in each sub-array is

$$C_{MSB,total} = \sum_{i=1}^{K} C_i = (2^K - 1)C_o,$$

$$C_{LSB,total} = C_o + \sum_{i=K+1}^{N} C_i = (2^{N-K})C_o.$$

(2.3)

The key advantage of such architectures is that the size of the total capacitance does not increase exponentially with the resolution compared to the CBW DAC, reducing the switching power consumption and improving the settling time. The key limitation lies in the parasitic capacitances that destroy the desired binary ratio of the capacitive-array DAC, degrading the ADC's linearity. DAC mismatch calibration

circuits can improve the linearity of the split capacitive-array DAC [63–65] but limited resolution range. Therefore, in this dissertation, two new types of split capacitive-array DAC architectures are proposed to reduce the area, the power consumption and improve the linearity compared to the CBW DAC and the BWA DAC. Further details will be discussed in Chapter 6.

Figure 2.7: Schematic diagram of a BWA DAC.

#### 2.3.4 Passive charge sharing capacitive-array DAC

The CBW DAC can be used for passive charge sharing (instead of charge redistribution) to sample the input signal and to perform the binary-scaled feedback during the bit-cycling phase. This type of architecture processes the sampled signal in the charge domain instead of voltage domain and it avoids the use of power-consuming reference buffers [12, 66]. The ADC uses tracking capacitors to pre-track the input signals in all clock phases except during the sampling phase. Therefore, it has sufficient time to track the input and no settling problems occur. In the sampling phase, the input is sampled on a capacitor and during the conversion cycle, the charge is added to or subtracted from the sampling capacitor until the result converges to zero. For differential inputs, the sampled signals converge together and the average processed voltages become lower than the charge-redistribution SAR ADC, posing a great challenge to overcome the thermal noise limit in charge sharing SAR ADCs. This architecture also requires a complex switching network to perform

the charge addition and substraction, which easily affects the linearity of the DAC. As such, it is more intuitive to develop a more energy efficient switching method for the CBW DAC rather than charge sharing DAC.

#### 2.3.5 Non-binary (sub-radix-2) capacitive-array DAC

In the design of a high speed SAR ADC, the SAR ADC suffers from DAC settling issues and the incompletely settled DAC leads to a wrong decision. Thus, the DAC settling issue limits the sampling rate of the SAR ADC. A non-binary weighted capacitive-array can tolerate DAC settling error at the cost of increased design complexity and hardware overhead [67]. This technique generates more decision levels and reduces the effective input range by a factor smaller than 2 after each bit cycling phase. Therefore, even if a wrong decision happens during a conversion, as long as the remaining bit cycling operations are correct, it is possible to get a correct digital output code at the cost of extra bit cycles. There are several digital codes for each input voltage. By generating more decision levels, a certain range of errors do not have influence on the conversion result. However, it increases the design complexity and hardware overhead. It needs extra circuits, such as ROM and arithmetical unit to correct the digital output code and it is not easy to achieve matching layout for non-binary scaled capacitive-array. Liu et al first reported a binary-scaled error compensation method which results in less hardware and the capacitive-array is binary-scaled which is favoured in device matching for layout [26].

# Chapter 3

## **Analytical Study Of The**

# **Capacitive-Array DAC's Switching**

## **Methods**

#### 3.1 Introduction

In the design of a low power SAR ADC, the switching power consumption in the capacitive-array DAC constitutes a significant part of the total power consumption and it even determines the lower bound on the ADC power consumption [5]. The switching power consumption depends on the total capacitance, input signal swing, and the switching method used. Therefore, it is instructive to have a thorough understanding of the switching power consumption for the various switching methods, such as charge-recycling switching [68], energy-saving switching [69], set-and-down switching [70],  $V_{CM}$  charge-recovery switching [23]. Furthermore, each method has a different impact on the comparator's dynamic offset, the DAC's linearity and the ADC's dynamic performance. For example, switching methods in [70–72] does not have a constant common-mode input throughout the entire

bit-cycling phase, thus causing the dynamic offset of the comparator to vary and degrading the ADC's linearity [73].

For ease of understanding, all calculations are demonstrated with a 3-bit differential SAR ADC. The differential architecture is preferred because it is less susceptible to supply and substrate noises and increases input signal swing with a good common-mode noise rejection.

#### 3.2 Analysis of switching energy

The switching power consumption can be analyzed by calculating the total energy drawn from the reference voltages  $V_{REFP}$  and  $V_{CM}$  when switching the capacitive-array. An example of the switching power consumption of the reference voltage,  $V_{REFP}$ , due to the capacitor switching for an N-bit SAR ADC can be calculated

$$P_{REFP} = \frac{V_{REF}}{T_S} \sum_{i=1}^{N} Q_i \tag{3.1}$$

where  $V_{REF}$ ,  $V_{REFP}$ ,  $V_{CM}$  and  $V_{REFN}$  are related by

$$V_{REF} = V_{REFP} - V_{REFN}, (3.2)$$

$$V_{CM} = 0.5 \times (V_{REFP} - V_{REFN}).$$

(3.3)

where  $T_S$  is the time period for the entire conversion phase. In most structures, one clock cycle is allocated for the sampling phase and N clock cycles for the bit cycling phase. Therefore,  $T_S = (N+1)/f_{CLK}$  where  $f_{CLK}$  is the clock frequency of the SAR ADC.  $Q_i$  can be calculated at each clock cycle and it can be generalized into the sampling to MSB transition phase and the bit cycling phase.

#### 3.2.1 From sampling to MSB transition phase

The fundamental principle of sampling the input voltages,  $V_{IP}$  and  $V_{IN}$  to the capacitive-array DACs can be generally classified into the conventional charge-redistribution sampling technique (figure 3.1), the top plate sampling technique (figure 3.2) and the bottom plate sampling technique (figure 3.3) [8]. It is assumed that at the beginning of the bit-cycling phase, the input voltages have been fully sampled and that the sampling switches are open.

For the conventional charge-redistribution sampling technique (figure 3.1), the input voltages,  $V_{IP}$  and  $V_{IN}$  are sampled onto the bottom-plate of the capacitive-array DACs. During the transition to the bit-cycling phase, the total charge  $Q_1$  that supplies from the reference voltages  $V_{REFP}$  and  $V_{CM}$  to the capacitive-array DACs is

$$Q_{1} = \Delta Q[DACp_{0} \rightarrow DACp_{1}] + \Delta Q[DACn_{0} \rightarrow DACn_{1}]$$

$$= C_{3}[(V_{REFP} - V_{DACP,1}) - (V_{IN} - V_{DACP,0})]$$

$$+ \sum_{i=0}^{2} C_{i}[(V_{REFP} - V_{DACN,1}) - (V_{IP} - V_{DACN,0})]$$

$$= 4C[(V_{REFP} - (V_{CM} - V_{IN} + V_{REF}/2)) - (V_{IN} - (V_{CM}))]$$

$$+ 4C[(V_{REFP} - (V_{CM} - V_{IP} + V_{REF}/2)) - (V_{IP} - (V_{CM}))]$$

$$= \underline{4CV_{REF}}.$$

(3.4)

The amount of switching energy for N-bit SAR ADC is  $2^{N-1}CV_{REF}^2$  and it is noted that there is no difference between the switching power consumptions for the SAR ADC with and without an explicit S/H circuit. This is due to the fact that although the initial charge is different, the voltage changes across the capacitors are the same for these two cases.

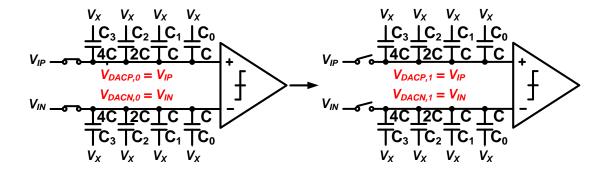

Figure 3.1: Conventional charge-redistribution sampling technique.

For the top-plate sampling technique (figure 3.2), the input voltages,  $V_{IP}$  and  $V_{IN}$  are sampled onto the top-plate of the capacitive-array DACs while the bottom-plate are reset to the reference voltage  $V_X$ . The total charge  $Q_1$  that supplies from the reference voltage  $V_X$  to the capacitive-array DACs is

$$Q_{1} = \Delta Q[DACp_{0} \rightarrow DACp_{1}] + \Delta Q[DACn_{0} \rightarrow DACn_{1}]$$

$$= \sum_{i=0}^{3} C_{i}[(V_{X} - V_{DACP,1}) - (V_{X} - V_{DACP,0})]$$

$$+ \sum_{i=0}^{3} C_{i}[(V_{X} - V_{DACN,1}) - (V_{X} - V_{DACN,0})]$$

$$= \underline{0}.$$

(3.5)

Figure 3.2: Top plate sampling technique.

Similarly, for the bottom-plate sampling technique (figure 3.3), the input voltages,  $V_{IP}$  and  $V_{IN}$  are sampled onto the bottom-plate of the capacitive-array DACs while the top-plate are reset to the reference voltage  $V_X$ . The total charge  $Q_1$  that supplies from the reference voltage  $V_X$  to the capacitive-array DACs is

$$Q_{1} = \Delta Q[DACp_{0} \rightarrow DACp_{1}] + \Delta Q[DACn_{0} \rightarrow DACn_{1}]$$

$$= \sum_{i=0}^{3} C_{i}[(V_{Y} - V_{DACP,1}) - (V_{IN} - V_{DACP,0})]$$

$$+ \sum_{i=0}^{3} C_{i}[(V_{Y} - V_{DACN,1}) - (V_{IP} - V_{DACN,0})]$$

$$= 4C[(V_{Y} - (V_{X} - V_{IN} + V_{Y})) - (V_{IN} - V_{X})]$$

$$= 4C[(V_{Y} - (V_{X} - V_{IP} + V_{Y})) - (V_{IP} - V_{X})]$$

$$= \underline{0}. \tag{3.6}$$

Figure 3.3: Bottom plate sampling technique.

The top-plate and bottom-plate sampling techniques do not drawn any energy from the reference voltages. The merits and flaws for implementing each technique have been discussed in Chapter 2.1.1.

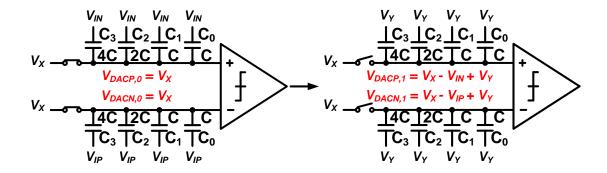

#### 3.2.2 Bit-cycling phase

At every period in the bit-cycling phase, the capacitive-array DAC goes through either "up" or "down" transition occurs. An "up" transition occurs when only a capacitor is required to be switched from one reference voltage to another. As shown in figure 3.4, the second largest capacitor, 2C is switched from  $V_{REFN}$  to  $V_{REFP}$ . A "down" transition occurs when the larger capacitor is switched to a lower voltage reference and the smaller capacitor is switched to a higher voltage reference. As shown in figure 3.5, the capacitor, 4C is switched down from  $V_{REFP}$  to  $V_{REFN}$  while the capacitor, 2C is switched up from  $V_{REFN}$  to  $V_{REFP}$  simultaneously. Intuitively, the switching energy for these two transitions are different.

In the "up" transition (figure 3.4), the total charge  $Q_{2,UP}$  that supplies from the reference voltage  $V_{VREFP}$  to the capacitive-array DACs is

$$Q_{2,UP} = \triangle Q[DACp_1 \to DACp_2] + \triangle Q[DACn_0 \to DACn_1]$$

$$= C_3[(V_{VREFP} - V_{DACP,2}) - (V_{VREFP} - V_{DACP,1})]$$

$$+ C_2[(V_{VREFP} - V_{DACP,2}) - (V_{VREFN} - V_{DACP,1})]$$

$$+ \sum_{i=0}^{1} C_i[(V_{VREFP} - V_{DACN,2}) - (V_{VREFP} - V_{DACN,1})]$$

$$= 4C[(V_{VREFP} - 5V_{VREF}/4 + V_{VIN}) - (V_{VREFP} - V_{VREF} + V_{VIN})]$$

$$+ 2C[(V_{VREFP} - 5V_{VREF}/4 + V_{VIN}) - (V_{VREFN} - V_{VREF} + V_{VIN})]$$

$$+ 2C[(V_{VREFP} - 3V_{VREF}/4 + V_{VIP}) - (V_{VREFP} - V_{VREF} + V_{VIP})]$$

$$= \underline{CV_{REF}}.$$

(3.7)

In the "down" transition (figure 3.5), the total charge  $Q_{2,DOWN}$  that supplies from the reference voltage  $V_{VREFP}$  to the capacitive-array DACs is

$$Q_{2,DOWN} = \Delta Q[DACp_1 \to DACp_2] + \Delta Q[DACn_0 \to DACn_1]$$

$$+ C_2[(V_{VREFP} - V_{DACP,2}) - (V_{VREFN} - V_{DACP,1})]$$

$$+ C_3[(V_{VREFP} - V_{DACN,2}) - (V_{VREFN} - V_{DACN,1})]$$

$$+ \sum_{i=0}^{1} C_i[(V_{VREFP} - V_{DACN,2}) - (V_{VREFP} - V_{DACN,1})]$$

$$= 2C[(V_{VREFP} - 3V_{VREF}/4 + V_{VIN}) - (V_{VREFN} - V_{VREF} + V_{VIN})]$$

$$+ 4C[(V_{VREFP} - 5V_{VREF}/4 + V_{VIP}) - (V_{VREFN} - V_{VREF} + V_{VIP})]$$

$$+ 2C[(V_{VREFP} - 5V_{VREF}/4 + V_{VIP}) - (V_{VREFP} - V_{VREF} + V_{VIP})]$$

$$= 5CV_{REF}.$$

(3.8)

The switching energy for the "down" transition is five times more than the switching energy for the "up" transition.

Figure 3.4: An example of an "up" transition in the capacitive-array DAC.

Figure 3.5: An example of a "down" transition in the capacitive-array DAC.

### 3.3 Examples of switching methods

#### 3.3.1 Charge-redistribution switching method for the CBW DAC

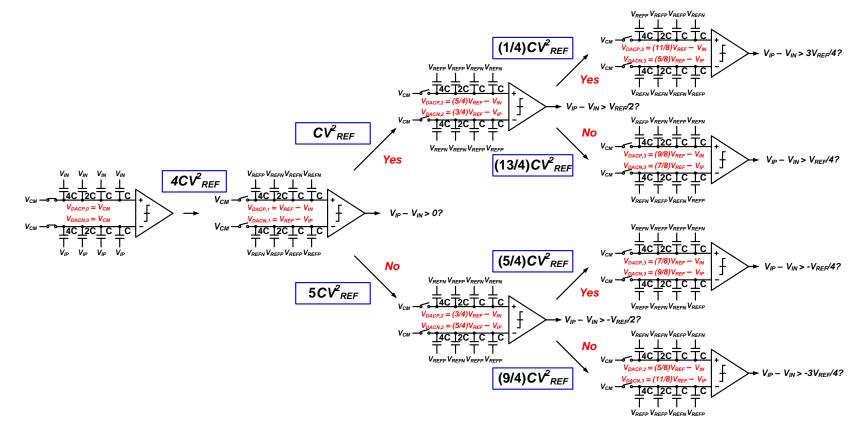

From the earlier analyses in Section 3.2, the binary search procedure is simple and intuitive. However, it is not an energy efficient switching scheme, especially when the unsuccessful trials occur. An example of a 3-bit SAR ADC with the charge-redistribution switching method is shown in figure 3.7. The quantitative energy consumption of each switching phase is also shown in the figure 3.7.

The average switching energy for an *N*-bit SAR ADC using the switching method can be derived as:

$$E_{ave} = \sum_{i=1}^{N} (2^{N+1-2i})(2^{i} - 1)CV_{REF}^{2},$$

(3.9)

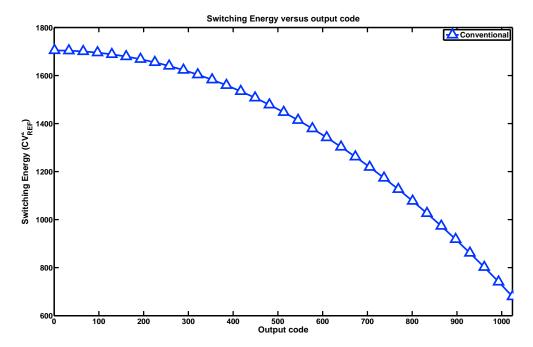

For a 10-bit ADC, this switching method consumes  $1363.33-CV_{REF}^2$ . As shown in figure 3.6, the efficient switching occurs when all the attempts are successful.

Figure 3.6: Switching energy versus output code

Figure 3.7: A 3-bit SAR ADC with the conventional switching method.

#### 3.3.2 Charge-redistribution switching method for the BWA DAC

As discussed in Chapter 2.3.2, the BWA DAC architecture reduces the total number of the capacitors by a factor up to  $2^{N/2+1}$ . In order to calculate the overall power consumption of this architecture due to capacitor switching, the total charge that supplies to the capacitive-array DAC during the *K*-bit MSB and (*N*-*K*)-bit LSB conversions can be calculated separately and then substituted back in equation (3.1).

The total charge consumption during the first *K*-bit is the same as a *K*-bit binary-weighted capacitive DAC.

$$\sum_{i=1}^{K} Q_i = 2^K C_o V_{REF} \times \left\{ \frac{5}{6} - \left(\frac{1}{2}\right)^K - \frac{1}{3} \left(\frac{1}{4}\right)^K - \frac{1}{2} \left(\sum_{i=1}^{K-1} \frac{D_i}{2^i}\right)^2 - \left(\frac{1}{2}\right)^K \sum_{i=1}^{K-1} \frac{D_i}{2^i} \right\},$$

(3.10)

where  $D_1, D_2, \ldots, D_K$  are the binary outputs of the ADC.

To calculate the total charge consumption during the next N-K clock cycles, one must consider that each of the K-bit MSB capacitors is connected to either  $V_{REFP}$  or  $V_{REFN}$  based on the value of  $D_1, D_2, \ldots, D_K$  digital bits already determined during the previous clock cycles. The charge consumption in the following clock cycle is obtained from

$$Q_{i} = C_{i}V_{REF} + \left(C_{i} + \sum_{j=K+1}^{i-1} C_{j}D_{j}\right)(V_{M_{i-1}} - V_{M_{i}})$$

$$+ \left(\sum_{j=1}^{K} C_{j}D_{j}\right)(V_{DAC_{i-1}} - V_{DAC_{i}}), \qquad K+1 \leq i,$$

(3.11)

where  $V_{M_i}$  and  $V_{DAC_i}$  (node voltages annotated in figure 2.7) are given by

$$V_{M_{i}} = V_{REF} \times \left\{ \frac{C_{i} + \sum_{j=1}^{K} C_{j} D_{j}}{C_{MSB,total} + C_{M} || C_{LSB,total}} \times \frac{C_{M}}{C_{M} + C_{MSB,total}} + \frac{C_{i} + \sum_{j=K+1}^{i-1} C_{j} D_{j}}{C_{LSB,total} + C_{M} || C_{MSB,total}} \right\}$$

(3.12)

and

$$V_{DAC_{i}} = V_{REF} \times \left\{ \frac{\sum_{j=1}^{K} C_{j} D_{j}}{C_{MSB,total} + C_{M} || C_{LSB,total}} + \frac{C_{i} + \sum_{j=K+1}^{i-1} C_{j} D_{j}}{C_{LSB,total} + C_{M} || C_{MSB,total}} \times \frac{C_{M}}{C_{M} + C_{MSB,total}} \right\},$$

(3.13)

substituting equations (3.12) and (3.13) in (3.11) and the total charge consumption can be obtained.

For a 10-bit ADC with MSB:LSB=5:5 segmentation, this switching method consumes only 87.29- $CV_{REF}^2$ , achieving a 93.6% energy reduction.

#### 3.3.3 Step-and-down switching method for the CBW DAC

An example of top-plate sampling technique is demonstrated in the step-and-down switching method. It was first reported for a 10-bit SAR ADC with a differential CBW DAC [70]. A detailed switching method is described as follow:

- 1. <u>Sampling Phase</u>: The differential input signals,  $V_{IP}$  and  $V_{IN}$ , are sampled through the top plate of the CBW DAC while the bottom plates of the capacitors are reset to  $V_{REFP}$ .

- 2. <u>Bit-cycling Phase</u>: The S/H sampling switches are turned off and the comparator directly performs the first comparison without switching any capacitor.

- 3. According to the comparator's output, the largest capacitor on the higher voltage potential side is switched to  $V_{REFN}$  and the other side remains unchanged.

- 4. Step 2 3 are repeated for the next N 1 cycles until the output of the DAC converges towards  $V_{REFN}$ .

From the discussions in Section 3.2.1, during the sampling phase, the DAC does not draw any energy from the  $V_{REFP}$ . During each bit cycle, there is only one capacitor switched, which reduces both charge transfer in the DAC and the transitions of the control circuit and switch buffer, resulting in smaller power dissipation. This method uses one of the least number of switches and unit capacitors and it does not require upward transition. However, the common-mode voltage from the DAC gradually decreases from  $V_{CM}$  to  $V_{REFN}$ . Since the common-mode voltage is not fixed at any particular voltage, therefore the performance of the SAR ADC is limited by the comparator's signal-dependent dynamic offset. Furthermore, the harmonic distortions tend to be more severe through the use of top-plate sampling technique.

An example of a 3-bit SAR ADC with the step-and-down switching method is shown in figure 3.8. The average switching energy for an *N*-bit SAR ADC using the switching method can be derived as:

$$E_{ave} = \sum_{i=1}^{N-1} (2^{N-2-i})CV_{REF}^2.$$

(3.14)

For a 10-bit ADC, this switching method consumes only 255.5- $CV_{REF}^2$ , achieving a 81% energy reduction.

Figure 3.8: A 3-bit capacitive array with set-and-down switching method.

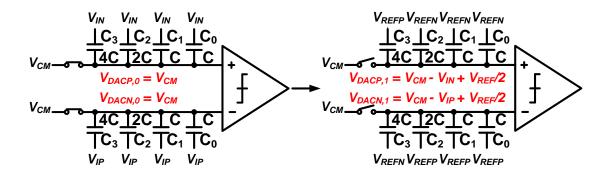

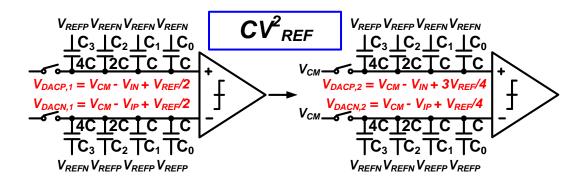

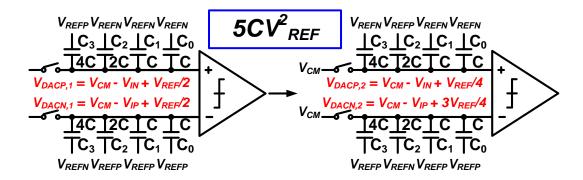

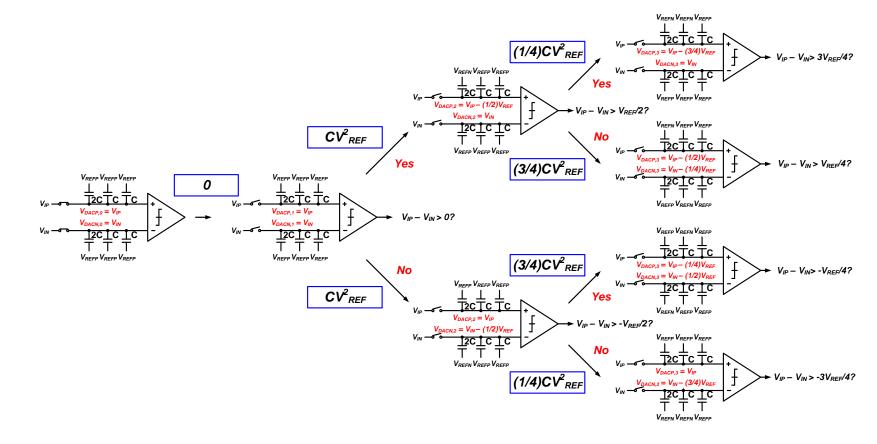

#### 3.3.4 $V_{CM}$ -based switching method for the CBW DAC

An example of top-plate sampling technique is demonstrated in the  $V_{CM}$ -based switching method. It operates in a similar way as the set-and-down switching method [23]. A detailed swithing method is described as follow: