# TEMPERATURE SENSORS IN SOI CMOS FOR HIGH TEMPERATURE APPLICATIONS

JERRIN PATHROSE VAREED (B. Tech., M.Sc)

**A THESIS SUBMITTED**

FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING

NATIONAL UNIVERSITY OF SINGAPORE

2014

## **DECLARATION**

I hereby declare that this thesis is my original work and it has been written by me in its entirety. I have duly acknowledged all the sources of information which have been used in the thesis.

This thesis has also not been submitted for any degree in any university previously.

Aerow

Jerrin Pathrose Vareed 4 December 2014

## **ACKNOWLEDGEMENT**

First of all I would like to express sincere gratitude to my advisor, Associate Professor Xu Yong Ping for his valuable support and guidance throughout my PhD journey. His consistent encouragement and excellent suggestions have greatly helped the success of this research as well as my growth as a researcher.

My sincere thanks goes to my supervisors at A\*STAR Institute of Microelectronics (IME), Dr. Je Minkyu and Dr. Kevin Chai for their inputs and providing me with all the facilities during my PhD attachment. My special thanks to Dr. Zou Lei at NUS and research staff at IME whose constant feedback helped me to improve my research. I am very grateful to Economic Development Board of Singapore (EDB) for providing me scholarship to pursue my dream of obtaining a PhD degree.

I would also like to thank the Laboratory staffs at Signal Processing and VLSI Lab at NUS and Integrated Circuits and Systems Lab at IME for their support with the design softwares, lab equipments, chip assembly etc. I thank all the friends and members of VLSI Lab at NUS for the wonderful discussions and help.

Last but not least, thanks goes to my parents, V.V Pathrose and Rosily Pathrose, wife Fiji, sister Jeny, brother Justin for their unconditional love, patience and support during last five years as well as throughout my education.

## TABLE OF CONTENTS

| ACKNOWLEDGEMENTI                             |

|----------------------------------------------|

| TABLE OF CONTENTSII                          |

| SUMMARY IV                                   |

| LIST OF TABLES VI                            |

| LIST OF FIGURES                              |

| LIST OF ABBREVIATIONSX                       |

| CHAPTER 1 INTRODUCTION1                      |

| 1.1 HIGH TEMPERATURE ELECTRONICS             |

| 1.2 TECHNOLOGIES FOR HT DESIGN               |

| 1.3 HT TEMPERATURE SENSOR                    |

| 1.3.1 TEMPERATURE SENSOR                     |

| 1.3.2 VOLTAGE REFERENCE                      |

| 1.4 RESEARCH SCOPE AND OBJECTIVES            |

| 1.5 Research Contributions                   |

| 1.6 PUBLICATIONS                             |

| 1.7 Organization of the thesis               |

| CHAPTER 2 LITERATURE REVIEW15                |

| 2.1 HT DESIGN TECHNIQUES                     |

| 2.1.1 LEAKAGE COMPENSATION                   |

| 2.1.2 BIASING                                |

| 2.2 SMART TEMPERATURE SENSOR                 |

| 2.1.3 VOLTAGE REFERENCE                      |

| 2.1.4 TEMPERATURE SENSOR                     |

| 2.2 SUMMARY                                  |

| CHAPTER 3 THRESHOLD VOLTAGE BASED SMART      |

| TEMPERATURE SENSOR FRONT-END                 |

| 3.1 THRESHOLD VOLTAGE TEMPERATURE DEPENDENCE |

| 3.2   | $V_{TH}Extraction$ and CTAT Voltage Generation                  | 47 |

|-------|-----------------------------------------------------------------|----|

| 3.3   | VOLTAGE REFERENCE                                               | 51 |

| 3.4   | EXPERIMENTAL RESULTS AND ANALYSIS                               | 54 |

| CHA   | APTER 4 TIME-DOMAIN SMART TEMPERATURE SENSOR                    | 63 |

| 4.1   | PROPOSED TECHNIQUE FOR RATIOMETRIC TEMPERATURE MEASUREMEN<br>63 | T  |

| 4.2   | TEMPERATURE SENSOR VERSION 1                                    | 66 |

| 4.2.1 | ARCHITECTURE AND OPERATION                                      | 66 |

| 4.2.2 | CIRCUIT DESIGN                                                  | 68 |

| 4.2.3 | MEASUREMENT RESULTS AND DISCUSSION                              | 73 |

| 4.3   | TEMPERATURE SENSOR VERSION 2                                    | 76 |

| 4.3.1 | CIRCUIT DESIGN                                                  | 76 |

| 4.3.2 | 2 DIGITAL PROCESSING AND CALIBRATION                            | 80 |

| 4.3.3 | EXPERIMENTAL RESULTS AND ANALYSIS                               | 82 |

| CHA   | APTER 5 CONCLUSION AND FUTURE WORK                              | 88 |

| 5.1   | Conclusion                                                      | 88 |

| 5.2   | FUTURE WORK                                                     | 89 |

| BIB   | LIOGRAPHY                                                       | 90 |

## **SUMMARY**

HT temperature sensors are critical circuit blocks in oil-well instrumentation, where temperatures of deep reservoirs go above 200°C. The temperature information is used to obtain the reservoir characteristics as well as temperature compensation of other circuits. This research proposes two temperature sensor designs based on threshold voltage and bandgap principle in SOI CMOS technology.

The first design is a temperature sensor front-end based on threshold voltage temperature dependency operating up to 250°C. The core of the design is threshold voltage extraction technique. The proposed threshold voltage extraction circuit eliminates the non-linear temperature dependent mobility and mobility ratio terms, thus achieving wide operating temperature range. The voltage reference proposed as part of this front-end achieves a mean box-model temperature coefficient of 27 ppm over a temperature range of -25 to 250°C, which is the lowest reported in the HT category. The temperature inaccuracy of the front-end is within  $\pm 1.8\%$  for the temperature range of 275°C. This design has one of the widest operating temperatures reported in literature.

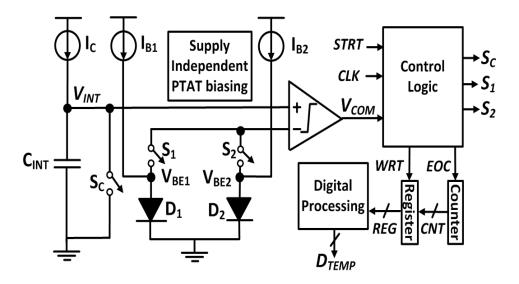

The second design is a time-domain bandgap based temperature sensor operating up to 225°C. The architecture does not have an explicit bandgap reference and only requires the ratio of two diode voltages to obtain ratiometric measurement. This is achieved through a mapping function at the digital back-end. The sensor is implemented with simple time-domain

iv

architecture, resulting in lower power consumption. The design achieves a worst-case inaccuracy of  $+1.6^{\circ}$ C/ $-1.5^{\circ}$ C and consumes only 20µA from a 4.5-V supply. A simple one-point calibration technique at room temperature is done in this work. The proposed architecture has the best FOM reported in the HT category. To the best of author's knowledge, this design is the first bandgap based temperature sensor operating above 200°C.

## LIST OF TABLES

| TABLE 1-1: TEMPERATURE RANGE OF ICS                  | 1  |

|------------------------------------------------------|----|

| TABLE 2-1: SUMMARY OF VOLTAGE REFERENCE PERFORMANCE  | 44 |

| TABLE 2-2: SUMMARY OF TEMPERATURE SENSOR PERFORMANCE | 44 |

| TABLE 3-1: STATISTICAL LINEARITY OF CTAT OUTPUTS     | 59 |

| TABLE 3-2: VOLTAGE REFERENCE PERFORMANCE COMPARISON  | 60 |

| TABLE 4-1: TEMPERATURE SENSOR PERFORMANCE COMPARISON | 85 |

## **LIST OF FIGURES**

| FIGURE 1.1: SIMPLIFIED DOWN-HOLE INSTRUMENTATION SYSTEM (TI)                                           |

|--------------------------------------------------------------------------------------------------------|

| FIGURE 1.2: SOI DEVICE CROSS SECTION AND LAYOUT                                                        |

| FIGURE 1.3: GLOBAL TEMPERATURE SENSOR MARKET (2011) [4]                                                |

| FIGURE 2.1: DIFFERENTIAL PAIR LEAKAGE COMPENSATION [22]16                                              |

| FIGURE 2.2: OUTPUT STAGE LEAKAGE [22]                                                                  |

| FIGURE 2.3: ZTC BIAS POINT [23]                                                                        |

| FIGURE 2.4: G <sub>M</sub> /I <sub>D</sub> curves of SOI NMOS transistor for various temperatures [24] |

| FIGURE 2.5: TYPICAL SMART TEMPERATURE SENSOR ARCHITECTURE                                              |

| FIGURE 2.6: RATIOMETRIC CONCEPT FOR TEMPERATURE MEASUREMENT                                            |

| FIGURE 2.7: (A), (B) TYPICAL BGR CIRCUITS, AND (C) CIRCUIT IN [27]24                                   |

| FIGURE 2.8: HIGH TEMPERATURE BGR USING LATERAL PNP [28]25                                              |

| FIGURE 2.9: THRESHOLD VOLTAGE BASED HT REFERENCE [33]27                                                |

| FIGURE 2.10: OPERATING PRINCIPLE AND BANDGAP VOLTAGES CHARACTERISTICS. 29                              |

| FIGURE 2.11: BLOCK DIAGRAM AND SIMPLIFIED CIRCUIT DIAGRAM [44]                                         |

| FIGURE 2.12: V <sub>BE</sub> PROCESS SPREAD                                                            |

| FIGURE 2.13: BASIC TEMPERATURE-TO-PULSE GENERATOR [10]                                                 |

| FIGURE 2.14: TIME-DOMAIN SAR SMART TEMPERATURE SENSOR [46]                                             |

| FIGURE 2.15: LINEARITY ENHANCEMENT TECHNIQUE [46]                                                      |

| FIGURE 2.16: ARDL DELAY CELL [46]                                                                      |

| FIGURE 2.17: BLOCK DIAGRAM AND BGR FREE DIGITIZATION TECHNIQUE [11] 36                                 |

| FIGURE 2.18: ETF SCHEMATIC AND CMOS LAYOUT [49]                                                        |

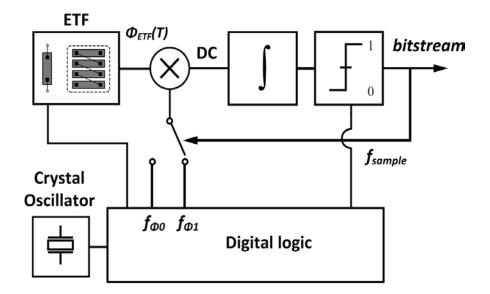

| FIGURE 2.19: PDΣΔM READ-OUT [49]40                                                                     |

| FIGURE 2.20: (A) <i>V<sub>D</sub></i> , (B) <i>V<sub>REF</sub></i> AND (C) ADC [54]                    |

| FIGURE 2.21: (A) ARCHITECTURE (B) V/F CONVERTER                                                        |

| FIGURE 3.1: (A) NMOS AND (B) PMOS THRESHOLD VOLTAGE EXTRACTION CELLS. 48                               |

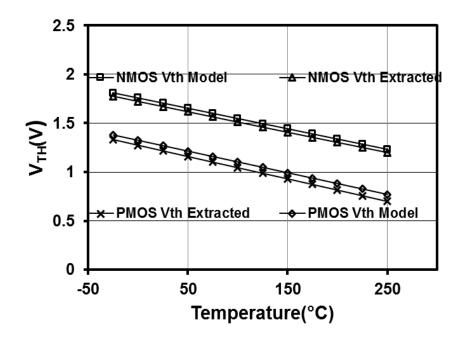

| FIGURE 3.2: SIMULATED THRESHOLD VOLTAGES (FROM $V_{\text{TH}}$ extraction cell and device model) versus temperature      |

|--------------------------------------------------------------------------------------------------------------------------|

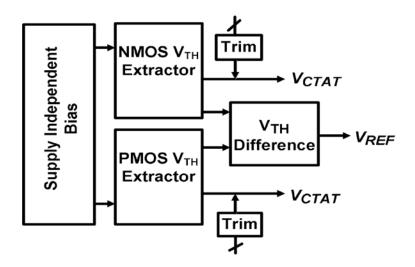

| Figure 3.3: Block diagram of the proposed $V_{\mbox{\tiny TH}}$ based voltage reference. 51                              |

| FIGURE 3.4: SCHEMATIC OF THE PROPOSED VOLTAGE REFERENCE                                                                  |

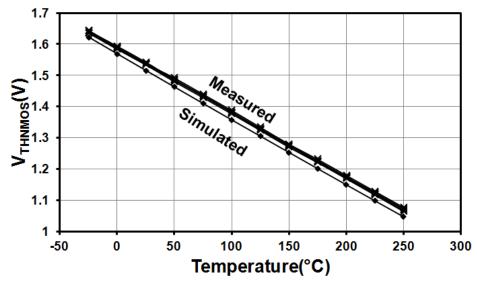

| FIGURE 3.5: Measured and simulated extracted NMOS $V_{\mbox{\tiny TH}}$                                                  |

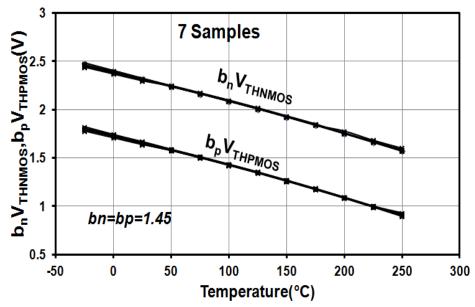

| FIGURE 3.6: MEASURED EXTRACTED NMOS AND PMOS $V_{\text{TH}}$ (scaled, trimmed) 55                                        |

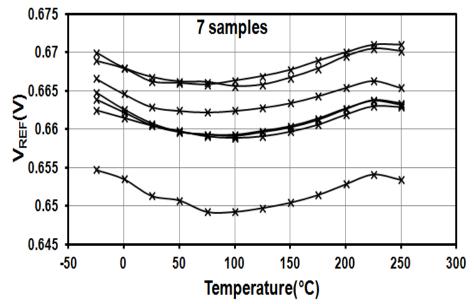

| FIGURE 3.7: MEASURED OUTPUT OF THE VOLTAGE REFERENCE                                                                     |

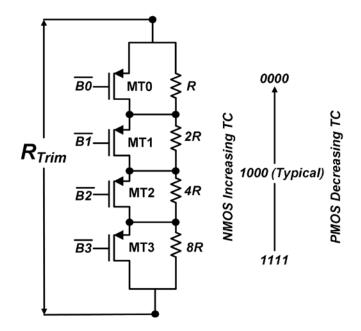

| FIGURE 3.8: BINARY-WEIGHTED TRIM RESISTOR                                                                                |

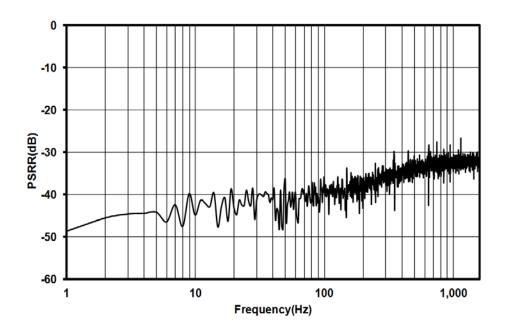

| FIGURE 3.9: MEASURED PSRR OF THE VOLTAGE REFERENCE                                                                       |

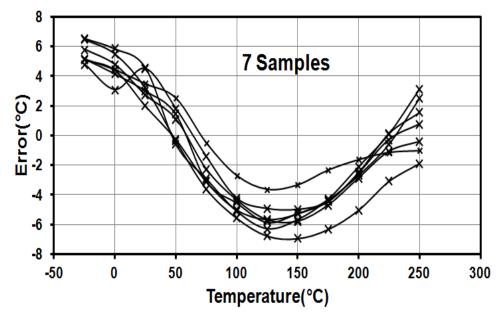

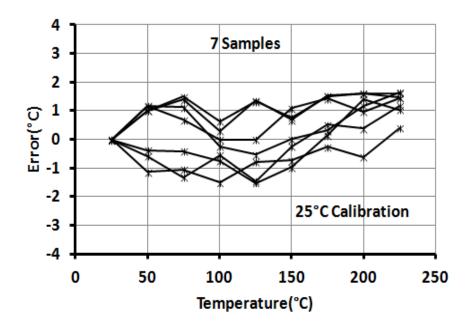

| FIGURE 3.10: MEASURED TEMPERATURE ERROR OF 7 SAMPLES FROM RATIOMETRIC OUTPUT                                             |

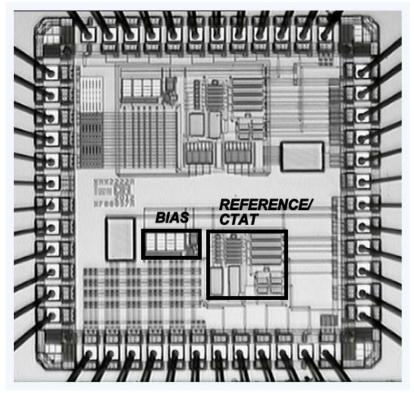

| FIGURE 3.11: CHIP MICROPHOTOGRAPH                                                                                        |

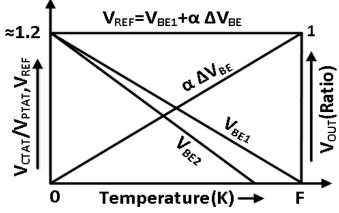

| FIGURE 4.1: BANDGAP CTAT/PTAT VOLTAGES AND REFERENCE                                                                     |

| FIGURE 4.2: SENSOR ARCHITECTURE VERSION 1                                                                                |

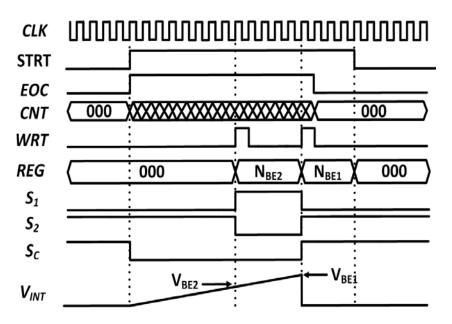

| FIGURE 4.3: TIMING DIAGRAM FOR VERSION 167                                                                               |

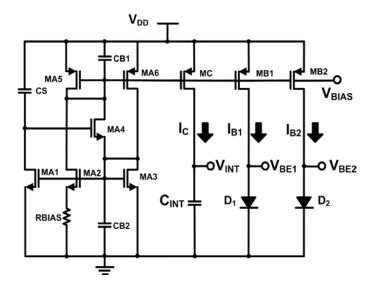

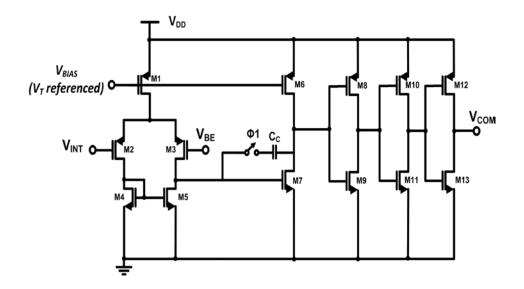

| FIGURE 4.4: BIAS CIRCUIT SCHEMATIC OF VERSION 1                                                                          |

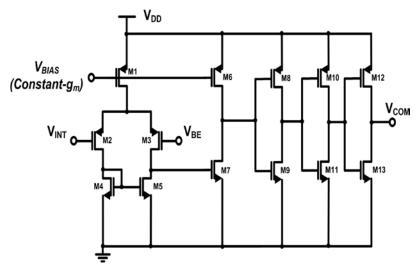

| FIGURE 4.5: COMPARATOR SCHEMATIC VERSION 1                                                                               |

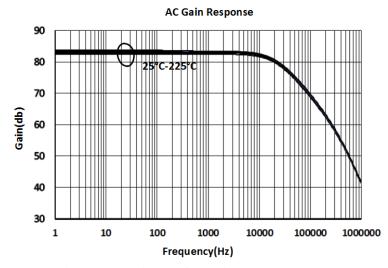

| FIGURE 4.6: GAIN PLOT FOR VARIOUS TEMPERATURES70                                                                         |

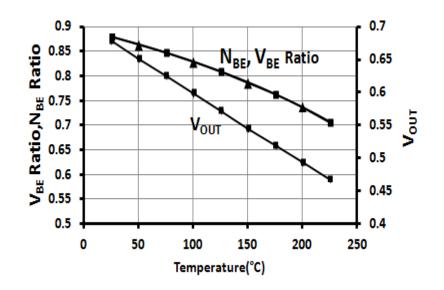

| FIGURE 4.7: SIMULATED VOLTAGE, COUNT RATIO COMPARISON AND MAPPED RATIOMETRIC OUTPUT $V_{\rm OUT}$ 71                     |

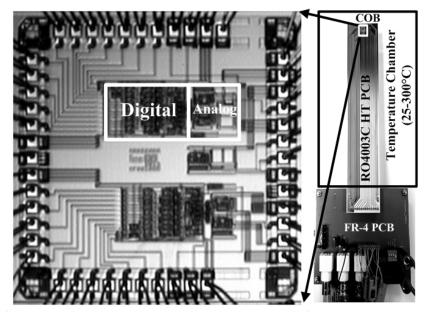

| FIGURE 4.8: MEASUREMENT SET-UP                                                                                           |

| FIGURE 4.9: CHIP MICROPHOTOGRAPH OF VERSION 1                                                                            |

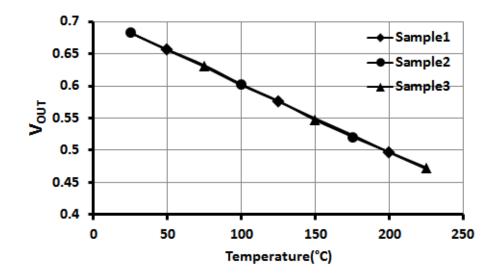

| FIGURE 4.10: MEASURED RATIOMETRIC OUTPUT FOR 3 SAMPLES                                                                   |

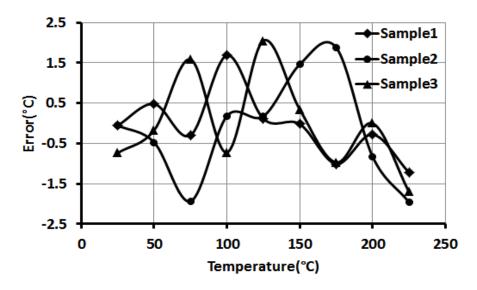

| FIGURE 4.11: MEASURED TEMPERATURE ERROR OF 3 SAMPLES75                                                                   |

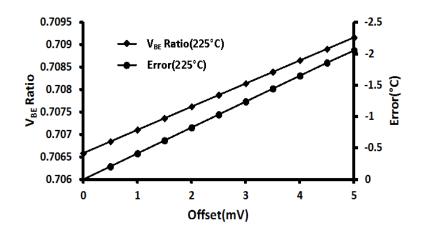

| FIGURE 4.12: SIMULATED $V_{BE}$ ratio and temperature error (at worst case temperature of 225°C) vs. comparator offset76 |

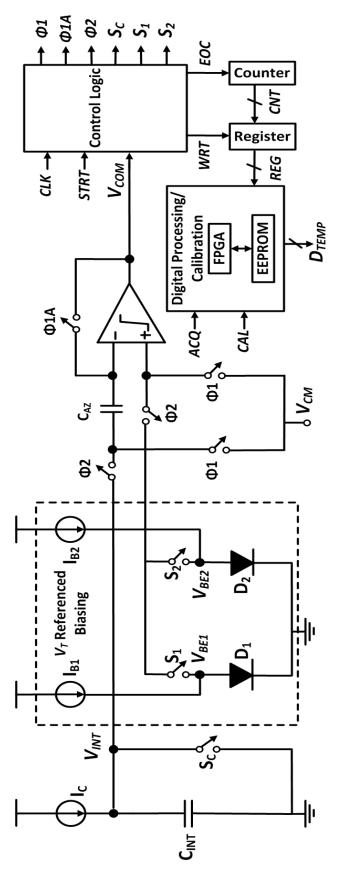

| FIGURE 4.13: SENSOR ARCHITECTURE VERSION 2                                                                               |

| FIGURE 4.14: TIMING DIAGRAM FOR VERSION 2                                                                                |

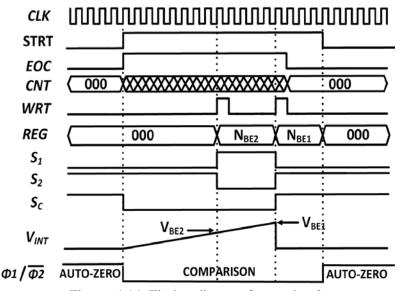

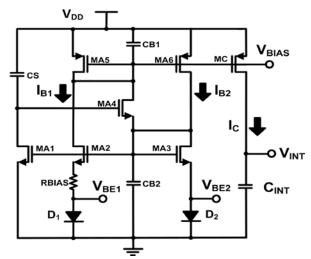

| FIGURE 4.15: BIAS CIRCUIT SCHEMATIC FOR VERSION 279                                                                      |

| FIGURE 4.16: OPEN-LOOP COMPARATOR SCHEMATIC                                                                              |

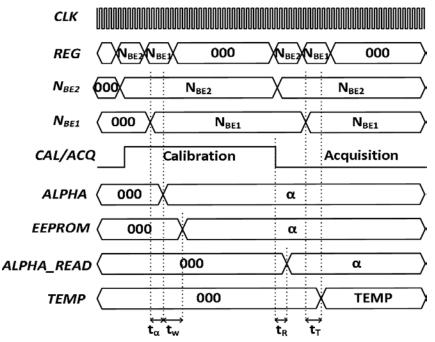

| FIGURE 4.17: CALIBRATION AND DIGITAL PROCESSING TIMING DIAGRAM | 31 |

|----------------------------------------------------------------|----|

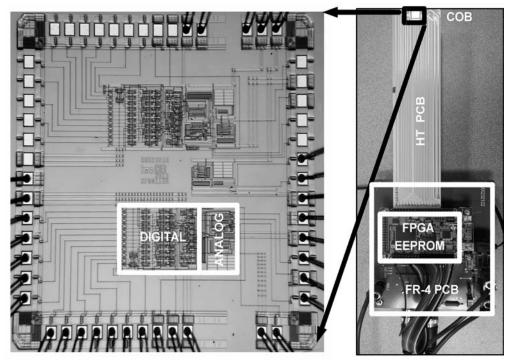

| FIGURE 4.18: DIE-PHOTO AND HIGH TEMPERATURE MEASUREMENT SET-UP | 32 |

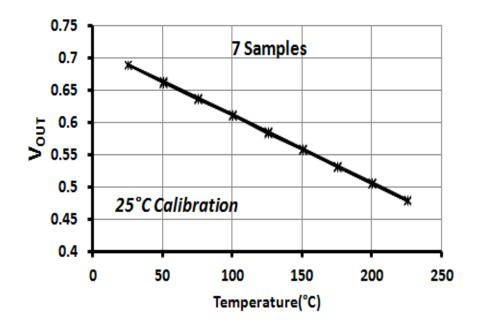

| FIGURE 4.19: MEASURED RATIOMETRIC OUTPUT OF 7 SAMPLES          | 33 |

| FIGURE 4.20: MEASURED TEMPERATURE ERROR OF 7 SAMPLES.          | 34 |

## LIST OF ABBREVIATIONS

| LWD    | LOGGING WHILE DRILLING                   |

|--------|------------------------------------------|

| SOI    | SILICON-ON-INSULATOR                     |

| BOX    | BURIED OXIDE LAYER                       |

| PDSOI  | PARTIALLY DEPLETED SOI                   |

| FDSOI  | FULLY DEPLETED SOI                       |

| ZTC    | ZERO TEMPERATURE COEFFICIENT             |

| ADC    | ANALOG-TO-DIGITAL CONVERTER              |

| DAC    | DIGITAL-TO-ANALOG CONVERTER              |

| BGR    | BANDGAP REFERENCE                        |

| TC     | TEMPERATURE COEFFICIENT                  |

| СТАТ   | COMPLEMENTARY TO ABSOLUTE TEMPERATURE    |

| PSRR   | POWER SUPPLY REJECTION RATIO             |

| RTD    | RESISTANCE TEMPERATURE DETECTOR          |

| DSP    | DIGITAL SIGNAL PROCESSOR                 |

| SAR    | SUCCESSIVE APPROXIMATION REGISTER        |

| СТАТ   | COMPLEMENTARY TO ABSOLUTE TEMPERATURE    |

| DEM    | DYNAMIC ELEMENT MATCHING                 |

| FOM    | FIGURE-OF-MERIT                          |

| FPGA   | FIELD PROGRAMMABLE GATE ARRAY            |

| EEPROM | ELECTRICALLY ERASABLE PROGRAMMABLE READ- |

| СОВ    | CHIP-ON-BOARD                            |

### <u>CHAPTER 1</u>

## **INTRODUCTION**

Integrated Circuits are classified into various categories based on their temperature range of operation as given in TABLE 1-1. Though there is no

| Category         | Lower | Upper  |

|------------------|-------|--------|

| Commercial       | 0°C   | 70°C   |

| Industrial       | -40°C | 85°C   |

| Extended         | -40°C | 125°C  |

| Military         | -55°C | 125°C  |

| High Temperature | -55°C | >125°C |

TABLE 1-1: TEMPERATURE RANGE OF ICS

standard upper limit for the high temperature category, in the context of this research it is referred to as the temperatures which ensure robust operations for the major high temperature applications such as oil and gas exploration, jet engine, military and automotive electronics. The conventional bulk CMOS does not operate reliably at high temperatures above 125°C. Therefore, technology, design and measurement method need to be reconsidered to meet the application requirements. In addition, deep understanding of temperature property of devices is also required to enable wide temperature range of operation. This thesis is dedicated to high temperature category of integrated circuits, temperature sensors in particular.

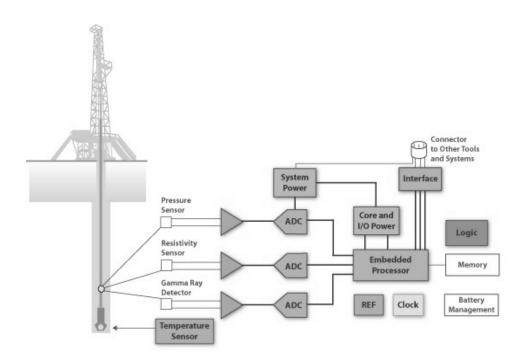

Figure 1.1: Simplified down-hole instrumentation system (TI).

#### **1.1 High Temperature Electronics**

High temperature electronics has various applications in automotive, aircraft, space, oil-well instrumentation etc. The integrated circuits developed in this research target applications for oil and gas exploration in deep sea, which operate in harsh environments such as extremely high temperatures and pressures. The temperature range that is required is 25°C to (200-300°C) depending on the depth of the well. Due to the declining oil and gas reserves, the industry is motivated to drill deeper and hence the temperatures could reach up to 300°C.

In oil and gas industry, information about the well is logged to understand the well characteristics. Electrical, acoustic, nuclear and electromagnetic measurements are carried out using the sensors in the tool string. Individual measurement or a combination of these is used to determine the petro-physical characteristics such as porosity, saturation, hydrocarbon content etc. which ultimately determine commercial feasibility of the well for exploration. The logging is done using wireline (after drilling) or Logging While Drilling (LWD) method. In LWD, the instrumentation is attached to the drill collar and the various parameters are logged during the drilling process. This allows the making of real-time decisions about the direction of drilling and prospects of the well. Figure 1.1 shows a simplified block diagram of a down-hole instrumentation system [1]. The instrumentation needs to withstand high temperature and pressure which increases with the depth of the well. The instrumentation also needs to be very compact. On-chip instrumentation can significantly reduce the size of the electronics and more sensors could be incorporated into the tool string. This has significant impact on the oil industry and has generated great interest in High Temperature IC's for oil-well instrumentation.

#### **1.2 Technologies for HT design**

Leakage current, latch-up susceptibility, electromigration etc. are the important factors which result in the failure of CMOS IC's at high temperatures. Though high temperature circuits have been demonstrated in bulk CMOS by design techniques [2], [3], it shifts the focus away from the core performance of the circuit designed and focus is more on ensuring HT operation. One of the key issues of HT operation is the leakage current, which is proportional to the junction area and increases with temperature, and it can be 4-5 orders of magnitude greater at 250°C than at 25°C. Hence, for robust operation, alternative process options need to be explored. The HT process

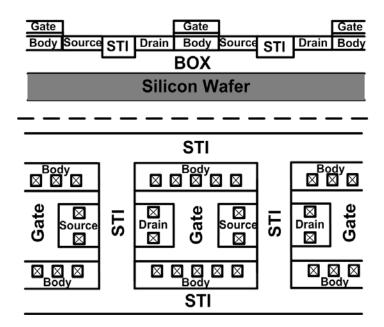

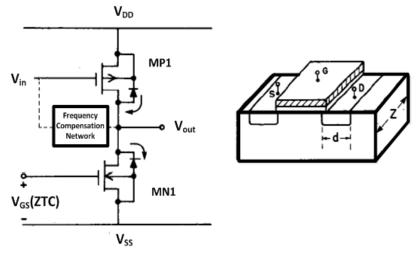

Figure 1.2: SOI device cross section and layout.

options available are wide bandgap materials such as Silicon Carbide (SiC), Gallium Arsenide (GaAs), diamond and SOI. Among them, SOI is a more popular technology, since it is well established and commercial SOI processes are available.

The advantage of SOI over bulk CMOS for high temperature ICs are as following. Firstly, the junction leakage is reduced because of the reduced PN junction area due to the Buried Oxide Layer (BOX). Secondly, latch-up is completely eliminated in SOI because the devices are fully dielectrically isolated, laterally by trench isolation and vertically by BOX isolation. Hence, the parasitic bipolar transistors that enable latch-up do not exist. Figure 1.2 shows the cross-section and layout of an SOI device and illustrates the lateral and vertical isolation of SOI transistors. In addition to the reduction of junction leakage current, sub-threshold leakage is reduced in HT SOI processes as a result of the increased threshold voltage. Transistors in SOI processs are classified as Partially Depleted SOI (PDSOI) and FDSOI (Fully Depleted SOI), depending on the thickness of the active silicon layer (at the surface above the BOX) relative to the depths of the source-drain junction and channel depletion layers in the device with the operating voltages applied. For a PDSOI transistor, the silicon surface layer is thicker than the depth of the depletion region in the channel, whereas for an FDSOI transistor, the silicon surface layer is equal to the depth of the depletion region in the channel. Thus, the bulk of the transistor will be partially depleted in PDSOI or fully depleted in FDSOI. To form a FDSOI transistor, the channel doping concentration must be low enough that the depletion region extends throughout the entire thickness of the silicon layer. When the silicon surface layer is thicker than about 200nm, the transistor will typically be partially depleted, unless the channel doping concentration is very low, in which case the resulting threshold voltage would be too low for practical CMOS applications.

Both FDSOI and PDSOI have pros and cons. The advantages of FDSOI over PDSOI are:

- The sub-threshold slope of FDSOI is steeper compared to PDSOI. It allows low threshold voltages of FDSOI transistors for acceptable sub-threshold leakages. It also has low parasitic capacitance. These features make it suitable for low-voltage and low- power applications.

- 2) The electrical effects due to floating body effects such as 'kink' effect(discontinuity in the  $I_{ds}$  vs  $V_{ds}$  curve) is lesser for FDSOI compared to PDSOI.

However, the disadvantages of FDSOI include:

- A body contact cannot be added to FDSOI, because a resistive body region does not exist under most operating conditions.

- 2) The device parameters such as threshold voltage of any CMOS device are sensitive to the silicon surface film thickness. This results in an additional source of process variance in the fabrication of FDSOI CMOS due to the smaller silicon thickness.

These are the reasons why, at present, the fabrication of commercial CMOS on SOI typically employs partially depleted (PD) devices and hence for this research PDSOI is adopted.

#### **1.3 HT Temperature Sensor**

The main focus of this research is temperature sensors operating at high temperatures above 200°C. HT temperature sensor is a critical component in any oil-well instrumentation system. To measure the temperature, a temperature independent reference voltage is needed. Hence, design of voltage reference is an integral part of digital temperature sensor design. The sections 1.3.1 and 1.3.2 below give a brief overview of temperature sensor and voltage reference.

#### 1.3.1 Temperature Sensor

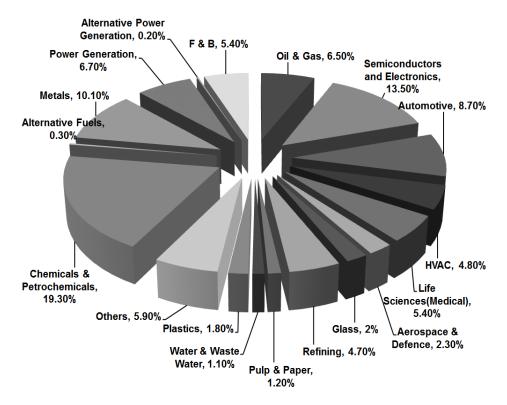

Temperature sensor is a ubiquitous part of any electronic appliance today and is widely used in instrumentation and control systems. Figure 1.3 shows the global temperature sensor market classified on the type of industry of application. The popular temperature sensing methods are using RTD (Resistance Temperature Detector), thermocouple, thermistor and semiconductor thermal properties. The choice of the sensing method depends

6

Figure 1.3: Global temperature sensor market (2011) [4].

on the temperature range of operation, linearity, accuracy, package, area occupied etc. The applications of temperature sensors can be broadly categorized into:

- 1) Temperature control, such as in thermostat.

- On-board or chip temperature measurement, such as in microprocessors, for system performance and reliability.

- 3) Temperature compensation for circuits and systems whose performance varies with temperature.

- Temperature information can also be used to sense some physical quantity which has a strong correlation to temperature.

Integrated sensors can be designed based on different sensing methods as given below.

- The most popular among them is the bandgap based temperature sensor which is based on the temperature dependency of base-emitter voltage of a BJT or forward voltage of a diode which has a complementary to absolute temperature (CTAT) characteristic. Majority of industry grade sensors belong to this category. The early smart temperature sensors are mostly in bipolar technologies [5], [6], [7]. Since 1990's, bandgap temperature sensors based on CMOS technology have been published, which makes use of parasitic BJTs available in the CMOS process. Some of the pioneer CMOS designs are by Krummenacher [8] (1990) and Bakker [9] (1996).

- 2) The other popular temperature sensing method that is compatible with latest CMOS processes is the time-domain temperature sensors which are fully digital in nature [10]. The sensing principle of these sensors is based on the temperature dependency of inverter delay chains.

- 3) Resistor based temperature sensors [11] are based on the temperature dependence of on-chip resistors for sensing.

- 4) Recently, thermal diffusivity based temperature sensors have been reported. The sensing principle of these sensors is based on the time taken for the heat to diffuse through the substrate, which is dependent on thermal diffusivity [12].

Some of the key performance parameters of temperature sensors are operating temperature range, accuracy (including number of calibration points), power consumption and chip area. The weightage of the performance parameters varies from application to application.

#### 1.3.2 Voltage Reference

For digitization of temperature, a temperature independent voltage reference is essential. In addition to the functionality as temperature independent reference for digital temperature sensor, voltage references also have applications in biasing circuits, ADC, DAC and power management circuits, etc.

Since most semiconductor physical parameters have temperature dependency, a temperature independent voltage is not readily available. Zeroorder references such as reverse biased zener diode voltages are available but not suitable for precision application such as temperature sensing. Hence, at least first-order compensated references are always preferred, i.e the temperature independent reference is constructed from the cancellation of TC's (Temperature Coefficient) of two voltages which has well defined and reproducible temperature properties.

The most popular voltage reference is the Bandgap Voltage Reference (BGR). The idea was first proposed by Hilbiber in 1964 [13]. Since then a variety of circuit topologies based on the principle have been published. Some of the classic designs are by Wildlar [14], [15], Kuijk [16] and Brokow [17]. The basic principle of operation for BGR is the TC cancellation of forward voltage of a diode or base emitter voltage ( $V_{BE}$ ) of a bipolar transistor with a  $\Delta V_{BE}$  voltage (difference of  $V_{BE}$ 's of two transistors). The former has a CTAT (Complementary to absolute temperature) characteristic and the latter has PTAT characteristic. MOS transistor based voltage references have also been reported as they are fully compatible with CMOS processes. Their operating principles are mostly based on circuit topologies, which cancel the

temperature dependency of mobility or threshold voltage of the MOS transistors. In [18], the inverse temperature dependency of mobility is used to cancel the threshold voltage temperature dependency of the MOS transistor and in [19] the difference of the threshold voltages of two transistors with similar temperature dependency but different absolute value is used, so that the difference of the two threshold voltages is temperature independent. Effectiveness of the temperature compensation over wide temperature range is evaluated by the box model TC metric [20]. A good TC is mandatory for application of voltage references for smart temperature sensor design. In addition to TC, the other performance metric is Power Supply Rejection Ratio (PSRR), since ideal voltage reference needs to be supply independent. Other parameters, such as power consumption, is also important.

#### **1.4 Research Scope and Objectives**

The main objective of this research is to design a smart temperature sensor and a voltage reference for ruggedized electronics system operating at temperatures above 200°C. The intended application is the data logging system for oil well drilling, where both temperature sensor and voltage reference are needed. The operating temperature can be as high as 250°C. The temperature sensor is used during the logging process where, temperature, together with other electrical measurements, is logged for understanding of the oil-well characteristics. It is also used for temperature compensation of other function blocks in the system. The voltage reference is used as a temperature independent reference for the temperature sensor and is also a critical part of other blocks in the system, such as power management blocks and bias circuits. Few existing temperature sensors can operate above  $200^{\circ}$ C and their performances are limited at high temperature. The research in this thesis aims to develop temperature sensors and voltage references with enhanced performance and wide operating temperature range above  $200^{\circ}$ C.

#### **1.5 Research Contributions**

The research in this thesis has made the following contributions:

The SOI technology is not a familiar technology for the mainstream circuit designers. Hence, device and technology study is done and differences from bulk CMOS are identified. Prototype circuits are fabricated and high temperature measurement methods were identified. This ground work enabled progress of this PhD research as well as for the HT electronics group.

A new temperature sensor front-end based on threshold voltage extraction principle is proposed and demonstrated. The voltage reference is also designed as part of the temperature sensor front-end and achieves the best TC reported in the HT category. In addition, this design has one of the widest temperature range reported in literature.

In the second part of this thesis, a new time-domain architecture for a bandgap based temperature sensor without an explicit bandgap reference is proposed. It is power and area efficient and achieves excellent performance in the high temperature category. This architecture is not limited to SOI and high temperature applications and can be easily ported to bulk CMOS for applications such as microprocessor thermal monitoring. To the best knowledge of the author, this design is the first bandgap based temperature sensor operating above 200°C and has the best FOM in this category of temperature sensors operating above 200°C.

#### **1.6 Publications**

The following publications are generated from the research in this thesis.

- [1] J. Pathrose, L. Zou, K. T. C. Chai, M. Je, and Y. P. Xu, "Temperature Sensor Front End in SOI CMOS Operating up to 250°C," *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 61, pp. 496-500, 2014.

- [2] J. Pathrose, C. Liu, K.T.C Chai and Y.P Xu, "A Time-Domain Bandgap Temperature Sensor for High Temperature Applications," (Accepted for publication in *IEEE Transactions on Circuits and Systems II: Express Briefs*).

- [3] J. Pathrose, L. Zou, K. T. C. Chai, M. Je, and Y. P. Xu, "A time-domain smart temperature sensor without an explicit bandgap reference in SOI CMOS operating up to 225°C," in 2013 IEEE Asian Solid-State Circuits Conference (A-SSCC), 2013, pp. 173-176.

- [4] J. Pathrose, X. Gong, L. Zou, J. Koh, K. T. C. Chai, M. Je, and Y. P. Xu, "High temperature bandgap reference in PDSOI CMOS with operating temperature up to 300°C," in 2012 IEEE International Symposium on Radio-Frequency Integration Technology (RFIT), 2012, pp. 110-112.

- [5] L. Zou, <u>J. Pathrose</u>, K. T. C. Chai, M. Je, and Y. P. Xu, "Sample-and hold circuit with dynamic switch leakage compensation," *Electronics Letters*, vol. 49, pp. 1323-1325, 2013.

A provisional patent also has been filed for the project which is given below.

[1] Jerrin Pathrose, Yong Ping Xu, Minkyu Je, Lei Zou, Kevin TC Chai, Jeongwook Koh, "Vth Extraction Circuit in SOI CMOS for Temperature Sensor and Voltage Reference," *SG provisional patent*, filed on 31 Jan. 2013 (SG 201300779-4).

#### **1.7 Organization of the thesis**

The thesis is organised as follows:

Chapter 2 is the literature review and divided into two parts. First part discusses the techniques for HT and wide temperature design with emphasis on biasing and leakage compensation. The second part presents the existing works on various smart temperature sensor designs. This part is further divided into sensing mechanisms and voltage reference which is part of the sensor front-end. Various categories of sensing mechanisms in literature are studied and the trade-offs are identified for each category.

Chapter 3 presents the proposed threshold voltage based temperature sensor front-end. It describes the threshold voltage temperature dependency, the proposed extraction circuit, the voltage reference design and the simulation results. The experimental results on silicon and discussion, as well as the comparison with other state-of-the-art works and the limitations of the design are presented in the end.

Chapter 4 describes the proposed time-domain smart temperature sensor design based on bandgap sensing principle. Two versions of the design are presented. The architecture, simulation and measurement results of both versions are given. The discussion and comparison with other state-of-the-art works are also presented.

Chapter 5 summarizes the findings of this thesis. The future works are also suggested at the end of the Chapter.

## <u>CHAPTER 2</u>

### LITERATURE REVIEW

Integrated temperature sensors have become popular during last 30-40 years. Several sensing methods, architectures and design techniques have been established during this period. This Chapter reviews the existing designs and discusses the advantages and disadvantages of each. As the research focus in this thesis is on temperature sensors for high temperature applications, the existing HT design techniques are first reviewed. Finally, the works reviewed in this chapter are summarized.

#### 2.1 HT design techniques

The initial HT designs are mostly in bulk CMOS and use circuit techniques to mitigate leakage issues. In addition to leakage compensation, various temperature compensation techniques have also been proposed for wide temperature range design. These techniques will be reviewed in the following sub-sections below.

#### 2.1.1 Leakage Compensation

Leakage current is the most important factor which prevents bulk CMOS circuits from robust operation at high temperatures. Designs using mainstream bulk CMOS have been demonstrated to operate up to 250°C. They apply leakage compensation techniques to extend the temperature range. However, these techniques introduce additional design constraints which limit the sensor performance. The major source of leakage current is the drain (source) reverse

Figure 2.1: Differential pair leakage compensation [22].

biased diode junction leakage current. This leakage is dominated by generation-recombination leakage up to 130-150°C and diffusion leakage for temperatures above that. Reference [21] models the leakage current in conventional CMOS processes and its effect on the characteristics of typical analog sub-circuits.

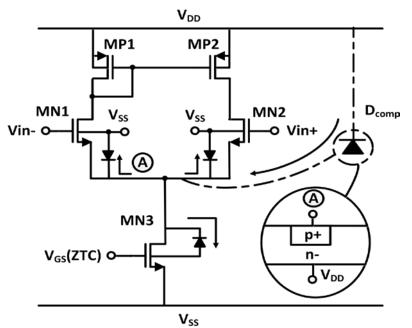

The leakage compensation applied to the differential input stage and output stage of an op-amp is given in [22]. The technique is to match the leakage current at each critical node so that the operating point is maintained over the temperature range of interest. For example, the node *A* in Figure 2.1, has an imbalance in the leakage currents (all leakage currents flowing out of the node) and hence it results in a drift in the bias conditions with temperature. Therefore, a compensation diode  $D_{comp}$  is added to match the leakage current at this node. The junction area of the diode should be such that it can balance the leakage currents of MN1, MN2 and MN3. For the output stage shown in Figure 2.2, the leakage current matches as far as the direction of current flow

Figure 2.2: Output stage leakage [22].

is concerned. However, for magnitude cancellation, the area of the reversed biased diodes should also match. The condition for complete cancellation is

$$W_P(MP1) \cdot d_P(MP1) = W_N(MN1) \cdot d_n(MN1) \tag{1}$$

where  $d_p$ ,  $d_n$ ,  $W_p$  and  $W_n$  are the diffusion length of NMOS, diffusion length of PMOS, width of NMOS, width of PMOS transistor respectively. However, the sizing is determined by the various performance metrics such as driving strength, slew rate, bandwidth etc. which are crucial for operation in the normal temperatures. One option is to use compensation diode with appropriate sizing like in Figure 2.1, but this is at the expense of additional capacitance. Thus, there is a trade-off between temperature range and the performance. This is a serious constraint in realizing the full potential of the circuit and hence alternate technology options need to be considered. SOI technology is very promising in this regard and has given more flexibility to the designer to optimize the performance. Therefore, in this research SOI technology is adopted.

#### 2.1.2 Biasing

For HT and wide temperature range operation, the biasing techniques should be robust and stabilize the performance of the circuit. Two biasing techniques have been commonly adopted. They are Zero Temperature Coefficient (ZTC) biasing and  $g_m/I_d$  method.

#### 2.1.2.1 ZTC

ZTC biasing point corresponds to a gate voltage/drain current operating point which remains constant with temperature. ZTC biasing [22] is one of the important techniques in high temperature design especially for OTA. The principal advantages of ZTC technique are [23]:

- 1) It maintains a constant operating point over a wide range of temperatures such that no transistors operate out of saturation.

- 2) It allows for a similar relative decrease in transconductance of the transistor such that the poles and zeros keep the same relative position, thus ensuring stability of the circuit over a wide range of temperatures.

- Design simplicity and ensures reliable circuit operation when several stages are used.

ZTC technique, as shown in Figure 2.3, has been very effective in maintaining stable operating point and hence reliable circuit operation as proven in [23]. It provides a bias point that is temperature independent. However, it results in performance degradation of the amplifier over wide temperature ranges.

The main disadvantages of ZTC are:

Figure 2.3: ZTC bias point [23].

- 1) The ZTC bias point corresponds to strong inversion region for bulk as well as PDSOI, unlike in FDSOI [23] where ZTC bias point is in the moderate inversion region. The high overdrive voltage associated with ZTC bias for PDSOI as well as bulk CMOS results in reduced intrinsic gain due to the low  $g_m$  as well as reduced signal swing.

- 2) The  $g_m$  decrease with temperature can affect the small signal performances of the amplifier like gain, bandwidth etc., especially when the amplifier is required to operate over a wide range of temperatures.

#### 2.1.2.2 gm/Id

$g_m/I_d$  is a design technique that allows a unified design methodology in all regions of operation of the MOS transistor [24]. In this method, the relationship between the ratio of the transconductance  $g_m$  over dc drain current  $I_D$  and the normalized drain current  $I_N = I_D / (W/L)$  is used as a fundamental design metric. The choice of  $g_m/I_D$  is for the following three reasons [24]:

19

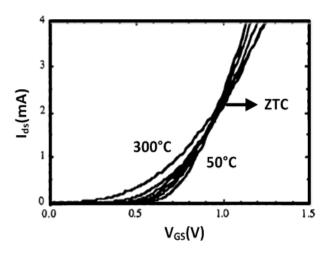

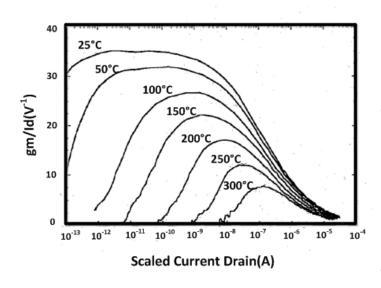

Figure 2.4: g<sub>m</sub>/I<sub>D</sub> curves of SOI NMOS transistor for various temperatures [24].

1) Many performance metrics of analog circuits can be expressed in terms of  $g_m/I_D$ . For example, the dc gain  $A_V$  of a common source amplifier can be expressed in the form

$$A_V = -\frac{g_m}{I_D} V_A \tag{2}$$

where  $V_A$  is the Early Voltage which controls the small signal output conductance.

- 2)  $g_m/I_D$  gives an indication of the device operating region. It has a maximum value of  $1/(nV_T)$  where *n* is the sub-threshold slope factor and  $V_T$  is the thermal voltage. The value decreases as the operating point moves towards strong inversion.

- 3)  $g_m/I_D$  can be used for calculating the transistor dimensions based on the desired performances.

Figure 2.4 shows the  $g_m/I_D$  vs.  $(I_D/(W/L))$  plot for different temperatures. The maximum plateau value on the left and hyperbolic behaviour on the right side of the figure corresponds to weak and strong inversion, respectively. In

Figure 2.5: Typical smart temperature sensor architecture.

between comes the moderate inversion. By applying the  $g_m/I_D$  design methodology, the plot can be used for design at specified temperatures. From the plot it can be observed that, for stabilization of  $g_m/I_D$  over wide range of temperatures, the transistor has to be operated in the strong inversion region. At lower  $I_D$ , the leakage current dominates at higher temperatures and  $g_m/I_D$ tends to zero as can be seen from Figure 2.4. The low value of  $g_m/I_D$  is because leakage current superimposes on the sub-threshold channel current at higher temperatures. In strong inversion the  $g_m/I_D$  degradation with temperature is due to the decrease in mobility.

#### 2.2 Smart Temperature Sensor

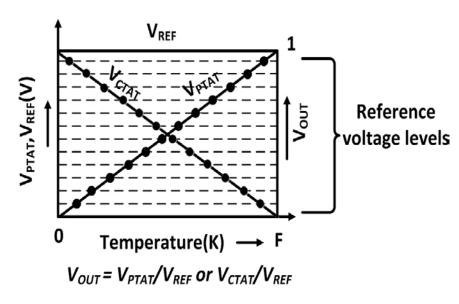

The typical architecture of a smart temperature sensor is shown in Figure 2.5. It consists of an analog temperature sensor front-end (CTAT or PTAT signal and voltage reference) [25], [26] and an ADC for digitization. The temperature signal is compared with various temperature independent reference voltage levels to digitize the temperature. This is equivalent to taking ratio of the temperature signal to the reference voltage, which is the

Figure 2.6: Ratiometric concept for temperature measurement.

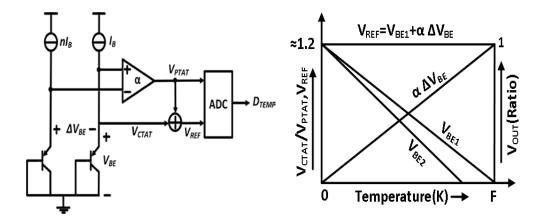

concept of ratiometric measurement [7]-[9]. Figure 2.6 illustrates the ratiometric sensing technique for a general temperature sensor for either PTAT voltage  $V_{PTAT}$  or CTAT voltage  $V_{CTAT}$  and reference voltage  $V_{REF}$ . Here,  $V_{OUT}$  is the ratiometric output and the dotted lines are the various ratiometric outputs or the reference voltage levels corresponding to different temperatures. *F* is the full scale temperature. From the ratiometric output  $V_{OUT}$ , the temperature in Kelvin is obtained by simple linear scaling, namely,  $F \times V_{OUT}$  for PTAT output and  $F \times (1-V_{OUT})$  for CTAT output.

#### 2.1.3 Voltage Reference

Voltage reference is a critical circuit for ratiometric measurement of temperature as illustrated in Figure 2.6. So far, bandgap reference is the most popular category of voltage references. In addition, references based on mobility and a threshold voltage has also been proposed.

The basic principle of a BGR is to cancel the temperature coefficient (TC) of the base-emitter voltage  $V_{BE}$  which has a negative TC or Complementary to

Absolute Temperature (CTAT) characteristic, with a PTAT voltage from the difference of two base-emitter ( $\Delta V_{BE}$ ) biased at different current densities, which has a positive TC.  $V_{BE}$  can be expressed using the following equation

$$V_{BE} \approx V_{go} - \frac{T}{T_r} [V_{go} - V_{BE}(Tr)] - (\eta - x) V_T \ln(\frac{T}{T_r})$$

(3)

where  $V_{go}$  is the base-emitter voltage at 0°K, equal to the bandgap voltage of silicon which is  $\approx 1.2$ V,  $V_{BE}(Tr)$  is the  $V_{BE}$  at reference temperature  $T_r$ ,  $\eta$  is a process dependent constant and x is the temperature dependent exponential of the bias current. As observed from the equation, there is a linear term as well as a non-linear logarithmic term which results in non-linearity. However, the non-linear term is much smaller compared to the linear temperature dependency and hence the first and most important target is to cancel the linear component using a PTAT voltage.

The PTAT voltage,  $\Delta V_{BE}$ , or CTAT voltage,  $V_{BE}$ , along with the reference forms the temperature sensor front-end. Several topologies have been proposed for BGR with high performance. Two BGR designs, one in the conventional temperature [27] and one in the high temperature category [28] are discussed here. One of the main error sources in any BGR design is the process variation of  $V_{BE}$ , the main reason for which is the process spread of saturation current  $I_s$  which is dependent on base doping and transistor area. Analysis in prior literature shows that a difference of  $\Delta I_s$ ,  $(I_s + \Delta I_s)$  due to process variation results in a  $V_{BE}$  variation of  $-V_T(\Delta I_s/I_s)$  which has a PTAT characteristic. Moreover, since  $V_{BE}$  at 0°K is a physical constant, namely, the bandgap voltage, the process variation of  $V_{BE}$  has just one degree of freedom and hence one-point calibration is enough to mitigate the process variation.

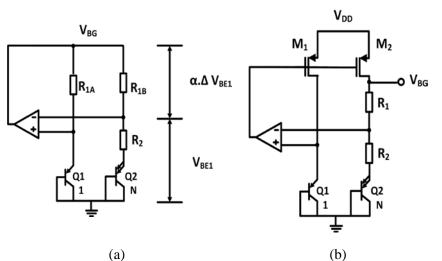

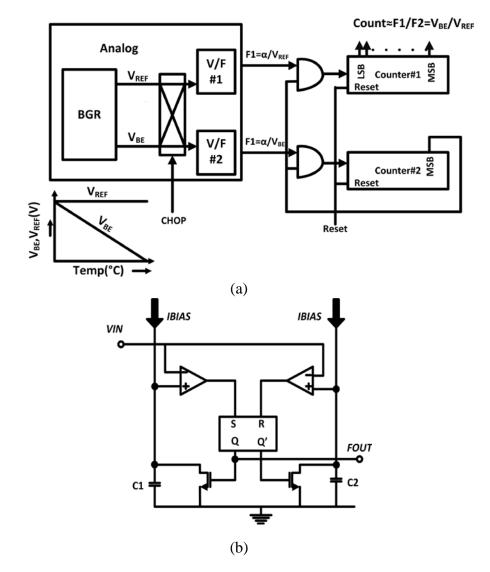

Figure 2.7: (a), (b) Typical BGR circuits, and (c) circuit in [27].

This is one of the significant advantages of BGR based reference, as well as temperature sensor.

Two of the typical designs for a bandgap reference are given in Figure 2.7 (a), (b). Design (b) eliminates the loading effect of the amplifier in (a) and thus avoids the buffer stage for the op-amp. The mismatch between the transistors M1 and M2 in (b) due to threshold voltage and aspect ratio mismatch results in a non-PTAT error. Hence a BGR with several improvements is reported in

Figure 2.8: High temperature BGR using lateral PNP [28].

[27], as shown in Fig. 2.7(c). Reference [27] identifies that the major sources of error are resistor and transistor mismatches,  $V_{BE}$  and  $\Delta V_{BE}$  process variation,  $V_{BE}$  non-linearity, op-amp offset and errors due to packaging stress and presents various techniques to remove the error sources in a BGR, as well as design considerations of a general BGR.

This design adopts a matched resistor topology and uses substrate PNP as the sensing element. As op-amp offset typically results in a non-PTAT error, the error cannot be cancelled by trimming and the error also has a statistical variation. Hence, chopper stabilization is applied for offset cancellation. Chopping technique is adopted due to the fact that it has a continuously available output, unlike auto-zero cancellation where output is available only during one phase. However, chopping typically needs large external capacitors to remove the high frequency ripple due to the up-modulated offset. In this work the ripple is removed by a switched-capacitor notch filter [29], [30] in the feedback loop as shown in Figure 2.7 (c).  $V_{BE}$  process variations as well as other PTAT errors due to mismatches are removed by trimming R3.  $R_T$  is part of the resistor  $R_3$  which can be trimmed.  $I_L$  models the leakage current of the switches used for trimming.  $R_3$  is selected as the trimmable resistor due to leakage current considerations. The error due to leakage current increases by  $I_L.R_3$ , if  $R_{1A}$  is trimmed instead of  $R_3$ . To reduce stress related errors, the dies are packaged with a stress-relieving coating between the die and the molding.

The high temperature bandgap reference in [28] is one of the few works operating above 200°C. It is implemented in FDSOI technology. The device used is lateral-pnp transistor derived from SOI transistor using body as base and the gate biasing is such that the transistor is in accumulation region. The use of lateral-pnp facilitates the adoption of the classical BGR topology [16] in Figure 2.8 unlike substrate-pnp where substrate is grounded always. Nevertheless, substrate PNP is still a superior device in terms of better BJT characteristics. The amplifier used is a single stage OTA and the biasing technique applied is ZTC biasing which is the popular technique for HT designs, which is explained in Section 2.1.2.1. This design achieves a TC of 100ppm and consumes 200µA from a 4.5-V supply.

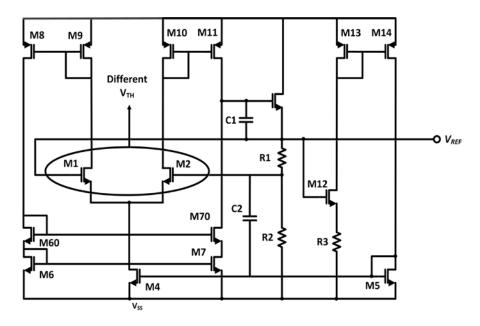

The non-BGR category of references is based on the temperature dependency of mobility and threshold voltages ( $V_{th}$ ) of MOS transistors. They have simpler circuit topologies and less error sources compared to BGR. References based on  $V_{th}$  difference of same type of devices (NMOS or PMOS) have been reported [31]–[33]. In these works, different  $V_{th}$  is generated with additional process steps, which is costly or may not be feasible in the available commercial processes.

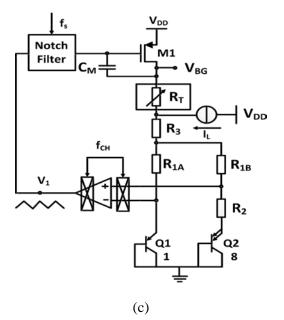

Figure 2.9: Threshold voltage based HT reference [33].

The high temperature work among these [33] achieves a TC of 50ppm for a temperature up to 200°C. The circuit topology of [33] is shown in Figure 2.9. This design uses a thin film (100nm) Separation by Implantation of Oxygen (SIMOX) technology which is similar to SOI technology and thus reduces leakage current at high temperatures. The design has an op-amp in feedback configuration. The differential pair transistors M1 and M2 are fabricated to have different threshold voltages by virtue of the different doping concentrations. Since M1 and M2 are biased by identical drain currents, the  $V_{GS}$  difference is same as the  $V_{TH}$  difference and hence the output is a temperature independent voltage which is proportional to the difference of threshold voltages.

Voltage references based on threshold voltage properties with transistors operating in sub-threshold region are useful in low power applications [34]– [36]. However, the leakage currents at high temperatures, as well as large mismatch and process variations, limit the robustness of such references. Voltage references based on  $V_{GS}$  difference [37] and threshold voltage difference of NMOS and PMOS transistors [38] have good TC, but have limited temperature range up to 130°C. The mobility ratio term for the reference voltage in [37] limits the operating temperature range since complete compensation is achievable only at a desired reference temperature, and therefore its application for temperature sensing is limited to temperature threshold detection [39], [40] at the reference temperature.

SiC technology based designs are gaining popularity for HT designs, though it is costly. An HT design has been published recently [41], which is based on the temperature dependencies of mobility of SiC transistor and the TC of a Schottky diode. The design achieves a mean box model TC of 71ppm with a power consumption of 1.8mA and a PSRR of -47.6db@100Hz, up to 250°C.

#### 2.1.4 Temperature Sensor

Various sensing mechanisms have been proposed for smart temperature sensors. These include bandgap based temperature sensors, time-domain temperature sensors, resistor based and most recently thermal diffusivity based temperature sensors. In the following sub-sections, overviews of these temperature sensors are presented.

### 2.1.4.1 Bandgap based temperature sensors

Bandgap based temperature sensors have been the widely adopted sensing mechanism because of the robustness of the temperature characteristics of BJT and its well established design methodology. Bandgap based temperature sensor designs are predominantly voltage domain temperature sensors.

28

Figure 2.10: Operating principle and bandgap voltages characteristics.

The front-end (Figure 2.5) of a bandgap smart temperature sensor is well known and is based on the BGR principle which is explained in Section 2.1.3. The PTAT voltage  $V_{PTAT}$  (sensing signal) and  $V_{REF}$  (BGR) are generated by the front-end. The ADC does the ratiometric measurement as shown in Figure 2.6 of  $V_{PTAT}$  and  $V_{REF}$  and hence synthesizes the digital output. The operating principle and the corresponding bandgap front-end voltage characteristics are shown in Figure 2.10. The sensing device is substrate PNP transistor which is a parasitic device in CMOS process. It is preferred over lateral PNP because of its more ideal exponential characteristics due to factors such as more one-dimensional flow of current, less variations in saturation current due to lithographic errors in emitter area [42].

The bandwidth requirement for the temperature sensor is dependent on various factors such as thermal mass of package, power dissipated etc. Therefore, typical target for temperature sensors is around 10 conversions per second. Typical inaccuracies in the normal temperature range are within  $\pm 2^{\circ}$ C for well-designed sensors in this category.

Figure 2.11: Block diagram and simplified circuit diagram [44].

Some of the notable CMOS smart sensor bandgap designs are [9], [43], [44]. Reference [9] is one of the pioneer works in this area. This work achieves a 2-point calibrated inaccuracy of  $\pm 1^{\circ}$ C (uncalibrated accuracy of  $\pm 7^{\circ}$ C) for a temperature range of -40 to 120°C. Precision techniques such as DEM, nesting chopping technique, curvature correction etc. are applied to reduce the errors and errors have been reduced to  $\pm 0.5^{\circ}$ C [43] and  $\pm 0.1^{\circ}$ C [44] for temperatures up to 120°C and 125°C respectively. [43] and [44] use low stress ceramic packages and the individual trimming is done after packaging to remove errors due to packaging.

Figure 2.12:  $V_{BE}$  process spread.

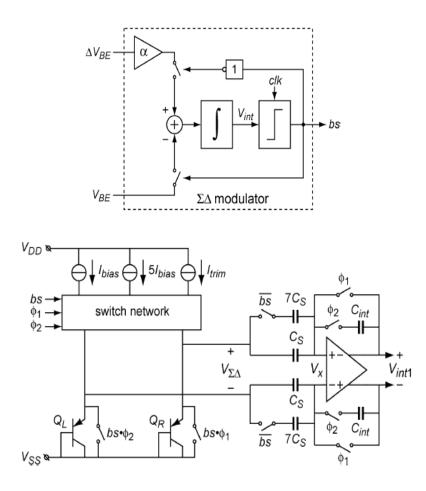

This section will discuss the state-of-the-art temperature sensor based on bandgap principle [44]. This design achieves a state-of-the-art accuracy of  $\pm 0.1^{\circ}$ C and operates up to 125°C. It is achieved by a combination of precision techniques and excellent device characterisation. The A-to-D conversion is done based on the sigma-delta modulation (SDM) principle and charge balancing. Figure 2.11 shows the block diagram and simplified circuit diagram of the temperature sensor.  $V_{BE}$  and  $\alpha \Delta V_{BE}$  are integrated depending on the comparator output *bs* so that effectively the average input to the integrator is zero i.e the charge added by  $\alpha \Delta V_{BE}$  is removed by  $V_{BE}$ . The average value of the bitstream  $\mu$  is given by the following equation

$$\mu = \frac{\alpha \Delta V_{BE}}{V_{BE} + \Delta V_{BE}} = \frac{V_{PTAT}}{V_{REF}}$$

(4)

which corresponds to the ratiometric output  $V_{OUT}$  shown in Figure 2.6. The switched capacitor implementation of the design also facilitates offset and 1/f noise cancellation by correlated double sampling (CDS) technique.

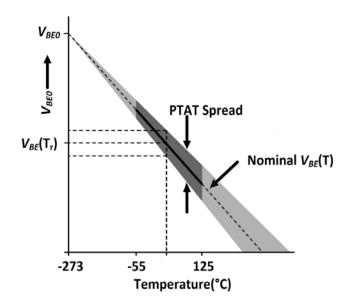

Temperature dependencies of  $V_{BE}$  are the core of the front-end design. One of the major advantages of bandgap sensors is that the process variation of  $V_{BE}$ has just one degree of freedom about the 0K point. This facilitates one-point calibration at any temperature to mitigate this process variation. Figure 2.12 demonstrates this characteristic in a simplified way [42]. In addition,  $V_{BE}$  also has a curvature which is dependent on a process parameter as well as the temperature dependency of the bias current. To facilitate one point calibration of  $V_{BE}$ , the bias current needs to be trimmed. Trimming is achieved conventionally by adjusting the emitter areas or bias current of transistors by switchable transistors and current sources. Trimming is done in this work by a sigma-delta DAC which trims the bias current. This saves chip area when compared to the previous approaches such as binary scaled current/resistor trimming. It also achieves high resolution compared to other approaches. To improve the matching, Dynamic Element Matching (DEM) is applied, i.e the unit current sources are switched in the sigma-delta cycles and hence the mismatch errors are averaged out.

In spite of multiple error sources, the voltage domain bandgap temperature sensors achieve excellent accuracy using a combination of various error correction techniques, as well as excellent device characteristics. However, the design depends on analog intensive precision techniques and circuit design applied here are more suitable for early technology nodes. Recently, the same voltage domain bandgap sensors have been demonstrated in latest technologies [45] using vertical NPN transistors. However, precision analog intensive design in nanometer technology nodes is still a challenge.

Figure 2.13: Basic temperature-to-pulse generator [10].

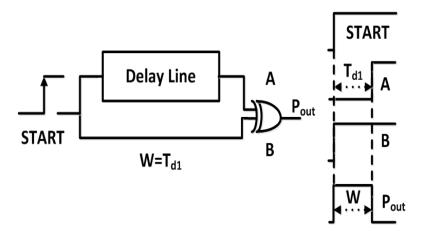

## 2.1.4.2 Time-domain delay chain temperature sensors

Time-domain temperature sensors based on delay chains was proposed so as to be fully compatible with digital CMOS processes. The basic building block of these temperature sensors is the temperature-to-delay cell as shown in Figure 2.13. Once the temperature dependent delay is obtained, it is digitized by a Time-to-Digital (TDC) converter [10]. The delay line invariably is made up of inverter chains whose propagation delay (average of low to high and high to low delay) is given by the following equation.

$$T_{P} = \frac{\left(L/W\right)C_{L}}{\mu C_{ox}\left(VDD - V_{TH}\right)} \ln\left\{\frac{1.5V_{DD} - 2V_{TH}}{0.5V_{DD}}\right\}$$

(5)

where  $\mu$  is the mobility,  $V_{TH}$  is the threshold voltage,  $V_{DD}$  is the power supply, W/L is the aspect ratio of an inverter with an equivalent NMOS and PMOS,  $C_L$ is the loading capacitance of the inverter. Here the temperature dependent factors are  $\mu$  and  $V_{TH}$ . Since  $V_{DD}$  is much higher than  $V_{TH}$ ,  $\mu$  becomes the major temperature dependent factor. Mobility decreases with temperature and therefore  $T_P$  has a PTAT characteristic.

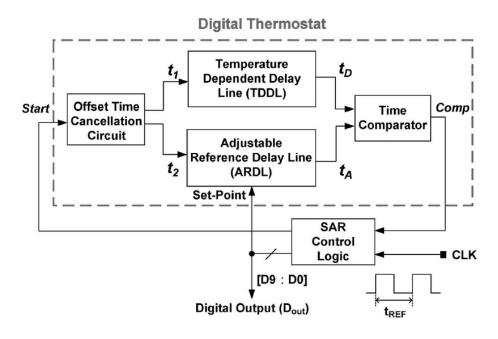

Figure 2.14: Time-domain SAR smart temperature sensor [46].

An implementation of the concept is given in [46] and the proposed architecture is in Figure 2.14. This is an improved version of [47] with SAR control logic to speed up the set-point programming. Temperature Dependent Delay Line (TDDL) produces a delay which is proportional to temperature. Offset cancellation circuit reduces or eliminates the delay at the lower end of the temperature range, thus reduces the measurement time and the output bits required. The time comparator is used to find the delay difference between the ARDL and TDDL delay lines and the SAR control logic adjusts the set-point so that ARDL delay matches TDDL delay.

The mobility dependence on temperature has a non-linear characteristic and therefore the propagation delay too has a curvature. The non-linearity error still exists even though the aspect ratios of TDDL are optimized for linearity enhancement. To mitigate this problem, instead of having a temperature compensated ARDL cell, a non-linearity is introduced in the ARDL cell, with the effect of linearizing the digital time-domain output as

Figure 2.15: Linearity enhancement Figure 2.16: ARDL delay cell [46].

shown in Figure 2.15. The ARDL cell is shown in Figure 2.16. For an optimum  $V_{GS}$  voltage of P3 which is set by sizing of P1, P3 and N1 the conduction current is temperature independent. To achieve curvature compensation, the devices are sized such that minor temperature sensitivity is introduced to match the curvature of TDDL. However, this temperature compensation technique is only applicable for a small temperature range of 90°C as demonstrated in this work. The proposed design occupies and area of 0.6mm<sup>2</sup> in 0.35µm technology with 100 TDDL delay cells and 1024 ARDL delay cells and achieves a worst case inaccuracy of 0.6°C.

This category of sensors is the first fully-digital temperature sensors to be reported and hence can be seamlessly integrated into the latest CMOS technologies. One potential disadvantage is the limitation for spot sensing applications where the spatial temperature variation is to be measured since the temperature sensing is done by the entire delay chain in this case. As can be inferred from (5), the delay has a direct dependence on  $V_{DD}$  and therefore suffers from inherent supply rejection. In addition, two-point calibration is always needed for these sensors to mitigate the process variation.

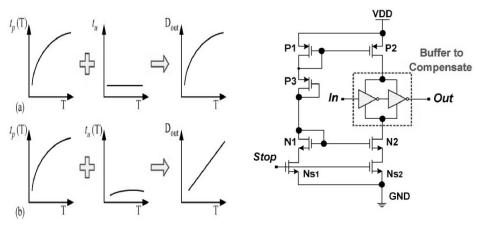

Figure 2.17: Block diagram and BGR free digitization technique [11].

## 2.1.4.3 Resistor Based

Platinum resistor based temperature sensors have been proposed for their precision and wide temperature range. Similarly, The TC of on-chip resistors has been used for temperature sensing purposes [11], [48]. The state-of-the-art resistor TC based temperature sensor is proposed in [11]. The temperature signal  $V_{PTAT}$  is generated as shown in the block diagram of Figure 2.17. SAR control logic is used to digitize the PTAT signal with the reference voltages derived from a BGR free resistor string. The expression for the PTAT output voltage is given by

$$V_{PTAT} = A_V \cdot I_B \cdot R_{10} \cdot TC \cdot \Delta T \tag{6}$$

where  $A_V = (1+R_4/R_3)$  and *TC* is the difference of the TC's of R<sub>1</sub> and R<sub>3</sub> (R<sub>4</sub>). To maximize the temperature sensitivity, resistors with positive temperature coefficient *TC<sub>P</sub>* is chosen for R<sub>1</sub> and negative temperature coefficient *TC<sub>N</sub>* for R<sub>3</sub>, R<sub>4</sub> are used. To obtain the desired PTAT signal the relationship R<sub>10</sub> = R<sub>30</sub> || R<sub>40</sub> needs to be satisfied which is attained by one-point calibration. R<sub>10</sub>, R<sub>30</sub>, R<sub>40</sub> are the resistance values of R<sub>1</sub>, R<sub>3</sub>, R<sub>4</sub> at 0°C.

Conventionally, a BGR is required for the DAC in SAR digitization. However, obtaining a precise BGR with minimum TC for temperature sensing application is non-trivial. The contribution of this work is in avoiding the use of a precision BGR for the SAR logic. The desired reference voltages obtained from an ideal BGR are shown by dotted lines in Figure 2.17. If a BGR is not used, assuming negative TC for the voltages, it results in an error in the reference voltages  $e_1$ ,  $e_2$ , ... $e_n$  for the different reference levels. To solve this problem, the authors propose an Unevenly Weighted Resistor String (UWRS) DAC. The resistor string UWRS DAC produce the desired reference levels  $V_{k,BGR}$ , by designing the nominal reference voltage at  $T_0$  for each k to be

$$V_{k,R}(T0) = \frac{V_{k,BGR}}{1 + TC_{N} \cdot (T_k - T_0)}$$

(7)

The temperature characteristics in (7) achieved in this design by adding compensating resistors of 0.5  $R_{LSB}$  value into appropriate positions in the resistor string. This work has achieved state-of-the-art results for resistor based smart temperature sensor with an accuracy of 0.5°C for a temperature range of 100°C and consumes 20µA of current from 1.8V power supply.

The most critical requirement of this design is resistors whose TCs are well characterized and with less spread. In addition, some resistances may have a second-order temperature coefficient, which contributes to non-linearity error for the temperature sensor. Considering the value of sensing resistors, which is 80 kilo-ohms, 100 kilo-ohms and 400 kilo-ohms for R1, R3, R4, respectively and hence the area occupied, this sensing method may not suitable for spot sensing/ spatial temperature detection within a chip, but suitable for general purpose applications.

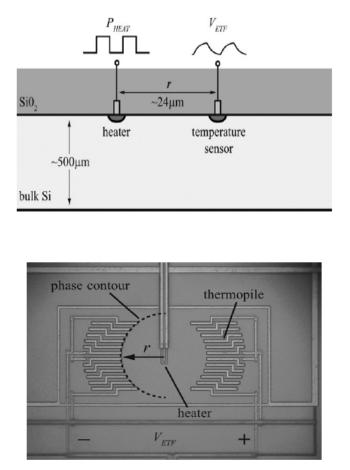

## 2.1.4.4 Thermal Diffusivity

In the high temperature category of sensors, thermal diffusivity based sensors are promising. The advantage is their un-calibrated accuracy, which is limited only by lithographic spread and not by wafer-to-wafer or batch-tobatch spread. Hence, the accuracy has been found to improve with technology node. Almost all the category of sensors so far needs at least one-point calibration to achieve a decent performance. However, thermal diffusivity based sensors achieve comparable accuracy without calibration.

The basic sensing element of thermal diffusivity based sensor [49] is the Electrothermal Filter (ETF) the schematic and CMOS implementation of which is given in Figure 2.18. The ETF consists of a heater and a temperature sensor. The heat generated from the heater element diffuses through the substrate to create temperature fluctuations in the sensor. The time it takes for the heat to diffuse is a function of absolute temperature. The temperature dependent factor is known as thermal diffusivity *D* which has a temperature dependency of  $1/T^{1.8}$ . The phase shift  $\Phi_{ETF}$  at the sensor output is given by the following equation

Figure 2.18: ETF schematic and CMOS layout [49].

$$\Phi_{ETF} = -r_{\sqrt{\frac{\prod f_{drive}}{D}}}$$

(8)

where  $f_{drive}$  is the driving frequency of the heater, r is the distance to the heater which in this work is 24µm and is accurately determined especially in latest technologies. Therefore if the  $f_{drive}$  is constant,  $\Phi_{ETF}$  has an almost linear dependency with temperature of T<sup>0.9</sup>. The heater in this work is a p+ diffusion resistor and the sensor is a thermopile made up of a series of diffusion/aluminium junctions.

One of the advantages of this category of sensor is that due to its timedomain nature, ETF's are unaffected by leakage currents. The buried oxide layer in SOI improves the SNR when compared to bulk CMOS

Figure 2.19:  $PD\Sigma\Delta M$  read-out [49].

implementations [50], [51] due to the reduction in heat loss by the buried oxide layer. The output of the sensor is a phase shifted signal at a known frequency and hence the readout circuit is a phase detector.

The sensor achieves a  $3\sigma$  un-calibrated accuracy of  $\pm 0.6^{\circ}$ C up to 225°C. This category of sensors has the best reported un-calibrated accuracy. The design consumes a power of 3.5mW and occupies an area of 1mm<sup>2</sup>. The limitation of power is due to the fact that the sensing mechanism is based on heat dissipation and the heat is generated by an electrical source. Due to the thermal isolation by BOX layer in SOI the power needed for heat source is lesser for SOI when compared to bulk CMOS. For optimum performance of this category of sensors thermal modelling of the ETF is essential [52]. This may need interdisciplinary expertise when compared to other category of sensors where the sensing mechanism is based on CMOS devices such as BJT, transistor, resistor etc.

40

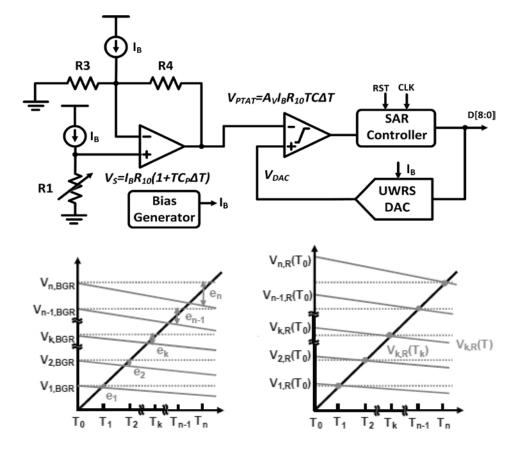

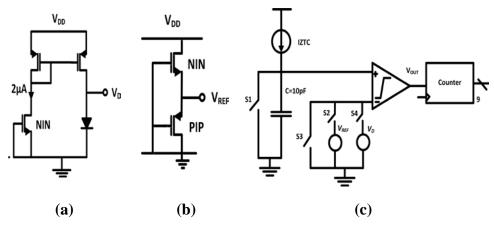

Figure 2.20: (a) *V*<sub>D</sub>, (b) *V*<sub>REF</sub> and (c) ADC [54].

## 2.1.4.5 Time-domain ratiometric sensors

Two designs coming under this category are discussed in this section. One is a recent work from Intel [53]. Other design [54] is for high temperature work operating above 200°C. Both designs follow the ratiometric principle of comparing a temperature dependent signal to a temperature independent voltage reference. However, the ratiometric measurement is done in timedomain.

The technology used in [54] is FDSOI. The temperature dependent signal, generated by a SOI PIN diode  $V_D$  which has a CTAT characteristic and the reference voltage  $V_{REF}$  [55] are shown in Figure 2.20 (a) and (b), respectively. The ratiometric output is given by

$$\alpha = \frac{V_D}{V_{REF}} \tag{9}$$

Figure 2.21: (a) Architecture (b) V/F converter.

The temperature sensor architecture is shown in Figure 2.20 (c). It is based on a conventional TDC architecture. The capacitor is charged with a ZTC current and the count to reach  $V_D$  is compared to reach the count  $V_{REF}$ , which is fixed. The circuit achieves a temperature error of 3.9°C after 2-point calibration and 2.85°C after 7-point calibration. From the analysis by the author, it is found that the major reason for inaccuracy is the non-linearity/TC of the reference voltage  $V_{ref}$ . The total power consumption is 50µA from a 3 V supply. The main advantage of this design is that the architecture is simple and hence power consumption is low. The architecture needs a precision voltage reference operating over a wide temperature range with good TC. The high temperature  $V_{ref}$  generator of this design [55] has a high TC which deteriorates the temperature performance. Another requirement of this architecture is that of a precise ZTC current which may be challenging to realize considering the process dependencies.

The second design in [53] is based on ratiometric principle and designed for thermal monitoring purposes. The main requirement for these applications is compactness so that the sensor can be placed in multiple locations. The accuracy requirements are relaxed and the typical accuracy needed is  $\pm 1^{\circ}$ C at throttle and  $\pm 5^{\circ}$ C at 50°C.

The architecture of this sensor is shown in Figure 2.21 (a). The analog part consists of a BGR which generates  $V_{BE}$  and  $V_{REF}$  and two voltage-to-frequency converters. The voltage to frequency converters are used to convert  $V_{REF}$  and  $V_{BE}$  to frequencies  $F_1$  and  $F_2$ , respectively. The schematic of the V/F converter is given in Figure 2.21 (b). This sensor achieves a 3 $\sigma$  accuracy of <4.5°C after sensor and BGR calibration (resistor trimming) at 100°C. The design consumes 3.8mW of power and occupies a chip area of 0.02mm<sup>2</sup> and is fabricated in 32nm technology node.

## 2.2 Summary

Initial high temperature designs were done in bulk CMOS. Leakage at high temperatures is a bottleneck for robust operation bulk CMOS. This calls for special care with respect to leakage compensation/reduction in bulk CMOS

43

| Parameter            | [33]                 | [28]     | [41]               | [27]                 |

|----------------------|----------------------|----------|--------------------|----------------------|

| Technology           | SIMOX                | FDSOI    | SiC                | 0.16-μm<br>CMOS      |

| Temperature<br>Range | 25–200°C             | 25–300°C | 25–250°C           | $-40 - 125^{\circ}C$ |

| TC(ppm)              | 50                   | 100      | 71(mean)           | 5–12                 |

| Туре                 | Threshold<br>Voltage | Bandgap  | Diode/<br>Mobility | Bandgap              |

| Extra Masks          | Yes                  | No       | No                 | No                   |

| Samples              | 1                    | 1        | 2                  | 61                   |

| Calibration          | N.A                  | N.A      | N.A                | 1                    |

| Current              | N.A                  | 200µA    | 1.8mA              | 55μΑ                 |

| PSRR                 | N.A                  | N.A      | -47.6db<br>@100Hz  | -74db@DC             |

TABLE 2-1: SUMMARY OF VOLTAGE REFERENCE PERFORMANCE

[22]. Use of SOI technology enabled the circuit designer to focus on the performance of the circuit without being limited by leakage. Recently, SiC technology has also been used for HT design.

TABLE 2-1 summarizes the performance of the salient voltage reference designs discussed in the review. From the table it is found that there is further scope for performance improvement in the HT category and in turn, the HT

| Parameter             | [54]       | [49]                   | [46]                     | [44]                | [53]                |

|-----------------------|------------|------------------------|--------------------------|---------------------|---------------------|

| Process               | FDSOI      | 0. 5µm SOI<br>BiCMOS   | 0.35µm<br>CMOS           | 0.7μm<br>CMOS       | 32nm<br>CMOS        |

| Sensing               | PIN Diode  | Thermal<br>Diffusivity | Delay Line               | Bandgap             | Bandgap             |

| Calibration<br>Points | 2          | 0                      | 2                        | 1                   | 1                   |

| Current               | 50μΑ       | 700µA                  | 12μΑ                     | 75μΑ                | 3.8mA               |

| Accuracy              | 3°C        | 0.6°C                  | 0.6°C                    | 0.1°C               | 2.25°C              |

| Area                  | N/A        | 1 mm <sup>2</sup>      | 0.6mm <sup>2</sup>       | 4.5mm <sup>2</sup>  | 0.02mm <sup>2</sup> |

| Temperature<br>Range  | 25 – 250°C | -70 – 225°C            | $0-90^{\circ}\mathrm{C}$ | -55 – 125°C         | 20 – 100°C          |

| Inaccuracy<br>FOM*    | N/A        | 5.6x10 <sup>5</sup>    | 2.3x10 <sup>4</sup>      | 2.3x10 <sup>3</sup> | 3.1x10 <sup>3</sup> |

TABLE 2-2: SUMMARY OF TEMPERATURE SENSOR PERFORMANCE

temperature sensor performance. TABLE 2-2 summarizes the performance of the salient temperature sensor designs discussed in the review. As far as HT operation is concerned, to the best knowledge of the author there is no BGR based temperature sensor operating above 200°C.

In this thesis, a non-BGR temperature sensor front-end based on threshold voltage operating up to 225°C and a time-domain bandgap smart temperature sensor up to 250°C are presented.

# CHAPTER 3

# THRESHOLD VOLTAGE BASED SMART TEMPERATURE SENSOR FRONT-END

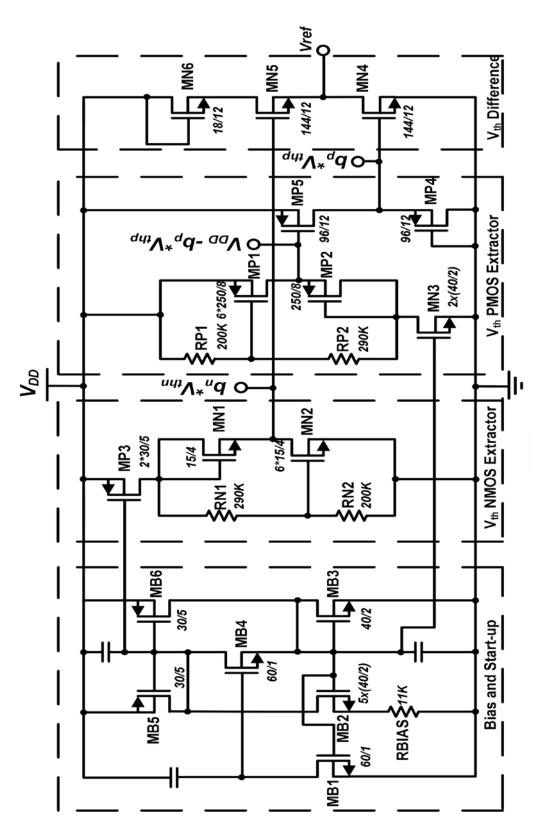

This chapter proposes a temperature sensor front-end based on threshold voltage temperature dependency of NMOS and PMOS transistors. The core of this design is the threshold voltage ( $V_{th}$ ) extraction cell. The proposed topology does not need op-amp or BJT's. The temperature information can be extracted from the ratiometric output of the CTAT and the reference voltage. The front-end achieves one of the widest operating temperatures reported in literature. The sections below describe the design.

# 3.1 Threshold Voltage Temperature Dependence

The  $V_{th}$  dependencies for bulk CMOS and thick film PD-SOI CMOS are analyzed in [56]. The TC of  $V_{th}$  is given by

$$\frac{\partial V_{th}}{\partial T} = \frac{\partial \phi}{\partial T} \left[ 1 + \frac{q}{C_{ox}} \sqrt{\frac{\varepsilon_{si} N_a}{kT \ln(N_a / n_i)}} \right]$$

(10)

where the Fermi potential  $\Phi$  and intrinsic carrier concentration  $n_i$  is given by the following equations [57]

$$\phi = \frac{kT}{q} \ln(\frac{N_a}{n_i}) , \ n_i = 3.9 \cdot 10^{16} \cdot T^{3/2} \cdot e^{-(E_g/2kT)}$$

(11)

q is the electron charge, k is the Boltzmann constant,  $N_a$  is the doping concentration,  $\varepsilon_{si}$  is the silicon permittivity,  $C_{OX}$  is the gate capacitance per unit area and  $E_g$  is the silicon bandgap energy. Substituting for  $n_i$  in  $\Phi$  and differentiating (11) we get,

$$\frac{\partial \phi}{\partial T} = 8.63 \times 10^{-5} \left[ \ln(N_a) - 38.2 - \frac{3}{2} \left\{ 1 + \ln(T) \right\} \right]$$

(12)

From (10) and (12) it is inferred that the dominant process dependent parameter for TC is the doping concentration  $N_a$ . The standard deviation of  $N_a$ in the SOI process we use is around 5%. However, the presence of  $N_a$  in the natural logarithm and square root term reduces the dependency of threshold voltage TC on  $N_a$ . This makes V<sub>th</sub> a good candidate for temperature sensing with regard to the impact of process variation on TC. The temperature dependence of  $n_i$  in (10) and ln(T) term in (12) results in higher order terms for V<sub>th</sub> TC and introduces non-linearity. The temperature dependency of V<sub>th</sub> from (10) and (12) can be modeled as [58],

$$V_{th}(T) = V_{th}(T_{nom}) + (K_{t1} + \frac{K_{t1l}}{L_{eff}} + K_{t2} \times V_{bseff})(\frac{T}{T_{nom}} - 1)$$

(13)

where  $K_{t1}$ ,  $K_{t11}$  and  $K_{t2}$  represent  $V_{th}$  TC dependency on the process parameter, channel length and body bias respectively. For the PDSOI process used in this work,  $K_{t1}$ ,  $K_{t11}$  and  $K_{t2}$  have the values corresponding to  $V_{th}$  TC of - $2.11 \text{mV/}^{\circ}\text{C}$ ,  $-0.103 \text{mV} \cdot \mu \text{m/}^{\circ}\text{C}$  and  $0.07 \text{mV/}^{\circ}\text{C}$ , respectively, for NMOS transistors. The corresponding values for PMOS transistors are  $-2.2 \text{mV/}^{\circ}\text{C}$ ,  $-0.1 \text{mV} \cdot \mu \text{m/}^{\circ}\text{C}$  and  $0.067 \text{mV/}^{\circ}\text{C}$ . It is noted in (13) that, in addition to circuit tuning, the  $V_{th}$  TC can also be tuned by channel length and body bias.

## 3.2 V<sub>TH</sub> Extraction and CTAT Voltage Generation

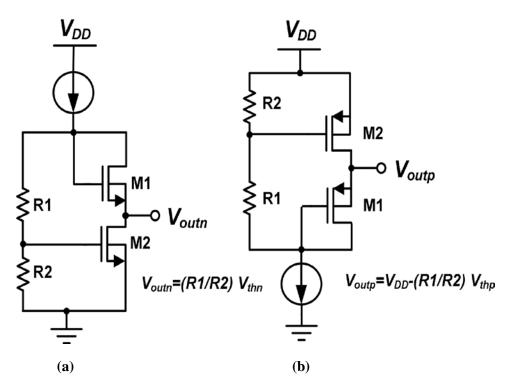

The analysis in Section 3.1 shows that the threshold voltage of either PMOS or NMOS is a good candidate to implement a CTAT voltage, provided that the

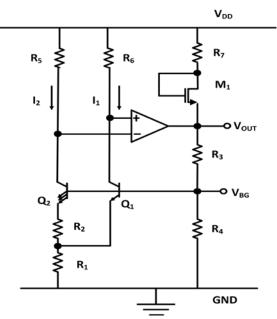

Figure 3.1: (a) NMOS and (b) PMOS threshold voltage extraction cells.

threshold voltage can be extracted. A simple  $V_{th}$  extraction topology based on square-law model is proposed in this work. The circuit structure has been used for a voltage reference in [34], based on sub-threshold operation characteristics of CMOS transistors. In this work, the topology is converted to  $V_{th}$  extraction circuit by operating the transistors in strong inversion and saturation region and applying square-law model to derive  $V_{th}$  extraction conditions. The proposed NMOS and PMOS  $V_{th}$  extraction cells are shown in Figure 3.1 (a) and (b). Based on simple voltage division principle in Figure 3.1 (a) we get,

$$(V_{outn} + V_{GS1}) \cdot \frac{R2}{R1 + R2} = V_{GS2} \tag{14}$$

From (14), V<sub>outn</sub> can be written as,

$$V_{outn} = V_{GS2} \left( 1 + \frac{R1}{R2} \right) - V_{GS1}$$

(15)

Applying square law for the strong inversion operation and neglecting channel length modulation effect,  $V_{GS}$  is typically expressed as,

$$V_{GSi} = V_{THi} + \sqrt{\frac{2I}{k_i}}$$

(16)

where,  $k_i = \mu_n Cox(W_i/L_i)$ . Substituting, for  $V_{GS}$  from (16) in (15), the expression for the output voltage for NMOS cell is given by

$$V_{outn} = \left(V_{TH\,2} + \sqrt{\frac{2I}{k_2}}\right) \left(1 + \frac{R_1}{R_2}\right) - \left(V_{TH\,1} + \sqrt{\frac{2I}{k_1}}\right)$$

(17)

Simplifying (17) we get,

$$V_{outn} = \frac{R1}{R2} V_{thn2} + V_{thn2} - V_{thn1} + \sqrt{2I} \left( \left(1 + \frac{R1}{R2}\right) \frac{1}{\sqrt{k_2}} - \frac{1}{\sqrt{k_1}} \right)$$

(18)

If  $V_{thn1} \approx V_{thn2} \approx V_{thn}$ ,