# SOURCE/DRAIN ENGINEERING IN INGAAS N-MOSFETS FOR LOGIC DEVICE APPLICATIONS

**SUJITH SUBRAMANIAN**

NATIONAL UNIVERSITY OF SINGAPORE

# SOURCE/DRAIN ENGINEERING IN INGAAS N-MOSFETS FOR LOGIC DEVICE APPLICATIONS

### **SUJITH SUBRAMANIAN**

B.Tech., CUSAT M.Sc., NTU and TUM

# A THESIS SUBMITTED FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

### NUS GRADUATE SCHOOL FOR INTEGRATIVE SCIENCES AND ENGINEERING

NATIONAL UNIVERSITY OF SINGAPORE

## DECLARATION

I hereby declare that the thesis is my original work and it has been written by me in its entirety. I have duly acknowledged all the sources of information that have been used in the thesis.

This thesis has also not been submitted for any degree in any university previously.

Sujith Subramanian

24 JULY 2014

### Acknowledgements

This thesis was made possible with the support and contribution of many individuals.

I wish to thank, first and foremost, my research advisor, Prof. Yee-Chia Yeo, for his continuous support and encouragement during my Ph.D. study and research. His advice and guidance throughout my graduate studies has been invaluable. I am grateful to have had the opportunity to learn under his tutelage, and I believe that everything that I have learned from him over the past few years will be beneficial in my career and life.

I owe my deepest gratitude to Ivana, Eugene, Vijay, Zhou Qian, Xingui, Mahendran, and Sachin for their valuable contributions to this thesis. I would also like to thank our collaborators from NTU: Daosheng, Satrio, and Prof. Yoon Soon Fatt for their contribution to this work.

A special thanks to Ashvini, Ivana, Eugene, Kain Lu, Kian Hui, Gong Xiao, Guo Cheng, Samuel, Pannir, Kien Mun, and Sachin for all the fun times and the wonderful memories that I take with me. I would also like to thank all my other colleagues at Silicon Nano Device Laboratory (SNDL): Hock Chun, Shao Ming, Pengfei, Liu Bin, Huaxin, Lanxiang, Zhu Zhu, Tong Yi, Yinjie, Cheng Ran, Yang Yue, Chunlei, Phyllis, Tong Xin, Wenjuan, Wang Wei, Dong Yuan, Xu Xin, Han Han, Annie, Du Fang, Lei Dian, Sandipan and Maruf. It has truly been an honor and a privilege to have worked with you guys. I would also like to thank Jerrin, Deepak, Ganesh and Supriya for their support and encouragement which has helped me through the course of my Ph.D. study. I would also like to extend my appreciation and gratitude to Mr. O Yan, Mr. Patrick Tang, Ms. Yu Yi, and all the emergency response team (ERT) members for providing technical and administrative support and ensuring the safety and proper functioning of the cleanrooms and lab. I would like to acknowledge the technical staff of IMRE and DSI, for facilitating the use of equipment's and providing the services such as SIMS and TEM used in this work. In addition, I would like to acknowledge Dr. Rinus Lee from SEMATECH for the useful discussions in some of our collaboration projects.

Last but not the least, I would also like to extend my deepest and sincere gratitude to my mom, dad, brother and all the other family members who have supported and encouraged me throughout the years in all my endeavors.

## **Table of Contents**

| DECLARATION                                                 | iii  |

|-------------------------------------------------------------|------|

| Acknowledgements                                            | iv   |

| Table of Contents                                           | vi   |

| Summary                                                     | ix   |

| List of Tables                                              | xii  |

| List of Figures                                             | xiii |

| List of Symbols                                             | XXV  |

| Chapter 1 Introduction                                      | 1    |

| 1.1 Background                                              | 1    |

| 1.2 Scaling Challenges of Transistors                       | 2    |

| 1.2.1 Leakage currents                                      | 3    |

| 1.2.2 Random dopant fluctuation                             | 5    |

| 1.2.3 Power constrained scaling                             | 5    |

| 1.3 Motivation for Using III-V Materials                    | 6    |

| 1.4 Challenges for III-V CMOS Logic                         | 9    |

| 1.4.1 Realization of high-quality gate stack                | 10   |

| 1.4.2 Integration on a Si platform                          |      |

| 1.4.3 III-V P-MOSFETs                                       | 13   |

| 1.4.4 Source/Drain regions with low $C_{GD}$ and $R_{SD}$   | 14   |

| 1.4.5 Density of States (DOS) Bottleneck                    | 15   |

| 1.5 Objective and Organization of Thesis                    | 16   |

| Chapter 2 Source/Drain Series Resistance in InGaAs N-MOSFET | s 18 |

| 2.1 Introduction                                            |      |

| 2.2 Concept of Source/Drain Series Resistance               | 18   |

| 2.3 Elements of Source/Drain Resistance                     | 19   |

| 2.4 Source/Drain Engineering in III-V N-MOSFETs             | 21   |

| 2.5 Self-Aligned Metallic Contacts for InGaAs N-MOSFETs                                                                      |              |

|------------------------------------------------------------------------------------------------------------------------------|--------------|

| 2.5.1 Ni-InGaAs Contact Technology                                                                                           |              |

| 2.5.2 Other Self-Aligned Contact Schemes                                                                                     |              |

| 2.6 Summary                                                                                                                  |              |

| Chapter 3 Selective Wet Etching Process for Contact Formation in                                                             | ı InGaAs N-  |

| MOSFETs with Self-Aligned Source and Drain                                                                                   |              |

|                                                                                                                              | 25           |

| 3.1 Introduction                                                                                                             |              |

| 3.2 Experimental Procedures                                                                                                  |              |

| 3.2.1 Method of Determining the Etch Rate and Selectivity                                                                    |              |

| 3.2.2 Selection of Chemicals and Conditions                                                                                  |              |

| 3.3 Results and Discussion                                                                                                   |              |

| 3.3.1 Selective Etch of Ni over Ni-InGaAs                                                                                    |              |

| 3.3.2 Selective Etch of NiPt over NiPt-InGaAs                                                                                |              |

| 3.4 Conclusion                                                                                                               |              |

| Chapter 4 Embedded Metal Source/Drain for In0.53Ga0.47As N-Ch                                                                |              |

| Thin Body Field-Effect Transistor                                                                                            |              |

| 4.1 Introduction                                                                                                             |              |

| 4.2 InGaAs UTB-FET with an <i>e</i> MSD Architecture                                                                         | 60           |

| 4.2.1 Formation of Ni-InAlAs                                                                                                 | 60           |

| 4.2.2 Device Fabrication                                                                                                     |              |

| 4.2.3 Results and Discussion                                                                                                 | 65           |

| 4.3 Evaluating eMSD Architecture for Future Technology Nodes: A                                                              | A Simulation |

| Study                                                                                                                        | 74           |

| 4.3.1 Structure and Parameters Used for Simulation                                                                           | 74           |

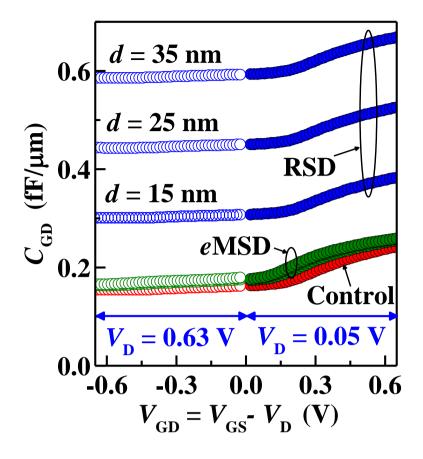

| 4.3.2 Effect of S/D Thickness on the Parasitic Capacitance ( $C_{GD}$ )                                                      | 77           |

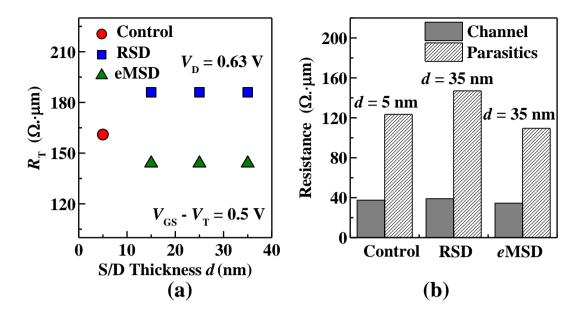

| 4.3.3 Effect of S/D Thickness on the Parasitic Resistance $(R_{SD})$                                                         |              |

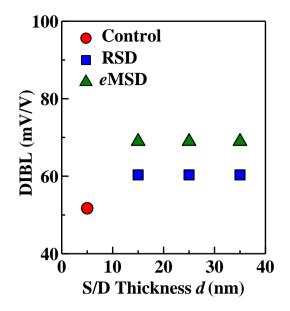

| 4.3.4 Influence of S/D Thickness on Short Channel Effects                                                                    |              |

| 4.3.5 InGaAs FinFET with eMSD to Reduce Short Channel Effects                                                                |              |

| 4.4 Conclusion                                                                                                               |              |

| Chapter 5 P <sub>2</sub> S <sub>5</sub> /(NH <sub>4</sub> ) <sub>2</sub> S <sub>x</sub> -Based Sulfur Monolayer Doping for S | ource/Drain  |

| Extensions in InGaAs N-MOSFETs                                                                                               |              |

|                                                                                                                              |              |

| 5.1 Introduction                                                                                                             |              |

| 5.2 SMLD of InGaAs using $P_2S_5$ and $(NH_4)_2S_x$                   | 91  |

|-----------------------------------------------------------------------|-----|

| 5.2.1 Motivation for Using P2S5/(NH4)2Sx                              | 91  |

| 5.2.2 Surface Chemistry                                               | 91  |

| 5.2.3 Blanket and TLM Sample Preparation                              |     |

| 5.3 Material Characterization                                         | 94  |

| 5.4 Optical Characterization Using IRSE                               |     |

| 5.4.1 Motivation for Using IRSE                                       |     |

| 5.4.2 Details of the Measurement                                      |     |

| 5.4.3 Results and Discussion                                          |     |

| 5.5 MOSFET Fabrication and Characterization                           | 107 |

| 5.6 Conclusion                                                        | 112 |

| Chapter 6 Conclusion and Future Directions                            | 114 |

| 6.1 Conclusion                                                        | 114 |

| 6.2 Contributions of This Thesis                                      |     |

| 6.2.1 Selective Etching Process for the Formation of Self-Aligned M   |     |

| InGaAs N-MOSFETs                                                      |     |

| 6.2.2 <i>e</i> MSD Architecture for InGaAs N-MOSFETs with Self-Align  |     |

| S/D                                                                   |     |

| 6.2.3 $P_2S_5/(NH_4)_2S_x$ -Based Monolayer Doping Technique for SDEs |     |

| MOSFETs                                                               |     |

| 6.3 Future Directions                                                 | 116 |

| References                                                            | 119 |

| Appendix                                                              | 158 |

| List of Publications                                                  |     |

### Summary

Source/Drain Engineering in InGaAs N-MOSFETs for Logic Device

Applications

by

Sujith Subramanian

Doctor of Philosophy – NUS Graduate School for Integrative

Sciences and Engineering

National University of Singapore

For the past four decades, silicon (Si) based complementary metal-oxidesemiconductor (CMOS) technology has been dominating digital integrated circuits (ICs) in the semiconductor industry. Over the years, as transistors are scaled down and their performance enhanced, the need for these devices to consume lower power has become essential. Power consumption in ICs can be minimized by reducing the supply voltage ( $V_{DD}$ ) and leakage currents in the transistor. In the past few years, improvement in device performance has been brought about through innovations in the design of the MOSFET (such as strain engineering). However, it will be challenging to continue this performance enhancement of Si CMOS transistors in the near future, due to the fundamental limitations in the material properties of Si. Due to these fundamental limits, reducing the  $V_{DD}$  further would have direct repercussions on the device performance. Therefore, non-Si electronic materials have been explored for future logic applications. InGaAs, with its high electron mobility, is an attractive candidate to replace Si as the channel layer for N-MOSFETs at sub-10 nm technology nodes. However, several challenges need to be overcome before this technology can be successfully integrated in the IC manufacturing process.

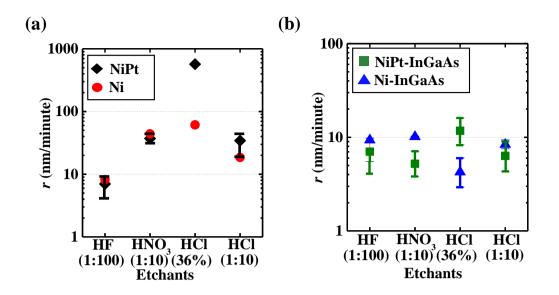

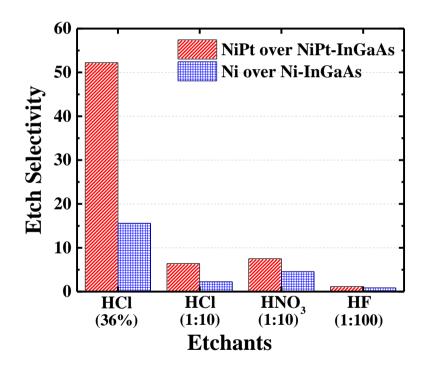

In this thesis, source/drain (S/D) engineering for InGaAs N-MOSFETs is explored. Contact metals with low bulk resistivities, and low contact resistivities on highly n-type doped (n<sup>++</sup>) InGaAs are needed to reduce S/D resistances ( $R_{SD}$ ) and in turn boost the drive current of the MOSFETs. Due to their material properties, Ni based alloys (such as Ni-InGaAs and NiPt-InGaAs) are attractive materials for potential use as S/D contacts in InGaAs N-MOSFETs. Therefore, a selective etching process was developed to evaluate the feasibility of using Ni-InGaAs and NiPt-InGaAs as contact materials in an InGaAs N-MOSFET. The etch rates of Ni-InGaAs and NiPt-InGaAs in several wet etch chemistries were extracted using various characterization techniques. Subsequently, the selectivities of etching Ni and NiPt over Ni-InGaAs and NiPt-InGaAs, respectively, were determined. High selectivities were obtained for HCl and HNO<sub>3</sub> based chemistries, making them the most favorable choices for the selective removal of Ni and NiPt over Ni-InGaAs and NiPt-InGaAs, respectively.

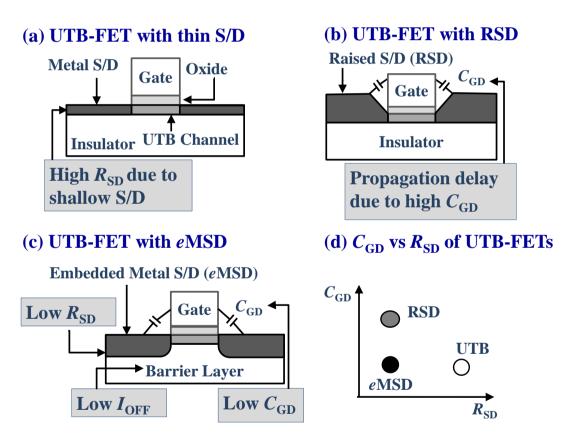

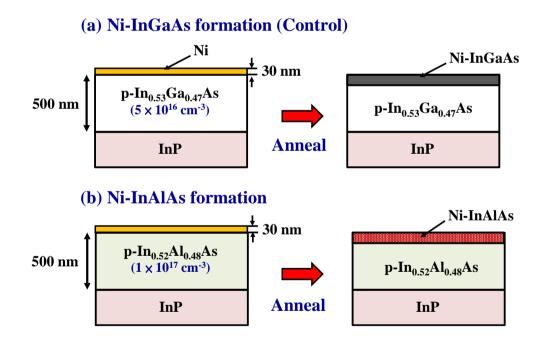

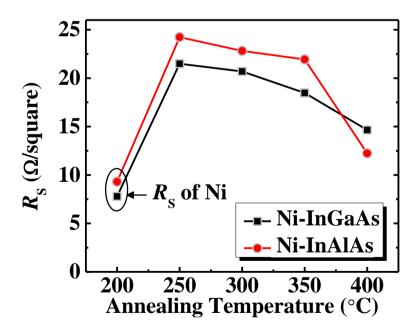

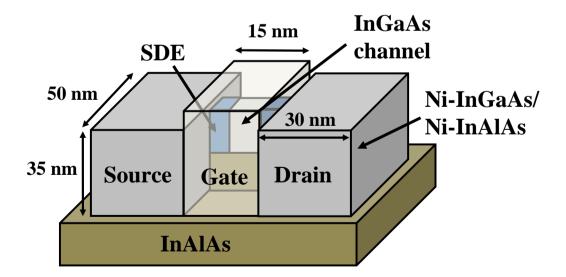

For achieving transistors with high drive current and switching speed, it is important to minimize the parasitic gate-to-drain capacitance ( $C_{GD}$ ) and  $R_{SD}$ . In addition, at sub-10 nm technology nodes, advanced structures such as ultra-thin body FETs are required to reduce the short channel effects (SCE). In this thesis, an embedded metal S/D (*e*MSD) architecture was developed to reduce  $R_{SD}$  and  $C_{GD}$  in InGaAs nchannel UTB-FETs. Long channel devices with Ni-InGaAs/Ni-InAlAs *e*MSD were successfully demonstrated with the help of the selective etching process developed earlier. In addition, the viability of using the eMSD design at future technology nodes was evaluated using technology computer aided design (TCAD) simulations. The results indicated that UTB-FETs with  $R_{SD}$  and  $C_{GD}$  that meet the International Technology Roadmap for Semiconductors (ITRS) requirements, can be achieved using the *e*MSD design. In addition, 3D structures such as fin field effect transistors (FinFETs) would be eventually required to further reduce SCEs such as drain-inducedbarrier-lowering (DIBL).

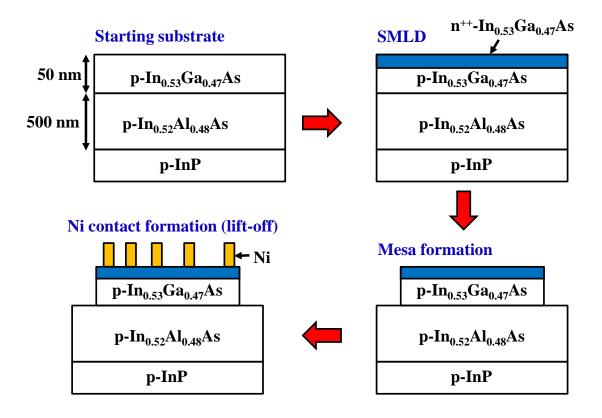

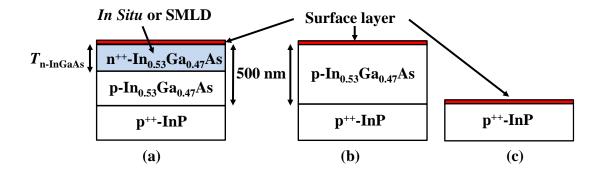

To further reduce the  $R_{SD}$  in InGaAs N-MOSFETs, ultra-shallow S/D extension (SDE) regions with low resistances are required. These ultra-shallow junctions have to be very abrupt and highly doped. Hence, sulfur monolayer doping (SMLD) using P<sub>2</sub>S<sub>5</sub>/(NH<sub>4</sub>)<sub>2</sub>S<sub>x</sub> solution was developed for the formation of SDEs in InGaAs N-MOSFETs. The n<sup>++</sup>-InGaAs films formed using SMLD were studied using various characterization methods. The electrical resistivities, carrier relaxation times and active doping concentration ( $N_D$ ) of the shallow n<sup>++</sup>-InGaAs films were then extracted using Infrared Spectroscopic Ellipsometry (IRSE). Sub-10 nm n<sup>++</sup>-InGaAs layers were realized using SMLD with  $N_D$  of ~1.7 × 10<sup>19</sup> cm<sup>-3</sup>. The SMLD process using P<sub>2</sub>S<sub>5</sub>/(NH<sub>4</sub>)<sub>2</sub>S<sub>x</sub> was demonstrated on planar InGaAs N-MOSFETs and the effect of the dopant activation conditions on device performance was studied.

# **List of Tables**

| Table 1.1. | Scaling trends to improve integrated circuit performance [5]                                  |

|------------|-----------------------------------------------------------------------------------------------|

| Table 2.1. | Benchmarking the various self-aligned contact schemes on                                      |

|            | In <sub>0.53</sub> Ga <sub>0.47</sub> As                                                      |

| Table 3.1. | Etch rates of Ni and Ni-InGaAs in various etch chemistries40                                  |

| Table 3.2. | Chemical reactions between Ni and HCl or HNO <sub>3</sub> [251]40                             |

| Table 3.3. | Etch selectivity of Ni over Ni-InGaAs in different etchants                                   |

| Table 4.1. | Summary of the parameters used in the 2D simulation77                                         |

| Table 4.2. | Comparison of the merits of the different S/D architectures86                                 |

| Table 5.1. | Electrical and physical parameters for SMLD and in situ doped n <sup>++</sup> -InGaAs samples |

| Table 5.2. | The activation efficiency calculated from the active and total sulfur                         |

|            | dose obtained from IRSE and SIMS measurements106                                              |

### **List of Figures**

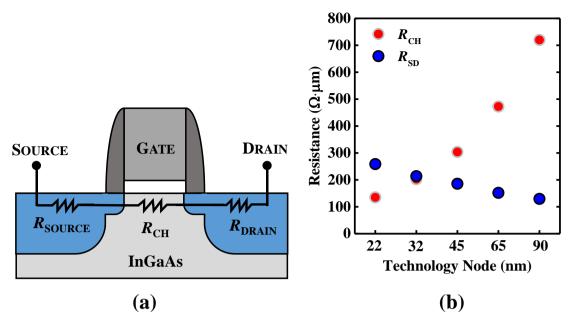

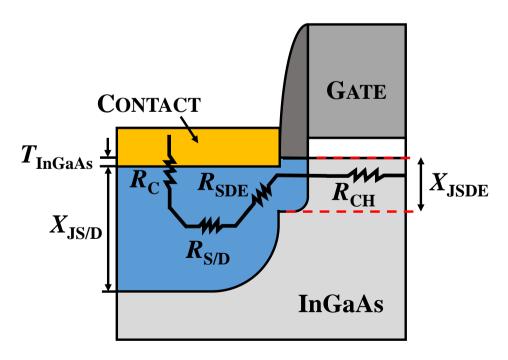

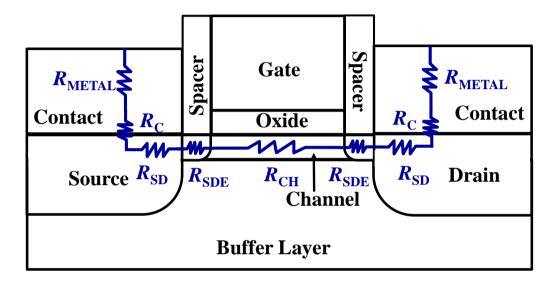

- **Fig. 2.1.** (a) Schematic illustrating the different resistance components in an InGaAs N-MOSFET (in the linear regime). The total resistance  $R_{\rm T}$  of the transistor is the summation of the channel resistance  $R_{\rm CH}$ , and the parasitic resistance  $R_{\rm SD} = R_{\rm SOURCE} + R_{\rm DRAIN}$ . (b) The scaling trend for  $R_{\rm CH}$  and  $R_{\rm SD}$  in Si N-MOSFETs (taken from Ref. [164]). As  $R_{\rm CH}$

reduces with gate length,  $R_{\rm T}$  becomes dominated by  $R_{\rm SD}$ . Therefore,  $R_{\rm SD}$  needs to be minimized to achieve a high  $I_{\rm ON}$  in the transistor. .19

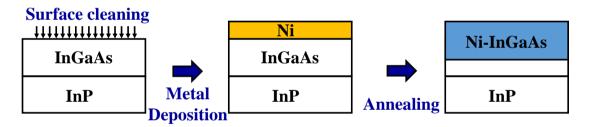

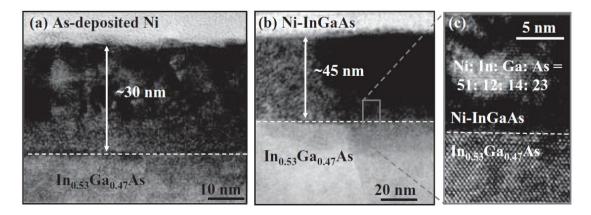

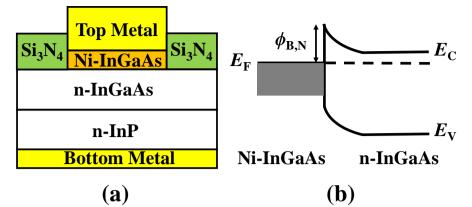

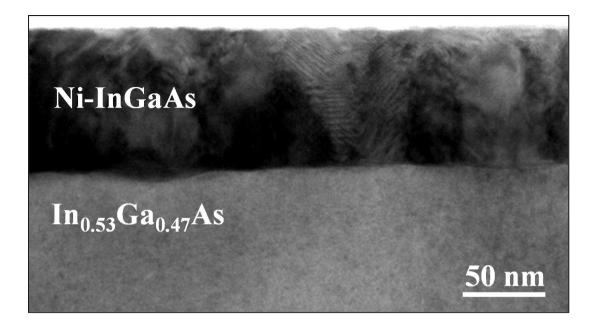

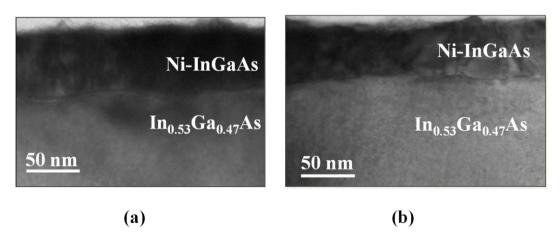

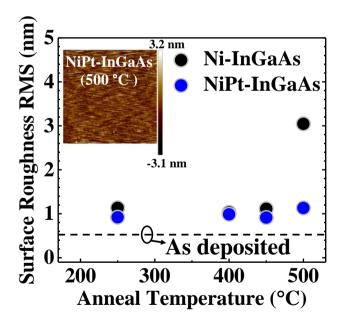

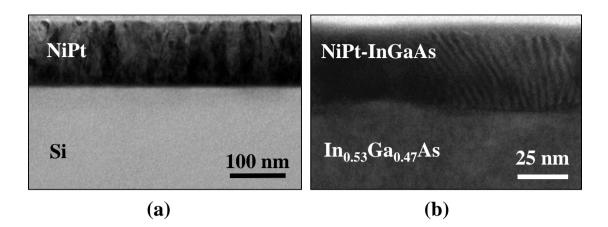

- Fig. 2.4. (a) As-deposited Ni film (~30 nm) on an InGaAs/InP substrate. (b) The ~45 nm thick Ni-InGaAs film formed after the samples were annealed at 250 °C. (c) High resolution TEM of the Ni-InGaAs/InGaAs interface. Crystalline Ni-InGaAs was formed and the atomic compositions of Ni, In, Ga, and As were 51, 12, 14, and 23, respectively. These figures are taken from Ref. [226]......24

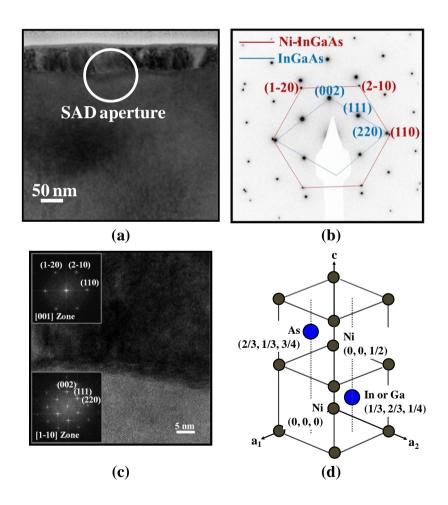

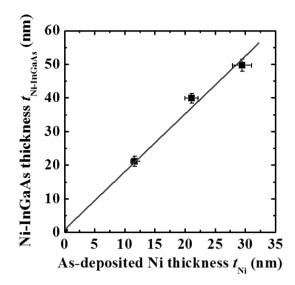

- Fig. 2.5. (a) TEM image of the Ni-InGaAs/InGaAs sample. (b) The SAD pattern obtained from the region shown in (a). The diameter of the circle is 150 nm. (c) High resolution TEM image of Ni-InGaAs/InGaAs. The corresponding diffraction patterns are shown in the inset. (d) Unit cell of Ni-InGaAs phase. Ni-InGaAs shows a NiAs (B8) type of structure. These figures are taken from Ref. [227]. ....25

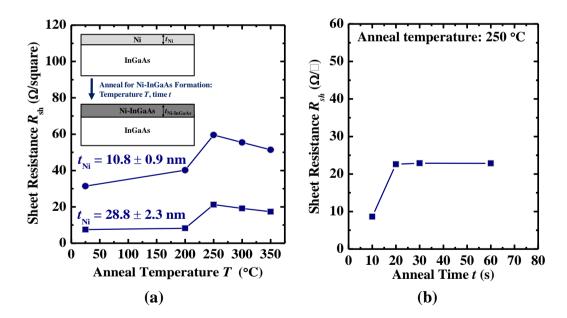

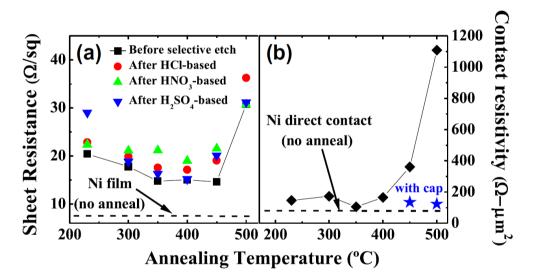

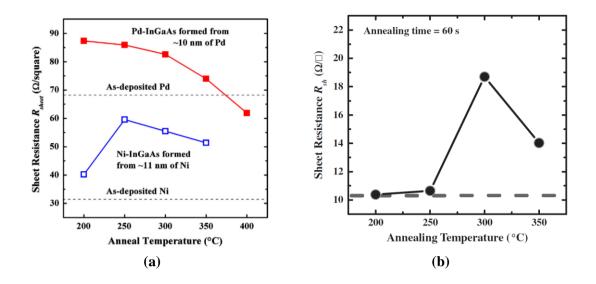

- **Fig. 2.8.** (a)  $R_S$  of Ni-InGaAs as a function of  $T_{anneal}$ . The samples were annealed for 5 min in vacuum.  $R_S$  before and after selective wet etching of unreacted metal is also plotted. (b)  $\rho_C$  of Ni-InGaAs as a function of  $T_{anneal}$  on samples with (blue stars) and without (black

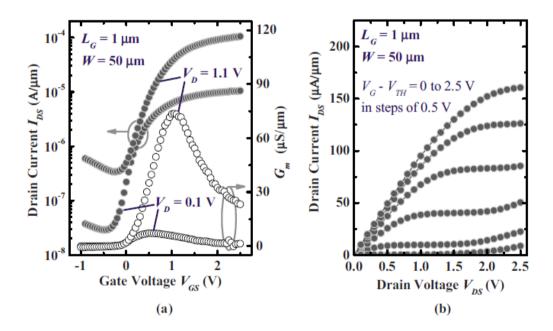

- **Fig. 2.11.** (a)  $I_{\rm D}$ - $V_{\rm GS}$  and  $G_{\rm M}$ - $V_{\rm GS}$  plot of an In<sub>0.7</sub>Ga<sub>0.3</sub>As N-MOSFET with selfaligned Ni-InGaAs S/D. The device with  $L_{\rm G} = 1 \ \mu m$  has an  $I_{\rm ON}$  of ~100  $\mu$ A/ $\mu$ m and peak  $G_{\rm M}$  of 74  $\mu$ S/ $\mu$ m at  $V_{\rm D} = 1.1$  V. (b)  $I_{\rm D}$ - $V_{\rm D}$ characteristics of the same transistor at various gate overdrives ( $V_{\rm GS}$ -  $V_{\rm T}$ ), from 0 V to 2.5 V. These figures are taken from Ref. [232]..30

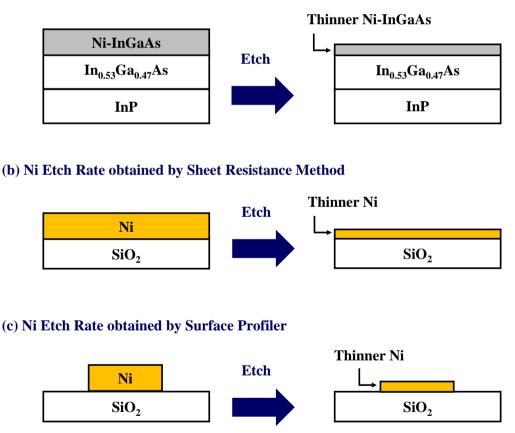

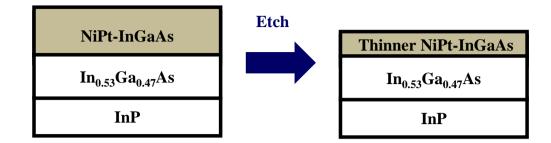

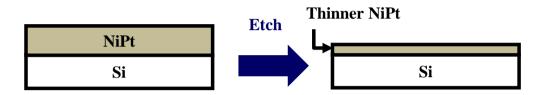

- Fig. 3.2. Schematic of the samples used for determining the etch rates of Ni-InGaAs and Ni; (a) Unpatterned or blanket sample comprising of Ni-InGaAs formed on In<sub>0.53</sub>Ga<sub>0.47</sub>As/InP substrate, (b) blanket sample

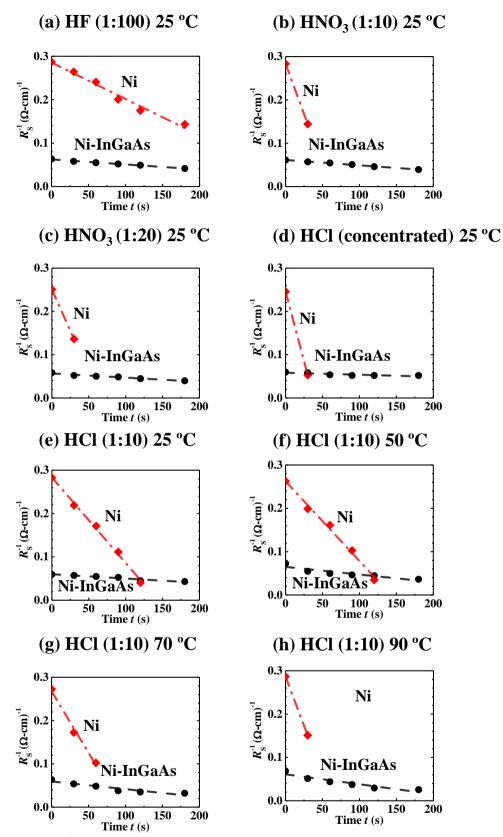

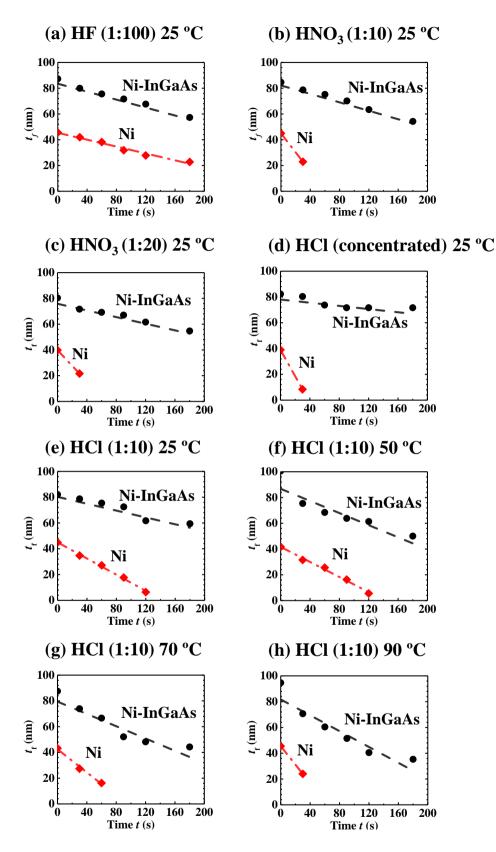

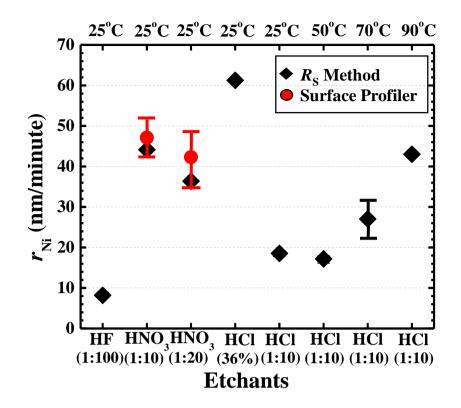

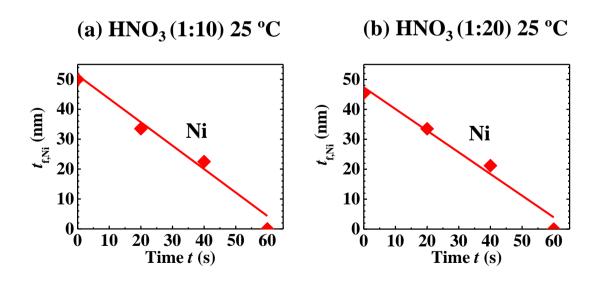

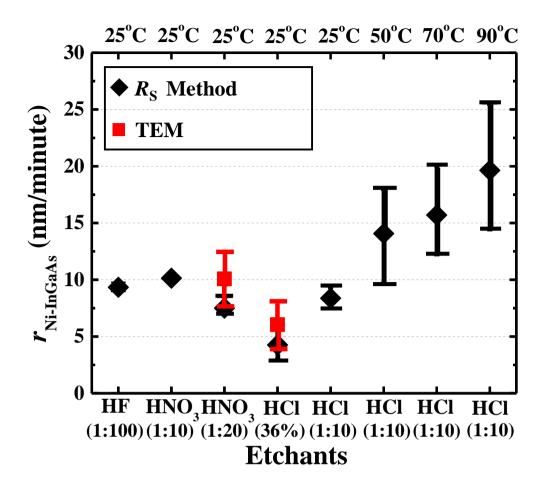

- Fig. 3.3. Rs<sup>-1</sup> versus time (t) plot for various etch chemistries: (a) HF:H<sub>2</sub>O (1:100), (b) HNO<sub>3</sub>:H<sub>2</sub>O (1:10), (c) HNO<sub>3</sub>:H<sub>2</sub>O (1:20), (d) HCl (concentrated), (e) HCl:H<sub>2</sub>O (1:10) 25 °C, (f) HCl:H<sub>2</sub>O (1:10) 50 °C, (g) HCl:H<sub>2</sub>O (1:10) 70 °C, (h) HCl:H<sub>2</sub>O (1:10) 90 °C. The R<sub>s</sub> increases with time indicating a decrease in the metal thickness. ...42

- Fig. 3.8. The etch rate of Ni-InGaAs in the various etch chemistries which are obtained from the  $R_{\rm S}$  method and from TEM images. HCl (concentrated) etches Ni-InGaAs the slowest. HNO<sub>3</sub>:H<sub>2</sub>O (1:10) etches Ni-InGaAs faster compared to HNO<sub>3</sub>:H<sub>2</sub>O (1:20). The etch

rate of Ni-InGaAs in HCl:H<sub>2</sub>O (1:10) at room temperature was low and it increased with higher temperatures. It was also observed that HF: H<sub>2</sub>O (1:100) etches Ni-InGaAs at a slow rate......47

- Fig. 3.10. Schematic of the samples used for determining the etch rates of NiPt-InGaAs and NiPt; (a) Blanket sample comprising of Ni-InGaAs formed on In<sub>0.53</sub>Ga<sub>0.47</sub>As/InP substrate, and (b) blanket sample comprising of NiPt deposited on a Si substrate......50

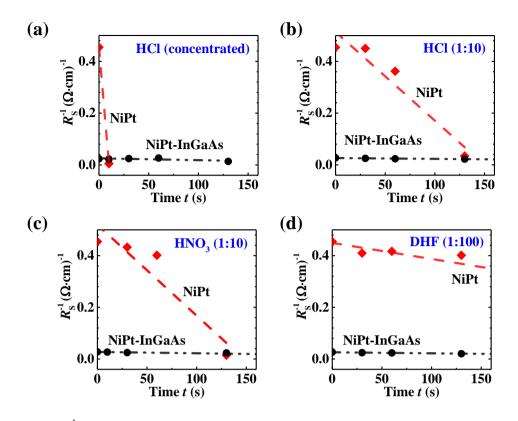

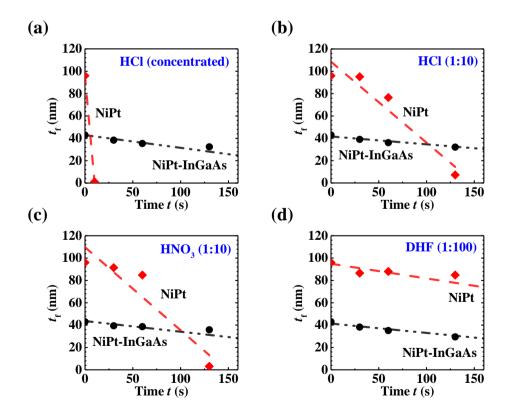

- Fig. 3.13.

$R_{\rm S}^{-1}$  versus time (t) plots for various etch chemistries: (a) HCl

(concentrated), (b) HCl:H<sub>2</sub>O (1:10), (c) HNO<sub>3</sub>:H<sub>2</sub>O (1:10), (d)

HF:H<sub>2</sub>O (1:100).

- **Fig. 3.16.** Comparison of etch selectivities between NiPt over NiPt-InGaAs and Ni over Ni-InGaAs using various etch chemistries. The incorporation

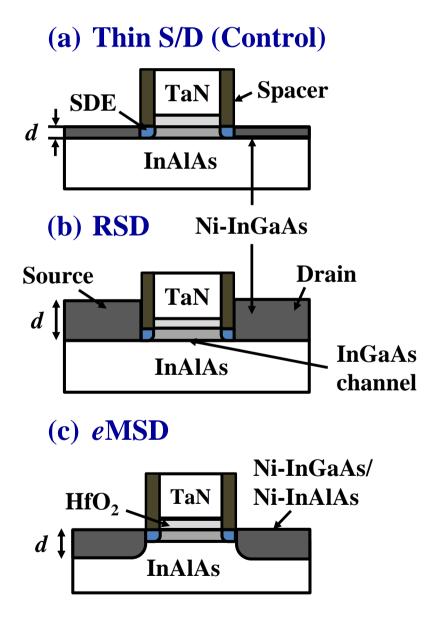

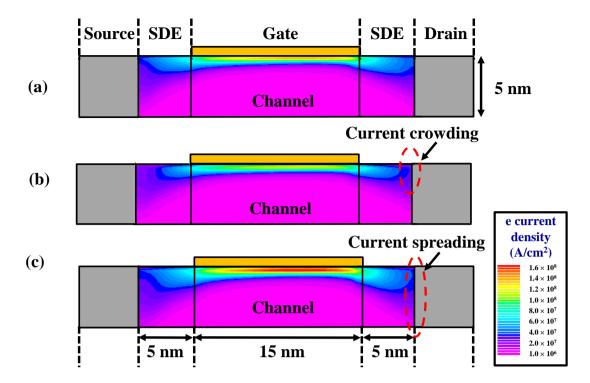

- **Fig. 4.1.** (a) UTB-FET with thin S/D suffers from a high  $R_{SD}$ . (b) It can be resolved by using a UTB-FET with a Raised S/D structure (RSD). However, this increases the number of process steps during device fabrication and increases the  $C_{GD}$ ; thus, reducing the switching speed of the transistor. (c) Both problems can be resolved using the UTB-FET with embedded metal S/D (*e*MSD). (d)  $C_{GD}$ - $R_{SD}$  of UTB-FETs. UTB-FET with *e*MSD provides a low  $R_{SD}$  without compromising  $C_{GD}$ .

- **Fig. 4.3.**  $R_S$  of Ni-InGaAs and Ni-InAlAs alloys formed using different annealing temperatures.  $R_S$  of both the alloys are comparable......61

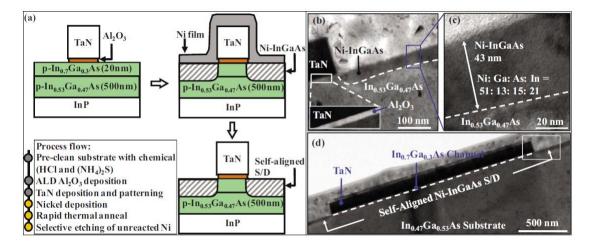

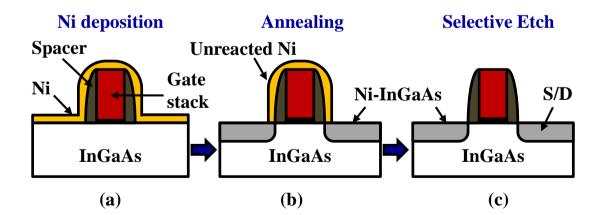

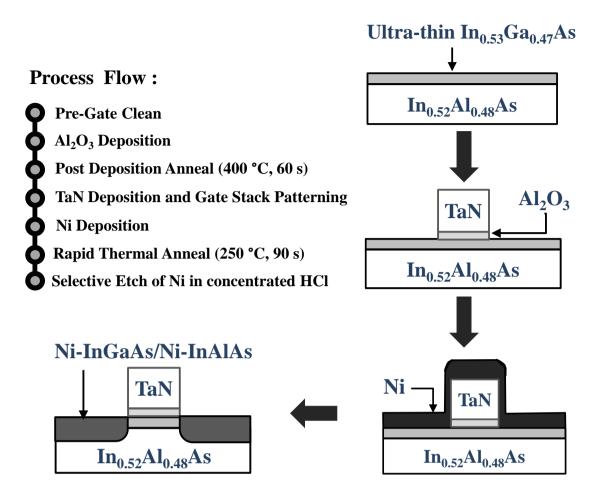

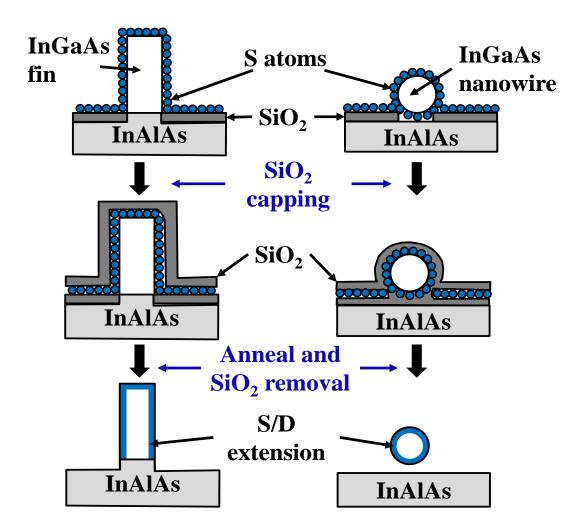

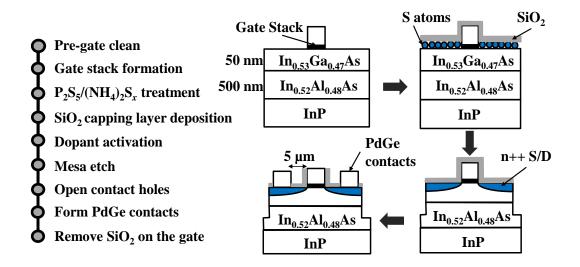

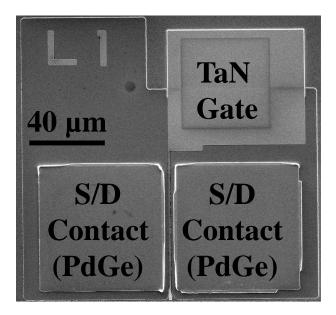

- Fig. 4.4. Process flow for the fabrication of an n-channel InGaAs UTB-FET with self-aligned eMSD. The S/D was formed by depositing ~35 nm of Ni, which was then annealed to form Ni-InGaAs/Ni-InAlAs eMSD.

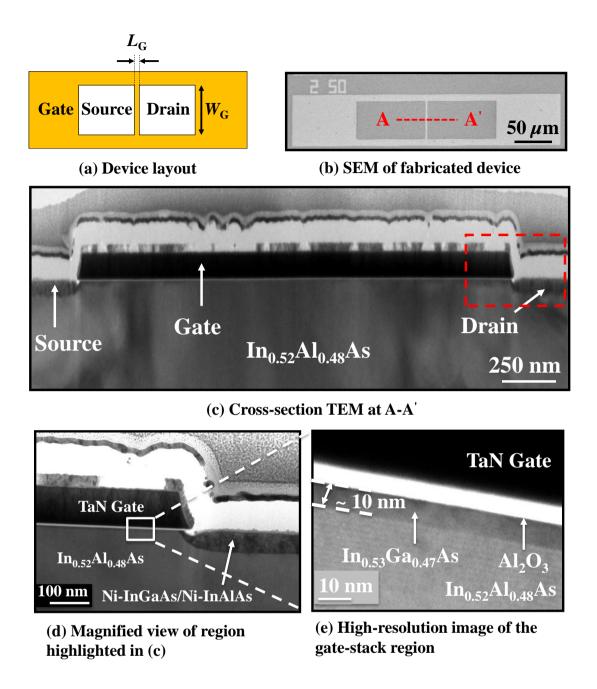

- Fig. 4.5. (a) Device layout, and (b) top-view SEM image of the fabricated UTB-FET. (c) The cross-sectional TEM image (along A-A') of the UTB-FET with self-aligned *e*MSD. (d) A magnified view of the gate and drain regions, and (e) an HR-TEM image of the TaN/Al<sub>2</sub>O<sub>3</sub>/InGaAs/InAlAs stack. The ultra-thin InGaAs channel

|            | layer was 10 nm thick and the Ni-InGaAs/Ni-InAlAs <i>e</i> MSD layer was ~65 nm thick                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

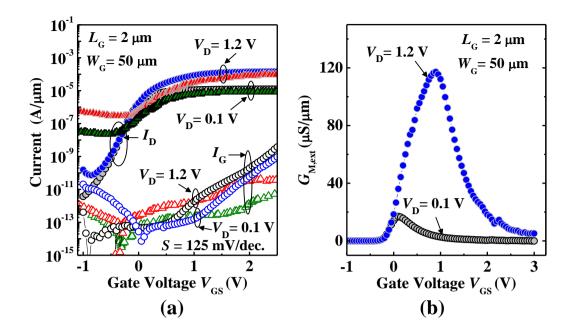

| Fig. 4.6.  | (a) $I_D$ , $I_G$ versus $V_{GS}$ for control device (triangles) and UTB-FET (circles), and (b) $G_{M,ext}$ - $V_{GS}$ curves of a UTB-FET with <i>e</i> MSD. $I_{ON}/I_{OFF}$ ratio of ~10 <sup>6</sup> and a peak $G_{M,ext}$ of 118 µS/µm at $V_D$ =1.2 V were obtained                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

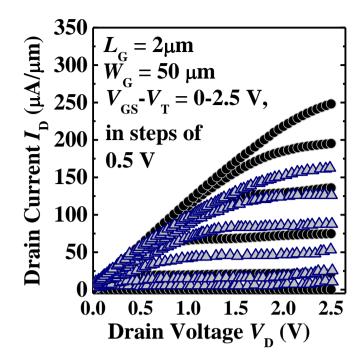

| Fig. 4.7.  | $I_{\rm D}$ - $V_{\rm D}$ plot for the control device (triangles) and UTB-FET with <i>e</i> MSD (circles). Gate overdrive ( $V_{\rm GS}$ - $V_{\rm T}$ ) was varied from 0 to 2.5 V in steps of 0.5 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

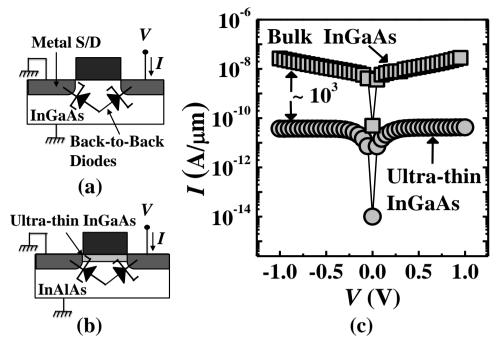

| Fig. 4.8.  | Schematics of back-to-back diodes formed on (a) bulk-InGaAs/InP,<br>and (b) on ultra-thin InGaAs/InAlAs <i>e</i> MSD layer. (c) <i>I-V</i> curves show<br>a ~10 <sup>3</sup> reduction in reverse current due to the presence of the InAlAs<br>barrier layer [Energy band gap ( $E_G$ ) = 1.48 eV]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

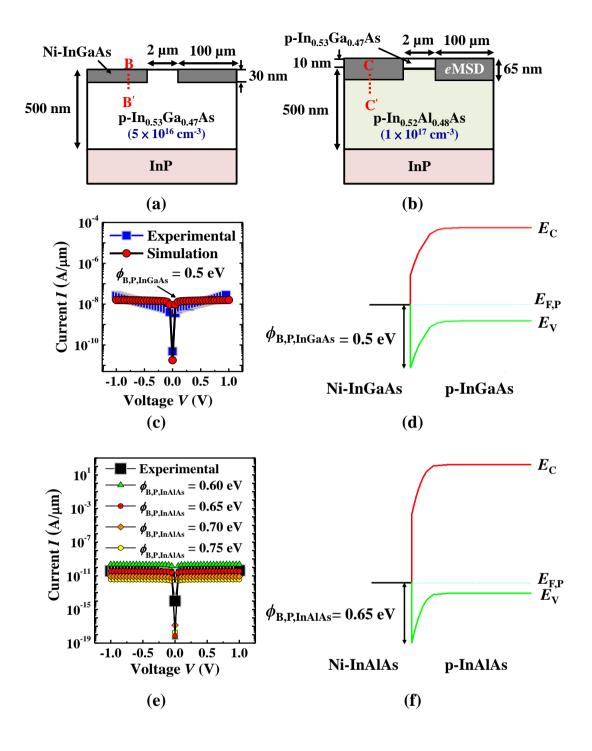

| Fig. 4.9.  | Schematic of back-to-back diodes structures on (a) bulk-InGaAs/InP,<br>and (b) on ultra-thin InGaAs with an InAlAs barrier layer on InP, used<br>for the TCAD simulation. (c) The simulated <i>I-V</i> curves for the bulk-<br>InGaAs/InP structure and (d) the corresponding energy band diagram<br>across B-B' (no voltage bias applied). <i>I-V</i> curves shows good<br>agreement with the experimental results for $\phi_{B,P,InGaAs} = 0.5$ eV. (e)<br>The simulated <i>I-V</i> curves for the ultra-thin InGaAs/InAlAs/InP<br>structure, and (f) the corresponding energy band diagram across C-C'<br>(no voltage bias applied). A $\phi_{B,P,InAlAs}$ of 0.65 eV was extracted by<br>matching the simulation results with the experimental results shown<br>in Fig. 4.8 (c) |

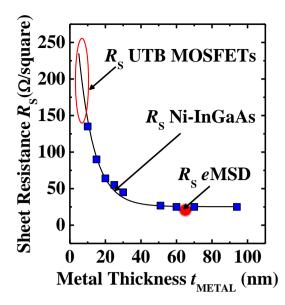

| Fig. 4.10. | $R_{\text{S}}$ - $t_{\text{METAL}}$ of UTB-FET with <i>e</i> MSD and Ni-InGaAs. The $R_{\text{S}}$ of the 65 nm thick <i>e</i> MSD was 20 $\Omega$ /square71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

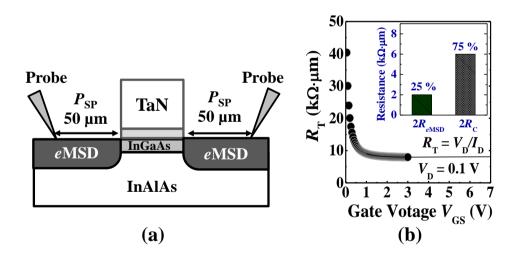

| Fig. 4.11. | (a) Schematic of the cross-section (A-A') of the device shown in Fig. 4.5 (b). The S/D probe spacing from the device channel ( $P_{\text{SP}}$ ) was ~50 $\mu$ m. (b) Plot of the total resistance ( $R_{\text{T}} = V_{\text{D}}/I_{\text{D}}$ ) as a function of $V_{\text{GS}}$ in the linear regime ( $V_{\text{D}} = 0.1$ V) of the same device as in Fig. 4.6. The components of $R_{\text{SD}}$ are shown in the inset of (b). It consists of the <i>e</i> MSD resistance ( $R_{\text{eMSD}}$ ) and the contact resistance ( $R_{\text{C}}$ ) between                                                                                                                                                                                                                        |

| Ni-InGaAs and the InGaAs channel. Their percentage contribution to |

|--------------------------------------------------------------------|

| $R_{\rm SD}$ is ~25 % and ~75 %, respectively                      |

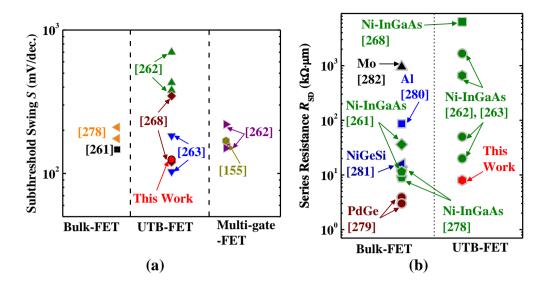

| Fig. 4.12. | Benchmarking (a) <i>S</i> of UTB-FET with <i>e</i> MSD, bulk-InGaAs N-MOSFETs with metal S/D, UTB-FETs with thin metallic S/D, and multi-gate FETs with metal S/D, and (b) $R_{SD}$ of InGaAs N-MOSFET with <i>e</i> MSD with reported $R_{SD}$ of bulk-InGaAs N-MOSFETs and UTB-FETs with thin metallic S/D                                            |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 4.13. | Schematics of the structures used for the 2D simulation: (a) UTB-<br>FET with thin S/D (control), (b) UTB-FET with RSD, and (c) UTB-<br>FET with <i>e</i> MSD                                                                                                                                                                                           |

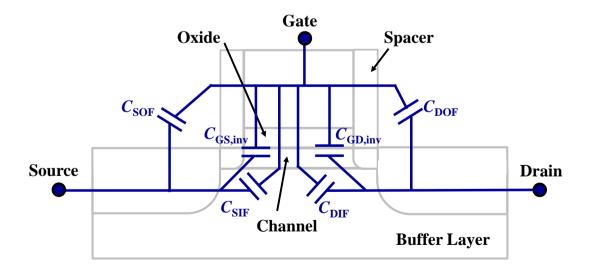

| Fig. 4.14. | Schematic showing the different capacitance components in a UTB-<br>FET                                                                                                                                                                                                                                                                                 |

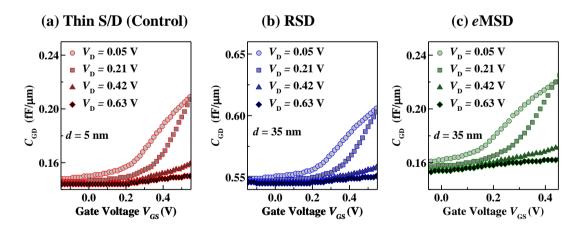

| Fig. 4.15. | $C_{GD}$ as a function of $V_{GS}$ for different $V_D$ in InGaAs UTB-FETs with<br>(a) thin S/D, (b) RSD, and (c) <i>e</i> MSD. The parasitic components can<br>be observed at low $V_{GS}$ where inversion layer in the channel is yet to<br>be formed. The RSD architecture results in a high parasitic<br>capacitance due to an increase in $C_{DOF}$ |

| Fig. 4.16. | $C_{\rm GD}$ as a function of $V_{\rm GD}$ is compared for the different S/D architectures. $C_{\rm GD}$ for devices with <i>e</i> MSD thicknesses are comparable to the control structure. $C_{\rm GD}$ increases with <i>d</i> for the RSD architecture due to higher $C_{\rm DOF}$                                                                   |

| Fig. 4.17. | Schematic showing the different resistance components in a UTB-<br>FET                                                                                                                                                                                                                                                                                  |

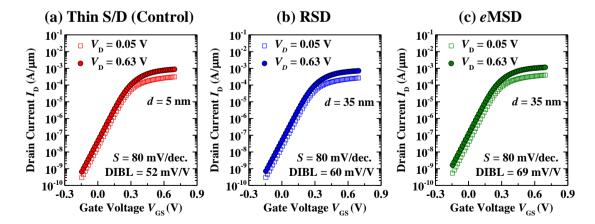

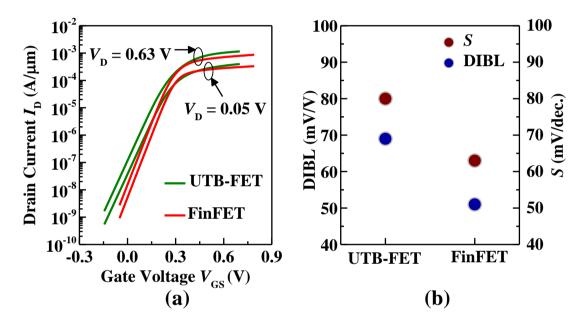

| Fig. 4.18. | $I_{\rm D}$ as a function of $V_{\rm GS}$ for different $V_{\rm D}$ in InGaAs UTB-FETs with (a) thin S/D, (b) RSD, and (c) eMSD. In the control sample, for $L_{\rm G}$ of 15 nm, $I_{\rm D}$ of ~0.9 mA/µm at $V_{\rm D}$ of 0.63 V was obtained. A higher DIBL was observed for the RSD and eMSD structures                                           |

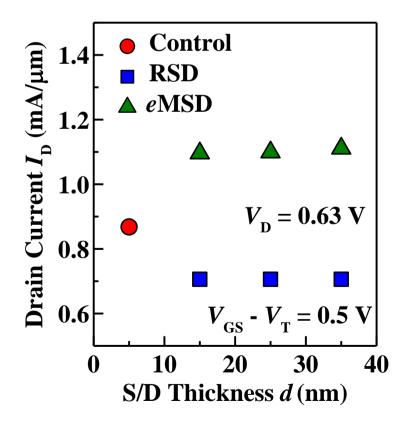

| Fig. 4.19. | $I_{\rm D}$ is compared with varying <i>d</i> . The comparison is done at a $V_{\rm GS}$ - $V_{\rm T}$ of 0.5 V due to DIBL effect in the <i>e</i> MSD structure                                                                                                                                                                                        |

| Fig. 4.20. | Current density contours ( $V_{GS} - V_T = 0.5V$ , $V_D = 0.63$ V) for (a) thin                                                                                                                                                                                                                                                                         |

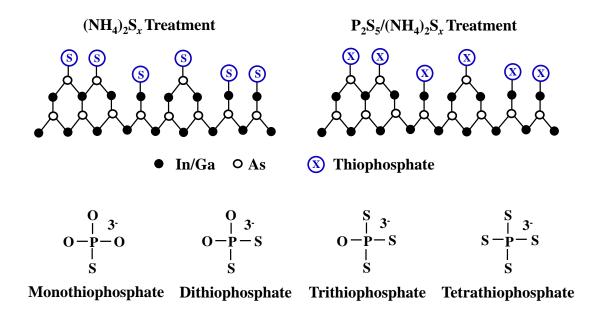

- Fig. 5.2. Schematic showing a (001) InGaAs surface after treatment with  $(NH_4)_2S_x$ , or  $P_2S_5/(NH_4)_2S_x$ . Hydrolysis of  $P_2S_5$  results in the

formation of various thiophosphates. These thiophosphates can react and form compounds on the InGaAs surface......90

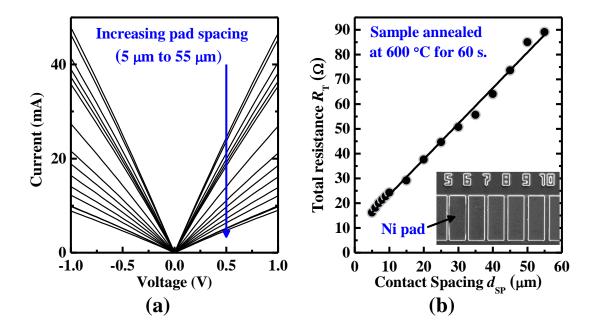

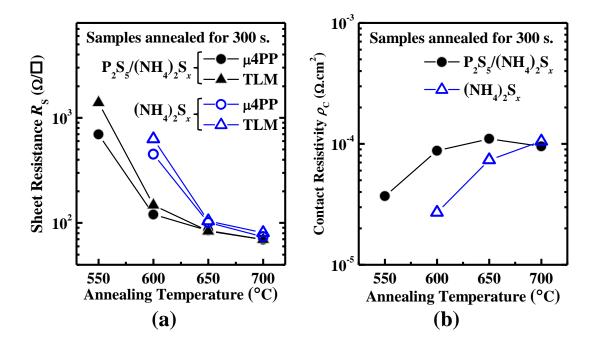

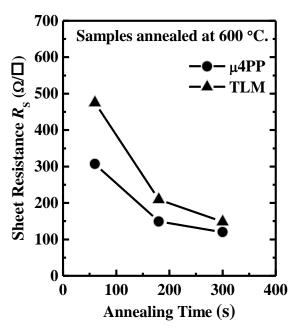

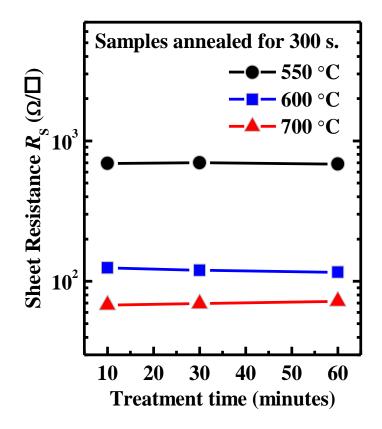

- Fig. 5.6. Sheet resistance  $R_S$  as a function of annealing time for samples treated with  $P_2S_5/(NH_4)_2S_x$  solution and annealed at 600 °C.  $R_S$  decreases as the annealing time for the dopant activation step is increased. .......96

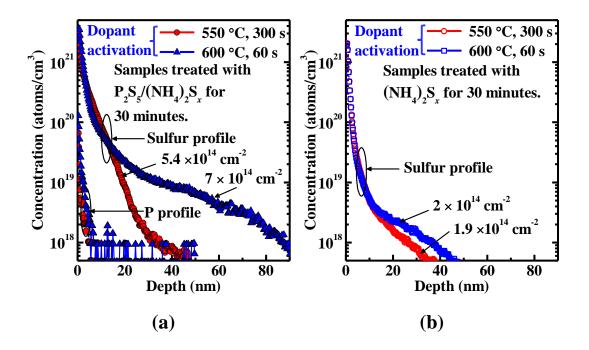

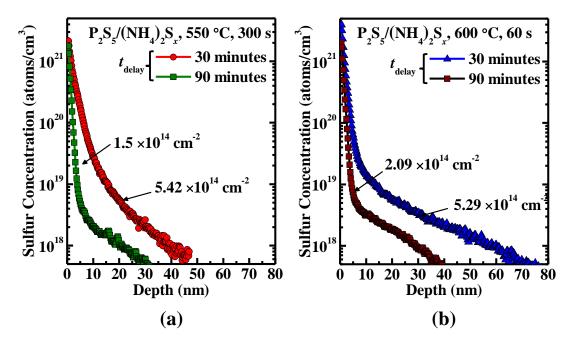

- **Fig. 5.8.** SIMS profiles of samples doped using (a)  $P_2S_5/(NH_4)_2S_x$  or (b)  $(NH_4)_2S_x$  solution. The samples treated with  $P_2S_5/(NH_4)_2S_x$  exhibit a higher sulfur dose than those treated with  $(NH_4)_2S_x$  for the same dopant activation conditions. A small amount of phosphorus (P) can

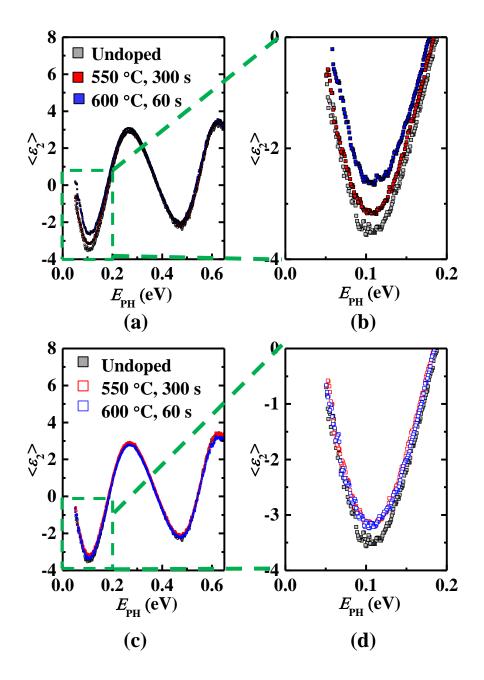

- **Fig. 5.11.** Imaginary part of the pseudo dielectric function  $\langle \varepsilon_2 \rangle$  obtained from SMLD samples. (a)  $\langle \varepsilon_2 \rangle$  from the P<sub>2</sub>S<sub>5</sub>/(NH<sub>4</sub>)<sub>2</sub>S<sub>x</sub> based samples for the entire energy range (0.05 0.65 eV), and (b) a magnified view of the energy range (0.05 0.2 eV) where the signals from the SMLD samples can be distinguished from the undoped sample. (c)  $\langle \varepsilon_2 \rangle$  from the (NH<sub>4</sub>)<sub>2</sub>S<sub>x</sub> based samples for the entire energy range (0.05 0.65 eV), and (d) a magnified view of the energy range (0.05 0.2 eV) where the signals from the signals from the signals from the undoped sample. (a)  $\langle \varepsilon_2 \rangle$  from the (NH<sub>4</sub>)<sub>2</sub>S<sub>x</sub> based samples for the entire energy range (0.05 0.65 eV), and (d) a magnified view of the energy range (0.05 0.2 eV) where the signals from the SMLD samples can be distinguished from the undoped sample. (a)  $\langle \varepsilon_2 \rangle$  from the undoped sample. (b)  $\langle \varepsilon_2 \rangle$  from the signal stress for the energy range (0.05 0.2 eV) where the signal stress for the energy range (0.05 0.2 eV) where the signal stress from the SMLD samples can be distinguished from the undoped sample. (c)  $\langle \varepsilon_2 \rangle$  from the undoped sample stress for the energy range (0.05 0.2 eV) where the signal stress from the SMLD samples can be distinguished from the undoped sample. (c)  $\langle \varepsilon_2 \rangle$  from the undoped sample. (c)  $\langle \varepsilon_2 \rangle$  from the undoped sample stress for the energy range (0.05 0.2 eV) where the signal stress from the SMLD samples can be distinguished from the undoped sample. (c)  $\langle \varepsilon_2 \rangle$  from the undoped sample stress from the undoped sample stress from the SMLD samples can be distinguished from the undoped sample. (c)  $\langle \varepsilon_2 \rangle$  from the undoped sample stress from the undoped stress from the undoped stress from the u

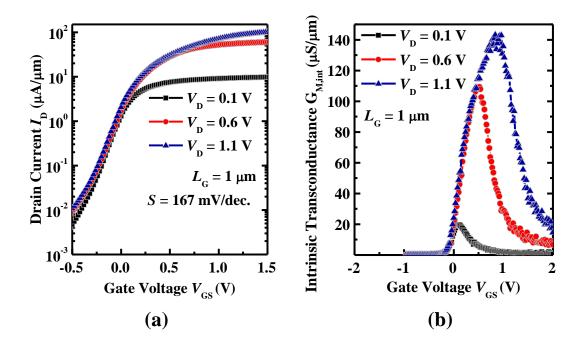

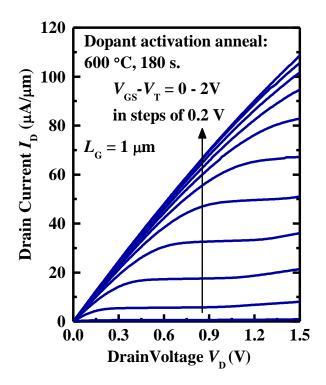

- **Fig. 5.14.** (a)  $I_{\rm D}$ - $V_{\rm GS}$ , and (b)  $G_{\rm M,int}$ - $V_{\rm GS}$  characteristics of the planar transistor shown in Fig. 5.13. The device has a reasonable subthreshold swing

# **List of Symbols**

| а, с                  | Lattice parameters                             |

|-----------------------|------------------------------------------------|

| $A^{*}$               | Richardson's constant                          |

| $A_{\mathrm{CHIP}}$   | Area of semiconductor chip                     |

| $A_{\mathrm{D}}$      | Area of diode                                  |

| $A_{ m eff}$          | Effective contact area                         |

| $A_{ m G}$            | Gate area                                      |

| $A_{ m pole}$         | Magnitude of the pole                          |

| $C_{\mathrm{DIF}}$    | Inner fringing capacitances at the drain side  |

| $C_{\rm DOF}$         | Outer fringing capacitances at the drain side  |

| Cellips               | Fitting parameter in the Drude model           |

| $C_{ m GD}$           | Gate-to-drain capacitance                      |

| $C_{ m GD,inv}$       | Inversion capacitance at the drain side        |

| $C_{ m GG}$           | Total gate capacitance                         |

| $C_{ m GS}$           | Gate-to-source capacitance                     |

| $C_{ m GS,inv}$       | Inversion capacitance at the source side       |

| $C_{\mathrm{InGaAs}}$ | InGaAs capacitance                             |

| $C_{ m OF}$           | Parasitic outer fringing capacitances          |

| Cox                   | Gate oxide capacitance                         |

| Cout                  | Output capacitance per transistor              |

| $C_{\mathrm{SIF}}$    | Inner fringing capacitances at the source side |

| $C_{\rm SOF}$         | Outer fringing capacitances at the source side |

| d                     | Thickness of the S/D                           |

| $D_{ m it}$           | Interface trap density                         |

| $d_{ m SP}$           | TLM contact spacing                            |

| $E_{ m C}$                   | Conduction band energy              |

|------------------------------|-------------------------------------|

| $E_{ m G}$                   | Energy band gap                     |

| $E_{ m F}$                   | Fermi energy                        |

| E <sub>P</sub>               | Plasmon energy                      |

| $E_{ m PH}$                  | Photon energy                       |

| $E_{ m pole}$                | Pole energy                         |

| $E_{ m V}$                   | Valence band energy                 |

| f                            | Clock frequency                     |

| $G_{\mathrm{D}}$             | Drain transconductance              |

| $G_{\mathrm{M}}$             | Transconductance                    |

| <i>G</i> <sub>M,ext</sub>    | Extrinsic transconductance          |

| $G_{ m M,int}$               | Intrinsic transconductance          |

| Ι                            | Current                             |

| ID                           | Drain current                       |

| I <sub>D,Sat</sub>           | Saturation drain current            |

| I <sub>G</sub>               | Gate leakage current                |

| ILEAK                        | Leakage current of the transistor   |

| Ioff                         | Off-state current                   |

| Ion                          | On-state current                    |

| Is                           | Diode saturation current            |

| Iss                          | Source-to-drain sub-surface leakage |

| Is2D                         | Direct source-to-drain leakage      |

| Κ                            | Boltzmann constant                  |

| k                            | Dimensionless scaling factor        |

| $k_{d1}, k_{d2}, and k_{d3}$ | Equilibrium rate constants          |

| Lc                           | Contact length                      |

| L <sub>G</sub>    | Gate length                                             |

|-------------------|---------------------------------------------------------|

| $L_{ m Ni}$       | Nickel contact pad length                               |

| $L_{\rm SDE}$     | Source-drain extension length                           |

| L <sub>S/D</sub>  | Lateral diffused length of the deep source-drain region |

| $L_{\mathrm{T}}$  | Transfer length                                         |

| $m^*$             | Effective mass of carriers                              |

| me*               | Electron effective mass                                 |

| n                 | Electron carrier concentration                          |

| Ν                 | Doping concentration                                    |

| $N_{ m A}$        | P-type doping concentration                             |

| N <sub>D</sub>    | N-type doping concentration                             |

| $N_{ m S,Source}$ | Carrier concentration near the source edge              |

| $N_{\mathrm{T}}$  | Total number of transistors in a chip                   |

| р                 | Hole carrier concentration                              |

| P <sub>CHIP</sub> | Power consumption per chip                              |

| $P_{\mathrm{D}}$  | Dynamic power                                           |

| $p_{O2}$          | Partial pressure of O <sub>2</sub> in the solution      |

| Ps                | Static power                                            |

| $P_{\mathrm{SP}}$ | Probe spacing from the channel                          |

| <i>q</i>          | Elementary charge                                       |

| $Q_G$             | Gate charge                                             |

| $Q_{ m inv}$      | Inversion charge density                                |

| r                 | Etch rate                                               |

| r <sub>c</sub>    | Dealessottaring scafficient                             |

|                   | Backscattering coefficient                              |

| r <sub>Ni</sub>   | Etch rate of Nickel                                     |

| R <sub>C</sub>                 | Contact resistance                                                                                     |

|--------------------------------|--------------------------------------------------------------------------------------------------------|

| $R_{\rm C,eff}$                | Effective contact resistance                                                                           |

| <i>R</i> <sub>CH</sub>         | Channel resistance                                                                                     |

| R <sub>DRAIN</sub>             | Drain resistance                                                                                       |

| $R_{e\rm MSD}$                 | Resistance of the eMSD regions                                                                         |

| $R_{ m METAL}$                 | Metal contact resistance                                                                               |

| R <sub>S</sub>                 | Sheet resistance                                                                                       |

| R <sub>SD</sub>                | Source-drain series resistance                                                                         |

| $R_{ m S/D}$                   | Deep S/D resistance                                                                                    |

| $R_{\rm SDE}$                  | Source-drain extension resistance                                                                      |

| $R_{\mathrm{S},e\mathrm{MSD}}$ | Sheet resistance of the <i>e</i> MSD                                                                   |

| R <sub>SOURCE</sub>            | Source resistance                                                                                      |

| R <sub>T</sub>                 | Total resistance                                                                                       |

| S                              | Subthreshold swing                                                                                     |

| Т                              | Temperature                                                                                            |

| t                              | Time                                                                                                   |

| Tanneal                        | Annealing temperature                                                                                  |

| tanneal                        | Annealing time                                                                                         |

| t <sub>delay</sub>             | Time delay between $P_2S_5/(NH_4)_2S_x$ treatment and deposition of the SiO <sub>2</sub> capping layer |

| t <sub>f</sub>                 | Thickness of film                                                                                      |

| t <sub>f,Ni</sub>              | Thickness of nickel film                                                                               |

| <i>t</i> f,Ni-InGaAs           | Thickness of Ni-InGaAs film                                                                            |

| T <sub>InGaAs</sub>            | Thickness of InGaAs                                                                                    |

| <i>t</i> METAL                 | Metal thickness                                                                                        |

| t <sub>Ni</sub>                | Nickel thickness                                                                                       |

| T <sub>n-InGaAs</sub>          | Thickness of n-type doped InGaAs                                                                       |

| T <sub>OX</sub>    | Oxide thickness                              |

|--------------------|----------------------------------------------|

| $T_{ m P}$         | Propagation delay of a CMOS inverter         |

| V                  | Voltage                                      |

| V <sub>D</sub>     | Drain voltage                                |

| $V_{ m DD}$        | Supply voltage                               |

| $V_{ m GS}$        | Gate voltage                                 |

| Vinj               | Injection velocity                           |

| $V_{\mathrm{T}}$   | Threshold voltage                            |

| $V_{ m T,lin}$     | Linear threshold voltage                     |

| V <sub>T,Sat</sub> | Saturation threshold voltage                 |

| W <sub>C</sub>     | Contact width                                |

| $W_{ m G}$         | Gate width                                   |

| $W_{ m Ni}$        | Nickel contact pad width                     |

| x                  | Indium composition                           |

| $X_{ m JSDE}$      | Junction depth of the source-drain extension |

| $X_{ m JS/D}$      | Junction depth of the deep source-drain      |

| α                  | Dimensionless scaling factor                 |

| $\mathcal{E}_0$    | Permittivity of free space                   |

| Es                 | Permittivity of the semiconductor            |

| κ                  | Relative permittivity                        |

| $\mu_{ m e}$       | Electron mobility                            |

| $\mu_{	ext{eff}}$  | Effective channel mobility                   |

| $\mu_{ m h}$       | Hole mobility                                |

| ħ                  | Planck's constant                            |

| ρ                  | Bulk resistivity                             |

| $ ho_{ m C}$       | Contact resistivity                          |

| $ ho_{ m InGaAs}$         | Resistivity of InGaAs                            |  |

|---------------------------|--------------------------------------------------|--|

| $ ho_{ m n-InGaAs}$       | Resistivity of n-type doped InGaAs               |  |

| $ ho_{ m Ni}$             | Resistivity of nickel                            |  |

| $ ho_{	ext{Ni-InGaAs}}$   | Resistivity of Ni-InGaAs                         |  |

| $ ho_{ m NiPt}$           | Resistivity of nickel platinum                   |  |

| $ ho_{	ext{NiPt-InGaAs}}$ | Resistivity of NiPt-InGaAs                       |  |

| $ ho_{ m SDE}$            | Source-drain extension region resistivity        |  |

| $ ho_{ m S/D}$            | Resistivity of the deep source-drain region      |  |

| $\phi_{ m B}$             | Effective barrier height                         |  |

| $\phi_{ m B,N}$           | Effective electron barrier height                |  |

| $\phi_{\mathrm{B,P}}$     | Effective hole barrier height                    |  |

| $\phi$ B,P,InAlAs         | Schottky barrier height of Ni-InAlAs on p-InAlAs |  |

| $\phi$ B,P,InGaAs         | Schottky barrier height of Ni-InAlAs on p-InGaAs |  |

| η                         | Diode ideality factor                            |  |

| $\mu_{ m max}$            | Maximum mobility                                 |  |

| $\mu_{ m min}$            | Minimum mobility                                 |  |

| τ <sub>e</sub>            | Carrier relaxation time                          |  |

| <82>                      | Imaginary part of the pseudo dielectric function |  |

# Chapter 1

### Introduction

#### 1.1 Background

Modern complementary metal-oxide-semiconductor (CMOS) logic circuits are designed using n-channel and p-channel metal-oxide-semiconductor field-effect transistors, henceforth denoted as N-MOSFETs and P-MOSFETs, respectively. CMOS technology is predominantly silicon (Si) based as the Si semiconductor material is readily available and cheap. Since the early 1970s, the continuous success of semiconductor companies has heavily depended on the 'down-scaling' of the metaloxide-semiconductor field-effect transistor (MOSFET). Over the years, transistor dimensions have been scaled down to realize high-performance MOSFETs with high ON-state current ( $I_{ON}$ ). In addition, dimension scaling increases the packing density (number of transistors per unit area), which in turn reduces cost per transistor. Furthermore, down-scaling the supply voltage ( $V_{DD}$ ) reduces power consumption in circuits, which in turn reduces packaging and cooling costs.

Intel's latest processor, code-named 'Ivy Bridge' at the 22-nm technology node, packs about 1.4 billion transistors in a 160 mm<sup>2</sup> area [1]. A transistor behaves like a switch in logic circuits. It is expected to switch at extremely fast speeds while consuming very low energy. Intel's Ivy Bridge runs 4000 times faster and consumes 5000 times lesser energy compared to its first processor, the '4004' [2]. Furthermore, the cost per transistor has reduced by a factor of about 50,000 in the last 40 years [2].

Down-scaling of  $V_{DD}$  is one of the main challenges currently faced by Si CMOS technology [3]. As mobility enhancement in Si MOSFETs reaches its limits, further scaling of  $V_{DD}$  compromises the switching speed of the transistor. Therefore, new materials, processes, and device architectures have to be developed to overcome the physical scaling limits of conventional Si MOSFETs.

#### **1.2 Scaling Challenges of Transistors**

The scaling of transistors in CMOS technology has followed Moore's law, which states that the number of transistors in integrated circuits (ICs) doubles roughly every two years [4]. However, it is essential that the circuit performance and power consumption of the chip do not deteriorate as the device dimensions are scaled down. In 1970, Dennard *et al.* [5] proposed a scaling methodology to enhance integrated circuit performance without increasing power consumption (Table 1.1). Power consumption per chip ( $P_{CHIP}$ ) can be expressed as follows [6]:

$$P_{\text{CHIP}} \propto f \cdot C_{\text{OUT}} \cdot V_{\text{DD}}^2 \cdot N_{\text{T}} + V_{\text{DD}} \cdot I_{\text{LEAK}} \cdot N_{\text{T}}, \qquad (1.1)$$

where *f* is the frequency of signal change that scales by a factor of 1/k,  $C_{OUT}$  is the total output capacitance per transistor which scales by a factor of *k*,  $N_T$  is the total number of transistors ( $N_T \propto \alpha/k^2$ ), and  $I_{LEAK}$  is the leakage current of the transistor. As  $I_{LEAK}$  is negligible in devices with large gate length ( $L_G$ ),  $P_{CHIP}$  is dominated by the first term in Equation (1.1). This means that if the chip area ( $A_{CHIP}$ ) is constant (i.e.  $\alpha = 1$ ), then  $N_T \propto 1/k^2$  and  $P_{CHIP}$  remains constant. However, in recent years, power consumption has not been reduced adequately through  $V_{DD}$  scaling and  $P_{CHIP}$  has increased by ~10<sup>5</sup> times [6]. Furthermore,  $I_{LEAK}$  becomes significant as  $L_G$  is scaled down aggressively. The following subsections describe the background information on the various effects that limit transistor scaling.

| Circuit or device parameters         | Symbol                             | Scaling factor |

|--------------------------------------|------------------------------------|----------------|

| Gate length                          | $L_{ m G}$                         | k              |

| Gate width                           | $W_{ m G}$                         | k              |

| Gate oxide thickness                 | $T_{\rm OX}$                       | k              |

| Supply voltage                       | $V_{ m DD}$                        | k              |

| Drive current in saturation regime   | I <sub>D,Sat</sub>                 | k              |

| $I_{\rm D,Sat}$ per unit $W_{\rm G}$ | $I_{\mathrm{D,Sat}}/\mu\mathrm{m}$ | 1              |

| Gate oxide capacitance               | Cox                                | k              |

| Propagation delay                    | $T_{ m P}$                         | k              |

| Chip area                            | $A_{\mathrm{CHIP}}$                | α              |

| Number of transistors                | $N_{\mathrm{T}}$                   | $lpha/k^2$     |

| Power consumption per chip           | $P_{\mathrm{CHIP}}$                | α              |

**Table 1.1.**Scaling trends to improve integrated circuit performance [5].

\*  $\alpha$  and k are dimensionless scaling factors.

#### **1.2.1 Leakage currents**

Quantum-mechanical tunneling of carriers through energy barriers [i.e. channel-gate dielectric barrier, source/drain (S/D)-to-substrate barrier, and S/D-to-channel barrier] in highly scaled MOSFETs results in leakage currents, which in turn increases power dissipation. These leakage currents are: (i) gate leakage ( $I_G$ ) by tunneling mechanism, (ii) source-to-drain sub-surface leakage ( $I_{SS}$ ), and (iii) direct source-to-drain leakage ( $I_{S2D}$ ) by tunneling of carriers through the channel barrier.

In Si CMOS technology, as the device dimensions are scaled down, the silicon dioxide (SiO<sub>2</sub>) gate dielectric thickness ( $T_{OX}$ ) was reduced to achieve good electrostatic gate control over the channel region. Reducing  $T_{OX}$  leads to a higher gate oxide capacitance ( $C_{OX}$ ) which can be expressed in the following equation:

$$C_{\rm OX} = \frac{\varepsilon_0 \cdot \kappa \cdot A_{\rm G}}{T_{\rm OX}}, \qquad (1.2)$$

where  $\varepsilon_0$  is the permittivity of free space,  $\kappa$  is the relative permittivity of the dielectric, and  $A_G$  ( $L_G \cdot W_G$ ) is the area of the gate. However, the decrease in  $T_{OX}$  results in an increase in  $I_G$  due to the tunneling of electrons or holes from the channel to the gate (through the gate dielectric) for N-MOSFETs and P-MOSFETs, respectively. A higher  $C_{OX}$  can also be achieved by increasing  $\kappa$  of the gate dielectric [7], which can be achieved by using Si oxynitride composites [8]-[11] or high- $\kappa$  dielectrics [12]-[26].

A second significant source of leakage is the  $I_{SS}$ .  $I_{SS}$  is a result of poor gate control of the electrostatic potential at regions between the source and the drain that are far away from the dielectric-channel interface. As  $L_G$  is scaled down, the drain voltage ( $V_D$ ) pulls down the potential barrier near the source region resulting in  $I_{SS}$  [27]. 3D structures such as fin field effect transistors (FinFETs) or nanowire transistors have been proposed to minimize  $I_{SS}$  [28]-[41]. The wrap around gate architectures in these devices provide excellent electrostatic gate control even at the sub-surface regions, thus, reducing  $I_{SS}$ .

The third leakage current component is  $I_{S2D}$ . This component becomes significant as the  $L_G$  becomes less than 10 nm (at room temperature) [42]. This extra tunneling current tends to be smaller than the other leakage components at such device dimensions [3].

#### **1.2.2 Random dopant fluctuation**

In the current Si CMOS technology, doping concentration (*N*) in regions such as the channel or S/D of MOSFETs, are well controlled by the conventional beam-line ion implantation and annealing process. However, this process cannot accurately control the position of the dopants, which results in spatial fluctuations in the local doping concentration. This leads to a device-to-device variation in the threshold voltage ( $V_T$ ) of the MOSFETs. As  $L_G$  is scaled down to sub-22 nm, the  $V_T$  is eventually controlled by 100 dopant atoms or less, which makes it difficult to keep the  $V_T$  variation low.

This effect can be reduced by moving the dopants away from the channel surface using retrograde doping [43]-[46]. Another approach is to use an undoped channel and tuning the  $V_{\rm T}$  by varying the work function of the metal gate [47]-[49] or using multiple-gate architectures [50]-[52].

#### **1.2.3 Power constrained scaling**

There are two main types of power dissipation in a CMOS circuit: (a) dynamic and (b) static. In CMOS technology, dynamic power ( $P_D$ ) is a result of the switching action during logic operations.  $P_D$  is a strong function of  $V_{DD}$  as shown below [53]:

$$P_{\rm D} \propto C_{\rm OUT} \cdot V_{\rm DD}^{2} \cdot f \,. \tag{1.3}$$

$P_{\rm D}$  can be minimized by reducing the  $V_{\rm DD}$ . The other component is the static power ( $P_{\rm S}$ ), which manifests during the holding of the logic states between the switching operations [53]:

$$P_{\rm S} \propto I_{\rm LEAK} \cdot V_{\rm DD}$$

(1.4)

$I_{\text{LEAK}}$  is a combination of the different leakage currents described in Section 1.2.1.  $P_{\text{S}}$  is unavoidable and becomes a dominant factor as the device dimensions are scaled down. Decreasing  $I_{\text{LEAK}}$  by the various methods explained earlier in Section 1.2.1, reduces  $P_{\text{S}}$ .

#### **1.3 Motivation for Using III-V Materials**

The carrier transport in transistors with extremely small  $L_G$  is typically in the quasi-ballistic or ballistic regime. The saturation drain current ( $I_{D,Sat}$ ) of such a transistor is limited by the thermal injection velocity ( $v_{inj}$ ) and is given by [54]-[55]:

$$I_{\rm D,Sat} = q \cdot N_{\rm S,Source} \cdot v_{\rm inj} \cdot \left(\frac{1 - r_{\rm C}}{1 + r_{\rm C}}\right) = C_{\rm OX} \cdot W_{\rm G} \cdot v_{\rm inj} \cdot \left(\frac{1 - r_{\rm C}}{1 + r_{\rm C}}\right) \cdot \left(V_{\rm GS} - V_{\rm T}\right), \tag{1.5}$$

where q is the elementary charge (1.6×10<sup>-19</sup> C),  $N_{S,Source}$  is the carrier concentration near the source edge,  $r_c$  is the backscattering coefficient which is a measure of the number of carriers that are scattered back to the source, and  $V_{GS}$  is the gate voltage. The injection velocity and  $N_{S,Source}$  are a function of the effective mass of the charge carriers in the channel material [56]-[57]. Materials with a small effective mass along the transport direction (high  $v_{inj}$ ) and a large effective mass [i.e. high density of states (DOS)] in the transverse direction are desired to achieve high  $I_{D,Sat}$  in MOSFETs.

Since the last decade, strain techniques have been employed in Si MOSFET to boost its channel mobility [58]-[68] and achieve high  $I_{D,Sat}$ . However, Si technology is reaching its limits in terms of mobility enhancement using strain engineering. One method to attain high channel mobility, and therefore  $I_{D,Sat}$  in MOSFETs, is to replace the Si channel with high-mobility materials that have high intrinsic carrier mobilities and low effective mass for the carriers. III-V compound semiconductors are promising

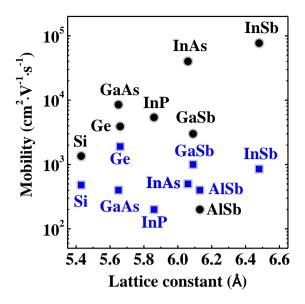

**Fig. 1.1.** Plot of the electron (black circles) and hole mobilities (blue squares) at 300 K, for Si, germanium (Ge) and various III-V compound semiconductors.

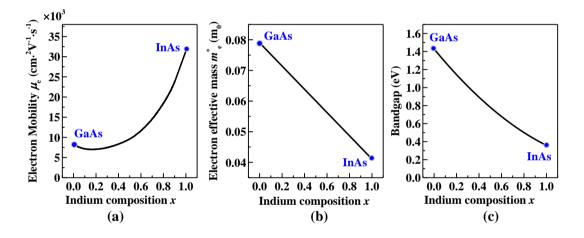

**Fig. 1.2.** (a) Electron mobility ( $\mu_e$ ) versus composition *x* for In<sub>*x*</sub>Ga<sub>1-*x*</sub>As.  $\mu_e$  increases with higher indium composition. (b) Electron effective mass  $m_e^*$  versus composition *x* for In<sub>*x*</sub>Ga<sub>1-*x*</sub>As.  $m_e^*$  decreases with increasing indium composition, leading to higher  $\mu_e$  in (a). (c) Band gap  $E_G$  versus composition *x* for In<sub>*x*</sub>Ga<sub>1-*x*</sub>As. In<sub>*x*</sub>Ga<sub>1-*x*</sub>As offers a wide range of  $E_G$  from 0.36 eV to 1.42 eV.

candidates for potential use as channel materials in N-MOSFETs, due to their high electron mobility ( $\mu_e$ ) [Fig. 1.1] [69].

In addition, III-V MOSFETs can be fabricated using the conventional "top-down" lithography processes currently used in Si CMOS. Furthermore, III-V compound semiconductors provide a wide selection of band gaps and materials. Hence, III-V

heterostructures allow greater flexibility in band gap engineering and device design for both high-performance and low-power applications, compared to Si-based heterostructures [such as Si/silicon germanium (SiGe)].

Due to these advantages, III-V materials have been studied extensively (including various arsenides and antimonides) [70]-[95], for potential application in CMOS technology. Indium gallium arsenide (InGaAs) is a promising alternative for possible use as the channel material of N-MOSFETs [95]. The  $\mu_e$  of InGaAs, as a function of the indium composition (*x*), is plotted in Fig. 1.2 (a) [96].  $\mu_e$  increases with increasing *x* due to a reduction in the electron effective mass ( $m_e^*$ ) [97], as shown in Fig. 1.2 (b). The minima observed in Fig 1.2 (a), in the region of  $x \sim 0.1$  to 0.2, can be attributed to alloy scattering [96]. In addition, InGaAs offers a wide range of band gaps from 0.36 eV [indium arsenide (InAs) with x = 1] to 1.42 eV [gallium arsenide (GaAs) with x = 0] as illustrated in Fig. 1.2 (c) [98].

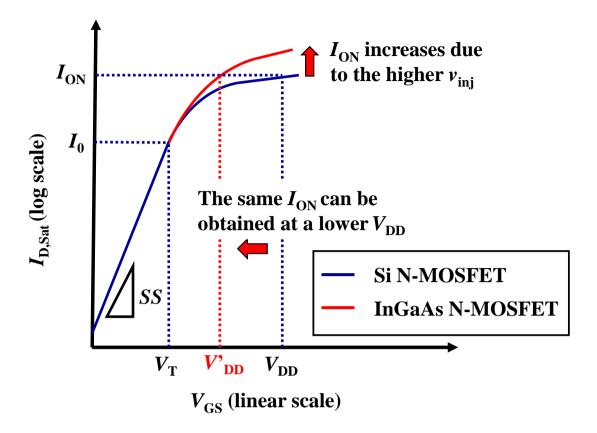

According to the International Technology Roadmap for Semiconductors (ITRS), InGaAs could be used in CMOS technology as early as 2018 [99]. Fig 1.3 illustrates  $I_{D,Sat}$  versus  $V_{GS}$  of an InGaAs N-MOSFET and a Si N-MOSFET. Although the DOS in InGaAs is lower than that in Si, the higher  $v_{inj}$  of InGaAs results in a higher  $I_{ON}$  at the same off-current ( $I_{OFF}$ ) [at a fixed gate overdrive ( $V_{GS} - V_T$ )] compared to the Si N-MOSFET [69]. The high  $I_{ON}$  in turn reduces the propagation delay ( $T_P$ ) of the CMOS inverter [100]:

$$T_{\rm P} \approx \frac{C_{\rm L} \cdot V_{\rm DD}}{4} \cdot \left(\frac{1}{I_{\rm ON,N}} + \frac{1}{I_{\rm ON,P}}\right),\tag{1.6}$$

where  $C_L$  is the total load capacitance of the CMOS inverter.  $I_{ON,N}$  and  $I_{ON,P}$  are the ON-state current of the N-MOSFET and the P-MOSFET, respectively. Furthermore, by replacing the channel of the N-MOSFET with InGaAs, the supply voltage can be

**Fig. 1.3.** Comparison of  $I_{D,Sat}$ - $V_{GS}$  between a Si N-MOSFET (blue solid curve) and an InGaAs N-MOSFET (red solid curve). A higher  $I_{ON}$  can be achieved for the InGaAs N-MOSFET at the same gate overdrive ( $V_{GS}$ - $V_T$ ). Furthermore, using an InGaAs N-MOSFET allows the down-scaling of  $V_{DD}$  without compromising  $I_{ON}$ . The InGaAs and Si N-MOSFETs are assumed to have the same subthreshold swing (*S*).

reduced ( $V_{DD}$ ) to maintain the same  $I_{ON}$  and  $I_{OFF}$ . Since these devices have a low  $P_D$  (at a fixed switching frequency) [Equation (1.3)], they can be used in low operating power (LOP) applications.

# 1.4 Challenges for III-V CMOS Logic

Several challenges need to be overcome before Si can be replaced with a new channel material at future technology nodes. If III-V materials are introduced in the sub-10 nm technology nodes, they will have to outperform the Si alternative. In addition, the III-V transistors must be realized in a cost-efficient manner and should

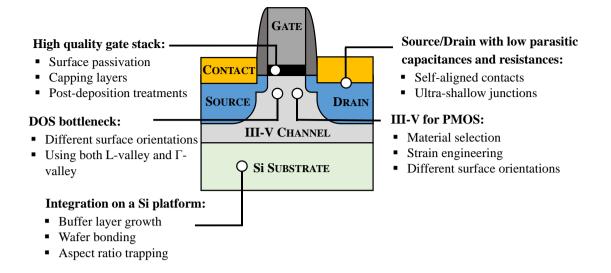

**Fig. 1.4.** Schematic illustrating the key technical challenges faced in the realization and integration of high mobility III-V channel MOSFET on Si substrates for future logic applications.

be scalable over a few technology nodes. Some of the problems that need to be addressed include: (i) formation of a high-quality gate stack (with minimal trap density), (ii) achieving low gate-to-drain capacitances ( $C_{GD}$ ) and S/D resistances ( $R_{SD}$ ), (iii) realizing high-performance III-V P-MOSFETs, (iv) integration of III-V transistors on a Si platform, and (v) "DOS bottleneck". Fig. 1.4 illustrates these key challenges. These technical challenges are described in the following subsections.

## **1.4.1 Realization of high-quality gate stack**

The gate stack of a MOSFET typically consists of a metal gate and a high- $\kappa$  dielectric layer. The gate stack is an important part of a transistor as it controls its switching behavior. A high-quality interface with minimal defects between the gate-dielectric and the channel is necessary for the gate to function properly. Hence, the dielectric must be free of trapped charges and other defects, have a smooth interface with minimal interfacial imperfections, and have high thermal stability. The native oxides of III-V have very poor electrical properties in comparison with that of Si. A high interface state trap density ( $D_{it}$ ) between the gate dielectric, and the channel

interface results in 'Fermi level pinning' [101]. This phenomenon, which is common in III-V materials, inhibits the ability of the gate to modulate the surface potential of the channel [101]. Moreover, the high surface roughness at the dielectric channel interface,  $D_{it}$ , and the defects or traps in the gate dielectric severely degrades the mobility of carriers in the channel. The mobility degradation can be attributed to mechanisms such as phonon, coulomb, and surface roughness scattering [102]-[103]. Therefore, a high-quality dielectric-channel interface is paramount in fully utilizing the advantages of III-V materials over Si in terms of mobility and  $v_{inj}$ .

In 2003, GaAs MOSFET with aluminum oxide (Al<sub>2</sub>O<sub>3</sub>) deposited using atomic layer deposition (ALD) was demonstrated [104]. During ALD, native oxide on the GaAs surface was removed in the early stages of deposition [105]-[107], which was followed by the immediate deposition of the high- $\kappa$  dielectric (i.e. Al<sub>2</sub>O<sub>3</sub>). Subsequently, this ALD process was demonstrated on InGaAs [108], InAs [109], and indium phosphide (InP) [110] MOSFETs with promising results. Several techniques to passivate III-V surfaces have been investigated to improve the quality of gate stacks deposited on III-V materials in order to reduce the amount and influence of dielectric and interface defects. These include (i) surface cleaning prior to deposition [111]-[112], (ii) inserting interfacial layers between the dielectric and the channel [113]-[114], (iii) post-deposition treatments [111], [115], (iv) alternate high- $\kappa$  dielectrics [116]-[117], (v) changing the surface orientation of the III-V material [118]-[120], and (vi) using a buried-channel device structure [121]-[122]. The best results have been obtained in an InGaAs buried-channel structure, where the gate stack consists of an InP capping layer, and an ALD  $TaSiO_x$  dielectric [121]. The performance of this InGaAs N-MOSFET exceeded that of the state-of-the-art Si N-MOSFET [69].

## 1.4.2 Integration on a Si platform

The integration of III-V transistors on a Si substrate is a key challenge that needs to be addressed. Integration is essential as it decreases the production cost due to the existing mature Si processing technology. Various integration techniques have been proposed including (a) buffer layer growth [73], [123]-[124], (b) III-V-on-insulator (III-V-OI) [125]-[127], and (c) aspect ratio trapping (ART) [128]-[133].

Direct growth of III-V materials on Si is extremely challenging due to their large lattice mismatch. The abrupt lattice transition can be resolved by employing a buffer layer such as  $In_xAl_{1-x}As$  or  $Al_xGa_{1-x}As$ , where the lattice constant is gradually increased from that of Si to the lattice of the desired III-V material. The misfit dislocations and defects are confined in the buffer layer, allowing the growth of defect-free III-V layers that are fully relaxed or slightly strained. Successful integration of  $In_{0.7}Ga_{0.3}As$  and  $In_{0.53}Ga_{0.47}As$  MOSFETs have been demonstrated on Si by molecular beam epitaxy (MBE) [121] and metal organic chemical vapor deposition (MOCVD) [124] techniques, respectively. However, the buffer layer thickness which is typically around 1  $\mu$ m has to be drastically reduced to ensure the feasibility of this approach. A thin buffer layer is essential because it requires shorter growth time. A shorter growth time increases the throughput during the fabrication process, which in turn reduces cost of production.

Another way to integrate III-V on Si is by the layer transfer of the desired III-V material onto a Si substrate covered by a dielectric such as SiO<sub>2</sub> or Al<sub>2</sub>O<sub>3</sub>, which is similar to the well-established silicon-on-insulator (SOI) technology. The desired III-V layer grown on a donor wafer is transferred to an oxide-covered Si substrate by direct wafer bonding and etch back process [125], or by epitaxial layer transfer [126]-[127]. Similar to SOI, the III-V-OI layer can be either relaxed or strained [134].

However, the main challenge for this approach is that it requires expensive sacrificial donor wafers. For example, to produce III-V-OI on a 12 inch Si wafer, the III-V layers need to be grown on a 12 inch donor wafer, which is not only challenging, but also expensive.

Recently, a promising integration approach called ART was introduced which allows direct growth of III-V material on Si without the need of a thick buffer layer [131]. In this technique, the III-V materials are grown in high-aspect-ratio SiO<sub>2</sub> trenches on Si. The dislocations formed during the growth of the III-V materials on Si (induced by large lattice mismatch) are terminated on the SiO<sub>2</sub> sidewalls. Hence, the material that grows out of the trench is free of dislocations and can be used for device fabrication. Ge, GaAs and InP films have been grown using ART [128]-[133]. ART combined with epitaxial lateral overgrowth (ELO) produces uniform films with low defect density [131]. GaAs MOSFETs have been demonstrated using ART-ELO [128].

Although there are several promising integration approaches, detailed studies on the defect density and solutions to minimize these defects have not been explored. Furthermore, achieving both N-MOSFETs and P-MOSFETs with different channel materials and lattice constants on a same planar surface will be extremely challenging. These critical issues needs to be addressed in the near future.

## **1.4.3 III-V P-MOSFETs**

There is a large imbalance between  $\mu_e$  and hole mobility ( $\mu_h$ ) in III-V materials, as seen in Fig. 1.1. There is not a single material with both  $\mu_e$  and  $\mu_h$  above 5000 cm<sup>2</sup>·V<sup>-1</sup>·s<sup>-1</sup> and 1500 cm<sup>2</sup>·V<sup>-1</sup>·s<sup>-1</sup>, respectively. In addition,  $\mu_h$  is significantly lower than  $\mu_e$ , which results in a lower  $I_{ON}$  for the P-MOSFET compared to the N-MOSFET. Therefore, a future where III-V N-MOSFETs and P-MOSFETs, made of different materials with different lattice constants, seems inevitable. A  $\mu_h$  of ~1500 cm<sup>2</sup>·V<sup>-1</sup>·s<sup>-1</sup> in indium gallium antimonide (InGaSb) [135], ~ 1300 cm<sup>2</sup>·V<sup>-1</sup>·s<sup>-1</sup> in gallium antimonide (GaSb) [136], and ~1,200 cm<sup>2</sup>·V<sup>-1</sup>·s<sup>-1</sup> in indium antimonide (InSb) [137] have been achieved. These are now the most promising candidates for channel materials in III-V P-MOSFETs. Uniaxial strain has been used in the channel of Si P-MOSFETs to boost their performance to match that of the N-MOSFET [138]. This approach can be explored for III-V semiconductor materials [139]-[141]. III-V P-MOSFETs using GaAs [142], InGaAs [143], GaSb [144], and InGaSb [144] have been demonstrated. However, their performance still lags behind that of the III-V N-MOSFETs. Currently, Ge P-MOSFET technology [145], which is more mature, has the advantage over III-V P-MOSFETs.

## 1.4.4 Source/Drain regions with low C<sub>GD</sub> and R<sub>SD</sub>

Low  $C_{GD}$  and  $R_{SD}$  are vital to achieve transistors with high  $I_{ON}$  and short  $T_{P}$ .  $C_{GD}$  is slightly higher due to the higher permittivity of the III-V materials over Si (about 10 % higher for In<sub>0.53</sub>Ga<sub>0.47</sub>As). Moreover, the device structure has a significant impact on  $C_{GD}$ . Parasitic outer fringing capacitances ( $C_{OF}$ ), associated with the gate sidewalls, become dominant as the devices scale down [138]. For instance, introducing raised S/D architectures increases  $C_{OF}$ , as the proximity between the S/D and the gate sidewall reduces. Similarly, high  $R_{SD}$  is a significant concern at future CMOS technology nodes. The channel resistance ( $R_{CH}$ ) in III-V MOSFETs decreases significantly as the  $L_G$  scales down aggressively. Therefore, the  $I_{ON}$  is eventually limited by  $R_{SD}$ .  $R_{SD}$  becomes more critical in advanced device structures such as FinFETs [74]-[75] and nanowire transistors [146]-[149].

A self-aligned S/D architecture can be used to reduce  $R_{SD}$ . In this scheme, the contacts are formed without an optical alignment to the gate. Self-alignment reduces

the distance between the gate and the contact, thus reducing  $R_{SD}$ . Self-aligned contacts have been successfully demonstrated on III-V HEMTs with promising results [150]-[151]. The resistivity of the S/D regions has to be small to reduce  $R_{SD}$ . Compared to Si MOSFETs, a lower  $R_{SD}$  can be achieved with InGaAs as the S/D material. Although the active n-type doping that can be achieved in InGaAs (mid-10<sup>19</sup> cm<sup>-3</sup>) is lower than that of Si (mid-10<sup>20</sup> cm<sup>-3</sup>), a lower resistivity can be attained due to the much higher  $\mu_e$ [> 1000 cm<sup>2</sup>·V<sup>-1</sup>·s<sup>-1</sup> (at room temperature)] [152] in InGaAs compared to Si

Furthermore, a very low Ohmic contact resistance ( $R_C$ ) is required between the contact metal and the highly n-type doped S/D regions. A low contact resistivity ( $\rho_c$ ) of ~1×10<sup>-8</sup>  $\Omega$ ·cm<sup>2</sup> on n-type In<sub>0.53</sub>Ga<sub>0.47</sub>As has been shown using *in situ* deposited molybdenum (Mo) contacts [153]-[154]. Hence, Mo is a good candidate for non-self-aligned contacts in InGaAs N-MOSFETs. However, for self-aligned contacts on InGaAs, the lowest  $\rho_c$  was obtained for nickel-indium gallium arsenide (Ni-InGaAs) metallic contacts (~1×10<sup>-6</sup>  $\Omega$ ·cm<sup>2</sup>) [155]-[156]. The  $\rho_c$  of Ni-InGaAs needs to be reduced further to compete with the *in situ* Mo contacts.

## 1.4.5 Density of States (DOS) Bottleneck

As mentioned in Section 1.3, when III-V channel materials are introduced at future technology nodes, MOSFETs will be operating in the quasi-ballistic or ballistic regime. At such extremely scaled device dimensions,  $I_{D,Sat}$  will depend on  $v_{inj}$  and DOS [Equation 1.5]. Although the small transport mass of the charge carriers in III-V materials leads to a high  $v_{inj}$ , they have low DOS in the  $\Gamma$ -valley. The low DOS will decrease the inversion charge ( $Q_{inv}$ ) in the channel of a MOSFET (at a given  $V_{GS}$ ), which will reduce  $I_{D,Sat}$ . This is commonly known as the "DOS bottleneck" [157]. The key to realizing high-performance III-V MOSFETs at sub-10 nm technology nodes is to increase the DOS while maintaining a high-enough  $v_{inj}$ . The DOS bottleneck can be overcome by changing the surface orientations of the III-V materials and using the L-valley along with the  $\Gamma$ -valley [158]-[162].

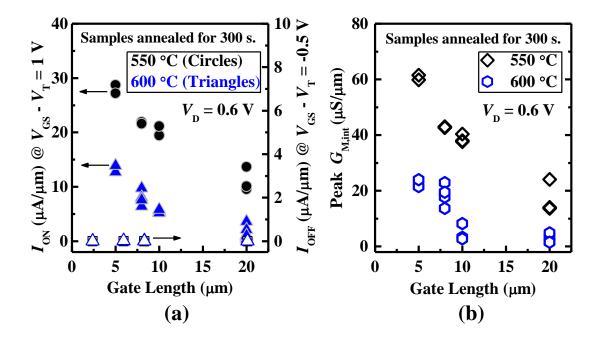

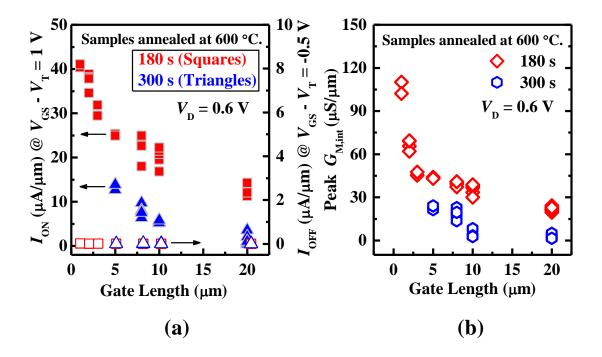

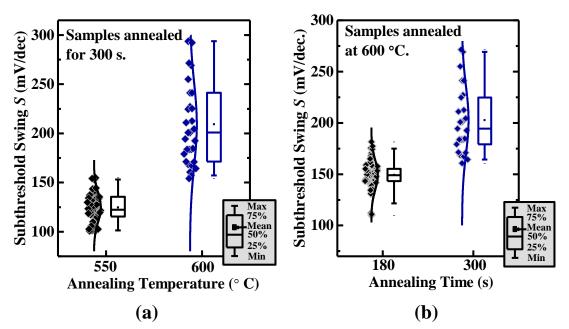

## **1.5** Objective and Organization of Thesis