## NONUNIFORMLY SAMPLED DIGITAL SIGNAL PROCESSING FOR LOW-POWER BIOMEDICAL APPLICATIONS

HONG YIBIN

NATIONAL UNIVERSITY OF SINGAPORE

## NONUNIFORMLY SAMPLED DIGITAL SIGNAL PROCESSING FOR LOW-POWER BIOMEDICAL APPLICATIONS

HONG YIBIN (B.Eng. (Hons.), NUS)

## A THESIS SUBMITTED

### FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

## DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING

### NATIONAL UNIVERSITY OF SINGAPORE

### DECLARATION

I hereby declare that this thesis is my original work and it has been written by me in its entirety.

I have duly acknowledged all the sources of information which have been used in the thesis.

This thesis has also not been submitted for any degree in any university previously.

Hong Yibin

#### ACKNOWLEDGEMENT

I would like to express my deepest gratitude towards my supervisor Professor Lian Yong, who gave me the opportunity to conduct cutting-edge research in this challenging and exciting new field. His patient guidance, insightful advice and continuous encouragement played a vital part in my progress and accomplishments. Being his student, I also benefited tremendously from his vast knowledge, clear vision and profound wisdom.

My sincere appreciation also goes to Dr. Xu Yong Ping and Dr. Yang Zhi for their valuable comments during my qualifying exams and inspiring discussions throughout the course of my study. Helps and suggestions from them have ensured the road to my destination was far less bumpy than it could have been.

I also feel truly grateful to all my lab-mates and team members from both the Signal Processing and VLSI lab as well as the Bioelectronics Lab. To name but a few, Dr. Liew Wen-Sin, Dr. Tan Jun, Mr. Xu Xiaoyuan, Dr. Zou Xiaodan, Mr. Chacko John Deepu, Dr. Zhang Jinghua, Dr. Yang Zhenglin, Mr. Zhang Xiaoyang, Mr. Wang Lei, Mr. Zhang Zhe, Mr. Li Yong Fu, Dr. Mahmood Khayatzadeh, Mr. Xue Chao, Mr. Li Ti and Mr. Zhang Daren, their kind help and cheerful support over the years have certainly been indispensable to me.

Last but most importantly, I am deeply indebted to my parents, Mr. Hong Chengrong and Mrs. Xu Deping, as well as my girlfriend Xue Fei, whose unconditional love and selfless care have always been my source of courage and strength to conquer the challenges and stand the pressure during those hard times along the journey. I dedicate this thesis as a humble gift to them.

## TABLE OF CONTENTS

| Declarationi                                           |

|--------------------------------------------------------|

| Acknowledgementiii                                     |

| Table of Contentsv                                     |

| Summaryix                                              |

| List of Figures xiii                                   |

| List of Tablesxxi                                      |

| List of Abbreviations xxiii                            |

| CHAPTER 1 Introduction                                 |

| 1.1 Motivation1                                        |

| 1.2 Background                                         |

| 1.3Research Contributions8                             |

| 1.4 Organization of the Thesis10                       |

| CHAPTER 2 Conventional Uniform DSP                     |

| 2.1 Theories                                           |

| CHAPTER 3 Nonuniform Sampling and Uniform Conversion21 |

| 3.1 Uniform DSP vs. Nonuniform DSP21                   |

| 3.2 Level-Crossing Sampling                            |

| 3.2.1 Concept                                          |

| 3.2.   | 2 Quantization Scheme                            | 5 |

|--------|--------------------------------------------------|---|

| 3.2.   | 3 Hysteresis                                     | 5 |

| 3.2.   | 4 Simulation with Real ECG Signals28             | 3 |

| 3.3    | Interpolation                                    | 1 |

| 3.3.   | 1 Comparison of Interpolation Methods            | 1 |

| 3.3.   | 2 Implementation of Linear Interpolator          | 5 |

| 3.4    | Digital Filtering                                | ) |

| CHAPTI | ER 4 Continuous-Time DSP                         | 5 |

| 4.1    | Introduction                                     | 5 |

| 4.2    | Matlab Simulation                                | ) |

| 4.3    | Quantitative Analysis of Quantization Distortion | 5 |

| 4.4    | Variable-Resolution Quantizing Scheme            | ) |

| 4.5    | Asynchronous Delta Modulation                    | 3 |

| 4.6    | Benefits and Drawbacks of CT DSP Systems         | 5 |

| CHAPTI | ER 5 Memristor-Based Timing Storage Circuit      | ) |

| 5.1    | The Memory Effect of Memristors                  | ) |

| 5.2    | Sandglass Analogy75                              | 5 |

| 5.3    | Memristor Models                                 | 3 |

| 5.4    | Circuit Implementation                           | ) |

| 5.5    | Practical Considerations                         | 1 |

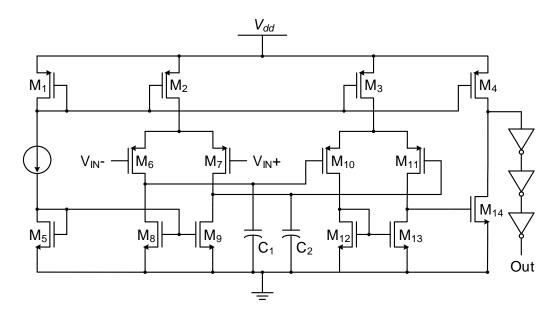

| 5.6 Con   | nparator Design                                        |

|-----------|--------------------------------------------------------|

| CHAPTER 6 | Memristor-Based CT Digital Filters91                   |

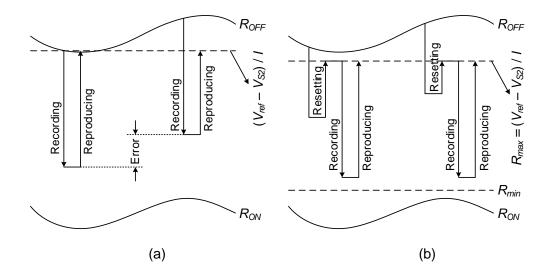

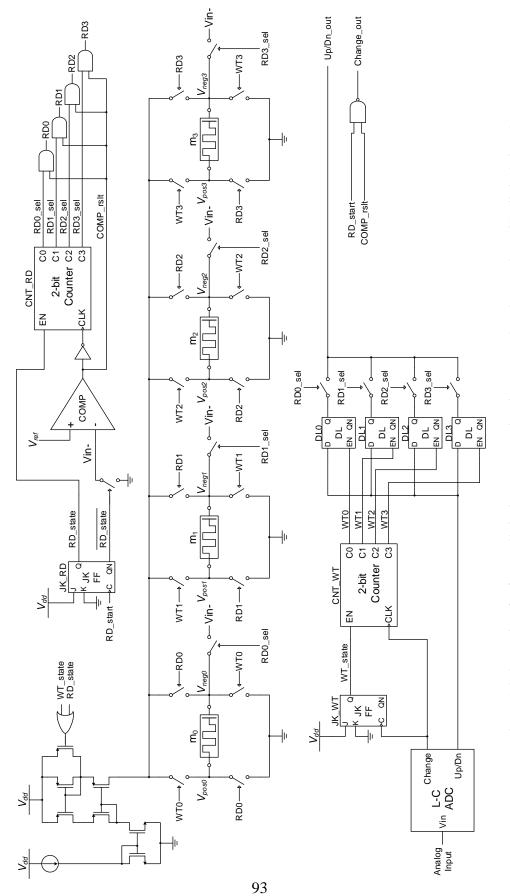

| 6.1 Rec   | ording and Reproducing CT Digital Signals91            |

| 6.1.1     | Timing Storage Cell Integration91                      |

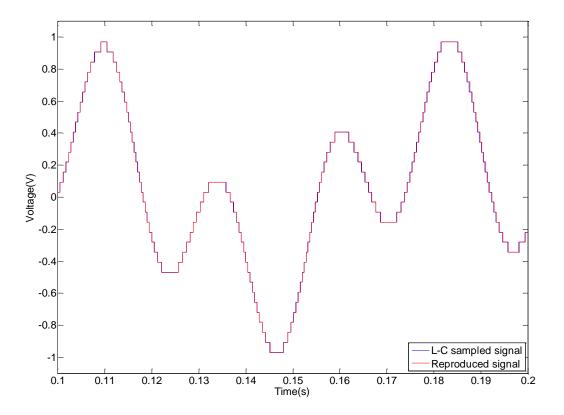

| 6.1.2     | Sinusoidal Signals96                                   |

| 6.1.3     | Biomedical Signals97                                   |

| 6.2 CT    | Digital Filters100                                     |

| 6.2.1     | Memristor-Based Delay Blocks                           |

| 6.2.2     | CT FIR Low-Pass Filter                                 |

| 6.2.3     | CT FIR S-G Filter                                      |

| CHAPTER 7 | CT FIR Filters with Frequency Response Masking121      |

| 7.1 Free  | quency Response Masking in Conventional FIR Filters121 |

| 7.2 Free  | quency Response Masking in CT FIR Filters128           |

| 7.2.1     | Overall structure                                      |

| 7.2.2     | Frequency response                                     |

| 7.2.3     | Accumulator Design                                     |

| 7.2.4     | Adder/Subtractor Design136                             |

| 7.2.5     | Delta Modulator Design                                 |

| 7.2.6     | Cascading CT FIR Filters with Delta Modulators151      |

| 7.2.7     | Simulation Results                                     |

| CHAPTER 8 | Conclusion and Future Work15 | 7 |

|-----------|------------------------------|---|

| 8.1 Cor   | nclusion15                   | 7 |

| 8.2 Fut   | ure Work15                   | 9 |

| REFERENCE | ES16                         | 1 |

#### SUMMARY

"It always seems impossible until it's done." - Nelson Mandela

The concept of preventive healthcare systems has attracted increasing attention in recent years, wherein the health condition of each individual is to be monitored in real time by wearable or implantable devices. In cases when a symptom is detected in its early stage, immediate treatments can be made before the situation worsens, increasing the chances of healing with reduced cost.

The biggest challenge in designing such monitoring devices is their battery life, as frequent replacement of the batteries would be highly intolerable considering the wearable or implantable nature of these devices. Energy harvesting techniques can be a solution to achieving uninterrupted monitoring in continuous time, wherein the devices would be powered primarily using energy harvested from human bodies, such as heat and body movements. However, the energy can be gained from these sources are very limited in amount, which poses a very stringent requirement on the power consumption of such devices.

Conventional digital signal processing (DSP) systems take samples from analog inputs periodically without considering their statistical properties. For biomedical signals, fast changes only occur in brief moments while most of the time the signal varies slowly. Processing such sporadically-varying signals using the conventional approach gives rise to a large number of samples that carry redundant information, wasting power not only in the Analog to Digital Converter (ADC), but also in the subsequent digital signal processor (DSP). New signal processing approaches with better energy efficiency for biomedical applications were thus investigated in this work.

With its event-driven nature, level-crossing sampling is well suited for digitizing biomedical signals with burst-type waveforms. However, conventional DSP techniques cannot be directly applied to level-crossing sampled data, as they are not uniformly spaced in time. Based on a study conducted to compare different interpolation methods, a new approach to convert signals sampled using level-crossing analog to digital conversion (ADC) back into uniform format using linear interpolation is proposed. The choices of various design parameters including level-crossing sampling resolution, interpolation frequency and interpolation resolution are examined to achieve a good balance between signal quality and power consumption. Significant energy saving is achievable from the reduction in sampling rate and filter order as compared to a conventional uniform DSP system.

To further improve the energy efficiency of this processing scheme by making fully use of the statistical properties of biomedical signals, a new class of systems called continuous-time (CT) DSP systems have been investigated. Operating in continuous time and discrete amplitude, CT DSP combines the best attributes of both conventional analog signal processing (ASP) and conventional DSP. On one hand, quantized amplitude allows signal processing that involves only '0's and '1's, giving rise to the benefit of noise immunity and programmability. On the other hand, it does not suffer from aliasing by operating in continuous time. More importantly, its signal-dependent sampling rate also enables power saving both in the ADC and in the DSP for slowly-varying portions of the input, making it a perfect match for biomedical signals.

One major drawback of CT DSP however, is that the processed results cannot be directly saved due to the fact that they are defined in continuous time, as it would require infinite memory to save an infinite number of points. This limits CT DSP to real-time processing tasks only. To solve this problem, a novel timing storage circuit based on memristors is proposed. Its ability to store and reproduce timing information in an analog manner without performing quantization allows CT digital signals to be recorded for later use, extending the benefits of CT DSP to applications that require signal storage.

The implementation of delay blocks in CT digital filters is another big challenge. Since the incoming data are not synchronized to a global clock, registers used to delay signals in conventional digital filters are not applicable in CT DSP systems. As a result, analog delay blocks such as inverter chains and their variants are usually employed to delay CT digital signals with no information loss. Depending on the amount of delay needed, these delay blocks can be very costly in terms of power consumption and chip area. For biomedical signals with very low bandwidth, the required delay is usually in the millisecond range or even longer. It would hence be very difficult if not impossible to implement such long delay using inverter chains. The proposed timing storage circuit is then adopted to delay CT digital signals in a more efficient way. Lastly, the amounts of delay of the proposed memristor-based delay blocks can be easily adjusted by changing the frequency of an external square wave, allowing the delay blocks to be effectively duplicated without consuming much additional power and area. This makes it possible to apply frequency response masking (FRM) techniques in CT DSP, enabling the design of sharp-transition CT FIR filters with reduced orders and thereby saving power and area. A delta modulator is also proposed to allow for the first time the cascading of CT FIR filters that operate on delta-modulated signals.

Based on circuit simulations with real electrocardiogram (ECG) signals, the memristor-based CT DSP systems proposed in this work was proven to be a good fit for biomedical applications. Significant power saving was achieved compared to the current state-of-the-art CT digital filters.

## **LIST OF FIGURES**

| Fig. 1.1 Four categories of signal processing systems: both time and amplitude                 |

|------------------------------------------------------------------------------------------------|

| can be either continuous or discrete, leading to a total of four                               |

| combinations3                                                                                  |

| Fig. 1.2 Block diagram of an ASP system4                                                       |

| Fig. 1.3 Block diagram of a conventional uniform DSP system                                    |

| Fig. 2.1 Uniform sampling of an analog signal $x(t)$ in the time domain                        |

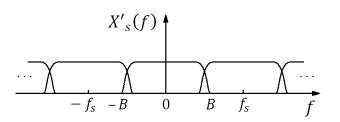

| Fig. 2.2 Uniform sampling of an analog signal $X(f)$ in the frequency domain16                 |

| Fig. 2.3 Illustration of aliasing in the frequency domain                                      |

| Fig. 2.4 Illustration of aliasing in the frequency domain                                      |

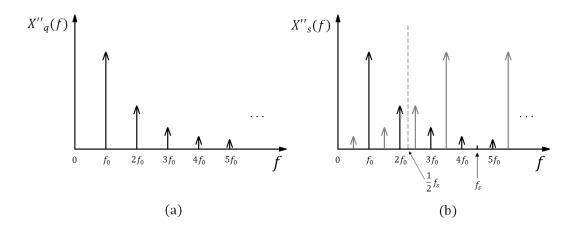

| Fig. 2.5 Fourier transforms of (a) the quantized signal $x_q$ ''(t) and (b) the sampled        |

| signal $x_s''(t)$ (only the first side-lobe at $f_s$ is included for better clarity)           |

| from the new equivalent system which performs quantizing before                                |

| sampling18                                                                                     |

| Fig. 3.1 (a) Level-crossing ADC: the thick solid curve represents the analog input,            |

| the thin staircase waveform represents the digital output. The set of                          |

| quantization boundaries are represented by the dashed lines. (b) The                           |

| corresponding power dissipation of the level-crossing ADC23                                    |

| Fig. 3.2 Input-output transfer characteristic of a middle-tread quantizer. $\varDelta$ denotes |

| the quantizer resolution and $X_{max}$ denotes the maximum allowable input                     |

| range25                                                                                        |

Fig. 3.3 Level-crossing ADC in the presence of noise for (a) quantizers without hysteresis and (b) quantizers with hysteresis. In both plots, the thick solid

| curve represents the analog input, the thin solid staircase waveform                          |

|-----------------------------------------------------------------------------------------------|

| represents the digital output. The quantization boundaries are represented                    |

| by the dotted lines. $\varDelta$ denotes the quantizer resolution and $\delta_{hyst}$ denotes |

| the amount of hysteresis introduced                                                           |

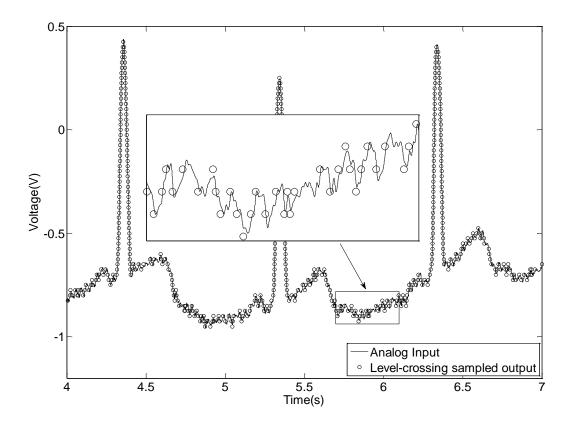

| Fig. 3.4 Level-crossing sampling of ECG signal #151 retrieved from the MIT-                   |

| BIH arrhythmia database. The solid curve represents the original analog                       |

| input and the series of bubbles represent the level-crossing sampled                          |

| output                                                                                        |

| Fig. 3.5 Nearest neighbor interpolation result of the level-crossing sampled data             |

| obtained in Fig. 3.4. The series of bubbles represent the level-crossing                      |

| sampled data, and the solid curve with crosses on it represents the nearest                   |

| neighbor interpolated result                                                                  |

| Fig. 3.6 Illustration of linear interpolation                                                 |

| Fig. 3.7 Linear interpolation result of the level-crossing sampled data obtained in           |

| Fig. 3.4. The series of bubbles again represent the level-crossing sampled                    |

| data, and the solid curve with crosses on it represents the linearly                          |

| interpolated result                                                                           |

| Fig. 3.8 Cubic interpolation result of the level-crossing sampled data obtained in            |

| Fig. 3.4. The series of bubbles again represent the level-crossing sampled                    |

| data, and the solid curve with crosses on it represents the cubic                             |

| interpolated result                                                                           |

| Fig. 3.9 Illustration for the need of a memory buffer in the linear interpolator38            |

xiv

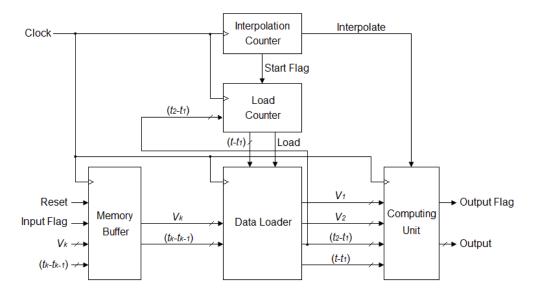

| Fig. 3.10 Implementation of the linear interpolator. The main blocks include a       |

|--------------------------------------------------------------------------------------|

| memory buffer, a data loader, a computing unit, an interpolation counter             |

| and a load counter                                                                   |

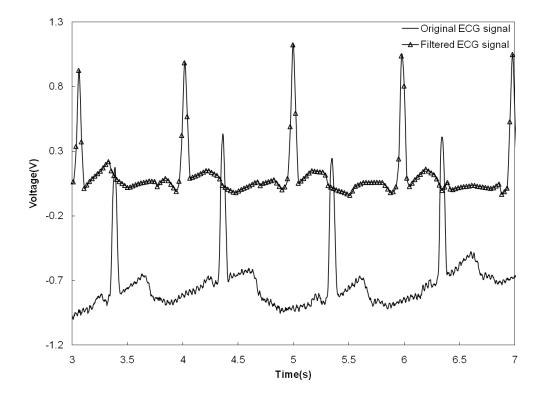

| Fig. 3.11 High-pass filtered result of the linearly interpolated data. The solid     |

| curve represents the original ECG signal, while the curve with triangles             |

| represents the filtered output42                                                     |

| Fig. 4.1 Block diagram of a CT DSP system                                            |

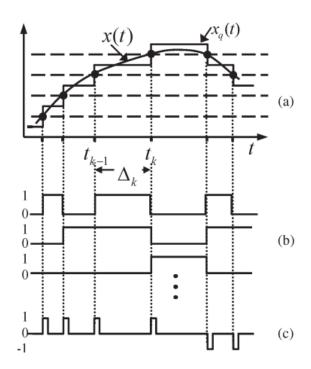

| Fig. 4.2 (a) Input signal, level-crossing samples, and quantized signal. (b) Digital |

| representation of quantized signal. (c) Delta-modulation of (b). [47]47              |

| representation of quantized signal. (c) Dena modulation of (b). [17]17               |

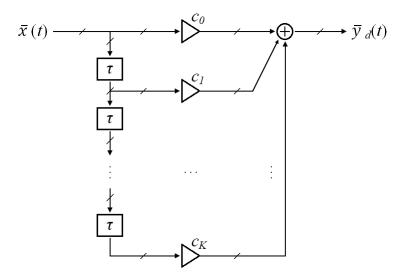

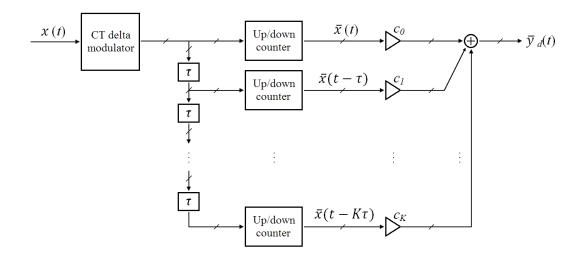

| Fig. 4.3 Architecture of a K-th order CT FIR filter                                  |

|                                                                                      |

| Fig. 4.3 Architecture of a K-th order CT FIR filter                                  |

| <ul><li>Fig. 4.3 Architecture of a K-th order CT FIR filter</li></ul>                |

| <ul> <li>Fig. 4.3 Architecture of a K-th order CT FIR filter</li></ul>               |

| <ul> <li>Fig. 4.3 Architecture of a K-th order CT FIR filter</li></ul>               |

| Fig. 4.3 Architecture of a K-th order CT FIR filter                                  |

| <ul> <li>Fig. 4.3 Architecture of a K-th order CT FIR filter</li></ul>               |

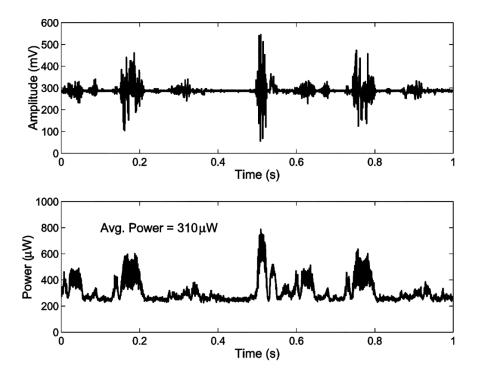

| Fig. 4.6 Plot of input speech signal (top) and the instantaneous power                  |

|-----------------------------------------------------------------------------------------|

| consumption (bottom) of the CT ADC/DSP/DAC system [43]54                                |

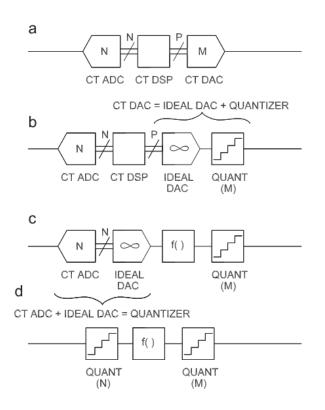

| Fig. 4.7 Four input-output equivalent representations of a CT ADC-DSP-DAC.              |

| The top row shows an actual implementation of a CT ADC-DSP-DAC                          |

| while the others are mathematical simplifications, resulting in a simple                |

| but equivalent system at the bottom. [44]55                                             |

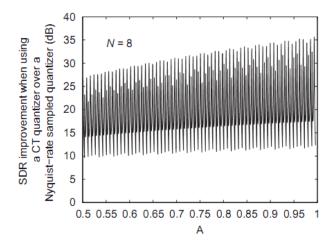

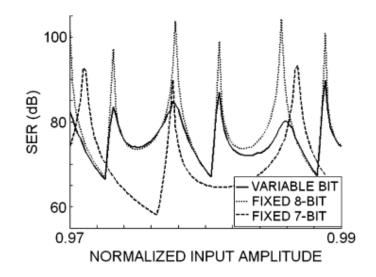

| Fig. 4.8 The improvement in SDR of an 8-bit CT quantizer over a Nyquist-rate            |

| sampled quantizer acting on a 1kHz sinusoid with a bandwidth of 26kHz                   |

| as a function of amplitude [44]57                                                       |

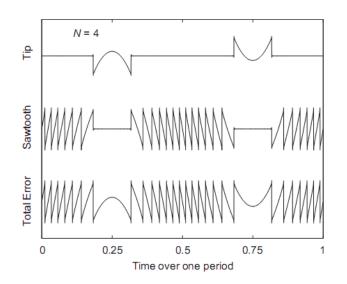

| Fig. 4.9 The total error waveform is the sum of the 'tip' portion and the 'sawtooth'    |

| portion [44]58                                                                          |

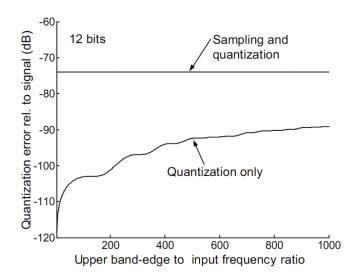

| Fig. 4.10 Quantization power relative to signal power for a sinusoidal input, as a      |

| function of the ratio of bandwidth to input frequency. No oversampling is               |

| assumed in the case of conventional DSP [41]59                                          |

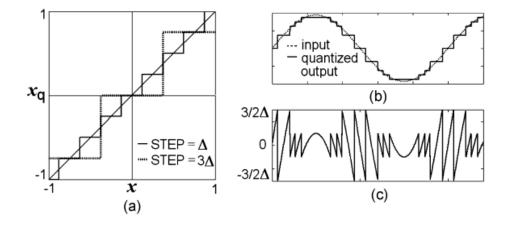

| Fig. 4.11 VR quantizing achieved by skipping two steps. (a) VR transfer                 |

|                                                                                         |

| characteristic. (b) Example output. (c) Resulting symmetric quantization                |

| characteristic. (b) Example output. (c) Resulting symmetric quantization<br>error. [45] |

|                                                                                         |

| error. [45]                                                                             |

| error. [45]                                                                             |

| error. [45]                                                                             |

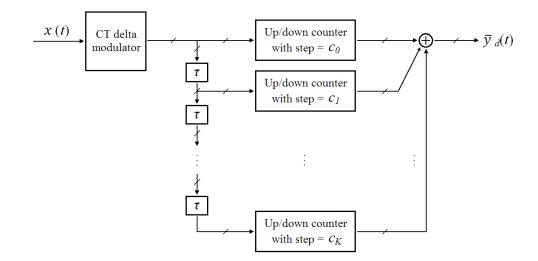

| Fig. 4.13 Architecture of a CT FIR filter implemented using asynchronous delta         |

|----------------------------------------------------------------------------------------|

| modulation64                                                                           |

| Fig. 4.14 Improved architecture of a CT FIR filter implemented using                   |

| asynchronous delta modulation65                                                        |

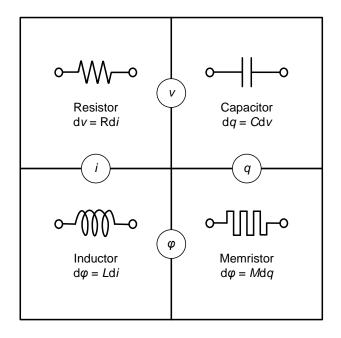

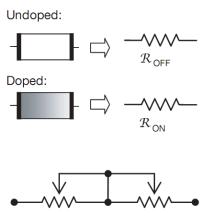

| Fig. 5.1 The four fundamental passive circuit elements and four fundamental            |

| circuit variables70                                                                    |

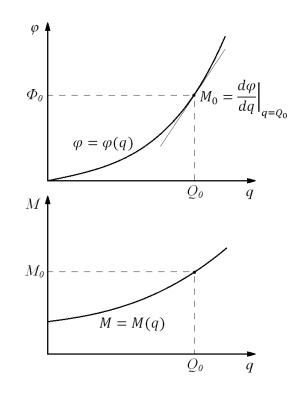

| Fig. 5.2 Plots of a $\varphi - q$ curve and its corresponding $M - q$ characteristic   |

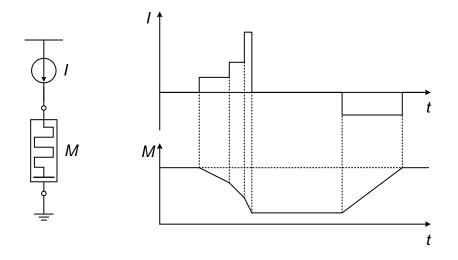

| Fig. 5.3 Change in memristance under different current levels and directions73         |

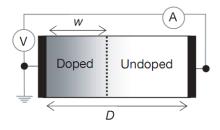

| Fig. 5.4 Structure of the HP memristor and the coupled variable resistor model         |

| [22]74                                                                                 |

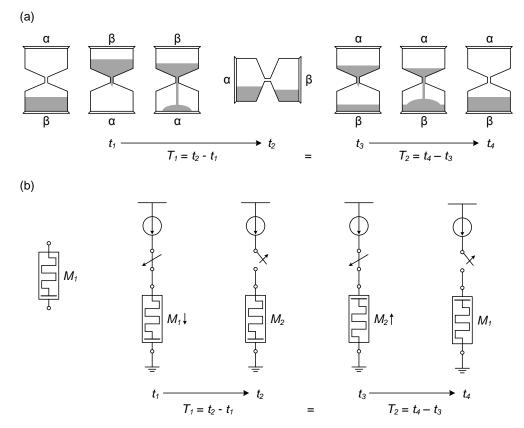

| Fig. 5.5 (a) Illustration of time tracking using a sandglass. (b) Illustration of time |

| tracking using a memristor76                                                           |

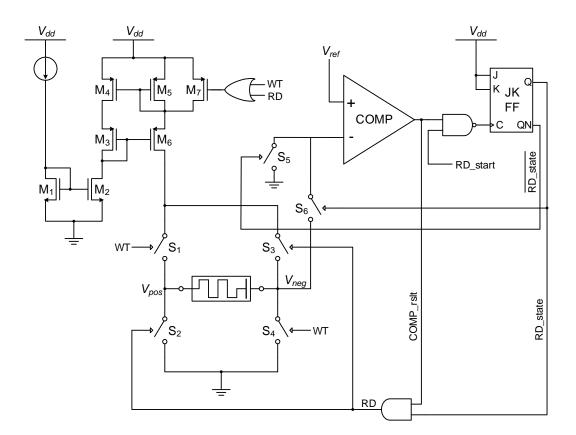

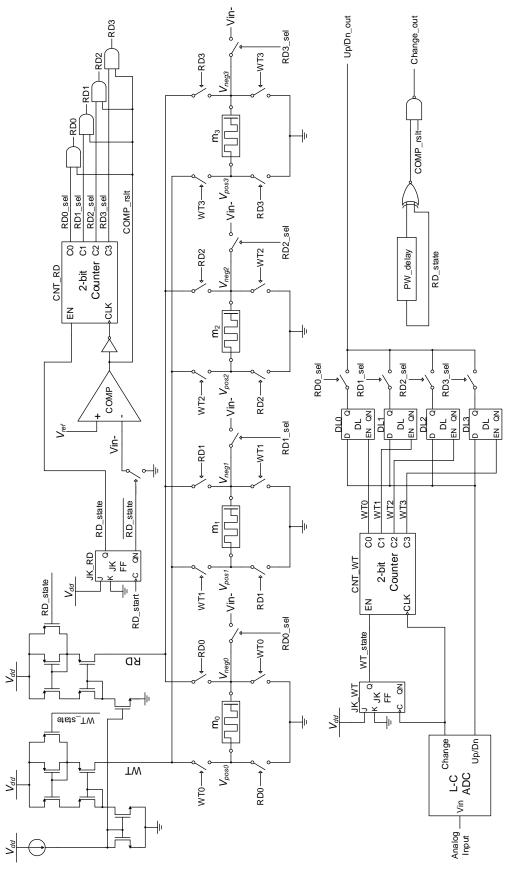

| Fig. 5.6 Schematic of a single timing storage cell80                                   |

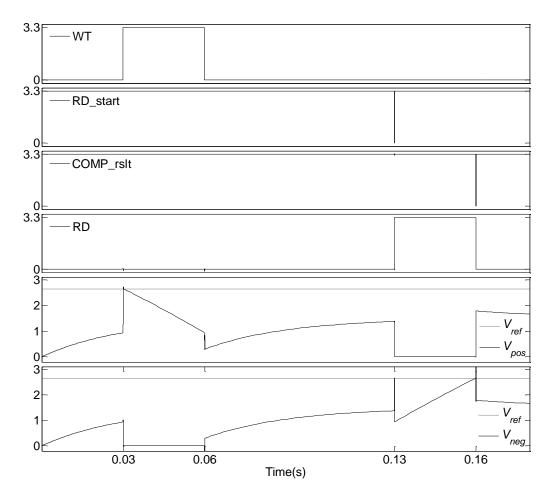

| Fig. 5.7 Simulation waveforms of the single timing storage cell83                      |

| Fig. 5.8 Range of memristance values used considering process variation85              |

| Fig. 5.9 Schematic of the comparator                                                   |

| Fig. 6.1 Schematic of a four-cell timing storage circuit to record and reproduce       |

| CT digital signals93                                                                   |

| Fig. 6.2 Reproduction of the level-crossing sampled sinusoidal signal using the        |

| proposed timing storage circuit. The blue curve represents the original                |

|                                                                                        |

| signal and the red curve represents the reproduced signal97                            |

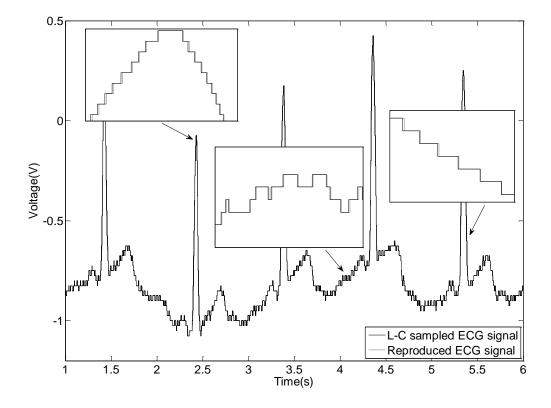

| Fig. 6.3 Level-crossing sampling of ECG signal #151 retrieved from the MIT-            |

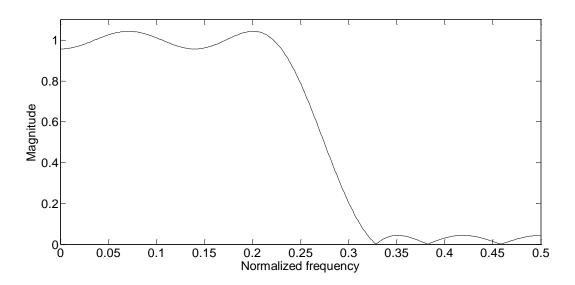

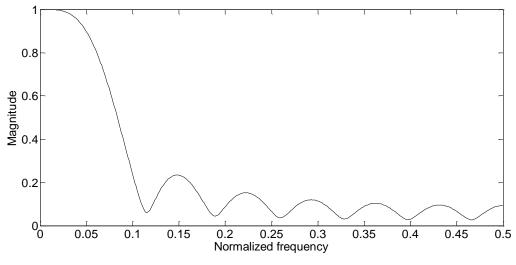

- Fig. 6.6 Frequency response of the low-pass filter ......107

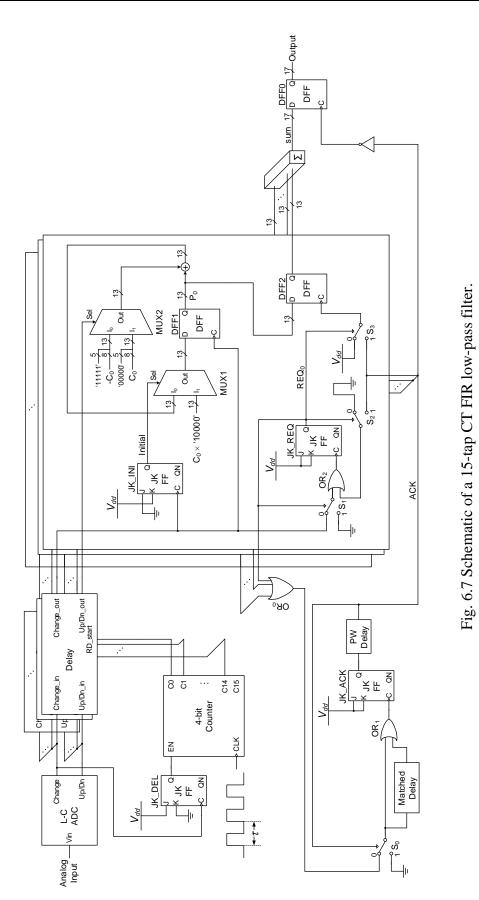

- Fig. 6.7 Schematic of a 15-tap CT FIR low-pass filter. ..... 109

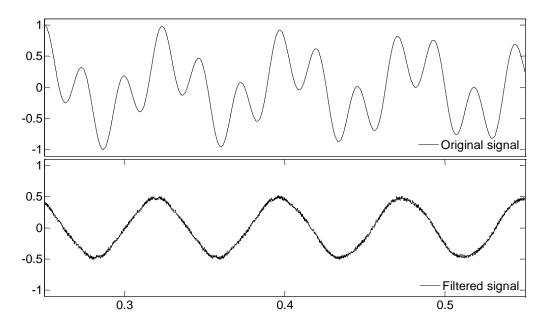

- Fig. 6.8 Sinusoidal signal before and after low-pass filtering.

113

Fig. 6.9 Frequency response of the S-G filter.

117

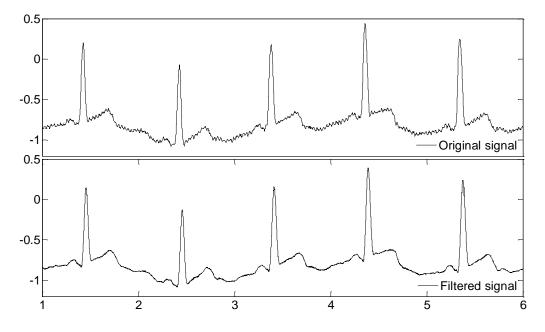

Fig. 6.10 ECG signal before and after filtering.

118

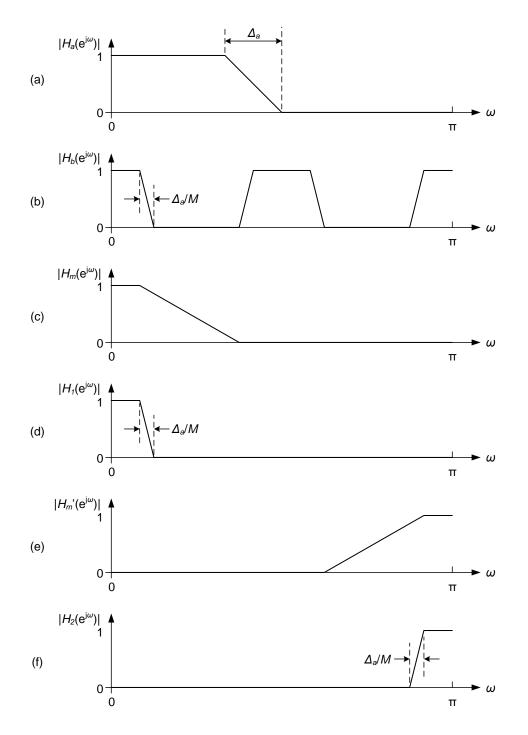

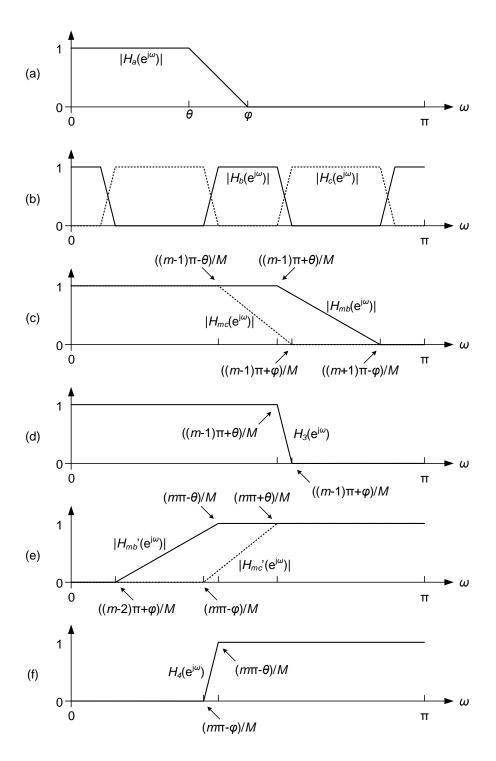

Fig. 7.1 Simple FRM for designing narrow-band sharp-transition FIR filters.

122

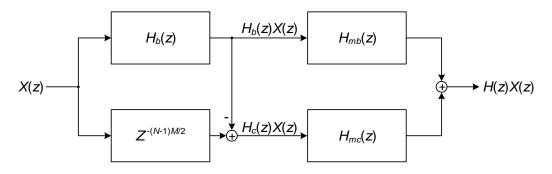

Fig. 7.2 Complementary FRM for designing wide-band sharp-transition FIR

Fig. 7.3 Block diagram of a complementary FRM filter......127

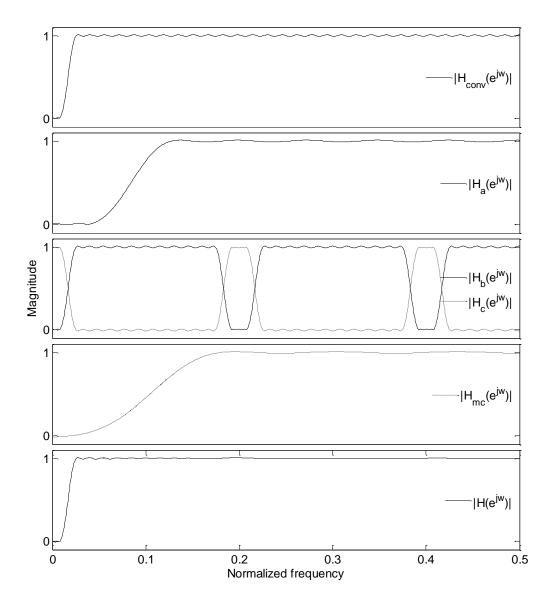

Fig. 7.5 A high-pass filter designed using complementary FRM. The five subplots shows the frequency responses of (a) the conventional filter designed without using FRM, (b) the conventional filter with the transition band widened by a factor of 5, (c) the multiple pass band filter obtained by replacing each delay block in (b) by a series of 5 identical delay blocks

|          | (solid line) and its complementary filter (dotted line), (d) the mask | ting |

|----------|-----------------------------------------------------------------------|------|

|          | filter, (e) the resulting complementary FRM filter                    | 132  |

| Fig. 7.6 | Schematic of a 7-bit accumulator                                      | 134  |

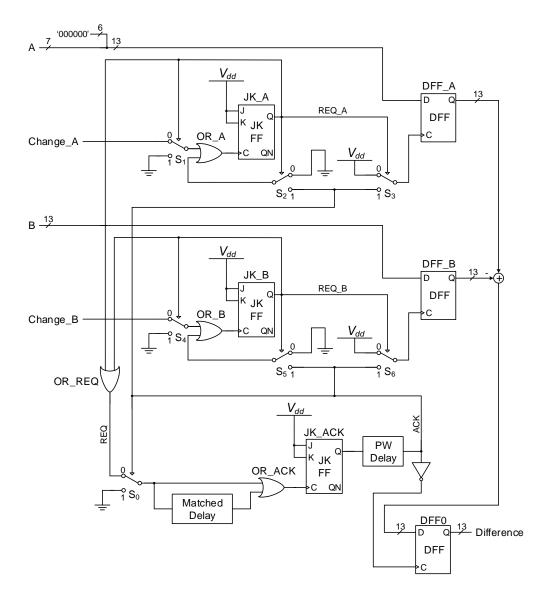

| Fig. 7.7 | Schematic of a 13-bit CT subtractor.                                  | 136  |

| Fig. 7.8 | Schematic of a 13-bit delta modulator.                                | 140  |

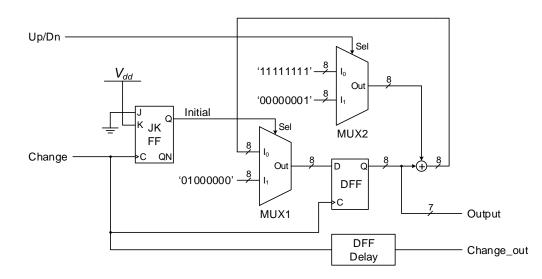

| Fig. 7.9 | Schematic of a 13-bit accumulator with variable initial value         | 141  |

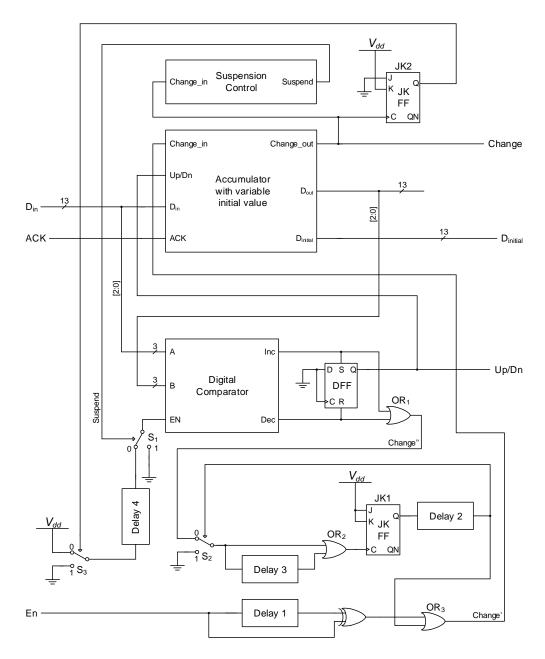

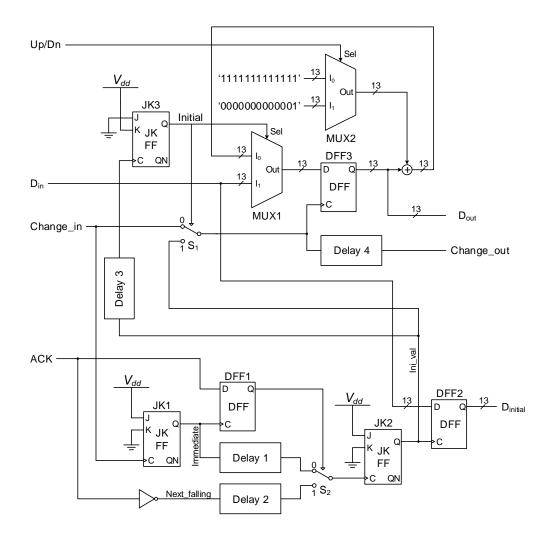

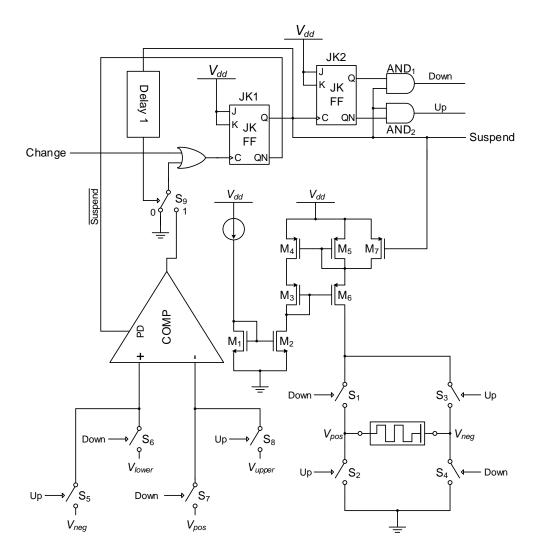

| Fig. 7.1 | 0 Schematic of a memristor-based suspension control unit              | 148  |

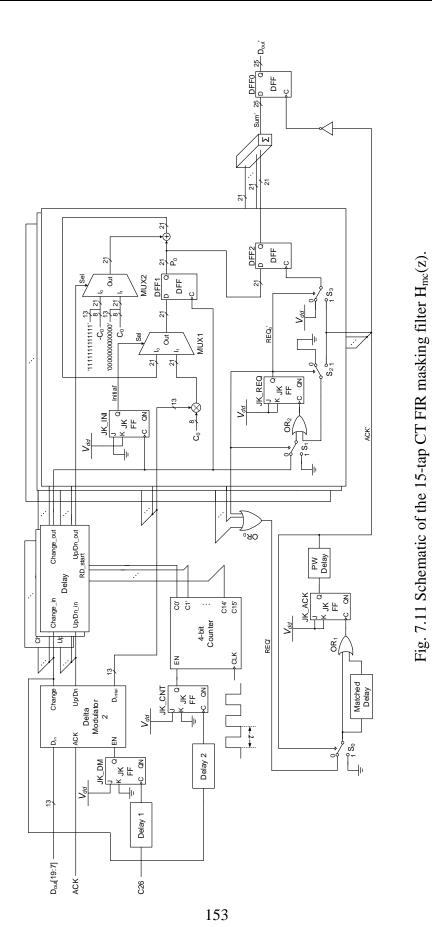

| Fig. 7.1 | 1 Schematic of the 15-tap CT FIR masking filter $H_{mc}(z)$           | 153  |

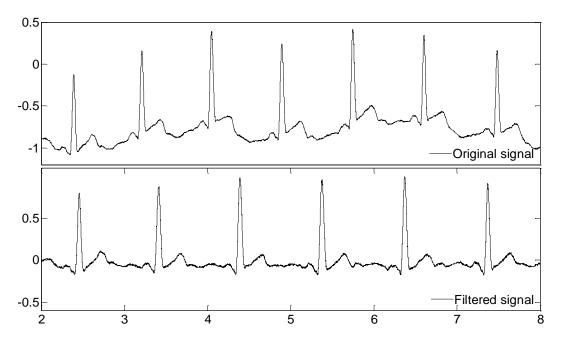

| Fig. 7.1 | 2 ECG signal before and after high-pass filtering                     | 155  |

## LIST OF TABLES

| Table 1.1 Advantages and disadvantages of DSP systems                |

|----------------------------------------------------------------------|

| Table 3.1 Linear interpolation error for different resolutions    37 |

| Table 3.2 Design parameters of the high-pass filter41                |

| Table 4.1 Design parameters of the low-pass filter                   |

| Table 5.1 Parameter values for memristor model    84                 |

| Table 6.1 Coefficients of the FIR low-pass filter    107             |

| Table 6.2 Comparison of Analog Delay Circuits    114                 |

| Table 6.3 Coefficients of the FIR S-G filter                         |

| Table 6.4 Comparison of Analog Delay Circuits    118                 |

| Table 7.1 Design parameters of the high-pass filter                  |

| Table 7.2 Filter orders with different scaling factor M.    130      |

| Table 7.3 Time to take the initial value under different conditions  |

| Table 7.4 Truth table of "Inc" of the digital comparator             |

| Table 7.5 Truth table of "Dec" of the digital comparator.    145     |

| Table 7.6 Parameter values for memristor model    150                |

| Table 7.7 Power consumption of each block within the filter          |

## LIST OF ABBREVIATIONS

| ADCAnalog to Digital Conversion / Analog to Digital ConverteASPAnalog Signal Processing | er |

|-----------------------------------------------------------------------------------------|----|

| ASP Analog Signal Processing                                                            |    |

|                                                                                         |    |

| CT Continuous-time                                                                      |    |

| CTCA Continuous-Time and Continuous-Amplitude                                           |    |

| CTDA Continuous-Time and Discrete-Amplitude                                             |    |

| D/A Digital to Analog                                                                   |    |

| DAC Digital to Analog Converter                                                         |    |

| DFF Delay Flip-Flop                                                                     |    |

| DSP Digital Signal Processing / Digital Signal Processor                                |    |

| DTCA Discrete-Time and Continuous-Amplitude                                             |    |

| DTDA Discrete-Time and Discrete-Amplitude                                               |    |

| FFT Fast Fourier Transform                                                              |    |

| FIR Finite Impulse Response                                                             |    |

| FR Fixed Resolution                                                                     |    |

| FRM Frequency Response Masking                                                          |    |

| GPS Global Positioning System                                                           |    |

| IIR Infinite Impulse Response                                                           |    |

| JKFF J-K Flip-Flop                                                                      |    |

| LSB Least Significant Bit                                                               |    |

| MOS Metal Oxide Semiconductor                                                           |    |

| MSB Most Significant Bit                                                                |    |

| S/H  | Sample-and-Hold                      |

|------|--------------------------------------|

| SDR  | Signal to Distortion Ratio           |

| S-G  | Savitzky-Golay                       |

| SNDR | Signal to Noise and Distortion Ratio |

| TFF  | Toggle Flip-Flop                     |

| VR   | Variable Resolution                  |

# CHAPTER 1

#### INTRODUCTION

#### **1.1 Motivation**

With an unprecedentedly fast pace of our society, people today work and live under tremendous pressure. Factors including unhealthy diet, lack of exercise and environmental pollutions have all contributed to an ever increasing number of patient records in hospitals and clinics every day. In fact, this situation is expected to become even worse with the aging of our population. The conventional healthcare system is therefore facing sever challenges in meeting the needs of everyone due to the limited availability of doctors and medical facilities. Such high demand also leads to continuous increase in healthcare costs, making it less affordable to the general public. This motivates a new prevention oriented healthcare model, in which the health condition of each individual is continuously monitored to allow potential problems to be discovered and treated at the earliest possible stage, maximizing the chances of cure with a minimum need of medical resources [1-3].

In order to achieve the large-scale continuous monitoring required by this prevention oriented healthcare system, wearable or implantable devices that are capable of recording and processing biomedical signals in real time will be needed [4-10]. The acquired signals can be stored locally in the built-in memory and some preliminary processing may be performed to determine the user's health condition. If anything goes wrong, the corresponding part of the recorded signal will be sent to the user's smart phone via a short-distance wireless communication link. The smart phone will then process the received signal more thoroughly to examine whether the problems indeed exist, and if necessary, the results will be sent via the cellular network to medical centers for doctors to decide if any treatments are required. In the case of an emergency, the device will send an alert signal to the smart phone, which will then notify medical centers for immediate response. With the location of the patient provided by the Global Positioning System (GPS) of the smart phone and the biomedical signals recorded by the device, the right treatment can be arranged and delivered to the patient within the shortest amount of time.

Such devices should come in small size and light weight, so that minimal interruption will be caused to our daily activities when they are carried every day. However, battery life is perhaps the greatest challenge in designing such devices, because for implantable devices, we can't afford to open up the chest of a patient every few days just to replace the battery. Of course the situation for wearable devices will be better, but the need of battery-changing will still be a big trouble. Therefore, the ultimate solution is to power such devices using energy harvested from our human bodies, such as heat and body movements [11-15]. This however, poses a very stringent requirement on the power consumption of such devices, as the energy can be gained from these sources are very limited in amount.

Conventional DSP samples and processes an analog signal periodically without considering the statistical properties of it. For biomedical signals, fast changes only occur in short periods while most of the time the signal does not vary significantly. Processing such sporadically varying signals using the conventional approach would give rise to a large number of samples that carry redundant information, wasting power both in the ADC and in the DSP. This motivates my research in new signal processing approaches that use power more efficiently.

#### **1.2 Background**

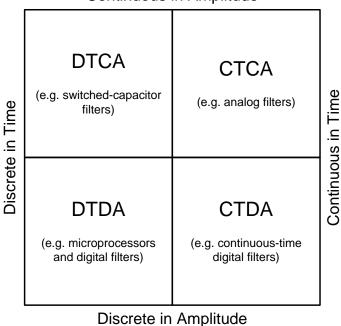

It is widely accepted that signal processing systems can be classified into four categories, depending on whether the signal they process is continuous or discrete

Continuous in Amplitude

Fig. 1.1 Four categories of signal processing systems: both time and amplitude can be either continuous or discrete, leading to a total of four combinations.

in time and amplitude [16-18], as illustrated in Fig. 1.1.

Traditionally, signal processing systems were implemented using analog circuits that operate in continuous-time and continuous-amplitude (CTCA). Examples like passive RC filters and active op-amp-based Butterworth filters belong to this category. These ASP systems correspond to the first quadrant in Fig. 1.1.

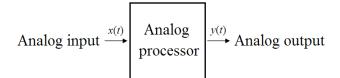

The block diagram of an ASP system is shown in Fig. 1.2 below. Since such systems do not involve sampling or quantizing, aliasing does not occur. Yet due to the nature of analog signals, ASP systems are very sensitive to noise, matching and component tolerances, which not only limits the attainable accuracy, but also leads to high power consumption if large dynamic ranges are required.

Fig. 1.2 Block diagram of an ASP system.

To overcome the drawbacks of ASP systems, DSP systems that operate in discrete-time and discrete-amplitude (DTDA) were developed with the advent of digital computers. Examples including microprocessors and dedicated DSP chips belong to this category corresponding to the third quadrant in Fig. 1.1. Since all signal sources in the real world are analog in nature, a DSP system needs to first convert the analog input into its digital form before processing in the digital

domain. Unless the digital output is to be saved for a later use, digital-to-analog conversion is also needed after processing.

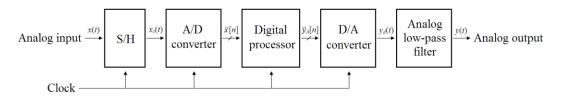

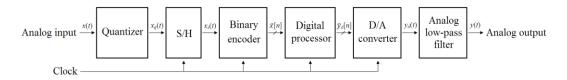

Fig. 1.3 shows the block diagram of a conventional uniform DSP system. Since the analog input varies with time, a sample-and-hold (S/H) circuit is used first to sample the analog input at periodic intervals and hold the sampled value constant at the input of the analog to digital (A/D) converter to allow accurate conversion. The output of the S/H circuit is a staircase-shaped analog signal, which after fed into the ADC is translated into a binary data stream containing only '0's and '1's. It is then possible to process this binary stream using digital circuitry. The resulting output of the digital processor, which is another binary stream, can either be stored in digital media or converted back to its analog form using a digital-to-analog (D/A) converter (DAC). An analog low-pass filter is added to remove any undesirable high-frequency distortions beyond the band of interest.

Fig. 1.3 Block diagram of a conventional uniform DSP system.

Since digital signals are binary data streams containing only '0's and '1's, they can be encoded using the lowest and highest voltages in real circuits. Even though component tolerances, temperature changes and other various disturbances will still cause the exact voltage level to fluctuate, there will be no ambiguity in interpreting the signal as long as the fluctuations are within the noise margin – the amount by which the signal exceeds the threshold for a proper '0' or '1'. Therefore unlike ASP systems, the accuracy of DSP systems does not depend on the precise values of voltage levels, resulting in better noise immunity.

In terms of signal storage, DSP systems are also much more reliable than ASP systems. Digital signals can be stored almost indefinitely without any loss of information on various storage media such as optical discs and flash memory. These stored binary data can also be easily transferred and duplicated with absolute fidelity. In contrast, stored analog signals deteriorate rapidly as time progresses and the information lost can never be recovered.

In addition, arithmetic operations like addition and multiplication of digital signals can be more easily implemented using binary logic, making it possible to realize highly sophisticated and complex processing algorithms that are much harder if not impossible to realize in the analog domain.

Moreover, since both the signals and the coefficients involved in the processing operations of a DSP system are represented as binary words, the accuracy can be easily adjusted by changing the word length. If very high accuracy is needed, even floating-point arithmetic can be used.

Last but not least, there are no big problems for DSP systems to deal with signals of very low frequencies, while for ASP systems it will need inductors and capacitors that are physically very large in size.

Despite all these advantages mentioned above, DSP systems also have their disadvantages as compared to ASP systems. First and foremost, DSP systems suffer from aliasing because of its use of sampling and quantizing. More details about aliasing will be discussed in Chapter 2. Second, according to the Nyquist-Shannon sampling theorem, the sampling frequency has to be at least twice the highest frequency component present in the analog input. However, due to the finite operating speed of digital circuitry, the sampling frequency cannot increase indefinitely. This limits the applicable frequency range of DSP systems. For example, radio-frequency (RF) signals in the GHz frequency range cannot be processed in the digital domain with the current technology. Lastly, DSP systems usually consume lots of power, especially when compared to analog passive filters that consume almost zero power. This is because of its more complex structure consisting of multiple blocks.

The advantages and disadvantages of DSP systems as compared to ASP systems are summarized in Table 1.1 below.

| Advantages                               | Disadvantages                               |

|------------------------------------------|---------------------------------------------|

| Better noise immunity                    | Aliasing                                    |

| More reliable signal storage             | Inability to process high-frequency signals |

| Possible complex processing              | High power consumption                      |

| Easier control of accuracy               |                                             |

| Ability to process low-frequency signals |                                             |

Table 1.1 Advantages and disadvantages of DSP systems.

To overcome the drawbacks of aliasing and high power consumption while preserving the benefits listed above, the relatively unexplored CT DSP systems which operate in continuous-time and discrete-amplitude (CTDA) were chosen to be the main focus of my research. Nevertheless, other nonuniformly sampled digital signal processing approaches were also investigated.

#### **1.3 Research Contributions**

In this work, new nonuniformly sampled digital signal processing approaches were developed, and improvements were also made on existing ones to make them more suitable for low-power biomedical applications.

To take advantage of the statistical properties of biomedical signals, a new signal processing scheme combining level-crossing sampling and conventional uniform DSP with the aid of linear interpolation was proposed. It was show by an example that a system designed using this processing scheme was able to achieve 88.8% reduction in the sampling rate and 92.6% reduction in the order of the filter. Designed using a 0.35  $\mu$ m technology, the linear interpolator for this system consumed an average power of 12.1  $\mu$ W under a 3.3-V supply.

With signal dependent power consumption not only in the digitization part, but also in the processing part, CT DSP is believed to be an ideal choice for biomedical signals. However, the inability of signal storage and power consuming delay implementation used to be the two main obstacles to its adoption in biomedical applications. By making use of the memory effect of memristors, a timing storage circuit was proposed to allow the recording and reproducing of CT digital signals, which extended the benefits of CT DSP to applications that require signal storage. Various design considerations and practical challenges were analyzed in details. Circuit simulation verified the feasibility of this approach.

More importantly, it was proven that the delay blocks in CT DSP systems could also be replaced by the proposed timing storage circuits, enabling significant power and area saving for low-frequency biomedical applications. An ECG signal processing example using the proposed method achieved more than 20% power saving compared to the current state-of-the-art CD DSP system implementations, without even considering the much older process and higher supply voltage used. With a 0.35  $\mu$ m process, a 15-tap CT FIR filter designed using this method consumed an average power of 6.196  $\mu$ W under a 3.3-V supply.

Lastly, the tunability of the proposed memristor-based delay implementation also enabled the use of FRM techniques in designing sharp-transition CT FIR filters with reduced filter orders. A delta modulator was proposed to allow for the first time the cascading of CT FIR filters that operate on delta-modulated signals. As an example, a CT FRM high-pass filter with a combined order of 40 was designed using the same 0.35- $\mu$ m process. This filter consumed a total power of 28.0  $\mu$ W under the same 3.3-V supply, which was about 75.2% lower than the power consumed by a 168<sup>th</sup>-order filter capable of achieving the same frequency response specifications.

9

Shown below is a list of publications achieved in this work:

- Y. Hong, I. Rajendran, and Y. Lian, "A new ECG signal processing scheme for low-power wearable ECG devices," in *Proc. 2011 Asia Pacific Conf. Postgraduate Research in Microelectronics and Electron.* (*PrimeAsia'11*), 2011, pp. 74-77.

- Y. Hong, Z. Xie, and Y. Lian, "Wireless wearable ECG sensor design based on level-crossing sampling and linear interpolation," in *Proc.* 2013 IEEE Int. Symp. Circuits Syst. (ISCAS'13), 2013, pp. 1300-1303.

- Y. Hong and Y. Lian, "A memristor-based continuous-time digital FIR filter for biomedical signal processing," *IEEE Trans. Circuits Syst. I* (Resubmitted after revision).

### **1.4 Organization of the Thesis**

This thesis is organized as follows:

In Chapter 2, the drawbacks of conventional uniform DSP is reviewed to show why it is not an energy-efficient choice for biomedical signals with long periods of inactivity. Some projects based on uniform DSP is also briefly mentioned.

In Chapter 3, a new signal processing scheme combining level-crossing sampling and conventional uniform DSP with the aid of linear interpolation is presented.

In Chapter 4, a literature review of CT DSP is conducted to show why it can be a perfect fit for biomedical signals. Two major problems of CT DSP that make it hard to be applied in biomedical applications are discussed: the first is its inability of signal storage, and the second is its power and area costly delay implementation for low-frequency signals.

In Chapter 5, a memristor-based timing storage circuit is proposed to allow the recording and reproducing of CT digital signals. Various design considerations and practical challenges are analyzed in details.

In Chapter 6, the proposed timing storage circuit is used to replace the delay blocks in CT DSP systems. Simulation on ECG signals show significant power saving compared to the current state of the art.

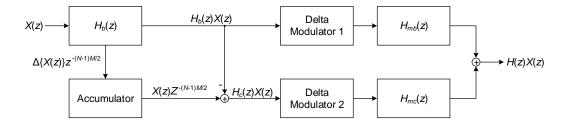

In Chapter 7, the use of FRM techniques in designing sharp-transition CT FIR filters with reduced orders is discussed. A delta modulator is proposed to enable for the first time the cascading of CT FIR filters.

In Chapter 8, a summary about my research in this work is made to conclude this thesis.

# CHAPTER 2 CONVENTIONAL UNIFORM DSP

## **2.1 Theories**

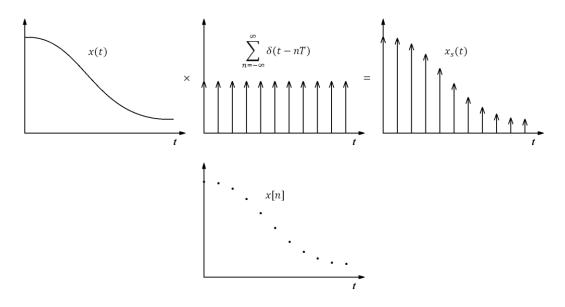

In a conventional uniform DSP system, the analog input is first sampled periodically before being converted into its digital form using an ADC. The resulting outputs are therefore uniformly spaced in time, i.e. the time intervals between any two consecutive samples are equal to the same sampling interval *T*.

Mathematically, uniform sampling is equivalent to multiplying the analog input x(t) with a unit impulse train (also known as the Dirac comb function) that has a period of T [19, 20]. The sampled signal  $x_s(t)$  can then be expressed as

$$x_s(t) = x(t) \sum_{n=-\infty}^{\infty} \delta(t - nT) = \sum_{n=-\infty}^{\infty} x(nT) \delta(t - nT), \quad (2-1)$$

where  $\delta(t-nT)$  is a unit impulse (also known as the Dirac delta function) at nT, and integer n is the sample index. From this expression it is obvious that  $x_s(t)$  is another impulse train scaled to the values of x(t) at the corresponding time instants. In other words, the sampled signal is zero everywhere except at instants t=nT. Thus for a signal of finite duration, a finite number of samples will be generated for subsequent processing and storage. Information contained in the original analog input x(t) is then transferred to the sequence

$$x[n] = \{\dots, x(-t), x(0), x(t), x(2t), x(3t), \dots\}$$

(2-2)

It should be remembered that all the elements in the sequence x[n] are still continuous in value, since quantization has not been performed yet.

A graphical illustration of uniform sampling is shown in Fig. 2.1. Even though the sampled signal  $x_s(t)$  are considered to be discrete in time, electrically it is still analog in nature: the signal values between consecutive samples are just zero, rather than undefined.

Fig. 2.1 Uniform sampling of an analog signal x(t) in the time domain.

All the above discussions are based on signals in their time-domain representations. It is sometimes more efficient however, to investigate signals in the frequency domain, as it provides information about the frequency content present in a signal, which are not easily visible from the time-domain waveforms. The frequency-domain representation (also referred to as spectrum) of a signal can be obtained by taking the Fourier transform of its time-domain representation. The Fourier transform X(f) of a continuous-time signal x(t) is given by

$$F\{x(t)\} = X(f) = \int_{-\infty}^{\infty} x(t) e^{-j2\pi f t} dt,$$

(2-3)

where F{} denotes the Fourier transform operation.

To investigate uniform sampling in the frequency domain, Fourier transform is performed on the sampled signal  $x_s(t)$ . From (2-1)  $x_s(t)$  is equal to the product of x(t) and the Dirac comb function  $\sum_{n=-\infty}^{\infty} \delta(t - nT)$ . Since multiplication in the time domain is equivalent to convolution in the frequency domain, the frequency transform  $X_s(f)$  of  $x_s(t)$  is equal to the convolution of X(f) and the Fourier transform of the Dirac comb function:

$$F\{x_{s}(t)\} = F\{x(t) \times \sum_{n=-\infty}^{\infty} \delta(t - nT)\}$$

$$= F\{x(t)\} * F\{\sum_{n=-\infty}^{\infty} \delta(t - nT)\}$$

$$= X(f) * \frac{1}{T} \sum_{n=-\infty}^{\infty} \delta\left(f - \frac{n}{T}\right)$$

$$= X(f) * f_{s} \sum_{n=-\infty}^{\infty} \delta(f - nf_{s})$$

$$= f_{s} \sum_{n=-\infty}^{\infty} X(f - nf_{s}).$$

(2-4)

It is obvious from (2-4) that the spectrum of  $x_s(t)$  is the periodic version of the spectrum of x(t) with a period equal to the sampling frequency  $f_s$ . A frequency-domain illustration of uniform sampling is shown in Fig. 2.2.

A signal x(t) is said to be frequency band-limited to *B* Hertz if its Fourier transform X(f) is zero beyond that frequency [19]. *B* is also called the bandwidth

of x(t) and is equal to the highest frequency component present in x(t), as shown by X(f) in Fig. 2.2(a).

Fig. 2.2 Uniform sampling of an analog signal X(f) in the frequency domain.

A band-limited signal x(t) can be perfectly reconstructed from its discrete-time samples x[n] if the sampling frequency  $f_s$  (the reciprocal of the sampling interval T) is at least twice the signal bandwidth B. This is commonly referred to as the Nyquist-Shannon sampling theorem [19]. The minimum sampling frequency  $f_N =$ 2B for perfect reconstruction is called the Nyquist sampling rate. Signals sampled at a rate lower than the Nyquist rate are said to be under-sampled. Undersampling will cause frequency content beyond  $f_s/2$  in the original signal to overlap after sampling, as illustrated in Fig. 2.3. Such overlapping makes it impossible to reconstruct the original signal from the sampled output, giving rise to an undesirable phenomenon called aliasing.

Fig. 2.3 Illustration of aliasing in the frequency domain.

At this point, it may seem like there will be no problems of aliasing as long as a sampling frequency higher than the Nyquist rate is used. However, this is not true for DSP systems, which operate not only in discrete-time, but also in discrete-amplitude. After sampling is performed on the analog input, the value of each sample will next be rounded to a nearest discrete level among a predefined set – a process called quantizing. This finite number of quantization levels will then be encoded using binary words, which can be processed using digital circuitry. Even though the sampled signal  $x_s(t)$  does not see overlapping in the frequency domain (as shown in Fig. 2.2), quantizing as a nonlinear operation will introduce a lot more frequency components than are present in  $X_s(f)$ . These new frequency components will be related to both the frequency content already present in  $X_s(f)$  and the sampling frequency  $f_s$ , making it difficult to analyze the overall effect. This calls for a new equivalent system model as shown in Fig. 2.4.

Fig. 2.4 Illustration of aliasing in the frequency domain.

The new model is exactly the same as the block diagram of a uniform DSP system as shown in Fig. 1.3, except that the sequence of sampling and quantizing are switched (In Fig. 1.3, the quantizer and binary encoder are represented as a single ADC block). The two models are equivalent because the input-output relationship of a S/H block followed by a quantizer is identical to that of a quantizer followed by a S/H block [21].

When quantizing is performed directly on the input, harmonic distortions will arise due to the nonlinearity of the quantizer. In the frequency domain, these distortions are located at integer multiple frequencies of the original signal, but with decaying magnitude as frequency increases. The quantized spectrum  $X''_q(f)$ of a single-tone sinusoidal signal  $x''(t) = \sin(2\pi f_0 t)$  is sketched in Fig. 2.5(a) for illustration. As can be seen, apart from the fundamental component at  $f_0$ ,  $X''_q(f)$ also contains harmonic components at  $mf_0$  (*m* being any integer), occupying an infinite bandwidth.

Fig. 2.5 Fourier transforms of (a) the quantized signal  $x_q$  '(t) and (b) the sampled signal  $x_s$  '(t) (only the first side-lobe at  $f_s$  is included for better clarity) from the new equivalent system which performs quantizing before sampling.

The quantized signal  $x_q$  ''(t) is then sampled at  $f_s = 4.5f_0$ . The Nyquist rate for this input x''(t) = sin( $2\pi f_0 t$ ) is  $f_N = 2f_0$ , since  $f_0$  is the highest frequency component in the original signal. Therefore the sampling frequency used is much higher than the Nyquist rate, satisfying the Nyquist-Shannon sampling theorem. However, due to the harmonics introduced during quantizing, frequency overlapping still occurs in the sampled signal spectrum  $X''_s(f)$ , as shown in Fig. 2.5(b). From this sketch it is noticed that even though shifted versions of the fundamental component are all outside the baseband (indicated by the vertical dashed line at  $2.25f_0$ , which is half the sampling frequency), shifted harmonic components at  $pf_{s}+mf_0$  (*p* being any integer) are aliased into the baseband, causing distortion to the signal of interest. In this sketch, only the first periodic side-lobe is included (for better clarity), but in fact all further side-lobes will have harmonics falling into the baseband, giving rise to a noise floor that covers the entire frequency range.

In summary, conventional uniform DSP systems will always suffer from aliasing, even if the Nyquist-Shannon sampling theorem is satisfied. This is due to its discretization in both time and amplitude.

Discrete-time Continuous-amplitude (DTCA) signal processing systems (second quadrant of Fig. 1.1) which only sample the analog input signal without quantizing it, will not suffer from aliasing if only the sampling theorem is satisfied. This is obvious from the previous discussion. However, DTCA systems share most of the disadvantages of analog systems, like its sensitivity to noise and component tolerances. Since the target of my research is mostly on biomedical applications, such as ECG and electroencephalogram (EEG) systems that usually involve a lot of noise resulted from patient body movement and ambient interference, the ability to reject noise will be vital to the overall performance of a system. DTCA systems that are sensitive to noise are therefore not considered.

The final class of signal processing systems – CTDA systems (fourth quadrant of Fig. 1.1) that only quantize the analog input without sampling it do not have

the problem of aliasing either. Even though harmonic distortion will still be present, most of them will be beyond the frequency band of interest and therefore does not affect the system performance, leading to a better signal quality in terms of in-band signal to distortion ratio (SDR). On the other hand, discretization in amplitude gives CTDA systems most of the advantages of digital systems, such as noise immunity and programmability. These benefits make CTDA systems an ideal choice for processing biomedical signals. In fact even more attractive advantages like reduced power consumption will be gained by using levelcrossing sampling. More details about level-crossing sampling and CTDA systems will be discussed in Chapter 3 and Chapter 4 respectively.

# CHAPTER 3 NONUNIFORM SAMPLING AND UNIFORM CONVERSION

#### 3.1 Uniform DSP vs. Nonuniform DSP

A conventional uniform DSP system takes samples from its analog input, digitizes and processes them periodically according to a clock. Such a system does not take advantage of the statistical properties of the analog input, but instead it samples the analog input at a constant rate that is at least twice the signal bandwidth, no matter how fast or how slow the signal changes.

For biomedical signals, such as ECG signals, fast changes only occur in brief moments while most of time the signal varies slowly. Sampling such sporadically varying signals using the conventional uniform approach would give rise to a large number of samples that carry redundant information, wasting power not only in digitization, but also in subsequent processing [22, 23].

Nonuniform DSP was therefore developed to process signals with a combination of fast changes and long periods of inactivity. In [24-26], level-crossing sampling is first used to digitize the analog input, before Second-order polynomial interpolation is used to convert the resulting nonuniform samples back

into uniform format. The uniform digital signals can then be processed in the conventional way. In [27], nearest neighbor interpolation is used for uniform conversion due to its lower error in variance estimation. In [28], A local timer is adopted for timing quantization, and asynchronous filtering is performed by processing the convolution product between the interpolated impulse response and the interpolated input signal. In [29-32], an activity selection algorithm is employed to select and window the active part of non-uniformly sampled signals. Nearest neighbor interpolation is used to resample the active parts of the signal before adaptive rate filtering is performed.

#### **3.2 Level-Crossing Sampling**

#### 3.2.1 Concept

Unlike conventional uniform DSP systems, which sample the input at a fixed clock frequency, level-crossing sampling takes the statistical properties of the inputs into consideration [24, 33-36]. Only when a significant change occurs in the input will a new sample be generated. For low-frequency or inactive inputs, the constant-frequency sampling in conventional uniform DSP systems simply wastes power. For level-crossing sampling however, slow inputs naturally result in sparse samples, which lead to lower dynamic power dissipation. During silent periods of the input, the system waits for a change in the signal while dissipating no dynamic power.

This is achieved by employing a level-crossing ADC that generates samples only when the input crosses a predefined set of regularly-spaced amplitude

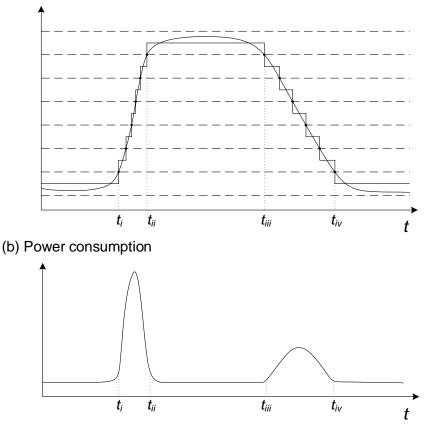

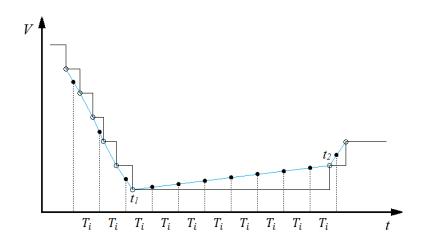

(a) Signal waveforms of a level-crossing ADC

Fig. 3.1 (a) Level-crossing ADC: the thick solid curve represents the analog input, the thin staircase waveform represents the digital output. The set of quantization boundaries are represented by the dashed lines. (b) The corresponding power dissipation of the level-crossing ADC.

boundaries, as illustrated by the dashed lines in Fig. 3.1(a). Each solid line resting in the middle of two dashed lines is used to represent the quantized value for signals falling within the two boundaries. This finite number of solid lines can then be encoded using binary words, yielding the digital representation of a levelcrossing ADC.

As can be seen from the power dissipation plot shown in Fig. 3.1(b), significant power is consumed only during the two time intervals  $t_i$ - $t_{ii}$  and  $t_{iii}$ - $t_{iv}$ , when substantial changes occur in the analog input. The first interval also has a

higher peak than the second interval since during  $t_i$ - $t_{ii}$  the input changes more drastically and therefore samples are being generated more frequently. During the rest of the time when the input remains more or less constant, the system consumes minimum static power mainly due to biasing current and transistor leakage. Such adaptive-rate sampling of level-crossing ADC makes it well suited for biomedical signals that exhibit burst-type waveforms.

This however creates another problem since the samples obtained from a level-crossing ADC are not uniformly spaced in time, as is the case for a conventional uniform-sampling ADC. Most of the available digital signal processing theories and techniques were developed based on uniform sampling, which means they cannot be directly applied to the digital output of a level-crossing ADC. Although efforts have been made in developing the corresponding theories and techniques for nonuniformly sampled digital signals, no systematic approaches have been formed yet. Techniques like general discrete Fourier transform and Lomb's algorithm face problems like noise in spectra [37, 38].

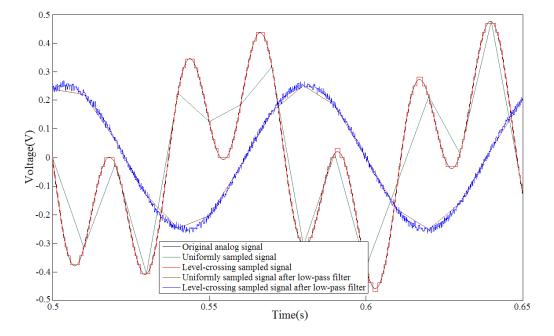

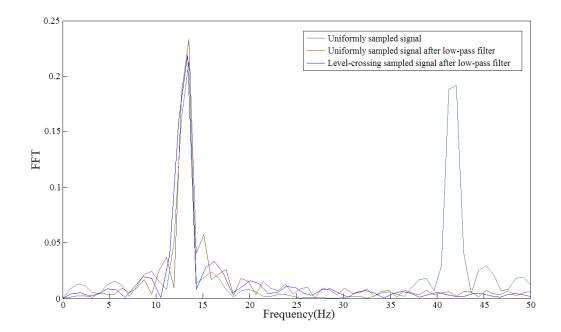

With these constraints, a new system that combines level-crossing sampling and conventional synchronous processing with the aid of linear interpolation is proposed. The overall computation complexity and power consumption of this new processing scheme is expected to be significantly lower than those of the conventional uniform approach. Matlab simulation on real ECG signals showed that the signal quality is preserved with an average error of less than 2%, while the average sampling rate of such a new system is only 11.2% of the sampling rate of a uniform DSP system.

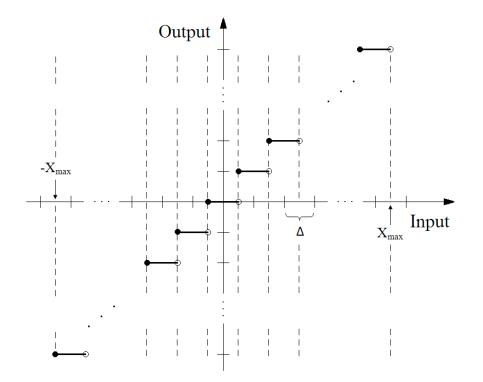

Fig. 3.2 Input-output transfer characteristic of a middle-tread quantizer.  $\Delta$  denotes the quantizer resolution and  $X_{max}$  denotes the maximum allowable input range.

# 3.2.2 Quantization Scheme

The input-output transfer characteristic of an *N*-bit middle-tread quantizer used for level-crossing sampling is shown in Fig. 3.2. The horizontal axis corresponds to the analog input, which is continuous, while the vertical axis corresponds to the digital output, which only takes discrete values. The regularlyspaced dashed lines again represent the quantization boundaries.  $\Delta$  denotes the quantizer resolution and  $X_{max}$  is the maximum allowable input range. They can be calculated from:

$$\Delta = \frac{D}{2^N},\tag{3-1}$$

$$X_{max} = D(1 - \frac{1}{2^N}), \tag{3-2}$$

where *D* denotes the full dynamic range. The reason why the maximum allowable input range is less than the full dynamic range is that one quantization level is purposely left unused, in order to preserve odd symmetry in the transfer characteristic.

# 3.2.3 Hysteresis

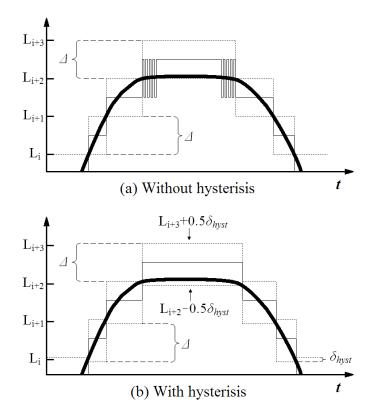

Biomedical signals such as ECG signals are usually very noisy. Such noises

Fig. 3.3 Level-crossing ADC in the presence of noise for (a) quantizers without hysteresis and (b) quantizers with hysteresis. In both plots, the thick solid curve represents the analog input, the thin solid staircase waveform represents the digital output. The quantization boundaries are represented by the dotted lines.  $\Delta$  denotes the quantizer resolution and  $\delta_{hyst}$  denotes the amount of hysteresis introduced.

may result from patient body movement, ambient electromagnetic interference as well as other various types of disturbances. This has a severe impact on level crossing sampling. Every time the analog input approaches a quantization boundary, the added noises make the signal crossing that boundary back and forth even though it actually is not, as shown in Fig. 3.3(a). This causes the levelcrossing ADC to generate extra unnecessary samples. Such noise-induced samples provide no additional information about the signal of interest, yet they consume significant power in both the ADC as well as the subsequent DSP.

To avoid such undesirable noise-induced toggling, hysteresis is purposely introduced in the quantizer, as illustrated in Fig. 3.3(b). Normally, when the analog input is situated between the two boundaries  $L_i$  and  $L_{i+1}$ , a new sample will be generated once the following condition is violated:

$$L_i \le x(t) < L_{i+1}.$$

(3-3)

To introduce hysteresis, the above condition is modified as

$$L_{i} - \frac{1}{2}\delta_{hyst} \le x(t) < L_{i+1} + \frac{1}{2}\delta_{hyst}.$$

(3-4)

In other words, each quantization interval is now widened by an amount equal to  $\delta_{hyst}$ . For any two neighboring intervals, the upper boundary of the lower interval is no longer aligned with the lower boundary of the higher interval, creating an overlapping between the two. This way, when the analog input increases over a certain boundary causing the ADC to produce a new sample, it must decrease by at least  $\delta_{hyst}$  before another sample to be generated. This prevents the input from

going back and forth between neighboring intervals in the presence of noise, as long as the amount of fluctuation is less than  $\delta_{hyst}$ .

#### **3.2.4** Simulation with Real ECG Signals

The choice of sampling resolution N is a tradeoff between signal quality and power consumption. A higher sampling resolution which corresponds to denser quantization intervals allows the analog input to be tracked more accurately. On one hand, a finer set of quantization intervals leads to lower quantization errors and therefore improves the signal to noise and distortion ratio (SNDR). On the other hand, due to the event-driven nature of level-crossing sampling, small variations present in the input can only be captured if the quantization interval is narrow enough. However, unlike conventional Nyquist-based DSP, wherein the sampling frequency and quantization resolution are independent, the average sampling rate in level-crossing sampling has an exponential dependence on the quantization resolution used. This implies as N increases, the average sampling rate and the resulting dynamic power consumption also rises very rapidly. Therefore, a resolution just enough to capture the required degree of accuracy will be most desirable.

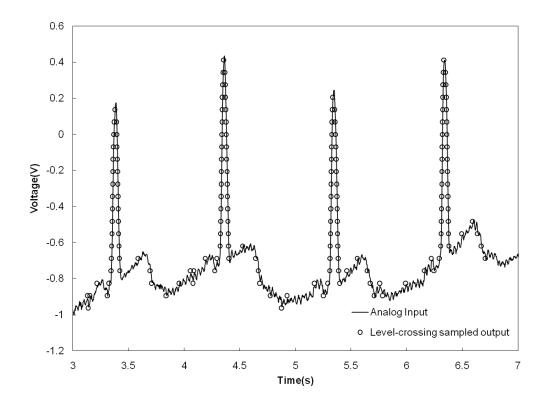

To find the sampling resolution suitable for ECG signals, Matlab simulations were performed on real ECG signals retrieved from the MIT-BIH database [39]. These signals in the database have already been digitized at 360 Hz and 11 bits using conventional uniform sampling. To make them suitable for level-crossing sampling, these signals were first up-sampled to 36 kHz so that they behave

nearly the same as analog signals, which are supposed to be seen by levelcrossing ADCs in real scenarios. Extensive level-crossing sampling simulations with different values of N were then conducted on different ECG records. With a 3-bit quantizer used in the level-crossing ADC, the ECG waveforms are barely captured: only the QRS waves are captured with all other details lost. Even for the QRS waves the peak heights are not accurately reflected due to the coarse quantization intervals. Better results are achieved when N=4: the QRS peaks are more accurate, although the P and T waves are still missed occasionally. The positions of these small waves are however of vital importance for diagnosis, which calls for an even higher sampling resolution. The results become

Fig. 3.4 Level-crossing sampling of ECG signal #151 retrieved from the MIT-BIH arrhythmia database. The solid curve represents the original analog input and the series of bubbles represent the level-crossing sampled output.

satisfactory when *N* is increased to 5 bits. Most of the details are well preserved in the digitization process. Fig. 3.4 shows a portion of the level-crossing sampling result of record 151 using a 5-bit quantizer. The resulting average sampling rate is around 40 Hz, with slight deviations among different ECG records. An 88.8% reduction is achieved in the sampling frequency as compared to the original signal, yet negligible sacrifice is incurred in signal quality thanks to the signal-dependent adaptive-rate sampling of level-crossing ADC.

The high-frequency noise present in the original signal also needs to be suppressed by introducing hysteresis. Despite the gain of noise immunity and better robustness, the introduction of hysteresis also causes a certain degree of distortion to the digitized output due to the nonlinearities involved in this operation [21]. A proper choice for the value of  $\delta_{hyst}$  is therefore needed to achieve a good balance between the pros and cons. The best amount of hysteresis should be one that is just enough to prevent noise-induced toggling so that the amount of distortion introduced is minimized. By observing the ECG records from the MIT-BIH database, it was noticed that most of the fluctuations caused by noise have peak-to-peak amplitudes of no more than a quarter of one quantization interval corresponding to a 5-bit quantizer. Therefore,  $\delta_{hyst}$  was chosen to be 25%. This parameter of a level-crossing ADC can also be made tunable to accommodate different noise levels under different circumstances.

# **3.3 Interpolation**

# **3.3.1** Comparison of Interpolation Methods

Due to the many reasons mentioned in Section 3.2.1, the nonuniform samples obtained from the level-crossing ADC must first be converted to uniform format before any traditional DSP techniques can be applied. Of course uniform oversampling would serve the purpose but that again makes the sampling rate high, canceling the benefit of reduced power consumption achieved by levelcrossing sampling. Therefore, various interpolation techniques were investigated to achieve the uniform conversion while keeping the total number of samples the same. Predicting signal values from neighboring samples may sound risky, but considering the event-driven nature of level-crossing sampling it is realized that the signal value between any two consecutive samples is in fact guaranteed to be bounded between those two samples, since any further crossing of quantization boundaries will trigger the ADC to produce additional samples. Therefore, it is fair to conclude that extracting information through interpolation is safe for levelcrossing sampled data.

Theoretically, if the time and amplitude values of the nonuniform samples are known to infinite precision, it is possible to compute the amplitude at any time

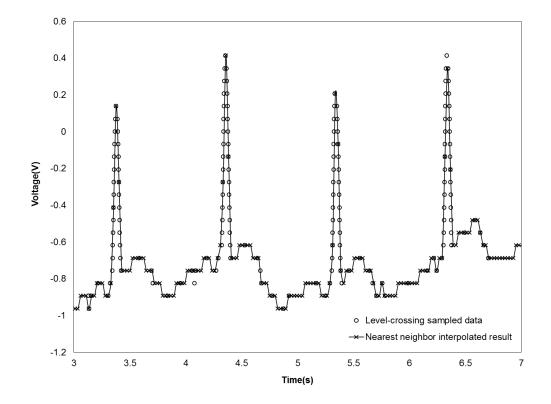

Fig. 3.5 Nearest neighbor interpolation result of the level-crossing sampled data obtained in Fig. 3.4. The series of bubbles represent the level-crossing sampled data, and the solid curve with crosses on it represents the nearest neighbor interpolated result.

instant to infinite precision using an infinite degree interpolation polynomial. This is obviously not the case in practical scenarios, since the sample values are only known to a finite precision (5 bit in this case), and any interpolation scheme must also have a finite order for it to be implementable. Therefore, classical techniques including nearest neighbor interpolation, linear interpolation and cubic interpolation are explored and compared.

Nearest neighbor interpolation is the simplest interpolation wherein the value at the interpolated point is assigned with the value of the closest point [40]. In terms of computational efficiency this is the best since it requires no multiplication at all. However, the signal quality of nearest neighbor interpolation is poor. A staircase-like waveform is obtained after the interpolation as shown in Fig. 3.5.

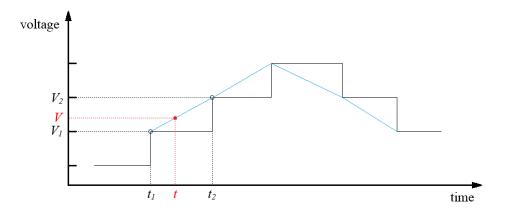

As shown in Fig. 3.6, for linear interpolation, the weighted average of the two closest nonuniform samples at  $t_1$  and  $t_2$  is taken to be the value of the interpolated

Fig. 3.6 Illustration of linear interpolation

point at t [40], given by

$$V(t) = V_1 + (V_2 - V_1) \frac{t - t_1}{t_2 - t_1}.$$

(3-5)

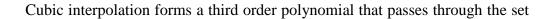

The computational complexity of linear interpolation is higher than that of the nearest neighbor interpolation, but the signal quality is significantly better. Fig. 3.7 shows the linearly interpolated result from the nonuniform samples obtained in Fig. 3.4. The pointwise average error between the linearly interpolated result and the original input is only 1.53%.

Fig. 3.7 Linear interpolation result of the level-crossing sampled data obtained in Fig. 3.4. The series of bubbles again represent the level-crossing sampled data, and the solid curve with crosses on it represents the linearly interpolated result.

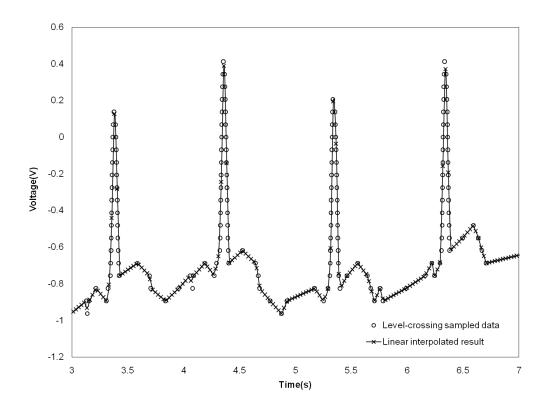

Fig. 3.8 Cubic interpolation result of the level-crossing sampled data obtained in Fig. 3.4. The series of bubbles again represent the level-crossing sampled data, and the solid curve with crosses on it represents the cubic interpolated result.

of interpolated points between any two nonuniform samples [40]. The detailed algorithm is very complex and is not presented here. Such complexity translates into increased circuit area and power consumption, but the signal quality for this case is in fact not any better: The resulting waveform is plotted in Fig. 3.8. The pointwise average error of the cubic interpolated signal is 1.59%, which is slightly higher than that of linear interpolation.

With the above comparison, linear interpolation is chosen for the proposed processing scheme due to its nice balance between signal quality and computational efficiency.

#### 3.3.2 Implementation of Linear Interpolator

Having decided to adopt linear interpolation, the interpolation frequency  $f_i$  and interpolation resolution M are two parameters need to be determined. The spacing between neighboring interpolated points is determined by  $f_i$ . Similar to the choice of level-crossing sampling resolution N, the choice of  $f_i$  is again a tradeoff between signal quality and power consumption. The parts of ECG signals that are most sensitive to changes in the interpolation frequency are the QRS waves, where the fastest changes take place. If the frequency is not high enough, these fast changes are more likely to be distorted than the slowly varying P and T waves. Matlab simulation shows that when  $f_i = 30$ Hz, the interpolation results suffer severe information loss at the QRS portions. Even when  $f_i$  is increased to 40Hz, the peak heights are not always accurately reflected. Satisfactory interpolation cannot be achieved until  $f_i$  is increased to 50Hz, when all the QRS waves are well preserved in the linear interpolation process.

When linear interpolation is performed, there is also a need for increase in the quantization resolution. If the interpolation results keep the same quantization resolution of the level-crossing ADC, which is 5 bits in this case, then each interpolated point will have the exact same value as one of the two samples  $V_1$  and  $V_2$ , depending on which one is closer. This effectively becomes nearest neighbor interpolation. To get more accurate results through linear interpolation, each quantization interval must be further divided, which means the interpolation resolution M needs to be higher than the sampling resolution N. Extensive simulation is again performed for different values of M. The interpolated signal is

|                  | Average Error (%) |              |              |              |

|------------------|-------------------|--------------|--------------|--------------|

| ECG record index | <i>M</i> =9       | <i>M</i> =10 | <i>M</i> =11 | <i>M</i> =12 |

| 100              | 1.64              | 0.94         | 0.64         | 0.55         |

| 101              | 1.67              | 0.94         | 0.65         | 0.56         |

| 102              | 1.68              | 0.92         | 0.61         | 0.52         |

| 103              | 1.81              | 1.07         | 0.75         | 0.65         |

| 104              | 1.77              | 1.04         | 0.74         | 0.64         |

| 105              | 1.65              | 0.93         | 0.65         | 0.58         |

| 106              | 1.76              | 0.99         | 0.69         | 0.60         |

| 111              | 1.74              | 0.93         | 0.61         | 0.52         |

| 221              | 1.73              | 0.97         | 0.68         | 0.61         |

Table 3.1 Linear interpolation error for different resolutions

compared to the original ECG signal by computing the point-wise average error between the 36kHz-upsampled versions of the two. The results are summarized in Table 3.1. As can be seen from this table, the average error drops significantly as M is increased from 9 bits to 11 bits, but the improvements brought by further increase from 11 bits onwards are marginal. The interpolation resolution is therefore chosen to be 11 bits.

Fig. 3.10 shows the block diagram of the linear interpolator implemented. Although interpolations can be carried out in real time, there has to be a small amount of delay between the level-crossing sampled signal and the interpolated signal. This is due to the non-causality of a linear interpolation system: as can be

Fig. 3.10 Implementation of the linear interpolator. The main blocks include a memory buffer, a data loader, a computing unit, an interpolation counter and a load counter.

Fig. 3.9 Illustration for the need of a memory buffer in the linear interpolator

seen from Fig. 3.6, the interpolated value at t not only depends on a past sample at  $t_1$ , but also depends on a future sample at  $t_2$ . As illustrated in Fig. 3.9, in cases when the level-crossing samples, as represented by the bubbles, are much sparser than the interpolation interval  $T_i$ , then all the interpolated points sandwiched between  $t_1$  and  $t_2$  will depend on the sample at  $t_2$  that comes much later. A delay

that equals the maximum possible time difference  $T_{max}$  between  $t_1$  and  $t_2$  must therefore be waited before any interpolation can be carried out. For my case, this value is 0.25 seconds. During this period however, there could also be a large number of samples arriving, depending on the rate of change in the analog input. These samples need to be saved temporarily for the computations performed 0.25s later. A buffer is therefore employed for this purpose. Its capacity is determined in such a way that the maximum number of samples generated by the 5-bit levelcrossing ADC within 0.25 seconds can be stored. Every time a new sample is received, both its sample value and its quantized time spacing from the earlier sample will be saved into the buffer with the oldest set of data discarded. However, it is always guaranteed that any sample points generated within the past 0.25s are ready to be retrieved from the buffer.

The interpolation counter serves two purposes. The first is to hold the rest of the circuits idling for 0.25s upon start-up, as samples are being accumulated in the buffer, and then wake them up 0.25s later by asserting the "Start Flag". The second is to request an interpolation result from the computing unit every 0.02s, according to the 200Hz interpolation frequency.

The load counter is adopted to control data loading from the memory buffer to the data loader, the outputs of which will be fed into the computing unit for computations of interpolated results upon requests from the interpolation counter. Every time a new sample is loaded into the data loader, the load counter will be reset to zero. Once this counter reaches the time spacing of  $t_2$ - $t_1$  for the current pair of samples loaded in the data loader, a new sample will be read into the register for  $V_2$  from the buffer, and the old  $V_2$  value is passed to the register for  $V_1$ . The same updates happen for the timing data.