# Ultra High Voltage IC design

With a 400V CMOS technology, a dimmer application.

### Fabián Torres Álvarez

Supervisors: Alfredo Arnaud Joel Gak A thesis presented for the degree of Master of Science

Department of Engineering Universidad Católica del Uruguay Montevideo, Uruguay June 23, 2020

## **Resumen Publicable**

Con la popularización de tecnologías de fabricación de circuitos integrados de ultra alto voltaje (UHV), surge la posibilidad de diseñar circuitos integrados conectados directamente a la red de distribución, con aplicaciones en fuentes compactas, domótica, smart-grids, entre otras.

Este proyecto propone el diseño, fabricación y caracterización de circuitos en tecnología UHV. Se toma como ejemplo un atenuador por corte de fase de dos terminales.

Al momento de escribir esta tesis, no existen circuitos integrados comerciales que implementan un atenuador por corte de fase completo, ni se pudo encontrar artículos académicos haciendo referencia a dispositivos similares.

El circuito fue diseñado en una tecnología de 1 µm UHV MOS (XDM10 de XFAB) en una oblea de silicio sobre aislante (SOI). Puede operar con un ciclo de trabajo hasta 95 % de potencia (80 % en tiempo) y una carga de hasta 100 W, lo que es adecuado para lámparas atenuables de LED.

El área total de silicio ocupada es de  $6.5 \,\mathrm{mm}^2$  sin contar pads. Debido a limitaciones tecnológicas, la versión final del atenuador es casi completamente integrada. Dos capacitores de bajo voltaje y cuatro diodos UHV quedan por fuera del ASIC.

Palabras Clave — circuitos integrados, ultra alto voltaje, dimmer, bajo consumo

## Abstract

The advent of Ultra High Voltage (UHV) technologies for integrated circuit fabrication opens up new possibilities for the design of circuits that connect directly to the power distribution network, with applications in the design of compact power sources, domotics, smart-grids, etc.

This project proposes the design, fabrication and characterization of circuits in an UHV technology, of which a fully integrated two terminal phase-cut dimmer was chosen as an example.

At the time of writing this thesis, no commercially available integrated circuit exists that fully implements a phase cut dimmer, and no academic papers could be found referencing similar circuits.

The circuit was designed on a  $1 \,\mu\text{m}$  UHV MOS technology in a silicon-on-insulator (SOI) wafer (XDM10 from XFAB). The dimmer can operate with a duty cycle of up to 95% power (80% time) and a load of up to 100 W which is adequate for modern domestic dimmable LED lights.

The total occupied silicon area is  $6.5 \text{ mm}^2$  without pads. Because of technological limitations, the final version of the dimmer is almost fully integrated. Two low voltage capacitors and four UHV diodes are outside the ASIC.

Index Terms — integrated circuits, ultra high voltage, dimmer, low power

# Acknowledgements

I would like to thank projects POS\_NAC\_2017\_1\_140389 and FCE\_3\_2018\_1\_148263 which provided financial support for the development and fabrication of this thesis.

I would like to thank all the free software developers who spent their time and effort into creating many of the tools that made this project possible asking for nothing in return.

# Contents

| 1        | Intr           | roduction                               | <b>11</b> |

|----------|----------------|-----------------------------------------|-----------|

|          | 1.1            | The problem                             | 11        |

|          | 1.2            | In this thesis                          | 11        |

|          | 1.3            | State of the art                        | 12        |

|          |                | 1.3.1 Leading and Trailing Edge Dimmers | 12        |

|          | 1.4            | Motivation                              | 12        |

|          | 1.5            | Circuit Scheme                          | 13        |

|          | 1.6            | Dimmer specifications                   | 14        |

| <b>2</b> | UH             | V CMOS Technology Description           | 16        |

|          | 2.1            | Introduction                            | 16        |

|          | 2.2            | XDM10                                   | 16        |

| 3        | Cire           | cuit Description                        | 20        |

|          | 3.1            | UHV Power Switches                      | 20        |

|          | 3.2            | Gate Driver                             | 25        |

|          | 3.3            | Power Management                        | 29        |

|          |                | 3.3.1 Maximum Duty Cycle                | 29        |

|          |                | 3.3.2 Circuit Implementation            | 32        |

|          |                | 3.3.3 Sizing                            | 39        |

|          | 3.4            | Zero Crossing Detector                  | 43        |

|          |                | 3.4.1 Sizing                            | 45        |

|          | 3.5            | Control Logic                           | 46        |

|          | 3.6            | Top Level                               | 49        |

| 4        | $\mathbf{Sim}$ | nulations                               | 51        |

|          | 4.1            | Switches                                | 51        |

|          |                | 4.1.1 DC transfer                       | 51        |

|          |                | 4.1.2 Transient simulation              | 52        |

|          | 4.2            | Power Management System                 | 56        |

|          |                | 4.2.1 Start Up                          | 56        |

|          |                | 4.2.2 Steady State, Idle                | 58        |

|          |                | 4.2.3 Steady State, Maximum Duty Cycle  | 59        |

|          | 4.3            | Zero Crossing Detector                  | 63        |

|          |                | 4.3.1 Transient Simulation              | 63        |

|          |                | 4.3.2 DC Transfer                       | 66        |

|          | 4.4            | Top Level Circuit                       | 68        |

|          |                | 4.4.1 Typical                           | 68        |

|   |                                 | $4.4.2 \\ 4.4.3$                                                      |                                                                                                                   | 69<br>69                                                                                            |  |  |  |

|---|---------------------------------|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|--|--|--|

| 5 | Lay<br>5.1<br>5.2<br>5.3        | Switch<br>Gate I<br>Power<br>5.3.1<br>5.3.2                           | es                                                                                                                | <b>72</b><br>72<br>73<br>74<br>74<br>74<br>74<br>74                                                 |  |  |  |

|   | $5.5 \\ 5.6$                    | Input/                                                                | Output                                                                                                            | 78<br>78                                                                                            |  |  |  |

| 6 | Mea<br>6.1<br>6.2<br>6.3<br>6.4 | 6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>Switch<br>6.3.1<br>6.3.2<br>6.3.3 | Low Voltage DC                                                                                                    | <b>83</b><br>84<br>84<br>84<br>85<br>87<br>87<br>88<br>91<br>93<br>95<br>95<br>96<br>96<br>98<br>98 |  |  |  |

| 7 | <b>Con</b><br>7.1               | <b>clusio</b><br>Future                                               |                                                                                                                   | <b>99</b><br>.00                                                                                    |  |  |  |

| A | Appendices 104                  |                                                                       |                                                                                                                   |                                                                                                     |  |  |  |

|   | A.1<br>A.2<br>A.3<br>A.4        | Incanc<br>LED I<br>LED I                                              | lescent Lamp       1         Lamp       1         Lamp       1         Lamp       2         Joic LED Lamp       1 | 05<br>06<br>07<br>08<br>09<br>10                                                                    |  |  |  |

# List of Figures

| $1.1 \\ 1.2 \\ 1.3$ | Application diagram of a phase cut dimmer                                      | 12<br>13<br>14                       |

|---------------------|--------------------------------------------------------------------------------|--------------------------------------|

| 1.4                 | Top level blocks for the UHV dimmer                                            | 15                                   |

| $2.1 \\ 2.2$        | XDM10 core module cross section for low voltage CMOS transistors               | $\begin{array}{c} 17\\18\end{array}$ |

|                     |                                                                                |                                      |

| 3.1                 | Switching device options offered by the working technology.                    | 20                                   |

| 3.2                 | Switches block architecture options.                                           | 21                                   |

| 3.3                 | Current flow on switches options                                               | 22                                   |

| 3.4                 | I–V curve for the unit IGBT included in XDM10                                  | 23                                   |

| 3.5                 | Peak heat IGBT dissipation                                                     | 24                                   |

| 3.6                 | Switches block symbol                                                          | 24                                   |

| 3.7                 | Level Shifter used as a Gate Driver                                            | 25                                   |

| 3.8                 | 20  V MOS transfer testbench                                                   | 26                                   |

| 3.9                 | MOS transfer test bench results                                                | 27                                   |

| 3.10                | Gate Driver Symbol                                                             | 28                                   |

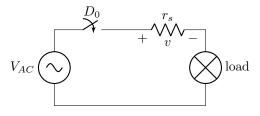

|                     | Application diagram of a phase cut dimmer                                      | 29                                   |

|                     | Two terminal phase cut dimmer in open state.                                   | 29                                   |

|                     | Two terminal phase cut dimmer in closed state                                  | 29                                   |

|                     | Chopped Sine Wave example                                                      | 31                                   |

|                     | Portion of the energy reaching the load plotted against the dimmer duty cycle. | 33                                   |

|                     | Power System simplified                                                        | 34                                   |

|                     | Power System current paths                                                     | 35                                   |

|                     | Full implementation for the power system                                       | 36                                   |

| 3.19                | Full implementation for the diode divider                                      | 37                                   |

| 3.20                | Diode divider symbol.                                                          | 38                                   |

|                     | Power System block symbol                                                      | 38                                   |

|                     | Current flow through the power management system in low power mode             | 40                                   |

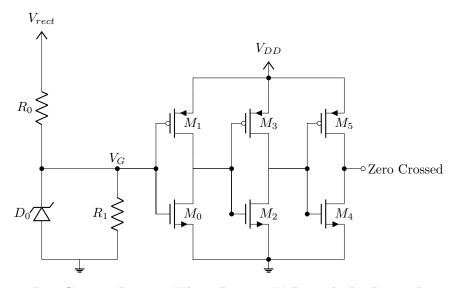

|                     | Zero Crossing Detector schematic                                               | 43                                   |

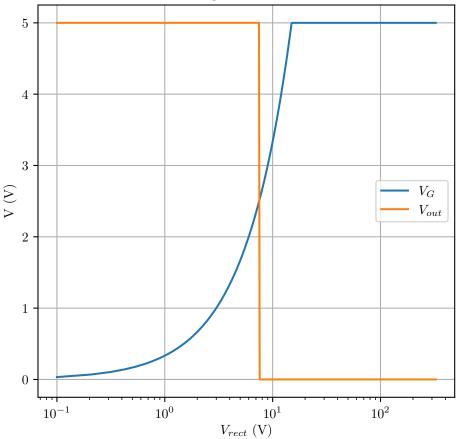

|                     | Zero Crossing Detector DC transfer                                             | 44                                   |

|                     | Zero Crossing Detector block symbol.                                           | 45                                   |

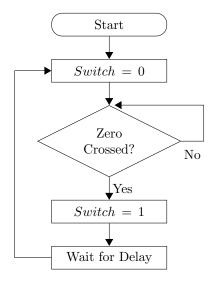

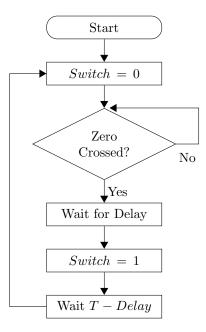

| 3.26                | Leading edge dimer flow chart                                                  | 46                                   |

|                     | Trailing edge dimer flow chart                                                 | 47                                   |

|                     | Control Logic symbol.                                                          | 48                                   |

|                     | Dimmer Top Level block diagram                                                 | 49                                   |

| 3.30                | Dimmer ASIC symbol                                                             | 49                                   |

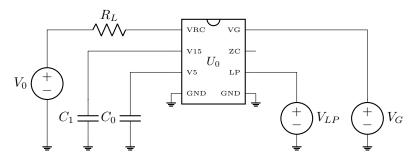

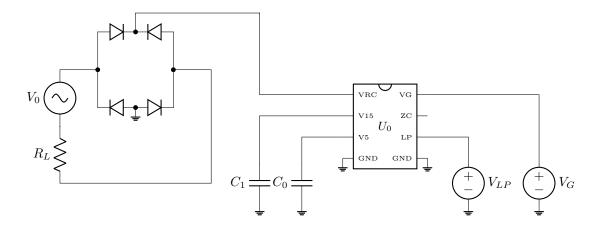

| 3.31       | Dimmer ASIC typical set up                                                     | 50         |

|------------|--------------------------------------------------------------------------------|------------|

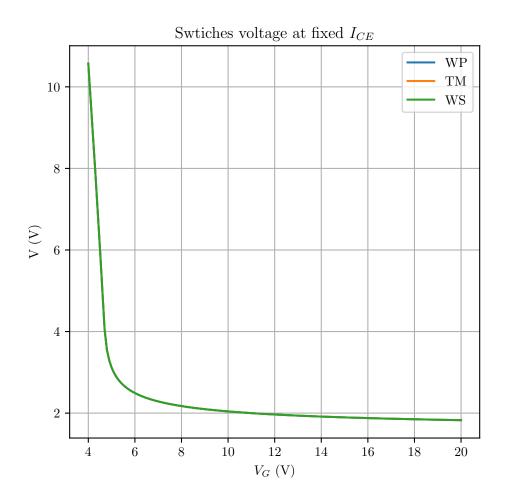

| 4.1        | Schematic of the DC simulation done on the Switches block                      | 52         |

| 4.1        | DC Simulation for Switches.                                                    | $52 \\ 53$ |

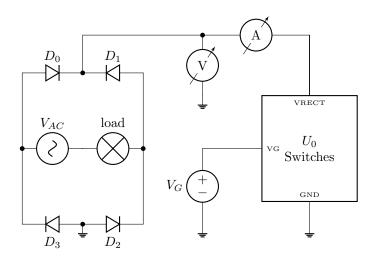

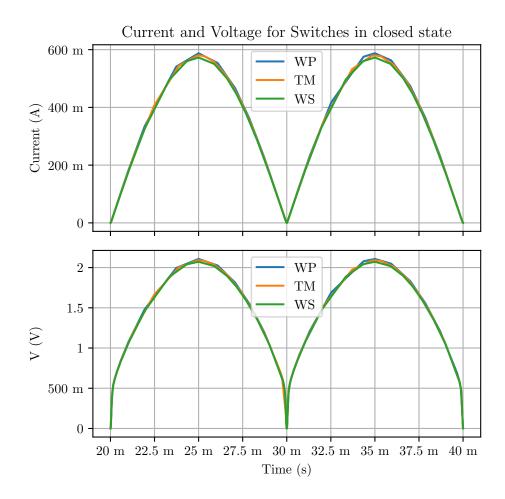

| 4.3        | Schematic of the transient simulation done on the switches block.              | 55 54      |

| 4.3<br>4.4 | Simulation for closed Switches.                                                | 55         |

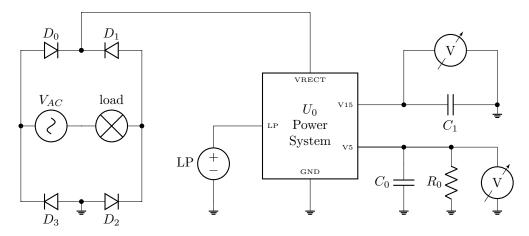

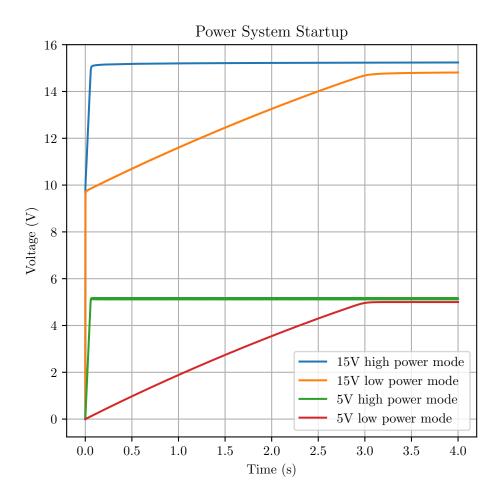

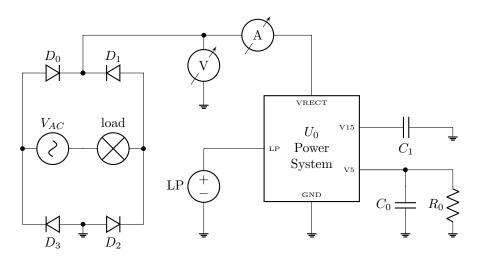

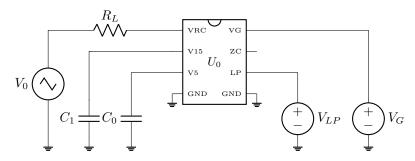

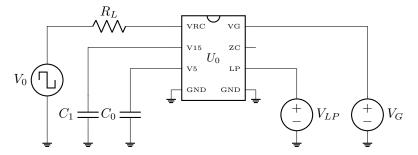

| 4.5        | Power System start up simulation schematic.                                    | 56         |

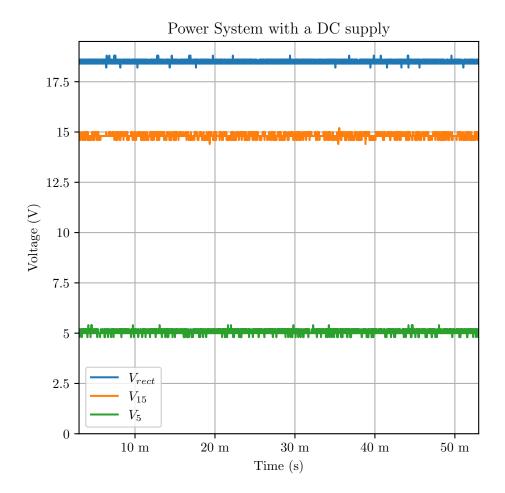

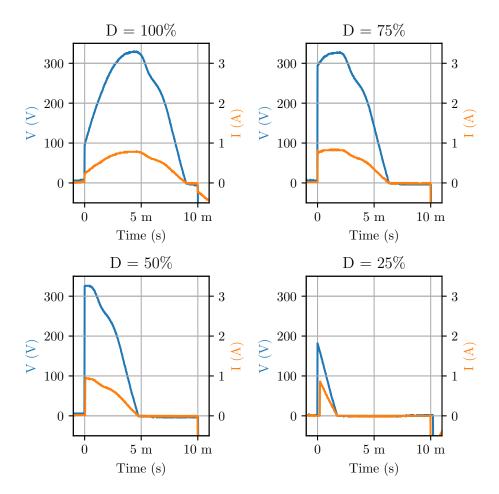

| 4.6        | Power System start up simulation                                               | 57         |

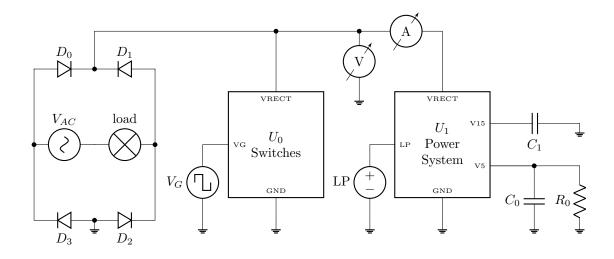

| 4.7        | Schematic of the transient simulation for the Power Management System at max-  | 01         |

|            | imum power conditions.                                                         | 58         |

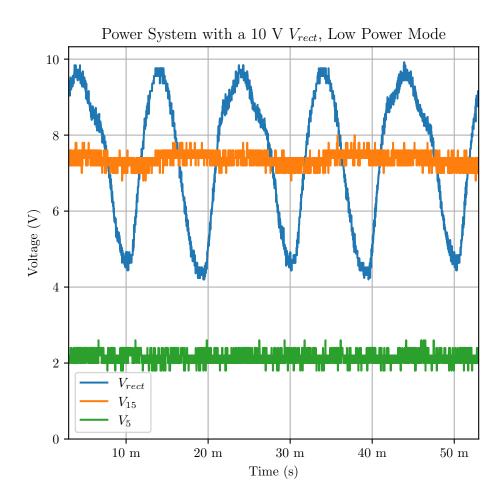

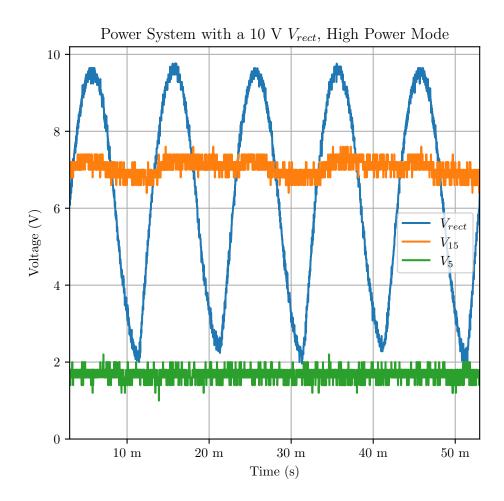

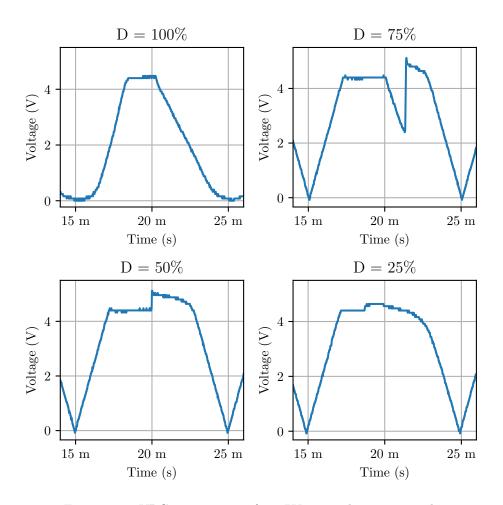

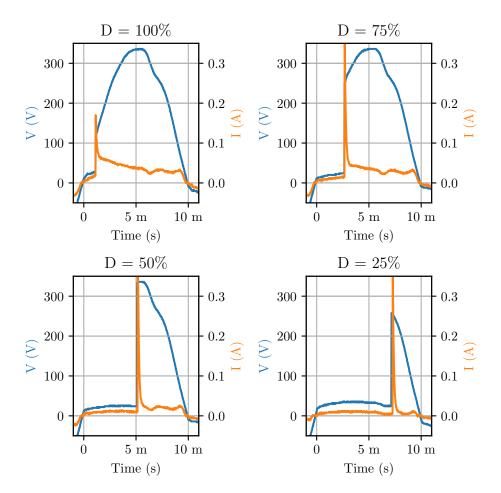

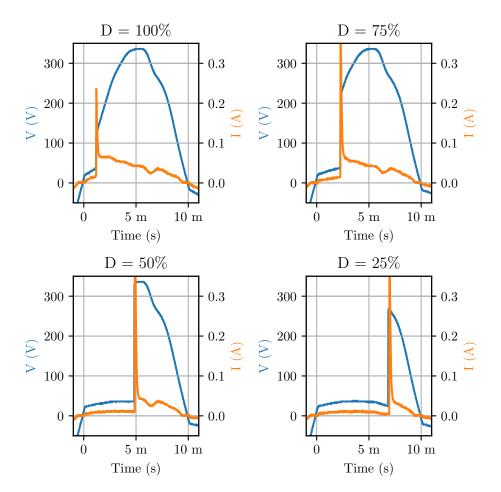

| 4.8        | Power management max power transient simulation for low and high power mode.   | 59         |

| 4.9        | Schematic of the transient simulation done on the Power Management System at   |            |

|            | maximum duty cycle conditions.                                                 | 61         |

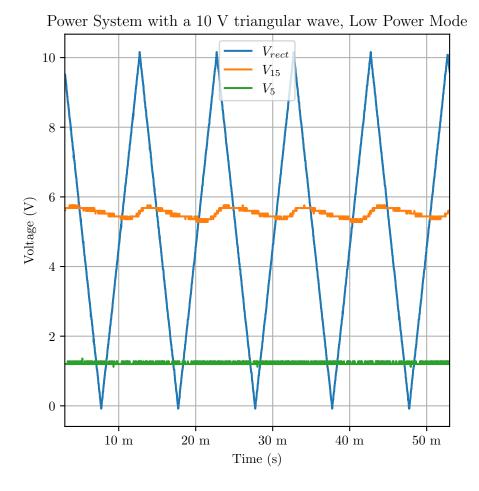

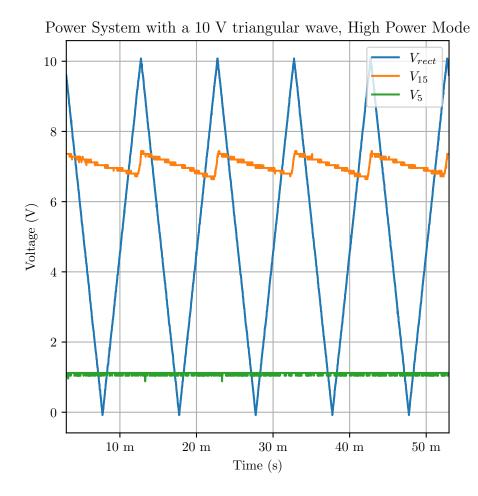

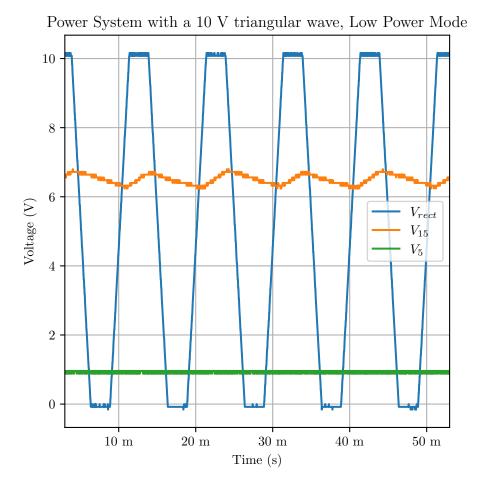

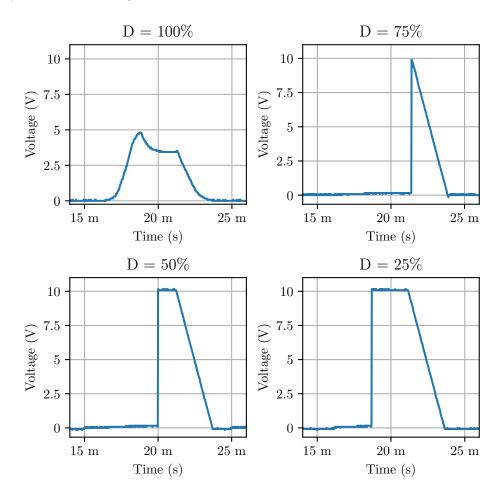

| 4.10       | Power management max duty cycle transient simulation for low and high power    |            |

|            | mode                                                                           | 62         |

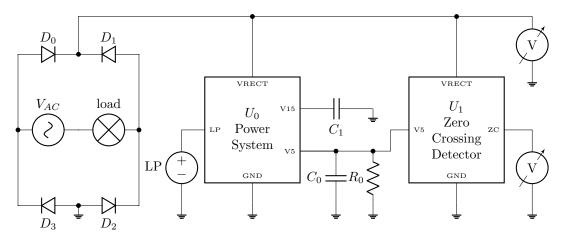

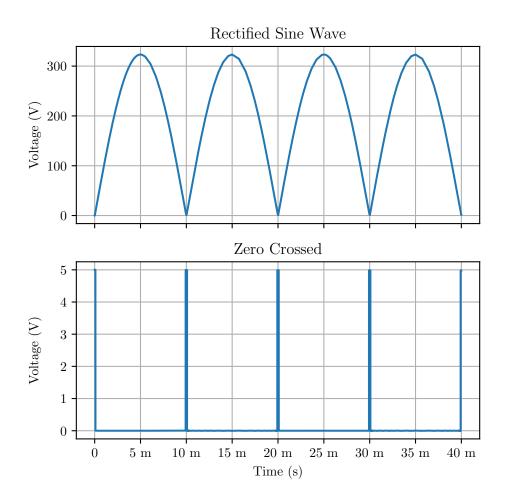

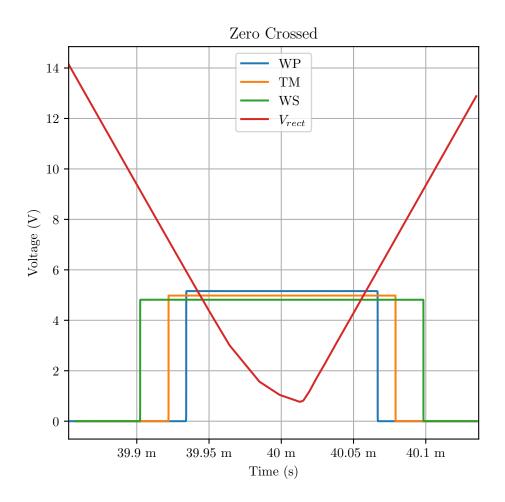

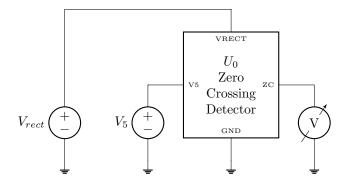

|            | Schematic for the Zero Crossing detector transient simulator.                  | 63         |

|            | Zero Crossing detector transient simulation                                    | 64         |

|            | Zero Crossing detector transient corner simulations for detection threshold    | 65         |

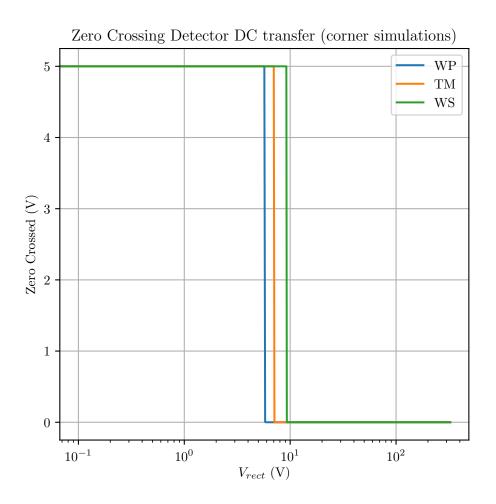

|            | Zero Crossing Detector DC sweep simulation schematic.                          | 66         |

|            | Zero Crossing Detector DC transfer.                                            | 67         |

|            | Top level transient simulation test bench.                                     | 68         |

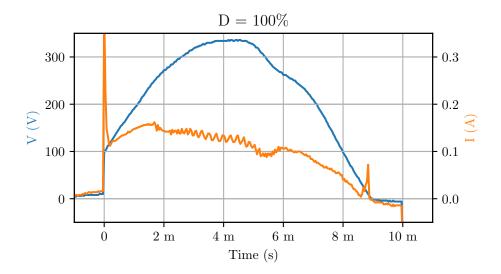

|            | Top level transient simulation for the UHV dimmer.                             | 69         |

|            | Top level transient simulation for the UHV dimmer in idle state.               | 70         |

| 4.19       | Top level transient simulation for the UHV dimmer at maxduty cycle, high power | = 1        |

|            | mode                                                                           | 71         |

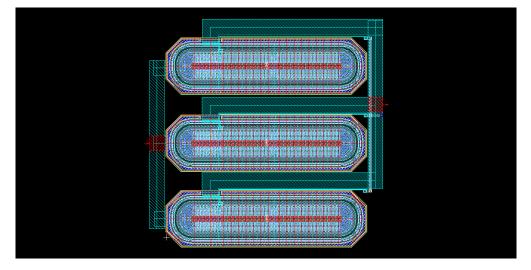

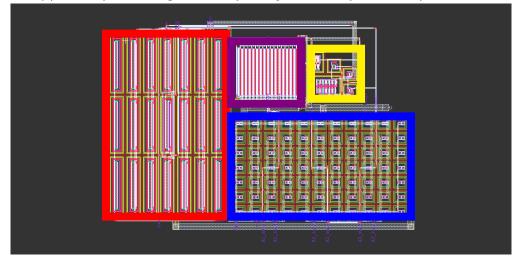

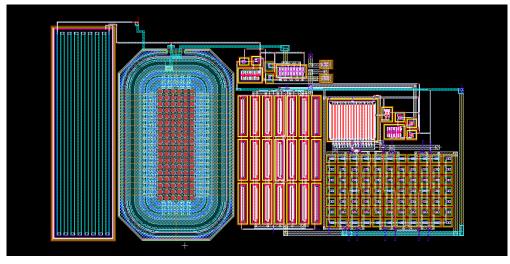

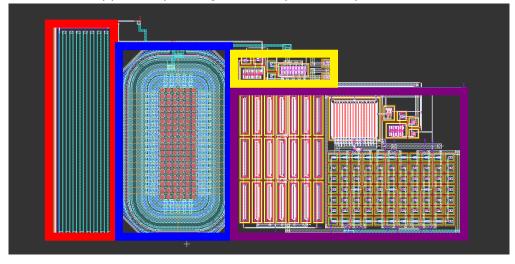

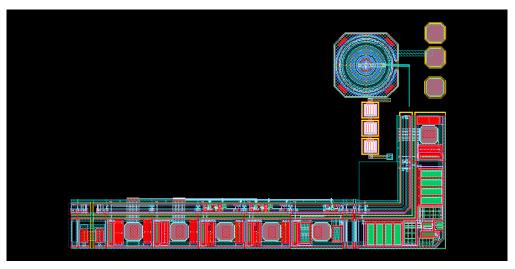

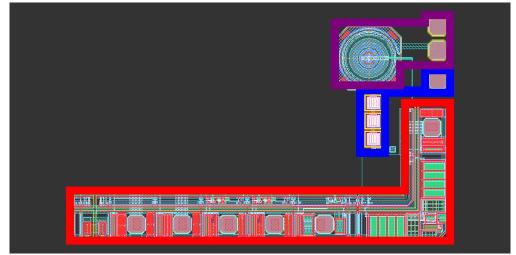

| 5.1        | Switches layout of the UHV dimmer.                                             | 72         |

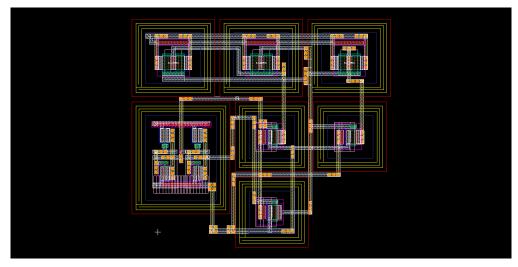

| 5.2        | Gate Driver layout of the UHV dimmer                                           | 73         |

| 5.3        | Power System Voltage Divider layout of the UHV dimmer                          | 75         |

| 5.4        | Power System layout of the UHV dimmer                                          | 76         |

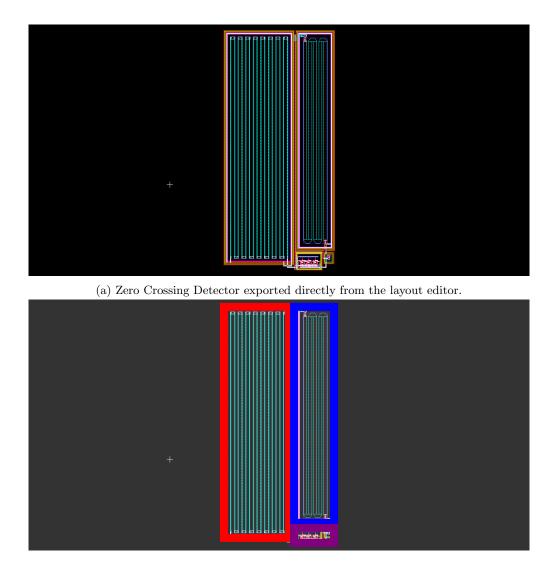

| 5.5        | Zero Crossing Detector layout of the UHV dimmer                                | 77         |

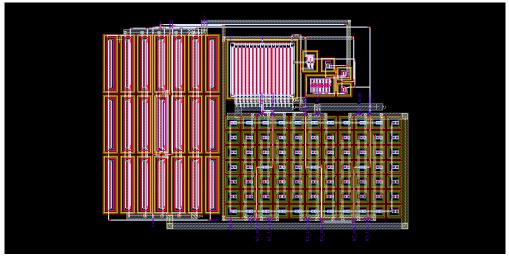

| 5.6        | IO layout of the UHV dimmer.                                                   | 79         |

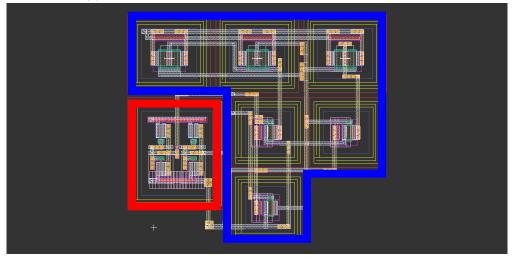

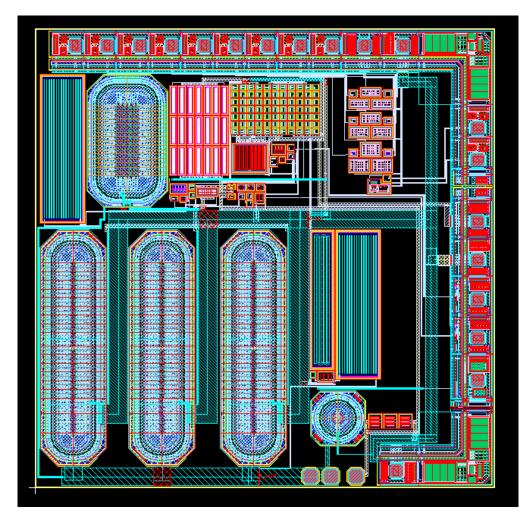

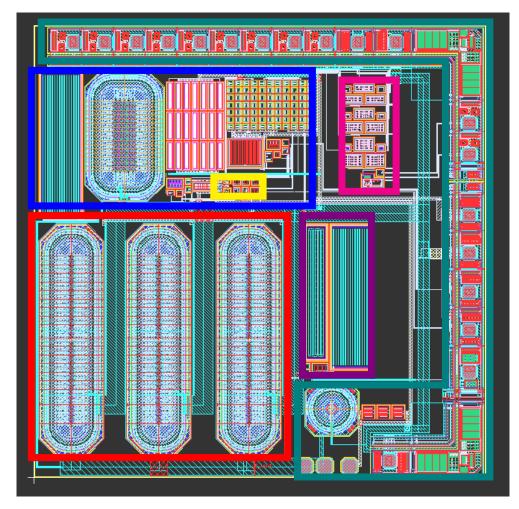

| 5.7        | Top level layout of the UHV dimmer.                                            | 80         |

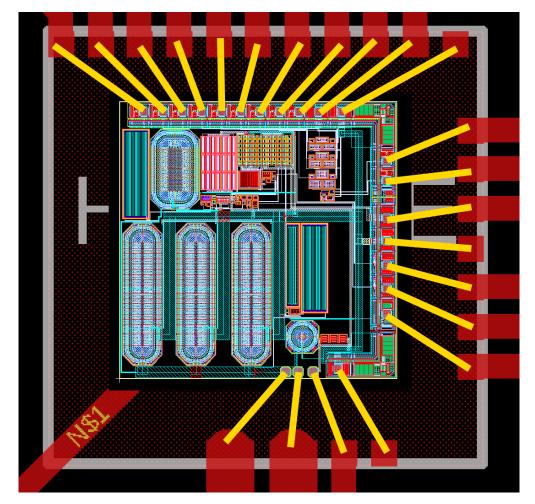

| 5.8        | Top level layout annotated.                                                    | 81         |

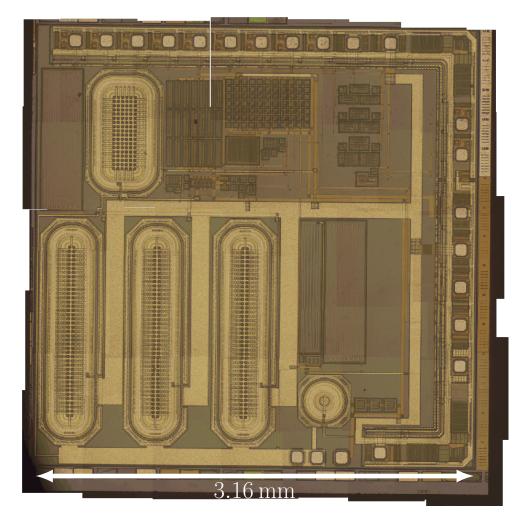

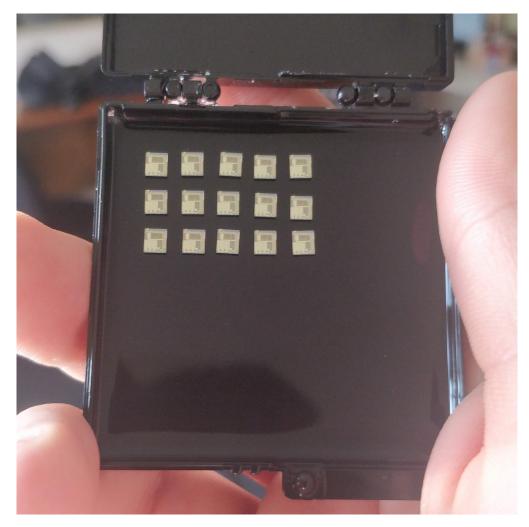

| 5.9        | Microscope picture of the ASIC                                                 | 82         |

|            |                                                                                |            |

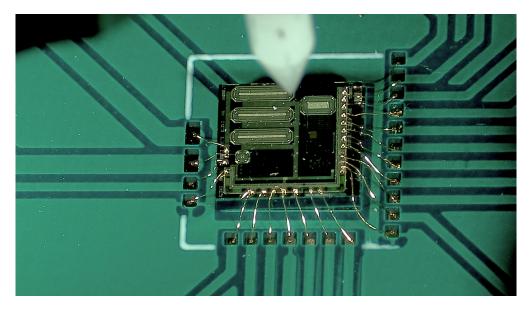

| 6.1        | Physical bonding of the dimmer chip.                                           | 83         |

|            | Measurement setup for LV DC signal                                             | 84         |

| 6.3        | Measurement set up for LV sine wave signal                                     | 85         |

| 6.4        | Measurement set up for LV triangular wave signal                               | 86         |

| 6.5        | Measurement set up for LV trapeze wave signal                                  | 86         |

| 6.6        | Power System measurement for a LV DC signal, in High Power Mode                | 87         |

| 6.7        | Power System measurement for a LV sine wave signal, in Low Power Mode          | 89         |

| 6.8        | Power System measurement for a LV sine wave signal, in High Power Mode         | 90         |

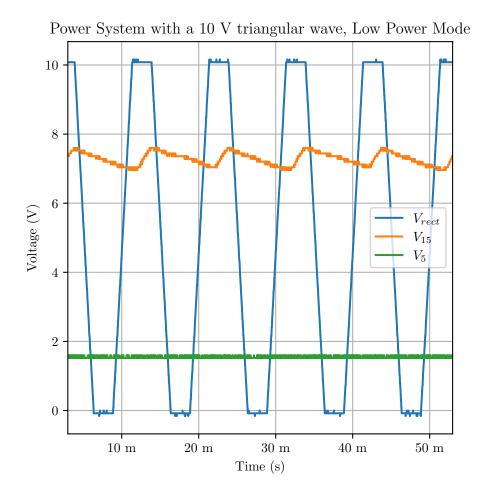

| 6.9        | Power System measurement for a LV triangular wave signal, in Low Power Mode.   | 91         |

|            | Power System measurement for a LV triangular wave signal, in High Power Mode.  | 92         |

|            | Power System measurement for a LV trapeze wave signal, in Low Power Mode.      | 93         |

|            | Power System measurement for a LV trapeze wave signal, in High Power Mode.     | 94         |

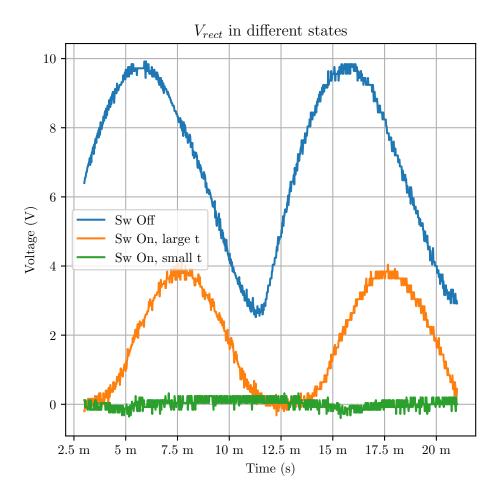

| 6.13       | VRC measurement for a LV sine wave signal.                                     | 95         |

| 6.14 | VRC measurement for a LV trapeze wave signal.                                  | 96  |

|------|--------------------------------------------------------------------------------|-----|

| 6.15 | VRC measurement for a LV triangular wave signal.                               | 97  |

| 6.16 | Zero Crossing Detector measurement for a LV sine wave signal                   | 98  |

| A.1  | Lamps current measurement schematic                                            | 105 |

| A.2  | Incandescent lamp measurements                                                 | 106 |

| A.3  | LED lamp 1 measurements                                                        | 107 |

| A.4  | LED lamp 2 measurements                                                        | 108 |

| A.5  | Dichroic LED lamp measurements                                                 | 109 |

| B.1  | Manufactured chip without encapsulation                                        | 111 |

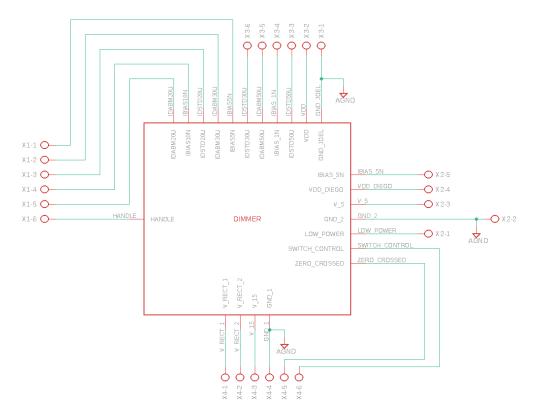

| B.2  | Schematic of the PCB designed for bonding the dimmer ASIC                      | 112 |

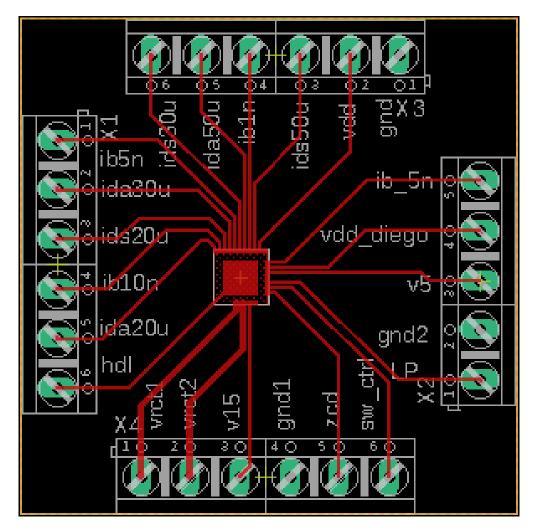

| B.3  | Layout of the PCB designed for bonding the dimmer ASIC.                        | 113 |

| B.4  | Bonding diagram of the PCB from Figure B.3 and the ASIC from Figure B.1. $\ .$ | 114 |

# List of Tables

| 1.1          | Target design specifications.                                                      | 15       |

|--------------|------------------------------------------------------------------------------------|----------|

| $2.1 \\ 2.2$ | Technology devices summary reference table                                         | 17<br>18 |

| 2.3          | XDM10 MV MOS device characteristics.                                               | 18       |

| 2.4          | XDM10 UHV MOS device characteristics.                                              | 18       |

| 2.5          | XDM10 IGBT device characteristics.                                                 | 19       |

| 2.6          | XDM10 BJT device characteristics.                                                  | 19       |

| 2.7          | XDM10 resistors device characteristics                                             | 19       |

| 2.8          | XDM10 diodes device characteristics                                                | 19       |

| 2.9          | XDM10 power metal device characteristics                                           | 19       |

| 3.1          | MOS transfer SPICE simulation input data                                           | 26       |

| 3.2          | MOS transfer SPICE simulation results.                                             | 26       |

| 3.3          | Size relation for the Gate Driver MOS transistors according to Equations 3.2       |          |

|              | and 3.3 with the results from the simulations shown in Table 3.2.                  | 28       |

| 3.4          | Device dimensions for transistors in the Level Shifter                             | 28       |

| 3.5          | Maximum duty cycle by design                                                       | 32       |

| 3.6          | Device dimensions for the full implementation of the power system shown in Fig-    |          |

|              | ure 3.18 on page 36                                                                | 41       |

| 3.7          | Device dimensions for the Power System Diode Divider                               | 42       |

| 3.8          | Device dimensions for the Zero Crossing Detector.                                  | 45       |

| 4.1          | Switches DC simulation values                                                      | 51       |

| 4.2          | Switches DC simulation result.                                                     | 52       |

| 4.3          | Simulation for Switches                                                            | 52       |

| 4.4          | Power System start up simulation device values.                                    | 56       |

| 4.5          | Power management start up convergence voltage and time                             | 57       |

| 4.6          | Initial Conditions for Power System steady state simulation at maximum power.      | 58       |

| 4.7          | Average current for the Power System steady state at maximum power                 | 60       |

| 4.8          | Initial Conditions for Power System steady state simulation at maximum duty cycle. | 60       |

| 4.9          | Average current for the transient simulation of the Power Management System at     |          |

|              | maximum duty cycle condition                                                       | 60       |

|              |                                                                                    | 63       |

|              | Detection threshold voltage Zero Crossing Detector corners                         | 66       |

|              |                                                                                    | 68       |

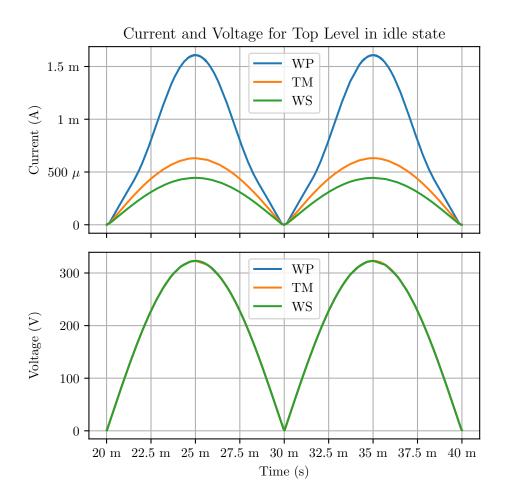

|              | Average Power consumed by the ASIC in idle state.                                  | 69       |

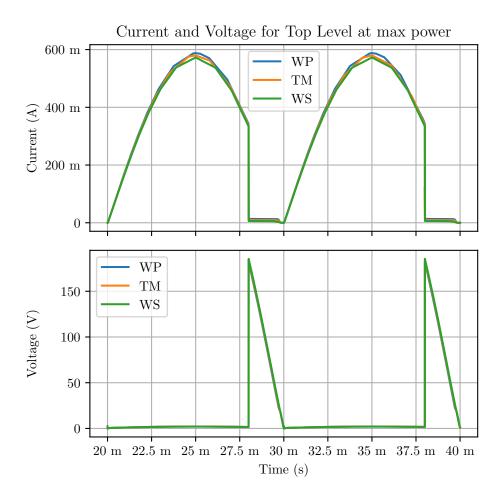

| 4.14         | Average Power consumed by the ASIC in maximum duty cycle conditions                | 71       |

| 5.1 | Layout size for the Switches.                                                                                   | 72  |

|-----|-----------------------------------------------------------------------------------------------------------------|-----|

| 5.2 | Layout size for the Gate Driver                                                                                 | 74  |

| 5.3 | Layout size for the Power Management System Voltage Divider                                                     | 74  |

| 5.4 | Dimensions for the Power Management System layout.                                                              | 74  |

| 5.5 |                                                                                                                 | 78  |

| 6.1 | LV DC setup components                                                                                          | 84  |

| 6.2 | LV triangle wave signal setup components                                                                        | 85  |

| 6.3 |                                                                                                                 | 85  |

| 6.4 | LV trapeze wave signal setup components                                                                         | 86  |

| 6.5 |                                                                                                                 | 88  |

| 6.6 | Power System current consumption with a LV DC signal                                                            | 88  |

| 6.7 |                                                                                                                 | 88  |

| 6.8 | Power System measurement with a LV triangular wave signal                                                       | 92  |

| 6.9 | Power System measurement with a LV trapeze wave signal                                                          | 94  |

| 7.1 | Final design specifications                                                                                     | 99  |

| A.1 | Commercially available lamps used to measure current with their respective model, brand, nominal power and type | 105 |

# Chapter 1 Introduction

#### 1.1 The problem

Using extended and gradual diffusions, varying the levels of dopants, and utilizing also a thick gate oxide, ultra high voltage (UHV) technologies enable the fabrication of several variants of integrated MOS, BJTs, diodes and even IGBTs that can withstand up to hundreds of Volts [1, 2].

In the past, these technologies were highly specific and costly, but with the advent of domotics, LED lights, efficient power sources, micro-actuators and displays, their use has expanded to most consumer applications lowering the cost and having frequent multi-project wafer runs (MPW).

However, open fabs are still few and references with specific information such as [3, 4, 5] are scarce. Access to most information about UHV circuits is restricted, since most of the work on UHV requires a specific know-how and is being developed inside companies. Hence, academic work in this area results interesting.

A fully integrated phase cut dimmer was chosen as an example application to gain experience and propose innovative IC designs for feeding low power circuits.

#### 1.2 In this thesis

Chapter 1 provides an introduction to the project including state of the art, the most significant design challenges, and the design specifications.

Chapter 2 is an introduction to the chosen fabrication technology, and a summary of the devices that were most significant to this project.

Chapter 3 describes in detail the schematic for each of the designed blocks, and the respective design decisions. This section also includes sizing of all components and devices.

Chapter 4 shows the schematics used for simulation and the results of said simulations for all blocks in the circuit.

Chapter 5 includes the physical layout of the circuit that was sent for fabrication, as well as a microscope image of the fabricated circuit.

Chapter 6 includes the measurements performed on the circuit after fabrication.

Chapter 7 provides a discussion and analysis of the results, and a comparison between expectations and final results.

Outside the main body of the thesis, two appendices are included that provide complimentary information to the main design activities.

Appendix A focuses on electrical current measurements for off-the-shelf lamps and an offthe-shelf discrete phase cut dimmer similar to the integrated dimmer that was designed in this project.

Appendix B includes the schematics and PCB layout that were necessary for connection to the integrated dimmer in the macroscopic world.

#### **1.3** State of the art

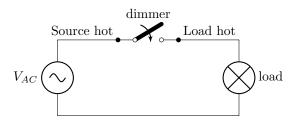

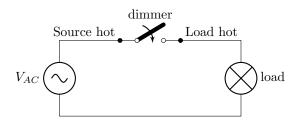

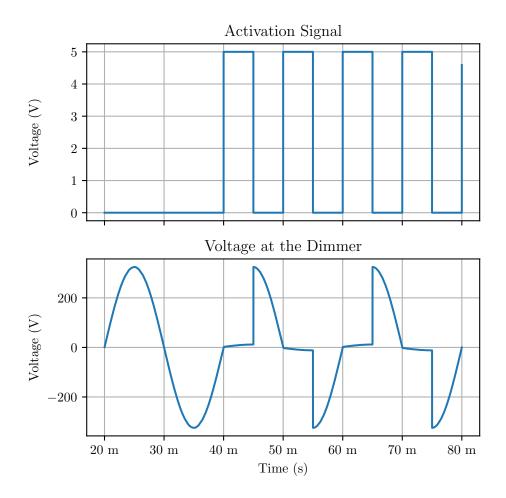

Phase-cut dimmers are circuits that chop the 110 VAC to 230 VAC, 50 Hz to 60 Hz sine wave to the load to modulate power, as shown in Figure 1.1 and Figure 1.2 on the following page.

Figure 1.1: Application diagram of a phase cut dimmer

The classic implementation of this circuit uses a TRIAC as the main switch and a DIAC to trigger it because of its low cost although they present *leading-edge* limitations [6]. Over the last years, microcontroller [7] and IGBT [8] based solutions have been reported, which allow for a finer control of specially prepared LED and CFL lamps [9, 10].

Even though approximations to solving this problem such as [8] exist, no commercial integrated circuit (IC) exists that implements a complete dimmer with its own power management and a power switch stage.

#### 1.3.1 Leading and Trailing Edge Dimmers

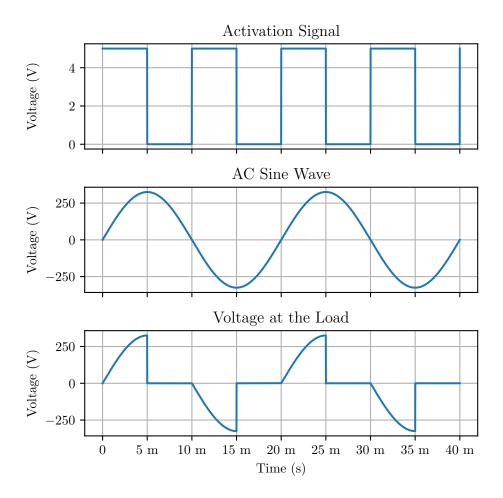

There are two basic dimmer strategies depending on the part of the sine wave that gets chopped called leading and trailing edge. Leading edge dimmers begin cutting off the AC sine wave right after it crosses zero, whereas trailing edge dimmers stop cutting off the AC sine wave when it crosses zero (see Figure 1.3 on page 14).

Classic TRIAC dimmers are of the leading-edge type because the TRIAC itself turns-off on the zero cross. On the other hand trailing edge dimmers are said to better control LED lamps because they usually represent a capacitive load, and an abrupt turn-on edge current spike is avoided.

#### 1.4 Motivation

At the time of writing this thesis, no academic papers could be found referencing similar circuits. BQN [11] is a local manufacturer and exporter of dimmer circuits, who has expressed interest

in the development of this project for improving their existing technologies.

The research group at UCU has experience with HV technologies, and is looking to expand its areas of work into the novel UHV technologies and devices like integrated UHV IGBTs and diodes.

Therefore, academic research in this area is of interest.

Figure 1.2: Load voltage example in a phase-cut dimmer.

#### 1.5 Circuit Scheme

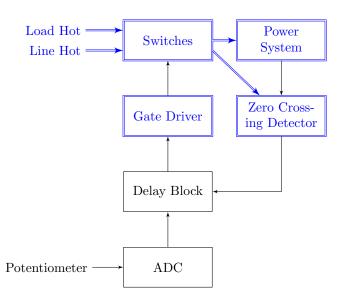

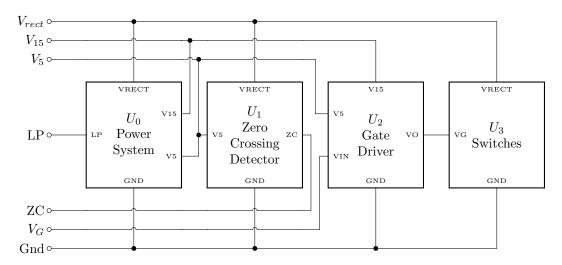

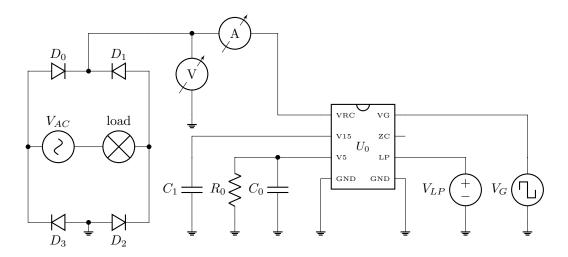

The proposed design is shown in Figure 1.4 on page 15, and it consists of six blocks that can be divided into power and logic related.

The power related blocks (double line in Figure 1.4 on page 15) are *Switches* through which power is delivered to the load, a *Gate Driver* to operate the switches, a *Power System* to manage and provide LV DC power to all the circuit blocks in Figure 1.4 on page 15 from the AC source, and a *Zero Crossing Detector* to keep the system in phase with the 50 Hz to 60 Hz sine wave.

The logic related blocks (single line in Figure 1.4 on page 15) are a *Delay Block*, that implements a finite state machine (FSM) to control the duty cycle of the switch activation, and an *Analog to Digital Converter* (ADC) to read an analog input to control the duty cycle.

Because the logic related blocks can be implemented with well-known and standard low power microcontrollers [7, 12], only the power related blocks are included in the current implementation of the design.

Figure 1.3: Dummy simulation to illustrate the difference between a trailing and leading edge dimmer.

#### **1.6** Dimmer specifications

The aim of this project is to design, simulate and fabricate a functional prototype for an integrated phase cut dimmer.

Even though this is an academic project, decisions had to be made as if it were part of a commercial product. As such, the most important metrics are power consumption (limited by its ability to be embedded into a wall) and its ability to deliver power to a load.

A final design constraint was added to the silicon area it can occupy to be fabricated in a MPW, and have a low manufacturing cost compliant with a consumer application.

The full target specifications are shown in Table 1.1 on the following page.

Figure 1.4: Top level blocks for the UHV dimmer. *Load Hot* and *Line Hot* are the dimmer terminals that connect to the load and to the grid respectively as shown in Figure 1.1 on page 12. *Potentiometer* is an extra analog input to control the duty cycle. Blue double line blocks represent power related blocks and single line blocks represent logic related blocks. Blue double line arrows represent UHV connections and single line arrows represent low voltage connections.

| Measure                                    | 1      | Value | Unit            |

|--------------------------------------------|--------|-------|-----------------|

| Idle state power consumption               | $\leq$ | 100   | mW              |

| On state power consumption                 | $\leq$ | 4     | W               |

| Max power percentage delivered to the load | $\geq$ | 95    | %               |

| Max power delivered to the load            | $\geq$ | 100   | W               |

| Total silicon area                         | $\leq$ | 10    | $\mathrm{mm}^2$ |

| Fully integrated                           |        | Yes   |                 |

Table 1.1: Target design specifications.

### Chapter 2

# UHV CMOS Technology Description

#### 2.1 Introduction

The design of high voltage integrated circuits naturally requires the use of specially prepared fabrication technologies designed to withstand the elevated voltage levels of a typical domestic AC power network.

In this work, the selected process is XDM10 from XFAB [13, 14], a 1.0 µm Modular 350 V Trench Insulated BCD Process Technology on SOI wafer. This technology provides a wide variety of devices including high voltage MOS, BJTs and IGBTs, as well as regular 5 V core CMOS, high-resistivity poly resistors, 5 V Zener diodes, and Schottky diodes.

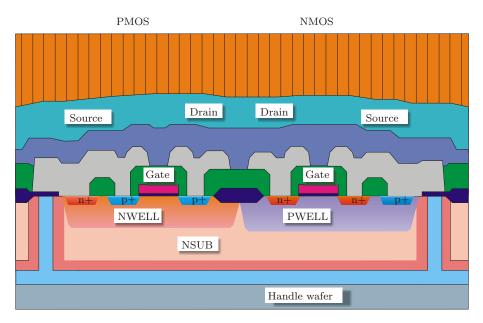

To withstand elevated UHV voltages, XDM10 includes dielectric trench insulation at wafer level [14]. Figure 2.1 on the next page shows a vertical cross section for low voltage CMOS transistors.

#### 2.2 XDM10

There are three main aspects that make XDM10 from XFAB [13, 14] a suitable technology for UHV power switching applications.

First, the use of extended and gradual diffusions allows for UHV transistors with breakdown voltages of up to 400 V. The use of thick gate oxide allows for up to 20 V gate-source voltage, significantly higher than traditional CMOS technologies. Finally, trench isolation allows for UHV and LV devices to be fabricated in close proximity without the risk of latch up.

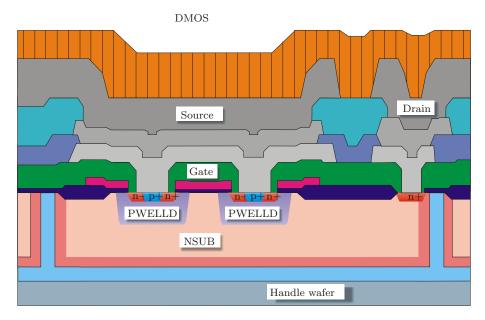

Figure 2.2 on page 18 shows a cross section of an UHV DMOS transistor displaying all three of these strategies.

XDM10 offers UHV MOSFETs, BJTs and IGBTs, as well as a 5 V CMOS core with a wide variety of ready to use digital and analogue cells. For analogue applications, several capacitor and resistor devices can be realized. Finally, isolating trenches allow for the use of forward diodes.

After careful study of the manufacturer's process specifications [15] and with aid of Spice simulations (Section 4.1), ni34b IGBTs were chosen as the main switching element of this circuit, because they provide the largest current per unit of area.

A summary of the available devices offered by the technology is shown in the tables indicated by Table 2.1 on the next page. All device characteristics are taken from the official XFAB

Figure 2.1: XDM10 core module cross section for low voltage CMOS transistors [15].

documentation [15, 16].

| Device Type  | Table | Page |

|--------------|-------|------|

| LV CMOS      | 2.2   | 18   |

| MV CMOS      | 2.3   | 18   |

| UHV MOS      | 2.4   | 18   |

| IGBT         | 2.5   | 19   |

| BJT          | 2.6   | 19   |

| Resistors    | 2.7   | 19   |

| Diodes       | 2.8   | 19   |

| Metal Layers | 2.9   | 19   |

Table 2.1: Technology devices summary reference table.

Figure 2.2: XDM10 core module cross section for an UHV DMOS transistor [15].

| Device                       | Name           | $ V_T $ (V) | $I_{DS}$ (µA/µm) | $\max  V_{DS} $ (V) | $\max V_{GS}$ (V) |

|------------------------------|----------------|-------------|------------------|---------------------|-------------------|

| $5\mathrm{V}$ NMOS           | ne             | 0.80        | 150              | 5.5                 | 18                |

| $7\mathrm{V}\ \mathrm{NMOS}$ | nea            | 0.86        | 150              | 7.0                 | 18                |

| $5\mathrm{V}\ \mathrm{PMOS}$ | pe             | 0.95        | 65               | 5.5                 | 18                |

| $7\mathrm{V}\ \mathrm{PMOS}$ | $\mathbf{pea}$ | 0.95        | 65               | 7.0                 | 18                |

| Device                        | Name                  | $ V_T $ (V) | $R_{ON} \ (k\Omega \cdot \mu m)$ | $\max  V_{DS}  (\mathbf{V})$ | $\max V_{GS}$ (V) |

|-------------------------------|-----------------------|-------------|----------------------------------|------------------------------|-------------------|

| 20 V NMOS                     | nme                   | 0.8         | 19                               | 20                           | 18                |

| $20\mathrm{V}\mathrm{PMOS}$   | pme                   | 0.75        | 60                               | 20                           | 18                |

| $15\mathrm{V}\ \mathrm{NMOS}$ | nmea                  | 0.78        | 15                               | 15                           | 18                |

| 20 V PMOS                     | pmea                  | 0.62        | 45                               | 20                           | 18                |

| $32\mathrm{V}$ NMOS           | $\operatorname{nmeb}$ | 0.8         | 21                               | 32                           | 18                |

Table 2.2: XDM10 LV CMOS device characteristics.

Table 2.3: XDM10 MV MOS device characteristics.

| Device                                   | Name    | $\max  V_{DS}  (\mathbf{V})$ | $\max V_{GS}$ (V) | $\max I_D (\mathrm{mA})$ |

|------------------------------------------|---------|------------------------------|-------------------|--------------------------|

| 370 V DMOS, scalable                     | nd34a   | 340                          | 20                | 20                       |

| $370 \text{ V} \text{ DMOS}, 370 \Omega$ | nd34bs  | 340                          | 20                | 150                      |

| 370 V DMOS, scalable,                    | nd34bsw | 340                          | 20                | 425                      |

| wide metal connect                       |         |                              |                   |                          |

Table 2.4: XDM10 UHV MOS device characteristics.

| Device                       | Name  | $ V_T $ (V) | $\max V_{CE}$ (V) | $\max V_{GE}$ (V) | $\max I_C (\mathrm{mA})$ |

|------------------------------|-------|-------------|-------------------|-------------------|--------------------------|

| $400\mathrm{V}\mathrm{IGBT}$ | ni34b | 1.7         | 340               | 20                | 220                      |

|   | Device                   | Name | Beta $(\beta)$ | $V_{BE} (\mathrm{mV})$ | $\max V_{CE}$ (V) |

|---|--------------------------|------|----------------|------------------------|-------------------|

| - | $370\mathrm{V}$ vertical | qnvd | 65             | 650                    | 330               |

Table 2.6: XDM10 BJT device characteristics.

| Device          | Name | $R_S (\Omega/\Box)$ | $\max V(\mathbf{V})$ |

|-----------------|------|---------------------|----------------------|

| PWELLD          | rpwd | 1530                | 50                   |

| POLYD, P+ impl. | rpd  | 190                 | 350                  |

| Table 2.7: XDM1 | ) resistors d | levice cha | racteristics. |

|-----------------|---------------|------------|---------------|

|-----------------|---------------|------------|---------------|

| Device                       | Name        | V (V)                                   | max breakdown I<br>(mA/µm) | max forward I<br>(mA) |

|------------------------------|-------------|-----------------------------------------|----------------------------|-----------------------|

| 4.8 V Zener<br>30 V Schottky | dzeb<br>dsa | $\begin{array}{c} 4.8\\ 30 \end{array}$ | 1                          | 1                     |

| Table 2.8: XDM10 diodes device characteristics | Table $2.8$ : | XDM10 | diodes | device | characteristics |

|------------------------------------------------|---------------|-------|--------|--------|-----------------|

|------------------------------------------------|---------------|-------|--------|--------|-----------------|

| Device  | Name           | $R_S (\Omega/\Box)$ | $\max J/W \ (mA/\mu m)$ | $\max V$ (V) |  |

|---------|----------------|---------------------|-------------------------|--------------|--|

| Metal 1 | rm1            | 0.05                | 0.8                     | 350          |  |

| Metal 2 | $\mathrm{rm}2$ | 0.05                | 0.8                     | 350          |  |

| Metal 3 | $\mathrm{rm}3$ | 0.013               | 7.0                     | 350          |  |

Table 2.9: XDM10 power metal device characteristics.

### Chapter 3

## **Circuit Description**

#### 3.1 UHV Power Switches

The UHV power switches are the element of the circuit that blocks or allows feeding power to the load. Their design is crucial to the ASIC because most of the occupied die area, and the total on-state power dissipation of the IC is determined by these switches.

The first decision is to select the device type.

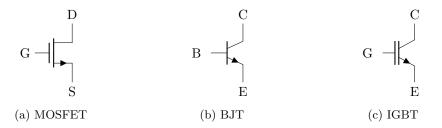

The XDM10 technology offers three different types of transistors capable of switching up to 230 V rms: MOSFET, BJT and IGBT, as shown in Figure 3.1.

Figure 3.1: Switching device options offered by the working technology.

After careful study of the manufacturer's process specifications shown in Tables 2.4, 2.5, 2.6, ni34b IGBTs were chosen because they provide the largest current per unit of area. SPICE simulations for all corner models are included in Section 4.1.

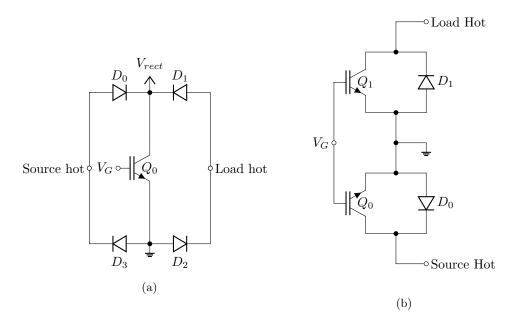

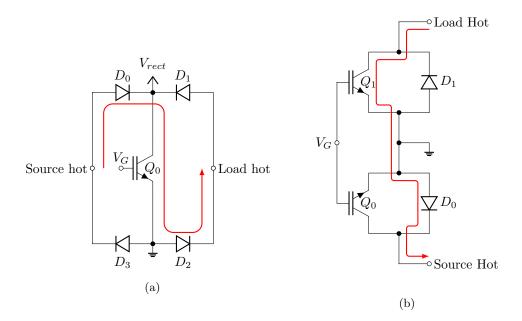

The next step was choosing the connection configuration to the AC power source. Two options were considered as shown in Figure 3.2 on the next page.

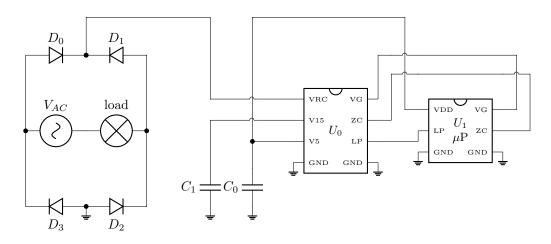

The first one, consists of a diode bridge rectifier with a single transistor connected between the rectified terminals as described in [17]. When  $Q_0$  is in conduction state, current will flow between *Source hot* and *Load hot* and the voltage between  $V_{rect}$  and *Gnd* will be near zero, as illustrated in Figure 3.3a on page 22. When  $Q_0$  is in cut-off state, there will be no current flow between *Source hot* and *Load hot* and the voltage between  $V_{rect}$  and *Gnd* will be a rectified version of the AC power source.

The second option, shown in Figure 3.2b on the next page, consists of two series transistors, each in anti-parallel with a diode as described in [18]. When  $V_G$  is higher than the ground reference, one of  $Q_0$  or  $Q_1$  enter conduction state, and the diode in parallel to the other transistor

Figure 3.2: Switches block architecture options.

enters conduction state to close the circuit, as illustrated in Figure 3.3b on the following page. When the value of  $V_G$  is low with respect to ground,  $Q_0$  and  $Q_1$  will not enter conduction state, and there will be no current flow between *Source hot* and *Load hot*.

The main advantage of the first option over the second on is the existence of two circuit nodes  $V_{rect}$  and Gnd so at all times it can be assumed that  $V_{rect} \ge Gnd$ .

The main advantage of the second option over the second one is a lower on-state power consumption, since the current path includes a transistor and only one diode instead of two.

When considering the total silicon area, it is worth noting that the first option requires one UHV transistor against two, but four UHV diodes instead of two. For the target technology, it was found that UHV diodes occupy about twice the area than UHV IGBTs at the same current.

Finally, the option shown in Figure 3.2a was chosen because its  $V_{rect}$  and Gnd terminals simplify the design of the DC voltage sources to power the remaining ASIC's blocks.

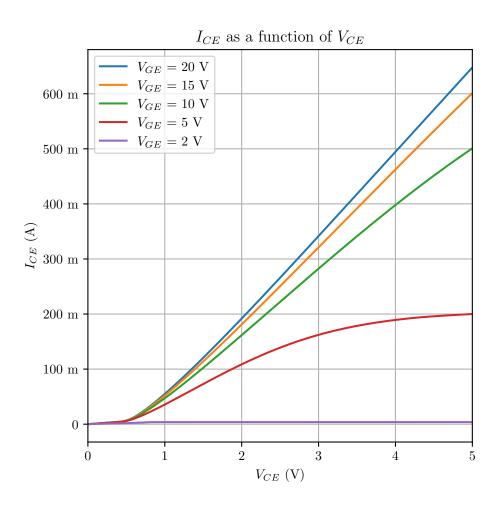

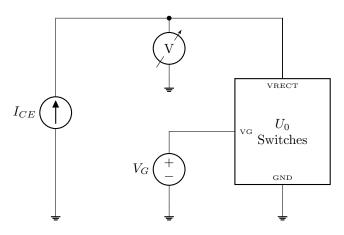

Because  $Q_0$  is a UHV IGBT, there are not many degrees of freedom for the designer, particularly width and length are fixed. The I–V curve for the base ni34b IGBT is presented in Figure 3.4 on page 23.

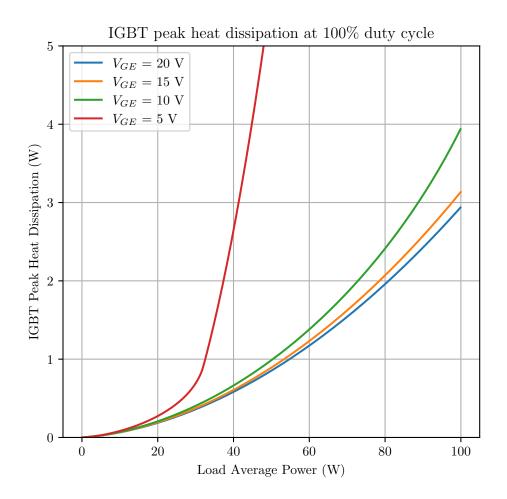

Heat dissipation of a base IGBT as a function of the power delivered to an AC load can be calculated from the I–V curve in Figure 3.4, as shown in Figure 3.5 on page 24. This is of interest, because both heat dissipation and power delivery to the load are specifications defined in Table 1.1 on page 15.

On-state heat dissipation for a given load can be reduced by connecting multiple unit IGBT devices in parallel. With the available silicon area in the MPW, it was determined that the largest possible multiplicity was M = 3.

Current density limitations established by the manufacturer were such that it was not possible to integrate the diodes  $D_{0-3}$  from Figures 3.2, and 3.3 on the following page into the MPW thus they will be later connected outside (discrete components).

Figure 3.3: Current flow diagram (represented with red) on the switches block architecture options in Figure 3.2.

It was originally planned to include at least one UHV diode in the ASIC for characterization, as [15] is not consistent about the reason behind the current limitations. However, no UHV diodes could be included in the final ASIC because of silicon area constraints.

From now on, the switches block will be represented with the symbol in Figure 3.6 on page 24.

Figure 3.4: I–V curve for the unit IGBT included in XDM10.

Figure 3.5: Peak heat dissipation for a unit IGBT device at 100% duty cycle as a function of the power delivered to an AC load.

Figure 3.6: Symbol representing the Switches block. This block does not include diodes  $D_{0-3}$  which, for the moment, could not be integrated into the ASIC.

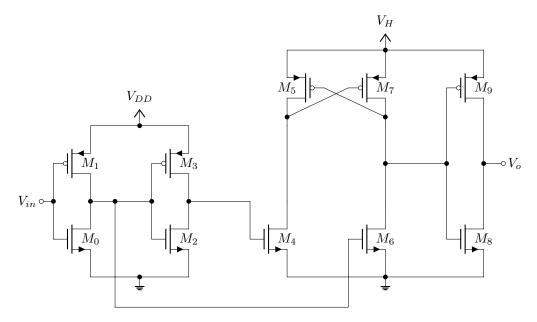

Figure 3.7: Schematic of a Gate Driver Level Shifter [21].  $M_{0-3}$  are low voltage MOS transistors and  $M_{4-9}$  are high voltage MOS transistors. The bulk terminal of all MOS transistors is connected to the respective source.

#### 3.2 Gate Driver

Controlling the gate of an IGBT like  $Q_0$  from Figure 3.2a is not a trivial process. A low onstate gate voltage produces low channel conductivity, thus limiting the power delivery to the load. However, higher on-state gate voltages are harder to produce by the Power Management System, with diminishing conductivity returns.

In addition, the gate driver needs to be designed to be able to drive a large capacitive load of up to hundreds of pF like the gate of a UHV IGBT [19, 20].

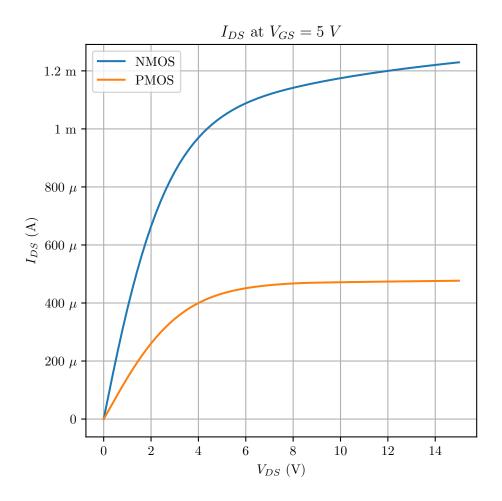

An on state gate voltage level of 15 V was chosen as a compromise between the 5 V used for logic and 20 V, which is the maximum value supported by the technology. Figures 3.4 on page 23 and 3.5 on the previous page show that the difference between 15 V and 20 V is not significant for power delivery purposes.

The circuit implemented to operate as a gate driver consists of a blind range level shifter as described in [21], and is shown in Figure 3.7.

According to [21],

$$\frac{W_5/L_5}{W_4/L_4} = \frac{\mu_n}{2\mu_p} \frac{\left(V_{DD} - V_{TN}\right)^2}{\left(V_H - V_{TP}\right)V_{TP}}$$

(3.1)

Where  $W_i$ ,  $L_i$  are the width and length respectively of the *i*-th transistor,  $\mu_n$  and  $\mu_p$  are the electron and hole mobilities,  $V_{DD}$  is the lower side supply voltage,  $V_H$  is the higher side supply voltage, and  $V_{TN}$  and  $V_{TP}$  are the threshold voltages for N and P high voltage MOS transistors respectively.

$V_{DD}$  and  $V_H$  have been determined by design to be 5 V and 15 V respectively, and sensible approximations for  $V_{TN}$  and  $V_{TP}$  can be found in the manufacturer's data sheet. However, it

is not trivial to determine  $\mu_n$  and  $\mu_p$  from the manufacturer provided documentation for HV transistors, and thus the relation between them was determined with aid of SPICE simulations.

The relation between  $\mu_n$  and  $\mu_p$  can be determined by dividing the classic MOSFET drain source saturation current expression [22] as shown in Equations 3.2, 3.3.

$$I_{DSat} = \frac{\mu C_{ox}}{2} \frac{W}{L} (V_{GS} - V_{th})^2$$

(3.2)

$$\frac{\mu_n}{\mu_p} = \frac{I_{DSatN}}{I_{DSatP}} \frac{\frac{W_P}{L_P}}{\frac{W_N}{L_N}} \frac{\left(V_{GSP} - V_{thP}\right)^2}{\left(V_{GSN} - V_{thN}\right)^2}$$

(3.3)

Where  $I_{DSat}$  is the drain source saturation current, and  $C_{ox}$  is the gate oxide capacitance per area unit, which is equal for NMOS and PMOS transistors in the technology used.

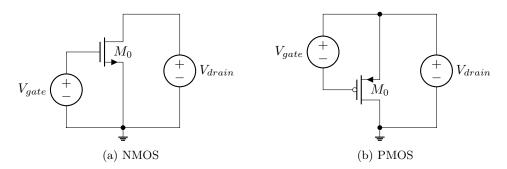

With the circuit shown in Figure 3.8 and the transistor sizes in Table 3.1,  $I_{DSat}$  was determined by fixing  $V_{qate}$  and sweeping  $V_{drain}$  for an NMOS and a PMOS transistor.

Figure 3.8: Test bench used to determine the transfer curve for HV (20 V) MOS devices. In all cases, bulk is connected to source.

|              | NMOS | PMOS | Unit          |

|--------------|------|------|---------------|

| W            | 10.0 | 10.0 | μm            |

| $\mathbf{L}$ | 3.0  | 4.5  | $\mu m$       |

| $V_{th}$     | 745  | 590  | $\mathrm{mV}$ |

| $V_{GS}$     | 5.0  | 5.0  | V             |

Table 3.1: MOS transfer SPICE simulation input data

Simulation results are shown in Table 3.2 and in Figure 3.9 on the following page.

$$\frac{1}{I_{DSat}} \frac{1.23}{1.23} \frac{0.477}{0.477} \text{ mA}$$

Table 3.2: MOS transfer SPICE simulation results for the test bench shown in Figure 3.8.

By substituting the saturation current results into Equations 3.2 and 3.3, the size relations can be calculated as shown in Table 3.3 on page 28.

Finally, MOS transistors were given sizes. Low voltage MOS were given minimum size, and high voltage sizes were first calculated and later adjusted using SPICE simulations.

Figure 3.9: SPICE simulation results for the transfer curve of two HV (20 V) MOS devices with the sizes from Table 3.1 on the preceding page.

The final results are presented in Table 3.4 on the following page.

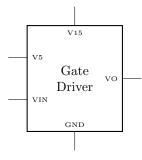

From now on, the gate driver block will be represented with the symbol in Figure 3.10 on the next page.

|                           | Value |

|---------------------------|-------|

| $\mu_n/\mu_p$             | 1.85  |

| $\frac{W_5/L_5}{W_4/L_4}$ | 1.53  |

Table 3.3: Size relation for the Gate Driver MOS transistors according to Equations 3.2 and 3.3 with the results from the simulations shown in Table 3.2.

|       | $\max V (V)$ | Device Type | $W \ (\mu m)$ | L ( $\mu m$ ) |

|-------|--------------|-------------|---------------|---------------|

| $M_0$ | 5            | NMOS        | 10.0          | 1.2           |

| $M_1$ | 5            | PMOS        | 10.0          | 1.3           |

| $M_2$ | 5            | NMOS        | 10.0          | 1.2           |

| $M_3$ | 5            | PMOS        | 10.0          | 1.3           |

| $M_4$ | 15           | NMOS        | 10.0          | 3.0           |

| $M_5$ | 15           | PMOS        | 20.0          | 4.5           |

| $M_6$ | 15           | NMOS        | 10.0          | 3.0           |

| $M_7$ | 15           | PMOS        | 20.0          | 4.5           |

| $M_8$ | 15           | NMOS        | 10.0          | 3.0           |

| $M_9$ | 15           | PMOS        | 20.0          | 4.5           |

Table 3.4: Device dimensions for transistors in the Level Shifter shown in Figure 3.7 on page 25

Figure 3.10: Symbol representing the Gate Driver block shown in Figure 3.7 on page 25.

#### 3.3 Power Management

One of the biggest challenges in the design of the ASIC is to provide a reliable DC source to power the rest of the circuits from the AC grid.

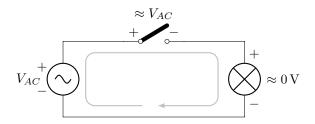

The proposed dimmer in Figure 3.11 is a two-terminal device. Thus the dimmer will see the complete rectified AC sine wave when the switch is open, but voltage will fall to almost zero while power is being delivered to the load. This behaviour is illustrated in Figures 3.12 and 3.13 respectively.

Figure 3.11: Application diagram of a phase cut dimmer

Figure 3.12: Two terminal phase cut dimmer in open state.

Figure 3.13: Two terminal phase cut dimmer in closed state.

However, the dimmer itself requires to power its internal circuits, and this power cannot be obtained when a near zero voltage is applied to its terminals. Thus a two-terminal dimmer cannot operate at 100% duty cycle. A solution to this challenge is described in Section 3.3.1.

#### 3.3.1 Maximum Duty Cycle

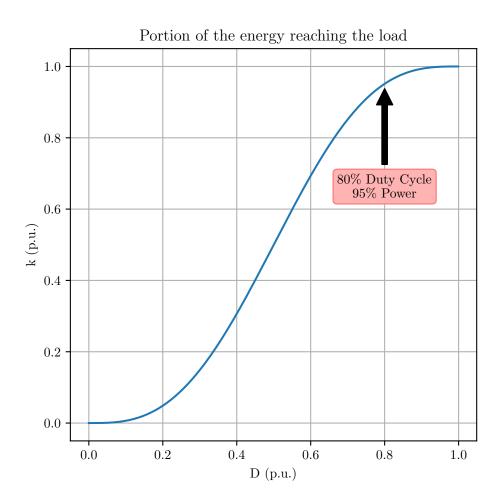

The amount of the energy per AC cycle that is actually delivered to the load as a function of the dimmer duty cycle can be studied by computing the quotient between the energy reaching the load when the dimmer is present and when the load is connected directly to the AC. This is shown in Eq. 3.4.

$$k = \frac{P_L}{P_{\max}} \tag{3.4}$$

Where k is the portion of the energy reaching the load,  $P_L$  is the average power reaching the load over an AC power cycle, and  $P_{\text{max}}$  is the average power that would reach the load over an AC power cycle if the load was connected directly to the AC.

$P_{\text{max}}$  can be computed as the average value of the instant power transmitted to the load, as shown in Eq. 3.5. This is a well known equation and its result could be presented without further elaboration (see Eq 3.8). However, it is worth looking into the solution as it will make the process clearer to compute  $P_L$ .

$$P_{\max} = \frac{1}{T} \int_0^T \frac{v^2(t)}{R_L} \,\mathrm{d}t$$

(3.5)

Where T is the AC signal period,  $R_L$  is the effective load resistance and v(t) is the AC voltage sine wave.

By substituting v(t) by its explicit sine wave form from Eq. 3.6, it is possible to calculate the integral.

$$v(t) = \sqrt{2} \ V_{eff} \sin\left(\frac{2\pi}{T}t\right) \tag{3.6}$$

Where  $V_{eff}$  is the effective (rms) value for v(t).

$$P_{\max} = \frac{1}{T} \int_0^T \frac{v^2(t)}{R_L} dt$$

$$= \frac{1}{T} \int_0^T \frac{2 V_{eff}^2 \sin^2\left(\frac{2\pi}{T}t\right)}{R_L} dt$$

$$= \frac{2 V_{eff}^2}{T \cdot R_L} \int_0^T \sin^2\left(\frac{2\pi}{T}t\right) dt$$

Making use of the trigonometric identity shown in Eq. 3.7 this equation can be further simplified.

$$\sin^{2}(x) = \frac{1 - \cos(2x)}{2}$$

$$P_{\max} = \frac{2 V_{eff}^{2}}{T \cdot R_{L}} \int_{0}^{T} \frac{1}{2} - \frac{1}{2} \cos\left(\frac{4\pi}{T}t\right) dt$$

(3.7)

Because the terms of the integral are a constant value and a pure sinusoid over a multiple of its period, the result of the integral can be trivially solved to get the result shown in Eq. 3.8.

$$P_{\max} = \frac{2 V_{eff}^2}{T \cdot R_L} \cdot \frac{T}{2}$$

$$P_{\max} = \frac{V_{eff}^2}{R_L}$$

(3.8)

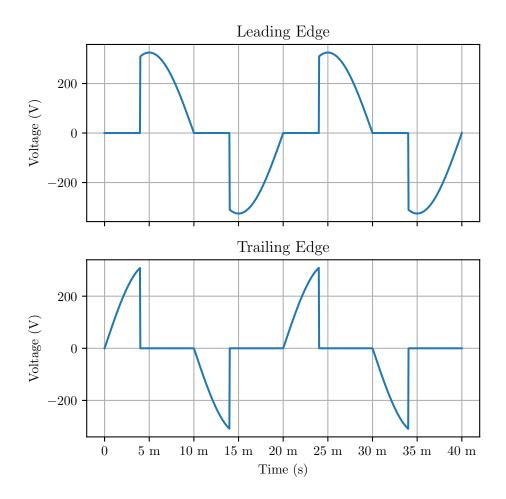

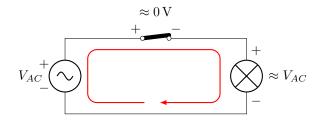

For a trailing edge dimmer,  $P_L$  can be modelled as shown in Figure 3.14 with the same voltage sine wave from Eq. 3.5 on the previous page multiplied by a periodic step function u(t) as shown in Eq. 3.10.

$$P_L = \frac{1}{T} \int_0^T \frac{v^2(t) \ u^2(t)}{R_L} \ \mathrm{d}t \tag{3.9}$$

$$u(t) = \begin{cases} 1 & \text{if } 0 < t + k \cdot \frac{T}{2} < D \cdot \frac{T}{2} \\ 0 & \text{if } D \cdot \frac{T}{2} < t + k \cdot \frac{T}{2} < \frac{T}{2} \\ k \in \mathbb{Z} \end{cases}$$

(3.10)

Figure 3.14: Chopped sine wave signal example, as seen by the load in a phase-cut dimmer.

Where D is the operating Duty Cycle for the dimmer. By substituting Eq. 3.10 in Eq. 3.9 it is possible to obtain the following equation:

$$P_L = \frac{1}{T} \left( \int_0^{\frac{T}{2} \cdot D} \frac{v^2(t)}{R_L} \, \mathrm{d}t + \int_{\frac{T}{2}}^{\frac{T}{2} \cdot (1+D)} \frac{v^2(t)}{R_L} \, \mathrm{d}t \right)$$

With a symmetry argument for the sine function, it can be said that both integrals will give the same result, thus giving the following equation:

$$P_L = \frac{2}{T} \int_0^{\frac{T}{2} \cdot D} \frac{v^2(t)}{R_L} \, \mathrm{d}t$$

By substituting Eq. 3.6 on page 30 and Eq. 3.7 on page 30 the integral can be computed.

$$P_L = \frac{2}{T} \int_0^{\frac{T}{2} \cdot D} \frac{2 V_{eff}^2 \sin^2\left(\frac{2\pi}{T}t\right)}{R_L} dt$$

$$= \frac{4 V_{eff}^2}{T \cdot R_L} \int_0^{\frac{T}{2} \cdot D} \sin^2\left(\frac{2\pi}{T}t\right) dt$$

$$= \frac{V_{eff}^2}{R_L} \left(D - \frac{1}{2\pi}\sin(2\pi D)\right)$$

The final expression for the power reaching the load is shown in Eq. 3.11.

$$P_L = \frac{V_{eff}^2}{R_L} \left( D - \frac{\sin(2\pi D)}{2\pi} \right) \tag{3.11}$$

Because of the symmetry inherent to the sine function, the computation for a leading edge dimmer is analogous and provides the exact same result.

Finally, by substituting Eq. 3.8 on page 30 and Eq. 3.11 into Eq. 3.4 on page 30 the result for the power portion reaching the load is given in Eq. 3.12 and plotted in Figure 3.15 on the following page.

$$k = \frac{\frac{V_{eff}^2}{R_L} \left(D - \frac{\sin(2\pi D)}{2\pi}\right)}{\frac{V_{eff}^2}{R_L}}$$

$$k = D - \frac{\sin(2\pi D)}{2\pi}$$

(3.12)

Based on Eq. 3.12, a maximum duty cycle was arbitrarily chosen as shown in Table 3.5 to optimize power reaching the load.

ValueUnitD

$$80$$

$\%$ k $95$  $\%$

Table 3.5: Maximum design duty cycle and power percentage reaching the load.

#### 3.3.2 Circuit Implementation

As mentioned in Section 3.1 on page 20 and Section 3.3 on page 29, the Power Management System provides two DC levels from a rectified and potentially chopped voltage sine wave (Figure 3.14 on the previous page).

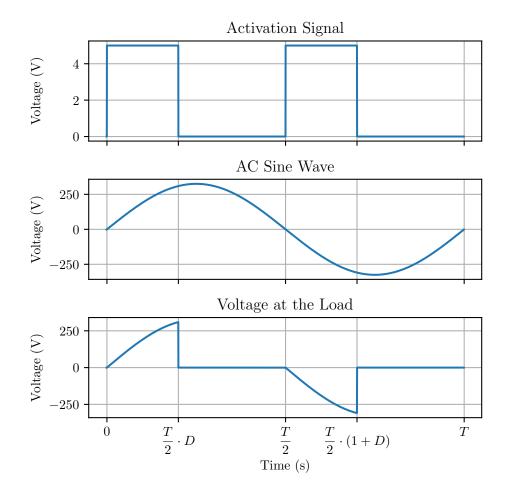

Figure 3.15: Portion of the energy reaching the load plotted against the dimmer duty cycle.

The DC voltages are obtained by harvesting charge from the load, and storing it in tank capacitors. The system must also be able to keep its DC voltages stable when working at a maximum dimmer duty cycle of 80%, as specified in Table 3.5 on the preceding page, and draw in as little current as possible when the dimmer is not in use.

For this reason, two modes were designed for the Power Management System. The Low Power Mode is meant for idle state, and its main objective is drawing in as little current as possible while keeping its internal voltage sources. The High Power Mode is meant for quick charging of the internal voltage source capacitors, and for use when the ASIC is running at full capacity and maximum duty cycle.

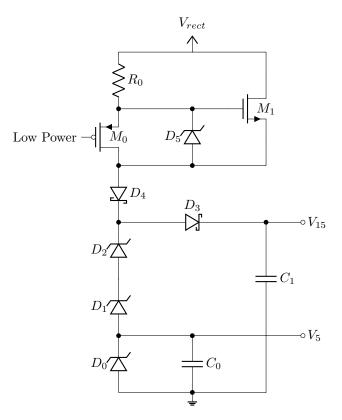

A first approach with most functional components is shown in Figure 3.16 on the next page. The lower part of the circuit consists of a series of 5 V Zener diodes  $D_{0-2}$  which will provide 5 V and 15 V when current flows through them. The excess current not required to excite the

Zener diodes will be held by the tank capacitors  $C_0$  and  $C_1$  to be used by the other ASIC blocks. Diode  $D_3$  prevents the capacitor  $C_1$  from leaking its charge into  $D_{0-2}$  and  $C_0$ , and diode  $D_4$

prevents charge leaking from  $C_0$  when the dimmer is on and  $V_{rect}$  is at a near zero value.

The upper part of the circuit implements the two operation modes, and can provide a low or

Figure 3.16: Simplified implementation for the Power Management System delivering 5 V and 15 V from a potentially chopped voltage sine wave.  $D_0$ ,  $D_1$ ,  $D_2$  and  $D_5$  are 5 V Zener diodes,  $D_3$  and  $D_4$  are Schottky diodes,  $M_0$  is an HV (20 V) PMOS transistor and  $M_1$  is an UHV NMOS transistor. All MOS transistors have their bulk connected to their sources, that are not included in the figure for the sake of simplicity

high resistance path for current from  $V_{rect}$  depending on the input signal Low Power.

Low power mode can be controlled from outside the ASIC with a 0 V to 5 V signal, which is adapted to the 0 V to 20 V range inside the ASIC with a pull up circuit.

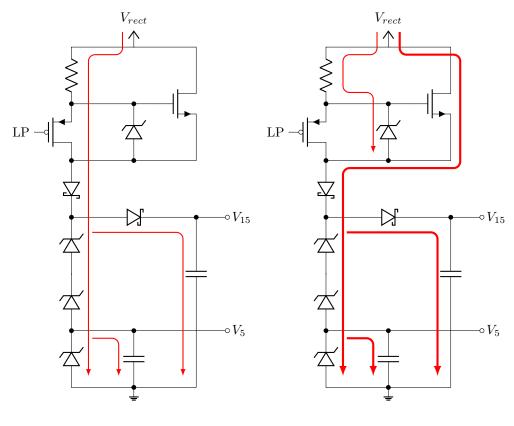

When Low Power is in low state,  $M_0$  acts like a closed switch, causing the  $V_{GS}$  of transistor  $M_1$  to be near zero, thus acting like an open switch. All current delivered to  $C_0$  and  $C_1$  is limited by a high value integrated poly resistor  $R_0$ . The current path can be observed in Figure 3.17a on the following page.

When Low Power is in high state,  $M_0$  acts like an open switch, causing  $R_0$  current to go through  $D_5$  which will impose 5 V  $V_{GS}$  on transistor  $M_1$  allowing for a larger current to reach  $C_0$  and  $C_1$ . This current path can be observed in Figure 3.17b on the next page.

A MOS device  $M_1$  was chosen over a low value resistor or other linear components because when operating in saturation mode it can provide a flat current transfer, allowing the circuit to draw in significant current when  $V_{rect}$  is near zero, and not excessive current at the peak.

Resistor  $R_0$  can be sized by considering the current needed by the ASIC in idle state.

The 5V source will have to power the logic for the ASIC, which is represented by a low power microcontroller and can be in the order of a few  $\mu$ A [12]. The 15V DC source only powers the Gate Driver circuit from section 3.2 on page 25, which has negligible static current consumption,

(a) Low Power Mode. (b) High Power Mode.

Figure 3.17: Current path for the Power Management System in different power modes.

and thus can safely be ignored for this analysis.

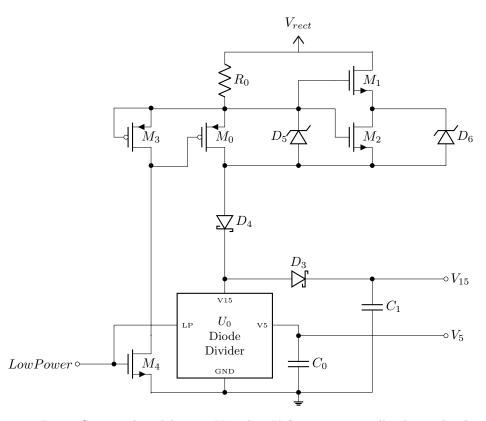

Because of technology limitations, it was not possible to implement the Power Management System *as is*, and some new devices were introduced as depicted in Figures 3.18 on the next page and 3.19 on page 37.

The first problem found in the implementation was that transistor  $M_1$  has fixed dimensions given by the technology, which causes it to draw excessive current ( $\approx 35 \text{ mA}$ ) when a  $V_{GS}$  of 5 V is applied. To compensate for this, a 20 V HV NMOS transistor  $M_2$  was included as a source degeneration element [23]. A final issue arises with  $M_2$  when Low Power Mode is activated, no current flows through  $M_{1-2}$  and large values of  $V_{SD}$  can be applied. For this reason, a 5 V Zener diode  $D_6$  was added in parallel with  $M_2$  to control its  $V_{SD}$  range.

The pull up network for controlling Low Power Mode was also included at this stage. It consists of two 20 V HV MOS transistors  $M_3$  and  $M_4$  which act as pull up logic. To ensure that  $M_4$  is able to drive  $M_0$ ,  $M_4$  was given a far larger multiplicity. This solution was chosen over other more complex alternatives for its simplicity and robustness given the importance of the Power Management System in the ASIC as a whole.

Another significant change is the replacement of Zener diodes  $D_{0-2}$  with the block  $U_0$  in Figure 3.20 on page 38. The reason for this change is the 1 mA maximum current specification for Zener diodes provided by the manufacturer. If their multiplicity is low, the Zener's current

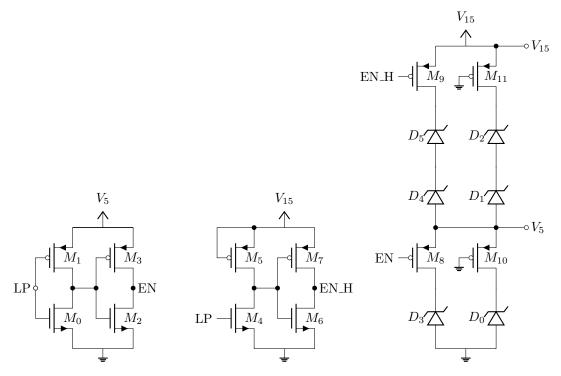

Figure 3.18: Power System that delivers 5 V and 15 V from a potentially chopped voltage sine wave.  $D_5$  and  $D_6$  are 5 V Zener diodes,  $D_3$  and  $D_4$  are Schottky diodes,  $M_0$  and  $M_3$  are HV (20 V) PMOS transistors,  $M_2$  and  $M_4$  are HV (20 V) NMOS transistors,  $M_1$  is a UHV NMOS transistor, and  $U_0$  is the voltage Diode Divider shown in Figure 3.19 on the following page. All MOS transistors have their bulk connected to their sources, that are not included in the figure for the sake of simplicity

when in High Power Mode (up to 14 mA) is too large. If their multiplicity is high, the current in Low Power Mode ( $\approx 200 \,\mu\text{A}$  peak) is not enough to reach their nominal voltage. Thus, a circuit that connects and disconnects Zener diodes according to the operation mode was designed, and is presented in Figure 3.19 on the following page. This block is represented with the symbol in Figure 3.20 on page 38.

The diode divider consists of three sub blocks, the first one consists of transistors  $M_{0-3}$  and is the series of two MOS inverters. Its main objective is to avoid loading the input named LPwith a larger gate.

The second sub block consists of transistors  $M_{4-7}$ , implementing a simple level shifter to translate the input named LP from the 0 V to 5 V range to the 0 V to 15 V range. This sub block is like the simple level shifter implemented by  $M_3, M_4$  in the Power Management System shown in Figure 3.18. Likewise,  $M_5$  was given a far larger W/L than  $M_7$  to ensure its driving capabilities.

The third sub block is the most interesting part of the diode divider. When the input named LP is in high state (meaning the ASIC is in low power mode), transistors  $M_8$  and  $M_9$  will be in open state. This means that the current will flow from the  $V_{15}$  terminal to Gnd through the

Figure 3.19: Diode voltage divider circuit that delivers 5 V and 15 V from a potentially chopped voltage sine wave.  $D_{0-5}$  are 5 V Zener diodes,  $M_0$  and  $M_2$  are LV NMOS transistors,  $M_1$ ,  $M_3$ ,  $M_8$  and  $M_{10}$  are LV PMOS transistors,  $M_4$  and  $M_6$  are HV (20 V) NMOS transistors,  $M_5$ ,  $M_7$ ,  $M_9$  and  $M_{11}$  are HV (20 V) NMOS transistors, All MOS transistors have their bulk connected to their sources, that are not included in the figure for the sake of simplicity

$D_{0-2}$  diodes, which have low multiplicity, and  $(V_5, V_{15})$  will be able to reach their desired voltage with a low current. When the input named LP is in low state (and the ASIC is in high power mode), transistors  $M_8$  and  $M_9$  will be in closed state. This means that current will flow from the  $V_{15}$  terminal to Gnd through both the  $D_{0-2}$  and  $D_{3-6}$  diodes. Because diodes  $D_{3-6}$  have high multiplicity, the larger currents drawn from the normal mode will not be out of the nominal values of any Zener diode. Transistors  $M_{10}$  and  $M_{11}$  are fixed in closed state, added for the sake of symmetry.

From now on, the Power Management System block will be represented with the symbol in Figure 3.21 on the next page.

Figure 3.20: Symbol representation for the Diode Divider block shown in Figure 3.19 on the preceding page.

Figure 3.21: Symbol representation for the Power System block shown in Figure 3.18 on page 36.

#### 3.3.3 Sizing

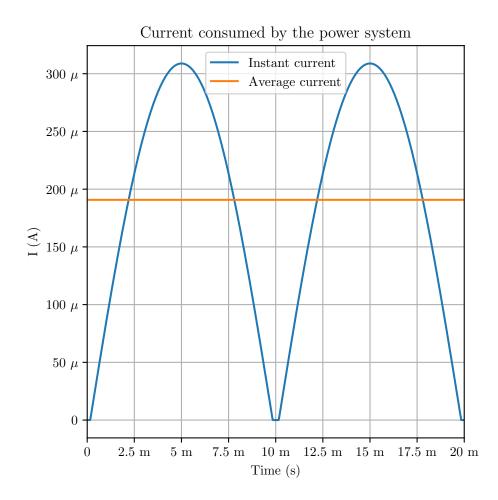

Prior to device sizing, it is necessary to estimate the current consumption in low and high power modes. Low power mode must power a modern low power microcontroller in idle state, which can be in the order of  $45 \,\mu\text{A}$  with a clock of  $1 \,\text{MHz}$  [12]. With this information, a nominal current of  $200 \,\mu\text{A}$  was chosen for this application to provide a safety margin.

When operating in low power mode, the main current limiting element is the resistor  $R_0$ . By examining the full implementation of the Power Management System from Figure 3.18 on page 36, it is possible to notice that one of its terminals is fixed at 15 V and the other one varies according to a rectified voltage sine wave with amplitude  $\sqrt{2} \times 230 \text{ V} \approx 325 \text{ V}$ . Given that 15 V is considerably smaller than 325 V, a reasonable approximation for the average current consumption can be obtained by assuming that all of  $V_{rect}$  is applied directly to  $R_0$ .

If  $I_{avg}$  is the average power management system's current, T is the AC signal period, and  $V_{eff}$  is the AC signal effective value.

$$I_{avg} = \frac{2}{T} \int_{0}^{\frac{T}{2}} \frac{V_{rect}}{R_0} dt \qquad (3.13)$$

$$I_{avg} = \frac{2}{T} \int_{0}^{\frac{T}{2}} \frac{\sqrt{2} \cdot V_{eff} \sin(\frac{2\pi}{T}t)}{R_0} dt$$

$$I_{avg} = \frac{2\sqrt{2} \cdot V_{eff}}{T \cdot R_0} \int_{0}^{\frac{T}{2}} \sin\left(\frac{2\pi}{T}t\right) dt$$

$$I_{avg} = \frac{2\sqrt{2} \cdot V_{eff}}{\pi \cdot R_0} \qquad (3.14)$$

A value of  $R_0 \approx 1.04 \,\mathrm{M\Omega}$  is obtained, by substituting  $V_{eff} = 230 \,\mathrm{V}$  and  $I_{avg} = 200 \,\mathrm{\mu A}$  into Eq. 3.14, thus  $M_0$  was given a W/L of 4.5/10  $\mathrm{\mu m}$  so that its saturation current is significantly higher than 200  $\mathrm{\mu A}$ .

Pull up transistor  $M_3$  was given the same W and L as  $M_0$  and a multiplicity m = 8 so that it can properly act as a pull up resistor.  $M_4$  was given minimum dimensions ( $W/L = 2.5/3.5 \mu$ m).

Next, the high power mode components had to be sized.

A major design constraint is that the system must provide energy to the logic circuits even when working at the maximum duty cycle of 80% as defined in Table 3.5 on page 32. In other words, the charge harvested at the first 20% of an AC semi cycle in high power mode should at least be equal to the one harvested in a full cycle in low power mode, as shown in Eq. 3.15.

$$\min(Q_{hp}) \ge \max(Q_{lp}) \tag{3.15}$$

Where  $Q_{hp}$  is the charge that can be harvested in high power mode, and  $Q_{lp}$  is the charge that can be harvested in low power mode.

The best case scenario for  $Q_{lp}$  is when the ASIC never enters conduction state, and its value is given by the average current computed in Eq. 3.14 multiplied by the duration of an AC semi cycle. The worst case scenario for  $Q_{hp}$  is when the activation signal duty cycle (D) is at its highest.

The current limiting element for the high power mode is a MOS transistor in saturation mode. Because of this, current consumption can be considered constant, and the total charge can be expressed as the product of its current times a semi cycle period. This is shown in Eq. 3.16 on the next page.

Figure 3.22: Current flow through the power management system in low power mode.

$$(1-D) \cdot \frac{T}{2} \cdot I_{hp} \ge \frac{T}{2} \cdot I_{avg\_lp}$$

$$(1-D) \cdot I_{hp} \ge I_{avg\_lp}$$

$$(3.16)$$

Where  $I_{hp}$  is the current drawn in high power mode,  $I_{avg,lp}$  is the average current consumed during low power mode defined in 3.14 on the preceding page, D is the activation signal duty cycle and T is the AC signal period.

As pointed in Table 3.5 on page 32, the maximum D value is 0.8, thus a lower bound for  $I_{hp}$  can be found by substitution as shown in Eq. 3.17.

$$I_{hp} \ge \frac{I_{avg\_lp}}{1-D} = \frac{200\,\mu\text{A}}{0.2} = 1\,\text{mA}$$

(3.17)

Transistor  $M_1$  was sized to handle this current. However, because  $M_1$  is a UHV transistor, there are not many degrees of freedom for the designer, particularly width and length are fixed,

hence its saturation current cannot easily be controlled. Transistor  $M_2$  was then sized for the designed saturation current ( $W/L = 16/3.5 \ \mu m$ ).

Diode  $D_5$  was given minimum multiplicity (m = 1) since it should only take the same current as the Low Power mode, and diode  $D_6$  was given minimum multiplicity (m = 1) because it should conduct current only when  $(M_1, M_2)$  are off, thus negligible current flows through.  $D_3$ and  $D_4$  were given dimensions so that they can conduce all current in a worst case scenario (W/L = 21/2.0 µm).

Capacitor  $C_0$  is a crucial element for the ASIC, since it holds the charge to power the logic circuitry. A large  $C_0$  is necessary to keep the logic voltage stable. A capacitance value can be found assuming a constant average current of 200 µA will be taken per AC semi cycle, and the worst case will happen when the duty cycle is at its maximum value and  $C_0$  needs to hold the voltage stable for 80 % of a semi cycle, which is 8 ms for a 50 Hz signal. Given a constant current, the voltage fluctuation in a capacitor follows Eq. 3.18.

$$\Delta V = \frac{I \times \Delta t}{C} \tag{3.18}$$

Where  $\Delta V$  is the voltage fluctuation, I is the applied current,  $\Delta t$  is the time interval, and C is the capacitance.

To improve the supply robustness supporting a wide range of microcontrollers, a worst case steady current of 2 mA and a voltage drop of 5 % were chosen. With this scenario, a capacitance value of  $\approx 100 \,\mu\text{F}$  is obtained.

The main design constraint for capacitor  $C_1$  is that it should not incur in a significant voltage drop when connected to the switches from section 3.1 on page 20 through the gate driver from section 3.2 on page 25. This size was determined with aid from SPICE simulations.

The final size/values for all devices from the power system shown in Figure 3.18 on page 36 are presented in Table 3.6.

| Name  | $\max V (V)$ | Device type    | Dimension     | Value     | Unit               |

|-------|--------------|----------------|---------------|-----------|--------------------|

| $M_0$ | 20           | PMOS           | W/L           | 10 / 4.5  | μm/μm              |

| $M_1$ | 350          | NMOS           | centre pieces | 8         | —                  |

| $M_2$ | 20           | NMOS           | W/L           | 16 / 3.5  | $\mu m/\mu m$      |

| $M_3$ | 20           | PMOS           | W/L           | 80 / 4.5  | μm/μm              |

| $M_4$ | 20           | NMOS           | W/L           | 2.5 / 3.5 | µm/µm              |

| $D_3$ | 40           | Schottky Diode | W/L           | 21 / 2.0  | µm/µm              |

| $D_4$ | 40           | Schottky Diode | W/L           | 21 / 2.0  | µm/µm              |

| $D_5$ | 5            | Zener Diode    | m             | 1         | _                  |

| $D_6$ | 5            | Zener Diode    | m             | 1         | _                  |

| $R_0$ | 350          | Resistor       | R             | 1.00      | $\mathrm{M}\Omega$ |

| $C_0$ | 5            | Capacitor      | $\mathbf{C}$  | 100       | $\mu F$            |

| $C_1$ | 15           | Capacitor      | $\mathbf{C}$  | 10        | nF                 |

Table 3.6: Device dimensions for the full implementation of the power system shown in Figure 3.18 on page 36

Finally, about the diode voltage divider  $U_0$  in Figure 3.18 on page 36, and 3.19 on page 37. Transistors  $M_0$ ,  $M_1$ ,  $M_2$ ,  $M_3$  constitute the series of two simple CMOS inverters, with arbitrary small dimensions ( $W/L = 10/1.2 \mu m$  for the NMOS and  $W/L = 10/1.3 \mu m$  for the PMOS). Transistors  $M_4$ ,  $M_5$ ,  $M_6$ ,  $M_7$  also constitute MOS inverters ( $W/L = 10/3.5 \mu m$  for the NMOS and  $W/L = 10/5.5 \mu m$  for the PMOS). The PMOS transistor of the first stage ( $M_5$ ) is working as a pull up resistor to change the voltage domain from 5 V to 15 V, and was given a multiplicity m = 2 to double its effective width and ensure its driving capabilities.

Diodes  $D_0$ ,  $D_1$ ,  $D_3$  conduce current during low power mode, and their multiplicity is m = 1 so that they all reach their 5 V knee voltage with  $I_{lp}$ . Diodes  $D_3$ ,  $D_4$ ,  $D_5$  conduce during Normal Mode, and their multiplicity is m = 14 so that the largest possible current is within their nominal value.

Transistors  $M_8$  and  $M_9$  give control over the connection of  $D_3$ ,  $D_4$ ,  $D_5$ , and they were given a large width ( $W/L = 22340/1.3 \mu m$  and  $W/L = 22340/5.5 \mu m$  respectively) to minimize their voltage drop when large currents flow through the diodes. Transistors  $M_{10}$  and  $M_{11}$  were included on the low power branch with  $W/L = 160/1.3 \mu m$  and  $W/L = 160/5.5 \mu m$  respectively, for the purpose of symmetry.

The final dimensions for all devices from the diode voltage divider shown in Figure 3.19 on page 37 are presented in Table 3.7.

| Name     | $\max V (V)$ | Device Type | Dimension | Value      | Unit          |

|----------|--------------|-------------|-----------|------------|---------------|

| $M_0$    | 5            | NMOS        | W/L       | 10 / 1.2   | μm/µm         |

| $M_1$    | 5            | PMOS        | W/L       | 10 / 1.3   | $\mu m/\mu m$ |

| $M_2$    | 5            | NMOS        | W/L       | 10 / 1.2   | $\mu m/\mu m$ |

| $M_3$    | 5            | PMOS        | W/L       | 10 / 1.3   | $\mu m/\mu m$ |

| $M_4$    | 15           | NMOS        | W/L       | 10 / 3.5   | $\mu m/\mu m$ |

| $M_5$    | 15           | PMOS        | W/L       | 20 / 5.5   | $\mu m/\mu m$ |