## PEDECIBA Informática

Instituto de Computación – Facultad de Ingeniería Universidad de la República Montevideo, Uruguay

# Tesis de Maestría en Informática

# On UML statecharts with variabilities

Pedro Andrés Vilanova Guerra

2012

Bentancourt Alves, Martín Diseño topológico de redes. Caso de estudio: The augmentation Steiner two-node survivable network problem ISSN 0797-6410

Tesis de Maestría en Informática Reporte Técnico RT 12-08

PEDECIBA

Instituto de Computación – Facultad de Ingeniería Universidad de la República. Montevideo, Uruguay, diciembre de 2011

PEDECIBA Informática Universidad de la República Montevideo, Uruguay

# On UML Statecharts with Variabilities

Pedro Andrés Vilanova Guerra Montevideo, Diciembre de 2011

Trabajo de tesis presentado para la obtención del grado de Magister en Informática de la Universidad de la República en el programa de Maestría del área Informática del PEDECIBA

Director de tesis: Dra. Nora Szasz

Tribunal: Dra. Claudia Pons - Revisora

Dr. Ariel Sabiguero Dra. Cristina Cornes

# Resumen

El uso de métodos formales para el diseño de software contribuye a la confiabilidad y robustez del sistema a construir. A medida que los sistemas se vuelven complejos, el enfoque formal es esencial, debido a que permite la demostrabilidad y verificabilidad del diseño. El diseño formal es un proceso que comienza con la etapa de especificación, en la cual el sistema es definido utilizando un lenguaje de modelado; luego la etapa de verificación, en la cual el sistema es analizado mediante un enfoque de corrección basado en pruebas formales utilizando herramientas matemáticas y, por último, la etapa de implementación, en la cual la especificación se convierte en código ejecutable. El Lenguaje de Modelado Unificado (UML por sus siglas en inglés) es un lenguaje específico ampliamente utilizado en la industria y la academia. Desafortunadamente, carece de una semántica formal que permita el desarrollo de modelos utilizando un enfoque de corrección basado en pruebas formales.

Este trabajo se centra en la especificación formal de familias de sistemas, y, en particular, en la semántica de maquinas de estados de UML (UML Statecharts) con variabilidades y sus aplicaciones a líneas de productos de software. La principal contribución es la definición de un formalismo que permite modelar el comportamiento de una familia de sistemas. Tal comportamiento se describe utilizando UML Statecharts en combinación con Diagramas de funcionalidades (Feature Diagrams), con el fin de representar las funcionalidades comunes y variantes de una familia. Para ello se define una relación de orden entre los UML Statecharts, que representa el hecho de que un statechart posee una estructura más rica que otro. Luego se define con precisión la forma de combinar diferentes extensiones de un mismo statechart. Utilizando estos conceptos, es posible definir el efecto que cada funcionalidad tiene en los productos en los cuales se encuentra presente. Estas definiciones proporcionan una forma muy simple de obtener la especificación del comportamiento de un producto de la línea como la combinación de los UML Statecharts que implementan todas las funcionalidades presentes en un producto en particular. Mas aún, se prueba que la relación de extensión propuesta constituye un refinamiento de comportamiento.

El presente enfoque se compara con el estado del arte y se estudia su aplicación práctica con el fin de visualizar sus beneficios y posibles debilidades. Adicionalmente, con el fin de comprobar la adecuacin de la propuesta, una gran parte de las ideas fueron implementadas en un prototipo utilizando Prolog.

Palabras clave: Máquinas de estado UML, Semántica formal, Modelado formal de variabilidades, Máquinas de estado con variabilidades, Líneas de productos de software.

## Abstract

The use of formal methods for software design contributes to the reliability and robustness of the system being constructed. As systems become more complex, the formal approach is essential, as it enables provability and verifiability of the design. Formal design is a process starting with the specification stage, in which the system is defined using a modeling language; it continues with the verification stage, in which the system is analyzed in a provable-correct approach using mathematical tools and finally, the implementation stage, in which the specification is converted into code. The Unified Modeling Language (UML) is a specification language widely used by the industry and the academia. Unfortunately, it lacks a formal semantics for the development of provably-correct models.

This work concerns with the formal specification of families of systems, and in particular with the semantics of UML Statecharts with Variabilities and its applications to Software Product Lines. The main contribution is the definition of a formalism which allows to model the behavior of an entire family of systems. Such behavior is described using UML Statecharts in combination with Feature Diagrams in order to represent the common and variant functionalities of the family. Using an order relation among statecharts, which represents when an UML statechart has a richer structure than another one, it is possible to precisely define how to combine different extensions of the same UML statechart into an integral new one. With these notions, it is possible to describe the effect that each feature has on the products in which it is present. These definitions provide a very simple way to obtain the specification of the behavior of a product of the line as the combination of the statecharts that implement all the features present in that particular product. Moreover, a proof that the proposed extension relation constitutes a behavioral refinement is given. The present approach is also compared with related work and its practical application is studied in order to visualize its benefits and possible weaknesses. Additionally, in order to check the adequacy of the present approach, most of the ideas were implemented in a prototype using Prolog.

Summarizing, this thesis contributes to the formalization of concepts widely used in practice as well as its implementation in modeling and formal reasoning tools.

**Key words:** UML Statecharts, Formal semantics, Formal variability modeling, Statecharts with variabilities, Software product lines.

# Contents

| 1 | Intr | roduction                                         | 1             |  |  |  |  |  |  |

|---|------|---------------------------------------------------|---------------|--|--|--|--|--|--|

|   | 1.1  | Contribution of this Work                         | 2             |  |  |  |  |  |  |

|   | 1.2  | Related Work                                      | 3             |  |  |  |  |  |  |

|   | 1.3  | Outline of this Thesis                            | 4             |  |  |  |  |  |  |

| 2 | Bac  | kground                                           | 5             |  |  |  |  |  |  |

|   | 2.1  | Model-Driven Development                          | 5             |  |  |  |  |  |  |

|   | 2.2  | Unified Modeling Language                         | 6             |  |  |  |  |  |  |

|   |      | 2.2.1 UML Statecharts                             | 7             |  |  |  |  |  |  |

|   | 2.3  | Formal Methods                                    | 8             |  |  |  |  |  |  |

|   | 2.4  | Formal Semantics Approaches of UML Statecharts    | 8             |  |  |  |  |  |  |

|   |      | 2.4.1 The Mathematical Approach                   | 9             |  |  |  |  |  |  |

|   |      | 2.4.2 Rationale of the Transition Based Formalism | 10            |  |  |  |  |  |  |

|   | 2.5  | Software Product Lines                            | 11            |  |  |  |  |  |  |

|   |      |                                                   | 11            |  |  |  |  |  |  |

|   |      | 2.5.2 Product derivation                          | 12            |  |  |  |  |  |  |

| 3 | Syn  | tax and Semantics of UML Statecharts              | 13            |  |  |  |  |  |  |

|   | 3.1  |                                                   | 13            |  |  |  |  |  |  |

|   | 3.2  |                                                   | 15            |  |  |  |  |  |  |

|   | 3.3  | <u> </u>                                          | 16            |  |  |  |  |  |  |

|   | 3.4  |                                                   | 17            |  |  |  |  |  |  |

|   | 3.5  |                                                   | 19            |  |  |  |  |  |  |

| 4 | Ext  | Extension and Union of UML Statecharts 21         |               |  |  |  |  |  |  |

| _ | 4.1  |                                                   | <b>-</b> - 21 |  |  |  |  |  |  |

|   | 1,1  |                                                   | 21            |  |  |  |  |  |  |

|   | 4.2  |                                                   | 23            |  |  |  |  |  |  |

|   |      |                                                   | 28            |  |  |  |  |  |  |

|   |      | 1                                                 | 29            |  |  |  |  |  |  |

| 5 | Var  | iability Modeling                                 | 31            |  |  |  |  |  |  |

| 0 | 5.1  |                                                   | 31            |  |  |  |  |  |  |

|   | 0.1  | 0                                                 | 31            |  |  |  |  |  |  |

|   |      | C v                                               | 33            |  |  |  |  |  |  |

|   | 5.2  |                                                   | 34            |  |  |  |  |  |  |

|   | 0.2  |                                                   | 34            |  |  |  |  |  |  |

|   |      | 5.2.2 Product Configuration                       | 34            |  |  |  |  |  |  |

|   |      | 0.2.2 II.04400 COMILLANDION                       |               |  |  |  |  |  |  |

CONTENTS viii

| 6 | Beh | avioral         | l Refinements                                       | 37 |  |  |  |

|---|-----|-----------------|-----------------------------------------------------|----|--|--|--|

|   | 6.1 | Extens          | sion Relation and Configurations                    | 37 |  |  |  |

|   |     | 6.1.1           | Monotonicity of next Function                       | 40 |  |  |  |

|   | 6.2 | Extens          | sion Relation as a Behavioral Refinement            | 43 |  |  |  |

|   | 6.3 | On the          | e Actions Generated by the SO Semantics             | 46 |  |  |  |

| 7 | The | The SC* Modeler |                                                     |    |  |  |  |

|   | 7.1 | Modeli          | ing Approach                                        | 51 |  |  |  |

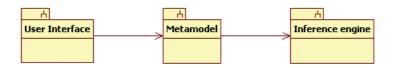

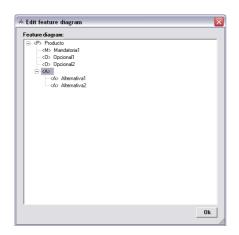

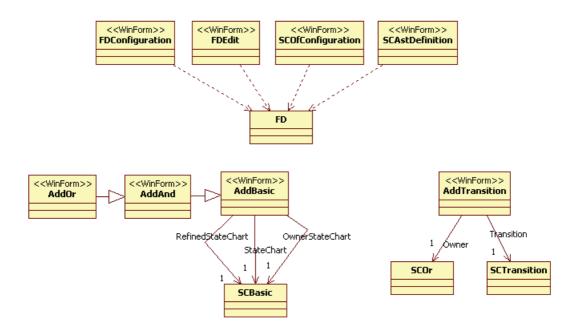

|   | 7.2 |                 | ecture                                              | 52 |  |  |  |

|   |     | 7.2.1           | User Interface                                      | 53 |  |  |  |

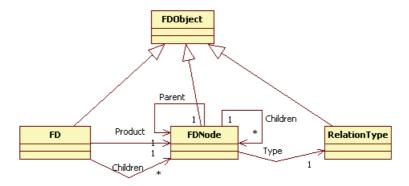

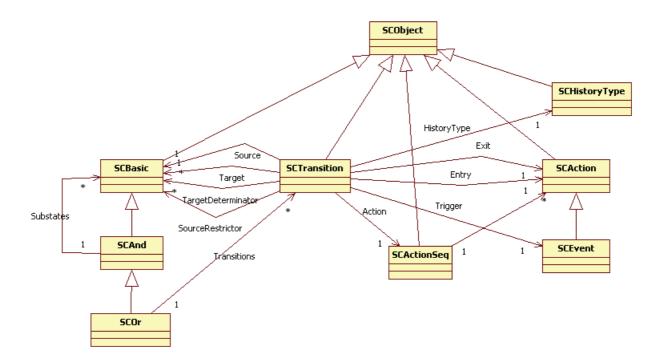

|   |     | 7.2.2           | Metamodel                                           | 54 |  |  |  |

|   |     | 7.2.3           | Inference Engine                                    | 56 |  |  |  |

| 8 | Cas | e study         | V                                                   | 59 |  |  |  |

|   | 8.1 | v               |                                                     |    |  |  |  |

|   | 8.2 |                 | ases                                                | 59 |  |  |  |

|   | 8.3 |                 |                                                     |    |  |  |  |

|   |     | 8.3.1           | Features                                            | 61 |  |  |  |

|   |     | 8.3.2           | Statecharts                                         | 62 |  |  |  |

|   |     | 8.3.3           | Feature Impact Description                          | 63 |  |  |  |

|   |     | 8.3.4           | Statechart with Variabilities                       | 66 |  |  |  |

|   |     | 8.3.5           | Examples of Products                                | 66 |  |  |  |

| 9 | Con | clusion         | ns and Further Work                                 | 71 |  |  |  |

|   | 9.1 | Summa           | ary and Conclusions                                 | 71 |  |  |  |

|   | 9.2 |                 | r work                                              | 72 |  |  |  |

|   |     | 9.2.1           | UML enrichments                                     | 73 |  |  |  |

|   |     | 9.2.2           | Relations with Lattice Theory                       | 74 |  |  |  |

|   |     | 9.2.3           | SC* Modeler and Integrated Development Environments | 74 |  |  |  |

# Chapter 1

## Introduction

Software reusability has become a key challenge for the software industry. Software reuse is the systematic (in contrast to ad hoc) use of existing software assets to construct new software. Although the idea of software reuse has been applied and practiced since programming began, the concept of systematic reuse, as a field of study in software engineering, was introduced by Doug McIlroy in 1969 [Mci69]. McIlroy envisioned the construction of complex systems using parameterized families of software components, able to satisfy the needs of any type of user. Later, David Parnas [Par72] developed the information hiding principle and the idea of program families, which became the engineering foundation for reuse based application development. Soon after, extensive research efforts on software reuse followed, with the result of the development of a great diversity of techniques. All of them includes some sort of abstraction (components seen as a "black box"), selection (catalogues of components), specialization (configuration of components through parameters) and/or integration (combination of components), as pointed out in [Kru92, FK05] and references therein.

Nowadays, reusability is of wide interest because of the need of software engineers to construct highly complex systems in a more reliable, cheaper and timely way [MC08, FK05, MMM95, PD93]. As pointed out in [FK05], a crucial breakthrough in software reuse is the concept of Software Product Lines (SPLs). The key idea is that most software systems are not entirely new, in contrast, they are variants of systems that have already been built. Essentially, a SPL consists of a family of systems that share functionality and satisfy, in general, the needs of a particular user [Gom05, CN02]. Recently, the Software Engineering Institute (SEI) [SEI11a] developed a framework called Product Line Engineering (PLE) for reuse-based development of a family of closely related applications [CN02]. The main goal of PLE is to achieve software reuse in a strategic, prescribed way, while using a managed set of features [JKB08].

Software PLE and Model-Driven Software Development (MDD) are two recent trends that have been drawing increased attention from the software development community. Essentially, MDD [BG05] is a software engineering methodology based on models of the system to be constructed and the evolution of those models, in order to perform an incremental development. Models allow to directly capture the needs of the stakeholders, and abstract from specific implementation details, more amenable to analysis. In MDD, models are source artifacts and they are used for automated analysis and code generation. Generative software development [Cza98] and related approaches have been the integration of PLE and MDD [CAK+05]. While MDD allows to represent different aspects of a SPL more abstractly, PLE provides a well defined scope, which puts the development and selection of appropriate modeling languages on a firm basis. Moreover, automated analysis and code generation permits the automatization of product line member creation.

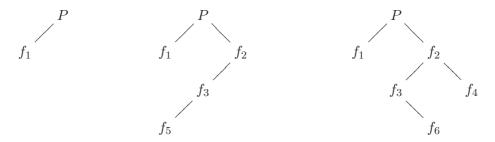

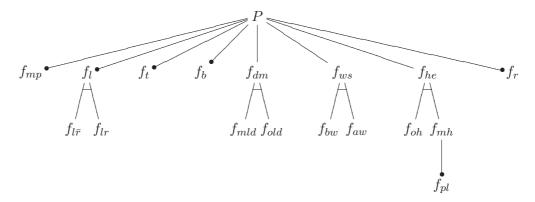

Feature modeling is a technique for representing the commonalities and variabilities

among a set of related systems in a concise way. Usually, Feature Diagrams (FD) are used to document this, using hierarchies of features that describe different types of variability [KCH<sup>+</sup>90, Kan10, CHE05a, CHE05b]. A particular technique of Model-Driven Development of Product Lines, based on model templates is proposed in [Cza05]. A feature-based model template consists of feature models and annotated models implementing the features. The annotations refer to the features and can have the form of any notation defined using the Meta-Object Facility (MOF) [omg06], such as Unified Modeling Language.

The Unified Modeling Language (UML) has become the industry and academic standard for system specification. UML Statecharts are one of the most important constituents of UML models, since they are widely used for modeling the reactive behavior of systems. The fact that the semantics of UML is only informally described leads to many ambiguities and inconsistencies, which renders difficult or impossible the application of a formal design process.

The subject of this thesis is the formal specification of families of systems that share some functionality. In particular, it investigates an expressive modeling formalism for specifying Software Product Lines, based on a formal approach of UML state machines, in conjunction with Feature Diagrams. By achieving this, the expressivity of UML Statecharts can be augmented with the explicit handling of behavior refinement. A complete semantics will allow the incorporation of the resulting proposal in Model-Driven Development methods.

## 1.1 Contribution of this Work

The primary goal of this thesis is to specify the behavior of a Software Product Line (SPL) using formal methods. It constitutes an advance towards a complete formal semantics of UML Statecharts with Variabilities in a SPL context. The main contribution is the formulation of a notion of refinement based on UML Statecharts, which can be integrated into software engineering tools. This could provide solid formal background that helps to bridge the gap between the needs of modern software development techniques for a formal specification language and UML, which is mainly described using natural language. Applying formal rigour to the precise semantics of these models and languages allows to automate the steps needed to transform models, as well as to trace and analyze those transformations. Each model should be based on a formalism, in order to rigorously define its syntax and semantics. Unfortunately, UML's lack of rigour can lead to ambiguous, imprecise and contradictive specifications.

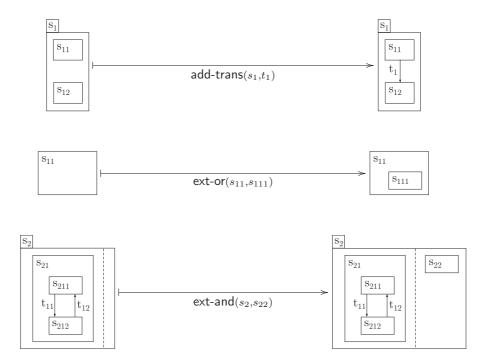

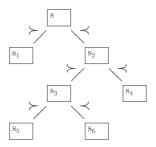

In this work, Feature Diagrams (FDs) are used to represent the common and variant functionality of a family of products, presenting a formal syntax for Feature Diagrams and its configurations. On the other hand, based on von der Beeck's [vdB02] UML Statecharts abstract syntax, an order relation is defined among the set of UML Statecharts, which represents when an UML statechart has a richer structure than another one. This relation sets the basis for the definition of behavior refinement of a UML statechart. Then, an operation able to combine different extensions of a given statechart is defined. With these notions, and given the description of a family of products as a FD, an UML Statechart with Variabilities is defined as a function that associates each feature of the FD with a statechart. The mapping must comply with the hierarchical structure and the feature restrictions, i.e., the more features a product has, the richer the statechart that models it must be. In this way, it is possible to describe the effect that each feature has on the products in which it is present. This definition provides a very simple and flexible way to obtain the specification of the behavior of any configuration of the product line as the combination of the statecharts that implement all the features present in that product. We consider both the extension relation and the definition of UML statechart with variabilities authentic contributions. The first one, because it provides an ordering among the abstract syntax defined in [vdB02], which proved to be a semantic preserving one, in the sense of a properly defined structural operational (SO) semantics. The second one, because it allows to integrate parts of two different modeling languages, FDs and UML Statecharts, through its abstract syntax.

Then, based on the extension relation, the concept of behavioral refinement of a UML statechart is explored. In contrast to most of the related work, in which there are no exhaustive proofs, it is proven that it is possible to extend a statechart without loosing any behavior, in the sense of the SO semantics proposed in [vdB02]. That is, when a statechart is extended, it is still possible to perform the same semantic transitions on it as before. Therefore, the extension relation can be considered as a behavioral refinement, as it preserves the behavior, but adding new functionalities. Moreover, it is also proved that the set of actions generated by the SO semantics of a given statechart is preserved with any possible extension of it. We consider this also as a contribution because, until the date this work was finished, there were no concrete formal refinement patterns for UML Statecharts, with the sole exception of [MNB04], which uses a different priority mechanism for the transition firing from UML's.

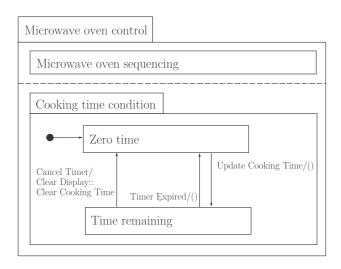

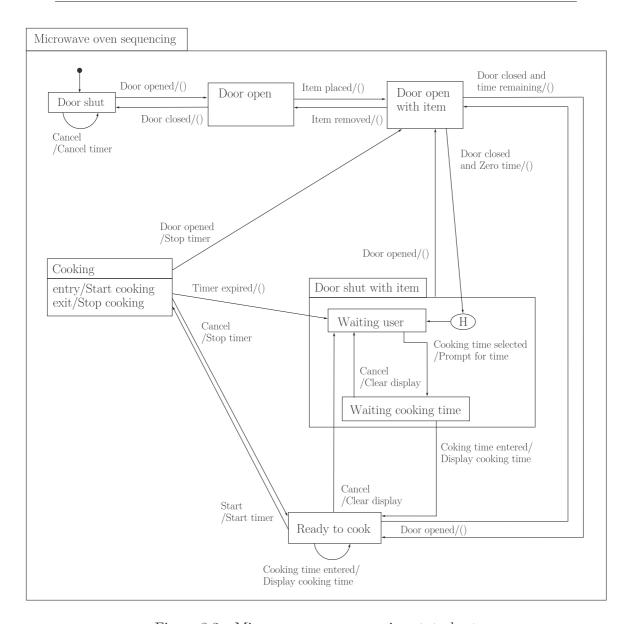

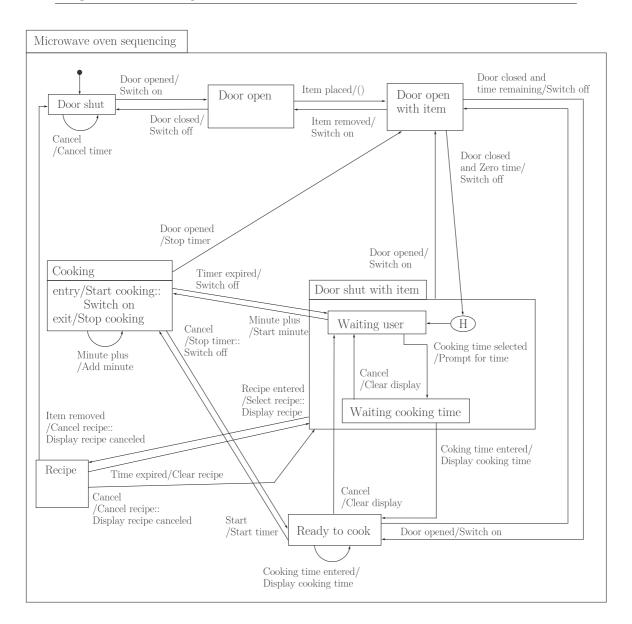

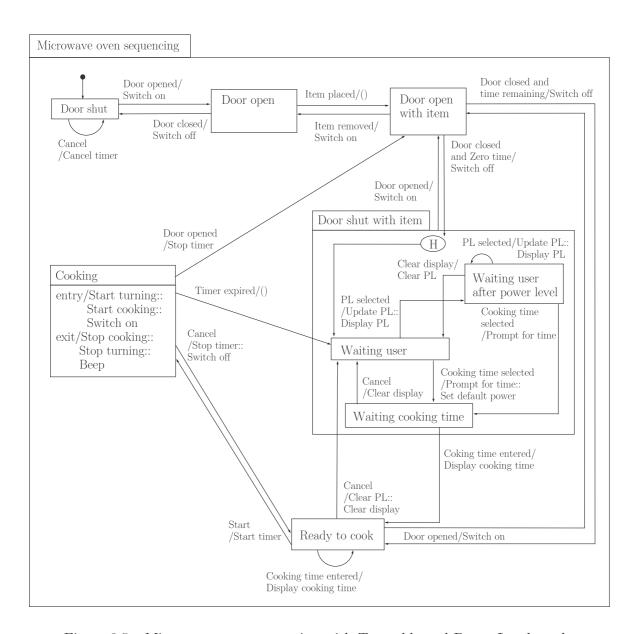

Finally, the practical point of view of this proposal is addressed, through the construction of a tool prototype called "SC\* Modeler". This prototype was constructed basically for checking the adequacy of the definitions and for exploring the possibilities of a future software engineering tool. Using this tool, a case study for a product line of microwave oven systems, adapted from a classic SPL modeling book [Gom05], was implemented.

## 1.2 Related Work

Variability modeling is a domain specific modeling technique, that is becoming more integrated into traditional software engineering. Unfortunately, it is not integrated to UML. Software Product Line Engineering with UML received a lot of attention in recent years, but most of these works "only concern variability in UML static models and few works concern behavioral models" [CABA09]. In a formal setting, few citations are relevant. In [CGW05] a formal semantics of UML interactions with variabilities is given, and in [ZHJ04a, ZHJ04c, ZHJ04b, CABA09] UML sequence diagrams with variabilities are formalized using an algebraic framework for synthesizing flat statecharts from the sequence diagrams. In [GL10], the authors define functions which map UML Statechart components to functionalities of a Feature Diagram. Then, the behavior of a product line is obtained essentially by a selection process, and not a combination of statecharts, in contrast to the present work. In [FG08], the authors define a general labeled transition system framework for describing families of products. Using this framework, products can be derived, but this approach is not intended to be used to describe product families, but rather "to give basic modeling concepts on which verification activities can be carried out".

Although UML Statecharts refinement has already been investigated in a formal setting [GL10], [MNB04] and [SK10], there is still a lack of a formal definition of behavioral refinement for UML Statecharts. The UML 2.0 documents use the term refinement (and its counterpart, abstraction) without a specific definition or meaning [Gr005]. Sun Meng et al. [MNB04] propose refinement patterns similar to the ones presented in this work. Their semantics is based on Lattela et.al. [LMM99], which uses a priority mechanism (of conflicting transitions) which is the opposite as required in the UML specification [Gr005]. Moreover, the refinement laws are abstract and elementary, and there are no proofs regarding the resulting behavior once the rules are applied.

The closest work to the present one, in terms of the results obtained, is the recent paper by Schönborn et al. [SK10], based on the semantics presented in [FS06]. Regarding the UML coverage of the semantics, they do not model history pseudostates, and according to them it is a "harder challenge" to implement, compared to other missing UML features like fork and join states. Moreover, they do not model entry and exit actions. Regarding the refinement patterns, the authors allow the removal of behavior from a statechart, contrary to the present work. With respect to the actions generated by the refined statecharts, which can be a "data-refinement" of the original actions, these are not treated in that work.

## 1.3 Outline of this Thesis

This thesis is structured as follows: In chapter 2, the general context of this work is presented. A brief description of the current state-of-the-art in formal approaches for UML Statecharts is given, together with the concept of Software Product Lines and its relation with Feature Diagrams as a tool for modeling the variability of a family of systems. In chapter 3, the syntax and semantics of UML Statecharts are presented. The work contained in this chapter is based on [vdB02]. In chapter 4, an extension relation is defined between UML Statecharts, in order to give a formal definition of when a given statechart has a richer behavior than another one. Then, it is shown how to combine different extensions of a given statechart into an integral new one. In chapter 5, main concepts and definitions of formal variability modeling are presented. The syntax and configurations of Feature Diagrams and the definition of UML Statechart with variabilities is given. An early version of the work contained in this chapter and the previous one is published in [SV08]. In chapter 6, it is proved that the extension relation can indeed be considered as a refinement, in the sense that it preserves the semantic transitions defined in the semantics. Moreover, a theorem that proves that the set of possible actions generated by a statechart are preserved by the refinement is given. The work contained in this chapter is published in [SV10]. In chapter 7, the description of a prototype implementation of the ideas introduced in this work is presented. In chapter 8, a case study for a product line of microwave oven systems is presented is order to analyze and validate the proposal. Conclusions, related work, and future research are given in chapter 9.

# Chapter 2

# Background

In this chapter, main concepts of behavior specification of families of systems are presented, constituting the general context in which the subject of this work is placed. Model-Driven Development is introduced, as a software engineering methodology based on the systematic use of models, capable of reducing development costs. The use of the Unified Modeling Language (UML) is motivated as a modeling language for this purpose, in particular, UML Statecharts for behavioral modeling. Next, a brief description of the current state-of-the-art in formal approaches for UML Statecharts is given and a rationale for the choice of the particular formalization used in this work is also examined. Finally, Software Product Lines are presented together with its relation with Feature Diagrams as a tool for modeling the inherent variability of a family of systems, and a brief description of the current state-of-the-art in formal variability modeling is presented.

## 2.1 Model-Driven Development

The use of models in engineering and applied sciences is one of the most fundamental technique for addressing inherent complexity. Models provide abstractions of a real-world system that enables the reasoning about that system by ignoring superfluous details while focusing on the relevant ones. Models are used in many ways: predicting the system behavior, reasoning about particular properties, early evaluation about possible system changes, and even communicating important system characteristics. Depending on what is considered relevant, various modeling concepts and notations may be used, in order to provide different "views" of the system. Furthermore, it is often necessary to transform between different views of the system at an equivalent level of abstraction, for example, between a structural view and a behavioral view. In other cases, a transformation converts models between levels of abstraction, usually from a more abstract to a less abstract view, by adding more detail.

Models and model transformations form the basis for a set of software development techniques known as Model-Driven Development (MDD) [BG05]. In that context, models are used to reason about the problem and the solution domain. Applying formal rigour to the semantics of these models, it is possible to define precise rules in order to automate the steps needed to transform one model to another; to trace between model elements and transformations and to analyse relevant characteristics of the models. Each model should be based on a formalism, in order to rigorously define its syntax and semantics. Syntax refers to the way that symbols may be combined to create well-formed sentences in the language, that is, the form and structure of symbols in a given language. Semantics, on the other hand, defines the meaning of syntactically valid strings in a language. Three main semantics approaches can be distinguished: Operational semantics, in which the meaning of a construct is specified by the computation it induces when it is executed

(how to execute); Denotational semantics, in which the meaning is modeled by mathematical objects that represent the effect of executing the constructs (effect of the execution); and Axiomatic semantics, in which the meaning is expressed through properties about the language constructs, expressed with axioms and inference rules from symbolic logic (correctness properties). Visual formalisms are also very useful in order to simplify the communication between different stakeholders involved in a software development process.

One specific implementation of the MDD is the Model-Driven Architecture (MDA), which is supported by the Object Management Group (OMG) [Gro11]. MDA introduces a set of layers that describe different levels of abstraction and uses model transformations as a central element, principally to transform high-level models (such as platform-independent models) toward more implementation-oriented models (platform-specific models). A key characteristic of the MDA approach is to recognize that transformations can be applied to abstract descriptions of some aspect of a system to add more detail, refine that description to be more concrete, or to convert it to another representation. The MDA approach provides an open, neutral basis for system interoperability via OMG's established modeling standards [BG05]. MDA uses the Unified Modeling Language (UML) as its specification language [Gro05]. This language has become the industry and academic standard for system specification.

## 2.2 Unified Modeling Language

The Unified Modeling Language (UML) is a set of graphical languages for specify and document the artifacts of a software-intensive system. These languages allow specifying a wide variety of aspects of a system, from static structure to dynamic behavior. Structure can be described with static model elements such as classes, relationships, nodes, and components. Behavior describes how the elements within the structure interact over time. Moreover, any UML language can be extended by its own extension mechanisms in order to define domain-specific models.

UML has its roots on object-oriented modeling languages. From the late 1980s, practitioners, faced with a new generation of increasingly complex software systems, began to experiment with alternative approaches to analysis and design. Learning from experience, three clearly prominent methods emerged, each one with its own notation: The Booch method devised by Grady Booch; the Object Modeling Technique (OMT) devised by Jim Rumbaugh; and the Object Oriented Software Engineering (also known as Objectory) devised by Ivar Jacobson. The UML standardization effort started officially in October 1994, with the establishment of a UML consortium, with several partners conformed by leading software industry firms. Finally, UML 1.0 was offered for standardization to the Object Management Group (OMG) in January 1997.

UML 2.0 presents four languages to specify dynamic behavior: Use Cases, State Machines, Activities, and Interactions. Use cases captures the behavior of the system as it appears to an outside user. It specifies functional requirements of the system from the user point of view. State Machines, which are the main concern of this work, specify the dynamic behavior of objects over time. Each object communicates with the rest of the world by detecting events and responding to them. An Activity is a graph of nodes that shows the flow of control and data through the concurrent steps of a computation. Finally, Interactions are used to describe how a set of objects interact with each other in a specific scenario.

UML is defined using a metamodel, that is, a model of the constructs in UML. The metamodel itself is expressed in UML. Each section of the UML specification document contains a diagram showing a portion of the metamodel; a text description of the elements defined in that section, with their attributes and relationships; a list of constraints on elements expressed in natural language and in Object Constraint Language (OCL); and a

text description of the dynamic semantics of the UML constructs defined in the section. According to [RJB04] "The dynamic semantics are therefore informal, but a fully formal description would be both impractical and unreadable by most". The metamodel is divided into two main packages, structure, which defines the static structure of UML and behavior, which defines the dynamic structure of UML.

Although UML is simple and flexible, it is not the ideal MDA specification language since it is defined using natural language and/or semi-formal language instead of being described in a fully formal way. The lack of a formal setting leads to ambiguous (interpreted in more than one way are possible), imprecise (no clear statement is made), inconsistent (some parts are in contradiction with other ones) and erroneous (it is unclear whether the implicitly given interpretation is the intended one) specifications, as pointed out in the literature [SG98, RW99, FSKdR05, FKS05]. Many of the detected ambiguities and inconsistencies are removed in UML 2.0 [Gro05], but new ones are introduced. Without a rigorous semantic definition, precise model behavior over time is not well defined and automatic code synthesis is not possible to achieve.

This deficiency can be understood in part, because there are thirteen diagram types in UML 2.0. Each notation itself forms a complex language, and the notations are interrelated and interdependent, making the task of providing a unified semantics very challenging [HR00]. These drawbacks are present since the beginning of UML, and promoted extensive academic work in order to solve them [BCR00, BLMF00, CGW05, CK01, Mer02, Krü02, CK04, SZ08, CGW06, BCR, GZK02, Jür02, RCA01, SH05, Stö03, BCD<sup>+</sup>06]. In general, these works were developed independently, which implies a weakness for achieving a complete and unified semantics. Recently, an heterogeneous approach to the semantics of UML is proposed which deals with the integration of different formalisms. The idea is to define a family of formalisms capturing various UML sublanguages, and morphisms that represent the expected semantic relationships between them [CKTW08]. For the purposes of this work, a survey on the formal semantics approaches for UML Statecharts is given in section 2.4.

## 2.2.1 UML Statecharts

In several branches of computer science state transition diagrams are commonly used to describe the behavior of real world systems. Those diagrams represent a model of computation called finite state machine, which consists of a finite set of states, an initial state, an input alphabet of events and a transition function which maps current states and event symbols to next states [HU79]. However, as soon as the behavior of the described system becomes complex, the diagram gets unmanageable from the modeler's point of view (this is usually called state and transition "explosion").

In the late 80's, Harel [Har87] developed an effective visual formalism able to express structure by means of hierarchical states. He called this visual formalism "statecharts". In Harel words, this new formalism "extends conventional state transition diagrams with essentially three elements, dealing, respectively, with the notions of hierarchy, concurrency and communication". Basically, it allows to describe states in a modular way. In contrast to the usual state transition diagrams which are flat, unstructured and sequential, in the statecharts philosophy each state consists of a hierarchy of states. Behavior is then modeled by the execution of series of actions which are determined by transitions that are triggered by events, one by one being dispatched. Unfortunately, Harel's extension comes with a price: it is only a visual formalism. Far from being a finished work, statecharts evolved over the years, summing up to at least 20 variants [Bee94, Har97].

UML behavioral state machines, UML Statecharts, are extensively used in the software engineering community for modeling the reactive behavior of object-oriented systems. UML Statecharts were incorporated by the OMG to UML 1.1 in 1997, and it was subject to examination during the UML 1.2 and 1.3 revisions. Moreover, UML Statecharts are one of

the four languages to specify dynamic behavior and serves the foundation for Interactions [Gro05], and was for Activities in UML 1.x.

## 2.3 Formal Methods

Formal methods is the name usually given to a set of design techniques that rigorously use mathematical models to build software systems. In contrast to other design systems, formal methods use mathematical proofs as a complement to system testing in order to ensure correct behavior. As systems become more complex, the formal approach to system design offers an additional level of confidence. Formal design can be seen as a three step process: First, the formal specification phase. The designer defines a system using a modeling language. This is the process of converting a problem written in natural language into a mathematical notation. Formal modeling languages syntax is rigorously defined, making it possible to distinguish between well-formed formulas and non-well-formed ones. The second phase is the verification: This is the stage in which formal methods differ most from other specification techniques and it involves the use of theorems in order to prove that the system is correct. It is a difficult process, because even a simple system comprises several theorems. In order to accomplish this, almost any formal method uses some sort of automated or semi-automated proving tool. These tools can prove elementary theorems, verify the semantics of the system, or just provide assistance for developing complicated proofs. The third and final phase is the implementation, in which the specification is converted into code. This conversion can be done using code generators in order to obtain provable-correct by construction implementation, which implies a substantial reduction of testing effort. Code generation is the essence of model driven approaches in order to be able to abstract specific implementation details from the designer's mind. Then, the the code generators automatically translate models into implementations.

As mentioned before, the main benefit of formal methods is provability. Furthermore, formality promotes discipline, because it requires thinking in a more systematic way. This discipline can help identifying faulty reasoning in earlier stages of software development. Formal methods also provide a formal and rigorous framework as in other classical (mechanical, civil) engineering processes. The use of formal specification languages, which are generally coupled with a system of logic inference, enables the construction of automatized tools that verify the formal properties of the conceptual models created in the earlier stages.

## 2.4 Formal Semantics Approaches of UML Statecharts

As mentioned in section 2.2 UML languages are only informally defined. Several efforts have been made in order to give formal semantics to these UML languages. In order to illustrate the landscape of different semantic approaches to UML Statecharts, a succinct categorization based on [CD05] and [DJPV02] is given. Three main broad categories of approaches can be distinguished, according to the underlying formalism: Mathematical Models, Rewriting Systems and Translation Approaches.

1. Mathematical Models: This category comprises semantic approaches which are based directly on standard mathematical concepts and notations. The advantage of using a mathematical notation is that it encourages precision and attention to detail, making it more likely that the resulting semantics is complete and unambiguous. In principle, the notation should be accessible to anybody with a standard mathematical background. Four subcategories can be distinguished: Labeled Transition Systems, Abstract State Machines, Petri Nets and other approaches. These approaches will be described in detail in section 2.4.1.

- 2. Rewriting Systems: A rewrite system typically consists of a set of rewrite rules, consisting of a left- and a right-hand side. The execution of a rewrite system involves the repeated application of the rules to some "configuration". In each application, an occurrence of the left-hand side of a rule in the configuration is replaced by the right-hand side. The execution terminates when no matching rule can be found. As a rewriting system based formalism, the authors distinguish between Graph Rewriting and Term Rewriting. Graph rewriting (also called graph transformation) provides a mathematically precise and visual specification technique by combining the advantages of graphs and rules into a single computational paradigm. On the other hand, Term rewriting is a similar concept to graph rewriting, except that the rewrite rules are performed on terms rather than on graphs. An introduction to the subject can be found on [EEPT06] and [BN98].

- 3. Translation Approaches: This category contains approaches which rely on translating a UML state machine into some other formal language, such as a specification language, the input language to a model checker, or a programming language. As a translation based formalism, the authors distinguish between Model Checking Languages and Specification Languages. Model checking is a well-researched dynamic analysis method in which systems are modeled as finite state models. Temporal logic is used to define properties and the models are checked to verify whether these properties hold. This approaches typically transforms UML Statecharts into a language designed for such analysis. It is important to mention that model checking languages are not considered truly formal languages. A good introduction to the subject is [Hol03]. On the other hand, several approaches attempt to inject formalism into UML state machines by translating them into an already formalized specification language, such as Z. An introduction to the subject can be found on [Jac96].

## 2.4.1 The Mathematical Approach

Since the formalism used in this work belongs to the mathematical approach, a detailed description is presented in this section. As mentioned before, four subcategories can be distinguished:

- Transition Systems: In general, a transition system is essentially a structure  $(S, \longrightarrow)$  where S is a set of configurations and  $\longrightarrow$  is a binary relation on  $S \times S$  (called the transition relation). Some examples of transition systems are Labeled Transition System (LTS), Kripke structures and Symbolic Transition Systems. A natural reference is [MP92, MP95]. The formalization used in the present work is included in this category. The most relevant approaches included in this category are [EW00, Esh09], [LMM99, GLM02, MLG06], [Kw000], [RACH00, CR09] and [vdB02].

- Abstract State Machines: Basically, Abstract State Machines (ASMs) are finite sets of transition rules of the form if Condition then Updates which transform abstract states. The Condition (also called guard) under which a rule is applied is an arbitrary predicate logic formula without free variables, whose interpretation evaluates to true or false. Updates is a finite set of assignments of the form  $f(p_1, ..., p_n) := p$  where  $p_i$  are arguments and p a specified value, which evaluates to  $v_i$  and v respectively. The execution is the change in parallel of f at the locations  $v_i$  to the value v. The syntax of ASMs is reminiscent of a simple imperative programming language which makes them quite accessible to users with a programming background. A software engineering introduction to ASMs is [BS03]. ASMs can also be considered transition systems [BCR04]. The most relevant approaches included in this category are [CR00, BCR04], [CHS00, SCH02], [JEJ04], [JÖ2, Jür04] and [KG10].

- Petri Nets: Petri nets are a well-studied and intuitive formalism that is both graphical and mathematical. Petri nets are a bipartite directed graph consisting of two kinds of nodes and two kinds of arcs. The nodes are places and transitions. The arcs are either input arcs or output arcs. A place is connected to a transition via an input arc. A connection from a transition to a place is established via an output arc. Arcs between the same kinds of nodes are not allowed. The places from which an arc runs to a transition are called the input places of the transition; the places to which arcs run from a transition are called the output places of the transition. A Petri net furthermore consists of tokens represented by dots within places. A transition of a Petri net may fire whenever there is a token at the start of all input arcs; when it fires, it consumes these tokens, and places tokens at the end of all output arcs. The firing is atomic, i.e., a single non-interruptible step. Natural references for Petri nets in software engineering are [Pet81, GV01]. Petri net formalism was introduced in [Pet62]. The most relevant approaches included in this category are [BP01, BP05], [BDM02, MC02], [KP00] and [GZ09].

- Other: It is a residual category of approaches that are not included in the preceding ones. Approaches included in this category are [LC08, LC09].

#### 2.4.2 Rationale of the Transition Based Formalism

The explanation of the fundamental reasons for choosing the transition based formalism starts with Gordon Plotkins's [Plo81] words on transition systems: "Very little is required in the way of mathematical background; all that will be involved is symbol-pushing of one kind or another of the sort which will already be familiar to readers with experience of either the non-numerical aspects of programming languages or else formal deductive systems of the kind employed in mathematical logic". Structural Operational Semantics (SOS) was introduced by Plotkin in [Plo81]. A SOS specification defines the behavior of a program in terms of a set of transition relations. SOS specifications take the form of a set of inference rules which define the valid transitions of a composite piece of syntax in terms of the transitions of its components. SOS was intended as being like an abstract machine but without all the complex machinery in the configurations, just the minimum needed to explain the semantical aspects of the programming language constructs. The extra machinery is avoided by the use of the rules, making the exploration of syntactical structure implicit rather than drearily explicit. In an operational semantics the focus are the operations the system can perform. In Plotkin's words: "... it is an operational method of specifying semantics based on syntactic transformations of programs and simple operations on discrete data. The idea is that in general one should be interested in computer systems whether hardware or software and for semantics one thinks of systems whose configurations are a mixture of syntactical objects - the programs and data - ...". In the operational semantics the meaning of a construct is specified by the computation it induces when it is executed on a machine. In particular, it is of interest how the effect of a computation is produced. This leads to an ease on the implementation of an SOS semantics in a rule based programming language, like Prolog.

Von der Beeck's [vdB02] semantics provides a reasonable coverage of UML 1.4 statecharts features, and it is easy to extend both its syntax and semantics. The approach includes full support of the history mechanism (shallow and deep cases) and intralevel transitions which are in general not supported by the rest of the approaches. As will be presented, the definition of the semantics is modularized in two phases as follows: In the first phase an auxiliary UML Statecharts semantics is defined which only deals with processing single input events, but not with sequences of input events. In a second phase this auxiliary semantics is used to define the (complete) UML Statecharts semantics, which is done by processing sequences of input events. This separation already supports modularity. Furthermore, concepts from the SOS approach are used, that is, the auxiliary semantics

is a function on the set of labeled transition systems and where the (semantic) transitions work on single input events. For the second phase, Kripke structures are used as the semantic domain. This selection simplifies the processing of event sequences considerably, since Kripke structures are very appropriate for modeling the fact that the output of one step serves as (part of) the input of the next step. Both phases constitute an operational and modular approach, such that comprehension as well as flexibility (e.g. with respect to subsequent enhancements) are supported without restricting preciseness.

Another advantage of von der Beeck's semantics is that all of the features implemented comply with the UML specification [Gro05], as for example the conflicting transitions execution priority or the maximality principle (in each step of the semantic execution, the maximum number of non conflicting transitions must be taken).

However, many features of UML State charts have not been considered in this work: final, junction, choice and terminate pseudostates; deferred, time, and change events; completion transitions; guards, variables, and data dependencies in transitions; creation and destruction of objects; send clauses within actions; and do actions. Some of those features can be covered easily, like final pseudostates and do actions. In section 9.2.1 a comment on possible extensions, in order to cover a wider range of UML 2.0 state charts features, will be given.

## 2.5 Software Product Lines

According to the Software Engineering Institute [SEI11a], a Software Product Line "is a set of software-intensive systems that share a common, managed set of features satisfying the specific needs of a particular market segment or mission and that are developed from a common set of core assets in a prescribed way. A Software Product Line epitomizes strategic, planned reuse.". One of the major motivations behind Software Product Lines (SPLs) is that they can be more efficient to manage a group of similar software systems as a whole, rather than considering each individual system on its own [Gom05, CN02, SEI11b]. The main goal of SPL engineering is to achieve software reuse in a strategic, prescribed way, while using a managed set of features [JKB08].

SPL engineering introduces two new dimensions into the traditional software engineering approaches: variability modeling and product derivation. Variabilities are characteristics or features that varies from one product to another, whereas product derivation is the process of constructing products from the product line.

#### 2.5.1 Variability Modeling

SPL engineering has to provides a mean to describe the commonalities and variabilities between different products. Usually, Feature Diagrams are used to document this. Feature Diagrams are a family of popular modeling languages used for engineering requirements in SPLs. Feature Diagrams were introduced by Kyo Kang in 1990 as part of the Feature-Oriented Domain Analysis (FODA), which is a method for systematic discovery and exploitation of commonality across related software systems to support software reuse [KCH<sup>+</sup>90, Kan10].

Although there were initial attempts to develop a formal definition for FD, the first systematic treatment of formal semantics was given by [SHT06, SHTB07]. In that work, Schobbens et al generalizes the various syntaxes found in the literature into a generic construction, called Free Feature Diagrams (FFD). The formal semantics is then defined at FFD level, in which "all formalization choices found a clear answer in the original FODA FD definition". Finally, they showed that the original FODA FD definition suffered no ambiguity problem. Due its importance, a comparison with the present work is given in chapter 5.

In [CHE05a] and [CHE05b], Czarnecki et al. define a new Feature Diagram language to account for staged configuration. They introduce feature cardinality (the number of times a feature can be repeated in a product) in addition to the more usual (group) cardinality. The semantics is defined in a staged process where FDs are translated into an extended abstract syntax, a context-free grammar and an algebra. In [JB08], the authors provide a formalization of dependencies between features and components and propose automated techniques to derive additional information and provide feedback to the user. Other approaches include [dJVI02] which proposes the use of context-free grammars and the feature configurations are defined as the sentences generated by the pertaining grammar. This idea is extended in [Bat05] by combining grammars and propositional logic. Van der Storm [VDS07] maps features to components, which are organized in a dependency tree.

### 2.5.2 Product derivation

Although variability in software systems is not a new problem, the key difference in a SPL context is that variability involves not only a single product and variability cannot be resolved after the product is delivered to the user. In this context, variability must be specified in the development process and is an integral part of the product line. The "single product" variability is usually called "run time variability", and the SPL variability is usually called "development time variability" [ZHJ04c].

Product derivation support of a particular SPL engineering approach is an important criteria in order to go beyond the description of the PL and serve the propose for resolving variability and obtaining products [CABA09]. Current product derivation approaches can be classified into two main categories: configuration based and transformation based [PKGJ08].

The first approach bases the derivation process on Feature Models (FD). For example, in the FORM approach [KKL<sup>+</sup>98], Kang et al. define a derivation process which starts with an analysis of commonality among applications in a particular domain. The model constructed during the analysis is called a feature model, which captures mandatory and alternative features. This model is used to define parameterized architectures and reusable components instantiatable during application development. According to the authors "Parameterization of artifacts with features and development of applications through selection of feature sets is a powerful synthesis technique for implementing an effective application generator for a stable domain". This refinement approach was later formalized by Czarnecki [CHE05a, CHE05b, Cza05]. In that work, feature models are mapped to UML activity and class diagrams via annotations, and then an automated configuration process is realized. In [Pre03], the author presents a set of graphic "plug-and-play" specification rules for the construction of statecharts, which allows to combine features based on semantic refinement. In that work, a refined statechart has fewer possible traces and is hence more concrete, in contrast to the present work in where a refined statechart has an augmented behaviour. In [VG07], the authors provide a mapping from the problem domain (modeled as a feature model) to the solution domain.

The second approach consists of transforming core assets rather than configuring them. In general this approach is aligned with MDA standards. Usually, at the requirements level, the product line is modeled in terms of UML use cases and then model transformations relates this requirements to core assets, modeled in terms of UML class and sequence diagrams. The variability is realized via stereotypes, and OCL constraints are used in order to ensure consistency. Finally, a model transformation taking the product line model as its parameter, transforms the core assets into a platform specific model which is finally implemented in the target platform [ZJ06, KMHC05, ZHJ04c].

## Chapter 3

# Syntax and Semantics of UML Statecharts

In this chapter, main concepts and definitions of UML Statecharts used in this work are presented. These definitions are based on the paper "A structured operational semantics for UML-statecharts" by M. von der Beeck [vdB02]. First, the formal syntax of UML Statecharts is presented and the concept of configuration is discussed. Then, given a UML statechart, it is shown how a UML statechart transition modifies the actual configuration of the state. After that, the two phase semantics is presented, first, the auxiliary semantics which only deals with single input events, and second, the complete semantics who deals with sequences of input events.

## 3.1 Syntax

UML Statecharts (or simply statecharts) constitutes a notation to describe behavioral aspects of a system. As mentioned before, UML Statecharts are a generalization of finite state diagrams. Basically, UML Statecharts consist of states and transitions between them. The main feature of statecharts is that states can be refined, defining a state hierarchy. The decomposition of a state can be either sequential or parallel. In the first case, a state is decomposed into a new state automaton (OR state), while in the second case a state is decomposed in two or more automata that can execute concurrently (AND state). Transitions are directed arrows between states. A transition connects a source state to a target state, and inter-level transitions are allowed. Transitions are labeled by a trigger event, a sequence of actions and the type of history of the target state. There is a history mechanism that allows transitions to reenter a sequential state in the last active substate. UML Statecharts follow the run-to-completion assumption, that is, "an event occurrence can only be taken from the pool and dispatched if the processing of the previous current occurrence is fully completed" [Gro05].

UML distinguishes between states and pseudostates. The key difference is that pseudostates are never elements of an active state configuration; they mainly serve to model compound transitions or to reduce the graphical complexity. Pseudostates do not have names or associated actions. An example is the history pseudostate.

Let  $\mathcal{S}$ ,  $\mathcal{T}$ , A, E be countable sets of state names, transition names, actions and events respectively with  $\mathsf{E} \subseteq \mathsf{A}$ .  $\mathcal{S}$  contains an empty name denoted by  $\lambda$ . Events and actions are denoted by a,b,c,... and sequences of events as well as actions by  $\alpha,\beta,\gamma,...$ . The empty sequence is denoted by (). The set  $\mathsf{SC}$  of statecharts is inductively defined by the rules in figure 3.1, together with the functions name:  $\mathsf{SC} \to \mathcal{S}$ , that is, the name of the statechart, and the predicate wf-tran (defined below), which decides if a transition is well formed with

respect to a set of states. Abusing the notation,  $\mathsf{name}(s)$  is abbreviated with  $\hat{s}$ . The same applies to transitions.

$$\frac{\hat{s} \in \mathcal{S} \quad en, ex \in \mathsf{A}^*}{[\hat{s}, (en, ex)] \in \mathsf{SC}} \quad \mathsf{Basic} \qquad \frac{s_1, ..., s_n \in \mathsf{SC}, \ \hat{s}_i \neq \hat{s}_j \ \forall_{i \neq j}}{[\hat{s}, (s_1, ..., s_n), (en, ex)] \in \mathsf{SC}} \quad \mathsf{And}$$

$$\frac{s_1, ..., s_n \in \mathsf{SC}, \ \hat{s}_i \neq \hat{s}_j \ \forall_{i \neq j}}{[\hat{s}, (s_1, ..., s_n), (en, ex)] \in \mathsf{SC}} \quad \mathsf{And}$$

$$\frac{s_1, ..., s_n \in \mathsf{SC}, \ \hat{s}_i \neq \hat{s}_j \ \forall_{i \neq j}}{\hat{s} \in \mathcal{S}, \ \hat{s} \neq \hat{s}_i \ \forall_{i = 1...n}} \quad T \subseteq \mathsf{T}, \ \mathsf{wf-tran}(\{s_1, ..., s_n\}, t) \ \forall t \in T$$

$$\hat{s}_l \in \mathcal{S}.l \in \{1, ..., n\}$$

$$\hat{s}_d \in \mathcal{S}.d \in \{1, ..., n\}$$

$$en, ex \in \mathsf{A}^*$$

$$\widehat{[\hat{s}, (s_1, ...s_n), \hat{s}_d, \hat{s}_l, T, (en, ex)]} \in \mathsf{SC} \quad \mathsf{Or}$$

Figure 3.1: Syntax of Statecharts

The rules are explained as follows:

**Basic Statecharts:**  $s = [\hat{s}, (en, ex)]$  is a basic statechart with name  $\hat{s}$ , entry sequence of actions en, exit sequence of actions ex and type(s) = basic.

**And-Statecharts:**  $s = [\hat{s}, (s_1, ..., s_n), (en, ex)]$  is an and-statechart with name  $\hat{s}$ , parallel substates  $s_1, ..., s_n, n > 0$ , entry sequence of actions en, exit sequence of actions ex and  $\mathsf{type}(s) = \mathsf{and}$ .

**Or-Statecharts:**  $s = [\hat{s}, (s_1, ..., s_n), \hat{s}_d, \hat{s}_l, T, (en, ex)]$  is an or-statechart with name  $\hat{s}$ , parallel substates  $s_1, ..., s_n, \ n > 0$ , entry sequence of actions en, exit sequence of actions ex,  $\hat{s}_d$  is the name of the default initial substate<sup>1</sup>, where  $d \in \{1, ..., n\}$  is the index of the default initial substate,  $\hat{s}_l$  is the name of the current active substate of s,  $l \in \{1, ..., n\}$  is the index of the current active substate, T is the set of transitions between its substates,  $s_1$  is the default state of s,  $\mathsf{type}(s) = \mathsf{or}$ . The syntax presented in [vdB02] is extended, requiring a default substate in the Or-Statechart. According to the UML superstructure specification [Gro05], a composite state without initial substate can be considered as an ill-formed model. Then, in this work, an initial substate is required.

The set of transitions T is included in  $T := \mathcal{T} \times \mathcal{S} \times \mathcal{P}(\mathcal{S}) \times \mathsf{E} \times \mathsf{A}^* \times \mathcal{P}(\mathcal{S}) \times \mathcal{S} \times \mathsf{HT}$ , where  $\mathsf{HT} = \{\mathsf{none}, \mathsf{shallow}, \mathsf{deep}\}$  are the history types.

Further define:

$$\begin{split} &\mathsf{SC}_B = \{s {\in} \mathsf{SC} \mid \mathsf{type}(s) {=} \mathsf{basic} \} \\ &\mathsf{SC}_A = \{s {\in} \mathsf{SC} \mid \mathsf{type}(s) {=} \mathsf{and} \} \\ &\mathsf{SC}_O = \{s {\in} \mathsf{SC} \mid \mathsf{type}(s) {=} \mathsf{or} \}. \end{split}$$

Given a statechart s, the following projection functions are defined:  $\mathsf{act}\text{-}\mathsf{en}(s) := en$  and  $\mathsf{act}\text{-}\mathsf{ex}(s) := ex$  which are the corresponding entry and exit sequences of actions. Given a

<sup>&</sup>lt;sup>1</sup>In order to simplify the notation, the name is denoted with the index only, because within a statechart each substate can be uniquely referred to by its name.

statechart transition  $t = \langle \hat{t}, \hat{s}_i, S_r, e, \alpha, T_d, \hat{s}_j, ht \rangle \in \mathsf{T}$ , the following are defined:  $\mathsf{name}(t) := \hat{t}$ , is the name of the transition t,  $\mathsf{sou}(t) := s_i$ ,  $\mathsf{tar}(t) := s_j$ , are the source and target states of t respectively,  $\mathsf{sou-r}(t) := S_r$ , is the source restriction set,  $\mathsf{ev}(t) := e$ , is the triggering event of t,  $\mathsf{act}(t) := \alpha$ , is the action sequence associated to t,  $\mathsf{tar-d}(t) := T_d$ , is the target determinator set,  $\mathsf{historyType}(t) := ht$ , is the history type of t. A transition t uses the history mechanism, if  $\mathsf{historyType}(t) \in \{\mathsf{deep}, \mathsf{shallow}\}$ . There are two types of history pseudostates defined in UML: shallow and deep history. A shallow history pseudostate is used to represent the most recently active substate. The shallow history pseudostate does not recurse into its substates active state configuration. A deep history pseudostate, in contrast, recurses into the most recently active substates of that substate, if they exist. That is, it "remembers" the active substates along the state hierarchy down to the basic states.

Source restriction and target determinator provide a means for modeling an interlevel transition by a simple transition on the level of the uppermost states the interlevel transition exits and enters. The source and target of the interlevel transition are represented as additional label information by the source restriction and the target determinator.

In the definition of Or-statecharts, the predicate wf-tran  $\subseteq \mathcal{P}(\mathsf{SC}) \times \mathsf{T}$ , defined by mutual recursion, decides if a transition t is well formed with respect to a set of states  $s_1,...,s_n$  and it is defined as wf-tran( $\{s_1...s_n\},t$ )  $\subseteq (\mathsf{sou}(t),\mathsf{tar}(t) \in \{s_1...,s_n\}) \wedge (\mathsf{sou-r}(t) \in \mathsf{ec-all}(\mathsf{sou}(t)) \vee \mathsf{sou-r}(t) = \emptyset) \wedge (\mathsf{tar-d}(t) \in \mathsf{ec-all}(\mathsf{tar}(t)) \vee \mathsf{tar-d}(t) = \emptyset)$ . The definition of ec-all is postponed to the next section. Please note that the definition of wf-tran is well founded.

Note that the definition of SC implies that, within a state chart, each substate can be uniquely referred to by its name. This is an important fact regarding configurations, which is the topic of the next section. From now on, if there is no risk of ambiguity, when denoting a state only the syntactic elements that are relevant in each case are shown. The abbreviation  $s_{1..k}$  for  $s_1, s_2, ..., s_k$  is extensively used. Finally, the substitution notation is used as follows: If t is a term, then  $t_{[a/b]}$  is the term which results from replacing all occurrences of a in t by b.

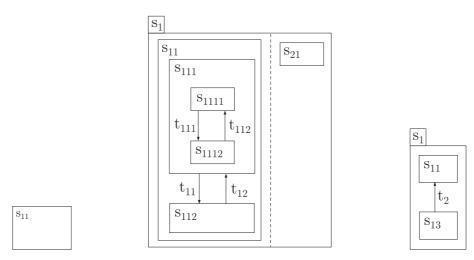

In figure 3.2 a graphical representation of each type of state is shown.

Figure 3.2: Basic-; And-; Or- statechart examples, respectively

## 3.2 Statechart Configurations

A configuration is a valid global state of a state chart. While the system is in a configuration, events can occur. In response, the system leaves the current configuration by taking a set of transitions, and enters a new configuration. At the same time, new events can be generated to which the system should respond in the same way. A configurations describes snapshots of a statechart execution.

The function conf:  $SC \to \mathcal{P}(S)$  gives the current configuration of a statechart s, i.e. the set of the names of all currently active substates within s (also including  $\hat{s}$ ):

```

\begin{array}{ll} \mathsf{conf}([\hat{s}]) & := \{\hat{s}\} \\ \mathsf{conf}([\hat{s}, (s_{1..n}), l, T]) & := \{\hat{s}\} \cup \mathsf{conf}(s_l) \\ \mathsf{conf}([\hat{s}, (s_{1..n})]) & := \{\hat{s}\} \cup \bigcup_{i=1..n} \mathsf{conf}(s_i) \end{array}

```

The function conf-all:  $SC \to \mathcal{P}(\mathcal{P}(\mathcal{S}))$  computes the set of all potential configurations of a statechart s (complete or incomplete). By potential, it is implied that not only the current active substate of an or-substate is considered, but all possibilities for choosing such a substate. Note the difference with the definition of conf. The term incomplete denotes a configuration which results from an application of conf-all where the recursion terminates before the basic states are reached. This definition is crucial to handle interlevel transitions just like normal transitions on the level of the uppermost states that the inter-level transition exits and enters.

```

\begin{array}{lll} \operatorname{conf-all}([\hat{s}]) & := \{\{\hat{s}\}\} \\ \operatorname{conf-all}([\hat{s},(s_{1..n}),T]) & := \{\{\hat{s}\} \cup c | \exists i \in \{1..n\}.c \in \operatorname{conf-all}(s_i)\} \cup \{\{\hat{s}\}\} \\ \operatorname{conf-all}([\hat{s},(s_{1..n})]) & := \{\{\hat{s}\} \cup \bigcup_{i=1..n} c_i | c_i \in \operatorname{conf-all}(s_i)\} \cup \{\{\hat{s}\}\} \end{array}

```

Incomplete configurations are realized in the second and third cases of the definition by the union with the term  $\{\{\hat{s}\}\}$ . Note that  $\forall s \in SC : conf(s) \in conf-all(s)$ .

The set of possible partial configurations is further expanded in order to include incomplete parallel configurations. An incomplete parallel configuration is such that it is possible to know the configuration of some of the parallel components of a state, but not all of them. That is,

```

\begin{array}{ll} \text{ec-all}([\hat{s}]) & := \{\{\hat{s}\}\} \\ \text{ec-all}([\hat{s},(s_{1..n}),T]) & := \{\{\hat{s}\} \cup c | \exists i \in \{1..n\}.c \in \text{ec-all}(s_i)\} \cup \{\{\hat{s}\}\} \\ \text{ec-all}([\hat{s},(s_{1..n})]) & := \{\{\hat{s}\} \cup \bigcup_{i \subseteq \{1,..,n\}} c_i | c_i \in \text{ec-all}(s_i)\} \cup \{\{\hat{s}\}\} \end{array}

```

The first two cases are analogous to conf-all. The third one allows as a valid configuration a parallel incomplete one, that is, one can "choose" a subset of  $\{s_1,..,s_k\}$ . For example, let  $s = [\hat{s}, (s_1,..s_k)]$ , where  $s_1,...,s_k \in \mathsf{SC}_B$ . Then,  $\mathsf{ec\text{-all}}(s_i) = \{\{\hat{s}_i\}\}$ ,  $\forall i = 1,..k$  and

ec-all

$$(s) \supset \{\{\hat{s}_1\}, \{\hat{s}_3, \hat{s}_2\}, \{\hat{s}_1, \hat{s}_4, \hat{s}_k\}\}\$$

The need of this relaxation will become clear later, in section 6.1. Note that, by definition,  $\forall s \in SC : conf-all(s) \subseteq ec-all(s)$ .

## 3.3 Computing the Next State

If a UML state chart transition is executed, particularly its history type and possibly its target determinator have to be considered. Therefore, the function  $\operatorname{next}$  is defined, which computes the next state after a UML state chart transition t is executed. Later, this function is used in the SO semantics rule which handles transition execution in an OR state chart.

Given a UML statechart transition t, with target s, history type  $ht=\mathsf{historyType}(t)$  and target determinator  $N=\mathsf{tar-d}(t)$  the function next:  $\mathsf{HT} \times \mathcal{P}(\mathcal{S}) \times \mathsf{SC} \to \mathsf{SC}$  computes the UML statechart term  $s'=\mathsf{next}(ht,N,s)$  which results after the execution of transition

t.

$$\begin{split} & \mathsf{next}(ht, N, [\hat{s}]) & := [\hat{s}] \\ & \mathsf{next}(ht, N, [\hat{s}, (s_{1..n}), l, T]) & := \begin{cases} & [\hat{s}, (s_{1..n})_{[s_j/\mathsf{next}(ht, N, s_j)]}, j, T] \\ & \mathsf{if} \ (\exists \nu \in N, \ j \in \{1..n\}).\nu = \hat{s}_j \\ & \mathsf{next-stop}(ht, [\hat{s}, (s_{1..n}), l, T]) \ \mathsf{otherwise} \end{cases} \\ & \mathsf{next}(ht, N, [\hat{s}, (s_{1..n})]) & := [\hat{s}, (\mathsf{next}(ht, N, s_1), ..., \mathsf{next}(ht, N, s_n))] \end{split}$$

The terms s and  $s' = \mathsf{next}(ht, N, s)$  have identical static structure, only the currently active substate information may change. Here it becomes clear why the naming convention is needed: If N contains one of the state names of the substates  $s_1, ..., s_n$  then the active state is replaced by  $s_j$  and the function is recursively applied. Then, if  $N = \mathsf{tar-d}(t)$ , the target determinator information is exploited when zooming into the state hierarchy. Otherwise, i.e. if N does not contain a name  $\nu$  of one of the state names of the substates  $s_{1...k}$ , function  $\mathsf{next-stop}$  is called which uses the history type information to determine currently active substates of a state:

$$\mathsf{next\text{-}stop}(ht, [\hat{s}, (s_{1..n}), d, l, T]) := \left\{ \begin{array}{ll} [\hat{s}, (s_{1..n}), d, l, T] & \text{if } ht = \mathsf{deep} \\ [\hat{s}, (s_{1..n})_{[s_d/\mathsf{def}(s_d)]}, d, d, T] & \text{if } ht = \mathsf{none} \\ [\hat{s}, (s_{1..n})_{[s_l/\mathsf{def}(s_l)]}, d, l, T] & \text{if } ht = \mathsf{shallow} \end{array} \right.$$

Note that, if ht = none, then the active state is now the default substate, and the function def is used to initialize the substate  $s_d$ .

The function next-stop uses the function def:  $SC \to SC$  which defines for an  $s \in SC_O$  that its currently active substate is given by its default substate:

$$\begin{array}{ll} \operatorname{def}([\hat{s}]) & := [\hat{s}] \\ \operatorname{def}([\hat{s}, (s_{1..n}), d, l, T]) & := [\hat{s}, (s_{1..n})_{[s_d/\operatorname{def}(s_d)]}, d, d, T] \\ \operatorname{def}([\hat{s}, (s_{1..n})]) & := [\hat{s}, (\operatorname{def}(s_1), ..., \operatorname{def}(s_n))] \end{array}$$

When a UML statechart transition t is taken, a set of actions is executed. In general, if a transition from state  $s_i$  to  $s_j$  with action part  $\alpha$  is taken, then the sequence of actions  $ex::\alpha::en$  is executed, with  $ex \in \mathsf{exit}(s_i)$ ,  $en \in \mathsf{exit}(s_j)$ , where the infix operator :: appends sequences of actions.

```

\begin{array}{lll} & \text{exit}([\hat{s},(en,ex)]) & := \{ex\} \\ & \text{exit}([\hat{s},(s_{1..k}),l,T,(en,ex)]) & := \{ex' :: ex \mid ex' \in \text{exit}(s_l)\} \\ & \text{exit}([\hat{s},(s_{1..k}),(en,ex)]) & := \{ex' :: ex \mid ex' \in \text{exit}(s_l)\} \\ & \text{entry}([\hat{s},(en,ex)]) & := \{en\} \\ & \text{entry}([\hat{s},(s_{1..k}),l,T,(en,ex)]) & := \{en :: en' \mid en' \in \text{entry}(s_l)\} \\ & \text{entry}([\hat{s},(s_{1..k}),(en,ex)]) & := \{en :: m_1 :: .: :: m_k \mid \exists p : \{1..k\} \leftrightarrow \{1..k\} . \forall_i \ m_i \in \text{entry}(s_{p(i)})\} \\ & \text{where "$\leftrightarrow$" denotes a bijective function.} \end{array}

```

## 3.4 Structured Operational Semantics

Given  $s \in SC$ , its structured operational semantics (SO semantics)  $[\![s]\!]_{aux}$  is given by a Labelled Transition System  $(C, L, \longrightarrow, \mathsf{conf}(s))$  where C is a set of state label sets (configurations),  $L \subseteq \mathsf{E} \times \mathsf{A}^* \times \{0,1\}$  is the set of labels,  $\longrightarrow \subseteq C \times L \times C$  is the semantic<sup>2</sup> transition relation, and  $\mathsf{conf}(s)$  is the start configuration.

C is defined as  $C := \mathsf{conf-all}(s)$ , where L and  $\longrightarrow$  are defined by the rules in figure 3.3. We note  $c \stackrel{e}{\to} {}^f_{\alpha} c'$  for  $(c, (e, \alpha, f), c') \in \longrightarrow$ , and  $c \stackrel{e}{\to} {}^f$  for  $\not \exists c', \alpha.c \stackrel{e}{\to} {}_{\alpha} c'$ .

$<sup>^2\</sup>mathrm{We}$  use the term semantic to differentiate the semantic transition relation from the syntactic element UML transition.

$$\begin{aligned} & \mathbf{Idle} \\ & \frac{\widehat{[\hat{s}]} \overset{e}{\rightarrow}^{0}_{\langle \rangle} \widehat{[\hat{s}]}}{\widehat{[\hat{s}]}} \text{ BAS} \\ & \mathbf{Progress} \\ & \frac{\langle \hat{t}, l, S_r, e, \alpha, T_d, m, ht \rangle \in T, \quad S_r \subseteq \text{conf}(s_l), \quad s_l \overset{e}{\rightarrow}^{1}}{\widehat{[\hat{s}, (s_{1..k}), l, T]} \overset{e}{\rightarrow}^{1}_{ex::\alpha::en} \widehat{[\hat{s}, (s_{1..k})[s_m/\text{next}(ht, T_d, s_m)], m, T]}} \text{ OR-1} \\ & \text{where } ex \in \text{exit}(s_s) \text{ and } en \in \text{entry}(\text{next}(ht, T_d, s_t)) \\ & \mathbf{Propagation of progress} \\ & \frac{s_l \overset{e}{\rightarrow}^{1}_{\alpha} s'_l}{\widehat{[\hat{s}, (s_{1..k}), l, T]} \overset{e}{\rightarrow}^{1}_{\alpha} \widehat{[\hat{s}, (s_{1..k}), l, T]}} \text{ OR-2} \\ & \mathbf{Propagation of stuttering} \\ & \frac{\widehat{[\hat{s}, (s_{1..k}), l, T]} \overset{e}{\rightarrow}^{0}_{\gamma} \widehat{[\hat{s}, (s_{1..k}), l, T]}}{\widehat{[\hat{s}, (s_{1..k}), l, T]} \overset{e}{\rightarrow}^{0}_{\gamma} \widehat{[\hat{s}, (s_{1..k}), l, T]}} \text{ OR-3} \\ & \mathbf{Composition} \\ & \frac{\forall_{j \in \{1, \dots, k\}} \cdot s_j \overset{e}{\rightarrow}^{j}_{\alpha_j} s'_j}{\widehat{s}'_{\beta=1} f_j \widehat{[\hat{s}, (s'_{1..k})]}} \text{ AND } \left(\alpha \in \text{perm}(\alpha_{(i)})\right) \\ & \widehat{[\hat{s}, (s_{1..k})]} \overset{e}{\rightarrow}^{\sqrt{j}}_{\beta=1} f_j \widehat{[\hat{s}, (s'_{1..k})]}} \\ & \text{AND} \left(\alpha \in \text{perm}(\alpha_{(i)})\right) \end{aligned}$$

Figure 3.3: Rules of the SO semantics

The stuttering flag f is used to reflect the priority mechanism for statecharts transitions. It also allows the semantics to fullfill the maximality condition of UML statecharts, that is, a maximal number of non conflicting statechart transitions is taken when a semantic transition is performed. The stuttering flag f can take the values 0 or 1. If f=0, then no statechart transition is taken, only the event e is consumed. If f=1 a statechart transition is taken. The flag is needed to assure that idle steps can only occur if no non-idle step is possible. A key role is played by the stuttering step (f=0), since when no UML statechart transition can be taken, a stuttering step (loop) can be done.

Let us explain the OR rules:

**OR-1:** This rule models a semantic transition from a statechart transition. Given a statechart transition of an OR state with trigger e, then that state can perform a semantic transition with positive flag and trigger e, given that, the source restriction is a complete current configuration of the currently active substate  $s_l$   $(S_r \subseteq \mathsf{conf}(s_l))$  and  $s_l$  cannot perform a semantic transition with input e and positive flag.

OR-2: This rule propagates the progress of rule OR-1. If the current active substate can perform a semantic transition with positive flag, then the OR state may perform a semantic transition with positive flag.

**OR-3**: This rule propagates the negative flag. That is, if the current active substate can perform a semantic transition with negative flag, and if the OR state cannot perform a semantic transition with positive flag, then the OR state can perform a semantic transition to itself with positive flag.

## 3.5 Complete Semantics