ISSN 1688-2784

Universidad de la República Facultad de Ingeniería

# Energy-efficient memories for wireless sensor networks

### Tesis presentada a la Facultad de Ingeniería de la Universidad de la República por

Leonardo Steinfeld Volpe

en cumplimiento parcial de los requerimientos para la obtención del título de Doctor en Ingeniería Eléctrica.

DIRECTOR DE TESIS Dr. Luigi Carro ...... Univ. Federal do Rio Grande do Sul, Brasil

TRIBUNAL

Dr. Eduardo Grampín ..... Universidad de la República Dr. Augusto Fröhlich<sup>\*</sup> .... Univ. Federal de Santa Catarina, Brasil Dr. Diógenes da Silva Jr<sup>\*</sup> .... Univ. Federal de Minas Gerais, Brasil

\* Revisor externo

DIRECTOR ACADÉMICO Dr. Fernado Silveira ...... Universidad de la República

> Montevideo 28 de noviembre de 2013

${\it Energy-efficient\ memories\ for\ wireless\ sensor\ networks},\ {\it Leonardo\ Steinfeld\ Volpe}$

ISSN 1688-2784

Esta tesis fue preparada en  $LAT_EX$  usando la clase iietesis (v1.0). Contiene un total de 130 páginas. Compilada el Monday 16<sup>th</sup> June, 2014. http://iie.fing.edu.uy/

# Acknowledgments

This thesis would not have been possible without the support of many people around me. I apologize beforehand to those who are not explicitly mentioned here, although I hope I had expressed my gratitude.

First of all, I would like to thank my advisor, Luigi, for his support along the time during the thesis and sharing his valuable time. I also would like to specially thank Fernado whose help was fundamental during these years. I am sure that this thesis would not have been possible without his support.

I also wish to thank Patricia, who was the third fundamental cornerstone, because she encouraged me during these long hard years, and for her effort specially during my stays in Porto Alegre and during the last 6 months taking care of little Salva more than usual.

I also wish to thanks my colleagues and administrative staff at IIE.

The work in this thesis is in part supported by ANII, CSIC, and CAPES.

Last but not least, I would like o thank the reviewers and members of the jury who kindly accepted to review my work.

This page is intentionally left blank.

A Salvador y Patricia, mis verdaderos amores.

This page is intentionally left blank.

# Resumen

Las redes de sensores inalámbricas (RSI o WSN, por sus siglas en inglés) agregan computación y sensado al mundo físico, posibilitando un rango de aplicaciones sin precedentes en muchos campos de la vida cotidiana, como por ejemplo monitoreo ambiental, manejo de ganado, cuidado de personas adultas mayores y medicina. solo por mencionar algunas. Una RSI consta de nodos sensores, los cuales representan un nuevo tipo de computadora embebida en red, caracterizada por tener grandes restricciones de recursos. El diseño de un nodo sensor presenta muchos desafíos, ya que es necesario que sean, pequeños, confiables, de bajo costo y con muy bajo consumo de energía, ya que se alimentan de pilas o recolectan energía del medio. En un nodo sensor, la potencia instantánea del transceptor (radio) es usualmente algunos órdenes de magnitud mayor que la potencia de procesamiento. Sin embargo, la energía de comunicación es solamente dos veces mayor que la energía de procesamiento. Por otro lado, el escalado de la tecnología CMOS permite mayor *performance* a menores precios, posibilitando aplicaciones distribuidas más refinadas con más procesamiento local. El aumento de la complejidad de las aplicaciones requiere memorias de mayor tamaño, que a su vez aumenta el consumo de potencia. Este escenario empeora ya que las corrientes de fuga son cada vez más importantes en transistores de menor tamaño.

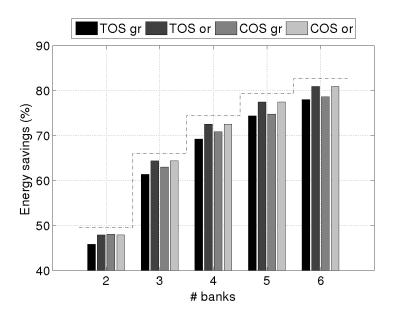

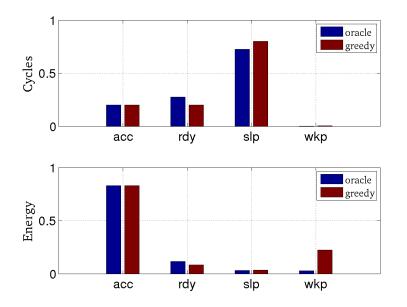

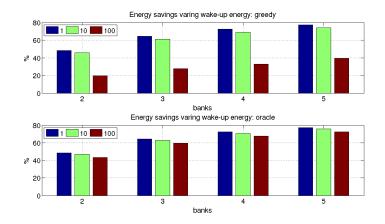

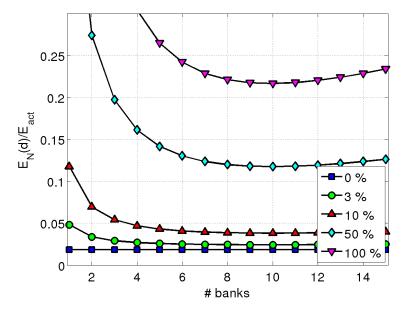

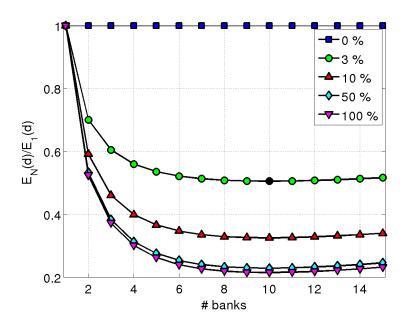

En el presente trabajo de tesis se caracteriza el consumo de energía de un nodo sensor, y se investigan diferentes arquitecturas de memoria para ser integrado en las RSI futuras, mostrando como las memorias SRAM con un estado de *sleep* pueden ser convenientes en sistemas que operan con bajos ciclos de trabajo. Si además la memoria se divide en bancos que pueden ser controlados de manera independiente, se pueden poner los bancos inactivos en estado *sleep*, incluso cuando el sistema está activo. Aunque esta es una técnica conocida, los límites de ahorro de energía no habían sido exhaustivamente determinados, ni tampoco la influencia de la política de gestión de energía usado. Se propone un nuevo modelo detallado del ahorro de energía para bancos uniformes con dos políticas de gestión: best-oracle y greedy. Nuestro modelo proporciona información valiosa de los factores fundamentales (provenientes del sistema y la carga de trabajo) que son escenciales para alcanzar el máximo ahorro alcanzable. Gracias a nuestro modelado, en tiempo de diseño se puede estimar el número óptimo de bancos para lograr grandes ahorros de energía. El problema de asignación del código a los bancos fue resuelto usando programación lineal entera. En el contexto de esta tesis, se realizaron experimentos usando dos aplicaciones reales de redes de sensores inalámbricas (basadas en TinyOS y ContikiOS). Los resultados mostraron una reducción de energía cercano a 80%

para un *overhead* de partición de 1% con una memoria de diez bancos para una aplicación con gran carga. El ahorro depende del patrón de acceso a memoria y los parámetros de la memoria (tales como cantidad de bancos, *overhead* de partición, reducción de energía del estado *sleep* y el costo energético de *wake-up*. El ahorro de energía decrece para ciclos de trabajo bajos. Sin embargo, igualmente se alcanzan ahorros de energía significativos, por ejemplo, aproximadamente 50% para ciclos de trabajo de 3% usando la memoria anterior. Finalmente, nuestros resultados sugieren que debe ser cuidadosamente evaluado el uso de políticas de gestión de energía avanzados, ya que la política *best-oracle* es solo marginalmente mejor que la política *greedy*.

# Abstract

Wireless sensor networks (WSNs) embed computation and sensing in the physical world, enabling an unprecedented spectrum of applications in several fields of daily life, such as environmental monitoring, cattle management, elderly care, and medicine to name a few. A WSN comprises sensor nodes, which represents a new class of networked embedded computer characterized by severe resource constraints. The design of a sensor node presents many challenges, as they are expected to be small, reliable, low cost, and low power, since they are powered from batteries or harvest energy from the surrounding environment. In a sensor node, the instantaneous power of the transceiver is usually several orders of magnitude higher than processing power. Nevertheless, if average power is considered in actual applications, the communication energy is only about two times higher than the processing energy. The scaling of CMOS technology provides higher performance at lower prices, enabling more refined distributed applications with augmented local processing. The increased complexity of applications demands for enlarged memory size, which in turn increases the power drain. This scenario becomes even worse as leakage power is becoming more and more important in small feature transistor sizes.

In this work the energy consumption of a sensor node is characterized, and different memory architectures were investigated to be integrated in future wireless sensor networks, showing that SRAM memories with sleep state may benefit from low duty-cycle operating system. SRAM memory with power-manageable banks puts idle banks in sleep state to further reduce the leakage power, even when the system is active. Although it is a well known technique, the energy savings limits were not exhaustively stated, nor the influence of the power management strategy adopted. We proposed a novel and detailed model of the energy saving for uniform banks with two power management schemes: a best-oracle policy and a simple greedy policy. Our model gives valuable insight into key factors (coming from the system and the workload) that are critical for reaching the maximum achievable energy saving. Thanks to our modeling, at design time a near optimum number of banks can be estimated to reach more aggressive energy savings. The memory content allocation problem was solved by an integer linear program formulation. In the framework of this thesis, experiments were carried out for two real wireless sensor network application (based on TinyOS and ContikiOS). Results showed energy reduction close to 80% for a partition overhead of 1% with a memory of ten banks for an application under high workload. Energy saving depends on the

access patterns to memory and memory parameters (such as number of banks, partitioning overhead, energy reduction of the sleep state and the wake-up energy cost). The energy saving drops for low duty-cycles. However, a very significant reduction of energy can be achieved, for example, roughly 50% for a 3% duty-cycle operation using the above memory.

Finally, our findings suggest that adopting an advanced power management must be carefully evaluated, since the best-oracle is only marginally better than a greedy policy.

# Contents

| A        | ckno            | wledgr | nents                                             | i            |

|----------|-----------------|--------|---------------------------------------------------|--------------|

| A        | ckno            | wledgr | nents                                             | ii           |

| R        | $\mathbf{esum}$ | ien    |                                                   | $\mathbf{v}$ |

| A        | bstra           | ict    |                                                   | vii          |

| 1        | Intr            | oduct  | ion                                               | 1            |

|          | 1.1             | Motiv  | ation                                             | 1            |

|          | 1.2             | Goals  | and contributions                                 | 4            |

|          | 1.3             | Thesis | organization                                      | 5            |

| <b>2</b> | Sen             | sor no | de platform                                       | 7            |

|          | 2.1             | Sensor | r node hardware                                   | 8            |

|          |                 | 2.1.1  | Evolution and future trends of hardware platforms | 8            |

|          |                 | 2.1.2  | Ultra low-power processors                        | 10           |

|          | 2.2             | Sensor | r node software                                   | 13           |

|          |                 | 2.2.1  | TinyOS                                            | 13           |

|          |                 | 2.2.2  | ContikiOS                                         | 14           |

|          |                 | 2.2.3  | Higher level abstractions: Java virtual machines  | 14           |

|          | 2.3             | Low-p  | ower techniques and methodologies                 | 16           |

|          |                 | 2.3.1  | Fundamentals of low-power design                  | 16           |

|          |                 | 2.3.2  | Dynamic power management                          | 17           |

|          | 2.4             | Chara  | cterization of sensor platforms                   | 19           |

|          |                 | 2.4.1  | Power model                                       | 19           |

|          |                 | 2.4.2  | Energy breakdown                                  | 22           |

|          | 2.5             | Summ   | ary and conclusions                               | 28           |

| 3        | Me              | mories | for sensor nodes                                  | <b>31</b>    |

|          | 3.1             | Memo   | ry fundamentals                                   | 31           |

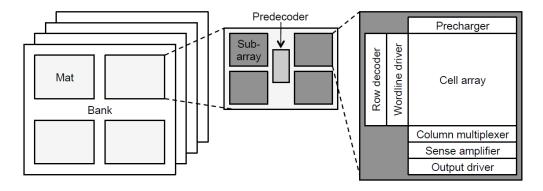

|          |                 | 3.1.1  | Memory internal architecture                      | 33           |

|          |                 | 3.1.2  | Memories for embedded systems and sensor nodes    | 34           |

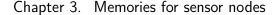

|          |                 | 3.1.3  | Memory organizations                              | 35           |

|          | 3.2             | Flash  | and SRAM memories                                 | 37           |

|          |                 | 3.2.1  | Flash memory                                      | 37           |

## Contents

|          |          | 0                                                               | 41         |

|----------|----------|-----------------------------------------------------------------|------------|

|          |          |                                                                 | 43         |

|          | 3.3      | ±                                                               | 45         |

|          | 3.4      | 1 0                                                             | 48         |

|          |          |                                                                 | 48         |

|          | 3.5      | Summary and conclusions                                         | 55         |

| 4        | Ban      | 0                                                               | 57         |

|          | 4.1      | 1 87                                                            | 58         |

|          |          |                                                                 | 59         |

|          | 4.2      |                                                                 | 60         |

|          | 4.3      |                                                                 | 61         |

|          |          |                                                                 | 62         |

|          |          |                                                                 | 62         |

|          |          |                                                                 | 63         |

|          | 4.4      |                                                                 | 65         |

|          | 4.5      | Summary and conclusions                                         | 67         |

| <b>5</b> | Exp      | erimentation and results                                        | 71         |

|          | 5.1      | Evaluation methodology                                          | 71         |

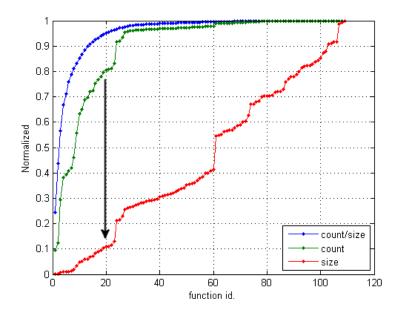

|          |          | 5.1.1 Benchmarks and applications                               | 72         |

|          |          | 5.1.2 Optimization problem: memory contents allocation to banks | 73         |

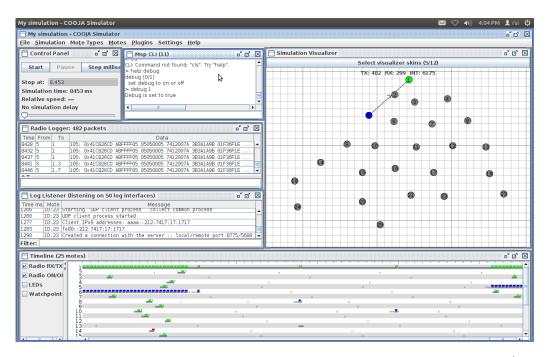

|          |          | 5.1.3 Simulation and evaluation tools                           | 75         |

|          | 5.2      | Results and Discussion                                          | 75         |

|          |          | 5.2.1 Power management policy                                   | 75         |

|          |          | 5.2.2 Partition overhead effect on energy savings               | 78         |

|          |          | 5.2.3 Duty-cycle operation                                      | 78         |

|          | 5.3      | Summary and conclusions                                         | 80         |

| 6        | Con      | clusions                                                        | 83         |

|          | 6.1      | Summary of the thesis                                           | 83         |

|          | 6.2      | Main contributions                                              | 85         |

|          | 6.3      | Future works                                                    | 86         |

| Α        | Mer      | nory simulations                                                | 89         |

|          |          | •                                                               | 89         |

|          | A.2      | NVSim estimations                                               | 90         |

| в        | Eva      | luation tools                                                   | 93         |

| _        | B.1      |                                                                 | 93         |

|          | B.2      | 0 10                                                            | $95 \\ 95$ |

|          | <b>.</b> |                                                                 | 95         |

| Re       | efere    | ncias                                                           | 99         |

|          |          |                                                                 |            |

| In       | dice     | de tablas 11                                                    | 10         |

Contents

Índice de figuras

112

This page is intentionally left blank.

# Chapter 1

# Introduction

This chapter introduces the context of the work presented in this thesis. The first section presents a description of the wireless sensor networks and the motivation of this work, to finally highlight some open challenges that need to be addressed to enable an ubiquitous adoption of these networks. The next section discusses the specific goals of our work and continues enumerating the main contributions of the present thesis. Finally, we conclude the chapter providing a road-map for the rest of this document.

## 1.1 Motivation

Wireless sensor networks (WSNs) embed computation and sensing in the physical world, enabling an unprecedented spectrum of applications in several fields of daily life. A WSN comprises sensor nodes, which sense the environment, process the acquired data and communicate the information to other sensor nodes. In traditional sense-and-send applications the sensor nodes route the raw data to a sink node to make it available to users, while in distributed computing applications the data is processed in the network by neighbor nodes, exchanging messages to directly output meaningful information or take actions. The sensor node represents a new class of networked embedded computer that is characterized by severe resource constraints: computation power, available memory for program and data storage, and especially energy.

Since the nodes are usually placed in inaccessible locations and in large number, they are powered from batteries or harvest energy from the environment [38]. In both cases low-power operation is mandatory, in the former case to avoid frequent batteries or nodes replacement, and in latter case to suit the scarce available energy or to minimize the harvesting system cost and size (e.g. solar panel). A canonical sensor node consists of the following blocks: a processing component (usually a microcontroller) with wireless communication capabilities (RF transceiver), sensors/actuators and a power supply subsystem [95]. The communication and computation subsystems are the main sources of energy dissipation in a WSN node. The RF transceiver is usually the most power-consuming component of a sensor

#### Chapter 1. Introduction

node, and since the WSN emergence the communication energy cost has dominated the overall budget. Consequently, a significant research effort has been made since then for reducing this communication energy cost [19] [5]. The Medium Access Control (MAC) layer design is crucial, since it directly controls the transceiver determining the power profile drain. The use of advanced MAC protocols has helped in improving the energy efficiency for communication [20], becoming comparable to the processing energy [51].

Nevertheless, in more recent intensive processing applications the energy spent in computing could be much larger than the energy spent in communication. Nowadays, it is generally accepted that efforts toward energy reduction should target communication and processing [87]. At the same time, reducing the computational energy enables further optimizations concerning communication, since usually actual techniques are restricted by the low computational capabilities and low memory footprints.

Despite computation energy concerns, expectations for higher performance and lower prices continue to increase with each new CMOS technology generation. In this regard, as technology scales, novel applications can be devised, where previously their cost in terms of price were unacceptable, since the capacity of sensor nodes integrated processors has increased. More refined applications performing distributing computing, also known as collaborative information processing, will become key elements of larger pervasive infrastructures such as Internet of Things (IoT) [109] or Cyber-Physical Systems (CPS) [80]. However, this increasing complexity of applications using wireless sensor networks soon becomes a barrier to the adoption of these networks. The currently available wireless sensor network programming models do not scale well from simple data collection models to collaborative information processing ones. On a different scenario, complex distributed applications have been developed for powerful platforms (such laptops, smartphones, etc.), but they are not appropriate, since they require intensive computation that current WSN platforms can not afford. If they were equipped with a more powerful microcontroller, they would result in a too power-hungry platform, sacrificing energy [29]. New programming models are essential to develop complex distributed applications, and at the same time obtain a decent level of energy-efficiency.

Novel virtual-machines (VMs) and middlewares that are designed with WSN in mind are efforts in the direction of complex networks. There are several benefits in using virtual machines in WSN [72]. First, VMs allow applications to be developed uniformly across WSN platforms. Platform-independent applications can be written using VM abstractions whose implementations are scaled to meet different resource constraints. VMs provide a clean separation of system software and application software, which reduces the cost of reprogramming after deployment. Finally, VMs mask the variations among the WSN platforms through a common execution framework [68]. Middlewares even go further, adding a higher-level of abstraction to allow a smaller programming effort of distributed systems, such as the WSNs, and to achieve interoperability [80]. Middleware is usually defined as the software that lies between the operating system and applications running on each node of the system providing support for the development, maintenance, deployment and execution of WSN application [24]. A middleware provides standard interfaces, abstractions and a set of services to hide the working internals that simplify the application development, while hiding the heterogeneity of the system, which then enables interoperability. Nevertheless, higher abstractions add new levels of indirection increasing the execution overhead, which in turns increases the energy consumption. Summarizing, one of the actual major issues of WSN research is providing high-level application programming abstractions and reducing the processing energy consumption to leverage creative and more complex applications of the future.

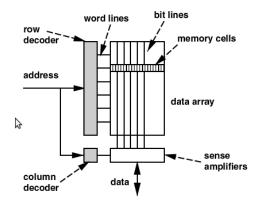

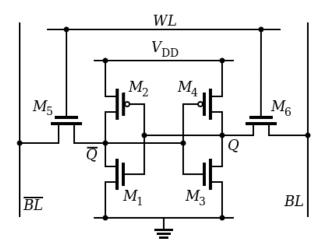

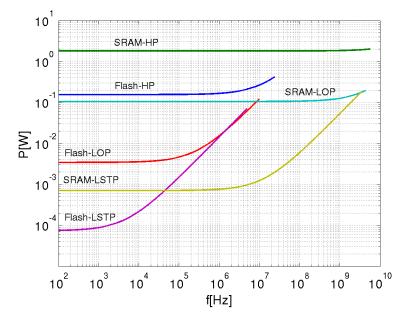

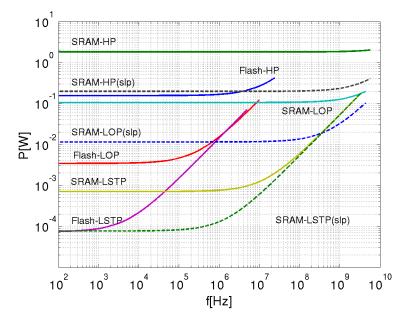

Regarding processing, a programmable processor, in contrast to hardwired logic, allows a single hardware resource to implement different applications by running different software stored in memory. The cost of this unquestionable flexibility is that a processor spends significant more energy on instruction and data supply than performing arithmetic [28]. Microcontrollers embed, in addition to a processor, programmable I/O peripherals (such as timers/counters, serial ports, and so on) and memory. They usually have two kinds of memory: a readwrite memory (e.g. SRAM) and non-volatile memory (e.g. Flash). The former memory is needed for storing temporal data (variables), and the later for storing the program and constants, retaining the content even though it is not powered. The code can be executed directly from non-volatile memory, known as execute in place (XIP) or first copied from Flash to RAM (shadow memory) [61]. As executing code from SRAM consumes considerable less energy than executing from Flash (this matter is addressed later in Chapter 3), to provide enough SRAM space for placing the code should be considered in WSN applications in order to reduce the node energy consumption. Since SRAM occupies more area per bit than Flash memory, there is a trade-off between area cost and energy reduction. The best option for the memory architecture should be carefully considered, choosing from full shadow the code from Flash into SRAM to schemes borrowing ideas from scratch-pad or even cache memories themselves [9].

Moreover, the aforementioned increased complexity of applications (reflected in software complexity) demands for increasing memory size. In some applications the code size is doubling every ten months [108]. WSN applications follows this general trend, but at a lower rate hampered by hardware limitations, as can be observed in the evolution of applications memory footprints (as we shall see in the next chapter). Larger memory size requires more power, as it has been found that the memory system is responsible for a large portion of the total energy budget in SoCs [25]. A downside of the scaling of CMOS technology is the increase of leakage current to the point that it may represent up to 50% of the total power consumption of a circuit [59, 63].

This problem is getting worst as more transistors are put in large circuits as memory arrays. Therefore, the reduction of leakage power in the memory system is definitely a primary target in future embedded systems, particularly in deeply pervasive systems such as WSN.

Partitioning a SRAM memory into multiple banks that can be independently

#### Chapter 1. Introduction

accessed reduces the dynamic power consumption, and since only one bank is active per access, the remaining idle banks can be put into a low-leakage sleep state to also reduce the static power [41]. However, the power and area overhead due to the extra wiring and duplication of address and control logic prevents an arbitrary fine partitioning into a large number of small banks. Therefore, the final number of banks should be carefully chosen at design time, taking into account this partitioning overhead. The memory organization may be limited to equallysized banks, or it can allow any bank size [73]. Moreover, the strategy for the bank states management may range from a greedy policy (as soon as a bank memory is not being accessed it is put into low leakage state) to the use of more sophisticated prediction algorithms [18].

# 1.2 Goals and contributions

Some of the most important challenges that need to be addressed for future wireless sensor networks are:

- high level programming abstractions for the ease of development and to enable more complex applications;

- energy-efficient platforms compatible with application lifetime requirements

Considering the challenges above and all motivations discussed before, the main goal of this thesis is memory energy reduction aiming to extending WSN node lifetime, and at the same time enabling higher level of programming abstraction for application development and consequently contribute to a widespread adoption of WSN technology.

This thesis makes three main contributions: Firstly, it contributes with a characterization and analysis of the run-time execution of typical current application developed based on the most popular WSN operating systems (TinyOS and ContikiOS). We show that memory energy consumption may hamper the spreading of WSN application that involves complex processing.

A second contribution of this work is, after a review of available memories for using in WSN processors to hold program code, the benefits of using a SRAM memory with a low-leakage sleep state are stated.

A third and the most important contribution of this work is the proposal of using banked memories with power management to cope with the increasing leakage current, result from the scaling of CMOS technology. This could help to manage the increasing complexity of applications and, at the same time, to extend the life-time of the WSN nodes. Analytical expressions for the energy savings are derived from a memory model to determine the impact of design decision as power management strategy, memory architecture and technology parameters, and the application run-time behavior.

#### 1.3. Thesis Organization

# 1.3 Thesis Organization

This thesis is divided into seven chapters, whose contents are summarized in the following paragraphs:

- Chapter 1 has described the wireless sensor networks and the motivation for this thesis, enumerating the main challenges and briefly describing the contribution of this work.

- Chapter 2 reviews actual platforms (software and hardware), and low-power techniques and methodologies, particularly those which are applied for reducing the energy consumption in sensor nodes. Next, the energy consumption is characterized, showing its dependence on the hardware platform power parameters and software architecture.

- Chapter 3 describes current memories available for embedded system, reviews its main characteristics highlighting which are suitable for WSN embedded processors with special emphasis on energy efficiency. The energy consumption of Flash and SRAM are compared, focusing on the pros and cons of each memory technology. The SRAM memory with sleep state is introduced, and potential energy savings delimited. Finally, a memory with power-manageable banks is modeled and the main characteristics described.

- Chapter 4 investigates in depth the memory architecture introduced last in the previous chapter. Expressions for the energy savings are derived, gaining valuable insight into key factors that are fundamental for achieving huge savings. Two power management policies are modeled and discussed.

- Chapter 5 presents experiments carried out to asses energy savings. The energy savings limits predicted by our model are compared to savings results obtained by simulation for different configurations.

- Chapter 6 summarizes the work developed in the framework of this thesis, highlights the main contributions and discusses future works.

This page is intentionally left blank.

# Chapter 2

# Sensor node platform

A key element of wireless sensor networks is the sensor node. A basic sensor node is composed of the following building blocks: a processing element with a radio (RF transceiver), sensors/actuators and a power supply subsystem. Node power consumption results from the sum of the power contributions of its electronic components, which in turn depend on the component state and the actual operation performed. The power profile drain, i.e. the instantaneous power as a function of the time, determines the effective node energy consumption. The hardware together with software and external factors, as the environment and the interaction with the network, dictates the power profile drain of each node. The hardware defines the power level consumption. The network design and the communication protocols influence the behavior of the nodes. The message exchange within or between the nodes determine the state and actions of the node, particularly the radio operation mode, i.e. receive, transmit or sleep mode, and the microcontroller opeartion mode. Finally, the software implements the final application, usually on top of an operating system or a higher lever abstraction. The operating system provides services to ease application development, including a communication stack that implements network protocols. Also, provides abstractions across platforms to hide hardware resources differences and thus improve portability.

This chapter introduces the main design challenges of sensor node platforms. The first section briefly presents the evolution of hardware sensor nodes and future trends. It also surveys some efforts on designing ultra low-power processors, some targeting wireless sensor networks. The second section discuss the software sensor node, describing in detail the most widespread software platforms, TinyOS and ContikiOS, and emerging Java virtual machines. The third section introduces the fundamentals of low-power techniques and the main concepts for dynamic power management. The next section presents an energy characterization of a popular sensor node, showing that increasing the complexity of applications must be accompanied with a reduction of processing power. Finally, the conclusion summarizes the chapter, including a brief discussion of the main aspects.

#### Chapter 2. Sensor node platform

### 2.1 Sensor node hardware

#### 2.1.1 Evolution and future trends of hardware platforms

The wireless sensor networks was envisaged in the early nineties as a pervasive technology where sensor nodes are as small as fine particles of dust. This idea was materialized in the Smart Dust project by Kristofer S. J. Pister et al. at University of California, Berkeley, aiming at integrating a complete sensing/communication platform inside a cubic millimeter [62]. Later, in collaboration with other researches, including David Culler and his group from Berkeley too, they developed also hardware and software platforms following the open-source model. These hardware platforms, in the order of a few cubic centimeters, were built using commercial off-the-shelf (COTS) chips, named macro motes or simply motes. These sensor nodes together with its sequels (available as commercial products too), commonly named as Berkeley motes, are still one of the most popular in the academia, as the *mica* [27] and *telos* [90]. The software platform developed is composed by the operating system TinyOS [55] and the nesC language [44] (nesC, for network embedded systems C).

Most hardware platforms that are built using COTS components use microcontrollers of one of the two families: AVR from Atmel Corporation (8-bit processor, e.g. Atmega128) and MSP430 from Texas Instruments (16-bit processor, e.g. MSP430F1611). The selected radio varies according to the frequency range usually in one of the ISM bands<sup>1</sup>, and if they are compliant or not with the IEEE 802.15.4 LR-WPANs standard (low-rate wireless personal area networks). They have evolved from byte-oriented to packet-oriented radio, incorporating in silicon new functionalities defined in the standard, such as data encryption or automatic preamble generator.

Some years later after the release of the first sensor nodes, more powerful platforms were developed, featuring ARM cores running at hundreds of MHz, for example Sun SPOT by SUN (now Oracle). However, their high power requirements drain the batteries in days or even hours, therefore limiting its use to a narrow set of applications. More recently, some sensor nodes were equipped with newer low power 32-bit microcontrollers, offering increased computation power with a power consumption of about one order of magnitude higher than the Berkeley motes [66].

Table 2.1 compares some of the most representatives motes from the beginning of the WSN to the present: *telos*, *micaz*, *AVR-Raven*, *Wismote*, *LOTUS* and *econotag*. The table shows the microcontroller and radio chips used in each sensor node (for an extensive list of surveyed platforms, please see [50]). For the sake of clarity are only considered the main characteristics of the chips, and the current consumption of the most important operation modes.

As can be seen from the table, there is a clear trend toward increasing the processing power, adopting 32-bits processors running at higher frequencies. The

<sup>&</sup>lt;sup>1</sup>There are other alternatives for the transmission medium different from the electromagnetic waves (radio frequency), such as optical or water (in underwater sensor networks).

|                    | $\operatorname{unit}$ | telos       | micaz          | AVRaven        | wismote     | LOTUS         | econotag         |

|--------------------|-----------------------|-------------|----------------|----------------|-------------|---------------|------------------|

| Microcontroller    |                       | MSP430F1611 | Atmega128L     |                | MSP430F5438 | LPC1758 (NXP) | MC13224V         |

| Core               |                       | MSP430      | AVR            |                | 4           | ARM Cortex-M3 | <b>TDMI ARM7</b> |

|                    |                       | 16 -bits    | $8	ext{-bits}$ | $8	ext{-bits}$ |             | 32-bit        | 32-bit           |

| Speed $(f_{max})$  | $\mathrm{MHz}$        | ×           | ×              |                |             | 100           | 24               |

| Prog. mem.         | KB                    | 48          | 128            |                |             | 512           | 128              |

| Data mem.          | KB                    | 10          | 4              |                |             | 64            | 96               |

| Active current     | $\mathbf{mA}$         | 4           |                | 5              | 8.9         | 50            | 3.3              |

| Sleep current      | $\mu A$               | 2           | . –            | 15             | 2.1         | 10            | 5.1              |

| Transceiver        |                       | CC2420      | 420            | AT86RF230      | CC2520      | AT86RF231     | 1 Integrated PiP |

| Rx current         | $\mathrm{mA}$         | 19.         | 7              | 16             | 18.5        | 13.2          | 22               |

| Tx current         | $\mathrm{mA}$         | 17.4        | 4              | 17             | 25.8        | 14.4          | 29               |

| Link budget        | $\mathrm{dBm}$        | 94          |                | 104            | 103         | 104           | 100              |

| Sleep current      | $\mu \mathrm{A}$      | 426         | 9              | 1500           | 1600        | 400           | I                |

| Deep sleep current | $\mu A$               | 20          |                | 0.02           | 175         | 0.02          | 5.1              |

| comparison. |

|-------------|

| nodes (     |

| Sensor      |

| Fable 2.1:  |

2.1. Sensor node hardware

#### Chapter 2. Sensor node platform

transceiver consumption power consumption remains at the same level but providing an increase of output power (about 3 dBm in average).

In order to have a complete and accurate picture of the overall power consumption of the different sensor motes, it would be necessary to precise the application characteristics and workload, e.g., how much processing and communication is needed and how long the radio and microcontroller remains in a sleep state. Unfortunately there is no neutral benchmarks available yet, to even compare ultra low-power processors<sup>2</sup>. From the data in Table 2.1, it is apparent that the amount of memory is increasing, and that the program memory increases at a higher rate than data memory. This fact could be interpreted as increasing demand for memory by applications.

Because of space limitations, we have not included a significant number of sensor nodes and modules built using COTS components (commercial or academic) but the tendency is confirmed: increasing processing power with lower rate of power consumption rise, as presented by Ko et al. [66].

#### 2.1.2 Ultra low-power processors

In the last years, there has been a large amount of research dealing with platform power optimization for WSN. Most proposals follow an application-driven approach to design and implement a custom system architecture (see [88] for a brief review and comparison of different approaches). These architectures are more power efficient than general purpose commodity microcontrollers.

Raval et al. [97] conducted a workload analysis for a WSN application scenario running TinyOS-based application software on a platform equipped with a ATmega128L microcontroller (the same microcontroller present in a mica sensor node). The application included a simple filter processing, where the output data was sent to a sink node. They therefore proposed a processor platform tuned for running a suite of applications developed using TinyOS. The tuned platform included an application-specific programmable processor core and a hardware accelerator for offloading a small, but frequently used, set of instructions. The platform maintained near binary compatibility with the conventional microcontroller, consuming 48% less energy than the baseline processor when executing the same WSN application suite.

Hempestead et. al. [51] embraced also the accelerator-based computing paradigm, including acceleration for the network layer (routing) and the application layer (data filtering), but focusing on reducing the leakage current during long idle times. The proposed architecture disable the accelerators via  $V_{DD}$ -gating. According to their results the proposed architecture achieved between one to two orders of magnitude reduction in power dissipation over commonly used microcontroller, depending on the workload. More specifically, 100 times less power when idle, and from 10-600 times less energy when active.

<sup>&</sup>lt;sup>2</sup>At the time of writing of the present work, the Embedded Microprocessor Benchmark Consortium (EEMBC) is working on ULPBench <sup>TM</sup>Benchmark Software, with the participation of dozens of top companies that design and manufacture microcontrollers.

#### 2.1. Sensor node hardware

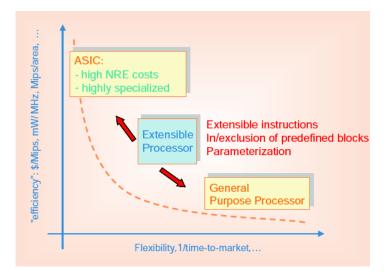

Figure 2.1: Custom hard-wired logic, extensible processor and general purpose processor [52].

Pasha et al. [88] architecture followed a hardware specialization with power gating approach, but incorporated the concept of distributed hardware microtasks in control-oriented applications. They proposed a complete system-level flow, in which a node was built out of microtasks that are activated on an event-driven basis. An application-specific architecture is synthesized for each microtask, optimized by hand. They combined this specialized architecture with power gating to reduce both dynamic and static power. As in the Hempestead work, the focus was on the bulk workload such as device drivers, medium access control (MAC) protocols and routing, since the nodes normally don't have a compute-intensive operating system kernel (as shall be detailed in Section 2.2).

Kwong et al. [69] adopted the aboves techniques, and additionally applied supply voltage scaling to below the device threshold in logic and SRAM circuits. They proposed a technique to mitigate the effects of process variation, increasingly important at low voltages in deeply scaled technologies. A 16-bit microcontroller core was designed to operate at sub-threshold voltage down to 300 mV. Energyconstrained systems that can afford some performance degradation may benefit from the subthreshold processor design.

The confrontation between general purpose microcontrollers and applicationspecific programmable processors can not be addressed without the economic point of view. Although we do not deal with this issue that arises when considering the scale dimension, it should be taken into account to get a low power sensor node, and, at the same time, with lower cost for a wide-spread adoption of WSNs. It is also worth mentioning that as the more flexible a processor, the more likely to be massively chosen. Fig. 2.1 reproduce the diagram presented by Henkel et al. [52] showing the trade-off of custom hard-wired logic, extensible processor (application specific processor) and general purpose processor. The aforementioned works focus on reducing the energy spent in processing, in general. Thus, it can be enlightening seeing where the energy goes in a processor.

#### Chapter 2. Sensor node platform

| RISC Processor              |                             |

|-----------------------------|-----------------------------|

| Technology                  | TSMCCL013G ( $V_{DD}$ 1.2V) |

| Clock Frequency             | $200 \mathrm{~MHz}$         |

| Average Power               | 72  mW                      |

| Instruction supply          | 70 pJ 42 %                  |

| Data supply                 | 47 pJ 28 %                  |

| Arithmetic (add & multiply) | 10  pJ $6 %$                |

| Clock and control logic     | 40 pJ 24 %                  |

|                             |                             |

Table 2.2: Processor configuration and energy consumption per operation (based on [6]).

Dally et al. [28] proposed an efficient programmable architecture for computeintensive embedded applications, and for comparison purposes a detailed energy breakdown of a conventional RISC (SPARC V8) processor was provided. The results are reproduced partially in Table 2.2 (see [28] and [6] for details). The table shows the relative energy for instruction supply, data supply, arithmetic, and clock and control logic, representing 42%, 28%, 6% and 24% of the total energy consumption respectively. The presented data is quite revealing since it shows that the processor spends most of its energy on instruction and data supply, 70%. This result indicates that some research effort should focus on reducing the energy consumption on supplying data to processors.

Moreover, Verma [110] illustrated that the relative SRAM memory consumption in processors increases as processors consumption decreases by applying advanced design techniques. The processor with the lowest power consumption, among the surveyed ones in [110], is a custom MSP430 processor with 16 KB SRAM cache, operating at 0.3 V [70], where the embedded SRAM consumes 69% of the total processor power. Hence, the energy consumption in ultra-low-power processors is greatly dominated by memory accesses.

Chapter 3 analyze in detail the memory energy consumption evolution with the technology scaling, showing that the reduction of memory energy consumption is a major goal for future and more complex WSNs.

In summary, reducing the power taken by naïve memory organizations enables more computationally demanding algorithms to be implemented with the extra power resources, expanding the range of WSN applications. Moreover, the communication protocols are actually restricted by the low computational capabilities and low memory footprints of current low-power processors, hence reducing the computational energy will enable to adopt more complex communications protocols leading to further optimizations to reduce the communication energy [51].

## 2.2 Sensor node software

A sensor node is basically a reactive system that responds to external stimulus: a successful reception of a packet, a communication timeout, a time trigger to initiate some measurement, data ready interruption that may trigger further processing, and so on. Sensor network applications are intrinsically event-driven, so that the software designer or programmer typically adopts event-based software architectures or operating systems, like TinyOS [71] and ContikiOS [36]. Both are perhaps the most popular embedded operating systems for wireless sensor networks in the academia and the industry. There are other interesting alternatives developed by the research community, but they do not have such a large amount of people involved (user and developers), nor any other clear advantages. To mention a few of them: Mantis OS [15] and SOS [49], which are no longer under active development; LiteOS [21] provides Unix-like abstractions but apparently it is not fully operational; and RETOS [23], which includes interesting features like variable system timer, but the source code is not provided. For a review of operating systems and network protocols please refer to [38]. Additionally, there are other operating systems from outside the academia, some commercially offered, e.g., FreeRTOS (open source but do not include network support) and  $\mu C/OS$ (open source with many licensing options). Some microcontroller, radio and SoC manufacturing companies provide operating systems (e.g., TI-RTOS from Texas Instrument and MQX<sup>TM</sup> from Freescale) and stacks (e.g. simpliciTI and Z-Stack from Texas Instruments, BitCloud from Atmel).

The remainder of this section briefly present TinyOS and ContikiOS. Also, some Java virtual machines specially designed for sensor nodes are reviewed.

### 2.2.1 TinyOS

TinyOS<sup>3</sup> based applications are developed using nesC [44], the companion programming language which is an extension of the C programming language. TinyOS embraces the component-based paradigm where different functions are encapsulated within components which are connected each other using interfaces [71]. TinyOS provides components and interfaces for the very common needs, from lowlevel abstractions such as timing management and I/O interface, to higher levels such as communication protocol stacks (including medium access control and routing). The architecture relies on non-blocking functions that run to completion, and consequently a single stack is used avoiding high-cost context-switches.

Some of these software components abstract hardware components. TinyOS extends to all components the split-phase needed to avoid busy-wait in hardware transactions. For this purpose *commands* and *events* are used, which are essentially functions. Normally an operation is initiated through a *command* call. When a transaction lasts too long, the operation is completed later by a *event* callback. Operations initiated from a hardware interrupt (interrupt service routine, ISR), labeled as asynchronous, must be kept short to not delay other ISRs. Larger

<sup>&</sup>lt;sup>3</sup>www.tinyos.net

#### Chapter 2. Sensor node platform

computations must be deferred through a function post, *task*, to be scheduled later outside of the ISR context. The tasks are serviced by a simple tasker in a first-input first-output basis. As the tasks run to completion, long tasks should be split in many shorter ones to share the processor time.

TinyOS provides timing services through *timers* components based on one or several system ticks implemented using hardware timers. TinyOS also includes a library to support threads, named TOSThreads [65].

### 2.2.2 ContikiOS

ContikiOS<sup>4</sup> based applications are developed using the multithreading programming model based on protothreads [37]. The programming language is standard ANSI C. Each process has its corresponding protothread. Processes uses a special construct that have a blocking semantic for waiting for events by verifying a condition. If the condition is false the process yields the processor. The protothreads are implemented as an ordinary function that returns when it blocks (the condition is false). But before returning, the function saves the location where it got blocked, so that it can resume the execution later at that point. The protothread primitives are ingeniously defined by macros, which expands in a switch-case construction. The kernel schedules blocked processes in response to an event. The events are either internal, e.g. a message posted from other processes, or external, e.g. triggered by a hardware interrupt. For that, the kernel has a queue of pending events from which the next event to be processed is picked. Then the kernel traverse the process list calling the respective protothread to process the event.

ContikiOS has a process to offer timer services. A system tick periodically wakes up the process.

The protothread adoption by ContikiOS has some implications: the application has a single stack, since the protothreads returns when blocks; local variables values are not preserved between invocations; and since the kernel is not preemptive the processes should explicitly yield control in long computations. As a consequence ContikiOS and TinyOS share many characteristics. Despite taht they follow different paradigms, i.e. component-based model versus multithreading, at execution time they behave similarly, since both are event-driven in nature.

### 2.2.3 Higher level abstractions: Java virtual machines

There are many advantages in using higher level languages in WSNs [80]. Moreover, the adoption of Java as the wireless sensor network programing language is an interesting option, considering the worthwhile features of the language, such as productivity gain thanks to the associated object-oriented software engineering. Furthermore, Java virtual machines (JVM) provide memory protection through type safety, dynamic memory management with garbage collection, and a clean interface for developing platform-independent applications. Middlewares, if present, are easily implemented on top of a JVM.

<sup>&</sup>lt;sup>4</sup>www.contiki-os.org

Finally, the Java language is very popular among programmers and it definitely requires a much shorter learning curve than the nesC of TinyOS and even the widespread language C. As a consequence, Java is a good candidate for becoming the wireless sensor network language within the Internet of Things.

Many Java virtual machines for wireless sensor networks have been reported, which are implemented on "bare metal" microcontrollers. Squawk [99] targeted the relative rich resource SunSPOT platform. Whereas Darjeeling [16] and Taka Tuka [4] were designed to meet the resource constraints of the so-called Berkeley motes. All of them implement a split architecture, aiming to offload embedded runtime processing. The bytecodes are post processed on host, performing bytecode verification, static linking within group of classes and optimizing bytecodes to reduce code size. The achieved code reduction was up to 3-4 times w.r.t. the original Java classes [16].

These two virtual machines, in fact, are no truly implemented on "bare metal", since they rely in an underlaying operating system, either TinyOS and/or ContikiOS. Nevertheless, it is worth noting that it is simply periodically scheduled a task or process to run the interpreter. They also use the already present hardware abstraction layer (drivers to access the hardware platform) and the communication primitives. As a result, the virtual machines as software platform, currently depend on existing modules and protocol stack to build applications. In other words, the software implemented in Java constitutes still a thin layer. However, low-level hardware devices can be successfully accessed using an object-oriented abstraction, *Hardware objects* introduced by [98], and hardware interrupts by [67].

The potential of middlewares built on top of a Java virtual machines has been assessed implementing a mobile object tracking system [2]. We modeled the application using UML (Unified Modeling Language) and implemented using mobile agents with the help of the frameworks JADE [8] and later AFME [30]. An initial evaluation were made from the extracted metrics from the UML models as well as from the generated Java code. The application developed using AFME framework was deployed on a network of SunSPOT sensor nodes running the Squawk Java virtual machine, confirming that significant consumption of processing resources and energy consumption [29].

Additionally. Mote Runner [22] is an interesting virtual machine that execute "bytecodes" generated from the compiled Java or C# programs. An event-driven programming model is adopted using delegates as primitive run-time types.

The interpretation overhead cost and the extra memory required in Java may argue against interpreted languages adoption in WSN. However, bytecodes show a denser representation than their directly executed counterpart, as a consequence interpreted code exhibits smaller power dissipation during over-the-air reprogramming. Consequently, a huge savings in code space and amount of transmitted information can be obtained when a relatively high rate of code updates are needed [101]. Finally, the case for interpreted languages expands as the processing power consumption is reduced; or stated otherwise, lower processing power enables higher abstraction levels and a wider adoption of wireless sensor networks. Chapter 2. Sensor node platform

### 2.3 Low-power techniques and methodologies

In most cases, sensor nodes are powered from batteries, hence the main goal of sensor node design is to extend the node's lifetime. The battery characteristics, including the current rate-capacity effect and the recovery effect, could prevent adopting a simple, and at the same time, precise battery discharge model. In this work we are not considering these second order effects. Decoupling capacitors are usually distributed along the supply bus, which flatten the demand of current drain from the battery. As a result, both effects are minimized, and at the same time the battery usage is maximized [89]. In this context, the metric used for lowpower design is energy or average power, which are interchangeable. Moreover, power is hereinafter sometimes interchanged with current, although not explicitly mentioned, when a nominal supply voltage is considered.

Section 2.1.2 presented the energy breakdown inside a processor, describing where the energy goes. Next, it is briefly described why the energy is consumed in digital circuits and how to reduce the power consumption by means of design techniques and methodologies.

### 2.3.1 Fundamentals of low-power design

The power dissipation of digital circuits are classified in dynamic and static. Dynamic power consumption is associated with the switching of logic values. Static power refers to the power consumed when the device is powered up but it is idle.

The dynamic power has two components: the first corresponds to useful logic operation coming from charging and discharging the output capacitance on a gate; the second is due to short-circuit power that flows through the inverter transistors during a transition (when both are not fully off). The later component is useless power, and it can be minimized by a careful design. The former component can be expressed as:

$$P_{dyn} = CV_{DD}\Delta V f\alpha_{sw}, \qquad (2.1)$$

where C is the total capacitance of the circuit,  $V_{DD}$  is the supply voltage,  $\Delta V$  is the voltage swing, f is the clock frequency, and  $\alpha_{sw}$  denotes the expected switching activity ratio.

The dynamic power can be minimized performing optimizations at different levels: architectural, logic and circuit design, aiming at reducing the contribution of the different components present in the equation. Some techniques focus on lowering the switching activity in the logic gates for a specific function. Because the dynamic power depends quadratically on the supply voltage (when it is consider rail-to-rail operation, i.e.,  $\Delta V = V_{DD}$ ), lowering the supply voltage is an effective way of reducing the dynamic power.

In addition, the relationship between the transistor gate delay,  $t_{inv}$ , and supply voltage is given by:

$$t_{inv} = \frac{kV_{DD}}{(V_{DD} - V_{th})^{\alpha}};$$

(2.2)

where  $V_{th}$  is the threshold voltage,  $\alpha$  has a value in the range 1 to 2, and k is a technology constant [94].

From this it is clear that, to keep the performance,  $V_{th}$  must be lowered with  $V_{DD}$  (and hence  $V_{GS}$ ). However, lowering  $V_{th}$  results in an exponential increase in the sub-threshold leakage current.

These conflicting design objectives had lead to optimization approaches such as: multi-voltage, where different blocks in a circuit have different supply voltages according to the speed requirements; multi-threshold, trading leakage current for speed at different parts of a circuit; clock gating, stopping the clock to reduce the dynamic power to zero. If some performance degradation is accepted, the operating frequency is lowered, so that the voltage can be decreased, technique know as voltage-frequency scaling. In small features technologies, from 90 nm and beyond, the leakage is becoming increasingly important, and it can not dismissed [45]. A common technique to reduce the static power is to shut down the power supply of an inactive logic block, known as power gating.

### 2.3.2 Dynamic power management

Dynamic power management (DPM) refers to the design methodology that dynamically modifies the configuration of a system to decrease its power consumption, while meeting some performance requirement. DPM includes a set techniques to achieve energy-efficient computation by selectively reducing the necessary performance or turning off components when they are underutilized or idle.

DPM relies on two fundamental premises: the system computation load is non uniform during the operation time; and second, it is possible to predict with a certain degree of accuracy, the fluctuations of workload [10]. Another important consideration is that the observation and prediction should not involve a significant energy cost, and that this cost must balance the obtained energy saving.

DPM can be applied at different levels, i.e., to the whole system as a unit, or to their constituent components. The system components or modules are supposed to have multiple modes of operation or power states, and that it is possible to dynamically switch between these states. Needless to say, the more power consumption, the higher performance achieved or the more services offered. The transitions between operation modes may have an associated cost, in terms of delay and energy. If the component is not operational during a non instantaneous transition, there is a performance loss. Moreover, the transition energy cost has a major impact on the benefits of DPM, as we shall see later.

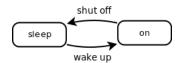

Each component can be modeled using a finite-state representation, called power state machine. This simple abstract model holds for many single-chip components like processors and memories [10]. The system can be modeled as the Cartesian product of the finite-state machine of the system components, however neither all the transition nor the states are valid. This approach is used in the next section to model a sensor node build from COTS components. The power model of a component having two power states, namely active and sleep, is shown in Fig. 2.2.

#### Chapter 2. Sensor node platform

Figure 2.2: Power model of a two states component.

A power manager is the system component that control the states of the other system modules by implementing a policy based on some observation and/or assumption on the workload [10]. The power management approach for defining a policy can be divided into two different categories: non-adaptive or adaptive. The first category includes: greedy and fixed time-out, and the second: predictive wake-up or shut-down. The static techniques are ineffective when the workload is non-stationary; hence some adaptive methods can be applied, for example to dynamically adjust the time-out parameter at the expense of implementation complexity [40].

The break-even time for a sleep state, or any inactive state, is the minimum time required to compensate the cost of entering the state without performance degradation. The inactivity time in the sleep state has a duration equal to the sum of the actual time spent in the sleep state and the time spent to enter and exit it. To be worthwhile entering the sleep time, the inactivity time must be enough to enter and exit the sleep state, and to compensate the additional power consumption.

The break-even time is the sum of the total transition time,  $T_{tr}$ , i.e., the time required to enter and exit the sleep state, and the minimum time that has to be spent in the sleep state to compensate the additional transition energy,  $E_{tr}$ .

The total transition energy is the sum of the wake-up and the shut-down energies,  $E_{tr} = E_{wkp} + E_{sht}$ . The average power transition is  $P_{tr} = E_{tr}/T_{tr}$ .

The break-even time is

$$T_{be} = \frac{E_{tr} - T_{tr} P_{slp}}{P_{act} - P_{slp}}, \quad \text{if} \quad P_{tr} > P_{act}$$

$$T_{be} = T_{tr}, \qquad \qquad \text{if} \quad P_{tr} \le P_{act} \tag{2.3}$$

where  $P_{act}$  and  $P_{slp}$  are the active and sleep power respectively.

In the case of the telos's microcontroller, the transition time is equal to the wake-up time, since the shut-down time is zero. During wake-up, the microcontroller core and peripheral circuit are powered. It must wait until the digitally controlled oscillator stabilizes to source the master clock and become operational again. The microcontroller wake-up time from sleep state (LMP3) is about 6  $\mu$ s (for a clock frequency greater than 1 MHz). The power consumption required during this process is less than the active power. Consequently, the break-even time is equal the transition time,  $T_{be} = T_{tr}$ , since  $P_{tr} \leq P_{act}$  (Eq. 2.3).

The power saving potential by adopting a dynamic power management depends on system and the workload. Depends on the system through the following factors: the power level of the different states, the performance constraints, and the management policy and implementation of the power manager.

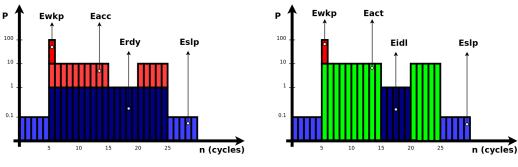

#### 2.4. Characterization of sensor platforms

We define an ideal power manager as one that has a priori knowledge of the entire workload trace, so that it is capable of controlling the component optimally. The ideal power manager wakes the component up just in time for serving upcoming requests, if no performance penalty is tolerated, and it puts the component in sleep state at the beginning of all idle periods longer than the break-even time. We name the policy used by the ideal power manager, best-oracle. *Best* because the component is optimally controlled, and *oracle* in the sense that it "knows the future" workload, so that the ideal power manager is able to take optimal decisions.

The simplest policy is based on a greedy method, which turns the component off a soon as it is idle, and the component is turned on as soon as it is required. A major advantage of greedy policy is its simplicity. But it has two important drawbacks: the strategy does not consider the energy cost of transitions, hence, it may put the component in a lower power state for a short period of time, although if it not worth it; and since it takes some time for the component to be operational again, the response time is increased. One of the most common technique to reduce the first effect is fixed-timeout policy. It uses the elapsed idle time to decide a transition to a lower power state. This simple algorithm may improve the efficiency of the greedy policy, preventing energy waste in short idle times at the expense of reducing the energy saving in long idles times.

Consider the corner case of a system or component in which the transitions between power states are instantaneous and have negligible power cost. The optimum policy is greedy, since it worth transitioning to low power states to save energy all the times. Additionally, there is no performance loss, since the component is fully operational as soon as a new service request is received. Intuitively, the lower the latency and the energy cost of the transitions, the more likely greedy policy approaches to the optimum energy savings.

# 2.4 Characterization of sensor platforms

We conducted some experiments in order to investigate the energy breakdown in a telos sensor mote. The most important components of macro motes are, as already mentioned, the microcontroller and the radio. The node also includes one or more sensors. The sensor in some cases may represent an significant contribution to node power consumption and processor time for acquiring the data from the sensor [100]. One example is CMOS cameras in image applications [96]. Next, for sake of simplicity a sensor with negligible contribution, in terms of power and time, is considered, such as a temperature sensor included in telos mote [90].

#### 2.4.1 Power model

Following the guidelines of DPM, the strategy for reduced power consumption is to keep most of the time the node in states of minimum power.

These states must guarantee proper operation according to requirements, e.g. availability of certain services. The power management approach most widely adopted is greedy.

Chapter 2. Sensor node platform

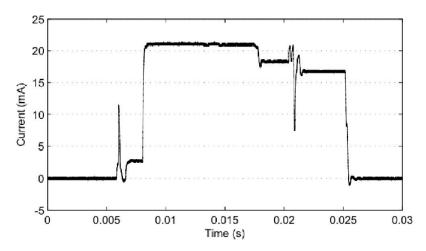

Figure 2.3: Typical current profile of sensor node (telos) [60].

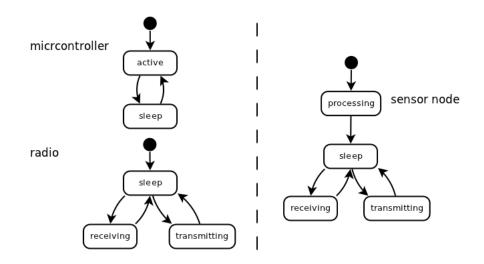

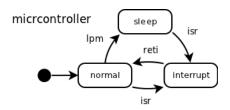

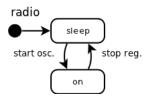

Fig. 2.3 shows an example of current consumption of a telos node as a function of time, where can be clearly identified different current levels. These levels are roughly constant for a certain period of time, which correspond to the given node states. The node states result from the composition of the microcontroller and radio states. The microcontroller operates alternating between two states: sleep and active. The sleep state corresponds to the low-power mode LPM3, in which the core processor is power-down and a timer/counter is feed with an asynchronous external crystal oscillator of 32768 Hz. This timer is used by the operating system (e.g. TinyOS and ContikiOS) to generate a system tick, even when the microcontroller is in a low-power mode. In active mode, the processor run normally clocked from an integrated digitally controller oscillator (by default TinyOS at 4.20 MHz and ContikiOS at 3.9 MHz.). The radio has many operational states, but it can be represented accurately, functionally and in terms of power consumption, with three states: sleep, transmitting<sup>5</sup>, and receiving. Fig. 2.4 shows the microcontroller (top left), and the radio (bottom left) state charts. However, not all node compound states are valid.

The sensor node state chart (Fig. 2.4, right side) only represents valid states and transitions. Table 2.3 lists node states and the corresponding current consumption<sup>6</sup>. The nominal consumption values corresponds to values extracted from datasheets, and the measured values were obtained on a single sensor node. Despite the fact that the consumption may vary between particular devices and with operating condition [56], these values facilitate a first order comparison of power levels of node states.

From the table is evident that the instantaneous power of the radio (receive or transmit mode) exceeds the processing power (microcontroller in active mode) in around one order of magnitude. Therefore, in the early days of wireless sensor

<sup>&</sup>lt;sup>5</sup>An single output power level of 0 dBm is usually used, and thus, modeled.

<sup>&</sup>lt;sup>6</sup>The value showed for the active mode current corresponds to  $f_{DCO}=1$  MHz.

#### 2.4. Characterization of sensor platforms

Figure 2.4: Sensor node states.

| Table 2.3: Sensor node states | and consumption | (telos). |

|-------------------------------|-----------------|----------|

|-------------------------------|-----------------|----------|

| State        |                 |              | Consumption        |               |  |

|--------------|-----------------|--------------|--------------------|---------------|--|

| Sensor node  | Microcontroller | Radio        | Nominal            | Measured      |  |

| Processing   | Active          | Sleep        | $500 \ \mu A$      | $363 \ \mu A$ |  |

| Receiving    | Active          | Receiving    | $19.3 \mathrm{mA}$ | 21.0  mA      |  |

| Transmitting | Active          | Transmitting | $17.9~\mathrm{mA}$ | 20.8  mA      |  |

| Sleep        | Sleep           | Sleep        | $5.1 \ \mu A$      | $5.2 \ \mu A$ |  |

networks, the communication energy cost dominated the overall budget. Consequently a significant research effort has been made since then to reduce the communication energy contribution. The MAC layer design is crucial, since it directly controls the transceiver determining the power profile drain. The use of advanced MAC protocols had helped in improving the energy efficiency for communication [20].

Prayati et al. [91] isolated and measured each contribution to the overall node power consumption, confirming the values above and providing a model from which the total energy can be estimated as a function of the different power levels and the corresponding duty-cycles (i.e. the fraction of time a power contribution is present).

The roughly constant energy consumption associated to different states has been exploited to estimate the energy consumption by the node itself, in ContikiOS (Energest [36]), and later in TinyOS (Quanto [42]). Also, it has been used to profile the radio activity using a second sensor node that logs the sequence of time during which the radio spend in each state [75]. This method had served to assess the communication efficiency in real deployments in precise agriculture applications [76].

#### Chapter 2. Sensor node platform

In Energest and Quanto the node measure and accumulate the elapsed time in each state. Periodically the values are reported to the sink node where each energy consumption contribution is computed. The energy consumption can be expressed as the sum of each state contribution, computed as the power level multiplied by the accumulated time in the corresponding state. The state transitions contribution can be neglected. The microcontroller wake-up time is about 6  $\mu$ s, for clock frequency greater than 1 MHz, which correspond to six cycles at 1 MHz and less than two of cycles at 4 MHz. The radio oscillator startup time, i.e. transition from low to active power, is about 600  $\mu$ s, and corresponds to the time spent to transmit about 18 bytes, roughly the MAC protocol overhead.

The sensor node energy consumption after elapsed a time t is

$$E(t) = P_{prc}t_{prc} + P_{tx}t_{tx} + P_{rx}t_{rx} + P_{slp}t_{slp}$$

(2.4)

where  $t_{prc} + t_{tx} + t_{rx} + t_{slp} = t$ , and the time and power subscripts refers to processing, transmitting, receiving and sleep state respectively, of Fig. 2.4 (right side) and Table 2.3.

Thus, the average power  $(P_{avq} = E/t)$  is

$$P_{avg} = P_{prc}d_{prc} + P_{tx}d_{tx} + P_{rx}d_{rx} + P_{slp}d_{slp}$$

$$\tag{2.5}$$

where  $d_i = t_i/t$  for  $i \in \{prc, rx, tx, slp\}$ , the respective duty-cycles.

The expression can be rewritten as

$$P_{avg} = P_{prc}^* d_{prc} + P_{tx}^* d_{tx} + P_{rx}^* d_{rx} + P_{slp}$$

(2.6)

where  $P_i^* = P_i - P_{slp}$  for  $i \in \{prc, rx, tx\}$  is the power increment from the sleep power baseline.

Consequently, the average power consumption can be computed adding to the sleep power baseline consumption, the power contribution of the other states, expressed as the power increment respect to this reference multiplied by the corresponding average duty-cycle.

#### 2.4.2 Energy breakdown

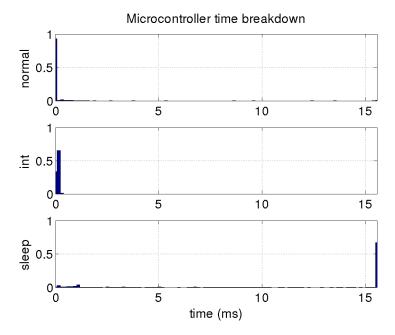

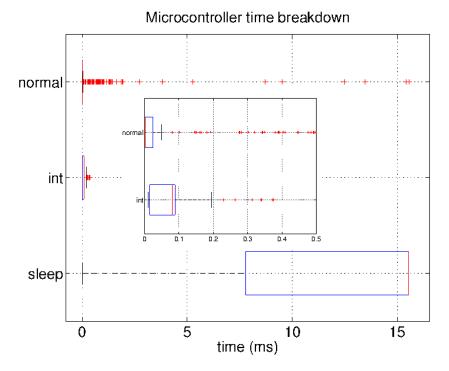

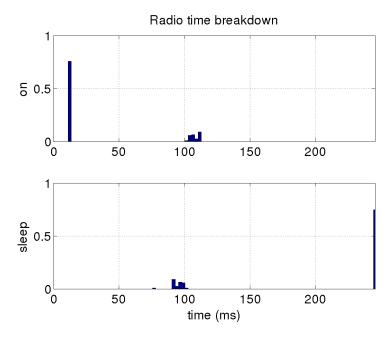

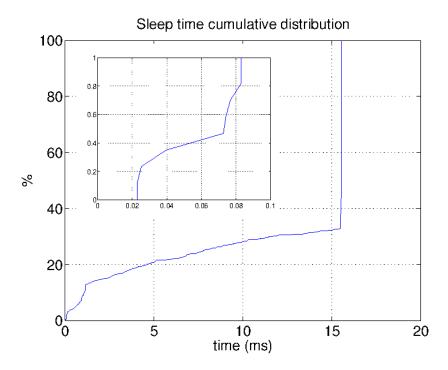

We took two different approaches to estimate the energy contribution of the different component states. The first method was based on the Energest module included in ContikiOS [36]. The average power consumption was estimated using Eq. (2.6) from the information of the time spent in the different states of the microcontroller and the radio. The second one was based on simulations and offline trace analysis, and it was focused on further investigate the microcontroller time breakdown.

The criteria for selecting the case study were: public availability of source files, practical, and almost ready-to-use applications. Unfortunately, the number of cases complying with the aforementioned restrictions are scarce. We chose two data-collection application from the standard distribution of TinyOS (version 2.1.0) and ContikiOS (release 2.5). Both applications are similar, each node of

#### 2.4. Characterization of sensor platforms

| OS        | Application              | text  | bss | data | #functions |

|-----------|--------------------------|-------|-----|------|------------|

| TinyOS    | MultihopOscilloscope     | 32058 | 122 | 3534 | 1081       |

| ContikiOS | rpl-collect (udp-sender) | 47552 | 232 | 9250 | 489        |

Table 2.4: Application parameters (size in bytes).

the network periodically samples a temperature sensor and the readings are transmitted to a sink node using a network collection protocol. MultihopOscilloscope (TinyOS) uses Low-Power listening (LPL) protocol [79] for medium access control, and CTP (Collection Tree Protocol) [46] for network routing. On the other hand, rpl-collect (ContikiOS) rely in ContikiMAC [34,35] for communicating with neighboring nodes, and the Contiki implementation of RPL (IPv6 Routing Protocol for Low power and Lossy Networks) [112], ContikiRPL [107], for routing packages.

The applications were compiled for a telos sensor node using the standard toolchain required by the software platforms (see the corresponding project site for details). Table 2.4 summarizes section sizes and number of functions of the selected applications.

#### Time measurement in field (Energest)

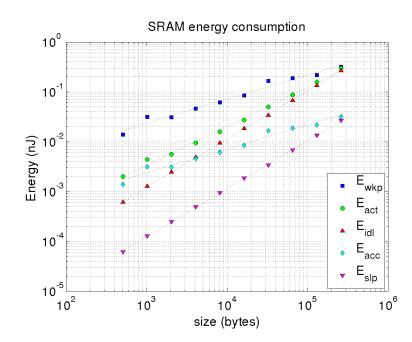

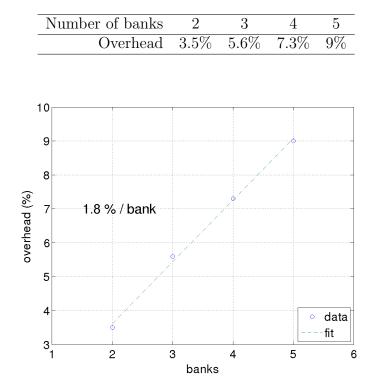

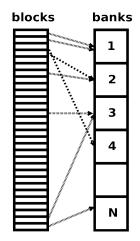

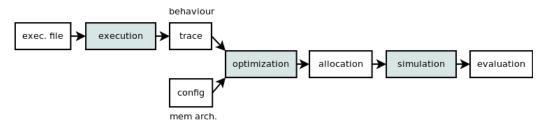

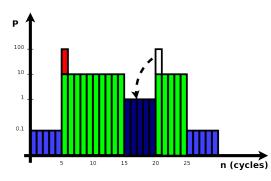

The ContikiOS module Energest measures the time elapsed in predefined states. The time resolution is 7.8125 ms (inherited form the *rtimer* module, 1/128 sec) Energest includes the sensor states showed in Fig. 2.4 where the state *processing* is split in two states to differentiate the processing performed in a interrupt context from the normal processing (usually named as cooperative to highlight its non-preemtiveness nature). The Energest and the application source codes were modified to remove some limitations, and thus suit our needs (for details see Appendix B.2.1).