# Prototipado en FPGAs para inyección de fallas. Aplicación a sistemas distribuidos sobre bus CAN

Tesis de maestría en Ingeniería Eléctrica

#### Julio PÉREZ ACLE

#### Director de Tesis:

Matteo SONZA REORDA, Politecnico di Torino, Italia

#### Director Académico:

Rafael CANETTI, IIE, Facultad de Ingeniería, Universidad de la República, Uruguay

#### Tribunal:

Rafael CANETTI, IIE, Facultad de Ingeniería, Univ. de la República, Uruguay

Marcelo LUBASZEWSKI, Univ. Federal do Rio Grande do Sul, Brasil

Gregory RANDALL IIE, Facultad de Ingeniería, Univ. de la República, Uruguay

Raúl VELAZCO, INPG, Laboratoire TIMA, Grenoble, Francia

Instituto de Ingeniería Eléctrica

Facultad de Ingeniería

Universidad de la República

Montevideo, Uruguay 8 de setiembre de 2005 ISSN: 1510-7264 - Reporte Técnico Nº

#### Contenido

| Introduc                | eción                                                       | 1           |

|-------------------------|-------------------------------------------------------------|-------------|

| Resul                   | tados                                                       | 3           |

| Crono                   | ología                                                      | 4           |

| Organ                   | nización del documento                                      | 4           |

|                         |                                                             |             |

| Parte I De <sub>l</sub> | pendabilidad y técnicas de inyección de fallas              | 7           |

| Capítulo                | o 1 Dependabilidad. Un resumen de los principales conceptos | 9           |

| 1.1.                    | Definiciones                                                | 10          |

| 1.2.                    | Las amenazas: Fallas (faults), Errores (errors), y Malfunc  | ionamientos |

| (failu                  | res)                                                        | 10          |

| 1.3.                    | Los Atributos de la dependabilidad                          | 12          |

| 1.4.                    | Los Medios para alcanzar dependabilidad                     | 13          |

| Pre                     | vención de fallas                                           | 13          |

| To                      | lerancia a fallas                                           | 14          |

| Rei                     | moción o eliminación de fallas                              | 15          |

| Pre                     | dicción de fallas                                           | 15          |

| Capítulo                | 2 Técnicas de inyección de fallas                           | 17          |

| 2.1.                    | Finalidades de la inyección de fallas                       | 17          |

| 2.2.                    | Espacio de fallas (Fault Space)                             | 18          |

| 2.3.                    | Modelo FARM                                                 | 19          |

| 2.4.                    | Estimación estadística de cobertura de fallas               | 21          |

| 2.5.                    | Inyección de fallas por mecanismos Hardware                 | 23          |

| 2.6.                    | Inyección de fallas por mecanismos Software                 | 25          |

| 2.7.                    | Inyección de fallas sobre modelos de descripción hardware   | 26          |

| Iny                     | rección basada en Simulación                                | 26          |

| Iny                     | rección basada en Emulación                                 | 28          |

| Parte II Pro            | otocolo CAN y redes a bordo de automóviles                  | 31          |

| Capítulo                | o 3 Protocolo Can                                           | 33          |

| 3.1.         | Breve descripción del protocolo CAN                                   | 33   |

|--------------|-----------------------------------------------------------------------|------|

| 3.2.         | Protocolos de capas superiores sobre CAN                              | 35   |

| 3.3.         | Dependabilidad y CAN                                                  | 36   |

| Capítulo     | 4 Uso de redes a bordo de automóviles                                 | 41   |

| 4.1.         | Sistemas electrónicos a bordo                                         | 41   |

| 4.2.         | Diversidad de requerimientos                                          | 42   |

| 4.3.         | Clasificación de redes según SAE                                      | 43   |

| 4.4.         | Ejemplo                                                               | 44   |

| Parte III De | esarrollos y experimentos                                             | 47   |

| Capítulo     | 5 Desarrollo del controlador de protocolo CAN                         | 49   |

| 5.1.         | Requerimientos. ¿Por qué un nuevo controlador?                        | 49   |

| 5.2.         | Descripción del controlador y estado actual del desarrollo            | 50   |

| Capítulo     | 6 Ambiente para inyección de fallas                                   | 53   |

| 6.1.         | Soporte para inyección de fallas                                      | 54   |

| Iny          | ección a nivel del bus CAN                                            | 54   |

| Iny          | ección en el interior del controlador CAN                             | 55   |

| 6.2.         | Ambiente basado en simulación                                         | 60   |

| 6.3.         | Ambiente basado en emulación en prototipo hardware                    | 62   |

| Em           | ulación de aplicación: Castor                                         | 63   |

| Em           | ulación de la red: Pollux                                             | 65   |

| Capítulo     | 7 Experimentos realizados                                             | 67   |

| 7.1.         | Primera serie de experimentos: interrogación cíclica de nodos esclavo | s 67 |

| Elo          | conjunto F: Fallas                                                    | 68   |

| Cor          | njunto A: tráfico destinado a Activar las fallas                      | 69   |

| Car          | npañas basadas en simulación                                          | 70   |

| Car          | npañas basadas en emulación                                           | 72   |

| Res          | sultados y conclusiones de la primera serie de experimentos           | 74   |

| 7.2.         | Segunda serie de experimentos: maniobra de viraje en un automóvil     | 74   |

| Des          | scripción del sistema                                                 | 75   |

| Mo           | delo FARM                                                             | 76   |

| Res          | ultados                                                               | 82   |

| Rec          | cursos utilizados y performance obtenida                              | 85   |

| Con         | clusiones de la segunda serie de experimentos85                    |

|-------------|--------------------------------------------------------------------|

| Capítulo    | 8 Conclusiones y trabajos futuros                                  |

| 8.1.        | Resultados obtenidos                                               |

| 8.2.        | Trabajos futuros                                                   |

| 8.3.        | Comentarios finales                                                |

|             |                                                                    |

| Referencias | 591                                                                |

|             |                                                                    |

| Anexos      | 97                                                                 |

| Anexo 1     | Dependabilidad. Índice de términos y su correspondencia con los    |

| términos    | en idioma inglés99                                                 |

| Anexo 2     | Trabajos publicados                                                |

| 8.1.        | 16th Symposium on Integrated Circuits and Systems Design (SBCCI)   |

| 2003        | 105                                                                |

| 8.2.        | 18th IEEE International Symposium on Defect and Fault Tolerance in |

| VLSI        | Systems (DFT'03) 2003                                              |

| 8.3.        | 17th Symposium on Integrated Circuits and Systems Design (SBCCI)   |

| 2004        | 107                                                                |

| 8.4.        | IEEE High-level Design Validation and Test Workshop (HLDVT) 2004   |

|             | 108                                                                |

Existen cada día más sistemas críticos en los que la indisponibilidad del servicio u otro malfuncionamiento provocado por fallas puede tener consecuencias muy graves, tanto desde el punto de vista económico como en eventuales daños a las personas o al medio ambiente.

En el diseño y la operación de sistemas de este tipo deben tomarse precauciones para minimizar la cantidad de salidas de servicio y malfuncionamientos. Esto puede hacerse por la vía de minimizar la cantidad de fallas, por la vía de hacer que el sistema sea capaz de seguir brindando el servicio en presencia de fallas, o por la vía de minimizar las consecuencias de un servicio deteriorado.

Tiene interés entonces conocer en primera instancia a qué fallas estará expuesto un sistema dado y con qué frecuencia se producirán, y en una segunda instancia evaluar cuál será el comportamiento del sistema frente a esas fallas. El objetivo de un análisis de este tipo varía a lo largo del ciclo de vida del sistema: en la fase de desarrollo será útil para depurar y mejorar los mecanismos de tolerancia a fallas. En la fase de producción servirá para verificar si se han alcanzado o no los niveles requeridos de confiabilidad y justificar así la confianza que pueda depositarse en el servicio brindado por el sistema. Para realizar esta evaluación existen métodos analíticos y métodos experimentales.

Las técnicas de inyección de fallas son métodos experimentales que consisten en analizar el comportamiento de un modelo o un prototipo del sistema frente a fallas provocadas artificialmente. En particular en sistemas que involucren circuitos electrónicos digitales, que son los que nos ocuparán en este trabajo, la inyección de fallas consistirá en modificar por algún mecanismo el valor de señales de entrada o internas del circuito. Las principales ventajas de esta técnica son la repetibilidad de los experimentos y el permitir obtener una cantidad estadísticamente suficiente de experimentos en un tiempo varios órdenes de magnitud menor al necesario si nos limitáramos a observar las fallas producidas naturalmente en el sistema en operación.

La inyección de fallas es una herramienta útil para depurar los mecanismos de tolerancia a fallas durante la fase de desarrollo, para evaluar qué fracción de las fallas a las que se somete el sistema provocarán un malfuncionamiento del mismo y para evaluar la gravedad de los efectos provocados por esos malfuncionamientos. Para estimar otras métricas relacionadas a la confiabilidad hace falta además obtener información sobre la distribución estadística de las fallas.

Por otra parte, la industria automotriz es un área en la que hay una demanda creciente de requerimientos de confiabilidad sobre sistemas electrónicos. Cada vez más funciones críticas para la seguridad (control de frenado, suspensión, volante) están pasando a ser realizadas por unidades electrónicas de control (ECUs) interconectadas a través de una red de datos con una topología de bus. Uno de los estándares más utilizados para esa red de datos a bordo es CAN (Controller Area Network) introducido por Bosch y posteriormente normalizado como el estándar ISO 11898.

El objetivo del presente trabajo fue alcanzar el estado del arte de las técnicas de inyección de fallas y principalmente explorar la utilización de técnicas de prototipado en FPGAs para acelerar campañas de inyección de fallas en sistemas electrónicos digitales.

El área de aplicación elegida fue la de sistemas distribuidos formados por las unidades electrónicas de control de un automóvil interconectadas por un bus CAN. Los controladores del protocolo CAN y el propio bus fueron prototipados en un circuito sintetizado dentro de un único chip.

Se plantearon objetivos en cierto modo contrapuestos: por un lado se procuró analizar el efecto de fallas en el interior del controlador de acceso al bus CAN, para lo que hace falta modelar en detalle el circuito del controlador. Por otro lado se trazó como objetivo analizar el efecto de las fallas a un nivel lo más alto posible, idealmente al nivel del comportamiento del vehículo. De este modo es posible incluir en el análisis el efecto de los mecanismos de tolerancia a fallas intrínsecos del sistema, como puede ser la inercia mecánica en el caso de un vehículo, así como de los mecanismos de tolerancia a fallas introducidos ex-profeso en el diseño de la aplicación y el protocolo de comunicaciones. Este doble objetivo obligó a describir diferentes partes del

sistema con diferentes niveles de abstracción para poder llegar a un modelo computacionalmente accesible.

#### Resultados

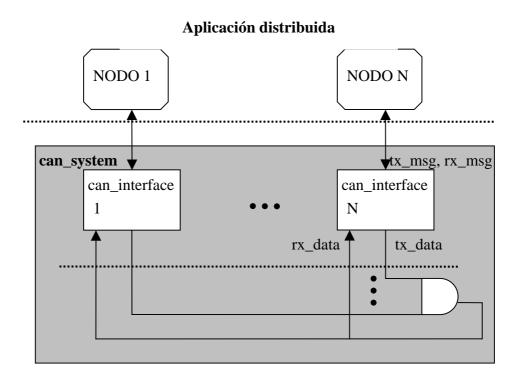

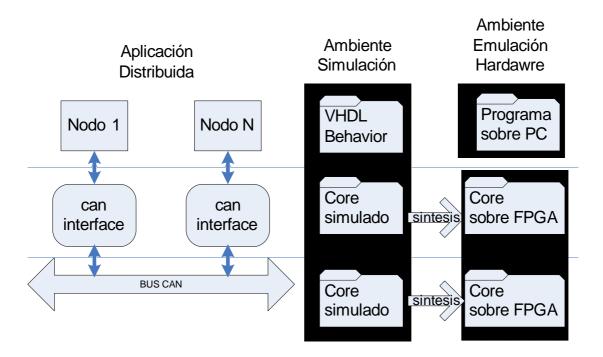

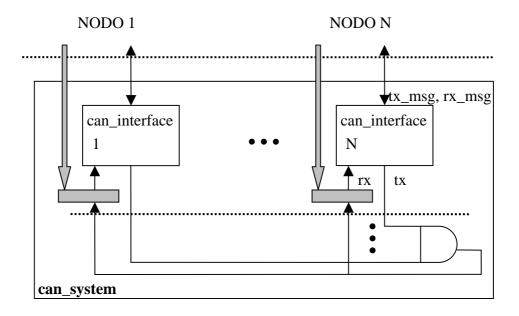

Como resultado de este trabajo se obtuvieron herramientas para simplificar la realización de campañas de inyección de fallas sobre modelos de transferencia de registros de sistemas distribuidos comunicados por un bus CAN. Se desarrollaron dos conjuntos de herramientas que comparten la misma descripción en lenguaje VHDL (Very high speed integrated circuit Hardware Description Language) del bus y de los controladores de acceso al mismo. Por un lado se desarrollaron herramientas para inyección en un simulador VHDL estándar ejecutando en un computador (se utilizó Modelsim), en las que el comportamiento de cada unidad de control se describe como módulos VHDL simulables. Por otro lado, herramientas para inyección de fallas sobre un prototipo hardware en que los controladores de acceso al bus y el propio bus fueron sintetizados en una placa FPGA insertada en un slot PCI de un computador personal, mientras que el comportamiento de las unidades de control es emulado por software.

Un subproducto importante de los trabajos realizados para la presente tesis fue la obtención de la descripción en VHDL sintetizable de un controlador de acceso a bus CAN. Este desarrollo fue necesario porque se pretendió analizar el efecto de fallas sobre los registros internos de los controladores de acceso al bus CAN, para lo que fue necesario tener acceso al código fuente del mismo a efectos de poder introducir las modificaciones requeridas para la inyección de fallas.

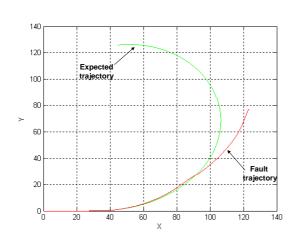

Se realizaron varias campañas de inyección de fallas donde se ensayaron las herramientas desarrolladas obteniéndose una muy buena performance en cantidad de fallas inyectadas por unidad de tiempo. Utilizando las herramientas desarrolladas junto con un modelo del comportamiento de un vehículo, desarrollado previamente por otro grupo de investigación del Politecnico di Torino, fue posible analizar los efectos de cada falla a lo largo del sistema y en consecuencia identificar las fallas críticas desde el punto de vista de la seguridad del vehículo.

Los resultados numéricos de los experimentos de inyección de fallas presentados en este trabajo están fuertemente influidos por lo bien o mal que se comporta frente a

fallas el controlador CAN utilizado. Dicho controlador no fue diseñado con el objetivo de hacerlo tolerante a fallas y no hubo un interés especial por hacer una evaluación cuantitativa de sus atributos en cuanto a confiabilidad.

Entonces, los resultados más fuertes del presente trabajo no son los resultados numéricos, que no son generalizables, sino que son por un lado los resultados cualitativos en cuanto a los efectos que puede tener una falla en el controlador CAN sobre el comportamiento de un vehículo, y por otro lado la metodología de modelado en diferentes niveles y las herramientas desarrolladas tendientes a integrar esos diferentes niveles en un mismo experimento.

#### Cronología

Las tareas para el desarrollo descrito líneas arriba fueron realizadas principalmente durante dos pasantías realizadas a principios de 2003 y a principios de 2004 en el Dipartimento di Automatica e Informatica del Politecnico di Torino. En ambas pasantías trabajé en el seno del grupo dirigido por el tutor de esta tesis Matteo SONZA, en estrecha colaboración con Massimo VIOLANTE del mismo grupo.

Resultados parciales de estos trabajos fueron publicados previamente en memorias de conferencias [18] [20] [21] [22] [19].

#### Organización del documento

El trabajo está organizado en tres partes principales y varios anexos.

En la Parte I se presenta la terminología y un resumen de los principales conceptos de *dependabilidad* [Capítulo 1] y los antecedentes en técnicas de inyección de fallas [Capítulo 2].

En la Parte II se hace una breve presentación del área de aplicación elegida, más precisamente del protocolo CAN [Capítulo 3] y de las redes utilizadas en la industria automotriz [Capítulo 4].

En la Parte III se describen las herramientas desarrolladas y los experimentos realizados. En [Capítulo 5] se presenta el controlador de protocolo CAN desarrollado, en [Capítulo 6] el ambiente para permitir la inyección de fallas y en [Capítulo 7] las

campañas experimentales realizadas. Algunas conclusiones y líneas de trabajo futuro se resumen en [Capítulo 8].

### **PARTE I**

# DEPENDABILIDAD Y TÉCNICAS DE INYECCIÓN DE FALLAS

En esta parte se introducen algunos conceptos básicos para las técnicas de inyección de fallas.

En el Capítulo 1 se presentan términos y definiciones relativos a la capacidad de los sistemas de proveer un servicio en el cual se pueda confiar en forma justificada, y a los mecanismos con que cuentan los diseñadores y usuarios de esos sistemas para fundamentar esa confianza. Esa propiedad de un sistema se denomina en inglés dependability. En el Anexo 1 se presenta un resumen de la terminología utilizada en este trabajo y su correspondencia con los términos utilizados en otros idiomas.

La disciplina de inyección de fallas es introducida en el Capítulo 2. Se presentan las definiciones básicas, las diferentes finalidades perseguidas al realizar experimentos de inyección de fallas y los principales antecedentes en el área. Se pone el énfasis en la inyección de fallas en circuitos electrónicos digitales, y en particular en las técnicas que se utilizaron en el presente trabajo: inyección de fallas en simulaciones de circuitos descritos a nivel de transferencia de registros e inyección de fallas en prototipos de los circuitos sintetizados dentro de un FPGA.

#### Capítulo 1

# Dependabilidad. Un resumen de los principales conceptos

Existen una serie de términos para referirse a conceptos relacionados con la confiabilidad de los sistemas que, por tener significados similares entre sí en lenguaje natural, dieron durante mucho tiempo lugar a confusión y superposiciones. Durante los años 80 hubo varios trabajos que fueron formando una estructura de conceptos y terminología consistentes. Esta estructura fue sintetizada en un trabajo de Laprie [30] y varias actualizaciones posteriores [10] [24] [53][5].

La dependabilidad de un sistema se define como su capacidad de proveer un servicio en el cual se puede confiar en forma justificada. Es un concepto cualitativo que integra diferentes aspectos o atributos cuantificables (confiabilidad, disponibilidad, seguridad, etc.). El desempeño de los sistemas en estos aspectos no es el ideal debido a la existencia de fallas, errores y malfuncionamientos (denominados amenazas a la dependabilidad en la terminología de Laprie). Para mejorar la dependabilidad se procura en forma combinada por un lado evitar, tolerar y eliminar las fallas y por otro lado estimar la cantidad y posibles consecuencias de las mismas. A estas técnicas se les llama en conjunto los medios para alcanzar la dependabilidad.

Las técnicas de inyección de fallas consisten en analizar el comportamiento real o simulado de un sistema en presencia de fallas provocadas artificialmente. Estas técnicas se utilizan con diferentes finalidades: en la etapa de desarrollo para depurar, corregir o verificar los elementos y mecanismos que pretenden hacerlo tolerante a fallas; más adelante para caracterizar y cuantificar los malfuncionamientos provocados por las fallas que escapan a estos mecanismos, contribuyendo así a justificar la confianza depositada en el servicio.

Se presenta en lo que resta de este Capítulo 1 un resumen de la terminología presentada por Laprie, poniendo énfasis en los aspectos más relevantes para las técnicas de inyección de fallas desarrolladas en el resto del trabajo. Dado que en su mayor parte se trata de definiciones se ha preferido hacer una traducción casi textual

de las partes de textos de Laprie [24] [53] que más interesan para nuestro trabajo. En el Anexo 1 se da un glosario de términos y su correspondencia con los términos en inglés utilizados en los trabajos originales.

#### 1.1. Definiciones

Una exposición sistemática de los conceptos de *dependabilidad* consiste de tres partes: las **amenazas** a, los **atributos** de, y los **medios** por los cuales la *dependabilidad* es obtenida.

Los sistemas de cómputo se caracterizan por cuatro propiedades fundamentales: funcionalidad, performance, costo, y *dependabilidad*. La *dependabilidad* es la capacidad de proveer un servicio en el cual se puede confiar en forma justificada. El **servicio** que provee un sistema es su comportamiento tal como es percibido por sus usuarios; un **usuario** es otro sistema (físico, humano) que interactúa con el primero en la **interfaz del servicio**. La **función** de un sistema es aquello para lo cual fue creado, y está descrita en la especificación funcional del mismo.

# 1.2. Las amenazas: Fallas (faults), Errores (errors), y Malfuncionamientos (failures)

Se entrega un servicio correcto cuando el servicio implementa la función del sistema.

Un malfuncionamiento del sistema es un evento que ocurre cuando el servicio provisto se desvía del servicio correcto. Un sistema puede malfuncionar ya sea porque no cumple con la especificación o porque la especificación no describe adecuadamente la función. Un malfuncionamiento es una transición desde servicio correcto a servicio incorrecto, i.e., a no implementar la función del sistema. Una transición desde servicio incorrecto a servicio correcto es una restauración de servicio. El intervalo de tiempo durante el cual se entrega servicio incorrecto es una salida de servicio.

Un **error** es un estado del sistema que puede provocar un subsiguiente malfuncionamiento: cuando un error llega a la interfaz del servicio y altera el servicio suministrado sucede un malfuncionamiento. Una **falla** es la causa hipotética o adjudicada de un error. Una falla está **activa** cuando produce un error, de lo contrario está **dormida**.

Un sistema no siempre malfunciona de la misma manera. Las maneras en que un sistema puede malfuncionar son sus **modos de malfuncionamiento.** Los modos de malfuncionamiento caracterizan al servicio incorrecto desde tres puntos de vista: a) el dominio del malfuncionamiento (de valor, de temporización), b) la percepción del malfuncionamiento por los diferentes usuarios del sistema (consistentes o no), y c) las consecuencias del malfuncionamiento en el ambiente.

Un sistema consiste de un conjunto de componentes que interactúan, por lo tanto el estado del sistema es el conjunto de los estados de sus componentes. Inicialmente una falla provoca un error en el estado de uno o varios componentes, pero no se produce un malfuncionamiento del sistema hasta tanto el error no llega a la interfaz del servicio brindado por el sistema. Una forma conveniente de clasificar los errores es describirlos en términos de los malfuncionamientos que provocan, usando la terminología introducida más arriba: errores de valor vs. errores de temporización; errores consistentes o inconsistentes ('Bizantinos') cuando la salida va a más de un componente; errores de diferente severidad: menores, ordinarios, catastróficos. Un error es **detectado** si su presencia en el sistema es indicada por un mensaje o señal de error originada en el interior del sistema. Errores que están presentes pero no han sido detectados son **errores latentes**.

Las fallas y sus orígenes son muy variados. Posibles criterios de clasificación de las mismas son:

- La fase de creación o ocurrencia de la falla (fallas de desarrollo, fallas operativas)

- Las fronteras del sistema (fallas internas o externas)

- Fallas de hardware o de software

- Causa fenomenológica (Fallas naturales o humanas)

- Intencionalidad (Fallas deliberadas o no deliberadas)

- Persistencia (Fallas permanentes o transitorias)

Se puede argüir que introducir las causas fenomenológicas como criterio de clasificación puede conducir recursivamente a preguntas como "¿y por qué los programadores cometen errores?", "¿por qué fallan los circuitos integrados?". El concepto falla sirve para detener la recursión. Por eso la definición dada: causa hipotética o adjudicada de un error. Esta causa adjudicada o hipotética puede variar dependiendo del punto de vista elegido: mecanismos de tolerancia a fallas, ingeniero de mantenimiento, centro de reparaciones, desarrollador, físico en semiconductores, etc..

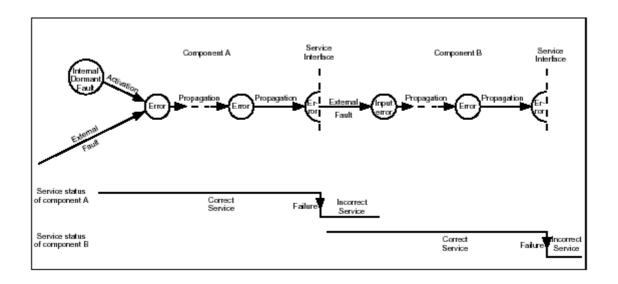

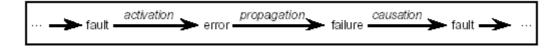

A la relación entre fallas, errores, y malfuncionamientos descrita líneas arriba se le llama **patología de las fallas,** y se resume en la Fig. 2, que muestra la cadena fundamental de propagación de las amenazas a la *dependabilidad*. Los arcos en esa cadena expresan una relación de causalidad entre fallas, errores, y malfuncionamientos.

Fig. 1 Propagación de errores. (tomada de [53])

Fig. 2 Cadena fundamental de las amenazas a la dependabilidad (tomada de [53])

#### 1.3. Los Atributos de la dependabilidad

La Dependabilidad es un concepto integrador que abarca los siguientes atributos: disponibilidad: estar listo para proveer servicio correcto; confiabilidad: continuidad

de servicio correcto; **seguridad-safety**: ausencia de consecuencias catastróficas sobre los usuarios y el ambiente; **confidencialidad**: ausencia de difusión no autorizada de información; **integridad**: ausencia de alteraciones no adecuadas del estado del sistema; **mantenibilidad**: aptitud para ser sometido a reparaciones y modificaciones.

Cada uno de los atributos listados arriba puede ser requerido con más o menos énfasis dependiendo de la aplicación: siempre se requiere disponibilidad, si bien en grados diversos, mientras que confiabilidad, seguridad-safety, y confidencialidad pueden o no ser requeridos. El grado en el cual un sistema posee los atributos de *dependabilidad* debería ser interpretado en un sentido relativo, probabilístico y no en un sentido absoluto, determinístico: debido a la inevitable presencia u ocurrencia de fallas, los sistemas no son nunca totalmente disponibles, confiables o seguros.

Las variaciones en el énfasis puesto en los diferentes atributos de la *dependabilidad* afectan directamente cual es el adecuado balance de técnicas (**prevención**, **tolerancia**, **remoción** y **predicción de fallas**) a ser empleadas para hacer que el sistema resultante sea *dependable*.

Este problema es aún mas grave ya que algunos de los atributos coliden (e.g. disponibilidad y seguridad-safety, disponibilidad y seguridad-security), haciendo necesarios compromisos de diseño.

#### 1.4. Los Medios para alcanzar la dependabilidad

El desarrollo de un sistema de cómputo *dependable* requiere la utilización combinada de un conjunto de cuatro técnicas: **prevención de fallas**: cómo evitar la ocurrencia o introducción de fallas; **tolerancia a fallas**: cómo proveer servicio correcto en presencia de fallas; **remoción de fallas**: cómo reducir el número o la severidad de las fallas; y **predicción de fallas**: cómo estimar el número actual, la incidencia futura y las posibles consecuencias de las fallas.

#### Prevención de fallas

La prevención de fallas se obtiene empleando técnicas de buen diseño y de control de calidad. Estas son técnicas generales de ingeniería y exceden ampliamente la disciplina de la *dependabilidad*, por lo que no nos extenderemos sobre este tema.

#### Tolerancia a fallas

La tolerancia a fallas intenta mantener la entrega de un servicio correcto en presencia de fallas activas. En general se implementa por medio de la detección de errores y la posterior recuperación del sistema.

La **detección de errores** origina un mensaje o señal de error en el interior del sistema. Un error presente que no ha sido detectado es un error latente. Existen dos clases de técnicas para la detección de errores: (a) detección de errores concurrente, que tiene lugar durante la entrega del servicio; y (b) detección de errores "preemptiva", que tiene lugar con la entrega del servicio suspendida; chequeando el sistema en busca de errores latentes y fallas dormidas.

La **recuperación del sistema** lo transforma desde un estado que contiene uno o más errores y (posiblemente) fallas a un estado sin fallas y errores detectados que puedan volverse a activar.

La recuperación consiste en el manejo de errores y de fallas.

El **manejo de errores** elimina errores del sistema. Puede tomar dos formas: (a) **rollback**, en que la transformación del estado del sistema consiste en llevar al sistema a un estado previamente almacenado, anterior a la detección del error; este estado almacenado es un **checkpoint**, (b) **rollforward**, donde el estado sin errores detectados es un estado nuevo.

El manejo de fallas evita que las fallas localizadas sean activadas nuevamente. El manejo de fallas involucra cuatro pasos: a) diagnóstico, que identifica y registra la o las causas de errores en términos de ubicación y tipo. b) aislación de la falla, que excluye física o lógicamente a los componentes en falla de participar en el suministro del servicio, i.e., se hace que la falla se convierta en dormida. c) reconfiguración del sistema, que o bien introduce componentes de reserva o reasigna las tareas sobre los componentes que no han fallado. d) reinicialización del sistema, que chequea, actualiza y registra la nueva configuración. Usualmente a continuación de este manejo de fallas se realiza un mantenimiento correctivo que elimina la falla aislada. El factor que distingue la tolerancia a fallas del mantenimiento es que el mantenimiento requiere la participación de un agente externo.

El disponer de redundancia suficiente permite recuperar al sistema sin una detección de errores explícita. A esta forma de recuperación se le llama **enmascaramiento de fallas**.

#### Remoción o eliminación de fallas

La remoción de fallas se realiza tanto durante la fase de desarrollo como durante la vida operativa de un sistema.

Durante la fase de desarrollo de un sistema, la remoción de fallas consta de tres pasos: verificación, diagnóstico y corrección. **Verificación** es el proceso de controlar si el sistema cumple las llamadas condiciones de verificación. Si no las cumple entonces corresponde proceder con los otros dos pasos: **diagnosticar** las fallas que impidieron cumplir las condiciones y luego realizar las **correcciones** necesarias.

Las técnicas de verificación pueden clasificarse dependiendo de si involucran o no ejercitar el funcionamiento del sistema. A la verificación de un sistema sin una ejecución del mismo se le llama **verificación estática**. Verificar un sistema a través de una ejecución del mismo es una **verificación dinámica**. La ejecución puede ser simbólica o puede ser una ejecución real con entradas reales aplicadas al sistema en lo que se llama **test de verificación** (o **test** a secas) del sistema. Un aspecto importante es la verificación de los mecanismos de tolerancia a fallas, ya sea a) verificación estática formal, y b) tests en los cuales los patrones de test deben contener fallas o errores, a esto último se le denomina **inyección de fallas**.

La remoción de fallas durante la vida operativa del sistema es el **mantenimiento**, ya sea preventivo o correctivo.

#### Predicción de fallas

La predicción de fallas es llevada a cabo realizando una evaluación del comportamiento del sistema con respecto a la ocurrencia o activación de fallas. Esta evaluación puede realizarse de dos formas: (1) evaluación cualitativa u ordinal, que procura identificar, clasificar y ordenar los modos de malfuncionamiento; (2) evaluación cuantitativa o probabilística, que procura evaluar en términos probabilísticos el grado de satisfacción de determinados atributos de la

dependabilidad; estos atributos pueden verse entonces como medidas de la dependabilidad.

La alternancia entre servicio correcto y servicio incorrecto se cuantifica para definir confiabilidad, disponibilidad y mantenibilidad como medidas de la *dependabilidad*: (1) **confiabilidad**: una medida de la provisión continuada de servicio correcto, o en forma equivalente, el tiempo hasta la falla; (2) **disponibilidad**: una medida de la provisión de servicio correcto con respecto a la alternancia "servicio correcto-servicio incorrecto"; (3) **mantenibilidad**: medida del tiempo hasta la restauración del servicio desde la última falla, o en forma equivalente, provisión continuada de servicio incorrecto. (4) **seguridad-safety:** es una extensión de confiabilidad: Si se agrupan bajo un estado "seguro" los estados de servicio correcto y los estados de servicio incorrecto debidos a fallas no catastróficas, entonces puede definirse seguridad-safety como el tiempo hasta malfuncionamientos catastróficas.

Las dos principales maneras de atacar la evaluación probabilística de las medidas de *dependabilidad* son el **modelado** y el **test de evaluación**. Cuando se evalúan sistemas tolerantes a fallas, la cobertura provista por los mecanismos de manejo de fallas y errores tienen una importancia fundamental. La evaluación de esta cobertura también puede realizarse por modelado o por testing, usualmente llamado en este caso **inyección de fallas**.

Finaliza aquí el resumen de la terminología de *dependabilidad* introducida por Laprie. En el próximo apartado se presentan los antecedentes y las técnicas más usuales de inyección de fallas.

#### Capítulo 2

#### Técnicas de inyección de fallas

La inyección de fallas consiste en analizar el comportamiento de un modelo del sistema en presencia de fallas provocadas artificialmente. Usualmente los sistemas están modelados con diferentes niveles de abstracción [9][17] en cada una de las etapas del proceso de desarrollo. Así, en las etapas iniciales el sistema puede estar modelado con cadenas de Markov, redes de Petri o algún otro modelo analítico; más adelante se puede utilizar un modelo en nivel de transferencia de registros (RTL) para simular el sistema o, si el modelo es sintetizable, cargarlo en un FPGA y emular su funcionamiento; finalmente pueden inyectarse las fallas físicamente sobre un prototipo o un ejemplar del producto final. En este trabajo se ha incursionado en la inyección de fallas sobre modelos RTL del sistema, tanto sobre una simulación como sobre el circuito sintetizado en un FPGA.

A continuación se presentan los diferentes objetivos perseguidos al realizar experimentos de inyección de fallas. Luego se introduce el modelo FARM, una abstracción comúnmente utilizada para especificar y describir experimentos de inyección de fallas, y finalmente se hace un rápido repaso de ventajas, desventajas y principales antecedentes para cada uno de los mecanismos de inyección utilizados comúnmente

#### 2.1. Finalidades de la inyección de fallas

La inyección de fallas se utiliza con finalidades de ayuda al diseño y de verificación [10] [9] [17].

En etapas tempranas del desarrollo de un sistema es una herramienta útil para ejercitar los mecanismos de tolerancia a fallas en presencia de las fallas que supuestamente deben soportar. Esto permite detectar tempranamente imperfecciones de los mecanismos de tolerancia a fallas y de los procedimientos de test, e iniciar en consecuencia un ciclo de corrección y rediseño. En este contexto la inyección de fallas es una herramienta de **ayuda al diseño**, facilitando la **detección y remoción de**

fallas de diseño en los mecanismos de tolerancia a fallas y en los procedimientos de test.

La finalidad en este caso es identificar las fallas que escapan a los mecanismos de detección, caracterizar la gravedad de las consecuencias acarreadas por ellas y recoger información adicional que pueda ser útil para el rediseño. Es fundamental la repetibilidad de los experimentos, para verificar luego de introducida la corrección si esta fue efectiva.

La inyección de fallas es también una herramienta importante para pronosticar la frecuencia y gravedad de los malfuncionamientos que tendrá el sistema durante su operación (**predicción de fallas**). A esto contribuye ya que permite medir la **cobertura** de los procedimientos de verificación y los mecanismos de tolerancia a fallas con respecto al tipo de fallas inyectadas. La cobertura de un test es la fracción de las fallas que son puestas en evidencia por el mismo. El concepto es análogo para el caso de los mecanismos de tolerancia a fallas. Otro resultado de la inyección de fallas es la obtención de medidas de parámetros de funcionamiento del sistema, como los tiempos de latencia de errores y tiempos de activación de fallas.

La evaluación de la cobertura de los procedimientos de test y de los mecanismos de tolerancia de fallas por sí sola no es suficiente para evaluar otros atributos de la *dependabilidad*. Para estimar parámetros cuantitativos como tiempo medio entre fallas, disponibilidad, confiabilidad, hace falta además tener conocimiento de la distribución estadística de las fallas que se producen.

#### 2.2. Espacio de fallas (Fault Space)

Un enfoque interesante es ver a cada una de las fallas que pueden afectar a un sistema como puntos en un espacio multidimensional al que se le llama **espacio de fallas** (**FS**). Las dimensiones del espacio de fallas incluyen características temporales como el instante de ocurrencia y la duración de la falla (cuándo), indicación de cuál es el tipo de falla producido y eventualmente el valor asociado a la misma (cómo) y la ubicación dentro del sistema del elemento en el cual se produce la falla (dónde).

El espacio de fallas definido así busca modelar todas las fallas que pueden ocurrir en el sistema. Sin embargo es muy difícil obtener un modelo de fallas que sea completo en el sentido de cubrir todas las fallas posibles, y es también muy difícil demostrar que un modelo dado es completo. Por otra parte la dificultad y duración de un experimento de inyección de fallas evidentemente crece al ampliar el espacio de fallas.

Otro factor a tener en cuenta es la distribución estadística de la ocurrencia de cada tipo de falla. Si bien esta distribución es a menudo difícil de estimar, en muchos casos puede afectar fuertemente los resultados obtenidos.

Debido a la dificultad en estimar todos estos factores, a menudo se toman soluciones de compromiso con respecto al espacio de fallas a considerar. Sin embargo esto no debe olvidarse a la hora de valorar la aplicabilidad de los resultados a determinado sistema.

#### 2.3. Modelo FARM

El modelo FARM [9][17] para caracterizar a una serie de experimentos de inyección de fallas fue desarrollado en LAAS-CNRS a comienzos de los años 90. En este modelo los experimentos se describen a partir de cuatro conjuntos de entradas o salidas del sistema: el conjunto F (faults) lista las fallas que se van a inyectar al sistema; el conjunto A (activation) consiste en el conjunto de patrones de entrada suministrados al sistema bajo prueba; en cada experimento se inyecta una falla y se registra un conjunto R (readouts) de salidas; y finalmente a partir del análisis de los elementos de los tres conjuntos anteriores se deduce un conjunto M (measures) de medidas.

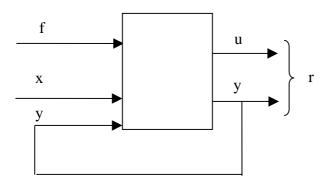

Fig. 3 Diagrama de bloques mostrando explícitamente a las fallas como una entrada.

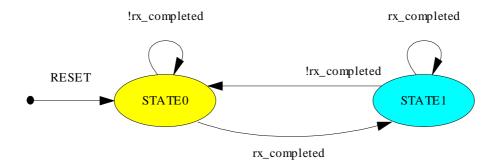

En el diagrama de bloques de la Fig. 3 se ha extendido el diagrama tradicional de una máquina de estados finita para indicar explícitamente a la falla a inyectar como una entrada.

El conjunto F es la lista de fallas a inyectar durante la serie de experimentos. Es sólo un subconjunto de las fallas posibles, seleccionado dentro del espacio de fallas FS que se haya modelado para el sistema.

La activación del sistema queda determinado por la secuencia de entradas externas x(t) aplicadas y el valor inicial yo del estado y del sistema en t=0, al inicio del experimento. Junto con las características del sistema bajo ensayo determina si una falla dada se activa produciendo un error o no, de ahí su denominación. El conjunto A está formado por la lista de las diferentes duplas (x(t), yo) que se utilicen en los experimentos.

En el conjunto R se registran tanto salidas externas **u** como estados **y**.

En el sistema ampliado para considerar explícitamente las fallas, una vez elegida la terna (x(t), yo, f) queda determinada la evolución de las salidas u(t) y de los estados y(t). El comportamiento del sistema puede verse como una transformación T entre un dominio de entrada formado por las posibles ternas (x(t), yo, f) y un dominio de salida formado por las correspondientes trayectorias de salidas y estados (u(t), y(t)). Cada terna determina un posible experimento de inyección de fallas.

$$T\{(x(t), yo, f)\} = (u(t), y(t))$$

A menudo para un conjunto de activación dado ( $x_a(t)$ ,  $yo_a$ ), se toma como referencia el experimento en el cual no se inyecta falla alguna. A este experimento se le llama "golden run". Una falla inyectada es activada durante un experimento si la trayectoria en el dominio de salida difiere de la registrada durante el experimento de referencia:

$$T(x_a(t), yo_a, f) != T(x_a(t), yo_a, fg)$$

; donde fg denota "ausencia de falla".

Una diferencia con la *golden run* indica que se produce un error, pero no necesariamente un malfuncionamiento del sistema. Dicho de otra forma, diferentes trayectorias en el dominio de salida pueden ser igualmente aceptables y mantener el servicio brindado por el sistema dentro de lo especificado. Cuando en una serie de

experimentos de inyección de fallas se clasifican las fallas de acuerdo al modo de malfuncionamiento que provocan, el conjunto M incluye predicados o aseveraciones cuyo resultado lógico indica si durante el experimento se produjo o no determinado malfuncionamiento [11] [41]. Este conjunto de aseveraciones en definitiva describe los *modos de malfuncionamiento* del sistema. Su elaboración es difícil de generalizar y exige conocimiento y análisis específico del sistema bajo prueba. Por ese motivo es una parte importante del esfuerzo de preparación de una serie de experimentos de inyección de fallas y es una de las principales dificultades para automatizar la generación de experimentos de inyección de fallas.

#### 2.4. Estimación estadística de cobertura de fallas

En este apartado se incluye una muy breve presentación de la estimación estadística de la cobertura de fallas a partir de experimentos de inyección, y en particular de la influencia de la distribución de probabilidad con que se seleccionan las fallas dentro del espacio de fallas sobre la estimación de la cobertura. Un análisis más completo puede encontrarse en [17].

Cuando se utiliza inyección de fallas para realizar un análisis cuantitativo, el parámetro básico a calcular es la cobertura de los mecanismos de tolerancia a fallas. Esta se define como la siguiente probabilidad condicional:

$C = P(Manejo \ adecuado \ de \ la \ falla \ | \ Ocurrió \ una \ falla \ del \ espacio \ FS)$

Representemos la ocurrencia de una falla con una variable aleatoria F con recorrido en el espacio de fallas FS, excluido el caso "ausencia de falla". Entonces la sumatoria de P(F=f) en todas las fallas f del espacio de fallas FS vale 1. Representemos también al evento "manejo adecuado de una falla" con otra variable aleatoria binaria Y(Y=1) si la falla se manejó de manera adecuada y Y=0 en caso contrario). Entonces la cobertura puede expresarse como el valor esperado de la variable Y:

$$C = \sum_{f \in FS} P(Y = 1 | F = f).P(F = f)$$

$$C = \sum_{f \in FS} y(f).P(F = f)$$

El primer factor valdrá 0 o 1 dependiendo de si la falla f está cubierta, de manera que para un sistema dado este factor puede representarse por una función fija y(f).

El segundo término representa la distribución de probabilidad de ocurrencia de las fallas dentro del espacio de fallas.

Si al realizar un experimento de inyección de fallas seleccionamos las mismas con una distribución de probabilidades diferente, entonces tendremos una nueva variable aleatoria F' con su correspondiente distribución P(F'=f). Se debe introducir una variable aleatoria binaria Y' diferente de Y para describir el evento "manejo adecuado de la falla durante el experimento de inyección de fallas". Al valor esperado C' de esta nueva variable aleatoria se le llama **cobertura forzada**.

$$C' = E[Y']$$

$$C' = \sum_{f \in FS} y(f).P(F' = f)$$

La distribución de F' es elegida al diseñar el experimento de inyección de fallas, mientras que la distribución de F es una característica del sistema bajo prueba. Tiene interés entonces estudiar la relación entre C y C' para ayudar a estimar el valor de C a partir de los resultados experimentales. En [17] se demuestra que:

$$C = C' + \rho$$

Dónde  $\rho$  es la covarianza entre la variable aleatoria Y' y el cociente entre la probabilidad real y la probabilidad forzada P(F = f) / P(F' = f), definido en cada punto del espacio FS. En [17] también se demuestra que el valor esperado de ese cociente es 1.

El valor de  $\rho$  puede ser positivo o negativo, y en consecuencia la cobertura forzada puede ser mayor o menor que la cobertura real.

Intuitivamente, la cobertura para la distribución de fallas real será mayor que la cobertura forzada (covarianza  $\rho$  positiva) si el mecanismo de tolerancia a fallas cubre mejor las fallas que son más probables en la distribución real que las fallas que son más probables en la distribución forzada. Esto muestra la importancia de modelar en

forma adecuada el espacio de fallas y su distribución de probabilidad ya que de lo contrario el resultado obtenido (la cobertura forzada) puede diferir de la cobertura de fallas reales tanto en más como en menos.

#### 2.5. Inyección de fallas por mecanismos Hardware

En la inyección de fallas por mecanismos hardware se dispone de un prototipo real del sistema en el cual se provocan fallas por medios físicos y se analiza el comportamiento posterior del mismo. En la mayoría de los casos la inyección de fallas por mecanismos hardware involucra la utilización de equipamiento de test externo para permitir la inyección de fallas y el registro y análisis de sus efectos. Por ese motivo este mecanismo suele ser más costoso que otros mecanismos.

Dado que se aplica sobre un prototipo o sobre un ejemplar funcionante del producto final, este mecanismo se utiliza en general en la fase de producción.

Se distinguen dos tipos de mecanismos [2]:

- Mecanismos hardware con contacto. En estos mecanismos el dispositivo inyector entra en contacto físico directo con el circuito bajo prueba. Ejemplos de estos mecanismos son la inyección de fallas a nivel de pines de circuito integrado, puntos de prueba en el circuito impreso o contactos de conector de una plaqueta.

- Mecanismos hardware sin contacto. En este caso el inyector no tiene contacto físico directo con el circuito, sino que a través de alguna fuente externa produce algún fenómeno físico que induce efectos parásitos dentro del circuito que modifican su comportamiento. Algunos fenómenos físicos utilizados son el bombardeo con partículas pesadas y la interferencia electromagnética.

En el caso de inyección con contacto los modelos de fallas más utilizados son las fallas "stuck-at", puentes entre contactos adyacentes, desconexión, etc.

Se utilizan técnicas de *forzado* o de *inserción*. En las técnicas de forzado el inyector se conecta directamente al terminal del circuito integrado o conector de que se trate sin desconectar nada en el circuito bajo prueba. En este caso la impedancia de salida del inyector debe ser muy baja de manera que el nivel lógico impuesto por el inyector

"domine" al nivel lógico impuesto por el circuito. Esto puede provocar corrientes mayores a las garantizadas en las salidas bajo prueba, con el consiguiente riesgo de dañar el circuito.

En las técnicas de inserción el dispositivo inyector se intercala entre salida y entrada. La complejidad mecánica y la manipulación necesaria para preparar un experimento son mayores, pero a cambio se disminuye fuertemente el riesgo de dañar el circuito.

Entre las ventajas de los mecanismos hardware de inyección de fallas podemos distinguir las siguientes:

- los experimentos se ejecutan a la velocidad real del sistema, por lo general mucho mayor que la velocidad de simulación.

- el sistema bajo test es por lo general el producto final o casi final. Por lo tanto se puede detectar y corregir las fallas de diseño introducidas en las fases finales de desarrollo y producción.

La lista de desventajas por su parte incluye:

- requiere equipamiento de test costoso.

- en el caso de inyección con contacto el riesgo de dañar el circuito es importante.

- con el crecimiento sostenido de los niveles de integración, la cantidad de puntos del circuito accesibles ya sea para observar o controlar (inyectar) se hace muy limitada.

- en el caso de inyección por interferencia electromagnética o por bombardeo con partículas pesadas es muy limitado el control sobre el instante y la ubicación exacta de la falla, y por lo tanto la repetibilidad de los resultados de un experimento.

Existen numerosos ejemplos de dispositivos diseñados para inyección de fallas a nivel de pines. Uno de los más conocidos es MESSALINE [9], un sistema para inyección de fallas a nivel de pines por la técnica de forzado desarrollado en LAAS-CNRS,

Francia. Un ejemplo más reciente es AFIT (Advanced Fault Injection Tool) [16] desarrollado por la Universidad Politécnica de Valencia, España.

#### 2.6. Inyección de fallas por mecanismos Software

Si el sistema bajo análisis involucra a un microprocesador entonces en muchos casos es conveniente utilizar el propio procesador del sistema para inyectar fallas o registrar sus efectos. De esta forma se puede realizar inyección de fallas implementada por software, técnica a menudo referida por la sigla en inglés SWIFI (SoftWare Implemented Fault Injection). Se utiliza este mecanismo tanto para inyectar fallas hardware (p. ej. introducir un bit-flip en un registro para emular una falla del tipo Single Event Upset) como fallas software (p. ej. la introducción de bugs por la vía de modificar el código).

La principal ventaja de la inyección de fallas por mecanismos software es el reducido costo, ya que no requiere equipamiento de test especial para su realización. Permite además tener acceso a detalles internos de la aplicación o del sistema operativo totalmente impensables con otros mecanismos de inyección de fallas.

Las desventajas de este mecanismo incluyen:

- la observabilidad y controlabilidad se limita a los elementos accesibles por el programador. La resolución en el eje de tiempos está limitada a los instantes de comienzo de las instrucciones de lenguaje ensamblador del programa bajo prueba. La ubicación de las fallas que es posible inyectar se reduce a los registros internos del procesador y la memoria externa. No es posible por ejemplo inyectar fallas en los Flip-Flops del bloque de control de la CPU. Tampoco es sencillo inyectar fallas en la memoria caché.

- Es muy difícil introducir fallas permanentes.

- En el caso de aplicaciones de tiempo real la inyección por mecanismos software puede ser inaceptablemente intrusiva, ya que la ejecución del software de inyección ocupa tiempo de CPU y puede por tanto impedir el cumplimiento de deadlines.

Existen varios ejemplos de sistemas que utilizan técnicas SWIFI, tanto para sistemas dedicados como para analizar aplicaciones corriendo en sistemas operativos comerciales. BOND [13] es un sistema para inyección de fallas en aplicaciones corriendo sobre sistemas operativos Microsoft desarrollado en el Politecnico di Torino, Italia. XCEPTION [14] es una herramienta SWIFI desarrollada en la Universidad de Coimbra, Portugal. MAFALDA [12] está orientada a aplicaciones de tiempo real con microkernels comerciales, desarrollado en LAAS-CNRS, Francia. FERRARI [8] es una herramienta para emular fallas y errores hardware en computadores Unix, desarrollado en la universidad de Texas, Austin, Estados Unidos.

## 2.7. Inyección de fallas sobre modelos de descripción hardware

Si se dispone de la descripción del sistema en algún lenguaje de descripción hardware (VHDL, Verilog) entonces puede realizarse la inyección de fallas o bien simulando el circuito o bien cargando en un FPGA un prototipo hardware sintetizado a partir del modelo del sistema. Al segundo mecanismo se le denomina a veces inyección de fallas por emulación (emulated fault injection). Se comentan a continuación las dos alternativas.

#### Inyección basada en Simulación

Para esta técnica de inyección de fallas es necesario disponer de un modelo del sistema bajo prueba que permita simular el comportamiento del mismo en presencia de fallas. Esta simulación puede realizarse en diferentes niveles de abstracción, por lo que esta técnica puede utilizarse en etapas tempranas del desarrollo como ayuda al diseño de los mecanismos de tolerancia a fallas. Se utilizan modelos en VHDL, Verilog u otros lenguajes que pueden ser desarrollados especialmente para la campaña de inyección de fallas o ser parte de las descripciones utilizadas para la especificación o síntesis del sistema.

Las ventajas principales de la inyección de fallas en simuladores VHDL o Verilog son:

Bajo costo al no ser necesario hardware de propósito específico.

- Puede utilizarse en etapas tempranas del diseño suministrando información útil para el diseñador.

- Alta observabilidad y controlabilidad, es posible observar o alterar el valor lógico de cualquier elemento interno del circuito en cualquier instante.

Como contrapartida, el tiempo de simulación es muy prolongado para cualquier circuito de tamaño razonable y el desarrollo de los modelos a menudo requiere un esfuerzo considerable. Por otra parte la inyección de fallas se realiza sobre la ejecución simulada de un modelo del sistema y no sobre un ejemplar del sistema final, por lo que no podrá activar fallas que se introducen o manifiestan en las etapas posteriores del desarrollo.

Existen varios caminos para inyectar fallas en la ejecución simulada del sistema bajo prueba. Un primer método consiste en modificar el valor lógico de un elemento interno del circuito mediante comandos del simulador utilizado. Esta técnica tiene la ventaja de ser poco intrusiva al no modificar el código del modelo del sistema. Tiene en cambio la desventaja de atar la implementación al simulador utilizado ya que los comandos de simulador son en general propietarios.

Otra alternativa es modificar el código del modelo para inyectar fallas y observar el comportamiento del mismo. En esta línea una posibilidad es el agregado de componentes a la descripción del circuito para permitir modificar (saboteurs) y observar (probes) el valor lógico de un elemento interno del circuito. Otra alternativa es introducir mutaciones en el código fuente de la descripción hardware del circuito. La variedad de mutaciones que se pueden introducir es amplia: reemplazar un componente en una descripción estructural (p. ej. cambiar un AND por un OR) o modificar estructuras de control en una descripción estructural (p. ej. reemplazar una condición por un valor fijo TRUE (stuck-then) o FALSE (stuck-else), perturbar el valor de una señal, etc.).

Por último, en el caso de modelos VHDL una técnica poco invasiva consiste en inyectar las fallas modificando la definición de los tipos de datos y las funciones de resolución de VHDL. De esta forma pueden definirse asignaciones adicionales a la señal que se desea perturbar que predominen sobre las asignaciones normales del diseño original.

Existen varias herramientas para modificar más o menos automáticamente el código de descripción hardware y realizar campañas de inyección de fallas basadas en simulación. MEFISTO [11] es un conjunto de herramientas desarrollado en colaboración por LAAS-CNRS, Francia (MEFISTO-L) y Chalmers University of Technology (MEFISTO-C) que utilizan casi todas las técnicas enumeradas. VFIT [15] es una herramienta desarrollada en la Universidad de Valencia, España, que utiliza las técnicas de mutaciones de código, saboteurs y comandos de simulador.

Durante el trabajo en esta tesis se realizó inyección de fallas basada en simulación utilizando la técnica de saboteurs sobre una red de nodos conectados por un bus CAN como se presenta en la sección 6.2 Ambiente basado en simulación. Los resultados fueron presentados en [22].

#### Inyección basada en Emulación

Si el modelo que se dispone es sintetizable, la inyección de fallas puede acelerarse en órdenes de magnitud por la vía de realizar la prueba sobre un prototipo hardware en lugar de en una simulación. Generalmente esto se hace sintetizando el circuito y cargándolo en un FPGA. Una ventaja adicional es que el sistema puede probarse en condiciones más similares a las de operación normal.

Para inyectar fallas sobre el prototipo hardware es necesario no solamente agregar los mecanismos para observar y perturbar las señales internas sino también para controlar el instante en que se inyecta la falla. Debido a eso las modificaciones que es necesario introducir al circuito son importantes y a menudo específicas para cada sistema.

En este trabajo se realizó inyección de fallas basada en emulación para acelerar el análisis del sistema citado en el apartado anterior [21] y sobre un sistema más complejo que reproduce el funcionamiento de los nodos embarcados en un automóvil durante una maniobra normalizada en la que se realiza un viraje en U [20].

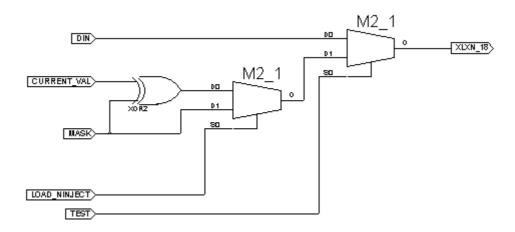

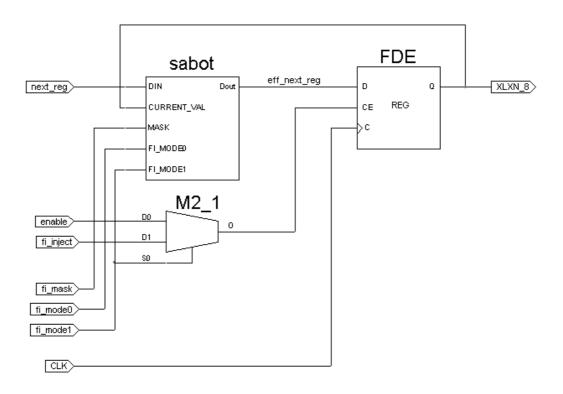

La técnica de inyección de fallas por emulación de circuito en prototipo hardware fue introducida en forma independiente en [3] y en [1] para inyectar fallas del tipo "stuckat". Otros antecedentes de esta técnica incluyen trabajos en el Politecnico di Torino [6] anteriores a las pasantías realizadas para esta tesis. En esos trabajos, para inyectar fallas del tipo "bit-flip" se modifica el circuito de la siguiente manera: para cada

elemento de memoria en el cual se desea inyectar fallas (FF1) se agrega un FF adicional (FF2) en el cual se almacena un "1" si se desea perturbar el elemento de memoria asociado y un cero en caso contrario. En el instante de inyección se conecta a la entrada de FF1 el exor entre su entrada original y el valor almacenado en FF2, complementando de esa manera el valor cargado si FF2 está activado. Los FF adicionales se conectan entre ellos en una cadena de registros de desplazamiento denominada "mask chain". Esta cadena de registros de desplazamiento se utiliza también para observar el valor almacenado en los elementos de memoria del circuito en un instante determinado.

## **PARTE II**

# PROTOCOLO CAN Y REDES A BORDO DE AUTOMÓVILES

Esta parte consta de dos capítulos. En el primero de ellos se presentan los aspectos del protocolo CAN que resultaron más importantes para el desarrollo del controlador y los experimentos de inyección de fallas.

Se presenta también un breve resumen sobre la utilización de redes de comunicaciones para interconectar las unidades electrónicas de control (ECUs) con que están equipados los automóviles en la actualidad. El objetivo perseguido en esta descripción es dar una idea de los requerimientos que se imponen sobre estos sistemas en aspectos como temporización, confiabilidad y posibilidad de consecuencias catastróficas de fallas, para ilustrar los criterios seguidos en la clasificación de malfuncionamientos en los experimentos descritos en la Parte III.

En ambos capítulos se busca además poner juntos conceptos y referencias recogidos durante los estudios realizados para la presente tesis, como forma de facilitar posibles estudios posteriores.

### Capítulo 3

#### Protocolo CAN

El protocolo CAN (Controller Area Network) fue desarrollado inicialmente por Bosch [37] [42] a mediados de la década del 80 y posteriormente fue normalizado como el estándar ISO 11898 en 1993. Ha sido utilizado por la industria automotriz para las redes a bordo de automóviles desde 1992.

#### 3.1. Breve descripción del protocolo CAN

Se brinda a continuación una breve descripción del protocolo. Descripciones más extensas pueden encontrarse en la propia especificación o p. ej. en [26].

CAN es un protocolo de múltiple acceso con detección de colisión no destructiva, resuelta por prioridades. La especificación define dos valores posibles para el estado del bus: recesivo y dominante. Si el bus es manejado simultáneamente por más de un nodo el valor dominante prevalece sobre el valor recesivo. Usualmente el valor recesivo está asociado al valor lógico "1" y el valor dominante al valor lógico "0", de manera que la lógica del bus puede interpretarse como un "and" cableado.

Los datos se intercambian en tramas que contienen un identificador (ID) y entre 0 y 8 bytes de datos. El campo ID de cada trama no identifica al nodo que envía el mensaje sino al tipo de mensaje. Es responsabilidad del diseñador de cada aplicación definir como se asignan los ID a las tramas generadas por los diferentes nodos del sistema.

Las tramas con información pueden ser de dos tipos: tramas de datos o requerimientos de transmisión remota (tramas RTR). Las tramas RTR solamente tienen encabezado y se utilizan para solicitar la transmisión de una trama de datos con el mismo identificador.

Existen dos formatos posibles para el encabezado de las tramas, que difieren en el campo ID y en algunos campos auxiliares de control. En el formato estándar el campo ID es de 11 bits. Este formato era el único disponible en la primera versión del protocolo. En el formato extendido en cambio, el campo ID está formado por la

concatenación del ID básico de 11 bits con el ID extendido de 18 bits, totalizando 29 bits.

Si se produce una colisión entre dos nodos que inician la transmisión de una trama al mismo tiempo, se utiliza un mecanismo de arbitración por prioridad para resolver el conflicto. Lo que se hace es ir comparando cada bit a medida que los contendientes escriben sobre el bus el campo ID y algunos bits adicionales del encabezado de la trama (IDE que indica el formato de ID y RTR que indica el tipo de trama), que conjuntamente se denominan campo de arbitración. A la primera diferencia en estos campos, el nodo que escribió un valor recesivo lo detecta porque lee del bus un valor dominante y debe retirarse de la contienda convirtiéndose en receptor. El nodo que puso el valor dominante sigue adelante con la transmisión sin notar siquiera que hubo un conflicto. El nodo perdedor podrá reintentar una vez finalizada la transmisión de la trama por el ganador.

El protocolo CAN fue desarrollado para ser utilizado en sistemas con fuertes requerimientos de confiabilidad, por lo que fue provisto con múltiples mecanismos de detección de errores:

- error de bit. Cada nodo cuando escribe sobre el bus verifica que se lea el mismo valor escrito. Existen un par de excepciones a esta regla (arbitración de prioridades, reconocimiento de recepción de trama).

- error de bit de relleno (stuff). el transmisor inserta bits de relleno para evitar secuencias de más de 5 bits iguales. Es un error si se reciben 6 bits seguidos iguales.

- error de CRC. El transmisor agrega al final de la trama un código de redundancia cíclica de 15 bits calculado sobre la trama completa incluyendo el encabezado.

- error de forma y error de reconocimiento. Se detectan cuando se recibe alterado el valor de algunos bits de formato fijo en la trama.

Un análisis detallado de los mecanismos de detección de errores de CAN puede encontrarse en [28].

Para procurar asegurar la consistencia de la información recibida por todos los nodos, si un nodo detecta un error debe escribir sobre el bus un valor dominante durante seis períodos de bit, forzando de esta forma un error de bit de relleno en el resto de los nodos conectados al bus. De esta manera la transmisión no se completa y el nodo transmisor deberá retrasmitir la trama. A esa secuencia de seis bits en valor dominante se le llama trama de error. Como se muestra más adelante, ese objetivo de asegurar la consistencia en la recepción de las tramas no siempre puede lograrse.

Existe un mecanismo de confinamiento de fallas para evitar que el bus se bloquee completamente en presencia de una falla permanente. Para eso cada nodo lleva la cuenta de la cantidad de errores recientes de transmisión y de recepción. En funcionamiento normal, un nodo se encuentra en el estado "activo frente a errores" ("error active") y su comportamiento frente a un error es el descrito líneas arriba. Si el valor de los contadores de errores supera un umbral predeterminado, entonces el nodo pasa al estado "pasivo frente a errores" ("error passive") en el cual el nodo puede seguir enviando y transmitiendo tramas pero se debe auto imponer las siguientes restricciones: a) luego de transmitir una trama debe esperar ocho tiempos de bit adicionales antes de intentar transmitir nuevamente, para permitir iniciar una transmisión a otros nodos; b) al detectar un error debe generar una trama de error especial sin escribir el valor dominante sobre el bus. Si se siguen detectando errores y los contadores superan un segundo umbral, entonces el nodo pasa al estado "bus off" en el cual no debe manejar el bus por ningún motivo. Se debe mantener en este estado hasta que observe el bus inactivo por un período prolongado preestablecido.

#### 3.2. Protocolos de capas superiores sobre CAN

Los sistemas distribuidos que utilizan un bus CAN en general pueden modelarse en un modelo simplificado de tres capas: física, enlace y aplicación. La especificación de CAN publicada por Bosch [42] se refiere solamente a las subcapas inferiores de la capa de enlace. Para la capa física existen varias alternativas en uso, siendo la más difundida la especificada en la norma ISO 11898-2 [51].

En el presente trabajo no fue utilizado ninguno de los protocolos existentes para la capa de aplicación. Se trabajó directamente sobre la especificación CAN de Bosch, se desarrolló un controlador CAN que la implementa y se ensayaron los mecanismos de

inyección de fallas en aplicaciones sencillas apoyadas directamente sobre los servicios provistos por el controlador CAN desarrollado.

Si bien no se profundizó en las soluciones en uso para implementar las capas superiores del modelo de referencia OSI, se listan a continuación algunas de las que aparecen referidas más a menudo.

En un inicio la mayoría de las soluciones fueron propietarias: cada fabricante implementó sus propios protocolos y reglas para solucionar problemas como el mapeo de las señales de la aplicación a las tramas CAN, el manejo de señales periódicas, la asignación de IDs a cada tipo de mensaje y la definición de primitivas de comunicación. Rápidamente aparecieron y se difundieron varios protocolos de uso más abierto.

Un ejemplo de estos protocolos para aplicaciones automotrices es el conjunto de estándares desarrollado por el consorcio OSEK/VDX [48] formado por fabricantes europeos de automóviles y partes, en particular el protocolo OSEK Communication [32]. En realidad OSEK Communication es un concepto mucho más amplio en que CAN es una de las posibles redes de comunicación.

Varios protocolos de capas superiores se utilizan en aplicaciones industriales. Uno de ellos es CANopen, desarrollado y gestionado por la organización CAN in Automation (CiA) [43]. CANopen define en forma estandarizada el mapeo de datos de la aplicación a varios tipos de "Data Objects", que luego envía como tramas CAN. Además de CANopen, en el sitio web de CiA se listan otros protocolos utilizados en aplicaciones industriales (CANKingdom [44], DeviceNet [47]).

#### 3.3. Dependabilidad y CAN

El protocolo CAN es un protocolo reconocido por sus buenas características desde el punto de vista de su robustez frente a fallas, y desde este punto de vista ha sido exhaustivamente estudiado por la academia y la industria. Esto ha permitido evaluar su influencia en la *dependabilidad*. Ha permitido también detectar varias debilidades que no pueden ser resueltas por CAN, y esto ha estimulado a buscar soluciones agregando funcionalidades en las capas superiores o desarrollando nuevos protocolos que probablemente desplacen a CAN a mediano plazo para algunas aplicaciones.

La mayoría de los trabajos sobre CAN se concentran en estudiar el efecto de errores en la comunicación: uno o varios bits en la trama invierten su valor. Las causas más estudiadas para estos errores son fallas a nivel del cableado del bus o del driver que fuerza un valor sobre el bus. Esto es totalmente razonable porque en un ambiente agresivo, sujeto a golpes y vibraciones como es un automóvil es esperable que por lejos las fallas de cableado sean las más frecuentes. Las herramientas desarrolladas en el presente trabajo permiten no solo inyectar fallas a nivel de capa física sino también a nivel de la lógica del controlador de acceso al bus. Si bien estas fallas son menos frecuentes sus efectos pueden también ser muy graves como se muestra en Parte III.

Muchos de los estudios y mejoras propuestas pueden agruparse como esquemas de cableado redundante para soportar cortocircuitos o falsos contactos en el bus. Algunas soluciones propuestas involucran replicar tanto el cableado físico como el controlador CAN, quedando por cuenta de la aplicación o de un árbitro decidir cuál es la réplica que falla en caso de diferencias. Una solución propuesta por Rufino [51] aprovecha el comportamiento de los niveles recesivo y dominante de CAN. Básicamente lo que propone es replicar solamente el medio físico y los drivers, y combinar en recepción con una compuerta AND los niveles recibidos. Es necesario agregar un temporizador y lógica adicional para detectar las fallas del tipo "stuck-at-dominant".

El protocolo CAN tiene algunos problemas que inicialmente no fueron advertidos. El mecanismo de forzar errores de relleno mediante tramas de error explicado en el apartado anterior procura garantizar que una trama es recibida en forma consistente por todos los nodos: o todos la reciben bien o se fuerza un error en todos los nodos para que la trama sea retransmitida. Este objetivo no se cumple si algún nodo recibe un bit erróneo en una posición precisa en el penúltimo bit del delimitador de fin de trama [25]. En ese caso se dan situaciones en que la trama no es recibida en forma consistente, ya sea por duplicación (algunos nodos reciben la trama dos veces) u omisión (algunos nodos no reciben la trama). Se dice entonces que CAN no es capaz de garantizar la propiedad de difusión atómica ("atomic broadcast") por sí solo, haciendo necesario agregar mecanismos para eso en capas superiores de protocolo. Un fenómeno interesante detectado en los experimentos de inyección de fallas realizados en el presente trabajo es que fallas del tipo "bit-flip" en registros del bloque

de control del controlador CAN provocaron el mismo efecto descrito más arriba [ver Parte III7.1].

Otro conjunto de debilidades reportadas del protocolo CAN tienen que ver con los mecanismos de confinamiento de fallas, pensado para identificar y aislar fallas permanentes. Navet y Gaujal muestran a través de un análisis de cadenas de Markov que en condiciones desfavorables pero realistas de interferencia en el bus es relativamente fácil entrar en el estado bus-off [52]. En otro trabajo [4] Navet sostiene que la principal debilidad desde este punto de vista es que los nodos deben diagnosticarse a sí mismos, y esto es imposible por ejemplo en caso de una falla en el oscilador del controlador CAN. El mismo argumento vale para fallas como las analizadas en el presente trabajo, que afecten al bloque de control del controlador CAN.

Otro grupo importante de trabajos y estudios relacionados con el protocolo CAN son los realizados desde la óptica de los sistemas distribuidos de tiempo real. Los trabajos en esta área estudian propiedades como la probabilidad de cumplimiento de *deadlines* y el establecimiento de cotas a los tiempos máximos de recepción de una trama en presencia de fallas; y el efecto sobre estas propiedades de la política de programación (scheduling) de los mensajes sobre el bus [7][27][29].

Desde este punto de vista es importantísimo el resultado señalado líneas arriba sobre la imposibilidad de garantizar "atomic broadcast". Han sido propuestos varias modificaciones a CAN y nuevos protocolos que procuran corregir estas debilidades. Varios de estos protocolos sustituyen el arbitraje por prioridad utilizado por CAN para resolver las colisiones en el acceso al bus por una política de evitar las colisiones a través de esquemas "Time Division Multiple Access" (TDMA). Estos protocolos se adaptan muy bien al intercambio de mensajes periódicos (que son la mayoría en aplicaciones automotrices) ya que el acceso al bus por cada nodo se realiza cíclicamente en slots de tiempo prefijados estáticamente en el diseño del sistema, simplificando en gran forma el cálculo de cotas para los tiempos de respuesta. A estos sistemas se les llama "Time-Triggered", mientras que a las redes como las del protocolo CAN clásico se les denomina "Event-Triggered". Varios de los nuevos protocolos propuestos son soluciones mixtas, que reservan una ventana de tiempo dentro del ciclo TDMA para el intercambio de mensajes no periódicos.

En la Time Triggered Architecture se desarrollaron algunos de los primeros protocolos de este tipo propuestos: Time Triggered Protocol en sus variantes de alta (TTP/C) [34] y baja (TTP/A) [35] velocidad. Estos protocolos fueron desarrollados por el Grupo de Sistemas de Tiempo Real de la Universidad de Tecnología de Viena liderado por Hermann Kopetz [50], e impulsados comercialmente por la empresa TTTech [49].

Bosch desarrolló una variante de CAN, denominada TTCAN (por Time-Triggered CAN) que tiene la virtud de ser relativamente compatible con CAN [36].

Finalmente, el protocolo FlexRay Communications Systems [31] es el más firme candidato a ser utilizado en aplicaciones automotrices con muy fuertes requerimientos de tolerancia a fallas [4]. Está siendo desarrollado por un consorcio de actores de la industria automotriz europeos y estadounidenses, incluyendo fabricantes de automóviles (BMW, DaimlerChrysler, GM, Volkswagen), de partes (Bosch) y de componentes electrónicos (Philips).

## Capítulo 4

#### Uso de redes a bordo de automóviles

Se presenta en este capítulo un muy breve resumen sobre la utilización de redes de comunicaciones para interconectar las unidades electrónicas de control (ECUs) distribuidas a bordo de los automóviles modernos. El objetivo perseguido en esta descripción es dar una idea de los requerimientos que se imponen sobre estos sistemas en aspectos como temporización, confiabilidad y posibilidad de consecuencias catastróficas de fallas, para ilustrar los criterios seguidos en la clasificación de malfuncionamientos en los experimentos descritos en Parte III. Se busca también poner juntos conceptos y referencias recogidos durante los estudios realizados para la presente tesis, como forma de facilitar posibles estudios posteriores.

Se advierte sin embargo que no es un tema en el que se haya incursionado a fondo. Para una revisión más extensa y muy actualizada de esta temática el lector puede referirse a un trabajo de Navet publicado recientemente [4].

#### 4.1. Sistemas electrónicos a bordo

Una tendencia sostenida en los últimos años ha llevado a que los automóviles actuales estén equipados con una cantidad importante de sistemas electrónicos con finalidades que van desde mejorar la seguridad de pasajeros y conductor, hasta asistir al conductor en determinadas maniobras o mejorar el confort a bordo.

Gradualmente más y más funcionalidades van pasando a ser realizadas por las denominadas Unidades Electrónicas de Control (ECUs) formadas por sensores y actuadores manejados por un microcontrolador. Inicialmente cada ECU era autónoma pero rápidamente se vio la ventaja de comunicar ECUs con funciones diferentes para poder compartir sensores para las señales compartidas, o de partir una función en ECUs diferentes para alivianar el cableado a sensores y actuadores. Esa red de comunicación entre ECUs rápidamente evolucionó de una topología en malla a una topología en uno o varios buses al aumentar la cantidad de ECUs utilizadas en un automóvil.

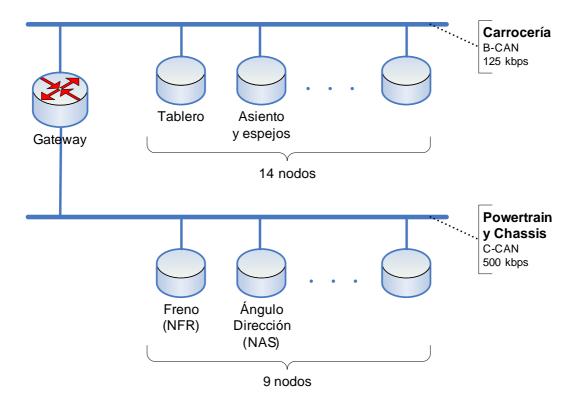

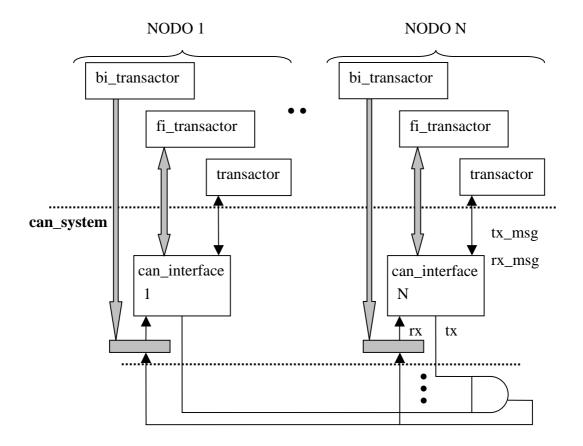

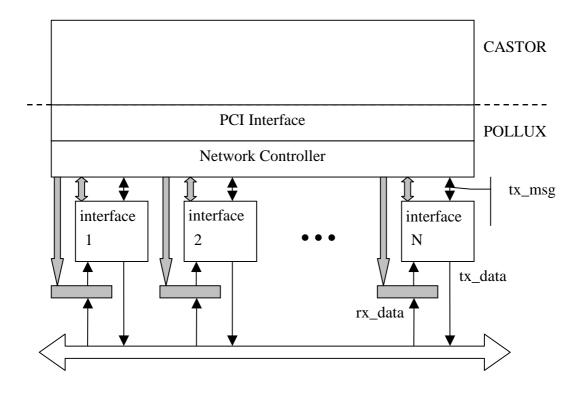

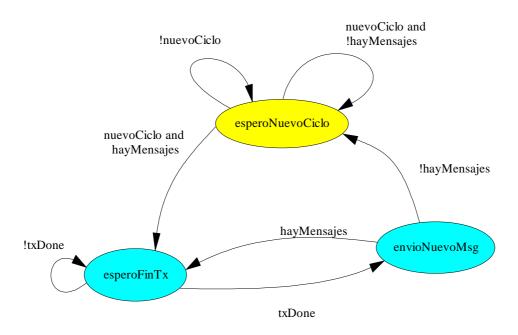

Según un trabajo citado en [4] algunos automóviles de lujo actuales llegan a tener unas 70 ECUs que intercambian unas 2500 señales diferentes. El modelo de automóvil en el cual se inspiraron las aplicaciones de ejemplo elaboradas para los experimentos de Parte III7.2 cuenta con 25 ECUs distribuidas sobre 2 buses CAN.