# Low Power Integrated LC Voltage Controlled Oscillator in CMOS Technology at 900MHz

Por

#### Rafaella Fiorelli

Tesis Presentada Ante el Instituto de Ingeniería Eléctrica Para Cumplir con Parte de los Requisitos del Grado de

# MAGISTER EN INGENIERÍA ELÉCTRICA En el Área de MICROELECTRÓNICA

Tutor:

Prof. Dr. Fernando Silveira

#### Tribunal:

Prof.Dr.Wilhelmus Van Noije, USP, Brazil Prof. Juan Mártony, UdelaR, Uruguay MSc.Julio Pérez Acle, UdelaR, Uruguay

> Instituto de Ingeniería Eléctrica Facultad de Ingeniería Universidad de la República Montevideo, Uruguay

> > December 2005

ISSN: 1510-7264

Type setted in LATEX  $2\varepsilon$

# Contents

| Lis | st of I | Figures                                                      | vi     |

|-----|---------|--------------------------------------------------------------|--------|

| Lis | st of T | Tables                                                       | ix     |

| Re  | sume    | n                                                            | Х      |

| Al  | strac   | t                                                            | xi     |

| Αg  | gradec  | cimientos                                                    | xiii   |

|     |         | $\operatorname{oduction}$                                    |        |

| 2.  |         | ysis and design of -Gm LC VCOs                               | 5      |

| ۷.  | 2.1     | Introduction                                                 | 5<br>5 |

|     | 2.1     | Principles and Topologies of -Gm LC VCO                      | 5      |

|     | 2.3     | Cross-coupled transistors block                              | 10     |

|     | 2.4     | Complementary cross-coupled -Gm LC VCO                       | 13     |

|     | 2.5     | Design Methodology                                           | 15     |

|     | 2.6     | Amplitude stabilization mechanism                            | 19     |

|     | 2.7     | Moderate inversion design                                    | 21     |

|     | 2.8     | Layout design and its consequences in the design methodology | 22     |

|     | 2.9     | Current Source design                                        | 24     |

|     | 2.10    | Final Design                                                 | 25     |

| 3.  | Phas    | se Noise in LC VCOs                                          | 33     |

|     | 3.1     | Introduction                                                 | 33     |

|     | 3.2     | Phase Noise Definition                                       | 33     |

|     | 3.3     | Review of existing Phase Noise Models                        | 34     |

|     |         | 3.3.1 Linear time invariant model                            | 34     |

|     |         | 3.3.2 A linear time varying phase noise theory               | 37     |

|     | 3.4     | Noise Sources                                                | 42     |

|     | 3.5     | Trade-offs in -Gm LC VCOs                                    | 44     |

|     | 3.6     | Phase Noise results obtained from simulation                 | 48     |

|     | 3.7     | Conclusions                                                  | 50     |

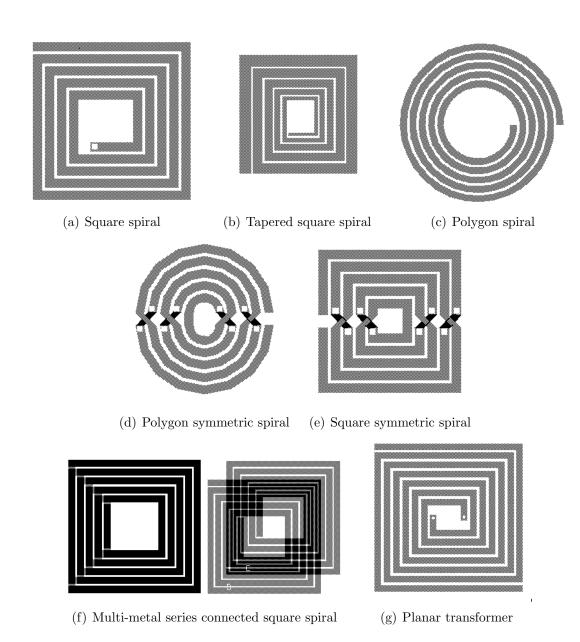

| 4. | Indu | ctors Design                                                  | 53 |

|----|------|---------------------------------------------------------------|----|

|    | 4.1  | Introduction                                                  | 53 |

|    | 4.2  | Inductor Types                                                | 53 |

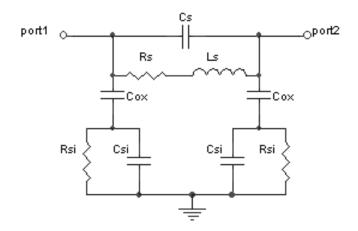

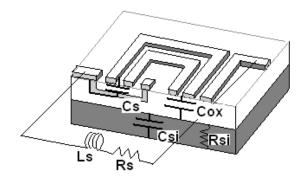

|    | 4.3  | Modelling                                                     | 54 |

|    | 4.4  | Inductor losses                                               | 58 |

|    |      | 4.4.1 Metal Losses                                            | 58 |

|    |      | 4.4.2 Substrate Losses                                        | 59 |

|    | 4.5  | VCO Phase noise and Inductor                                  | 60 |

|    | 4.6  | Simulation tools                                              | 61 |

|    | 4.7  | Inductor Design                                               | 63 |

| 5. | Vara | ctor Design                                                   | 69 |

|    | 5.1  | Introduction                                                  | 69 |

|    | 5.2  | Varactors topologies                                          | 69 |

|    | 5.3  | Quality factor and Parasitic Resistance of the I-MOS varactor | 75 |

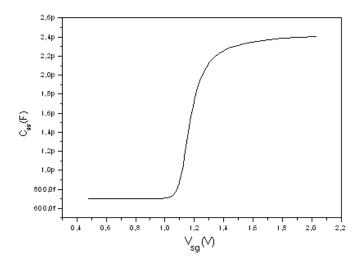

|    | 5.4  | Final Varactor Design                                         | 76 |

|    | 5.5  | Conclusions                                                   | 79 |

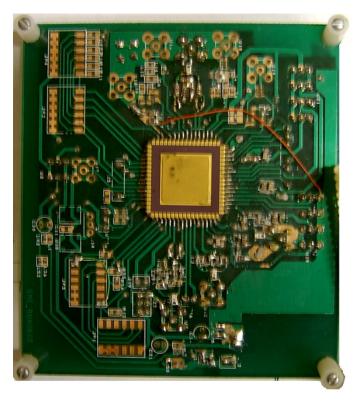

| 6. | Meas | surements                                                     | 81 |

|    | 6.1  | Introduction                                                  | 81 |

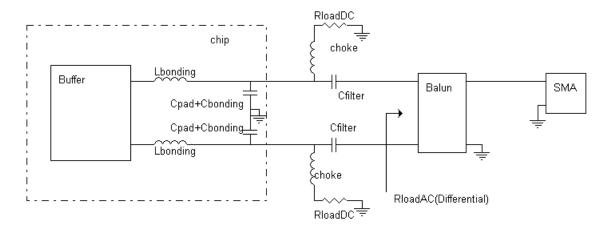

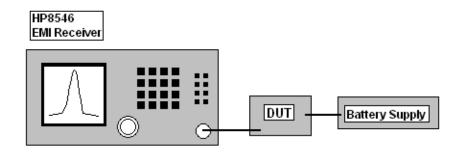

|    | 6.2  | Measurement Setup                                             | 81 |

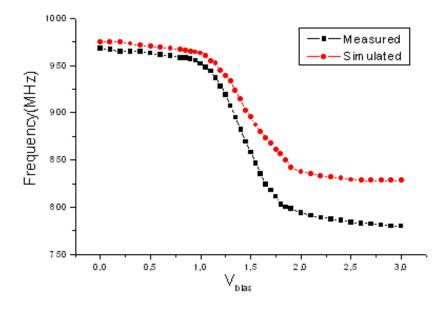

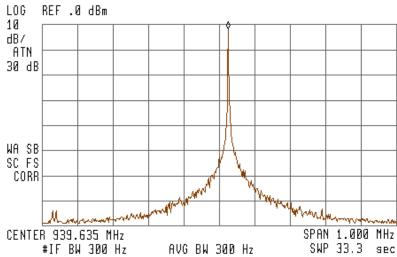

|    | 6.3  | PSD measurements                                              | 83 |

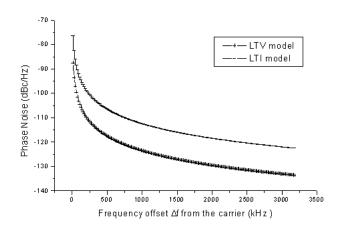

|    | 6.4  | Phase noise measurements                                      | 84 |

|    | 6.5  | Conclusions                                                   | 86 |

| 7. | Cond | clusions and Future Work                                      | 87 |

|    | 7.1  | Introduction                                                  | 87 |

|    | 7.2  |                                                               | 87 |

|    | 7.3  |                                                               | 88 |

|    | 7.4  | * -                                                           | 88 |

|    | 7.5  |                                                               | 88 |

|    | 7.6  |                                                               | 89 |

|    |      |                                                               |    |

| Α.  |        |                                                                                              | 1 |

|-----|--------|----------------------------------------------------------------------------------------------|---|

|     | A.1    | Relation between the bandwidth of the tank impedance and the tank quality factor             | 1 |

|     | A.2    | Phase Noise vs. the transconductance-to-current ratio 92                                     | 2 |

|     | A.3    | Equivalence between the inductor series resistance and the parallel resistance               | 2 |

|     | A.4    | Deduction of the $R_{si,ox}$ and $C_{si,ox}$ values                                          | 4 |

|     | A.5    | I-MOS varactor Gate capacitance versus $i$                                                   | 5 |

| В.  |        |                                                                                              | 7 |

|     | B.1    | Comparison of the phase noise performance of a all-nMOS LC VCO and of a complementary LC VCO | 7 |

| C.  |        |                                                                                              | 1 |

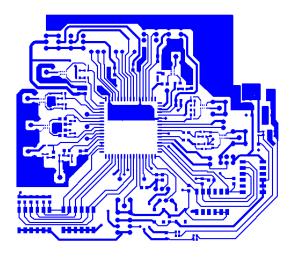

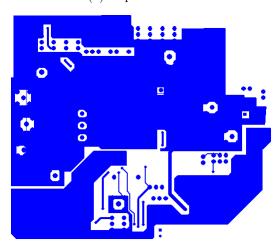

|     | C.1    | Layout of the PCB                                                                            | 1 |

| Bil | oliogr | eaphy                                                                                        | 4 |

# List of Figures

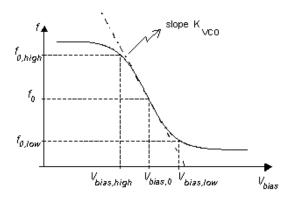

| 2.1  | Typical curve of the VCO frequency versus $V_{bias}$                                                          | 6  |

|------|---------------------------------------------------------------------------------------------------------------|----|

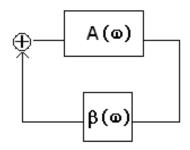

| 2.2  | Types of oscillator models                                                                                    | 7  |

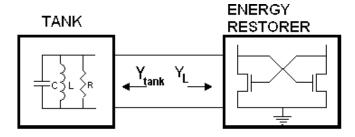

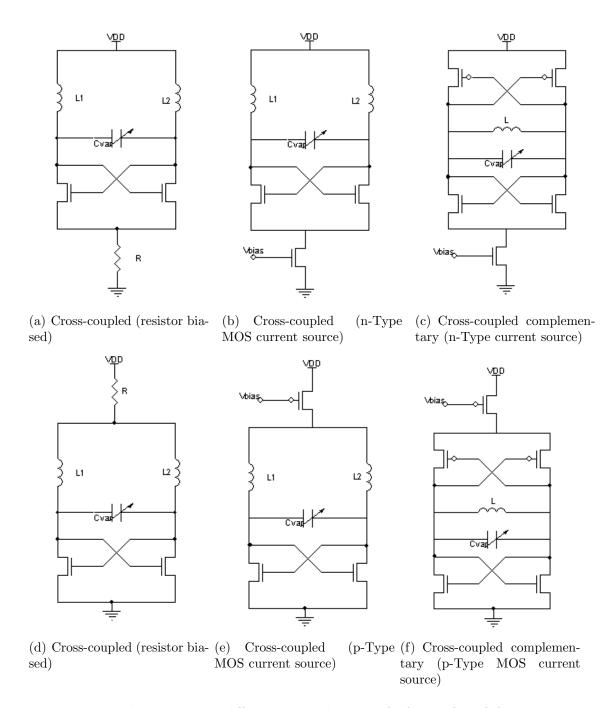

| 2.3  | Different topologies of -Gm LC VCO                                                                            | 9  |

| 2.4  | Small signal cross-coupled block models                                                                       | 12 |

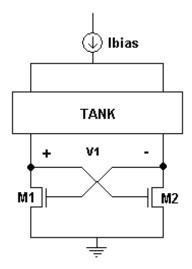

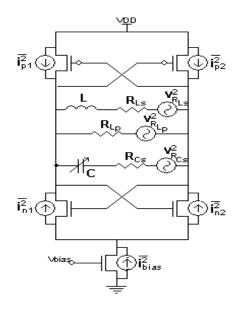

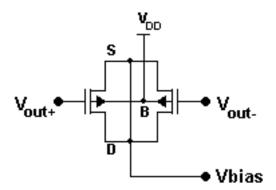

| 2.5  | Complementary VCO topology used in this work                                                                  | 13 |

| 2.6  | Small signal quasi-static cross-coupled complementary VCO model                                               | 14 |

| 2.7  | $g_m/I_D$ vs. $I_D/(W/L)$ measured and estimated                                                              | 16 |

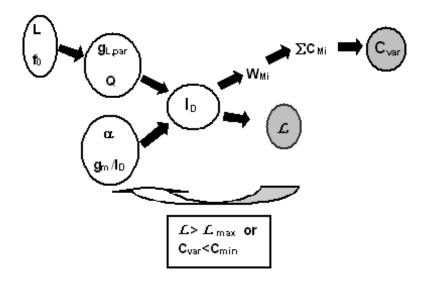

| 2.8  | Design methodology                                                                                            | 17 |

| 2.9  | Width of nMOS cross coupled transistors vs. $g_m/I_D$ and L                                                   | 18 |

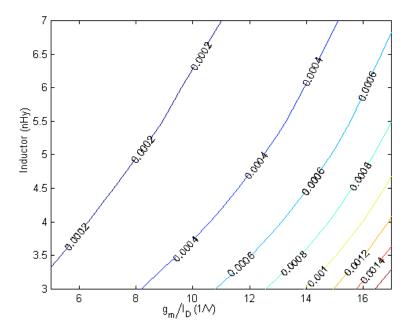

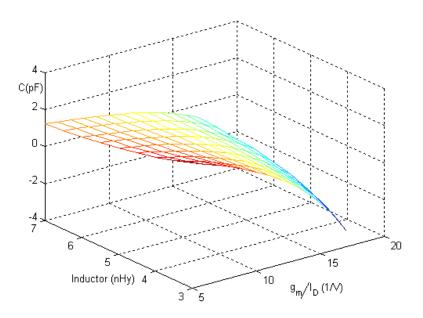

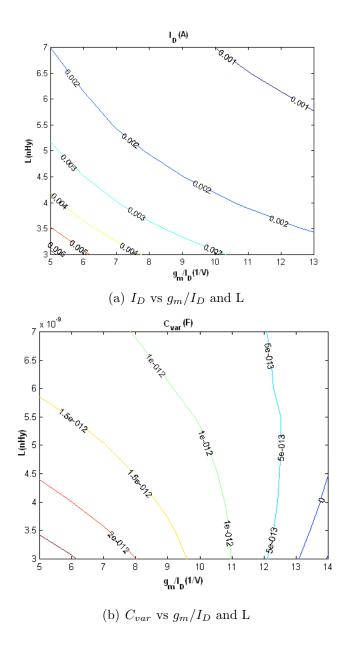

| 2.10 | Varactor capacitance vs. $g_m/I_D$ and L                                                                      | 18 |

| 2.11 | Amplitude stabilization mechanism in a -Gm block                                                              | 20 |

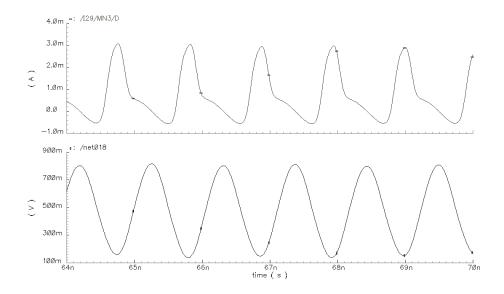

| 2.12 | Drain current of the VCO cross-coupled transistors vs. time                                                   | 20 |

| 2.13 | Drain current of the cross-coupled transistors and varactor capacitance versus $g_m/I_D$ and inductor value L | 27 |

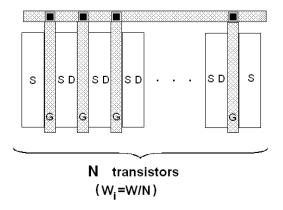

| 2.14 | Multi-fingered layout of a transistor with width W                                                            | 28 |

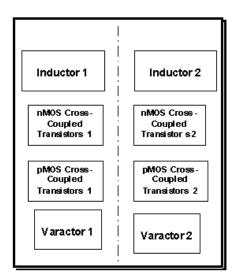

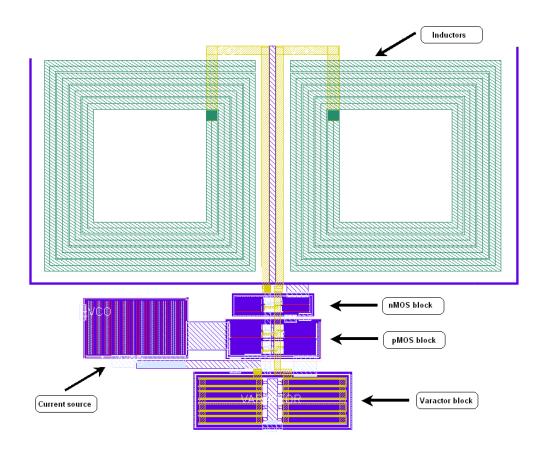

| 2.15 | Floorplan of the cross-coupled complementary -Gm LC VCO $$                                                    | 28 |

| 2.16 | Separate transistor layout and interlaced layout of the pMOS cross-coupled block                              | 29 |

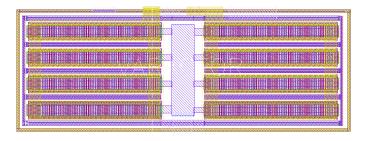

| 2.17 | Final varactor layout                                                                                         | 30 |

| 2.18 | Current source layout                                                                                         | 30 |

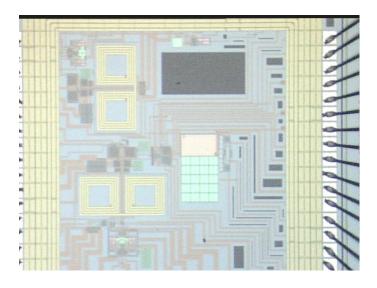

| 2.19 | Final layout of the fabricated VCO                                                                            | 31 |

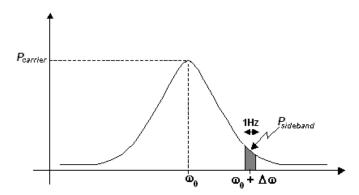

| 3.1  | Signal spectrum and SSB power                                                                                 | 34 |

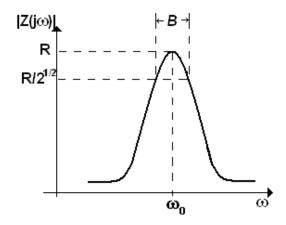

| 3.2  | RLC oscillator                                                                                                | 35 |

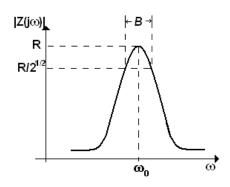

| 3.3  | Equivalent tank impedance value                                                                               | 35 |

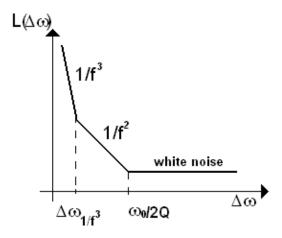

| 3.4  | Asymptotic graphic of Phase Noise                                                                             | 37 |

| 3.5  | Impulse responses of LC tank                                                                                                                          | 38 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----|

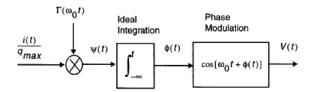

| 3.6  | Block diagram of the process                                                                                                                          | 40 |

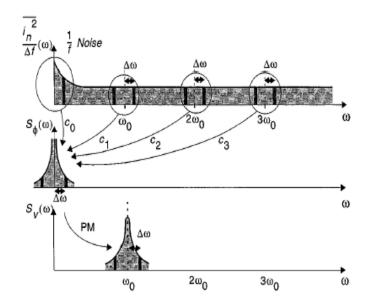

| 3.7  | Evolution of circuit noise into phase noise                                                                                                           | 41 |

| 3.8  | Differential and complementary VCO                                                                                                                    | 42 |

| 3.9  | Noise sources in a complementary differential LC-VCO oscillator                                                                                       | 43 |

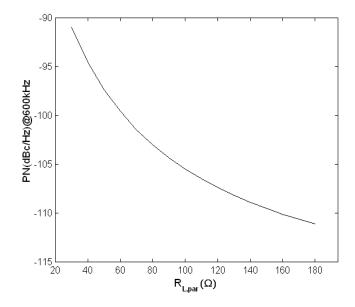

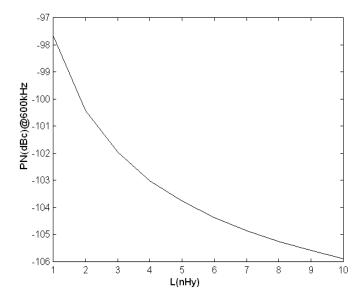

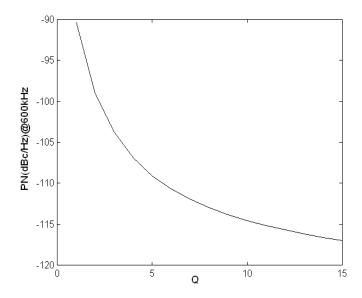

| 3.10 | Phase noise versus parallel tank resistance @ 600kHz from the carrier, considering a constant L                                                       | 46 |

| 3.11 | Phase noise versus Inductance @ 600kHz from the carrier, considering a constant Q                                                                     | 46 |

| 3.12 | Phase noise versus inductor quality factor Q @ 600kHz from the carrier, with a fixed L                                                                | 47 |

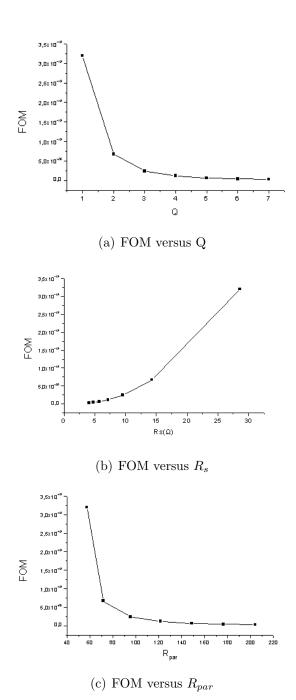

| 3.13 | Figure of Merit (defined in 3.38) versus Q, $R_s$ and $R_{par}$                                                                                       | 49 |

| 3.14 | Figure of Merit versus $g_m/I_D$                                                                                                                      | 50 |

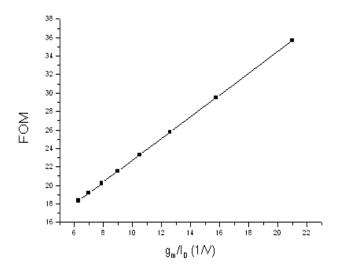

| 3.15 | Phase Noise vs. Inductance @600kHz offset from carrier for several gm/Id.                                                                             | 51 |

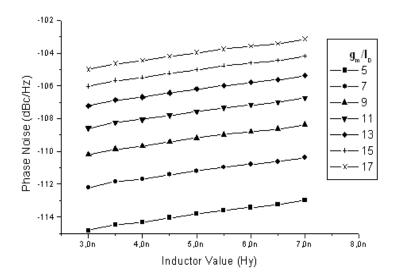

| 3.16 | Phase noise versus the offset frequency calculated with Matlab for the designed VCO, for the LTI and LTV models                                       | 51 |

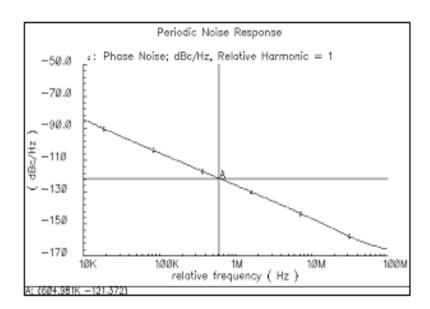

| 3.17 | Simulated Phase Noise in Cadence                                                                                                                      | 52 |

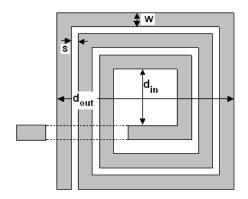

| 4.1  | Types of inductors' layout                                                                                                                            | 55 |

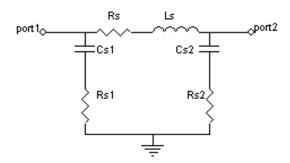

| 4.2  | $\pi$ net                                                                                                                                             | 56 |

| 4.3  | Monolithic inductor cross section view                                                                                                                | 56 |

| 4.4  | Inductor physical parameters                                                                                                                          | 57 |

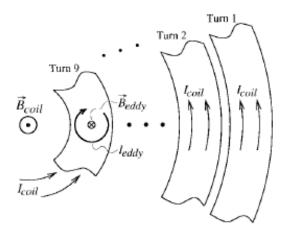

| 4.5  | Eddy currents                                                                                                                                         | 59 |

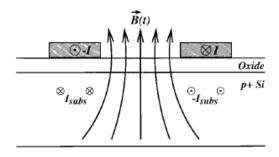

| 4.6  | Generation of substrate current on planar inductors                                                                                                   | 60 |

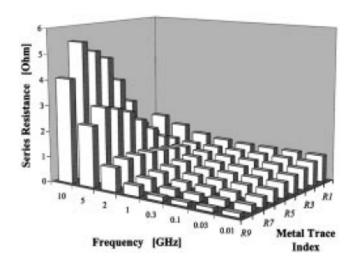

| 4.7  | Individual series resistance per metal trace                                                                                                          | 60 |

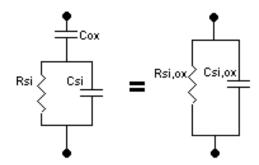

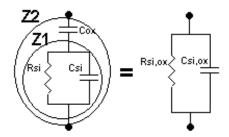

| 4.8  | Conversion of the configuration of $R_{si}$ , $C_{si}$ and $C_{ox}$ into a scheme of a capacitor $C_{si,ox}$ and a resistance $R_{si,ox}$ in parallel | 61 |

| 4.9  | $\pi$ -model used in the ASITIC program                                                                                                               | 62 |

| 4.10 | Scheme of the technology's layers                                                                                                                     | 64 |

| 4.11  | Technology data given to the RF inductor's modeler                                                                                                      | 64  |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

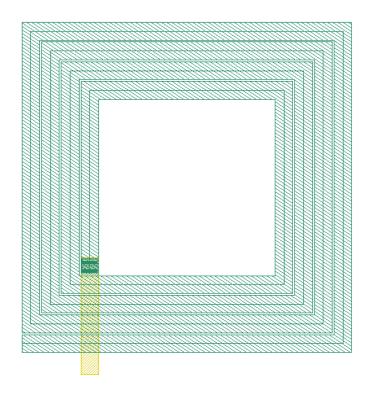

| 4.12  | Final layout design of the inductor                                                                                                                     | 65  |

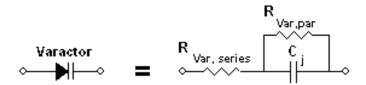

| 5.1   | Used symbol of the p-n varactor and its simplified model                                                                                                | 70  |

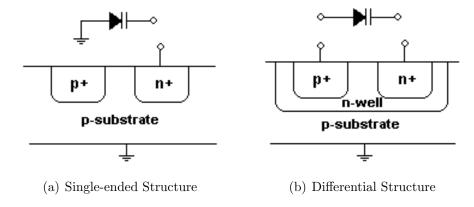

| 5.2   | Typical structures of p-n reverse bias diode                                                                                                            | 70  |

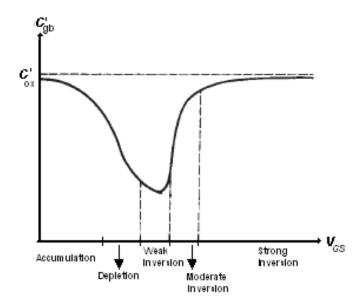

| 5.3   | Capacitance per unit area $C_{gb}^{'}$ versus $V_{GB}$                                                                                                  | 71  |

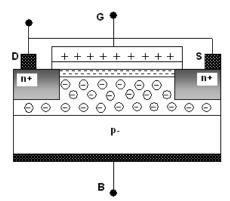

| 5.4   | Transistor MOS seen as a three terminal structure                                                                                                       | 72  |

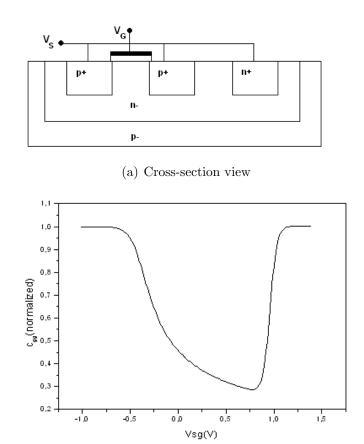

| 5.5   | Characteristics of the D-S-B structure                                                                                                                  | 73  |

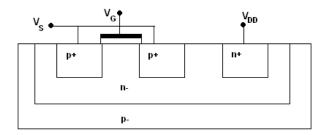

| 5.6   | Inversion-mode MOS                                                                                                                                      | 74  |

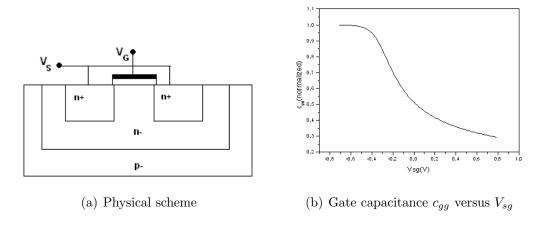

| 5.7   | Accumulation-mode MOS                                                                                                                                   | 75  |

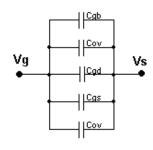

| 5.8   | Differential structure of two I-MOS varactors                                                                                                           | 76  |

| 5.9   | Inversion-mode varactor small-signal electrical model                                                                                                   | 77  |

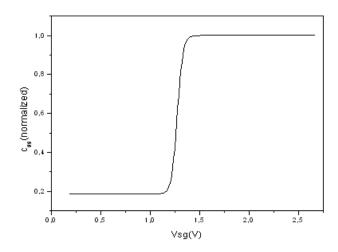

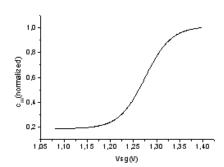

| 5.10  | Simulated $c_{gg}$ curve of both varactors                                                                                                              | 78  |

| 5.11  | Varactor Layout                                                                                                                                         | 80  |

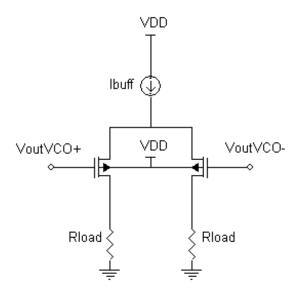

| 6.1   | Structure of the buffer used                                                                                                                            | 82  |

| 6.2   | Scheme of the buffer and its load (AC and DC load) as it is implemented in the PCB                                                                      | 82  |

| 6.3   | Measurement setup for PSD tests and Phase Noise tests                                                                                                   | 83  |

| 6.4   | VCO oscillation frequency versus $V_{bias}$                                                                                                             | 84  |

| 6.5   | Die-photograph containing the PLL and the isolated VCO                                                                                                  | 85  |

| 6.6   | VCO oscillation frequency versus $V_{bias}$                                                                                                             | 85  |

| A.1   | Equivalent tank impedance value                                                                                                                         | 91  |

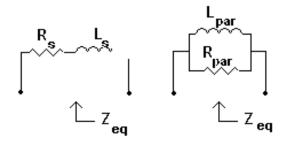

| A.2   | Equivalence of parallel circuit and series circuit                                                                                                      | 93  |

| A.3   | Conversion of the configuration of $R_{si}$ , $C_{si}$ and $C_{ox}$ into a scheme of a capacitor $C_si$ , $ox$ and a resistance $R_{si,ox}$ in parallel | 94  |

| B.1   | Comparison of phase noise performance of a all-nMOS and a differential LC VCO                                                                           | 97  |

| C.1   | Layout of the PCB                                                                                                                                       | 102 |

| $C_2$ | Final fabricated PCB                                                                                                                                    | 103 |

# List of Tables

| 1.1 | Published works of LC voltage controlled oscillators' design of the last few years    | 2  |

|-----|---------------------------------------------------------------------------------------|----|

| 2.1 | Bias current of each cross-coupled transistors versus $g_m/I_D$ and inductor L        | 21 |

| 2.2 | Capacitance of each varactor versus $g_m/I_D$ and inductor L                          | 22 |

| 2.3 | Final values of L and $g_m/I_D$ obtained from the implemented algorithm .             | 25 |

| 2.4 | Final values of several variables of the VCO design                                   | 26 |

| 4.1 | Values of the constants $K_1$ and $K_2$ (defined in [1])                              | 58 |

| 4.2 | Geometric parameters obtained with the function $\it optarea$ of ASITIC               | 65 |

| 4.3 | Parameters of the inductor calculated using the Yue's Model and the Mohan expressions | 66 |

| 4.4 | Parameters of the inductor calculated using ASITIC                                    | 66 |

| 4.5 | Parameters of the inductor calculated using RF Spectre Inductors' Modeler             | 66 |

| 6.1 | $K_{VCO}$ simulated and measured                                                      | 83 |

| 6.2 | Phase noise measured at $V_{DD} = 3V$ and $I_{bias} = 3mA$                            | 84 |

## Resumen

En este trabajo fue diseñado un oscilador controlado por voltaje tipo LC en la banda de 900MHz. Se usó una tecnología CMOS de  $0.35\mu m$ , se trabajó con inductores internos al chip y varactores MOS de inversión. Fue realizada una revisión de los modelos más importantes de ruido de fase en osciladores LC. Para optimizar el compromiso entre el ruido de fase y el consumo, el bloque de transistores cruzados fue diseñado para trabajar en la region de inversión moderada. La metodología de diseño presentada utiliza el modelo ACM y la metodología  $g_m/I_D$ . El oscilador controlado por voltaje finalmente diseñado tiene un consumo de corriente de 3mA con una fuente de voltaje de 3V y su ruido de fase medido es de -107dBc/Hz@1MHz. Estos resultados muestran que se alcanzó un buen compromiso entre el ruido de fase y el consumo del circuito.

# Abstract

In this work, a low power LC voltage controlled oscillator at the 900MHz band has been designed. A  $0.35\mu m$  CMOS technology, monolithic inductors and inversion MOS varactors have been used. A review of the most important models of phase noise in LC oscillators has been done. In order to optimize the trade-off between the phase noise and the consumption, the cross-coupled pair transistors were designed to work in the moderate inversion region. A design methodology using the ACM model and the  $g_m/I_D$  methodology is presented. The voltage controlled oscillator finally designed has a current consumption of 3mA with a 3V power supply and a measured phase noise of -107dBc/Hz@1Mz. Those results show that a good trade-off between phase noise and power consumption was reached.

# Agradecimientos

Me gustaría expresar brevemente mi más sincera gratitud a todas aquellas personas que, de una u otra forma, me apoyaron y ayudaron durante estos dos años. Sin ellas no hubiese podido realizar satisfactoriamente este trabajo.

Primeramente, deseo agradecer a mi tutor, el Prof. Dr.Fernando Silveira, por su invaluable guía a lo largo de todo este trabajo. Las fructíferas discusiones generadas y el apoyo brindado -tanto académico como humano- durante estos años fueron indispensables para haber llevado esta tesis de maestría a buen puerto. Sinceramente, muchísimas gracias.

Por supuesto que quiero agradecer a las demás personas que integran el Grupo de Microelectrónica: MSc.Pablo Aguirre, MSc.Leonardo Barboni, Ing.Pablo Mazzara, Ing.Linder Reyes e Ing.Conrado Rossi. Son muchísimos los momentos que necesité de su ayuda y siempre la obtuve.

Deseo agradecer también a todas las personas que trabajan el en IIE. Para los profesores, investigadores y personal no docente y para las secretarias (y sus chocolates), muchísimas gracias por hacer posible que algunos de nosotros podamos realizar posgrados en Uruguay.

Me gustaría agradecer a la Facultad de Ingeniería en su conjunto por haberme otorgado la beca de maestría. También agradezco a CSIC por haber apoyado financieramente mi pasantía en Bélgica.

Deseo expresar mi sincera gratitud a los integrantes del Laboratorio de Circuitos Integrados DICE de la Universitè catolique de Louvain la Neuve, en Bélgica, muy especialmente al Dr. Denis Flandre por permitirme trabajar durante tres meses en su laboratorio y a Laurent Vancaille y Bertrand Parvais entre muchos otros, por haber sido tan hospitalarios durante mi estadía en Bélgica.

Deseo agradecer al Prof. Dr. Silva Martinez y a Alberto Valdes-García de la Universidad Texas A&M de Estados Unidos por habernos brindado información muy valiosa sobre software de simulación de inductores, tan necesario para este trabajo.

Agradezco a la institución MOSIS a través de su programa MEP, por habernos permitido realizar chips de prueba al comienzo de ésta maestría.

Mi pasantía en Bélgica no hubiese sido tan interesante y enriquecedora si no hubiese tenido en gusto de conocer a dos personas tan especiales como son Gonzalo Picún y Silvia Rojas. Nunca sabré como pagarles por todo lo que hicieron por mí en esos meses. Muchas gracias.

Quiero agradecer de corazón a mis amigos. Siempre me han alentado a seguir adelante y se han interesado en lo que hago a pesar que aún no he sido capaz de explicarles claramente que he estado estudiando. Quiero nombrar especialmente a dos personas. A Denise Dalva por haberme acompañado incondicionalmente durante estos años. A Claudia Fumero, porque somos tan diferentes y tan iguales.

A mi novio Alfredo Arnaud. Alfre, tengo la gran suerte que tú, mi amor, entiendas lo que yo estudio. Te doy gracias por las infinitas horas del tiempo que me brindaste y que tanto me ayudaron. Te agradezco por haber estado junto a mi todos estos años. Definitivamente no hubiese llegado hasta aquí sin ti.

Quiero agradecer por último a mi familia: a mis adorados padres, Adriana y Reynaldo y al más genial de los hermanos, Enzo. Ellos me han dado la fuerza y el cariño que necesité para llegar hasta aquí. También agradezco a Florencia, la hermana que me regalaron de grande y a Chiche, la abuela que me regalaron de grande. A mis abuelos, porque sin ellos no estaría aquí y a Teco y Neca mis segundos padres.

Le dedico este trabajo a dos personas que no están aquí hoy pero que estoy segura estarían felices de ver hasta donde he llegado. A mi querida Maestra Elena, y a Valentín.

# Chapter 1 Introduction

The explosive growth in radio-frequency applications has resulted in an increasing demand of wireless devices such as transceivers, receivers and transmitters [2] [3] [4] [5] [6] [7] [8] [9] [10]. The applications where these devices are used are uncountable. They go from short to long range communications systems and from very low to very high bit rates (such as local area networks). Depending on the application is the requirements of the power consumption of the system; for example, for short range and low bit rate communications the power consumption might be low. Sometimes the application fixes the voltage source needed; if the devices must use battery power supply and must have autonomy of several years its power consumption must be of few microwatts. If the system can be supplied by the mains network the power consumption can be of the order of miliwatts or even more. From the previous discussion it is clear that the system requirements such as autonomy, range of communication or bit rates strongly condition the device design.

The work presented in this document is part of a design of a transmitter working in the band of 900MHz. It is intended that this transmitter works under most of the specifications of the IEEE 802.15.4 norm [11], whose applications are directed to very low power consumption and very low data bit-rates. These devices are usually attached to sensors of temperature, humidity, pressure, acceleration, chemical products among many others. They can log data coming from the sensors or from an external data source. They can be used in agronomy (as reporting the soil conditions or tracing the cattle), in cars (sending tires' pressure or the state of the brakes), in industry (monitoring the temperature or the humidity of a controlled process of difficult or almost impossible access ) and even at home.

One of the most important blocks of the transmitter is the phase locked loop (PLL) which fixes the channel frequency. A PLL is a system with a feedback loop where an oscillator is controlled in such a way that its output signal has same phase that the reference input signal. Its key block to obtain a good PLL performance is the Voltage Controlled Oscillator (VCO). This block has an internal device that modifies its characteristics with a change in an input voltage  $V_{bias}$ . When  $V_{bias}$  changes the VCO frequency oscillation is modified. The VCO features determine the good quality of the PLL obtained. The VCO studied for this thesis was part of a PLL, which is under test. It has been used a LC VCO (L represents the inductance and C the capacitance of the VCO). It was designed in a  $0.35\mu m$  standard CMOS digital technology. The oscillation is produced at the frequency at which L and C resonate. All the components of the VCO are on-chip, which means that it has monolithic inductors. We obtained a compact design with no need of external chip components. However, the standard CMOS technology used constrains the quality factor of the inductor obtained, which jeopardizes the performance of the VCO

| Reference | ${f Technology}$              | $\mathbf{Freq}$    | Phase Noise                              | Tuning Range | Consumption        | Inductors             | Varactors         |

|-----------|-------------------------------|--------------------|------------------------------------------|--------------|--------------------|-----------------------|-------------------|

| [12]      | $0.5\mu m \text{ CMOS}$       | $434 \mathrm{MHz}$ | -111dBc/Hz @600kHz                       | 1.6%         | $0.23 \mathrm{mA}$ | off-chip              | accumulation-mode |

| [13]      | $0.6\mu m \text{ CMOS}$       | $2.4\mathrm{GHz}$  | -118dBc/Hz $@1MHz$                       | 11%          | $9 \mathrm{mA}$    | on-chip               | inversion-mode    |

| [14]      | $0.25\mu m \text{ CMOS}$      | $4\mathrm{GHz}$    | -117dBc/Hz $@1MHz \parallel$             | 15%          | $3 \mathrm{mA}$    | on-chip               | new structure     |

| [15]      | $0.7\mu m \text{ CMOS}$       | $1.8\mathrm{GHz}$  | -116dBc/Hz @600kHz                       | 13%          | $4\mathrm{mA}$     | on-chip               | ?                 |

| [16]      | $0.35\mu m \text{ CMOS}$      | $2.4\mathrm{GHz}$  | -105dBc/Hz @100kHz                       | 14%          | $4.5 \mathrm{mA}$  | on-chip               | accumulation-mode |

| [17]      | $0.18 \mu m { m CMOS}$        | $5.3\mathrm{GHz}$  | -124dBc/Hz $@1\mathrm{MHz}$              | 10%          | $7.5 \mathrm{mA}$  | on-chip               | p+/n-well diodes  |

| [18]      | $0.65\mu m \ \mathrm{BiCMOS}$ | $2\mathrm{GHz}$    | -125dBc/Hz $@600 \mathrm{kHz} \parallel$ | 11%          | $19 \mathrm{mA}$   | on-chip               | p+/n-well diodes  |

| [19]      | $0.35\mu m \text{ CMOS}$      | $1.3\mathrm{GHz}$  | -119dBc/Hz $@600 \mathrm{kHz} \parallel$ | 28%          | $6\mathrm{mA}$     | on-chip and bond-wire | accumulation-mode |

| [20]      | $0.35\mu m \ \mathrm{BiCMOS}$ | $2\mathrm{GHz}$    | -117dBc/Hz @600kHz                       | 26%          | $4\mathrm{mA}$     | on-chip               | ?                 |

| [21]      | $0.25\mu m \text{ CMOS}$      | $1.8\mathrm{GHz}$  | -121dBc/Hz @600kHz                       | ?            | $2 \mathrm{mA}$    | on-chip               | ?                 |

|           |                               |                    |                                          |              |                    |                       |                   |

Table 1.1: Published works of LC voltage controlled oscillators' design of the last few years

1. Introduction 3

[22][23][24].

This kind of VCOs has been widely studied in the last years, and several publications have shown very interesting results on this matter. To show the state-of-the-art of this subject, it is given a summary of the most important works in Table 1.1. The benchmarks used to compare these works are: the phase noise reached at a certain frequency, the tuning range of the VCO, the current consumption and construction of the inductor on-chip or off-chip. The results depend also on the technology used, the working frequency and the kind of varactors implemented. In this summary the range of frequency given goes from 433MHz to 5.3GHz. We focused particularly on designing a VCO with the lowest possible current consumption without increasing too much the phase noise.

To design the VCO transistors the  $g_m/I_D$  methodology [25] was utilized. This unifies the treatment of all regions of operation, and with this it is obtained a relation between  $g_m/I_D$  and the normalized current  $I_D/(W/L)$ . It is found that the  $g_m/I_D$  curve is a common characteristic of all the transistors belonging to a same process.

The ACM model [26] has been the transistor model used to do the analytical computations. This physically based model describes all the operation regions with continuous, simple and accurate expressions. This kind of model was a necessity in our work as we were interested in studing the VCO transistors in all the operation regions, specially in the moderate inversion region. Combining the ACM model and the  $g_m/I_D$  methodology it is very easy to compute the transistor dimensions. The VCO initial specifications were the following:

- the technology must be a CMOS standard technology.

- the VCO will be used in a very low power consumption system so it must have a power consumption as low as possible.

- the supply voltage will be 3V but can drop to 2.4V (if two batteries of 1.2V are used).

- the phase noise of the PLL depends strongly on the phase noise of the VCO, so an acceptable value of the last one must be reached to fulfill as much as possible the IEEE802.15.4[11] requirements.

- the occupied area of the VCO is limited to  $600\mu m$  by  $600\mu m$  -it has been an arbitrary chosen value-.

- the tuning range must be at least 3.2%, because the band of 915MHz of the IEEE802.15.4[11] is 15MHz around 915MHz.

- it has to handle a load capacitance (coming from the other blocks of the PLL) of 0.6pF on each output port.

The summary of the contents of this work is as follows:

- Chapter 2: Analysis and design of -Gm LC VCOs In this chapter is studied the type of VCOs used. Various architectures are presented and it is discussed why the used topology is chosen. Also it is studied the mechanism of oscillation of these devices. The design methodology proposed in this work and the choice of transistors working in moderate inversion region is explained. Finally, a discussion on the design of the layout is given.

- Chapter 3: Phase Noise in LC VCOs The phase noise is a fundamental characteristic of the VCO. Two models -an empirical and a physical-based model-are described, showing the advantages of each one of them. The noise sources and the phase noise expressions of the topology used are given. A discussion of the trade-offs between the phase noise and the power consumption is presented. Finally, the values of the phase noise (calculated and simulated) are shown.

- Chapter 4: Inductors Design In this chapter several types of monolithic inductors are shown as well as some models to calculate its physical characteristics. The simulation tools used during this work are proposed. Finally, the inductor design methodology is described and the parameters of the final inductor used are shown.

- Chapter 5: Varactor Design In this chapter the most common topologies of varactors are presented and, specifically, the varactor topology used in this work is deeply studied. At the end, the final varactor characteristics are shown.

- **Chapter 6: Measurements** In this chapter the measurement setup is presented as well as the measured results.

- Chapter 7: Conclusions and Future Work

# Chapter 2 Analysis and design of -Gm LC VCOs

#### 2.1 Introduction

The voltage controlled oscillators (VCO) designed in CMOS technologies have become nowadays a real solution in the band of radio frequencies (from now on RF) because of having achieved low power consumption and low phase noise values.

Also the use of on-chip inductors is now acceptable in RF [15] [19] [18] [27]. In the band of 900MHz it has been also possible to design and use monolithic inductors despite its size [28]. In this frequency the size of the inductor increases because in an LC oscillator the oscillation frequency  $\omega_0$  is:

$$\omega_0^2 = \frac{1}{LC} \tag{2.1}$$

and if the frequency  $\omega_0$  decreases and the capacitor value is maintained constant the inductor value must increase.

In this chapter the principles and equations that governs the  $G_m$  LC VCO type will be studied. Various of its topologies are reviewed, putting particular attention in the complementary cross-coupled -Gm LC VCO, which is the one used throughout this work.

Also a VCO design methodology is presented using the equations that determine the VCO oscillation and the ACM CMOS transistor model [26]. This methodology is based on finding good trade-offs between power consumption and phase noise.

Another aim of this chapter is to show that at 900MHz the cross-coupled transistor block can work correctly in moderate inversion and that at this level of inversion the power consumption is improved without jeopardizing other characteristics of the VCO.

Finally the complete set of design parameters of the utilized VCO are presented.

# 2.2 Principles and Topologies of -Gm LC VCO

A VCO is an oscillator whose oscillation frequency -or working frequency- can be modified using an external bias voltage  $V_{bias}$ . It is very important the way the frequency of the VCO f varies when  $V_{bias}$  changes. If the curve f vs  $V_{bias}$  is as shown in Fig.2.1, some characteristics of the VCO can be defined. Firstly, there is a central zone of the curve where the frequency varies linearly with  $V_{bias}$  as shown with the straight line of Fig.2.1. The limits of the linearized zone are where the straight line begins to separate from the curve. The voltages where these limits occur are

Figure 2.1: Typical curve of the VCO frequency versus  $V_{bias}$

called  $V_{bias,low}$  and  $V_{bias,high}$  and correspond to the lower and higher frequency limits  $(f_{0,low} \text{ and } f_{0,high})$ . We define the VCO central frequency  $f_0$  as the frequency f when  $V_{bias} = (V_{bias,low} + V_{bias,high})/2$ . Another parameter defined in the VCO is the  $K_{VCO}$ , the tuning constant. It is determined by the tuning slope [29], and it is defined as:

$$K_{VCO} = \left| \frac{d(f(V_{bias}))}{d(V_{bias})} \right| \tag{2.2}$$

This expression can be approximated as:

$$K_{VCO} \approx \left| \frac{f_{0,high} - f_{0,low}}{V_{bias,high} - V_{bias,low}} \right|$$

(2.3)

In this work the element that changes its characteristics when the bias voltage changes is a varactor (a variable capacitor); it modifies its capacitance when its drain voltage  $V_D$  is modified ( $V_{bias} = V_D = V_S$ ). In Chap.5 a complete study of this structure will be done.

The kind of LC VCOs studied here are called Harmonic Oscillators because they are capable of produce an almost pure sinusoidal oscillation with good phase noise and spectral purity. <sup>1</sup>.

These oscillators can be modelled in two ways which are equivalent [30]: one is the feedback model and the other is the negative-resistance model. Both descriptions are equivalent and depending on the topology of the circuit is the one utilized.

The first model is shown in Fig.2.2(a) and consists of a forward block A(s) and a feedback block  $\beta$ (s). To work as an oscillator this circuit has to obey the Barkhausen criterion:

<sup>&</sup>lt;sup>1</sup>The phase noise represents the phase and frequency fluctuations of the VCO -the VCO noise-; thus the higher the phase noise the poorer the quality of the VCO. This will be studied deeply in Chap.3.

(a) Feedback model

(b) Negative-resistance model

Figure 2.2: Types of oscillator models

$$Re(A\beta) = 1 \tag{2.4}$$

$$Im(A\beta) = 0 \tag{2.5}$$

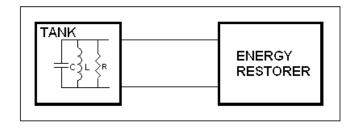

The other model is depicted in Fig.2.2(b); it has two blocks, one determines the frequency (tank) and the other is the active circuit (also called energy restorer). For this model the equation that has to be fulfilled is:

$$Y_L + Y_{tank} = 0 (2.6)$$

where  $Y_L$  is the admittance of the energy restorer and  $Y_{tank}$  is the admittance of the tank. From this expression the working frequency and the oscillation condition is obtained.

The tank filters the non-sinusoidal current signal coming from the active block and obtains in its terminals a sinusoidal voltage. As the tank has a non-zero resistance it losses energy and then the oscillation might disappear. To maintain the oscillation it is needed the active block (or energy restorer) that brings back the energy lost in the filter. Nevertheless, it also generates lot of harmonics in its output current, which are filtered in the tank. This model is called negative-resistance model because the energy restorer can be seen as a negative resistance that compensates the parasitic resistance of the tank.

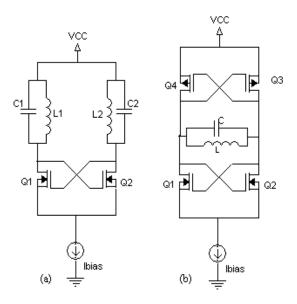

In this work the -Gm LC VCO is modelled as a negative-resistance oscillator. Its energy restorer comprises one or two blocks of two cross-coupled MOS transistors. They have the gate of one transistor connected to the drain of the other -and viceversa- and its sources are short-circuited. The conductance seen from the drains of the two cross-coupled transistor block is negative, as it will be shown later and its value is  $-Gm = -g_m/2$  (this is why those circuits are called "-Gm" oscillators). There is a direct dependence between the biasing of these transistors and the value of the negative resistance of the energy restorer in these oscillators.

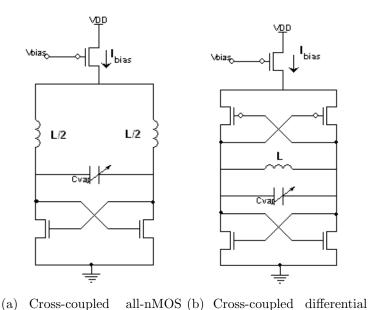

There are several topologies of -Gm oscillators, being the most common used the following ones (depicted in Fig.2.3).

#### 1. all-nMOS cross-coupled transistors with resistor bias.

The basic one consist of two nMOS cross-coupled transistors connected to the tank by its drains and biased by a resistor connected between the MOS sources and ground (GND) or between the tank and  $V_{DD}$ , as it is shown in Figs.2.3(a) and 2.3(d). A variant of this topology is the circuit without the resistance. The drawback of this topology is the direct dependence of the properties of the circuit with the voltage source's fluctuations and technology parameter variations (for example the  $V_{GS}$  voltage modifies the bias current). It can be seen specially in the non-constant value of the bias current throughout a complete cycle, which can lead to an increment in the phase noise with respect to other topologies if the resistance value is not well chosen [31].

#### 2. all-nMOS cross-coupled transistors structure with MOS current source.

It is a variant of the previous topology but instead of a resistor bias it uses a MOS current source. In Fig.2.3(b) it is depicted the nMOS source and in Fig.2.3(e) it is the pMOS source.

3. Cross-coupled complementary topology. It is composed by two blocks of cross-coupled pair transistors -pMOS and nMOS- and an MOS current source. In Fig.2.3(c) it is the one with an nMOS source and in Fig.2.3(f)it has the pMOS source.

In [32] it is shown that the second topology has worse results in terms of phase noise that the third one (a brief explanation of this matter is given in App.B.1).

In the third structure both blocks are designed to have the same transconductance value, which means that each nMOS and pMOS transistor has the same transconductance  $(g_{m,p} = g_{m,n} = g_m)$ . In this case the total negative resistance  $-G_m$  of both blocks is

$$-G_m = -2 \cdot g_m / 2 = -g_m \tag{2.7}$$

Figure 2.3: Different topologies of -Gm LC VCO

However, the addition of two more transistors -specially the p-MOS onesraises the value of the parasitic capacitance which might be a problem in the design. Also this topology cannot scale down to lower the supply voltage compared with the all-nMOS cross-coupled topology because it uses an extra  $V_{gs}$ . On the other hand as in the all-nMOS structure the dc value of the drain voltage is almost  $V_{DD}$ , the dc voltage drop across the channel is larger than in the complementary VCO, which can lead to stronger velocity saturation [21].

A topology which has not been shown in Fig.2.3 is the one that uses a cross-coupled p-MOS transistor block instead of a n-MOS one. As it is studied in [17] the all-pMOS topology with pMOS current source has a little better performance respect of the all-nMOS structure with nMOS current source.

The pMOS current source that is used in the second and third structures fixes the bias current of the VCO independent of the supply voltage. As the current source adds phase noise to the VCO and the pMOS transistors have better flicker noise figures, in this work it has been used the pMOS transistors to build the the current source.

In our design we have chosen the cross-coupled complementary topology ( see Fig.2.3(f)) to design our VCO.

### 2.3 Cross-coupled transistors block

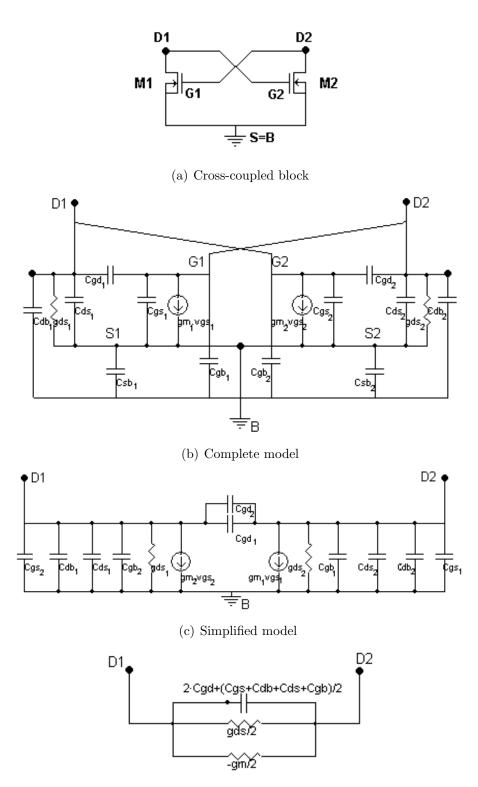

To study the operation of the VCO it is needed to know how the cross coupled transistors block works. To do that, we will study this block using the small-signal model for the transistors. In this study -as depicted in Fig.2.4(a), their common source has a constant voltage value because the circuit has a symmetrical structure (the transistors are considered identical) and the output voltage (the voltage between its drains) is differential. Then this point is considered virtual ground at small-signal.

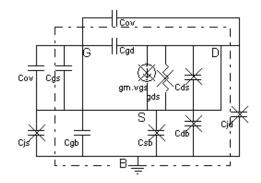

The transistor model used is the quasi-static model five intrinsic capacitance model which considers the capacitances  $C_{gd}$ ,  $C_{gs}$ ,  $C_{db}$ ,  $C_{gd}$ ,  $C_{gb}$  [33]. It has been also considered the capacitance  $C_{ds}$ . In the used model there are not considered the channel resistance, the gate intrinsic resistance and the transconductance delay [34] [35]).<sup>2</sup>

The extrinsic capacitances are also considered in the study. In Fig.2.4(b) is the small-signal model of the block. The overlap and junction capacitances are included together with the intrinsic ones, despite they are not explicitly mentioned in the scheme).

As bulk and source voltages are *virtual ground*, the capacitances  $C_{sb}$  are short-circuited in the small-signal operation, being the resulting circuit the one shown in Fig.2.4(c).

Since the transistors, their bias current and their capacitances are considered identical; and as the gate of one transistor is crossed with the drain of the other; a

<sup>&</sup>lt;sup>2</sup>The designed nMOs transistors work below the quasi-static limit, the pMOS are a bit over that limit.

simple differential model of the block can be obtained (see Fig.2.4(d)). The capacitance  $C_{gd,1}||C_{gd,2}$  is split in two capacitances in series of value  $2 \cdot (C_{gd,1}||C_{gd,2})$  and the middle point can be considered as virtual ground. Then it is possible to have all the capacitances of the circuit in parallel and to obtain the equivalent capacitance seen by the drains of the transistors, whose value is:

$$C_{eq,-Gm} = 2C_{gd} + \frac{(C_{gs} + C_{db} + C_{ds} + C_{gb})}{2}$$

(2.8)

To explain the transformation of the transconductance of the transistors into a negative resistance shown in Fig.2.4(d) lets take the transistor M1 of Fig.2.4(a). The gate-source voltage of M1 is the drain-source voltage of M2, then  $g_{m,1}v_{gs,1} = g_{m,1}v_{ds,2}$ . As  $v_{ds,1} = -v_{ds,2}$  (because of the differential output voltage) then  $g_{m,1}v_{gs,1} = -g_{m,1}v_{ds,1}$ . Not considering the capacitances and the conductance  $g_{ds}, -g_{m,1}v_{ds,1}$  is the current going through  $v_{ds,1}$ , then  $-g_{m,1}$  can be seen as a negative resistance between drain and source.

Then the total equivalent conductance of this block is:

$$G_{eq} = -\frac{g_m}{2} + g_{ds} (2.9)$$

Assuming that in the bias point the transistor is in the saturation region,  $g_{ds} \ll g_m$  and then:

$$G_{eq} \cong -\frac{g_m}{2} = -G_m \tag{2.10}$$

Using the ACM transistor model [26], the expression of the  $C_{eq,-Gm}$  in saturation is:

$$C_{eq,-Gm} = 2 \cdot C_{ov,gd} + \frac{C_{ov,gs} + C_{jd,db}}{2} + \frac{(n-1)C_{ox} + \left(\frac{2}{3}C_{ox}(\sqrt{1+i}-1)\frac{\sqrt{1+i}+2}{(\sqrt{1+i}+1)^2}\right)}{2n}$$

(2.11)

where n is the slope factor [36], slightly dependent on the gate voltage, greater than one and usually smaller than two. i is the normalized current [26]:

$$i \cong \frac{I_D}{I_S} \tag{2.12}$$

and

$$I_S = \mu n C_{ox} \frac{U_t^2}{2} \frac{W}{L} \tag{2.13}$$

where  $\mu$  is the carrier mobility,  $C_{ox}$  is the oxide capacitance per unit area,  $U_t$  is the thermal voltage and W and L are the width and length of the transistors.

(d) Equivalent simplified model

Figure 2.4: Small signal cross-coupled block models

Figure 2.5: Complementary VCO topology used in this work

## 2.4 Complementary cross-coupled -Gm LC VCO

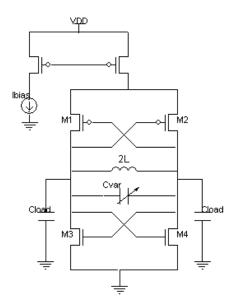

As it has been already said, the VCO used in this work is the complementary cross-coupled -Gm LC VCO with a pMOS current source (see Fig. 2.5). We have decided to work with a complementary topology because of its very good phase noise response with respect to the one that uses a nMOS pair. We also used a pMOS current source because the 1/f noise of pMOS is generally found to be less than for an nMOS one with the same dimensions (a deeper study of the phase noise subject will be done in Chap.3).

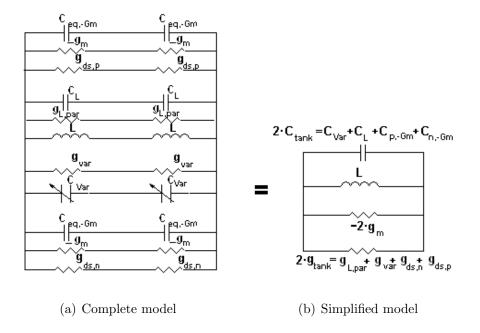

The physical model of this VCO topology considering the cross-coupled block model and the parasitics of the varactor and inductor is shown in Fig.2.6(a). The inductor value is L and it has associated a conductance  $g_{L,par}$  and a capacitance  $C_L$ . The varactor's capacitance is  $C_{var}$  and its associated conductance is  $g_{var}$  (its inductance is neglected) -the parasitics of the inductor and varactor are studied in Chaps. 4 and 5-. The tank conductance is:

$$2g_{tank} = g_{L,par} + g_{var} + g_{ds,n} + g_{ds,p} (2.14)$$

In Fig. 2.6(b) is the simplified model of this circuit.

This circuit oscillates when the Eq.2.6 is met. If this equation is separated in the imaginary and real part, are obtained the following two equations:

$$2 \cdot g_m = g_{tank} \cong g_{L,par} \tag{2.15}$$

and

$$f_0 = \frac{1}{2\pi\sqrt{L \cdot C_{tank}}} \tag{2.16}$$

Figure 2.6: Small signal quasi-static cross-coupled complementary VCO model

with

$$C_{tank} = C_{Var} + C_L + C_{n,-Gm} + C_{p,-Gm}$$

(2.17)

As the VCO is usually loaded with a non-negligible capacitance  $C_{load}$  (see Fig. 2.5) this must be taken into account in the  $C_{tank}$ :

$$C_{tank} = C_{var} + C_L + C_{n,-Gm} + C_{p,-Gm} + C_{load}$$

(2.18)

The condition of oscillation is (see Eq. 2.15)

$$g_m \ge g_{tank}/2 \tag{2.19}$$

Consequently, when a VCO is designed, it is usual to take a more conservative relation between the  $g_m$  and the tank conductance using the oscillation factor  $\alpha$ :

$$2 \cdot g_m = \alpha \cdot g_{tank} \tag{2.20}$$

The oscillation factor has an arbitrary value, usually equal to 3 (which is considered conservative). This factor gives security to the design; if it is considered almost 1, it is probable that the current value would be lower but it is also probable that the oscillator does not start because of the spread in the value of the VCO components. In the Sec.2.6 there will be a deeper explanation on this matter.

Usually the conductances  $g_{ds}$  and  $g_{var}$  are low enough respect of the  $g_{L,par}$  to be neglected.

## 2.5 Design Methodology

The design methodology presented here can be used in any of the VCO topologies shown previously, but it is focused on particularly the cross-coupled complementary -Gm LC VCO.

The specifications of the VCO are very related with the system in which it is part. The VCO designed here will be part of a Phase Locked Loop (PLL), whose specifications of power and phase noise are rigorous so that it can be used in communication circuits (as transmitters and receivers) which fulfill the IEEE 802.15.4 standard. The VCO can modify substantially the phase noise or power consumption values [37] of a PLL. Thus, one of the most important VCOs specifications are the maximum power consumption and the maximum phase noise (and sometimes the minimum peak output voltage).

As this VCO has on-chip inductors and these take substantial silicon area, the total VCO area is usually an important fraction of the total area of the system in which it is embedded. For this reason, the maximum VCO total area is also specified. The on-chip inductors are strongly conditioned by this requirement.

The VCO physical parameters to be found in the design flow are: the inductance value and its parasitics, the varactor's value and its characteristics, the size of the pMOS and nMOS transistors and the size of the bias current pMOS transistors. It has to be considered the parasitics of the layout in the design -usually capacitances at the working frequencies- and the load capacitance  $C_{load}$  of the load of the VCO.

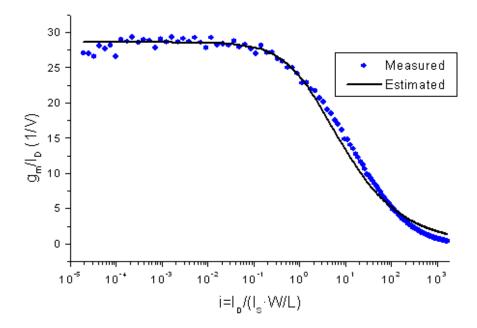

One important design parameter used in this methodology is the transconductance-to-current ratio  $g_m/I_D$  [25]. This ratio can be expressed in terms of the normalized current i (Eq.2.12) [33]:

$$\frac{g_m}{I_D} = \frac{2}{nU_t(\sqrt{1+i}+1)} \tag{2.21}$$

As  $i = I_D/I_S$  and  $I_S \propto W/L$  then

$$i = k \cdot I_D / (W/L) \tag{2.22}$$

with

$$k = \frac{2}{\mu n C_{ox} U_t^2} \tag{2.23}$$

It means that  $g_m/I_D$  can be plotted versus  $I_D/(W/L)$ . This curve is a characteristic curve that depends only on the technology. Particularly this characteristic curve is very useful as it relates the transistor  $g_m/I_D$  with  $g_m$  knowing the drain current  $I_D$  (and viceversa); or relates the transistor aspect ratio W/L with  $g_m$  knowing  $I_D$ . Its typical behaviour is showed in Fig.2.7, where it is plotted the measured characteristic curve of  $g_m/I_D$  of the nMOS transistor  $0.35\mu m$  technology.

The technology used also determines the characteristics of:

• the inductance: its value L, the quality factor Q, the resistive losses  $R_{L,par}$ .

Figure 2.7:  $g_m/I_D$  measured and estimated for a  $L=0.35\mu m, W=200\mu m$  nMOS transistor (estimation calculated implementing the ACM model [33] in a Matlab routine, with n=1.25)

- the varactor: its capacitive curve, the VCO gain  $K_{VCO}$ .

- the transistors: the parasitic capacitances and  $g_m$ .

From Eq.2.15 and the assumption that  $g_{tank} \approx g_{L,par}$ ,  $g_m = \alpha \cdot g_{L,par}/2$ . Then, if  $g_m/I_D$  of the transistors  $M_i$ ,[i=1..4] is increased while  $\alpha$  and the inductance electrical characteristics (L,  $g_{L,par}$ , $C_L$ ) are fixed,  $g_m$  is set and  $I_D$  decreases (with  $I_D = I_{bias}/2$ ). It leads to a reduction in the VCO power consumption. However, the minimum possible value of  $I_D$  is limited by the maximum oscillator phase noise value specified [38] [39], as it increases when  $I_D$  drops (the Phase Noise behaviour will be studied in Chap.3). It is also limited by the parasitic capacitances of the transistors  $M_i$ , i=1..4 (see Fig. 2.5), since an increment in  $g_m/I_D$  with  $g_m$  constant produces an increment in the transistor's width[33]:

$$W = L \cdot g_m \cdot \frac{kg_m/I_D}{\frac{4}{nU_t} \left(\frac{1}{nU_t} - g_m/I_D\right)}$$

(2.24)

An increment in the transistor width W also restricts the oscillation frequency and diminish the tuning range. It is because a higher W is equivalent to higher transistor parasitic capacitances -which reduces the possible varactor capacitance or makes it negative-.

Considering the previous discussion, the proposed VCO design methodology is presented in the scheme of Fig.2.8. Given an inductor value L and a oscillation frequency  $f_0$ , the inductor dimensions and its parameters are calculated ( $g_{L,par}$  and

Figure 2.8: Design methodology

Q among others). With these parameters,  $g_m/I_D$  and  $\alpha$ , it is found  $I_D$ . Using the transistor's characteristic curves of Fig.2.7 or the Eq.2.21, the width of Mi's are obtained. At last, the varactor capacitance  $C_{var}$  is calculated. If the phase noise  $\mathcal{L}$  is higher than  $\mathcal{L}_{max}$  or the varactor capacitance  $C_{var}$  is less than a  $C_{var,min}$  then the  $g_m/I_D$  or the L chosen have to be changed.

With the previous discussion about the complementary VCO and the design methodology several possible situations can be pointed out:

- Using Eq.2.24, if  $g_m/I_D$  is fixed, when the inductor value increases the transistor width W decreases (see Fig.2.9). The reason is that the rise of the inductor also increases the inductor series resistance, decreasing  $g_{L,par}$  and hence the  $g_m$  of the transistors (see Eq.2.15).

- Also from Eq.2.24 for a fixed inductor, if  $g_m/I_D$  rises then W increases because  $g_m$  is constant. This behaviour is shown in Fig.2.9.

- Usually the inductor capacitance is higher than the transistor capacitances and then if the inductor value grows, despite the transistor width falls, the varactor capacitance decreases (remember that the total VCO capacitance must fulfill the Eq. 2.16) (see Fig.2.10,  $C_{var}$  versus L).

- For a constant inductor value, the  $g_m$  is constant and if  $g_m/I_D$  increases, from Eq.2.24, the W increases and the varactor capacitance decreases. The total capacitance of the VCO can be so high that  $C_{var}$  would fall below zero ( see in Fig.2.10 the plot of  $C_{var}$  versus  $g_m/I_D$ )

The VCO output voltage is a specification which has been taken into consideration in the methodology design but it has had less influence that the phase noise

Figure 2.9: Width of nMOS cross coupled transistors vs.  $g_m/I_D$  and L

Figure 2.10: Varactor capacitance vs.  $g_m/I_D$  and L

and consumption constrain. The output voltage amplitude of the oscillation can be approximated as [21]:

$$V_{out} = \frac{4}{\pi} \frac{I_{bias}}{g_{tank}} \cong \frac{4}{\pi} \frac{I_{bias}}{g_{L,par}}$$

(2.25)

with  $I_{bias} = 2 \cdot I_D$ . The intuitive idea of this expression is that when the VCO oscillates the LC tank resonates and its impedance is equal to the tank resistance. The tank attenuates the harmonics of the current and leaves the fundamental of the input current. A differential voltage of the Eq.2.25 is generated with this current if a rectangular current waveform is considered [21].

It means that a high output voltage amplitude is reached when the current  $I_D$  grows, which goes against the reduction of the power consumption. Then, as we decided to choose the VCO with the lower possible current consumption , then its output amplitude is fixed and the output voltage constrain has not been considered. This type of oscillators usually have high current values and the equivalent inductor conductance is not small. It is expected that the designed VCO peak to peak output voltage amplitude would be around  $1V.^3$

The quiescent output voltage depends on the zone in which the transistor works. In this work the transistor is biased in such a way to be in moderate inversion, then the  $V_{GS}$  is around  $U_t$  (see the chapter four of [35]).

### 2.6 Amplitude stabilization mechanism

Until now we have accepted that the oscillator starts but it has not been shown how the oscillator arrives to the steady-state. To give a brief and qualitative explanation it will be supposed in the following discussion that the transistors of both cross-coupled blocks are in saturation.

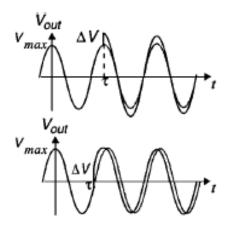

In the following it will be illustrated the control amplitude mechanism of the VCO. In this kind of oscillators the output voltage  $V_1$  is sinusoidal but not the output current, which has all the possible harmonics of the working frequency  $f_0$  as it is shown in Fig.2.12:

$$V_{out}(t) = V_1 \cdot \cos(\omega_0 t) \tag{2.26}$$

$$i_{out}(t) = \sum_{n=1}^{\infty} i_n \cos(\omega_0 t)$$

(2.27)

Using the scheme of Fig.2.11, and considering that  $i_1$  is the fundamental component of the drain current, it is defined the transconductance  $G_{m1}$  as:

$$G_{m1} = \frac{i_1}{V_1} \tag{2.28}$$

<sup>&</sup>lt;sup>3</sup>This amplitude was not sufficient for the PLL to work correctly, so it has been used a preamplifier to increase this value

Figure 2.11: Amplitude stabilization mechanism in a -Gm block

Figure 2.12: Drain current of the VCO cross-coupled transistors vs. time

where  $G_{m1}$  is the large signal transconductance at  $\omega_0$ ,  $i_1$  and  $V_1$  are the drain current and the drain voltage of the transistor  $M_1$ , respectively. When the voltage  $V_1$  is very small we are working at small-signal and then

$$G_{m1} = g_m = \frac{2I_S}{nU_t}(\sqrt{1+i} - 1) \cong \frac{I_S}{nU_t}i = \frac{I_D}{nUt} \quad V_1 \ll U_t$$

(2.29)

with  $I_S$ ,  $U_t$ , n and i as defined previously.

When we are working in large-signal, the output current tends to be sharp

spikes [39], whose average value is  $I_{bias}$ . Then the fundamental current  $i_1$  is:

$$i_1 = \frac{2}{T_0} \int_0^{T_0} i_{out} cos(\omega_0 t) dt \cong \frac{2}{T_0} \int_0^{T_0} i_{out} dt = 2I_D$$

(2.30)

where  $T_0 = 1/(2\pi f_0)$  is the signal period. The approximation is valid at large-signal because the peak of current will occur when  $cos(\omega_0 t) \approx 1$ , and around this point the current  $i_{out}$  is considered to be almost 0. Then

$$G_{m1} = \frac{2I_D}{V_1} \quad V_1 \gg U_t$$

(2.31)

Comparing Eq.2.29 with Eq.2.31, it is clear that  $G_{m1}$  in large signal is lower than  $G_{m1}$  in small signal and also that the large signal transconductance is inversely proportional to the voltage  $V_1$ . The previous discussion shows that the VCO has a negative feedback which controls the output voltage amplitude.

## 2.7 Moderate inversion design

This work has been focused on design a 910MHz VCO with cross-coupled transistors in moderate inversion. This choice has been done for various reasons. Firstly, we want to show that the  $g_m/I_D$  methodology [25] can be used in radio-frequency and that is possible to work far from strong inversion with advantageous trade-offs in the VCO performance (reduction of power consumption in the VCO without jeopardizing the phase noise).

In Fig.2.7 the current consumption and the varactor capacitance  $C_{var}$  are given for different values of  $g_m/I_D$  and different inductor values, using a  $0.35\mu m$  technology. To give some numeric examples, the bias current of the transistor and  $C_{var}$  are given for various combinations of  $g_m/I_D$  and L in Tables 2.1 and 2.2 respectively.

| $g_m/I_D(1/V)$ | L(nHy) | $I_{bias}(\mathrm{mA})$ |

|----------------|--------|-------------------------|

| 5              | 3      | 13                      |

| 5              | 7      | 4.2                     |

| 8              | 3      | 8                       |

| 8              | 7      | 2.6                     |

| 11             | 3      | 5.8                     |

| 11             | 7      | 1.9                     |

Table 2.1: Bias current of each cross-coupled transistors versus  $g_m/I_D$  and inductor L

As it can be seen in these pictures and numbers, the bias current decreases more than a half when the transconductance-to-current ratio increases from 5 to 11, with a fixed inductor (for a 7nHy inductor  $I_{bias}$  is 4.2 and 1.9mA respectively). It means that working at  $g_m/I_D = 11$  -at a low-moderate inversion zone-, we are

| $g_m/I_D(1/V)$ | L(nHy) | Cvar(pF) |

|----------------|--------|----------|

| 5              | 3      | 5.8      |

| 5              | 7      | 2.4      |

| 8              | 3      | 3.6      |

| 8              | 7      | 1.8      |

| 11             | 3      | 1.4      |

| 11             | 7      | 1.1      |

| 12             | 3      | 0.4      |

| 12             | 7      | 0.8      |

Table 2.2: Capacitance of each varactor versus  $g_m/I_D$  and inductor L

reducing roughly to a half the power consumption. If we were able to work at weak inversion with  $g_m/I_D=17$ , for example, the bias current would be around 1.3mA for an L=7nHy, which is not so lower than the bias current of  $g_m/I_D=11$ . The current consumption from moderate inversion to weak inversion does not change so much but what does increase is the width of the transistor, which rises the transistor capacitances so much that at  $g_m/I_D=17$  the varactor capacitance would be -8pF, a negative capacitance!.

In case of working in strong inversion the current consumption increases considerably. In Sec.3.6 it is shown that the improvement in phase noise when working in strong inversion does not compensate the increment in the power consumption.

Then it is in moderate inversion where a good trade-off between power consumption and physical constrains is observed.

In the Chap.3 it can be seen that the phase noise values in moderate inversion are acceptable to be used in real applications.

# 2.8 Layout design and its consequences in the design methodology

The layout design is a very delicate and difficult task in radio-frequency because lots of effects begin to appear at these bands and commonly they degrade the performance of the system, specially if a careless layout is done. Some effects are: the appearance of transmission lines, inductive, capacitive and resistive parasitics, the antenna-effect, substrate coupling and others. But which is also true is that many of these problems can be considerably reduced if a good layout is performed.

The transmission lines and antenna-effect are almost neglected if the higher dimensions of the circuit are below one tenth of the wave length (in the working band  $\lambda/10 \approx 30mm$ , which has never exceeded)[40]. The coupling substrate is important when more than one circuit with different signals are used, for example when a power amplifier and a VCO are used, both circuits have to be shielded using a guard ring connected to ground, to effectively fix the substrate to the ground voltage [41].

In case of the parasitics of the interconnecting wires we only considered their parasitic capacitances and not their resistance parasitics because most of the wires of the design are short and the ones that are a bit more long were made wide enough to be discarded the resistive effect. For example, the metal wire that connects the drains of the transistors nMOS and pMOS has a length of  $100\mu m$  and a width of  $10\mu m$  approximately, and is one of the largest traces of the circuit. The sheet resistance of the metal is  $70m\Omega_{square}$ , then the total resistance of this trace is around  $0.7\Omega$ . For a bias current of 1mA the voltage drop between the drains is around 0.7mV, negligible respect of the signals of the VCO.

Regarding the transistors, as the width W of them is very large (hundreds of  $\mu m$ ), the gate resistance due to the resistive poly-silicon and the contacts has a considerable value. To decrease this resistance a multi-fingered layout has been made, which means that N transistors with a width of W/N are all connected in parallel, as it is seen in Fig.2.14. As the gate resistance of each transistor is in parallel with the other gates, the result resistance is around N times smaller than the simple structure. However this kind of layout needs a lot of interconnection wires which increases the parasitic capacitances.

From what has been discussed, in the design methodology the layout parasitics have to be considered. In this work, the resistances of the multi-fingered structure transistors and of the wires are not considered in the methodology. Also the parasitic inductances are neglected. Therefore the unique parasitics considered are the capacitances. The following is a detailed discussion on this matter.

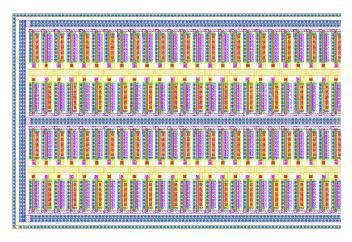

Due of the need of maintaining the symmetry of the cross-coupled complementary architecture, the layout has been disposed with an axial symmetry as it is in Fig.2.15. This disposition is of great importance specially in terms of phase noise minimization.

#### Parasitic capacitances

The 900MHz -Gm LC VCO designed in this work occupies an important amount of silicon area because:

- 1. the inductors are quite big (each one can take tenths of thousands of  $\mu m^2$ ) because the working frequency is not too high.

- 2. as the varactor capacitance has been implemented with a MOS transistor, to reach the wanted capacitance the varactor width is considerable.

- 3. as the transistors were designed to work in moderate inversion they have widths of hundreds of  $\mu m$ .

The influence of these three blocks in the total parasitic capacitances are considered separately to study their influence. We took care of these parasitics in the post-layout stage by adjusting the varactor size to achieve the wanted frequency.

The inductors' parasitic capacitances will be studied in Chap.4 and these are quite well-known so they are added from the beginning in the VCO methodology design when the inductor parasitics are calculated. But it has to be mentioned that

the traces that carry the signals to the inductors have a non-negligible length which cause parasitic capacitances.

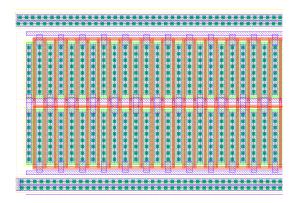

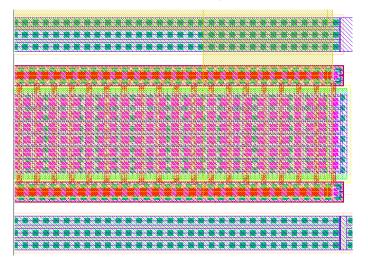

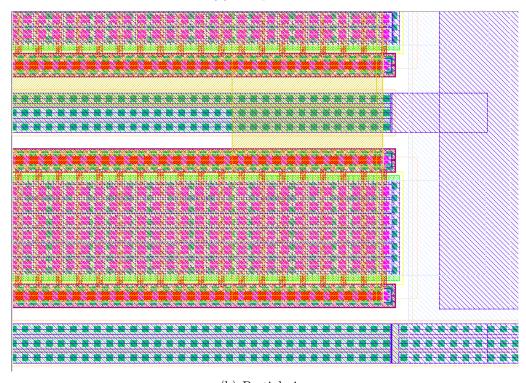

The layout of the cross-coupled transistors can be made in two different ways. One is to design interlaced transistors and the other is to design each transistor separately. In Figs.2.16(a) and 2.16(c) are depicted the complete view of the separate and interlaced nMOS cross-coupled block, respectively. In the design both have been done as it is seen in Fig.2.16(a). The former has much more parasitic capacitances than the last one because the capacitances that appear with the interconnect wires increases considerably the total parasitic capacitances. If the detail of the interlaced layout of Fig.2.16(b) is compared with the interlaced layout of Fig.2.16(d) it is visible that there is a larger quantity of interconnect wires in the former one.

However separate transistors decrease the matching of the  $g_m$ , despite the large size of the transistors diminish this effect. As it is very difficult to estimate the total parasitic capacitances added by the wires because of the need of several iterations between the algorithm results and the designed layout, in this work the separate-transistor architecture has been chosen.

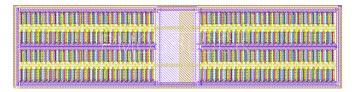

To maintain the symmetry of the layout the varactor has to be divided into two parts. The same situation that appeared with the cross-coupled transistor block is repeated here: each transistor of the varactor can be drawn separately or interlaced with the other one. In this case it has been found that it is even more difficult to interlace both transistors than in the case before mentioned. Also in this situation the parasitic capacitances are very large. Then we decide to use the separate layout in our design. The complete layout and a detail of the connections of the multi-fingered transistors are shown in Figs.2.17(a) and 2.17(b), respectively.

# 2.9 Current Source design

The election of the current source to be used and its design has been studied in several works (for example in [17] [21]). It has been payed so much attention to this subject because a bad choice in the type of the source or in the sizing would jeopardize the phase noise of the complete VCO.

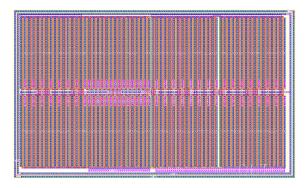

In [17] it has been shown that the best current source is a current mirror of pMOS tansistors. Also the size of these transistors has to be as large as possible to reduce the thermal and 1/f noise because they are inversely proportional to the width of the transistor[33][42]. The size of the current source is  $W = 2000\mu m$  and  $L = 1\mu m$ . The final layout view of the current source is in Fig.2.18

It can be added a capacitor in parallel with the bias current source to reduce the oscillation of the source of the cross-coupled pMOS transistors and therefore the phase noise, but its drawback is that it decreases the output impedance of the source voltage  $V_{DD}$  making the VCO more susceptible to voltage supply variations [21].

### 2.10 Final Design

Considering the foregoing analysis and design methodology the VCO design is given in this section. The final election of the variables involved attempted to fulfill the compromise between power consumption and phase noise by working in moderate inversion, the requirements of output voltage and the maximum area budget. The considerations of possible technology variations in passive and active devices have also been considered.

It has been created an algorithm in Matlab [43] that implements the design methodology proposed in Fig.2.8. The design has been done in a  $0.35\mu m$  CMOS standard technology; the supply voltage used is  $V_{DD}=3$  Volts and the central frequency is 915MHz. The design space has been obtained varying the inductor and the  $g_m/I_D$ . This election has been done because:

- the inductor is a difficult component whose characteristics -series resistance and quality factor- modifies substantially the behaviour of the VCO;

- the transconductance-to-current ratio variation modifies the current consumption and the transistor size.

Also with the series resistance of the inductor it can be obtained the  $g_m$  of the transistors and with the  $g_m/I_D$  the drain current needed. And finally, as it has been said previously, we want to test the  $g_m/I_D$  methodology [25] in this kind of circuits.

In the design we use a limited number of these variables: L varies between 3nHy and 7nHy at steps of 1nHy, and  $g_m/I_D[1/V]$  goes from 5 to 17, at steps of  $1V^{-1}$ . We considered that, due to the variations in the technology, a smaller simulated step would not be neither useful nor clear. The final design values of  $g_m/I_D$  and L obtained from the algorithm are given in Table 2.3.

| Design Parameter | Value |

|------------------|-------|

| L (nHy)          | 5     |

| $g_m/I_D$        | 11    |

Table 2.3: Final values of L and  $g_m/I_D$  obtained from the implemented algorithm

As we would like to design the VCO transistors in moderate inversion arise the problem discussed in Sec.2.8: the value of  $C_{var}$ . In this particular design the variable that fundamentally limits is the  $C_{var}$ , as it can be seen in Table 2.2. The  $C_{var}$  decreases very rapidly after  $g_m/I_D=11$  as it is shown in Fig.2.13(b) so a good compromise has been found in this value.

The transistor length is the minimum of the technology:  $0.35\mu m$  to have the maximum  $f_t$  available.

In Table 2.4 there are the most important VCO variables:

#### **Final Layout**

| Design Parameter | Value      | Design Parameter | Value       |

|------------------|------------|------------------|-------------|

| L                | 5nHy       | $R_{L,par}$      | $90\Omega$  |

| $C_{L,eq}$       | 90fF       | $C_{load}$       | 600fF       |

| $I_D$            | 1.5mA      | $g_m$            | 0.030S      |

| $C_{var}$        | 700fF      | $W_{var}$        | $1600\mu m$ |

| $W_n$            | $336\mu m$ | $W_p$            | $782\mu m$  |

Table 2.4: Final values of several variables of the VCO design

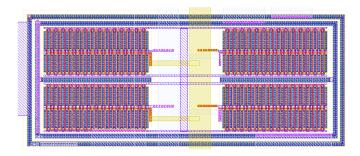

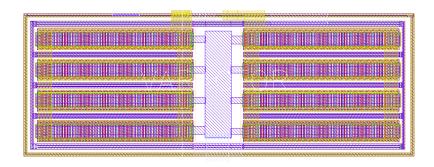

The final layout of the VCO is depicted in Fig.2.19. All the blocks except of the inductors (see Chap.4) have been previously presented as well as a detailed view of them. The layout obeys the floorplan given in Fig.2.15. The total silicon area occupied is of  $600\mu m$  by  $500\mu m$  approximately (around  $0.3mm^2$ ).

All the active blocks have been surrounded by double guards to isolate them and to avoid latch up. The inductors have been partially guarded to ground to decrease the substrate noise coupling though the inductors [44] [45].

Figure 2.13: Drain current of the cross-coupled transistors and varactor capacitance versus  $g_m/I_D$  and inductor value L

2.10 Final Design

Figure 2.14: Multi-fingered layout of a transistor with width W

Figure 2.15: Floorplan of the cross-coupled complementary -Gm LC VCO

(a) Final layout of the pMOS block

(b) Detail of the structure of the final pMOS block

(c) Interlaced layout of the pMOS block (not used in the final VCO design)  $\,$

(d) Detail of the structure of the interlaced pMOS block

Figure 2.16: Separate transistor layout and interlaced layout of the pMOS cross-coupled block

(a) General view of the final varactor (the two separate group of transistors are clearly appreciated)

(b) Detail of the varactor layout showing the multi-fingered transistors interconnected

Figure 2.17: Final varactor layout

Figure 2.18: Current source layout

Figure 2.19: Final layout of the fabricated VCO

# Chapter 3 Phase Noise in LC VCOs

#### 3.1 Introduction

In this chapter the Phase Noise in electrical oscillators is studied. A general definition of phase noise for a typical oscillator and particulary expressions of it for LC-VCO are provided. Also, there are described their most important models, divided in Lineal Time Invariant (LTI) and Lineal Time Variant (LTV) ones. The noise sources in the complementary LC-VCO is studied, and expressions of its phase noise are derived. Finally the calculus and simulation results of the designed -Gm LC VCO are shown.

#### 3.2 Phase Noise Definition

When an ideal oscillator is modelled, its output can be expressed as:

$$V_{out} = A\cos[\omega_0 t + \phi] \tag{3.1}$$

where amplitude A and arbitrary phase  $\phi$  are constant values. Therefore, the spectrum of this signal are two impulses at frequencies  $\pm f_0 = \frac{\omega_0}{2\pi}$ , where  $f_0$  is the frequency of oscillation [46].

However, when using a real oscillator, the amplitude and the phase are affected by noise and are time-variant, so the output is now:

$$V_{out}(t) = A(t)\cos[\omega_0 t + \phi(t)] \tag{3.2}$$

were  $\phi(t)$  is called the excess phase of the output. The spectrum of this signal has sidebands close to the frequency of oscillation  $f_0$ .