# LOW POWER CIRCUITS DESIGN USING RESISTIVE NON-VOLATILE MEMORIES

HUANG KEJIE

## A THESIS SUBMITTED

### FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

## DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING

## NATIONAL UNIVERSITY OF SINGAPORE

2014

# DECLARATION

I hereby declare that this thesis is my original work and it has been written by me in its entirety. I have duly acknowledged all the sources of information which have been used in the thesis.

This thesis has also not been submitted for any degree in any university previously.

科杰

Huang Kejie 12 July 2014

# Acknowledgments

This thesis would not have been possible without the guidance, support, and love of many people to whom I would like to express my deepest gratitude.

First of all, I'd like to sincerely thank my supervisor, Prof. Lian Yong, for the great efforts he has put on my academic and guidance. His insightful and inspiring guidance has helped me grow as an independent researcher and good team player, which will continue to have profound influence on my future endeavor.

I am also very grateful to Prof. Zhao Rong, who provided me a research job in Singapore University of Technology and Design after I left Data Storage Institute. She has given me tremendous help to support my Ph.D study with useful data and insights for my research.

Lastly, I'd like to thank my parents Huang Difu and Sun Yudi, my sister Huang Xvxia, my brother-in-law Chen Quantong for their unconditional love wherever I am. I also want to express my gratefulness to my wife Ming Zhaoyan who gave birth and takes care of our daughter Huang Yuxi, and has helped me a lot in my Ph.D study. Our daughter was born during my Ph.D pursing period, and made my Ph.D study joyful and colorful.

# Contents

| List of | Tables                                                      | v  |

|---------|-------------------------------------------------------------|----|

| List of | Figures v                                                   | ii |

| Chapte  | r 1 Introduction                                            | 1  |

| 1.1     | Motivation                                                  | 1  |

| 1.2     | Resistive NVMs                                              | 5  |

|         | 1.2.1 STT-MRAM                                              | 7  |

|         | 1.2.2 PCM                                                   | 1  |

|         | 1.2.3 RRAM                                                  | 2  |

| 1.3     | Resistive NVMs for Low Power                                | 4  |

|         | 1.3.1 Break Even Point (BEP)                                | 4  |

|         | 1.3.2 Using STT-MRAM as the Retention Register              | 5  |

|         | 1.3.3 Integrating RRAM/PCM in FPGAs                         | 6  |

| 1.4     | Related Works                                               | 7  |

|         | 1.4.1 Non-volatile Latch/Flip-flop                          | 7  |

|         | 1.4.2 Non-volatile FPGAs                                    | 20 |

| 1.5     | My Contributions                                            | 25 |

| 1.6     | Thesis Organization                                         | 27 |

| Chapte  | er 2 Non-volatile Latch/FF for Zero Standby Power Systems 2 | 8  |

| 2.1    | Introd | luction                                          | 28 |

|--------|--------|--------------------------------------------------|----|

| 2.2    | Propo  | sed nvLatch/nvFF                                 | 29 |

|        | 2.2.1  | The State Saving Mode                            | 32 |

|        | 2.2.2  | The State Restoration Mode                       | 33 |

|        | 2.2.3  | The Normal Latch Mode                            | 34 |

|        | 2.2.4  | Non-volatile Flip-flop                           | 34 |

| 2.3    | Simula | ation Results                                    | 36 |

|        | 2.3.1  | Analysis the impact of VDD                       | 37 |

|        | 2.3.2  | The performance of the proposed $\mathrm{nvFF}$  | 38 |

|        | 2.3.3  | Analysis the impact of MTJ parameters            | 45 |

| 2.4    | Summ   | ary                                              | 50 |

| Chapte | er 3 I | localized Array for Zero Sleep Power Systems     | 51 |

| 3.1    | Introd | luction                                          | 51 |

| 3.2    | Propo  | sed Scheme                                       | 53 |

|        | 3.2.1  | Circuit Architecture                             | 55 |

|        | 3.2.2  | Minimum Sleep Time                               | 57 |

| 3.3    | Locali | zed STT-MRAM Array Design                        | 58 |

|        | 3.3.1  | Dual-Step-Write for Low VDD                      | 59 |

|        | 3.3.2  | Read-before-Write for Low Power                  | 60 |

|        | 3.3.3  | Pipelined Quad-Phase Write Scheme for High Speed | 62 |

|        | 3.3.4  | $2\sigma$ Write Scheme for Low Power             | 66 |

|        | 3.3.5  | Reference Resistance Generator                   | 70 |

| 3.4    | Simula | ation Results                                    | 77 |

|        | 3.4.1  | Spice Simulation Results of the Proposed Array   | 78 |

|        | 3.4.2  | Analysis of the Reference Resistance Generator   | 85 |

| 3.5    | Summ   | ary                                              | 88 |

| Chapte     | er 4 I | Non-volatile Switch based FPGA            | 89  |

|------------|--------|-------------------------------------------|-----|

| 4.1        | Introd | luction                                   | 89  |

|            | 4.1.1  | Baseline 2D FPGA                          | 90  |

|            | 4.1.2  | Access Device                             | 91  |

| 4.2        | Propo  | sed Storage Element                       | 92  |

| 4.3        | Propo  | sed non-volatile FPGA                     | 93  |

|            | 4.3.1  | Proposed Crossbar Array and Switch Point  | 96  |

|            | 4.3.2  | Proposed Look-Up Table                    | 98  |

| 4.4        | Layou  | t and Area Estimation                     | 99  |

|            | 4.4.1  | Routing of the RRAM cells proposed nvFPGA | 99  |

|            | 4.4.2  | Area Estimation                           | 101 |

| 4.5        | Simul  | ation Results                             | 102 |

|            | 4.5.1  | Write Power and Reliability               | 103 |

|            | 4.5.2  | RC Delay Simulation Results               | 108 |

|            | 4.5.3  | LUT Comparison                            | 108 |

|            | 4.5.4  | VPR Simulation Results                    | 109 |

| 4.6        | Summ   | nary                                      | 111 |

| Class      |        | Normal Attended AM Land EDCA              | 110 |

| Chapte     |        | Non-volatile SRAM-based FPGA              | 112 |

| 5.1        |        | luction                                   |     |

| 5.2        | 1      | osed nvSRAM based FPGA                    |     |

|            |        | Working Modes and Power Advantage         |     |

| <b>F</b> 0 | 5.2.2  | Multi-context FPGA and Area Advantage     |     |

| 5.3        |        | sed Storage Element                       |     |

|            | 5.3.1  | Single Context nvSRAM                     |     |

|            | 5.3.2  | Multi-context nvSRAM                      |     |

| 5.4        |        | ation Results                             |     |

|            | 5.4.1  | Single Context Simulation Results         | 125 |

|        | 5.4.2  | Mul  | ti-cont | text | Sim | ulatio | on R | esult | s. | • | ••• | <br>• | <br> | <br>•          | . 128 |

|--------|--------|------|---------|------|-----|--------|------|-------|----|---|-----|-------|------|----------------|-------|

| 5.5    | Summ   | ary  |         |      |     |        |      |       |    | • |     | <br>• | <br> | <br>. <b>.</b> | . 133 |

| Chapte | er 6 C | Conc | usion   | s    |     |        |      |       |    |   |     |       |      |                | 134   |

| Acrony | /ms    |      |         |      |     |        |      |       |    |   |     |       |      |                | 137   |

# List of Tables

| 1.1 | Comparison of conventional and emerging memories. Most data                  |    |

|-----|------------------------------------------------------------------------------|----|

|     | other than those of RRAMs were taken from [1]                                | 6  |

| 1.2 | Comparison among different approaches in the <code>nvLatches/nvFFs.</code> . | 18 |

| 2.1 | Description of the $90nm$ embedded MTJs and $45nm$ CMOS process.             | 36 |

| 2.2 | The write energy comparison among different write approaches. $\ .$ .        | 36 |

| 2.3 | The performance of our proposed nvFF                                         | 39 |

| 2.4 | The performance comparison among the proposed nvFF, conven-                  |    |

|     | tional nvFFs and the CMOS retention FF during saving operation.              |    |

|     |                                                                              | 42 |

| 2.5 | The performance comparison among the proposed nvFF, conven-                  |    |

|     | tional nvFFs and the CMOS retention FF during normal operation.              | 44 |

| 2.6 | The estimated area comparison among the proposed nvFF, conven-               |    |

|     | tional nvFFs and the CMOS retention FF during normal operation.              | 45 |

| 3.1 | Example of pipelined quad-phase saving scheme. Row clock is used             |    |

|     | in the table                                                                 | 62 |

| 3.2 | Example of pipelined quad-phase saving scheme with the $2\sigma$ write       |    |

|     | approach. Row clock is used in the table                                     | 70 |

| 3.3 | Description of the 45nm embedded MTJs process                                | 77 |

| 3.4 | Per cell area overhead comparison among different retention schemes.                           |

|-----|------------------------------------------------------------------------------------------------|

|     | The data in the '()' have included 6 transistors for scan chains. The                          |

|     | number of transistors are estimated based on M=64 and G=8K 83                                  |

| 3.5 | The comparison among non-volatile Flip-flips and proposed schemes.                             |

|     | The sleep energy and $t_{BEP}$ are based on M=64. $\eta$ is set to 10% 85                      |

| 4.1 | The number of RRAM cells and the RRAM area partition of each                                   |

|     | FPGA block                                                                                     |

| 4.2 | The simulation results of the RC delay among our proposed scheme,                              |

|     | the conventional '1R' and SRAM schemes                                                         |

| 4.3 | The speed, power and area comparison among different LUT schemes.109                           |

| 5.1 | The control logic information of our proposed nvSRAM in different                              |

|     | operation modes. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $121$ |

| 5.2 | The parameters of the PCM used in the simulation                                               |

| 5.3 | The results comparison among the SRAM, proposed nvSRAM, $[2]$                                  |

|     | and [3]                                                                                        |

# List of Figures

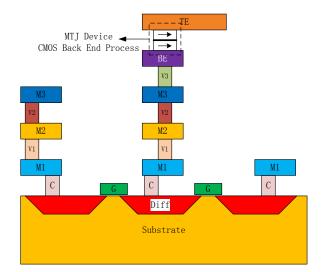

| 1.1 | CMOS Front End Process and STT-MRAM Back End Process                         | 7  |

|-----|------------------------------------------------------------------------------|----|

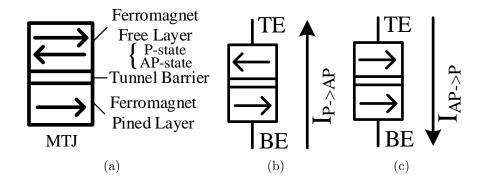

| 1.2 | (a) Block diagram of a 1T1MTJ structure of an STT-MRAM cell.                 |    |

|     | (b) Writing from P to AP state. (c) Writing from AP to P state               | 8  |

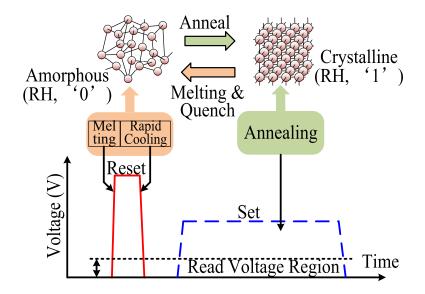

| 1.3 | Phase change materials reversibly switch between amorphous and               |    |

|     | poly-crystalline states by electrical pulses.                                | 12 |

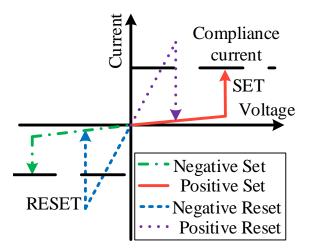

| 1.4 | Possible combinations of set and reset I-V curves. The combinations          |    |

|     | can be 'positive set, positive reset', 'positive set, negative reset',       |    |

|     | 'negative set, positive reset' and 'negative set, negative reset'. $\ . \ .$ | 13 |

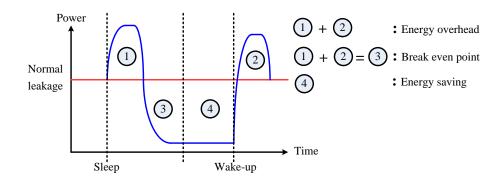

| 1.5 | Break even point                                                             | 14 |

| 1.6 | Existing approaches using nvLatches. (a) Latch is used as write              |    |

|     | driver; (b) $V_{th}$ drop in the write path; (c) Serial write                | 19 |

| 1.7 | (a) Conventional SRAM storage element to configure FPGAs (S-                 |    |

|     | RAM; (b) non-volatile storage element to configure the switch tran-          |    |

|     | sistor in FPGAs (1T2R); and (c) non-volatile storage element to              |    |

|     | replace the switch transistor and SRAM (2T1R, or '1R'). $\ldots$             | 20 |

| 1.8 | (a) The high leakage current issue, and (b) the write disturbance            |    |

|     | issue in the conventional RRAM based non-volatile SP. The en-dash            |    |

|     | lines are the paths to program the RRAM cells, and dash-dot-dot              |    |

|     | lines are the sneak paths.                                                   | 23 |

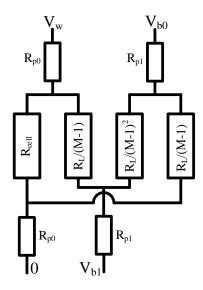

| 1.9 | Equivalent circuit of a diode-less crossbar array. $R_{cell}$ is the RRAM                              |    |

|-----|--------------------------------------------------------------------------------------------------------|----|

|     | cell resistance under programming, $R_L$ is the resistance of RRAM                                     |    |

|     | cells in LRS, $M$ is the dimension size of the array, $R_{p0}$ is the input                            |    |

|     | parasitic resistance from the switch, metal, etc., $R_{p1}$ is the paral-                              |    |

|     | lelled input parasitic resistance, which is $R_{p0}/(M-1)$ for $V/2$ or                                |    |

|     | $V/3$ write scheme and infinite for floating scheme, $V_w$ , $V_{b0}$ and $V_{b1}$                     |    |

|     | are the writing voltage, and biasing voltages for the unselected word                                  |    |

|     | lines and bit lines, respectively                                                                      | 24 |

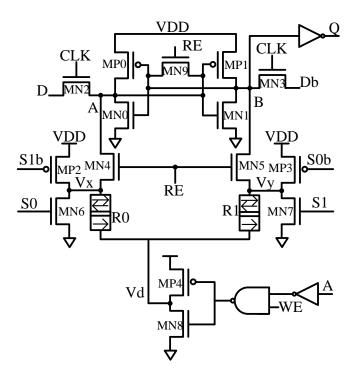

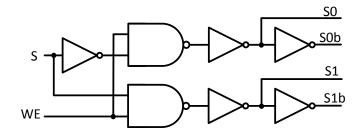

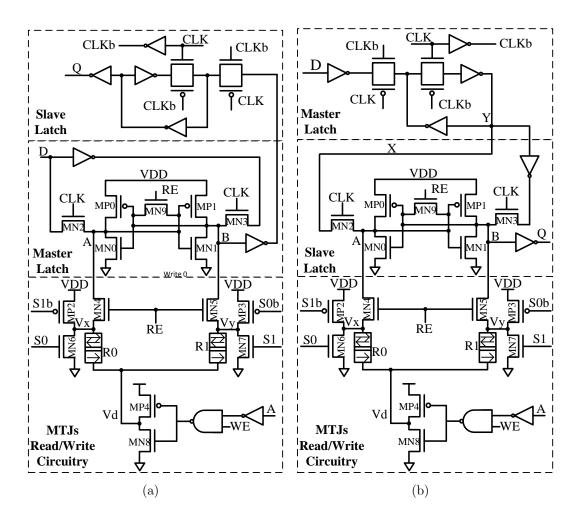

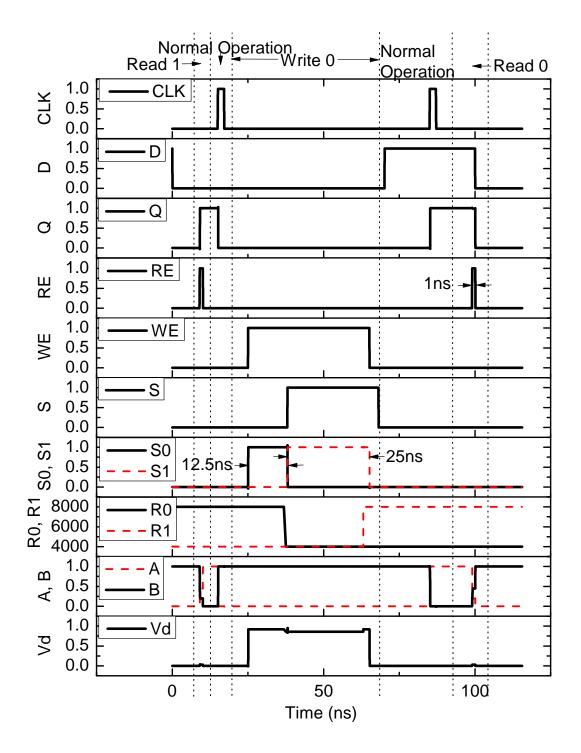

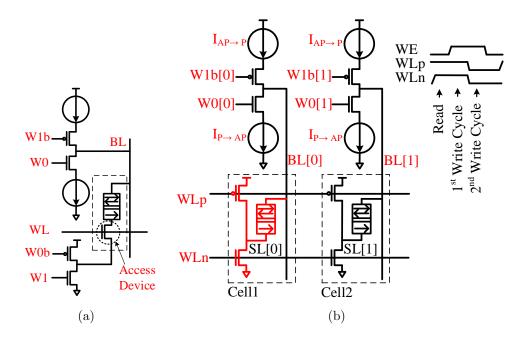

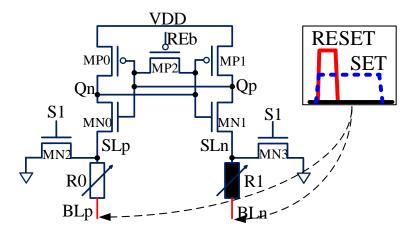

| 2.1 | $\label{eq:proposed} \ {\rm STT-MRAM} \ {\rm based \ non-volatile \ latch \ with \ two-phase \ write}$ |    |

|     | approach                                                                                               | 30 |

| 2.2 | Two-phase write operation control logic to generate $S0, S0b, S1$                                      |    |

|     | and $S1b$                                                                                              | 31 |

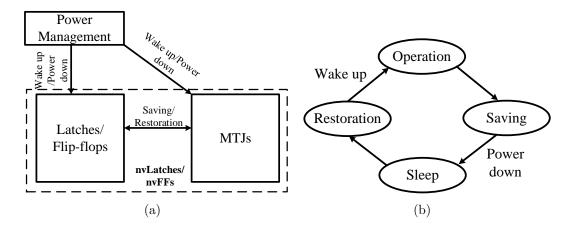

| 2.3 | (a) Block diagram of the system level controller to save the states of                                 |    |

|     | the proposed nvLatches/nvFFs in the MTJs; (b) The four operation $\$                                   |    |

|     | modes of the proposed nvLatches/nvFFs                                                                  | 32 |

| 2.4 | Proposed STT-MRAM based nvFFs. (a) The nvLatch is used as a                                            |    |

|     | master latch in the nvFF; (b) The nvLatch is used as a slave latch                                     |    |

|     | in the nvFF                                                                                            | 35 |

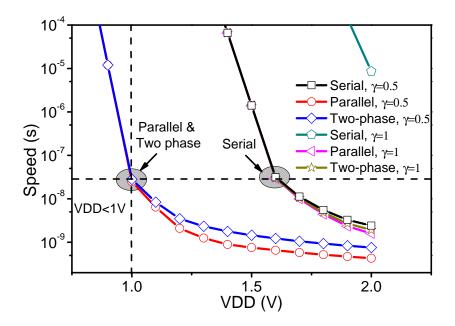

| 2.5 | The supply voltage vs. the nvFF saving speed among three write                                         |    |

|     | approaches                                                                                             | 38 |

| 2.6 | The nvFF saving speed vs. saving energy among three write ap-                                          |    |

|     | proaches                                                                                               | 39 |

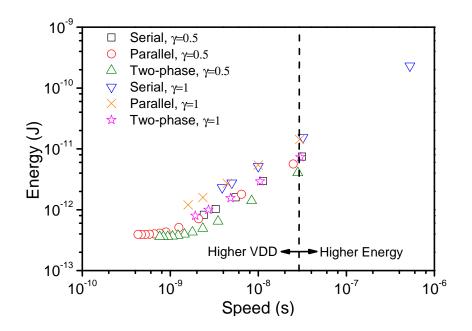

| 2.7 | The simulation results of the proposed nvFF. It has two read oper-                                     |    |

|     | ations (restoration), one write operation (saving) and two normal                                      |    |

|     | FF operations.                                                                                         | 40 |

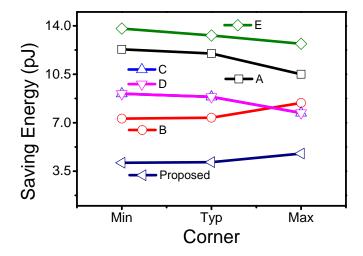

| 2.8  | The corner simulation results among the proposed nvFF and the                            |    |

|------|------------------------------------------------------------------------------------------|----|

|      | conventional nvFFs. Min corner: MTJ size $-5\%,\mathrm{Jc0}-5\%,\mathrm{transistor}$     |    |

|      | width $+5\%;$ Max corner: MTJ size $-5\%,$ Jc0 $-5\%,$ transistor width                  |    |

|      | +5%. A: [4]; B: [5]; C: [6]; D: [7]; E: [8]                                              | 41 |

| 2.9  | Sleep energy comparison among different nvFFs and conventional                           |    |

|      | CMOS FFs. A: [4]; B: [5]; C: [6]; D: [7]; E: [8]; F: [9]                                 | 43 |

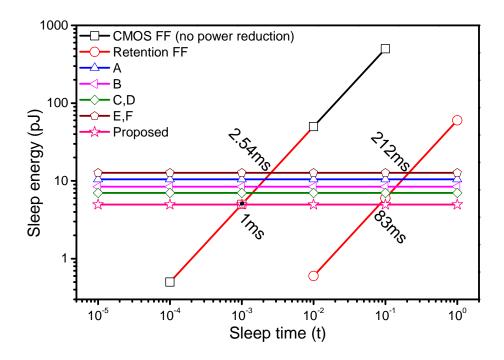

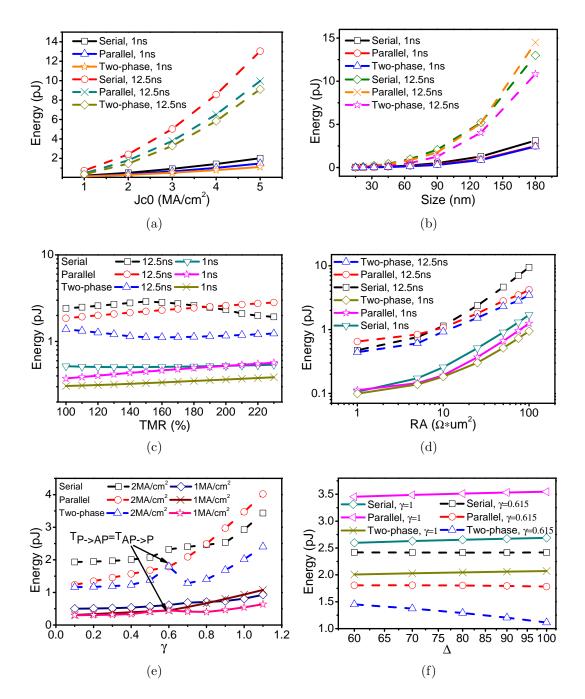

| 2.10 | The supply voltage requirement of the three write approaches vs.                         |    |

|      | (a) $J_{c0}^{P \to AP}$ , (b) size of the MTJ cells, (c) TMR, (d) RA, (e) $\gamma$ , and |    |

|      | (f) thermal stability $\Delta$ .                                                         | 46 |

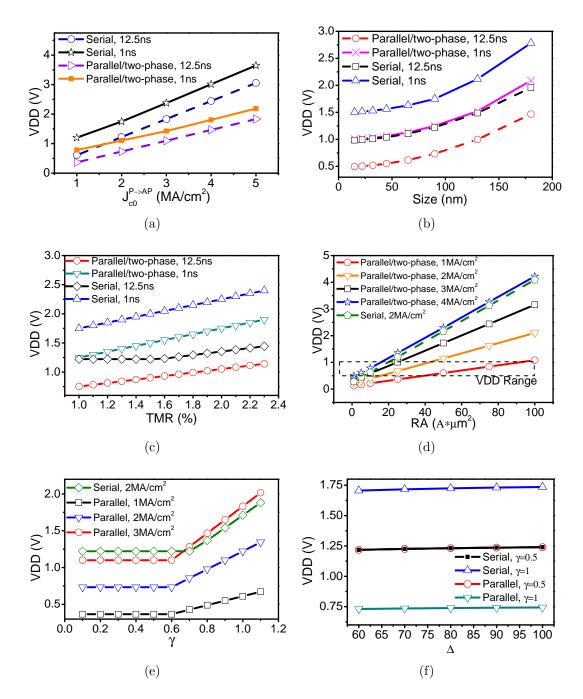

| 2.11 | The required nvFF saving energy for the three write write approach-                      |    |

|      | es vs. (a) $J_{c0}^{P \to AP}$ , (b) size of the MTJ cells, (c) TMR, (d) RA, (e)         |    |

|      | $\gamma$ , and (f) thermal stability $\Delta$                                            | 48 |

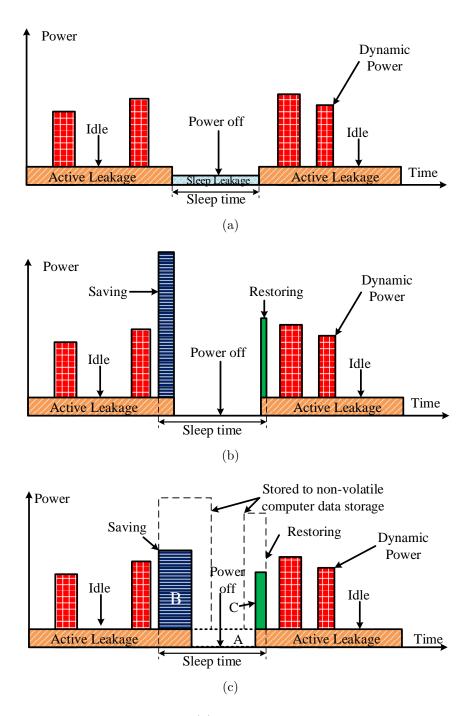

| 3.1  | Power consumption of (a) CMOS retention registers based approach-                        |    |

| 0.1  |                                                                                          |    |

|      | es, (b) nvFF based approaches, and (c) proposed dedicated NVM                            | 50 |

|      | array based approach.                                                                    | 52 |

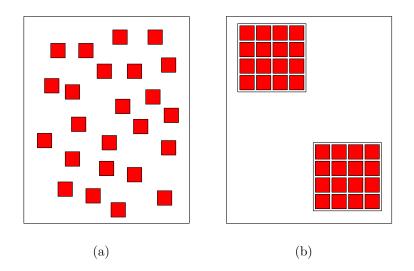

| 3.2  | (a) MTJ cells are distributed randomly in conventional nvFF schemes;                     |    |

|      | (b) localized NVM arrays in our proposed scheme                                          | 54 |

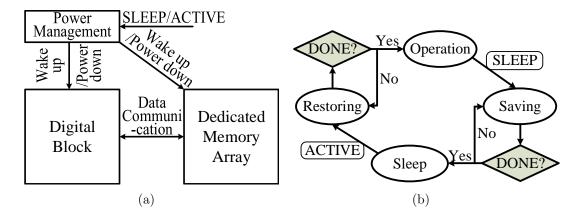

| 3.3  | (a) Top diagram of the scan based approach to save the states of                         |    |

|      | the registers in the local dedicated NVM array; (b) The four modes                       |    |

|      | of our proposed low power system.                                                        | 55 |

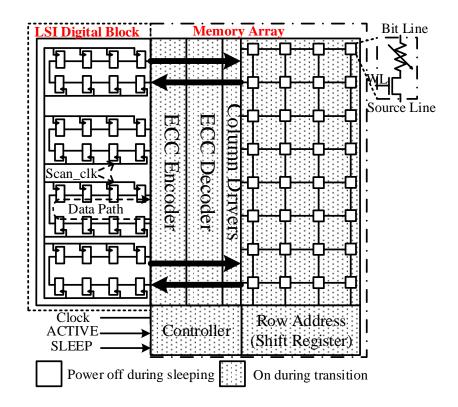

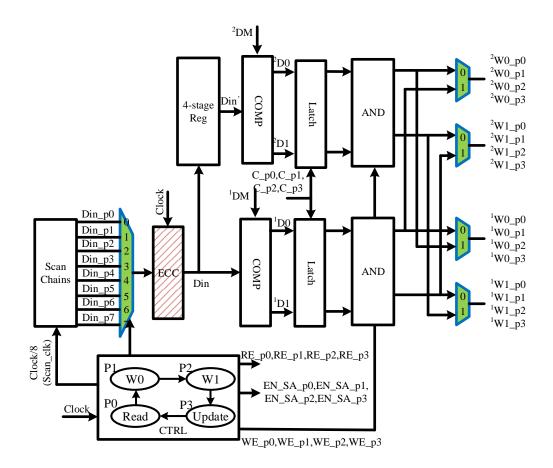

| 3.4  | Proposed architecture with the localized non-volatile memory array.                      |    |

|      | Left side of the diagram is the LSI block. Right side of the diagram                     |    |

|      | is the NVM array with the memory controller                                              | 56 |

| 3.5  | (a) The access device in conventional write schemes significantly                        |    |

|      | limit the write current passing through the MTJ. (b) Proposed dual-                      |    |

|      | step-write scheme to achieve low VDD                                                     | 59 |

|      |                                                                                          |    |

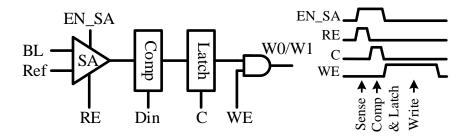

| 3.6  | The sensing and comparing block diagram for the read-before-write             |    |

|------|-------------------------------------------------------------------------------|----|

|      | scheme                                                                        | 61 |

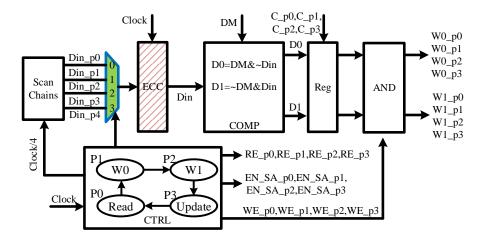

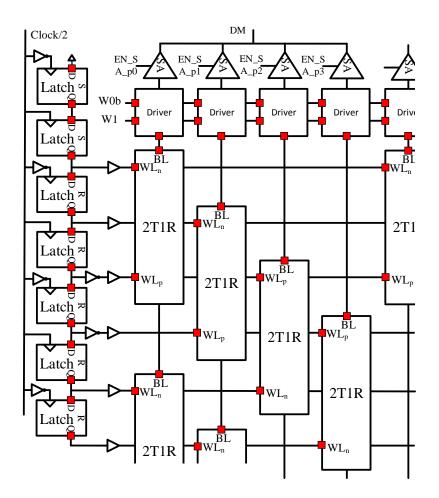

| 3.7  | Proposed pipelined quad-phase control block diagram                           | 63 |

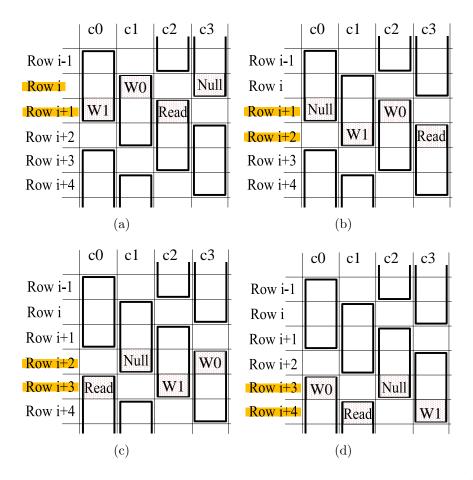

| 3.8  | The array diagram of our proposed quad-phase writing approach.                | 64 |

| 3.9  | Block diagrams of our proposed pipelined scheme in the (a) $i^{th}$ , (b)     |    |

|      | $(i+1)^{th}$ , (c) $(i+2)^{th}$ and (d) $(i+3)^{th}$ system clocks. Each time |    |

|      | two rows are active simultaneously. The active row addresses are              |    |

|      | highlighted in the figures.                                                   | 65 |

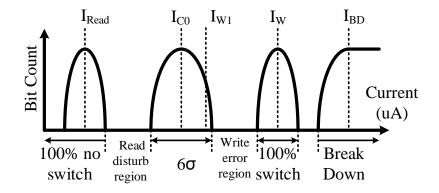

| 3.10 | Distribution of characteristic currents in STT-MRAM array [10]                | 66 |

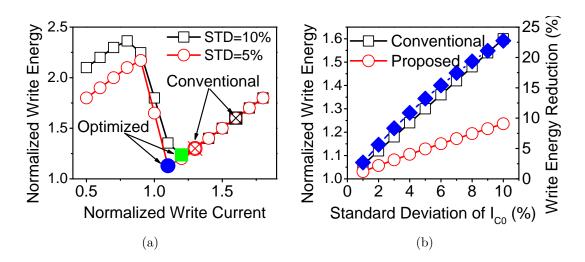

| 3.11 | (a) The relationship between the first write current amplitude and            |    |

|      | the total write energy with our proposed write scheme. (b) The                |    |

|      | relationship between the standard deviation of $I_{c0}$ in percentage         |    |

|      | and the write energy improvement with our proposed write scheme.              | 68 |

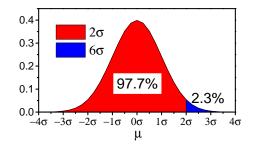

| 3.12 | The distribution of the $2\sigma$ writing                                     | 68 |

| 3.13 | Proposed pipelined quad-phase control block diagram for the $2\sigma$         |    |

|      | saving approach.                                                              | 69 |

| 3.14 | The block diagram of 8 memory channels for the $2\sigma$ saving approach.     | 69 |

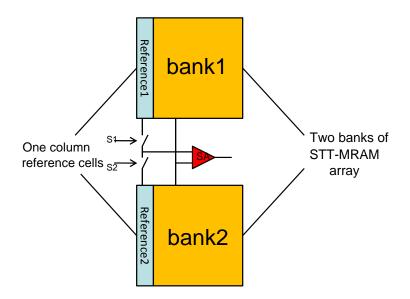

| 3.15 | Share the reference columns for two adjacent banks, reference1 is             |    |

|      | from bank1 and put closely to bank1 array, while reference2 is from           |    |

|      | bank2 and put closely to bank2 array and sense amplifier is shared            |    |

|      | by two banks of STT-MRAM array                                                | 72 |

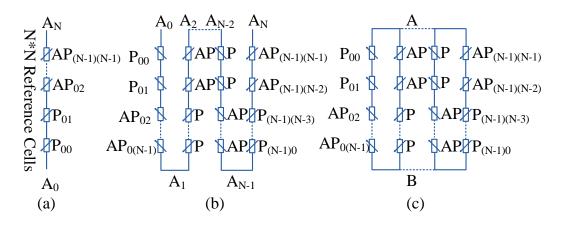

| 3.16 | Example for concept of reference cell folding. (a) Reference cells            |    |

|      | connected in series before folding. (b) Folding the whole column              |    |

|      | of reference cells to a $N \times N$ array. (c) Final construction of the     |    |

|      | $N \times N$ reference array by connecting the folded points                  | 73 |

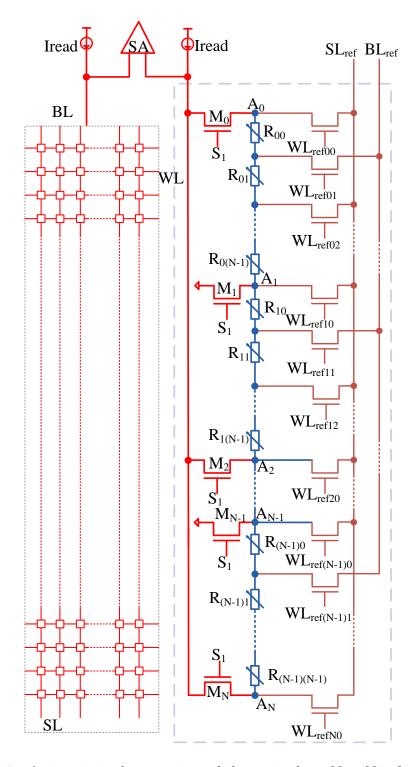

| 3.17 | 7 A circuit implementation of the equivalent $N \times N$ reference circuit |    |

|------|-----------------------------------------------------------------------------|----|

|      | when there are $2^{2n}$ cells in one reference column in which cells are    |    |

|      | averaged to obtain the equivalent resistance                                | 75 |

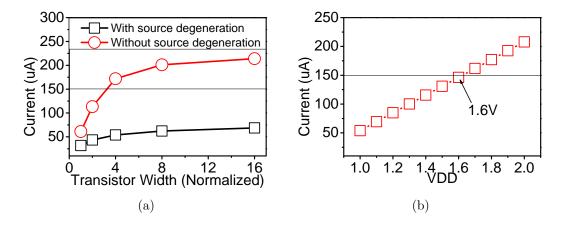

| 3.18 | 8 (a) The width of the access transistors vs. the write current that        |    |

|      | can pass through, (b) the VDD of the 1T1R scheme vs. the write              |    |

|      | current.                                                                    | 78 |

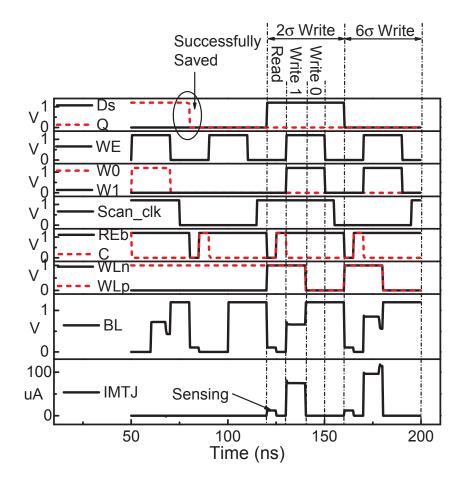

| 3.19 | 9 The waveform of the read-before-write and verify-after-write func-        |    |

|      | tions                                                                       | 79 |

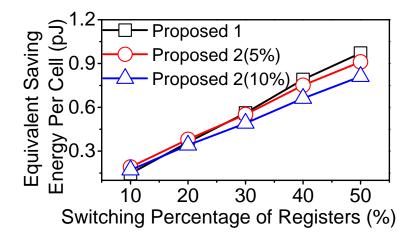

| 3.20 | ) The relationship between the power comparison of our proposed t-          |    |

|      | wo schemes and switching percentage of registers to be saved. 'Pro-         |    |

|      | posed 1' and 'Proposed 2' are the scheme without and with $2\sigma$         |    |

|      | write approach, respectively. In this simulation, the standard devi-        |    |

|      | ations of the intrinsic switching current distribution were set to $5\%$    |    |

|      | and 10%, and the saving energy of our proposed scheme without               |    |

|      | $2\sigma$ write approach was set to the same for both intrinsic switching   |    |

|      | current distributions. The scan chain length is set to 64. $\ldots$ .       | 80 |

| 3.21 | 1 The relationship between the power reduction and operation clock          |    |

|      | cycles. In this simulation, the averaged switching activities of reg-       |    |

|      | isters were set to $4\%$ and $16\%,$ and the standard deviation of the      |    |

|      | intrinsic switching current distribution was set to $10\%.$ The scan        |    |

|      | chain length is set to 64                                                   | 81 |

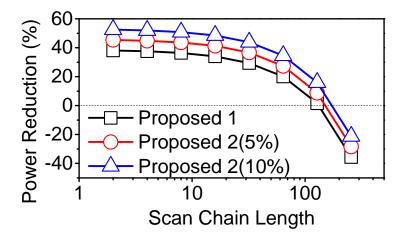

| 3.22 | 2 The relationship between the power reduction and the scan chain           |    |

|      | length. In this simulation, the standard deviations of the intrinsic        |    |

|      | switching current distribution were set to $5\%$ and $10\%,$ and $50\%$ of  |    |

|      | the registers were switched.                                                | 82 |

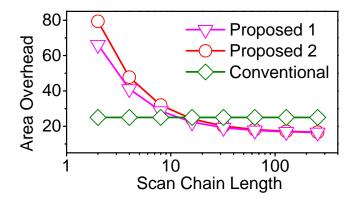

| 3.23 | 3 Normalized area overhead. The area is normalized to the minimum           |    |

|      | width transistors                                                           | 83 |

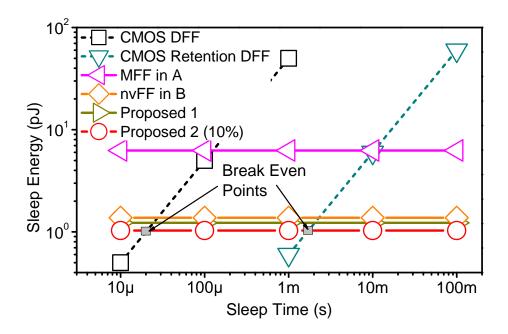

- 3.24 The sleep power consumption comparison among conventional structures and our proposed schemes.  $\eta$  is set to 10%. The sleep energy for MFF and nvFF are based on a single cell. A: [9]; B: [11]. . . . . 84

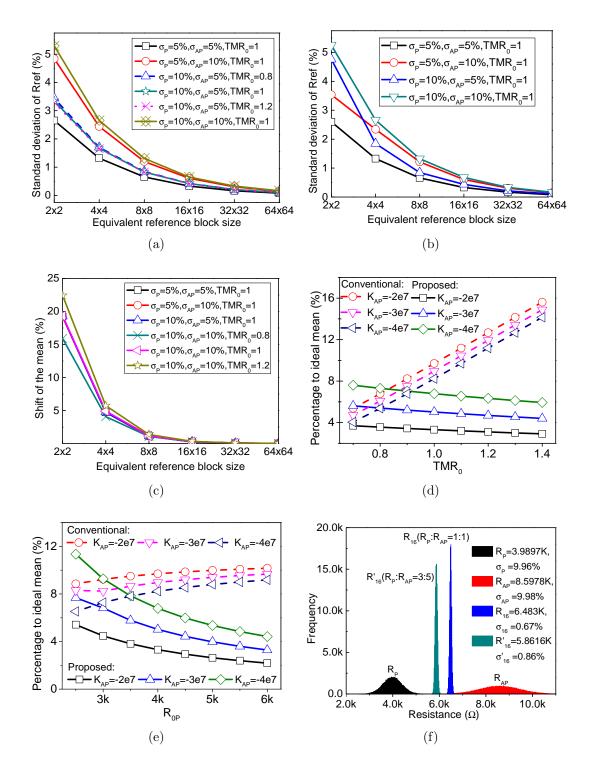

- 3.25 Python simulation results for distribution and deviation versus different equivalent reference block size. Distribution of the 16 × 16 equivalent reference array versus  $\sigma_P$  and  $\sigma_{AP}$  (a) without write failure and (b) with one AP cell stuck to P state; (c) Shift of the mean versus different equivalent reference block size; Deviation from the ideal mean versus (d) TMR ( $R_{0P} = 4000$ ) and (e)  $R_P$  ( $TMR_0 = 1$ ) with different slope of  $R_{AP}$ , where  $I_{read} = 20\mu A$ , N = 16; (f) Circuits simulation results for equivalent 16 × 16 reference block size. The standard deviations of both  $R_P$  and  $R_{AP}$  are set to 10% . . . . 86

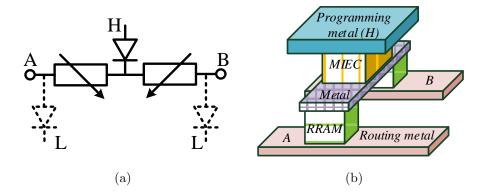

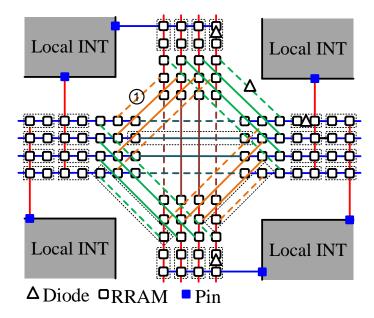

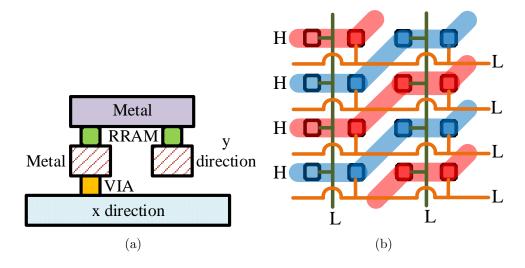

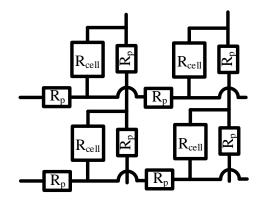

- 4.3 (a) Top view structure of the proposed stacking RRAM based n-vFGPA, (b) schematic diagram of the memory in our proposed nvF-PGA system. The RRAM cells are arranged using '1D2R' crossbar array structure.

94

- 4.4 The schematic of our proposed '1D2R' based non-volatile FPGA.The crossbar structure is used for both CB and local interconnect. 95

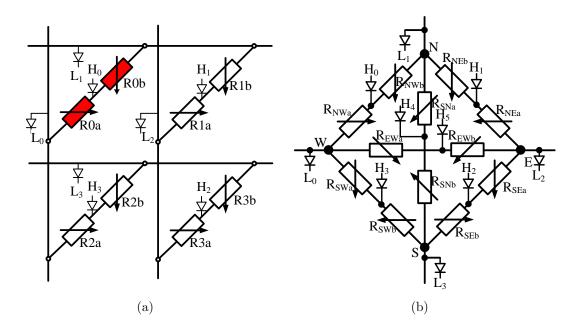

- 4.5 The schematic view of '1D2R' based (a) non-volatile crossbar array structure; (b) non-volatile switch point (SP). The non-volatile crossbar array is used in the CB and local interconnect. . . . . . . . 96

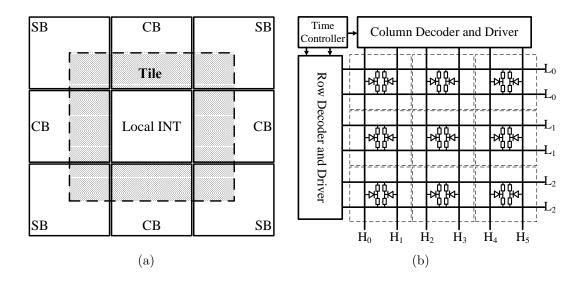

| 4.6  | The SB and CB structures used in the proposed nvFPGA. The                      |     |

|------|--------------------------------------------------------------------------------|-----|

|      | switch box is based on Universal architecture. To simplify, the                |     |

|      | '1D2R' storage elements show only two RRAM cells in the dash                   |     |

|      | line boxes                                                                     | 97  |

| 4.7  | Our proposed '1D2R' based non-volatile look-up table. It is an                 |     |

|      | example of a 2-input LUT, and it can be extended to the other                  |     |

|      | LUT size.                                                                      | 99  |

| 4.8  | (a) The cross-section view of the switch in CB; (b) our proposed               |     |

|      | crossbar routing architecture to program the RRAM cells. $\ldots$ .            | 101 |

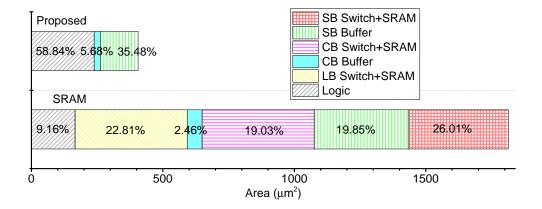

| 4.9  | Area consumptions of the SRAM-based FPGA tile and our pro-                     |     |

|      | posed '1D2R' based FPGA tile. The switch and SRAM area in our                  |     |

|      | proposed '1D2R' based scheme is negligible because they are placed             |     |

|      | on top of the CMOS circuits.                                                   | 103 |

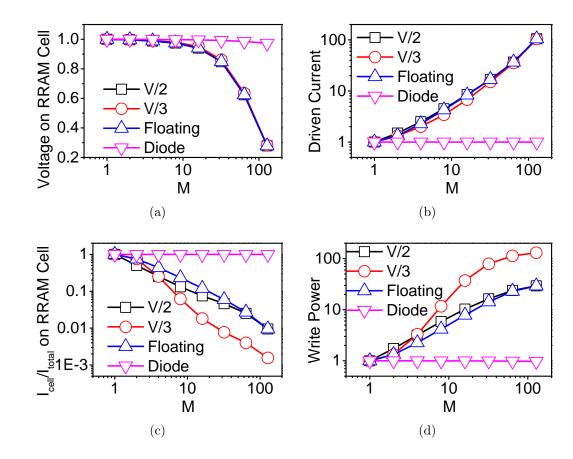

| 4.10 | A simulation diagram of the diode-less or transistor free crossbar             |     |

|      | array with parasitic resistance $({\cal R}_p)$ in the word lines and bit lines | 104 |

| 4.11 | (a) The normalized write voltage across the selected RRAM cell;                |     |

|      | (b) the normalized required current at the input driver of the bit             |     |

|      | line or word line; (c) the write current analysis of different RRAM            |     |

|      | array schemes; (d) the normalized total write power. All results are           |     |

|      | normalized to the one single RRAM cell                                         | 105 |

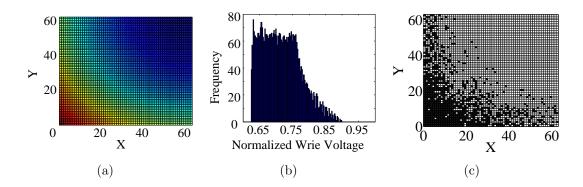

| 4.12 | (a) The write voltage distribution in a $64\times 64$ diode-less crossbar      |     |

|      | RRAM array due to the parasitic resistance in the word lines and               |     |

|      | bit lines; (b) the histogram plot of the normalized write voltage              |     |

|      | distribution in a $64\times 64$ diode-less crossbar RRAM array; (c) the        |     |

|      | programming results in the $64\times 64$ diode-less crossbar RRAM ar-          |     |

|      | ray. Black color represents successfully programmed cells and white            |     |

|      | color represents unprogrammed cells                                            | 106 |

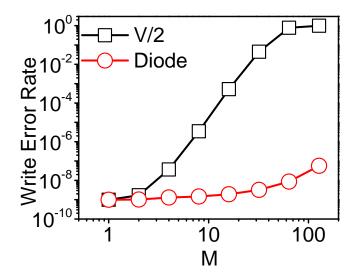

| 4.13 | The write error rate comparison between $V/2$ write scheme and the                                                 |

|------|--------------------------------------------------------------------------------------------------------------------|

|      | scheme using diode as the selector                                                                                 |

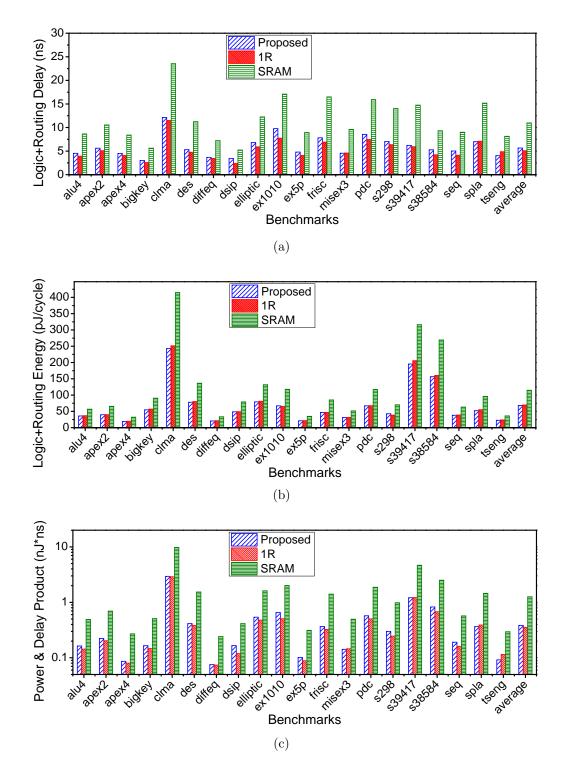

| 4.14 | (a) The delay simulation results; (b) the power simulation results;                                                |

|      | (c) the power and delay product results. The three schemes are                                                     |

|      | simulated based on 20 MCNC test benches with VPR and the power $% \mathcal{A}$                                     |

|      | model in $[12, 13]$                                                                                                |

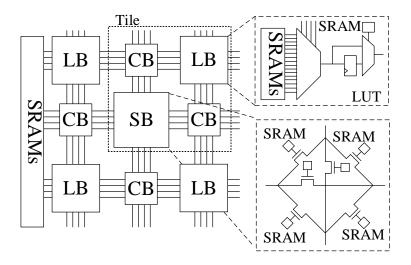

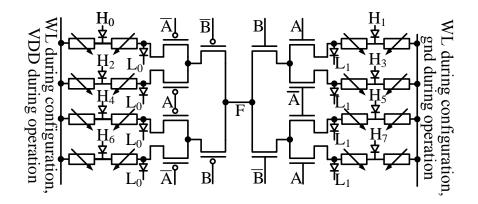

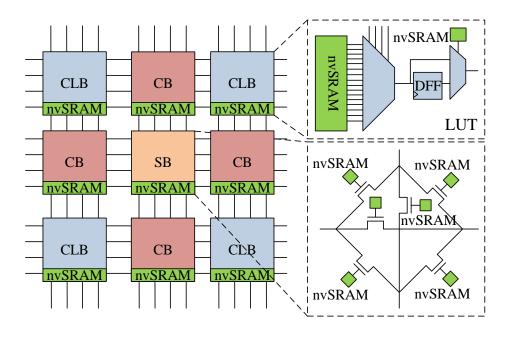

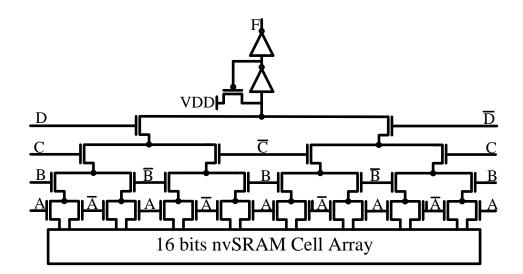

| 5.1  | The proposed nvSRAM based FPGA Architecture. 6T SRAMs are                                                          |

|      | replaced by our proposed nvSRAMs. SB, CB and CLB are switch                                                        |

|      | block, connection block and configurable logic block, respectively. $% \left( {{{\bf{n}}_{\rm{s}}}} \right)$ . 114 |

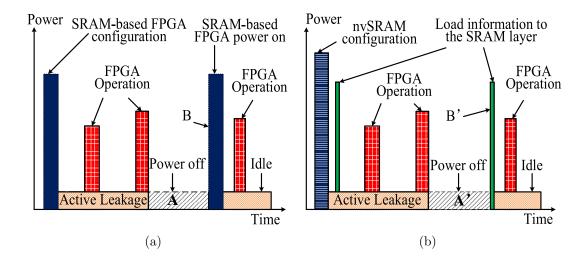

| 5.2  | The power consumption of the (a) SRAM-based FPGA and (b) our                                                       |

|      | proposed nvSRAM-based FPGA in different operation modes 115 $$                                                     |

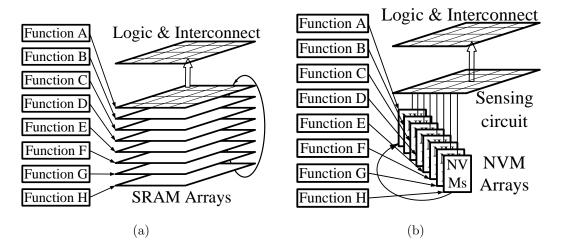

| 5.3  | (a) Conventional SRAM-based multi-context FPGA; (b) Proposed                                                       |

|      | nvSRAM based multi-context FPGA                                                                                    |

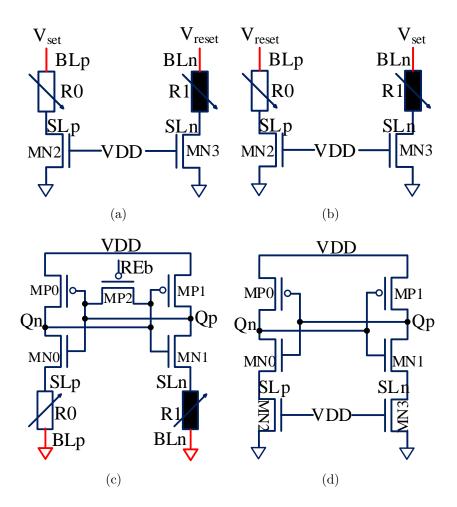

| 5.4  | The proposed single-context nvSRAM. The signals $BL_p$ and $BL_n$                                                  |

|      | are shared with other nvSRAMs in the same column                                                                   |

| 5.5  | The proposed single context in the (a) write mode, (b) read mode,                                                  |

|      | and (d) FPGA execution mode                                                                                        |

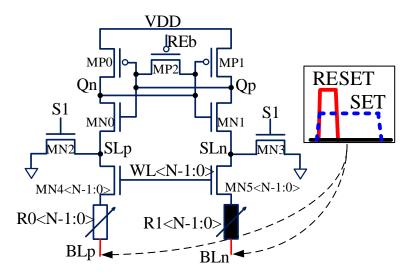

| 5.6  | The proposed multi-context nvSRAM. The signals $BL_p$ and $BL_n$                                                   |

|      | are shared with other nvSRAMs in the same column                                                                   |

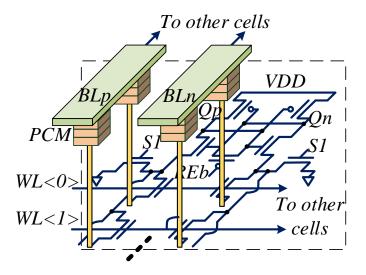

| 5.7  | A schematic of the nvSRAM 3D integration. The phase change                                                         |

|      | material is deposited in the format of thin-film on the top of the                                                 |

|      | CMOS transistors                                                                                                   |

| 5.8  | The 4-input LUT structure used to evaluate the proposed nvSRAM. 123                                                |

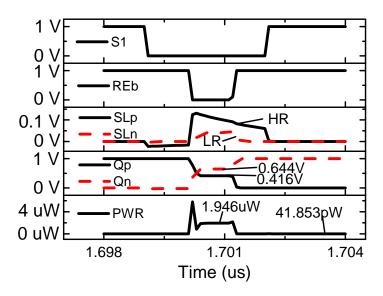

| 5.9  | The power and delay simulation results of the proposed nvSRAM                                                      |

|      | when loading the states from PCM cells to the latch                                                                |

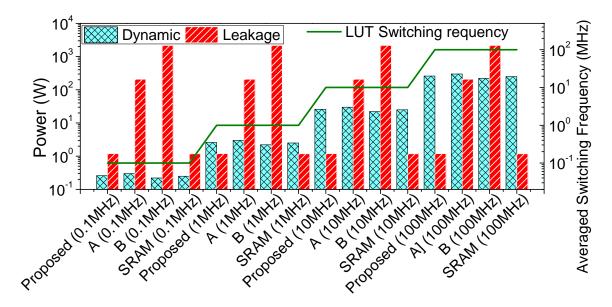

| 5.10 | The power consumption comparison among different LUT architec-                                                     |

|      | tures. A: [2]; B: [3]                                                                                              |

|      |                                                                                                                    |

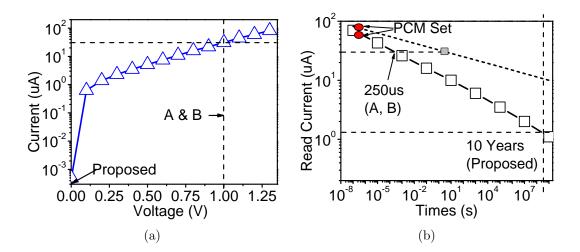

| 5.11 | (a) IV curve of the PCM cell in the amorphous state. (b) the PCM            |       |

|------|-----------------------------------------------------------------------------|-------|

|      | retention of the designs in $[2,3]$ , and our proposed nvSRAM. A: $[2]$ ;   |       |

|      | B: [3]                                                                      | . 127 |

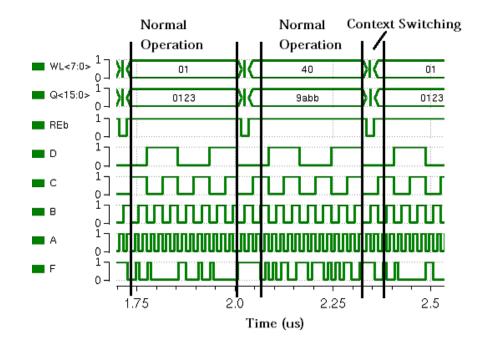

| 5.12 | The RTR simulation results of the proposed 8-context nvSRAM                 |       |

|      | based 4-input LUT                                                           | . 128 |

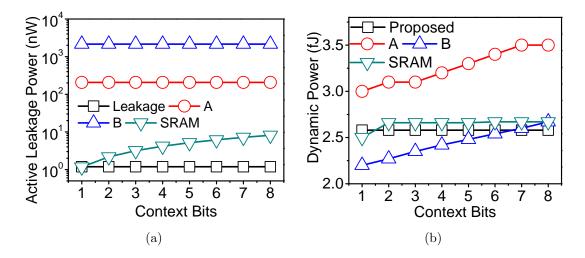

| 5.13 | the 4-input LUT (a) active leakage power and (b) dynamic power              |       |

|      | comparison among the 6T SRAM, the designs in $[2, 3]$ , and the             |       |

|      | proposed nvSRAM. A: [2]; B: [3]. $\ldots$ $\ldots$ $\ldots$ $\ldots$        | . 129 |

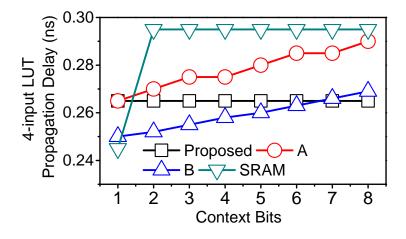

| 5.14 | The propagation delay comparison among the 6T SRAM, the de-                 |       |

|      | signs in $[2,3]$ , and the proposed nvSRAM based 4-input LUTs.              |       |

|      | A: [2]; B: [3]                                                              | . 130 |

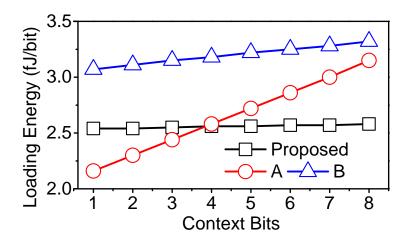

| 5.15 | 4-input LUT loading power comparison among the 6T SRAM, the                 |       |

|      | designs in [2,3], and the proposed nvSRAM. A: [2]; B: [3]. $\ldots$         | . 130 |

| 5.16 | 8-context 4-input LUT power comparison among the designs in [2,             |       |

|      | 3], and the proposed nvSRAM. All of the results are normalized to           |       |

|      | the SRAM based 8-context 4-input LUT under the same conditions.             |       |

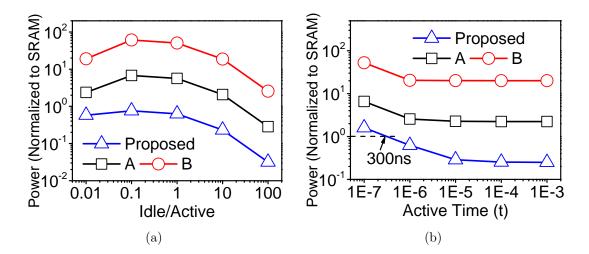

|      | The average LUT switching frequency is set to 10MHz. (a) The                |       |

|      | power consumption versus the ratio of idle time and active time.            |       |

|      | The active time is set to $1ms$ . (b) The power consumption versus          |       |

|      | the active time. The ratio of idle time and active time is 0.9. A: $[2]$ ;  |       |

|      | B: [3]                                                                      | . 131 |

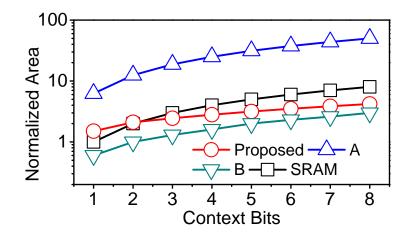

| 5.17 | Area comparison among the 6T SRAM, the design in $\left[2\right]$ and our   |       |

|      | proposed nvSRAM. The area is normalized to the single context $6\mathrm{T}$ |       |

|      | SRAM. A: [2]; B: [3]                                                        | . 132 |

#### Abstract

The increasing leakage current in the complementary metal oxide semiconductor (CMOS) circuits due to technology nodes scaling down has been one of the critical issues in the current generation digital circuits and field programmable gate arrays (FPGAs). There are growing research effort in the integration of resistive non-volatile memory (NVM) cells to achieve low power high performance circuits. Although the reported circuits help to minimize the sleep power consumption of the system, there are various drawbacks that limit the performance or reliability of the circuits.

This dissertation presents new schemes for both digital circuits and FPGAs to achieve low power and high performance circuits. The new non-volatile flip-flops (nvFFs) and localized NVM array based on spin transfer torque MRAM (STT-MRAM) are proposed to retain the states of registers during standby. Both designs are targeting for the low VDD and low write power. The nvFF can be designed as a standard cell to be compatible with digital design flow thus the design cycle could be greatly reduced. The localized NVM array could further reduce the power consumption with higher density. The non-volatile storage elements proposed for the non-volatile FPGAs (nvFPGAs) are targeting for the high reliability, high density and low power. Compared to the conventional nvFPGAs, the reliability is significantly improved and power is greatly reduced, while compared to the static random access memory (SRAM) based FPGAs, the FPGA area and power could be greatly reduced.

# Chapter 1

# Introduction

# 1.1 Motivation

CMOS logic technology nodes have been scaled down for more than 40 years [14–18] to achieve higher density and better performance. According to Moore's law, the transistor dimensions are scaled down by 30% (0.7×) every technology generation, and therefore increases operating frequency by about 40% (1.4×) [19]. To keep electric field constant and maintain a high drive current, supply voltages and threshold voltages have been scaled down in proportion to metal oxide semiconductor field effect transistor (MOSFET) device dimensions, resulting in an exponential increase in sub-threshold leakage [20,21]. Consequently, the standby leakage power dissipation is rapidly becoming a substantial contributor to the total power dissipation in memories or state retention in duty cycled systems. For those standby-power-critical systems, which have long idle times punctuated by bursts of activity, such as cell phones, tablet laptops and wireless sensor networks, this standby power consumption reduces the effectiveness of duty-cycling. Large standby leakage power by significant challenge to achieve the goal of low power.

To address the high standby leakage power issue in battery powered sys-

tems, increasing battery capacity and harvesting energy from the environment are two possible solutions. However, the energy density of the battery is improved by less than 7% every year [22]. Alternatively, the energy scavenging could compensate the leakage power loss during standby. However, according to the research records from National Renewable Energy Laboratory (NREL), the energy harvest efficiency gains by less than 1% every year [23]. Therefore, other solutions are required to reduce the leakage power.

There are four main sources cause the leakage current in a CMOS transistor [24]: 1. Reverse-biased junction leakage current; 2. Gate induced drain leakage; 3. Gate direct-tunneling leakage; 4. Subthreshold (weak inversion) leakage. Among these four leakage sources, "gate induced drain leakage" is not a component of the leakage of an OFF state transistor. The "subthreshold leakage" is the drain-source current of a transistor operating in the weak inversion region, in which the diffusion current of the minority carriers dominates. The magnitude of the subthreshold current is a function of the temperature, supply voltage, device size, and the process parameters [24]. Among these parameters, the threshold voltage  $(V_{th})$  plays a dominant role.

In current CMOS technologies, the relatively low  $V_{th}$  due to scaling makes the subthreshold leakage current  $(I_{SUB})$  much larger than the other leakage current components.  $I_{SUB}$  is calculated by using the following formula [24]:

$$I_{SUB} = \frac{W}{L} \mu \nu_T^2 C_{sth} e^{\frac{V_{GS} - V_{th} + \eta V_{DS}}{n\nu_T}} (1 - e^{-\frac{V_{DS}}{\nu_T}})$$

(1.1)

where W and L are the transistor width and length, respectively.  $\nu_T = kT/q$  is the thermal voltage at the temperature T,  $C_{sth} = C_{dep} + C_{it}$  denotes the summation of the depletion region capacitance per unit area of the MOSFET gate and the interface trap capacitance per unit area of the MOSFET gate,  $\mu$  and  $\eta$  denote the carrier mobility and the drain induced barrier lowering (DIBL) coefficient [25], respectively. n is the slope shape factor and is calculated as:

$$n = 1 + \frac{C_{sth}}{C_{ox}} \tag{1.2}$$

where  $C_{ox}$  denotes the gate input capacitance per unit area of the MOSFET gate. When a transistor is in the OFF state  $(V_{GS}=0)$ , the subthreshold leakage can be reduced by increasing  $V_{th}$  or reducing  $V_{DS}$ . Multiple threshold voltage levels [26, 27], well-bias control [28, 29] have been used to increase  $V_{th}$ , and stack effect based method [30], VDD reduction and power gating (PG) [31–34] have been used to reduce  $V_{DS}$ . Among these techniques, PG is one of the most effective means, in which inactive blocks are turned off by inserting a high threshold sleep transistor between the power supply and digital circuits. This scheme is efficacious for reducing leakage power when a large scale integrated (LSI) function block is in the sleep state. However, part of the blocks need to be powered on due to the volatile nature of retention registers. Therefore, the leakage still exists in both logic circuits and decoupling capacitors. Moreover, the wake-up process, *i.e.*, transition from sleep to active mode, involves a large rush current through the sleep transistors. Due to the inductance from power rails and packages, this rush current can cause Ldi/dt noise, which is manifested as ground bounce when a footer is used, or as VDD fluctuation when a header is used [35–37]. PG control should be carefully designed so that the integrity of the data in retention elements is guaranteed.

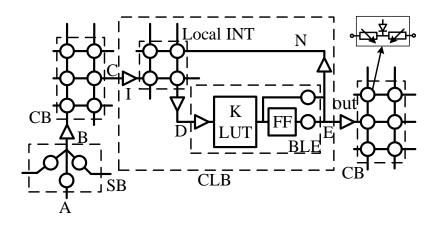

As the counterpart of the application specific integrated circuits (ASICs), FPGAs have been rapidly growing in the integrated circuit (IC) market share due to the post-fabrication reconfigurability, fast time to market, design fault tolerant, and low development cost. Hence SRAM-based FPGA logic circuits have been under focused development in the past 20 years [38–41]. SRAMs are used to configure logics and routing information to realize the required functionalities. FPGA interconnects including switch blocks (SBs), connection blocks (CBs), and configuration SRAMs account for around 80 - 90% of the total area, delay and power. In contrast, the logic blocks (LBs) occupy only 10 - 20% of the total area [42–44]. Thus, reducing the length of interconnects and improving the configuration memory cells are the key of the FPGA design.

Additionally, SRAM-based FPGAs require reprogramming each time when powering on, because SRAMs lose the configuration information after powering down. Moreover, as CMOS technology nodes scale down to 90*nm* and below, the leakage power has rapidly become the dominant component of total power dissipation [45, 46]. As a result, SRAM-based FPGAs suffer from slow power-on speed, high power-on power and leakage power. The high power-on power and slow power-on speed limit the power-off opportunities of the FPGA. In other words, it is not possible to power off the FPGA when the idle time between two events is short. Moreover, additional external NVM is required to store the configuration information.

Integrating NVMs in the CMOS circuits is an effective solution to reduce the leakage current. By replacing the dynamic random access memory (DRAM) or SRAM in FPGAs, or retaining the states of the registers into the NVMs, the whole system can be fully powered off without losing information. However, the conventional nvFF and nvFPGA schemes suffer from various weaknesses including high VDD, high write power, high active leakage power, low read/write reliability, etc. The details of the related works will be discussed in Section 1.4. Therefore, new integration solutions and architectures are required to address various weaknesses in the conventional resistive NVM based flip-flops (FFs) and FPGAs. In this dissertation, we will propose several schemes to design the non-volatile latch (nvLatch) or the localized array to replace the retention registers for the standby power free systems. In addition, new FPGA storage elements/architecures are proposed based on the resistive NVMs to achieve the low power, high performance and high density.

# 1.2 Resistive NVMs

The conventional FLASH memory has been used to achieve low power systems. Each memory cell in a FLASH memory consists of only one MOSFET with an additional floating gate. In spite of the wide application of FLASH memories in commercial products, e.g. digital cameras, memory sticks and tablets, the current FLASH memory technology has various disadvantages. The primary limitation of FLASH memory is that while their design is superb for 5V operation, while the standard logic level has decreased from 5V to 3.3V to 1V and will eventually decrease to 0.5V in the coming years. FLASH memories (based on the Fowler-Nordheim tunneling) cannot reliably function at 0.5V. The remedy by inserting internal 'charge pumps' for programming will decrease yields, increase cost and failure mechanisms [47]. The other disadvantages are much longer write and erase times and much lower write/erase cycles (1e5) than DRAM, as shown in Table 1.1). In addition, the FLASH memory technology will touch the miniaturization limit when the lateral feature size of DRAMs and FLASH memories shrinks down to 21nm (for DRAM technology 2016 and for FLASH technology 2013) [1,48,49]. In a summary, the conventional FLASH, is facing limitations of the scale down, endurance, speed and operation voltage.

Fortunately, the emerging memories may address the limitations of the FLASH memory [1, 48, 49]. There are more than a dozen non-volatile memories have been considered as emerging memories. For example, resistive random access memorys (RRAMs) [50–61], magnetic RAMs (MRAMs) [11, 62–66], phase change memorys (PCMs) [67–74], carbon nanotube memory [75], racetrack memory [76, 77], ferroelectric RAMs (FeRAMs) [78], millipede memory [79], molecu-

|                | Baseline Technologies |           |           |                   | Prototypical Technologies |             |            |

|----------------|-----------------------|-----------|-----------|-------------------|---------------------------|-------------|------------|

| Type           | SRAM                  | DRAM      | NOR-      | NAND-             | MRAM                      | PCM         | RRAM       |

|                |                       |           | Flash     | Flash             |                           |             |            |

| Cell elementes | 6T                    | 1T1C      | 1T        | 1T                | 1T1R                      | 1T(D)1R     | 1T(D)1R    |

| Storage Mech-  | Latch                 | Stack     | Floating  | Floating          | Magneti -                 | phase-      | resistance |

| anism          |                       | /trench   | gate      | gate              | zation                    | change      | change     |

|                |                       | capacitor | /charge   | /charge           |                           |             |            |

|                |                       |           | trap      | trap              |                           |             |            |

| Feature size   | 45 nm                 | 36 nm     | 90nm      | 22nm              | 65 nm                     | 20nm        |            |

| Cell area      | $140F^{2}$            | $6F^{2}$  | $10F^{2}$ | $4F^{2}$          | $20F^{2}$                 | $4F^{2\ b}$ | $4F^{2}c$  |

| Write/ erase   | $0.2 \mathrm{ns}/$    | < 10 ns/  | 1us/ 10m- | $1 \mathrm{ms}/$  | 35 ns/                    | 10 ns/      | 5ns/5ns    |

| time           | 0.2 ns                | < 10 ns   | S         | $0.1 \mathrm{ms}$ | 35ns                      | 100ns       | [83]       |

| Endurance      | >1e16                 | >3e16     | >1e5      | >1e4              | >1e12                     | 1e9         | >1e10      |

| (Cycles)       |                       |           |           |                   |                           |             | [84]       |

| Write Opera-   | 1                     | 2.5       | 10        | 15                | 1.8                       | 3           |            |

| tion Voltage   |                       |           |           |                   |                           |             |            |

| (V)            |                       |           |           |                   |                           |             |            |

| Write Energy   | 5e - 16               | 4e - 15   | 1e - 10   | >2e - 16          | $2.5e{-12}$               | 6e - 12     |            |

| (J/bit)        |                       |           |           |                   |                           |             |            |

Table 1.1: Comparison of conventional and emerging memories. Most data other than those of RRAMs were taken from [1].

lar memory [80], programmable metallization cells (PMCs) memory [81], DNA memories [82], etc. Among these memories, RRAMs, MRAMs and PCMs have been considered as emerging memories to potentially overcome the limitations of DRAMs and FLASH memories. Unlike FLASH and DRAM which use charge as the information carrier, RRAMs, MRAMs and PCMs rely on non-volatile, resistive information storage in the memory cells, thus exhibit zero standby power consumption, and hold the potential to scale to much smaller geometries than charge memories. These characteristics, coupled with their CMOS-compatibility, fast read/write speed, high density and write endurance, make resistive memories promising candidates for storing the register information with no off-state leakage current. They also provide an excellent opportunity to achieve high speed, high density, instant power on and superior energy efficiency FPGAs. The comparison between the conventional and emerging memories is given in Table 1.1.

A cross section schematic shown in Fig. 1.1 illustrates the integration process of the resistive NVMs in the CMOS process. The CMOS front end process includes the bottom substrate, CMOS layers, and metal layers. The CMOS-

Figure 1.1: CMOS Front End Process and STT-MRAM Back End Process

compatible back end process deposits the resistive NVM layer between two metal layers (top electrode (TE) and bottom electrode (BE)). magnetic tunnel junction (MTJ) is used in this example, but it worths noting that the MTJ layer could be RRAM, PCM or other resistive NVMs.

#### 1.2.1 STT-MRAM

MRAMs that have been considered as possible candidates to replace several types of current memories such as embedded SRAMs, DRAMs and FLASH memories. There are two main types of MRAMs have been developed: field-writing MRAM and STT-MRAM. The field writing MRAM is written by a magnetic field around the current line. The primary issue of field-write MRAM is the high write current, which makes scaling down difficult.

STT-MRAM has combined the advantages of SRAMs (high speed), DRAMs (scalability) and FLASH memories (non-volatility) [85], promising it as a next-generation memory candidate. However, the OFF/ON ratio is big concern since low resistance ratio leads to low read reliability. Another concern is the high

energy dissipation during operation.

Figure 1.2: (a) Block diagram of a 1T1MTJ structure of an STT-MRAM cell. (b) Writing from P to AP state. (c) Writing from AP to P state

A typical STT-MRAM structure is illustrated in Fig. 1.2(a). The MTJ device has a low resistance of  $R_P$  when the magnetic moment of the free layer is parallel to that of the pinned layer (P-state) and a high resistance of  $R_{AP}$  when the free layer moment is oriented anti-parallel to the pinned layer moment (AP-state). When the current flows from BE to TE, the MTJ switches from P-state to AP-state  $(P \rightarrow AP)$ , as shown in Fig. 1.2(b). If the current flows in the opposite direction, the MTJ changes from AP-state to P-state  $(AP \rightarrow P)$ , as shown in Fig. 1.2(c). The tunnel magnetoresistance (TMR) ratio of an MTJ cell is defined as  $TMR = (R_{AP} - R_P)/R_P$ . The resistance of a STT-MRAM cell can be expressed as:

$$R_{MTJ} = |I_{MTJ}| * K_{MTJ} + R_0 \tag{1.3}$$

where  $I_{MTJ}$  is the current goes through the MTJ cell in either direction,  $K_{MTJ}$ is the slope of  $R_{MTJ}$ ,  $R_0$  is the zero current resistance.  $K_{MTJ}$  has two values  $K_P$ and  $K_{AP}$ , which are the slope of  $R_P$  and  $R_{AP}$ , respectively.  $R_0$  also has two values  $R_{0P}$  and  $R_{0AP}$ , which are the  $R_P$  and  $R_{AP}$  value when  $I_{MTJ} = 0$ .

Usually the distributions of the values of  $R_P$  and  $R_{AP}$  follow a Gaussian

distribution [86, 87] which can be written as

$$f(R) = \frac{1}{\sqrt{2\pi(\sigma_{MTJ} * R_{MTJ})^2}} e^{-\frac{(R-R_{MTJ})^2}{2(\sigma_{MTJ} * R_{MTJ})^2}}$$

(1.4)

where  $\sigma_{MTJ}$  is the deviation in percentage for  $R_{AP}$  or  $R_P$ .

At a finite temperature, thermal agitation plays an important role in reducing the switching current at long switching pulses (>10ns) [88,89]. In this slow thermal activated switching regime, the switching pulse width is dependent on the switching current amplitude and thermal stability factor  $\Delta = K_u V/k_B T$  of the free layer, where  $k_B$  is the Boltzmann's constant, T is the temperature, and  $K_u V$  is anisotropy energy. A model that describes the correlation of the parameters was proposed by Néel-Brown [90]:

$$J_c = J_{c0} \left(1 - \frac{1}{\Delta} ln(\frac{T_{WR}}{\tau_0})\right)$$

(1.5)

where  $T_{WR}$  is the pulse width of switching current,  $\tau_0$  is the inverse of the attempt frequency, and  $J_{c0}$  is the intrinsic switching current density. The intrinsic current density  $J_{c0}$  required for current driven magnetization reversal in an MTJ with the magnetization in the film plane can be expressed as

$$J_{c0} = \left(\frac{2e}{\hbar}\right)\left(\frac{\alpha}{\eta}\right)\left(t_F M_s\right)\left(H_k + 2\pi M_s\right) \tag{1.6}$$

where  $M_s$  and  $t_F$  are the magnetization and thickness of the free layer respectively,  $\alpha$  is the damping constant, and  $H_k$  is the effective anisotropy field including magneto-crystalline anisotropy and shape anisotropy. The spin transfer efficiency  $\eta$ , is a function of the current polarity, polarization, and the relative angle between the free and pinned layers. When  $J_c > J_{c0}$ , an initial stable magnetization state of the free layer along the easy axis becomes unstable at zero temperature and the magnetization enters a stable precessional state or a complete reversal occurs. From (1.5), one can estimate the critical current density  $J_{c0}$  by extrapolating the experimentally observed switching current density  $J_c$  at  $t = \tau_0$ . For fast precessional switching in nanosecond (ns) regime (less than a few ns), the required switching current is several times greater than the instability current  $J_{c0}$  [88,89]. The switching current density can be estimated as

$$J_c = J_{c0} + \frac{Cln(\pi/2\theta)}{T_{WR}} \tag{1.7}$$

where  $\theta$  is the initial angle between the magnetization vector of the free layer and the easy axis, and C is the fitting parameter. At finite temperature,  $\theta$  is a thermal distribution.

The probability that a data of the STT-MRAM is switched for a given time t at least unit time is expressed by using the Poisson distribution [88,91,92]:

$$f_{switch}(I,t) = 1 - e^{-\frac{t}{t_p}}$$

(1.8)

where  $t_p$  is derived from (1.5),  $I = J_c \times A$  is the writing current amplitude, and A is the area of the MTJ.

Read disturbance is related to the margin between the read and write currents. The probability that the read disturbance occurs at a given read current  $I_{read}$  is given by

$$P = \int_0^{I_{read}} f_{switch}(I) dI \tag{1.9}$$

More intuitively, if the read disturbance rate of a M Gb STT-MRAM is 1ppm, P is smaller than  $1/(N \times M \times 1024^3 \times 10^6)$ .

To achieve low read disturbance, i.e. accidental writing of a bit while trying to read the bit, the read current has to be much smaller than the median critical current [88]. Assuming that all other parameters remain the same but with 5% deviation in the median critical current, the read disturbance probability is increased by several orders of magnitude at a specified read current [88]. The read current has to be reduced to about 20% the median critical current to maintain the same level of read disturbance error rate.

#### 1.2.2 PCM

It has been more than four decades since the first idea to use phase-change materials in memory devices [93, 94]. However, the low material quality and high power consumption of this technology prevented it from the commercialization. In the last few decades, the great improvement in the semiconductor manufacturing technology and the quality of PCM provides the phase-change material based NVMs a second life.

The PCM provides the benefits of high density [95], high scalability [96], low cost [97] and high resistance ratio  $(R_H/R_L)$  [98, 99]. The  $4F^2$  small PCM cell size based on 20nm technology node has been achieved by Samsung [100, 101]. The high resistance ratio between the Amorphous (*RESET*) and Crystalline (*SET*) states increases the read reliability and the sense speed. Moreover, PCM also has the potential to achieve nano-second [102–104] and sub micro-ampere current switch [105]. PCMs are expected to replace NOR-FLASH memories in the memory market at present. Recent progress in PCM technology has provided a clear demonstration of the excellent scaling potential to and beyond the 16nm generation [70].

The typical PCM structure is a chalcogenide layer (*i.e.*, Ge2Sb2Te5, or GST) sandwiched between a metal contact and a heat electrode. Phase-change materials exhibit an ability for reversible phase transition between the Amorphous and Crystalline phases with the help of Joule heating. This phase transition brings about a change in the resistance as well as the reflectivity. The heat produced by the passage of an electric current through the heating element is used to transform the material between the poly-crystalline and amorphous states. As shown in Fig. 1.3, if the chalcogenide material is quickly heated (melting) and quenched (rapid cooling), it will be reset to the amorphous state (high resistance state,  $R_H$ , binary '0'). On the other hand, if the material is held in its crystallization

Figure 1.3: Phase change materials reversibly switch between amorphous and poly-crystalline states by electrical pulses.

temperature range for some time (annealing), it will be set to the poly-crystalline state (low resistance state,  $R_L$ , binary '1'). The cell resistance between the polycrystalline and amorphous states may have orders difference. Therefore, as shown in Fig. 1.3, *RESET* (quickly heating and quenching) requires short pulse and high voltage, while *SET* (holding in crystallization temperature) requires long pulse and medium voltage. To avoid unintended write, the read voltage should be much lower than the *SET* voltage.

#### 1.2.3 RRAM

Resistive NVMs generally include all types of NVMs using two or more distinctive resistance states as the binary numbers '0' and '1'. In principle, PCMs and MRAMs could be considered as resistive NVMs as well. The resistive switch in each memory cell consists of a switching layer sandwiched by TE and BE. This capacitor-like switching cell is characterized by two distinctive resistance states: a high resistance state (HRS) and a low resistance state (LRS). The basic idea of the RRAM switch mechanism is that a dielectric, which is normally insulating, can be made to conductive through a filament or conduction path. The RRAM can be reversibly switched between HRS (filament broken) and LRS (filament reformed) by applying an appropriate voltage. Reversible resistive switching was observed in various materials, such as Nb2O5, Al2O3, SiO2 and TiO2 [106–110].

Figure 1.4: Possible combinations of set and reset I-V curves. The combinations can be 'positive set, positive reset', 'positive set, negative reset', 'negative set, positive reset' and 'negative set, negative reset'.

Several possible combinations of set and reset curves are shown in Fig. 1.4. For unipolar switching, the lower voltage acts as set and the higher voltage in the same direction acts as reset, whereas for bipolar switching only 'negative set, positive reset (eightwise)' or 'positive set, negative reset (counter eightwise)' is possible [111,112].

RRAM has the potential to become the front runner among the emerging NVMs. Compared to PCM, RRAM operates at a faster switching speed (less than 10ns). Compared to MRAM, it has a simpler process, smaller cell structure ( $4F^2$  metal insulator metal (MIM) stack), and higher resistance ratio. Compared to FLASH memory, it has a much lower switching voltage and much higher switching speed. The 30nm cell size of the RRAM has been demonstrated by Industrial

Figure 1.5: Break even point

Technology Research Institute (ITRI) recently [79], and it is believed that the oxygen motion may take place in regions as small as 2nm [113].

# 1.3 Resistive NVMs for Low Power

#### 1.3.1 Break Even Point (BEP)

Before the discussion of the applications of the emerging NVMs, we introduce the concept of break even point (BEP) which is an important merit to judge the power reduction benefit with the new NVMs. Most microelectronic systems spend considerable time in a standby state. The energy consumed by the non-volatile memory to save or restore the information must be considered carefully. If there no cost of transiting to and from a standby power state, the greedy policy of entering the low power state as soon as the system is idle may be adopted. Otherwise, the expected duration of the standby state must be accurately calculated and taken into account when devising a power management policy. When the sleep period is longer than BEP as shown in Fig. 1.5, the system could be power off to reduce the leakage power. BEP is defined by the time when the reduced sleep energy (area 3) equals to the energy required to save and restore the system (area 1 and 2, respectively). Therefore, the standby leakage power in area 4 is reduced. Otherwise, if the system is powered off when the standby time is short than BEP, the total power increases. Hence, the low saving and restoring energy should be the primary consideration when integrating NVMs in CMOS circuits to achieve zero standby power system.

#### 1.3.2 Using STT-MRAM as the Retention Register

As the discussed in Section 1.2, the intrinsic features of the three NVMs determine their applications in the integration in CMOS circuits. PCM and RRAM have simpler process and lower cost than STT-MRAM. However, the high program voltage of PCM [114,115] and RRAM [116,117] limits their integration in digital circuits, especially when the supply voltage scales down to 1V and below. Among these three candidates, STT-MRAM exhibits the advantages of fast switching speed between parallel (P) and anti-parallel (AP) states [58, 63, 118], and low switching current [118] or voltage [64], making it a potential candidate to be integrated with deep sub micron CMOS processes without a level shifter. Therefore, STT-MRAM is the best choice among these three candidates to replace the retention registers to achieve zero standby digital systems. This is because the states of the digital systems have to be saved to the NVM cells each time when powering down, and read them back to the digital systems each time when powering on. Hence, fast read/write speed and low read/write power are crucial to reduce the BEP. In other words, STT-MRAM allows the digital systems to be powered off in a much shorter idle period between two activities.

The state-of-art design to retain the states of the FFs during standby is the nvFF scheme, which has combined the FF and NVM in one cell. Hence it could be designed as a standard cell to design cycle. Saving the states to a NVM array is another solution, which could adopt more technique to improve the performance and reduce the BEP as well. But it has to be elaborated upon the size, area, architecture, etc. Otherwise, the total power may be increased.

## 1.3.3 Integrating RRAM/PCM in FPGAs

The emerging resistive NVM technologies with the advantages of high density, near zero power-on delay, and superior energy efficiency have provided an excellent platform to advance the FPGA technology. Since FPGAs only need to be programmed once during configuration, the slow write time and high write voltage may not an issue in such applications. In contrast, the low process cost and the high reliability due to high resistance ratio make PCM/RRAM more attractive in the FPGA applications.

Among them, RRAM becomes the front runner among resistive NVMs due to its fast switching speed (less than 10ns [59]), small cell size  $(4F^2 [119])$ , high resistance ratio [120], low switching voltage [121] and current [122], and compatible to current CMOS processes, etc. The six order resistance ratio of the RRAM has been demonstrated in [123]. These merits enable RRAM as a universal replacement of the SRAM and switch in the SRAM-based FPGAs. The states of the RRAM cells are configured as ON/OFF switches initially in the routing and logic blocks, thus achieving various functions as the conventional SRAM-based FPGAs. The new nvFPGA will achieve much higher density and greater reduction of the RC delay in the routing. Moreover, the RRAM-based switch also addresses the  $v_{th}$  drop issue in the SRAM-based FPGAs.

PCM could be a universal NVM [68] as well that provides the benefits of high density [95], high scalability [96], low cost [97] and high resistance ratio [99]. The  $4F^2$  small PCM cell size based on 20nm technology node has been achieved by Samsung [101]. The high resistance ratio between the amorphous (*RESET*) and poly-crystalline (*SET*) states increases the read reliability. Moreover, PCM also has the potential to achieve nano-second [102] and sub micro-ampere current switch [105]. Coupling with its low cost process, it is also a good choice to replace the SRAM in the conventional FPGAs. To replace the switch directly requires high resistance difference between the amorphous state and crystalline state, but it is only 2-3 orders currently.

Therefore, both RRAM and PCM could be design as non-volatile SRAMs (nvSRAMs) to configure the single-context FPGAs, or even multi-context FPGAs to achieve low power and high density. In addition, the high resistance ratio of the RRAM enables it a universal replacement of the switches and SRAMs to attain high performance and high density nvFPGAs.

# 1.4 Related Works

### 1.4.1 Non-volatile Latch/Flip-flop

Integrating the NVM into the digital circuits is an effective solution to retain the states of the FFs, thus the whole system can be fully powered off. In particular, it is only necessary for all FFs to be nonvolatile if the function blocks are clock-synchronized. Employing nvFF can provide a more efficient use of energy in System-on-Chips (SOCs) for standby-power-critical and quick-startup applications, especially the battery powered appliances. The nvFFs could be designed as standard cells to be compatible with the digital design flow, thus the design cycle could be greatly reduced.

Many nvFF works have been reported [4–9, 124, 125] to integrate NVMs in the latches or FFs to achieve zero standby power consumption systems. Though their proposed circuits have efficiently reduced the sleep power consumption of the system, their performance is limited by various weaknesses, such as updating MTJs states every clock cycle, latch is used as write driver, the "source degeneration" effect in the write path, serial write, etc. Table 1.2 summarizes different approaches

| nvFFs                            | Saving | Saving | Latch | Latch  | VDD  | Preferred    |

|----------------------------------|--------|--------|-------|--------|------|--------------|

|                                  | speed  | power  | speed | size   |      |              |

| Update MTJs<br>every clock cycle | Low    | High   | Low   | -      | -    |              |

| Update MTJs<br>before sleep      | High   | Low    | High  | -      | -    | $\checkmark$ |

| Serial write                     | High   | High   | -     | Large  | High |              |

| Parallel write                   | High   | Medium | -     | Medium | Low  |              |

| Two-phase write                  | Low    | Low    | -     | Small  | Low  | $\checkmark$ |

| MTJs inside the latch            | -      | -      | Low   | -      | -    |              |

| MTJs outside<br>the latch        | -      | -      | High  | _      | -    | $\checkmark$ |

| Latch as the write driver        | -      | -      | Low   | Large  | -    |              |

| Latch as the sense amplifier     | -      | -      | High  | Small  | -    | $\checkmark$ |

Table 1.2: Comparison among different approaches in the nvLatches/nvFFs.

implemented in those nvFFs.

There are growing research efforts in the integration of MTJs in the latches or FFs [4–9]. Although the reported circuits help to minimize the sleep power consumption of the system, there are several drawbacks limit the nvFFs performance as summarized below.

- 1. The requirement of updating MTJ states every clock cycle [4] and [8]. Updating MTJ states every clock cycle does not necessary reduce the sleep power consumption of the system. On the contrary, it increases the power consumption and reduces the speed during normal FF operation. Moreover, it also reduces the endurance of the MTJs. The states of the FFs only need to be retained in the MTJs during sleep mode.

- 2. The requirement of latch as write driver [5,8,9]. The use of the latch as part of the write driver may require large size transistors in the latch.

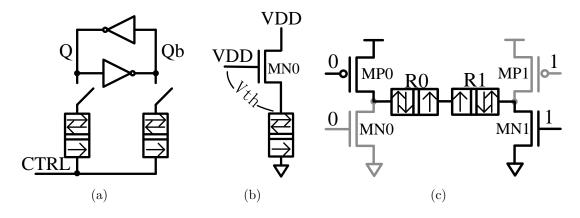

Figure 1.6: Existing approaches using nvLatches. (a) Latch is used as write driver; (b)  $V_{th}$  drop in the write path; (c) Serial write.

As a result, it not only slows down the latch operation speed due to the large parasitic capacitances, but also affects data integrity. For example, in Fig. 1.6(a) the write voltage on CTRL may flip the state of the latch before saving the state into the MTJs.

- 3. The "source degeneration" effect in the write path [5,6,8]. As shown in Fig. 1.6(b), the "source degeneration" effect caused by  $V_{th}$  drop in the write path limits the write current when the source of the transistor is connected to the MTJ. Therefore, higher VDD is required to pump in sufficient current into the MTJs to switch their states, resulting in high power consumption and area.

- 4. The serial write approach [4,6,7]. The serial write approach to store the states of FFs into the MTJs, as shown in Fig. 1.6(c), requires VDD to be higher than  $V_{P\to AP} + V_{AP\to P}$ , where  $V_{P\to AP}$  and  $V_{AP\to P}$  are the  $P \to AP$  and  $AP \to P$  switching voltages, respectively. Therefore, the serial write approach requires either high VDD or low  $V_{P\to AP}$  and  $V_{AP\to P}$ . The high VDD may result in high power consumption and scaling down difficulty. Low  $V_{P\to AP}$  and  $V_{AP\to P}$  may face long switching time.

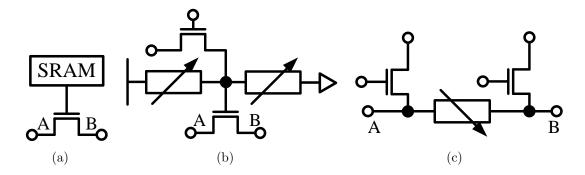

Figure 1.7: (a) Conventional SRAM storage element to configure FPGAs (S-RAM); (b) non-volatile storage element to configure the switch transistor in FP-GAs (1T2R); and (c) non-volatile storage element to replace the switch transistor and SRAM (2T1R, or '1R').

5. MTJs are embedded in the latch [4,7–9]. It may slightly reduce the FF operation speed by embedding the MTJ cells inside the latch.

#### 1.4.2 Non-volatile FPGAs

To address the leakage issue in the SRAMs, people are turning their attention to the emerging resistive NVM technologies. With the advantages of near zero poweron delay, dynamic reconfiguration, and superior energy efficiency, the nvFPGAs have been the object of intense development in the past few years. Many works have been reported to integrate RRAM [126], PCM [2,127] or STT-MRAM [128] in the FPGA circuits. FPGAs have the opportunity to significantly reduce the area, power and delay with emerging resistive NVMs. We categorize the conventional FPGA configuration memory technologies into three, i.e. SRAM, 2T1R, 1T2R, as shown in Figs. 1.7(a), 1.7(c) and 1.7(b), respectively.

1. SRAM. The SRAM-based FPGA storage element to configure the FPGA function as shown in Fig. 1.7(a) has three key weaknesses. First, SRAM-based FPGAs have to load the configuration information every time when powered on, which reduces the effectiveness of the off/on duty-cycling. Sec-

ond, to keep electric field constant and maintain a high drive current, supply voltages and threshold voltages have been scaled down in proportion to MOSFET device dimensions, resulting in an exponential increase in subthreshold leakage [20, 21]. Hence the leakage power dissipation of SRAMbased FPGAs is rapidly becoming a substantial contributor to the total power dissipation of FPGAs. The last one is the interconnects include SBs, CBs, and configuration SRAMs account for more than 80% of the total area, delay and power of the FPGAs [43, 44].

To improve the performance and reduce the area of FPGA, the NVM-based solutions are under focused development. There are two main solutions: 1T2R scheme and 2T1R scheme. However, both solutions have various weak-nesses that limit their feasibility to be integrated in FPGAs. The detailed will be discussed in the following.

2. **1T2R**. The '1T2R' scheme as shown in Fig. 1.7(b) was reported in [2,3,129–131] to replace the conventional SRAM cell with the NVM-based storage element to have the advantages of instant power-on and zero standby power. Unfortunately, it suffers from high active leakage power and low reliability issues, which limit their application in FPGAs. The high active leakage power and low reliability are caused by the insufficient  $R_H$ . The low reliability is caused by the low retention of RRAM/PCM cells with a bias voltage of VDD during operation.

One of the important concerns to integrate the NVM in FPGAs is its retention. The NVM may lose its advantage over other volatile memories if the states can only be retained a few seconds. For example, retention failure of PCM occurs when the phase-change material in the amorphous state is crystallized into the poly-crystalline state. The crystallization process can be accelerated by chip temperature and/or reading bias voltage [132], also named as thermal disturbance and read disturbance, respectively. The bias voltage on PCM cells will heat up phase change material. The crystallization speed of PCM is dependent on the temperature and increases when the temperature is higher. The elevated temperature due to the bias voltage will result in fast crystallization and hence poor retention. This is also one of the reasons to hold the read voltage much lower than *SET* voltage. Since the read voltage exponentially reduces the retention time [132], it is better to bias PCM cells at 0V during FPGA operation which could greatly improve their retention performance. The read disturbance not only exists in PCM, but is also one of the major issues in RRAM [133] and STT-MRAM [64], since the read operation shares the same current path as the write operation.

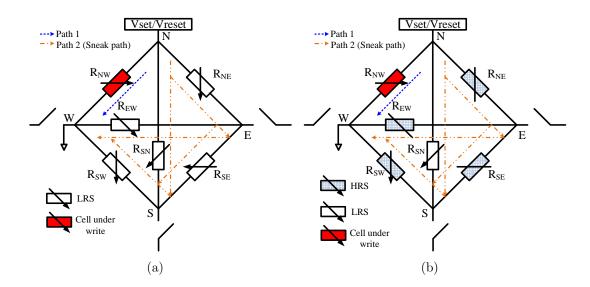

3. **2T1R**. The '2T1R' (or '1R') scheme as shown in Fig. 1.7(c) was suggested in [129, 134–136] to replace the NMOS switch and SRAM cell to achieve high speed and density. Although it addresses some of the issues in SRAM solution, it faces problems such as significant low write reliability and high write power due to the high leakage current in the sneak paths. For example, to program RRAM cell  $R_{NW}$  between nodes N and W in Fig. 1.8(a), the potential on N is at  $V_{set}$  or  $V_{reset}$  (where  $V_{set}$  and  $V_{reset}$  are the RRAM set and reset switching voltages, respectively) and the potential on node W is the ground. However, if  $R_{NW}$ ,  $R_{SN}$  and  $R_{SW}$  are at high, low and low resistance states, respectively, the majority current goes through  $R_{SN}$ and  $R_{SW}$ , resulting extremely large leakage current since the resistance of RRAM cells in HRS and LRS has two to six orders difference. Therefore, the current on  $R_{NW}$  may be insufficient to switch the selected cell. The write disturbance may worsen the write reliability. As shown in Fig. 1.8(b), if  $R_{NW}$ ,  $R_{SN}$  and  $R_{SW}$  are at high, low and high states, respectively, the potential on  $R_{NW}$  and  $R_{SW}$  is almost the same. As a result, both  $R_{NW}$  and

Figure 1.8: (a) The high leakage current issue, and (b) the write disturbance issue in the conventional RRAM based non-volatile SP. The en-dash lines are the paths to program the RRAM cells, and dash-dot-dot lines are the sneak paths.

$R_{SW}$  may be switched.