## Efficient Power Management for Heterogeneous Multi-Core Architectures

Thannirmalai Muthukaruppan Somu (B.S, State University of New York, Buffalo, 2009)

### A THESIS SUBMITTED FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

### DEPARTMENT OF COMPUTER SCIENCE SCHOOL OF COMPUTING NATIONAL UNIVERSITY OF SINGAPORE

$\boldsymbol{2014}$

# Declaration

- I hereby declare that this thesis is my original work and it has been written by me in its entirety.

- I have duly acknowledged all the sources of information which have been used in the thesis.

- This thesis has also not been submitted for any degree in any university previously.

Thannirmalai Muthukaruppan Somu July 2014

### Acknowledgements

The research contributions in this thesis would not have been possible without the guidance, advice, mentorship and supervision of several people.

First and foremost, I would like to express my deepest gratitude to my advisor Tulika Mitra. I still remember the day when I joined her group. I was raw and lacking all the essential skills required to become a good researcher. Not to mention that my knowledge in computer architecture was near zero. She was patient and successful in transforming me into a decent researcher despite being a highmaintenance student. Throughout the years, I have acquired valuable knowledge from her, which helped me grow both professionally and personally. Her vision, commitment and ambition towards good quality contributions have shaped my personality in many ways. Her level of commitment to the most intricate details of a problem has always amazed me. She has always been supportive and caring, especially during my difficult times. I feel eternally indebted to her and respect her as a son respects a caring mother.

Besides my advisor, I would like to thank Prof. Wong Weng Fai and Prof. Colin Tan for their invaluable and intriguing comments that has shaped this research work. I am highly indebted to Cambridge Silicon Radio plc (CSR) for their generous financial and logistics (board) support without which this thesis would not have been possible. I am also very thankful to thank Sanjay Vishin from CSR for all the productive discussions. His critical thinking and intellectual foundation have influenced the contributions in this thesis in many ways.

There is no shortage of my fellow colleagues and collaborators to thank. First, I would like to sincerely thank Haris Javaid from UNSW. Haris has made me understand on how to present an idea to a wider audience in a convincing manner. I will remember his mentorship and guidance for life. From the day I joined the eCO lab (that is what we call ourselves now), Mihai has always been there to listen, comment, positively criticize and support in all my research endeavours. I thank him for showing me how a researcher should quantitatively evaluate an idea in an effective manner. I would like to thank Vanchi for patiently listening to my rants, crazy ideas and philosophical believes. And more importantly he was instrumental in keeping me sane in the lab. The best time of my PhD was during my collaborations with Mihai and Vanchi. Thanks guys for giving an awesome and memorable time. I am grateful for Chen Liang for traveling this journey of PhD together in all the ups and downs. I would also like to thank Anuj for his support. His eagerness to develop numerous ideas in very short span is astonishing. I would like to thank all my lab mates: Huping, Chundong, Sudipta, Alok, Lee Kee, Tan Cheng, Henry and Jiao Qing for keeping an healthy research environment. A special thanks goes to Mahesh, without whom I would have never met my advisor.

I was fortunate enough to meet lots of nice people in Singapore. Their friendship and kindness helped me sail through the ups and downs of my life in Singapore. Each and everyone one of them have touched my heart in a very positive manner. Thanks to P-boy, SK, Director, Kauntz, Raaju, Poli samiyar, PM and Gii. I thank all the mamis (SK, P-boy and TKB wives) for providing enough home cooked and healthy food. My sincere thanks goes to Badri Mama, Manavalan Mama and TKB for enriching the spiritual side of my life. A special thanks goes to Ancy Alexander for his guidance about life in general.

Last, but certainly not the least, I would like to acknowledge my family. I would not be who I am today without their support. I owe everything to my family. Mani, my brother, has been instrumental in supporting and guiding me in all the major crucial phases of my life. I am always grateful for his passion to see me grow in life. Appa and Amma have always trusted and encouraged me in numerous ways. Appa, you have always been a great role model for me right from my childhood. Amma, as a token of your immeasurable love and support I would like to dedicate this thesis to you.

# Contents

| Declaration                         |      | i    |

|-------------------------------------|------|------|

| Acknowledgements                    |      | ii   |

| Contents                            |      | v    |

| Abstract                            |      | xi   |

| List of Tables                      |      | xiii |

| List of Figures                     |      | xv   |

| Related Publications                |      | xx   |

| 1 Introduction                      |      | 1    |

| 1.1 Motivation and Objective        | <br> | 1    |

| 1.2 Contributions                   | <br> | 5    |

| 1.2.1 Run-time technique            | <br> | 6    |

| 1.2.1.1 Predictive power management | <br> | 6    |

| 1.2.1.2 Reactive power management   | <br> | 7    |

|   |     | 1.2.1.3 Lifetime-reliability aware power management   | 8  |

|---|-----|-------------------------------------------------------|----|

|   |     | 1.2.2 Design-time technique                           | 8  |

|   | 1.3 | Organization                                          | 9  |

| 2 | Rel | ated Work                                             | 10 |

|   | 2.1 | Static technique - Static architecture                | 10 |

|   |     | 2.1.1 DVFS                                            | 11 |

|   |     | 2.1.2 Processor customization                         | 11 |

|   |     | 2.1.3 Cache customization                             | 12 |

|   |     | 2.1.4 DVFS and processor customization                | 12 |

|   |     | 2.1.5 DVFS and task mapping                           | 12 |

|   |     | 2.1.6 Processor customization and task mapping        | 13 |

|   |     | 2.1.7 Processor customization and cache customization | 13 |

|   | 2.2 | Dynamic technique - Static architecture               | 13 |

|   |     | 2.2.1 Homogeneous Multi-cores                         | 14 |

|   |     | 2.2.2 Heterogeneous Multi-cores                       | 15 |

|   |     | 2.2.3 Computational Economics                         | 16 |

|   |     | 2.2.4 Power-Performance Model                         | 17 |

|   | 2.3 | Dynamic technique - Dynamic architecture              | 17 |

| 3 | Pov | ver-Performance Modeling on Heterogeneous Multi-cores | 19 |

|   | 3.1 | ARM big.LITTLE architecture                           | 22 |

|   | 3.2 | Performance Modeling                                  | 25 |

|   |     | 3.2.1 $CPI_{steady}$ estimation                       | 29 |

|   |     | 3.2.2   | CPI stack model of big core                     | 30 |

|---|-----|---------|-------------------------------------------------|----|

|   |     | 3.2.3   | CPI stack model of small core                   | 32 |

|   |     | 3.2.4   | Latency of miss events and performance counters | 33 |

|   |     | 3.2.5   | Contribution of CPI stack components            | 34 |

|   | 3.3 | Inter-o | core miss estimation                            | 35 |

|   | 3.4 | Power   | Modeling                                        | 39 |

|   | 3.5 | Runtii  | me Scheduler                                    | 42 |

|   |     | 3.5.1   | Performance Estimation                          | 43 |

|   |     | 3.5.2   | Energy Estimation                               | 43 |

|   | 3.6 | Exper   | imental Evaluation                              | 43 |

|   |     | 3.6.1   | Performance estimation accuracy                 | 46 |

|   |     | 3.6.2   | Power estimation accuracy                       | 50 |

|   |     | 3.6.3   | Phase behavior                                  | 50 |

|   |     | 3.6.4   | Asymmetric vs Symmetric multi-core              | 51 |

|   | 3.7 | Summ    | ary                                             | 52 |

| 4 | Hie | rarchio | cal Power Management                            | 54 |

|   | 4.1 |         | big.LITTLE architecture                         | 57 |

|   |     | 4.1.1   | Impact of DVFS                                  | 58 |

|   |     |         | •                                               |    |

|   |     | 4.1.2   | Impact of active cores on cluster power         | 58 |

|   |     | 4.1.3   | Migration Cost                                  | 59 |

|   | 4.2 | Power   | Management Framework                            | 60 |

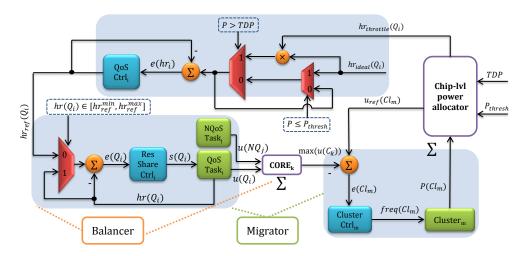

|   |     | 4.2.1   | Per-Task Resource Share Controller              | 63 |

|   |      | 4.2.2  | Per-Cluster DVFS Controller                    | 64  |

|---|------|--------|------------------------------------------------|-----|

|   |      | 4.2.3  | Chip-Level Power Allocator                     | 64  |

|   |      | 4.2.4  | Per-Task QoS Controller                        | 66  |

|   |      | 4.2.5  | Load Balancer and Migrator                     | 66  |

|   | 4.3  | Exper  | imental Evaluation                             | 67  |

|   |      | 4.3.1  | Implementation Details                         | 67  |

|   |      | 4.3.2  | Results                                        | 70  |

|   | 4.4  | Summ   | ary                                            | 78  |

| 5 | Prie | ce The | ory based Power Management                     | 79  |

|   |      |        | n Overview                                     | 80  |

|   | 5.1  | Syster |                                                | 80  |

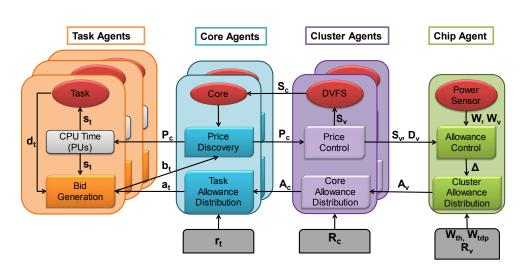

|   | 5.2  | Power  | management Framework                           | 82  |

|   |      | 5.2.1  | Agents Overview                                | 84  |

|   |      | 5.2.2  | Supply-Demand Module                           | 85  |

|   |      |        | 5.2.2.1 Task Dynamics                          | 86  |

|   |      |        | 5.2.2.2 Cluster Dynamics                       | 87  |

|   |      |        | 5.2.2.3 Chip Dynamics                          | 89  |

|   |      |        | 5.2.2.4 Stability of the Supply-Demand module  | 94  |

|   |      | 5.2.3  | Load Balancing and Task migration (LBT) module | 96  |

|   |      |        | 5.2.3.1 Stability of the LBT module            | 101 |

|   |      | 5.2.4  | Invocation Frequency                           | 102 |

|   | 5.3  | Exper  | imental Evaluation                             | 103 |

|   |      | 5.3.1  | Experimental Setup                             | 103 |

|   |     | 5.3.2 Workload Selection                                                                           |

|---|-----|----------------------------------------------------------------------------------------------------|

|   |     | 5.3.3 Comparative Study                                                                            |

|   |     | 5.3.4 Impact of priorities and savings                                                             |

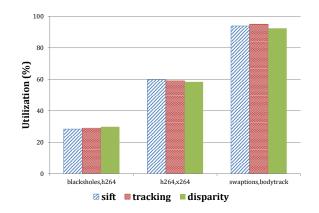

|   |     | 5.3.5 Scalability                                                                                  |

|   | 5.4 | Summary                                                                                            |

|   | 5.5 | Future Work                                                                                        |

| 6 | Dyı | namic Reliability Management 116                                                                   |

|   | 6.1 | Parameter Selection                                                                                |

|   | 6.2 | Dynamic Reliability Management                                                                     |

|   |     | 6.2.1 Naive Bayesian Classifier                                                                    |

|   |     | 6.2.2 Performance Prediction Model                                                                 |

|   |     | 6.2.3 Search Space Pruning                                                                         |

|   | 6.3 | Experimental Evaluation                                                                            |

|   | 6.4 | Summary                                                                                            |

| 7 | Ene | ergy-Aware Synthesis of Application Specific MPSoCs 133                                            |

|   | 7.1 | Problem Formulation                                                                                |

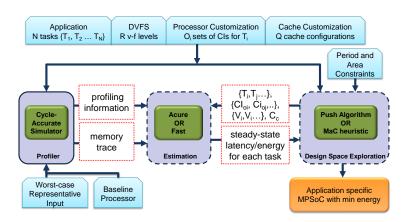

|   | 7.2 | Proposed Framework                                                                                 |

|   |     | 7.2.1 Profiler                                                                                     |

|   |     | 7.2.2 Latency and Energy Estimation                                                                |

|   |     | 7.2.2.1 Accurate (Acure) Estimator $\ldots \ldots \ldots 142$                                      |

|   |     | 7.2.2.2 Fast Estimator $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 140$ |

|   |     | 7.2.3 Design Space Exploration                                                                     |

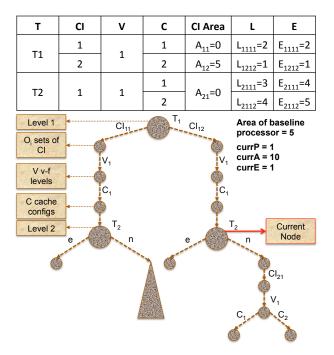

|    |      | 7.2.3.1        | Prune and Search (Push) Algorithm | 148 |

|----|------|----------------|-----------------------------------|-----|

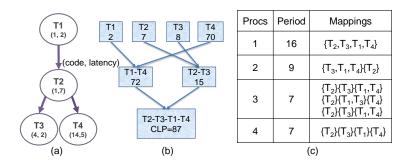

|    |      | 7.2.3.2        | Map and Customize (MaC) Heuristic | 150 |

|    | 7.3  | Experimental M | Methodology                       | 153 |

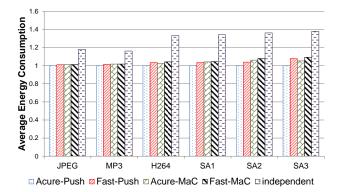

|    | 7.4  | Results        |                                   | 155 |

|    | 7.5  | Summary        |                                   | 158 |

| 8  | Cor  | nclusions      |                                   | 159 |

| 9  | Fut  | ure Work       |                                   | 160 |

| Bi | blio | graphy         |                                   | 162 |

## Abstract

Relentless Complementary Metal-Oxide Semiconductor (CMOS) scaling at deep sub-micron level has resulted in increased power density in microprocessor, which forced the computing systems to move in the direction of parallel architectures with homogeneous multi-cores. However, the emergence of dynamic and diverse workloads combined with the failure of Dennard Scaling facilitated the growth of heterogeneous multi-cores. The presence of heterogeneity enables better match between application demand and computation capabilities leading to substantially improved performance and energy-efficiency. In spite of significant benefits in terms of both performance and energy consumption, the heterogeneous multicore systems introduce many of design and scheduling challenges. In this thesis, we address various challenges involved in designing heterogeneous multi-cores.

In the first part of this thesis, we focus on developing power management schemes for heterogeneous multi-cores that can satisfy application's demand with low energy consumption under the Thermal Design Power (TDP) constraint. First, we develop a performance and power model of heterogeneous cores having different performance and power consumption characteristics that can be used in any predictive scheduling approach. Second, we propose two reactive power management frameworks: *Hierarchical Power Management* (HPM) and *Price theory based Power Management* (PPM). All the aforementioned dynamic power management frameworks were evaluated on a real Advance RISC Machines (ARM) big.LITTLE heterogeneous multi-core platform. Our experimental evaluations establish the superiority of the power management schemes compared to the existing state-of-the-art techniques. Lastly, we propose a power-aware dynamic reliability management technique that can meet both reliability and thermal/power constraints, while optimizing the performance. In the second part of this thesis, we propose a comprehensive framework that help to design the most energy-efficient application-specific Multi-Processor System on Chips (MPSoCs). We model the synthesis of energy-efficient MPSoC as a design space exploration problem involving four design parameters: DVFS, processor customization, cache customization and task mapping. Experiments reveal that our framework can reduce energy consumption compared to solutions obtained from a combination of existing techniques.

Overall in this thesis, we address power consumption related challenges exhibited in heterogeneous multi-core systems by proposing both static and dynamic power management techniques. While the first part of the thesis focuses on the dynamic techniques, the second part elaborates the static solutions.

# List of Tables

| 3.1 | Architectural Parameters of Cortex-A7 and Cortex-A15              | 23 |

|-----|-------------------------------------------------------------------|----|

| 3.2 | Estimated latency in cycles for miss events on A15 and A7 $\ .$ . | 33 |

| 3.3 | Hardware Performance Counters on A15 and A7                       | 33 |

| 3.4 | Training and Test Benchmarks                                      | 45 |

| 4.1 | Migration Cost within cluster in usec.                            | 59 |

| 4.2 | Migration Cost in msec from A7 to A15 cluster                     | 60 |

| 4.3 | Migration Cost in msec from A15 to A7 cluster                     | 60 |

| 4.4 | Controller Features.                                              | 61 |

| 4.5 | Linux kernel modifications.                                       | 69 |

| 4.6 | Benchmarks description.                                           | 70 |

| 4.7 | Heartbeats in QoS benchmarks                                      | 70 |

| 4.8 | Controller Parameters.                                            | 71 |

| 4.9 | Quantitative comparison of HPM with Linaro scheduler              | 74 |

| 5.1 | Task and Core Level Dynamics Example                              | 87 |

| 5.2 | Cluster Level Dynamics Example                                    | 88 |

| 5.3 | Chip Level Dynamics Example                                       | 93 |

| 5.4 | Illustration of conversion from heart rate to demand with min and |     |

|-----|-------------------------------------------------------------------|-----|

|     | max heart rate being 24 hb/s and 30 hb/s respectively             | 104 |

| 5.5 | Benchmarks description                                            | 105 |

| 5.6 | Workload Sets                                                     | 106 |

| 5.7 | Computational overhead for varying number of clusters $V$ , cores |     |

|     | per cluster $C$ , and tasks per core $T$                          | 114 |

| 7.1 | Cache state across iterations of a task                           | 144 |

| 7.2 | Maximum error in the Acure and Fast estimators                    | 155 |

| 7.3 | Exploration time (in secs) of optimization techniques             | 157 |

# List of Figures

| 1.1 | Dennard's constant field scaling                                           | 2  |

|-----|----------------------------------------------------------------------------|----|

| 1.2 | Overall Contributions of the thesis                                        | 6  |

| 1.3 | ARM big.LITTLE asymmetric multi-core                                       | 8  |

| 3.1 | Performance improvement, energy consumption ratio and EDP                  |    |

|     | ratio of A15 in comparison to A7.                                          | 25 |

| 3.2 | Inter-core performance, power estimation from $P$ to $P'$                  | 26 |

| 3.3 | Estimated $CPI_{steady}$ and $CPI_{miss}$ of different inputs for the same |    |

|     | benchmark on A7 and A15                                                    | 27 |

| 3.4 | Estimation of steady state CPI of a program using gcc.                     | 29 |

| 3.5 | Estimated CPI stack components on A7 and A15 for a subset of               |    |

|     | benchmarks                                                                 | 34 |

| 3.6 | Online scheduler with power-performance estimation                         | 42 |

| 3.7 | Intra-core model validation accuracy using $CPI_{steady}$ obtained         |    |

|     | through compile-time analysis compared to the accuracy assuming            |    |

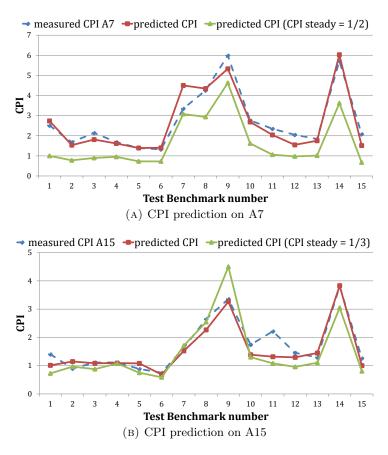

|     | $CPI_{steady} = 1/D$                                                       | 47 |

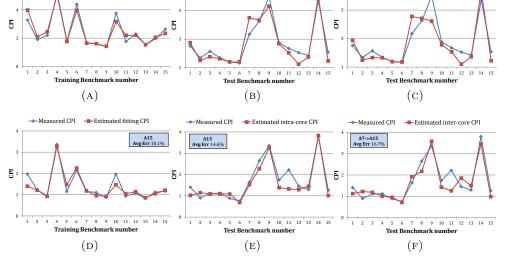

| 3.8  | CPI stack model fitting error on training benchmarks, intra-core    |    |

|------|---------------------------------------------------------------------|----|

|      | model validation error using test benchmarks and inter-core CPI     |    |

|      | estimation error for Cortex-A7 (top row) and Cortex A-15 (bot-      |    |

|      | tom row)                                                            | 48 |

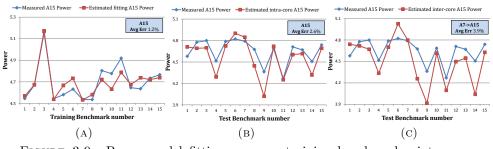

| 3.9  | Power model fitting error on training benchmarks, intra-core model  |    |

|      | validation error using test benchmarks and inter-core power esti-   |    |

|      | mation error for Cortex-A15.                                        | 48 |

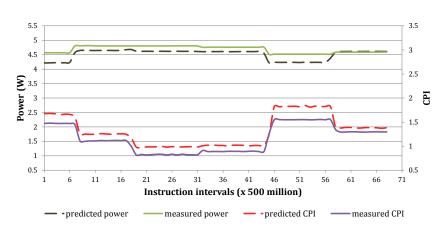

| 3.10 | Continuous CPI and power estimation from A7 to A15 for <i>astar</i> |    |

|      | benchmark.                                                          | 51 |

| 3.11 | Comparison of percentage of time heart rate was met between         |    |

|      | symmetric and asymmetric multi-core.                                | 52 |

| 3.12 | 2 Comparison of energy consumption between symmetric and asym-      |    |

|      | metric multi-core                                                   | 52 |

|      |                                                                     |    |

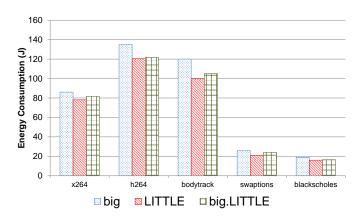

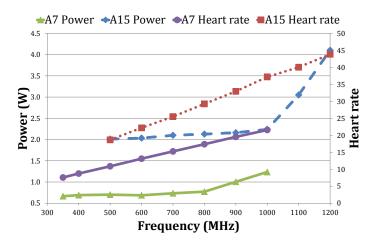

| 4.1  | Power and heart rate with varying frequency.                        | 57 |

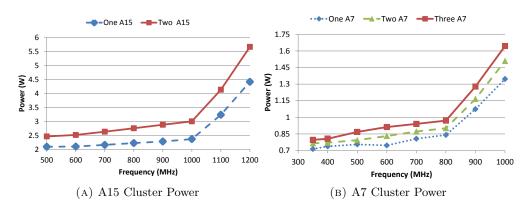

| 4.2  | Impact of number of active cores on cluster power                   | 58 |

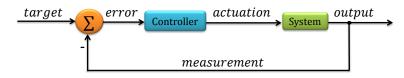

| 4.3  | Feedback based Controller.                                          | 60 |

| 4.4  | Overview of the hierarchical power management system coordi-        |    |

|      | nating multiple controllers.                                        | 61 |

| 4.5  | Picture of the Vexpress board.                                      | 68 |

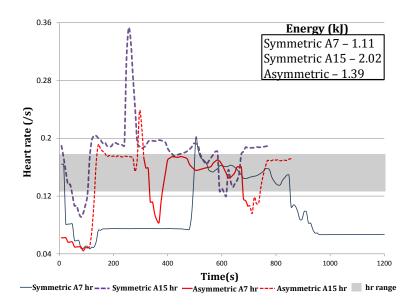

| 4.6  | x264: Heart rate on symmetric & asymmetric multi-core               | 72 |

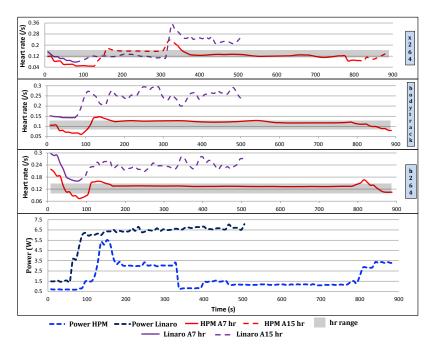

| 4.7  | HPM versus stock Linaro scheduler equipped with DVFS governor       |    |

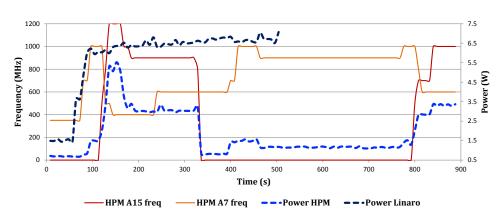

|      | and inter-cluster migration.                                        | 74 |

| 4.8  | Frequency and power consumption plot (HPM versus stock Linaro             |     |

|------|---------------------------------------------------------------------------|-----|

|      | scheduler)                                                                | 75  |

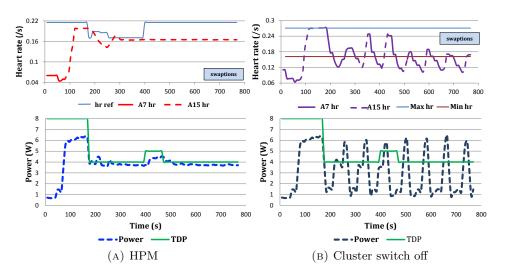

| 4.9  | Comparison of HPM and Linaro extended with cluster switch-off             |     |

|      | policy under TDP constraint                                               | 76  |

| 4.10 | Fairness of non-QoS tasks.                                                | 77  |

| 5.1  | Agent Interaction Overview                                                | 83  |

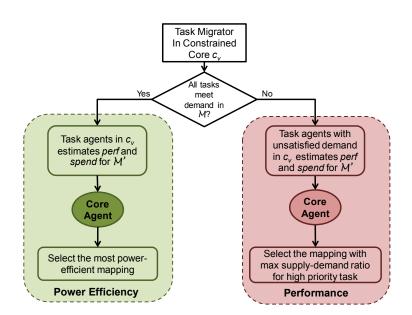

| 5.2  | Task Migration in Constrained Core.                                       | 100 |

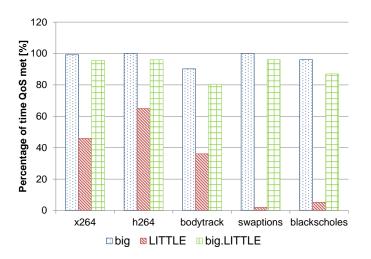

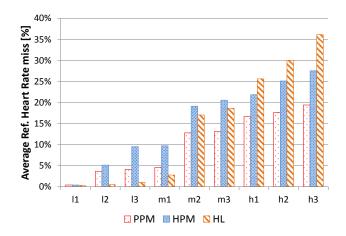

| 5.3  | Comparison of the percentage of time the tasks do not meet the            |     |

|      | reference heart rate range (no TDP constraint)                            | 108 |

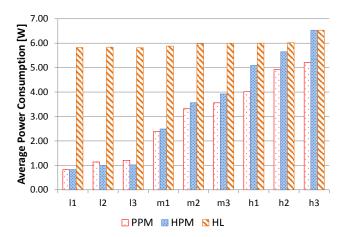

| 5.4  | Comparison of power consumption (no TDP constraint)                       | 108 |

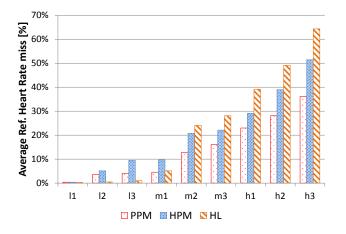

| 5.5  | Comparison of the percentage of time the tasks do not meet the            |     |

|      | reference heart rate range under TDP constraint of 4W                     | 109 |

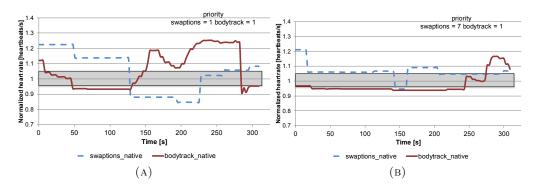

| 5.6  | Normalized performance of swaptions and body<br>track where $[0.95, 1.0]$ | 5]  |

|      | is the normalized performance goal                                        | 110 |

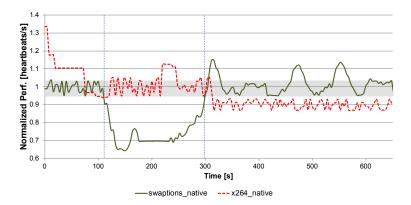

| 5.7  | Normalized performance of swaptions and $x264$ when $[0.95, 1.05]$        |     |

|      | is the normalized performance goal                                        | 111 |

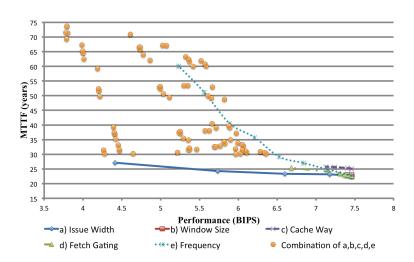

| 6.1  | MTTF vs. Performance for different adaptation mechanisms for              |     |

|      | the benchmark bzip2                                                       | 118 |

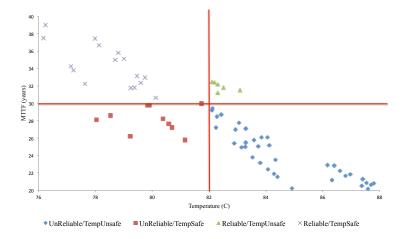

| 6.2  | MTTF vs. temperature for different architectural configurations           |     |

|      | for the benchmark crafty                                                  | 119 |

| 6.3  | Performance-reliability tradeoff.                                         | 121 |

| 6.4  | Performance-temperature tradeoff.                                         | 122 |

| 6.5 | Comparison of different DRM techniques                               | 131   |

|-----|----------------------------------------------------------------------|-------|

| 6.6 | Time varying trends for bzip2.                                       | 132   |

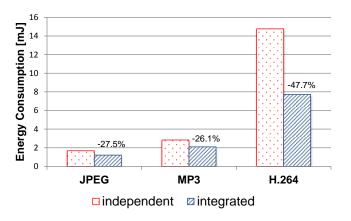

| 7.1 | Comparison of 'independent' and 'integrated' optimization tech-      |       |

|     | niques                                                               | 135   |

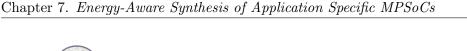

| 7.2 | (a)Task graph (b)MPSoC architecture                                  | 138   |

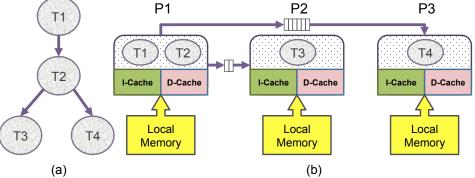

| 7.3 | Different task mappings on an MPSoC.                                 | 140   |

| 7.4 | Framework Overview.                                                  | 141   |

| 7.5 | Illustration of Push algorithm.                                      | 149   |

| 7.6 | Illustration of map stage: (a)Task graph (b)Task sequencing (c)Diffe | erent |

|     | task mappings.                                                       | 152   |

| 7.7 | Illustration of customize stage.                                     | 152   |

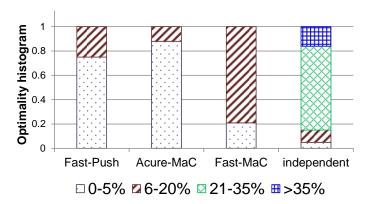

| 7.8 | Comparison of different optimization techniques, normalized to       |       |

|     | Acure-Push                                                           | 156   |

| 7.9 | Error distribution in different optimization techniques for SA3      |       |

|     | application.                                                         | 156   |

For Amma, Appa and Mani...

# **Related Publications**

T. S. Muthukaruppan, and T. Mitra. Lifetime Reliability Aware Architectural Adaptation. In *IEEE International Conference on VLSI Design and 2013 12th International Conference on Embedded Systems (VLSID)*, 2013.

T. S. Muthukaruppan, M. Pricopi, V. Venkataramani, T. Mitra and S. Vishin.

Hierarchical power management for asymmetric multi-core in dark silicon era.

In ACM Proceedings of the 50th Annual Design Automation Conference (DAC), 2013.

M. Pricopi, T. S. Muthukaruppan, V. Venkataramani, T. Mitra and S. Vishin. Power-performance modeling on asymmetric multi-cores. In *IEEE International Conference on Compilers, Architecture and Synthesis for Embedded Systems* (CASES), 2013.

T. S. Muthukaruppan, H. Javaid, T. Mitra and S. Parameswaran. Energy-aware synthesis of application specific MPSoCs. In *IEEE International Conference on Computer Design (ICCD)*, 2013.

T. S. Muthukaruppan, A. Pathania and T. Mitra. Price theory based power management for heterogeneous multi-cores. In *ACM Architectural Support for Programming Languages & Operating Systems (ASPLOS)*, 2014.

## Chapter 1

# Introduction

In the modern era, computers have penetrated all facets of human life. They have revolutionized the way we think, interact and perform our day-to-day activities. One of the reasons for this indispensable addiction is the variety of features that they offer such as recreation, health-care, transportation etc. We use computers in various forms and sizes such as laptops, tablets, smart phones, etc. even being oblivious to their presence at times. The increasing number of computing devices have inevitably led to an increasing demand on energy resources. Hence, it is crucial to develop energy-efficient computers – a design choice that helps in designing computers that are small, fast, efficient and generate less heat. *Heterogeneous computing* has emerged as a popular design option for realizing energy-efficient computers. In this thesis, we discuss and develop heterogeneous systems that have a positive impact on the energy consumption.

#### **1.1** Motivation and Objective

The significant compound annual growth rate of 14% [6] for the microprocessor industry in the past 40 years is heavily attributed to the success of Moore's law [85], which states that the number of transistors doubles once every eighteen

| Dimensions            | 0.7x | $\mathbf{r}$       |

|-----------------------|------|--------------------|

| Voltage               | 0.7x | $\bigtriangledown$ |

| Doping Concentrations | 0.7x | $\langle \neg$     |

| Area                  | 0.5x | $\checkmark$       |

| Capacitance           | 0.7x |                    |

| Frequency             | 1.4x |                    |

| Power                 | 0.5x | $\bigtriangledown$ |

FIGURE 1.1: Dennard's constant field scaling.

months. This is achieved by scaling various transistor dimensions like channel length, channel width, and oxide thickness. The main challenge in integrating more transistors across generations is to prevent the chip from melting. It is in fact the Dennard Scaling [30] that has enabled the success of Moore's law for the past 40 years. Figure 1.1 shows the scaling factor for Dennard's constant electric field scaling. According to Dennard Scaling, for complementary metal-oxide-semiconductor (CMOS) transistors, scaling the dimensions, voltage and doping concentrations by 0.7 times results in an area reduction of 0.5 times of the original transistor. Similarly, the capacitance reduces by a factor of 0.7 times, while the frequency increases by a factor of 1.4times. The dynamic power consumption of a transistor is given by the formula  $Capacitance \times Frequency \times Voltage^2$ . Therefore, for constant electric field, ideally the power consumption of the transistor reduces by the factor of 0.5 times. Therefore, at every new process technology, the power consumption scales by the same factor as the area, which results in constant power density in the chip. It is the fusion of Moore's law with Dennard Scaling that resulted in exponential performance increase in microprocessors.

Unfortunately, Dennard Scaling has started failing in recent generations due to the relatively slow scaling of supply voltage, resulting in increased dynamic power density. The non-ideal scaling of supply voltage is attributed to the following reasons: a) need for higher performance, which can be obtained only at high supply voltage and b) relatively stagnant threshold voltage to control the static power consumption. Thus, as more and more of transistors are integrated in the same area in the future generations, the power density will increase rapidly. The increase in power density has resulted in increase in on-chip temperature of the microprocessors. High on-chip temperatures can affect the following features:

- Leakage Power: There exists positive feedback relationship between the leakage power and the temperature [77, 112]. Increase in temperature results in increasing the leakage power, which in turn can increase the temperature resulting in a thermal runway.

- **Reliability:** Extensive studies [108] have shown that the lifetime reliability of microprocessors is significantly affected by the high on-chip temperatures. The advent of various failure mechanisms like electro migration, stress migration, gate oxide breakdown, and thermal cycles surges with high on-chip temperature.

Traditionally, the researchers have relied upon packaging and cooling technologies (heat sink, convection resistance, fan etc.) to bring down the high temperatures in modern microprocessors. The maximum power dissipation handled by the given packaging and cooling solutions is defined as Thermal Design Power (TDP). The chips with higher TDP limits have better cooling solutions. Unfortunately, as we are already in the era of mobility, integrating advanced cooling solutions to mobile devices is both expensive and infeasible. From the above discussions, it is clear that reducing power dissipation to lower on-chip temperature is the most important design goal in modern high performance microprocessors.

For continued adherence to Moore's law and to combat the increase in power consumption, the computing systems have made an irreversible transition towards parallel architectures with multi-cores and many cores. From the virtue of the power model described in [86], for the same compute capability, the power consumption of a dual core reduces by four times compared to that of a single microprocessor. However, with continued non-ideal CMOS scaling, power and thermal limits are rapidly bringing the computing community to another crossroad where a chip can have many cores but a significant fraction of them are left un-powered, or dark, at any point in time [37]. This phenomenon, known as dark silicon, is immediately visible in the computing space due to the increasing cooling costs of the chip. Furthermore, the emergence of sophisticated and power hungry mobile applications like speech processing, pattern recognition, audio/video editing etc. have further exacerbated the power challenges in the mobile devices.

The dark silicon era is driving the emergence of heterogeneous multi-cores, which exhibit diverse power/performance characteristics. Unlike homogeneous multicores, exploiting the potential of heterogeneous multi-cores is not straightforward. First, the major challenge in designing heterogeneous multi-cores is how to efficiently explore the complex design space so as to improve the efficiency of the power-performance tradeoff. Secondly, for static and pre-designed heterogeneous multi-cores, the capability can only be fully exploited with a proper online scheduling support. Hence, it is imperative that both the design of heterogeneous multi-core and scheduling should be prudently crafted.

The most popular choice of mechanism for power reduction is dynamic voltage and frequency scaling (DVFS). Few recent works [96, 108] have claimed that there is a decrease in overall lifetime reliability of the microprocessors due to aggressive power management policies. For example, frequent voltage-frequency (v-f) levels transition can introduce thermal cycling, which can significantly reduce the mean time to failure (MTTF) of the microprocessors. Hence, it is also important to design power management scheme that has minimal impact on the lifetime reliability. The above discussions motivate the need for efficient power management schemes for heterogeneous multi-cores that can exhibit following desirable features:

- The power should not be allowed to exceed the power budget defined by TDP.

- The performance requirements of various applications have to be met under the power budget with minimal energy consumption.

- The reduction in power consumption should not come at the expense of sacrificing the lifetime reliability of the microprocessor.

To meet the above challenges and fulfill the objectives, we propose efficient power management schemes in this thesis. This work investigates various power management schemes like DVFS, task migrations, load balancing, custom instruction selection etc. in a detailed manner.

#### **1.2** Contributions

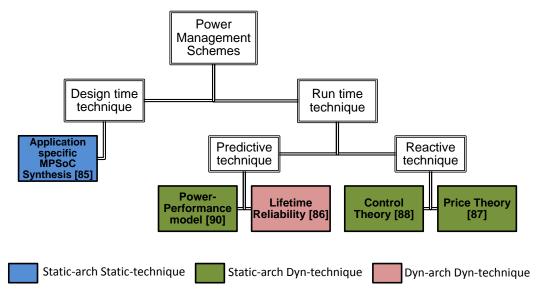

This thesis makes following key contributions (as shown in Figure 1.2):

- We develop a power-performance model [92] for commercial heterogeneous multi-core: ARM big.LITTLE. Our model can be deployed with any prediction based dynamic power management scheme.

- We propose two reactive dynamic power management schemes based on the strong foundations of *control theory* [90] and *price theory* [89].

- We explore the effect of heterogeneity in terms of micro-architectural adaptation on the lifetime reliability of microprocessors [88].

- We also propose a comprehensive framework for synthesis of application specific MPSoC for multimedia applications. Our framework searches for

a design with minimum energy consumption under area and period constraints [87].

FIGURE 1.2: Overall Contributions of the thesis.

#### 1.2.1 Run-time technique

#### 1.2.1.1 Predictive power management

The ability to estimate the performance/power characteristics for various workloads for each core type in heterogeneous multi-cores can solve the scheduling challenges in determining the best workload-to-core mapping. Hence, in the first contribution, we develop power-performance model for ARM big.LITTLE. While an application is executing on ARM Cortex-A7 (alternatively ARM Cortex-A15), we collect profile information provided by hardware counters, and estimate power and performance characteristics of the same application on ARM Cortex-A15 (alternatively ARM Cortex-A7). We evaluate the accuracy of our estimation on real ARM big.LITTLE hardware platform. Our evaluations clearly states the accuracy of our power-performance model. We also develop a scheduling algorithm based on the proposed estimation model for ARM big.LITTLE heterogeneous multi-core.

#### 1.2.1.2 Reactive power management

The second contribution of this thesis is to propose a dynamic power management framework for heterogeneous multi-cores like ARM big.LITTLE in mobile platforms, that can satisfy application's demand expressed in terms of Quality of Service (QoS) with low energy consumption under Thermal Design Power (TDP) constraint. We propose two reactive run-time power management frameworks.

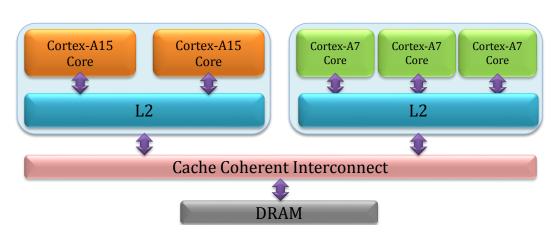

First, we propose *Hierarchical Power Management* (HPM) [90] for heterogeneous multi-cores – in particular ARM big.LITTLE [7] (as shown in Figure 1.3) architecture in the context of mobile embedded platforms — that can provide satisfactory user experience while minimizing energy consumption within the Thermal Design Power (TDP) constraint. Our HPM framework is based on the solid foundation of control theory and integrates multiple controllers to collectively achieve the goal of optimal energy-performance tradeoff under restricted power budget. Second, we propose *Price theory based Power Management* (PPM) [89] for heterogeneous multi-cores that can contain any number of clusters of different core types (unlike HPM which can handle only at most two clusters with each containing different core types). Our PPM framework borrows strong basics from the concept of *price theory* from economics, which makes the technique scalable, holistic and priority-driven.

Aforementioned techniques (HPM and PPM) have been build as an extension of *Linux completely-fair scheduler* while preserving all of its desirable properties such as fairness, non- starvation etc. Finally, both the frameworks have been implemented on a test version of the ARM big.LITTLE heterogeneous multicore architecture and we report power, performance results from this real chip (as

FIGURE 1.3: ARM big.LITTLE asymmetric multi-core.

opposed to simulation). We experimentally evaluate and establish the superiority of our approaches compared to the existing state-of-the-art.

#### 1.2.1.3 Lifetime-reliability aware power management

The third contribution of this thesis is to propose a dynamic reliability management technique for lifetime reliability enhancement via micro-architectural adaptations. We propose a dynamic reliability management (DRM) technique that exploits architectural adaptation in conjunction with dynamic voltage/frequency scaling (DVFS). In this contribution, the heterogeneity is evident from the dynamic architectural adaptation. We employ an online Bayesian classifier that can efficiently detect the reliable configurations, while a performance prediction model selects the one with best performance among all the reliable configurations. We later extend our approach to meet both reliability and thermal constraints. The thermal constraints act as proxy for power constraints.

#### 1.2.2 Design-time technique

The final contribution of this thesis is a framework for design of heterogeneous application-specific MPSoC for multimedia applications [87]. Modern MPSoCs

for multimedia applications have to deliver a certain performance to provide reasonable quality of service to the users (performance constraint), must have area smaller than a certain limit due to the size of the portable devices (area constraint), and should have low energy consumption to increase the battery life. Therefore, application specific MPSoCs are deployed in portable devices [41] where an MPSoC is (extremely) customized for a given application under an objective function and various constraints. This contribution focuses on customization of MPSoCs for multimedia applications with the objective of minimum energy consumption under performance and area constraints.

To summarize, the run time techniques [89, 90, 92] proposed in thesis are dynamic techniques on a static heterogeneous architecture except for the one proposed in [88] (which is a dynamic technique on a dynamic heterogeneous architecture), while the design time technique [87] proposed is a static technique engaged on a static heterogeneous architecture.

#### **1.3** Organization

The rest of this thesis is organized as follows. Chapter 2 discusses related work. Chapter 3 discusses the power-performance estimation model for heterogeneous multi-core. Chapter 4 and 5 elaborates the various reactive based run-time power management framework for heterogeneous multi-cores. Chapter 4 proposes control theory based power management framework in detail. Chapter 5 proposes price theory based power management framework that improves on the technique explained in Chapter 4. Chapter 6 proposes a dynamic reliability management technique for microprocessors. Chapter 7 describes the static design time technique for synthesizing energy-efficient application specific MPSoC. Chapter 8 describes the conclusion of this thesis and Chapter 9 explains possible avenues of future work.

### Chapter 2

# **Related Work**

In this chapter, we briefly present the overview of the previously published work on power management based on the categories described in Figure 1.2. The categorization is based on the type of architecture and technique, which can be either *static* or *dynamic*. For static techniques, the mechanisms are determined at the design time. Unlike static techniques, the dynamic techniques adapt according to the workload at run-time. Similarly, in terms of architecture, static architectures are fixed at design time (for example, ARM big.LITTLE). In this thesis, we adapt micro-architectural parameters like issue-width, window size and cache sizes at run-time to emulate dynamic heterogeneous architectures.

#### 2.1 Static technique - Static architecture

Power management techniques can be built into the system at the design time either in software or hardware. Static techniques are mostly applicable for embedded domain, where the hardware-software co-design is very relevant. In recent years, application specific MPSoCs have become a promising option for designing embedded portable devices, because of their high performance and low energy consumption. There is a plethora of work on designing of application specific MPSoCs, where researchers have considered different objective functions, constraints and design parameters. We report the most relevant works categorized according to the four design parameters: DVFS, processor customization, cache customization and task mapping.

#### 2.1.1 DVFS

The authors of [38, 39] used DVFS to balance workload across processors connected in a pipeline, in order to reduce their energy consumption. They proposed feedback controllers to monitor the occupancy levels of buffers in the pipeline, and either increased or decreased the v-f level of a processor accordingly. Chen et al. [23] also considered a pipeline of processors with the availability of DVFS; however, they minimized the energy consumption of the system under an endto-end application deadline using quadratic programming.

#### 2.1.2 Processor customization

Bonzini et al. [18] studied the effects on energy consumption and performance due to addition of custom instructions in an ASIP. They built an estimation model for a simplescalar-like processor to quickly evaluate different custom instructions. In [17], the authors characterized the energy benefits of extending the baseline instruction set architecture of an FPGA based soft processor. Lin et al. [76] targeted multiobjective optimization of an ASIP where custom instructions are added considering area and energy consumption. They used mixed integer linear programming for an optimal solution and a simulated annealing based heuristic for a near-optimal solution.

#### 2.1.3 Cache customization

The authors of [48, 125] explored the design space of a cache (cache size, line size, associativity) to select a cache configuration with minimum energy consumption. The authors proposed a heuristic to quickly search through complex design space of cache configurations for a near-optimal solution. Rawlins et al. [95] targeted run-time tuning of L1 data cache to minimize energy consumption of a heterogeneous MPSoC architecture. They proposed a heuristic to quickly search through through the design space with minimal run-time overhead.

#### 2.1.4 DVFS and processor customization

Jung et al. [63] customized an MPSoC, where custom instructions and different v-f levels were used for the ASIPs in the system. They employed mixed integer linear programming to find the design point with minimum dynamic energy consumption under an area constraint.

#### 2.1.5 DVFS and task mapping

Ruggiero et al. [99] considered an MPSoC with variable number of processors and DVFS. They used a design space exploration algorithm to determine the optimal number of processors and v-f levels for a given application to minimize the MPSoC's power consumption under quality of service constraints. The authors of [14] considered resource allocation and voltage selection problem in an MPSoC. They minimized MPSoC's energy consumption with the use of integer programming and constraint programming. Lu et al. [78] considered the problem of task mapping/scheduling and DVFS in homogeneous MPSoCs. They proposed a processor utilization based algorithm for task mapping and exploited the slacks available in periodic tasks to minimize energy consumption.

#### 2.1.6 Processor customization and task mapping

Sun et al. [113] proposed an iterative algorithm to select custom instructions for ASIPs in an MPSoC along with the mapping and scheduling of tasks to maximally improve performance under an area constraint. A dynamic programming based algorithm was introduced in [25] to find optimal mapping of tasks on ASIPs of an MPSoC under a period constraint, where custom instructions for ASIPs and interval-based mapping were considered.

#### 2.1.7 Processor customization and cache customization

The works in [59, 60, 103] considered a pipeline of ASIPs for multimedia applications. They maximized performance improvement per unit area [103] or minimized area under performance constraints [59, 60] while exploring custom instructions and cache configurations. Pruning algorithms, heuristics and integer linear programming based approaches were proposed in these works.

It is clear that none of the above works considered combined use of DVFS, processor customization, cache customization and task mapping, which has a potential to save significant amounts of energy. To the best of our knowledge, our contribution of designing heterogeneous MPSoC is the first to use these techniques together for energy minimization under performance and area constraints in application specific MPSoCs for multimedia applications.

# 2.2 Dynamic technique - Static architecture

Design time techniques are beneficial for static architectures when the workloads are known a priori. On the other hand, dynamic techniques are required for applications exhibiting phase behaviours [53] (which is difficult to capture in static techniques). Most of the commercial mobile platforms, which are not applicationspecific have static architectures. Examples include NVIDIA's Tegra [28], Qualcomm's Snapdragon [56] and Samsung's Exynos [29] platforms. We discuss different types of dynamic techniques on static architectures in detail.

#### 2.2.1 Homogeneous Multi-cores

There exists plenty of prior works on dynamic power management on homogeneous multi-core systems. Most of the works focus on power management using any combination of techniques like DVFS, load balancing and task migrations. Few recent works [26, 80, 82, 122] focuses on power management of homogeneous multi-core systems based on the control theory. [82] allocates the chip power budget to each of the power islands, which is in turn distributed to the individual cores by employing DVFS. The authors in [93] proposed a hierarchical feedback-based control system for power management in server farms. Isci et al. [58] evaluate a DVFS based global power management policy with various objectives like prioritization, power balancing and throughput for different combinations of benchmarks. Rangan et al. [94] explore the use of thread migration in power management compared to the traditional DVFS scheme. The authors in [115] proposed a power management technique based on linear programming using DVFS and thread mapping. In [122], the authors present a control theory based power management framework using per-core DVFS capability and dynamic cache resizing. Ma et al. [80] present a scalable power management solution for workloads that contain a mix of multi-threaded and single-threaded applications in homogeneous chip multiprocessor. However, these solutions are designed for homogeneous multi-core systems and require non-trivial modifications to adapt them to heterogeneous multi-cores.

#### 2.2.2 Heterogeneous Multi-cores

The potentials of heterogeneous multi-cores in terms of power-performance efficiency have been illustrated in [12, 24, 69, 70, 118]. However, the heterogeneity introduces additional complexity to the dynamic/runtime scheduler [27, 70]. [74] proposed a scheduling algorithm for heterogeneous cores that incorporates the following techniques: a) asymmetric aware load balancing, b) fast-core first scheduling and c) NUMA-aware migrations. Similarly, the authors in [100] proposed an asymmetric-aware scheduler, where ILP intensive and TLP intensive threads are scheduled in fast and small cores, respectively. In both the works, the heterogeneous cores are simply symmetric cores using different frequency levels without any micro-architectural differences. [68] identified the key metrics such as external and internal stalls, for mapping a task to the appropriate core type to improve performance. The heterogeneity is achieved by limiting the instruction retirement bandwidth. Operating system support for heterogeneous architecture with non-identical but overlapping ISA was proposed in [75]. Craeynest et al. [118] propose a scheduling technique for asymmetric multi-cores using online performance estimation across different core types. Similarly, Koufaty et al. [69] propose a dynamic heterogeneous aware scheduler, which schedules tasks with very low memory stalls on complex cores for higher performance. However, none of these techniques consider power management as an optimization criteria.

A study by Winter et al. [123] evaluates various scheduling and power management techniques for heterogeneous multi-cores with special considerations to the scalability of the approaches. They propose a thread scheduling algorithm called *Steepest Drop*, which has a light overhead and completely ignores the DVFS technique. The technique Pack & Cap proposed in [26] uses thread packing and DVFS to maximize performance under a TDP constraint. Schranzhofer et al. [101] introduce a static solution for task to core mapping problem in heterogeneous MPSoC. [27] developed energy-aware scheduling for a single task on Intel QuickIA heterogeneous platform with two cores. Our work dynamically incorporates all the three techniques (load balancing, task migration and DVFS) in both *HPM* and *PPM* frameworks to meet performance demands at minimum energy consumption under a power budget.

#### 2.2.3 Computational Economics

One of the dynamic power management technique (PPM) proposed in this thesis is based on price theory, which borrows lots of inspiration from computational economics. Few existing works [9, 22, 34–36, 50, 79, 98] borrow economic theory ideas to develop power or thermal management schemes. Ebi et al. [34] propose an agent-based power distribution scheme for multi-cores, where the trading commodity is the power units. Agent based dynamic thermal management techniques are proposed in [9, 47], where negotiations are made in the market to make efficient task migration decisions. Roy et al. [98] propose an energy management technique for mobile devices based on abstractions such as isolation, delegation and subdivision. This technique requires building an offline energy model for a system, which consists of a multi-core that uses two different ISA (ARM11 and ARM9).

Some prior works [22, 50, 79] employ welfare economics in datacenters to improve power efficiency. [50, 79] employ Mixed Integer Linear Programming (MILP) technique for determining the optimal allocation of resources. Lubin et al. [79] present power management in homogeneous multi-core datacenters. This approach is extended to heterogeneous systems in [50]. The solving time is quite high (800ms) for MILP formulation. This is only suitable for datacenter workloads exhibiting relatively stable phases so that allocation decisions can be made at long intervals (e.g., 10-minute interval). But such high overhead cannot be tolerated in a mobile platform with dynamic workloads where the allocation decisions need to be revised multiple times per second.

#### 2.2.4 Power-Performance Model

We also propose a power-performance estimation model for heterogeneous multicore. Considerable number of prior works [19, 44, 66] have developed analytical performance models for processors. The two predominant approaches employed in building performance models are mechanistic modeling and empirical modeling. Mechanistic models are purely based on the insights of the target processor architecture. In [64, 66], the authors developed a simple interval based mechanistic model for out-of-order cores that assumes a sustained background performance level, which is punctuated by transient miss-events. The models from [64, 66] was further improved in [43] by weighing the dispatch stage in detail. Eyerman et al. [19] propose mechanistic model for superscalar in-order processors. In empirical modeling, the performance model is considered as a black box and typically inferred using statistical/regression techniques. Joseph et al. [62] use non-linear regression performance modeling. In [72], the authors employ spline-based regression modeling for performance and power across different micro-architectural configurations. The authors in [44] propose hybrid mechanistic-empirical modeling for commercial processor cores with few simplistic assumptions. However, the model proposed in this thesis uses the combination of compile-time analysis, mechanistic modeling and empirical modeling to construct performance models for both out-of-order and in-order cores with better accuracy on a real platform.

## 2.3 Dynamic technique - Dynamic architecture

Our last contribution is a power/thermal aware dynamic reliability management technique. Traditionally, dynamic thermal management techniques were employed as a convenient proxy to improve the lifetime reliability of the processors [109]. Commonly employed mechanisms that reduce temperature include DVFS, activity migration [33, 107], fetch gating and clock gating. However, these techniques do not consider the lifetime reliability problem explicitly. Donald et al [33] weighed the efficiency of various combinations of DVFS, clock gating and migration for thermal management.

Several techniques have been proposed for lifetime reliability (also known as hard errors) management. Srinivasan et al. [109] proposed an architectural level analytical model, called Reliability-Aware Micro-Processor (RAMP), for temperature induced lifetime reliability. They explore the effectiveness of optimizing the architectural configurations and the voltage/frequency settings statically to meet the reliability target. Karl et al. [67] proposed the use of a proportionalintegral-derivative (PID) controller based DRM technique. The most common technique employed for DRM is DVFS, possibly with a feedback controller. Dynamic wearout centric job scheduling in chip multiprocessor proposed in [45] employs a fine grained reliability management at the module-level of the cores. As these approaches focus only on the lifetime reliability, the peak temperature constraint is not considered.

We show that dynamically adapting architectural configurations along with DVFS can provide better performance and meet both reliability and/or thermal constraints. Also, while previous works are mostly reactive in nature, i.e., the performance is throttled only when reliability constraint is violated, we propose a predictive DRM technique. Also, we extend our technique to accommodate both reliability and thermal/power constraints.

# Chapter 3

# Power-Performance Modeling on Heterogeneous Multi-cores

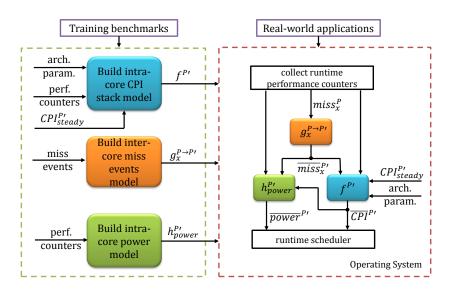

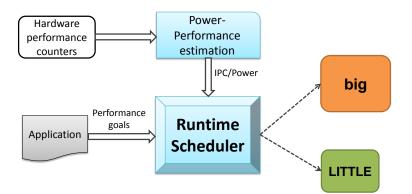

A predictive technique that can estimate power-performance across different core types in heterogeneous multi-cores can solve the challenge of scheduling the workload to the appropriate core types. In this chapter, we propose a power-performance estimation model for heterogeneous multi-cores that can be efficiently employed in any prediction based scheduling power management technique. We also develop an online predictive scheduling algorithm which leverages the benefits of the developed power-performance model.

Earlier proposals [13, 69, 74] employed a simple strategy of scheduling memoryintensive workloads on the small core and compute-intensive workloads on the big core. Recently [119] has shown that this strategy may lead to sub-optimal mappings and it is imperative to accurately estimate the power-performance characteristics of a workload on different core types. The Performance Impact Estimation (PIE) mechanism proposed in [119] is a dynamic technique that collects profile information while executing the application on any one core type, and estimates the performance on the other core type. This estimation allows the scheduler to make appropriate adjustments to the application-core mapping at runtime. However, the PIE mechanism [119] has few shortcomings that renders it difficult, if not impossible, to be deployed on real hardware. First, the estimation is based on a number of simplifying assumptions such as the presence of identical cache hierarchy and branch prediction on both core types, which are unrealistic for commercial asymmetric multi-cores. Second, the PIE mechanism requires profile information, such as the inter-instruction dependency distance distribution, that cannot be collected on existing cores and requires specialized hardware support. Third, power estimation is completely missing as [119] focuses on throughput oriented server workload. Finally, and most importantly, the mechanism is evaluated using simulator where one has complete flexibility in choosing the core configurations.

We develop power-performance model for commercial heterogeneous multi-core: ARM big.LITTLE. While an application is executing on ARM Cortex-A7 (alternatively ARM Cortex-A15), we collect profile information provided by hardware counters, and estimate power and performance characteristics of the same application on ARM Cortex-A15 (alternatively ARM Cortex-A7). We evaluate the accuracy of our estimation on real ARM big.LITTLE hardware platform. We also construct a runtime scheduler that uses the estimation model for meeting the performance goals of an application under minimal energy consumption.

Our modeling and estimation on real hardware are challenging in many ways. First, the big core and the small core are dramatically different, not just in the pipeline organization, but also in terms of memory hierarchy and the branch predictor — a reality that is ignored in all previous works [69, 100, 119]. These differences render the power, performance estimation from one core type to another considerably more difficult. Second, we are constrained by the performance counters available on the cores and their idiosyncrasies; for example, while the big core provides the L2 cache write access counter, it is unavailable on the small core. More importantly, in contrast to simulation based modeling work, we cannot rely on additional profiling information, such as inter-instruction dependency [119], that can only be collected by introducing extra hardware.

We overcome the challenges outlined above using a combination of static (compile time) program analysis, mechanistic modeling [64, 66], which builds analytical model from an understanding of the underlying architecture, and empirical modeling [62, 72], which employs statistical inferencing techniques like regression to create an analytical model.

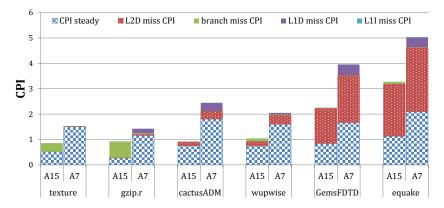

Our performance model for any core centers around the CPI (cycles per instruction) stack that quantifies the impact of different architectural events (such as data dependency, cache miss, branch misprediction etc.) on the execution time. While we can obtain information about certain events (e.g., cache miss, branch misprediction) from the hardware counters, other information such as data dependency are not readily available. We rely on compile time static program analysis technique to capture the data dependency information and its impact on pipeline stalls.

Once we develop the CPI stack based performance model for each core, we proceed to estimate the CPI stack of the second core given the CPI stack of the first core. We employ regression modeling to estimate the architectural events (cache miss, branch misprediction) on the second core given information about the architectural events on the first core. These estimates of architectural events can be plugged into the CPI stack model of the second core to derive the CPI value and hence the performance estimate. Finally, our power model uses the CPI value along with additional information, such as instruction mix, memory behavior etc., to estimate the power behavior of the core.

Our concrete contributions in this chapter are the following.

- We propose a combination of static program analysis, analytical modeling, and statistical techniques to model the performance of individual cores and estimate power, performance across different cores on single-ISA heterogeneous multi-core platforms.

- Ours is the first work towards performance estimation across asymmetric cores on real hardware. Estimation on real hardware is challenging compared to simulation based studies [119] due to distinctly different configurations of the cores, memory hierarchy, and unavailability of some of the required hardware counters.

- Ours is the first work to model CPI stack on real out-of-order and in-order cores. [44] is the only existing work that models CPI stack for commercial out-of-order processors; but does not consider in-order processors. We demonstrate that our CPI stack model is more accurate as we combine the strengths of static program analysis and runtime analytical modeling.

- Ours is the only work to derive power estimation on the second core solely based on the execution profile on the first core. Existing works [27] require execution of the application on both cores to estimate power, an assumption that is unrealistic when migration cost from one core type to another is relatively high, as is the case in our setting.

- We implement a runtime predictive scheduler that integrates the powerperformance estimation model for single-ISA heterogeneous multi-core platform. The online scheduler achieves the performance goals with minimal energy consumption for an application.

# 3.1 ARM big.LITTLE architecture

We first describe the micro-architectural features of the ARM big.LITTLE heterogenous multi-core that we model for power, performance estimation. The

| Parameter            | Cortex-A7           | Cortex-A15        |

|----------------------|---------------------|-------------------|

| Pipe-line            | In-order            | Out-Of-Order      |

| Issue Width          | 2                   | 3                 |

| Fetch Width          | 2                   | 3                 |

| Pipeline Stages      | 8-10                | 15-24             |

| Branch Predictor     | 512-entry BTB       | 2K-entry BTB      |

|                      | 2-way               | 2-way             |

| L1 I-cache           | 32 KB/2-way $/32 B$ | 32 KB/2-way/64B   |

| L1 D-cache           | 32 KB/4-way $/64 B$ | 32 KB/2-way/64B   |

| L2 Unified-cache     | 512 KB/8-way/64B    | 1MB/16-way $/64B$ |

| Frequency Levels     | 8                   | 8                 |

| Frequency Range(MHz) | 350-1000            | 500-1200          |

| Voltage Range(mV)    | 900 - 1050          | 900 - 1050        |

Chapter 3. Power-Performance Modeling on Heterogeneous Multi-cores

TABLE 3.1: Architectural Parameters of Cortex-A7 and Cortex-A15

single-ISA heterogeneous architecture consists of high performance Cortex-A15 cluster and power efficient Cortex-A7 cluster, as shown in Figure 1.3. The evaluation platform we use in this work contains a prototype chip with two Cortex-A15 cores and three Cortex-A7 cores at 45nm technology. All the cores implement ARM v7A ISA. The Cortex-A15 is complex out-of-order superscalar core that can execute high intensity workloads, while Cortex-A7 is a power efficient in-order core meant for low intensity workloads. While each core has private L1 instruction and data caches, the L2 cache is shared across all the cores within a cluster. The L2 caches across clusters are kept seamlessly coherent via the CCI-400 cache coherent interconnect.

Table 3.1 summarizes the micro-architectural parameters of Cortex-A15 and Cortex-A7, obtained from publicly released data. It should be evident that the cores are genuinely asymmetric in nature. The 2-way issue in-order pipeline of A7 containing 8-10 stages is dramatically different from the 3-way issue out-of-order pipeline of A15 containing 15-24 pipeline stages. Moreover, even the cache configurations and branch predictors are distinctly different in A15 compared to A7. Most previous works [69, 100, 119] assume that the memory parameters are identical across different core types.

The architecture provides DVFS feature per cluster. The A7 cluster provides

eight discrete frequency levels between 350 MHz - 1 GHz, while the A15 cluster also provides eight discrete frequency levels between 500 MHz - 1.2 GHz. Note that all the cores within a cluster should run at the same frequency level. Moreover an idle cluster can be powered down if necessary. As our focus is on power, performance estimation across core types, we conduct the experiments by setting the same voltage (1.05 Volt) and frequency (1 GHz) for the two clusters. Estimating power, performance for different frequency levels is left as future work. We also consider execution of a sequential application on either A7 or A15, that is, we only use one core at a time and the idle cluster is powered down.

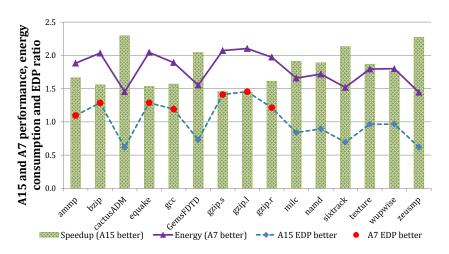

The heterogeneous cores exhibit different power and performance characteristics across workloads. Figure 3.1 shows the performance speedup, energy consumption ratio, and EDP (Energy-Delay product) ratio for 15 selected benchmarks on A15 in comparison to A7. Clearly, A15 has significant performance improvement compared to A7 (average speedup of 1.86); more importantly, the speedup varies significantly across benchmarks from 1.45 to 2.30. In terms of power, it is expected that A7 has lower average power compared to A15 for all the benchmarks. While average power on A7 is 1.44Watt, the average power on A15 varies from 4.20Watt to 5.15Watt. Even though A7 has worse performance, it can completely make up for it in terms of power to achieve far superior energy efficiency compared to A15 (1.78 times lower energy on average). A7 is also more energy efficient for all the benchmarks.

But in embedded systems, especially in interactive systems such as smartphones, we are more interested in the combination of energy and delay to decide on workload-to-core mapping because both battery life and response time are equally important. This metric is captured as Energy-Delay product (EDP). Interestingly, in terms of EDP, there is no clear winner: A15 is more efficient than A7 for 8 benchmarks due to faster execution that overcomes the power inefficiency, while A7 is superior for the remaining 7 benchmarks due to lower power consumption. Thus, the scheduler needs both power and performance behavior on a core type to decide on the appropriate mapping.

As observed in [119] and validated in our experiments, it is impossible to predict the power, performance characteristics of an application on different core types based on simple metrics such as memory access intensity. We also observe that the average migration cost across clusters is quite high: 2.10ms to move a task from A7 to A15, and 3.75ms to move from A15 to A7. This renders it unrealistic to first execute a workload on each cluster separately and then make the workload-core mapping decision as proposed in [27]. Thus it is essential to accurately estimate the CPI for performance and use the CPI to estimate power. We do so through power, performance modeling in the next section.

# 3.2 Performance Modeling

The aim of performance modeling is to estimate the performance of an application on a second core type (small/big) given its execution profile on the first core (big/small) type. Our model centers around CPI stacks. The basic observation

FIGURE 3.1: Performance improvement, energy consumption ratio and EDP ratio of A15 in comparison to A7.

FIGURE 3.2: Inter-core performance, power estimation from P to P'.

behind the model is that the CPI follows a sustained background level performance  $CPI_{steady}$  punctuated by miss events that show up as temporary peaks.  $CPI_{steady}$  captures the cycles spent in the architectural events tightly coupled to the pipeline such as data dependency among instructions and structural hazards, while  $CPI_{misses}$  represents the cycles spent due to the external events such as cache miss and branch mispredicton.

$$CPI = CPI_{steady} + CPI_{miss} \tag{3.1}$$

The performance estimation framework shown in Figure 3.2 comprises of three major steps. The first step is an off-line procedure where we build *intra-core CPI stack model* for each core type.

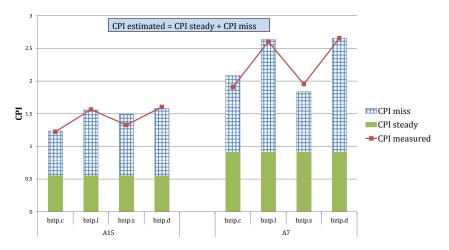

While  $CPI_{miss}$  can be expressed in terms of miss events and their latencies, computing  $CPI_{steady}$  requires presence of elaborate hardware mechanisms [119] that can collect inter-instruction dependencies and are not available in existing processors. We avoid additional hardware mechanism by observing that  $CPI_{steady}$ is an intrinsic characteristics of a program on a core type and is stable across different program inputs, whereas  $CPI_{miss}$  is highly dependent on the program inputs. For example, Figure 3.3 shows the estimated  $CPI_{steady}$  and  $CPI_{miss}$  values of *bzip* benchmark for different program inputs on A7 and A15. Note that expectedly  $CPI_{steady}$  is higher on A7 than A15 because A15 with out-of-order execution engine can better exploit instruction-level parallelism in the presence of data dependencies and structural hazards. The estimated CPI is the summation of the estimated  $CPI_{steady}$  and  $CPI_{miss}$ . For reference, we have also plotted the measured CPI. Our assumption that  $CPI_{steady}$  of an application on a core type is stable across different program inputs is validated here as the variation in CPI has been captured accurately only through variation in  $CPI_{miss}$ .

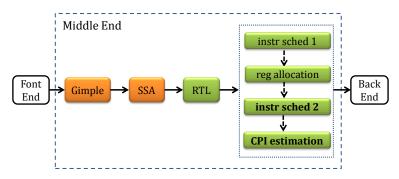

We exploit this observation to estimate  $CPI_{steady}$  of a program on both core types at compile time (see Section 3.2.1) and encode this information with the binary executable. In other words, we estimate both  $CPI_{steady}^{big}$  and  $CPI_{steady}^{small}$  for a program at compile time. Most modern compilers have an optimization pass that takes care of instruction scheduling based on the hardware description of the processor pipeline. We modify the compiler in the instruction scheduling phase to estimate the  $CPI_{steady}$ . For applications with distinct phases, i.e., multiple computation kernels with different behavior, we estimate separate  $CPI_{steady}$ value for each phase.

FIGURE 3.3: Estimated  $CPI_{steady}$  and  $CPI_{miss}$  of different inputs for the same benchmark on A7 and A15.

To build the CPI stack on a core P, we collect the execution profiles of a set of training benchmarks through the hardware counters. We then combine analytical modeling with linear and non-linear regressions to derive the CPI stack model that accurately captures the contributions of the different events to performance. The CPI stack model can thus be expressed as the function  $f^P$  where

$$CPI^{P} = f^{P}(CPI^{P}_{steady}, miss^{P}_{X}, latency^{P}_{X})$$

$$(3.2)$$

where  $miss_X^P$  and  $latency_X^P$  are the number of occurrences and latency of each occurrence of the miss event X on processor P.

The second step is another offline procedure where we develop regression models that estimate the occurrence of different miss events on processor P' given the frequency of the miss events on processor P. These *inter-core miss event estimation models* are built by collecting and correlating corresponding miss events on both cores using a set of training benchmarks. The inter-core estimation model from P to P' for an event X can be expressed by a function  $g_X^{P\to P'}$  where

$$\overline{miss}_X^{P'} = g_X^{P \to P'} \left( miss_X^P \right) \tag{3.3}$$

where  $\overline{miss}_{X}^{P'}$  is the predicted occurrence of miss event X on  $P'^{1}$ .

At runtime, when a new application is running on core P, the operating system collects the counter values at regular intervals to get information about the miss events on P. For each miss event X, it uses inter-core miss event estimation model to predict  $\overline{miss}_X^{P'}$  on core type P'. Finally, it plugs in the estimated miss event counter values in the CPI stack model of P' to predict  $\overline{CPI}^{P'}$ , which is inter-core estimated performance.

$$\overline{CPI}^{P'} = f^{P'}(CPI_{steady}^{P'}, \overline{miss}_X^{P'}, latency_X^{P'})$$

(3.4)

<sup>&</sup>lt;sup>1</sup>We use  $\overline{M}$  to indicate the estimated value of a metric across cores.

where  $CPI_{steady}^{P'}$  is estimated using analytical models, while  $\overline{miss}_{X}^{P'}$  is estimated using linear and non-linear regression models. It has been well established in literature [44] that analytical models are far more accurate than regression models. However, building analytical models for miss events are extremely difficult due to the presence of heterogeneous memory hierarchy and branch predictor.

#### **3.2.1** $CPI_{steady}$ estimation

Computing the  $CPI_{steady}$  value of a program on real hardware is challenging due to limited information that is exposed through the performance counters. While [119] proposes hardware counters that can count dynamic data dependencies and structural hazards for this purpose, the overhead of such counters is quite high due to the increased amount of book-keeping. An alternative is to simply assume  $CPI_{steady}^{P} = 1/D$  where D is the dispatch width of processor P [44]. This assumption only holds true for perfectly balanced pipelines where the number of functional units for each type of operation is equal to the dispatch width and hence there is no structural hazards. It is not realistic as commercial processors do have unbalanced number of functional units. More importantly, the assumption completely ignores the dependency of  $CPI_{steady}^{P}$  on the characteristics of the program, in particular, inter-instruction data dependencies. We sidestep this problem by computing  $CPI_{steady}^{P}$  of a program on core P at compile time.

FIGURE 3.4: Estimation of steady state CPI of a program using gcc.

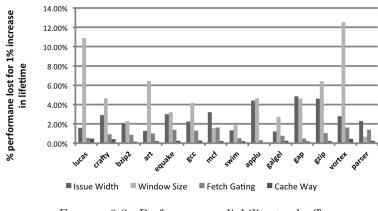

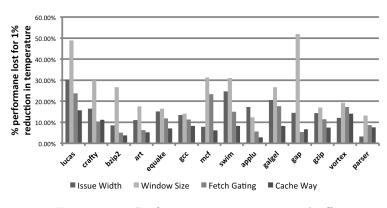

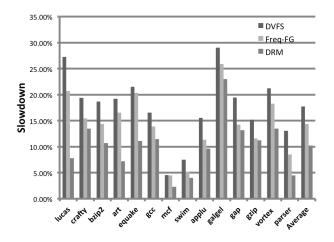

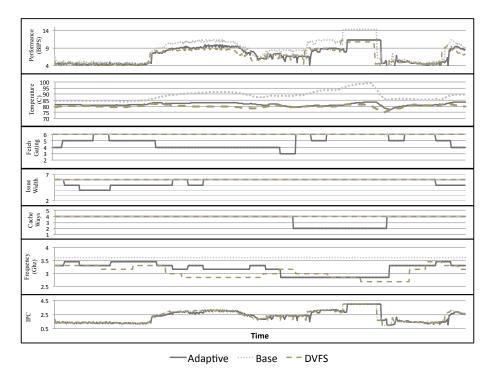

We use *gcc* compiler, where instruction scheduling optimization pass is performed twice, before and after register allocation pass (see Figure 3.4). When scheduling instructions, the algorithm uses a detailed description of the target processor pipeline. At this stage, the compiler is aware of the data dependencies among instructions and the structural hazards due to the limited number of the functional units in the processor pipeline.