# STUDY ON $IN_{0.53}GA_{0.47}As$ MOS DEVICES WITH PLASMA- $PH_3/N_2$ TREATMENT AND DEVICE STRUCTURE OPTIMIZATION

#### SUMARLINA AZZAH BTE SULEIMAN

(B. Eng.(Hons.), NUS)

# A Thesis Submitted for the Degree of Doctor of Philosophy

Department of Electrical and Computer Engineering

National University of Singapore

#### Declaration

I hereby declare that the thesis is my original work and it has been written by me in its entirety. I have duly acknowledged all the sources of information which have been used in the thesis.

This thesis has also not been submitted for any degree in any university previously.

Sumarlina Azzah Bte Suleiman

25th may 2014

#### Acknowledgements

I would like to acknowledge my supervisors, Prof. Lee Sungjoo and Prof. Ganesh Samudra for their knowledge, insightful guidance, encouragement and sincere concern throughout my graduate course, as well as giving me the opportunity to research this interesting field. They had always been there to listen and to give advice, and showed different possible ways to approach a research problem. Their dedication to research has touched my heart and motivated me to be persistent to accomplish any goal.

I am also very grateful to Chartered Semiconductor Manufacturing, Ltd. (now known as GLOBALFOUNDRIES) for the financial support and to Dr. Chan Lap, Dr. Ng Chee Mang as well as Dr Leong Kam Chew, not only for their teaching and training but also for their valuable advice on my future career. In addition, to Ms Li Leng from Spice Modelling team for allowing me to use the temperature dependent measurement equipment there.

Special thanks go to Mr. Yong, Mr. O Yan, Patrick, Boon Teck, and Mr. Sun for their kind help and sharing their invaluable experiences in frequent collaborations. I would like to thank my SNDL colleagues and peers, Oh Hoon Jung, Jian Qiang, Weifeng, Wangjian, Yi da, Ram, and many others for insightful discussion and the friendship shared.

Last, but not the least, I would like to give a sincere big thank you to my parents, sisters and grandmother who have been always supportive and encouraging throughout the Ph.D course in NUS. Any words of acknowledgement are not enough to express my deepest gratitude to them. Their continuous love, sacrifice, support, encouragement, and prayer have motivated me to strive even harder.

### **Table of Contents**

| Ac          | knowledgementsi                                                                                                                 |

|-------------|---------------------------------------------------------------------------------------------------------------------------------|

| Ta          | ble of Contentsii                                                                                                               |

| Su          | mmaryix                                                                                                                         |

| Lis         | st of Tablesxi                                                                                                                  |

| Lis         | st of Figures xii                                                                                                               |

| Lis         | st of Symbols and Acronymsxx                                                                                                    |

| 1.          | Introduction and Motivation1                                                                                                    |

| 1.1         | . Silicon Transistor Scaling: Benefits and Issues                                                                               |

| 1.2         | . Motivation of III-V Channel Materials for Future CMOS applications                                                            |

| 1.3         | . Challenges of III-V CMOS Technology4                                                                                          |

| ]           | 1.3.1. Formation of High Quality and Thermodynamically stable Gate Stack for In <sub>0.53</sub> Ga <sub>0.47</sub> As N-MOSFETs |

| 1           | 1.3.2. Channel Engineering                                                                                                      |

| ]           | 1.3.3. Formation of Ultrashallow Junctions With Low S/D resistance                                                              |

| 1.4.        | Thesis Outline9                                                                                                                 |

| <b>2.</b> ] | Literature Review and Fabrication Process20                                                                                     |

| 2.1.        | . Overview of In <sub>x</sub> Ga <sub>1-x</sub> As Passivation Techniques20                                                     |

| 2           | 2.1.1. Overview of the mechanism of plasma-PH $_3/N_2$ treatment23                                                              |

| 2.2         | . Overview of Charge Pumping Technique24                                                                                        |

| 2.3         | . Overview of Gate Leakage mechanisms                                                                                           |

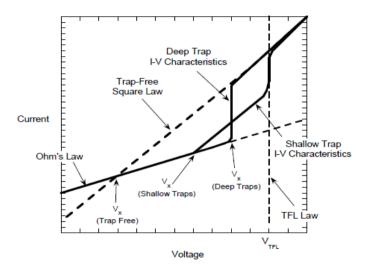

| ,           | 2.3.1. Space Charge Limited Conduction27                                                                                        |

|             | 2.3.1.1. Trap Free Insulator and Insulator with Shallow Traps28                                                                 |

| 2           | 2.3.2. Frenkel Poole (FP) Emission30                                                                                            |

| 2.4         | . Overview of Mobility Scattering Mechanisms on high-k/In <sub>0.53</sub> Ga <sub>0.47</sub> As MOS Devices                     |

| ,           | 2.4.1. Coulombic Scattering and Phonon Scattering31                                                                             |

| ,           | 2.4.2. Interface Dipole Scattering32                                                                                            |

| 2.5         | Process Flow of In <sub>0.53</sub> Ga <sub>0.47</sub> As MOSFETs Fabricated33                                                   |

| 2.5.1.    | Long Channel MOSFET Fabrication Process                                                                                                                               | .34 |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.5.2.    | Short channel sub-2µm channel length MOSFET Fabrication Process.                                                                                                      | .37 |

|           | rmal stability and Electrical Performance of plas<br>Passivated HfAlO/In <sub>0.53</sub> Ga <sub>0.47</sub> As MOSFET                                                 |     |

| 3.1. Inti | roduction and Motivation.                                                                                                                                             | 43  |

|           | ermal Stability Analysis of plasma-PH <sub>3</sub> /N <sub>2</sub> Passivated In <sub>0.53</sub> Ga <sub>0.4</sub><br>DSFET                                           |     |

|           | ectrical characterization of plasma-PH <sub>3</sub> /N <sub>2</sub> passivated AlO/In <sub>0.53</sub> Ga <sub>0.47</sub> As MOSFET                                    | 53  |

| 3.4. Beno | chmarking of In <sub>0.53</sub> Ga <sub>0.47</sub> As MOSFETs                                                                                                         | 54  |

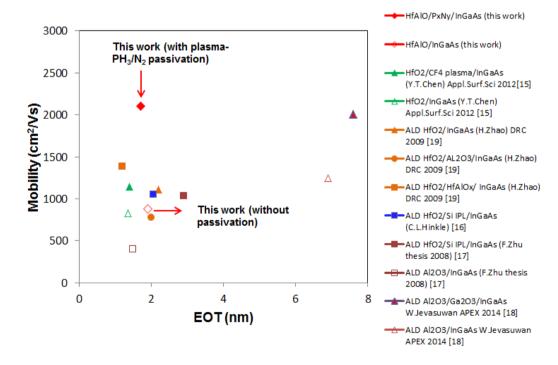

| 3.4.1.    | Mobility benchmark for high-k/In <sub>0.53</sub> Ga <sub>0.47</sub> As interface                                                                                      | 54  |

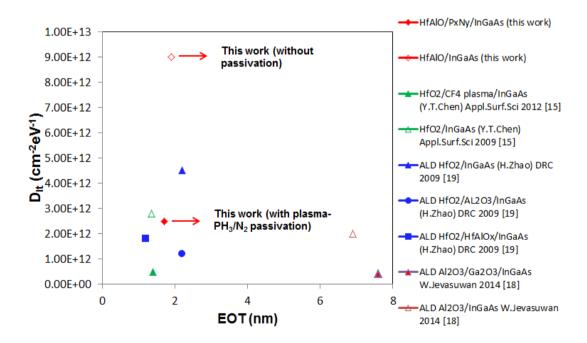

| 3.4.2.    | D <sub>it</sub> benchmark for high-k/In <sub>0.53</sub> Ga <sub>0.47</sub> As interface                                                                               | 55  |

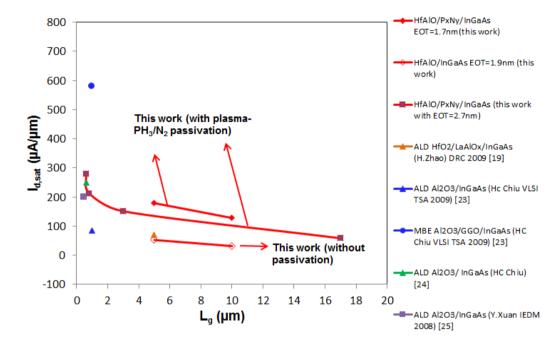

| 3.4.3.    | I <sub>d,sat</sub> benchmark for high-k/In <sub>0.53</sub> Ga <sub>0.47</sub> As interface                                                                            | 56  |

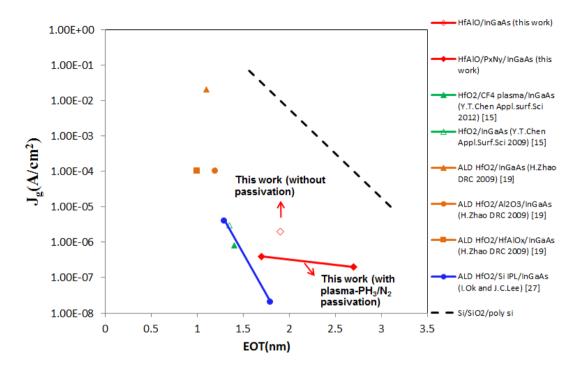

| 3.4.4.    | $J_g$ benchmark for high- $k/In_{0.53}Ga_{0.47}As$ interface                                                                                                          | .58 |

|           | nclusion                                                                                                                                                              |     |

| of plasi  | kage Current and Carrier Transport Mechanisms ma-PH <sub>3</sub> /N <sub>2</sub> Passivated In <sub>0.53</sub> Ga <sub>0.47</sub> As MOSFETs roduction and Motivation |     |

|           | rrier Transport and Leakage Mechanism of In <sub>0.53</sub> Ga <sub>0.47</sub> As OSFETs                                                                              | 65  |

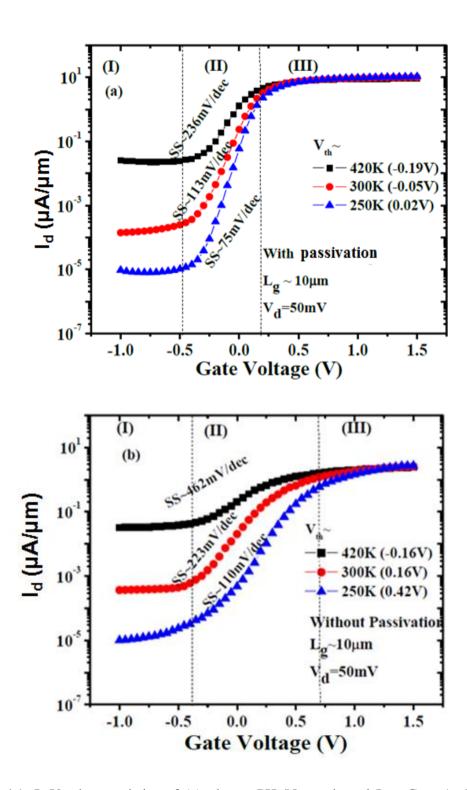

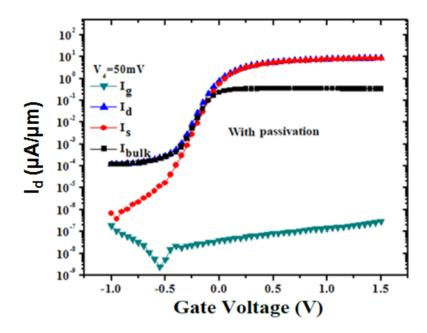

| 4.2.1.    | Carrier Transport and Off-state Leakage Mechanism                                                                                                                     | 66  |

| 4.2.2.    | Gate-leakage mechanism                                                                                                                                                | 72  |

| 4         | $J_g$ -V <sub>g</sub> Characteristics at 300 K                                                                                                                        | 72  |

|           | $\cdot$ .2.2.2. Temperature Dependence of $J_g$ -V $_g$ Characteristic                                                                                                |     |

|           | nclusion                                                                                                                                                              |     |

|           | Fects of plasma-PH $_3/N_2$ Passivation on Mobili lation Mechanisms of $In_{0.53}Ga_{0.47}As$ MOSFETs                                                                 | -   |

| 5.1. Inti | roduction and Motivation                                                                                                                                              | 84  |

| 5.2. Mo   | obility of plasma-PH <sub>3</sub> /N <sub>2</sub> Passivated In <sub>0.53</sub> Ga <sub>0.47</sub> As MOSFETs                                                         | 85  |

| 5.2.1.    | Mobility Extraction Technique                                                                                                                                         | 85  |

| 5.2.2     | Measurement of Temperature Dependence of Mobility                                                                                                                     | 86  |

| 5                | 5.2.3. Factors Causing Improvements in Mob passivated In <sub>0.53</sub> Ga <sub>0.47</sub> As MOSFET              |                                      |          |

|------------------|--------------------------------------------------------------------------------------------------------------------|--------------------------------------|----------|

|                  | 5.2.3.1. Effect of Interface states                                                                                |                                      | 90       |

|                  | 5.2.3.2. Effect of Phonon Scattering                                                                               |                                      | 95       |

|                  | 5.2.3.3. Effect of Interface Dipole Scatterin                                                                      | ıg                                   | 100      |

| 5.3.             | Conclusion                                                                                                         |                                      | 104      |

|                  |                                                                                                                    |                                      |          |

|                  | TCAD Simulation of Non-passivated                                                                                  |                                      |          |

|                  | ssivated In <sub>0.53</sub> Ga <sub>0.47</sub> As MOSFE'                                                           |                                      | _        |

| 6.1.             |                                                                                                                    |                                      |          |

|                  |                                                                                                                    |                                      |          |

| 0.2.             | Calibration of Simulation Parameters for 95 In <sub>0.53</sub> Ga <sub>0.47</sub> As MOSFET with Implanted S/D     | _                                    |          |

| 6.3.             | Effect of Interface Trap Density on Threshopassivated and plasma-PH <sub>3</sub> /N <sub>2</sub> Passivated M      |                                      |          |

| 6.4.             | Effect of Interface Trap Density on $I_d$ - $V_g$ Chapassivated and plasma- $PH_3/N_2$ Passivated Me               |                                      |          |

| 6.5.             | Performance Scalability of Implanted S/D In With and Without plasma-PH <sub>3</sub> /N <sub>2</sub> passivation    |                                      |          |

| 6.6.             | Conclusion                                                                                                         |                                      | 127      |

| 7                | <b>Optimization Studies of plasm</b>                                                                               | a-PH <sub>2</sub> /N <sub>2</sub> Pa | ssivated |

| In <sub>0.</sub> | $_{.53}$ Ga $_{0.47}$ As MOSFET for                                                                                | Sub-22nm                             | Device   |

| Per              | formance                                                                                                           |                                      | 130      |

| 7.1.             | Introduction and Motivation-Issues and Chal                                                                        | lenges                               | 130      |

| 7.2.             | Device Optimization of Implanted S/D In <sub>0.53</sub>                                                            | Ga <sub>0.47</sub> As MOSFE          | Т132     |

| 7.3.             | Raised S/D In <sub>0.53</sub> Ga <sub>0.47</sub> As MOSFET                                                         |                                      | 137      |

| 7                | 7.3.1. Source starvation and Performance scala Devices                                                             | •                                    |          |

| 7.4.             | Performance Scaling of Raised S/D With In <sub>0</sub> MOSFET                                                      |                                      |          |

| 7.5.             | Optimization of In <sub>0.53</sub> Ga <sub>0.47</sub> As MOSFET Dev<br>Performance Scalability up till Sub-22nm Te |                                      |          |

| 7                | 7.5.1. Effect of Thinner channel                                                                                   |                                      | 154      |

| -                | 7.5.2 Effect of Spacer Material                                                                                    |                                      | .158     |

| T ict | of P  | ublications                                                                         | 184 |

|-------|-------|-------------------------------------------------------------------------------------|-----|

| 8.2.  | Futu  | re Works                                                                            | 179 |

| 8.1.  | Con   | clusion                                                                             | 176 |

| 8. (  | Conc  | lusions and Future Researches                                                       | 176 |

| 7.6.  | Cone  | clusion                                                                             | 171 |

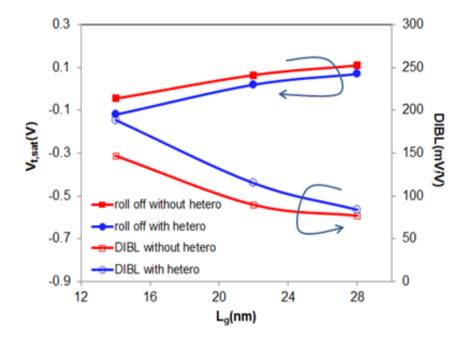

| 7     | .5.4. | Performance Scalability of Device With and Without Heterostructure and Benchmarking | 164 |

| 7     | .5.3. | Effect of Heterostructure Device.                                                   | 161 |

#### **Summary**

As the semiconductor industry approaches the limits of traditional silicon CMOS scaling, introduction of performance boosters like novel materials is becoming necessary. Nevertheless, several critical problems still need to be addressed.

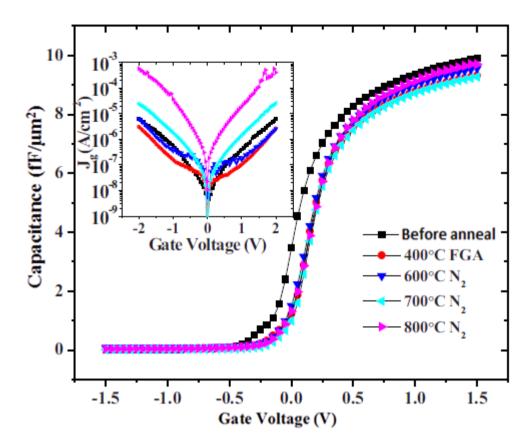

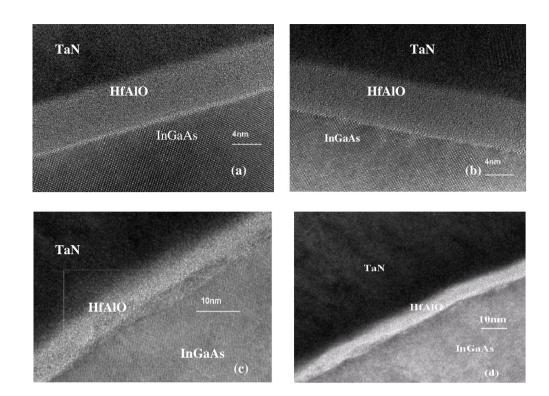

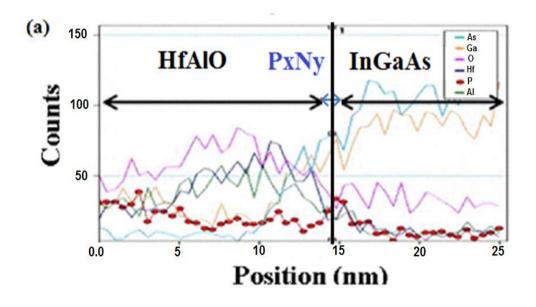

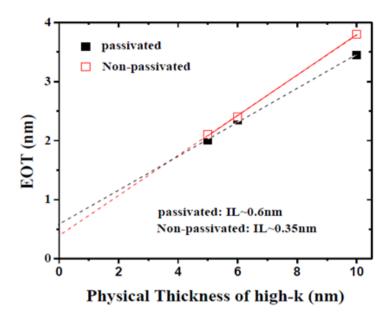

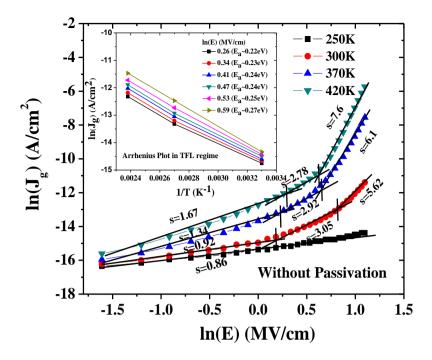

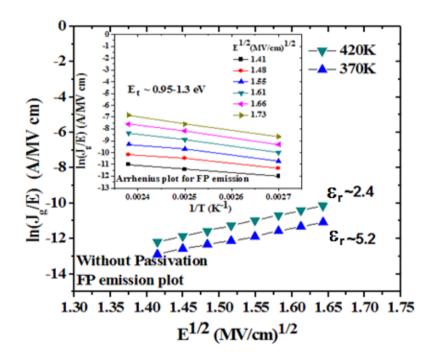

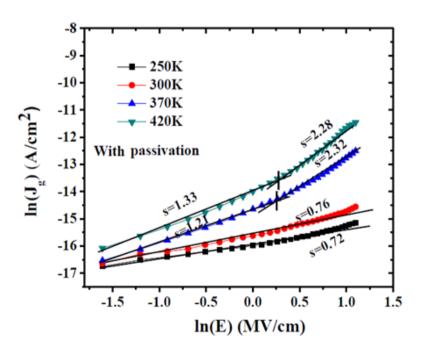

First part of the thesis focuses on the issue with high-k/In<sub>0.53</sub>Ga<sub>0.47</sub>As gate stack which is the high interface trap density resulting in gate stacks with low mobility, low I<sub>on</sub>, poor gate stack thermal stability and large gate leakage making it unsuitable for gate stack scalability. A passivation layer involving plasma-PH<sub>3</sub>/N<sub>2</sub> treatment on HfAlO In<sub>0.53</sub>Ga<sub>0.47</sub>As MOSFET has been used to address these issues. Plasma-PH<sub>3</sub>/N<sub>2</sub> passivated HfAlO/In<sub>0.53</sub>Ga<sub>0.47</sub>As gate stack reveals good thermal stability up till 800°C with much lower gate leakage due to the absence of Frenkel Poole emission associated with trap energy levels of ~0.95-1.3eV. The improvements of peak mobility and hence on-state performance of this passivated device can be attributed to the reduced trap states in the upper half of the bandgap, possibly due to reduced free As, resulting in reduced Coulombic scattering compared to non-passivated device. Also the existence of a thicker passivation layer giving a thickness of ~0.6nm for passivated device compared to the interfacial layer of ~0.35nm for non-passivated device reduces the soft optical phonon scattering contributed by the HfAlO. In addition, its robust passivation layer is effective in preventing the interdiffusion of elements between the oxide and In<sub>0.53</sub>Ga<sub>0.47</sub>As substrate, therefore reducing interface dipole scattering at high E-field and hence increases the mobility at high E-field compared to non-passivated device.

Further studies through TCAD simulations show that not only the concentration, but also the nature of the interface traps (acceptor-like vs donor-like) at upper half of the bandgap of the high- $k/In_{0.53}Ga_{0.47}As$  interface, can contribute to SS,  $V_{th}$  and hence  $I_{on}$ . It is shown that reduced acceptor-like traps at the interface of

high- $k/In_{0.53}Ga_{0.47}As$  plasma-PH<sub>3</sub>/N<sub>2</sub> pasivated device is responsible for reduced V<sub>th</sub> of the passivated device.

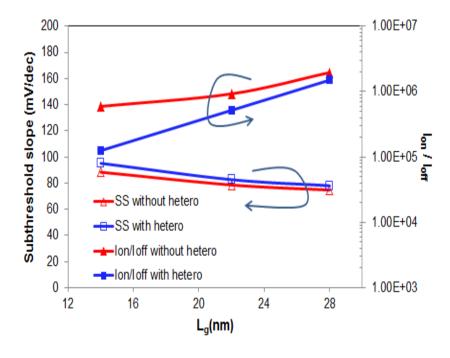

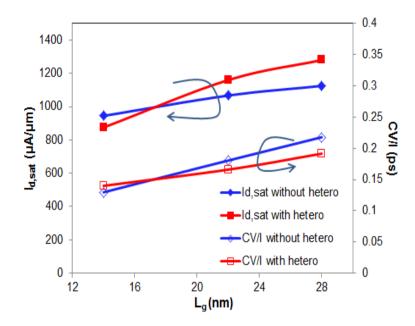

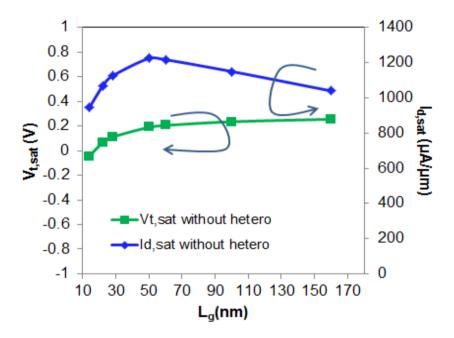

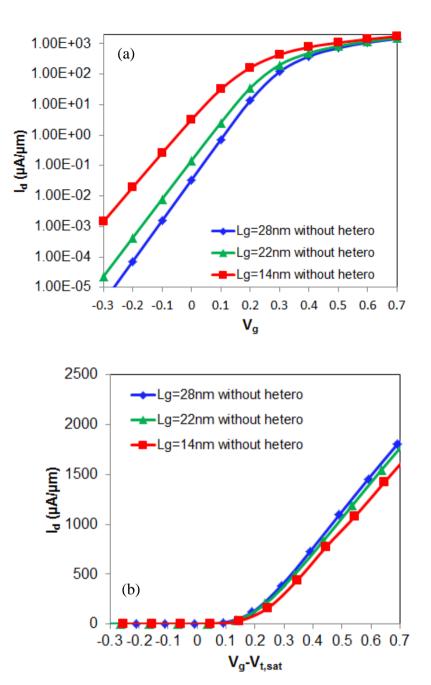

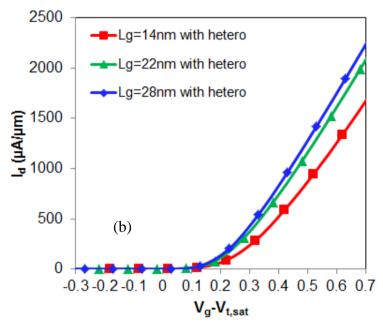

Second part of the thesis focuses on the issues with bulk-planar short channel implanted S/D In<sub>0.53</sub>Ga<sub>0.47</sub>As MOSFETs which include the large S/D parasitic series resistance due to low active carrier doping concentration resulting in source starvation and poor device electrostatic integrity. Therefore device optimization through TCAD simulation has been performed through reduced gate-to-S/D spacing with addition of 15nm wide spacer, halo doping and junction engineering through raised S/D structure. Raised S/D is effective in improving device performance relative to implanted S/D due to its ability to reduce source starvation and improve electrostatic integrity. Further optimization, suitable for 22nm and 14nm gate length plasma-PH<sub>3</sub>/N<sub>2</sub> passivated In<sub>0.53</sub>Ga<sub>0.47</sub>As MOSFETs, have also been predicted with channel engineering through RSD structure with thin channel of 3nm thickness, high-k spacers and R<sub>c</sub> of 93Ω.μm. This structure, without heterostructure for L<sub>g</sub>=14nm, is effective in achieving SS of 88.4mV/dec, DIBL=147mV/V with  $I_{d,sat}=1775\mu A/\mu m$  at  $V_g-V_{t,sat}=0.7V$ ,  $V_d=0.7V$ . On the other hand device with heterostructure gives SS of 95.2mV/dec, DIBL=188.8mV/V and I<sub>d,sat</sub>=2090µA/µm at  $V_g-V_{t,sat}=0.7V$ ,  $V_d=0.7V$ .

## **List of Tables**

| Table 1.1. Physical parameters of the commonly used semiconductors as channel materials [12]                                                                                                                                                                                                                                                                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 5.1. Summary of relative intensities of As-As chemical states at the In <sub>0.53</sub> Ga <sub>0.47</sub> As surfaces, obtained from the chemical shifts in As 3d core level emission. As a reference, the bulk In <sub>0.53</sub> Ga <sub>0.47</sub> As sample is prepared by in-situ Ar sputter etching about 10 Å of the non-treated sample and the XPS spectra is analyzed [23] |

| Table 6.1. Parameters used in the calibration of the device models                                                                                                                                                                                                                                                                                                                         |

| Table 7.1. The electrical data benchmarked against the simulation work performed by other groups [24,26] for $L_g \sim 15 \text{nm}$ . $I_{d,sat}$ is referring to $V_g = 0.7V$ when comparison is made to Ref [26] and $I_{d,sat}$ is referring to $V_g = 0.7V$ at fixed $I_{off}$ of $0.1 \mu A/\mu m$ when comparison is made to Ref [24]                                               |

# **List of Figures**

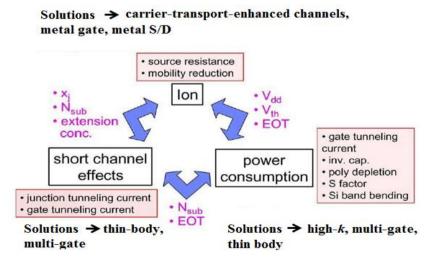

| Fig.1.1. Trade-off factors among on-current, power consumption/leakage current and short channel effects under simple device scaling and possible solutions [3]       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

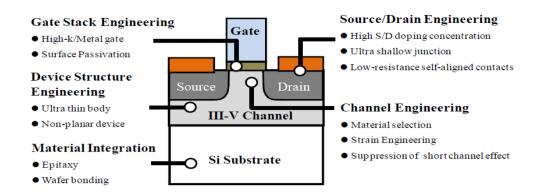

| Fig.1.2. Schematic illustration showing the technical challenges faced by high mobility III-V CMOS on Si substrates for future logic applications [13]                |

| Fig.1.3. Flowchart of the issues addressed in high- <i>k</i> /In <sub>0.53</sub> Ga <sub>0.47</sub> As MOSFETs in the first part of the thesis found in Chapters 3-6  |

| Fig.1.4. Flowchart of the issues addressed in high- <i>k</i> /In <sub>0.53</sub> Ga <sub>0.47</sub> As MOSFETs in the second part of the thesis found in Chapter 714  |

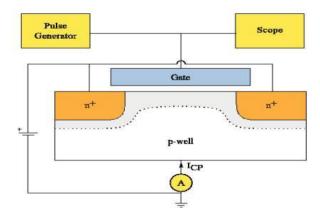

| Fig.2.1. Basic experimental set-up for charge pumping measurement [35]24                                                                                              |

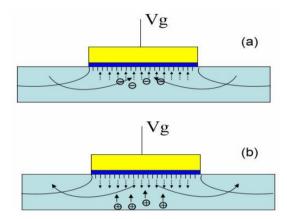

| Fig.2.2. Illustration of charge pumping effects by varying the $V_g$ (a) in inversion (b) in accumulation on a MOSFET [36]                                            |

| Fig.2.3. Space Charge limited current voltage characteristics for single set of traps containing trap free and shallow traps [44]                                     |

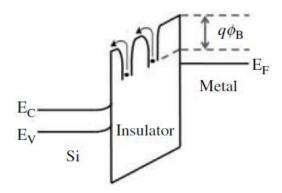

| Fig.2.4. Schematic energy band diagrams of Frenkel Poole emission [45]31                                                                                              |

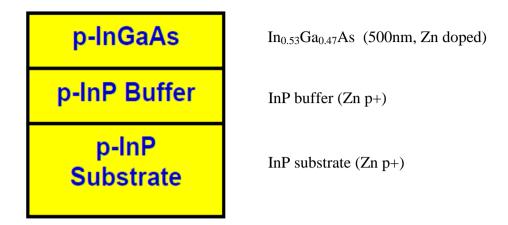

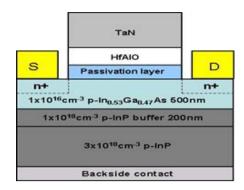

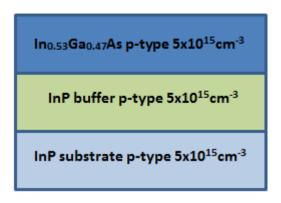

| Fig.2.5. MBE growth of p- $In_{0.53}Ga_{0.47}As$ on InP with the specifications provided. In <sub>0.53</sub> $Ga_{0.47}As$ is 500nm thick, lattice matched with InP33 |

| Fig.2.6. Process flow of long channel In <sub>0.53</sub> Ga <sub>0.47</sub> As N-MOSFET fabrication36                                                                 |

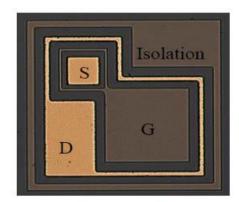

| Fig.2.7. Top view of a ring shape $In_{0.53}Ga_{0.47}As$ MOSFET, fabricated using a two-mask step                                                                     |

|                                                                                                                                                                       |

| Fig.2.8. Schematic cross section of the self-aligned In <sub>0.53</sub> Ga <sub>0.47</sub> As N-MOSFET integrated with CVD HfAlO gate dielectric and TaN metal gate37 |

|                                                                                                                                                                       |

| integrated with CVD HfAlO gate dielectric and TaN metal gate                                                                                                          |

| integrated with CVD HfAlO gate dielectric and TaN metal gate                                                                                                          |

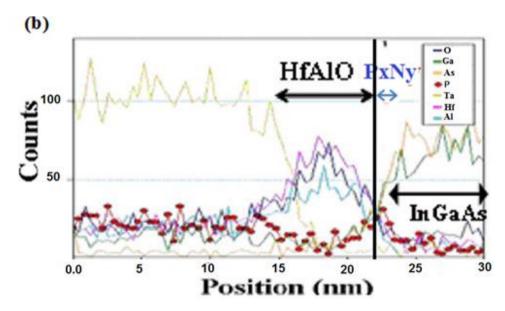

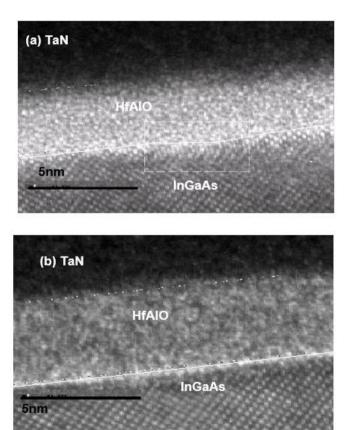

| from Fig.3.2(c) of TEM image and (b) uniform smooth interface taken from Fig.3.2(d) of TEM image                                                                                                                                                                                                                                                                                                                                                              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

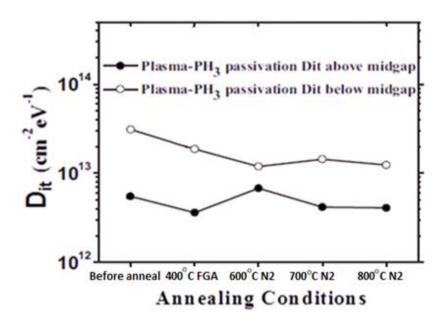

| Fig.3.4. Comparison of the D <sub>it</sub> of plasma-PH <sub>3</sub> /N <sub>2</sub> passivated devices which have undergone annealing conditions at 600°C N <sub>2</sub> 1min, 700°C N <sub>2</sub> 1min and 800°C N <sub>2</sub> 5s                                                                                                                                                                                                                         |

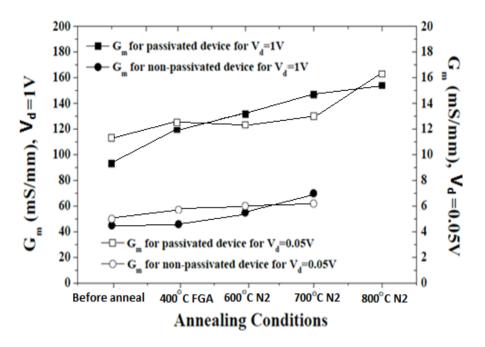

| Fig.3.5. Maximum transconductance ( $G_m$ ) which is normalized with gate width of 65µm, for plasma-PH <sub>3</sub> /N <sub>2</sub> passivated and non-passivated devices, which have undergone annealing conditions at 600°C N <sub>2</sub> 1min, 700°C N <sub>2</sub> 1min and 800°C N <sub>2</sub> 5s (only for plasma-PH <sub>3</sub> /N <sub>2</sub> passivated devices)                                                                                 |

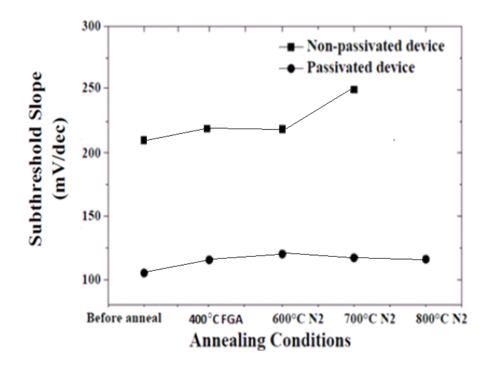

| Fig.3.6. Subthreshold slope taken at $V_d$ =0.05V which is normalized with gate width of 65µm, for plasma-PH <sub>3</sub> /N <sub>2</sub> passivated and non-passivated devices, which have undergone annealing conditions at 600°C N <sub>2</sub> 1min, 700°C N <sub>2</sub> 1min and 800°C N <sub>2</sub> 5s (only for plasma-PH <sub>3</sub> /N <sub>2</sub> passivated devices)                                                                           |

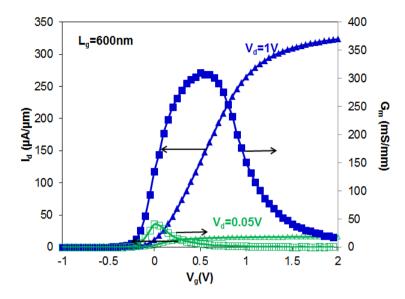

| $\label{eq:fig.3.7.} Fig.3.7. \ \ I_dV_g \ \ characteristics} \ \ of \ \ the \ \ P_xN_y\text{-passivated} \ \ TaN/HfAlO/In_{0.53}Ga_{0.47}As$ MOSFET with $L_g\text{=-}600\text{nm}$ , showing maximum $G_m$ of $310\text{mS/mm}$ 53                                                                                                                                                                                                                          |

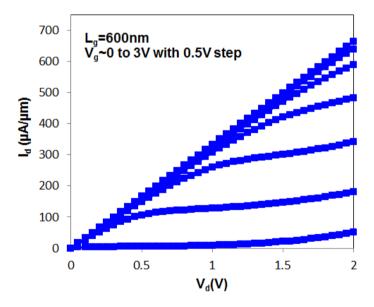

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                          |

| Fig.3.9. Mobility benchmarking with various passivation techniques including this work                                                                                                                                                                                                                                                                                                                                                                        |

| Fig.3.10. $D_{it}$ (taken at E-E <sub>i</sub> =0.25eV) as a function of EOT for devices with different passivation or bi-layer gate oxide.                                                                                                                                                                                                                                                                                                                    |

| Fig.3.11. Summary of drain current of representative work on $In_{0.53}Ga_{0.47}As$ MOSFETs, taken at $V_d$ =1V, $V_g$ - $V_{t,sat}$ =1.5V                                                                                                                                                                                                                                                                                                                    |

| Fig.3.12. Benchmarking of gate leakage current density, $J_g$ , at $V_{fb}+1V$ for MOSFETs for this work and other passivation techniques from literature                                                                                                                                                                                                                                                                                                     |

| Fig.4.1. $I_d$ - $V_g$ characteristics of (a) plasma-PH $_3$ / $N_2$ passivated $In_{0.53}Ga_{0.47}As$ N-MOSFET as a function of temperature. Ideal $V_{th}$ at 300 K is -0.098 V and (b) non-passivated $In_{0.53}Ga_{0.47}As$ N-MOSFET as a function of temperature. Ideal $V_{th}$ at 300 K is -0.096 V                                                                                                                                                    |

| Fig.4.2. Four-terminal $I_d$ - $V_g$ measurements on plasma-PH $_3$ / $N_2$ passivated In $_{0.53}$ Ga $_{0.47}$ As N-MOSFET showing $I_{off}$ dominated by $I_{bulk}$ , known as reverse biased drain-substrate junction leakage.                                                                                                                                                                                                                            |

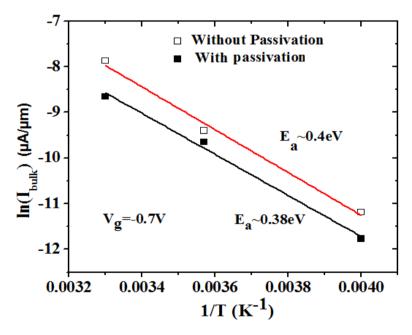

| Fig.4.3. Temperature dependence of substrate current ( $I_{bulk}$ ) of both plasma-PH <sub>3</sub> /N <sub>2</sub> passivated and non-passivated In <sub>0.53</sub> Ga <sub>0.47</sub> As N-MOSFET taken from temperatures between 300K to 250K. The $I_{bulk}$ values have been taken at $I_{off}$ values at $V_g$ =-0.7V from Fig.4.1(a) and 4.1(b). An activation energy of $E_g$ /2 extracted in Region (I) confirms SRH generation-recombination current |

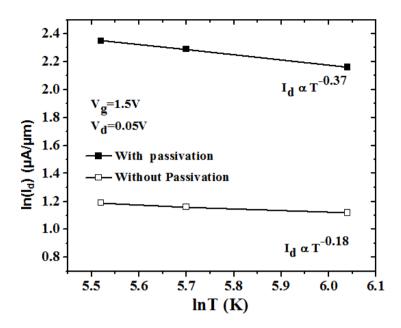

| Fig.4.4. $ln I_d $ vs $ln T $ plot of both plasma-PH $_3/N_2$ passivated and non-passivated $ln_{0.53}Ga_{0.47}As$ N-MOSFET showing a negative temperature dependence of the oncurrent                                                                                                                                                                                                                                                                        |

| $\label{eq:Fig.4.5.} Fig.4.5.~(a)~HR-TEM~image~of~non-passivated~N-MOSFET~and~(b)~HR-TEM~image~of~plasma-PH_3/N_2~passivated~In_{0.53}Ga_{0.47}As~N-MOSFET.~71$                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

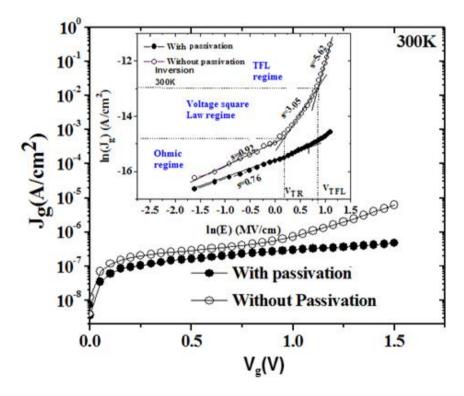

| Fig.4.6. $J_g$ characteristics of plasma-PH <sub>3</sub> /N <sub>2</sub> passivated and non-passivated In <sub>0.53</sub> Ga <sub>0.47</sub> As N-MOSFET at 300 K. Inset shows the ln  $J_g$   vs ln E  plot. EOT value of non-passivated In <sub>0.53</sub> Ga <sub>0.47</sub> As N-MOSFET is 1.9 nm and EOT value of passivated In <sub>0.53</sub> Ga <sub>0.47</sub> As N-MOSFET is 1.7 nm. The voltage boundaries and s values of J $\propto$ V <sup>s</sup> fits are also shown                                                                                                             |

| Fig.4.7. EOT vs physical oxide thickness of both passivated and non-passivated devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Fig.4.8. $ln J_g $ vs $ln E $ plot of non-passivated device at temperatures between 250K and 420K. Inset shows the Arrhenius plot in the TFL regime78                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Fig.4.9. $\ln(J_g/E)$ vs $E^{1/2}$ plots (FP fitting) observed in non-passivated $\ln_{0.53}Ga_{0.47}As$ N-MOSFET. Inset shows the Arrhenius plot in the FP emission regime                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Fig.4.10. $\ln  J_g $ vs $\ln  E $ plot of plasma-PH <sub>3</sub> /N <sub>2</sub> passivated $\ln_{0.53}Ga_{0.47}As$ N-MOSFET at temperatures between 250K and 420K                                                                                                                                                                                                                                                                                                                                                                                                                              |

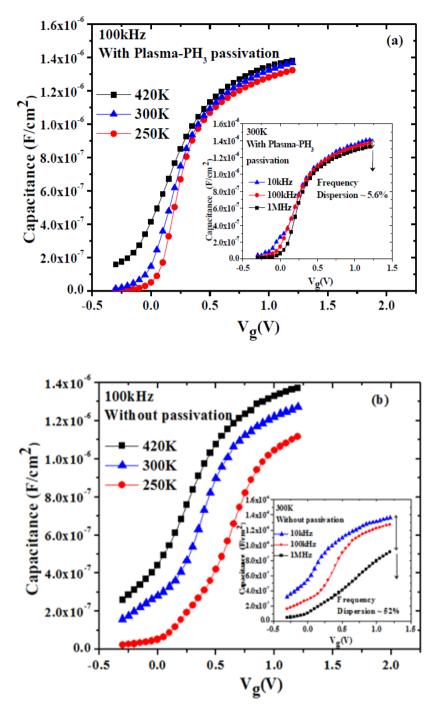

| Fig.5.1(a) C–V response at 100kHz with varying temperature of 250K to 420K of plasma-PH $_3$ /N $_2$ passivated HfAlO/In $_{0.53}$ Ga $_{0.47}$ As N-MOSFET. Inset (a) shows corresponding room-temperature $C$ – $V$ variation between 10kHz to 1MHz in passivated In $_{0.53}$ Ga $_{0.47}$ As devices and (b) C– $V$ response at 100kHz with varying temperature of 250K to 420K of non-passivated HfAlO/In $_{0.53}$ Ga $_{0.47}$ As N-MOSFET. Inset (b) shows corresponding room-temperature C– $V$ variation between 10kHz to 1MHz in non-passivated In $_{0.53}$ Ga $_{0.47}$ As devices. |

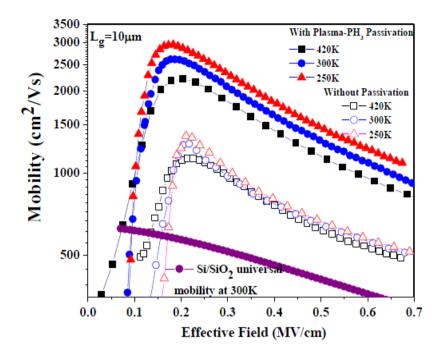

| Fig.5.2. Effective electron mobility in non-passivated and plasma-PH $_3$ /N $_2$ passivated HfAlO/In $_{0.53}$ Ga $_{0.47}$ As N-MOSFET at various temperatures from 250K to 420K, using the C-V correction method.                                                                                                                                                                                                                                                                                                                                                                             |

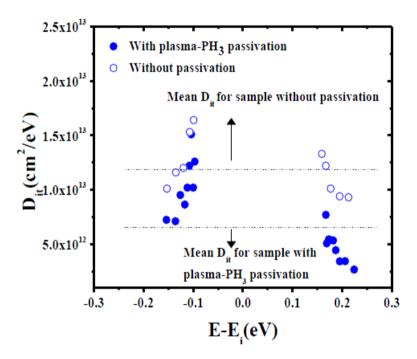

| Fig.5.3. Energy distribution of $D_{it}$ as determined by the $t_r$ and $t_f$ dependence of charge pumping currents. The horizontal lines represent the mean $D_{it}$ of the entire bandgap, for non-passivated and plasma-PH $_3/N_2$ passivated device92                                                                                                                                                                                                                                                                                                                                       |

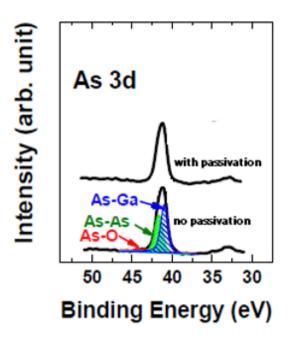

| Fig.5.4. XPS spectra for the $In_{0.53}Ga_{0.47}As$ surfaces with and without plasma-PH <sub>3</sub> /N <sub>2</sub> passivation treatment are shown for (a) As 3d. Typical results of deconvolution analysis are illustrated with the corresponding chemical bonds indicated [21]93                                                                                                                                                                                                                                                                                                             |

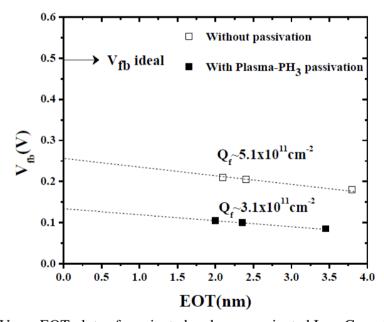

| Fig.5.5. $V_{\rm fb}$ vs EOT plots of passivated and non-passivated $In_{0.53}Ga_{0.47}As$ N-MOSFETs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

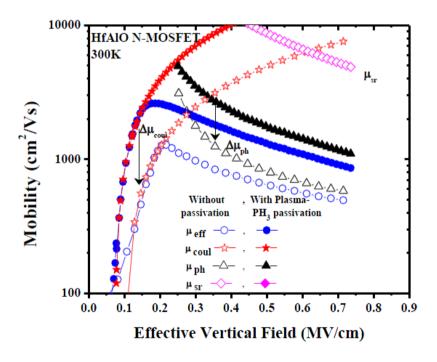

| Fig.5.6. $\mu_{eff}$ , $\mu_{coul}$ , $\mu_{ph}$ , $\mu_{sr}$ , for passivated and non-passivated device obtained using Matthiessen's rule.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

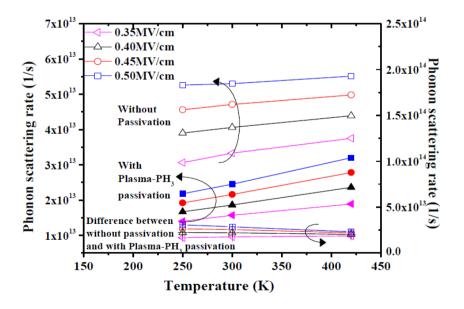

| Fig.5.7. Phonon scattering rate vs Temperature for passivated and non-passivated devices, with difference between both phonon scattering rates being contributed by the SO phonon scattering caused by HfAlO in the non-passivated device                                                                                                                                                                                                                                                                                                                                                        |

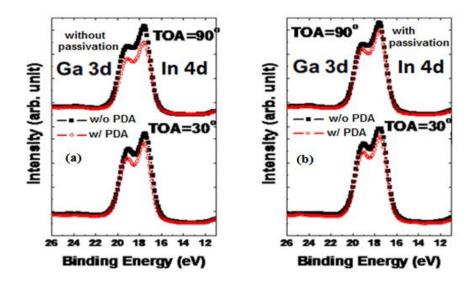

| Fig 5.8. Ga 3d and In 4d(a) XPS spectra for the $In_{0.53}Ga_{0.47}As$ surfaces without and (b) with plasma-PH <sub>3</sub> /N <sub>2</sub> passivation treatment are shown                                                                                                                                                                                                                                                                                                                                                                                                                      |

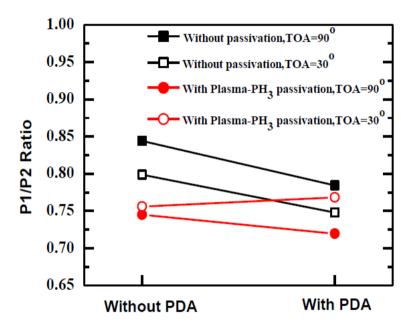

| without PDA) applied to the samples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

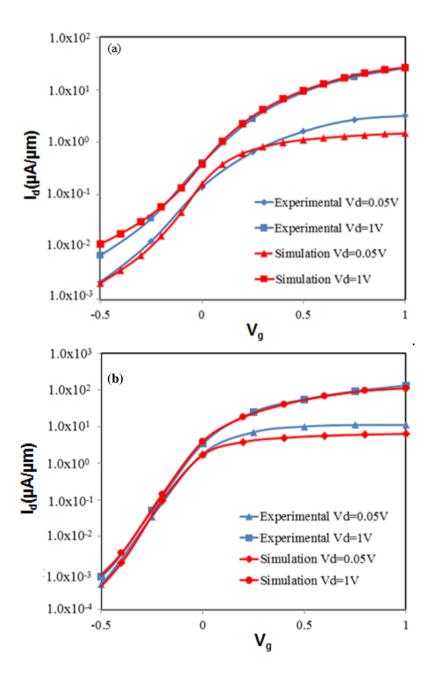

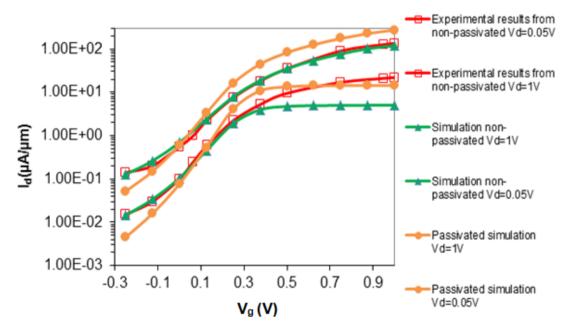

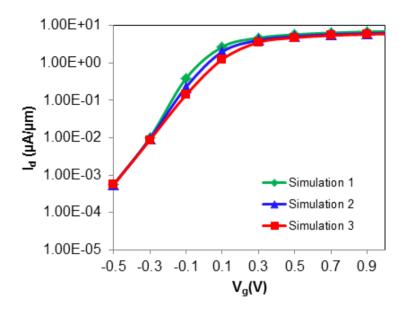

| Fig.6.1(a) Comparison between the experimental and simulated $I_d$ - $V_g$ characteristics of 4 $\mu$ m gate length non-passivated $I_{0.53}Ga_{0.47}As$ MOSFET and (b) Comparison between the experimental and simulated $I_d$ - $V_g$ characteristics of 4 $\mu$ m gate length plasma-PH <sub>3</sub> /N <sub>2</sub> $I_{0.53}Ga_{0.47}As$ MOSFET                                                                                                                                                                                           |

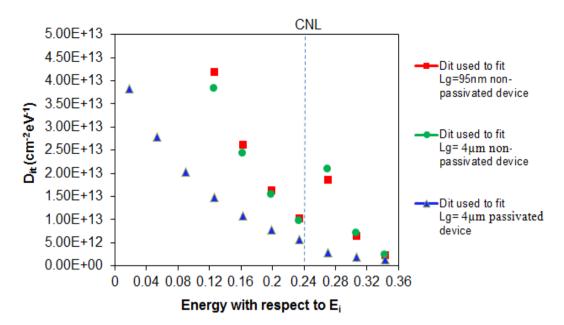

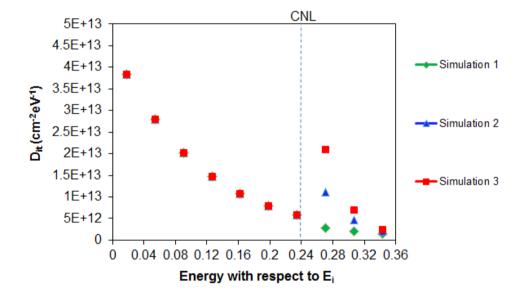

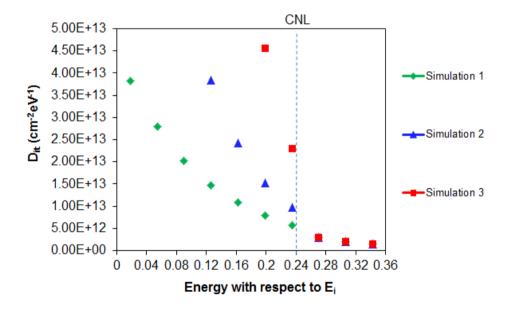

| Fig.6.2. $D_{it}$ distribution, with trap energy level with respect to the intrinsic Ferm level, of $HfO_2/In_{0.53}Ga_{0.47}As$ MOSFET with and without plasma-PH $_3/N_2$ passivation simulated for $I_d$ - $V_g$ fitting. Only the upper half of the bandgap is shown for fitting since the simulation results for surface channel architecture MOSFETs are sensitive to this part of the bandgap only [11]. Note that traps above the CNL are defined as acceptor-like traps while traps below this level are defined as donor-like traps. |

| Fig.6.3. Calibration of non-passivated $L_g$ =95nm with 10nm thick $HfO_2$ device showing matching to the experimental results. Expected performance enhancement prediction through plasma-PH $_3$ /N $_2$ passivation using simulation is also shown.                                                                                                                                                                                                                                                                                         |

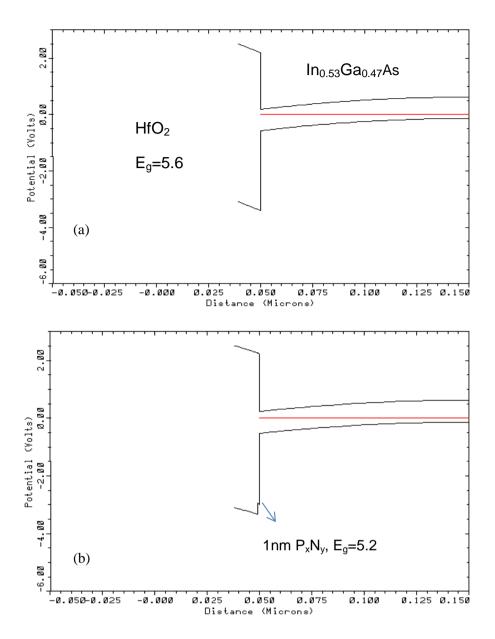

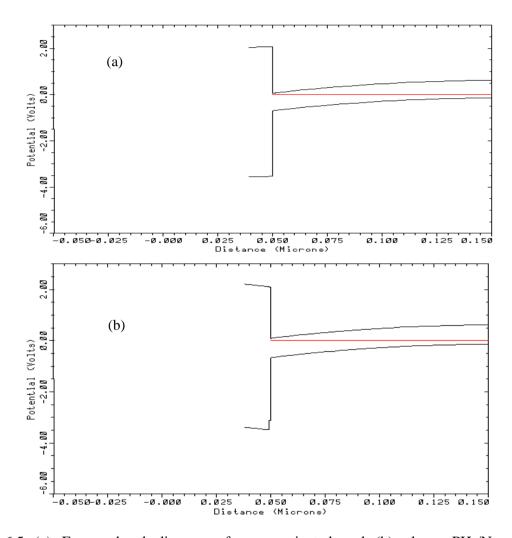

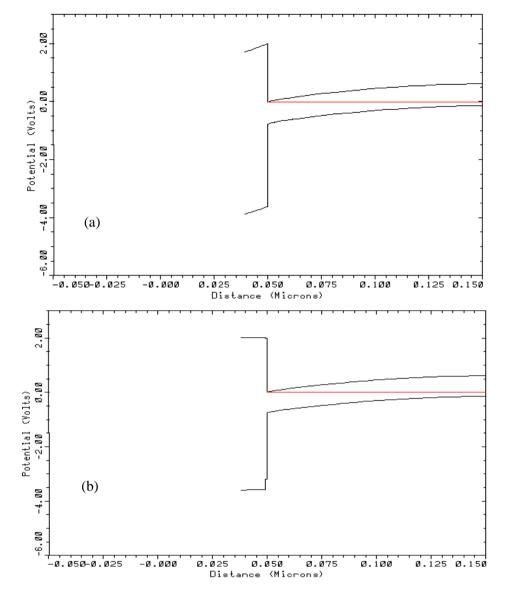

| Fig.6.4(a) Energy band diagram showing the conduction band energy, Fermi level energy and valence band of non-passivated and (b)plasma-PH $_3$ /N $_2$ passivated device taken at V $_g$ =-0.5V, V $_d$ =0.05V. The upper and lower black lines correspond to E $_c$ and E $_v$ respectively while horizontal line between E $_c$ and E $_v$ corresponds to E $_f$ .                                                                                                                                                                           |

| Fig.6.5 (a) Energy band diagram of non-passivated and (b) plasma-PH $_3$ /N passivated device before reaching strong inversion. Note that V $_g$ is taken at -0.036V for non-passivated corresponding to I $_d$ =0.1 $\mu$ A/ $\mu$ m from Fig.6.1(a) and V $_g$ at taken a -0.2V for passivated corresponding to I $_d$ =0.1 $\mu$ A/ $\mu$ m from Fig.6.1(b).                                                                                                                                                                                |

| Fig.6.6 (a) Energy band diagram of non-passivated and (b) plasma-PH $_3$ /N passivated device at the respective V $_{th}$ . Note that V $_g$ is taken at 0.1V for non-passivated device and V $_g$ is taken at -0.12V for passivated device                                                                                                                                                                                                                                                                                                    |

| Fig.6.7 (a) Distribution of acceptor-like trap density used in three simulations of Fig.6.7(b). The simulations have been varied such that acceptor-like traps, which correspond to energy trap levels beyond CNL, are increasing while the donor-like traps corresponding to energy trap levels below CNL are fixed                                                                                                                                                                                                                           |

| Fig.6.7 (b) MEDICI simulation of $In_{0.53}Ga_{0.47}As$ MOSFET with varying acceptor-like interface traps and fixing donor-like traps, with $D_{it}$ distribution shown in Fig.6.7(a). Acceptor-like traps increase $V_{th}$ and on-current. On current is degraded from 112 $\mu A/\mu m$ to $105\mu A/\mu m$ and $97\mu A/\mu m$ , and $V_{th}$ increases from 0, 0.02V to 0.1V, for $D_{it}$ distribution given as simulation 1,2, 3 respectively shown in Fig.6.7(a)                                                                       |

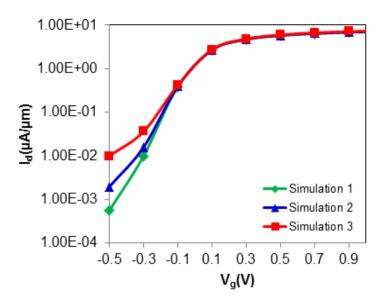

| Fig.6.7 (c) Distribution of donor-like trap density in three simulations of Fig.6.7(d variation. The simulations have been varied such that donor-like traps, which correspond to energy trap levels below CNL, are increasing while the acceptor-like traps corresponding to energy trap levels above CNL are fixed                                                                                                                                                                                                                           |

| interface traps and fixing acceptor-like traps with D <sub>it</sub> distribution shown in Fig.6.7(c). Donor-like traps change SS and off current of the device, keeping on-current unchanged.                                                                                                                                                                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

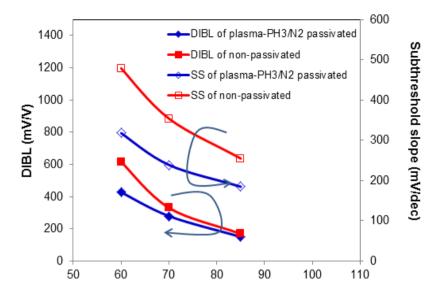

| Fig 6.8. Comparison of DIBL and subthreshold slope as a function of gate length for non-passivated vs plasma-PH $_3/N_2$ passivated, where EOT of non-passivated device is 3.2nm and passivated device is 3nm taken from the reported data [3]. The SS has been taken at $V_d$ =1 $V$                                                                                                         |

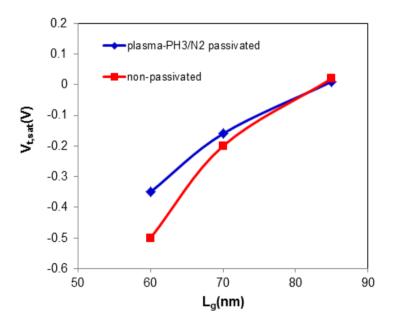

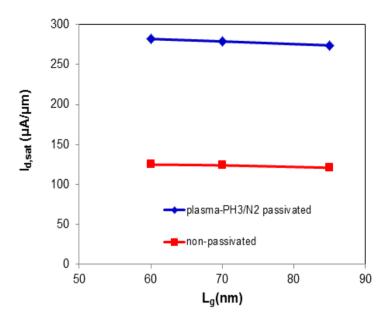

| Fig.6.9. Comparison of $V_{t,sat}$ vs $L_g$ for the two types of devices with scaling metrics at $1\mu A/\mu m$                                                                                                                                                                                                                                                                               |

| Fig.6.10. Comparison of $I_{d,sat}$ vs $L_g$ for the two types of devices at $V_d = 1V$ , $V_g = 1V$ , where EOT of non-passivated device is 3.2nm and passivated device is 3nm taken from the reported data [8]                                                                                                                                                                              |

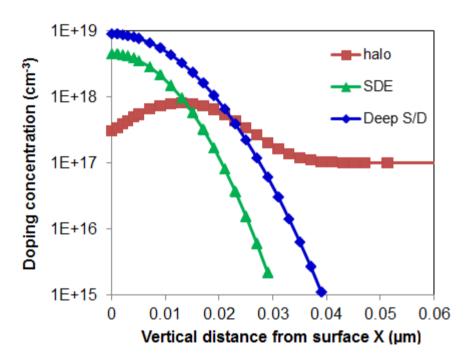

| Fig.7.1. 1D Doping profile for the extension, SD and halo implants by taking a vertical cut at the S/D                                                                                                                                                                                                                                                                                        |

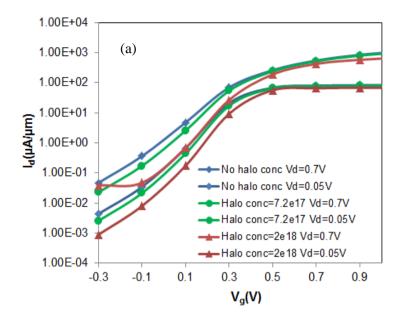

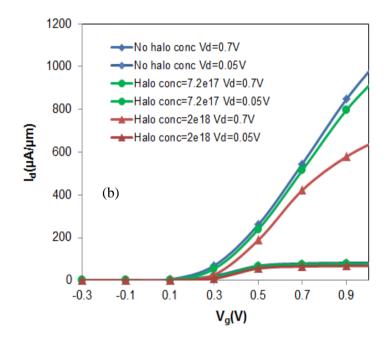

| Fig.7.2 (a) $I_d$ - $V_g$ plot for plasma- $PH_3/N_2$ passivated $L_g$ =70nm device with and without halo implant and (b) $I_d$ - $V_g$ plot in linear scale for plasma- $PH_3/N_2$ passivated device with and without halo implant. For devices with halo implant, the peak concentration is given by $7.2x10^{17} cm^{-3}$ and $2x10^{18} cm^{-3}$                                          |

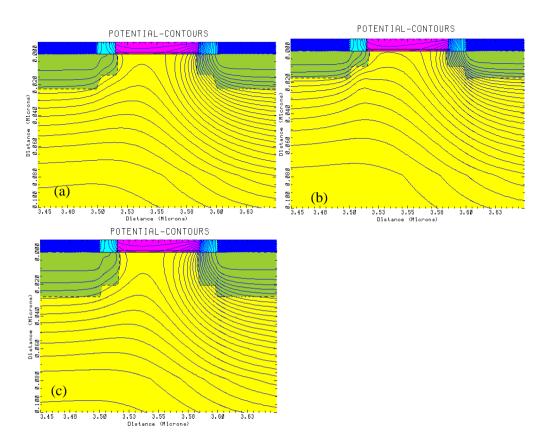

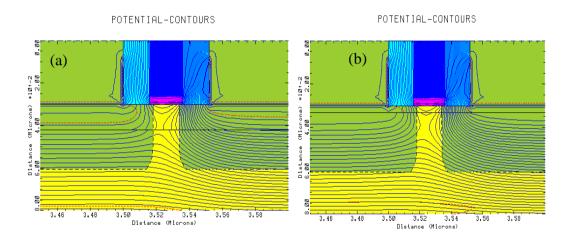

| Fig.7.3. 2D potential contours at $V_g$ =0V and $V_d$ =0.7V, for $L_g$ =70nm (a) with halo implant (7.2x10 <sup>17</sup> cm <sup>-3</sup> ) and (b) with halo implant (2x10 <sup>18</sup> cm <sup>-3</sup> ) and (c) without halo implant                                                                                                                                                     |

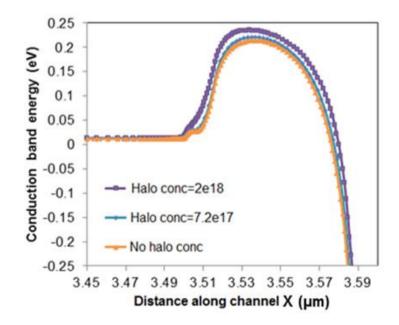

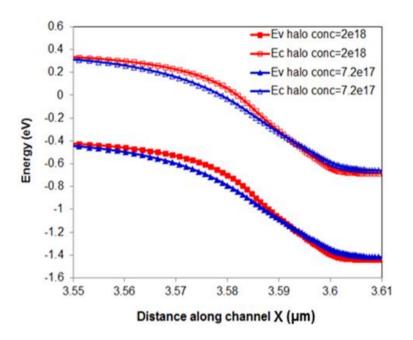

| Fig.7.4. Conduction band energy profile as a function of distance along the channel taken at 1nm below the $P_xN_y/In_{0.53}Ga_{0.47}Asinterface$ for $V_d$ =0.7V at $V_g$ =0V135                                                                                                                                                                                                             |

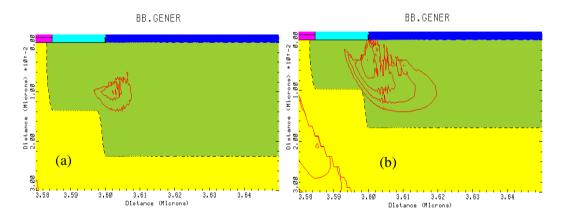

| Fig.7.5. Simulation 2D BTBT generation contours at $V_g$ =-0.3V and $V_d$ =0.7V, for $L_g$ =70nm (a) with halo implant $(7.2x10^{17}cm^{-3})$ and (b) with halo implant $(2x10^{18}cm^{-3})$                                                                                                                                                                                                  |

| Fig.7.6. Band diagram in the lateral direction for plasma-PH $_3/N_2$ passivated In $_{0.53}$ Ga $_{0.47}$ As MOSFETs with two different halo implant conditions, taken at V $_g$ =-0.3V, V $_d$ =0.7V at maximum BTBT generation point. From 1D profile, maximum BTBT generation occurs at x=3.6 $\mu$ m, y=0.01 $\mu$ m for Fig.7.5(a) and at x=3.6 $\mu$ m, y=0.004 $\mu$ m for Fig.7.5(b) |

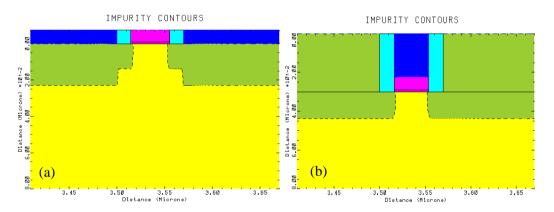

| Fig.7.7. 2D plots of the (a) Implanted S/D MOSFET and (b) Raised S/D MOSFET used in the simulation                                                                                                                                                                                                                                                                                            |

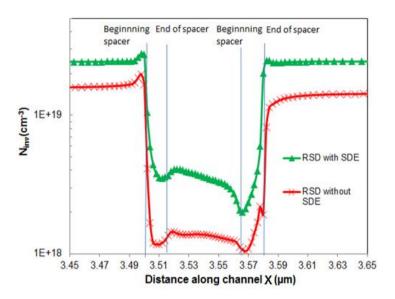

| Fig.7.8. Inversion electron concentration at 1nm below $P_xN_y/In_{0.53}Ga_{0.47}As$ interface taken along the channel direction at $V_g$ - $V_{t,sat}$ =0.5 $V$ , $V_d$ =0.7 $V$ , for $L_g$ =50nm for EOT=0.6nm.                                                                                                                                                                            |

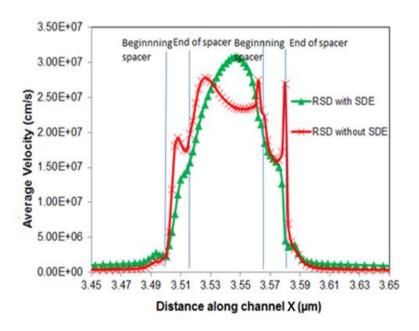

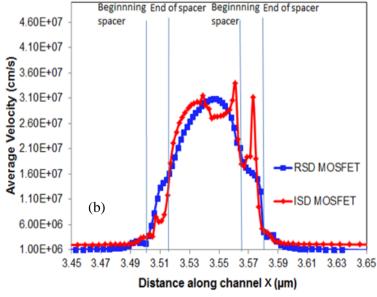

| Fig.7.9. Average electron velocity along the channel of the $In_{0.53}Ga_{0.47}As$ MOSFET taken at 1nm below $P_xN_y/In_{0.53}Ga_{0.47}As$ interface and at $V_g$ - $V_{t,sat}$ =0.5 $V$ , $V_d$ =0.7 $V$ for $L_g$ =50nm, EOT=0.6nm                                                                                                                                                          |

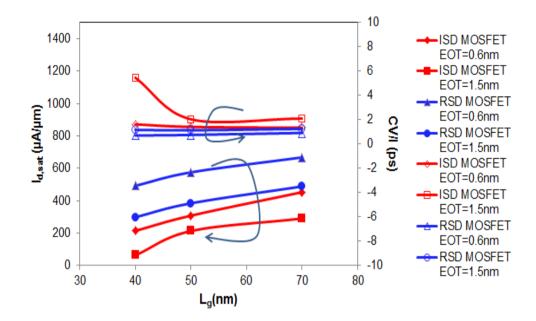

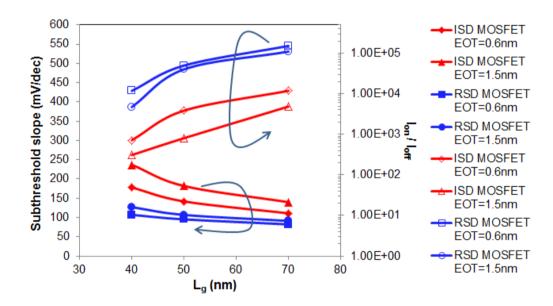

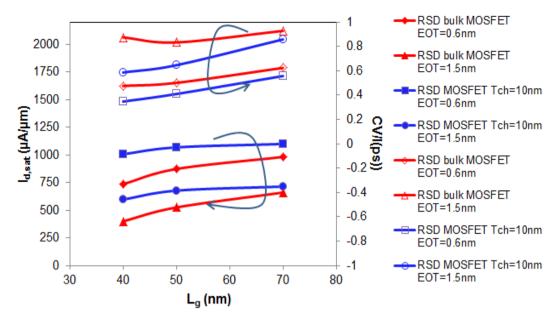

| Fig.7.10. Channel length and EOT dependences of $I_{\text{d,sat}}$ and CV/I shows far better                                                                                                                                                                                                                                                                                                  |

| performance of RSD over conventional ISD. $I_{d,sat}$ taken at $V_d=0./V, V_g-V_{t,sat}=0.5V$                                                                                                                                                                                                                                                                                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

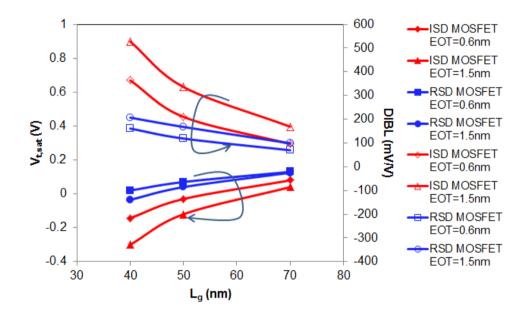

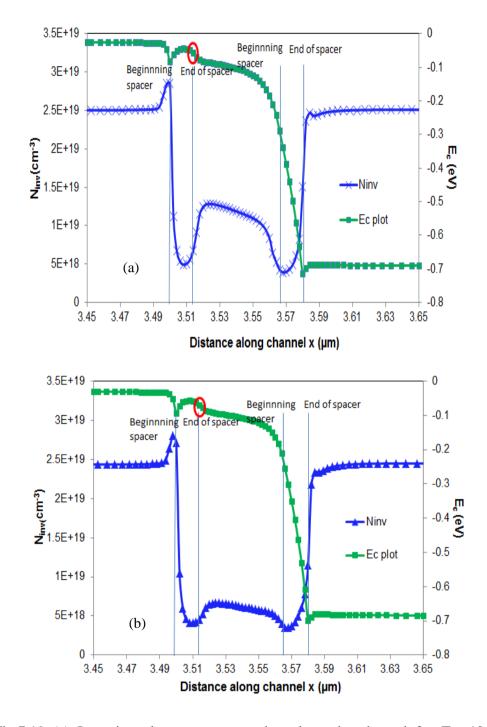

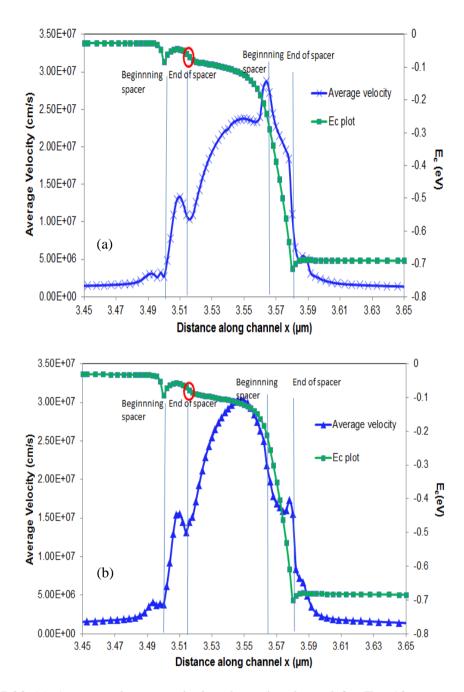

| Fig.7.11 (a) Comparison of inversion electron concentration between RSD and ISD MOSFETs, where $L_g$ =50nm, $V_g$ - $V_{t,sat}$ =0.5V and $V_d$ =0.7V and (b) Comparison of average electron velocity between RSD and ISD MOSFETs, where $L_g$ =50nm, $V_g$ - $V_{t,sat}$ =0.5V and $V_d$ =0.7V.                                                                                                   |

| Fig.7.12. Plot of $V_{t,sat}$ and DIBL vs $L_g$ for RSD and conventional ISD structures showing reasonable DIBL for RSD at 50nm                                                                                                                                                                                                                                                                    |

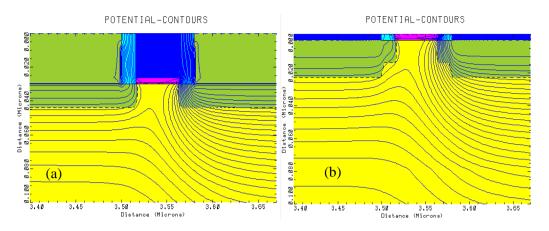

| Fig.7.13. 2D potential contour plot of (a) RSD $In_{0.53}Ga_{0.47}As$ MOSFET and (b) ISD $In_{0.53}Ga_{0.47}As$ MOSFET for $L_g$ =50nm taken at $V_g$ =0V, $V_d$ =0.7V                                                                                                                                                                                                                             |

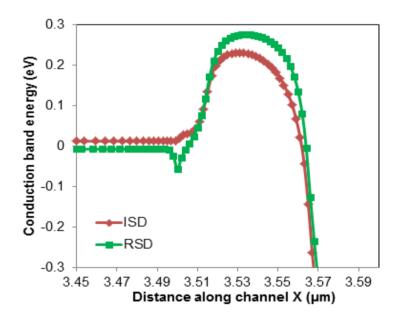

| Fig.7.14. Conduction band energy profiles for RSD $In_{0.53}Ga_{0.47}As$ MOSFET and ISD $In_{0.53}Ga_{0.47}As$ MOSFET for $L_g$ =50nm taken at $V_g$ =0V, $V_d$ =0.7V and taken at 1nm below the interface                                                                                                                                                                                         |

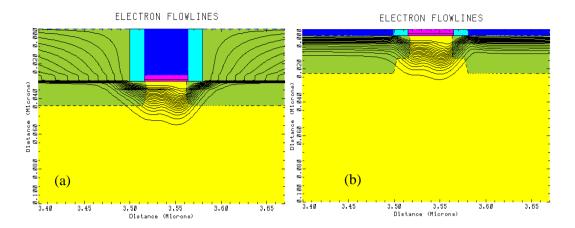

| Fig.7.15. Electron flowlines for (a) RSD $In_{0.53}Ga_{0.47}As$ MOSFET and (b) ISD $In_{0.53}Ga_{0.47}As$ MOSFET for $L_g$ =50nm taken at $V_g$ =0V, $V_d$ =0.7V. Electron flowlines in (a) do not start from within the spacer at the source unlike in (b)146                                                                                                                                     |

| Fig.7.16. Plot of SS and $I_{on}$ / $I_{off}$ ratio vs $L_g$ for RSD and ISD N-MOSFETs146                                                                                                                                                                                                                                                                                                          |

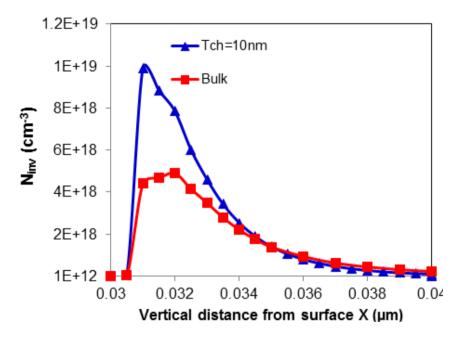

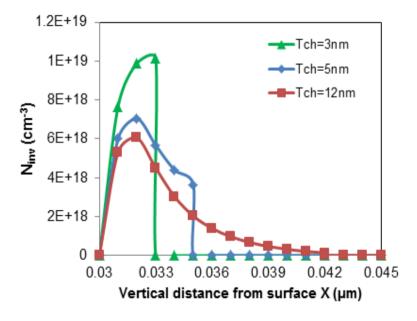

| Fig.7.17. Electron density distribution in the inversion layers for $In_{0.53}Ga_{0.47}As$ bulk and thin channel MOSFET for $L_g$ =40nm at EOT=0.6nm. Note that 0.03 $\mu$ m corresponds to the $P_xN_y/In_{0.53}Ga_{0.47}As$ interface and vertical distance from surface refers to distance away from $P_xN_y/In_{0.53}Ga_{0.47}As$ interface. Plot has been taken at the center of the channel. |

| Fig.7.18. Channel length and EOT dependences of I <sub>d,sat</sub> shows better performance of thin channel In <sub>0.53</sub> Ga <sub>0.47</sub> As MOSFET over bulk channel                                                                                                                                                                                                                      |

| Fig.7.19 (a) Inversion electron concentration along the channel for this channel=10nm structure for $L_g$ =50nm, $V_g$ - $V_{t,sat}$ =0.5V and $V_d$ =0.7V at EOT=0.6nm and (b) Inversion electron concentration along the channel for bulk structure for $L_g$ =50nm, $V_g$ - $V_{t,sat}$ =0.5V and $V_d$ =0.7V at EOT=0.6nm                                                                      |

| Fig.7.20 (a) Average electron velocity along the channel for thin channel=10nm structure for $L_g$ =50nm, $V_g$ - $V_{t,sat}$ =0.5V and $V_d$ =0.7V at EOT=0.6nm and (b) Average electron velocity along the channel for bulk structure for $L_g$ =50nm, $V_g$ - $V_{t,sat}$ =0.5V and $V_d$ =0.7V at EOT=0.6nm.                                                                                   |

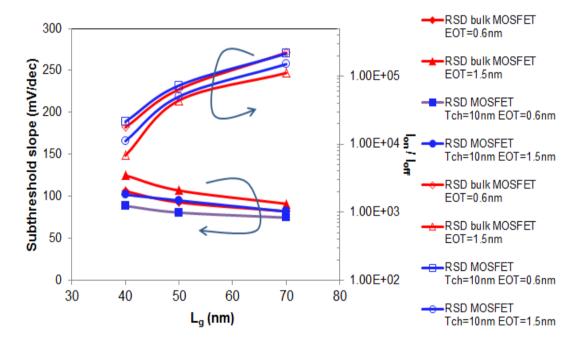

| Fig.7.21. Plot of $V_{t,sat}$ and DIBL vs $L_g$ for thin channel and bulk $In_{0.53}Ga_{0.47}As$ MOSFET                                                                                                                                                                                                                                                                                            |

| Fig.7.22 Plot of SS and $I_{on}$ / $I_{off}$ ratio vs $L_g$ for RSD bulk and thin channel MOSFETs                                                                                                                                                                                                                                                                                                  |

| Fig.7.23 Device design of the structure simulated                                                                                                                                                                                                                                                                                                                                                  |

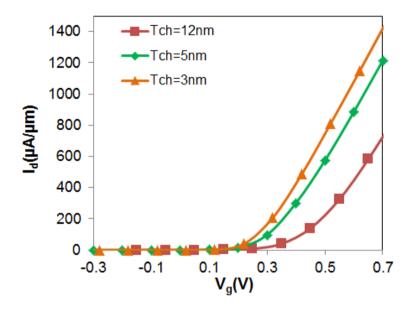

| Fig.7.24. $I_d$ - $V_g$ plot as a function of channel thickness for $V_d$ =0.7V at fixed $I_{off}$ of $0.1 \mu A/\mu m$                                                                                                                                                                                                                                                                            |

| Fig 7.25 Electron density distributions in the inversion layers computed for LITB                                                                                                                                                                                                                                                                                                                  |

| have been extracted at the middle of the channel region                                                                                                                                                                                                                                                                                                                                                                                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

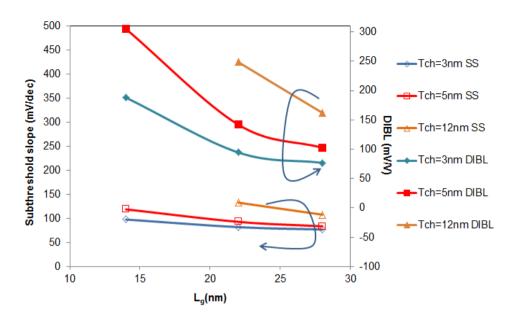

| Fig.7.26. SS and DIBL vs $L_{\rm g}$ characteristics as a function of channel thickness157                                                                                                                                                                                                                                                                                                                                                     |

| Fig.7.27. Potential contours for $L_g$ =22nm with (a) $T_{ch}$ =12nm and (b) $T_{ch}$ =3nm157                                                                                                                                                                                                                                                                                                                                                  |

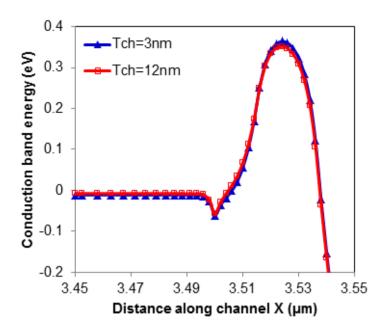

| Fig.7.28. Conduction band energy vs distance along the channel comparing $T_{ch}$ =12nm and $T_{ch}$ =3nm for $L_g$ =22nm device                                                                                                                                                                                                                                                                                                               |

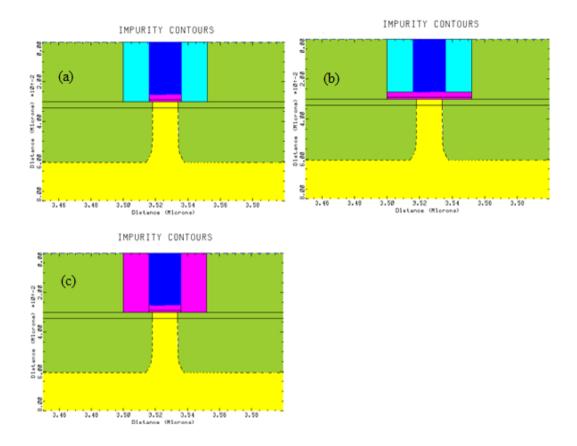

| Fig.7.29 Three different spacer material used on the $In_{0.53}Ga_{0.47}As$ MOSFET structures with Tch=3nm simulated with (a) $Si_3N_4$ spacer (b) HfO <sub>2</sub> extended to regions below spacer (c) HfO <sub>2</sub> spacer                                                                                                                                                                                                               |

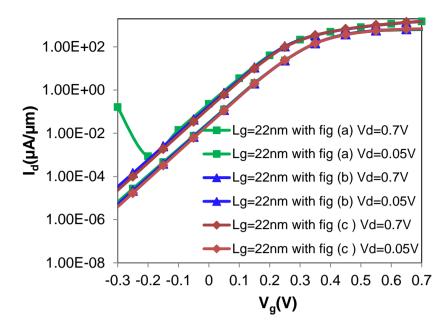

| Fig.7.30. I <sub>d</sub> -V <sub>g</sub> characteristics showing DIBL and GIDL with comparison with the 3 types of spacer material                                                                                                                                                                                                                                                                                                             |

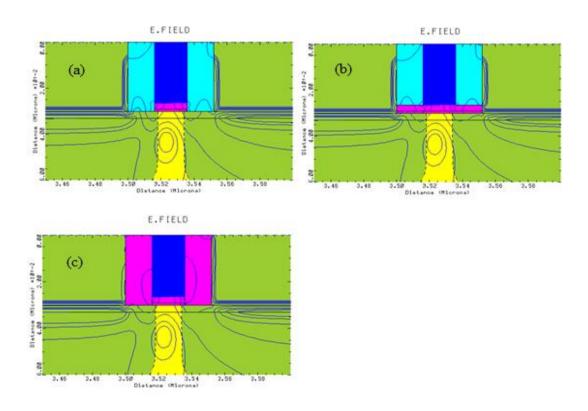

| Fig.7.31. 2D electric field plot taken at $V_g$ =-0.3V, $V_d$ =0.7V comparing the structure with three different spacer materials with (a) $Si_3N_4$ spacer (b) $HfO_2$ extended to regions below spacer (c) $HfO_2$ spacer                                                                                                                                                                                                                    |

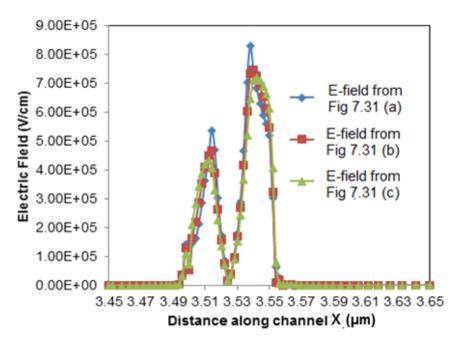

| Fig.7.32. Electric field contours taken at 1nm below the $P_xN_y/In_{0.53}Ga_{0.47}As$ interface at the region along the channel with $V_g$ =-0.3V and $V_d$ =0.7V. Here the electric field taken from Fig.7.31(a), especially at the region of the channel/drain interface, shows the most focused and abrupt field while the electric field taken from Fig.7.31(c) shows a laterally spread field which is responsible for its smaller GIDL. |

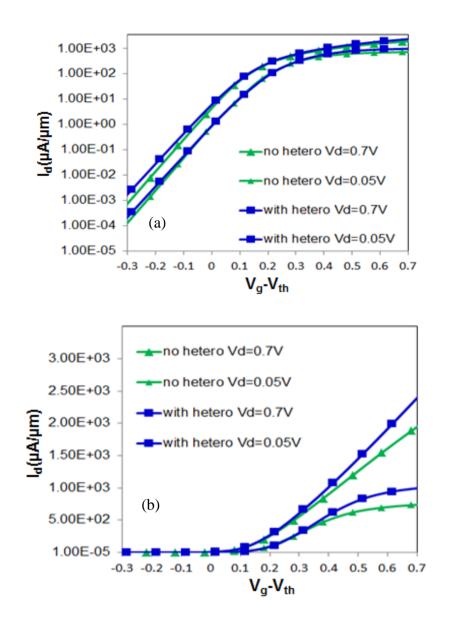

| Fig.7.33. $I_d$ – $(V_g$ - $V_{th})$ plot for (a) $V_d$ =0.7V and $V_d$ =0.05V, for $L_g$ =22nm devices with and without heterostructure in log scale and (b) $V_d$ =0.7V and $V_d$ =0.05V, for $L_g$ =22nm devices with and without heterostructure in linear scale.                                                                                                                                                                          |

| Fig.7.34. Electrostatic integrity as a function of gate length for device with and without heterostructure. Heterostructure device shows slightly worse SCE compared to without heterostructure.                                                                                                                                                                                                                                               |

| Fig.7.35. SS and $I_{\text{on}}/I_{\text{off}}$ a function of gate length for device with and without heterostructure.                                                                                                                                                                                                                                                                                                                         |

| Fig.7.36. $I_{d,sat}$ and CV/I plots for device without heterostructure as a function of $L_g$ with $I_{d,sat}$ taken at $V_d$ =0.7V, $V_g$ - $V_{t,sat}$ =0.5V                                                                                                                                                                                                                                                                                |

| Fig.7.37. Plot of $V_{t,sat}$ and $I_{d,sat}$ as a function of $L_g$ for $V_d$ =0.7V, $V_g$ - $V_{t,sat}$ =0.5V. $L_g$ below 50nm shows the region where the electrostatic effect from the drain becomes significant, resulting in significant roll off as well as causing reduced drive current with scaling.                                                                                                                                 |

| Fig.7.38 (a) $I_d$ - $V_g$ plot of device without heterostructure for $L_g$ =14nm, 22nm and 28nm taken at $V_d$ =0.7V and (b) Linear scale plot of $I_d$ - $(V_g$ - $V_{t,sat})$ for device without heterostructure for $L_g$ =14nm, 22nm and 28nm taken at $V_d$ =0.7V                                                                                                                                                                        |

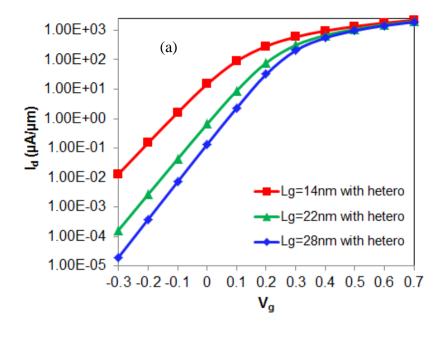

Fig.7.39 (a)  $I_d$ - $V_g$  plot of device with heterostructure for  $L_g$ =14nm, 22nm and 28nm taken at  $V_d$ =0.7V and (b)  $I_d$ - $(V_g$ - $V_{t,sat})$  plot of device with heterostructure for  $L_g$ =14nm, 22nm and 28nm taken at  $V_d$ =0.7V......170

# **List of Symbols and Acronyms**

| Symbol /Acronym    | Description                         |  |  |  |  |

|--------------------|-------------------------------------|--|--|--|--|

| ALD                | Atomic Layer Deposition             |  |  |  |  |

| В                  | Ballistic coefficient               |  |  |  |  |

| BTBT               | Band to band tunneling              |  |  |  |  |

| CBM                | Conduction band minima              |  |  |  |  |

| CD                 | Depletion capacitance               |  |  |  |  |

| $C_{g}$            | Gate capacitance                    |  |  |  |  |

| $C_{ m gc}$        | Gate-to-channel capacitance         |  |  |  |  |

| C <sub>it</sub>    | Interface trap capacitance          |  |  |  |  |

| $C_{ m lf}$        | Low frequency capacitance           |  |  |  |  |

| CNL                | Charge Neutrality Level             |  |  |  |  |

| C <sub>ox</sub>    | Gate oxide capacitance              |  |  |  |  |

| СР                 | Charge pumping                      |  |  |  |  |

| Cs                 | Semiconductor capacitance           |  |  |  |  |

| DIBL               | Drain Induced Barrier Lowering      |  |  |  |  |

| D <sub>it</sub>    | Interface trap density              |  |  |  |  |

| DOS                | Density of states                   |  |  |  |  |

| Ea                 | Activation energy                   |  |  |  |  |

| $\epsilon_{\rm r}$ | Dynamic dielectric constant         |  |  |  |  |

| EBL                | Electron beam lithography           |  |  |  |  |

| E <sub>c</sub>     | Conduction band minima              |  |  |  |  |

| EDT SCLC           | Exponentially distributed trap SCLC |  |  |  |  |

| EDX                | Energy Dispersion X-Ray             |  |  |  |  |

| $E_{F}$            | Fermi energy level                  |  |  |  |  |

| E <sub>i</sub>     | Intrinsic fermi level               |  |  |  |  |

| ЕОТ                | Equivalent oxide thickness          |  |  |  |  |

| E <sub>t</sub>     | Trap energy level                   |  |  |  |  |

| FN                 | Fowler-Nordheim                     |  |  |  |  |

| FP                 | Frenkel Poole                       |  |  |  |  |

| GGO                | Gallium-Gadolinium Oxide            |  |  |  |  |

| G <sub>m</sub>     | Maximum transconductance            |  |  |  |  |

| HCl                | Hydrochloric                        |  |  |  |  |

| I <sub>d,sat</sub> | Saturation drive current            |  |  |  |  |

| I <sub>on</sub>    | On-current                          |  |  |  |  |

| ISD                | Implanted Source/Drain              |  |  |  |  |

| k                                 | Permittivity                                     |  |  |  |  |

|-----------------------------------|--------------------------------------------------|--|--|--|--|

| $J_g$                             | Gate leakage current density                     |  |  |  |  |

| λ                                 | Correlation length                               |  |  |  |  |

| $L_{\rm g}$                       | Gate length                                      |  |  |  |  |

| LO                                | Longitudinal optical phonons                     |  |  |  |  |

| m*                                | Effective mass                                   |  |  |  |  |

| MBE                               | Molecular beam epitaxy                           |  |  |  |  |

| MLD                               | Mono-layer Doping                                |  |  |  |  |

| MOCVD                             | Metal-Organic-Chemical-Vapor-Deposition          |  |  |  |  |

| $\mu_{	ext{eff}}$                 | Effective mobility                               |  |  |  |  |

| $\mu_{coul}$                      | Mobility limited by coulombic scattering         |  |  |  |  |

| $\mu_{ph}$                        | Mobility limited by phonon scattering            |  |  |  |  |

| $\mu_{sr}$                        | Mobility limited by surface roughness scattering |  |  |  |  |

| (NH <sub>4</sub> ) <sub>2</sub> S | Wet sulfide                                      |  |  |  |  |

| $N_{\mathrm{inv}}$                | Inversion electron concentration                 |  |  |  |  |

| $N_{\rm t}$                       | Average trap concentration                       |  |  |  |  |

| PECVD                             | Plasma enhanced chemical vapour deposition       |  |  |  |  |

| PVD                               | Physical vapour deposition                       |  |  |  |  |

| $P_xN_y$                          | Phosphorus nitride                               |  |  |  |  |

| Q <sub>inv</sub>                  | Inversion charge density                         |  |  |  |  |

| r                                 | Backscattering rate                              |  |  |  |  |

| R <sub>c</sub>                    | Contact resistance                               |  |  |  |  |

| RMS                               | Root mean square                                 |  |  |  |  |

| RSD                               | Raised Source/Drain                              |  |  |  |  |

| $R_{sh}$                          | Sheet resistance                                 |  |  |  |  |

| SCLC                              | Space Charge Limited Conduction                  |  |  |  |  |

| SCE                               | Short channel effect                             |  |  |  |  |

| S/D                               | Source/Drain                                     |  |  |  |  |

| SE                                | Schottky Emission                                |  |  |  |  |

| SO                                | Soft optical                                     |  |  |  |  |

| SS                                | Subthreshold Slope                               |  |  |  |  |

| TMA                               | trimethyl aluminum                               |  |  |  |  |

| CV/I                              | Gate delay                                       |  |  |  |  |

| $	au_{ m c}$                      | Carrier transit time                             |  |  |  |  |

| $	au_{ m d}$                      | Dielectric relaxation time                       |  |  |  |  |

| $T_{\mathrm{ch}}$                 | Channel thickness                                |  |  |  |  |

| $t_{\mathrm{f}}$                  | Pulse fall time                                  |  |  |  |  |

| TFL               | Trap filled limited                             |  |  |  |  |  |

|-------------------|-------------------------------------------------|--|--|--|--|--|

| TO                | Transverse optical phonons                      |  |  |  |  |  |

| $t_{\rm r}$       | Pulse rise time                                 |  |  |  |  |  |

| UTB               | Ultra thin body                                 |  |  |  |  |  |

| $V_d$             | Drain voltage                                   |  |  |  |  |  |

| $V_{g}$           | Gate voltage                                    |  |  |  |  |  |

| $V_{inj}$         | Injection velocity                              |  |  |  |  |  |

| $V_{\mathrm{T}}$  | Thermal injection velocity                      |  |  |  |  |  |

| $V_{\mathrm{th}}$ | Threshold voltage at V <sub>d</sub> =0.05V      |  |  |  |  |  |

| $V_{t,sat}$       | Threshold voltage at V <sub>d</sub> =0.7V or 1V |  |  |  |  |  |

| W                 | Gate width                                      |  |  |  |  |  |

| $W_{ m eff}$      | Effective gate width                            |  |  |  |  |  |

#### **Chapter 1: Introduction and Motivation**

#### 1.1. Silicon transistor scaling: Benefits and Issues

Moore's Law predicted that the number of transistors placed on an integrated circuit (IC) would double every two years [1] and has been known to guide the progress. The device scaling is the key attribute for planar MOSFET circuitry in order to achieve significantly higher packing density per unit chip area, reduction of cost per function and improvement in circuit speed performance.

The key concept of the MOSFET scaling proposed by Dennard in 1974 [2] is that various structure and electrical parameters of MOSFET should be scaled simultaneously, which guarantees the reduction in device dimensions without compromising the current-voltage characteristics. However, as MOSFET continues to scale down to sub-100nm, the conventional device scaling is confronted with several limitations, which provide the trade-off relationships among on-current, power consumption and short channel effects as shown in Fig.1.1. One such example is that to maintain the on-current scaling with reduced gate length (Lg), oxide thickness has to be reduced, but this will cause greater power consumption in terms of high gate leakage current. Also, as Lg is scaled, significant control of channel by the gate is lost and the drain field begins to influence the channel formation, resulting in short channel effect (SCE). Hence, new device engineering methods to overcome these difficulties are much needed to mitigate the trade-offs.

These new device technologies, shown as possible solutions in Fig.1.1

[3] are known as the technology boosters, and they include technologies or

structures such as high-k/metal-gate for gate stack engineering, high carrier mobility or high carrier velocity channels, ultrathin-body (UTB) structures and multigate structures for channel engineering and metal source/drain (S/D) for S/D engineering. The principle of these technology boosters is to improve the device parameters such as gate leakage current, mobility, saturation velocity and short channel effects. For instance a 45nm process technology based on high-k, metal gate, and strained silicon was introduced in 2000 [4] while scaling of this technology continued to the 32nm technology node in 2009 [5]. More recently in 2011, FINFET structure was introduced to enable further scaling to the 22nm technology node [6]. As technology node progresses towards sub-20nm, fundamental limits of Si properties and gate pitch will impose limitations to the continuous scaling of device dimensions in terms of challenges to the conventional techniques and materials used for CMOS strain engineering. Therefore, future advancement of CMOS scaling would require novel channel materials, processes and device architectures.

Fig.1.1. Trade-off factors among on-current, power consumption/leakage current and short channel effects under simple device scaling and possible solutions [3].

# 1.2. Motivation of III-V Channel Materials for Future CMOS applications

When MOSFET is scaled to deep sub-100nm technology node, carrier transport in the scaled device becomes quasi-ballistic. It has been shown through simulation and experiments that injection velocity, instead of saturation velocity, is still a reliable performance indicator for the drive current [7-10].

Lundstrom's theory [11] initially pointed out based on scattering theory that the drain current at the saturation condition is dominated by thermal injection velocity,  $V_T$ , at the source side instead of the saturation velocity, in short channel devices. The saturation current of a short channel device can be expressed as:

$I_{d,sat} = C_{ox}W_{eff}V_{T}((1-r)/(1+r))(V_{g}-V_{th})$

Equation (1.1)

where

$$C_{ox}$$

is the gate oxide capacitance,  $W_{eff}$  is the effective gate width, r is the backscattering coefficient which indicates the number of carriers backscattered to the source,  $V_g$  is the voltage between the gate and the source,  $V_{th}$  is the threshold voltage, and  $V_T$  is the thermal injection velocity.  $V_T$  is dependent on low field mobility and r is inversely proportional to low field mobility [9-10]. For extremely scaled devices operating in the ballistic regime i.e. r=0, where the ballistic coefficient,  $B=((1-r)/(1+r))=1$ , the maximum current would be controlled by the injection velocity near the