# THE DESIGN OF LOW POWER ULTRA-WIDEBAND TRANSCEIVERS

Wang Lei

NATIONAL UNIVERSITY OF SINGAPORE

# THE DESIGN OF LOW POWER ULTRA-WIDEBAND TRANSCEIVERS

# Wang Lei

(B. Sci, Beijing Technology and Business University, China)

(M. Eng, Tsinghua University, China)

# A THESIS SUBMITTED FOR THE DEGREE OF DOCTOR OF PHILOSOPHY DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING

NATIONAL UNIVERSITY OF SINGAPORE

2013

## **DECLARATION**

I hereby declare that the thesis is my original work and it has been written by me in its entirety. I have duly acknowledged all the sources of information which have been used in the thesis.

This thesis has also not been submitted for any degree in any university previously.

Wang Lei

Wanz lei

15 Aug. 2013

### **ACKNOWLEDGEMENT**

I would like to express my sincere and deep gratitude towards my supervisor Professor Lian Yong for giving me the opportunity to work on this project. What I have learnt from him is not only about the project itself, but also including his profound knowledge and abundant experiences about life. I would also like to thank Dr. Heng Chun Huat for his valuable guidance and continuous encouragement. Without his understanding, inspiration and guidance every week, I could not have been able to complete these projects.

I am grateful to all administrative and technical staff for the help. I would like to thank all of my lab-mates for their help and useful conversation, including Saisundar Sankaranarayanan, Xu Xiaoyuan, Zou Xiaodan, Zhang Jinghua, Izad Mehran, Liew Wen-Sin, Tan Jun, Yang Zhenlin, Zhang Xiaoyang, Li Yong-Fu, Zhang Zhe, Hong Yibin, and Li Yile.

Last, but not least, I want to thank my parents and my wife for their love and support which is the source of strength for me.

#### TABLE OF CONTENTS

| SUMM   | IARY                                              | IV |

|--------|---------------------------------------------------|----|

| LIST ( | OF FIGURES                                        | 1  |

| LIST ( | OF TABLES                                         | 6  |

| LIST ( | OF ABBREVIATIONS                                  | 7  |

| СНАР   | TER 1 INTRODUCTION                                | 9  |

| 1.1    | BACKGROUND                                        | 9  |

| 1.1.   | .1 The Attractiveness of IR UWB Transceiver       | 9  |

| 1.1.   | 2 The Principle and Advantages of UWB Beamforming | 11 |

| 1.2    | MOTIVATION                                        | 14 |

| 1.3    | RESEARCH CONTRIBUTIONS                            | 15 |

| 1.4    | ORGANIZATION OF THE THESIS                        | 17 |

| СНАР   | TER 2 REVIEW OF UWB TRANSCEIVER ARCHITECTURES     | 18 |

| 2.1    | EXISTING UWB TRANSMITTER ARCHITECTURES            | 18 |

| 2.1.   | .1 Analog UWB Transmitters                        | 18 |

| 2.1.   | 2 Digital UWB Transmitters                        | 20 |

| 2.2    | EXISTING BEAMFORMING TRANSMITTER ARCHITECTURES    | 22 |

| 2.2.   | .1 IF Phase Shift Beamforming Transmitter         | 22 |

| 2.2.   | 2 RF Phase Shift Beamforming Transmitter          | 23 |

| 2.2.   | 3 LO Phase Shift Beamforming Transmitter          | 24 |

| 2.2.   | 4 True Time Digital Delay Beamforming Transmitter | 25 |

| 2.3    | EXISTING BEAMFORMING RECEIVER ARCHITECTURES       | 26 |

| 2.3.   | .1 Passive Phase Shift Beamforming Receiver       | 26 |

| 2.3.   | 2 Active Phase Shift Beamforming Receiver         | 27 |

| 2.4    | FINDINGS                                          | 28 |

| СНАР   | TER 3 SUB 1 GHZ IR UWB TRANSCEIVER                | 30 |

| 3.1    | SYSTEM REQUIREMENT AND DESIGN CONSIDERATION       | 30 |

| 3.2    | LINK BUDGET                                       | 31 |

| 3.3    | A SUB 1 GHz OOK IR UWB TRANSCEIVER                | 32 |

| 3.3.   | 1 The Proposed Architecture                       | 32 |

| 3.3.   | .2 All-Digital OOK UWB Transmitter                | 34 |

| 3.3.   | 3 The Proposed OOK UWB Receiver                   | 35 |

| 3.3.   | 4 DLL Based Clock Retiming Circuit                | 41 |

| 3.3.   | 5 Synchronization Scheme                          | 48 |

| 3.3.   | .6 Measurement Results                            | 50 |

| 3.3.   | .7 Comparison with other recent works             | 55 |

| CHAP  | TEI   | R 4 3-5 GHz UWB BEAMFORMING TRANSMITTER       | 57  |

|-------|-------|-----------------------------------------------|-----|

| 4.1.  | Тн    | E PROPOSED UWB BEAMFORMING TRANSMITTER SYSTEM | 57  |

| 4.2.  | Тн    | E CIRCUIT IMPLEMENTATION                      | 63  |

| 4.2   | 2.1.  | UWB Beamforming Delay Cell                    | 63  |

| 4.2   | 2.2.  | $\Delta\Sigma$ DLL Based Delay Calibration    | 68  |

| 4.2   | 2.3.  | UWB Transmitter Architecture                  | 84  |

| 4.2   | 2.4.  | PSDC Circuit                                  | 88  |

| 4.3.  | M     | EASUREMENT RESULTS                            | 95  |

| СНАР  | TEI   | R 5 0.1-10 GHz UWB BEAMFORMING RECEIVER       | 116 |

| 5.1   | INT   | FRODUCTION                                    | 116 |

| 5.2   | Sy    | STEM ARCHITECTURE                             | 119 |

| 5.3   | CII   | RCUIT IMPLEMENTATION                          | 120 |

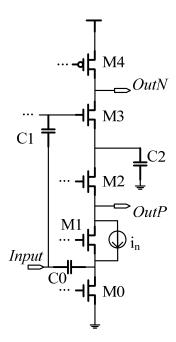

| 5.3   | B. 1. | Noise Canceling and Current Reuse LNA         | 120 |

| 5.3   | 3.2.  | True Time Delay Line                          | 125 |

| 5.4   | SIN   | MULATION RESULTS                              | 127 |

| CHAP  | TEI   | R 6 CONCLUSION AND FUTURE WORK                | 131 |

| 6.1.  | Co    | NCLUSION                                      | 131 |

| 6.2.  | FU    | TURE WORK                                     | 132 |

| REFER | RENC  | E                                             | 133 |

#### **SUMMARY**

The last decade has witnessed a tremendous growth in wireless communications. Among various types of wireless transceivers, the Impulse Radio ultra-wideband (IR UWB) transceiver offers exciting opportunities due to its amenability to fully digital implementation and duty cycling. Because of its digital pulse like nature, IR UWB can benefit from the scalability of CMOS technology and the tremendous digital signal processing power available. In this thesis, we will present three works that are related to different aspects of UWB. In the first work, we will present a sub 1 GHz on-off keying (OOK) UWB transceiver based on threshold detection targeting for low data rate energy efficient wireless communication. In the second work, a UWB beamforming transmitter is proposed in view of the voltage headroom reduction due to device downscaling. In the third work, a UWB beamforming receiver is proposed. With beamforming, much efficient energy could be achieved by directing the transmitter or receiver power in the desired direction.

The sub 1 GHz UWB transceiver was implemented in standard 0.35 µm CMOS technology. Due to the digital intensive architecture proposed, the transceiver achieves high energy efficiency of 100 pJ/bit and 600 pJ/bit during transmitting and receiving, respectively. The implemented transceiver can achieve BER smaller than 0.1% with communicating range less than 27 cm.

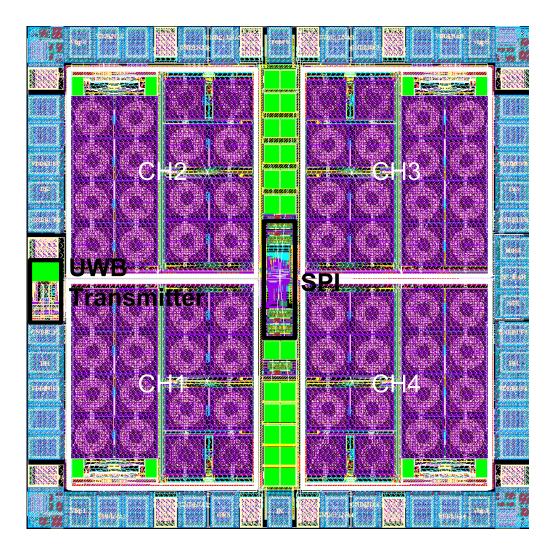

The 3-5 GHz UWB beamforming transmitter is implemented in 0.13  $\mu$ m CMOS. Through the proposed vernier delay line and delta-sigma delay locked loop ( $\Delta\Sigma$  DLL) based calibration, we achieve delay resolution of 10 ps, which is 10 times smaller than the currently reported state-of-the-art. Similarly,

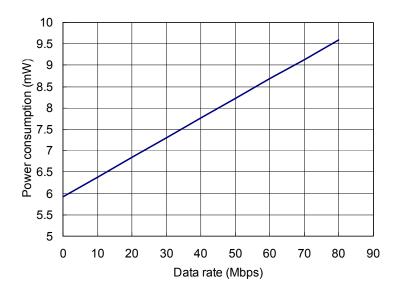

through digital intensive architecture, and careful optimization of various paths, the resulting beamformer only consumes 9.6 mW which is also 10 times smaller than other reported UWB beamformer.

The 0.1-10 GHz UWB beamforming receiver is implemented in 65 nm CMOS. Post layout simulation results show that we could achieve 225 ps delay range with 1.44 mm<sup>2</sup> area through the proposed Q compensated approach. This area is seven times smaller than the other UWB beamforming receiver based on passive LC true time delay.

# LIST OF FIGURES

| Figure 1.1. FCC Mask for UWB regulation.                            | 10 |

|---------------------------------------------------------------------|----|

| Figure 1.2. UWB beamforming transmitter principle                   | 14 |

| Figure 2.1. Analog UWB transmitter based on traditional analog appr |    |

|                                                                     | 19 |

| Figure 2.2. Analog UWB transmitter based on VCO.                    | 19 |

| Figure 2.3. Digital UWB transmitter in [16]                         | 20 |

| Figure 2.4. Digital UWB transmitter architectures based on DCO      | 21 |

| Figure 2.5. Beamforming transmitter with phase shift at IF stage    | 23 |

| Figure 2.6. Beamforming transmitter with phase shift at RF stage    | 24 |

| Figure 2.7. Beamforming transmitter with phase shift at LO          | 25 |

| Figure 2.8. True time digital delay beamforming transmitter         | 26 |

| Figure 2.9. Passive phase shifter.                                  | 27 |

| Figure 2.10. Active phase shifter                                   | 27 |

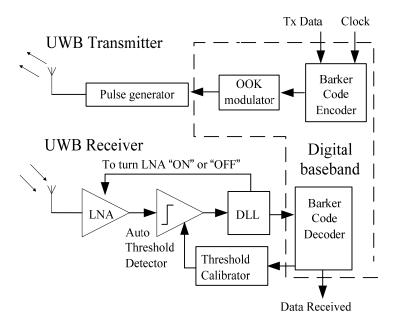

| Figure 3.1. The proposed IR UWB transceiver architecture            | 33 |

| Figure 3.2. UWB transmitter structure.                              | 34 |

| Figure 3.3. The LNA circuit.                                        | 35 |

| Figure 3.4. The LNA variable gain simulation results.               | 37 |

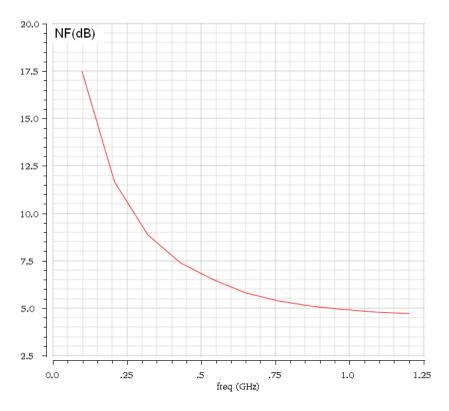

| Figure 3.5. The simulated <i>NF</i> of LNA                          | 38 |

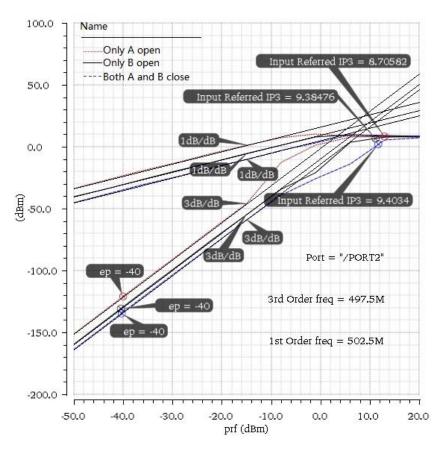

| Figure 3.6. The simulated <i>IP3</i> of LNA.                        | 39 |

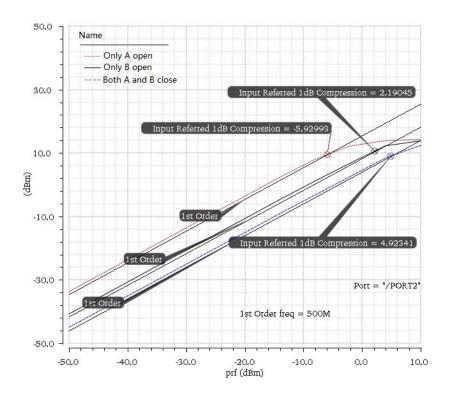

| Figure 3.7. The simulated <i>P1dB</i> of LNA.                       | 39 |

| Figure 3.8. Schematic of UWB receiver frontend.                     | 40 |

| Figure 3.9. Analog DLL architecture.                                | 41 |

| Figure 3.10. Semi-digital DLL architecture.                         | 42 |

| Figure 3.11. $\Delta\Sigma$ DLL architecture [40].                                                        | 43    |

|-----------------------------------------------------------------------------------------------------------|-------|

| Figure 3.12. Digital DLL architecture.                                                                    | 44    |

| Figure 3.13. The locking in procedure of the SAR DLL                                                      | 45    |

| Figure 3.14. The architecture of DLL-based clock re-timing circuit                                        | 46    |

| Figure 3.15. Harmonic locking problem in DLL.                                                             | 47    |

| Figure 3.16. Clock signal generation for SAR decision making logic.                                       | 47    |

| Figure 3.17. The implementation of digital back-end                                                       | 48    |

| Figure 3.18. Die photo of the IR UWB transceiver.                                                         | 50    |

| Figure 3.19. Measured transmitter output with spectrum.                                                   | 51    |

| Figure 3.20. UWB transceiver testing                                                                      | 52    |

| Figure 3.21. Receiver testing results.                                                                    | 53    |

| Figure 3.22. Reconstructed ECG waveform from RX data                                                      | 54    |

| Figure 3.23. The measured BER performance.                                                                | 54    |

| Figure 4.1. The proposed system architecture.                                                             | 58    |

| Figure 4.2. (a) Absolute delay generation. (b) Relative delay generati                                    | on.59 |

| Figure 4.3. (a) The principle of vernier delay line. (b) Delay cells sh                                   | _     |

| Figure 4.4. Beamforming delay chain subsystem.                                                            | 62    |

| Figure 4.5. The proposed linear delay generation and simulation result different corner and temperatures. |       |

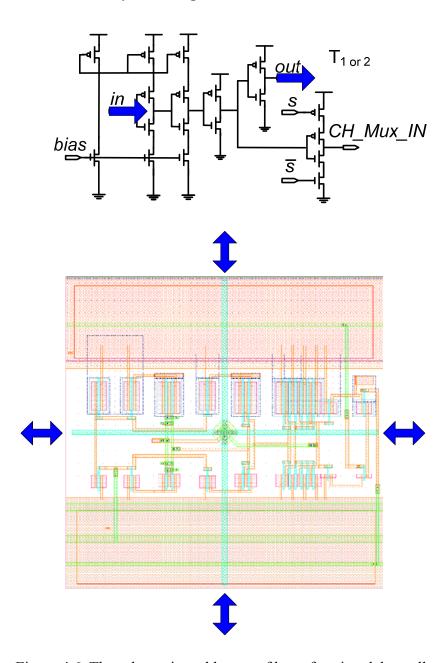

| Figure 4.6. The schematic and layout of beamforming delay cell                                            | 66    |

| Figure 4.7. The 4-channel matching.                                                                       | 67    |

| Figure 4.8. Counter based delay calibration adopted by [17]                                               | 68    |

| Figure 4.9. Counter based delay calibration waveform.                                                     | 69    |

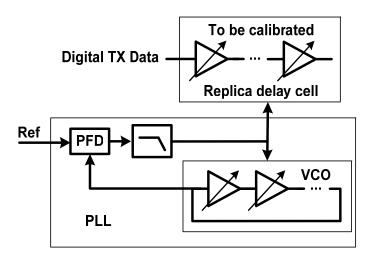

| Figure 4.10. PLL based delay calibration in [23].                                                         | 70    |

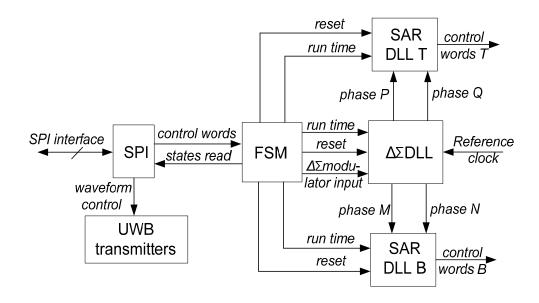

| Figure 4.11. The calibration system architecture.                                                                         | 71 |

|---------------------------------------------------------------------------------------------------------------------------|----|

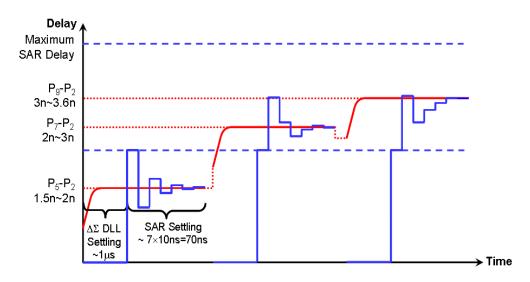

| Figure 4.12. $\Delta\Sigma$ DLL based calibration process.                                                                | 72 |

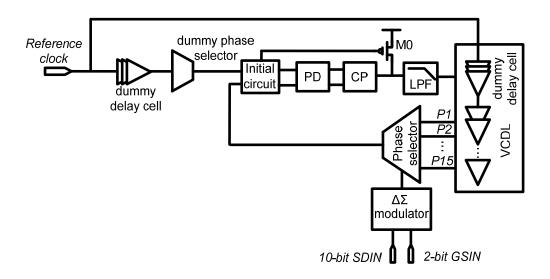

| Figure 4.13. The structure of $\Delta\Sigma$ DLL.                                                                         | 74 |

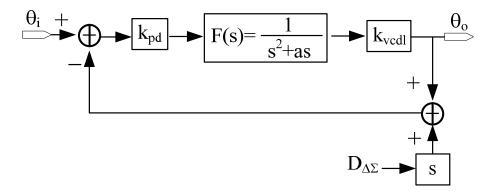

| Figure 4.14. The linear model of $\Delta\Sigma$ DLL.                                                                      | 75 |

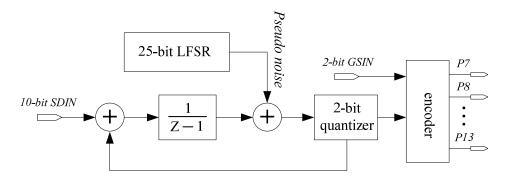

| Figure 4.15. The first order $\Delta\Sigma$ modulator.                                                                    | 75 |

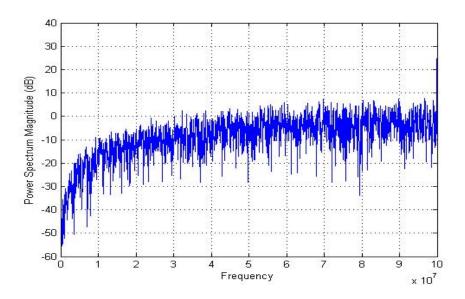

| Figure 4.16. The first order $\Delta\Sigma$ modulator spectrum.                                                           | 76 |

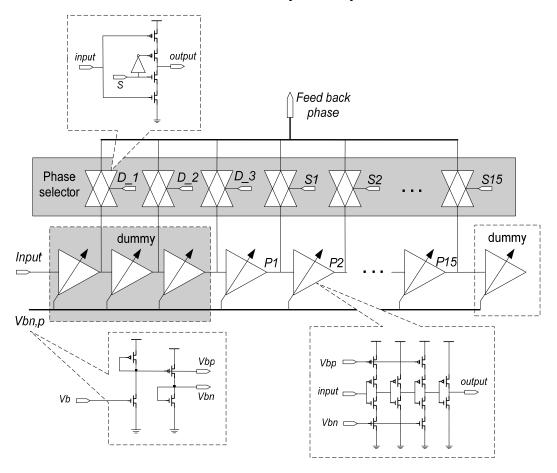

| Figure 4.17. VCDL and phase selector.                                                                                     | 78 |

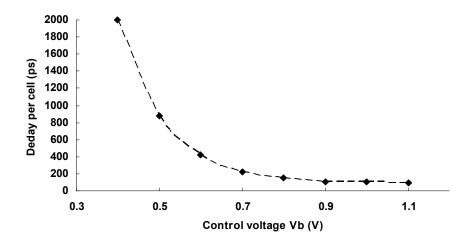

| Figure 4.18. The generated delay per cell under control voltage <i>Vb</i>                                                 | 79 |

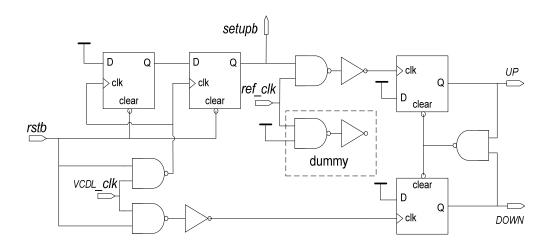

| Figure 4.19. Phase detector and startup circuit.                                                                          | 79 |

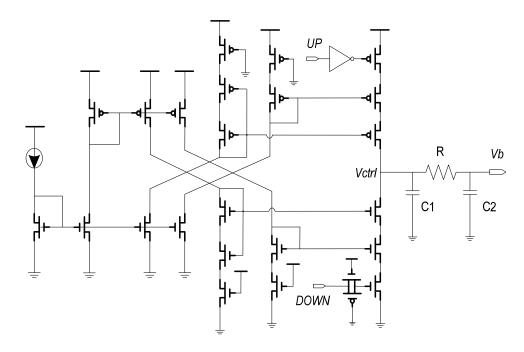

| Figure 4.20. Schematic of charge pump with loop filter                                                                    | 81 |

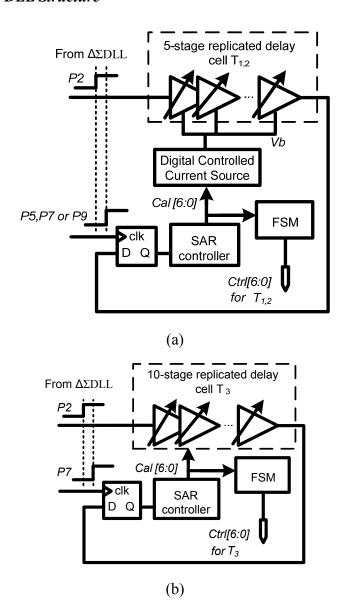

| Figure 4.21. The architecture of SAR DLL: (a) For beamforming calibration; (b) For UWB pulse center frequency calibration | -  |

| Figure 4.22. The flow chart of FSM.                                                                                       | 83 |

| Figure 4.23. The UWB transmitter architecture in [17] and gen pulse shape in 90nm and 0.13μm process                      |    |

| Figure 4.24. The structure of propsed UWB transmitter.                                                                    | 86 |

| Figure 4.25. The structure of UWB transmitter.                                                                            | 87 |

| Figure 4.26. The PSDC principle.                                                                                          | 89 |

| Figure 4.27. The PSDC circuit.                                                                                            | 91 |

| Figure 4.28. The squarer and integrator circuits in PSDC.                                                                 | 91 |

| Figure 4.29. The UWB pulse and the switch signal.                                                                         | 93 |

| Figure 4.30. The Monte-Carlo simulation of the switch signal                                                              | 94 |

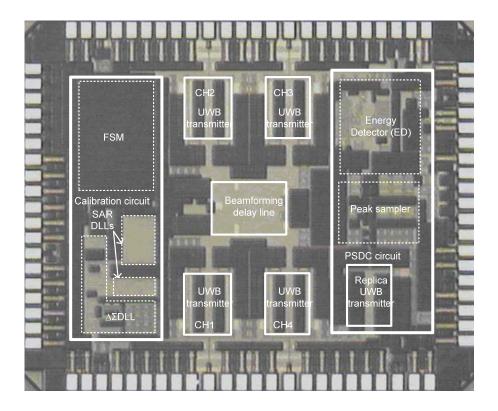

| Figure 4.31. Die photo of beamforming transmitter.                                                                        | 95 |

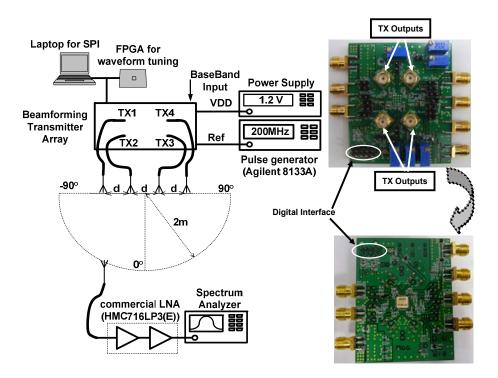

| Figure 4.32. Measurement setup.                                                                                           | 96 |

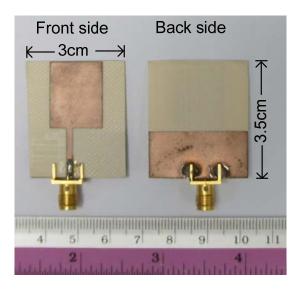

| Figure 4 33 The geometry of a single antenna                                                                              | 97 |

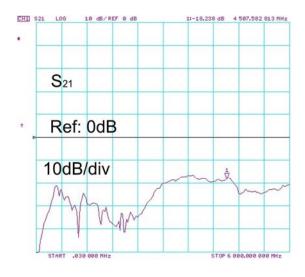

| Figure 4.34. The S <sub>21</sub> measurement of a single antenna97                                                                              |

|-------------------------------------------------------------------------------------------------------------------------------------------------|

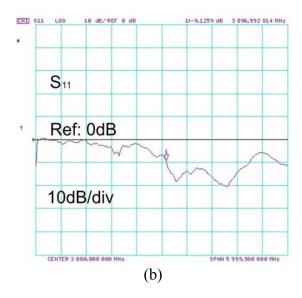

| Figure 4.35. The S <sub>11</sub> measurement of a single antenna                                                                                |

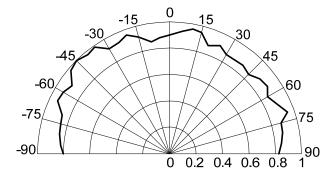

| Figure 4.36. The pattern of a single antenna                                                                                                    |

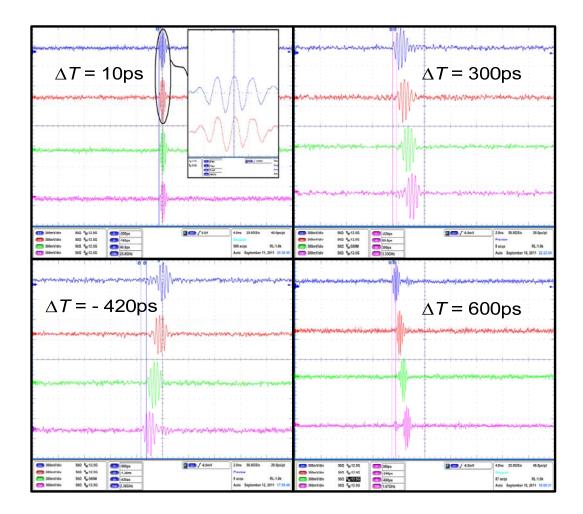

| Figure 4.37. The measured waveforms                                                                                                             |

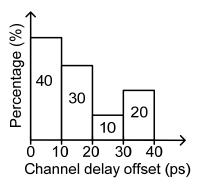

| Figure 4.38. Distribution of maximal channel delay offset (ps)100                                                                               |

| Figure 4.39. The delay calibration circuit performance of different chips for UWB center frequency                                              |

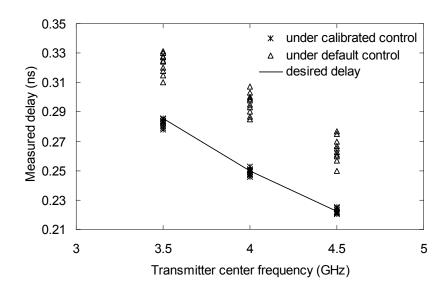

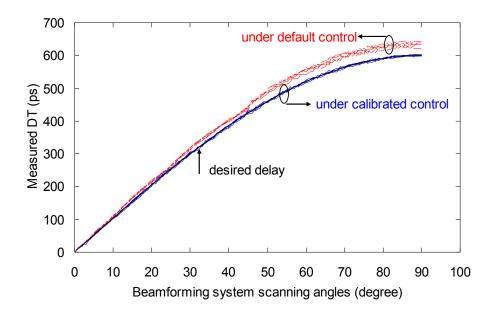

| Figure 4.40. The delay calibration circuit performance of different chips for Beamforming delay                                                 |

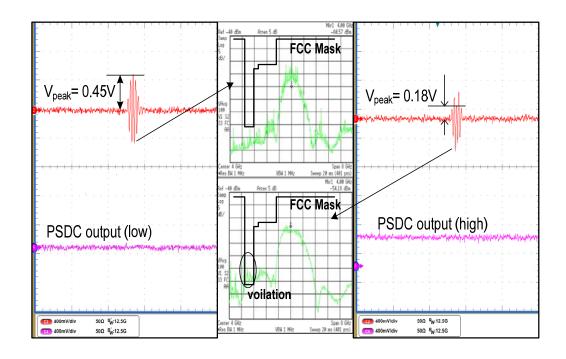

| Figure 4.41. PSDC circuit performance                                                                                                           |

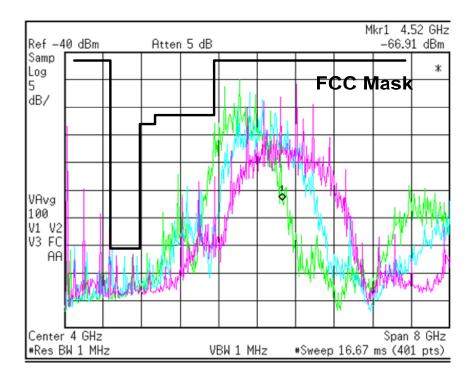

| Figure 4.42. Measured PSD at three UWB center frequency bands of 3.5, 4 and 4.5 GHz                                                             |

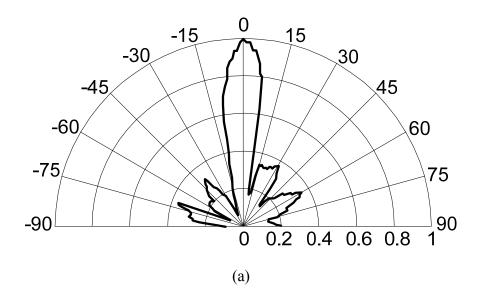

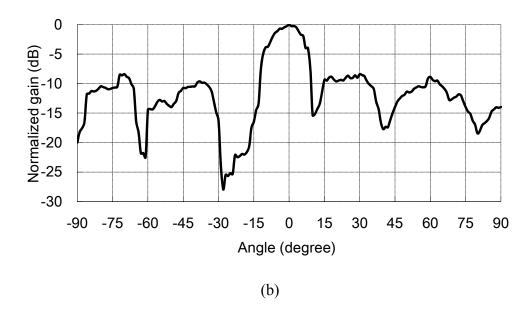

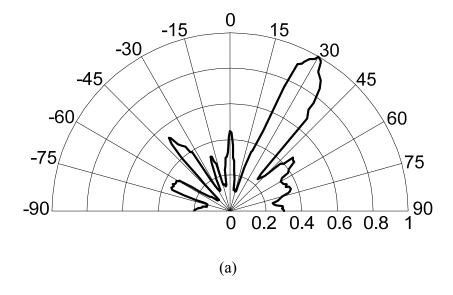

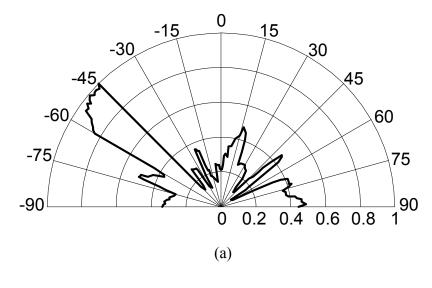

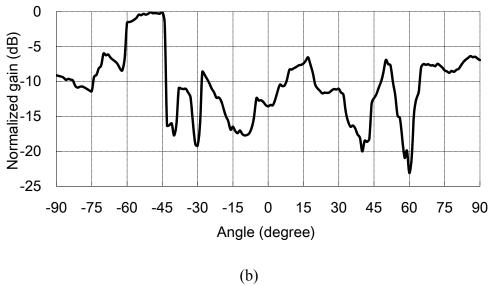

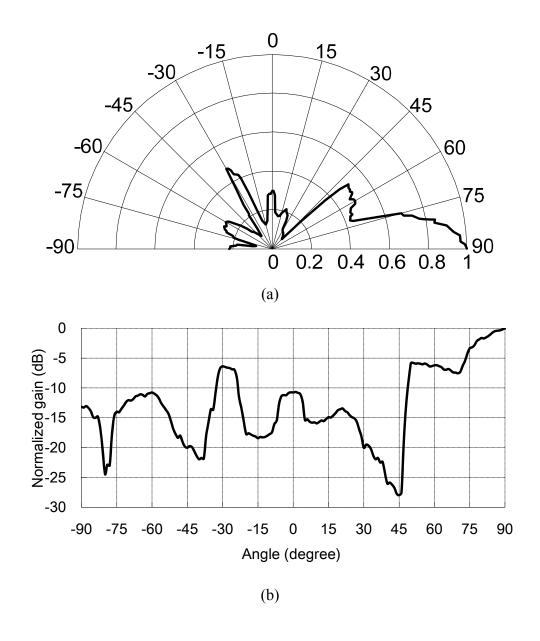

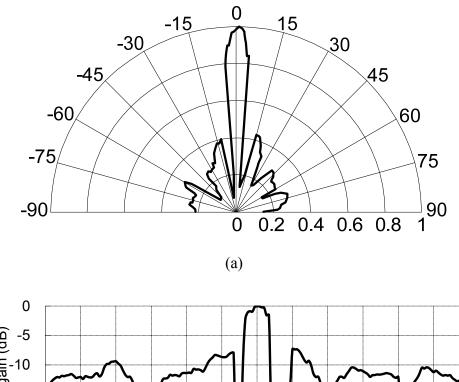

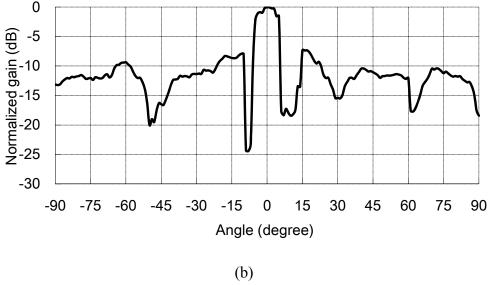

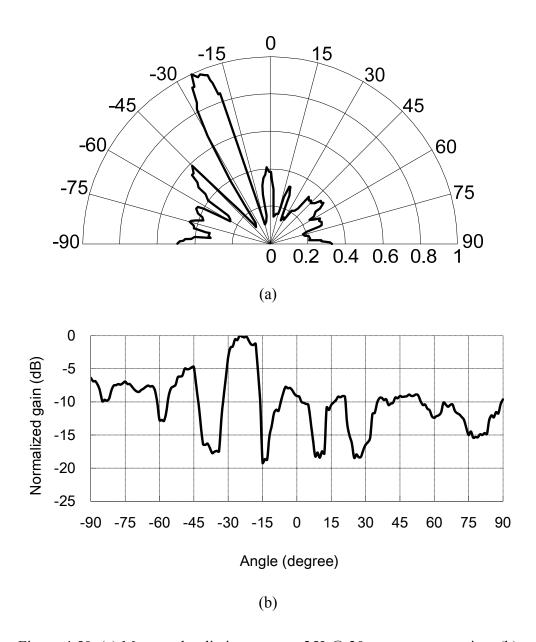

| Figure 4.43. (a) Measured radiation pattern 0° @ 18cm antenna spacing; (b) Measured radiation pattern 0° @ 18cm antenna spacing in dB scale     |

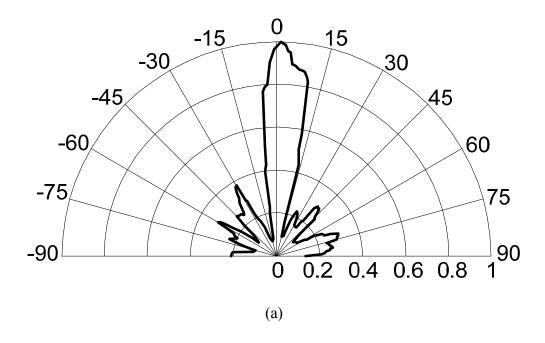

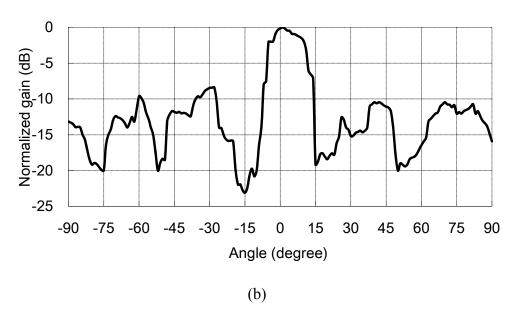

| Figure 4.44. (a) Measured radiation pattern 1° @ 18cm antenna spacing; (b) Measured radiation pattern 1° @ 18cm antenna spacing in dB scale     |

| Figure 4.45. (a) Measured radiation pattern 30° @ 18cm antenna spacing; (b) Measured radiation pattern 30° @ 18cm antenna spacing in dB scale   |

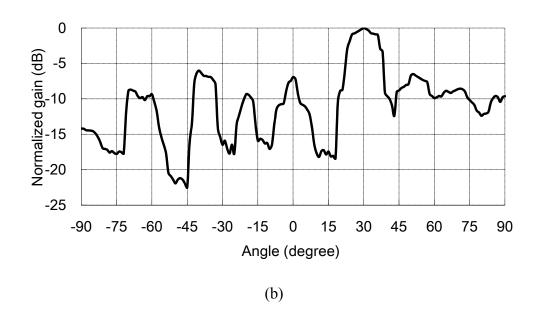

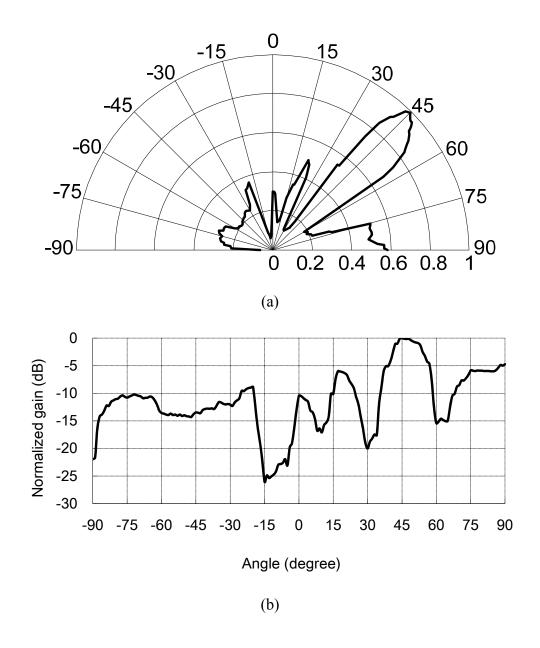

| Figure 4.46. (a) Measured radiation pattern 45° @ 18cm antenna spacing; (b) Measured radiation pattern 45° @ 18cm antenna spacing in dB scale   |

| Figure 4.47. (a) Measured radiation pattern -45° @ 18cm antenna spacing; (b) Measured radiation pattern -45° @ 18cm antenna spacing in dB scale |

| Figure 4.48. (a) Measured radiation pattern 90° @ 18cm antenna spacing; (b) Measured radiation pattern 90° @ 18cm antenna spacing in dB scale   |

| Figure 4.49. (a) Measured radiation pattern 0.4° @ 30cm antenna spacing;                                                                        |

| (b) Measured radiation pattern 0.4° @ 30cm antenna spacing in dB scale                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------|

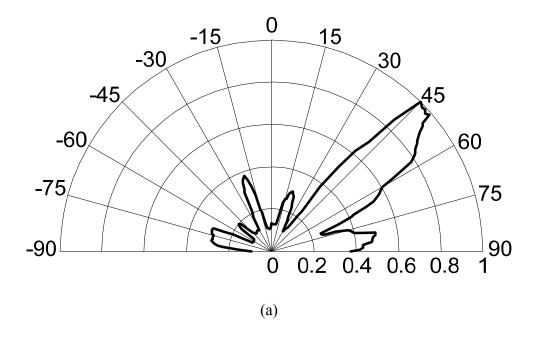

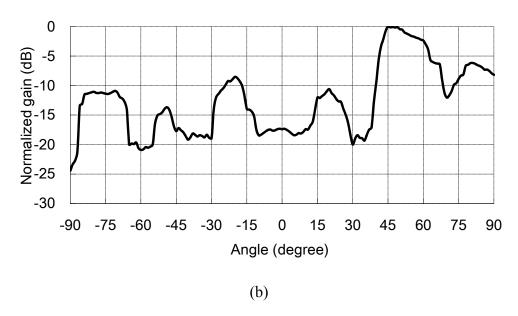

| Figure 4.50. (a) Measured radiation pattern -25° @ 30cm antenna spacing; (b) Measured radiation pattern -25° @ 30cm antenna spacing in dB scale |

| Figure 4.51. (a) Measured radiation pattern 45° @ 30cm antenna spacing; (b) Measured radiation pattern 45° @ 30cm antenna spacing in dB scale   |

| Figure 4.52. The beamforming transmitter power consumption at different data rate                                                               |

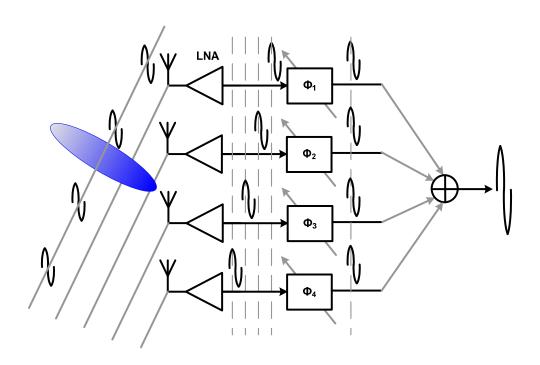

| Figure 5.1. Beamforming receiver principle illustration                                                                                         |

| Figure 5.2. Path sharing beamforming receiver architecture [7], [11], [25].                                                                     |

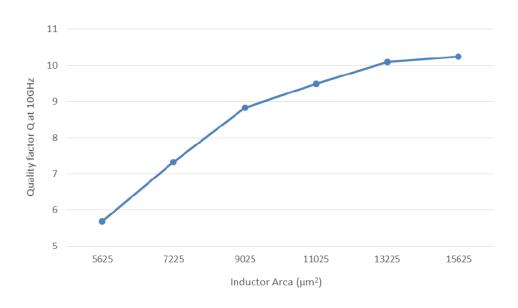

| Figure 5.3. The relationship between inductor Q and area                                                                                        |

| Figure 5.4. The proposed 4-channel UWB beamforming receiver architecture                                                                        |

| Figure 5.5. The proposed noise canceling and current reuse LNA (biasing not shown)                                                              |

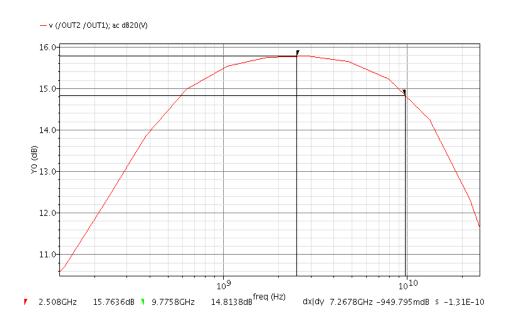

| Figure 5.6. The frequency response of the proposed LNA                                                                                          |

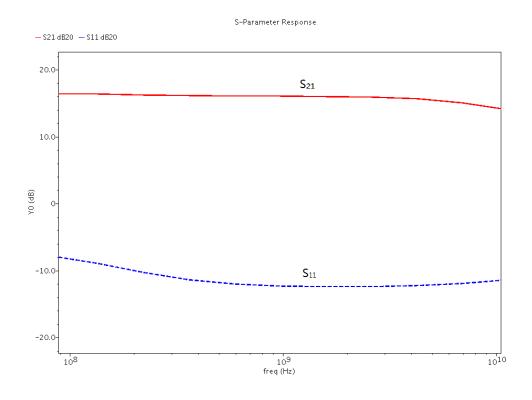

| Figure 5.7. The simulated S <sub>11</sub> and S <sub>21</sub> of the proposed LNA123                                                            |

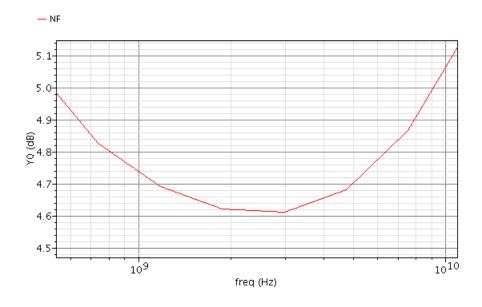

| Figure 5.8. The simulated noise performance of the proposed LNA123                                                                              |

| Figure 5.9. The IIP3 and P1dB simulation of the proposed LNA124                                                                                 |

| Figure 5.10. The true time delay line circuit                                                                                                   |

| Figure 5.11. The path-select amplifier                                                                                                          |

| Figure 5.12. The floor plan of the proposed beamforming receiver circuit.                                                                       |

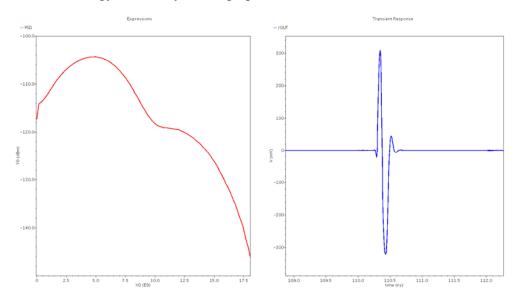

| Figure 5.13. The simulated UWB pulse and its spectrum                                                                                           |

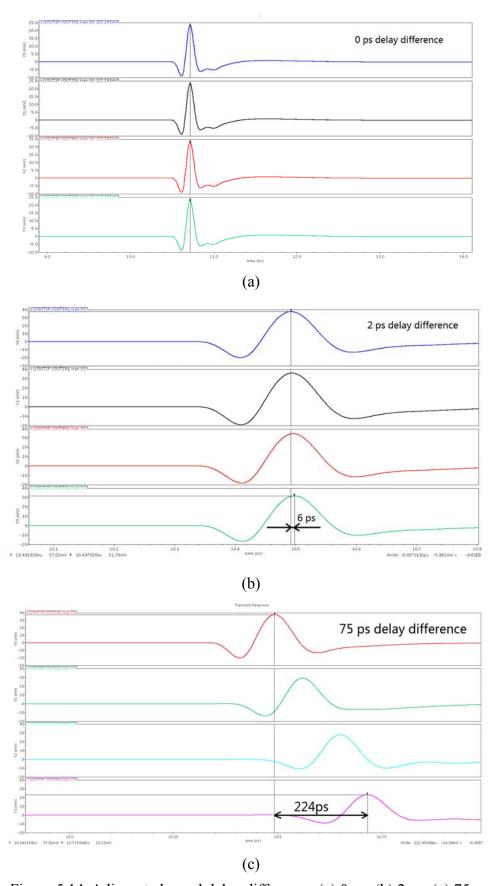

| Figure 5.14. Adjacent channel delay difference: (a) 0 ps; (b) 2 ps; (c) 75 ps                                                                   |

#### LIST OF TABLES

| Table 2.1 The UWB transmitters comparison.                                                     | 21 |

|------------------------------------------------------------------------------------------------|----|

| Table 3.1 Comparison with other recent transmitter works                                       | 55 |

| Table 3.2 Comparison with other receiver works                                                 | 56 |

| Table 4.1 (a) UWB beamformer performance comparison; (b) UV transmitter performance comparison |    |

| Table 5.1 LNA performance summary and comparison with others1                                  | 24 |

| Table 5.2 Beamforming receiver performance summary and comparis with others                    |    |

# LIST OF ABBREVIATIONS

4G Fourth Generation

BER Bit Error Rate

CMOS Complementary Metal-Oxide Semiconductor

DAC Digital to Analog Converters

DCO Digital Controlled Oscillator

DLL Delay Locked Loop

DSP Digital Signal Processing

EEG Electroencephalogram

EIRP Effective Isotropically Radiated Power

FCC Federal Communications Commission

FS Free Space

FSM Finite State Machine

IC Integrated Circuit

IF Intermediate Frequency

IM3 Third-order Inter-Modulation

IP3 Third-order Intercept Point

IR UWB Impulse Radio UWB

LO Local Oscillator

LFSR Linear Feedback Shift Register

LTE Long-Term Evolution

MICS Medical Implant Communications Service

OFDM Orthogonal Frequency Division Multiplexing

OOK On-Off Keying

P1dB 1-dB Compression Point

PA Power Amplifier

PD Phase Detector

PLL Phase Locked Loop

PSDC Power Spectral Density Calibration

PVT Process, Voltage and Temperature

RF Radio Frequency

SAR Successive Approximation Register

SNR Signal to Noise Ratio

SPI Serial-Peripheral Interface

UWB Ultra Wide Band

VCDL Voltage Controlled Delay Line

VCO Voltage Controlled Oscillator

WBAN Wireless Body Area Network

WLAN Wireless Local Area Networks

WPAN Wireless Personal Area Network

WSN Wireless Sensor Network

#### **CHAPTER 1 INTRODUCTION**

#### 1.1 Background

#### 1.1.1 The Attractiveness of IR UWB Transceiver

The customers' demand for ubiquitous wireless connectivity has opened up a new wave of challenges and opportunities for Radio Frequency (RF) integrated circuit design. In addition to high throughput Wireless Local Area Networks (WLAN), attention is now also being focused on lower power and lower data rate, indoor communications which mainly include home automation, smart toys, and medical cares [1], [2]. For example, for wireless body area network (WBAN) used for biomedical applications, the sensor nodes need to constantly collect, process, store and transmit the data to the servers. This places a stringent power requirement on the employed transceiver.

For sensor node application, Bluetooth and ZigBee with well-developed transceiver and protocol are commonly employed. However, their conventional narrow band RF architecture limits the achievable power consumption to tens of mW. Recently, transceiver based on medical implant communications service (MICS) band has also been developed [3]. Due to the narrow spectrum allocated (401 - 405 MHz), they are normally used for applications with data rate lower than a few 100 kbps. For these narrow band approaches, a large portion of power is consumed by frequency translation and synthesis. If the continuous sinusoidal waveform could be replaced by pulses, up/down converters can be eliminated and result in carrierless architecture.

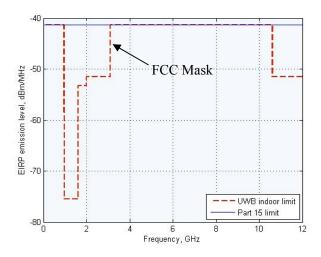

Ultra-wideband (UWB) has emerged as a promising candidate for low power sensor node application since the Federal Communications Commission (FCC) allocated 8 GHz bandwidth (0 - 960 MHz and 3.1 - 10.6 GHz, as shown in Figure 1.1) for such application, where any transmitting signal with its fractional bandwidth greater than 0.2 or its -10 dB bandwidth greater than or equal to 500 MHz can be classified as UWB [4]. The fractional bandwidth is defined as  $2(f_H - f_L)/(f_H + f_L)$ , where  $f_H$  is the spectrum upper -10 dB frequency and  $f_L$  is the lower -10 dB frequency. The maximum power level is -41 dBm/MHz.

Figure 1.1. FCC Mask for UWB regulation.

There are two competing UWB standards, i.e. the Orthogonal Frequency Division Multiplexing (OFDM) standard and the Impulse Radio UWB (IR UWB) standard. OFDM standard has been adopted by Wi-media alliance for implementing high data rate communication. OFDM system divides the entire 7.5 GHz (3.1-10.6 GHz) bandwidth to sub bands with each bandwidth slightly larger than 500 MHz and performs frequency hopping, like narrow band

approach. Therefore, its complexity and PA linearity requirement do not lead to energy efficient implementation.

On the other hand, IR UWB adopts short pulses, instead of continuous sinusoidal waveform. This carrierless feature can potentially offer high energy efficiency solution by eliminating frequency translation blocks and exploiting heavy duty cycling. It is also promising for mostly digital transceiver architecture.

In addition, the IR UWB narrow pulse in the time domain also offers accurate location and ranging capability. Its ranging resolution is given by

$$R = \frac{c}{2RW},\tag{1.1}$$

where BW is the bandwidth of the signal and c is the speed of light. If utilizing the 7.5 GHz bandwidth from 3.1 - 10.6 GHz, IR UWB radar resolution can achieve as high as 2 cm.

#### 1.1.2 The Principle and Advantages of UWB Beamforming

The pulse like nature of IR-UWB makes it amenable to CMOS digital technologies. The resulting transceiver could thus benefit from the down-scaling of CMOS devices by tapping on faster digital logic and tremendous digital signal processing power available [5]. The digital nature also provides programmability which is needed for calibration and tuning. On the other hand, transistors suffer from voltage headroom reduction due to down-scaling of CMOS devices. Although the down-scaling improves the transistor speed for RF requirement, it deteriorates the achievable output power due to the voltage headroom reduction and reliability concern.

One way of overcoming output power limitation is through on-chip or off-chip passive power combiners [5]. However, they are generally lossy and incur additional area or cost. Spatial power combination illustrated by narrowband phase array system offers a promising solution in terms of efficiency and cost-effectiveness [6]. Phased arrays have uniformly spaced antennas and produce beamforming in target direction with high gain while rejecting other direction interferers. The object movement could be detected by this beamsteering ability which is desirable for imaging and radar application. The multi-antenna technique is also adopted by Long-Term Evolution (LTE) and Fourth Generation (4G) digital cellular technologies as part of their standard. Therefore, phased array systems are attractive for both radar and communication application.

For narrow band system, the antenna array factor is given by the equation

$$AF(\theta) = \frac{\sin(N(kd\sin\theta - \beta)/2)}{N\sin((kd\sin\theta - \beta)/2)},$$

(1.2)

where  $\theta$  is the polar co-ordinate, N is the number of antenna elements, d is the spacing between the antenna elements,  $\beta$  is the angle at which the main lobe of the beam is focused and  $k=2\pi/\lambda$  is the propagation vector of the transverse electromagnetic wave which is inversely proportional to wavelength  $(\lambda)$ .

Due to the impulse like nature, UWB signal has a different array pattern expression [7]

$$AF(\theta) = \frac{erf(\sqrt{\pi}(N-1)d\sin\theta/(2\Delta Tc))}{(\sqrt{\pi}(N-1)d\sin\theta/(2\Delta Tc))},$$

(1.3)

where  $\theta$  is the polar coordinate, c is the velocity of light,  $\Delta T$  is the pulse width, N is the number of antenna array elements, and each element is separated by a distance of d.

In narrowband phased arrays, there are typically side lobes and grating lobes in the antenna pattern due to the potential zero in the denominator of Equation (1.1). On the other hand, UWB beamformer does not suffer from such issue.

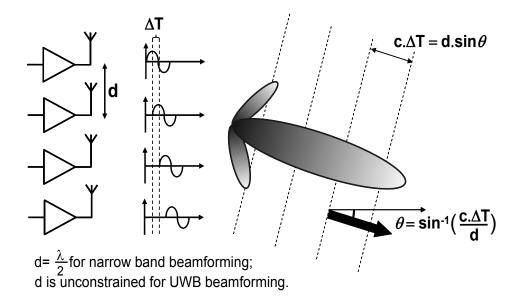

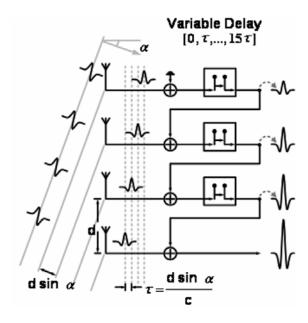

The 4-channel UWB beamformer is illustrated in Figure 1.2. In order to steer the main beam in the desired direction  $\theta$ , the relative delay between the signals fed to the adjacent antenna elements is given by

$$\Delta T = \frac{d\sin\theta}{c} \,. \tag{1.4}$$

Equation (1.4) indicates that the electromagnetic beam can be scanned electronically by controlling the relative delay between signals ( $\Delta T$ ) and distance between adjacent antennas. By keeping the relative delay between different signal path constant, the signals only add up coherently in the air along a particular direction and lead to beam steering in that direction which enables directional point-to-point communication and minimizes the interference to and from other narrow band systems [8]. For *N*-path phase array transmitter, the Effective Isotropically Radiated Power (EIRP) is improved by  $20\log(N)$  [9]. For *N*-path phased array receiver, the SNR could be improved by  $10\log(N)$  (dB) due to signal coherent addition [10].

Figure 1.2. UWB beamforming transmitter principle.

Due to the wide band of IR UWB signal, UWB beamforming could also achieve high depth resolution and range resolution at the same time [11]. UWB beamforming can also achieve possible sidelobe pattern shaping through pulse shape tuning [11], and eliminate the antenna spacing dependency on carrier wavelength [7]. Therefore, when compared to narrow band systems, beamforming in UWB also provides an additional degree of freedom in choosing the antenna spacing.

#### 1.2 Motivation

As mentioned earlier, IR UWB transceiver is a promising candidate to enable low power sensor node applications. IR UWB beamformer also has several unique advantages for imaging and radar applications. However, there is still room for improvement for both sub GHz IR UWB transceiver, and IR UWB beamformer, which are summarized as follows:

- 1. For transceivers, some reported architectures [12], [13], [14] do not fully exploit the digital nature of IR-UWB. Although these analog approaches could achieve high output power, they suffer from poor energy efficiency.

- 2. For digital intensive architecture, the circuit blocks are not optimized for high speed operation [15], [16], which often results in lower output amplitude and compromising communication range.

- 3. It is challenging to generate UWB pulse under FCC mask, so filters are generally required which are bulky.

- 4. For UWB beamformers, there are limited reported works on this aspect.

Most of them suffer from architecture limitation and result in poor

phase resolution with limited scanning range.

- 5. Conventional passive L-C based delay element has lossy and bulky problems, resulting in poor energy efficiency as well as large area.

#### 1.3 Research Contributions

Given the research gaps described above, we look into various novel ways of improving the performance of UWB transceiver and beamformer. The contributions of this research are listed below:

- 1. For sub 1 GHz UWB transmitter, we have proposed an all-digital solution with pulse width and amplitude programmability to achieve center frequency tuning and band shaping. Compared to existing works, we proposed technique and architecture to minimize the impact of parasitic and achieve larger output amplitude.

- 2. For sub 1 GHz receiver, threshold based detector with auto threshold detection scheme is proposed to improve the energy efficiency. From

- measurement, the transceiver achieves 100 pJ/bit and 600 pJ/bit for transmitter and receiver respectively.

- 3. For UWB beamforming transmitter, we employed vernier delay cell to achieve 10 ps delay resolution, which is 10 times smaller than the currently reported works.

- 4. ΔΣ DLL is proposed to perform the delay calibration. Through the optimized transmitter architecture as mentioned earlier, we also achieved 10 times power reduction compared to others. The beamfomer achieves 135° phase range with 1° phase resolution, while consuming 9.6 mW @ 80 Mbps. The transmitter achieves energy efficiency of 10 pJ/bit and transmitter efficiency of 7.5%.

- 5. To adjust the UWB pulse shape for meeting the FCC mask, a power spectral density calibration circuit is proposed.

- 6. For UWB beamforming receiver, Q compensated method was proposed. The 4-channel beamformer occupies small area of 1.44 mm<sup>2</sup>. This is seven times smaller than the other UWB beamformer based on passive delay with similar delay range.

#### The publications achieved to date are listed below:

- [1] <u>Lei Wang</u>, Yong Lian and Chun Huat Heng, "A Sub-GHz Mostly Digital Impulse Radio UWB Transceiver for Wireless Body Sensor Networks," *IEEE VLSI DAT*, 2013.

- [2] <u>Lei Wang</u>, Yong Lian and Chun Huat Heng, "3-5 GHz 4-Channel UWB Beamforming Transmitter with 1° Scanning Resolution through Calibrated Vernier Delay Line in 0.13μm CMOS," *IEEE Journal of Solid-State Circuit (JSSC)*, pp. 3145 3159, Dec. 2012 (Invited).

- [3] <u>Lei Wang</u>, Yong Xin Guo, Yong Lian, and Chun Huat Heng, "3-to-5GHz 4-channel UWB beamforming transmitter with 1° phase resolution through calibrated vernier delay line in 0.13µm CMOS," *IEEE International Solid-State Circuits Conference (ISSCC)*, pp.444-446, Feb. 2012.

- [4] <u>Lei Wang</u>, Chandrasekaran Rajasekaran, Yong Lian, "A 3–5 GHz all-digital CMOS UWB pulse generator," *Asia Pacific Conference on Postgraduate Research in Microelectronics and Electronics (PrimeAsia)*, pp.388-391, Sept. 2010.

#### 1.4 Organization of The Thesis

The following thesis is organized as follows. Chapter 2 will give a brief literature review on the architectures of IR UWB beamforming transmitter and receiver. The sub 1 GHz UWB transceivers are discussed in Chapter 3 with detailed design explanation and measurement result. Chapter 4 described the design and measurement of 3-5 GHz UWB beamformer. The UWB beamforming receiver is presented in Chapter 5. Finally, conclusion is given in Chapter 6.

# CHAPTER 2 REVIEW OF UWB TRANSCEIVER ARCHITECTURES

#### 2.1 Existing UWB Transmitter Architectures

One of the key challenges of IR UWB transmitter design is to generate UWB pulses that meet the FCC spectral mask as mentioned. Based on the approaches, reported UWB transmitters can be easily classified into analog or digital architecture.

#### 2.1.1 Analog UWB Transmitters

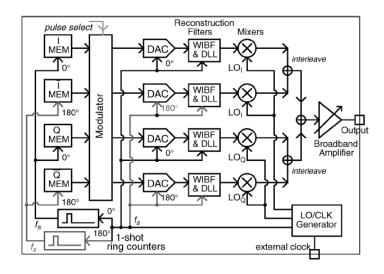

Analog UWB transmitter adopts similar approach as conventional narrow band RF design. In [12], the band shaping is achieved at baseband through DAC. After which, it is up-converted to the desired RF through mixer. Different sub-bands can be combined through RF summer before sending to a broad band amplifier as shown in Figure 2.1. Although accurate band-shaping can be obtained at baseband, it requires many power hungry blocks, such as DAC, LO, mixer and PA. Hence, they generally suffer from poor energy efficiency.

Figure 2.1. Analog UWB transmitter based on traditional analog approach.

Another analog based approach employs on-off modulation of VCO to eliminate the need of LO, mixer and DAC [13], [14], as illustrated in Figure 2.2. This approach allows large output amplitude due to the inductive peaking. However, the short turn-on-time requirement for VCO will impact its energy efficiency. In addition, additional LC filtering is often needed to achieve the desired band-shaping and thus incur area penalty.

Figure 2.2. Analog UWB transmitter based on VCO.

In general, analog based approach can achieve large output amplitude with accurate band shaping. However, they generally suffer from poor energy efficiency and area penalty.

#### 2.1.2 Digital UWB Transmitters

The pulse-like nature of IR-UWB makes it amenable to digital implementation. In general, the fundamental concept of digital architecture involves generating a string of digital pulses and modulating the amplitude of the digital pulses to achieve the desired band-shaping. Various approaches differ in their way of obtaining digital pulses. In [16] and [15], different delay edges are obtained through digital delay line. The delay edges are then combined through edge combiner to obtain the desired string of short pulses, as shown in Figure 2.3. The pulse width which determines the center frequency are adjustable through tunable delay cell. The number of pulses can be controlled by activating the desired number of edges.

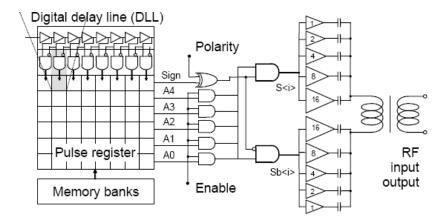

Figure 2.3. Digital UWB transmitter in [16].

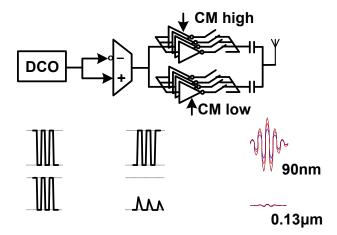

Figure 2.4. Digital UWB transmitter architectures based on DCO.

Table 2.1 The UWB transmitters comparison.

|                  | [12]   | [14]    | [13]  | [16]  | [15]    | [17]       |

|------------------|--------|---------|-------|-------|---------|------------|

| Took (nm)        | CMOS   | CMOS    | CMOS  | CMOS  | CMOS    | CMOS 00    |

| Tech. (nm)       | 90     | 130     | 180   | 90    | 180     | CMOS 90    |

| Supply (V)       | 1.25   | 1.35    | 1.8   | 1     | 1.8-2.2 | 1.2        |

| Energy efficiecy | 1250   | 186     | 920   | 22.6  | 12      | 17.5       |

| (pJ/pulse)       | 1250   | 100     | 920   | 22.0  | 12      | 17.5       |

|                  |        |         |       |       |         | 0.71-0.165 |

| Pulse amplitude  | 0.15V@ | 2.4V@   | 2.8V@ | 0.7V  | 0.06V@  | V          |

| (peak-peak)      | 4GHz   | 7.5 GHz | 4GHz  | (max) | 8GHz    | @2.1-5.7   |

|                  |        |         |       |       |         | GHz        |

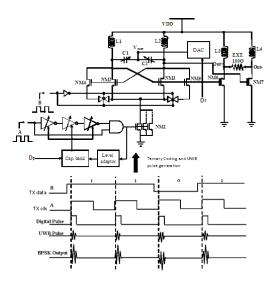

In [17], digital ring oscillator is employed to create a string of short pulses. The center frequency of ring oscillator is digitally tuned through DAC. Once a string of short pulses have been generated, each pulse amplitude is modulated digitally through buffer amplifier with different sizing depending on the pulse position as shown in Figure 2.4. This will result in a shaped IR-UWB signal and achieve the desired band shaping to meet the spectral mask. It should be pointed out that the need to transmit the resulting short pulses through a buffer

chain could result in excessive buffer size and reduce output amplitude. Hence, in general, digital approach can achieve better energy efficiency with moderate output amplitude. To summarize, various architectures performance are compared in Table 2.1.

The performance comparison of the above mentioned UWB transmitters is listed in Table 2.1. From this comparison table, we could find that analog approach could achieve larger output pulse amplitude, even higher than supply voltage [13, 14]. However their consumed power is relatively large, so the energy efficiency is poor. Better energy efficiency could be obtained by digital approach as in [15-17]. Among these works, the all-digital UWB transmitter in [17] achieves good energy efficiency, relatively high output amplitude, and without any bulky inductors.

#### 2.2 Existing Beamforming Transmitter Architectures

A beamforming transmitter contains an array of transmitters to generate the RF signals with beam steering in particular direction. Phase shifters are essential components for adjusting each channel phase. Depending on the phase shifter location, beamforming transmitter can be classified into following architectures.

#### 2.2.1 IF Phase Shift Beamforming Transmitter

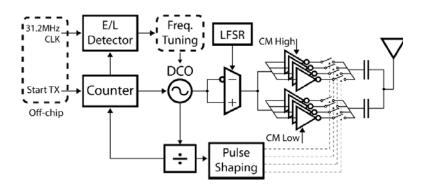

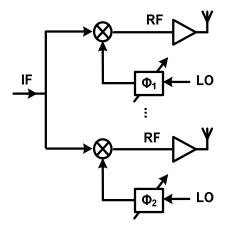

In this architecture, phase shifting is done at baseband before up-converting to RF, as shown in Figure 2.5 [18].

Figure 2.5. Beamforming transmitter with phase shift at IF stage.

Relatively low IF frequency could be chosen to relax the phase shifter design and make it less sensitive to parasitic. In addition, active phase shifters could be adopted instead of bulky and lossy passive ones [19]. However, active phase shifter suffers from linearity issue, especially for transmitter with large amplitude [20]. In addition, the earlier path separation implies duplication of many blocks from baseband up to the PA, which incurs both area and power penalty.

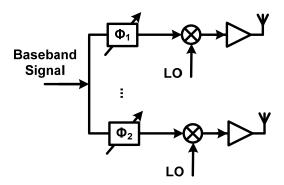

#### 2.2.2 RF Phase Shift Beamforming Transmitter

Phase shifting can also be performed after up-conversion as shown in Figure 2.6. Due to the higher frequency, passive phase shifter is generally adopted in this case.

Figure 2.6. Beamforming transmitter with phase shift at RF stage.

Although high frequency blocks, such as LO and mixer can be shared for this architecture, it is generally avoided to improve isolation [21], [14], [11]. Due to the LC phase shifter employed for such high frequency, it could incur significant area penalty and insertion loss due to the on-chip inductor with poorer Q.

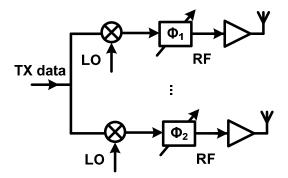

#### 2.2.3 LO Phase Shift Beamforming Transmitter

Phase shifting can also be introduced at LO as illustrated in Figure 2.7. It is a popular choice for narrow band system due to its minimal impact on different path gain [22]. However, it can suffer from signal distortion due to dispersion [9]. Unfortunately, it is not suitable for IR-UWB as the phase shift introduced by LO would not result in the desired time delay in IR-UWB signal.

Figure 2.7. Beamforming transmitter with phase shift at LO.

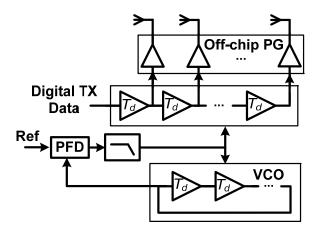

#### 2.2.4 True Time Digital Delay Beamforming Transmitter

Due to the pulse like nature of IR UWB, true time digital delay element has been proposed as phase shifter for UWB beamforming transmitter as shown in Figure 2.8 [23]. The identical delay Td between different paths could be generated when input TX data passes through the buffers. Although digital delay is simple and scalable with technology, its performance is often limited by the achievable absolute delay (Td) of each delay cell in a given technology. As an example, 10 ps absolute delay is needed to obtain 1° phase resolution with antenna spacing of 18 cm. To achieve such fine absolute delay, it will incur large power consumption even with advanced CMOS technology. The beamforming transmitter in [23] reported phase resolution of only  $10^{\circ}$  (absolute delay of 100 ps) and its baseband phase shifter alone consumes power as high as 100 mW.

Figure 2.8. True time digital delay beamforming transmitter.

#### 2.3 Existing Beamforming Receiver Architectures

Like beamforming transmitters, a beamforming receiver contains an array of receivers to receive the RF signals with beam steering in particular direction. Phase shifters are still essential components for adjusting each channel phase. Depending on the phase shifter location, beamforming receiver can also be classified into IF, RF and LO phase shift architectures [10], [24]. However, only RF phase shift architecture is suitable for UWB beamforming receiver due to similar reasons as beamforming transmitter. Depending on phase shifter implementation, UWB beamforming receiver could be categorized into passive or active phase shifter based architectures.

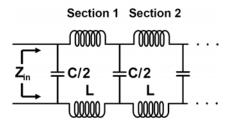

#### 2.3.1 Passive Phase Shift Beamforming Receiver

In this architecture, true time delay is performed by passive LC element [7], [11], [25] based on the approximation of transmission line segments. The delay of this structure is approximately

$$T_d = n\sqrt{LC} \tag{2.1}$$

where is n the number of LC sections as shown in Figure 2.9. To eliminate insertion loss of the passive LC elements, high Q inductors are usually adopted [7], [11], [25], resulting in bulky implementation especially when large delay range is needed.

Figure 2.9. Passive phase shifter.

#### 2.3.2 Active Phase Shift Beamforming Receiver

Figure 2.10. Active phase shifter.

UWB signal is phase shifted by active delay element in this architecture [26].

The high Q bulky on-chip inductors are avoided by a g<sub>m</sub>-RC or g<sub>m</sub>-C all-pass delay circuit as shown in Figure 2.10. However this active inductor based true time delay consumes large power and is difficult to operate for frequency higher than 3 GHz.

#### 2.4 Findings

From the literature review, digital approach for IR-UWB transmitters is generally preferred for good energy efficiency. Besides, it is impractical for multi-channel beamforming transmitter due to excessive area penalty. In addition, reliability is also a concern due to the lower gate oxide breakdown voltage in deep sub-micron technology. Another important factor keep us away from analog UWB transmitter is that we have to adopt a Digital to Analog Convertor (DAC) to convert the beamforming delay edges into analog input to the analog UWB transmitter. References [27] and [28] predict that digital phase shift beamforming transmitter is complex and power hungry due to DACs. They did not recognize the fact that digital phase could be converted to UWB pulse directly with duty-cycled nature and lower power feature. Therefore, we choose all-digital UWB transmitter without DAC.

To achieve short pulse width without incurring significant power or the need of most advanced technology, alternative digital architecture needs to be proposed for all-digital UWB transmitter. Similarly, for beamforming transmitter, true time digital delay offers attractive compact area solution. However, we need to come out with alternative architecture to achieve the desired small phase resolution without excessive power penalty.

As for UWB beamforming receiver, we want to operate up to 10 GHz, so the

active phase shifters could not be adopted. New design approach is needed for passive phase shifter to achieve large delay range with reasonable area consumption. In the following chapters, we will elaborate our proposed design further.

# CHAPTER 3 SUB 1 GHZ IR UWB TRANSCEIVER

# 3.1 System Requirement And Design Consideration

As mentioned earlier, IR-UWB can offer low cost and low power transceiver solution suitable for WBAN targeting for health care application. In this chapter, we will propose a sub 1 GHz IR-UWB transceiver caters for the basic ECG application. For such application, the transceiver needs to achieve 1 Mbps for a short communication range of less than 0.25 m within an office environment. Sub 1 GHz is chosen in this design to enable low power implementation by exploiting larger ratio of f/f<sub>T</sub>. In addition, it also offers better penetration.

As analyzed in chapter 2, digital based IR-UWB transmitter offers better energy efficiency with moderate output, and is thus adopted in this design. For the receiver portion, ADC based approach [29], [30] requires high speed GHz ADC and might not be an energy efficient approach. Reference [31] employs mixer down conversion whereas reference [32] employs template correlation that requires accurate synchronization. Both approaches are also not energy efficient due to the architecture complexity.

In this chapter, a digital intensive IR-UWB transceiver with intermittent operation will be covered. Detector based approach with automatic threshold detection is employed to address the power issue and will be discussed in subsequent sections.

# 3.2 Link Budget

There are many different UWB channel models [33, 34]. As indicated in [33] and [35], a simple and effective model is an ideal free space path in which there is no ground reflection and multi-path. It has a path loss that is proportional to the square ( $\alpha$ =2) of the separation d, and inversely proportional to the wavelength ( $\lambda$ ):

$$PL_{dB}(d) = \alpha \cdot 10 \log_{10} \left( \frac{4\pi d}{\lambda} \right) = \alpha \cdot 10 \log_{10} (d) + c$$

(3.1)

where c is a power scaling constant included in calibration.

Friis formula suggests that a 1 m path loss equals 35.5 dB for a signal operating at 1 GHz. The antennas are designed by others, and we do not have the antenna gain information, so combined antenna gain of -3 dBi is assumed for the transmitter and receiver together. Therefore, from Equation (3.1), a 25 cm distance exhibits a path loss of 23.5 dB. This is a conservative estimation, because the sub-1 GHz UWB signal has lower frequency. Besides the path loss, there are other losses incurred, such as cable loss, PCB, connector and etc. In our implementation, we conservatively assume 6 dB for such combined implementation losses (*IL*).

By approximating the transmitted UWB pulse with triangular pulse shape and peak-to-peak amplitude of 2 V, we could estimate the pulse energy as follows:

$$P_{TX} = \frac{(V_{pp} / 4)^2}{50} \cdot 1ns \cdot DR \tag{3.2}$$

where DR is the data rate of 1 Mbps, and pulse duration is assumed to be 1 ns. This results in  $P_{TX}$  of -23 dBm.

Hence the transmitted power available at the receiver input is

$$P_{TYA} = P_{TY} - PL - IL \tag{3.3}$$

where PL is the estimated 23.5 dB path loss, IL is the estimated 6 dB combined implementation losses. This results in  $P_{TXA}$  of -52.5 dBm.

The channel noise is

$$N_{channel} = -174 \frac{dBm}{Hz} + 10 \log_{10}(B)$$

(3.4)

which gives rise to -84 dBm noise power under 1 GHz channel bandwidth.

The minimum detectable power at the receiver front end is

$$P_d = SNR + N_{channel} + NF (3.5)$$

where NF is noise figure, and SNR is the required signal to noise ratio. Our system NF is estimated to be 17 dB. To obtain reasonable BER using our proposed threshold detector, 6 dB SNR is required from our system studies, so  $P_d$  is estimated to be -61 dBm.

Therefore, the estimated link margin is about 8.5 dB.

#### 3.3 A Sub 1 GHz OOK IR UWB Transceiver

#### 3.3.1 The Proposed Architecture

The proposed IR UWB transceiver architecture is shown in Figure 3.1. To increase communication reliability, 11-bit Barker Code is incorporated as coding scheme. At the transmitter side, TX data is first encoded in the digital

back-end using Barker Code Encoder. OOK modulation is adopted here. Finally, it generates the UWB pulse by the all-digital UWB pulse generator.

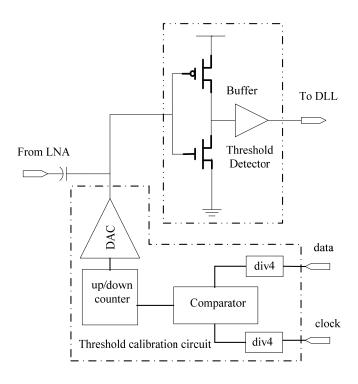

The receiver incorporates low noise amplifier (LNA) to strengthen the input signal. The amplified signal is compared with a threshold voltage using a threshold detector. It is not convenient to set the threshold value manually. When there is process, voltage and temperature (PVT) changes, the preset threshold value has to be readjusted. Therefore, auto-threshold detection is adopted for this OOK IR UWB receiver. The threshold voltage is provided by a calibration circuit. Clock re-timing and data recovery is performed using a low voltage low power SAR DLL. Finally, the digital backend decodes the received signal using Barker Code decoder.

Figure 3.1. The proposed IR UWB transceiver architecture.

# 3.3.2 All-Digital OOK UWB Transmitter

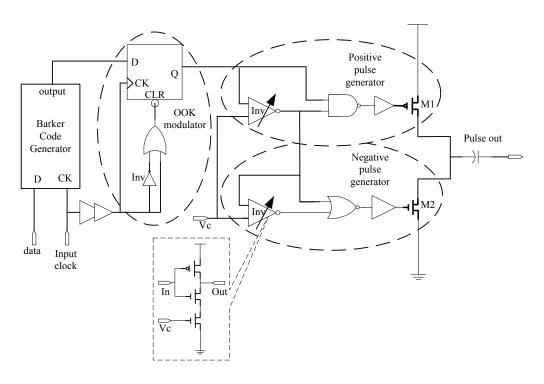

Figure 3.2. UWB transmitter structure.

The proposed OOK UWB transmitter is shown in Figure 3.2. As mentioned in Chapter 2, UWB transmitter architecture has the trade-off between energy efficiency and output power. This transmitter adopts digital architecture with improved output power. The modulated input data and its delayed version go through a NAND gate or a NOR gate to generate a narrow positive or negative pulse. The output of NAND or NOR gate turns on the PMOS or NMOS transistor respectively, which are sized to shape each pulse to the required amplitude. The buffers after NAND and NOR gates are used to drive the PMOS and NMOS. Larger pulse width and amplitude will be generated through a smaller external voltage, *Vc*. To generate peak to peak output amplitude of 2.5 V, the output current should be at least 50 mA. To get this large current, the sizing of output transistors is critical. The sizing of transistor M1 is determined by

$$\left(\frac{W}{L}\right)_{M1} = \frac{2I_{M1}}{K_p \cdot V_{gt}^2} \tag{3.6}$$

where Kp is a technological parameter, and Vgt is (Vgs-Vt), the over-drive voltage. 0.35  $\mu$ m technology is used here, so Kp is about 40  $\mu$ A/V<sup>2</sup>. Assuming the over-drive voltage to be 2 V here, we could get that the width of M1 is about 220  $\mu$ m. Considering layout parasitic, bonding wire, package, PCB connection, and other losses, a larger width of 300  $\mu$ m is adopted for M1. In a similar way, 150  $\mu$ m is chosen as the width for transistor M2.

# 3.3.3 The Proposed OOK UWB Receiver

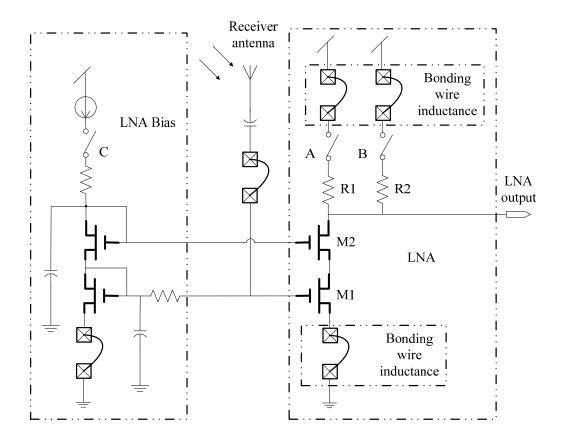

Figure 3.3. The LNA circuit.

Receiver front end has to incorporate gain stage to increase communication range. However, gain stage like LNA is typically power consuming. Therefore, the receiver front end has a trade-off between communication range and power consumption. Since the target application does not require long distance data transmission, a single stage LNA with variable gain is adopted. Reference [36] demonstrates that voltage matching generates larger signal amplitude than power matching for a sub 1 GHz LNA. Therefore, this LNA adopts voltage matching for threshold detection. It adopts cascode structure to increase its gain and bandwidth, as shown in Figure 3.3. The gain is tunable by changing the output resistance through switches A and B. Large current of 10 mA is assigned for this LNA. Actually its power consumption could be lowered by intermittent operation as shown later. According to [37], the optimum width of M1 is determined by

$$W_{opt} = \frac{1}{3\omega L C_{or} R_s} \tag{3.7}$$

where  $\omega$  (rad) is the operation frequency of 1 GHz, L is 0.35  $\mu$ m,  $C_{ox}$  is 5 mF/m², and  $R_s$  is 50 source resistance. Therefore, 600  $\mu$ m is chosen for the width of M1. Transistor M2 is cascoded to reduce the interaction of output node with input node by reducing the miler effect of M1's gate to drain capacitance. A relatively smaller size of 100  $\mu$ m is chosen here. The transistor sizing in the bias circuit is about five times smaller to reduce the power consumption.

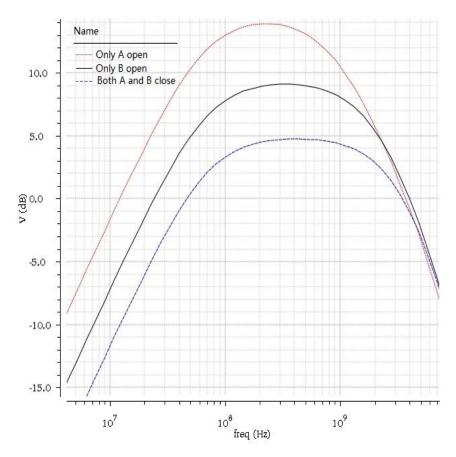

Considering voltage headroom at the output, R2 and R1 are designed to  $200 \,\Omega$  and  $100 \,\Omega$ , respectively. The post layout simulation result shows its gain could be varied from 3 dB to 12 dB, as shown in Figure 3.4. Its bandwidth covers from 100 MHz to 1 GHz. The antenna and bypassing capacitor form the high-pass filter while the low-pass filtering is achieved by the LNA output resistance and parasitic capacitance.

Figure 3.4. The LNA variable gain simulation results.

High Q inductor not only takes too much area, but also causes stability problem and ringing effect for the UWB pulses. The ringing effect may deteriorate the waveform and result in wrong decision for the threshold detection. Therefore, this LNA does not incorporate inductor. The receiver *NF* is dominated by the LNA which is the only RF block. The LNA's *NF* worst case simulation result is shown in Figure 3.5. Although the 1/f noise is much larger than the white noise below its corner frequency, the estimation of 17 dB *NF* is quite conservative when calculating the transceiver link budget.

Figure 3.5. The simulated *NF* of LNA.

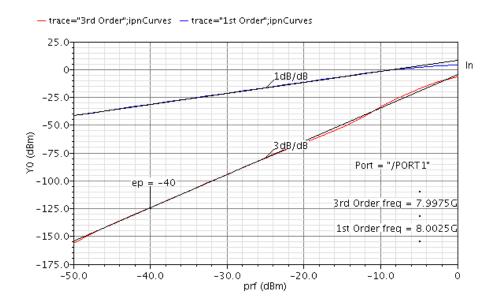

Due to the inherent nonlinearity of CMOS devices, unwanted beat products could be generated from third-order inter-modulation (IM3). Receiver third-order nonlinearity is commonly characterized by a third-order intercept point (IP3). IM3 may have a detrimental effect in narrow band RF communication system, because out of band signals may generate unwanted beat appearing within signal band. On the other hand, gain compression problem may arise when there is a large in band signal or an out of band blocker. The LNA IP3 performance and 1-dB compression point (P1dB) simulation result under different gain setting are shown in Figure 3.6 and Figure 3.7 respectively. The horizontal axis of Figure 3.6 represents the input power. Its vertical axis is the output power of the fundamental component and IM3. When large signal is present, the gain should be set smaller to prevent LNA saturation. Therefore, with variable gain setting, the compression problem is much relaxed.

Figure 3.6. The simulated *IP3* of LNA.

Figure 3.7. The simulated *P1dB* of LNA.

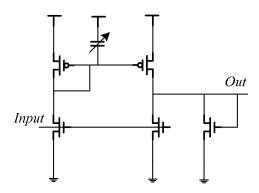

The receiver front end is power hungry due to LNA, so the LNA operates intermittently to reduce power consumption. It only operates during data arrival window of about 15 ns and is powered-down during other time. The data window is provided by DLL based clock retiming circuit. LNA power-down is achieved by turning off LNA operation stage and biasing through opening switches A, B and C, as shown in Figure 3.3.

Figure 3.8. Schematic of UWB receiver frontend.

The LNA is followed by an inverter-based threshold detector which is biased with high gain, as shown in Figure 3.8. The threshold value is provided by a threshold calibration circuit through a DAC. In 11-bit Barker Code, there are no more than four consecutive logical '0's or '1's (data '0' is encoded as "11100010010" and data '1' is "00011101101"). The calibration circuit takes

advantages of this characteristic to provide the threshold level. Suppose the default threshold value is preset relatively high. During calibration, it will be decreased if more than four consecutive logical '0's are received. On the other hand, the threshold level will be increased if more than four consecutive logical '1's are received. The calibration continues until the threshold level converges to the desired level.

# 3.3.4 DLL Based Clock Retiming Circuit

The uncertainty of block delay makes it difficult to predict the data arrival window for proper LNA operation. Both PLL and DLL could align the received data phase to clock by VCO or delay line. DLL is chosen in this work to obtain better jitter performance.

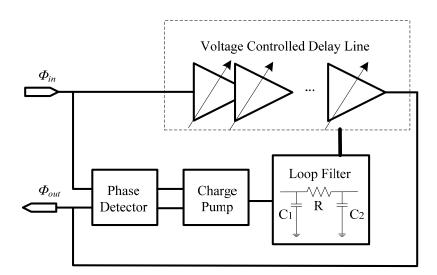

Figure 3.9. Analog DLL architecture.

Based on the delay line and control circuits, DLL architectures could be categorized into analog DLL, digital DLL, or semi-digital DLL. The analog DLL structure is shown in Figure 3.9. It matches the input and output phases

through voltage controlled delay line. The controlling voltage comes from a charge pump and loop filer. This voltage is proportional to the input and output phase difference.

Analog DLL could achieve good jitter performance due to the feedback loop with continuous delay but suffers from limited phase range [38]. Therefore, this architecture is not suitable for clock retiming circuit, because the received data phase could vary from 0 to  $2\pi$ . The area of analog DLL is also typically large due to bulky passive components used in low pass filter.

Figure 3.10. Semi-digital DLL architecture.

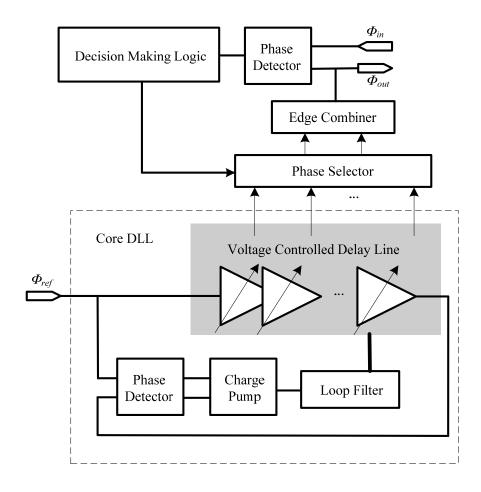

To widen the phase range of traditional analog DLL, semi-digital DLL has

been reported [39]. Its architecture is shown in Figure 3.10. It incorporates an analog DLL as a core DLL to generate multiple clock phases. Additional phase selector and interpolator are adopted to generate a coarse output phase. This output phase could be fine-tuned to match input phase through phase detector and decision making logic. Compared to analog DLL, its jitter performance is poorer due to the phase selector and interpolator, but its phase range is extended to  $0 - 2\pi$ . Thus, semi-digital DLL could be used for receiver clock retiming circuit. However, its dual loop architecture is too complex for our application.

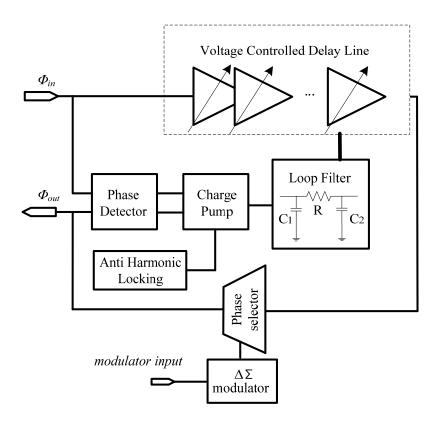

Figure 3.11.  $\Delta\Sigma$  DLL architecture [40].

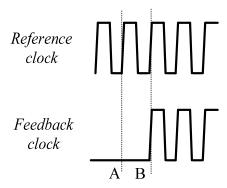

The emerging  $\Delta\Sigma$  DLL [40] is an improved architecture of semi-digital DLL, as shown in Figure 3.11. It also generates multiple clock phases to widen the phase range of traditional analog DLL. However unlike semi-digital DLL, it

reuses the phase detector and analog decision making circuit composed of charge pump and loop filter. Therefore, it has much simplified architecture than traditional semi-digital DLL. To lower the jitter due to phase selecting process, it incorporates a  $\Delta\Sigma$  modulator. Thus, it becomes a strong candidate which can achieve both fine delay resolution in the pico-second range and good jitter performance.

$\Delta\Sigma$  DLL could be adopted as receiver clock retiming circuit. However, this DLL has to be always on to provide time window, so large power will be consumed due to analog blocks.

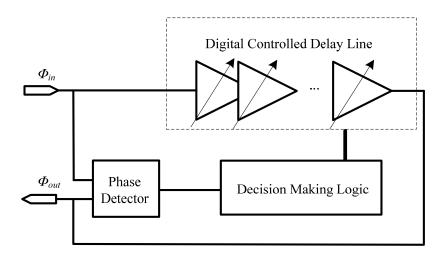

Figure 3.12. Digital DLL architecture.

Digital DLL architecture is shown in Figure 3.12. It adopts digital controlled delay line. Its control words are generated from digital logic, so this architecture is much simpler and less power consuming compared to above mentioned DLLs. Its phase shift could easily cover from 0 to  $2\pi$  due to fully digital control. It is also amenable to digital CMOS. Its delay resolution usually depends on absolute delay, so it is not very good and determined by

technology [41]. Actually, for our receiver clock retiming circuit, the delay resolution and jitter performance is not critical, because the time window provided by DLL only need to be large enough to cover the LNA set-up, amplification, and settling down. The timing resolution is not too much a concern for our intended application. Hence, digital DLL is adopted in this work.

The digital decision making logic could be implemented by shift registers, up/down counters, or successive approximation register (SAR) [42]. The DLL in this thesis adopts SAR controlled all-digital structure to achieve the short locking time. It adopts binary search scheme. The locking-in procedure of the SAR DLL is shown in Figure 3.13. The delay generated approaches the desired value in a binary way. For N-bit SAR DLL, it only takes N-step to lock in. Therefore, it has very short locking time. With shorter locking time, the LNA could be more quickly duty cycled to save power.

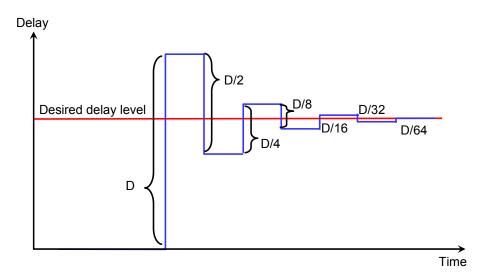

Figure 3.13. The locking in procedure of the SAR DLL.

The SAR DLL based clock retiming circuit is shown in Figure 3.14. It has a 1

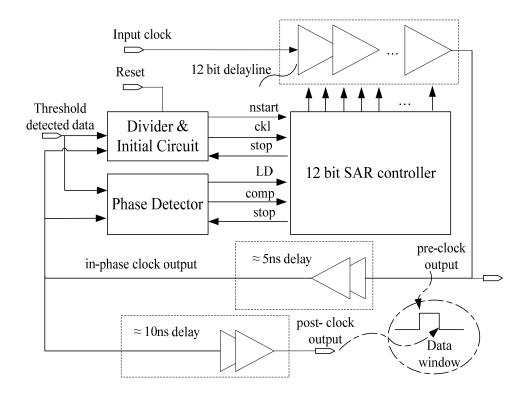

MHz clock as input. Another input is the threshold detected data. This circuit is able to align the "input clock" with the received "data" by delaying the input clock properly. The "in-phase clock output" signal is delayed version of the input clock after it passes through the digital controlled delay line. A phase detector compares the phases between "data" and "in-phase clock output". Based on this phase information, the SAR controller will decide whether to increase or decrease the delay.

Figure 3.14. The architecture of DLL-based clock re-timing circuit.

Figure 3.15. Harmonic locking problem in DLL.

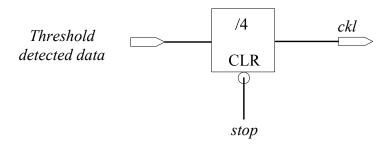

Harmonic locking is a common problem in traditional DLL [40]. As shown in Figure 3.15, there is potential that the feedback clock can be delayed by more than one reference clock and result in harmonic locking. Anti-harmonic locking detection circuit could be adopted to avoid this problem [40], but it will incur additional complexity in control. This problem is circumvented in this work by using divided "threshold detected data" as clock signal for decision making logic. The simple circuit is shown in Figure 3.16. No decision is made when there is no threshold detected data initially. In this way, the harmonic locking problem is eliminated during circuit start-up. It could also make sure SAR decision making logic has a 4 times slower clock than the other circuit. This is crucial for DLL, because every decision should be made based on circuit fully responded state.

Figure 3.16. Clock signal generation for SAR decision making logic.

The DLL delay resolution is about 0.2 ns. After this DLL is locked, the signal "pre-clock output" comes about 5 ns earlier than "data", "post-clock output" arriving about 10 ns later than "data". These two signals could generate a time window with an edge combiner to enable LNA to operate intermittently. If this window is too short, the BER will be affected. If this window is too long, the power consumption will too large. Therefore, this 15 ns time window is based on the trade-off between BER performance and power consumption. To make the DLL itself low power, low supply voltage is adopted. By reducing the supply voltage from 3 V to 1 V, only one ninth of dynamic power is needed to operate this DLL. Smaller supply voltage also reduces the charging current. This indicates the value of capacitors could be decreased to generate the same delay, so area could also be smaller.

# 3.3.5 Synchronization Scheme

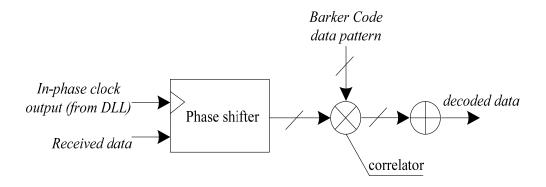

Figure 3.17. The implementation of digital back-end.

As mentioned, Barker Code is adopted in this system. A data '0' is encoded as "11100010010", while a data '1' is encoded as "00011101101". The use of

Barker Code enhances the communication reliability because the bitwise shifted version of the Barker Code has poor auto-correlation sum compared to its original version. The rising edge of the encoded data triggers the UWB pulses.

Decoding is performed in the receiver digital back-end, as shown in Figure 3.17. It incorporates a digital correlator. The received data is decoded by being correlated with Barker Code data pattern. The system declares synchronization only after three consecutive data '1's are detected with bit error rate of 2<sup>-33</sup> (every data '1' is encoded as 11-bit Barker Code).

# 3.3.6 Measurement Results

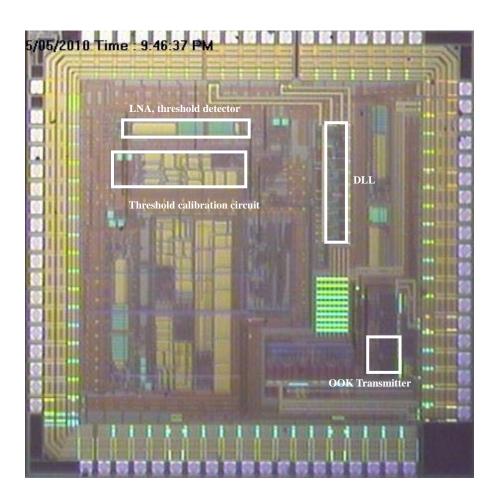

The OOK IR UWB transceiver circuit was implemented using a standard 0.35 µm CMOS technology. Its floor plan on the die photo is shown in Figure 3.18. With all-digital structure, the transmitter area is very small. It occupies an area of 0.09 mm<sup>2</sup>. The only passive component in the transmitter is the bypass capacitors. The receiver, including LNA, threshold detector, threshold calibration circuit and DLL, occupies an area of 1.2 mm<sup>2</sup>. The prototype is packaged using CQFP 80 package.

Figure 3.18. Die photo of the IR UWB transceiver.

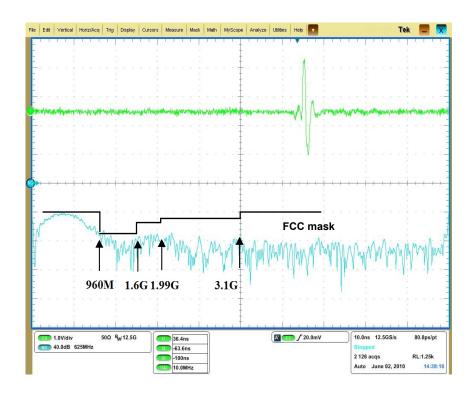

Figure 3.19. Measured transmitter output with spectrum.

The UWB transmitter is tested with Tektronix DPO71254 Digital Oscilloscope. The transmitted UWB pulse and its spectrum are shown in Figure 3.19. The FCC spectrum mask is satisfied with tunable UWB pulse width and amplitude. Its center frequency is around 500 MHz. Under a 3.3 V supply, 2.9 V<sub>PP</sub> output amplitude could be obtained as shown. It consumes about 30 μA under 3.3 V supply at 1 MHz data rate. Therefore, the transmitter achieves an energy efficiency of 100 pJ/pulse.

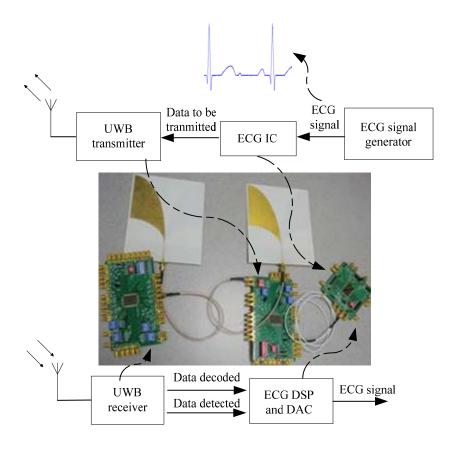

The test set up for the whole transceiver with ECG recording interface is shown in Figure 3.20. An ECG signal generator sends the cardiac waveforms to ECG recording circuit. After amplifying, digitizing and processing these signals, the ECG recording circuit generates digital TX input data for UWB transmitter.

Figure 3.20. UWB transceiver testing.

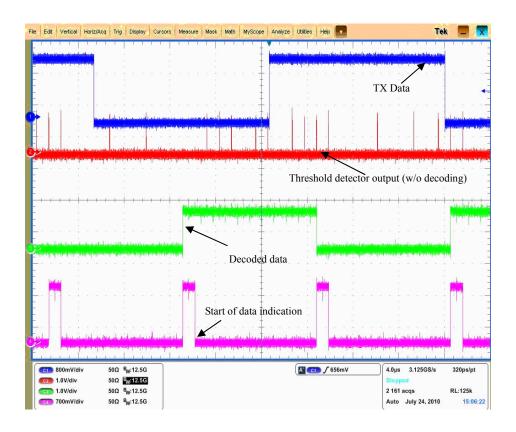

The transceiver system is tested wirelessly in office environment. The receiver main points testing results are shown in Figure 3.21. The data from ECG output is first encoded with Barker Code in the pulse generator. After receiver antenna and LNA, the threshold detected signals are shown as narrow pulses. Due to the limited IO pin number, the LNA is not tested separately. We could see the modulated data pattern in the threshold detector output (w/o decoding), i.e., data '0' being encoded as "11100010010" and data '1' being encoded as "00011101101".

Figure 3.21. Receiver testing results.

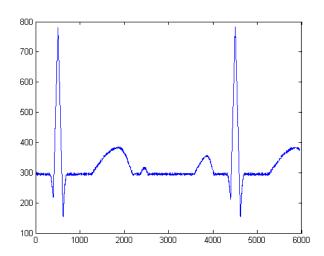

After the receiver digital back-end decoding, the transmitted data is recovered. The start of data indication is used for communication interface with the following ECG chip which could processes the RX data. Figure 3.22 shows the Matlab reconstructed ECG waveform from collected RX data of 25 cm wireless reception. By comparing the decoded RX data with TX data, BER could be calculated.

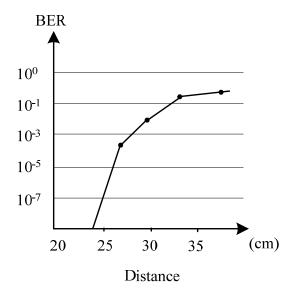

The measured BER performance is shown in Figure 3.23. Within 25 cm antenna distance in office environment, there is no error bit. Smaller than 10<sup>-3</sup> BER could be achieved if the communication distance increases to 27 cm. If longer distance is required for communication, more amplification stages should be designed to compensate the path loss. The receiver consumes 0.6

mW under intermittent operation at 1 Mbps. The measured receiver sensitivity is -53 dBm when the BER is below  $10^{-3}$  at 1 MHz data rate and communication distance of 25 cm.

Figure 3.22. Reconstructed ECG waveform from RX data.

Figure 3.23. The measured BER performance.

#### 3.3.7 Comparison with other recent works

Table 3.1 Comparison with other recent transmitter works

| Transmitter                                              | [43]              | [44]       | [45]      | This work |

|----------------------------------------------------------|-------------------|------------|-----------|-----------|

| Tech. (µm)                                               | CMOS 0.15         | CMOS 0.18  | CMOS 0.18 | CMOS 0.35 |

| Supply (V)                                               | 1                 | 1.8        | 1.8       | 3.3       |

| Power (mW)                                               | <0.001@<br>25kbps | 0.3@ 1Mbps |           | 0.1@1Mbps |

| Energy efficiency (pJ/pulse)                             | <40               | 300        | 27        | 100       |

| Output amplitude (V <sub>PP</sub> )                      | 0.7               | 1.6        | 0.6       | 2.9       |

| Peak-peak output<br>voltage/ Energy<br>efficiency (V/pJ) | >1.75%            | 0.53%      | 2.22%     | 2.9%      |

| Modulation                                               | BPSK              | OOK        | DPSK      | OOK       |

Table 3.1 shows the performance summary of proposed UWB transmitter and its comparison with other recently published CMOS UWB transmitters operating in 0-960 MHz. All these transmitters adopt digital structure. Work [44] consumes the highest power of 0.3 mW at 1 Mbps data rate, because its pulse width is as wide as 2 ns and it transmits differential signal to antenna. Work [43] consumes less power due to smaller amplitude of about 0.7 V<sub>PP</sub>. Work [45] gets output amplitude of 0.13 to 0.6 V<sub>PP</sub> with 23 μW to 74 μW power consumption. Higher peak to peak output voltage is desirable because it indicates higher output power and longer communication range. Therefore, to make a fair comparison, both energy efficiency and output voltage should be considered. Our work achieves the best results, when the peak to peak output voltage over energy efficiency is compared. Among these designs, this work is the simplest in structure and achieves the highest output pulse amplitude with medium power consumption.

The down-scaling improves the transistor speed for RF requirement. The advanced technology provides higher f<sub>T</sub> and smaller parasitic for the transistors, so good energy efficiency could typically be achieved. On the other hand, it deteriorates the achievable output power due to the voltage headroom reduction and reliability concern.

The receiver performance summary and comparison with other recent sub 1 GHz receivers are shown in Table 3.2. Both work [44] and this work intermittently operate LNA, thus consuming much lower power than work [43]. The static power is as large as 1.7 mW in [43], so we can expect a lot of power reduction by intermittent operation. This comparison shows that UWB transceiver could be duty cycled and a lot of power could be saved in this way. It is its architectural advantage. Work [44] consumes low power of 0.3 mW at 1 Mbps data rate, as half small as power consumption in this work, due to the use of more advanced technology and smaller time window for intermittent operation.

Table 3.2 Comparison with other receiver works

| Receiver                     | [43]       | [44]      | This work |

|------------------------------|------------|-----------|-----------|

| Tech. (µm)                   | CMOS 0.15  | CMOS 0.18 | CMOS 0.35 |

| Supply (V)                   | 1          | 1.8       | 3.5       |

| Power (mW)                   | 1.9@25kb/s | 0.3@1Mb/s | 0.6@1Mb/s |

| Energy efficiency (pJ/pulse) | 1900       | 300       | 600       |

# CHAPTER 4 3-5 GHZ UWB BEAMFORMING TRANSMITTER

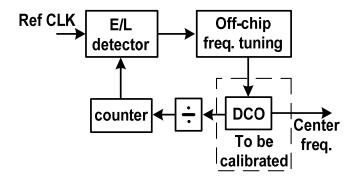

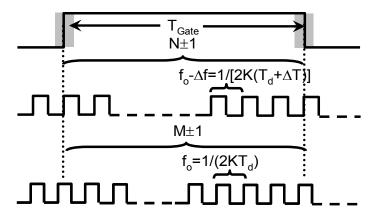

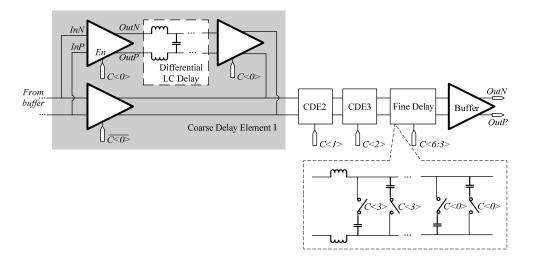

Based on the literature review on various beamforming architectures discussed in Chapter 2, beamforming transmitter with baseband digital true time delay element is adopted here for its small area and potential high energy efficiency. To overcome the delay resolution and power trade-off, we have proposed the use of Vernier delay line to achieve relative delay rather than absolute delay. This eliminates the trade-off involving delay resolution and power. We also proposed the use of  $\Delta\Sigma$  DLL and SAR DLL to achieve the desired frequency and delay calibration. The details of the proposed 4-channel 3-5 GHz UWB beamformer will be discussed next.

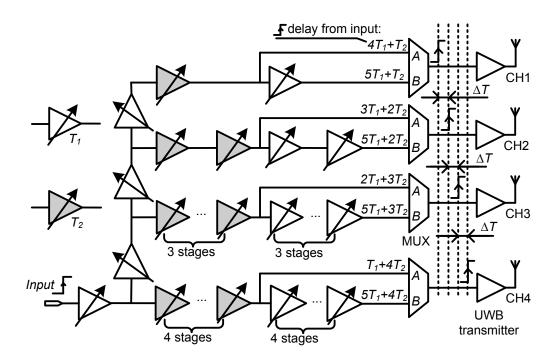

# 4.1. The Proposed UWB Beamforming Transmitter System

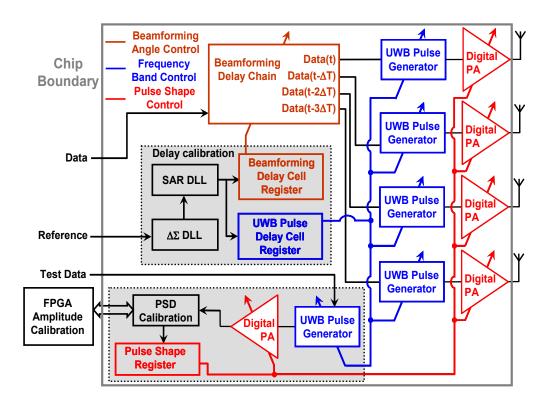

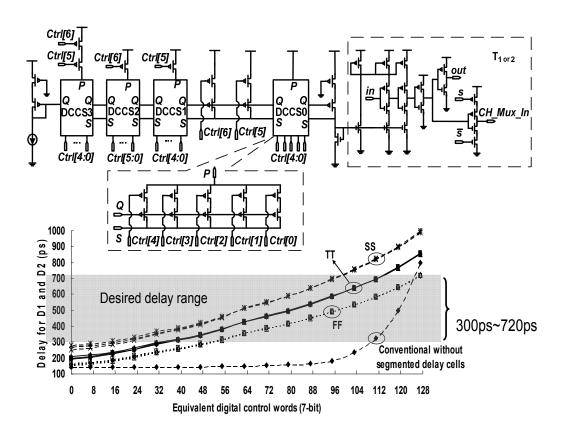

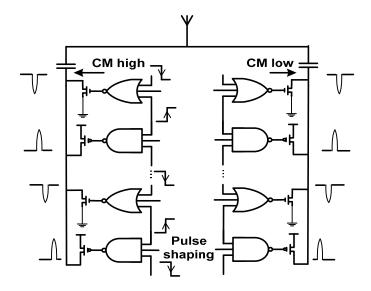

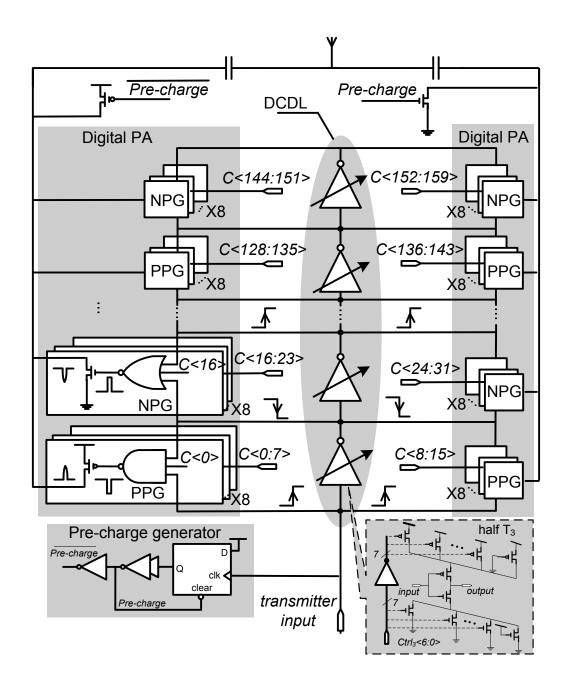

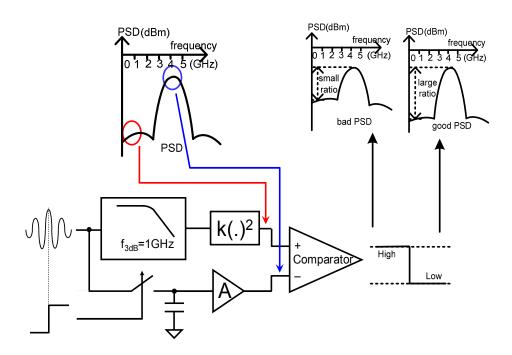

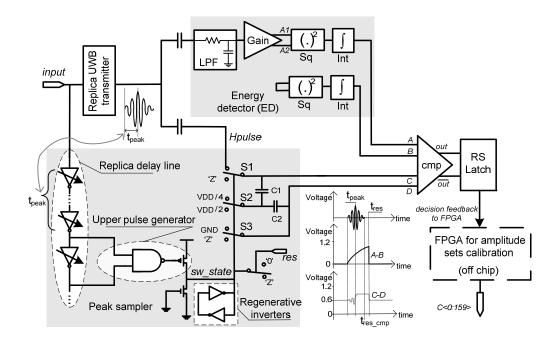

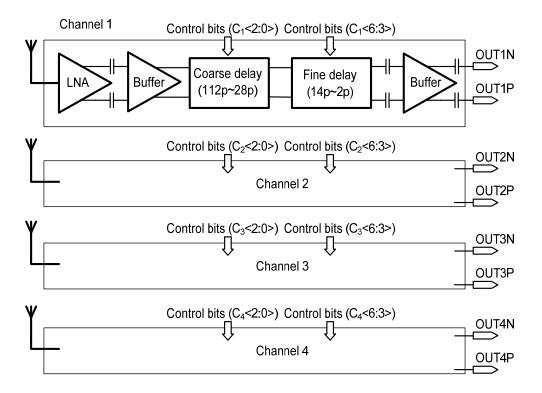

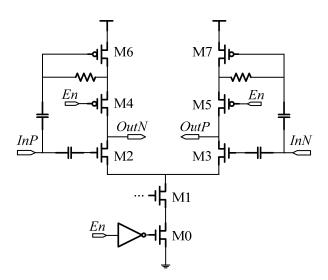

As shown in Figure 4.1, the proposed system consists of beamforming delay chain, four identical all-digital UWB transmitters, delay calibration circuit, and Power Spectral Density Calibration (PSDC) circuit. The baseband TX data is first delayed by the beamforming delay chain to generate equal path delay difference between adjacent channels. The delayed input edges in each path will then trigger the UWB transmitter to generate UWB pulses. There is also a digitally controlled inverter based delay line determining the UWB pulse center frequency. Local edge combining method is proposed to lower the power consumption. To minimize the static power consumption and increase the transmitter energy efficiency, fully digital delay cells are employed in this work. In order to obtain accurate path delay and UWB pulse center frequency,

these digital delay cells are calibrated by  $\Delta\Sigma$  DLL together with SAR DLL. Pulse shaping is also provided through eight levels amplitude tuning to achieve the desired UWB spectrum. A PSDC is also incorporated to provide automatic spectrum tuning to meet the desired UWB spectrum mask.

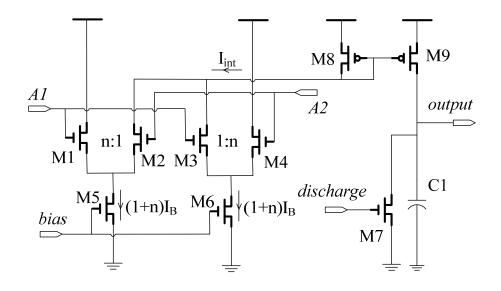

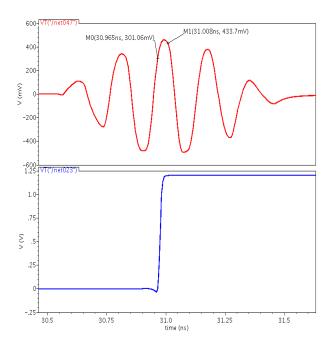

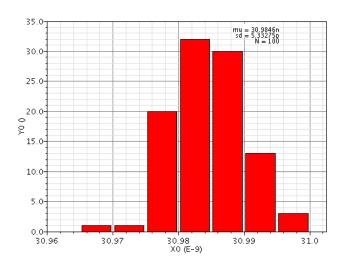

Figure 4.1. The proposed system architecture.

Based on the UWB beamforming analysis in Chapter 1, to achieve a fine scanning resolution, a small delay step is needed. To have a wide scanning range, a large delay range is required for certain antenna space. Our system chose 18 cm antenna space for testing. This antenna spacing is selected to make a fair comparison with other works. Fine delay resolution is desirable on two aspects. Firstly, it gives rise to small scanning resolution which is important for localization. Given a transmission radius of 2 m, 1° scanning resolution will correspond to 3.5 cm scanning range. If 10° scanning resolution is used, the scanning range degrades to about 35 cm. Secondly, the

small delay resolution can be traded off with smaller antenna spacing to achieve a given scanning resolution. For example, if the scanning resolution of 3° can be used, a 10 ps delay resolution will only require antenna spacing of 6 cm, which results in more compact UWB beamforming system. In the following subsection, we will discuss our proposed solution to achieve such a challenging specification.

#### 4.1.1. Delay Generation

Of the whole system structure, beamforming delay chain is the most crucial part. To generate 1° phase resolution at 18 cm antenna space, the delay step should be as small as 10 ps. To increase the scanning angle as large as 90°, the delay range should be as large as 600 ps.

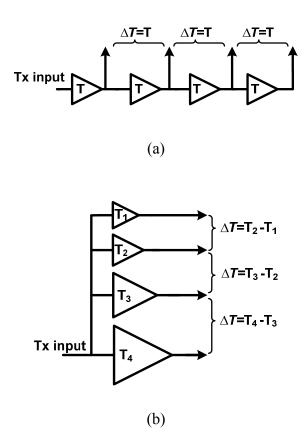

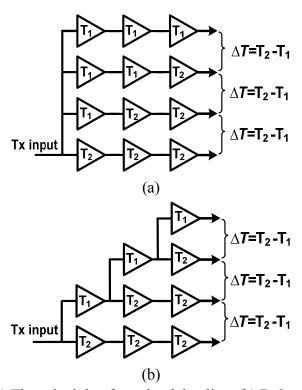

Figure 4.2. (a) Absolute delay generation. (b) Relative delay generation.

There are various ways of creating identical delay difference between each path. In references [11], [23] and [46], the delay difference is generated through cascading the delay cells in series like Fig. 4.2 (a). Simple delay matching and calibration will be achieved, because there is only one kind of delay cell. However, it is difficult to have one delay cell covering delay range from 0 to 600 ps with 10 ps delay step. In addition, to achieve the small delay region, excessive power would be required which will reduce the transmitter energy efficiency. An alternative approach is to connect the delay cell with different sizing in parallel as shown in Figure 4.2 (b). As the path delay is generated by relative delay difference, i.e.  $\Delta T = T_2 - T_1 = T_3 - T_2 = T_4 - T_3$ , the delay cell design can be much relaxed with smaller power consumption. However, adopting four different delay cells in the design will complicate the path matching and calibration. Therefore, there is a trade-off between delay resolution and path matching for these delay architectures.

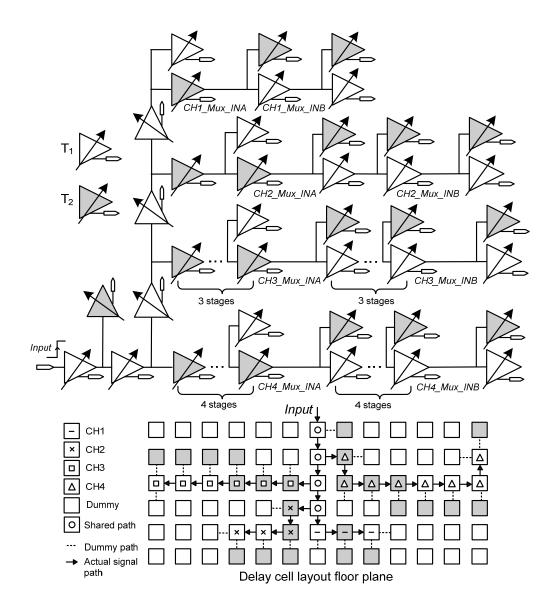

Figure 4.3. (a) The principle of vernier delay line. (b) Delay cells sharing.