## REAL-TIME MONITORING AND CONTROL OF CRITICAL DIMENSIONS IN LITHOGRAPHY

YANG GENG

A THESIS SUBMITTED

FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

DEPARTMENT OF ELECTRICAL AND COMPUTER

ENGINEERING

NATIONAL UNIVERSITY OF SINGAPORE

2012

#### DECLARATION

I hereby declare that the thesis is my original work and it has been written by me in its entirety. I have duly acknowledged all the sources of information which have been used in the thesis.

This thesis has also not been submitted for any degree in any university previously.

fr

Yang Geng

$24 \ {\rm December} \ 2012$

### Acknowledgments

I am grateful to many people for supporting me not only intellectually but also mentally and socially in my work and life besides work. These acknowledgements can only give a glimpse on how much I benefit and learn from all my mentors, colleagues, friends, and family. Thanks so much to all of you.

First of all, I wish to express my sincere gratitude to my supervisor Assoc. Prof. Arthur Tay, who supplies me with invaluable advice and guidance throughout my time at university concerning my research, writing, organization, and life. His insights in the semiconductor process control are always stimulating and many chapters of this thesis are shaped by the numerous discussions between us.

I also would like to thank my friends and colleagues who are working in the Advance Control Technology Lab. Their friendship, advice and encouragement make my experience at National University of Singapore unforgettable in my life. Special thanks are going to my parents and my wife for their companion and love. I would have never reached so far without their constant encouragement and support.

## Contents

| Acknow              | wledgn | nents                                               | i   |

|---------------------|--------|-----------------------------------------------------|-----|

| Summa               | ary    |                                                     | vi  |

| List of             | Table  | s                                                   | vii |

| List of             | Figure | es v                                                | iii |

| List of             | Acron  | nyms x                                              | iv  |

| List of Symbols xvi |        |                                                     | vi  |

| Chapte              | er 1 I | ntroduction                                         | 1   |

| 1.1                 | Motiva | ation                                               | 1   |

| 1.2                 | Review | w of Process Control for Lithography                | 7   |

|                     | 1.2.1  | Statistical process control                         | 8   |

|                     | 1.2.2  | Run-to-run control                                  | 9   |

|                     | 1.2.3  | Real-time control                                   | 10  |

| 1.3                 | Contri | ibution                                             | 11  |

|                     | 1.3.1  | Modelling and real-time control of multi-zone ther- |     |

|                     |        | mal system                                          | 11  |

|     |      | 1.3.2    | Ellipsometry equipment design and application                                                   | 12 |

|-----|------|----------|-------------------------------------------------------------------------------------------------|----|

|     |      | 1.3.3    | Dual-zone spatial CD in-situ real-time control through                                          |    |

|     |      |          | the PEB process                                                                                 | 13 |

|     |      | 1.3.4    | Feedforward/Feedback control framework for lithog-                                              |    |

|     |      |          | raphy process                                                                                   | 14 |

| 1   | .4   | Organ    | ization of the Thesis                                                                           | 15 |

| Cha | ιpte | er 2 I   | Dual-Zone Programmable Thermal Baking Sys-                                                      |    |

| t   | em   |          |                                                                                                 | 17 |

| 2   | 2.1  | Introd   | luction                                                                                         | 17 |

| 2   | 2.2  | Therm    | nal Modelling of the System                                                                     | 20 |

|     |      | 2.2.1    | System modelling                                                                                | 20 |

|     |      | 2.2.2    | Model verification                                                                              | 26 |

| 2   | 2.3  | Real-t   | ime Wafer Temperature Spatial Control                                                           | 31 |

|     |      | 2.3.1    | Experiment setup and control structure                                                          | 31 |

|     |      | 2.3.2    | Experimental result                                                                             | 35 |

| 2   | 2.4  | Conclu   | usion $\ldots$ | 44 |

| Cha | ıpt€ | er 3 S   | pectroscopic Ellipsometry Equipment Design and                                                  | l  |

| A   | 4pp  | olicatio | on                                                                                              | 46 |

| 3   | 8.1  | Introd   | luction                                                                                         | 46 |

| 3   | 8.2  | System   | n Modelling                                                                                     | 48 |

|     |      | 3.2.1    | Characterization of the PEB process                                                             | 48 |

|     |      | 3.2.2    | Working principle of the ellipsometry $\ldots \ldots \ldots$                                    | 50 |

| 3   | 3.3  | Equip    | ment Setup                                                                                      | 56 |

|               | 3.3.1    | Programmable thermal bake-plate                                                                 | 57  |

|---------------|----------|-------------------------------------------------------------------------------------------------|-----|

|               | 3.3.2    | Spectroscopic ellipsometer                                                                      | 59  |

|               |          | 3.3.2.1 Single probe spectroscopic ellipsometer                                                 | 59  |

|               |          | 3.3.2.2 Dual-probe spectroscopic ellipsometer                                                   | 61  |

| 3.4           | Exper    | rimental Results and Discussions                                                                | 61  |

| 3.5           | Concl    | usion                                                                                           | 68  |

| Chapt         | er 4 l   | Dual-Zone Real-Time Monitoring and Control of                                                   |     |

| $\mathbf{Cr}$ | itical D | Dimensions                                                                                      | 70  |

| 4.1           | Introd   | luction                                                                                         | 70  |

| 4.2           | Meası    | rement of CD Latent Image                                                                       | 72  |

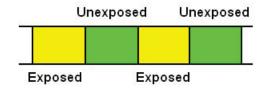

|               | 4.2.1    | Approach with RCWA                                                                              | 73  |

|               | 4.2.2    | Model verification                                                                              | 75  |

|               | 4.2.3    | Extraction of CD latent image profile from spectro-                                             |     |

|               |          | scopic ellipsometry measurement                                                                 | 79  |

| 4.3           | Contr    | ol Framework and Experimental Results                                                           | 81  |

|               | 4.3.1    | Control framework                                                                               | 81  |

|               | 4.3.2    | Experimental results and discussion                                                             | 86  |

| 4.4           | Concl    | usion $\ldots$ | 100 |

| Chapt         | er 5 H   | Feedforward/Feedback Control Framework for the                                                  |     |

| Lit           | hograp   | bhy Process                                                                                     | 101 |

| 5.1           | Introd   | luction                                                                                         | 101 |

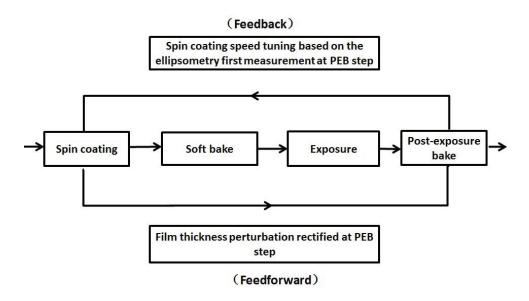

| 5.2           | Desig    | n of Control Framework                                                                          | 104 |

|               | 5.2.1    | Framework architecture                                                                          | 104 |

|               |          |                                                                                                 |     |

|     | 5.2.2 Module characterization        | 105 |

|-----|--------------------------------------|-----|

|     | 5.2.3 Control algorithm              | 108 |

| į   | Experimental Results and Discussions | 110 |

| ţ   | Conclusion                           | 115 |

|     |                                      |     |

| Cha | er 6 Conclusion                      | 117 |

| (   | Summary                              | 117 |

| (   | Future Works                         | 120 |

| D:L |                                      | 124 |

| B10 | graphy                               | 124 |

| Ap  | ndix                                 | 136 |

|     |                                      |     |

| Au  | or's Publications                    | 145 |

### Summary

Lithography is a key enabler accounting for a third of IC manufacturing costs. Critical dimension (CD) is the most important variable in the lithography sequence affecting the speed of the circuit. Current approaches to CD control are primarily based on a run-to-run strategy due to a lack of insitu sensors and control authority. In this thesis, we proposed an approach to conduct real-time CD monitoring and control. It is well-known that temperature has a direct effect on CD. First, a multi-zone programmable thermal processing system is developed, which is able to control the wafer temperature uniformity during the entire thermal cycle. Next, an in-situ ellipsometry system is established and integrated into the thermal process to measure the CD profile in real-time. Compared with the state of art in current semiconductor manufacturing based on a run-to-run strategy, the proposed real-time control system is capable to monitor and control the CD across wafer in real-time. Experimental results demonstrate that the real-time control system improves the across wafer CD uniformity more than 60% versus a run-to-run approach.

## List of Tables

| 1.1 | Lithography technology requirements for the next decade 5    |

|-----|--------------------------------------------------------------|

| 2.1 | Physical parameters of the thermal processing system 25      |

| 2.2 | Estimated air gap thickness and wafer warpage using the      |

|     | real-time control method with the proximity pin height of    |

|     | 210 $\mu$ m                                                  |

| 2.3 | Comparison between conventional baking, steady-state ap-     |

|     | proach and real-time approach                                |

| 3.1 | Experiment design 64                                         |

| 4.1 | CD latent image profile characterizations 80                 |

| 4.2 | Thermal coupling analysis                                    |

| 4.3 | Temperature variation vs Power input variation               |

| 5.1 | Thin film thicknesses with different spin speeds             |

| 5.2 | Bottom positions of signatures with respect to the different |

|     | film thicknesses                                             |

| 5.3 | Tuning performed at the spin coating step                    |

# List of Figures

| 1.1 | Transistor density and minimum feature [2]                        | 2  |

|-----|-------------------------------------------------------------------|----|

| 1.2 | Microlithography sequence                                         | 3  |

| 1.3 | Source of CD variation [5]                                        | 5  |

| 2.1 | Schematic diagram of the thermal processing system                | 21 |

| 2.2 | Photo of the thermal processing system                            | 21 |

| 2.3 | Open loop step responses for the 8-inch bake-plate. The           |    |

|     | bake-plate center and edge temperatures during the baking         |    |

|     | process are shown in subplots (a) and (b), respectively           | 28 |

| 2.4 | Plate and wafer temperature in simulation and experiment          |    |

|     | with air gap thickness be 140 $\mu m$ using the calculated model. |    |

|     | The bake-plate center temperatures, bake-plate edge tem-          |    |

|     | peratures, wafer center temperatures, and wafer edge tem-         |    |

|     | peratures during the baking process are shown in subplots         |    |

|     | (a), (b), (c) and (d), respectively. $\ldots$                     | 30 |

| 2.5 | Air gap estimation for conventional baking with 140 $\mu {\rm m}$ |    |

|     | proximity pins                                                    | 31 |

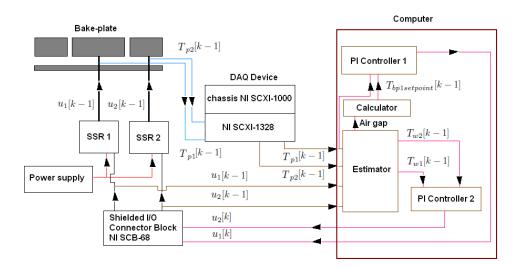

| 2.6  | Block diagram of the control systems framework, where $\boldsymbol{k}$         |    |

|------|--------------------------------------------------------------------------------|----|

|      | indicates the state, $T_{bp1setpoint}$ , $T_{w1}$ and $T_{w2}$ are the desired |    |

|      | plate reference temperature in center zone based on the esti-                  |    |

|      | mated air gaps, the estimated wafer temperatures in center                     |    |

|      | and edge zones, respectively                                                   | 34 |

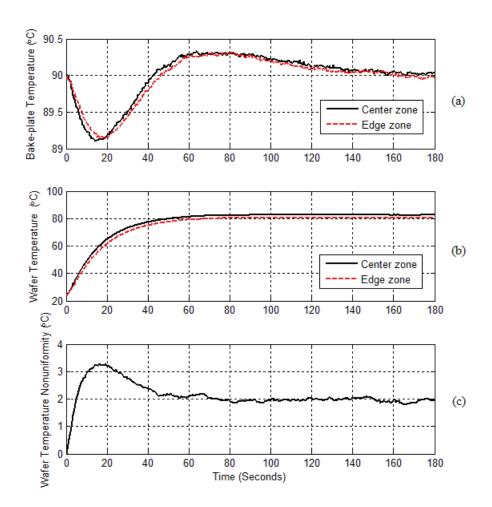

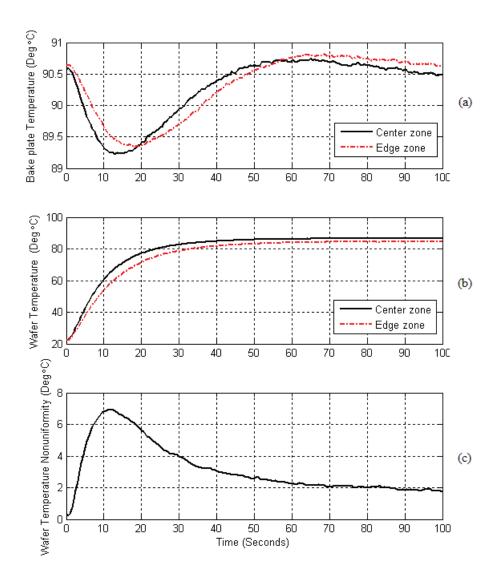

| 2.7  | Temperature profile of bake-plate and wafer for conventional                   |    |

|      | baking when a flat wafer is dropped on bake-plate with prox-                   |    |

|      | imity pin height of 210 $\mu \mathrm{m}.$ The bake-plate temperatures,         |    |

|      | wafer temperatures, and wafer temperature nonuniformity                        |    |

|      | during the baking process are shown in subplots (a), (b),                      |    |

|      | and (c), respectively. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$   | 36 |

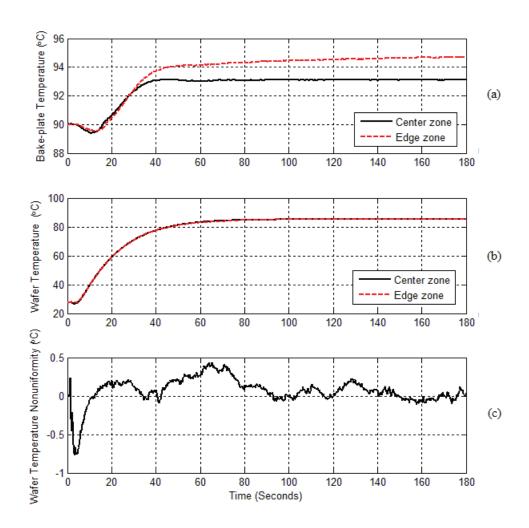

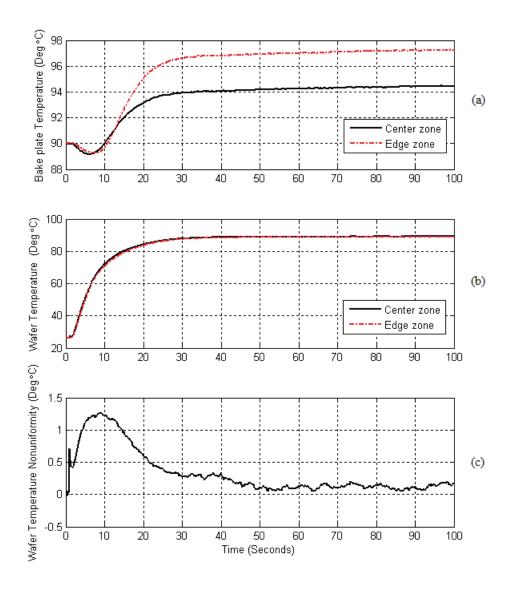

| 2.8  | Temperature profile of bake-plate and wafer for real-time                      |    |

|      | control method when a flat wafer is dropped on bake-plate                      |    |

|      | with proximity pin height of 210 $\mu \mathrm{m}.$ The bake-plate tem-         |    |

|      | peratures, wafer temperatures, and wafer temperature nonuni-                   |    |

|      | formity during the baking process are shown in subplots (a),                   |    |

|      | (b), and (c), respectively                                                     | 38 |

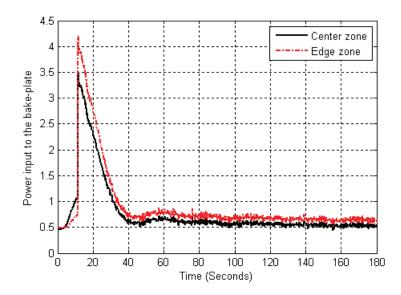

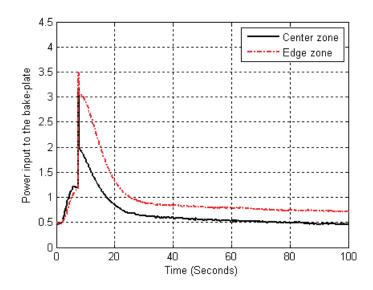

| 2.9  | Power inputs to bake-plate center and edge zones for real-                     |    |

|      | time control method when a flat wafer is dropped on bake-                      |    |

|      | plate with proximity pin height of 210 $\mu$ m                                 | 39 |

| 2.10 | Schematic of warpage setup                                                     | 40 |

2.11 Temperature profile of bake-plate and wafer for conventional baking when a wafer with center-to-edge warpage of 70 μm is dropped on bake-plate with proximity pin height of 210 μm. The bake-plate temperatures, wafer temperatures, and wafer temperature nonuniformity during the baking process are shown in subplots (a), (b), and (c), respectively. . . . . .

42

2.12 Temperature profile of bake-plate and wafer for real-time control method when a wafer with center-to-edge warpage of 70 μm is dropped on bake-plate with proximity pin height of 210 μm. The bake-plate temperatures, wafer temperatures, and wafer temperature nonuniformity during the baking process are shown in subplots (a), (b), and (c), respectively. . . 43

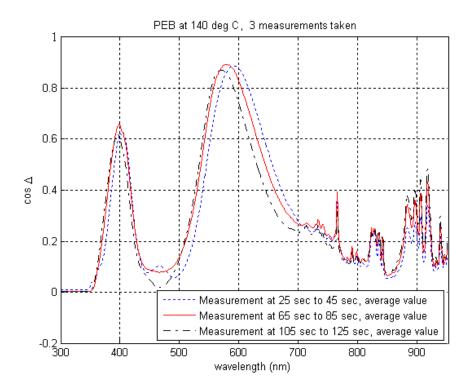

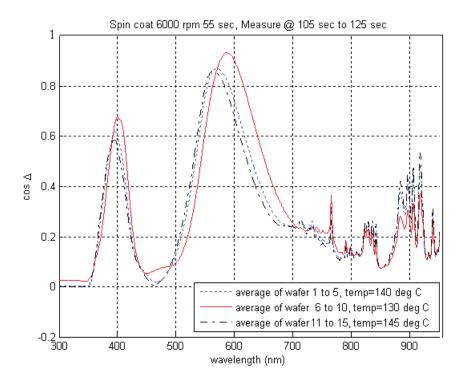

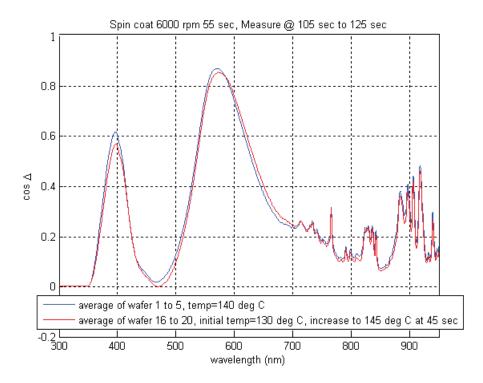

#### 2.13 Power inputs to bake-plate center and edge zones for realtime control method when a wafer with center-to-edge warpage of 70 $\mu$ m is dropped on bake-plate with proximity pin height 44 3.1523.2583.3 Single probe spectroscopic ellipsometer setup . . . . . . . 60 3.4623.5Dual-probe spectroscopic ellipsometer setup 63 Thermal effect for PEB bake at 140°C ..... 3.6653.7Thermal effect with baking temperature for PEB, measured 66

| 3.8  | Thermal effect with the change of baking temperature in the        |    |

|------|--------------------------------------------------------------------|----|

|      | middle                                                             | 67 |

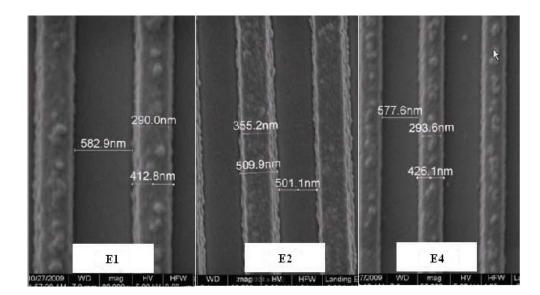

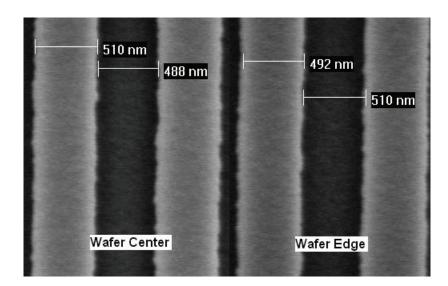

| 3.9  | SEM result                                                         | 68 |

| 4.1  | CD latent image grating structure                                  | 73 |

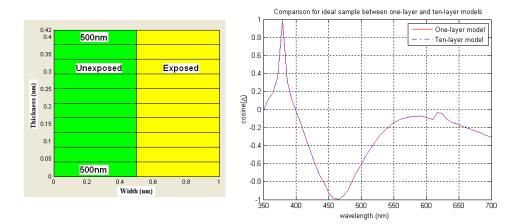

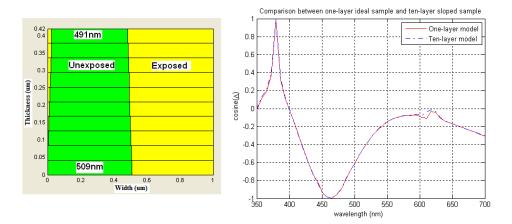

| 4.2  | Comparison between one-layer and ten-layer models for an           |    |

|      | ideal unslanted sample                                             | 76 |

| 4.3  | Comparison between the ideal unslanted sample in one-layer         |    |

|      | model and the sloped sample in ten-layer model $\ . \ . \ .$ .     | 76 |

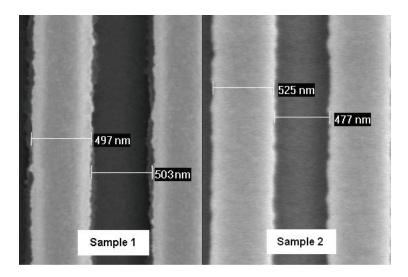

| 4.4  | Post-development DICD SEM verification                             | 77 |

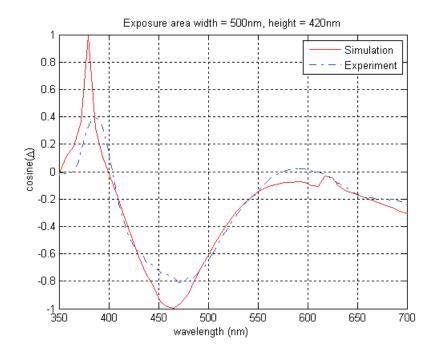

| 4.5  | Simulation and experimental results for $500 \text{ nm CD}$ latent |    |

|      | image profile with 420 nm thickness                                | 78 |

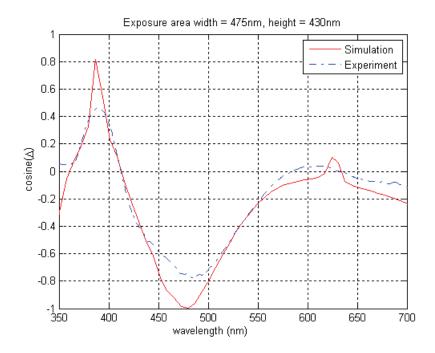

| 4.6  | Simulation and experimental results for $475 \text{ nm CD}$ latent |    |

|      | image profile with 430 nm thickness                                | 78 |

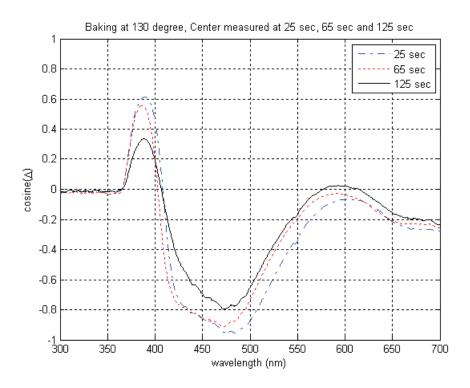

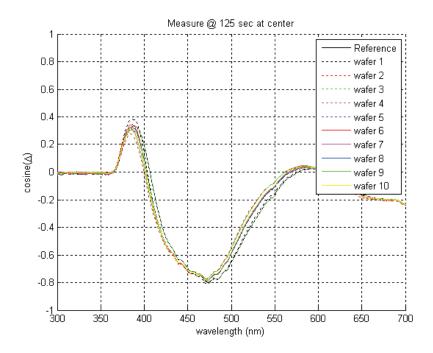

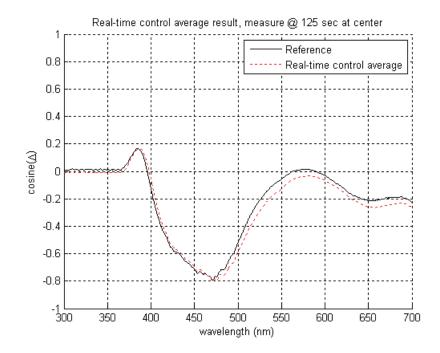

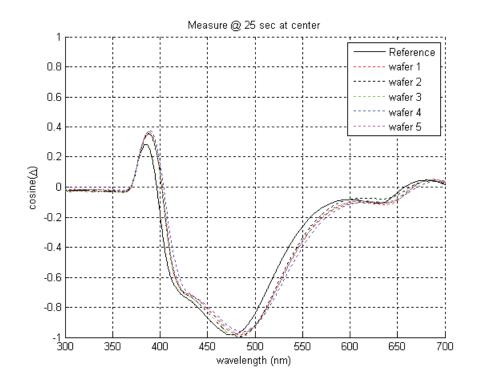

| 4.7  | Inline measured cosine signatures through PEB                      | 81 |

| 4.8  | CD latent image profile variations throughout the PEB process      | 82 |

| 4.9  | The scheme of the real-time control approach $\ldots$              | 83 |

| 4.10 | Open loop step responses for the 4-inch bake-plate. The            |    |

|      | bake-plate center and edge temperatures during the baking          |    |

|      | process are shown in subplots (a) and (b), respectively            | 89 |

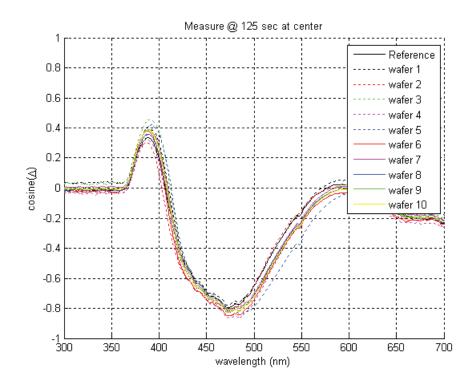

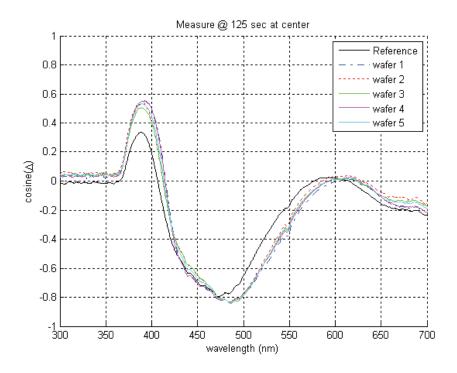

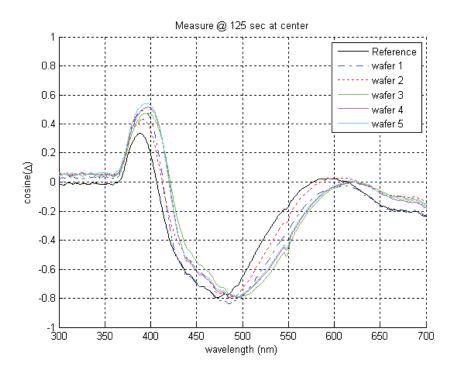

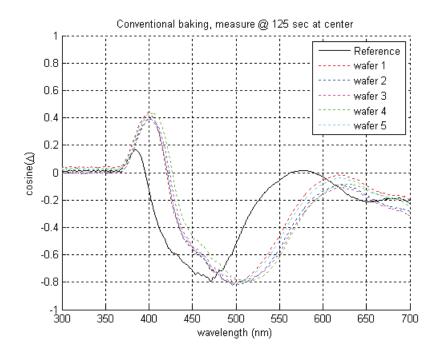

| 4.11 | The cosine signatures of conventional baking for PEB at $130$      |    |

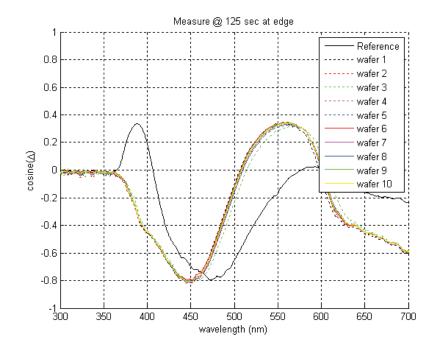

|      | °C for 125 sec at the wafer center $\ldots$                        | 90 |

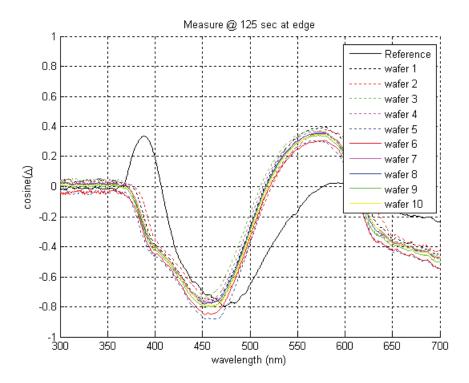

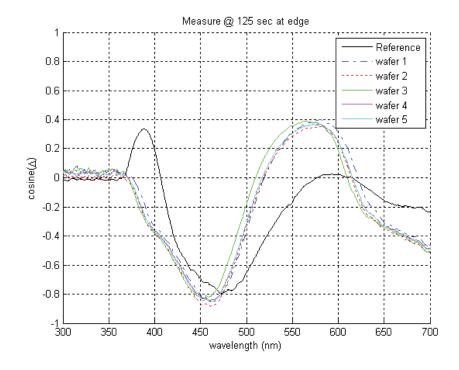

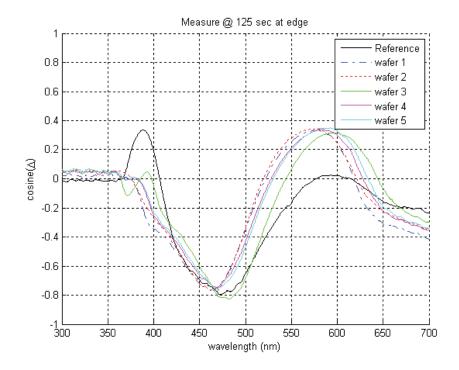

| 4.12 | The cosine signatures of conventional baking for PEB at $130$      |    |

|      | $^{\circ}$ C for 125 sec at the wafer edge $\ldots$                | 90 |

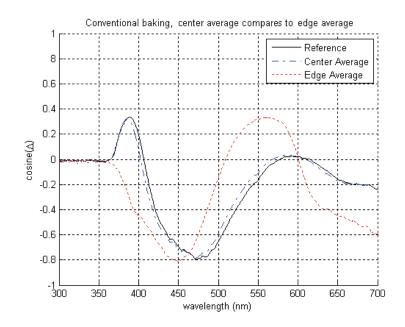

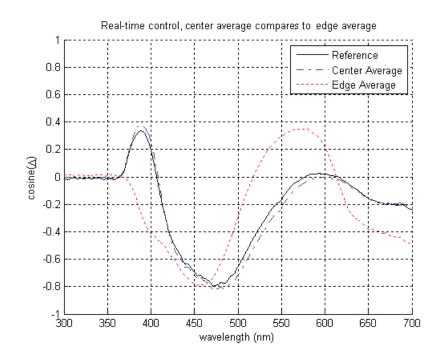

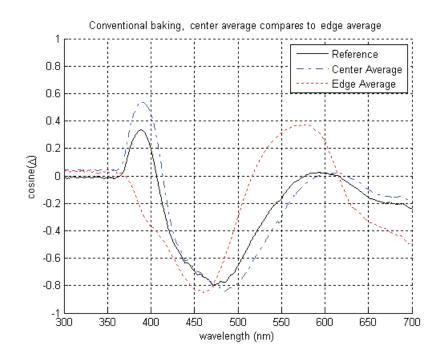

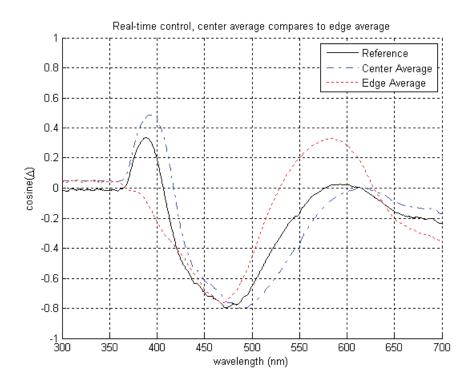

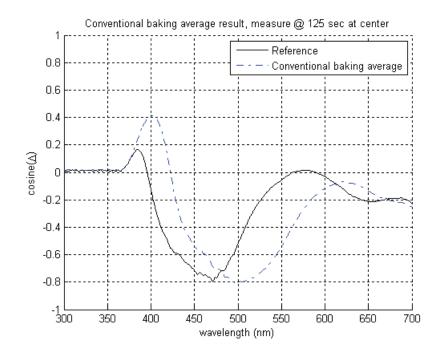

| 4.13 | Averaged cosine signatures of conventional baking for PEB                                        |    |

|------|--------------------------------------------------------------------------------------------------|----|

|      | at 130 °C for 125 sec $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$    | 91 |

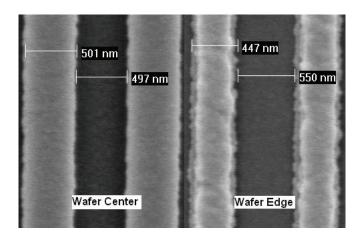

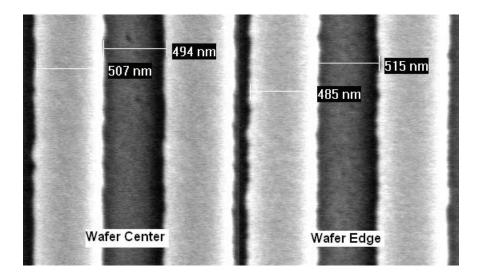

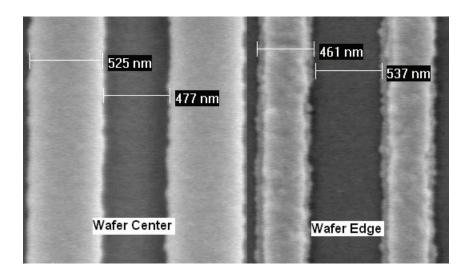

| 4.14 | SEM results for the conventional baking at 130 $^{\circ}\mathrm{C}$ for 125 sec                  | 91 |

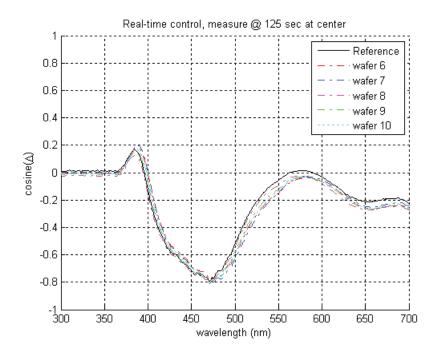

| 4.15 | Cosine signatures for in-situ real-time control through the                                      |    |

|      | PEB process at the wafer center                                                                  | 92 |

| 4.16 | Cosine signatures for in-situ real-time control through the                                      |    |

|      | PEB process at the wafer edge                                                                    | 93 |

| 4.17 | Averaged cosine signatures for in-situ real-time control through                                 |    |

|      | the PEB process                                                                                  | 94 |

| 4.18 | SEM results of the real-time temperature control through                                         |    |

|      | the PEB process                                                                                  | 94 |

| 4.19 | Cosine signatures of conventional baking for PEB at 130 $^{\circ}\mathrm{C}$                     |    |

|      | for 125 sec with spin coating at 5500 rpm at the wafer center                                    | 96 |

| 4.20 | Cosine signatures of conventional baking for PEB at 130 $^{\circ}\mathrm{C}$                     |    |

|      | for 125 sec with spin coating at 5500 rpm at the wafer edge .                                    | 96 |

| 4.21 | Averaged cosine signatures of conventional baking for PEB                                        |    |

|      | at 130 °C for 125 sec with spin coating at 5500 rpm                                              | 97 |

| 4.22 | SEM results for conventional baking at 130 $^{\circ}\mathrm{C}$ for 125 sec                      |    |

|      | with spin coating at 5500 rpm                                                                    | 97 |

| 4.23 | Cosine signatures for in-situ real-time control through the                                      |    |

|      | PEB process with spin coating at 5500 rpm at the wafer $% \left( {{{\rm{T}}_{{\rm{T}}}} \right)$ |    |

|      | center                                                                                           | 98 |

| 4.24 | Cosine signatures for in-situ real-time control through the                                      |    |

|      |                                                                                                  | 00 |

PEB process with spin coating at 5500 rpm at the wafer edge  $\ 98$

| 4.25 | Averaged cosine signatures for in-situ real-time control through            |

|------|-----------------------------------------------------------------------------|

|      | the PEB process with spin coating at 5500 rpm $\ldots \ldots 99$            |

| 4.26 | SEM results of the real-time temperature control for $125 \text{ sec}$      |

|      | with spin coating at 5500 rpm                                               |

| 5.1  | Architecture of the framework                                               |

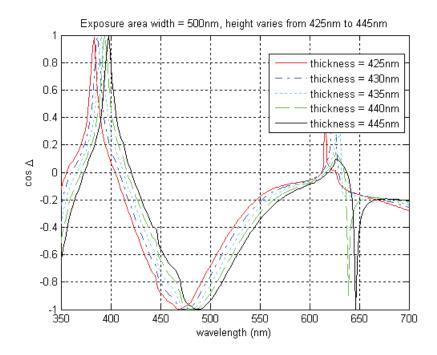

| 5.2  | Signature variations with respect to the photoresist thicknesses 109        |

| 5.3  | Cosine signature comparison for PEB at 130 $^{\circ}\mathrm{C}$ for 125 sec |

|      | with spin coating at 5800 rpm                                               |

| 5.4  | Average cosine signature comparison for PEB at 130 $^{\circ}\mathrm{C}$ for |

|      | 125 sec with spin coating at 5800 rpm 112                                   |

| 5.5  | Cosine signature comparison for in-situ real-time control through           |

|      | the PEB process with spin coating at 5800 rpm 113                           |

| 5.6  | Average cosine signature comparison for in-situ real-time                   |

|      | control through the PEB process with spin coating at $5800$                 |

|      | rpm                                                                         |

| 5.7  | Comparison of signatures between the in-situ measurements                   |

|      | and reference at 25 sec of PEB step                                         |

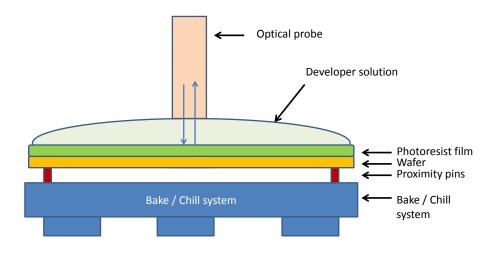

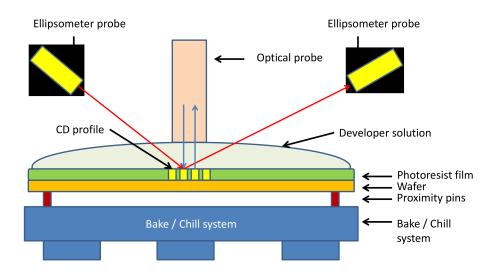

| 6.1  | Schematic diagram of the bake / chill system and the spec-                  |

|      | trometry probe                                                              |

| 6.2  | Schematic diagram of the bake / chill system, the spectrom-                 |

|      | etry probe and the ellipsometer probes                                      |

# List of Acronyms

| ADL  | Acid Diffusion Length                               |

|------|-----------------------------------------------------|

| AFM  | Atomic Force Microscopy                             |

| CD   | Critical Dimension                                  |

| CDU  | Critical Dimension Uniformity                       |

| DAQ  | Data Acquisition                                    |

| DI   | Deionized                                           |

| DICD | Develop Inspect Critical Dimension                  |

| DRAM | Dynamic Random-Access Memory                        |

| EUV  | Extreme Ultraviolet Lithography                     |

| HMDS | Hexamethyl Disilazane                               |

| IC   | Integrated Circuit                                  |

| ΙΟ   | Input/Output                                        |

| ITRS | International Technology Roadmap for Semiconductors |

| KPI  | Key Performance Indexes                             |

| LER  | Line-Edge Roughness                                 |

| MIMO | Multi-Input-Multi-Output                            |

|      |                                                     |

|      |                                                     |

- ML2 Mask Less Lithograph

- MSE Mean-Square-Error

- **NI** National Instrument

- **NIR** Near Infrared

- PAC Photoactive Compound

- **PEB** Post-exposure Bake

- PI Proportional-Integral

- ${\bf PWM} \qquad {\rm Pulse \ Width \ Modulation}$

- **RGA** Relative Gain Array

- **RTD** Resistance Temperature Detector

- R2R Run-to-Run

- RCWA Rigorous Couple-Wave Analysis

- **SEM** Scanning Electron Microscope

- **SPC** Statistical Process Control

- SSR Solid State Relay

- **TE** Transverse Electric

- **TM** Transverse Magnetic

- **UV** Ultraviolet

- VIS Visible Light

# List of Symbols

| $\alpha_0$      | thermal diffusivity of fluid                   |

|-----------------|------------------------------------------------|

| $\beta_0$       | volume thermal expansion coefficient of fluid  |

| $\Delta$        | phase shift                                    |

| $\Delta \Omega$ | change of spin speed                           |

| $\Delta T_{p1}$ | change of temperature of the bake-plate center |

| $\Delta T_{p2}$ | change of temperature of the bake-plate edge   |

| $\Delta T_{w1}$ | change of temperature of the wafer center      |

| $\Delta T_{w2}$ | change of temperature of the wafer edge        |

| $\Delta u_1$    | change of power input to the bake-plate center |

| $\Delta u_2$    | change of power input to the bake-plate edge   |

| δ               | factor constant                                |

| λ               | wavelength                                     |

| $\mu$           | kinematic viscosity                            |

| $\mu_0$         | initial kinematic viscosity                    |

| Ω               | spin speed                                     |

| $\Phi_f$        | refracted angle                                |

- $\Phi_i$  incident angle

- $\Psi$  the angle of the first diagonal of the rectangle in which the ellipse is enclosed

- $\rho$  density

- $\rho_c$  state of polarization

- $\sigma$  acid diffusion length

- $\theta$  variable angle

- $\zeta$  radiation dose

- $\zeta_{eff}$  effective dose

- A analyzer angle

- $A_0$  Arrhenius constant

- $A_e$  pre-exponential factor

- $A^{side}$  contact area between the adjacent element

- ${\cal A}_h^{bottom}$   $\,$  area of the bottom of the heater exposed to the ambient

- $A_w^{top}$  area of the wafer top exposed to the ambient

- $A_x$  analyzer matrix

- C thermal capacitance

- $C_0$  solute concentration at the free surface of the thin film

- $C_A$  concentration of species A

- $C_{ag}$  thermal capacitance of air gap

- $C_c$  thermal capacitance of cartridge

- $C_h$  thermal capacitance of heater

- $C_p$  thermal capacitance of bake-plate

| $C_w$                 | thermal capacitance of wafer                              |  |  |

|-----------------------|-----------------------------------------------------------|--|--|

| $CDVar_{bake}$        | CD variations caused by bake                              |  |  |

| $CDVar_{coat}$        | CD variations caused by spin coating                      |  |  |

| $CDVar_{develop}$     | CD variations caused by development                       |  |  |

| $CDVar_{expose}$      | CD variations caused by exposure                          |  |  |

| $CDVar_{total}$       | total CD variation                                        |  |  |

| <i>C</i> <sub>0</sub> | initial concentration of solid species in the photoresist |  |  |

| $C_{V}$               | specific heat capacity                                    |  |  |

| D                     | diffusion coefficient                                     |  |  |

| $D_0$                 | initial diffusion coefficient                             |  |  |

| $D_c$                 | decoupling matrix                                         |  |  |

| d                     | depth of fluid layer                                      |  |  |

| $E_0$                 | power of the light source                                 |  |  |

| $E_a$                 | activation energy                                         |  |  |

| $E_d$                 | field amplitude on the detector                           |  |  |

| $E_x$                 | sample matrix                                             |  |  |

| $e_1$                 | difference at the wafer center                            |  |  |

| $e_2$                 | difference at the wafer edge                              |  |  |

| $G_{bp-to-u}$         | transformation matrix between bake-plate and power input  |  |  |

| $G_{new,wfr-to-u}$    | new transformation matrix between wafer and power input   |  |  |

| $G_{wfr-to-u}$        | transformation matrix between wafer and power input       |  |  |

| g                     | acceleration of gravity                                   |  |  |

- H final coating thickness

- h convection coefficient

- $h^{top}$  wafer top convection coefficient

- $h_0$  initial thickness of fluid

- $h_1$  film thickness

- $h_c$  coating film thickness

- $h_l$  the l-th layer film thickness

- *I* intensity seen by detector

- $K_i$  integral gain

- $K_p$  proportional gain

- $K_{p1}$  real-time control constant parameter for center zone

- $K_{p2}$  real-time control constant parameter for edge zone

- k thermal conductivity

- $k_c$  rate constant of the chemical reaction

- $k_m$  mass transfer coefficient

- $k_r$  amount of absorption loss

- L effect of the lamp source

- $L_0$  characteristic length

- $l_p$  proximity pin height

- M molecular weight of the solvent

- m constant factor

- $N_r$  phase speed

- $\overline{N}_u$  Nusselt number

- n complex refractive index

- $n_1$  Cauchy coefficient

- $n_2$  Cauchy coefficient

- $n_3$  Cauchy coefficient

- *P* polarizer angle

- $P_v$  vapor pressure of the pure solvent

- $P_x$  polarizer matrix

- Pr Prandtl number

- *p* signature bottom position

- $p_r$  reference bottom position

- $q^{input}$  heater power

- $q_1$  heater power to center

- $q_2$  heater power to edge

| $q_{ag}^{bottom}$ | heat flow into the air gap element from bottom surface of air gap     |

|-------------------|-----------------------------------------------------------------------|

| $q_{ag}^{in}$     | heat flow into the air gap element from inner zone of air gap         |

| $q_{ag}^{out}$    | heat flow into the air gap element from outer zone of air gap         |

| $q_{ag}^{top}$    | heat flow into the air gap element from top surface of air gap        |

| $q_c^{bottom}$    | heat flow into the cartridge element from bottom surface of cartridge |

| $q_c^{in}$        | heat flow into the cartridge element from inner zone of cartridge     |

| $q_c^{out}$       | heat flow into the cartridge element from outer zone of cartridge     |

| $q_c^{top}$       | heat flow into the cartridge element from top surface of cartridge    |

| $q_h^{bottom}$ | heat flow into the heater element from bottom surface of heater         |

|----------------|-------------------------------------------------------------------------|

| $q_h^{in}$     | heat flow into the heater element from inner zone of heater             |

| $q_h^{out}$    | heat flow into the heater element from outer zone of heater             |

| $q_h^{top}$    | heat flow into the heater element from top surface of heater            |

| $q_p^{bottom}$ | heat flow into the bake-plate element from bottom surface of bake-plate |

| $q_p^{in}$     | heat flow into the bake-plate element from inner zone of bake-plate     |

| $q_p^{out}$    | heat flow into the bake-plate element from outer zone of bake-plate     |

| $q_p^{top}$    | heat flow into the bake-plate element from top surface of bake-plate    |

| $q_w^{bottom}$ | heat flow into the wafer element from bottom surface of wafer           |

| $q_w^{in}$     | heat flow into the wafer element from inner zone of wafer               |

| $q_w^{out}$    | heat flow into the wafer element from outer zone of wafer               |

| $q_w^{top}$    | heat flow into the wafer element from top surface of wafer              |

| $Q_T$          | total exposure dose                                                     |

| R              | universal gas constant                                                  |

| $R_x$          | rotation matrix                                                         |

| Ra             | Rayleigh number                                                         |

| r              | fluid thin film radius                                                  |

| $r_i$          | distance between the elements $i$ and $i + 1$                           |

| $r_p$          | reflectivity of TM wave                                                 |

| $r_s$          | reflectivity of TE wave                                                 |

| T              | temperature                                                             |

| $T_a$          | edge element temperature above ambient                                  |

| $T_{ag}$          | temperature of air gap above the ambient           |

|-------------------|----------------------------------------------------|

| $T_{ag1}$         | temperature of air gap center above the ambient    |

| $T_{ag2}$         | temperature of air gap edge above the ambient      |

| $T_{bp1setpoint}$ | bake-plate center set point                        |

| $T_c$             | temperature of cartridge above the ambient         |

| $T_{c1}$          | temperature of cartridge center above the ambient  |

| $T_{c2}$          | temperature of cartridge edge above the ambient    |

| $T_h$             | temperature of heater above the ambient            |

| $T_{h1}$          | temperature of heater center above the ambient     |

| $T_{h2}$          | temperature of heater edge above the ambient       |

| $T_p$             | temperature of bake-plate above the ambient        |

| $T_{p1}$          | temperature of bake-plate center above the ambient |

| $T_{p2}$          | temperature of bake-plate edge above the ambient   |

| $T_s$             | sampling time                                      |

| $T_w$             | temperature of wafer above the ambient             |

| $T_{w1}$          | temperature of wafer center above the ambient      |

| $T_{w2}$          | temperature of wafer edge above the ambient        |

| t                 | time                                               |

| $\tan \Psi$       | amplitude ratio upon reflection                    |

| u                 | control signal                                     |

| $u_1$             | control signal to center zone                      |

| $u_2$             | control signal to edge zone                        |

xxii

- $w_1$  the CD latent image linewidth

- $w_l$  the CD latent image linewidth at l-th layer

- $x_0$  mole fraction of the solvent

- z thickness

- $z_{ag,max}$  maximum air gap thickness

- $z_{ag,min}$  minimum air gap thickness

- $z_{ag1}$  air gap thickness at center zone

- $z_{ag2}$  air gap thickness at edge zone

### Chapter 1

### Introduction

#### 1.1 Motivation

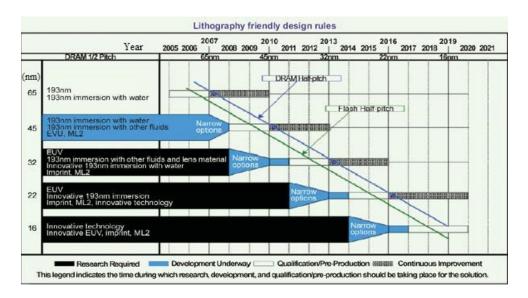

The continuing down-scaling of the transistor printed on the silicon wafer has been driven principally by the demand for the faster and larger scale integrated circuit (IC). According to the Moore's Law, the number of transistors that can be placed inexpensively on an IC increases exponentially, and it approximately doubles for every two years [1]. This law has continued for almost half a century until now and is not expected to stop for another decade at least. The trend can be clearly observed from Figure 1.1 [2].

Lithography is the most critical step for IC fabrication. It aims to transfer the pattern from the inscribed mask to the respective layer on wafer with stringent requirements for photoresist parameters and overlay control. Lithography accounts for a third of the total manufacturing costs [3]. It also acts like a technical ceiling for chip size further reduction es-

Figure 1.1: Transistor density and minimum feature [2]

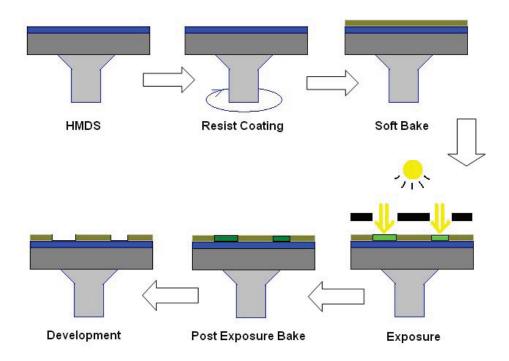

pecially when the technology advances to nanometer scale. This motivates researchers to do a lot of works in lithography process control for cost reduction and technology advancement. A typical lithography process is stated in Figure 1.2. The lithography sequence starts with a priming step to promote adhesion of the polymer photoresist material to the substrate by hexamethyl disilazane (HMDS) baking. After that, the photoresist is spun coated on the wafer substrate by using centrifugation force. Soft-bake is then conducted to evaporate the residual solvent and relax the stress of film generated by coating. Thereafter, the wafer is sent for radiation exposure through a patterned mask to create the latent image in the resist film. Once the exposure is completed, post-exposure bake (PEB) is performed to reveal those patterns latently existed in the photoresist, the bake enables the thermal activation of deprotection reaction which eliminates the dissolution inhibitor presented along the resist polymeric chain for the exposed area. After that, the lithography process comes to the last step, i.e. the development step. The exposed region becomes soluble in the developer solution and can be easily stripped away, revealing the three-dimensional resist pattern or develop inspect critical dimension (DICD).

Figure 1.2: Microlithography sequence

Critical dimension (CD) is the most important variable in lithography, defining the speed of the microprocessor. It describes the minimum half pitch resolvable for a diffraction limited optical projection system and mainly depends on the photoresist properties, equipment design, mask pattern adjustment, and process control. CD is considered so central to integrated circuit fabrication that industry calls each generation of the process after a dimension. The fact shows that the performance of an IC is highly assessed by the CD of the patterned feature on the photoresist layer. Some key performance indexes (KPI) such as gate delay and drive current are even inversely proportional to the gate length which is determined by CD. It is estimated that 1 nm CD variation in channel is equivalent to 1 MHz chip-speed variation and thus worth about \$ 7.50 in the chip's unit selling price [4]. Therefore, it is of great importance for precise monitoring and control of CD during the lithography process.

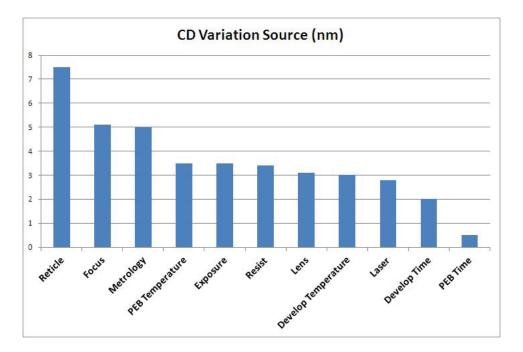

Steele et al. [5] attributed CD variations to all the process steps through lithography, which is shown in Figure 1.3. Assuming the significant variables in CD variance are independent. The combined contribution can be stated as

$$CDVar_{total}^{2} = CDVar_{coat}^{2} + CDVar_{develop}^{2} + CDVar_{bake}^{2} + CDVar_{expose}^{2} + \dots$$

(1.1)

where  $CDVar_{total}$  is the total CD variation caused by the whole process,  $CDVar_{coat}$ ,  $CDVar_{develop}$ ,  $CDVar_{bake}$ , and  $CDVar_{expose}$  are the CD variations caused by spin coating, development, bake, and exposure steps, respectively.

The down-scaling of the transistor size for the next decade is summarized in Table 1.1 by International Technology Roadmap for Semiconductors (ITRS) [2]. It shows approximate 30% CD linewidth reduction for every two to three years. The performance of the IC chip is directly related to the result of CD. As the CD linewidth continues to shrink, its variation tolerance also reduces, resulting in the tighter uniformity specifications to maintain the satisfied chip performance. To meet such stringent

Figure 1.3: Source of CD variation [5]

specifications for CD, advanced control technologies are highly demanded for the lithography process. Especially when the channel length of a transistor shrinks to sub-100 nm, an adequate and econ-friendly lithography process technology becomes an increasingly challenging task.

| Table 1.1. Litingraphy technology requirements for the next decade |      |      |      |      |      |      |      |  |  |  |

|--------------------------------------------------------------------|------|------|------|------|------|------|------|--|--|--|

| Year of Production                                                 | 2012 | 2013 | 2014 | 2015 | 2016 | 2017 | 2018 |  |  |  |

| DRAM $1/2$ pitch (nm)                                              | 32   | 28   | 25   | 23   | 20   | 18   | 16   |  |  |  |

| CD control (3 sigma) (nm)                                          | 3.3  | 2.9  | 2.6  | 2.3  | 2.1  | 1.9  | 1.7  |  |  |  |

Table 1.1: Lithography technology requirements for the next decade

In the literature, thermal processing system is commonly used for photoresist processing in the lithography, and it is usually applied at the PEB step. Investigations in [6] showed that the variation in gate CD for the PEB process generally ranged from 3 to 7 nm/°C. Conventional baking is the mainstream for current semiconductor manufacturing, which a hotplate of large thermal mass is maintained at a constant temperature by a feedback controller [7]. Because of the large thermal mass and sluggish dynamics, conventional baking system demonstrates great robustness to the temperature fluctuations and loading effects. However, these characteristics make conventional baking system misfit for the process control with tight tolerance. Moreover, conventional hotplate design also has hardware constraints for across wafer temperature control which is a source of across wafer process variation. Some novel programmable thermal processing systems have been developed in the last decade to address these issues. Tay et al. modelled and built a multi-zone thermal processing system in [8] and further extended in [9] which greatly enhanced the across wafer temperature uniformity at both transient and steady states by performing in-situ real-time power input control. In [10], the authors proposed a real-time photoresist extinction coefficient uniformity control algorithm with an array of spectrometers positioned above the bake-plate for in-situ parameters measurement. Subsequently, an in-situ real-time photoresist thickness and extinction coefficient control scheme was demonstrated in [11]. Similar research results were presented in [12] for the analysis of die-to-die CD uniformities. Differently, T. Tomita [13] also reported a CD uniformity (CDU) improvement technology with wafer warpage control oven for high volume manufacturing. The utilization of these novel designed thermal bake-plates allows more flexibility for thermal control in the lithography process.

Besides thermal bake-plate, researchers have also paid considerable attentions to the development of metrology tools. Scanning electron microscope (SEM) and atomic force microscopy (AFM) are the main CD metrology tools in the current semiconductor manufacturing. However, both of them can only measure the CD after the lithography process is completed. If the CD measurements are out of the limits and the rework is not allowed, the wafers have to be scrapped. It may waste thousands of dollars. Moreover, the recipe of the lithography process has also been updated on the basis of the current CD measurement. It may not be suitable for the next batch of wafers which may have different incoming conditions. To tackle these approach obstacles, the concept of the real-time photoresist properties monitoring and control through the lithography process is introduced and developed by researchers. An exploration of the real-time control system is presented in this thesis.

# 1.2 Review of Process Control for Lithography

Automated process control in semiconductor manufacturing grows increasingly due to the economic impact of efficiency and reproducibility. In lithography, automated inspection techniques such as ellipsometry allow operator to easily monitor the process and identify the equipment malfunction when the fault occurs. However, process engineer also expects an intelligent system which can recover the fault efficiently more than just inspection. Over the last decade, the desire for better automated process control has engendered a series of technology breakthroughs in advanced process control. This section will review some of them.

#### **1.2.1** Statistical process control

In manufacturing, the quality of a product is traditionally guaranteed by the post-manufacturing inspection. Each product may be accepted or rejected according to how well it meets the designed specifications. Variation is present in every process and can be categorized as either a common cause or an assignable cause. Process result exhibits that natural or common cause variation may form a bell-curve distribution. For these types of processes, a quality control method statistical process control (SPC) is proposed to ensure the production line running at full potential with minimum waste. The basic concept in SPC is the control chart which has an upper limit and a lower limit based on the acceptable process variation. The control chart is used to compare the measured data with a known distribution of data from an in-control process. For all the measured data within the limits, the products are characterized as qualified products. By using the most popular 3-sigma method in manufacturing industry, the confidence on quality is up to 95%. An assignable cause exists when a process is diagnosed as being out of the statistical control. The system can be brought back to the original benchmark once this assignable cause is eliminated. SPC can be applied to any process with the following characteristics: firstly, the output of process can be measured; secondly, the strength of each variation source can be determined numerically and further amenable to correction. SPC has been heavily applied in the semiconductor manufacturing. Unfortunately, SPC technique fails to provide the ideal process control. Although the out-of-control points may trigger the fault alarm, the equipment still needs to be shut down for diagnosis and correction manually. Moreover, different products may be processed in a given tool, resulting in different process specifications or even baseline drift. For these circumstances, SPC technique is too coarse to perform corrective action, and advance control technologies are in need to address this shortcoming.

#### 1.2.2 Run-to-run control

Run-to-run (R2R) control performs process parameter tuning based on the feedback or feedforward models between successive iterations of a given process. A reference is initially built, and the measurements are compared with the reference. Based on the difference, tunings on process parameters are conducted appropriately by using some algorithms. This control methodology keeps working through the lithography process so as to ensure the repeatability of the final CD result. Specifically, both feedback and feedforward models can be applied under the framework of R2R control. For feedback model, when CD linewidth is controlled by the PEB temperature, the drift of CD indicated by several consecutive runs can be feedback by the metrology sensor to the controller. Recipe tuning is then conducted on the PEB bake-plate before next wafer comes in. On the other hand, feedforward model can also be adopted for R2R control. In a feedforward situation, the properties of incoming wafer are used to tune the subsequent step parameter settings. For example, if the photoresist thickness suddenly drifts after soft bake, the PEB temperature may need to adjust properly to compensate this unexpected drift. R2R control may ensure a smooth manufacturing operation and guarantee the product reproducibility. However, its drawback is also very obvious that all the measurements are conducted after the process is completed and no real-time correction is performed on the measured sample. The incoming wafers usually have different conditions. There is no guarantee that the tuning based on the measured sample is ideal for the next incoming wafers. To solve this problem, the in-situ real-time control technologies are necessary.

#### 1.2.3 Real-time control

The essence of real-time control is to integrate the metrology sensor together with the process chamber. The sensor performs in-situ measurement and allows the actuator to react immediately based on the control algorithms. In lithography process, applying real-time temperature control at certain thermal baking steps such as soft bake or PEB can efficiently improve the CD uniformity. However, lithography actually consists of a series of process modules, and most of the real-time control methods are only employed within a single module. To make the system more robust and intelligent, it is necessary to have a framework to relate the successive modules throughout the lithography process. This framework also allows the operator to easily identify the fault and exclude the variation source from the previous steps.

### 1.3 Contribution

The most challenging parts for real-time control are the equipment design and implementation. This thesis proposes an approach to conduct realtime CD monitoring and control. It is well-known that temperature has a direct effect on CD. First, a multi-zone programmable thermal processing system is developed, which is able to control the wafer temperature uniformity during the entire thermal cycle. Next, an in-situ ellipsometry system is established and integrated into the thermal process to measure the CD profile in real-time. Experimental results demonstrate that the real-time control system is able to monitor and control the CD profile in real-time versus a run-to-run approach with more than 60% improvement. The summary of contributions is stated as below.

## 1.3.1 Modelling and real-time control of multi-zone thermal system

Current photoresist processes in advanced lithography systems are especially sensitive to temperature. This thesis presents an in-situ real-time method to control the wafer spatial temperature uniformity during thermal cycling of silicon wafer in the lithography sequence. These thermal steps are usually conducted by placing the substrate on the bake-plate for a given period of time. Tay et al. [8] have proposed an approach for controlling wafer temperature uniformity at steady-state. This thesis extends the approach by considering the dynamic properties of the system. A detailed physical model of the thermal system is first developed to describe the temperature relationship between the bake-plate and wafer. Next, by monitoring the bake-plate temperature and fitting the data into the model, the wafer temperature can be real-time calculated and controlled. This is useful as production wafer usually does not have temperature sensors embedded on it. As the thermal baking processes are subject to drifts, disturbances, and wafer warpage, a real-time correction of the bake-plate temperature is further established to improve the across wafer temperature uniformity. Compared with the method presented in [8], our approach performs well not only at steady-state, but also at the transient state. In particular, the equipment design includes a programmable dual-zone thermal processing system together with a model-based feedback controller.

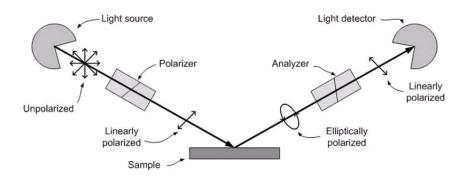

#### **1.3.2** Ellipsometry equipment design and application

Metrology is important for the entire microelectronics fabrication industry. Optical metrology is widely used at the nanometer scale for its nondestructive and non-invasive characteristics. Optical probes are especially favored for in-situ real-time monitoring because of their small footprint, fast response, high accuracy and robustness. This thesis applies the spectroscopic ellipsometry technique which can in-situ monitor the process. Ellipsometry is an optical technique devoted to the application of surface analysis, which measures a change in polarization as light reflects or transmits from a material structure [14]. Since the 1960s, as ellipsometry is developed to provide the sensitivity necessary to measure the nanometer-scale layers in microelectronics, interest in ellipsometry has grown steadily [15]. The advantage of using ellipsometry includes the non-destructive nature, high sensitivity, and simple implementation. Moreover, it is highly desirable to commission the ellipsometer as the contactless sensor for in-situ process monitoring to prevent wafer contamination in the semiconductor manufacturing. This thesis applies the spectroscopic ellipsometry at the PEB step to in-situ monitor the variation of CD latent image profile through thermal processing. Compared with the traditional SEM and AFM metrology techniques, ellipsometry demonstrates great capability for in-situ thin film properties measurement.

# 1.3.3 Dual-zone spatial CD in-situ real-time control through the PEB process

Conventional baking is commonly used at the PEB step where the bakeplate substrate is usually of large thermal mass and maintained at a constant temperature. Empirical experiments show that large across wafer CD nonuniformity exists at the end of the lithography process, which may lead to a significant yield loss. Semiconductor manufacturer can optimize the process flow to increase the device tolerance and compensate the CD nonuniformity [16]. However, as the device size keeps shrinking down and the wafer size keeps increasing up, the tolerance becomes much tighter than before. A multi-zone system is needed for better across wafer CD uniformity control. In this thesis, a dual-zone programmable thermal bake-plate is integrated together with a dual-probe spectroscopic ellipsometer. Based on this equipment integration, an effective in-situ real-time across wafer CD monitoring and control system is further developed. Firstly, the reference signatures regarding to the target DICD profiles are built. Secondly, an electromagnetic wave model based on the rigorous coupled-wave analysis (RCWA) is developed to relate the CD latent image profile with the ellipsometry measurement. At the PEB step, the spectroscopic ellipsometer performs in-situ photoresist properties measurement. The measured data can be characterized into CD profile by RCWA model. Thirdly, a realtime thermal control algorithm is proposed for across wafer CD uniformity improvement. Through the entire PEB process, the computer keeps comparing ellipsometry in-situ measurement with the reference for both wafer center and edge. Moreover, two decentralized PI controllers real-time adjust power inputs to the bake-plate center and edge based on the difference between measurement and reference. With the proposed dual-zone realtime CD monitoring and control system, the temperature profile across the bake-plate is controlled dynamically. The across wafer CD uniformity has been improved by more than 60% comparing with the conventional baking.

# 1.3.4 Feedforward/Feedback control framework for lithography process

Literature shows that CD variation attributes to all the steps of lithography. Application of in-situ real-time thermal control at the PEB step may improve the CD result but can not correct the variation source prior to the PEB step. To obtain an intelligent system which is able to effectively rectify the CD variation source and correct the recipe offset, this thesis strives for further improvements in the entire lithography process by building a feedforward/feedback control framework. The spin coating and PEB steps are selected as the controlled steps throughout the lithography process. For feedforward control, the perturbation caused by spin coating recipe offset is identified by the ellipsometer at the beginning of PEB process and then fixed by real-time thermal baking. When it comes to the feedback control, based on the in-situ measurement at the PEB step, the recipe of spin coating step is tuned appropriately before the next wafer comes in. With the application of such a feedforward/feedback control framework, apart from conducting real-time thermal control at the PEB step to achieve better CD results, the recipe offset at the spin coating step can also be corrected.

## 1.4 Organization of the Thesis

The rest of thesis is organized as follows. Chapter 2 describes the dual-zone programmable thermal system modelling and control. The spectroscopic ellipsometry working principle and its applications are presented in Chapter 3. Chapter 4 proposes an in-situ real-time across wafer CD monitoring and control system. Experiments are conducted with the real-time approach, demonstrating a significant CD uniformity improvement. Chapter 5 builds a feedforward/feedback control framework throughout the lithography process. It performs in-situ real-time CD control at the PEB step and further rectifies the perturbation at the spin coating step. Finally, conclusions and

potential future works are discussed in Chapter 6.

# Chapter 2

# Dual-Zone Programmable Thermal Baking System

## 2.1 Introduction

Temperature uniformity control is an important issue in photoresist processing with stringent specifications and has a significant impact on the CD. Variation in CD results in scrap products. The most temperature sensitive step in the lithography sequence is the PEB step. The variation in CD for this thermally activated process ranges from 3 to 7 nm/°C in bake temperature [6]. Requirements call for the temperature to be controlled within 0.1 °C across the wafer at temperatures between 70 °C and 150 °C [8], [17]. A number of recent investigations also showed the importance of proper bake-plate operation, both in steady and transient states, on CD control [18] - [25]. Two approaches exist in addressing this issue in industry. The first approach involves the development of less temperature sensitive photoresist. As outlined by the ITRS roadmap [2], there are currently no known manufacturing solutions and much work is required. The second approach is the development of algorithms [26], [27] and more advanced thermal processing systems [28], [29] for temperature and CD control, which is the approach undertaken in this chapter.

Thermal processing of semiconductor wafers is commonly performed by placing the substrate on a heated bake-plate for a given period of time. The heated bake-plate is held at a constant temperature by a feedback controller that adjusts the heater power in response to a temperature sensor embedded in the bake-plate near the surface. State-of-the-art heating systems consist of more heating zones. The wafers are usually placed on proximity pins to minimize contamination. When a wafer at room temperature is placed on the bake-plate, the temperature of bake-plate invariably drops first but recovers gradually because of closed-loop control. Different air gap sizes will result in different temperature drops in the bake-plate due to the difference in the air gap thermal resistance between the wafer and the bake-plate. A warped wafer will thus result in deviation of the wafer temperatures from its desired set points across the wafer surface.

Production wafers usually do not have temperature sensors embedded in them. Commercial bake-plates are usually calibrated based on test wafers with embedded sensors. However, as the processes are subject to drifts and disturbances, a fixed temperature set point is not able to address the issues. Any correction is therefore executed based on R2R control techniques, which depend on the sampling frequency of the wafers.

In [8], it demonstrated that information of the average air gap between the wafer and the bake-plate can be obtained with the use of system theory tools. The relationship between the wafer and plate temperatures at steady-state can then be derived from physical modelling of the baking process. By monitoring the maximum plate temperature drop, the average air gap in each heating zone can be estimated, and we are able to calculate the new bake-plate temperature set point to achieve the desirable steady-state temperature [8]. One of the major drawbacks of the mentioned approach is that it does not take into account the dynamic performances of the wafer temperature, although an improvement of steady-state temperature uniformity is obtained from about 1.1 °C to less than 0.1 °C when compared to conventional approaches where a simple feedback controller is used to regulate the plate temperature. The steady-state approach in [8] makes use of conduction thermal resistance terms which are strictly accurate only during steady-state. Consequently, that gives rise to significantly modelling error during the initial transient phase. It has also been reported that even though the resultant range of steady-state temperatures was minimized, the consequent gain in CD uniformity cannot be realized. This is attributed to the temperature distribution while rising to the PEB temperature [17].

In this chapter, a real-time wafer temperature control method to minimize temperature nonuniformity in the baking steps is proposed. The dynamic performance of the wafer temperature is improved. In contrast, the presented model adopts the full thermal diffusion formalism so that the thermal behavior during the initial transient period is properly captured. The average air gap thicknesses between the bake-plate and wafer in each of the heating zones, and consequently the wafer temperature can be extracted in real-time. The experimental result shows the feasibility of the proposed approach, and significant improvement is obtained when compared with conventional method and the steady-state approach [8].

The rest of Chapter 2 is organized as follows. In Section 2.2, the detailed thermal modelling is developed. The experimental results are then presented in Section 2.3. Finally, the conclusion is given in Section 2.4.

### 2.2 Thermal Modelling of the System

#### 2.2.1 System modelling

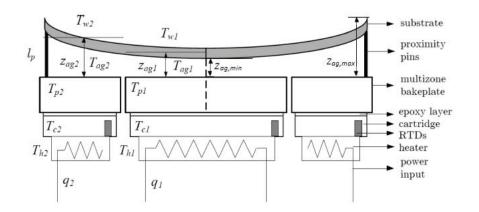

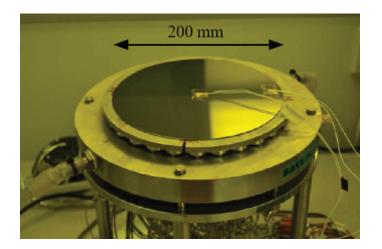

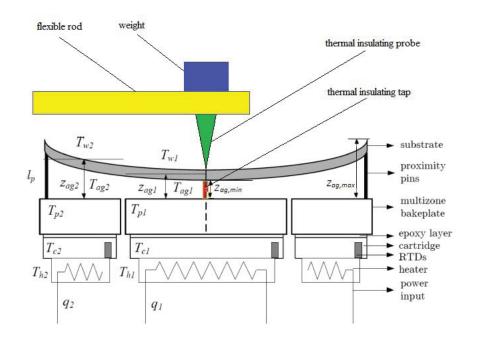

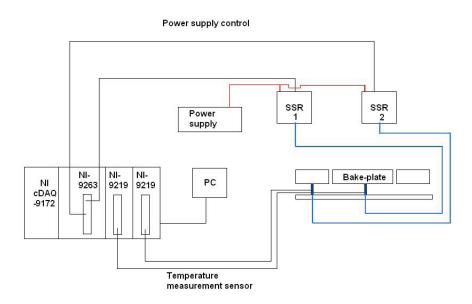

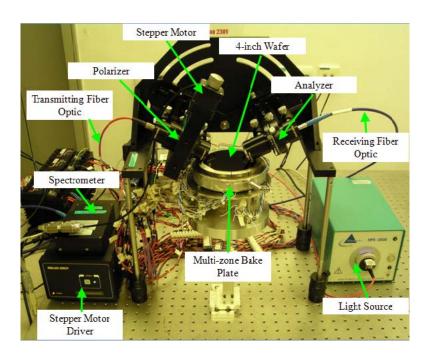

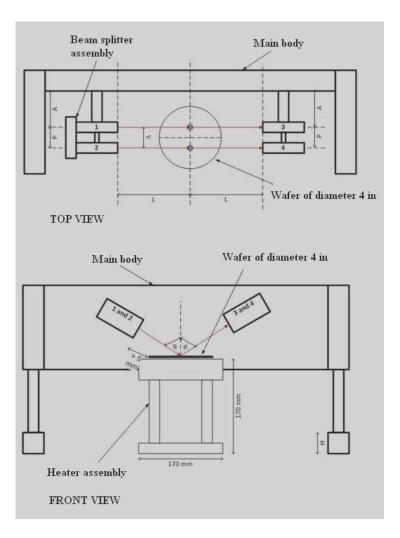

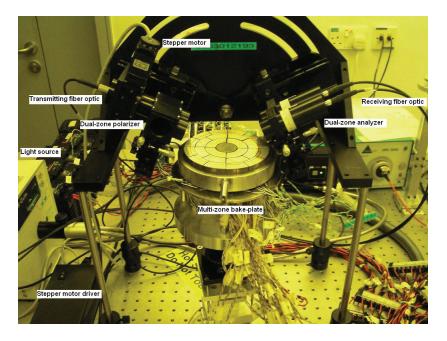

The multi-zone programmable thermal processing system used in this chapter is shown in Figures 2.1 and 2.2. In the baking process, the bake-plate is heated up by the cartridge heater attached to it. Resistive heating elements and resistance temperature detector (RTD) sensors are embedded in each of the heater cartridge, which are connected to the main heater plate via epoxy. The bake-plate consists a total of 64 of these heating elements in four annular rings. The center ring has 4 elements, the second to fourth annular rings has 12, 20, and 28 elements, respectively. Depending on the application, the number of heating zones of the bake-plate can be easily configured by simple connection of these heating elements. In the actual experimental work, the system is configured as a dual-zone system. The inner zone consists of 16 heating elements, the out zone consists of 48 heating elements. Each heating zone is configured with its own temperature sensor and electronics embedded in the cartridge for feedback control. The fact that zones are spatially disjointed by 1.27 mm air gap ensures no direct thermal coupling between the zones. Detailed description of the programmable thermal processing system can be found in the work of Tay et al [8].

Figure 2.1: Schematic diagram of the thermal processing system

Figure 2.2: Photo of the thermal processing system

Thermal energy transport mechanisms are usually classified as conduc-

tion, convection, and radiation. The second law of thermodynamics states that heat flows whenever there is a temperature gradient. For our thermal system, radiation heat transfer has limited application and can be ignored. Conduction and convection are the main mechanisms for thermal energy exchange. Energy balances on the elements in the system can be carried out to obtain a thermal model as follows:

$$C_w \dot{T}_w = q_w^{in} + q_w^{out} + q_w^{top} + q_w^{bottom}, \qquad (2.1)$$

$$C_{ag}\dot{T}_{ag} = q_{ag}^{in} + q_{ag}^{out} + q_{ag}^{top} + q_{ag}^{bottom}, \qquad (2.2)$$

$$C_p \dot{T}_p = q_p^{in} + q_p^{out} + q_p^{top} + q_p^{bottom}, \qquad (2.3)$$

$$C_c \dot{T}_c = q_c^{in} + q_c^{out} + q_c^{top} + q_c^{bottom},$$

(2.4)

$$C_h \dot{T}_h = q_h^{in} + q_h^{out} + q_h^{top} + q_h^{bottom} + q^{input}, \qquad (2.5)$$

where T is the temperature above the ambient, C is the thermal capacitance,  $q^{in}, q^{out}, q^{top}$  and  $q^{bottom}$  are the heat flows into the element from inner zone, outer zone, top surface, and bottom surface, respectively,  $q^{input}$  is the heater power and the subscripts w, ag, p, c, and h represent the wafer, the air gap, the bake-plate, the cartridge, and the heater, respectively. Detailed description of each of the terms are presented in the Appendix.

In the system, the wafer and the bake-plate can be discretized into several zones to simulate their temperature response. For each discrete element, heat is transferred between the adjacent inner and outer elements. There are

$$q_i^{in} = kA_i^{side} \frac{T_{i-1} - T_i}{r_{i-1}},$$

(2.6)

$$q_i^{out} = kA_{i+1}^{side} \frac{T_{i+1} - T_i}{r_i},$$

(2.7)

where k is the thermal conductivity,  $A^{side}$  is the contact area between the adjacent elements, and  $r_i$  is the distance between the elements i and i + 1.

For the edge element, the side surface is exposed to the ambient, so there is

$$q_n^{out} = h_{lm} \cdot A_{lm}^{side}(-T_a), \qquad (2.8)$$

where the subscript lm represents the different layers in the system, which are namely the wafer, the bake-plate, the cartridge and the heater. Variable  $T_a$  is the edge element temperature above the ambient. Variable h is the convection coefficient, which can be calculated as follows [30]:

$$h = \frac{k}{L_0} \overline{N}_u, \tag{2.9}$$

where  $L_0$  is the characteristic length,  $\overline{N}_u$  is the Nusselt number, and there is [30]

$$\overline{N}_u = \{0.6 + \frac{0.387(Ra)^{1/6}}{[1 + (0.559/Pr)^{9/16}]^{8/27}}\}^2,$$

(2.10)

where Ra is the Rayleigh number, Pr is the Prandtl number, and there are

$$Ra = \frac{g \cdot \beta_0 \cdot (T_1 - T_2) \cdot d^3}{\mu \cdot \alpha_0}, \qquad (2.11)$$

$$Pr = \mu/\alpha_0, \tag{2.12}$$

where g is the acceleration of gravity,  $\beta_0$  is the volume thermal expansion coefficient of fluid,  $T_1$  and  $T_2$  are the temperatures of two adjacent layers, d is the depth of fluid layer,  $\mu$  is the kinematic viscosity, and  $\alpha_0$  is the thermal diffusivity of fluid. The wafer top surface is exposed to the surroundings and so there is

$$q_n^{top} = h^{top} \cdot A_w^{top}(-T_w), \qquad (2.13)$$

where  $A_w^{top}$  is the area of the wafer top exposed to the ambient. The convection coefficient  $h^{top}$  can be calculated from the following [30]:

$$h^{top} = 0.54(Ra)^{1/4}.$$

(2.14)

The air gap between the wafer and bake-plate is about 100 to 300  $\mu$ m. The main mode of heat transfer between two materials separated by air depends on both the air gap and the temperature difference between the two materials [31]. When this air gap is below 5.8 mm, and their temperature difference is considerably smaller than 200 °C, the heat transfer mechanism is essentially conductive [31] and given by the following:

$$q_w^{bottom} = -k_{ag} A_{ag} \frac{\partial T_{ag}}{\partial z_{ag}}|_{boundary}, \qquad (2.15)$$

where z is the thickness. The effect of radiative heat transfer is negligible at the temperature range that we are interested [7].

Since the governing thermal transport between the elements in the system is conductive, at the boundary layer of two adjacent elements, there is

$$-k_a A_a \frac{\partial T_a}{\partial z_a}|_{boundary} = -k_b A_b \frac{\partial T_b}{\partial z_b}|_{boundary}, \qquad (2.16)$$

where the subscripts a and b represent the two vertical adjacent layers.

At the bottom layer of the system, the heater is exposed to the ambient, and there is

$$q_n^{bottom} = h_{bottom} \cdot A_h^{bottom} \cdot (-T_h), \qquad (2.17)$$

|                       | Property                      | Value                                                   |  |

|-----------------------|-------------------------------|---------------------------------------------------------|--|

| Wafer (Silicon)       | Density, $\rho$               | $2330 {\rm ~kg} {\rm ~m}^{-3}$                          |  |

|                       | Specific heat capacity, $c_v$ | $750 \ \mathrm{J} \ \mathrm{K}^{-1} \ \mathrm{kg}^{-1}$ |  |

|                       | Thermal conductivity, $k$     | $99 \text{ W m}^{-1} \text{ K}^{-1}$                    |  |

|                       | Convection coefficient, $h$   | $3.3824 \text{ W m}^{-2} \text{ K}^{-1}$                |  |

|                       | Thickness, $z$                | $0.700 \mathrm{~mm}$                                    |  |

| Air                   | Density, $\rho$               | $1.1 {\rm ~kg} {\rm ~m}^{-3}$                           |  |

|                       | Specific heat capacity, $c_v$ | $1000 \text{ J K}^{-1} \text{ kg}^{-1}$                 |  |

|                       | Thermal conductivity, $k$     | $0.03 \text{ W m}^{-1} \text{ K}^{-1}$                  |  |

| Bake-plate (Aluminum) | Density, $\rho$               | $2700 \text{ kg m}^{-3}$                                |  |

|                       | Specific heat capacity, $c_v$ | $917 \ \mathrm{J} \ \mathrm{K}^{-1} \ \mathrm{kg}^{-1}$ |  |

|                       | Thermal conductivity, $k$     | $250 \text{ W m}^{-1} \text{ K}^{-1}$                   |  |

|                       | Convection coefficient, $h$   | $7.271 \ {\rm W} \ {\rm m}^{-2} \ {\rm K}^{-1}$         |  |

|                       | Thickness, $z$                | $6.8 \mathrm{mm}$                                       |  |

| Epoxy                 | Thermal conductivity, $k$     | $0.35 \text{ W m}^{-1} \text{ K}^{-1}$                  |  |

|                       | Thickness, $z$                | 0.02  mm                                                |  |

| Cartridge (Aluminum)  | Density, $\rho$               | $2700 {\rm ~kg} {\rm ~m}^{-3}$                          |  |

|                       | Specific heat capacity, $c_v$ | $917 \ \mathrm{J} \ \mathrm{K}^{-1} \ \mathrm{kg}^{-1}$ |  |

|                       | Thermal conductivity, $k$     | $250 \text{ W m}^{-1} \text{ K}^{-1}$                   |  |

|                       | Convection coefficient, $h$   | $4.86 \text{ W m}^{-2} \text{ K}^{-1}$                  |  |

|                       | Thickness, $z$                | 4.4 mm                                                  |  |

| Heater (Aluminum)     | Density, $\rho$               | $2700 {\rm ~kg} {\rm ~m}^{-3}$                          |  |

|                       | Specific heat capacity, $c_v$ | $917 \ \mathrm{J} \ \mathrm{K}^{-1} \ \mathrm{kg}^{-1}$ |  |

|                       | Thermal conductivity, $k$     | $250 \text{ W m}^{-1} \text{ K}^{-1}$                   |  |

|                       | Convection coefficient, $h$   | $2.7828 \text{ W m}^{-2} \text{ K}^{-1}$                |  |

|                       | Thickness, $z$                | 5.4 mm                                                  |  |

Table 2.1: Physical parameters of the thermal processing system

where  $A_h^{bottom}$  is the area of the bottom of the heater exposed to the ambient. The convection coefficient  $h_{bottom}$  can be calculated from the following [30]:

$$\overline{N}_{u}^{bottom} = 0.27 (Ra)^{1/4}.$$

(2.18)

Most thermophysical properties are temperature dependent. However, for the temperature range of interest from 15 to 150 °C, it is reasonable to assume that they remain fairly constant and can be obtained from handbooks [32] as tabulated in Table 2.1.

#### 2.2.2 Model verification

The modelling equations are expressed in state-space form in the Appendix. To assess the quality of the proposed system model, we perform conventional baking process experiment and compare the simulation with the experimental results. In this work, the system dynamics for a dual-zone system are simulated. The objective is to demonstrate that the proposed model succeeds in predicting the experimental wafer temperatures using the bake-plate temperature and the input signal without resorting to the use of any fitting parameter and is therefore useful for scaling up.

In the experiment, a flat wafer at room temperature is dropped on the baking system with a proximity pin height,  $l_p$ , of 140  $\mu$ m. This causes the bake-plate temperature to drop at first but recovers gradually because of closed-loop control. Two proportional-integral (PI) controllers are used to control the temperature of the two zones of the bake-plate. The dynamic equation of the PI controller is

$$u(t) = K_p \cdot e(t) + K_i \cdot \int_0^t e(\tau) d\tau, \qquad (2.19)$$

where u(t) is the PI controller output at time t, e(t) is the difference between the measured temperature and the reference temperature at time t,  $K_p$  is the proportional gain, and  $K_i$  is the integral gain. As the standard PI controller is implemented in LabVIEW, the dynamic equation for the PI controller is actually

$$u[k] = u[k-1] + (K_p + K_i \cdot T_s) \cdot e[k] - K_p \cdot e[k-1], \qquad (2.20)$$

where u[k] is the current power input, u[k-1] is the previous power input,

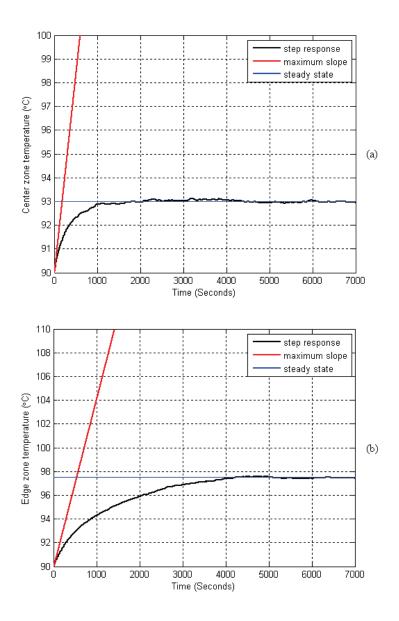

$T_s$  is the sampling time, e[k] is the current difference between the bakeplate temperature measurement and set point, and e[k-1] is the previous difference between the bake-plate temperature measurement and set point. The Ziegler-Nichols Reaction Curve Tuning Method is used for the PI controller tuning. This method is based on the open loop step response of the system. The selection of sampling time is discussed in Section 2.3. In the experiment, the sampling time is set to be 0.5 sec. The open loop step responses of the bake-plate center and edge are plotted in Figure 2.3. From the figures, we can obtain  $K_p = 1.0098$ ,  $K_i = 0.0634$  for the center zone, and  $K_p = 0.5556$ ,  $K_i = 0.0162$  for the edge zone. After several iterations of tuning, we finally use  $K_p = 1.00$ ,  $K_i = 0.10$  for the center zone, and  $K_p = 0.50$ ,  $K_i = 0.01$  for the edge zone in the experiment.

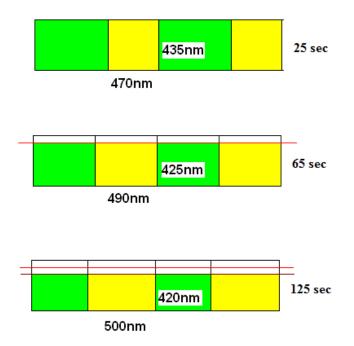

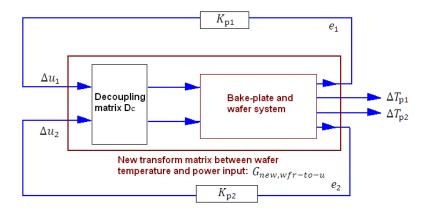

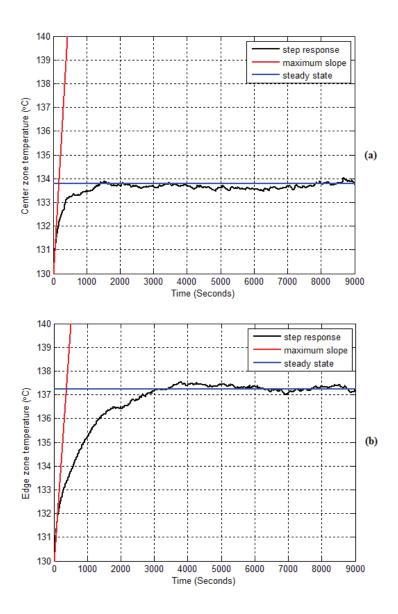

Figure 2.3: Open loop step responses for the 8-inch bake-plate. The bakeplate center and edge temperatures during the baking process are shown in subplots (a) and (b), respectively.

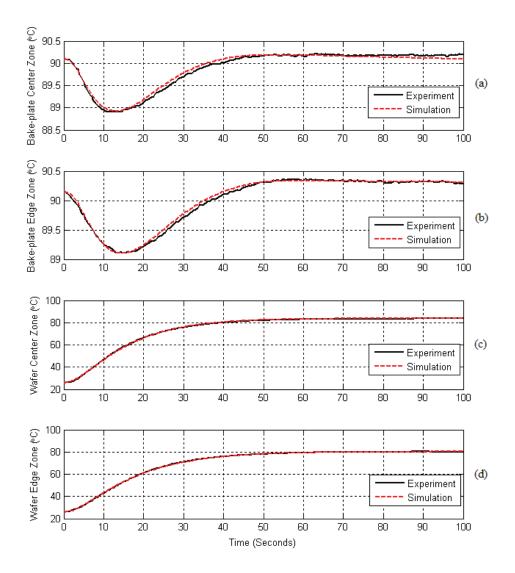

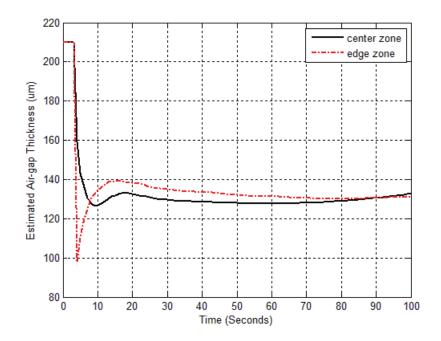

Figure 2.4 shows the comparison result of the simulation and experimental bake-plate temperatures and wafer temperatures when the air gap thickness is approximately 140  $\mu$ m. It can be seen that the agreement between of the wafer temperatures from simulation and experimental results is excellent, thereby verifying the effectiveness of the proposed thermal model. The estimated air gap thicknesses are plotted in Figure 2.5. Being confident of our system modelling, we then conduct real-time control experiment with the system model.

Figure 2.4: Plate and wafer temperature in simulation and experiment with air gap thickness be 140  $\mu$ m using the calculated model. The bake-plate center temperatures, bake-plate edge temperatures, wafer center temperatures, and wafer edge temperatures during the baking process are shown in subplots (a), (b), (c) and (d), respectively.

Figure 2.5: Air gap estimation for conventional baking with 140  $\mu \mathrm{m}$  proximity pins

# 2.3 Real-time Wafer Temperature Spatial Con-

## $\operatorname{trol}$

#### 2.3.1 Experiment setup and control structure