# DESIGN FOR MANUFACTURING IN IC FABRICATION: MASK COST, CIRCUIT PERFORMANCE AND CONVERGENCE

QU YIFAN (B.Eng.,SJTU)

# A THESIS SUBMITTED FOR THE DEGREE OF DOCTOR OF PHILOSOPHY NUS GRADUATE SCHOOL FOR INTEGRATIVE SCIENCES AND ENGINEERING

NATIONAL UNIVERSITY OF SINGAPORE

2013

#### Declaration

I hereby declare that the thesis is my original work and it has been written by me in its entirety. I have duly acknowledged all the sources of information which have been used in the thesis.

This thesis has also not been submitted for any degree in any university previously.

~

Qu Yifan 4 Dec 2013

## Acknowledgments

Completing this PhD degree is perhaps the most challenging period of the first 26 years of my life. The best and worst moments of my doctoral journey have been shared with many people. It is a great privilege to spend four years in NUS Graduate School for Integrative Sciences and Engineering and the Department of Electrical and Computer Engineering at National University of Singapore, and its members will always remain dear to me.

I would like to express my heartfelt gratitude to Prof. Lee Tong Heng and Assoc. Prof. Arthur Tay, who are not only supervisors but also role models. Their immense knowledge and patient guidance helped me throughout my four years of research and writing of this thesis. Special thanks to my Thesis Advisory Committee, Prof. Ben M. Chen and Dr. Gan Oon Peen for their guidance and useful and practical suggestions.

I would also like to thank Assoc. Prof. Heng Chun Huat, who provided stimulating ideas and encouraging and constructive feedback, and the precious opportunity to get access to the industry tools in VLSI lab. I would not have contemplated this road if not for the generous financial support given by the NGS Scholarship, as well as the resourceful coursework supported by the intellectual and helpful lecturers. Special gratitude goes to Prof. Wang Qing-Guo, Assoc. Prof. Ong Chong Jin, Prof. Lian Yong, Dr. Yao Libin, Assoc. Prof. Xiang Cheng, Assoc. Prof. Peter Chen, Prof. Xu Yong Ping, Dr. Venkatakrishnan Venkataramanan, Assoc. Prof. Lim Kah Bin and Dr. Chui Chee Kong, who have carefully instructed me with the knowledge in the realms of control technology, circuit design and computer vision.

Members of Center for Intelligent Control also deserve my sincerest gratitude. It would be hard to complete my research without precious and friendly assistance of the members of Advanced Control Technology Lab. Special thanks go to Mdm. S. Mainavathi and Mr. Zhang Hengwei for their utmost technical and logistical support, and Dr. Teh Siew Hong, Dr. Ngo Yit Sung, Dr. Yang Geng, Mr. Ang Kar Tien, Dr. Nie Maowen, Dr. Chen Xuetao, Mr. Yu Chao, Dr. Yang Yang, Dr. Xue Zhengui, Dr. Liu Lei, Dr. Yuan Jian, Dr. Xie Jing, Mr. Qi Jing, Mr. Shi Qixian, Mr. Shen Chengyao, and all my friends in Singapore, China and other parts of the world, who are the sources of laughter and support.

I wish to thank my parents and my deceased grandmother, whose love provided my inspiration and was my driving force, and my fiancee, Miss Gu Panyu, whose love and encouragement inspired me so that I could finish this journey. I hope this work makes you proud.

# Contents

| Acknow  | wledgments                     |  |   |   | i    |

|---------|--------------------------------|--|---|---|------|

| Summa   | ary                            |  |   |   | viii |

| List of | Figures                        |  |   |   | xi   |

| List of | Tables                         |  |   |   | XV   |

| List of | Abbreviations                  |  |   | x | viii |

| Chapte  | er 1 Introduction              |  |   |   | 1    |

| 1.1     | Background                     |  | • |   | 1    |

| 1.2     | Current OPC Methodologies      |  | • |   | 8    |

| 1.3     | Motivations                    |  |   |   | 13   |

|         | 1.3.1 Mask Cost                |  |   |   | 14   |

|         | 1.3.2 Circuit Performance      |  |   |   | 16   |

|         | 1.3.3 Convergence and Run-time |  | • |   | 18   |

| 1.4     | Contributions                  |  |   |   | 20   |

|     | 1.4.1 | Timing Performance Oriented Optical Proximity         |    |

|-----|-------|-------------------------------------------------------|----|

|     |       | Correction                                            | 20 |

|     | 1.4.2 | Process Window Aware Optical Proximity Correction .   | 23 |

|     | 1.4.3 | Optical Proximity Corrected Mask Simplification Using |    |

|     |       | Over-designed Timing Slack                            | 25 |

|     | 1.4.4 | Fast Optical Proximity Correction with Timing         |    |

|     |       | Optimization Ready Standard Cells                     | 27 |

| 1.5 | Organ | ization of the Thesis                                 | 28 |

## Chapter 2 Timing Performance Oriented Optical Proximity

| Cor | rectio | 1                                                 | 30 |

|-----|--------|---------------------------------------------------|----|

| 2.1 | Introd | uction                                            | 30 |

| 2.2 | Conve  | ntional OPC Methodologies                         | 31 |

| 2.3 | Timin  | g Performance Oriented OPC                        | 33 |

|     | 2.3.1  | Overall Flow                                      | 33 |

|     | 2.3.2  | Timing Performance Extraction                     | 34 |

|     | 2.3.3  | Mask Generation Algorithm                         | 36 |

| 2.4 | Simula | ation Results                                     | 38 |

| 2.5 | Applie | cation of Feedback Control to Improve Convergence | 42 |

|     | 2.5.1  | PI Controller                                     | 42 |

|     | 2.5.2  | Iterative Feedback Tuning                         | 43 |

| 2.6 | Simula | ation Results of PI Controllers                   | 44 |

|     | 2.6.1  | Basic PI Controller                               | 44 |

|     | 2.6.2 | Controlling OPC plant using other PID algorithms | 45 |

|-----|-------|--------------------------------------------------|----|

|     | 2.6.3 | Iterative Feedback Tuning Simulations            | 50 |

| 2.7 | Concl | usion                                            | 54 |

## Chapter 3 Process Window Aware Optical Proximity

|    | Cor   | rection | a                                                    | 55 |

|----|-------|---------|------------------------------------------------------|----|

|    | 3.1   | Introd  | luction                                              | 55 |

|    | 3.2   | Overv   | iew of Retargeting and Performance Based OPC Methods | 56 |

|    | 3.3   | Metho   | odology                                              | 58 |

|    |       | 3.3.1   | Overall Flow                                         | 58 |

|    |       | 3.3.2   | Timing Driven Retargeting                            | 59 |

|    |       | 3.3.3   | Sparse OPC                                           | 67 |

|    |       | 3.3.4   | Process Window Issue                                 | 69 |

|    | 3.4   | Result  | s and Discussions                                    | 72 |

|    |       | 3.4.1   | Gate Level Simulation                                | 72 |

|    |       | 3.4.2   | Circuit Level Simulation                             | 73 |

|    |       | 3.4.3   | Sensitivity Test Under Process Variation             | 75 |

|    |       | 3.4.4   | Mask Cost and CPU Run-time                           | 78 |

|    | 3.5   | Conclu  | usion                                                | 80 |

| Cł | napte | er 4 (  | Optical Proximity Corrected Mask Simplification      |    |

|    | Usiı  | ng Ove  | er-designed Timing Slack                             | 81 |

| 4.2 | Timing Yield and Over-designed Timing Slack | 83 |

|-----|---------------------------------------------|----|

81

| 4.3   | Characterizing of Timing Yield and Manufacturing Cost for |

|-------|-----------------------------------------------------------|

|       | Optical Proximity Correction Masks                        |

|       | 4.3.1 Problem Formulation                                 |

|       | 4.3.2 Characterization Method                             |

|       | 4.3.3 Simulation Results                                  |

| 4.4   | OPC Mask Simplification Methodology                       |

|       | 4.4.1 Timing Cost Function                                |

|       | 4.4.2 Mask Simplification Algorithm                       |

| 4.5   | Results and Discussions                                   |

|       | 4.5.1 An Example on Inverter                              |

|       | 4.5.2 Circuit Level Simulations                           |

| 4.6   | Conclusion                                                |

| Chapt | er 5 Fast Optical Proximity Correction with Timing        |

| Op    | timization Ready Standard Cells 109                       |

| 5.1   | Introduction                                              |

| 5.2   | Existing Electrically Driven OPC Methodologies 110        |

| 5.3   | Fast OPC Methodology 111                                  |

|       | 5.3.1 OPC Flow                                            |

|       | 5.3.2 Timing Optimization Ready Standard Cells 113        |

| 5.4   | Preliminary Results                                       |

| 5.5   | Hybrid Approach                                           |

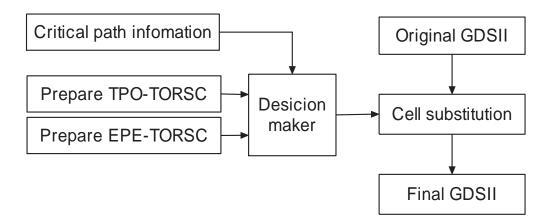

|       | 5.5.1 Flow of Proposed Hybrid Approach                    |

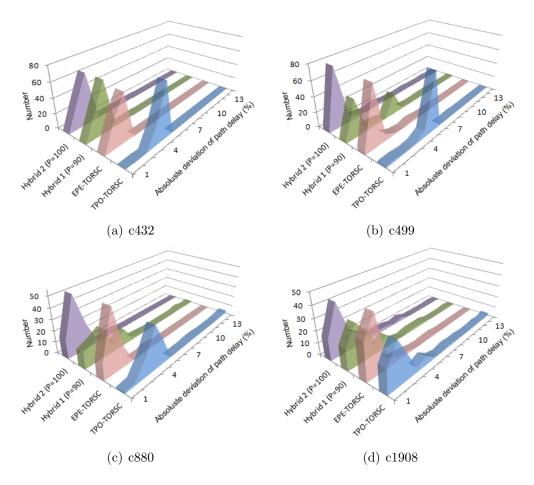

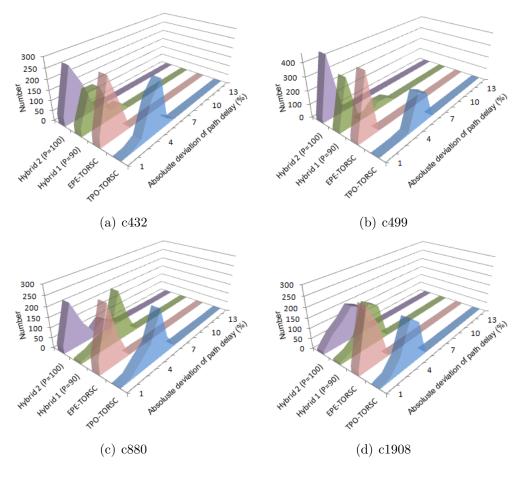

|        | 5.5.2 Simulation Results                      | 122 |

|--------|-----------------------------------------------|-----|

| 5.6    | Conclusion                                    | 126 |

| Chapt  | er 6 Conclusion                               | 128 |

| 6.1    | Summary                                       | 128 |

| 6.2    | Future Work                                   | 131 |

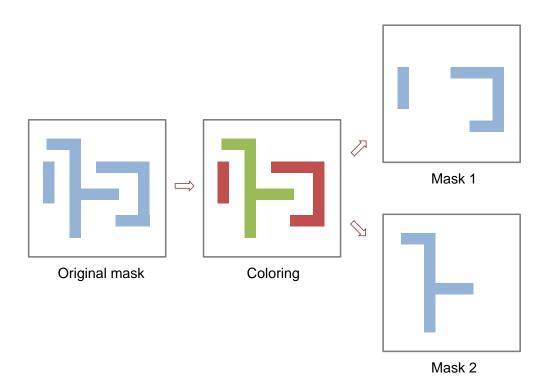

|        | 6.2.1 OPC for Double Patterning Techniques    | 131 |

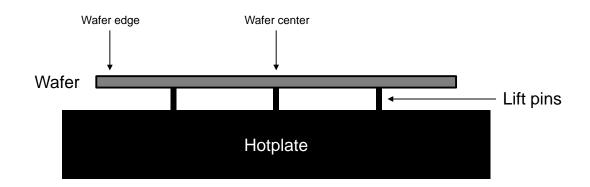

|        | 6.2.2 OPC for Extreme Ultraviolet Lithography | 132 |

|        | 6.2.3 Integration of Resist Processing in OPC | 133 |

| Autho  | r's Publications                              | 135 |

| Biblio | graphy                                        | 138 |

| Appen  | ndix A                                        | 152 |

| Appen  | ndix B                                        | 156 |

## Summary

The lithography process is the most critical step in the fabrication of integrated circuits (IC), accounting over a third of the total manufacturing cost. One of the key issues in the lithography process is the distortion of the printed images due to optical diffraction effect. To eliminate distortion of printed images at these advanced technology nodes, design for manufacturing (DFM) methods, such as optical proximity correction (OPC), have been implemented in the industry. Several problems exists in the current OPC techniques, such as mask cost, electrical performance and convergence issues. This thesis analyzes these problems and proposed a few novel approaches to improve OPC in terms of mask cost, circuit performance, convergence speed and run-time.

The International Technology Roadmap for Semiconductors (ITRS) identified a number of difficult OPC challenges for future technology nodes. The key challenges are to reduce OPC complexity, mask write-time and mask costs. The complexity of an OPC mask is determined by its level of fragmentation. A mask-cost-saving strategy with low fragmentation has been developed to address this issue, by using simple shapes, similar to the non-OPC schemes. The redundant sub-resolution shapes such as serifs, hammer heads and the stair-shaped edges are eliminated. The mask cost in terms of Manufacturing Electron Beam Exposure System (MEBES) file size is significantly reduced by 37% when tested on standard test chips, which can be directly translated into savings of the overall manufacturing cost, lower data volume and CPU processing time.

ITRS also highlighted that future OPC techniques should take into consideration circuit metrics such as circuit timing. This is critical since OPC edge insertion procedure may impact circuit performance. A timing-performance-aware OPC approach is developed to reduce the performance drift in circuit timing. The proposed approach optimizes post-OPC timing performance of the digital standard cells in terms of propagation delay. Simulations on benchmark circuits show up to 10% improvement compared to conventional shape-driven and electrically-driven OPC schemes. In addition, with accurate timing performance, process window could be enlarged by 88%, which means that the robustness under process variations is significantly improved.

Convergence is another important issue in OPC mask design methodology. A large number of iterations of edge perturbations are necessary in conventional OPC approaches in order to converge to the desired result. Feedback control theory is used to improve the convergence speed in the OPC iterations. A proportional-integral (PI) controller is utilized and the controller parameters are adaptively tuned with an iterative feedback tuning (IFT) algorithm for different processes. Simulation results show that the convergence speed is improved, and run-time is reduced by 80%, using various industrial standard test circuits.

Finally, for large circuits with numerous repetitive cells, a fast OPC technique is developed to accelerate the overall OPC run-time. The full layout is split into multiple single cells and OPC is conducted in parallel using lookup tables for each type of standard cell, thereby avoiding the computationally expensive full-chip OPC run-time. The average speed-up is up to 6 times when compared to conventional full chip OPC schemes.

# List of Figures

| 1.1  | Block diagram of lithography processing steps                                 | 2  |

|------|-------------------------------------------------------------------------------|----|

| 1.2  | Resolution enhancement techniques: (a) OAI; (b) PSM. $\ldots$                 | 6  |

| 1.3  | Optical proximity correction                                                  | 7  |

| 1.4  | An example of rule based OPC                                                  | 8  |

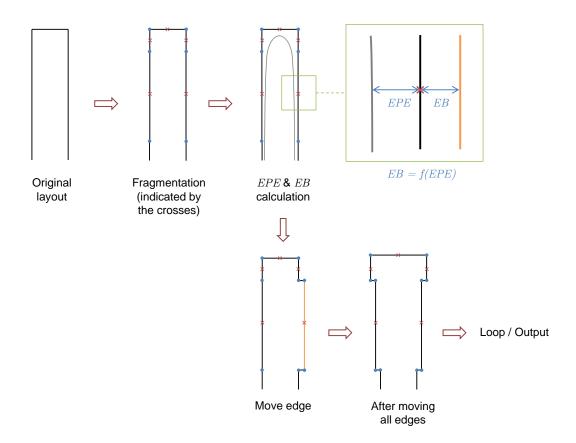

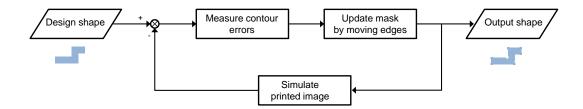

| 1.5  | A typical flowchart of model based OPC                                        | 9  |

| 1.6  | An example of model based OPC                                                 | 11 |

| 1.7  | Feedback block diagram of the model based OPC flow                            | 12 |

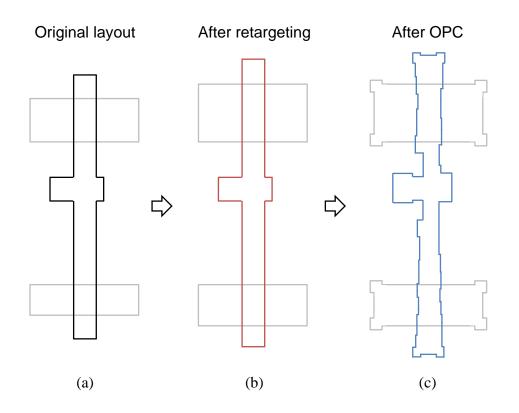

| 1.8  | Retargeting as a preprocess of OPC                                            | 12 |

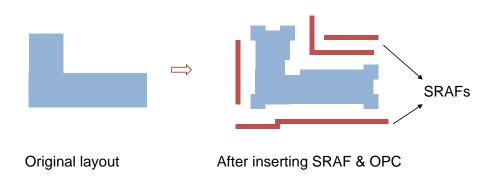

| 1.9  | Sub-Resolution Assist Features                                                | 13 |

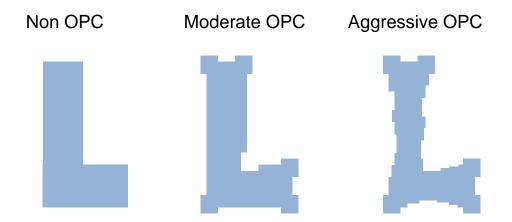

| 1.10 | Comparison of OPC schemes with increasing aggressiveness                      | 15 |

| 1.11 | Comparison of two OPC schemes: shape driven OPC vs. electrically driven OPC   | 18 |

| 1.12 | EPE step response of two OPC controllers                                      | 19 |

| 1.13 | A typical OPC controller block diagram                                        | 20 |

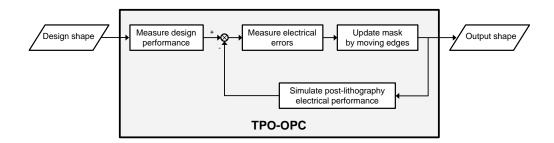

| 1.14 | Improvements of TPO-OPC from conventional model based OPC shown in Figure 1.6 | 22 |

| 1.15 | Control block diagram of the proposed approach                                | 23 |

| 1.16 | Improvements of PWA-OPC                                                       | 25 |

| 1.17 | Block diagram of OPC mask simplification method                                                                                                                                                                                                                                                                                                                                  | 26 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

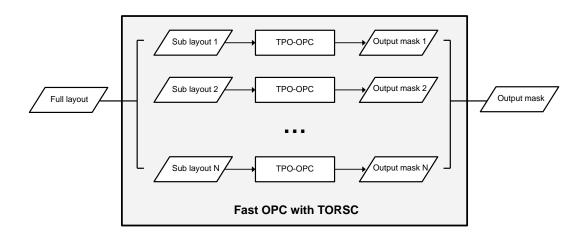

| 1.18 | Block diagram of fast OPC with TORSC                                                                                                                                                                                                                                                                                                                                             | 28 |

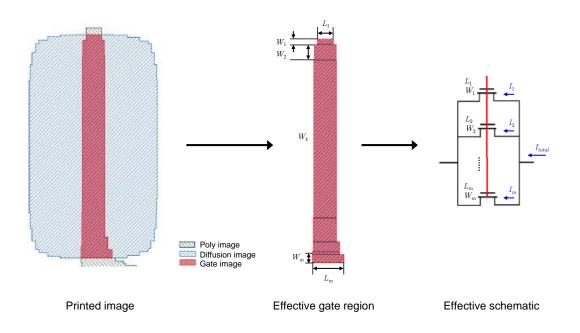

| 2.1  | Illustration of non-rectangular gate slicing method                                                                                                                                                                                                                                                                                                                              | 36 |

| 2.2  | TPO-OPC algorithm                                                                                                                                                                                                                                                                                                                                                                | 38 |

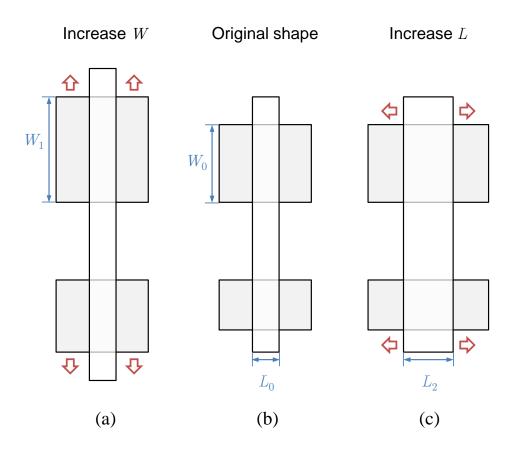

| 2.3  | Transistor resizing: (a) width increase from $W_0$ to $W_1$ , (b) original shape, (c) length increase from $L_0$ to $L_2$                                                                                                                                                                                                                                                        | 39 |

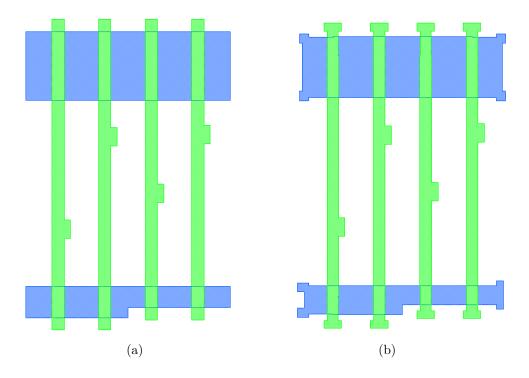

| 2.4  | Mask comparison of AOI211: (a) TPO-OPC; (b) EPE-OPC. (Only polysilicon and diffusion layers are displayed.)                                                                                                                                                                                                                                                                      | 41 |

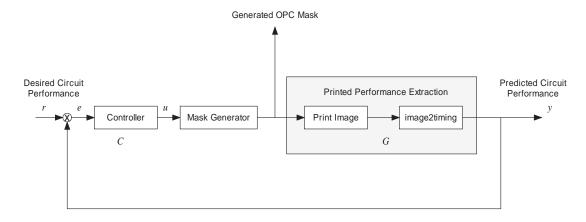

| 2.5  | Control block diagram in TPO-OPC                                                                                                                                                                                                                                                                                                                                                 | 43 |

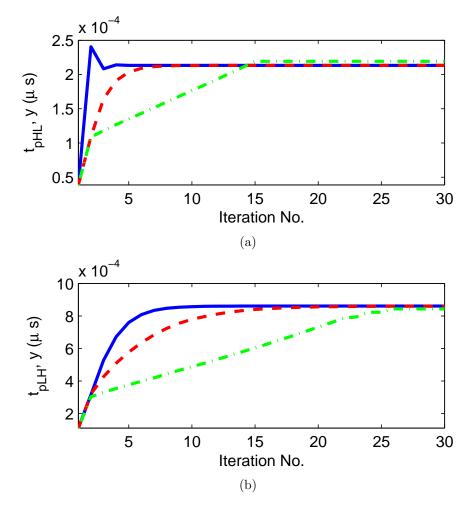

| 2.6  | Comparison of step response of cell NOR3: (a) NMOS site,<br>(b) PMOS site. Solid line: $K_{P1} = 1.0 \times 10^9$ , $K_{I1} = 1.0 \times 10^6$ ;<br>dashed line: $K_{P2} = 0.5 \times 10^9$ , $K_{I2} = 0.5 \times 10^6$ ; dash-dotted<br>line: fixed-step-size. An initial width of 50nm is set for all<br>transistors, so the initial output $y$ of each run remains the same. | 45 |

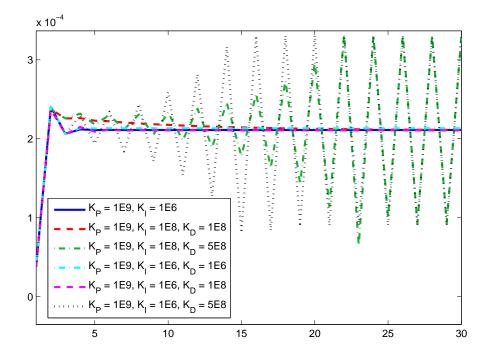

| 2.7  | Step responses of P, PI and PID controllers                                                                                                                                                                                                                                                                                                                                      | 47 |

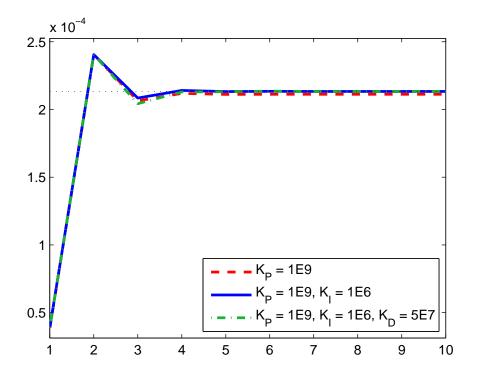

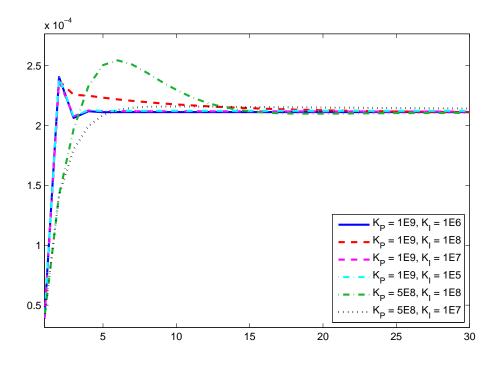

| 2.8  | Step responses of the PI controllers                                                                                                                                                                                                                                                                                                                                             | 49 |

| 2.9  | Step responses of the PID controllers                                                                                                                                                                                                                                                                                                                                            | 50 |

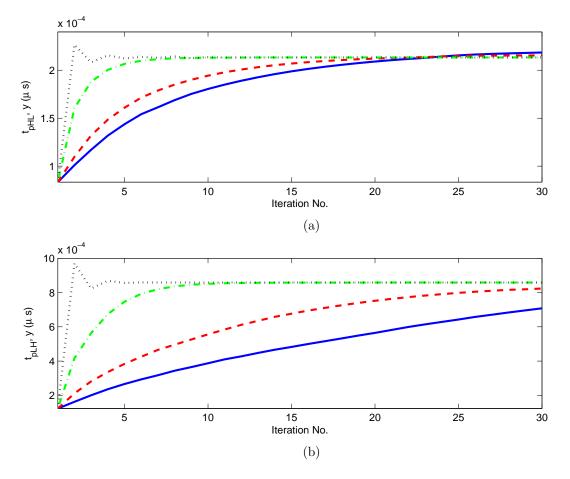

| 2.10 | Comparison of step response with different sets of controller<br>parameters for NMOS and PMOS sites respectively, solid line:<br>before IFT, dashed line: after 1 IFT simulation, dash-dotted<br>line: after 4 IFT simulations, dotted line: after 30 IFT<br>simulations                                                                                                         | 51 |

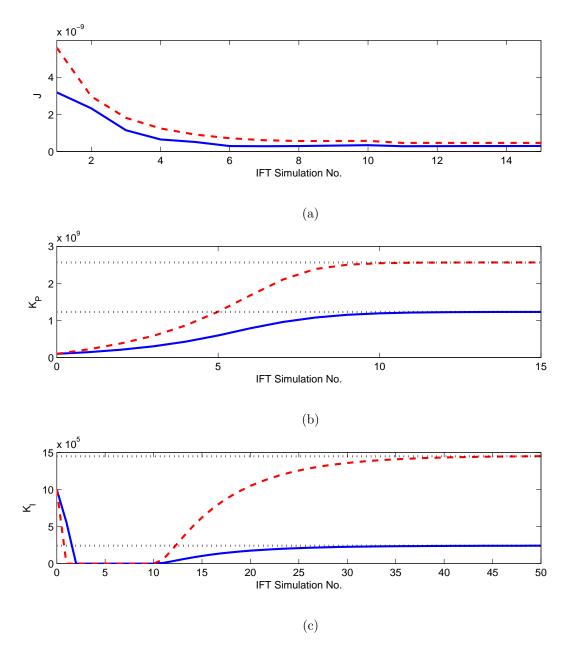

| 2.11 | IFT simulations for NOR3. (a)-(c): convergence of cost function, controller parameters $(K_P \text{ and } K_I)$ respectively, NMOS site: solid line, PMOS site: dashed line                                                                                                                                                                                                      | 53 |

| 3.1  | PWA-OPC block diagram                                                                                                                                                                                                                                                                                                                                                            | 59 |

| 3.2  | PWA-OPC algorithm                                                                                                                                                                                                                                                                                                                                                                | 60 |

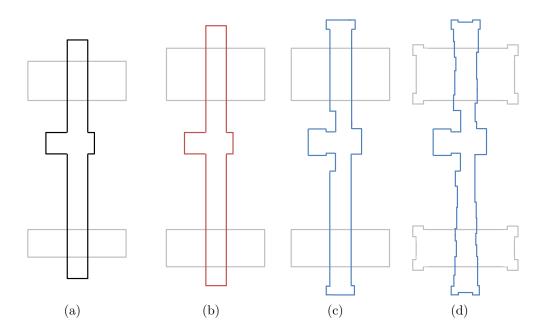

| 3.3  | <ul><li>PWA-OPC input/output layout example: (a) original shape,</li><li>(b) after retargeting, (c) after sparse OPC, (d) after dense OPC.</li><li>Poly layers are colored and diffusion layers are gray-colored.</li></ul>         | 61 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

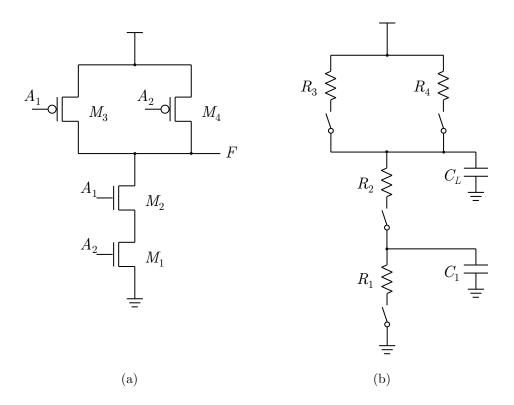

| 3.4  | Two-input NAND(NAND2): (a) schematic, (b) its<br>RC-equivalent model                                                                                                                                                                | 62 |

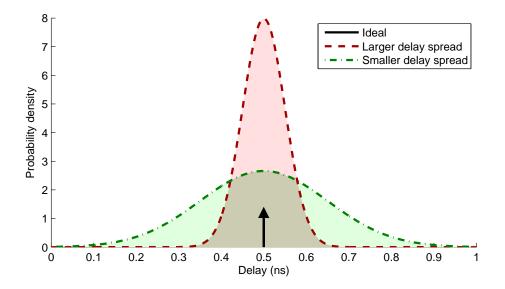

| 3.5  | Three kinds of path delay probability distribution function $\ .$ .                                                                                                                                                                 | 70 |

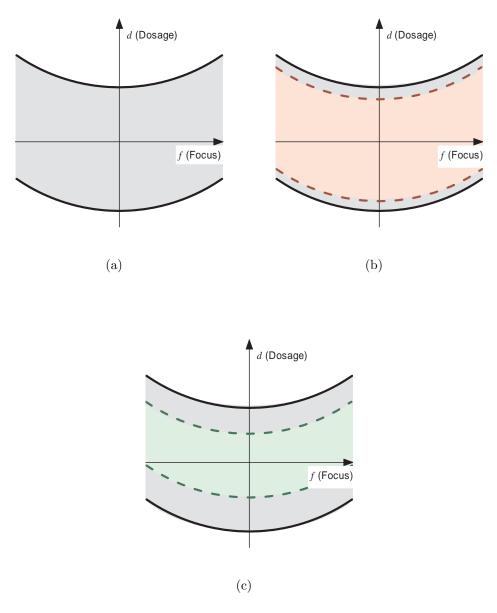

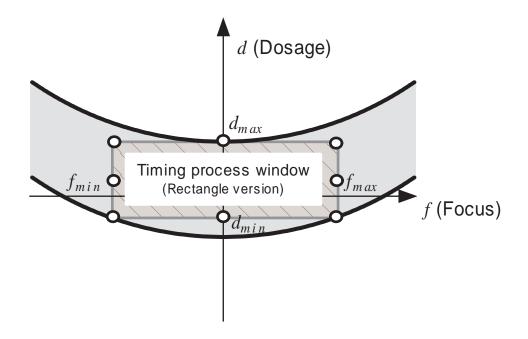

| 3.6  | Timing process window example, (a) TPW of ideal case, (b) TPW of the scheme with smaller delay spread, (c) TPW of the scheme with larger delay spread.                                                                              | 71 |

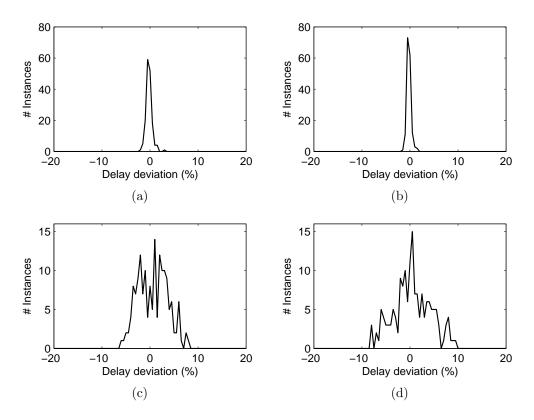

| 3.7  | Histogram of gate delay deviation: (a) PWA-OPC; (b)<br>PWA-OPC+Dense; (c) PB-OPC; (d) ED-OPC. Histogram of<br>SD-OPC is even worse than (c) and (d) and is not shown in<br>this series.                                             | 74 |

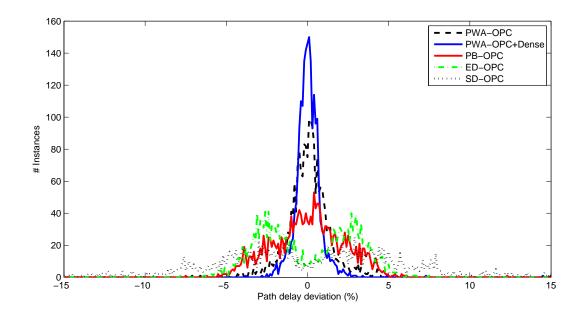

| 3.8  | Histogram of path delay deviation, circuit $c432$                                                                                                                                                                                   | 75 |

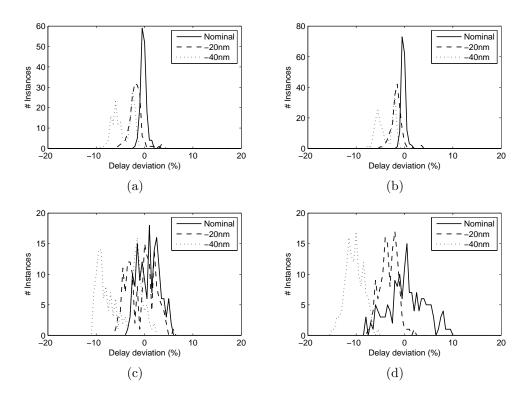

| 3.9  | Histogram of gate delay deviation under focus variation: (a)<br>PWA-OPC; (b) PWA-OPC+Dense; (c) PB-OPC; (d)<br>ED-OPC                                                                                                               | 77 |

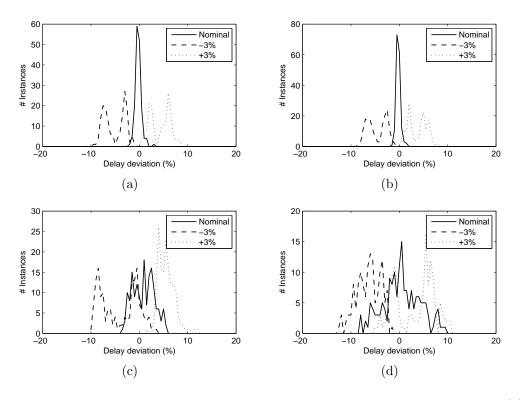

| 3.10 | Histogram of gate delay deviation under dosage variation: (a)<br>PWA-OPC; (b) PWA-OPC+Dense; (c) PB-OPC; (d)<br>ED-OPC                                                                                                              | 78 |

| 3.11 | Illustration of rectangle version of timing process window: the largest inscribed rectangle ensuring no timing violation occurs at all the eight border points.                                                                     | 79 |

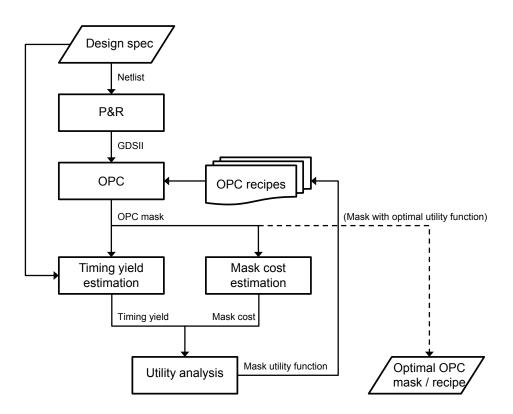

| 4.1  | Flowchart of proposed characterization method                                                                                                                                                                                       | 88 |

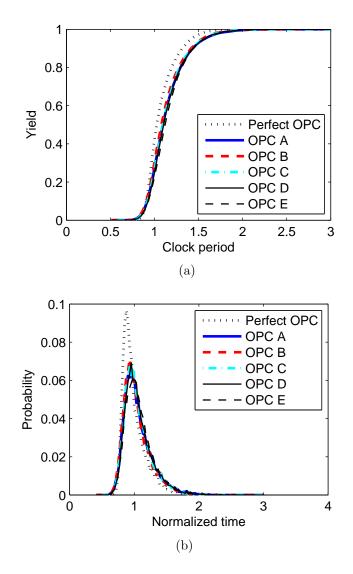

| 4.2  | Path delay PDF and timing yield of OPC A-E (c432) $\ldots$ .                                                                                                                                                                        | 89 |

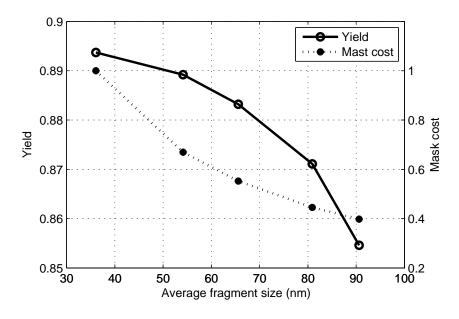

| 4.3  | Timing yield and mask cost (c432) $\ldots \ldots \ldots \ldots \ldots$                                                                                                                                                              | 90 |

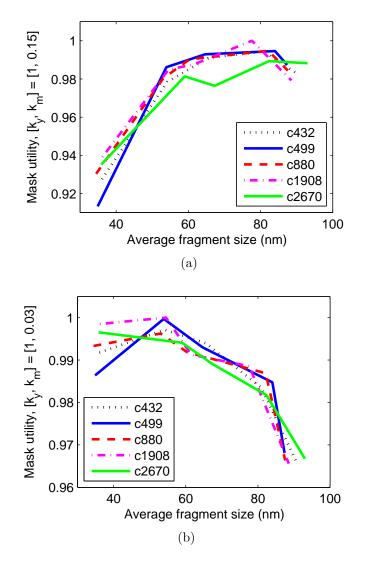

| 4.4  | Normalized mask utility of 5 circuits                                                                                                                                                                                               | 91 |

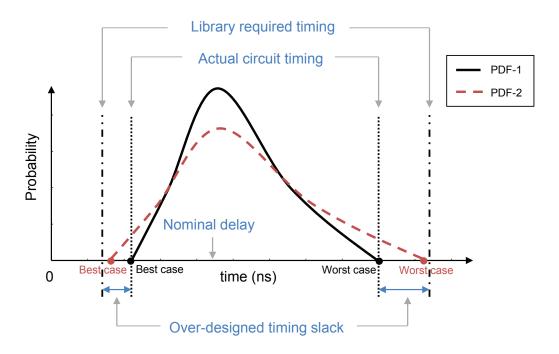

| 4.5  | Over-designed timing slack found in the path delay<br>probability density function (PDF) plot. PDF-1: complex<br>mask with better timing; PDF-2: less complex mask with<br>reduced timing slack but still meets library requirement | 93 |

| 4.6  | Flowchart of proposed OPC mask simplification method                                                                                                                    | 94  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

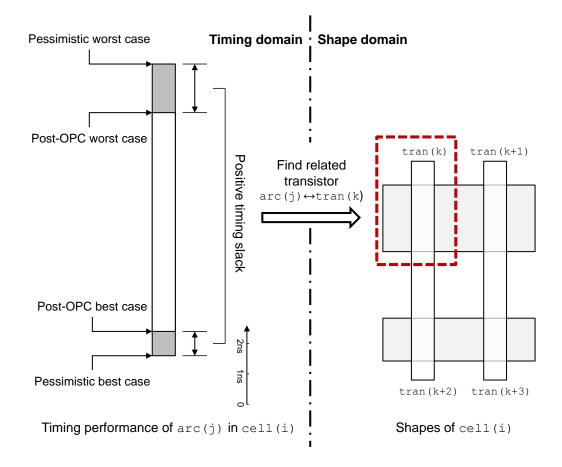

| 4.7  | Relating timing slack to shape slack                                                                                                                                    | 95  |

| 4.8  | OPC mask simplification algorithm                                                                                                                                       | 96  |

| 4.9  | Definitions of fragment geometry                                                                                                                                        | 99  |

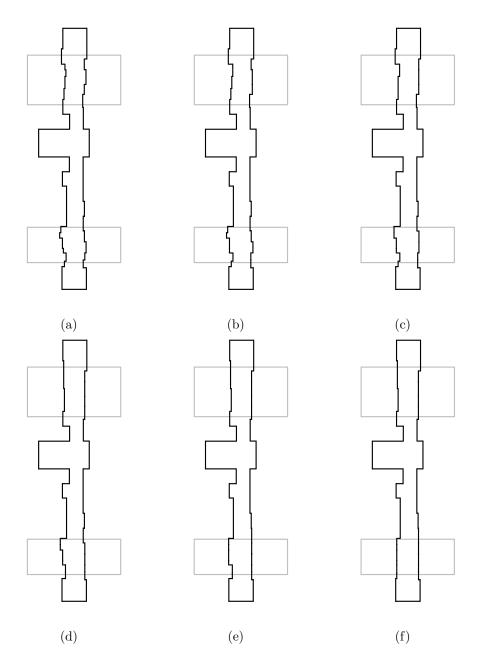

| 4.10 | Mask simplification progress: (a) Original OPCed mask, (b-f) simplified mask after iteration 1 to 5. (Only OPCed poly layers and non-OPCed diffusion layers are shown.) | 104 |

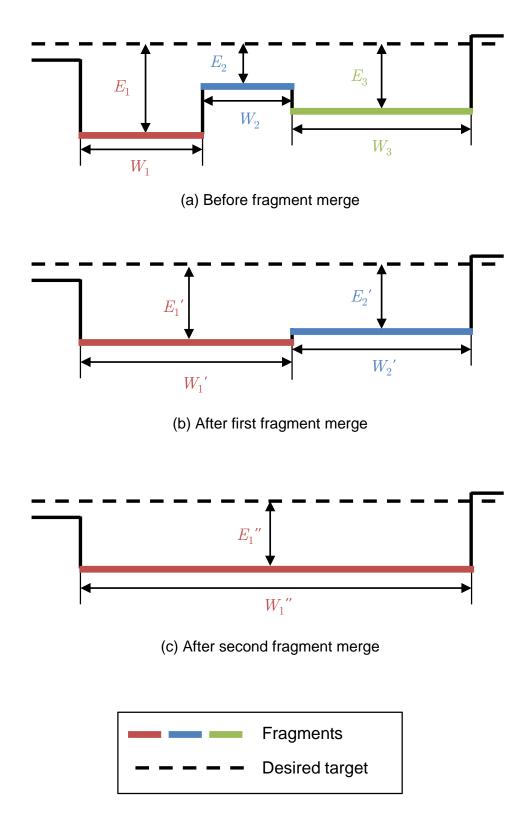

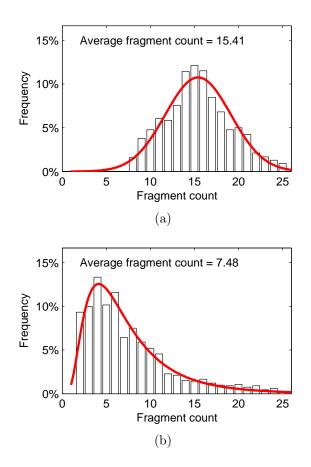

| 4.11 | Histogram of fragment count per transistor (c432): (a) original mask, (b) after mask simplification                                                                     | 105 |

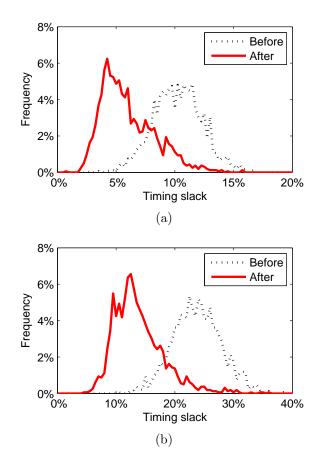

| 4.12 | Histogram of timing slack (c432): (a) best case, (b) worst case                                                                                                         | 107 |

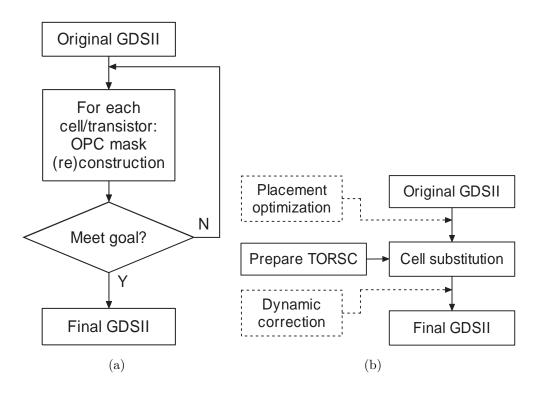

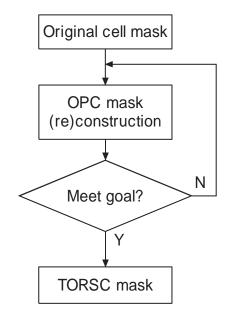

| 5.1  | Flowcharts of OPC schemes: (a) existing electrically driven OPC; (b) proposed fast OPC methodology                                                                      | 112 |

| 5.2  | TORSC generation flow                                                                                                                                                   | 113 |

| 5.3  | Full chip path delay $ TPE $ distribution, GDS-1 (P&R method 1)                                                                                                         | 116 |

| 5.4  | Full chip path delay $ TPE $ distribution, GDS-2 (P&R method 2)                                                                                                         | 117 |

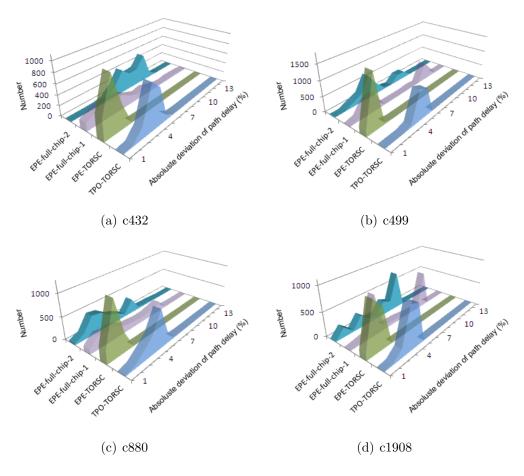

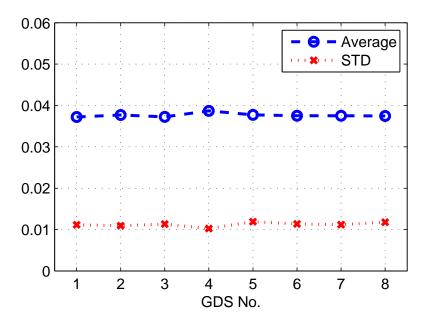

| 5.5  | Simulation of 8 different GDS's                                                                                                                                         | 118 |

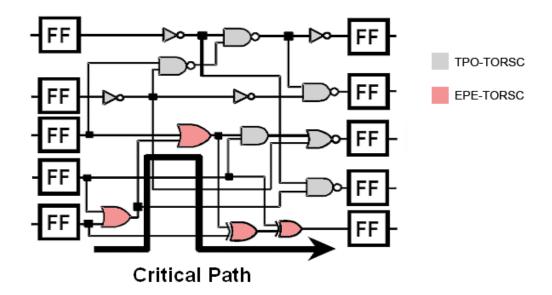

| 5.6  | Example in a digital circuit block                                                                                                                                      | 121 |

| 5.7  | Flowchart of proposed hybrid approach                                                                                                                                   | 122 |

| 5.8  | Simulation set 1: critical paths                                                                                                                                        | 124 |

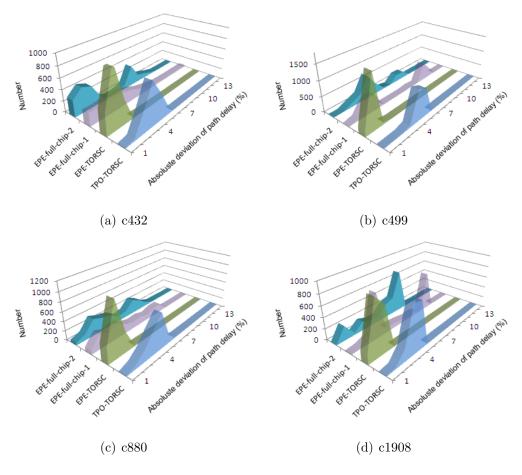

| 5.9  | Simulation set 2: random paths                                                                                                                                          | 126 |

| 6.1  | Mask decomposition of double patterning                                                                                                                                 | 132 |

| 6.2  | PEB: The temperature at the center of the hotplate increases more slowly than the temperature at the edge                                                               | 133 |

# List of Tables

| 1.1 | Down-scaling trend reported by International Technology<br>Roadmap for Semiconductors                                 | 4  |

|-----|-----------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Fragment count of OPC mask in Figure 1.10                                                                             | 14 |

| 1.3 | Mask data volume trend reported by ITRS                                                                               | 15 |

| 2.1 | Falling edge $(t_{pHL})$ timing performance comparison (normalized $t_{pHL}$ , with respect to INV design $t_{pHL}$ ) | 40 |

| 2.2 | Rising edge $t_{pLH}$ timing performance comparison (normalized $t_{pLH}$ , with respect to INV design $t_{pHL}$ )    | 40 |

| 2.3 | MEBES mask size comparison (unit: Byte)                                                                               | 41 |

| 2.4 | Control parameters for the three controllers                                                                          | 46 |

| 2.5 | Control parameters for the PI controllers                                                                             | 48 |

| 2.6 | Error signal and derivative control term in PID control $\ . \ . \ .$                                                 | 48 |

| 2.7 | Control parameters for the PID controllers                                                                            | 49 |

| 2.8 | Convergence time of NMOS sites (number of iterations to converge)                                                     | 54 |

| 2.9 | Convergence time of PMOS sites (number of iterations to converge)                                                     | 54 |

| 3.1 | Change in propagation time (%) when target shape of cell NAND2 is extended by 10nm. Positive numbers means the delay is increased due to the fragment shift, while negative numbers means the delay is decreased. | 64  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.2 | PMI, TMI, and mask cost (normalized with respect to mask cost of layout 1) vs average fragment size                                                                                                               | 69  |

| 3.3 | Comparison of gate delay deviation                                                                                                                                                                                | 73  |

| 3.4 | Comparison of PMI of full chip layouts $(\%)$                                                                                                                                                                     | 76  |

| 3.5 | Comparison of TMI of full chip layouts (%) $\ldots \ldots \ldots$                                                                                                                                                 | 76  |

| 3.6 | Process window area (TPW area unit: $nm \cdot \%$ )                                                                                                                                                               | 76  |

| 3.7 | OPC mask fragment count (normalized with respect to Non-OPC)                                                                                                                                                      | 79  |

| 3.8 | CPU run-time (normalized with respect to SD-OPC $^a)$ $\ . \ . \ .$                                                                                                                                               | 80  |

| 4.1 | Timing yield and mask cost of three OPC recipes, $T_0 = 46.5 ns$                                                                                                                                                  | 86  |

| 4.2 | Average fragment size of five OPC recipes                                                                                                                                                                         | 88  |

| 4.3 | Normalized mask utility of c432                                                                                                                                                                                   | 90  |

| 4.4 | Mask Simplification Progress (INV_X1)                                                                                                                                                                             | 102 |

| 4.5 | Mean fragment count per transistor and MEBES file size reduction                                                                                                                                                  | 106 |

| 4.6 | Timing slack at best cases (BC) and worst cases (WC) before<br>and after applying mask simplification, and its reduction (rd.)                                                                                    | 106 |

| 4.7 | CPU run-time of OPC and mask simplification, normalized with respect to c432's OPC run-time (172 sec.) $\ldots \ldots$                                                                                            | 106 |

| 5.1 | Normalized mask vertex count w.r.t c432 diffusion design mask vertex count, Scheme (1): TPO-TORSC; (2): EPE-TORSC; (3): EPE-full-chip-1; (4): EPE-full-chip-2                                                     | 119 |

| 5.2 | OPC run-time and speedup, (1): TPO-TORSC; (3): EPE-full-chip-1; (4): EPE-full-chip-2                                                                           | 120 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.3 | Number of critical cells                                                                                                                                       | 123 |

| 5.4 | Normalized mask vertex count w.r.t c432 diffusion design mask vertex count, Scheme (1): TPO-TORSC; (2): EPE-TORSC; (5): Hybrid 1 (P=90); (6): Hybrid 2 (P=100) | 125 |

# List of Abbreviations

The following table describes the significance of various abbreviations and acronyms used throughout the thesis.

| Abbreviation | Meaning                                                 |

|--------------|---------------------------------------------------------|

| 193nm        | optical lithography using ArF laser at 193nm wavelength |

| $\lambda$    | wavelength of the light source                          |

| ArF          | argon fluoride laser                                    |

| AOI          | AOI gate (AND-OR-Invert)                                |

| ASIC         | application-specific integrated circuit                 |

| CAR          | chemically amplified resist                             |

| CD           | critical dimension                                      |

| CDF          | cumulative distribution function                        |

| CMOS         | complementary metal-oxide-semiconductor                 |

| CPU          | central processing unit                                 |

| DE           | double exposure                                         |

| DFM          | design for manufacturing                                |

| DIFF         | diffusion area in wafer                                 |

| DoF           | depth of focus                                       |

|---------------|------------------------------------------------------|

| DP            | double patterning                                    |

| DRAM          | dynamic random-access memory                         |

| DUV           | deep ultraviolet                                     |

| EB            | edge bias                                            |

| EBL           | electron beam lithography                            |

| ED-OPC        | electrically driven optical proximity correction     |

| EPE           | edge placement error                                 |

| EPW           | electrical process window                            |

| EUV           | extreme ultraviolet                                  |

| $\mathbf{FF}$ | flip-flop or latch                                   |

| GDSII         | Graphic Design System II                             |

| GPW           | geometric process window                             |

| HDL           | hardware description language                        |

| HMDS          | Hexamethyldisilazane primer                          |

| Hyper-NA      | NA > 1.0 with immersion lithography technique        |

| IC            | integrated circuit                                   |

| IFT           | iterative feedback tuning                            |

| INV           | inverter                                             |

| ISCAS         | IEEE International Symposium on Circuits and Systems |

| ISCAS'85      | ISCAS benchmark circuits (1985)                      |

| ITRS          | International Roadmap for Semiconductor              |

| $k_1$  | a coefficient that encapsulates process-related factors |

|--------|---------------------------------------------------------|

| L      | length of a transistor                                  |

| LFD    | lithography friendly design                             |

| MEBES  | Manufacturing Electron Beam Exposure System             |

| MOSFET | metal-oxide-semiconductor field-effect transistor       |

| MP     | multiple patterning                                     |

| NA     | numerical aperture                                      |

| NAND   | NAND gate (NOT-AND)                                     |

| NILS   | normalized image log slope                              |

| NMOS   | n-channel MOSFET                                        |

| NOR    | NOR gate (NOT-OR)                                       |

| OAI    | off-axis illumination                                   |

| OAI    | OAI gate (OR-AND-Invert)                                |

| OPC    | optical proximity correction                            |

| PDF    | probability density function                            |

| PEB    | post exposure back                                      |

| PI     | proportional-integral controller                        |

| PID    | proportional-integral-derivative controller             |

| POLY   | polysilicon                                             |

| PMI    | process manufacturability index                         |

| PMOS   | p-channel MOSFET                                        |

| PSM    | phase-shift mask                                        |

| PVT    | process, voltage and temperature                    |

|--------|-----------------------------------------------------|

| PW     | process window                                      |

| P & R  | place and route                                     |

| RAM    | random-access memory                                |

| RET    | resolution enhancement technique                    |

| SADP   | self-aligned double patterning                      |

| SD-OPC | shape driven optical proximity correction           |

| SPICE  | Simulation Program with Integrated Circuit Emphasis |

| SRAF   | sub-resolution assist feature                       |

| STA    | static timing analysis                              |

| STD    | standard deviation                                  |

| TDR    | timing driven retargeting                           |

| TMI    | timing manufacturability index                      |

| TORSC  | timing optimization ready standard cell             |

| TPE    | timing performance error                            |

| TPW    | timing process window                               |

| UV     | ultraviolet                                         |

| W      | width of a transistor                               |

| XOR    | XOR gate (Exclusive OR)                             |

## Chapter 1

## Introduction

### 1.1 Background

Advances in integrated circuits (ICs) performance over the past 30 years owe much to the progress made in lithography. Lithography is a process used to create multiple layers of circuit patterns on a chip [1]. It is currently the largest capital investment and operating cost component of a leading-edge semiconductor fabrication plant, accounting for 35% of the costs of manufacturing ICs [2–4]. It is also the key enabler and "bottleneck" controlling the device scaling, circuit performance and magnitude of integration for silicon semiconductors. This integration drives the size, weight, cost, reliability and capability of electronic systems [5, 6].

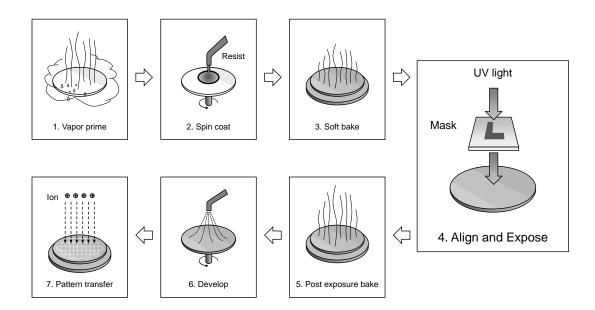

The lithography process consists of the following steps shown in Figure 1.1: vapor priming, spin coating, soft bake, alignment and exposure, post exposure bake, develop, and pattern transfer followed by resist striping [5, 7]. First, a primer called "Hexamethyldisilazane (HMDS)" is applied to the silicon wafer to improve the resist adhesion. A small quantity of resist is then dispensed onto the wafer, before the wafer is spun at high speed to deposit thin resist films uniformly. This is then followed by a soft bake step to reduce the remaining solvent concentration in the resist. In the alignment and exposure step, the resist-coated wafer has to undergo exposure to some form of radiation that will produce the pattern image on the resist. After exposure, a post exposure bake is performed to enable a chemical reaction to alter the resist solubility characteristic. The develop step utilizes chemical developers to remove exposed area of positive resist (or unexposed area of negative resist) to leave the desired mask pattern. Finally, pattern transfers such as etching, lift-off and implantation are conducted to build the micro-structures on the wafer.

Figure 1.1: Block diagram of lithography processing steps [5]

In Figure 1.1, steps 1-3 and 5-7 are usually combined in a machine called the *track*, while the machine used to conduct step 4 is called the *aligner*. In a lithography projection process, the imaging step is always subject to degradation from diffraction which causes imperfections in the projection system. This phenomenon becomes severe when feature size scales down and it significantly obstructed printing perfect shapes onto the wafer surface.

Driven by Moore's Law [8], the number of transistors on an IC has been increasing at the pace of approximately 2 times every 18 months in the past decades. Due to the demand of putting an increasing number of transistors on the same area of a silicon substrate, the size of transistors has to be down-scaled. The scaling factor is also in line with Moore's speed:  $0.7 \times$  per technology node. This trend is reported by the International Technology Roadmap for Semiconductors (ITRS) [9] as shown Table 1.1. The "critical dimension" (CD) in this table refers to the dimension of the smallest geometrical features on the semiconductor chip due to down-scaling. ITRS highlighted lithography as one of the key challenges in the next generation of technologies. As physical features of ICs shrink, lithography-induced effects, such as diffraction and optical proximity effects, become more prominent, resulting in design-for-manufacturing (DFM) issues, especially functional yield loss. It is also known as resolution limitations, as described in the following paragraphs.

Resolution in lithography is defined as the smallest feature that can be printed under adequate control. One commonly used indicator of resolution

| Year of first product shipment | Critical dimension |

|--------------------------------|--------------------|

| 2011                           | 36                 |

| 2012                           | 32                 |

| 2013                           | 28                 |

| 2015                           | 23                 |

| 2020                           | 13                 |

Table 1.1: Down-scaling trend reported by International Technology Roadmap for Semiconductors [9]

is CD (the minimum feature size in lithography). It is determined by the wavelength of the imaging light source ( $\lambda$ ) and the numerical aperture (NA) of the projection lens according to the Rayleigh resolution criterion [10]:

$$CD = k_1 \frac{\lambda}{\mathrm{NA}},\tag{1.1}$$

where  $k_1$  is a process dependent factor determined by resist capability, exposure and resist tool control, mask pattern adjustments and process control. It can be inferred from Equation (1.1) that smaller feature size can be printed by using smaller  $\lambda$  and larger NA. However, the optical devices are usually developed at a much lower pace than the speed at which the desired feature shrinks. Today's mainstream light source wavelength is still 193nm with argon fluoride (ArF) laser. The implementation of shorter wavelengths such as extreme ultraviolet lithography (EUV, expected to be 13.5nm) has been delayed due to immature technology for mass production [9]. In the past decades, NA has been increased from 0.16 to 1.35. Nevertheless, NA cannot continue to increase because of the depth of focus (DoF) restrictions [10]. The solution to smaller feature size is to decrease  $k_1$ , which encompasses the above-mentioned resolution limitations. This motivates the development of Resolution Enhancement Techniques (RETs).

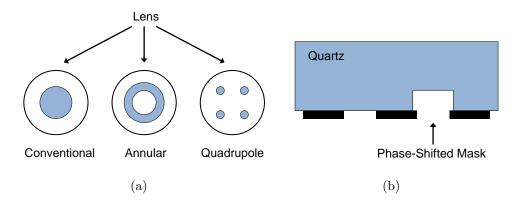

RETs are the predominant DFM techniques in current IC design flow [11, 12].RET approaches include Optical Proximity Correction (OPC), Off-Axis Illumination (OAI), Phase-Shift Mask (PSM), etc [7]. More recent RET approaches involve a combination of OPC, OAI and PSM. OPC is a technique to optimize mask patterns and improve fidelity of print images. OAI refers to any illumination shape that significantly reduces or eliminates the "on-axis" component of the illumination, that is, the light striking the mask at near normal incidence. Figure 1.2(a) shows two commonly used OAI sources when compared to the conventional "on-axis" source. The light is not projecting in the center area of the source. DoF can also be increased since the angle between the incident light and the mask plane is no longer perpendicular. PSM is used to overcome diffraction effects when images of neighboring parallel light beams interfere with each other. Figure 1.2(b) shows a typical phase-shift mask. A 180 degree inversion of the light beam phase can be found when transparent inversion layers (shifters) are added selectively. Resolution can thus be enhanced since less interference occurs. Among these approaches, OPC is noted as one of the key technologies enabling deep sub-wavelength IC fabriation [13]. It is also a major contributor to the mask costs and mask design turnaround time in lithography [14]. However, as feature size continues to decrease, it becomes more difficult and expensive to implement OPC [9]. Therefore, it is of

immense interest to develop new techniques to reduce the cost of OPC.

Figure 1.2: Resolution enhancement techniques: (a) OAI; (b) PSM.

OPC is an advanced mask engineering technique that is used to increase layout-to-wafer pattern fidelity. The goal of OPC is to enhance optical characteristics by making adjustments to the mask. This is accomplished by compensating mask geometry for known effects which will occur during imaging or subsequent processing [15–17]. To reiterate this more formally, as our problem statement:

**Problem Statement:** Given a desired geometric pattern on the wafer, find a mask design such that the final pattern remaining after the complete lithography process is as close as possible to the desired pattern.

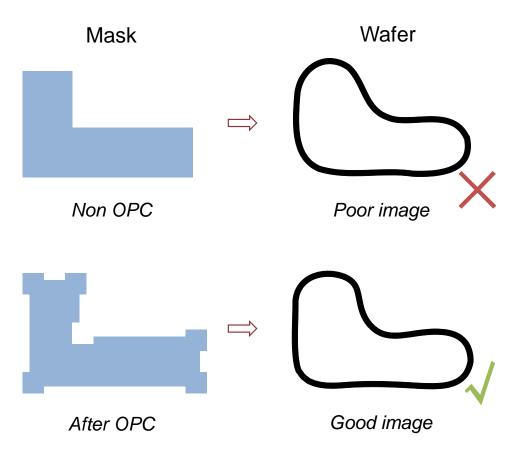

Figure 1.3 shows an example of using optical proximity correction. If the original mask without OPC is subject to lithography process, the resulting printed image on the wafer is poor, usually far from the target shape. Improvements in shapes are found after adopting OPC. The printed images on the wafer are usually closer to the target shape.

Figure 1.3: Optical proximity correction [7]

The benefits of OPC include more accurate CDs and better edge placement. Moreover, OPC enlarges process windows and improves yield for a given feature size. This allows more reliable pattern transfer at lower  $k_1$ values. However, problems exist with the application of OPC. Masks are more complicated due to the additional vertex, fragments and sub-resolution features. <sup>1</sup> Run-time to generate the mask is increased owing to the number of iterations in the OPC algorithms. These problems are inevitable with the current methodologies.

$<sup>^1\</sup>mathrm{Fragment}$  refers to the split short edges on the mask patterns, while vertex refers to the intersection of fragments.

### **1.2** Current OPC Methodologies

There are two types of OPC methodologies: rule based and model based [15]. Figure 1.4 shows an example of rule based OPC, in which feature corrections are conducted via a table look-up. The originally designed shapes are subjected to table look-ups in the rule based OPC process. These shapes are substituted according to their corresponding table entries. The overall OPC algorithm is rather simple, and run-time is an insignificant issue. However, as feature size scales downward, rule based OPC methods become incapable of dealing with mask patterns below 100nm technology node. Printed images of rule based OPC methods are no longer accurate in the state-of-the-art lithography. This motivates the development of model based OPC methods.

Figure 1.4: An example of rule based OPC

**INITIAL INPUT**

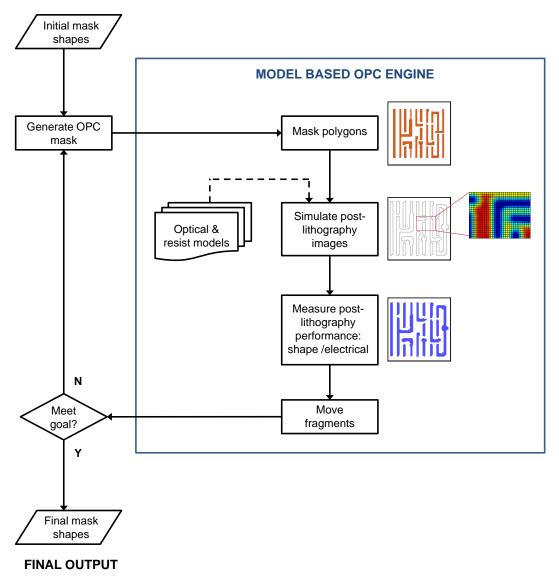

Figure 1.5: A typical flowchart of model based OPC

Model based OPC uses compact models to simulate print images dynamically and thereby move the edges on the mask to find the best solution. A typical flowchart of model based OPC is shown in Figure 1.5. The iterative model based OPC algorithm employs optical models and resist models to simulate post-lithography printed images in each loop. These printed images can be used to measure post-lithography performances such as shape and electrical metrics. The iteration stops when pre-defined criteria are met. The output in the last iteration is the final output OPC mask. Although CPU run-time of model based OPC is typically far more than that of rule based OPC, model based OPC can be applied to more complicated 2D shapes and is more accurate in terms of image fidelity. Model based OPC is the industry standard under 130nm process [18].

Most conventional model based OPC schemes are shape driven. In the model based OPC engine shown in Figure 1.5, a "measure post-lithography performance" step is conducted to measure contour errors. The most common error type is the Edge Placement Error (EPE), which is defined as the distance between the drawn edge location on the original design and the simulated edge location [18]. The objective of a shape driven OPC is to minimize the EPE so that the simulated design after exposure matches the original design closely. Figure 1.6 shows an example of shape driven OPC which tries to minimize *EPE*. First, a fragmentation procedure is conducted with respect to the original layout. Each edge is split into one or more In each OPC loop, EPE is calculated based on the target fragments. location and actual printed image of a fragment. Edge Bias (EB) is then derived as a function of EPE, *i.e.* EB = f(EPE). A typical example of this function is:  $EB = F(n) \cdot EPE$ , where F(n) is a function of iteration number, n. Next, the fragment is moved to a new location (a distance of EB away from previous location). After all fragments are relocated, the new layout is subjected to a new loop. The loop does not stop until convergence reaches or stop criteria are met [18]. It is interesting to note that the above description can be formulated as a feedback problem as shown in Figure 1.7.

Figure 1.6: An example of model based OPC

The preprocesses of OPC, the steps before actual OPC is conducted, include Retargeting and Sub-Resolution Assist Features (SRAFs) [19, 20]. Retargeting is a process to bias the edges of the original layout before OPC is conducted, based on the knowledge in process parameters and pattern offsets. With retargeting, it usually results in faster convergence. Figure 1.8

Figure 1.7: Feedback block diagram of the model based OPC flow

shows an example of retargeting. Figure 1.8(b) is the layout after retargeting, and OPC (Figure 1.8(c)) is conducted based on the post-retargeting layout.

Figure 1.8: Retargeting as a preprocess of OPC

SRAF is a process to insert scattering bars and other minor patterns into

the mask. The aim of SRAF is to improve contrast of light intensity and depth of focus. An SRAF is designed to improve the process margin of a resulting wafer pattern but not to be printed on the wafer. Figure 1.9 shows an example of SRAF insertion. The red polygons are SRAFs, which are part of the final mask. Although SRAFs will not appear in the printed image, the image quality can be improved.

Figure 1.9: Sub-Resolution Assist Features

### 1.3 Motivations

Despite the apparent advantages of OPC, problems exist in its applications in the industry. Manufacturing cost largely increases due to the complex shapes in OPC, while a more desirable metric of ICs, circuit performance, is not considered in the OPC loop [14, 21, 22]. Issues of convergence and run-time are also not adequately addressed. The research gaps introduced in this section motivate this thesis to design and implement new DFM techniques.

#### 1.3.1 Mask Cost

As reported in the lithography chapter in ITRS [9] in 2011, "reduced-cost" has become one of the key requirements of lithography. It is regarded as a "difficult challenge" to reduce complexity, write time and cost of the masks. In recent years, as OPC has been widely adopted, the complexity of the masks increased significantly. Extra vertex and extra fragments are introduced to the masks (a 4-8 times increase in fragment count [23]). The fragmentation in OPC is the main cause of the increase in extra vertex and extra fragments. The complexity of an OPC mask is determined by its level of fragmentation. High fragmentation results in short fragments and large fragment count. On the other hand, low fragmentation receives long fragments and small fragment count. Aggressiveness of OPC usually increases as fragment count increases. Figure 1.10 shows a series of OPC schemes with different levels of aggressiveness. The aggressiveness of OPC affects the mask complexity and hence the mask writing process; the mask write time is proportional to mask fragment count or vertex count [23]. The fragment counts of the three layouts in Figure 1.10 are tabulated in Table 1.2. It is clear that aggressive OPC increases mask fragment count and hence mask write time and manufacturing cost significantly.

| Table 1.2: Fragment count of OPC mask in Figure 1.10 |         |              |                |  |  |  |

|------------------------------------------------------|---------|--------------|----------------|--|--|--|

|                                                      | Non OPC | Moderate OPC | Aggressive OPC |  |  |  |

|                                                      | 6       | 30           | 67             |  |  |  |

Figure 1.10: Comparison of OPC schemes with increasing aggressiveness

Apart from the mask write time, mask cost is also related with data volume [9]. Aggressive OPC drives up the Graphic Design System II (GDSII)<sup>2</sup> layout file size. The resulting fractured data in terms of Manufacturing Electron Beam Exposure System (MEBES)<sup>3</sup> file size also increases. This exponential increase in data volume is highlighted in Table 1.3. Huge mask data size does not only consume disk space, but also incurs long CPU processing time. Therefore, there is a clear need to reduce mask data volume to save disk space and run-time.

| Year | DRAM $1/2$ pitch (nm) | Mask data volume (GB) |

|------|-----------------------|-----------------------|

| 2005 | 80                    | 260                   |

| 2007 | 65                    | 413                   |

| 2009 | 52                    | 655                   |

| 2011 | 36                    | 1570                  |

| 2013 | 28                    | 2220                  |

| 2015 | 23                    | 2970                  |

| 2020 | 13                    | Unclear               |

Table 1.3: Mask data volume trend reported by ITRS [9]

$<sup>^{2}</sup>$ GDSII stream format is the industry standard for data exchange of ICs. It is a binary file containing information of planar geometric shapes, text labels, etc.

$<sup>^{3}</sup>$ A MEBES file stores the fractured data of a mask. It is commonly supported by most mask writers [2].

The literature consists of several works on mask cost reduction [14, 22, 24, 25]. A method to reduce mask cost in the Self-Aligned Double Patterning (SADP) was introduced in [24], but it is only applicable to SADP lithography and is not feasible on other mainstream patterning methods. Gupta *et al.* [14] and Teh *et al.* [22] tried to reduce mask cost with consideration of circuit performance, but limitations in circuit performance exists (Section 1.3.1 will discuss such limitations). In [25], a regular fabric option was provided to optimize macro layout templates, but this required huge computational effort and significant layout changes.

#### **1.3.2** Circuit Performance

According to the latest ITRS report [9], limitations in lithography hardware resolution will require design flows to more explicitly account for the impact of RETs. RET tools such as OPC must become explicitly aware of circuit metrics such as timing and power. Such awareness aligns the tools with overall product goals and enables yield enhancements, manufacturing cost reductions, and improvement in mask data preparation time. As a consequence, the tools in the application-specific integrated circuit (ASIC) design flow will have to properly plan for RET and OPC modifications downstream.

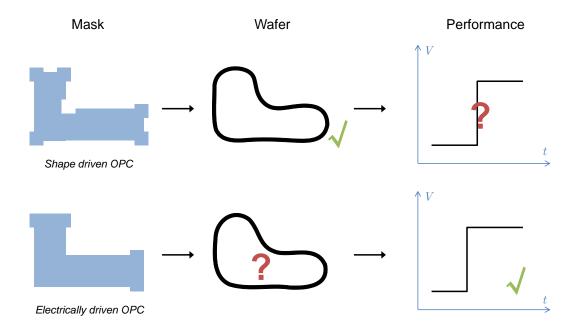

In the conventional shape driven OPC (SD-OPC) schemes, the impacts of the OPC edge insertion on the circuit performance are not taken into account during the correction. It is thus possible that an overcorrected OPC mask would just slightly outperform a moderately corrected OPC mask but at a much higher cost. Therefore, there is a need to incorporate the design intent (circuit performance) into the OPC flow to avoid the aforementioned scenario. In [14], circuit performance was incorporated into the OPC flow, where the tolerable EPE was predetermined from the timing analysis and the problem was solved as a constrained OPC insertion with geometry matching. Novel electrically driven OPC (ED-OPC) approaches based on the objective of minimizing the error in the current, rather than the EPE were also proposed in [21, 22]. Figure 1.11 illustrates the advantage of ED-OPC over SD-OPC. The first OPC scheme in the figure shows an SD-OPC while the second is an ED-OPC. ED-OPC ensures the electrical performance and its printed shapes are perhaps poor but still acceptable. On the other hand, though SD-OPC produces better printed shapes, its electrical performance is usually worse than that of ED-OPC [14, 21, 22, 26]. However, the problem of the existing ED-OPC approaches is that, the transistor drive current does not fully account for the desired circuit Instead, timing characteristics, such as propagation delay, are behavior. often a more desirable circuit behavior in digital logic gates [27]. The impacts of OPC and other lithography-induced imperfectness such as lens aberration and flare on the circuit performance have also been studied empirically and theoretically via various proposed evaluation methodologies [28–31]. Specifically, the circuit performance variability under different OPC settings were analyzed off-line to quantify the different OPC dissection algorithms [31]. A unidirectional link was established to connect the OPC

settings to post-OPC circuit performance but not otherwise.

Figure 1.11: Comparison of two OPC schemes: shape driven OPC vs. electrically driven OPC

This motivates the implementation of a new technique to complete the loop by feeding back the post-OPC timing performance and develop an ED-OPC algorithm to minimize the performance variation for a given design intent. A real-time performance extraction, instead of off-line analysis, is also desirable to accelerate the OPC engine.

#### **1.3.3** Convergence and Run-time

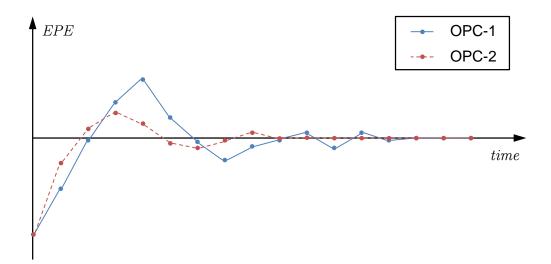

OPC convergence is another important issue in OPC mask design methodology. In model based OPC schemes, many iterations of the edge perturbations are necessary in order to converge to the desired result. Figure 1.12 illustrates the issue of convergence speed. The EPE step response of OPC-2 only takes 9 clock cycles to converge. However, the EPE step response of the OPC-1 is worse than OPC-2 in terms of number of iterations to converge. In some cases, oscillation and other instability issues can occur.

In IC fabrication, run-time means cost – long run-time halts the plant and causes loss in efficiency. Run-time in OPC is closely related to convergence of OPC. In model based OPC schemes, run-time is proportional to the number of loops to converge. In each loop, a computationally expensive lithography "print image" simulation is conducted. OPC with fast convergence can definitely reduce the number of iterations, and hence the length of run-time.

Figure 1.12: EPE step response of two OPC controllers

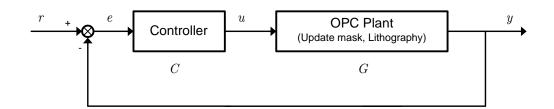

Therefore, there is a clear need to improve the convergence of OPC to reduce run-time and to avoid instability. Various techniques [32–35] have been proposed in the literature to improve the convergence of OPC. Figure 1.13 depicts the block diagram of a typical OPC controller. A controller is installed before the OPC plant to improve the convergence of OPC. However these techniques are primarily shape-driven OPC design methodologies and cannot be applied directly to electrically driven OPC platform. For this reason, a new technique is desirable to work with electrically driven OPC for better convergence.

Figure 1.13: A typical OPC controller block diagram

## **1.4** Contributions

In this thesis, new DFM approaches are proposed to address the aforementioned problems including mask cost, timing performance and convergence. The key contributions of the thesis are listed below.

# 1.4.1 Timing Performance Oriented Optical Proximity Correction

The previous sections have highlighted that the transistor drive current does not fully account for the desired circuit behavior, and timing characteristics are often a more desirable circuit behavior. Transistor drive-current-oriented methods [21, 22] lead to good transistor electrical performance but not good timing performance. In this work, a timing performance oriented OPC methodology (TPO-OPC) is developed to take timing performance into account in the OPC loop. The improvements are illustrated in Figure 1.14. This OPC methodology employs the integration of a lithography simulator and SPICE simulator to estimate the timing performance of a circuit after lithography. In contrast to conventional model based OPC, the idea of shape driven OPC is converted to electrically driven OPC. Specifically, instead of transistor drive current, timing performance is selected as the metric of electrical performance, since timing performance is a more direct indicator than transistor drive current. A transistor slicing model [36] is utilized to predict timing performance of non-rectangular gates of standard cell layouts. Masks are generated via iterative knowledge-based mask correction technique.

The feasibility of the proposed TPO-OPC is demonstrated via simulations by comparing its performance against conventional OPC schemes (typical EPE-OPC approaches) built in the commercial software. An industry standard open-source standard cell library is employed as the test circuit to conduct the comparison. Simulation results show that the proposed TPO-OPC approach outperforms the conventional scheme in two aspects. First, mask size in terms of MEBES file size is reduced by 24-36%. Second, timing accuracy in terms of propagation delay is improved by 2-4%.

Further improvements in convergence can be achieved by formulating the problem into a feedback control framework. The used of the PI controller is demonstrated in this work. The PI controller parameters can be chosen based on a heuristic approach according to different optical and lithography

Figure 1.14: Improvements of TPO-OPC from conventional model based OPC shown in Figure 1.6

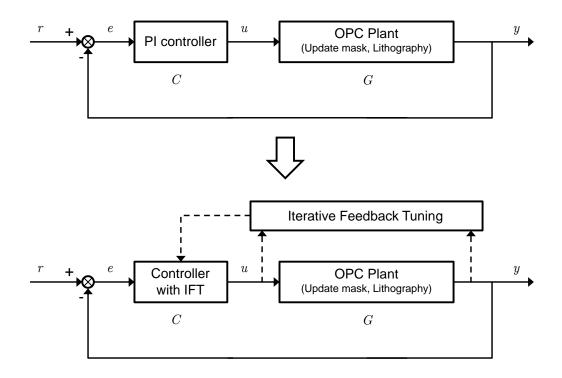

settings. A major limitation of such approaches is that the choice/tuning of the PI parameters is not a straight-forward task. In addition, as various optical and lithography settings changes for different processes, the PI controller parameters have to be re-tuned properly to avoid instability and increased correction time [37]. The difficulties in obtaining an accurate, low-ordered model of the lithography process means that most PID tuning formulas in literature cannot be applied. An iterative feedback tuning (IFT) algorithm [38–40] is used to address the above issues. This approach can adaptively tune the PI parameters as process setting changes and at the same time compute the tuning parameters for the optimal performance depending on the performance index. The control block diagram with IFT is depicted in Figure 1.15. Simulation results show that the proposed method outperforms the previous methods without feedback controller: the number of iterations is reduced by 80%.

Figure 1.15: Control block diagram of the proposed approach

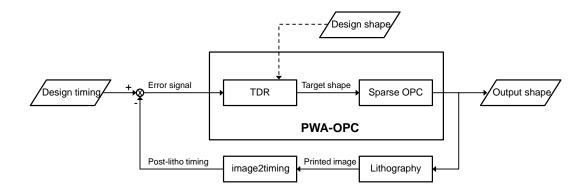

# 1.4.2 Process Window Aware Optical Proximity Correction

A complex complementary metal-oxide-semiconductor (CMOS) gate usually consists of a number of detail timing delays with different timing behaviors. This is the main obstacle which restricts previous methods from optimizing timing performance of a standard cell in a circuit. A process window aware OPC (PWA-OPC) technique using detail timing delay as the design metrics is designed and implemented. <sup>4</sup> The retargeting process before applying OPC is optimized. The process window is also considered in the algorithm.

<sup>&</sup>lt;sup>4</sup>Process window refers to the range of process parameters within which predefined specifications can be satisfied.

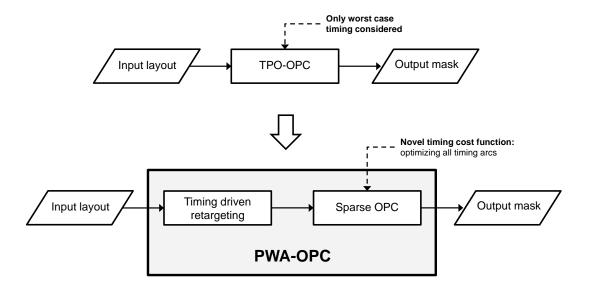

Advantages over previous methods are illustrated in the block diagram in Figure 1.16. A novel timing cost function is proposed (integrated in the timing driven retargeting part), which links timing domain electrical characteristics with shape domain mask patterns. Instead of optimizing only worst case delays, this method improves the timing performance of all cases. This implementation leads to better timing performance of the whole circuit under process variations. The main contributions of this work can be summarized as follows:

- Timing characteristics are employed as a direct metric for the proposed retargeting approach, which are not feasible in the earlier works in [21, 22] due to the complexity of circuit behavior. It was difficult to link the complex timing behavior with the printed mask pattern in the absence of the knowledge of the relationship between circuit timing performances and retargeting direction and amount. The implementation of this direct metric enables the algorithm to achieve better timing accuracy (improve by 2-5%) compared to other electrically driven OPC techniques [14, 21, 22].

- Due to the more accurate timing achieved through the proposed PWA-OPC method, the observed process window for the benchmark circuits is enlarged by 88% compared to previous methods. This directly translates to greater robustness against process variations.

- The aggressiveness of OPC can be reduced with a mask-cost-saving

strategy. Therefore a 73% mask reduction in terms of mask fragment count can be observed in this work.

Figure 1.16: Improvements of PWA-OPC

# 1.4.3 Optical Proximity Corrected Mask Simplification Using Over-designed Timing Slack

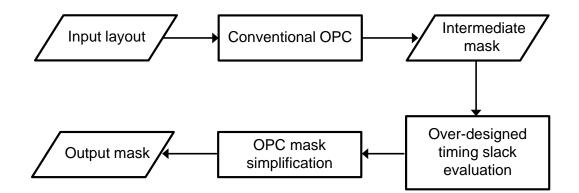

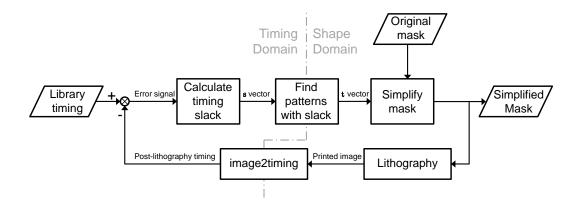

Due to the variations in semiconductor manufacturing process, ICs' working voltage and temperature (PVT), standard cells are usually designed conservatively with excessive timing slack. This over-designed timing slack has not been well utilized in the past. A method to simplify OPC mask using over-designed timing slack is proposed. This method is compatible with any existing OPC schemes, including SD-OPC and ED-OPC, and the block diagram is shown in Figure 1.17. The output mask of the existing OPC schemes is treated as an intermediate mask in the proposed method. This mask is then subjected to an over-designed timing slack evaluation, before the simplification is conducted. The over-designed timing slack can be extracted from the difference between post-OPC simulations and library data. A newly proposed timing cost function enables this work to link the complex circuit behavior of timing arcs with the printed mask pattern. A transistor can be labeled with "positive shape slack" if its related timing arc has positive timing slack. The mask simplification starts with an OPCed mask which is typically generated from a commercial dense OPC engine. An iterative algorithm is applied to simplify the mask patterns with "positive shape slack" labels. In each iteration, the timing slack will be updated from simulations on the simplified new mask. The final output mask is actually the mask of minimum complexity which still ensures post-OPC timing closure. This method is implemented on Nangate 45nm Open Cell Library [41] and the major contributions can be summarized as follows:

Figure 1.17: Block diagram of OPC mask simplification method

• Over-designed timing is utilized to reduce mask cost. Simulation result shows a 51% reduction in terms of polygon vertex count, which directly

relates with a significant reduction in mask cost.

- A timing cost function is adopted in work to exploit the relationship between timing slack and mask patterns. The use of the transistor sensitivity vector enables this work to selectively adjust the mask patterns without violating timing restrictions. Besides, a novel mask simplification algorithm is proposed in this work to reduce the number of fragments in the OPC mask.

- This mask simplification method is compatible with the current ASIC design flow and can be implemented directly after a conventional dense OPC process. No changes will be made on the designed logic, and no more feedback (redesign signal) to the design stage will be triggered.

# 1.4.4 Fast Optical Proximity Correction with Timing

#### **Optimization Ready Standard Cells**

As illustrated in Section 1.3, run-time in OPC is also a desirable metric. Run-time issue becomes severe when circuit size increases from one cell to hundreds of cells [42]. A fast cell-wise electrically driven OPC methodology is proposed to reduce run-time of TPO-OPC. The run-time for each cell of this OPC method (0.03sed) outperforms the fastest previous method (0.17sec) by 5 times. The overall block diagram is shown in Figure 1.18. The full layout is split into multiple single cells and TPO-OPC is conducted in parallel, for each type of standard cell. The standard cells after TPO-OPC, *i.e.* timing optimization ready standard cells (TORSCs), are stored in a lookup table. In the last step of OPC process, original layouts are substituted with the TORSCs. Run-time can be hugely saved with this method since full chip OPC is avoided.

Figure 1.18: Block diagram of fast OPC with TORSC

## 1.5 Organization of the Thesis

This thesis is organized as follows. Chapter 2 introduces the timing performance oriented optical proximity correction (TPO-OPC) methodology. The implementation of a feedback controller and an iterative feedback tuning algorithm is also presented in this chapter to improve OPC run-time and convergence. In Chapter 3, a process window aware OPC method is proposed for both standard cell and large full chip circuits. In Chapter 4, an investigation into timing yield is conducted. Based on the discovery of the relationship between timing yield and manufacturing cost, a method to reduce mask cost using over-designed timing slack is implemented. Chapter 5 presents the development of a cell-wise OPC to reduce run-time for circuit consisting of many repeated standard cells. Finally, conclusion and future work are provided in Chapter 6.

# Chapter 2

# Timing Performance Oriented Optical Proximity Correction

# 2.1 Introduction

As timing characteristics are often a more desirable circuit behavior, a timing performance oriented OPC methodology (TPO-OPC) is proposed. TPO-OPC uses timing performance, *i.e.* propagation delay of standard cells, as the design metric. A mask-cost-saving strategy is also employed in this work to reduce the complexity of OPC masks. Simulations on 45nm technology are conducted to validate this approach. Results show that the proposed TPO-OPC outperforms conventional EPE-OPC scheme in two aspects. Firstly, mask size in terms of MEBES data volume is also reduced by 24-36%. Secondly, timing accuracy is improved by 2-4%.

A feedback controller is also implemented to improve convergence speed and stability of the OPC algorithm. Simulation results show that the proposed method outperforms the previous method without feedback controller in terms of the number of iterations. As various optical and lithography settings change for different processes, the controller parameters have to be re-tuned properly to avoid instability. To re-tune controller parameters once settings change, the use of an iterative feedback tuning (IFT) method [38–40] is adopted in this chapter. Simulation shows that, with the IFT method, TPO-OPC process achieves better convergence time: the number of iteration is reduced from about 30 to 6 for most standard cells such as INV, NAND2 and NOR3.

This chapter is organized as follows. Section 2.2 provides an overview of conventional OPC methods. The TPO-OPC methodology, including overall flow, preliminary models and algorithms, is presented in Section 2.3. Section 2.4 discusses simulation results of the proposed TPO-OPC. Section 2.5 introduces the implementation of a feedback controller and the IFT algorithm to improve the convergence of OPC algorithms. Simulation results of the feedback controller and IFT algorithm are presented in Section 2.6. Finally, conclusions are drawn in Section 2.7.

# 2.2 Conventional OPC Methodologies

Conventional shape driven OPC (SD-OPC) which emphasizes on printed pattern matching with designed shape often results in extensive mask corrections and higher mask cost. In particular, it is possible that an over-corrected OPC mask would just slightly outperform a moderately corrected OPC mask but at a much higher cost. There is thus motivations to incorporate the design intent (circuit performance) into the OPC flow to avoid the aforementioned scenario. The literature consists of a number of OPC design that consider circuit performance matching [14, 21, 24, 25]. Gupta *et al.* [14] and Banerjee *et al.* [21] brought circuit performance information into their OPC flow, but they are primarily based on dense OPC schemes which still result in complicated OPC masks. In [25], a regular fabric option is provided to optimize macro layout templates, but this requires huge computational effort – all neighboring cells are combined into macro blocks under a restricted design rule – and results in significant layout changes. Zhang *et al.* [24] proposed an OPC method which considers circuit performance of the 1D cells in self-aligned double patterning lithography [43, 44], specifically for random-access memory (RAM) manufacturing, and hence cannot be applied directly in dominant patterning techniques for mainstream logic circuits.