# INGAAS N-MOSFETS WITH CMOS COMPATIBLE SOURCE/DRAIN TECHNOLOGY AND THE INTEGRATION ON SI PLATFORM

IVANA

NATIONAL UNIVERSITY OF SINGAPORE

2013

# INGAAS N-MOSFETS WITH CMOS COMPATIBLE SOURCE/DRAIN TECHNOLOGY AND THE INTEGRATION ON SI PLATFORM

IVANA

(B.Eng.(Hons.), NTU

# A THESIS SUBMITTED

# FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

# NUS GRADUATE SCHOOL FOR INTEGRATIVE SCIENCES AND ENGINEERING NATIONAL UNIVERSITY OF SINGAPORE

2013

Declaration

I hereby declare that the thesis is my original work and it has been written by me in its entirety. I have duly acknowledged all the sources of information which have been used in the thesis.

This thesis has also not been submitted for any degree in any university

#### previously.

20th October 20 13

Ivana

i

# Acknowledgements

The works in this thesis would have been impossible without the support and contribution of many individuals in many ways.

First and foremost, I would like to thank my research advisor, Dr. Yeo Yee Chia, for his advice and guidance throughout my graduate study at NUS. I have benefited immensely from his invaluable technical insight, knowledge, and experience shared. I would also like to thank him for his time and effort in guiding this thesis.

I would like to thank my co-advisor, Dr. Pan Jisheng from Institute of Materials Research and Engineering (IMRE-A\*STAR). He has always been there to give his instrumental advice and I have learned a lot through numerous discussions with him.

I am very grateful to have constructive support from many outstanding researchers and graduate students of Silicon Nano Device Laboratory (SNDL). Special thanks to Eugene Kong, Gong Xiao, Goh Kian Hui, Guo Huaxin, Dr. Samuel Owen, Sujith Subramanian, Zhang Xingui, Dr. Zhou Qian, and Zhu Zhu for their tremendous contribution in the works of this thesis. Dr. Zhou Qian's time and effort in providing TEM service on blanket samples are gratefully acknowledged. Special thanks also go to Dr. Pan Jisheng, Dr. Foo Yong Lim, and Dr. Zhang Zheng, I have benefited greatly from their vast experience in material characterization. I would also like to thank the team from NTU, Prof. Yoon Soon Fatt, Dr. Loke Wan Khai, Dr. Satrio Wicaksono, and Dr. Tan Kian Hua for their technical contribution as well as effort in the growth of substrates used in some of the works in this thesis. Without them, the works of this thesis would be impossible.

I would like to acknowledge technical staffs of IMRE who have provided services such as SIMS, XRD, HRTEM, and TEM on patterned samples. In addition, I would like to acknowledge Dr. Rinus Lee from SEMATECH for the useful discussions and material characterization supports given in some of the collaboration works.

To friends of SNDL, Guo Pengfei, Low Kain Lu, Phyllis Lim, Yang Yue, Zhan Chunlei, and many others, I am very grateful for their earnest help, useful discussions, and friendship throughout the journey. In addition, I would also like to extend my appreciation to technical staffs of SNDL, Mr. O Yan Wai Linn, Mr. Patrick Tang, and Ms. Yu Yi for their help in one way or another.

Finally, I would also like to extend my deepest gratitude to my mum, dad, brother, and Welly who have been very supportive, caring, and encouraging throughout my academic endeavors.

# **Table of Contents**

| Acknowledgements  | ii   |

|-------------------|------|

| Table of Contents | iv   |

| Summary           | viii |

| List of Tables    | X    |

| List of Figures   | xi   |

| List of Symbols   | xxi  |

## Chapter 1

### Introduction

| 1.1  | В  | ackground                                                       | .1 |

|------|----|-----------------------------------------------------------------|----|

| 1.2  | K  | ey Challenges of InGaAs MOSFETs                                 | .4 |

| 1.2. | .1 | Poor Interface Quality of InGaAs Gate Stack                     | .5 |

| 1.2. | .2 | Issues Related to The Scaling of InGaAs Transistors             | .6 |

| 1.2. | .3 | Lack of S/D Contact Technology Compatible with Si CMOS          | .7 |

| 1.2. | .4 | Issues Related to Heterogeneous Integration of InGaAs Transisto | rs |

|      |    | on Si Platform                                                  | 12 |

| 1.3  | R  | esearch Objectives                                              | 14 |

| 1.4  | Т  | hesis Organization                                              | 14 |

## Chapter 2

# CoInGaAs as a Novel Self-Aligned Metallic Source/Drain Material for Implant-less In<sub>0.53</sub>Ga<sub>0.47</sub>As n-MOSFETs

| 2.1 | Introduction | .16 | 5 |

|-----|--------------|-----|---|

|-----|--------------|-----|---|

| 2.2  | Co | InGaAs (   | Cont | tact Metal | llization Mod  | ule: C | CoInGaAs l | Formation, |    |

|------|----|------------|------|------------|----------------|--------|------------|------------|----|

|      | Ex | traction   | of   | Contact    | Resistivity,   | and    | Selective  | Wet-Etch   |    |

|      | Pr | ocess Dev  | velo | pment      |                |        |            |            | 17 |

| 2.2. | 1  | CoInGa     | As l | Formation  | 1              |        |            |            | 17 |

| 2.2. | 2  | Extracti   | on c | of Contact | Resistivity    |        |            |            | 22 |

| 2.2. | 3  | Selectiv   | e W  | et-Etch P  | rocess Devel   | opme   | nt         |            | 26 |

| 2.3  | D  | evice Inte | egra | tion and ( | Characterizati | on     |            |            | 34 |

| 2.4  | Su | mmary      |      |            |                |        |            |            | 40 |

### Chapter 3

# Material Characterization of Ni-InGaAs as a Contact Material for InGaAs Field-Effect Transistors

| 3.1 In | ntroduction41                                                                                                               |

|--------|-----------------------------------------------------------------------------------------------------------------------------|

| 3.2 Pl | hotoelectron Spectroscopy Study of Band Alignment at                                                                        |

| In     | nterface between Ni-InGaAs and InGaAs43                                                                                     |

| 3.2.1  | Sample Preparation and Methodology43                                                                                        |

| 3.2.2  | Work Function and Band Alignment Extraction46                                                                               |

| 3.3 C  | rystal Structure and Epitaxial Relationship of Ni-InGaAs                                                                    |

| Fi     | ilms formed on InGaAs by Annealing54                                                                                        |

| 3.3.1  | Sample Preparation                                                                                                          |

| 222    |                                                                                                                             |

| 3.3.2  | Ni-InGaAs Formation: Anneal Conditions, Elemental Composition,                                                              |

| 3.3.2  | Ni-InGaAs Formation: Anneal Conditions, Elemental Composition,<br>Material Structure and Thickness Ratio of Ni to Ni-InGaAs |

| 3.3.2  |                                                                                                                             |

## Chapter 4

# N-Channel InGaAs Field-Effect Transistors on Germanium-on-Insulator Substrates with Self-Aligned Ni-InGaAs Source/Drain

| 4.1 Introduction |  |

|------------------|--|

|------------------|--|

| 4.2 | Extraction of Contact Resistivity                       | 74 |

|-----|---------------------------------------------------------|----|

| 4.3 | InGaAs n-MOSFETs with Ni-InGaAs as Self-Aligned S/D     |    |

|     | material                                                | 77 |

| 4.4 | InGaAs n-MOSFETs Formed on Germanium-on-Insulator on Si |    |

|     | Substrate                                               | 84 |

| 4.5 | Pt Incorporation in Ni-InGaAs Metallization             | 90 |

| 4.6 | Summary                                                 | 96 |

|     |                                                         |    |

## Chapter 5

# Process Development for InGaAs-based Transistor and Laser Integration on GeOI on Si Substrates

| 5.1  | Introduction                                                                               |

|------|--------------------------------------------------------------------------------------------|

| 5.2  | Design Concept10                                                                           |

| 5.2. | 1 Layer Structure of Substrate for Transistor-Laser Integration10                          |

| 5.2. | 2 Device Layout Structure for Transistor and Laser Co-Integration.10                       |

| 5.2. | 3 Device Fabrication Process Flow of the InGaAs-based n-MOSFET                             |

|      | and QW Lasers10                                                                            |

| 5.3  | Electrical Performance of In <sub>0.7</sub> Ga <sub>0.3</sub> As Transistors Fabricated on |

|      | Grown Substrate for Transistor-Laser Integration11                                         |

| 5.4  | Impact of Growth Defects on The Electrical Performance of                                  |

|      | InGaAs transistor                                                                          |

| 5.5  | Summary13                                                                                  |

# Chapter 6

### **Conclusion and Future Works**

| 6.1  | С | Conclusion                                                          | 133      |

|------|---|---------------------------------------------------------------------|----------|

| 6.2  | С | Contributions of This Thesis                                        | 134      |

| 6.2. | 1 | CoInGaAs as a Novel Self-Aligned Metallic Source/Drain M            | Iaterial |

|      |   | for Implant-less In <sub>0.53</sub> Ga <sub>0.47</sub> As n-MOSFETs | 134      |

| 6.2.2     | Material Characterization of Ni-InGaAs as a Contact Material for |

|-----------|------------------------------------------------------------------|

|           | InGaAs Field-Effect Transistors135                               |

| 6.2.3     | N-Channel InGaAs Field-Effect Transistors on Germanium-on-       |

|           | Insulator Substrates with Self-Aligned Ni-InGaAs Source/Drain135 |

| 6.2.4     | Process Development for InGaAs-based Transistor and Laser        |

|           | Integration on GeOI on Si Substrates                             |

| 6.3 F     | uture Directions                                                 |

| Reference | e <b>s</b> 139                                                   |

| Appendix  | ζ.                                                               |

# **Summary**

Over the past few decades, scaling of Si transistors have contributed to advances in semiconductor technology. Further improvements in the drive current of Si transistors will soon be hindered by the fundamental limits imposed by the material properties of Si. InGaAs is a potential n-channel material for future highperformance CMOS applications for sub-11 nm technology nodes. This is mainly due to its low electron effective mass ( $m^*$ ) and high electron mobility. However, several technical challenges related to the lack of source/drain (S/D) contact technology compatible with Si CMOS and heterogeneous integration of InGaAs transistors on Si have to be overcome in order to take full advantage of its high mobility benefit. Even if these problems are addressed, physical limitations of the conventional metal interconnects are among other problems to be solved.

In this thesis, self-aligned metallization of InGaAs analogous to silicidation is explored. The reaction of Co and Ni with InGaAs to form M-InGaAs (M = Co or Ni) ohmic contact to n-type InGaAs was investigated. Selective wet etching process for the removal of Co or Ni over M-InGaAs was also developed. InGaAs n-MOSFETs with self-aligned M-InGaAs S/D were successfully demonstrated. The transistors exhibit good electrical characteristics. The results verify that silidice-like metallization concept can be adopted for InGaAs transistors.

This thesis also addresses challenges related to heterogeneous integration of InGaAs transistors on a Si platform. InGaAs n-MOSFETs were successfully

viii

integrated on GeOI on Si substrate by employing molecular beam epitaxy (MBE) through a graded-buffer growth approach. The InGaAs n-MOSFETs on GeOI on Si substrate have intrinsic transconductance value that compares very well with other reported state-of-the-art InGaAs transistors. This thesis demonstrates the feasibility of integrating InGaAs n-MOSFETs on Si substrate. Finally, this thesis presents research efforts directed towards realizing electronic-photonic device co-integration on Si platform as one possible solution to the bandwidth limitation of metal interconnect. Some key challenges associated with the co-integration of InGaAs-based transistors and lasers on GeOI on Si substrate were addressed. The work enables realization of InGaAs-based transistor and laser device at the intra-chip level.

# **List of Tables**

| Table 2.1. | Etch selectivity of Co over CoInGaAs in various etchants | .34 |

|------------|----------------------------------------------------------|-----|

| Table 3.1  | Comparison between Ni-InGaAs and CoInGaAs                | .72 |

# **List of Figures**

| Fig. 1.1  | (a) Schematic illustrating the source-to-drain leakage $(I_{SD,leak})$<br>and gate leakage $(I_G)$ of a transistor. (b) Band diagram across<br>the channel from source to drain of a transistor with long<br>(black lines) and short (dashed lines) $L_G$ . The drain voltage<br>$(V_{DS})$ affects the potential barrier $(q\Phi_B)$ at the source end of<br>transistor with small $L_G$ , resulting in barrier lowering. $E_c$ , $E_{Fermi}$ ,<br>and $E_v$ represent the conduction band, Fermi level, and valence<br>band, respectively                                   |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 1.2  | Electron effective mass of $In_xGa_{1-x}As$ versus indium composition [3]. $m_o$ is the free electron mass                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

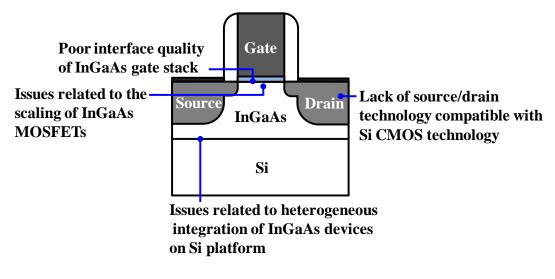

| Fig. 1.3  | Schematic illustrating key challenges faced by InGaAs MOSFETs4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

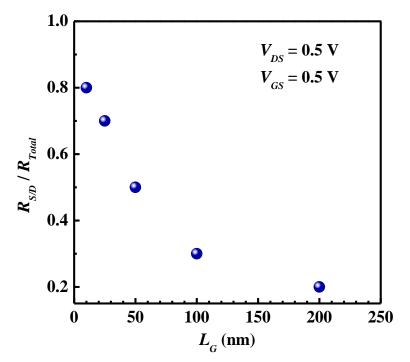

| Fig. 1.4  | Plot of $R_{S/D}/R_{Total}$ versus gate length $L_G$ for an advanced III-V transistor. The data point for $L_G = 50$ nm is from the reported experimental data in Ref. [31] taken at $V_{DS}$ and $V_{GS}$ of 0.5 V, while the rest of the data points were projected by the author by keeping $R_{S/D}$ constant and scaling the channel resistance in proportion to $L_G$                                                                                                                                                                                                   |

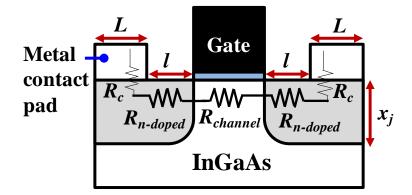

| Fig. 1.5  | Schematic of a InGaAs transistor with non-self-aligned S/D contacts, showing the various resistance components in a device. $R_c$ , $R_{n-doped}$ , and $R_{channel}$ are the contact resistance, the resistance of the n-doped source or drain, and the channel resistance, respectively. $x_j$ is the S/D junction depth and $l$ is the distance between the contact pad and the channel                                                                                                                                                                                    |

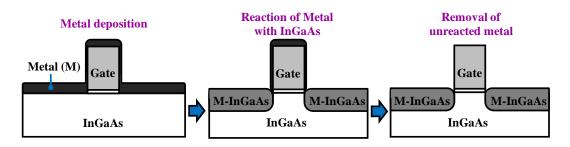

| Fig. 2.1. | An illustration of self-aligned silicidation-like metallization for<br>InGaAs transistor, which involves the reaction of a deposited<br>metal (M) with InGaAs forming a metallic material (denoted as<br>M-InGaAs) in the S/D region and the removal of the unreacted<br>metal                                                                                                                                                                                                                                                                                                |

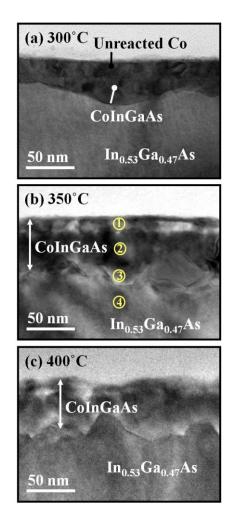

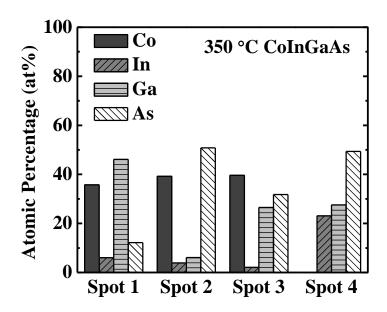

| Fig. 2.2. | TEM images of CoInGaAs formed by annealing 20 nm of Co on $In_{0.53}Ga_{0.47}As$ at (a) 300 °C, (b) 350 °C, and (c) 400 °C. Most of the as-deposited Co remained unreacted at 300 °C. In contrast, at 350 °C, the entire Co layer reacted with InGaAs to form a CoInGaAs layer. Energy Dispersive X-ray Spectroscopy (EDX) was performed at various spots in the CoInGaAs film formed at 350 °C, indicated by the spots labeled 1 to 4. After annealing Co on $In_{0.53}Ga_{0.47}As$ at 400 °C, a CoInGaAs layer with non-uniform thickness and a rough interface was formed. |

xi

| Fig. 2.3.  | EDX reveals the elemental atomic percentage found in localized spots at various parts of the CoInGaAs film formed at 350 °C, as indicated in Fig. 2.2(b). The EDX spot size is ~10 nm. It is observed that the CoInGaAs film comprises a Co-and Ga-rich layer on top of a Co- and As-rich layer20                                                                                                                                                                                                                     |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

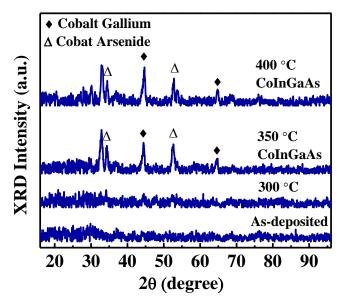

| Fig. 2.4.  | Grazing angle XRD spectra of Co on $In_{0.53}Ga_{0.47}As$ samples as-<br>deposited and annealed at 300, 350 and 400 °C. The presence<br>of CoGa and CoAs phases were observed in 350 and 400 °C<br>CoInGaAs film. The XRD characterization was carried out<br>through an external service contract in IMRE                                                                                                                                                                                                            |

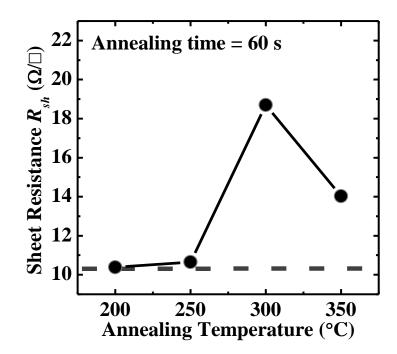

| Fig. 2.5.  | Sheet resistance $R_{sh}$ measured after annealing 20 nm of Co on In <sub>0.53</sub> Ga <sub>0.47</sub> As at various temperatures ranging from 200 to 350 °C for 60 s. The $R_{sh}$ of the sample annealed at 350 °C is that of the CoInGaAs film. The dashed line indicates the $R_{sh}$ of as-deposited Co                                                                                                                                                                                                         |

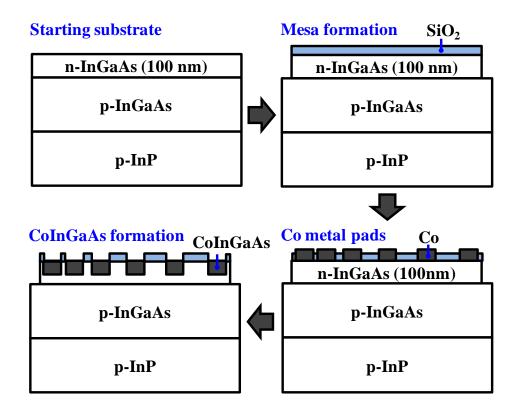

| Fig. 2.6.  | Schematics illustrating process flow for forming TLM structures, featuring mesa formation, formation of Co metal pads, and CoInGaAs formation23                                                                                                                                                                                                                                                                                                                                                                       |

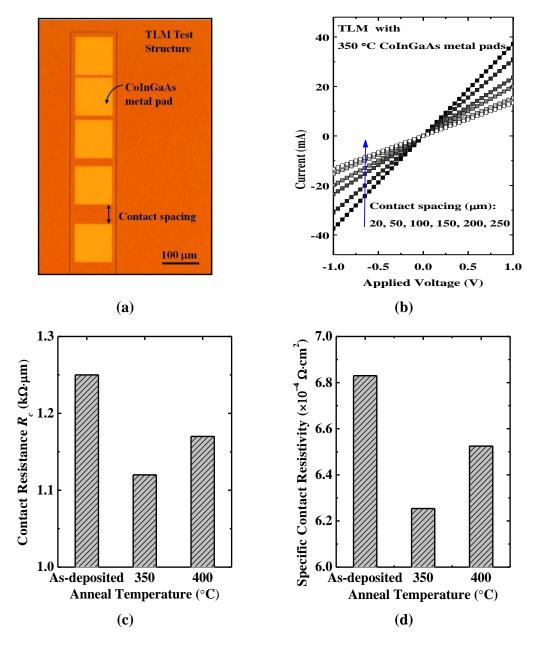

| Fig. 2.7.  | (a) Top-view optical microscope image of TLM structure with various contact spacings. This structure was used for the extraction of contact resistance and specific contact resistivity. (b) <i>I-V</i> curves obtained from a TLM structure with CoInGaAs metal contacts formed at 350 °C, showing ohmic behavior on $n^+$ -In <sub>0.53</sub> Ga <sub>0.47</sub> As. (c) Contact resistance $R_c$ and (d) specific contact resistivity of Co and CoInGaAs formed on $n^+$ -In <sub>0.53</sub> Ga <sub>0.47</sub> As |

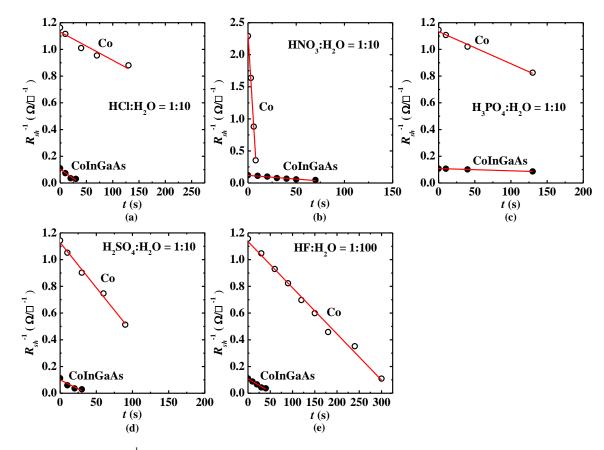

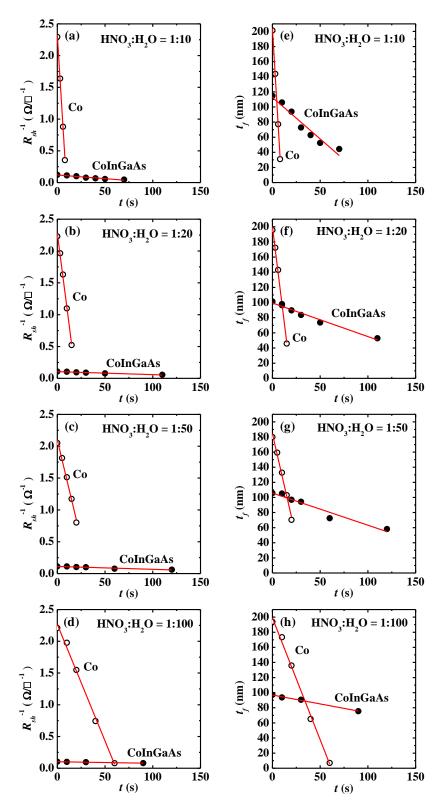

| Fig. 2.8.  | $R_{sh}^{-1}$ versus etch time <i>t</i> of Co and CoInGaAs films in various chemical solutions. $R_{sh}$ was recorded after each etch duration28                                                                                                                                                                                                                                                                                                                                                                      |

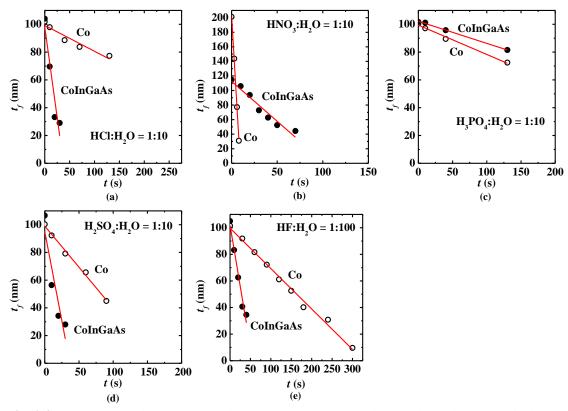

| Fig. 2.9.  | Co and CoInGaAs thickness $(t_f)$ versus etch time $(t)$ in various chemical solutions                                                                                                                                                                                                                                                                                                                                                                                                                                |

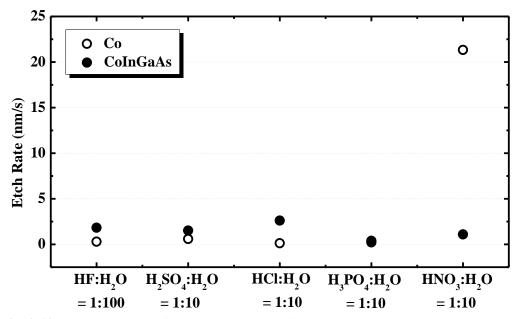

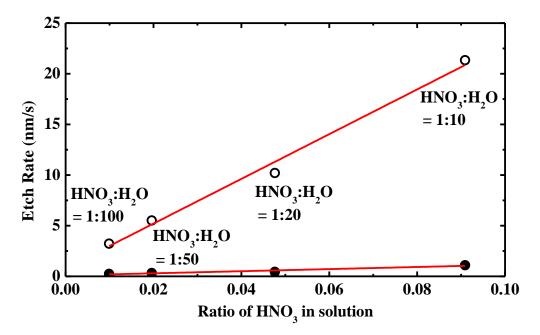

| Fig. 2.10. | Etch rate of Co and CoInGaAs films in various etchants. The gray and black symbols are the etch rate of Co and CoInGaAs, respectively                                                                                                                                                                                                                                                                                                                                                                                 |

| Fig. 2.11. | $R_{sh}$ versus $t$ (a-d) and the corresponding Co and CoInGaAs thickness $(t_f)$ versus $t$ (e-h) in various concentrations of HNO <sub>3</sub> solution. $R_{sh}$ was recorded after an etch duration                                                                                                                                                                                                                                                                                                               |

| Fig. 2.12. | Etch rate of Co and CoInGaAs films in various concentrations of HNO <sub>3</sub> solutions. The black open and solid symbols are the etch rate of Co and CoInGaAs, respectively. The HNO <sub>3</sub> :H <sub>2</sub> O ratio of 1:100, 1:50, 1:20, and 1:10 correspond to the molarity of 0.16, 0.31, 0.78, and 1.57 M, respectively                                                                                                                                                                                 |

xii

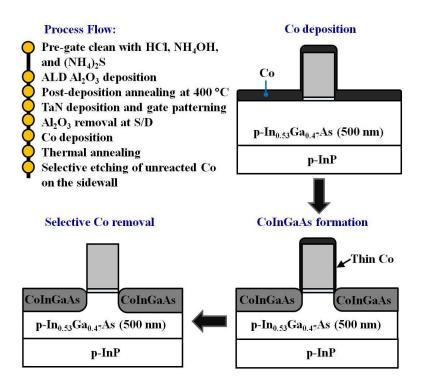

| Fig. 2.13. | Process flow for forming $In_{0.53}Ga_{0.47}As$ n-MOSFET with self-<br>aligned CoInGaAs metallic S/D. The schematics show the key<br>process steps, including Co deposition, reaction with InGaAs,<br>and selective Co removal                                                                                                                                                                                                                                     | 5  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

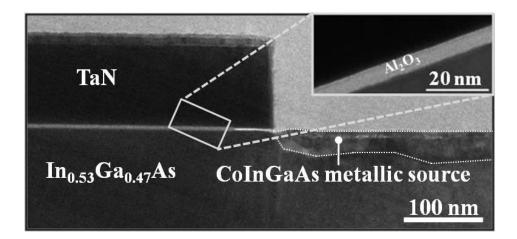

| Fig. 2.14. | Cross-sectional TEM images of $In_{0.53}Ga_{0.47}As$ MOSFET with<br>CoInGaAs metallic S/D formed using 350 °C 60 s anneal.<br>Annealing ~10 nm of Co formed 28-35 nm of CoInGaAs. The<br>inset shows a zoomed-in view of the TaN/Al <sub>2</sub> O <sub>3</sub> /In <sub>0.53</sub> Ga <sub>0.47</sub> As<br>gate stack. The physical thickness of the Al <sub>2</sub> O <sub>3</sub> gate dielectric<br>is ~6 nm                                                  | 6  |

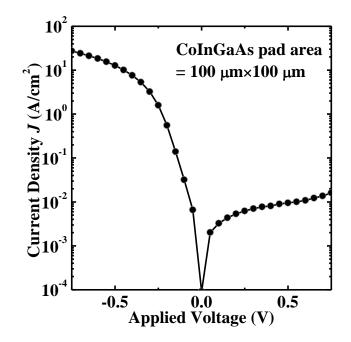

| Fig. 2.15. | CoInGaAs/p-In <sub>0.53</sub> Ga <sub>0.47</sub> As junction shows rectifying behavior.<br>Voltage was applied to the CoInGaAs while the InP substrate<br>was grounded                                                                                                                                                                                                                                                                                             | 57 |

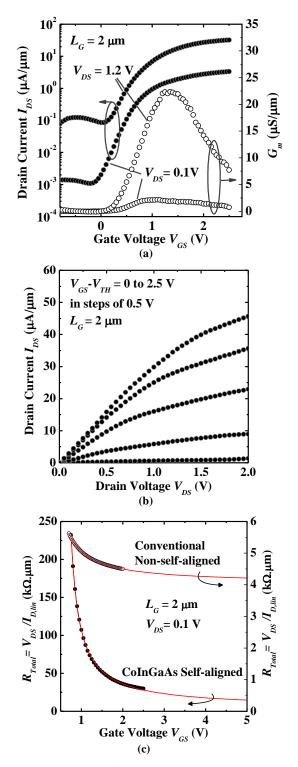

| Fig. 2.16. | (a) $I_{DS}$ - $V_{GS}$ curves of a In <sub>0.53</sub> Ga <sub>0.47</sub> As n-MOSFET with self-<br>aligned CoInGaAs S/D. $G_m$ is referred to the right axis. (b) $I_{DS}$ -<br>$V_{DS}$ plot for the same In <sub>0.53</sub> Ga <sub>0.47</sub> As n-MOSFET. Gate<br>overdrive $V_{GS}$ - $V_{TH}$ is varied from 0 to 2.5 V in steps of 0.5 V.<br>(c) Series resistance of transistors with conventional non-self-<br>aligned S/D and CoInGaAs self-aligned S/D | 59 |

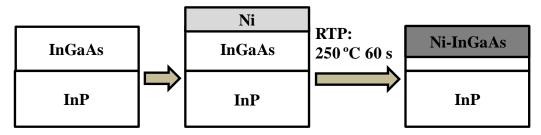

| Fig. 3.1.  | Schematics showing the preparation process of Ni-InGaAs samples4                                                                                                                                                                                                                                                                                                                                                                                                   | 4  |

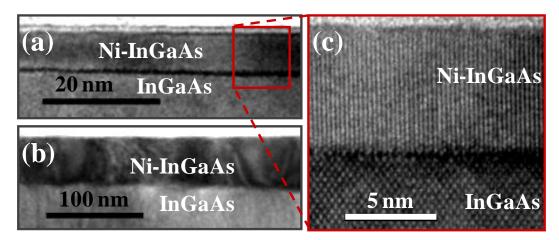

| Fig. 3.2.  | Transmission electron microscopy (TEM) images of (a) thin<br>and (b) thick Ni-InGaAs formed on $In_{0.53}Ga_{0.47}As$ substrate. (c)<br>The high resolution image shows periodic arrangement of<br>atoms in Ni-InGaAs layer, demonstrating good crystalline<br>quality                                                                                                                                                                                             | -5 |

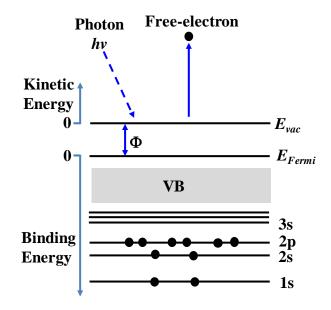

| Fig. 3.3.  | Schematic showing incoming photon causing photoemission of electron from a sample. Depending on the photon <i>hv</i> energy, free-electron near valence band (VB) down to core-level can be emitted4                                                                                                                                                                                                                                                               | 7  |

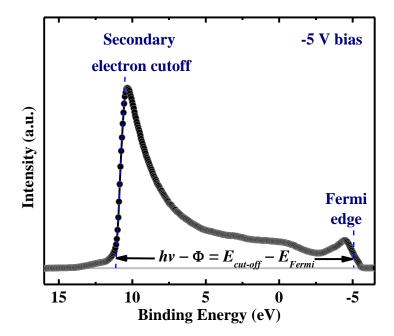

| Fig. 3.4.  | He I ( $hv = 21.2 \text{ eV}$ ) UPS spectra of thick Ni-InGaAs formed on In <sub>0.53</sub> Ga <sub>0.47</sub> As. A -5 V bias was applied to the Ni-InGaAs layer. Fermi edge position was determined as the center of the slope as indicated by vertical line. Secondary electron cut-off position was determined from the intercept of the slope with the background level (horizontal gray line)4                                                               | 8  |

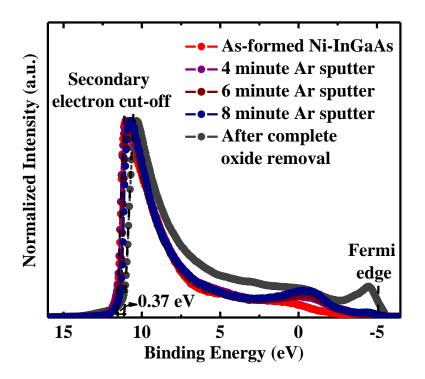

| Fig. 3.5.  | He I ( $hv = 21.2 \text{ eV}$ ) UPS spectra of as-formed, after Ar sputter,<br>and after complete oxide removal of thick Ni-InGaAs formed<br>on In <sub>0.53</sub> Ga <sub>0.47</sub> As. A -5 V bias was applied to the Ni-InGaAs<br>layer. The maximum difference in the spectra width is 0.37 eV4                                                                                                                                                               | 9  |

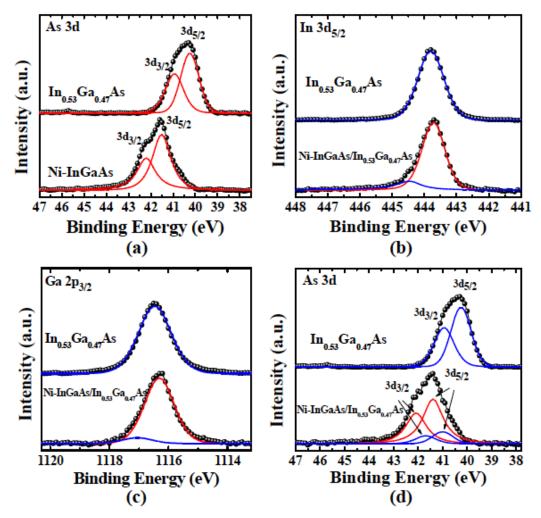

| Fig. 3.6.  | Normalized XPS core-level spectra of (a) As 3d for bulk Ni-<br>InGaAs (bottom) and $In_{0.53}Ga_{0.47}As$ (top) samples. Comparison<br>of (b) In $3d_{5/2}$ , (c) Ga $2p_{3/2}$ , and (d) As 3d from Ni-<br>InGaAs/In_{0.53}Ga_{0.47}As interface sample (bottom) and from bulk<br>In_{0.53}Ga_{0.47}As (top). The red and blue fitted curves correspond<br>to signal coming from Ni-InGaAs and In_{0.53}Ga_{0.47}As,<br>respectively. The In $3d_{5/2}$ , Ga $2p_{3/2}$ , and As 3d peaks at the<br>interface resides 0.75 eV higher than that of In_{0.53}Ga_{0.47}As<br>substrate determined by the difference between the blue fitted<br>curves. | 50 |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

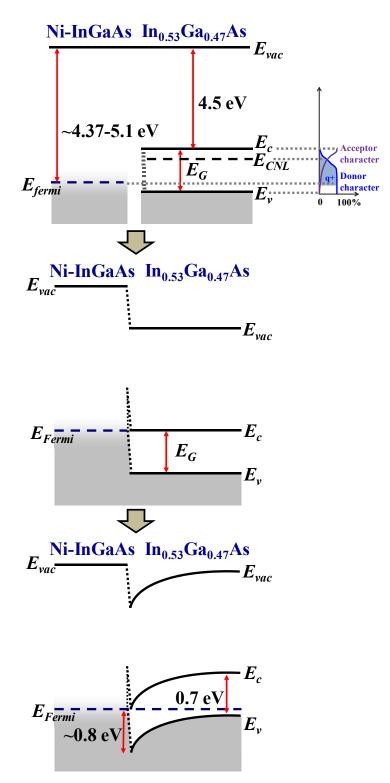

| Fig. 3.7.  | Schematics of energy band diagram showing interface dipole (dotted band) or Fermi level pinning could lead to a high electric field at the NiInGaAs-InGaAs interface. The band alignment of Ni-InGaAs in contact with In <sub>0.53</sub> Ga <sub>0.47</sub> As substrate is consistent with XPS results.                                                                                                                                                                                                                                                                                                                                             | 53 |

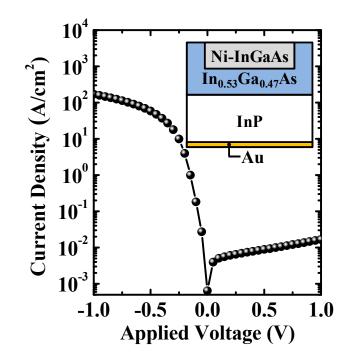

| Fig. 3.8.  | <i>I-V</i> characteristics measured between Ni-InGaAs pad and Au back-side contact to InP of a diode structure (inset). The dimension of Ni-InGaAs pad area is $100 \ \mu m \times 100 \ \mu m$ . The Ni-InGaAs/p-In <sub>0.53</sub> Ga <sub>0.47</sub> As junction shows rectifying behavior                                                                                                                                                                                                                                                                                                                                                        | 54 |

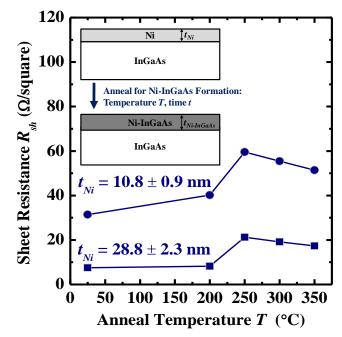

| Fig. 3.9.  | Sheet resistances $R_{sh}$ of Ni-on-InGaAs samples annealed at various temperatures for a fixed time of 60 s. The inset shows an illustration of the formation of Ni-InGaAs (bottom) by annealing as-deposited Ni-on-InGaAs (top) at temperature $T$ for time $t$ .                                                                                                                                                                                                                                                                                                                                                                                  | 56 |

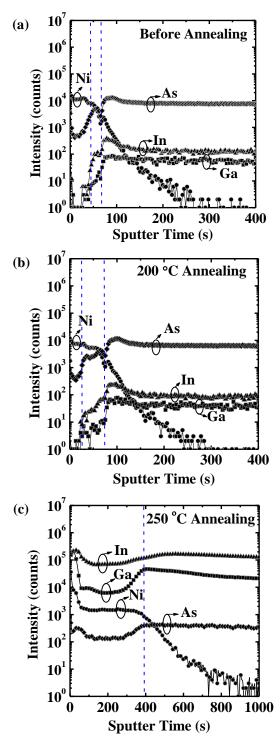

| Fig. 3.10. | Negative ion Secondary Ion Mass Spectrometry (SIMS) depth<br>profiles of Ni, In, Ga, and As for ~11 nm Ni on InGaAs (a)<br>before and (b) after annealing at 200 °C for 60 s. The dotted<br>lines represent the region where Ni and InGaAs could have<br>intermixed even before annealing. (c) Ni, In, Ga, and As<br>positive ion SIMS depth profiles of Ni-InGaAs formed at<br>250 °C for 60 s. The Ni-InGaAs/InGaAs interface is<br>represented by dotted line.                                                                                                                                                                                    | 58 |

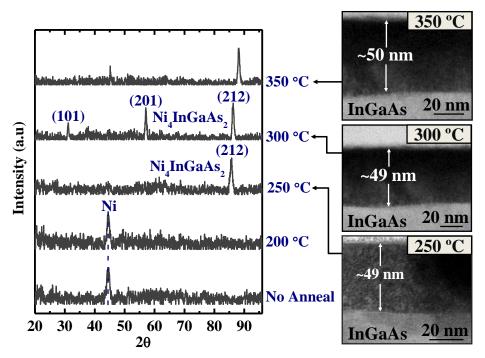

| Fig. 3.11. | XRD General Area Detector Diffraction System (GADDS) integrated diffraction intensity as a function of 2θ (left). TEM images showing the thicknesses of films formed at 250, 300, and 350 °C (right).                                                                                                                                                                                                                                                                                                                                                                                                                                                | 60 |

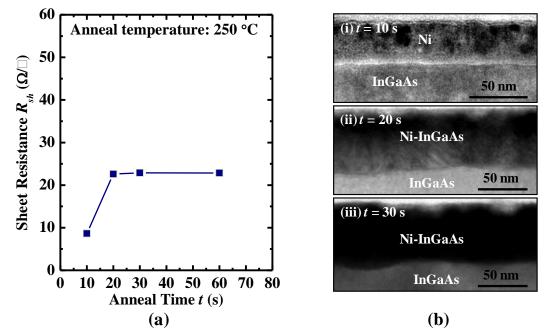

| Fig. 3.12. | (a) Time evolution of $R_{sh}$ for ~28 nm of Ni deposited on InGaAs annealed at 250 °C. (b) Transmission electron microscopy (TEM) images of Ni-on-InGaAs annealed at 250 °C for (i) 10 s, (ii) 20 s, and (iii) 30 s.                                                                                                                                                                                                                                                                                                                                                                                                                                | 60 |

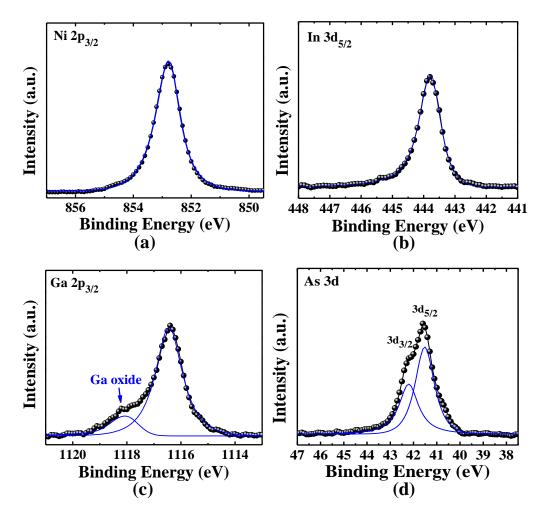

| Fig. 3.13. | X-ray Photoelectron Spectroscopy (XPS) spectra of (a) Ni $2p_{3/2}$ , (b) In $3d_{5/2}$ , (c) Ga $2p_{3/2}$ , and (d) As 3d. The elemental                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

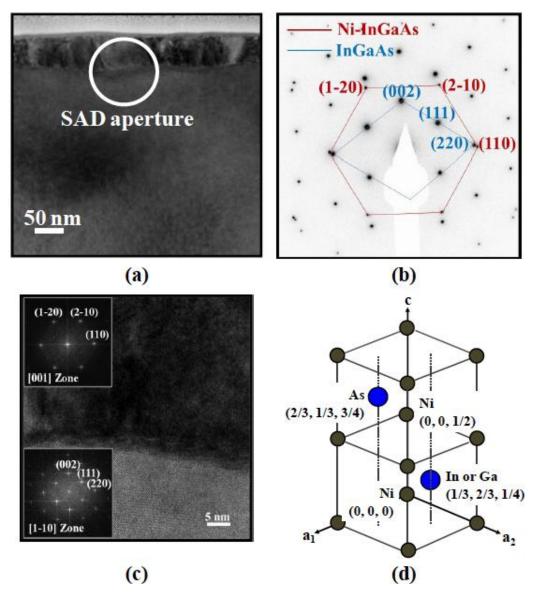

| Fig. 3.14. | composition of Ni-InGaAs was determined from the area under<br>the fitted peaks (blue lines) excluding the Ga oxide peak62<br>(a) TEM image of Ni-InGaAs/InGaAs sample where selective                                                                                                                                                                                                                                                      |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            | area diffraction (SAD) pattern shown in (b) was recorded. The<br>SAD aperture, as indicated by a circle, has a diameter of 150<br>nm. (c) High resolution TEM image of Ni-InGaAs/InGaAs<br>with insets showing the corresponding diffraction patterns<br>extracted by Fast Fourier Transform. (d) Unit cell of Ni-<br>InGaAs phase, illustrating the NiAs (B8) structure of Ni-<br>InGaAs                                                   |

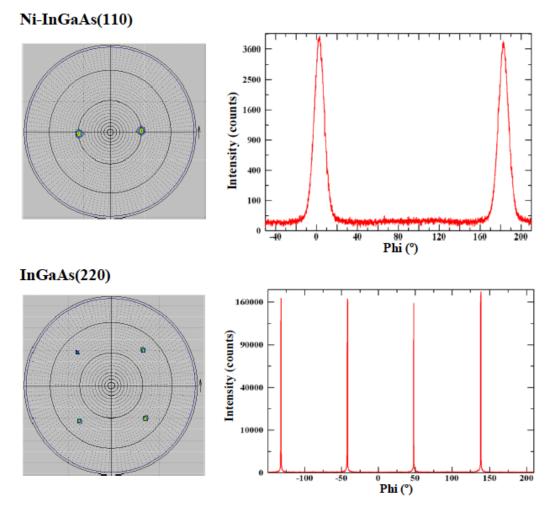

| Fig. 3.15. | X-ray pole figure (left) and the corresponding phi-scan (right) of Ni-InGaAs and InGaAs obtained from (110) and (220) diffraction planes                                                                                                                                                                                                                                                                                                    |

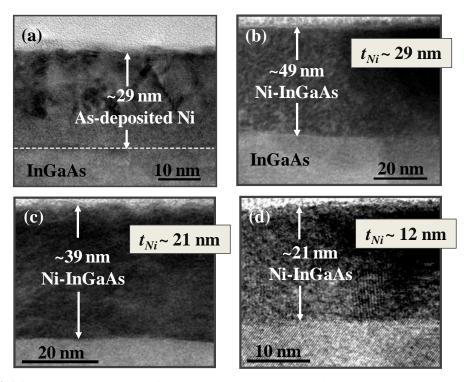

| Fig. 3.16. | TEM images of (a) ~29 nm as-deposited Ni on InGaAs, and (b) ~49 nm, (c) ~39 nm and (d) ~21 nm of Ni-InGaAs formed by annealing ~29 nm, ~21 nm and ~12 nm of as-deposited Ni on InGaAs, respectively                                                                                                                                                                                                                                         |

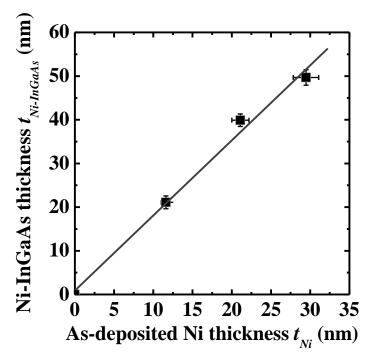

| Fig. 3.17. | Plot of Ni-InGaAs thickness versus as-deposited Ni thickness,<br>showing a linear relationship. The thickness ratio of ~1 : 1.7<br>for Ni to Ni-InGaAs is obtained by linear fitting. Thicknesses<br>of Ni-InGaAs and Ni were determined from TEM images                                                                                                                                                                                    |

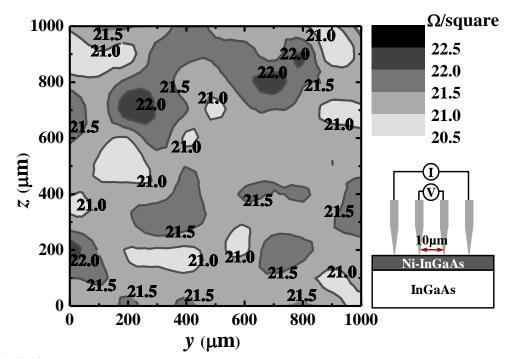

| Fig. 3.18. | Contour plot of sheet resistance of ~46-nm-thick Ni-InGaAs film in a 1 mm × 1 mm area as obtained by microscopic four-<br>point probe. In the scale bar (top right), sheet resistance values range from 20.5 $\Omega$ /square to 22.5 $\Omega$ /square, with an interval of 0.5 $\Omega$ /square. A schematic diagram (bottom right) shows the microscopic four-point probe with probe spacing of ~10 $\mu$ m used for $R_{sh}$ measurement |

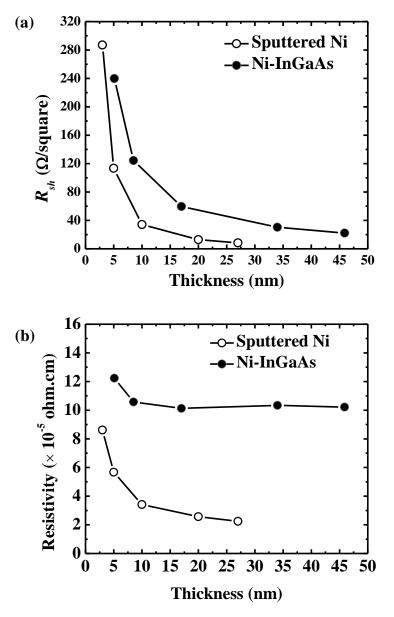

| Fig. 3.19. | (a) $R_{sh}$ of Ni and Ni-InGaAs as a function of thickness. (b) The electrical resistivity of Ni and Ni-InGaAs extracted from their $R_{sh}$ values and thicknesses. The thickness of Ni-InGaAs is obtained by multiplying the as-deposited Ni thickness and the thickness ratio (1.7) of Ni to Ni-InGaAs                                                                                                                                  |

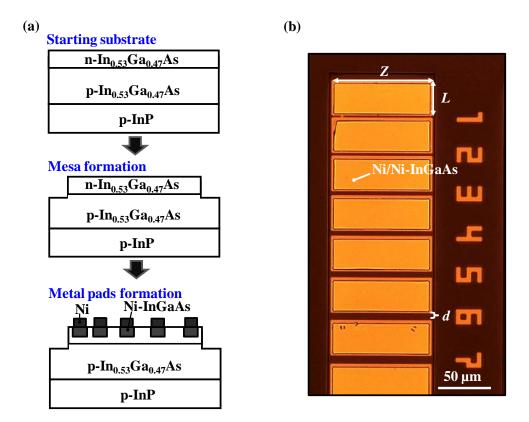

| Fig. 4.1.  | (a) Schematics of TLM test structure fabrication featuring mesa formation, Ni-InGaAs formation, and thick Ni metal pads deposition. (b) Optical microscope image showing the top view of the fabricated TLM test structure. <i>L</i> and <i>Z</i> are the length and width of Ni-InGaAs metal pad, respectively, while <i>d</i> is the distance between two adjacent metal pads                                                             |

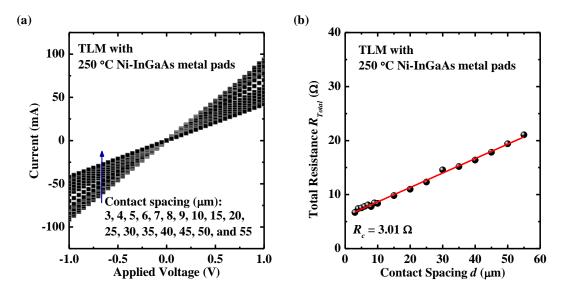

| Fig. 4.2.  | (a) <i>I-V</i> curves obtained from a TLM test structure with Ni-InGaAs metal contacts formed at 250 °C, showing ohmic                                                                                                                                                                                                                                                                                                                      |

|            | behavior on $n-In_{0.53}Ga_{0.47}As$ . (b) Total resistance versus Ni-<br>InGaAs contact spacing determined from the <i>I-V</i> curves77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

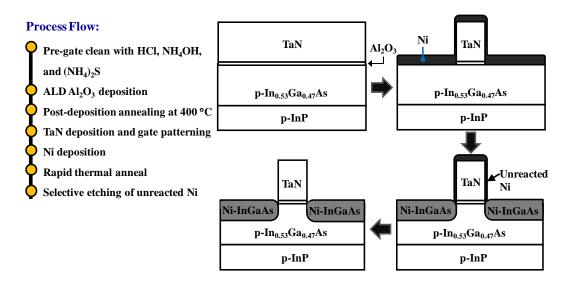

| Fig. 4.3.  | Process flow and schematics of the key process steps in the fabrication of $In_{0.53}Ga_{0.47}As$ n-MOSFETs with self-aligned Ni-InGaAs metal S/D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

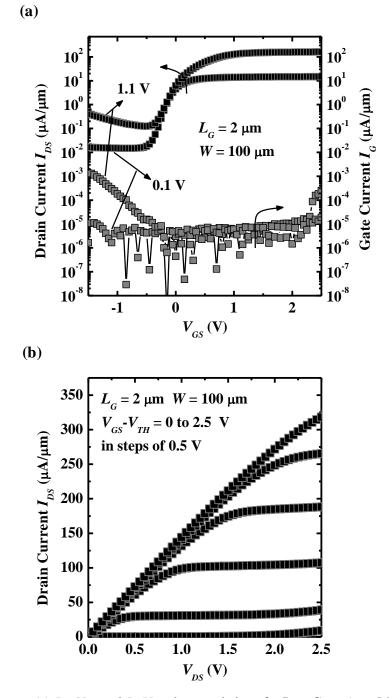

| Fig. 4.4.  | (a) $I_{DS}$ - $V_{GS}$ and $I_G$ - $V_{GS}$ characteristics of a In <sub>0.53</sub> Ga <sub>0.47</sub> As n-MOSFET with self-aligned Ni-InGaAs S/D. The gate length and gate width are 2 µm and 100 µm, respectively. The gate current is referred to the right axis. (b) $I_{DS}$ - $V_{DS}$ characteristics for the same In <sub>0.53</sub> Ga <sub>0.47</sub> As n-MOSFET at gate overdrive $V_{GS}$ - $V_{TH}$ from 0 to 2.5 V in steps of 0.5 V                                                                                                                                                                                                                                                                                                                     |

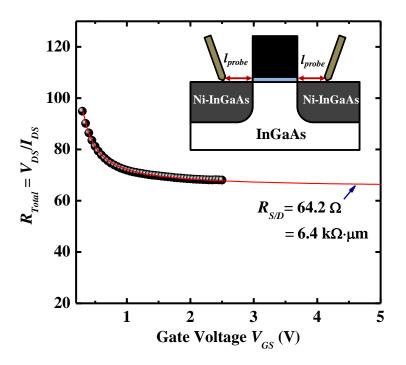

| Fig. 4.5.  | Total resistance ( $R_{Total} = V_{DS}/I_{DS}$ ) as a function of gate voltage<br>of the same device as in Fig. 4.4. $I_{DS}$ is the drain current in the<br>linear regime ( $V_{DS} = 0.1$ V). Higher applied gate voltage<br>causes the channel resistance to reduce which leads to a<br>reduction in the total resistance of the device. The resistance at<br>high $V_{GS}$ gives the $R_{S/D}$ value                                                                                                                                                                                                                                                                                                                                                                  |

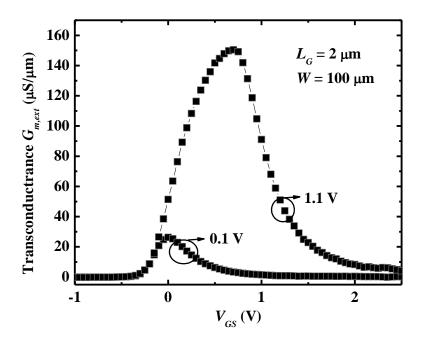

| Fig. 4.6.  | Extrinsic transconductance $G_{m,ext}$ of the same device as in Fig. 4.4 at $V_{DS}$ of 0.1 and 1.1 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

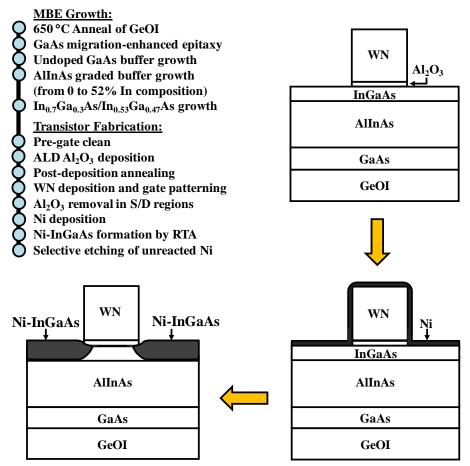

| Fig. 4.7.  | Process flow used in this experiment, including the growth of<br>InGaAs-on-GeOI and the fabrication of n-channel InGaAs<br>metal oxide semiconductor field-effect transistor (MOSFET).<br>Schematics on the right illustrate the self-aligned metallic S/D<br>formation scheme employed in the fabrication of transistor on<br>the MBE grown substrate                                                                                                                                                                                                                                                                                                                                                                                                                    |

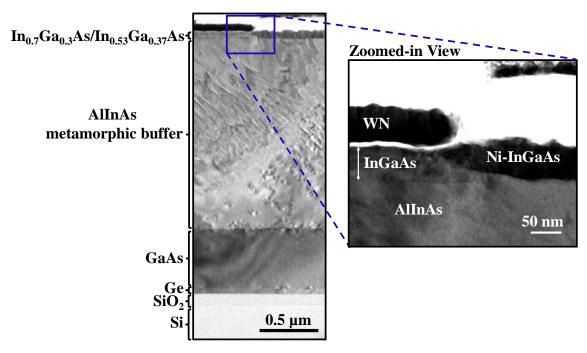

| Fig. 4.8.  | Cross-sectional TEM image of InGaAs-on-GeOI structure with $In_{0.7}Ga_{0.3}As$ channel n-MOSFET fabricated on it (left). High-resolution TEM image of the $In_{0.7}Ga_{0.3}As$ n-MOSFET with self-aligned Ni-InGaAs metallic S/D (right)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

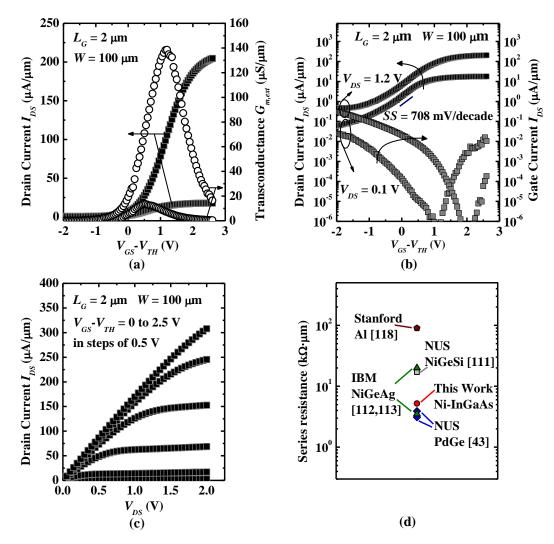

| Fig. 4.9.  | (a) $I_{DS}$ versus gate overdrive ( $V_{GS}$ - $V_{TH}$ ) of an n-MOSFET with In <sub>0.7</sub> Ga <sub>0.3</sub> As channel and Ni-InGaAs metallic S/D at $V_{DS} = 0.1$ and 1.2 V. The gate length of the device is 2 µm and the gate width is 100 µm. Transconductance $G_{m,ext}$ characteristic is referred to the right axis. The peak $G_{m,ext}$ at $V_{DS} = 1.2$ V is 138.5 µS/µm. (b) Log ( $I_{DS}$ ) and ( $I_G$ ) versus $V_{GS}$ - $V_{TH}$ of the same device at $V_{DS} = 0.1$ and 1.2 V (c) $I_{DS}$ - $V_{DS}$ plot of the same device at various gate overdrives ( $V_{GS}$ - $V_{TH}$ ) from 0 to 2.5 V. (d) Series resistance of InGaAs n-MOSFET with Ni-InGaAs source/drain is compared with other reported series resistance of InGaAs n-MOSFETs |

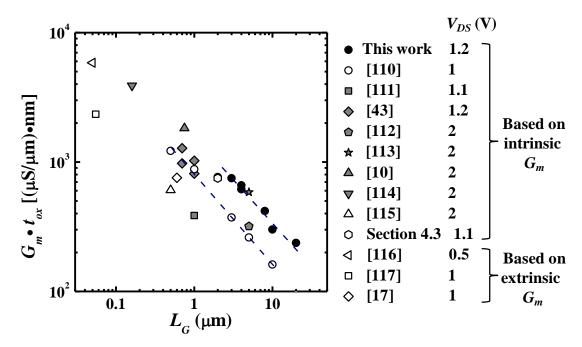

| Fig. 4.10. | Normalized peak transconductance $G_m t_{ox}$ is plotted as a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

**Fig. 4.10.** Normalized peak transconductance  $G_m t_{ox}$  is plotted as a function of gate length ( $L_G$ ). Device performance obtained in

|            | this work (black solid symbols) is compared with those<br>reported in other $In_xGa_{1-x}As$ channel n-MOSFETs in the<br>literature (gray solid symbols for $x = 0.7$ , open symbols for $x =$<br>0.53). Note that data from Ref. [17],[116]-[117] are extrinsic<br>$G_m$ , while those from the other references are intrinsic $G_m$ . The<br>$G_m$ data are from various $V_{DS}$ : $V_{DS} = 0.5$ V for Ref. [116], $V_{DS}$<br>= 1 V for Refs. [17],[110],[117], $V_{DS} = 1.1$ V for Ref. [111],<br>$V_{DS} = 1.2$ V for Ref. [43] and this work, and $V_{DS} = 2$ V for<br>Refs. [10],[112]-[115]. $G_m.t_{ox}$ obtained in this work is<br>significantly higher than those of $In_{0.53}Ga_{0.47}As$ MOSFETs<br>fabricated on Si (open circles) [110]. The connecting dashed<br>lines act only as a guide |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

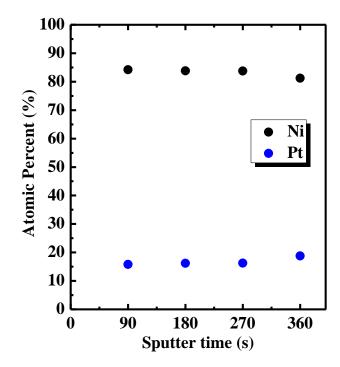

| Fig. 4.11. | XPS depth profiling across co-sputtered NiPt film. Pt concentration is ~15 at%, uniformly distributed in the film. The XPS characterization was done in IMRE through service contract                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Fig. 4.12. | (a) Sheet resistances $R_{sh}$ of NiPt (blue symbols) and Ni (black symbols) on p-type InGaAs samples annealed at various temperatures for a fixed time of 60 s. (b) Surface roughness of the annealed NiPt and Ni on InGaAs. The as-deposited NiPt and Ni films have similar RMS surface roughness of ~0.4 nm as represented by dotted lines                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Fig. 4.13. | Surface morphology of (a) as-deposited Ni and NiPt films, (b) 250 °C annealed Ni and NiPt films, (c) 500 °C formed NiPt-InGaAs and (d) Ni-InGaAs films in a 10 $\mu$ m × 10 $\mu$ m area obtained by AFM scan. The cross-section surface topology profile along section line A-A' is shown for 500 °C formed films                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

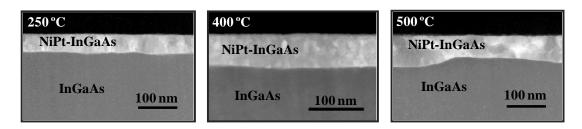

| Fig. 4.14. | Cross-sectional TEM of NiPt on InGaAs annealed at 250, 400, and 500 °C95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

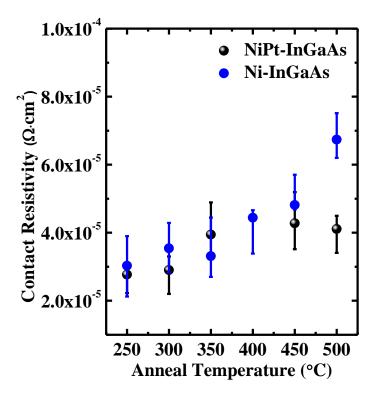

| Fig. 4.15. | Contact resistivity $\rho_c$ versus anneal temperature for NiPt-<br>InGaAs and Ni-InGaAs on n-type InGaAs. Same doping<br>concentration of ~2×10 <sup>19</sup> cm <sup>-3</sup> was used for a fair comparison95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

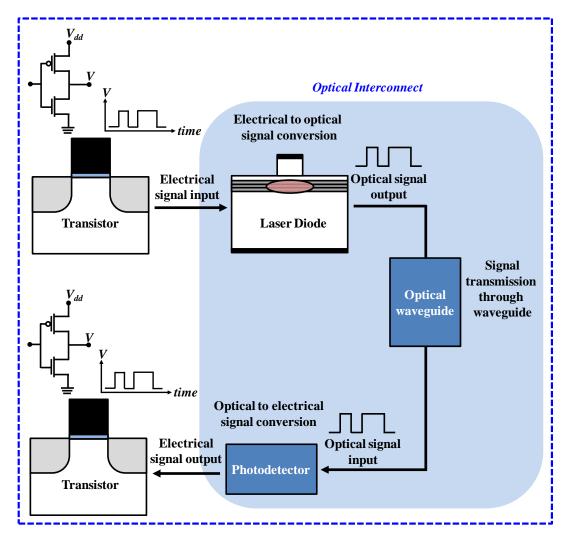

| Fig. 5.1.  | An illustration of electronic and photonic device integrated<br>system. The optical interconnect constitutes photonic devices<br>such as laser diode, optical waveguide, and photodetector.<br>Electrical output from transistor (e.g. of an inverter) is sent<br>through a laser diode where the electrical signal is converted to<br>optical signal. The optical signal is transmitted through a<br>waveguide and received by a photodetector to convert the<br>optical signal back to electrical signal that is received by<br>transistor of another inverter at the other end                                                                                                                                                                                                                                |

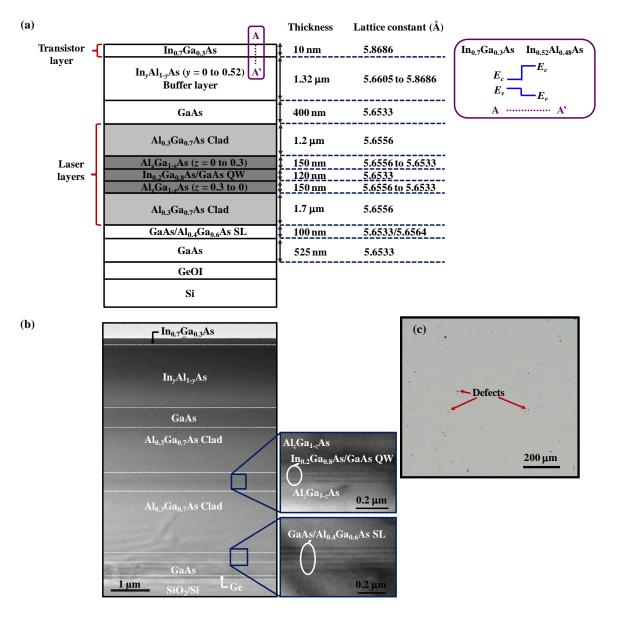

| Fig. 5.2. | (a) Structure of epilayers grown on GeOI substrate for<br>transistor-laser integration. (b) Transmission electron<br>microscopy (TEM) image of the grown substrate. (c) Optical<br>microscopy image showing the surface of the grown substrate<br>where defects are observed                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

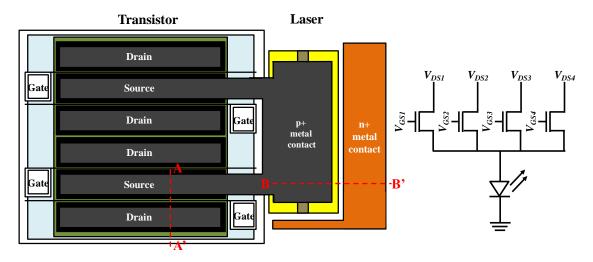

| Fig. 5.3. | (Left) schematic showing the top view of a transistor-laser<br>integrated circuit layout. The author involved in the discussion<br>on the mask layout design although the drawing of the actual<br>mask layout was not done by the author. Line A-A' and B-B'<br>are cross-section along which the schematics in Fig. 5.4 and<br>5.6 were drawn. The corresponding symbols (right) illustrate<br>the connection of the four transistors to a laser                                                                                                                                                                                                                                                                  |

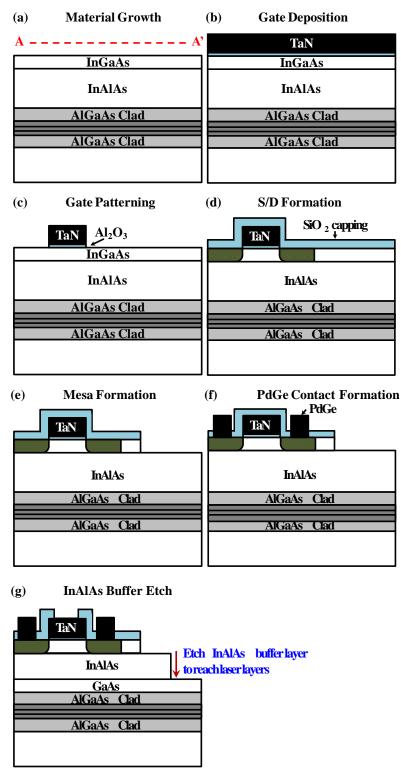

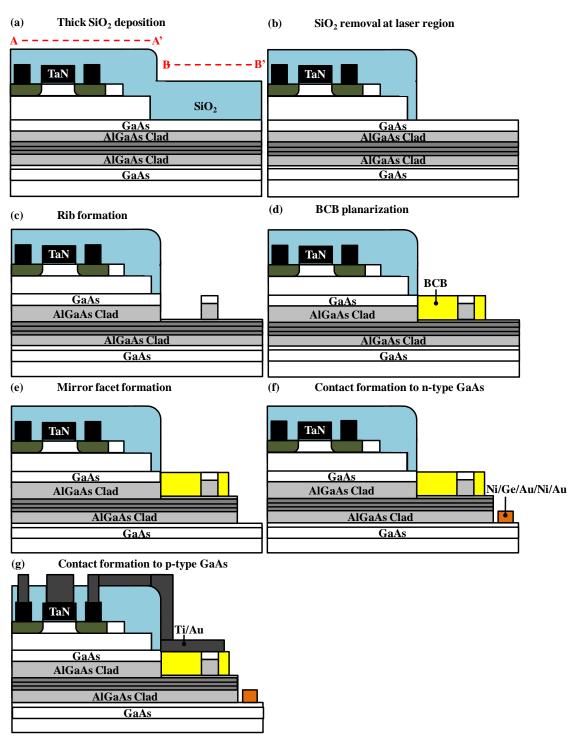

| Fig. 5.4. | Schematics showing transistor fabrication process flow.<br>Schematics are drawn along line A-A' in Fig. 5.3107                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

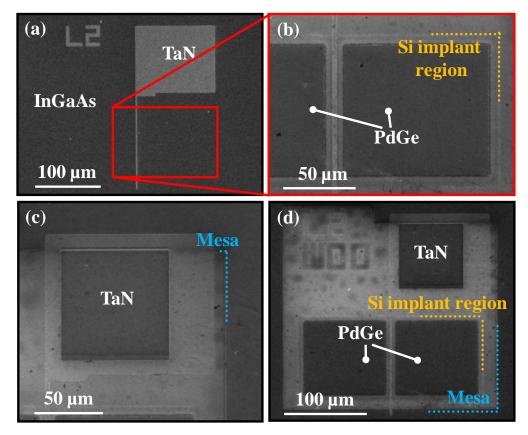

| Fig. 5.5. | Scanning electron microscopy (SEM) images showing a transistor after (a) gate formation, (b) Si implant and PdGe contact formation, (c) InGaAs mesa formation and $SiO_2$ removal on the gate pad. The completed transistor formation is shown in (d)                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

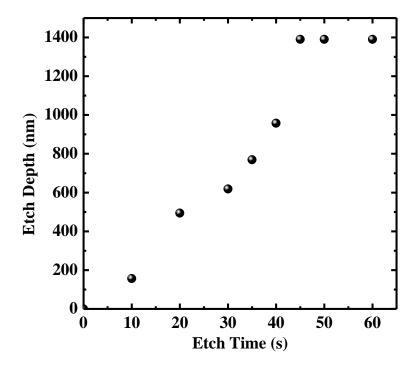

| Fig. 5.6. | Etch depth versus etch time of InAlAs buffer layer in HCl:H <sub>2</sub> O<br>= 3:1 solution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Fig. 5.7. | Schematics showing laser fabrication process flow, following<br>the completed transistor formation (line A-A') in Fig. 5.4. The<br>process steps of laser fabrication are drawn along line B-B' in<br>Fig. 5.3112                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

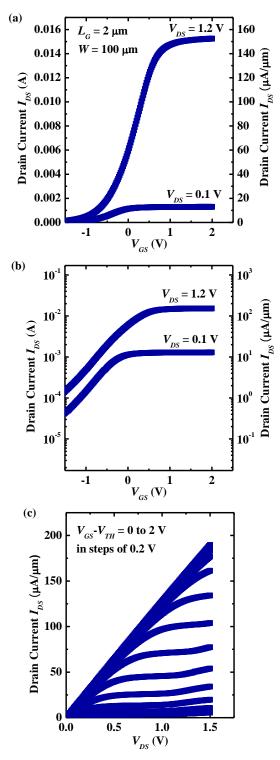

| Fig. 5.8. | (a) $I_{DS}-V_{GS}$ of In <sub>0.7</sub> Ga <sub>0.3</sub> As channel n-MOSFET on transistor-<br>laser integrated substrate obtained at $V_{DS} = 0.1$ and 1.2 V. The<br>gate length of the device is 2 µm and the gate width is 100 µm.<br>(b) Log ( $I_{DS}$ ) versus $V_{GS}$ of the same device at $V_{DS} = 0.1$ and<br>1.2 V. (c) $I_{DS}-V_{DS}$ plot of the same device at various gate<br>overdrives ( $V_{GS}-V_{TH}$ ) from 0 to 2 V                                                                                                                                                                                                                                                                     |

| Fig. 5.9. | Total resistance ( $R_{Total} = V_{DS}/I_{DS}$ ) as a function of gate voltage<br>of the same device as in Fig. 5.8. $I_{DS}$ is the drain current in the<br>linear regime ( $V_{DS} = 0.1$ V). S/D series resistance $R_{S/D}$ of ~76.3<br>$\Omega$ is extracted at higher applied gate voltage when the channel<br>is completely turned on and the total resistance is mainly<br>contributed by S/D resistance. The normalized $R_{S/D}$ to the<br>device gate width ( $W = 100 \mu m$ ) is ~7.6 k $\Omega \cdot \mu m$ . Inset shows<br>the schematic of a non-self-aligned transistor where metal<br>contact is <i>l</i> distance away from channel region. The <i>l</i> spacing<br>of this device is 5 $\mu m$ |

xviii

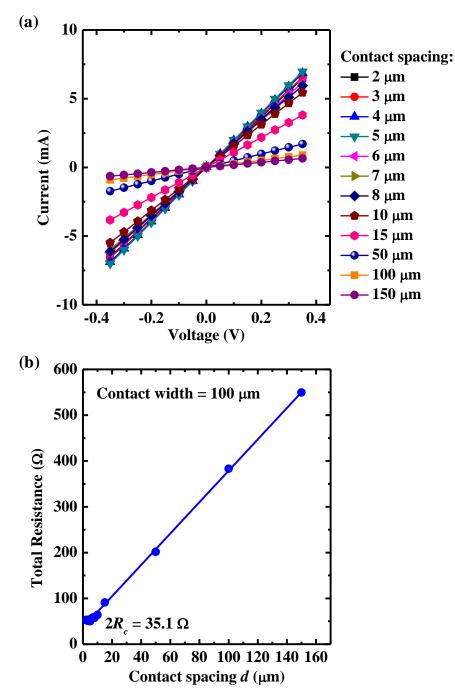

| Fig. 5.10. | (a) <i>I-V</i> curves measured between two adjacent PdGe metal contacts with different contact spacing formed on $n^+$ -InGaAs/InAlAs. (b) Plot of total resistance between two PdGe metal contacts as a function of the contact spacing. The intercept gives $2R_c$ of 35.1 $\Omega$ (also equals to 3.51 k $\Omega$ ·µm)117                   |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

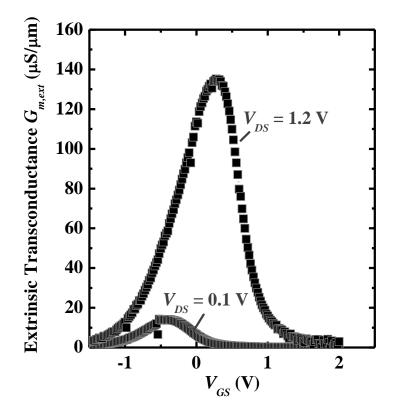

| Fig. 5.11. | Extrinsic transconductance of the same device as in Fig. 5.8118                                                                                                                                                                                                                                                                                 |

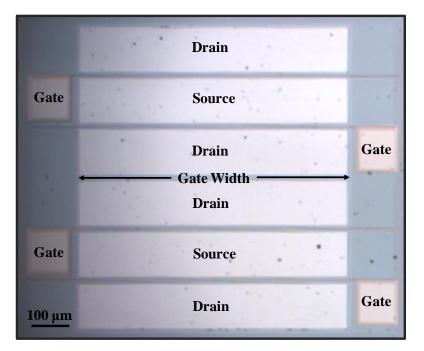

| Fig. 5.12. | Optical microscopy image of the fabricated transistors having large gate width ( $W = 720 \mu m$ ). The transistors were fabricated by the author using the substrate illustrated in Fig. 5.2                                                                                                                                                   |

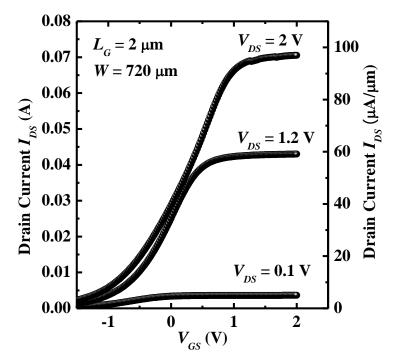

| Fig. 5.13. | $I_{DS}$ - $V_{GS}$ of a large-gate-width In <sub>0.7</sub> Ga <sub>0.3</sub> As transistor measured<br>at $V_{DS} = 0.1$ , 1.2, and 2 V. The gate length of the device is 2<br>$\mu$ m and the gate width is 720 $\mu$ m                                                                                                                       |

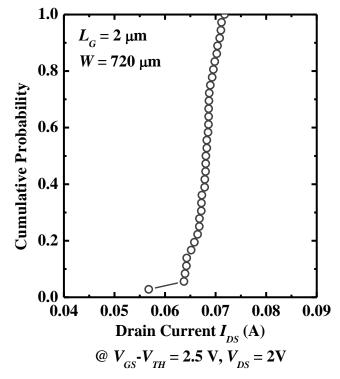

| Fig. 5.14. | Statistical plot showing the distribution of drain current at gate overdrive ( $V_{GS}$ - $V_{TH}$ ) of 2.5 V and $V_{DS}$ of 2 V. The drain current is in the range of 65 – 70 mA. The yield of the transistor fabrication is ~90%. ~50 transistors were measured for this plot                                                                |

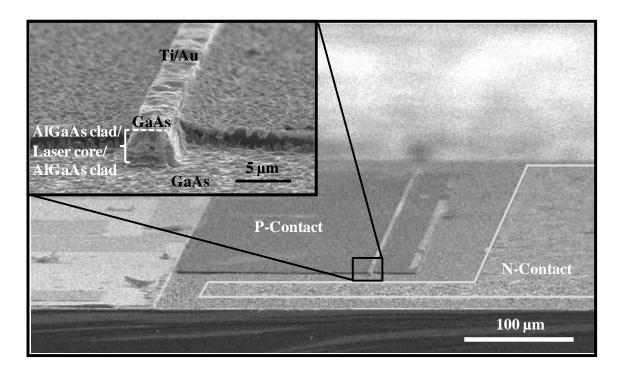

| Fig. 5.15. | SEM image of a laser fabricated with non-optimized<br>anisotropic dry etch recipe. Inset shows the rough mirror facet<br>formed121                                                                                                                                                                                                              |

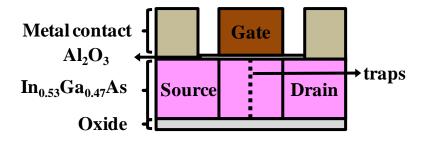

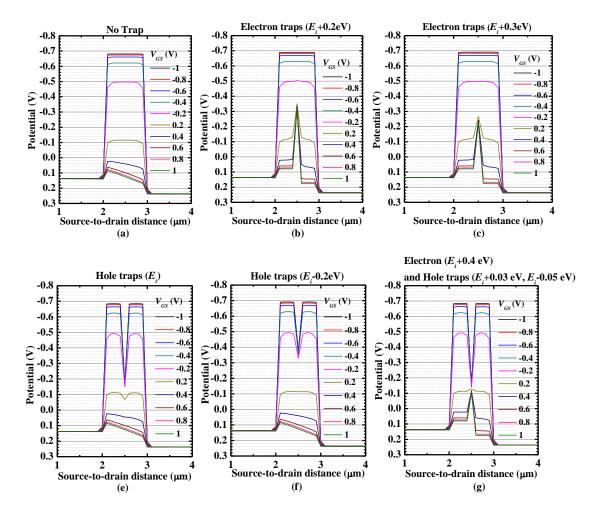

| Fig. 5.16. | Schematic of InGaAs device structure used in 2-D simulation. The thicknesses of $Al_2O_3$ and $In_{0.53}Ga_{0.47}As$ used in the 2-D simulation are 5 nm and 100 nm, respectively. The trap density used is $1 \times 10^{22}$ cm <sup>-3</sup>                                                                                                 |

| Fig. 5.17. | $I_{DS}$ - $V_{GS}$ characteristics of 2-D simulated InGaAs transistors<br>with the presence of (a) electron trap (acceptor characteristic),<br>(b) hole trap (donor characteristic), and (c) electron and hole<br>traps located at various energy positions                                                                                    |

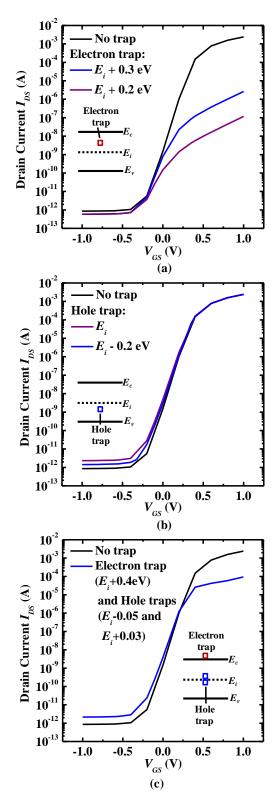

| Fig. 5.18. | Potential diagram of InGaAs at 2 nm below channel surface<br>from source to drain for transistor with (a) no trap, (b) electron<br>trap ( $E_i$ +0.2 eV), (c) electron trap ( $E_i$ +0.3 eV), (d) hole trap<br>( $E_i$ ), (e) hole trap ( $E_i$ -0.2 eV), and (f) electron ( $E_i$ +0.4 eV) and<br>hole traps ( $E_i$ -0.05 eV, $E_i$ +0.03 eV) |

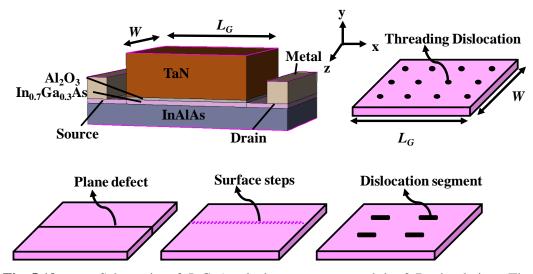

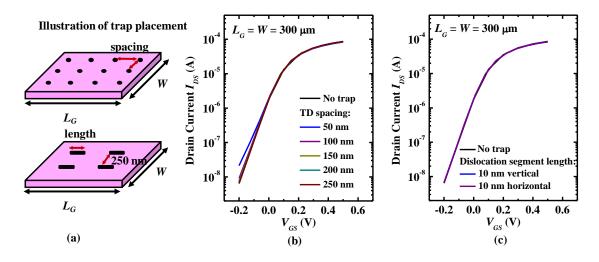

| Fig. 5.19. | Schematic of InGaAs device structure used in 3-D simulation. The thicknesses of $Al_2O_3$ and $In_{0.7}Ga_{0.3}As$ used in the 3-D simulation are 6 nm and 10 nm, respectively. The placement of traps to represent threading dislocation, dislocation segment, surface steps, and plane defect are illustrated                                 |

| Fig. 5.20. | (a) Illustration of trap placement to model threading dislocations and dislocation segments. $I_{DS}$ - $V_{GS}$ characteristics of 3-D simulated InGaAs transistors with (b) threading                                                                                                                                                         |

|            | dislocations with varying spacing and (c) dislocation segments<br>with varying length.                                                                                                                                                                                                                                                                                                              | .128 |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

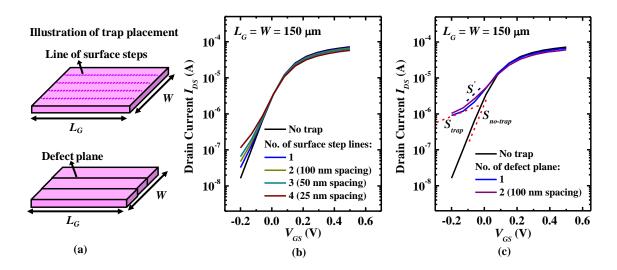

| Fig. 5.21. | (a) Illustration of trap placement of lines of surface steps and defect planes. $I_{DS}$ - $V_{GS}$ characteristics of 3-D simulated InGaAs transistors with various number of (b) lines of surface steps and (c) plane defects.                                                                                                                                                                    | .128 |

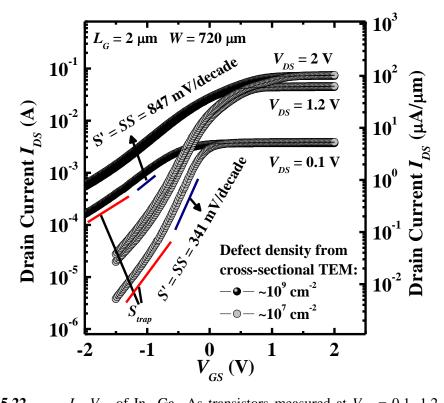

| Fig. 5.22. | $I_{DS}$ - $V_{GS}$ of In <sub>0.7</sub> Ga <sub>0.3</sub> As transistors measured at $V_{DS} = 0.1$ , 1.2, and 2 V. The gate length of the device is 2 µm and the gate width is 720 µm. Black and gray solid symbols are data obtained from transistor fabricated on InGaAs epilayer with defect density of ~10 <sup>9</sup> cm <sup>-2</sup> and ~10 <sup>7</sup> cm <sup>-2</sup> , respectively | .131 |

# List of Symbols

| Symbol           | Description                                         | Unit              |

|------------------|-----------------------------------------------------|-------------------|

| С                | Capacitance                                         | F                 |

| $C_{ox}$         | Oxide capacitance                                   | F                 |

| d                | Contact spacing                                     | μm                |

| $d_{las}$        | Thickness of quantum well                           | nm                |

| $D_{it}$         | Interface trap density                              | $cm^{-2}eV^{-1}$  |

| $E_c$            | Conduction band                                     | eV                |

| $E_{cut-off}$    | Binding energies of the secondary electron cut-off  | eV                |

| $E_{CNL}$        | Charge neutrality level                             | eV                |

| $E_{Fermi}$      | Fermi level                                         | eV                |

| $E_G$            | Bandgap                                             | eV                |

| $E_{v}$          | Valence band                                        | eV                |

| $G_D$            | Drain conductance                                   | S                 |

| $G_m$            | Transconductance (per unit width)                   | $\mu S/\mu m$     |

| $G_{m,ext}$      | Extrinsic transconductance (per unit width)         | $\mu S/\mu m$     |

| $G_{m,int}$      | Intrinsic transconductance (per unit width)         | $\mu S/\mu m$     |

| h                | Planck's constant                                   | eV∙s              |

| Ι                | current                                             | А                 |

| $I_{DS}$         | Drain current (per unit width)                      | $\mu A/\mu m$     |

| $I_G$            | Gate current (per unit width)                       | μA/μm             |

| $I_{off}$        | Off-state current (per unit width)                  | μA/μm             |

| Ion              | On-state current (per unit width)                   | μA/μm             |

| $I_{SD,leak}$    | Source-to-drain leakage current (per unit width)    | $\mu A/\mu m$     |

| $I_{th}$         | Threshold current                                   | А                 |

| J                | Current density                                     | A/cm <sup>2</sup> |

| k                | Boltzmann constant                                  | eV/K              |

| l                | The distance between contact pad and channel        | μm                |

| $l_{probe}$      | Distance between measurement probe and channel edge | μm                |

| L                | Length of metal pad                                 | μm                |

| $L_G$            | Gate length                                         | μm                |

| L <sub>las</sub> | Length of laser active layer                        | μm                |

| $L_T$                          | Transfer length                    | μm               |

|--------------------------------|------------------------------------|------------------|

| $m^*$                          | Carrier effective mass             | kg               |

| n                              | Carrier concentration              | cm <sup>-3</sup> |

| $N_A$                          | P-type doping concentration        | cm <sup>-3</sup> |

| $N_D$                          | N-type doping concentration        | cm <sup>-3</sup> |

| $P_{off}$                      | Standby power consumption          | W                |

| q                              | Electronic charge                  | С                |

| $q\Phi_{\scriptscriptstyle B}$ | Potential barrier                  | eV               |

| r                              | Etch rate                          | nm/s             |

| $r_{Co}$                       | Etch rate of Co                    | nm/s             |

| r <sub>CoInGaAs</sub>          | Etch rate of CoInGaAs              | nm/s             |

| R                              | Resistance                         | Ω                |

| $R_c$                          | Contact resistance                 | Ω                |

| $R_D$                          | Drain resistance                   | Ω                |

| $R_{sh}$                       | Sheet resistance                   | $\Omega/\Box$    |

| <b>R</b> <sub>sh,InGaAs</sub>  | Sheet resistance of n-InGaAs       | $\Omega/\Box$    |

| R <sub>n-doped</sub>           | Resistance of n-doped source/drain | Ω                |

| $R_S$                          | Source resistance                  | Ω                |

| $R_{Si-doped}$                 | Resistance of Si-doped layer       | Ω                |

| $R_{S/D}$                      | Source/drain series resistance     | Ω                |

| <b>R</b> <sub>Total</sub>      | Total resistance                   | Ω                |

| S                              | Etch selectivity                   | -                |

| t                              | Time                               | S                |

| $t_f$                          | Thickness of conductive film       | nm               |

| $t_{Ni}$                       | Ni thickness                       | nm               |

| $t_{NiPt}$                     | NiPt thickness                     | nm               |

| t <sub>Ni-InGaAs</sub>         | Ni-InGaAs thickness                | nm               |

| $t_{ox}$                       | Equivalent oxide thickness         | nm               |

| Т                              | Temperature                        | Κ                |

| V                              | Voltage                            | V                |

| $V_{dd}$                       | Supply voltage                     | V                |

| $V_{DS}$                       | Drain voltage                      | V                |

| $V_{GS}$                       | Gate voltage                       | V                |

| $V_{TH}$                      | Threshold voltage                             | V                   |

|-------------------------------|-----------------------------------------------|---------------------|

| W                             | Gate width                                    | μm                  |

| W <sub>las</sub>              | Width of laser active layer                   | μm                  |

| $X_j$                         | Source/drain junction depth                   | nm                  |

| Ζ                             | Width of metal pad                            | μm                  |

| $\lambda_m$                   | Mean free path                                | m                   |

| μ                             | Carrier mobility                              | $cm^2 V^{-1}s^{-1}$ |

| $\mu_n$                       | Electron mobility                             | $cm^2 V^{-1}s^{-1}$ |

| $\mu_p$                       | Hole mobility                                 | $cm^2 V^{-1}s^{-1}$ |

| $ ho_c$                       | Contact resistivity                           | $\Omega \cdot cm^2$ |

| $ ho_{f}$                     | Resistivity of conductive film                | $\Omega$ ·nm        |

| $ ho_{n\text{-}doped}$        | Resistivity of n-doped source or drain region | $\Omega$ ·nm        |

| $ ho_{Ni-InGaAs}$             | Resistivity of Ni-InGaAs                      | $\Omega$ ·nm        |

| $	au_{_{m}}$                  | Mean free time                                | S                   |

| $	au_{\scriptscriptstyle sp}$ | Carrier life time                             | S                   |

| v                             | Photon frequency                              | $s^{-1}$            |

| Φ                             | Work function                                 | eV                  |

| $\Phi^P_B$                    | Hole barrier height                           | eV                  |

| $\Phi^N_B$                    | Electron barrier height                       | eV                  |

# **Chapter 1**

# Introduction

#### 1.1 Background

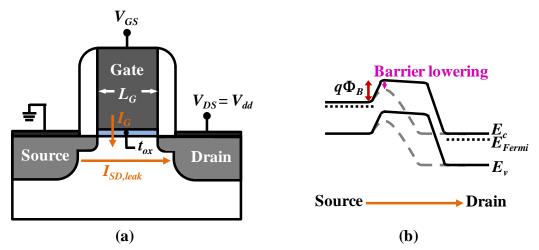

For the past few decades, the continuous scaling down of Si-based complementary metal-oxide-semiconductor (CMOS) devices has enabled higher device packing density and on-state current performance. This exponential increase in the number of devices in an integrated circuit (IC) over time, enabled by the advancement of semiconductor technology, has kept the technology scaling trend in line with Moore's law [1]-[2]. However, with the aggressive scaling of Si transistors, further improvements in the on-state current  $I_{on}$  will soon be hindered by the fundamental limits imposed by the material properties of Si. Moreover, as the transistor gate length ( $L_G$ ) is aggressively scaled to sub-hundred nanometer regime, high off-state leakage current ( $I_{off}$ ) also becomes a major concern. The high off-state leakage current is contributed by source-to-drain leakage ( $I_{SD,leak}$ ) and gate leakage ( $I_G$ ) as illustrated in Fig. 1.1(a).

In a transistor with large  $L_G$ , carriers moving from source to drain see a potential barrier ( $q\Phi_B$ ) at the source end [black line in Fig. 1.1(b)] that is influenced by the gate voltage ( $V_{GS}$ ) but not the drain voltage ( $V_{DS}$ ). However, as the gate length is shortened, the drain is close to the source and the  $V_{DS}$  influences

**Fig. 1.1** (a) Schematic illustrating the source-to-drain leakage  $(I_{SD,leak})$  and gate leakage  $(I_G)$  of a transistor. (b) Band diagram across the channel from source to drain of a transistor with long (black lines) and short (dashed lines)  $L_G$ . The drain voltage  $(V_{DS})$  affects the potential barrier  $(q\Phi_B)$  at the source end of transistor with small  $L_G$ , resulting in barrier lowering.  $E_c$ ,  $E_{Fermi}$ , and  $E_v$  represent the conduction band, Fermi level, and valence band, respectively.

the barrier at the source end. This results in a lower barrier seen by carriers moving from source to channel [dashed line in Fig. 1.1(b)], also known as drain induced barrier lowering (DIBL), which leads to higher  $I_{SD,leak}$  for transistors with short  $L_G$ . Hence, as the gate length becomes shorter, the equivalent oxide thickness ( $t_{ox}$ ) of the transistor needs to be reduced in order to achieve good gate control and suppress  $I_{SD,leak}$ . However, scaling of  $t_{ox}$  can lead to higher  $I_G$ .

The  $I_{off}$  contributes to high standby power consumption ( $P_{off}$ ) as expressed

by

$$P_{off} = I_{off} \times V_{dd}, \qquad (1.1)$$

where  $V_{dd}$  is the supply voltage. As such, the benefit of scaling is offset by power loss due to high  $I_{off}$ . Fortunately, this tradeoff faced by the scaling of Si transistors can be resolved by using an alternative channel material with higher carrier mobility, innovative device architectures, and high-k gate dielectric materials, so that  $I_{on}$  can be increased for a given  $I_{off}$ , or  $I_{off}$  can be reduced for a given  $I_{on}$ .

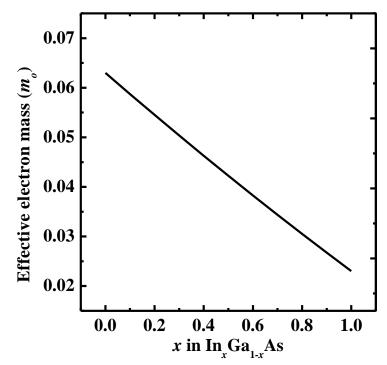

III-V materials such as  $In_xGa_{1-x}As$  (also denoted as InGaAs) are very attractive as alternative channel materials as they have much higher electron mobilities than silicon, due to their very low electron effective mass. The high electron mobility of  $In_xGa_{1-x}As$  makes it suitable for n-channel metal-oxidesemiconductor field-effect-transistors (MOSFETs) for future technology nodes. The dependence of carrier mobility ( $\mu$ ) in bulk materials on carrier effective mass ( $m^*$ ) can be expressed using

$$\mu = \frac{q\tau_m}{m^*} = \frac{q\lambda_m}{\sqrt{3kTm^*}},\tag{1.2}$$

where q is the electronic charge,  $\tau_m$  is the mean free time, k is the Boltzmann constant, T is the temperature, and  $\lambda_m$  is the mean free path. Fig. 1.2 shows the electron effective mass of  $\text{In}_x\text{Ga}_{1-x}\text{As}$  as a function of indium concentration [3]. Electron mobility increases with higher indium composition due to reduction in the electron effective mass. However, to enable successful integration of  $\text{In}_x\text{Ga}_{1-x}$ As devices into Si-based CMOS technology, several key challenges have to be addressed.

**Fig. 1.2** Electron effective mass of  $In_xGa_{1-x}As$  versus indium composition [3].  $m_o$  is the free electron mass.

#### 1.2 Key Challenges of InGaAs MOSFETs