# FLASH MEMORY MANAGEMENT WITH COOPERATION, ADAPTATION AND ASSISTANCE

#### CHUNDONG WANG

$(B.Sc.,\ XI'AN\ JIAOTONG\ UNIVERSITY,\ CHINA)$

#### A THESIS SUBMITTED

FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

DEPARTMENT OF COMPUTER SCIENCE

NATIONAL UNIVERSITY OF SINGAPORE

# **DECLARATION**

I hereby declare that the thesis is my original work and it has been written by me in its entirety. I have duly acknowledged all the sources of information which have been used in the thesis.

This thesis has also not been submitted for any degree in any university previously.

Chundong Wang November 14, 2013

# Acknowledgements

First of all, my deepest gratitude goes to my supervisor, Professor Wong Weng Fai, for his persistent and attentive guidance throughout my Ph.D. candidature. Professor Wong always inspires me and encourages to do research. His professional supervision is of great value to my career in the future.

I would like to express my sincere thanks to my dissertation committee members, Professor Tulika Mitra, Professor Roland Yap Hock Chuan and Professor Tei-Wei Kuo. They have spent a lot of time in reviewing my dissertation, and given me insightful comments and suggestions.

I am grateful to teachers during my Ph.D. study. They did teach me not only knowledge but all skills for a researcher. I also would like to thank administrative staffs of the school and the university for their help in the past five years.

Many thanks are due to my fellows in the Embedded Systems Research Labs and SoC, including Edward Sim, Ju Lei, Anderi Hagiescu, Liang Yun, Huynh Phung Huynh, Sudipta Chattopadhyay, Liu Shanshan, Qi Dawei, Ding Huping, Chen Jie, Chen Liang, Pooja Roy, Wang Jianxing, Mamohan Manoharan, Thannimalai Somu Muthukaruppan, Zhong Guanwen, Ramapantulu Lavanya, Guo Xiangfa, Li Bo, Su Bolan and many others that are not listed. I want to express my gratitude to Professor Jürgen Teich in University of Erlangen-Nuremberg, Professor Qi Yong, Professor Song Qinbao and Dr. He Liang in Xi'an Jiaotong University, Dr. Yang Wentong in the National University Health System, and Assistant Professor Yeh Chi-Tsai in Shih Chien University. I also want to thank Wang Dong, Hai Zhen, Cheng Peng, Chen Peng, Hu Ping, Zhang Kaibin and Li Zhenggang. I highly appreciate their encouragement and support.

I would love to extend the warmest thanks to my parents. They always believe me and encourage me to pursue my dreams. Twelve years ago I left my hometown for study. I wish we could live together soon after my graduation.

Finally, I want to thank my wife, Jiang Lina. I might not be able to write this dissertation without her love and understanding. We met ten years ago in our high school. She is always being supportive to me and helping me through all the hard times. This dissertation is dedicated to her.

# Contents

| D            | eclar              | ation                              | i         |

|--------------|--------------------|------------------------------------|-----------|

| $\mathbf{A}$ | ckno               | wledgements                        | ii        |

| C            | ontei              | nts                                | iii       |

| $\mathbf{A}$ | bstra              | act                                | vi        |

| Li           | st of              | Publications                       | iii       |

| Li           | st of              | Tables                             | ix        |

| Li           | st of              | Figures                            | X         |

| 1            | Inti               | roduction                          | 1         |

|              | 1.1                | Flash Memory Management            | 1         |

|              |                    | 1.1.1 NAND Flash Memory            | 1         |

|              |                    | 1.1.2 Flash Memory Management      | 2         |

|              | 1.2                | Problem Formulation and Motivation | 4         |

|              | 1.3                | Thesis Statement and Overview      | 6         |

|              | 1.4                | Organization of the Chapters       | 8         |

| 2            | Bac                | kground                            | 9         |

|              | 2.1                | NAND Flash Memory                  | 9         |

|              | 2.2                | Modules of Flash Memory Management | 11        |

|              | 2.3                | The Background of the Era          | 14        |

| 3            | ${ m Lit}\epsilon$ | erature Review                     | <b>15</b> |

|              | 3.1                | Flash Device and Its Potential     | 15        |

|              | 3.2                | Algorithms of Flash Management     | 17        |

|              |                    | 3.2.1 Schemes for Wear Leveling    | 17        |

|              |                    | 3.2.2 Schemes for Address Manning  | 19        |

|   |     | 3.2.3  | Schemes for RAM Buffer Management            | 21 |

|---|-----|--------|----------------------------------------------|----|

|   | 3.3 | Strate | gies Behind Flash Management                 | 23 |

|   |     | 3.3.1  | Module-Cooperative Flash Management          | 23 |

|   |     | 3.3.2  | Workload-adaptive Flash Management           | 24 |

|   |     | 3.3.3  | OS-involved Flash Management                 | 25 |

| 4 | ow  | L: Co  | operative Wear Leveling                      | 26 |

|   | 4.1 | Overv  | iew                                          | 26 |

|   | 4.2 | Challe | enge and Motivation                          | 28 |

|   | 4.3 | OWL'   | s Block Organization                         | 29 |

|   | 4.4 | Locali | ty-based Block Allocation                    | 30 |

|   | 4.5 | Scan a | and Transfer Scheme                          | 34 |

|   | 4.6 | Exper  | imental Evaluation                           | 37 |

|   |     | 4.6.1  | Experimental Methodology                     | 37 |

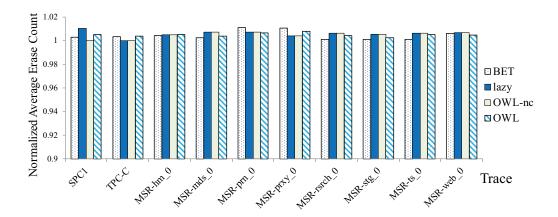

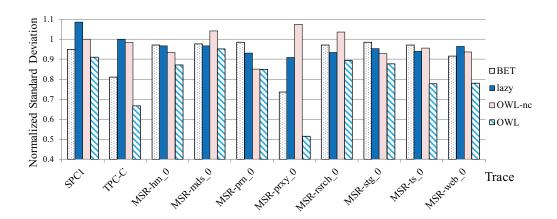

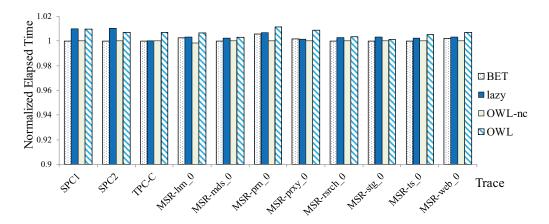

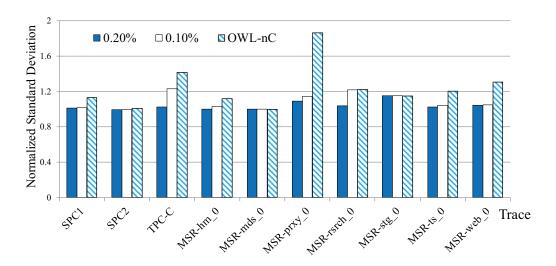

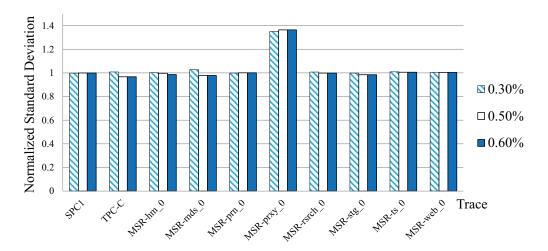

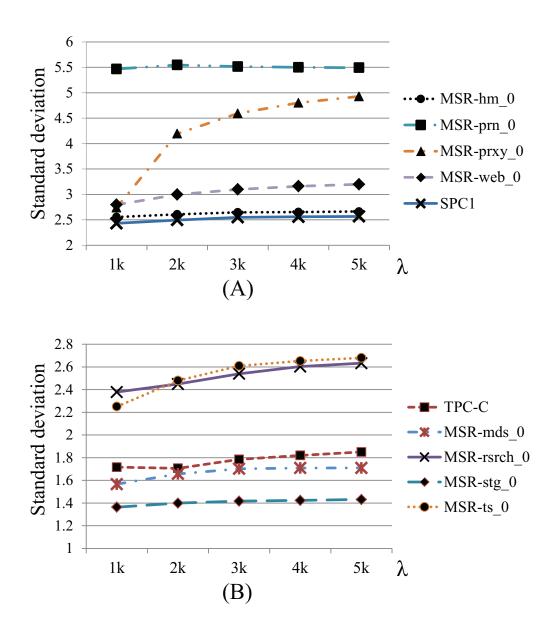

|   |     | 4.6.2  | Effectiveness of OWL                         | 38 |

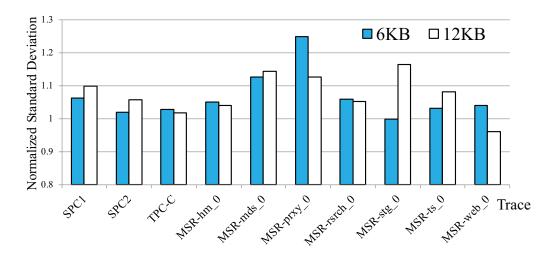

|   |     | 4.6.3  | Effects of BAT Size                          | 40 |

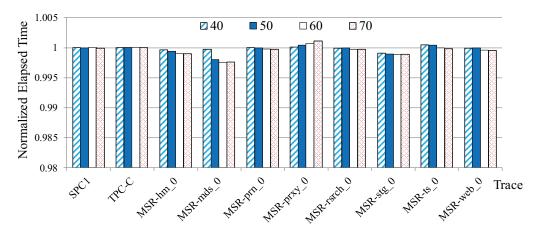

|   |     | 4.6.4  | Effectiveness of ST                          | 41 |

|   | 4.7 | Summ   | ary                                          | 44 |

| 5 | AD  | APT:   | Workload-Adaptive Hybrid Address Mapping     | 47 |

|   | 5.1 | Overv  | iew                                          | 47 |

|   | 5.2 | Online | e Adaptive Partitioning of the Log Space     | 49 |

|   | 5.3 | Predic | etive Transfers                              | 53 |

|   | 5.4 | Aggre  | gated Data Movement                          | 56 |

|   | 5.5 | Merge  | or Move Decision Procedure                   | 57 |

|   | 5.6 | Exper  | iments                                       | 57 |

|   |     | 5.6.1  | Configurations and Assumptions               | 57 |

|   |     | 5.6.2  | Performance Evaluation                       | 59 |

|   |     | 5.6.3  | Effects of Log Space Capacity                | 62 |

|   |     | 5.6.4  | Effects of Log Space Partitioning            | 63 |

|   |     | 5.6.5  | Impact of $\kappa$                           | 64 |

|   |     | 5.6.6  | Effects of the Interval Length on Adaptation | 64 |

|   |     | 5.6.7  | Effects of HAT Size                          | 65 |

|   |     | 5.6.8  | Tuning of Aggregation Threshold              | 66 |

|   | 5.7 | Summ   | ary                                          | 68 |

| 6 | Tre | eFTL:  | An Adaptive Tree in the RAM Buffer           | 71 |

|   | 6.1 | Overv  | iew                                          | 71 |

|   | 6.2 | The T  | ree in RAM                                   | 73 |

|    |        | 6.2.1  | The Three Levels                             | 73  |

|----|--------|--------|----------------------------------------------|-----|

|    |        | 6.2.2  | Address Translation With The Tree            | 75  |

|    | 6.3    | Lightv | veight Pruning of TreeFTL                    | 77  |

|    |        | 6.3.1  | Lightweight Pruning with Caching Groups      | 77  |

|    |        | 6.3.2  | Two-level LRU Selection Mechanism            | 80  |

|    | 6.4    | Discus | ssions on TreeFTL                            | 82  |

|    |        | 6.4.1  | Partitioning and RAM Space Utilization       | 82  |

|    |        | 6.4.2  | Workload Adaptation                          | 82  |

|    |        | 6.4.3  | Reliability and Garbage Collection           | 83  |

|    | 6.5    | Perfor | mance Evaluation                             | 83  |

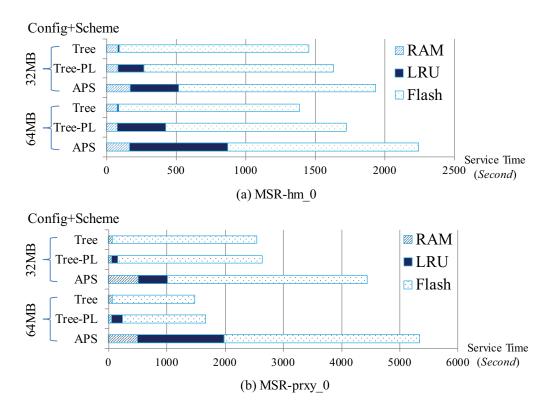

|    |        | 6.5.1  | Experimental Setup                           | 83  |

|    |        | 6.5.2  | Performance Improvements by TreeFTL          | 85  |

|    |        | 6.5.3  | Effect of the Lightweight LRU Selection      | 88  |

|    | 6.6    | Summ   | ary                                          | 90  |

| 7  | SAV    | V: OS- | -Assisted Wear Leveling                      | 91  |

|    | 7.1    | Overv  | iew                                          | 91  |

|    | 7.2    | Tempe  | erature of File Types                        | 93  |

|    |        | 7.2.1  | Update Frequency of A File Type              | 94  |

|    |        | 7.2.2  | Update Recency                               | 96  |

|    |        | 7.2.3  | Temperature of File Types                    | 97  |

|    | 7.3    | Wear   | Leveling with Temperature                    | 98  |

|    |        | 7.3.1  | Exponential Division of Flash Blocks         | 98  |

|    |        | 7.3.2  | Temperature Adjustment                       | 99  |

|    | 7.4    | A Pro  | totype of SAW                                | 99  |

|    | 7.5    | Exper  | imental Evaluation                           | 101 |

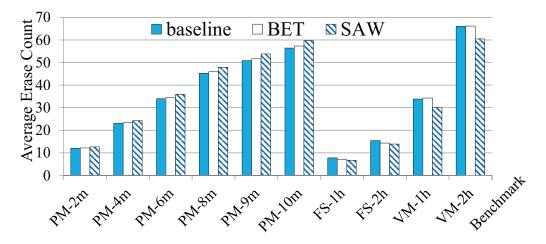

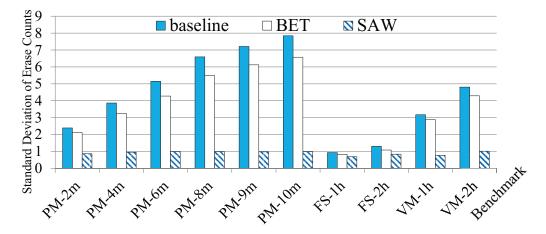

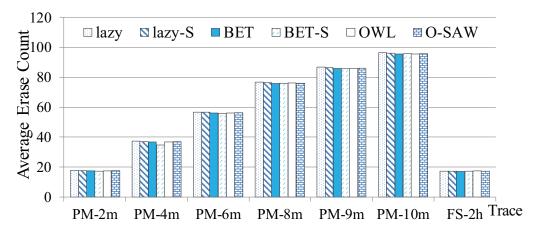

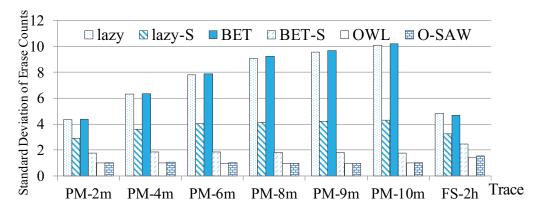

|    |        | 7.5.1  | The Effectiveness of SAW                     | 102 |

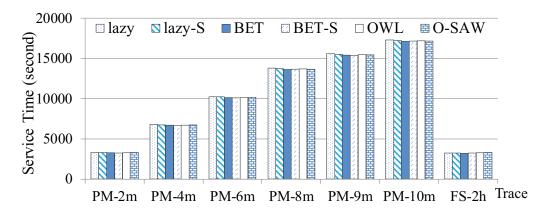

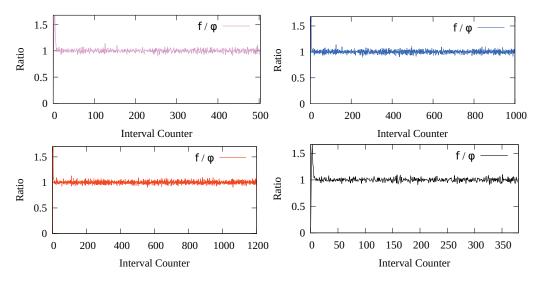

|    |        | 7.5.2  | The Accuracy of $f$ for $\varphi$            | 105 |

|    |        | 7.5.3  | The Impact of $oldsymbol{eta}$               | 106 |

|    |        | 7.5.4  | Impact of Interval Length                    | 106 |

|    |        | 7.5.5  | Full Results with the Prototype and FlashSim | 107 |

|    | 7.6    | Summ   | ary                                          | 107 |

| 8  | Cor    | clusio | n                                            | 113 |

|    | 8.1    | Thesis | s Contributions                              | 113 |

|    | 8.2    | Future | e Directions                                 | 114 |

| Bi | ihling | ranhv  |                                              | 115 |

## Abstract

NAND flash memory-based devices are ubiquitous for data storage in smart phones, personal computers and enterprise servers today. This can be attributed to the advantages of NAND flash memory over ferromagnetic material and volatile memory; in particular, they are lightweight, shock-resistance, energy-efficiency and non-volatility. However, NAND flash memory has inherent characteristics that are still serious concerns in its deployment. At the same time, the environments in which storage devices are used have become much more diverse in the past three decades since the invention of flash memory. Efficient and effective strategies to manage flash device are therefore necessary. This motivates us to innovate new approaches within this thesis.

The management of a NAND flash device is traditionally done by an embedded software called the *flash translation layer* (FTL). The FTL is developed in a modular design with each module being responsible for one aspect of flash management. For example, address mapping maps logical addresses of file systems to physical addresses of flash memory; wear leveling attempts to commit all flash blocks to age at a similar rate, and RAM buffer management aims to make the best use of the RAM buffer inside a flash device.

Our first idea is to have the modules of the FTL cooperate with one another. Modules are likely to have different and possibly independent perspectives with regards to flash management. Therefore, a module of the FTL may benefit from the knowledge of another. Based on this idea we have developed OWL. It is a wear leveling algorithm that works within hybrid address mapping. The latter

classifies allocation requests when allocating blocks for data storage. Cooperation between them goes beyond simply exchanging information. Instead, a part of the wear leveling module of OWL is co-developed with the hybrid mapping module so as to incorporate the latter's information and consideration upon deciding which block to be allocated.

Workload adaptation is our second idea. Flash-based storage devices serve workloads to store and access data. The ability of adapting to a given workload is essential due to the diversity of workloads. Address mapping and RAM buffer management are two functionalities of the FTL that relate to data access. We have first designed a hybrid mapping scheme named ADAPT. ADAPT achieves the goal of workload adaptation through separating and handling respective sequential and random requests. TreeFTL is another scheme we have devised to manage the RAM buffer of a flash device. TreeFTL caches metadata of address mapping and real data pages in the RAM space using a tree-like structure. To minimize the overheads of context switch between workloads, TreeFTL has a lightweight mechanism for evicting the LRU victims to make space.

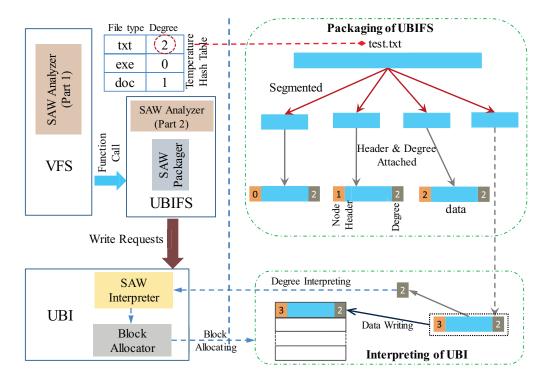

Our third idea is to enlist the help of the operating system (OS). Traditionally the FTL is self-contained and the OS is oblivious of storage devices. As the OS has a global perspective of data and files, we would like to use the OS's knowledge to assist the FTL to manage flash device. The result of this collaboration is a scheme we called SAW, of which the OS analyzes files to figure out quantitative hints for the FTL to perform wear leveling. Correspondingly the FTL customizes its block organization to utilize the hints received from the OS. Hints are packed along within data segments and delivered to the FTL. The FTL unpacks each segment, interprets the hint and conducts block allocation accordingly.

Experiments have been conducted to evaluate our proposals. Results confirm that our approaches in this thesis could gain significant improvements on device lifetime and access performance, respectively, with insignificant overheads.

# List of Publications

- 1. Chundong Wang and Weng-Fai Wong. Observational wear leveling: an efficient algorithm for flash memory management. In *Proceedings of the 49th Annual Design Automation Conference*, DAC '12, pages 235–242, San Francisco, California, USA, 2012. ACM.

- 2. Chundong Wang and Weng-Fai Wong. Extending the lifetime of NAND flash memory by salvaging bad blocks. In 15th Design, Automation, and Test in Europe (DATE 2012) conference, pages 260–263, Dresden, Germany. March 2012.

- 3. Chundong Wang and Weng-Fai Wong. ADAPT: Efficient workload-sensitive flash management based on adaptation, prediction and aggregation. In *Proceedings of the 2012 IEEE 28th Symposium on Mass Storage Systems and Technologies*, MSST '12, Pacific Grove, California, USA, April 2012.

- 4. Chundong Wang and Weng-Fai Wong. TreeFTL: Efficient RAM Management for High Performance of NAND Flash-based Storage Systems. In *Proceedings of the 16th Design, Automation and Test in Europe Conference*, DATE '13, pages 374-379, Grenoble, France. March 2013.

- 5. Chundong Wang and Weng-Fai Wong. SAW: System-assisted wear leveling on the write endurance of NAND flash devices. In *Proceedings of the 50th Annual Design Automation Conference*, DAC '13, pages 164:1-164:9, Austin, Texas, USA, 2013. ACM.

# List of Tables

| 3.1 | A Summary of the Latest Wear Leveling Algorithms                                         | 17  |

|-----|------------------------------------------------------------------------------------------|-----|

| 4.1 | Block Allocation Ratios in FAST                                                          | 29  |

| 4.2 | Capacities for Traces                                                                    | 37  |

| 5.1 | I/O Request Size of Various Workloads                                                    | 48  |

| 5.2 | Latencies of Large-block SLC NAND Flash Memory [38]                                      | 54  |

| 5.3 | Prediction Hit Rates and Aggregated Moves                                                | 62  |

| 6.1 | Latencies of SLC NAND Flash Memory [41]                                                  | 74  |

| 6.2 | Hit Ratios (%) of APS, JTL and Tree                                                      | 87  |

| 7.1 | Symbols of SAW Model                                                                     | 95  |

| 7.2 | Mean Difference of Standard Deviation with Five Intervals $(I)$ .                        | 106 |

| 7.3 | Average Erase Count, Standard Deviation, the Counts of Write                             |     |

|     | and Read Operations of ${\tt baseline}, {\tt BET} {\tt and} {\tt SAW} {\tt (1st\ Time)}$ | 108 |

| 7.4 | Average Erase Count, Standard Deviation, the Counts of Write                             |     |

|     | and Read Operations of ${\tt baseline}, {\tt BET}$ and ${\tt SAW}$ (2nd Time)            | 109 |

| 7.5 | Average Erase Count, Standard Deviation, the Counts of Write                             |     |

|     | and Read Operations of ${\tt baseline}, {\tt BET}$ and ${\tt SAW}$ (3rd Time)            | 110 |

| 7.6 | Average Erase Count and Standard Deviation of 5k, 10k, 15k,                              |     |

|     | 20k and 25k                                                                              | 111 |

| 7.7 | Average Erase Count, Standard Deviation and Service Time of                              |     |

|     | lazy and lazy-S                                                                          | 112 |

| 7.8 | Average Erase Count, Standard Deviation and Service Time of |     |

|-----|-------------------------------------------------------------|-----|

|     | BET and BET-S                                               | 112 |

| 7.9 | Average Erase Count, Standard Deviation and Service Time of |     |

|     | OWI. and O-SAW                                              | 119 |

# List of Figures

| 1.1  | A Logical Structure of NAND Flash Devices            | 3  |

|------|------------------------------------------------------|----|

| 1.2  | The Flash Memory Management                          | 4  |

| 2.1  | Structures and Operations of NAND Flash Memory       | 9  |

| 2.2  | Page Mapping and Block Mapping                       | 13 |

| 3.1  | Three types of merge(adopted from Lee et al. [62])   | 21 |

| 3.2  | Page-level Mapping: DFTL and CDFTL                   | 22 |

| 4.1  | Locality-based Block Allocation with BAT             | 31 |

| 4.2  | An Example of ST Scheme                              | 36 |

| 4.3  | Average Erase Counts of Each Trace                   | 38 |

| 4.4  | Standard Deviation of Erase Counts                   | 39 |

| 4.5  | Elapsed Time with Four Algorithms                    | 39 |

| 4.6  | The Effects of Different BAT Size                    | 40 |

| 4.7  | The Effects of ST with Various $\delta$ (A)          | 41 |

| 4.8  | The Effects of ST with Various $\delta$ (B)          | 41 |

| 4.9  | The Effects of $\lambda$ length                      | 42 |

| 4.10 | Normalized Elapsed Time with Various $\Gamma$        | 43 |

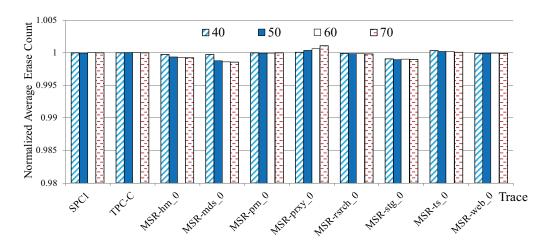

| 4.11 | Normalized Average Erase Count with Various $\Gamma$ | 44 |

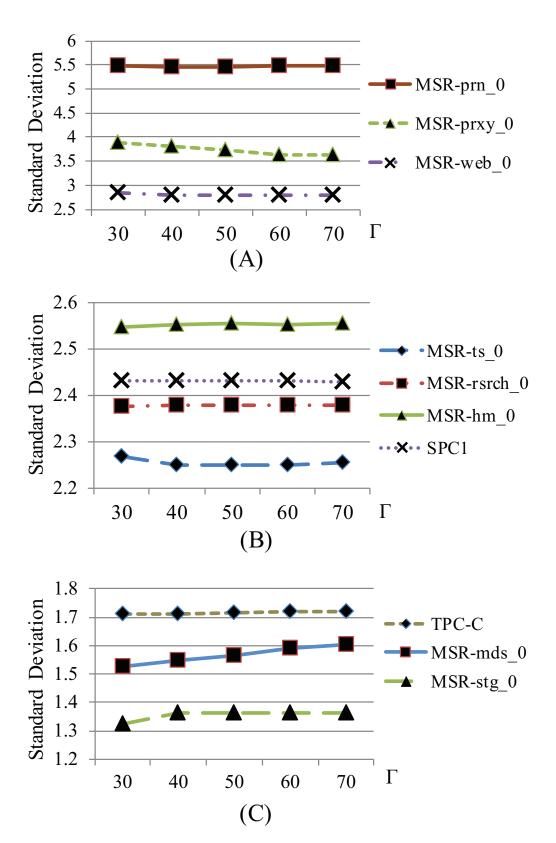

| 4.12 | Standard Deviation with Various $\Gamma$             | 45 |

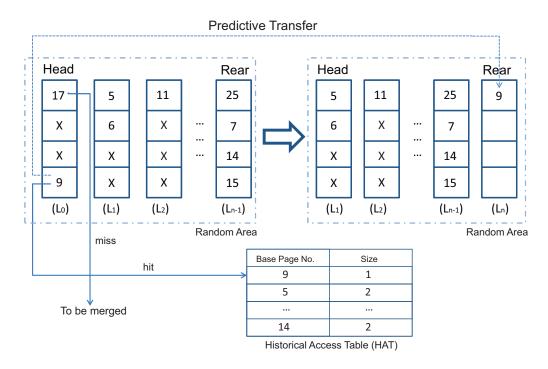

| 5.1  | Predictive Transfer with the Historical Access Table | 55 |

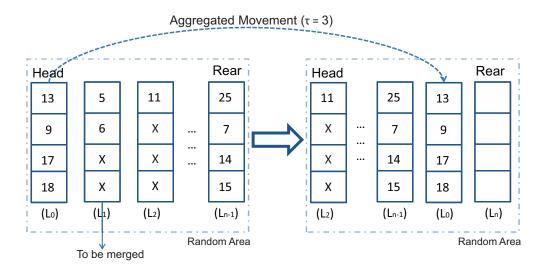

| 5.2  | Aggregated Data Movement                             | 56 |

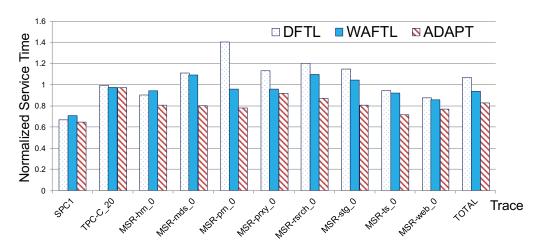

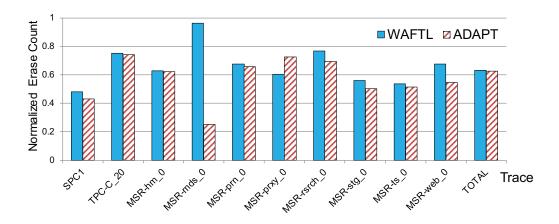

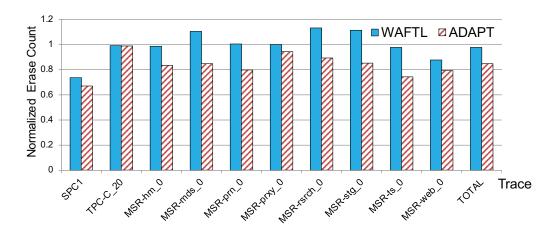

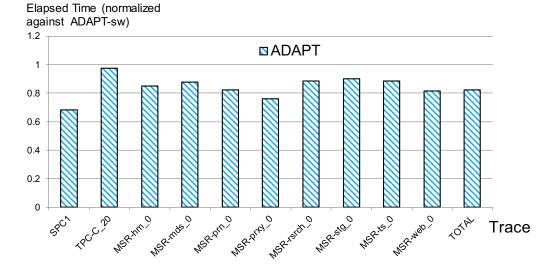

| 5.3  | Normalized Elapsed Time of DFTL, WAFTL and ADAPT                             | 60  |

|------|------------------------------------------------------------------------------|-----|

| 5.4  | Normalized Erase Counts of WAFTL and ADAPT $\ \ldots \ \ldots$               | 60  |

| 5.5  | Normalized Write Counts of WAFTL and ADAPT $\ . \ . \ . \ . \ .$             | 61  |

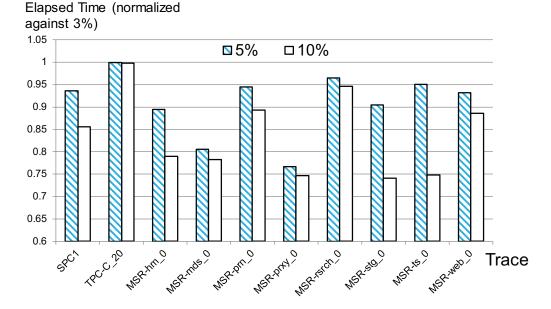

| 5.6  | Effects of Different Log Space Capacities                                    | 63  |

| 5.7  | Performance Impact of Log Space Partitioning                                 | 64  |

| 5.8  | Impact of Different Sequential Write Identification Thresholds               | 65  |

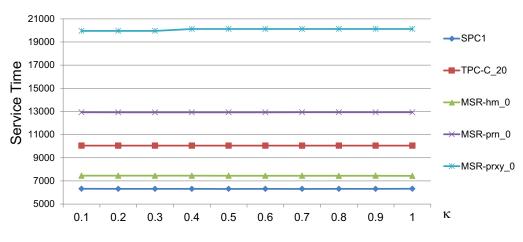

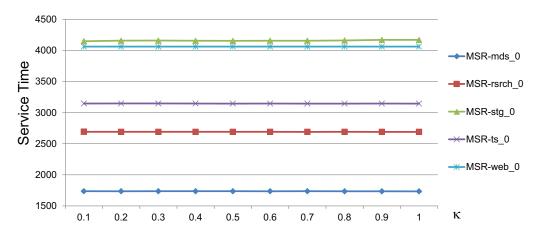

| 5.9  | The Effects of $\kappa$ (A)                                                  | 65  |

| 5.10 | The Effects of $\kappa$ (B)                                                  | 66  |

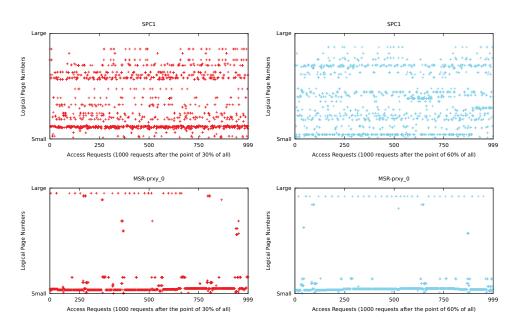

| 5.11 | Captures of Access Distribution for SPC1 and MSR-prxy_0 $$                   | 67  |

| 5.12 | The Effects of the Interval Length (A) $\ \ldots \ \ldots \ \ldots \ \ldots$ | 68  |

| 5.13 | The Effects of the Interval Length (B) $\ \ldots \ \ldots \ \ldots \ \ldots$ | 68  |

| 5.14 | Effects of Different HAT Sizes                                               | 69  |

| 5.15 | Performance of Aggregated Movement                                           | 70  |

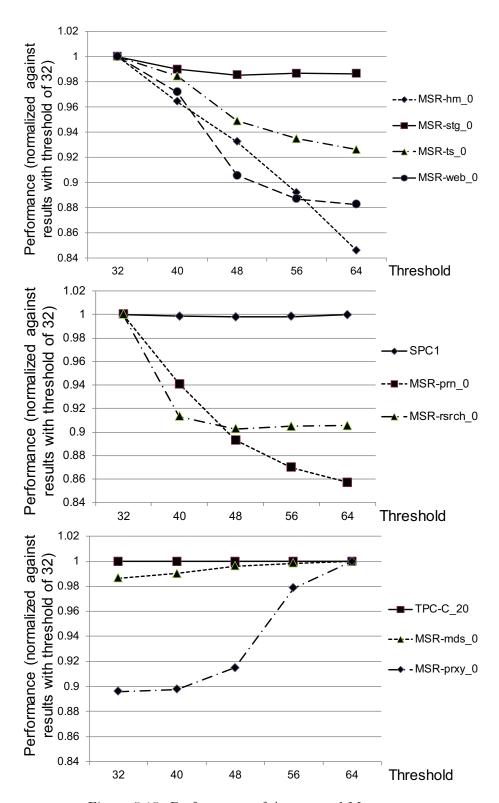

| 6.1  | A Conceptual Structure of TreeFTL                                            | 74  |

| 6.2  | Address Translation Process in TreeFTL                                       | 76  |

| 6.3  | The Sketch of TreeFTL's Victim Selection                                     | 78  |

| 6.4  | The Sketch of TreeFTL's Two-level LRU Selection Mechanism $$ .               | 80  |

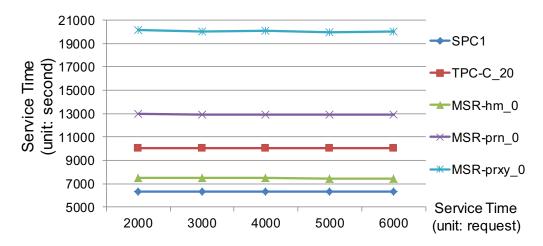

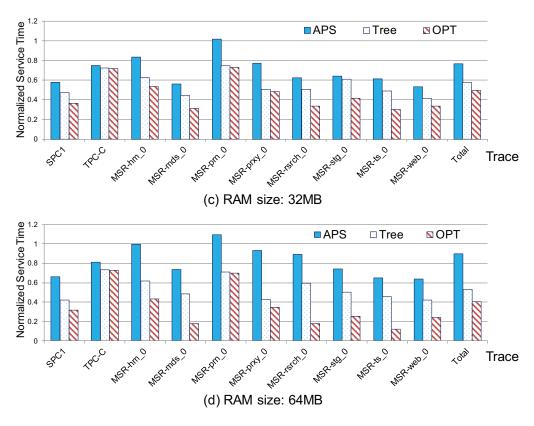

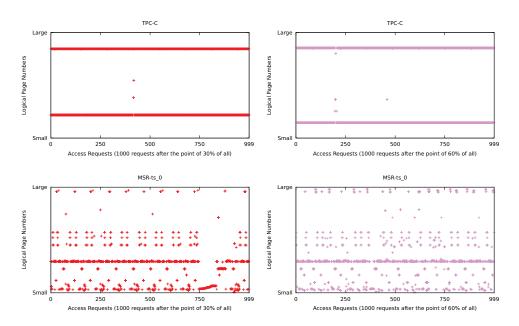

| 6.5  | Normalized Service Time for Traces (1)                                       | 84  |

| 6.6  | Normalized Service Time for Traces (2)                                       | 85  |

| 6.7  | Captures of Access Distribution for TPC-C and MSR-ts_0                       | 86  |

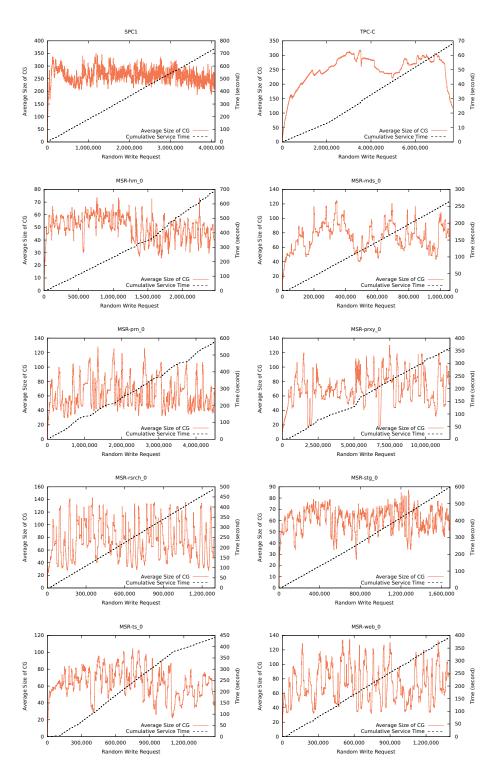

| 6.8  | Cumulative Service Time and Average Size of CG for Traces at                 |     |

|      | Runtime                                                                      | 89  |

| 6.9  | Effect of Lightweight Victim Selection                                       | 90  |

| 7.1  | A Sketch of SAW Prototype                                                    | 100 |

| 7.2  | Average Erase Count with Prototype                                           | 101 |

| 7.3  | Standard Deviation of Erase Counts with Prototype                            | 102 |

| 7.4  | Average Erase Count with FlashSim                                            | 103 |

| 7.5  | Standard Deviation of Erase Counts with FlashSim                             | 103 |

| 7.6 | Service Time with FlashSim                                          | 104 |

|-----|---------------------------------------------------------------------|-----|

| 7.7 | Fluctuation of $f/\varphi$ (Clockwise: PM-5m, PM-10m, FS-2h, VM-2h) | 105 |

| 7.8 | s and $\beta$ at Runtime (Clockwise: PM-5m, PM-10m, FS-2h, VM-2h)   | 105 |

## Chapter 1

## Introduction

The advent of flash memory has changed the persistent data storage of computer systems. NAND flash memory's non-volatility, lightweight, shock-resistance and scalability make it a promising candidate for the secondary storage in both embedded systems and general-purpose computing systems. However, the everincreasing utilization of NAND flash memory comes with its challenges. On the one hand, the environments in which NAND flash memory is used today vary significantly. For example, the access pattern of a smart-phone is very different from that of an enterprise server. On the other hand, NAND flash memory has been evolving to be denser and weaker than before. Also, the products made of NAND flash memory are getting diverse; they can be either emulated to be block devices or just exposed as raw flash devices. In all, these challenges necessitate revising existent strategies for managing NAND flash-based device. This thesis will hence present novel approaches on the management of NAND flash memory. Several management algorithms, which target either longer device lifetime or higher access performance, have been developed accordingly in order to achieve satisfactory effectiveness and efficiency.

#### 1.1 Flash Memory Management

#### 1.1.1 NAND Flash Memory

NAND flash memory is preferred in hand-held products like smart-phones, digital cameras and tablet computers, because of its lightweight and resistance to damage during movements [50]. Simultaneously, flash-based solid state drives (SSDs) are starting to replace traditional ferro-magnetic hard disk drives (HDDs) [1, 78]. Both personal computers (PCs) and enterprise servers have been utilizing flash-based SSDs for secondary storage. For example, the MacBook Air laptops

of Apple inc. are mature in marketplace. In 2008 Google announced a plan to use Intel SSD storage in its servers [20]. Later in the autumn of 2009, MySpace migrated its data from HDDs to SSDs produced by Fusion-io [72].

A NAND flash device consists of multiple flash memory chips. In a NAND flash chip there are hundreds of thousands of flash cells. Each flash cell has a single transistor with an extra metal strip, which is called the floating gate between the control gate and the oxide tunnel [5, 27, 89, 7]. To store data into a cell has to program it, which means to place a very high voltage to drive electrons to approach the floating gate. However, electrons will stay there unless a reverse voltage is applied to pull them off the floating gate. Such a process is referred to as an erase operation. Note that an erase operation takes a much longer time than a program operation. So it is unacceptable to update "in place" as the time caused by an additional erase operation is too costly. Herein lies the first key issue of NAND flash memory, which is, data have to be updated in an out-ofplace way: data to be updated are first written into a clean page and the original page of the data is invalidated to be dirty. Another issue is the units of the said program and erase operations for flash memory. Because of the fabrication, the unit for a program operation of NAND flash memory is a page, and the unit for an erase operation is a block. Generally a page consists of thousands of flash cells, and a block comprises scores of pages. The out-of-place updating and the access unit constraints are the main concerns for the improvement of access performance of NAND flash memory-based devices.

The third issue of NAND flash memory also comes from the flash cell structure. The oxide layer of the cell, the one that isolates the electrons of the floating gate, is alternatively strained by continual program and erase operations for storing data [82]. In a long run, the oxide layer would be punctured after too many P/E cycles [79]. Then the cell cannot store data any longer. A page that has a permanently defective cell is deemed to be "worn-out". It in turn makes the block it is in worn out. A worn-out bad block is supposed to be kept away from regular use [39, 67]. Worse, a flash chip that has excessive worn-out blocks has to be discarded. Such an issue is referenced as the write endurance of NAND flash memory. It adversely impacts the lifetime of NAND flash devices.

#### 1.1.2 Flash Memory Management

The characteristics of NAND flash memory, including access unit constraints, out-of-place updating and write endurance, are the foundation of all strategies for flash memory management. There are three goals for the flash memory management. First, the utilization of flash blocks and pages should be as high

Figure 1.1: A Logical Structure of NAND Flash Devices

as possible. Second, the performance of data access must be optimal. Third, the lifetime of flash device has to be entailed without too much performance degradation [44, 95].

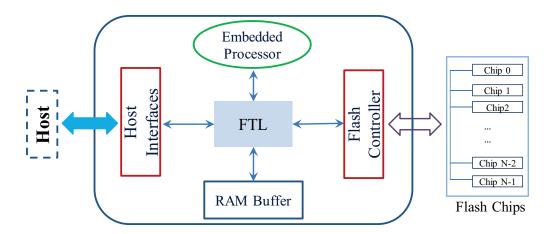

Figure 1.1 shows the logical structure of a common NAND flash device. It has an interface like USB or SATA that connects to the host system. Inside the flash device an embedded processor is equipped for computation. The RAM cache, also referenced as RAM buffer in some literatures, is used to buffer data and metadata. The flash controller conducts write, read and erase operations on flash chips. The FTL, which is abbreviated for the *flash translation layer*, is the embedded firmware that is responsible for the management of a flash device.

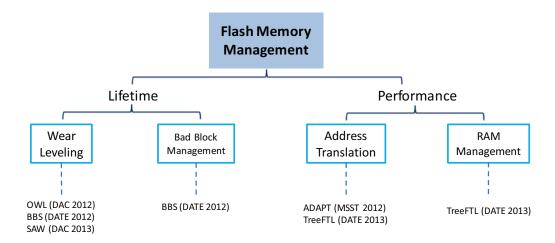

The functionalities of flash memory management include address mapping, wear leveling, bad block management (BBM), RAM buffer management and garbage collection, as is sketched in Figure 1.2. Address mapping is also known as address translation. We will use them interchangeably in this thesis. Address mapping is to map logical addresses given by the host file system to physical addresses in the form of flash block and page. Owing to the constraints of access units as well as out-of-place updating, address mapping of flash device is not that straightforward. Wear leveling is a technique targeting the issue write endurance of flash memory to avoid premature retirement of flash blocks. It aims to even out erase operations across all flash blocks. So it is used to ensure that flash blocks are worn at the same rate. Though, blocks may still go worn-out, and BBM is employed to trace them. RAM buffer is an important component of NAND flash devices. SRAM or DRAM has much shorter latency than NAND flash memory, and to utilize a RAM cache for buffering may favorably affect access performance of NAND flash devices. Garbage collection, also known as the reclamation, is caused by out-of-place updating that leaves invalid, obsolete

Figure 1.2: The Flash Memory Management

data behind. Such dirty data have to be demolished. The blocks and pages they take up can be vacated and cleaned for further use.

All the above functionalities of flash management are performed by one entity, i.e., the mentioned FTL. The FTL may be presented or named in different ways [68]. Here we reference them uniformly as the FTL for the ease of discussion. The FTL is designed in a modular way; each module of the FTL works on one functionality of flash management. Though, how to develop a module deserves special attention as it is not trivial to hold both the effectiveness and the efficiency simultaneously in hand.

#### 1.2 Problem Formulation and Motivation

The ever-increasing utilization of NAND flash memory indicates the bright future of flash devices. As the dollar/capacity offered by flash-based storage devices is continuously decreasing, the utilization would be further boosted. However, the concomitant challenges are ignorable. The dropping of price for NAND flash memory is partially caused by the Multi-Level Cell (MLC) technique to produce flash memory. Briefly speaking, a traditional flash cell can store only one bit per cell, which is called Single-Level cell (SLC) flash. Using MLC technique, two [61] or more [54] bits now can be stored just within one single cell. Since flash memory can be manufactured to be much denser with MLC technique, the reduction of production cost is not beyond expectation. However, the reduction of price is not free of charge on other aspects. Empirical evidence of worsening lifetime and reliability, as well as access performance, of MLC flash memory has been reported [27]. Though, MLC flash is still considered to be the mainstream in

marketplace [28], and most low-end and middle-level SSDs are made of MLC flash chips [15]. The two-fold MLC flash and its prevalence dictate that the embedded software to manage a flash device, i.e., the said FTL, should be fittingly designed to provide satisfying device lifetime and access performance.

Besides the issue of the development of NAND flash memory, which is derived from the innate characteristics of flash itself, the situations where flash device is being environed turn to be a concern also. Different workloads differently impose on the storage device. As access performance and write endurance of flash device are strongly correlated to the workload in service, to be adaptive to workload is widely advocated by researchers and practitioners [1, 15, 17, 45, 64, 78, 111]. A common way to speculate the access behavior of a workload is to assess the ratio of sequential to random requests. Sequential requests are ones that access a large number of pages. Random requests selectively access a handful of pages among a wide range. Flash-based device is believed to be favored by workloads with a high demand for random access requests [78] as flash memory need not rotate the actuator to locate the desired position like ferromagnetic hard disk. Nevertheless, random writes in a large storage space may lead to excessively long response latency, owing to write amplification caused by inevitable garbage collection as well as wear leveling [15, 33]. Worse, because of out-of-place updating, the various workloads of access requests result in various layouts of data across flash blocks. This may not be a big deal for hard disk, or byte-addressable SRAM and DRAM as they support in-place rewriting; for NAND flash memory, however, to recycle used space badly impacts access performance and device lifetime. Therefore, it is desirable for a flash device to have a good understanding of workloads for serving them.

In all, both the flash memory itself and its utilization motivate us to rethink of **how** to manage flash device. On the one hand, the management of flash device must highly regard the specifics of NAND flash memory. The aforementioned address mapping, for example, is not merely to map addresses; to allocate flash pages and blocks is one of its duties. The allocation of blocks and pages must abide by access constraints and erase-before-program issue of NAND flash memory. As for wear leveling, it is just employed to target the issue of write endurance of flash.

On the other hand, the management of flash device ought to be self-adaptive to various workloads. Existing strategies of previous works, however, have limitations on the adaptation. For example, FAST [60] is a classical FTL that was proposed for mapping addresses. It judiciously utilizes the access units of flash memory as well as out-of-place updating in managing blocks and pages to

accommodate data, but it lacks on the ability of handling sequential requests. The successor of FAST, the FASTer FTL [64], emphasizes on workloads found in OLTP systems. But OLTP system just represents one type of workloads.

The third perspective on flash device is to view it in a systemic way. Flash device is used for secondary storage in a computer system. It is not irrelevant to other components of the integration. Two implications lie herein. Firstly, flash device serves the upper-level OS to store and access data; in other words, it conducts communications with OS. So it is able to obtain substantial information from the OS for the purpose of managing flash device. TRIM command [21], which engages the modern OS in informing flash device of reclaiming space in advance, shows the feasibility of notification from the OS to the FTL. Although the TRIM command is simple, more complicated exchange is implied to be possible. Secondly, the management of flash device can be enhanced using the ideas reflected in other parts of the computer system. For example, the mentioned FAST FTL uses the idea of CPU cache for address mapping. The page management of virtual memory [97], as well as the virtual RAM drive constructed by a part of main memory [2], shares similar points with flash device as well. However, as flash itself differs from DRAM-based main memory, they cannot be directly applied to flash device. Though, their ideas are still referential to us.

#### 1.3 Thesis Statement and Overview

Given the challenges described above, the aim of this thesis, is to propose novel strategies for flash management which, on the one hand must take into consideration the idiosyncratic characteristics of NAND flash memory, and, on the other hand should be effective and efficient for a variety of workloads. With these in mind, we have taken three approaches to the problem. Since the FTL is the main agent in charge of managing a flash device, it is natural to start by exploring the internals of the FTL. Thus in the first approach we proposed new modes of the cooperation between modules of the FTL. A module is responsible for one functionality and it has its particular perspective with regards to flash management. The cooperation we proposed is not simply exchanging of messages in between. Rather it is the co-development of modules; a part of one module is embedded into another so as to gain immediate information on the nature of the ongoing accesses. By doing so it is expected that one module can benefit from the sharing with another one.

As flash device needs to be able to handle various workloads, our second attempt is on the workload adaptation of FTL modules. In other words, we intend to construct workload-adaptive modules. As a workload is nothing more than a series of consecutive access requests, the access behavior of a running workload can be learnt accordingly. The learning in turn helps the FTL handle future requests. In the end the management algorithm is able to adapt to different workloads.

The third approach we have explored is on the collaboration between the OS that sits in the upper level and the FTL that is in the lower-level storage device. The OS has good knowledge of applications, files and data, which is not available to the FTL. On the other side, the FTL autonomously manages the flash device in a manner that is transparent to the OS. So we involve the OS in the process of flash management. With the assistance of the OS, the FTL should profit from this involvement.

The main contributions of this thesis, also main ideas of this thesis, are as follows.

- Inter-module cooperation-based management for flash device is investigated. An algorithm for wear leveling, namely *Observational Wear Leveling* (OWL) [105] is proposed. The wear leveling module of OWL is codeveloped within the address mapping module. By doing so, OWL can succinctly classify data and accommodate them accordingly.

- Schemes for workload-adaptive address mapping and RAM buffer management have been proposed. ADAPT [103] is for address mapping and it is able to serve workloads that have variant mixes of sequential and random requests. TreeFTL [107], which manages the RAM buffer of flash device, can dynamically adapt to workloads as it has a self-adjustive structure maintained in the buffer.

- OS-assisted flash management has been studied. An algorithm named OS-Assisted Wear leveling (SAW) [106] was devised. The wear leveling of SAW relies on the OS's hints. The OS is responsible for the analysis over a massive number of files with a model, and the FTL performs wear leveling as it is notified. According to the idea of SAW, a prototype has been established upon open-source systems.

The effectiveness as well as efficiency of these approaches have been verified to be evident and significant by our experiments. We believe that our proposals are positive contributions to the field of flash memory management. We also hope that our explorations will help practitioners improve existing designs. Besides the widespread presence of flash device in mobile systems like smartphones, netbooks and tablet computers, it is also clear that flash memory will play an important role in the next generation of secondary storage for general-purpose computing systems. To summarize, we believe our proposals to be described in following chapters of this thesis will improve the utilization of flash-based storage devices in the near future.

#### 1.4 Organization of the Chapters

In this thesis, the three said approaches with several novel schemes would be described. This chapter has introduced an overview of NAND flash memory, flash-based device and the motivation for novel flash management strategies. Chapter 2 will give a detailed background of NAND flash memory. Chapter 3 surveys flash device and state-of-the-art schemes that were proposed for flash memory management. They are for different functionalities and the essence of their designs would be discussed. Chapter 4 is what we did to verify the effect of the module-cooperative approach. It presents the Observational Wear Leveling (OWL). For OWL, the module of address mapping assists the module of wear leveling to allocate flash blocks to data. In other words, address mapping classifies data and wear leveling accommodates them subsequently. Through cooperation the wear evenness is significantly improved with ignorable performance overheads. Chapter 5 and Chapter 6 are our attempts to develop workload-adaptive modules for flash management. Chapter 5 presents ADAPT. As mentioned, ADAPT is able to be adaptive to workloads that are variously mixed with random accesses and sequential accesses. Chapter 6 proposes an algorithm named TreeFTL [107] for RAM buffer management. TreeFTL is succinctly sensitive to running workloads. It adapts to workloads by dynamically partitioning the RAM space for buffering data and mapping addresses. The performance improvement has been reported through the employment of TreeFTL and ADAPT, respectively. Chapter 7 is about the OS-Assisted Wear leveling (SAW). For SAW, the OS is not unaware of flash memory management any longer. Instead, the FTL conducts wear leveling with hints provided by the OS. The hints are generated online through a model over a large number of files. The wear evenness is consequently improved due to the participation of the OS. Chapter 8 will conclude this thesis and possible future works would be briefly presented.

# Chapter 2

# Background

This chapter gives an overview of NAND flash memory as well as tactics preferred for flash memory management. It first details physical characteristics of NAND flash memory, including issues about flash cells, out-of-place updating and write endurance. Following these are aspects of flash memory management, including the modules of wear leveling, address mapping, RAM buffer management and bad block management, etc.

#### 2.1 NAND Flash Memory

NAND flash memory was invented by Masuoka et al. [71] of Toshiba. Its full name could be NAND flash Electrically Erasable Programmable Read-Only Memory (EEPROM or E<sup>2</sup>PROM) [89]. All the characteristics of NAND flash memory, as well as the modules of flash management firmware, are based on the structure of a NAND flash cell.

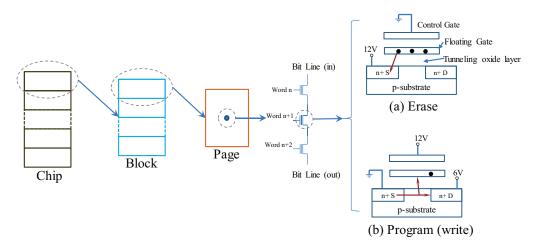

Figure 2.1: Structures and Operations of NAND Flash Memory

Flash Cell, Page and Block Figure 2.1 shows a sketch of the structure of a flash cell, with erase and program operations alongside. A flash cell is a transistor with an extra floating gate. Flash memory makes use of charge stored on the floating gate to accomplish the non-volatile storage [7]. The floating gate is a metal strip between the control gate and the tunnelling oxide layer of the transistor. It is sandwiched with oxide insulators, which enables the cell to retain charge for a long period of time even if the circuit power supply is cut off. To program or erase a flash cell is just to drive electrons. When the erase operation is conducted, under the voltage the electrons at the floating gate will be ejected to the source by tunnelling. The cell after an erase operation is in the '1' state. To program a cell to be '0' state, a reversed voltage must be applied to the control gate, and then electrons are driven to approach the floating gate.

SLC flash and MLC flash There are two types of NAND flash memory. One is single-level cell (SLC) flash memory of which each cell stores one bit. On the other hand, a cell of multi-level cell (MLC) flash is able to store two bits or more. Note that for SLC flash memory whether the bit is '1' or '0' is decided through sensing the voltage. The range of the voltage is divided into two halves with a threshold. If the voltage sensed is higher than the threshold, it is deemed to be '1'. Otherwise it is '0'. For MLC flash, more thresholds are inserted to set up more divisions over the voltage range. For example, if the range of the voltage is divided into four quarters, the cell can represent '00', '01', '10' and '11'; commonly two bits are stored in an MLC flash cell [26]. Products that have three bits stored in a cell are available in marketplace today. However, the increase of density is at the cost of the worsening endurance for a flash cell.

Out-of-place updating To do in-place updating is not reasonable for NAND flash memory. It is due to the physical characteristics of the flash cell. As is mentioned, electrons are trapped until an erase operation is conducted to pull them away. Considering the access units of NAND flash memory, to update data requires that a page should be rewritten. A flash page cannot be individually erased unless the whole block it is in is erased. Put in another way, if we tried to do in-place updating on a single page, we would have to rewrite all pages in a block after an erase operation. In this way the overhead caused by a write operation would be too significant due to many writes plus one erase operation. Out-of-place updating is yet acceptable. Every time data in a page are to be updated, an erased page will be allocated to accommodate them; the original page will be invalidated then.

Write endurance The issue of write endurance is another problem of NAND flash memory, which is also ascribed to the physical characteristics of flash

cells. It is obvious that both program operation and erase operation alternatively strain the oxide layer of a cell through applying voltages to drive electrons. After undergoing too many program/erase (P/E) flips (the reversals of voltage), finally the oxide layer cannot isolate the floating gate any longer. The limitation for MLC NAND flash memory is much tighter than SLC flash. For the former, it is about 10,000 cycles for a page; for the latter, it is about 100,000 cycles. As is said, the range of the voltage for NAND flash memory is divided into more parts. To program the bits for writing requires much more elaborate techniques. The finer adjustment adversely impacts the physical tolerance of the flash cell. This explains why MLC flash devices have a much shorter lifetime. For SLC flash devices, though it has a longer lifespan, the upper bound of P/E cycles is still not so satisfying for use.

#### 2.2 Modules of Flash Memory Management

The said flash translation layer (FTL) is the one that is responsible for the management of flash device. It can be found in flash-based block devices, such as SSDs or USB sticks. In an MTD device made of raw flash [98], it is presented in another form. As their functions are identical, we will reference them uniformly as the FTLs for the ease of discussion.

The FTL emulates flash devices like traditional block-interface devices to hide special characteristics of NAND flash memory. Main functionalities of flash management, including wear leveling, address translation, bad block management, RAM buffer management and garbage collection, are represented by respective modules of the FTL. We will first give an overview of wear leveling and address translation, as they are two basic modules for flash memory management.

Wear Leveling Wear leveling targets the issue of write endurance of flash memory. As is mentioned, limited program/erase flips exist for a flash page. However, previous algorithms of wear leveling mostly focus on erase operations as the physical limitation is mainly caused during the erasing procedure [89]. On the other hand, to reduce program/erase flips at the page-level is not reasonable as the unit of erase operations is a block. Besides, the coarser granularity of erasures can ease the module of wear leveling. Hence, it is preferred for wear leveling to spread erase operations over flash blocks.

Wear leveling's common tactic is to classify data and put them into suitable aged blocks. To do so a data structure called the *block aging table* (BAT) is needed [40]. It is used to record the age of each block. The age here refers to the erase count of a flash block. The more the erase count, the older the flash

block. As for data, they would be identified to be either hot or cold. Hot data are ones that are frequently updated. Otherwise, they are cold data. This is an inaccurate and rough classification on data. Because cold data are seldom or never rewritten after storage, they are preferred to being put into elder blocks. In this way elder block can avoid being erased soon. On the other hand, given a younger block that is used to accommodate hot data, as the data are likely to be invalidated soon, it would be erased soon for reclamation. Therefore, the wear evenness over flash blocks is gradually achieved.

Traditionally algorithms of wear leveling are classified into two categories. It can be either dynamic or static [10, 40]. Dynamic wear leveling generally selects the youngest free block for new data. Static wear leveling may vacate the block currently occupied by cold data for use. The latter is more prevalent today because all blocks are under consideration. Another perspective to classify wear leveling schemes is on how the module of wear leveling is triggered: an algorithm can be deemed to be proactive, passive or hybrid [105]. Proactive wear leveling aims to put data in suitable aged blocks actively. Upon allocation requests, the access frequency of the data has been estimated, and a block would be found and allocated accordingly. The overhead to do estimation is inevitable. Passive wear leveling swaps data between blocks when the wear evenness over blocks has been worsened beyond a certain limit. Hence, the evenness has to be continually detected at runtime. Hybrid wear leveling has both features.

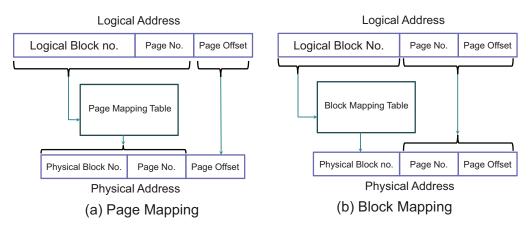

Address Mapping Address mapping, also known as address translation, is to translate logical addresses given by file systems to physical addresses in the form of flash block and page [103, 118, 107]. Page mapping and block mapping are two basic mapping schemes. Figure 2.2 sketches them.

Given a logical address, the FTL looks up in the mapping table to find the corresponding physical block number in the case of block mapping, or physical block number and page number in the case of page mapping. Page mapping is flexible to relocate data among pages. However, the overhead due to the fine granularity cannot be ignored. Specifically the size of the mapping table is troublesome. For a 64GB SSD with 2KB per page, there would be more than 32 million entries in the table. If 4 bytes are used for an entry, the table will be 128MB. It is difficult to maintain such a large table in RAM buffer for reference.

On the other side, block mapping works at the block-level. It has a much smaller mapping table, but it lacks flexibility owing to its coarse granularity. For a logical page, it can only reside within the same physical page of different blocks under block mapping. Therefore, to rewrite a page will cause block-level copying because data in neighbouring pages have to be migrated to next physical block

alongside. It is arduous to move so many data at one time for one single rewrite.

Figure 2.2: Page Mapping and Block Mapping

Hybrid mapping combines page mapping and block mapping. It separates all physical blocks into the *data space*, *log space* and *free block pool*. Each logical block is mapped to a block in data space using block-level mapping. As block mapping is not flexible, the log space is maintained to temporarily hold updates in page mapping. Updates are first absorbed by log pages. They will be merged to data space afterwards. Details of hybrid mapping will be shown in Chapter 3.

Bad Block Management (BBM) BBM can be viewed as an extension of wear leveling. It is used to trace bad blocks that contain permanently defective cells. Note that some bad blocks are already present when the flash device is shipped [39]; they are referred to as *initial* bad blocks. In the beginning, initial bad blocks are marked and recorded in a *Bad Block Table* (BBT) [37] by manufacturers. The worn-out block is another type of bad blocks that come out at runtime. A flash cell is likely to go defective after it undergoes excessive P/E cycles. If a cell wears out, the page it is in, as well as the block, will be identified to be *worn-out*. Worn-out bad blocks are recorded in the BBT also. In tradition, bad blocks are supposed to be kept away from regular use.

RAM Buffer Management RAM buffer is an important resource of NAND flash devices. The RAM buffer is made of SRAM [29, 86], DRAM [43, 49, 94, 99] or non-volatile RAM [47, 66, 83]. Although flash memory can be accessed at a much higher speed than magnetic hard disks, the gap between the requirement of host system and the performance of flash device is still wide. Moreover, considering the said out-of-place updating, a buffer to cache updated data is very necessary for a flash-based device.

Besides the metadata related to flash management, entries of the address mapping table and data pages are also cached in the RAM space. In this way, RAM buffer management serves the module of address mapping. Previously, the RAM space is used for one purpose, either address mapping or data buffering. Recently how to manage the RAM space for both uses has been explored.

Garbage Collection Garbage collection, also known as the reclamation [25], is usually designed within the wear leveling and/or address mapping. It is due to the out-of-place updating during address remapping. Invalid dirty data may be scattered across blocks after a period of execution [12, 15, 65]. When there are no flash blocks left for use, ones that have invalid data will be reclaimed. Yet valid data might exist in the block also. Therefore, for a victim block, the module of garbage collection needs to bypass invalid data, and move valid data to another clean block [33]. Then the victim block can be erased for future use. Besides affecting resource utilization, the scheduling of reclamation may have an impact on the access performance too.

#### 2.3 The Background of the Era

The strategies to manage flash device were simple when they were primarily utilized. The capacity of a flash device was in a small magnitude three decades ago. To assure wear evenness or conduct garbage collection in a 128MB flash drive at that time is much easier than a 1TB SSD today. The situations in which flash memory was equipped were not complicated also. It was mainly used in USB drives or digital cameras. Access behaviors observed in these portable computing systems are usually discontinuous and bulky. Such simple access patterns are not difficult for the FTL to handle.

Things have changed a lot in the past thirty years. The presence of smartphones and tablet computers, as well as the upgrade of enterprise servers, requires that the secondary storage should be supported by a lightweight, shock-resistant and energy-efficient material. Undoubtedly NAND flash is a promising candidate. Thanks to the development of manufacturing and techniques like MLC, the flash device now can be produced in a huge capacity at a lower price. However, the ever-increasing utilization and expansion make the flash device confront unprecedented obstacles. The challenges met by flash devices that are exposed to various workloads are real and tough. How to manage flash device effectively without loss of efficiency in different systems deserves thorough investigation; otherwise the further use of flash device will be hindered. Researchers and practitioners are pondering, as solutions to the above problems are about to enhance the utilization of flash devices. On this ground, next chapters will show our proposals to mange flash device for both effectiveness and efficiency.

## Chapter 3

### Literature Review

Before the descriptions of our approaches, we will first present flash device and its past and potential. Then an overview of existing designs about flash memory management would be shown. Related works will be categorized according to the aspects of flash memory management, including previous schemes for wear leveling, address mapping and RAM buffer management. The strategies relevant to the design of management modules would be discussed also.

#### 3.1 Flash Device and Its Potential

The evolution of flash memory entails it to be a promising candidate for the secondary storage of computer systems. The presence of flash device, however, is not unique. Generally speaking, there are two types of flash device. One is the raw flash device, which can be seen everywhere today as it is used in smartphones. The raw flash device directly exposes the physical characteristics of flash memory to the system, and the MTD hardware driver [98] helps the system write and read data. Flash memory management, though, is performed either by flash file systems or extra software layers. Note that file systems like Ext4 or NTFS cannot work immediately on raw flash devices. Flash file systems are ones that have been developed specifically for raw flash, including JFFS2 [112], YAFFS and YAFFS2 [70], as well as UBIFS [36]. These file systems cooperate with MTD drivers for data storage and access. They differ from Ext4 or NTFS in that they take into consideration characteristics of flash like erase-before-program issue and write endurance. So besides functionalities of common file systems, they also integrate modules relevant to flash management. JFFS2, YAFFS and YAFFS2 manage the flash device by themselves. UBIFS has a specific software layer called the UBI [23]. UBI can be viewed as a customized FTL for UBIFS. UBI has modules for address mapping and wear leveling while the garbage collection

is performed by UBIFS.

Another form of flash memory is to encapsulate flash chips into a drive that has a block input/output interface such as SSDs, USB thumb drives and micro-SD cards. Here the *block* does not means a flash block; the former is a sequence of bytes with a fixed length, used for data access and transmission, and the latter is the unit of erase operation of flash memory. In this thesis we will use the *block-interface device* to stand for *block device* to distinguish. Factually a basic use of FTL is to hide specifics of flash and emulate a flash device to be a block-interface device. By doing so, the flash device is able to be compatible with existing systems.

With the assistance of the FTL, file systems like Ext4 or NTFS can access data from block-interface flash-based device. It is not necessary for file systems to care about flash management as JFFS2 and YAFFS2 do. The FTL will be responsible for all management functionalities instead. As SSDs are springing in marketplace, much attentions have been paid to its inroad into enterprise servers and personal computers. Agrawal et al. [1] investigated the design tradoffs for SSD performance. They revealed that the access performance and the device lifetime of SSDs are highly workload-sensitive. They also argued that the layout of data is critical to both load balancing and wear leveling.

Later Narayanan et al. [78] gave an analysis on whether it is worth migrating the secondary storage of enterprise servers from ferromagnetic hard disks to SSDs. Their emphasis is on the cost versus capacity of SSDs. They addressed that the price of SSDs has to be decreased much more in order to replace HDDs. At the same time, Chen et al. [15] did experiments on low-end, middle-level and high-end SSDs to get insightful understanding upon performance issues of SSDs. Through measurements they found that the management of flash device ought to be more efficient for workloads. Other investigations for data-intensive workloads with flash memory were conducted as well [8]. Grupp et al. [27] did empirical estimates over flash memory to predict the future of SSDs. Their results point out that the density gain due to MLC techniques adversely impacts both performance and reliability of flash memory, which implicitly highlights the importance of the management firmware.

Besides real measures performed to flash products, the simulation of flash device is also attractive. For example, nandsim is a useful tool to simulate a raw flash device. It has been included in the Linux kernel [76]. Agrawal et al. [1] extended the DiskSim simulator to simulate an idealized SSD. Kim et al. [53] proposed FlashSim simulator, which is trace-driven and object-oriented. FlashSim allows researchers to implement their own FTLs for evaluation.

#### 3.2 Algorithms of Flash Management

In this section the classical algorithms on facades of flash memory management are presented. Fundamental and classical schemes would be presented in details while others are briefly described.

#### 3.2.1 Schemes for Wear Leveling

Table 3.1 shows four algorithms that were recently proposed for wear leveling. They all fall into the category of static wear leveling, although how they perform wear leveling significantly varies. Among these algorithms, the dual-pool scheme [9], BET [14] and lazy wear leveling [10] are activated only when the level of wear unevenness reaches some thresholds. So they perform wear leveling in a passive way.

Table 3.1: A Summary of the Latest Wear Leveling Algorithms

|                         |           | <u>~</u>                           | 0               |

|-------------------------|-----------|------------------------------------|-----------------|

| Algorithm               | Туре      | Block Organization                 | Address Mapping |

|                         | Passive   | Hot pool and cold pool: a block    |                 |

| Dual-pool [9]           |           | with valid data is in either pool, | Not constrained |

| Duai-poor [9]           |           | where blocks are prioritized upon  |                 |

|                         |           | their erase counts.                |                 |

|                         | Passive   | Block sets and BET: A set has      |                 |

| DET [14]                |           | one block or several consecutive   | Not constrained |

| BET [14]                |           | blocks to correspond a bit in the  |                 |

|                         |           | block erasing table (BET).         |                 |

|                         | Proactive | Multiple block lists: blocks that  | Page mapping +  |

| Rejuvenator [74]        | + Passive | have the same erase count are      | Hybrid mapping  |

|                         |           | grouped in a list.                 |                 |

| Lagranger leveling [10] | Passive   | Common way: free block pool,       | Urbrid manning  |

| Lazy wear leveling [10] |           | valid block pool, etc.             | Hybrid mapping  |

In dual-pool algorithm, hot data and cold data stay in the hot pool and the cold pool, respectively. When the difference on the erase count between the head of the hot pool and the rear of the cold pool exceeds a predefined threshold, the two blocks will swap their places. For each pool, it may also be adjusted by exchanging data between blocks to adapt to dynamic workloads.

The block erasing table, abbreviated as the BET, is a key structure of the algorithm developed by Chang et al. [14]. We shall use this acronym to reference their algorithm. For BET, blocks are first divided into sets, and a set may have one block or more. The BET consists of bits; each bit represents a block set. When a predefined interval begins, all bits in the BET are initialized to be '0'. If one block of a block set is erased within the interval, its associated bit in the BET will be set to '1'. The total number of erasures in the interval is recorded. If the count of erase operations over the number of erased blocks exceeds a predefined

threshold, BET will repeatedly pick un-erased blocks of the last interval, and perform data transfers, after which it will erase them until the wear skewness is smoothed out.

Jung et al. [44] proposed a group-based wear leveling algorithm which is similar to BET, as it records the summary information for a group of logically consecutive blocks. By doing so the memory footprints can be reduced. The main tactic of this group-based algorithm is on data swapping between flash blocks. It also considers the performance degradation due to inevitable wear leveling actions.

Lazy wear leveling [10] is a recently proposed scheme. It is performed in the merge procedure of hybrid mapping. As is mentioned in Chapter 2, the hybrid mapping maintains the block mapping between logical blocks and data blocks while the page mapping is used to temporarily hold updated data with log blocks. The merge is a procedure during which valid data of a victim log block are merged with valid data from corresponding data blocks into newly-allocated blocks. Prior to lazy wear leveling, a data block that is involved during merge, say D, will be immediately erased. In lazy wear leveling, however, if D's erase count is higher than the average by a threshold  $\Delta$  which can be tuned online, besides erasing D, the FTL will find a data block with cold data, say C, transfer C's data to D, erase C, and return C as a free block for future use.

In summary, the dual-pool scheme responds to the widening gap between two blocks' erasure counts, the BET scheme is activated when the erasures are unevenly distributed beyond an extent, and lazy wear leveling works when the block to be reclaimed is much older than the average. These reasons explain why we deem them to be "passive".

Rejuvenator [74] has both proactive and passive mechanisms. It allocates hot or cold data to young or old blocks respectively in a proactive way. It records recent access frequencies of logical pages, and identifies the temperature of pages accordingly. It also groups blocks that have the same erase count in a list. A list is in the *lower numbered lists* if its erase count is smaller than a dynamic threshold; or it is in *higher numbered lists*. When new write requests arrive, based on the recorded access information, cold data are put into younger blocks of the lower numbered lists using page mapping, and hot data are placed in elder blocks of the higher numbered lists in hybrid mapping. Between the smallest and biggest erase counts is a window. If the number of free blocks in either partition drops below two thresholds ( $T_L$  and  $T_H$ ) respectively, data will be moved out from the lowest list to upper lists, and the window is then adjusted. This is how Rejuvenator performs passive wear leveling.

Recently the reason of write endurance has been investigated in terms of bit error rate of flash cells, and algorithms have been designed accordingly [79, 117]. For the ERA algorithm proposed by Yang et al. [117], the metric to spread erase operations inside a flash device is imposed on error rates of blocks. Yet the spreading is based on data migration between flash blocks. Besides, analytic models for wear leveling of flash memory [96] were also constructed; they are referential to designers.

#### 3.2.2 Schemes for Address Mapping

Address mapping should be the most fundamental function of the FTL. Without it the flash device could not be usable at all. Page mapping [3] and block mapping [4] were devised based on the access units of page and block respectively. They are primary and simple. For an early flash device with a small capacity, they are sufficiently effective. However, with the advent of flash devices at a large capacity, the algorithms of [3] and [4] are not satisfying any longer as page mapping suffers from the large spatial overheads of address table while block mapping is inflexible at updating data [113, 103]. On this ground hybrid mapping that combines page mapping and block mapping was proposed.

The first attempt of hybrid mapping is BAST [52]. Its successor FAST [60] introduced more flexible associativity. FAST was in turn succeeded by FASTer [64] that exploited temporal locality for further performance improvement.

It is mentioned that hybrid mapping maintains data blocks using block-level mapping as well as a fixed number of log blocks in page-level mapping. Updates are first put into a log page instead of allocating a new data block. Hence, the log space formed by log blocks acts like a cache of processors [31] to data blocks. In BAST, there is a fixed one-one mapping between data blocks and log blocks. This inflexibility results in a poor utilization of log space. FAST, on the other hand, adopts a fully associative mapping between log space and all data blocks: a log block is no longer designated to one data block but shared by all. Thus, in terms of cache associativity, BAST maintains a direct mapped cache and FAST is fully associative. More complicated N-way associative schemes of log blocks have also been devised. Physical blocks are grouped together, and they are associated to a set of log blocks; the size of the set may be dynamically changed at runtime [80, 55]. Mapping schemes, like the superblock [46], LAST [62], KAST [18] and WAFTL [111], are also in the category of hybrid mapping but emphasize on garbage collection, multitasking and real-time systems, respectively. Besides, RNFTL [109] improves the utilization of flash blocks through reusing clean pages in blocks to be merged.

Mapping schemes that are conducted on other granularities have been proposed also [113, 63]. Generally they are derived from the above three categories. One is a set-based mapping strategy [19]. Each set contains multiple blocks. Logical sets are mapped to physical sets with another table used to store the mapping of logical block to physical block in a set. Lately another scheme is based on the concept of working set [116]. Additionally, Janus-FTL [56], as its name suggests, attempts to strike a balance between page mapping and block mapping at runtime.

Typically, the log space of hybrid mapping is over-provisioned to be 3% of all space [59, 64]. It is usually partitioned into a sequential area for sequential writes and a random area for random writes. FAST assigns one log block as its sequential area while LAST maintains a fixed number of blocks. They also have methods to identify whether a request is sequential or random.

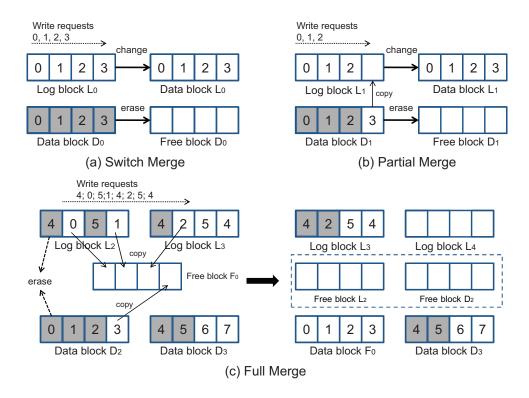

It is natural to process access requests for hybrid mapping. When a write request arrives, the FTL first checks whether the page in the mapped data block is clean. If not, a log page will be allocated to accommodate the data. The old copy will be invalidated. The relationship between the logical page and the log page is recorded in the log page mapping table. When no clean page is left in the log space, a victim log block will be picked out and merged with corresponding data blocks. After merging, the victim is erased and returned to the free block pool. Another clean block will be allocated to replenish the log space. Figure 3.1 is adopted from [62]. In Figure 3.1 a square is a page and a rectangle of four squares represents a flash block. The number in each square is the logical page number that it maps to. Data in a shaded page are invalid. In Figure 3.1(c), logical page 2 is mapped to data block  $D_2$  but cannot be rewritten directly. A page in log block  $L_3$  has to be allocated. Successive updates can be handled by more log pages, and mapping entries are changed accordingly. In Figure 3.1(c), three log pages in  $L_2$  and  $L_3$  are used for logical page 4. If all pages of log blocks are exhausted, a merge procedure must be performed to make space.

Figure 3.1 shows three types of merge in FAST. Switch merge and partial merge have lower overheads, and are expected in the sequential area. For a switch merge (shown in Figure 3.1(a)), the log block contains contiguous valid data from the same logical block. It can therefore be simply switched to data space. In a partial merge, the log block will also replace its relevant data block but some valid data in current data block have to be transferred to it first, as shown in Figure 3.1(b). Full merge is more complicated. FAST is fully associative and each log block is shared by all data blocks. Thus, a full merge is costly because each page with valid data in the log block must be (potentially)

Figure 3.1: Three types of merge(adopted from Lee et al. [62])

merged with a different data block. This requires many writes and erasures. FAST and FASTer organize the random area in a FIFO queue (that they called "round-robin"), and the victim log block for the full merge would be the one at the head of the random area.

Recently, content-aware FTLs that attempt to reduce duplicate writes have been proposed too. Examples include CAFTL [17] and CA-SSD [30].  $\Delta$ FTL [114] also considers content locality; if a similar copy comes for an existing data segment, only the difference will be stored by  $\Delta$ FTL. In all, they can potentially benefit from the content detection and reduction.

#### 3.2.3 Schemes for RAM Buffer Management

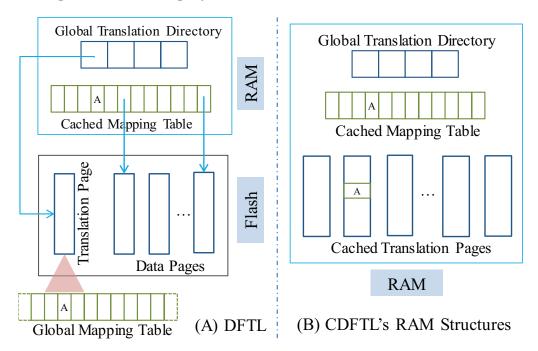

To manage the RAM buffer is an important responsibility of FTLs. Metadata and data that are under request both pass through the RAM buffer, so the RAM buffer is the most suitable one to reflect access behaviors of workloads. FTLs use RAM space to hold mapping entries. DFTL [29] loads entries from translation pages on demand. Besides single entries, CDFTL [86] selectively caches translation pages in a two-level structure, as is shown in Figure 3.2. Mapping entries form the first level, the *cached mapping table* (CMT). Evicted entries from the

CMT are first absorbed by cached translation pages in the second level. The second-level exploits the spatial locality in workloads since neighbouring logical addresses in a same translation page are likely to be accessed. DAC [85] is similar to CDFTL on caching mapping entries but the former works at block-level for large-scale flash storage systems.

Figure 3.2: Page-level Mapping: DFTL and CDFTL

Data buffering, especially for write requests, is another use of RAM space. A flash page is the buffering unit due to NAND flash memory's access constraints. BPLRU [51] utilizes a padding strategy within hybrid mapping. Unlike RAM buffer management that only writes data to flash memory upon evictions to free up space, BPLRU may read data from flash memory to pad a log block and flush all data of a block back. Padding is expected to avoid arduous merge procedures. However, reading data pages also costs time. A scheme named l-buffer [13] has been proposed to trade off padding for merging, and vice versa. Beside locally caching inside an individual device, buffering data for multiple flash devices have also been investigated. FlashCoop [110] is exemplary to show how to make use of remote RAM buffer of SSDs that are from neighbouring servers for data buffering.

APS [94] and JTL [35] are two recent proposals that use the RAM cache for mapping and buffering jointly in a flash device. APS reserves two small areas of RAM as "ghost caches". One is maintained to keep metadata of evicted mapping entries, while the other maintains the metadata of evicted data pages.

They are used to compute the expense caused by not enlarging the cache for mapping and buffering, respectively. Write or read misses in actual cache may hit in ghost cache. A cost-benefit model is built on these hit statistics to estimate the benefits of enlarging either partition. Because APS's estimation is based on values of the past interval, there are delays in adjusting to runtime workload. Moreover, APS uses the least recently used (LRU) algorithm at page-level or entry-level to find a victim for evictions in respective partition. The overhead of frequent LRU selections can be significant since tens of thousands of data pages and mapping entries exist in the RAM.

JTL statically partitions the RAM space into two halves, one for mapping, and the other for buffering. JTL uses a multi-level structure to manage mapping entries. For the level n  $(n \ge 0)$ , it has  $2^n$  entries. The number of levels is determined by the size of the RAM partition dedicated to mapping, and the size of a single entry. All levels are divided into two groups. As RAM cache is halved for buffering data pages, the mapping entries for these buffered pages form Group 0 and take up positions from level 0 to m. Remaining levels fall into Group 1, and their entries correspond to data pages that are still stored in flash. The entry in the top level corresponds to the most recently used data page. The entry of the newly-accessed page will drive the current entry in the top level to move down. One entry at level 1 may need to move to level 2 if no vacancy exists. More moves may follow in next levels. The victim to be moved in each level is randomly selected as entries in the same level is deemed to have similar access recency. When an entry reaches level m+1, its cached data page in RAM will be flushed to flash memory. By doing so, JTL can keep the recently used mapping entries and data pages cached in RAM.

## 3.3 Strategies Behind Flash Management

#### 3.3.1 Module-Cooperative Flash Management

Module cooperation is based on the hypothesis that modules can help each other within flash memory management. At the beginning of utilizing flash devices, the cooperation between modules were not necessary. Three decades have passed, and unprecedented obstacles come out to hinder the further use of flash-based storage devices. The module-cooperative approach turns to be the first feasible and possible way to seek for improvements.

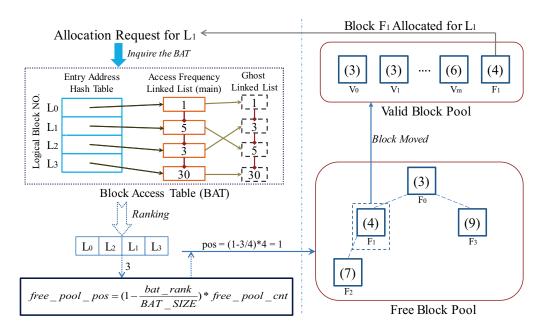

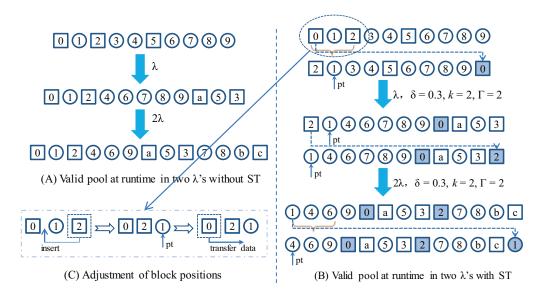

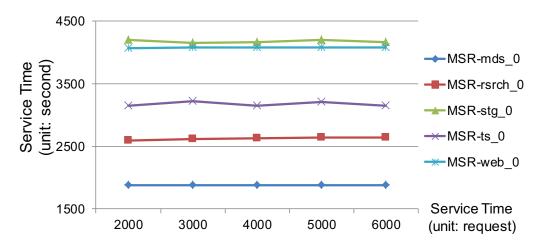

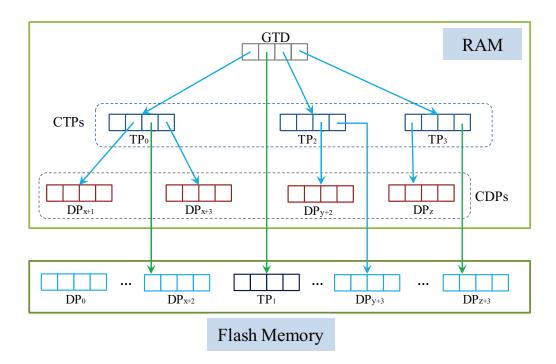

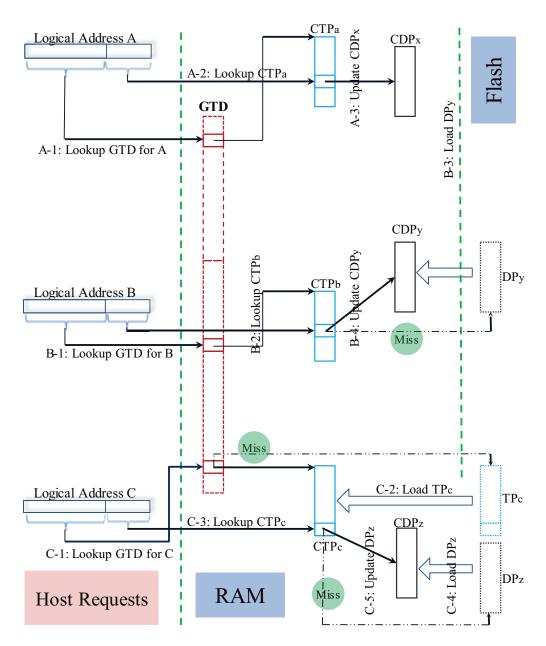

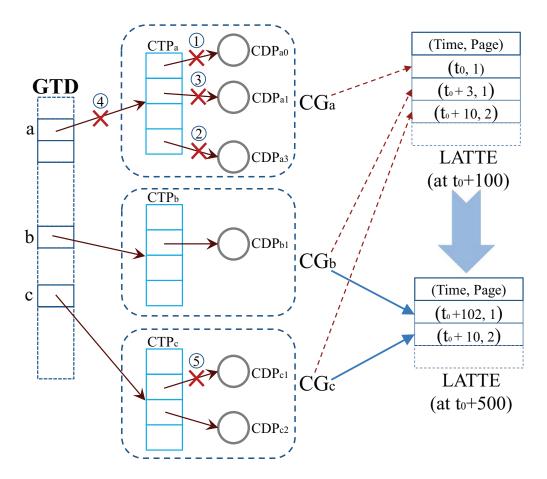

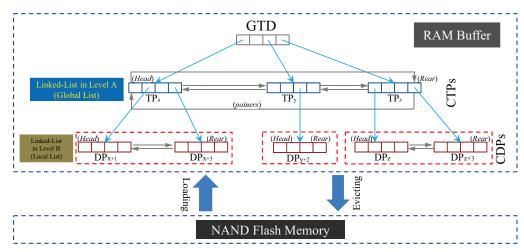

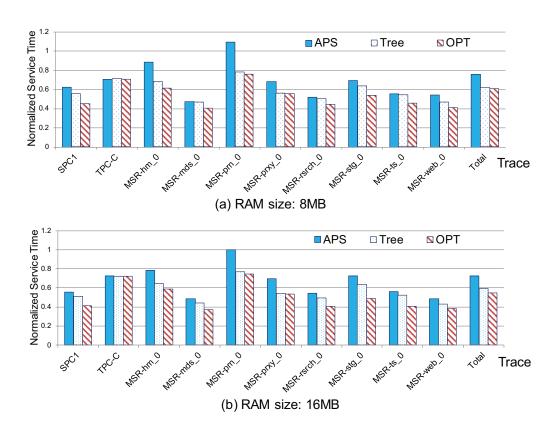

There have been some schemes proposed to make one module cooperate with another one. Let us take BPLRU [51] and l-buffer [13] that are for RAM buffer management for example. They both involve hybrid address mapping in. It