# ELECTROCHEMICAL DEPOSITION OF CIS FILMS FOR PHOTOVOLTAIC APPLICATIONS

ZHANG SHIYUN (B.Eng (Hons.), NTU)

# A THESIS SUBMITTED FOR THE DEGREE OF MASTERS OF ENGINEERING

# DEPARTMENT OF MATERIALS SCIENCE AND ENGINNERING NATIONAL UNIVERSITY OF SINGAPORE

# DECLARATION

I hereby declare that the thesis is my original work and it has been written by me in its entirety. I have duly acknowledged all the sources of information which have been used in the thesis.

This thesis has also not been submitted for any degree in any university previously.

ninguistione

Zhang Shiyun

26<sup>th</sup> Apr 2013

#### ACKNOWLEDGEMENT

I would to express my gratitude to the following people whom have in a way or another has contributed and/or helped me to make this entire Masters of Engineering study possible.

- Associate Professor, Dr. Blackwood D.J., Faculty staff of department of Materials Science & Engineering, for all your valuable guidance, patience and support.

- Director of MMI Holdings Ltd, Mr. SH Lee, for all past support and giving me the privilege on flexible working hours to make travelling down to school for evening class possible, as well as the grace to allow me study and run projects during working hours.

- Deputy Director, Mr. Jeffery Leong, Head of Department of Materials, Devices & Reliability Analysis (MDRA) and all fellow colleagues in MDRA department in A\*STAR-Institute of Microelectronics (IME) for your kind support and encouragement, as well as the privilege to access lab capabilities after working hours.

- Scientist, Dr. Chentir Mohamed Tahar, Institute of Microelectronics (IME) for the valuable guidance in getting XRD plots in place and valuable advices cum technical support.

- 5. Laboratory Technologists, Mr. Chen Qun, for your continual support XRD test and arrangement.

- 6. Laboratory Technologists, LEE Koi Kong Roger, for your kind and helpful support in getting annealing furnace done without

much hassle, and making the extra effort to collect samples outside NUS after working hours.

- Research staff and students under Prof. Blackwood (Hamed, Guiyang, Dong Qing, Rachel and Eugene) for your endless support and help in laboratory work and schedule.

- Senior Engineer, Mr. Stephan Tan, Delphi Automotive Singapore Pte Ltd, for believing in me that part time studies is still possible with all the encouragement as well as the valuable technical advice.

- 9. All Precision Magnetic Singapore Pte Ltd ex-colleagues for rendering all the help and support in balancing work and school loadings, getting Mo-strips samples done in workshop.

- My beloved family members and friends for all your countless support, prayers and encouragement. Thank you for believing in me.

## **TABLE OF CONTENT**

| ACKNOWLEDGEMENT  | II  |

|------------------|-----|

| TABLE OF CONTENT | IV  |

| SUMMARY          | VI  |

| LIST OF TABLES   | VII |

| LIST OF FIGURES  | IX  |

| 1. INTRO | DDUCTION                                          | 1   |

|----------|---------------------------------------------------|-----|

| 1.1      | THIN FILMS SOLAR CELLS – COPPER INDIUM DISELENIDE | 5   |

| 1.2      | PHOTOVOLTAIC DEVICES                              | 9   |

| 1.3      | DOPING AND DEGENERACRY OF SEMICONDUCTOR           | .10 |

| 1.4      | ELECTRODEPOSTION OF CUINSE2                       | .17 |

| 1.5      | DENDRITE GROWTH                                   | .25 |

| 1.6      | ANNEALING OF COMPOUNDING PRECUROSOR               | .28 |

| 1.7      | BACK CONTACT – Mo                                 | .33 |

| 2. EXPE | RIMENTAL DETAILS                                 | 35   |

|---------|--------------------------------------------------|------|

| 2.1     | SUBSTRATE PREPARATION                            | 35   |

| 2.2     | DEPOSITION OF CIS THIN FILMS                     | 35   |

| 2.3     | POST TREATMENT                                   | 37   |

| 2.4     | ELEMENTAL ANALYSIS BY ENERGY DISPERSIVE X-RAY (E | EDX) |

|         | SPECTROCOPY                                      | 38   |

| 2.5     | SURFACE MORPHOLOGY EVALUATION BY SCANNING        |      |

|         | ELECTRON MICROSCOPY (SEM)                        | 38   |

| 2.6     | PHASE ANALYSIS BY X-RAY DIFFRACTOMETER (XRD)     | 39   |

| 2.7     | ELECTRICAL CONDUCTIVITY BY PHOTOELECTRO-CHEMI    | CAL  |

|         | (PEC)                                            | 39   |

| 3. RESU | ILTS & DISCUSSION                             | 43    |

|---------|-----------------------------------------------|-------|

| 3.1     | ELEMENTAL ANALYSIS BY ENERGY DISPERSIVE X-RAY | (EDX) |

|         | SPECTROCOPY                                   | 43    |

| 3.2     | SURFACE MORPHOLOGY EVALUATION BY SCANNING     |       |

|         | ELECTRON MICROSCOPY (SEM)                     | 49    |

| 3.2.1   | CROSS-SECTION VIEW                            | 49    |

| 3.2.2   | SURFACE PROFILE MORPHOLOGY                    | 52    |

| 3.3     | PHASE ANALYSIS BY X-RAY DIFFRACTOMETER (XRD)  | 66    |

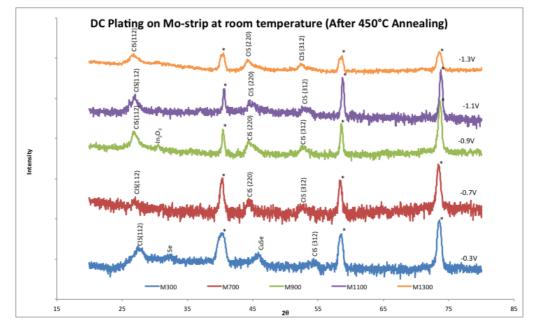

| 3.3.1   | MO-STRIP BY DC PLATING AT ROOM TEMPERATURE    | 66    |

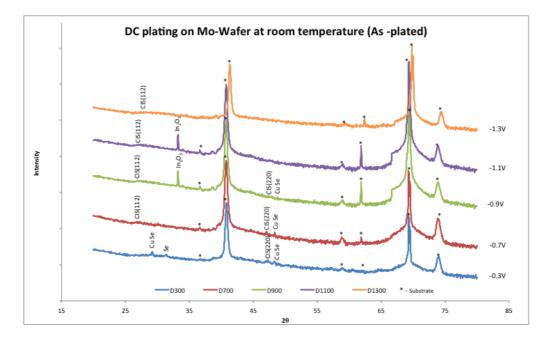

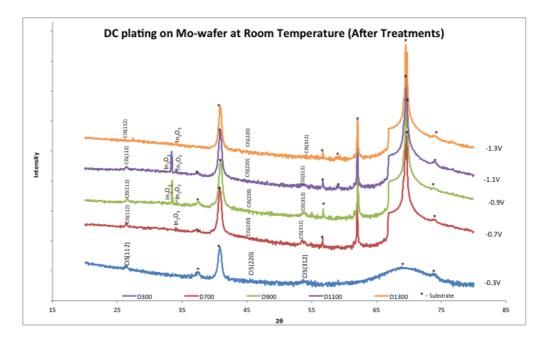

| 3.3.2   | MO-WAFER BY DC PLATING AT ROOM TEMPERATURE    | 70    |

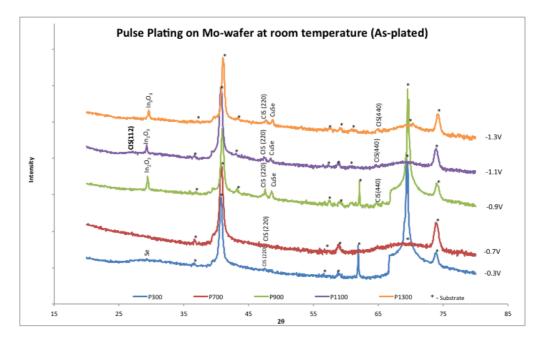

| 3.3.3   | MO-WAFER BY PULSE PLATING AT ROOM TEMPERATURE | 74    |

| 3.3.4   | MO-WAFER BY PULSE PLATING AT 40°C             | 77    |

| 3.4     | ELECTRICAL CONDUCTIVITY BY PHOTOELECTRO-CHE   | MICAL |

|         | (PEC)                                         | 80    |

| 84 | CULSION       | 4. CON |

|----|---------------|--------|

|    | FUTURE WORK . | 4.1    |

|    | ENCES         | REFER  |

#### **SUMMARY**

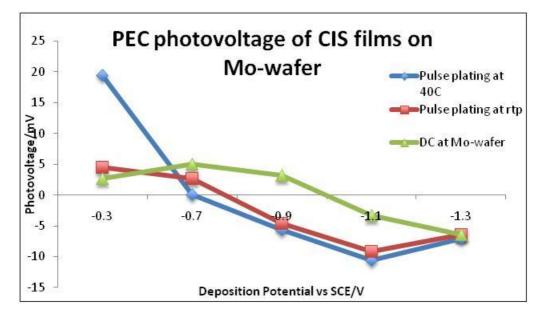

Copper indium diselenide polycrystalline films of p-, i- and n-type electrical conductivity were deposited on Molybdenum (metal strip and sputtered on Si-wafer) from a single bath using direct-current and pulse-plating deposition, at cathodic potential ranging -0.3V to -1.3V, with a thickness between 100-200nm. Electrochemical deposition mechanism results were correlated using Energy-Dispersive-X-ray Spectroscopy and X-Ray-Diffraction. Scanning-Electron-Microscopy was employed for surface morphology studies and Photoelectrochemical cell for p/i/n-type films conductivity. Photovoltage results indicate that p- and n-type CIS layers can be obtained by varying deposition potential under DC-plating at room temperature, pulse-plating at room temperature and 40°C on Mo-wafer. Generally, ptype can be obtained at relatively high potential of -0.3V and -0.7V, where n-type at more negative deposition potentials. To form a complete p-i-n junction from a single bath, pulse-plating at 40°C is recommended with negative plating limiting to pulse cycled from -0.3V (p-type) to -0.7V (intrinsic) and finally to -1.1V (n-type).

## **LIST OF TABLES**

| TABLE 1: SUMMARY OF EDX ELEMENTAL RESULTS ON THE CIS FILMS         |

|--------------------------------------------------------------------|

| DEPOSITED ON MO-STRIP AT ROOM TEMPERATURE BY DC PLATING 43         |

| TABLE 2: SUMMARY OF EDX ELEMENTAL RESULTS ON THE CIS FILMS         |

| DEPOSITED ON $MO$ WAFER AT ROOM TEMPERATURE BY $DC$ plating 43     |

| TABLE 3: SUMMARY OF EDX ELEMENTAL RESULTS ON THE CIS FILMS         |

| DEPOSITED ON MO WAFER AT ROOM TEMPERATURE WITH PULSE PLATING       |

| PLATING                                                            |

| TABLE 4: SUMMARY OF EDX ELEMENTAL RESULTS ON THE CIS FILMS         |

| DEPOSITED ON MO WAFER $40^{\circ}$ CWITH PULSE PLATING             |

| TABLE 5: CRYSTAL SIZE OF CIS ON MO-STRIP BEFORE AND AFTER          |

| ANNEALING AT 450°C, BASE ON CIS(211) PEAK WIDTHS68                 |

| TABLE 6: CALCULATED CRYSTALLITE SIZES FOR CIS DC PLATED ON MO-     |

| WAFER AT ROOM TEMPERATURE (AS PLATED)                              |

| TABLE 7: CRYSTALLITE SIZES OF CIS DC PLATED ON MO-WAFER BEFORE AND |

| AFTER POST TREATMENTS (ANNEALING + KCN ETCH) AT ROOM               |

| TEMPERATURE72                                                      |

| TABLE 8: TABULATION OF CRYSTAL SIZE OF CIS ON MO-WAFER (AS PLATED) |

| BEFORE AND AFTER TREATMENTS (ANNEALING + KCN ETCH) AT ROOM         |

| TEMPERATURE BY PULSE PLATING                                       |

| TABLE 9: TABULATION OF CRYSTAL SIZE OF CIS ON MO-WAFER (AS PLATED) |

| BY PULSE PLATING AT 40°C                                           |

| TABLE 10: TABULATION OF CRYSTAL SIZE OF CIS ON MO-WAFER BEFORE AND |

|--------------------------------------------------------------------|

| AFTER TREATMENTS (ANNEALING + KCN ETCH) BY PULSE PLATING AT        |

| 40°C                                                               |

| TABLE 11: PEC PHOTOVOLTAGE OF FILMS DEPOSITED ON MO-WAFER WITH       |

|----------------------------------------------------------------------|

| Pulse plating at room temperature, Pulse plating at $40^\circ C$ and |

| DC PLATING AT ROOM TEMPERATURE                                       |

## **LIST OF FIGURES**

| FIGURE 1: THE UNIT CELL OF CHALCOPYRITE LATTICE STRUCTURE          |

|--------------------------------------------------------------------|

| FIGURE 1. THE UNIT CELL OF CHALCOPYRITE LATTICE STRUCTURE          |

| FIGURE 2: TERNARY PHASE DIAGRAM OF CU-IN-SE SYSTEM. THIN FILM      |

| COMPOSITION NEAR PSEUDO-BINARY CU2SE-IN2SE3 TIE LINE 6             |

| FIGURE 3: PSEUDO-BINARY PHASE DIAGRAM OF CU-IN-SE SYSTEM           |

| FIGURE 4: SCHEMATIC ENERGY BAND DIAGRAM OF A PN-HETEROJUNCTION     |

| SOLAR CELL AT VARIOUS CONDITION                                    |

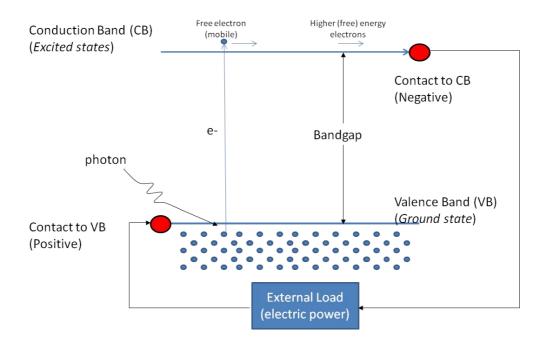

| FIGURE 5: SCHEMATIC OF SOLAR CELL WHERE ELECTRONS ARE PUMPED BY    |

| PHOTONS FROM THE VALENCE BAND (VB) TO CONDUCTION BAND              |

| (CB), AND EXTRACTED BY A CONTACT SELECTIVE TO THE                  |

| CONDUCTION BAND (AN N-DOPED SEMICONDUCTOR) AT A HIGHER             |

| (FREE) ENERGY AND DELIVERED TO AN EXTERNAL LOAD, AND               |

| RETURNED TO THE VALENCE BAND AT A LOWER (FREE) ENERGY BY           |

| A CONTACT SELECTIVE TO THE VALANCE BAND (A P-TYPE                  |

| SEMICONDUCTOR) 11                                                  |

| Figure 6: Energy band diagram of electrons and holes at $CB$ and   |

| VB RESPECTIVELY 13                                                 |

| FIGURE 7: ENERGY BAND DIAGRAM OF INTRINSIC, N-TYPE AND P-TYPE 15   |

| FIGURE 8: DEGENERATE N-TYPE(LEFT) AND P-TYPE(RIGHT) SEMICONDUCTOR. |

|                                                                    |

| FIGURE 9 : TEMPERATURE OF THE LIQUID IS ABOVE THE FREEZING         |

| TEMPERATURE, PROTUBERANCE ON THE SOLID-LIQUID INTERFACE            |

| WILL NOT GROW LEADING TO A MAINTENANCE OF A PLANAR                 |

| INTERFACE. LATENT HEAT IS REMOVED FROM THE INTERFACE               |

| THROUGH THE SOLID                                                  |

| FIGURE 10 : LIQUID IS UNDERCOOLED, A PROTUBERANCE ON THE SOLILD- |

|------------------------------------------------------------------|

| liquid interface can grow rapidly as a dendrite. Latent          |

| HEAT OF FUSION IS REMOVED BY RAISING THE TEMPERATURE OF          |

| THE LIQUID BACK TO THE FREEZING TEMPERATURE                      |

- FIGURE 11: MODEL SIMULATION OF ISOTROPIC, SINGLE-PHASE GRAIN GROWTH IN A POLYCRYSTALLINE MATERIAL. COLOR CORRESPONDS TO THE SITE INDICES. OVER TIME, AVERAGE GRAIN SIZE INCREASES AS LARGE GRAINS GROW AT THE EXPENSE OF

- FIGURE 12 : ILLUSTRATION OF FICK'S SECOND LAW ON THE DIFFUSION OF

FIGURE 14: VOLTAGE-TIME PROFILE OF PULSE DEPOSITION OF CIS THIN FILM.

$V_{c}$  ranging for -0.3V to -1.3V, whereas  $T_{R}$  = 2 second and

- FIGURE 15: N-TYPE SEMICONDUCTOR AND METAL (A) IN ISOLATION (B)

FIGURE 16: BAND PROFILES FOR THE P-TYPE SEMICONDUCTOR-METAL

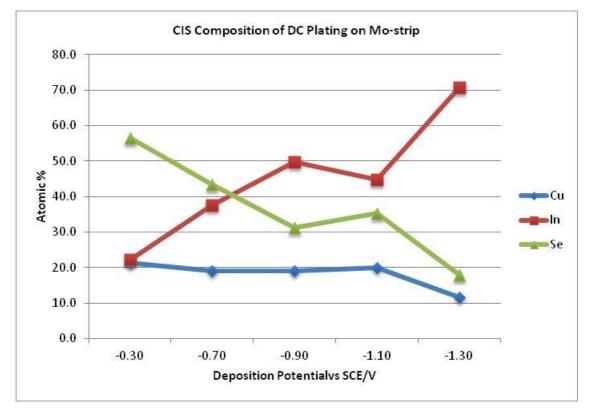

- FIGURE 17: COMPOSITION OF DC ELECTRODEPOSITION OF CIS THIN ON MO-STRIP AT ROOM TEMPERATURE AS A FUNCTION OF DEPOSITION

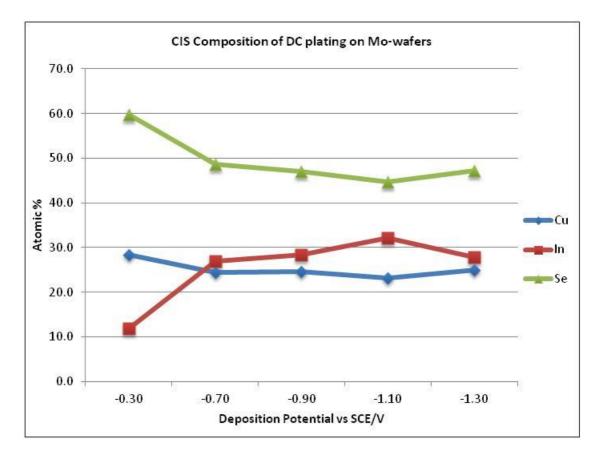

- FIGURE 18: COMPOSITION OF DC ELECTRODEPOSITION OF CIS THIN ON MO-WAFER AT ROOM TEMPERATURE AS A FUNCTION OF DEPOSITION

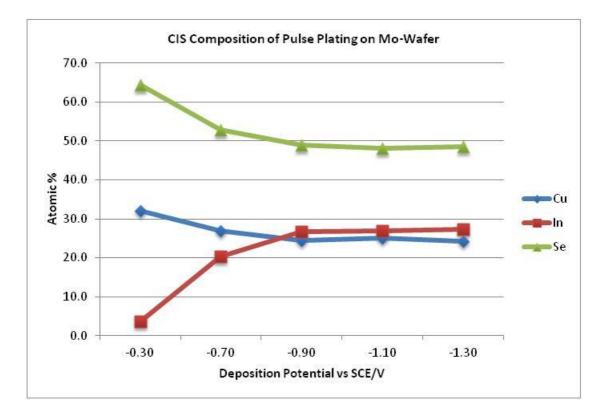

| FIGURE 19: COMPOSITION OF PULSE ELECTRODEPOSITION OF CIS THIN ON     |

|----------------------------------------------------------------------|

| MO-WAFER AT ROOM TEMPERATURE AS A FUNCTION OF                        |

| DEPOSITION POTENTIAL AS DETERMINED BY EDX                            |

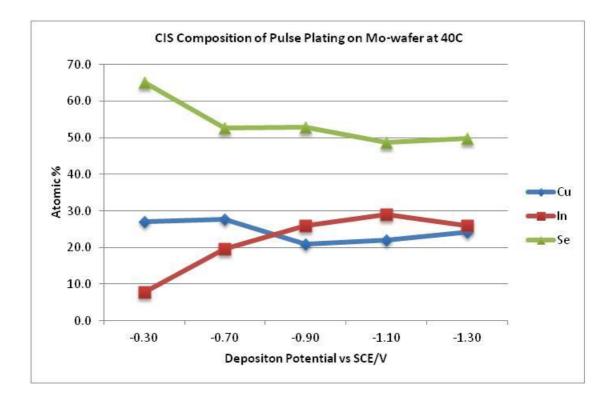

| FIGURE 20: COMPOSITION OF PULSE ELECTRODEPOSITION OF CIS THIN ON     |

| Mo-wafer at $40^{\circ}$ C as a function of deposition potential     |

| AS DETERMINED BY EDX 47                                              |

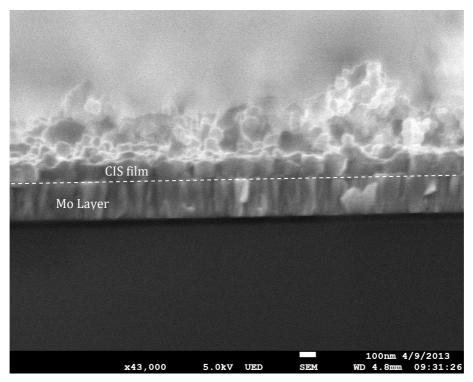

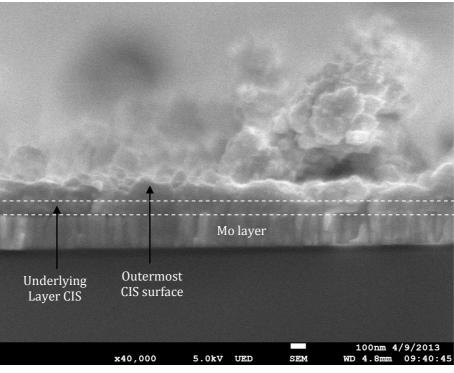

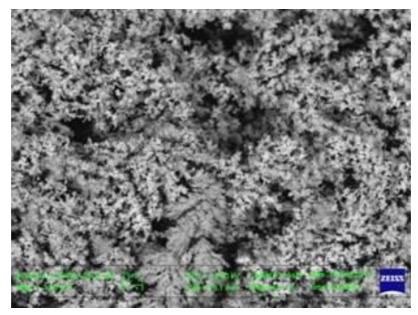

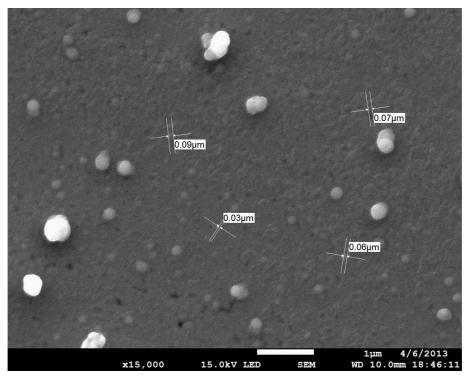

| FIGURE 21: MICROGRAPHS OF PULSE PLATING AT -0.9V AND DC PLATING AT   |

| -0.9V50                                                              |

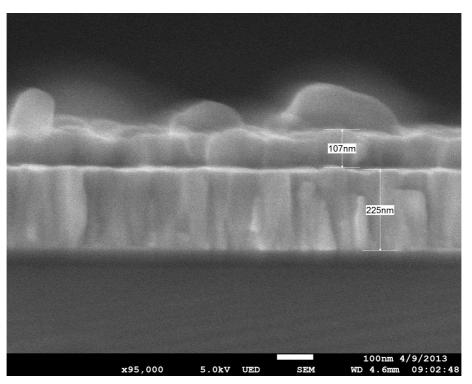

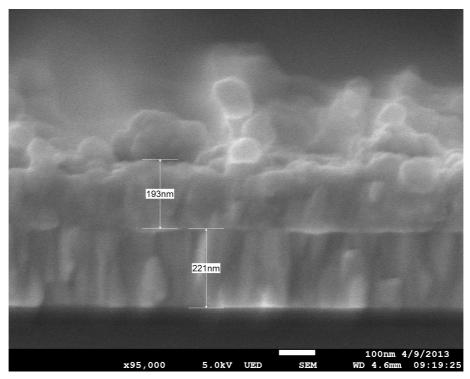

| FIGURE 22: MICROGRAPHS OF DC PLATING AND THICKNESS OF MO AND CIS     |

| FILMS                                                                |

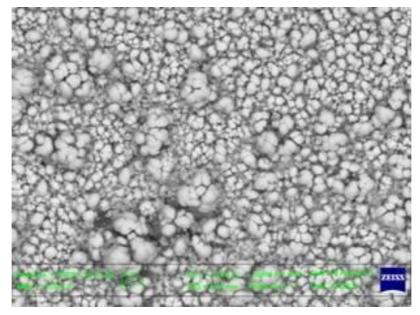

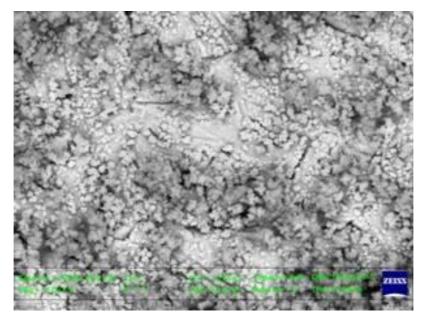

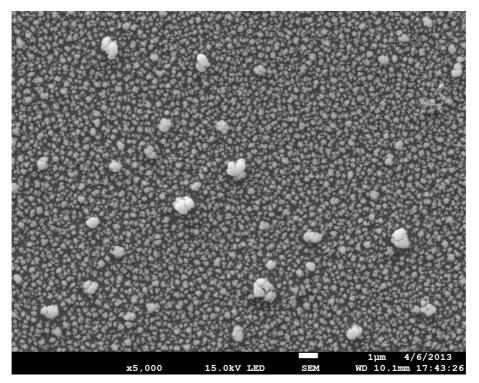

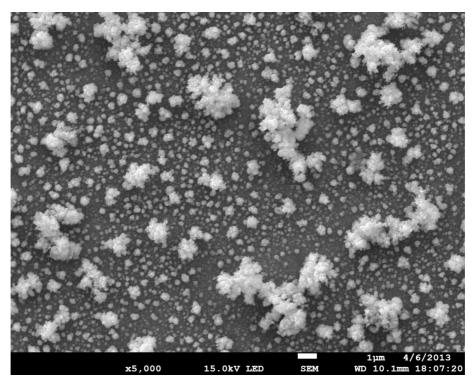

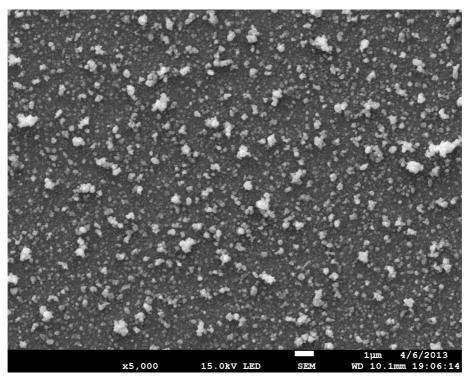

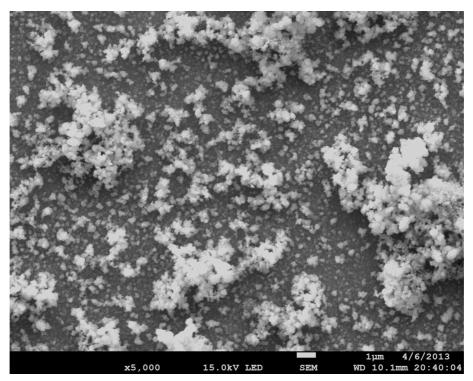

| FIGURE 23: DC PLATING ON MO WAFER AT ROOM TEMPERATURE                |

| MICROGRAPHS                                                          |

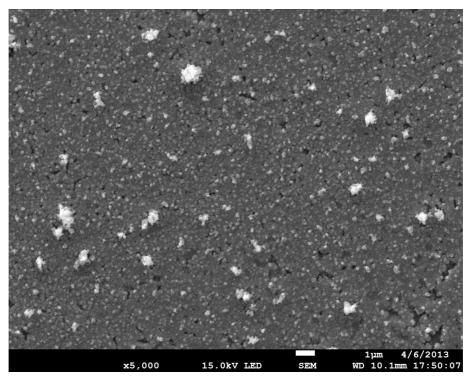

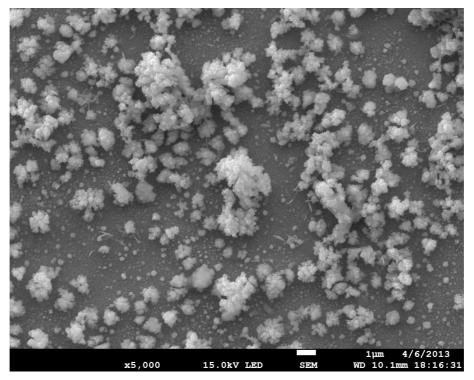

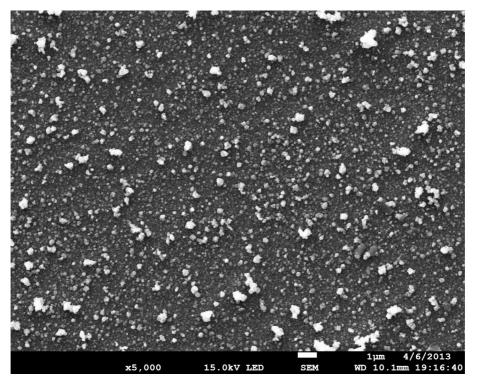

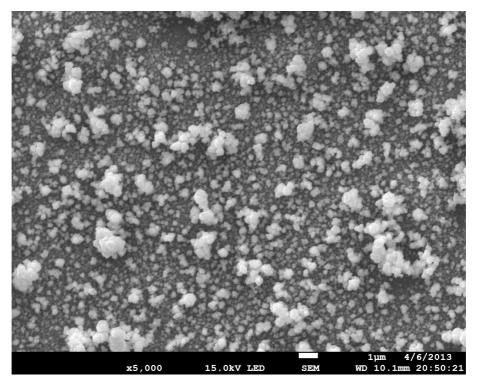

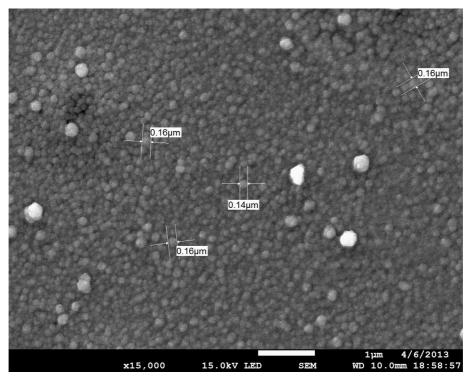

| FIGURE 24: DC PLATING ON MO WAFER AT ROOM TEMPERATURE                |

| MICROGRAPHS                                                          |

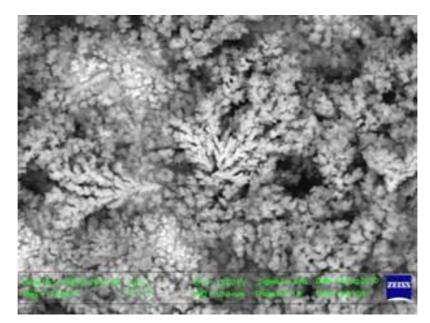

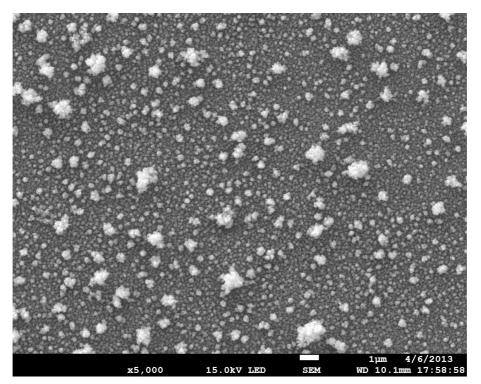

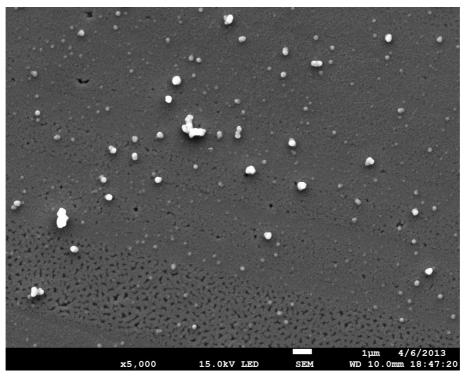

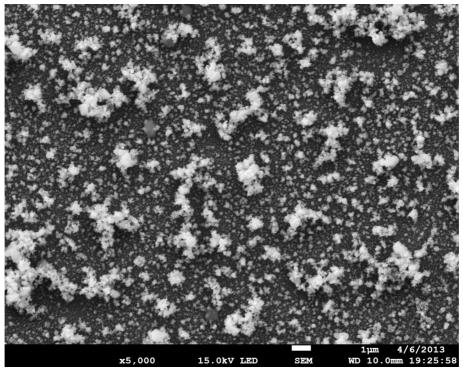

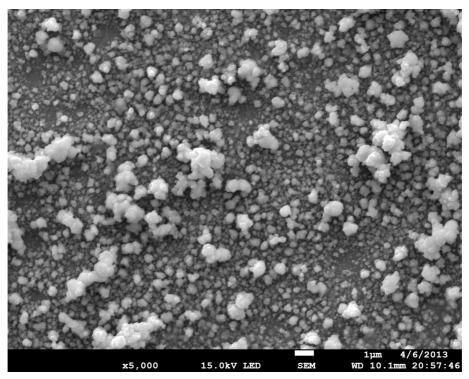

| FIGURE 25: PULSE PLATING ON MO-WAFER SUBSTRATE AT ROOM               |

| TEMPERATURE                                                          |

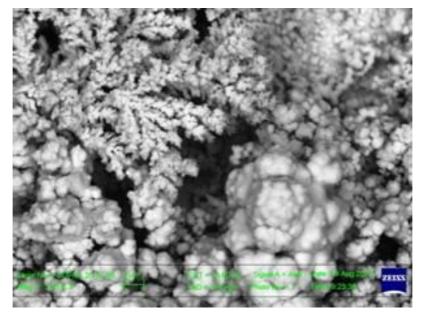

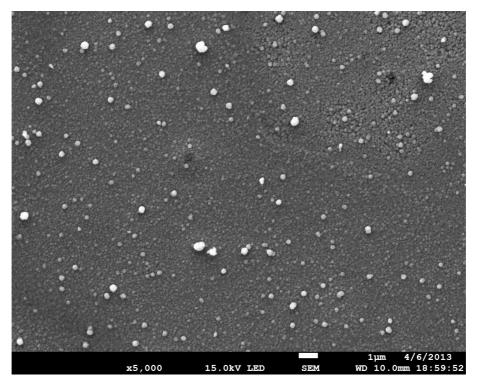

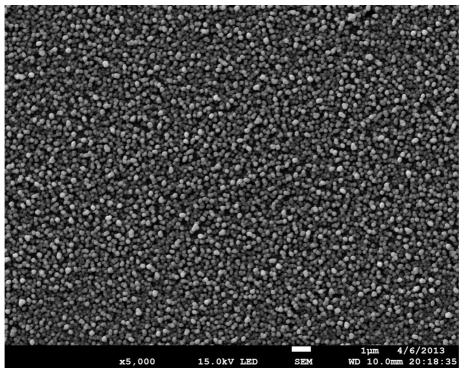

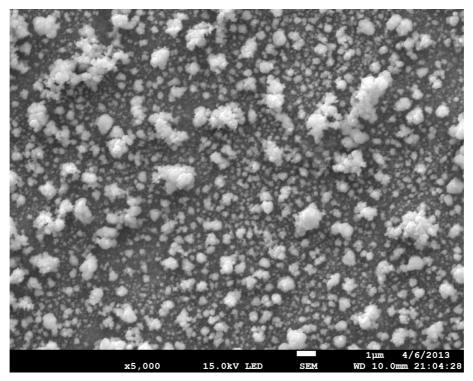

| FIGURE 26: PULSE PLATING ON MO-WAFER AT 40°C MICROGRAPHS 61          |

| FIGURE 27: PULSE PLATING SURFACE MORPHOLOGY AT ROOM TEMPERATURE      |

| AT -0.3V AND -0.7V AT HIGHER MAGNIFICATION                           |

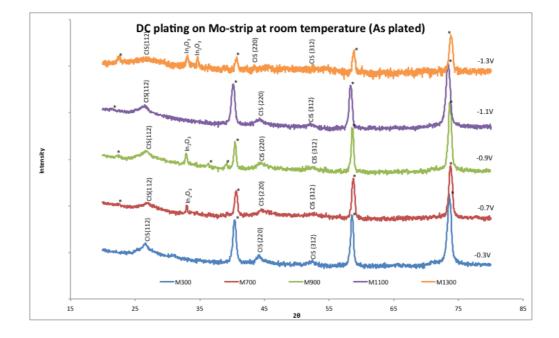

| FIGURE 28: XRD PLOT OF DC DEPOSITION OF CIS THIN FILM ON MO STRIP    |

| with potential at -0.3V, -0.7V, -0.9V, -1.1V and -1.3V               |

| PERFORMED AT ROOM TEMPERATURE                                        |

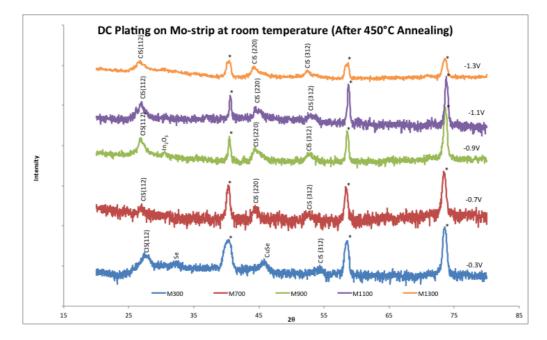

| FIGURE 29: XRD PLOT OF CIS THIN FILM ON MO STRIP AFTER ANNEALING AT  |

| $450^\circ C$ for 30min with potential at -0.3V, -0.7V, -0.9V, -1.1V |

| AND -1.3V PERFORMED AT ROOM TEMPERATURE                              |

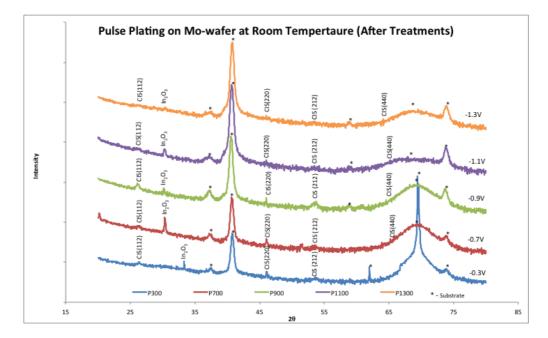

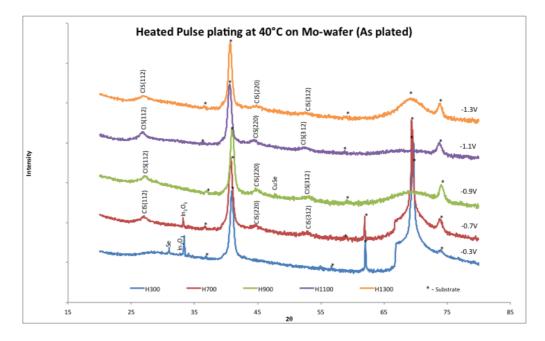

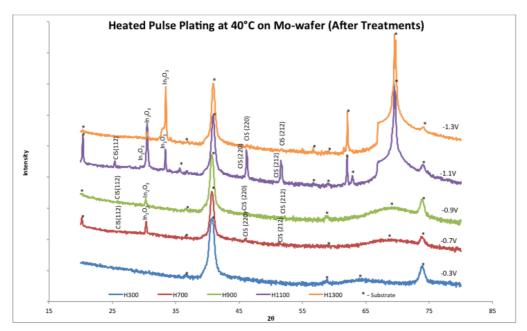

FIGURE 30: XRD PLOT OF CIS THIN FILM ON MO STRIP AFTER KCN ETCHING WITH POTENTIAL AT -0.3V, -0.7V, -0.9V, -1.1V AND -1.3V ..... 69 FIGURE 31: XRD PLOT OF DC DEPOSITION OF CIS THIN FILM ON MO WAFER WITH POTENTIAL AT -0.3V, -0.7V, -0.9V, -1.1V AND -1.3V AT FIGURE 32: XRD PLOT CIS THIN FILM AFTER POST TREATMENT ON MO WAFER WITH POTENTIAL AT -0.3V, -0.7V, -0.9V, -1.1V AND -1.3V FIGURE 33: XRD OF (AS PLATED) CIS THIN FILM DEPOSITED BY PULSE PLATING ON MO WAFER WITH POTENTIAL AT -0.3V, -0.7V, -0.9V, -FIGURE 34: XRD PLOT OF AFTER POST TREATMENT CIS THIN FILM DEPOSITED BY PULSE PLATING ON MO WAFER WITH POTENTIAL AT -0.3V, -0.7V, -0.9V, -1.1V AND -1.3V AT ROOM TEMPERATURE. FIGURE 35: XRD PLOT OF (AS PLATED) CIS THIN FILM DEPOSITED BY PULSE PLATING ON MO WAFER WITH POTENTIAL AT -0.3V, -0.7V, -0.9V, -FIGURE 36: XRD PLOT OF AFTER POST TREATMENT CIS THIN FILM DEPOSITED BY PULSE PLATING ON MO WAFER WITH POTENTIAL AT -0.3V, -0.7V, -0.9V, -1.1V AND -1.3V AT HEATED BATH AT 40°C. FIGURE 37: PEC PHOTOVOLTAGE ACROSS DC PLATING AT ROOM TEMPERATURE, PULSE PLATING AT ROOM TEMPERATURE AND

| Pulse plating at $40^{\circ}C$ on Mo-wafer, ranging from -C | ).3V |

|-------------------------------------------------------------|------|

| то -1.3 V.                                                  | 81   |

#### **1. INTRODUCTION**

Present global energy production is largely accomplished by burning of fossil fuels, which inevitably relates inherent issues associated with the limited resources as well as environmental problems. Solar energy from photovoltaic has received increasing favor as an alternative source for future electricity by converting direct sunlight to electricity.

However, the costs of producing photovoltaics (cost per watt) are higher than the conventional methods. As a result, it may not be the preferred choice between the two. Nevertheless, cost effectiveness can be lowered through improving efficiency or reducing production cost.

Copper Indium Diselenide (CIS) is one of the fastest developing materials for thin-film photovoltaic solar cells due to its excellent optical and photovoltaic properties through direct energy band gap and high absorption coefficient. Having the advantage of direct bandgap of  $\approx$  1.05eV by [8], Copper Indium Diselenide is consider a high absorption coefficient materials as well as having large minority carrier diffusion length, thus forming a suitable film for photovoltaic applications. Contreras *et al* [9] have achieved a high conversion efficiency of almost 19% with these materials.

CIS films can be prepared by gaseous and liquid phases, such as physical vapour deposition, sputtering, molecular beam epitaxy, metalorganic chemical vapour deposition etc. Electrodeposition has its advantage for mass production in terms of large surface area and high volume productions. It is more economical since the steps are simple [6] and does not required sophisticated high vacuum machines and stringent environments it also uses relative lower temperature than other processes. Generally, electrodeposition of CuInSe films can be simplified in the following written reaction:

$$Cu(II) + 2Se(IV) + In(III) + 13e^{-} \rightarrow CuInSe_{2}$$

Inevitably, the film would contain binary phases in addition to the chalcopyrite CIS phases [18] in acidic medium, namely  $Cu_xSe$  and  $In_2Se_3$ . The reactions can be summarized as follows:

- I.  $xCu(II) + Se(IV) + (2x+4)e^- \rightarrow Cu_xSe$

- II.  $3Se(-II) + 2In(III) \rightarrow In_2Se_3$

- III.  $Cu_2Se + In_2Se_3 \rightarrow CuInSe_2$

Where x is the ratio of fluxes at the electrode surface of Cu(II) ions and Se(IV) ions, which were proportional to the concentration of the ions in the electrolyte assuming reaction is limited by diffusion.

Formation of Copper Selenide  $Cu_2Se$  and Indium Selenide  $In_2Se_3$  occurs first before the formation of CIS growth. Deposition of  $Cu_2Se$  occurs initially which depends on the diffusion coefficient of the Se(IV) and Cu(II). With sufficient In(III) in the solution, Selenium deposited can further reduced to Se(-II) while reacting with In(III) producing  $In_2Se_3$ , which were controlled by the deposition potential [15].

Further findings were made by Chassing E. et al (2008) [5] on the electrodeposition mechanism on a rotating disc electrode. At deposition potentials between -0.3V to -0.4V,  $Cu_3Se_2$  were produced according to the following reactions:

$$3Cu(II) + 2 H_2SeO_3 + 8H^+ + 14e^- \rightarrow Cu_3Se_2 + 6H_2O$$

As deposition potential decrease further,  $Cu_3Se_2$  will be reduced to CuSe, and dissolution of Se(IV) would reduced to Se and deposit on CuSe, as follows:

$$Cu_3Se_2 + H_2SeO_3 + 4H^+ + 4e^- \rightarrow 3CuSe + 3H_2O$$

$$H_2SeO_3 + 4H^+ + 4e^- \rightarrow Se + H_2O$$

As the deposition potentials decreases to around -0.6V, Indium will be incorporated into the deposit. However, it was suggested that an amorphous passive layer would be form with stoichiometry close to CuSe<sub>2</sub>, that acts like a blocking absorbate, suspected to be In-Se compound. This layer has low conductivity easily absorbed onto the surface. After the formation In-Se compound, CuInSe<sub>2</sub> will be formed according to the general reaction as stated above:

In addition to the formation of CuinSe<sub>2</sub>, Se was also produced together with CuSe binary phase concurrently. As the deposition potential further reduced, the "passivation" effect would be lifted off as the deposition current were limited by diffusion of Se(IV) and Cu(II) ions. In another words, composition is mainly governed by the ratio of the Cu and Se in solution and the kinetics of indium reaction.

Moreover, Chaure *et al* [8] have extensively studied the growing both  $p^+$  and  $n^+$  layers by electrodeposition, which is useful for forming good ohmic contacts to both p-, and n- type CIS layers. The conductivity type of the deposited layers was obtained in terms of structural and electrical properties through PEC measurements, verified with XRD and XRF. Furthermore, by varying the deposition potential, it is possible to deposit p-, i- and n-type materials directly from a single

deposition bath. The electrical parameters could be manipulated to control the film's properties, structure and composition.

Studies have been made in growth of copper indium diselenide compound by electrodeposition on Mo-coated glass (FTO), Roussel *et al* indicates that the growth of CuSe phase on the initial nucleation before corporation of Indium can proceed, moreover, the publication shown that In/Cu ratio relations increase with deposition time [18].

In addition, Phok *et al* [15] had successfully grown CuInSe<sub>2</sub> nanowires on porous alumina templates by pulse plating, which gave a CuInSe<sub>2</sub> composition close to stoichiometry. The purpose of this thesis is to further study the electrodeposition processes for the preparation of thin film CuInSe<sub>2</sub> on Mo substrates, produced by Mo sputtered on wafer and directly Mo metal strip, to obtain p-, i- and n-type conductivity from a single chemical bath by both direct current and pulse plating profile.

# 1.1 THIN FILMS SOLAR CELLS – COPPER INDIUM DISELENIDE

History of CuInSe<sub>2</sub> solar cells works were initiated at Bell laboratories in the early 1970s [22] where they grew a wide selection of these materials and characterized their structural, electronic and optical properties. However, optimized efficiency is only 12% back then. CuInSe<sub>2</sub> was considered promising for solar cell because of it favorable electronic and optical properties, including direct bandgap with absorption coefficient and inherent p-type conductivity which will be further discussed in the following section.

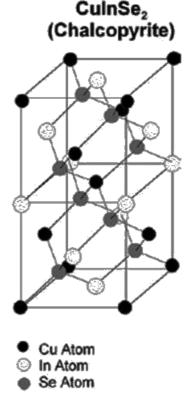

CulnSe<sub>2</sub> have chalcopyrite lattice structure, is a diamond-like structure, similar to sphalerite structure, with an order substitute of Group I (Cu) and Group III (In) elements on the Group II (Zn) sites of sphalerite. The diagram below shows a tetragonal unit cell of chalcopyrite lattice structure.

Figure 1: the unit cell of chalcopyrite lattice structure

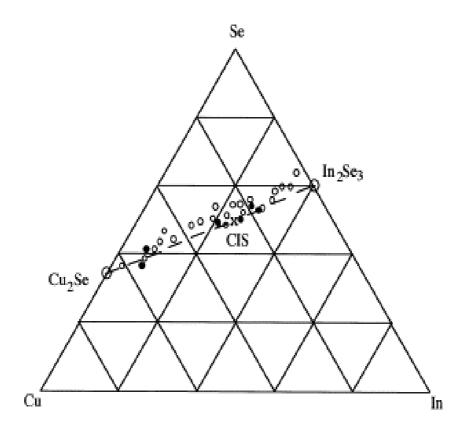

The deviation from c/a = 2 is called the tetragonal distortion and stem from different strengths of the Cu-Se and the In-Se bonds. Possible phases in Cu-In-Se system are indicated in the ternary diagram below:

Figure 2: Ternary phase diagram of Cu-In-Se system. Thin film composition near pseudo-binary Cu2Se-In2Se3 tie line

Chalcopyrite CuInSe is located in this line. A detailed Cu<sub>2</sub>Se-In<sub>2</sub>Se<sub>3</sub> tieline near CuInSe<sub>2</sub>is described by the pseudo-binary phase diagram reproduced in the figure below:

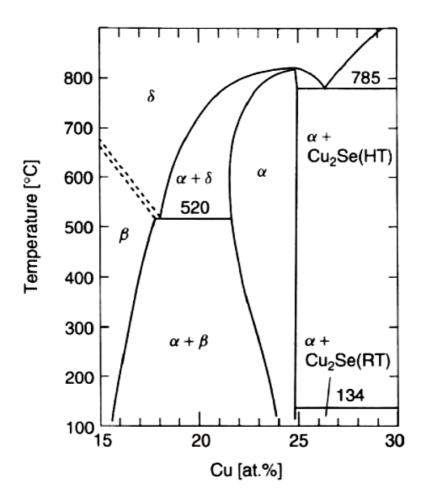

Figure 3: Pseudo-binary phase diagram of Cu-In-Se system

The chalcopyrite CuInSe<sub>2</sub> phase is denote as  $\alpha$ ,  $\delta$  is a high temperature phase with sphalerite, and  $\beta$  is an ordered defect compounds (ODC) known to have chalcopyrite structure with structurally ordered insertion of intrinsic defects. At lower temperature, single phase field for CuInSe<sub>2</sub> is relative narrow and does not contain the composition of 25% Cu. However at higher temperature around 500°C, thin films are typically grown, and phase field widen towards the In-rich side. Typically average composition of device-quality film has 22-24% Cu, which falls within a single phase region at growth temperature.

Generally most of the solar cells are made of mono or polycrystalline silicon. However, silicon is not an ideal absorber material for solar cells due to the presence of indirect band gap which does not absorb light as efficient as those with direct band gaps. In order to achieve sufficient light absorption, very thick and high quality silicon is used in solar cells and to allow for minority carrier lifetimes and diffusion length long enough such that recombination of the photo-generated charge carriers is minimized, to contribute to the photocurrent. Kasap [12] mentioned that Si-based solar cell efficiencies ranges from 18% for polycrystalline, up to 24% in high efficiency single crystal devices that have special structures to absorb as much photons as possible, known as homojunctions. The best Si-homojunction solar cell efficiencies are about 24% for single crystal passivated emitter rear locally diffused cells.

Nevertheless, due to the limitations of crystalline silicon, other absorber materials have been studied extensively, such as semiconductor with direct band gap with high absorption coefficients were studied for thin film application in solar cells.

Several advantages of thin film solar cells is preferred over crystalline silicon, in consideration of the follow, namely; usage of less material typically few micrometers, therefore impurities and crystalline imperfections can be greatly reduced relative a crystalline silicon. Secondly, there are a wide variety of processes to obtain thin films on inexpensive substrates (e.g. glass) as well as flexible substrate (e.g. flexible pcb), Lastly, composition of the thin film can be easily manipulate by processes.

Low cost thin film solar cell materials are usually CdTe (cadmium telluride), amorphous hydrogenated Silicon (a Si:H) and CuInSe<sub>2</sub> (Copper Indium Diselenide) and its alloy either Ga and/or S. Amorphous silicon has higher absorption coefficient and closer bandgap of 1.5eV from the ideal, than that of polycrystalline silicon. However, the major disadvantage of amorphous silicon made solar cell is the light-induced degradation leading to a drop of conversion efficiency from the initial value, knowning as "*Staebler-Wronski effect*".

This results from defects (such as dangling bonds) created by illumination that acts as recombination centers, causing stabilization efficiencies of amorphous silicon solar cell to be as low as 13% as mentioned by Kermell [13].

Unlike amorphous silicon, polycrystalline compound semiconductor materials such as CdTe (cadmium telluride) and CuInSe<sub>2</sub> (Copper Indium diselenide) and its alloy either Ga and/or S, do not face light-induced degradation. In addition, CuInSe<sub>2</sub>-based solar cell shown improvement after illumination under normal operating conditions. Besides, polycrystalline compound semiconductors have high absorption coefficient due the direct bandgaps.

In this thesis studies, CuInSe<sub>2</sub> were chosen as the absorber material for studies. Although the bandgap is 1.04eV, the feasibility of vary the bandgap by altering the material composition with alloy such as Ga or S, may achieve high bandgap of 1.5eV of CuGaS<sub>2</sub>. Studies shown that by altering the composition, CuInSe<sub>2</sub> can either be p-type or n-type, Kermell [14].

#### **1.2 PHOTOVOLTAIC DEVICES**

As solar cells, or photovoltaic devices, convert energy from the sunlight into electricity. Power generation part of a solid-state solar cells consist of a semiconductor that forms a rectifying junction either with another semiconductor or with another metal, producing an pn-diode or Schottky diode. However, there are some junctions such as semiconductors-insulators-semiconductors or a metal-insulatorsemiconductors junction were form by a thin film placed in between two semiconductors or a semiconductor and a metal. A pn-junction are therefore classified into homojunction and heterojunction according to whether the semiconductor materials on one side of the junction is the same as or different from that on the other side. Thin film solar cells are typically pn- or pin-diodes.

When the junction is illuminated with applied/external source, the semiconductor material absorbs the incoming photons when the energy (hv) is higher than that of the band gap of the semiconductor, forming an electron-hole pairs. These photogenerated electron hole pairs are separated by the internal electric field of the junction, whereby the electrons drifts to one side remaining the holes at the other side.

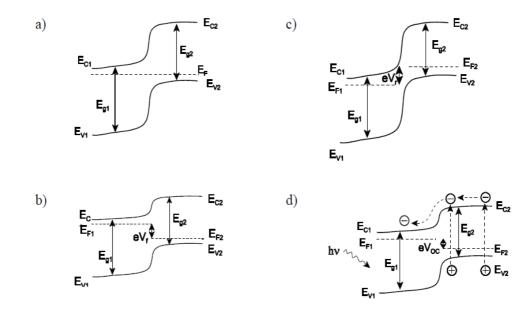

Figure 4: Schematic energy band diagram of a pn-heterojunction solar cell at various condition

The figure above illustrates a schematic energy band diagram of a pnheterojunction solar cell (a) thermal equilibrium without any illumination, (b) under forward bias, (c) under reverse bias influences, (d) when illuminated open circuit conditions.

#### **1.3 DOPING AND DEGENERACRY OF SEMICONDUCTOR**

As mentioned in previous section, being a semiconductor materials, solar cells have weakly bonded electrons occupying a band of energy

called the valence band. In a nutshell, when the energy exceed a certain threshold of the material known, as the bandgap energy, is applied to a valence electron, the bonds are broken and the electron is "free" to move around in a new energy band called the conduction band where it can "conduct" electricity through the material. Therefore these free electrons in the conduction band are separated from the valence band by the bandgap, measured in electron volt (eV). This energy needed to free an electron can be supplied by photons.

Figure 5: Schematic of solar cell where electrons are pumped by photons from the valence band (VB) to conduction band (CB), and extracted by a contact selective to the conduction band (an n-doped semiconductor) at a higher (free) energy and delivered to an external load, and returned to the valence band at a lower (free) energy by a contact selective to the valance band (a p-type semiconductor).

When a solar cell is exposed to external illumination or an applied field of sufficient energy, the incident solar photon is absorbed by the atoms, breaking the bonds of the valence electrons and pumping them up to higher energy in the conduction band (CB). Excitation of an electron form the valence band (VB) requires a minimum energy of a bandgap of the semiconductor, denotes as the E<sub>g</sub>, to the CB. Correspondently, a "hole" is create at the VB. An electron-hole pair is thus created.

At the conduction band, selective contact collects conduction band electrons and drives these freed electrons to an external circuit. The electron loses energy by doing work in the external circuit. They are then restored to the solar cell by returning the loop via a second selective contact, which they return to the valence band with the same energy they had initially started with. The potential at which the electrons are delivered to the external load is less than the threshold energy that excited the electrons i.e. the bandgap (refer to Figure 5).

Sunlight has a spectrum of photons distributed over a range of energy. Photons with energy greater than the bandgap energy can excite electrons from VB to CB and to external load for power generation.

The following section will give a brief introduction on the conductivity of semiconductors as well degeneracy which is similar to the case of solar cell.

The general equation for the conductivity of a semiconductor depends on electron concentration (n) and hole concentration (p), and it can be expressed in the following equation [12]:

$$\sigma = en\mu_e + ep\mu_h$$

Where n and p are electron and hold concentration in CB and VB respectively.

The density of state, denotes as  $g_{cb}(E)$ , in the CB is the number of states per unit energy per unit volume. The probability of finding an electron in a state with energy E is given by the Fermi-Dirac function f(E).

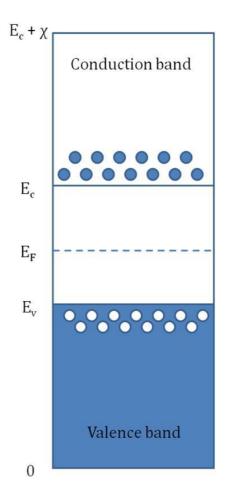

Figure 6: Energy band diagram of electrons and holes at CB and VB respectively.

Therefore, electron concentration in the CB can be expressed in the following equation;

$$n_E dE = g_{cb}(E) f(E) dE$$

$$n = \int_{E_c}^{E_c + \chi} g_{cb}(E) f(E) dE$$

Where  $g_{cb}(E) f(E) dE$  is the actual number if electrons per unit energy per unit volume  $n_E(E)$  in the CB.

Moreover, replacing the Fermi-Dirac statistic by Boltzmann statistic, and assuming the number of electrons in the CB is less than number of states in the band. In addition, considering a three dimensional PE well, the electron concentration leads to

$$n = N_c \exp\left[-\frac{\left(E_c - E_f\right)}{kT}\right]$$

Where kT is the product of the Boltzmann constant, k, and the temperature, T.  $N_c$  is the effective density state at CB edge.

Hence the hole concentration can also be expressed as follows:

$$p = N_v \exp\left[-\frac{\left(E_f - E_v\right)}{kT}\right]$$

Where  $N_{\nu}$  is the effective density of states at VB edge.

Taking the product of both the electron and hole concentration above,

$$np = N_c N_v \exp\left(-\frac{E_g}{kT}\right)$$

Where  $E_g = E_c - E_v$ .

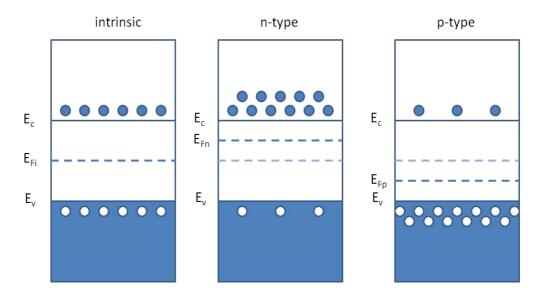

An intrinsic semiconductor is a pure semiconductor crystal (i.e. no impurities in the crystal) in which the electron and hole concentration are equal. When an electron and hole meets in the crystal, the electrons falls in energy and occupies the empty electronic states that the hole represents, this process is known as "recombine". Recombination of an electron and hole results in their annihilation.

Being an intrinsic semiconductor, n = p, and the intrinsic concentration (denote as  $n_i$ ) is therefore expressed as the following:

$$np = n_i^2 = N_c N_v \exp\left(-\frac{E_g}{kT}\right)$$

The condition  $np = n_i^2$  (also known as the *mass action law*) suggest that electron concentration can be increase in the CB over the intrinsic values, such as addition of impurities into the semiconductor crystal that donates electrons in the CB. This results in a n-type semiconductor where n > p. Similarly, it is feasible to add impurities to remove electrons in the VB such that it yields an p-type semiconductors.

The general band diagrams with the respective Fermi level for intrinsic, n-type and p-type semiconductor are illustrated below:

Figure 7: Energy band diagram of intrinsic, n-type and p-type.

Introducing small amount of impurities to an pure semiconductor (e.g. Si) crystal to obtain an semiconductor whereby the concentration of the carriers of one polarity is in excess of the other type as mention above. This type of semiconductor is known as extrinsic semiconductor. The process of introducing impurities is referred as doping. However, in the case of the CIS thin film, doping is not introduced from pure crystal, but the variation of elements within the composition by simultaneous

electrodeposition in a single bath, causes this phenomenon to occur of having different conductivity when varying composition.

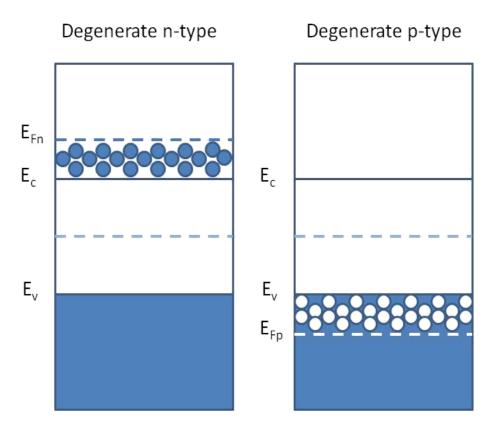

From the above electron concentration in CB expression  $n = N_c \exp\left[-\frac{(E_c - E_f)}{kT}\right]$  is base on replacing FermiDirac statistic with Boltzmann statistic, is valid when  $E_c$  is several kT above  $E_f$ . However, Kasap [22] highlighted that Pauli exclusion principle can be neglected and the electron statistic can be describe by Boltzmann statistic, where the n is only valid when  $n \ll N_c$ . Such semiconductor for which  $n \ll N_c$  and  $p \ll N_v$  are refer as nondegenerated semiconductor.

Nevertheless, for semiconductors where Pauli Exclusion Principle becomes significant in the electron statistic and Fermi-Dirac statistic is use. The *n* in  $n = N_c \exp \left[-\frac{(E_c - E_f)}{kT}\right]$  is not valid in such a case. Such semiconductors will have  $n > N_c$  or  $p > N_v$  are refer as degenerated semiconductors. These semiconductors exhibit properties towards metal-like than semiconductor-like. Usually this type of semiconductors occurs at high doping levels which were not the case in CIS thin film. However, for explanatory purpose, a highly doped case is used. For instance, the donor concentration in an n-type semiconductor is increase at sufficiently high doping level, the donor atoms become so close to each other such that the orbital overlaps to form an narrow energy band that overlaps and becomes part of the CB in the n-type semiconductor. Thus the  $E_c$  is shifted down and the  $E_g$  become narrower. The valence electrons from the donors fill the band from  $E_c$ . In such situation is similar to valence electrons filling overlapping energy band in a metal.

In a degenerate n-type semiconductor, the Fermi-level conductor is within the CB or above  $E_c$  similar to  $E_f$  is within the band of a metal. The majority of the states between  $E_c$  and  $E_f$  are fill with electrons. This can be illustrated as following:

Figure 8: Degenerate n-type(left) and p-type(right) semiconductor.

In case of a p-type degenerate semiconductor, the Fermi level lies in the VB below  $E_v$ . In such case of the degeneracy of semiconductor, the mass action law  $np = n_i^2$  can no longer be valid.

#### 1.4 ELECTRODEPOSTION OF CulnSe<sub>2</sub>

There are many methods to obtain thin film of CuInSe<sub>2</sub> solar cells. The type of processes use has direct impact on the properties of the thin films. For large scales manufacturing, cost of production may also have an direct impact on which process to chose from. Nevertheless, the underlying objective is to obtain a high efficiency solar cell.

One of the ways to obtain thin film of CuInSe<sub>2</sub> solar cells is by sequential processes either by co-evaporation from elemental sources or reactive annealing of precursor films under Se-rich environment. The annealing operation temperature typically above 400°C, which

enhanced the formation of MoSe<sub>2</sub> interlayers, but the resultant of high temperature may compensate for the loss of Se. Hence, annealing under Se-rich environment is preferred.

Co-evaporation from elemental sources is likely to yield high efficiency solar cell, and it consist of three stages [13, 22]. This process is commonly use in the market these days for preparation of CIGS film, instead of CIS films. However, this method is does yield high quality CIS or CIGS film in terms of orientation, it is usually applicable to small surface area, which is not feasible for mass production. This may due to the fact that co-evaporation requires very stringent process control to obtain the required composition, texture and electrical properties which is very difficult to achieve for large surface area.

Other methods of sequential processes may also involved process such as chemical vapor deposition, close-spaced vapor transport evaporation of compound sources, spray pyrolysis etc.

Beside the sequential process, electrodeposition involved one-step deposition of CIS-film. This usually involves liquid phase thin film deposition method base electrochemical reactions done by an external applied power. The setup is usually a three-electrode setup which will be introduced in the following section. One of the electrodes is used as a working electrode (cathode) on which the film will be deposited and grown, while the other one function as the counter electrode. The third electrode will be the reference electrode with reference to which the chemical potential of the working electrode is measured. Deposition is carried out at a constant potential (potentiostatically) or at constant current (galvanostatically) but the voltage and/or waveform or pulse can be use.

To achieve a desired film deposition, simultaneous reduction of all the constituent ions in suitable proportions occurring in this one step electrodeposition at the same potential is vital. This can be done by balancing the diffusion flux of the constituents ions to the cathode, or it can be done by employing the induced co-deposition mechanism. However, this method does not favor large surface area because the flux balance approach is that the concentration and potential ranges for the formation of stoichiometric product are relatively narrow, therefore variation in concentration and potential may results in large changes in film deposition.

The other way of achieving a desirable film deposition, is by inducing co-deposition mechanism. Film composition achieved by co-deposition mainly controlled by thermodynamics. This type of deposition were widely used in CdTe base solar cell and other binary compound semiconductors, which is much less sensitive to the unavoidable variation in the electrolyte composition than processes relying on balancing diffusion fluxes. Moreover, the drop of potential is minimal across large substrate.

Deposition of CIS based thin films were prepared base on flux approach until recent years where induced co-deposition approach has been utilized. Studies of under potential assimilation of indium (In) into films have been observed. This is due to the fact that in one step electrodeposition of CIS is usually performed from solutions where Cu and Se precursor concentrations are of the same order of magnitude, and In is in excess. As such, film stoichiometry is determined by deposition potential and ratio of diffusion fluxes of Se and Cu to the substrate surface.

Flux balance approach is preferred because one the major attributes comes from the formation of Copper-Selenide (Cu-Se) which does not follows the induced co-deposition mechanism. This is so firstly, reduction of Se<sup>4+</sup> to Se requires large overpotential or actual reduction potential is more negative than the standard reduction potential, and is dependent on the electrode surface. Secondly, the standard reduction potential of Cu<sup>+</sup> to Cu<sup>2+</sup> are close to the observed reduction potential of

Se<sup>4+</sup> and depending on the required Se overpotential, can be either more positive or more negative than that of Se<sup>4+</sup> ions. As such, independent co-deposition is observed instead of induced co-deposition in the Cu-Se system [14]. In addition, complication may arise from passivation nature of Se deposited at room temperature.

Solutions of the electrodeposition are usually made up from aqueous acidic solution containing Cu ions and In ions in either sulphate or chloride as. Aqueous selenium acid provides Se precursor, sometimes can be obtained from SeO<sub>2</sub> dissolved in slightly acidic solution. Nevertheless, in this thesis purpose, aqueous hydrochloride acid was added to reduce the pH of the solution to facilitate the reduction of  $HSeO_3^-$  in acidic environment. In such case, chloride base compound (i.e. indium chloride and Copper chloride) is use to reduce the present of sulphate ions in the makeup solution. In addition, potassium chloride is use as a supporting electrolyte.

Pioneering in CIS deposition were done by Bhattachrya [2], where global simplified electrodeposition reaction were determined as follows:

$$Cu(II) + 2Se(IV) + In(III) + 13e^{-} \rightarrow CuInSe_2$$

Roussel [18] had investigate the first stage of CIS deposition from acidic solutions on molybdenum (Mo) glass plates and determined that Mo is the best candidate thus far to be tested on back contact in CIS devices. In his investigation, a quasi-instantaneous three dimensional nucleation occurs. First nucleation was made up of Cu-Se phase without indium. Co-deposition of indium then started when Se/Cu ratio reaches close to 1, which confirms what Cu-Se phase is a prerequisite for indium corporation. The growth begins with very high copper content. The first nuclei are probably copper nanometric nuclei from the reduction of cupric species as follows:

$$Cu^{2+} + 2e^{-} \rightarrow Cu$$

- (1)

The first copper rich phase allows the incorporation of Se. Although the redox potential of the  $Se(IV)/Se^0$  couple is higher than the redox potential of  $Cu(II)/Cu^0$ , the Se(IV) species do not reduce separately on the bare Mo substrate. With the interaction with Cu, the incorporation reaction occurs as follows forming a binary Cu-Se phase.

$$Se(IV) + 2Cu^{0} + 4e^{-} \rightarrow Cu_2Se \qquad \qquad -(2)$$

The formation of  $Cu_2Se$  shows that Cu is monovolent and at low deposition period, Se is essentially as Se(-II). As the deposition time increases, Se/Cu ratio increases and formation of the Cu-Se phase with x increasing deposition time, can be described as follows:

$$Cu(II) + (1+x)Se(IV) + (6+4x)e^{-} → CuSe_{(1+x)}$$

(3)

For short deposition time, the Se/Cu is smaller than 2 indicates that the incorporation of Se is controlled by kinetic constrains rather than by diffusion.

Nevertheless,  $CuSe_{(1+x)}$  phase may coexist with  $Cu_2Se$  and small trace of  $Se^0$ .With increasing deposition time, more oxidized form of selenium Se(-II) were formed. When x increases, Se/Cu ratio becomes greater than 1, incorporation of Indium may occur according to the following reaction:

$$CuSe_{(1+x)} + x ln(III) + 3x e^{-} \rightarrow Culn_xSe_{(1+x)}$$

This reaction agrees that Cu-Se binary phase is a prerequisite for indium assimilation. As the deposition time increases beyond 60 seconds, the layer will coalesced and Se/Cu ratio is close to 2 which correspond to the ratio of diffusion fluxes of Se(IV) and Cu(II).

In a recent study, Roussel [18] mentioned that composition of the evolution in the initial stages and during growth shown a clear difference of substrate reactivity with regards to the reactive ions. Copper is easily incorporated at all stages and Selenium is more passive even when copper is present in the substrate to activate the incorporation.

As selenium accumulates on the extreme surface beyond the diffusion flux ratio shows that elemental Se formation is preferred than Se-rich compound. Therefore, reaction occurs at the surface area exhibit different kinetic parameters similar corrosion phenomena such as selective dissolution of alloys where surface composition is different from bulk.

Chaure *et al* [7] has made structural and electrical properties studies of polycrystalline of CulnSe<sub>2</sub> thin film from a one-step electrodeposition form a single electrodeposition bath on fluorine-doped tin oxide (FTO) substrate. Deposition were carried out potentiostatically in an aqueous solution containing 0.002M CuSO<sub>4</sub>, 0.004M  $In_2(SO_4)_3$ , and 0.004M  $H_2SeO_3$  with Cu : In : Se ratio of 1:2:2 in the electrolyte. The pH of the bath was maintained between 1.9 and 2.2 using highly-purity  $H_2SO_4$  solution. Bath temperature was maintained between 30°C to 40°C with stirring.

His studies showed that by varying cathodic potential yield different composition of CIS layers, as well as different conductivity determined by PEC. At cathodic potential below 0.6V yields copper-rich CIS layers, and above 0.9V yields indium-rich CIS layers. The conductivity

changes from p- to n- type as deposition cathodic voltage increase from low to high values. Between the two range (i.e. 0.7-0.85v), yields intrinsic CIS materials.

As a result of this study, the ability to obtain the type of conductivity by alter the deposition potential provides new possibilities to of forming ohmic contact of p- and n- type CIS layers.

Phok *et al* [15] has successfully fabricated vertically aligned arrays of CuInSe<sub>2</sub> (CIS) nanowires of controllable diameter and length. These were achieved by pulse cathodic electrodeposition from acidic electrolyte solution into anodized aluminum oxide templates. The growth of nanowires is consider to grow into nanoporous anodized alumina oxide template is because of the chemical inertness and periodicity. The template use consists of vertically open channels of amorphous aluminum oxide, which is self assembled into a host of hexagonal lattice using a two step anodization process.

Prior to the formation of the CIS nanowires, nanoporous anodized aluminum oxide template were fabricated. Electrolye solution contains 0.3M of oxalic acid dissolved in deionised water. Anodizations were carried out in a vertical two-electrode cell with platinum as the counter electrode at room temperature. The first step of anodization to produce a less than one micron in thickness aluminum oxide layer, was performed at constant voltage of 20V for 10mins. The oxide layer was then removed in a hot mixture of phosphoric acid and chromic acid for a few seconds.

The second step of anodization was performed at constant voltage ranging from 25V to 40V for less than 30mins. The barrier layer was then removed by ramping down the voltage at 1V/min followed by immersion in 50% phosphoric acid for less than 3mins. After which, a

thermal treatment at 230°C was carried out for several hours to removed the unwanted residuals such as hydroxide.

The CIS nanowires were then electrodeposited in anodized aluminum oxide by pulse plating. The electrolyte contains 1.5mM of copper sulphate hydrate, 2mM indium sulphate hydrate and 3.5mM seleneous acid and lithium chloride, dissolved in 100ml aqueous buffer solution (pH= 2.8) containing potassium hydrogen phthalate and hydrochloride acid. The electrodeposition was carried out in a two electrode cell with a platinum wire as counter electrode.

Before the pulse electrodeposition was administered, a first cathodic deposition was performed at 20V for few seconds to perforate any residual barrier layer. After which, several electrodeposition conditions employing voltage pulses of an amplitude of 1V, pulse width of 1s and a period of 3s were employed. Lastly, the electrodeposited CulnSe<sub>2</sub> nanowires were annealed at 220°C in vacuum to improve stoichiometry and crystallinity.

As a result, CIS nanowires array were synthesized, while pulsed potential was used to form CIS inside a nanoporous anodized alumina template of pore size ranging 5-40nm with pore length of 5um.

Valdes *et al* (2011) [21] had had made a recent investigation to addressed the benefits of cyclic pulsed electrodeposition of CulnSe<sub>2</sub> thin film on conductive glass. Prior to this study, highly efficient 3-D solar cells have been fabricated infiltrating nanostructure  $TiO_2$  with copper indium sulphides prepared using reactive pulses such as atomic layering deposition (ALD) and chemical vapor deposition (CVD), where such processes are pretty costly and sophiscated. Hence, this study may create future viability of infiltrating nanostructures of  $TiO_2$  with CIS electrodeposition by pulsing potential.

The CIS thin films were deposited on fluorine doped tin oxide (FTO) by cyclic pulse electrodeposition in a single bath configuration. A three electrode cell, with Pt mesh as counter electrode, saturated calomel electrode (SCE) as reference electrode was used. Precursor electrolyte contains  $25 \text{mmol}^{-1}$  CuCl<sub>2</sub>,  $10 \text{mmol}^{-1}$  InCl<sub>3</sub>, and  $5 \text{mmol}^{-1}$  SeO<sub>2</sub> with  $0.2 \text{mol}^{-1}$  KCl as supporting electrolyte. Concentrated HCl were use to adjust the pH between 2.0 - 2.5. Solution is purged with nitrogen to remove oxygen from the electrolyte prior to electrodeposition.

Studies were made with potentiostatic electrodeposition and cyclic pulse electrodeposition. Two potential were used in potentiostatic deposition namely; -0.7V and -0.9V, and time of deposition is 30min. As for cyclic pulse electrodeposition, one pulse consist of applying  $E_1$  ( = -0.7V and -0.9V) for 10s and  $E_2$  (= -0.1V) for another 10s. This continues for 90cycles which took about 1800s. After electrodeposition, films were annealed in argon at 500°C for 30mins, and followed by chemical etching with 0.5molL<sup>-1</sup> of KCN solution for 5mins.

Unlike the studies made by Chaure *et al* [7], Valdes *et al* (2011) [21] manage to obtain p-type conductivity CIS films from the above electrodeposition method.

#### **1.5 DENDRITE GROWTH**

Donald *et al.* [1] had defined nucleation as the formation of the first nano-size crystallite from molten material in the context of solidification. Generally, it refers to the initial stage of formation of one phase from another. In this section, discussion of nucleation is taken from solidification perspective but the phenomenon of nucleation is general and associated with phase transformation.

When a material solidifies, the energy associate with the crystalline structure of the solid is less than the energy of the liquid. This energy

difference between the liquid and the solid is the free per unit volume  $\Delta G_{\mu}$  and this is the driving force for solidification.

Once the solid nuclei of a phase forms, growth begins to occur as more atoms becomes more attached to the solid surface. The nature of growth of the solid nuclei depends on how heat is removed during solidification, i.e. to reduce the overall energy. During solidification, two type of heat to be removed, firstly the specific heat of the liquid and secondly the latent heat of fusion. The method to remove the latent heat of fusion determines the material's growth mechanism and final structure of the material.

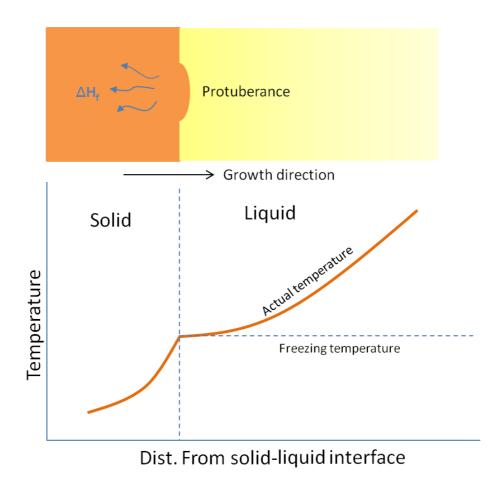

Figure 9 : Temperature of the liquid is above the freezing temperature, protuberance on the solid-liquid interface will not grow leading to a maintenance of a planar interface. Latent heat is removed from the interface through the solid.

A well-inoculate liquid containing nucleating agents cools under equilibrium conditions, heterogeneous nucleation occurs and therefore under-cooling is not required. Hence the temperature of the liquid at the solid-liquid interface is greater than the freezing temperature. The temperature of the solid is at or below freezing temperature. During solidification, latent heat of fusion is removed by conduction from solidliquid interface. Any small protuberance that begins to grow on the interface is surrounded by liquid above the freezing temperature as illustrated in the Figure 9. The growth of the protuberance will halt till the remainder of the interface catches up, this mechanism is known as the planar growth, occurs by the movements of a smooth solid-liquid interface into the liquid.

## Dist. From solid-liquid interface

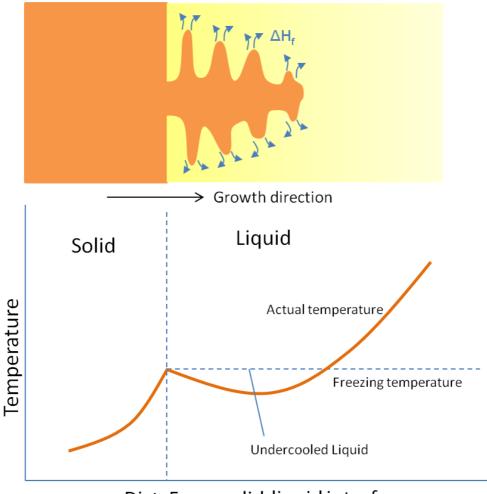

Figure 10 : Liquid is undercooled, a protuberance on the solild-liquid interface can grow rapidly as a dendrite. Latent heat of fusion is removed by raising the temperature of the liquid back to the freezing temperature.

On the other hand, when liquid is not inoculated and nucleation not desirable, under-cooling has to be carried out before the solid forms. In

such condition, the small solid protuberance that forms at the interface is known as the dendrites shown in Figure 10. These dendrites are favored in growth since the liquid before the solid-liquid interface is undercooled. As the dendrite grows, the latent heat of fusion is conducted into the undercooled liquid, raising the temperature of the liquid towards the freezing temperature. Secondary and tertiary dendrite arms can also form on the primary stalks to speed up the evolution of the latent heat. Dendritic growth continues until the undercooled liquid "warms" up to the freezing temperature. Remaining liquid shall then solidifies by planar growth. The difference between planar growth and dendritic growth arises because the different sinks for latent heat of fusion. In pure metals, dendritic growth can be represent only a small fraction of the total growth as follows:

Dendritic fraction

$$= f = \frac{c\Delta T}{\Delta H_f}$$

Where *c* is the specific heat of the liquid. Numerator  $c\Delta T$  represents the heat that the undercooled liquid can absorb, and the latent heat in the denominator  $\Delta H_f$  represents the total heat that must be given up during solidification. As undercooling  $\Delta T$  increases, more dendritic growth will occur. If the liquid is well inoculated, undercooling is almost zero, growth would generally be via planar front solidification mechanism.

#### **1.6 ANNEALING OF COMPOUNDING PRECUROSOR**

Electrodeposition of all elements simultaneously requires minutes of adjustment of concentration in the solution and the application of complexing agent. Hence, annealing at high temperature is inevitable in many processes due to the fact that the precursor film is not in its thermodynamic stable state in reaction step. This annealing of precursor compound is a re-crystallization process that completes with the deposition of the compound. Hence, optimization of the reaction step is difficult. For instance, cells with good efficiencies were obtained by a hybrid process combining electrodeposition of a Cu-rich CulnSe<sub>2</sub> films and subsequently conditioning by a vacuum evaporation step of In(Se),with annealing of films at elevated temperature is a suitable atmosphere is vital.

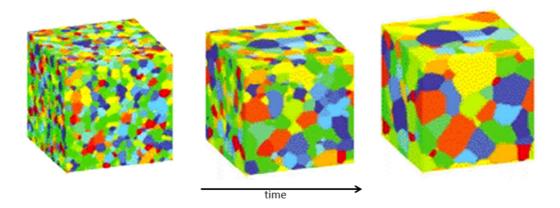

During the post treatment annealing, polycrystalline precursor expects certain grain growth. The precursor materials, being polycrystalline, contain large numbers of grain boundaries, which represent a highenergy area according to Donald *et al.* [1] because of inefficient packing of atoms. To achieve a lower overall energy of the materials, the grain boundaries have to be reduced by grain growth. This grain growth involves the movements of grain boundaries, allowing larger grains to grow in the expense of smaller grains, which can be illustrated in the following simulated model of a single phase grain.

Figure 11: Model simulation of isotropic, single-phase grain growth in a polycrystalline material. Color corresponds to the site indices. Over time, average grain size increases as large grains grow at the expense of small grains.

Figure 11 above shows grain growth occurs as atoms diffuse across the grain boundary from one grain to another. For grain growth in the material, diffusion of atoms across the grain boundary is required, and as a result, the growth of the grains is related to the activation energy need for an atom to "jump" across the boundary. Therefore the driving force for grain growth is the reduction of grain boundaries, which are defects. The presences of these grain boundaries cause the increase of free energy of the material. Hence the thermodynamic tendency is to drive the polycrystalline materials, in the case the precursor thin film, to increase the average grain size which can be achieved by applying external heat or lowering the activation energy.

Atoms or ions may possess thermal energy will move from a normal crystal structure location to occupy a nearby vacancy caused by an imperfection within the crystal structure, thus the atoms may "jump" across the grain boundary causing the grain boundary to move. The ability for an atom or ion to move or diffuse increase as temperature or thermal energy gain increases. This rate of diffusion is related by Arrhenius equations:

$$Rate = c_o \exp\left(\frac{-Q}{RT}\right)$$

Where  $c_o$  is a constant, R is the gas constant, T is the absolute temperature (K) and Q is the activation energy required to cause an Avogadro's number of atoms or ions to move.

Crystalline materials generally contains defects also known as vacancies, and the disorder of these vacancies creation increase in entropy, is able to minimize free energy therefore thermodynamically stabilize the crystalline material. In such materials, the atoms moves from one lattice position to another lattice position known as the selfdiffusion. Nevertheless, self diffusion effect is generally not significant. Hence, by increasing the thermal energy, diffusion can be carried out by vacancy diffusion and interstitial diffusion.

In vacancy diffusion, the atom leaves a regular lattice position and fills a vacancy in the crystal, as such creates a new vacancy and process continues. However interstitial diffusion occurs when a small interstitial atom or ion is present in the crystal structure, the atom or ion moves from one interstitial site to another interstitial site. Such diffusion does not require a prerequisite of available vacancy, and usually occurs much easier than vacancy diffusion.

The rate of diffusion at which atoms, ions, particles, and other species in a material can be measured by the flux (J), defines as the number of atoms passing through a plane of unit area per unit time. This can be summaries in Fick's first law as shown below:

$$J = -D\frac{dc}{dx}$$

Where *J* is the flux, *D* is the diffusivity and  $\frac{dc}{dx}$  is the concentration gradient. The negative sign suggest that the flux diffused from a region of higher concentration to a lower concentration. At microscopic scale the thermodynamic driving force for diffusion is concentration gradient, hence the net flux is created depending on temperature and concentration gradient.

The flux at a particular temperature is constant if the concentration gradient is also constant. However, this case is it is assume a steady state diffusion. Generally, in practical situation, a non-steady state diffusion has to be considered with the Fick's second law.

$$\frac{\partial c}{\partial t} = \frac{\partial}{\partial x} \left( D \frac{\partial c}{\partial x} \right)$$

Assuming the diffusion coefficient D is not a function of location x and the concentration c of diffusion species, Fick's second law can be simplified as follows:

$$\frac{\partial c}{\partial t} = D\left(\frac{\partial^2 c}{\partial x^2}\right)$$

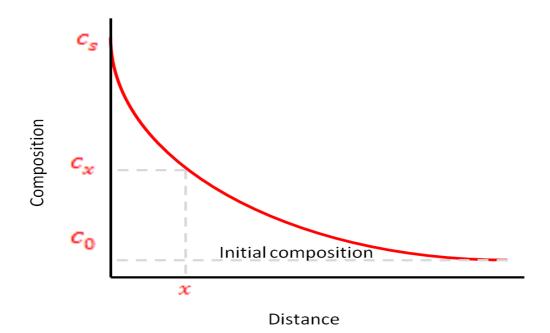

Figure 12 : Illustration of Fick's second law on the diffusion of atom into the surface of a material.

Considering the boundary conditions for a particular solution as illustrated in the above Figure 12, the solution can be written as follows:

$$\frac{c_s - c_x}{c_s - c_0} = \operatorname{erf}\left(\frac{x}{2\sqrt{Dt}}\right)$$

Where  $c_s$  is a constant concentration of the diffusion atom t the surface of the material,  $c_0$  is the initial uniform concentration of the diffusing atom in the material, and  $c_x$  is the of the diffusing atom at the location xbelow the surface after time t. This equation assumes the atoms or other diffusing species are moving in a single direction x. The function erf is the error function which mathematical definition is

$$erf(x) = \frac{2}{\sqrt{\pi}} \int_{0}^{x} exp(-y^{2}) \, dy$$

Where y is the argument of the error function, which also defines a complementary error function as follows :

$$erfc(x) = 1 - erf(x)$$

The above provides a brief discussion on diffusion and grain growth, driven by the reduction of grain boundary.

#### **1.7 BACK CONTACT – Mo**

Mo is widely used contact materials for base electrode in  $A^{I}-B^{III}-C^{\vee I}_{2}$  compound type thin film solar cells [19] because of its comparatively low cost, high melting  $A^{I}-B^{III}-C^{\vee I}_{2}$  point of about 2700°C and expected low diffusitivity in the semiconductor films. Polycrystalline Mo films are usually sputtered at room temperature or electron beam evaporated onto glass substrate at about 300°C, however in this thesis will be on Silicon wafer substrate. The resistivity of Mo increase with oxygen incorporation from the residual gas atmosphere and with increasing tensile stress in the film. These tensile stress adhere to the substrate better [20].

One on the main advantage molybdenum is that the reactivity of Mo with selenium or sulphur is relatively small. However, at high substrate temperature of about 500°C, a MoSe<sub>2</sub> film or MoS<sub>2</sub> film forms before or during the growth of chalcopyrite film. Therefore, MoX<sub>2</sub> (X=Se or S) can form at the Mo/Chalcopyrite interface and/or on top of the Mo layer before formation of chalcopyrite by exposing to chalcopyrite vapour.

This  $MoX_2$  (where X=Se or S) are layered semiconductors with an indirect bandgap of 1.06-1.16eV and 1.17-1.35eV respectively. Roland et al [19] reported that if  $MoX_2$  films were oriented is such that the c-axis is perpendicular to the substrate, where it shows weak van der waals bonding, the layer may impede the adhesion of the chalcopyrite absorber. However, it has shown that parallel orientation appeared to be the preferred orientation for  $MoX_2$  growth at the Mo/chalcopyrite interface which perpendicular orientation is preferred only at surface

controlled Mo chalcogenisation. Both processes may contribute to the  $MoX_2$  film thickness which the growth rate of c axis parallel is higher. In the parallel c axis configuration, diffusion of metal ions into the van fer waals planes of  $MoSe_2$  could lead to a chemical intermixing at  $MoSe_2/A^{I}-B^{III}-C^{VI}_2$  interface and induce the observed ohmic contact characteristic. In William N. (2011) [19] studies, it was reported that Ga diffusion into Mo layer is and diffusion of Cu, In and Se. The thickness of  $MoSe_2$  layer increases with increasing substrate temperature. It also decreases with increasing O content in the Mo layer.

The optical reflection of Mo in the wavelength ranges of 500-600nm is only 60% tested alternative back contacts with the aim of improving the back contact reflectivity. Chromium (Cr), Vanadium (V), Titanium (Ti) and Manganese (Mn) has been rule out due to strong reactivity with Selenium. However, the use of Tantalum (Ta) and Niobidium (Nb) leads to good device quality. Unlike molybedeum (Mo) and Tungseten (W), it was found that Ta and Nb back contact needs a Galium (Ga) back surface gradient for high open circuit voltage V<sub>oc</sub> [19] (i.e. the voltage the cell develops at zero load), probably due to the inferior properties of the selenium formed.

# 2. EXPERIMENTAL DETAILS

#### 2.1 SUBSTRATE PREPARATION

Two types of substrates were used for this study. The initial study of CIS plating used Mo-strips. These Mo strips were obtained from a 2mm thick Mo metal sheet cut into small coupons of  $1 \times 2$  cm. Being easily oxidized, the surface of the Mo strips were lightly polished with silicon carbide paper grid 600 before the start of the experiment to ensure that the CIS plated on the Mo surface.

The second type of substrate was obtained from Mo sputtered on an 8inch Silicon wafer by physical vapour deposition (PVD). The Mo deposited by pulsed DC sputtering at a pressure of about 1.5mTorr. The molybdenum thickness is about 200nm. Thickness of the molybdenum on Si wafer was inspected by FESEM cross sectioning instead of using a surface profiler. The samples were then cleaved by a diamond scriber to obtained approximately 1cm by 2cm, adhered to the copper wire contacts by silver paint protected by a layer coat of fast cured two-part epoxy. Before the start of the electrochemical deposition, the Mo substrates were cleaned in 25% ammonia for 5mins and rinsed with high purity water as per Chassing *et al* [6].

## 2.2 DEPOSITION OF CIS THIN FILMS

The solutions were prepared from analyital grade purity high purity water of at least  $18.2M\Omega$  by Millipore Elix Progard 2 5UV. Copper Indium Diselenide solution was made-up of aqueous 0.002M Cu<sub>2</sub>SO<sub>4</sub>, 0.004M InCl<sub>3</sub> and 0.004M H<sub>2</sub>SeO<sub>3</sub>, having a ratio of 1:2:2 in the electrolyte. If an off-white precipitation occurred after mixing the four solutions this was resolved by adjusting to pH 2 with aqueous 37% hydrochloride acid [18].

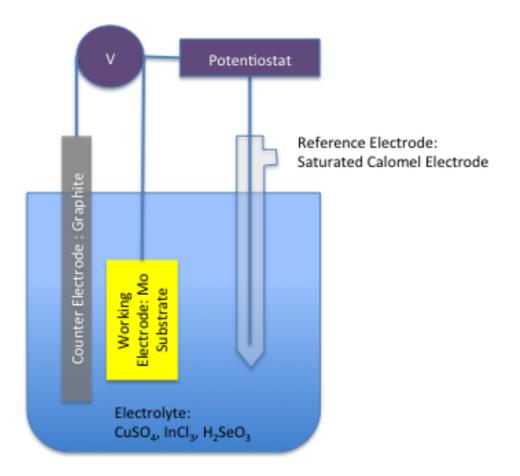

Electrodeposition of CIS thin film was carried out using ACM instruments Field Machine DSP. The setup is a three-electrode electrochemical cell consisting of a Saturated Calomel Electrode (SCE) (Hg/HgCl<sub>2</sub>/KCI) as the reference electrode, Mo substrate (either Mostrip or Mo-wafer) as the working electrode (Cathode) and graphite rod as the counter electrode (anode) as illustrated in Figure 13. All the potentials in this thesis are quoted versus the SCE system.

Figure 13: Electrodeposition setup

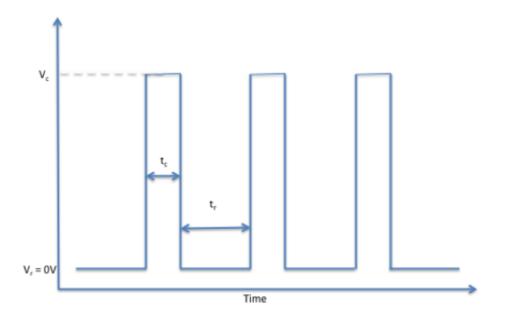

Three types of deposition were made. First DC deposition was performed at room temperature with both Mo-strip and Mo-wafer coupons. The second type of deposition was made with pulse deposition at room temperature employing a pulse width of 1 second  $(t_c)$  and period of 2 seconds rest  $(t_r)$  [15] with the voltage ranging from - 0.3V to -1.3V.as illustrated in Figure 14. The third type of deposition

used the same pulse plating profile as type two deposition, but the solution was heated to 40°C.

Figure 14: Voltage-time profile of pulse deposition of CIS thin film.  $V_c$  ranging for -0.3V to -1.3V, whereas  $t_r = 2$  second and  $t_c = 1$  second.

## 2.3 POST TREATMENT

The CIS thin films were subjected to post treatments to enhance the crystallinity of the CIS thin films at the Mo-CIS interface and to remove unwanted phases typically  $Cu_xSe_{1-x}$ . Phok *et al.* [15] have shown that annealing improves the adhesion between Mo-CIS interfaces by forming a more stable CIS thin film, as opposed to a  $Cu_xSe_{1-x}$  layer, at the Mo surface. This can be achieved by first annealing the samples at 450°C for 30mins in a vacuum environment to prevent oxidation from occurring by vacuum tube furnace and allow at least 4 hours to cool down to room temperature. These were followed by an etching of 5wt% KCN for a period of 5min in ultrasonic. The samples were then rinsed with high purify water and air dry. This etching step removes the excess Cu and Se compounds.

#### 2.4 ELEMENTAL ANALYSIS BY ENERGY DISPERSIVE X-RAY (EDX) SPECTROCOPY

The CIS thin film composition were analyzed by energy dispersive xray (EDX) using Oxford instruments Inc. Solid Drift detector (SDD) X-Max 80 with 80mm<sup>2</sup> active window run on Aztec software, and 10mm<sup>2</sup> convention EDX detector on Inca software. A working distance of 10mm and an acceleration voltage of 15kV were used to sufficiently cover all three elements (Cu, In and Se) for studies up to the k-alpha lines.

Qualitatively, results were normalized to and fixed to only quantify the above 3 elements for studies. This is because with high acceleration voltage, the interaction volume penetrates deeper thus Molybdenum (Mo) and Silicon (Si) were also detected.

The advantage of Aztec software is that the processing time and dead count were controlled by software, thus sufficient counts were collected. With 80mm<sup>2</sup> active window, the processing time is greatly reduced. No overlapping of peaks is suspected during the analysis by Aztec software, thus wavelength dispersive x-ray spectroscopy (WDS) is not required. Copper quantimization were performed on copper tape before the start of the test to ensure the quantitative results were optimized on convention 10mm<sup>2</sup> active window. All samples CIS thin films were analyzed after electrodeposition.

#### 2.5 SURFACE MORPHOLOGY EVALUATION BY SCANNING ELECTRON MICROSCOPY (SEM)

The CIS thin films surface morphologies were studied by means of Field Emission Gun Scanning Electron Microscopy (FESEM) using Zeiss Supra 25 and JEOL JSM 7800 FESEM. Secondary electron mode is use to give sufficient resolution, however, because the initial characterization of EDX requires a high acceleration voltage of 15kV, the surface topography is compensated. Nevertheless, both Zeiss and JEOL has lower electron detector (LEI or InLens), these detector would improve the topography of the surface as the detector has the ability to collect lower energy secondary electrons at the surface. Since samples are generally conductive and EDX is required in the earlier studies, no sputtering metallization (Pt/Au) were needed even micrographs shows slight charging effect on the bigger grains and dendrites. Thin films surface were taken after electrodeposition. Both surface profile and cross-section views were studied.

# 2.6 PHASE ANALYSIS BY X-RAY DIFFRACTOMETER (XRD)

To identify the phases present as well as the crystal structure of the CIS films, X-ray Diffraction spectroscopy was performed. All three types of substrates were examined both after electrodeposition and after post treatments. Although only the Mo strip substrate had XRD performed after annealing treatment. The XRD was carried out by Bruker's D8 Advance and DIFFRAC.SUITE software, incidental angle starting from 20° to 80° with 0.1 diffraction silt.

#### 2.7 ELECTRICAL CONDUCTIVITY BY PHOTOELECTRO-CHEMICAL (PEC)

Photoelectrochemical measurements allow a simple and fast characterization of the semiconducting properties of the film. The current-voltage characteristic of an illuminated semiconductor electrode in the contact with the redox electrolyte can be obtained easily by adding together the majority and minority current components [16].

Usually the working electrode is illuminated during measurement. Both polychromatic illumination (white light) and monochromatic illumination

can be use as long the energy of the light is higher than that of the energy bandgap of the semiconductor. If the film is photoactive, photocurrent or photovoltage will be detected i.e. when the current is higher under illumination than in the dark. The direction of the photocurrent or photovoltage gives the information of the conductivity type of the film whether it is p-, i- or n- type.

When a semiconductor is immersed in a solution, an electric field develops at the solid/liquid interface via charge transfer reactions between the two phases. The electric field enables the separation of charge carriers, analogously to a pn-junction or a Schottky junction. Illumination on the semiconductor cause an increase of the concentration of minority carriers such as electrons in a p-type semiconductor. The electric field drives the photogenerated minority carriers towards the semiconductor/liquid interface where they participate in electrochemical reactions in the solution with suitable redox species. Therefore a p-type semiconductor is capable of reducing more species under illumination than in the dark, resulting in an increase of cathodic current while the anodic current remains unaffected. An n-type semiconductor behaves likewise, where the anodic current increases under illumination than in the dark. PEC measurements provides information about the film properties after deposition.

Usually this type of experiment is carried out in an electrolyte solution containing redox species. The potential of which is in a suitable position with respect to the band edges of the semiconductor so that charge transfer reaction between the semiconductor and solution are possible. Nevertheless, band edge positions of CIS are dependent on the electrolyte and on the surface chemistry of the film [13]. In this project, the measurements were performed in aqueous 0.01M CuSO<sub>4</sub> electrolyte solution and the photovoltage shifts were recorded with respect to Saturated Calomel Electrode (SCE) (Hg/HgCl2/KCl<sub>(sat)</sub>) as the reference electrode connected to a high impedance voltmeter.

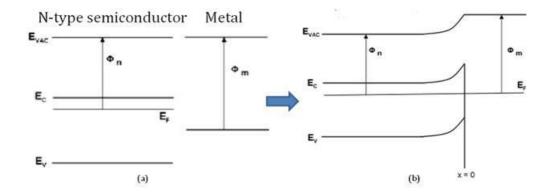

In the dark the CIS films form a Schotty barrier with the 0.1 M CuSO<sub>4</sub> electrolyte, which is similar to the "Metal-semiconductor junction" shown in the Figure 15. For instant a n-type semiconductor of work function  $\Phi$ n and metal of work function  $\Phi$ m, such that  $\Phi$ m <  $\Phi$ p.

Figure 15: n-type semiconductor and metal (a) in isolation (b) semiconductor –metal junction in equilibrium.

When the metal and semiconductor are separated from each other, the Fermi levels will look like those in Figure 15(a). When both are in electronic contact, the Fermi levels will line up as shown in Figure 15(b). This is achieved by the exchange of charge carriers across the junction, with the consequence that the layers approached equilibrium. The energy at the conduction band edge at the interface between semiconductor and metal is higher than in the bulk of the semiconductor.

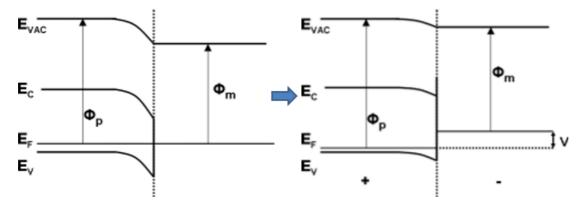

Upon illuminating with a 300 W Xenon lamp (Oriel Instruments) photons with energy greater than bandgap ( $E_g$ ) are absorbed by the semiconductor resulting in electron-hole pair generation. This causes electrons to be accumulated at the semiconductor side and holes in the metal side of the depletion region. The separation of the electrons and holes causes an electric field that opposes the initial field creating a photovoltage  $V_{photo}$ , equal to the difference in the Fermi levels of semiconductor and metal far from the junction as shown in Figure 16.

In the case of a semiconductor electrolyte junction the metal's Fermi level is replaced by the redox potential of the solution.

Figure 16: Band profiles for the p-type semiconductor-metal junction under illumination.

The polarity type of solid/liquid junction the CIS film deposited can thus be obtained when photovoltage is measure before and after illumination. That is an p-type semiconductor results in a positive photovoltage and a n-type a negative one. This study was done on DC plating and Pulse/heated Pulse plating on Mo-wafer substrates instead of Mo-strip substrates.

## 3. RESULTS & DISCUSSION

#### 3.1 ELEMENTAL ANALYSIS BY ENERGY DISPERSIVE X-RAY (EDX) SPECTROCOPY

Table 1 to Table 4 tabulate the elemental compositions, as determined by EDX, of the CIS films as plated by the various plating processes on the two different substrates at different deposition potentials ranging from -0.3V to -1.3V with respect to SCE.

- a) DC plating on Mo-strip

- b) DC plating on Mo-wafer

- c) Pulse plating on Mo-wafer

- d) Pulse plating on Mo-wafer at 40°C

| DC plating on Mo strip  |                        |      |      |  |

|-------------------------|------------------------|------|------|--|

| Cathodic Potential with | Composition (atomic %) |      |      |  |

| respect to SCE          | Cu                     | In   | Se   |  |

| Theoretical Values      | 25.0                   | 25.0 | 50.0 |  |

| -0.30                   | 21.2                   | 22.3 | 56.5 |  |

| -0.70                   | 19.0                   | 37.6 | 43.5 |  |

| -0.90                   | 19.1                   | 49.6 | 31.2 |  |

| -1.10                   | 19.9                   | 44.7 | 35.4 |  |

| -1.30                   | 11.5                   | 70.6 | 17.8 |  |

| Table 1: Summary of EDX elemental results on the CIS films deposited on Mo- | strip at |

|-----------------------------------------------------------------------------|----------|

| room temperature by DC plating.                                             |          |

Table 2: Summary of EDX elemental results on the CIS films deposited on Mo wafer at room temperature by DC plating.

| DC on Mo wafer          |                        |      |      |      |

|-------------------------|------------------------|------|------|------|

| Cathodic Potential with | Composition (atomic %) |      |      |      |

| respect to SCE          | Cu                     | In   | Se   |      |

| Theoretical Values      |                        | 25.0 | 25.0 | 50.0 |