## FABRICATION AND CHARACTERIZATION OF ADVANCED AIGaN/GaN HIGH-ELECTRON-MOBILITY TRANSISTORS

LIU XINKE

NATIONAL UNIVERSITY OF SINGAPORE

## FABRICATION AND CHARACTERIZATION OF ADVANCED AIGaN/GaN HIGH-ELECTRON-MOBILITY TRANSISTORS

## LIU XINKE (B. APPL. SC. (HONS.)), NATIONAL UNIVERSITY OF SINGAPORE

## A THESIS SUBMITTED FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

## DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING

### NATIONAL UNIVERSITY OF SINGAPORE

## DECLARATION

I hereby declare that this thesis is my original work and it has been written by me in its entirety. I have duly acknowledged all the sources of information which have been used in the thesis.

This thesis has also not been submitted for any degree in any university previously.

利和

LIU XINKE

30 May 2013

### Acknowledgements

First of all, I would like to express my appreciation to my mainsupervisor, Assistant Professor Yeo Yee Chia, for his guidance throughout my Ph.D. candidature at National University of Singapore (NUS). His knowledge and innovation in the field of semiconductor devices and nanotechnology has been truly inspirational. He has always been there to give insights into my research work and I have greatly benefited from his guidance.

I would also like to thank my co-supervisor, Associate Professor Tan Leng Seow, for his advice and suggestions throughout my candidature. Special thanks also go to Dr. Liu Wei, Dr. Pan Jisheng, Dr. Soh Chew Beng, and Dr. Chi Dongzhi, for their guidance and support while I was performing my experiments at Institute of Materials Research and Engineering (IMRE). I have greatly benefited from their vast experience in nitride material growth and characterization. I also acknowledge Liu Bin's help on the device stress simulation.

I would like to thank Dr. Koen Martens, from Interuniversity Microelectronics Centre (IMEC), Belgium, for his useful discussion on high temperature capacitance-voltage measurement. In addition, I am grateful to Professor Kevin Jing Chen and Mr. Kwok Wai Chan, from Hong Kong University of Science and Technology (HKUST), for their help on the high voltage device characterization.

I would also like to acknowledge the efforts of the technical staffs in silicon nano device laboratory (SNDL), specifically Mr. O Yan Wai Linn, Mr. Patrick Tang, and Ms Yu Yi in providing technical and administrative support for my research work. Thank Mr. O Yan Wai Linn again for his teaching on machine repairing. Appreciation also goes out to Ms. Teo Siew Lang and Mr. Yi Fan from IMRE for their help when I was doing device fabrication there.

I am also grateful for the discussions from many outstanding researchers and graduate students in SNDL. Special thanks to Dr. Chin Hock Chun for mentoring me during the initial phase of my research for the device fabrication. Special thanks also go to Liu Bin, Edwin Kim Fong Low, Zhan Chunlei, Tong Yi, and Kian Hui for their tireless support in device fabrication, measurements, and imaging when the conference deadline came. I would also like to thank Pannir, Yicai, Maruf, Zhihong, Kian Lu, Genquan, Phyllis, Ivana, Pengfei, Yang Yue, Gong Xiao, Yinjie, Zhou Qian, Samuel, Eugene, and many others for their useful discussions and friendships throughout my candidature. Helps from final year students, Lim Wei Jie, Woon Ting, Chen Yang, and Liu Chengye are also acknowledged.

I would like to extend my greatest gratitude to my family (father, mother, and elder sister) who have always encouraged my academic endeavors. Last but not least, I am also very grateful for the support, care and encouragement of my wife, Han Zhisu, throughout all these years. Sacrifices that you have made in the support of my academic pursuits will never be forgotten. Thank you for your love and devotion.

## **Table of Contents**

| Acknowledgementsi                                                                                                |

|------------------------------------------------------------------------------------------------------------------|

| Table of Contents iii                                                                                            |

| List of Tables viii                                                                                              |

| List of Figuresix                                                                                                |

| List of Symbolsxix                                                                                               |

| List of Abbreviationsxxii                                                                                        |

|                                                                                                                  |

| Chapter 1 Introduction1                                                                                          |

| 1.1 Overview of Gallium Nitride1                                                                                 |

| 1.1.1 Gallium Nitride Material and Potential Applications1                                                       |

| 1.1.2 AlGaN/GaN Heterostructure: Polarization Charge5                                                            |

| 1.2 Literature Review of High Voltage AlGaN/GaN HEMTs8                                                           |

| 1.3 Challenges of AlGaN/GaN High Electron Mobility Transistors14                                                 |

| 1.3.1 Formation of High Quality Gate Stack                                                                       |

| 1.3.2 Strain Engineering15                                                                                       |

| 1.3.3 Gold-Free CMOS Compatible Process16                                                                        |

| 1.4 Objective of Research                                                                                        |

| 1.5 Thesis Organization                                                                                          |

| Chapter 2 <i>In Situ</i> Surface Passivation of Gallium Nitride in Advanced Gate Stack Process                   |

| 2.1 Introduction                                                                                                 |

| 2.2 Development of In Situ Surface Passivation for Gallium Nitride23                                             |

| 2.2.1 Experiment                                                                                                 |

| 2.2.2 Effect of Vacuum Anneal on Interface Quality27                                                             |

| 2.2.3 Effect of SiH <sub>4</sub> or SiH <sub>4</sub> +NH <sub>3</sub> Treatment Temperature on Interface Quality |

| 2.3 Detailed Characterization of Interface State Density                                                         |

| 2.3.1 Need for Electrical Characterization at an Elevated Temperature .33                                        |

| 2.3.2 Method of Extracting Interface State Density [109]35                                                       |

| 2.3.3 Comparison of <i>In Situ</i> Passivation Methods                                                           |

| Chapter 3 AlGaN/GaN MOS-HEMTs with <i>In Situ</i> Vacuum An SiH <sub>4</sub> Treatment                                  |    |

|-------------------------------------------------------------------------------------------------------------------------|----|

| 3.1 Introduction                                                                                                        | 48 |

| 3.2 Device Fabrication                                                                                                  | 50 |

| 3.3 Results and Discussions                                                                                             | 54 |

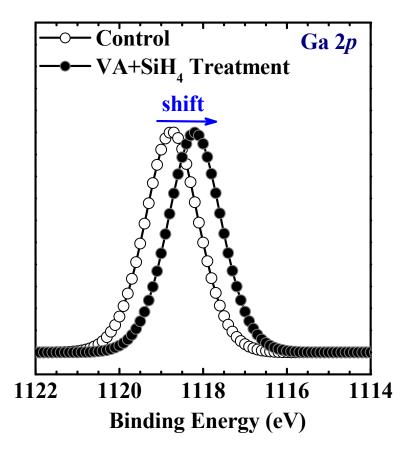

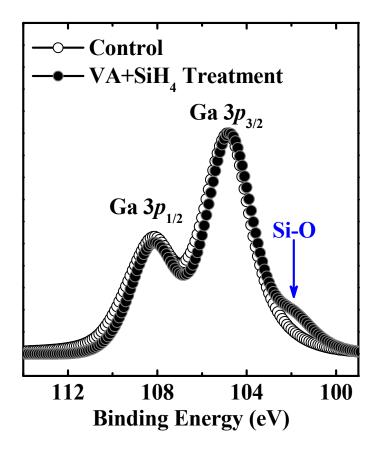

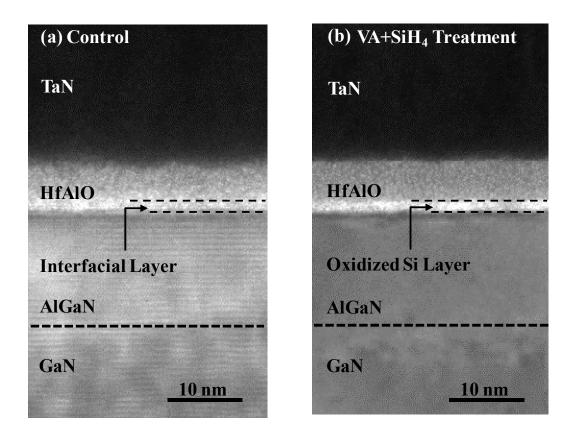

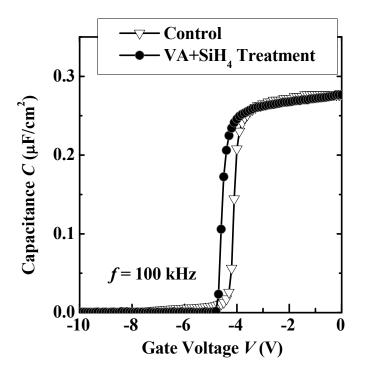

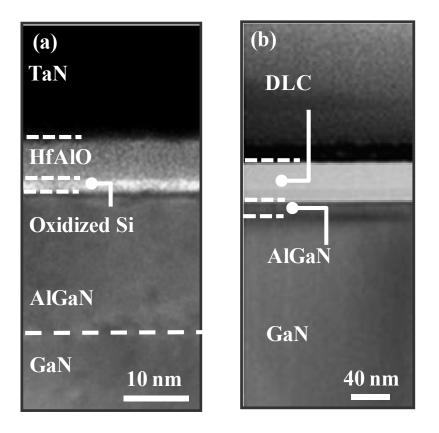

| 3.3.1 Material Characterization: XPS and TEM                                                                            | 54 |

| 3.3.2 Electrical Characterization of the AlGaN/GaN MOS-HEN and without <i>in situ</i> VA and SiH <sub>4</sub> Treatment |    |

| 3.4 Summary                                                                                                             | 72 |

### Chapter 4 Diamond-Like Carbon Liner with Highly Compressive Stress for Performance Enhancement of AlGaN/GaN MOS-HEMTs......73

| 4.1 Introduction                                                                         | 73 |

|------------------------------------------------------------------------------------------|----|

| 4.2 Device Concept and Stress Simulation                                                 | 75 |

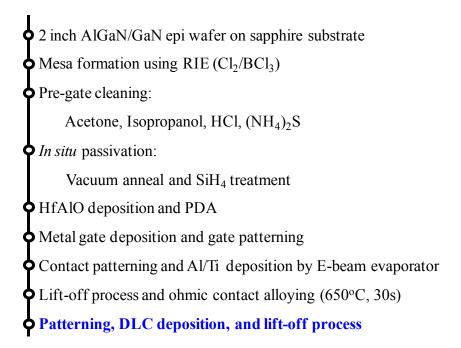

| 4.3 Integration of Diamond-like Carbon Liner on AlGaN/GaN MHEMTs                         |    |

| 4.4 Electrical Characterization of the Devices with and withou Diamond-Like Carbon Liner |    |

| 4.5 Summary                                                                              | 95 |

#### Voltage AlGaN/GaN **MOS-HEMTs** Chapter 5 High with я Complementary Metal-Oxide-Semiconductor Compatible Gold free 5.2.1 Fabrication of AlGaN/GaN-on-Silicon MOS-HEMTs using a 5.3 High Voltage AlGaN/GaN-on-Sapphire MOS-HEMTs ......108 5.3.1 Fabrication of AlGaN/GaN-on-Sapphire MOS-HEMTs using a

| Chapter 6 Conclusion and Future Work |  |

|--------------------------------------|--|

| 6.1 Conclusion                       |  |

| 6.2 Contributions of This Thesis     |  |

| 6.2.2 In Situ Vacuum Anneal and SiH4 Treatment on AlGaN/GaN MOS-<br>HEMTs                                                                                                                                                                                                          |   | 6.2.1 <i>In Situ</i> Surface Passivation for High Quality Metal Permittivity Dielectric Stack | •         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----------------------------------------------------------------------------------------------|-----------|

| MOS-HEMTs1266.2.4 High Voltage AlGaN/GaN MOS-HEMTs with CMOS Compatible<br>Gold-Free Process1266.3 Future Directions1276.3.1 Other Silicon Passivation Technique1276.3.2 Surface Passivation Technique on Other Nitride Material System1271286.3.3 Strain Engineering Technique128 |   |                                                                                               |           |

| Gold-Free Process1266.3 Future Directions1276.3.1 Other Silicon Passivation Technique1276.3.2 Surface Passivation Technique on Other Nitride Material System1276.3.3 Strain Engineering Technique128                                                                               |   | 6 6                                                                                           |           |

| <ul> <li>6.3.1 Other Silicon Passivation Technique</li></ul>                                                                                                                                                                                                                       |   | <b>e e</b>                                                                                    | 1         |

| <ul><li>6.3.2 Surface Passivation Technique on Other Nitride Material System127</li><li>6.3.3 Strain Engineering Technique</li></ul>                                                                                                                                               | e | 6.3 Future Directions                                                                         | 127       |

| 6.3.3 Strain Engineering Technique                                                                                                                                                                                                                                                 |   | 6.3.1 Other Silicon Passivation Technique                                                     | 127       |

|                                                                                                                                                                                                                                                                                    |   | 6.3.2 Surface Passivation Technique on Other Nitride Material                                 | System127 |

| 6.3.4 Source/Drain Series Resistance Reduction                                                                                                                                                                                                                                     |   | 6.3.3 Strain Engineering Technique                                                            |           |

|                                                                                                                                                                                                                                                                                    |   | 6.3.4 Source/Drain Series Resistance Reduction                                                | 128       |

| References130                                                                                          |

|--------------------------------------------------------------------------------------------------------|

| Appendix A163                                                                                          |

| Process Flow for Fabricating AlGaN/GaN MOS-HEMTs in This Work 163                                      |

| Appendix B                                                                                             |

| Silvaco TCAD Code Used for AlGaN/GaN MOS-HEMTs with <i>in situ</i> VA and SiH <sub>4</sub> Passivation |

| Appendix C                                                                                             |

| Taurus Abaqus Code Used for Stress Simulation167                                                       |

| Appendix D171                                                                                          |

| Sentaurus TCAD Code Used for DLC-Strained AlGaN/GaN MOS-HEMT                                           |

| Appendix E                                                                                             |

| First Author Publications Arising from This Thesis Research176                                         |

| Other Publications                                                                                     |

### Abstract

Fabrication and Characterization of Advanced AlGaN/GaN

High-Electron-Mobility Transistors

by

LIU Xinke

Doctor of Philosophy – Electrical and Computer Engineering National University of Singapore

AlGaN/GaN high electron mobility transistors (HEMT) have become a very promising candidate for the next generation high voltage electronic devices, mainly due to the superior material properties of GaN. Especially, the growth of GaN-on-silicon wafers with large diameters of 6 inches and 8 inches was demonstrated, which can enable the cost-effective fabrication of GaN power devices. This thesis focuses to explore the application of AlGaN/GaN HEMTs for the power devices beyond the silicon-based transistors.

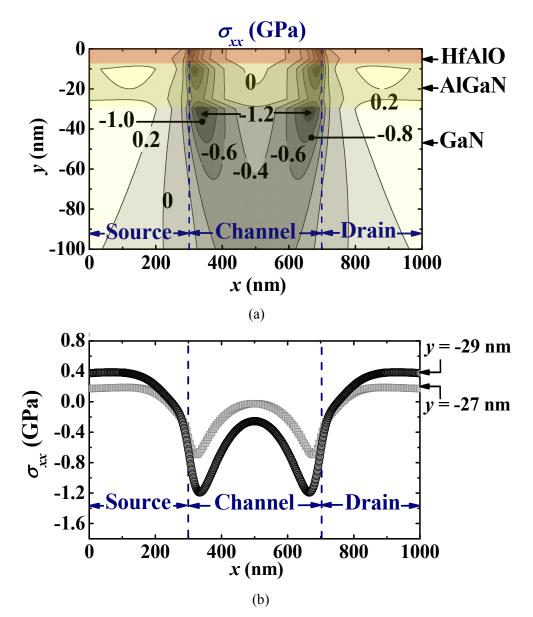

To take full advantage of AlGaN/GaN HEMTs, a gate dielectric process technology that provides good interfacial properties is required. In this thesis, an effective and highly manufacturable passivation technology based on a multi-chamber metal-organic chemical vapor deposition (MOCVD) gate cluster system was demonstrated. The key characteristics of the novel *in situ* passivation using vacuum anneal and silane (SiH<sub>4</sub>) treatment were determined and identified. AlGaN/GaN metal-oxide-semiconductor HEMTs (MOS-HEMTs) with *in situ* vacuum anneal and SiH<sub>4</sub> treatment exhibit good electrical characteristics. Further enhancement of AlGaN/GaN MOS-HEMTs by integration of a highly compressive stress liner was also investigated. This work explored a novel highly compressive diamond-like-carbon (DLC) stress liner to induce non-uniform stress along the channel of the AlGaN/GaN MOS-HEMTs. It was found that the compressive stress was induced by the DLC stress liner in the channel under the gate stack, thus reducing the polarization charge by piezoelectric polarization; a tensile stress was induced in the source/drain access regions between the gate and the source/drain (S/D) contacts, thus leading to an increase of the polarization charge and a reduction of source/drain series resistance.

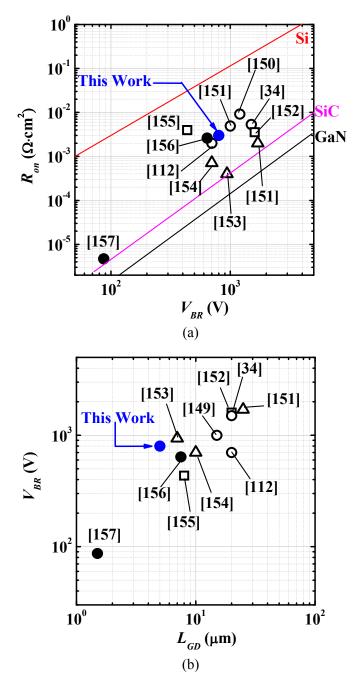

To enable cost-effective GaN power devices in the silicon complementary metal-oxide-semiconductor (CMOS) foundry, a CMOS compatible gold-free process is essential. Both high breakdown voltage AlGaN/GaN-on-silicon and -on-sapphire MOS-HEMTs were realized using a CMOS compatible gold-free process, where CMOS compatible ohmic contacts and gate stack were adopted. In this work, AlGaN/GaN-on-sapphire MOS-HEMTs achieved the highest breakdown  $V_{BR}$  of 1400 V, as compared to other gold-free AlGaN/GaN HEMTs reported to date.

## List of Tables

| Table 1.1. | Comparison of material properties of Si, GaAs, 4H-SiC, and GaN at 300 K. BFOM is Baliga's figure of merit for power transistor performance ( $\mu_{n.}\varepsilon_{r.}E_{G}^{3}$ ), and the benchmark is Si [5]. 2 |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 2.1. | Various deposition methods to achieve a high quality dielectric/GaN interface [37]-[44]. "-" means "not reported"21                                                                                                |

| Table 5.1. | Reports of AlGaN/GaN MOS-HEMTs with a CMOS compatible gold-free process [156]-[157], [172] and key device parameters.                                                                                              |

# **List of Figures**

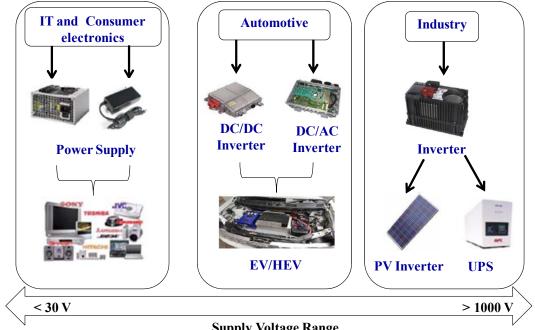

| Fig. 1.1. | Potential applications for GaN-based power devices. Based on<br>the supply voltage range, the applications are divided into three<br>categories: IT and consumer electronics, automotive, and<br>industry [8]                                                                                                                                                                                                                                           |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

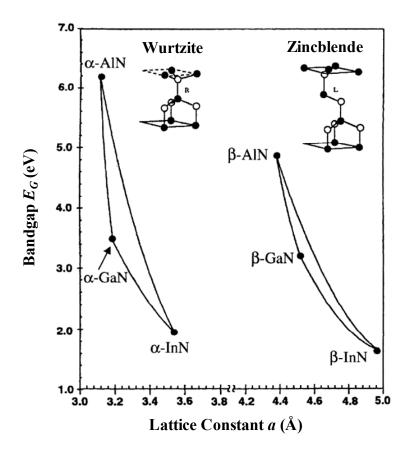

| Fig. 1.2. | Bandgap $E_G$ of hexagonal ( $\alpha$ -phase) and cubic ( $\beta$ -phase) InN, GaN, AlN, and their alloys versus lattice constant <i>a</i> [3]4                                                                                                                                                                                                                                                                                                         |

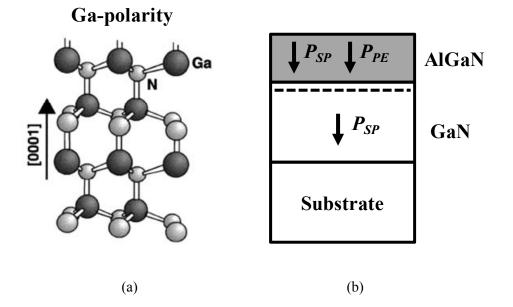

| Fig. 1.3. | (a) Schematic drawing of the crystal structure of wurtzite GaN with the Ga-polarity face. (b) Directions of the spontaneous ( $P_{SP}$ ) and piezoelectric ( $P_{PE}$ ) polarization for wurtzite AlGaN/GaN heterostructure with the Ga-polarity face are labeled [9]                                                                                                                                                                                   |

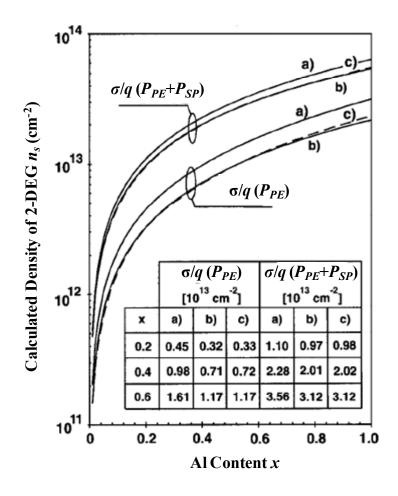

| Fig. 1.4. | The calculated density of 2-DEG $n_s$ of pseudomorphic AlGaN/GaN heterosture as a function of Al content <i>x</i> of the Al <sub>x</sub> Ga <sub>1-x</sub> N barrier layer [10]7                                                                                                                                                                                                                                                                        |

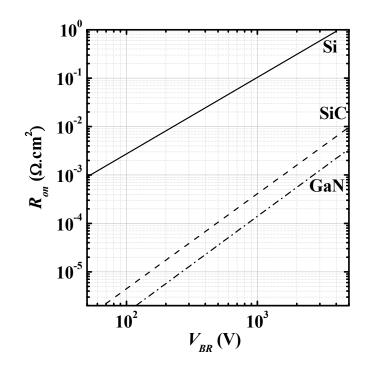

| Fig. 1.5. | Theoretical limit of the on-state resistance $R_{on}$ as a function of breakdown voltage $V_{BR}$ for GaN, SiC, and Si devices [11]9                                                                                                                                                                                                                                                                                                                    |

| Fig. 1.6. | Schematic diagrams of epitaxial layers and cross sections of (a) AlGaN/GaN HEMT with an overlapping gate [15], (b) insulated gate AlGaN/GaN HEMT with JVD deposited SiO <sub>2</sub> gate dielectric [24], (c) AlGaN/GaN HEMT with discrete multiple field plates [25], and (d) AlGaN/GaN HEMT with a trench gate [23]11                                                                                                                                |

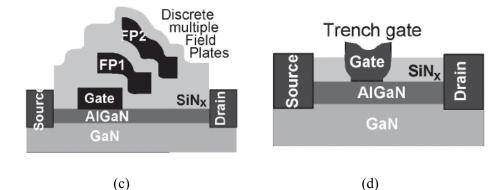

| Fig. 1.7. | Process flow of the substrate transfer technology [34]. (a)<br>Standard AlGaN/GaN HEMT on Si substrate. (b) Bonding to a<br>Si carrier wafer and Si (111) substrate removal, and BCB stands<br>for benzocyclobutene. (c) GaN/AlGaN buffer bonded to a glass<br>wafer. (d) Final device structure after releasing the carrier wafer.<br>G, S and D stand for gate, source and drain, respectively12                                                      |

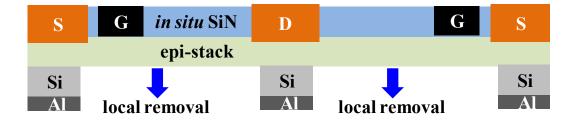

| Fig. 1.8. | Schematic cross section after the local silicon removal process [35]. G, S and D stand for gate, source and drain, respectively.13                                                                                                                                                                                                                                                                                                                      |

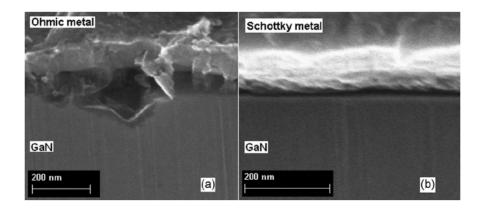

| Fig. 1.9. | Cross-sectional SEM images of (a) ohmic contact on AlGaN/GaN and (b) Schottky contact on AlGaN/GaN structure grown on Si substrate [36]13                                                                                                                                                                                                                                                                                                               |

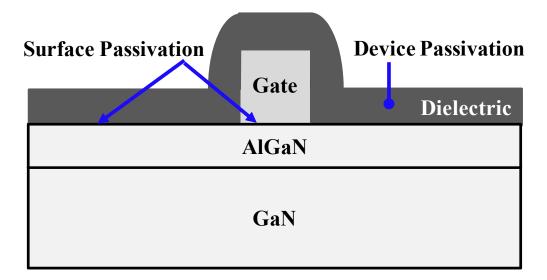

| Fig. 2.1. | Schematic diagram illustrating two approaches for passivating AlGaN/GaN HEMTs: surface passivation/treatment and device passivation                                                                                                                                                                                                                                                                                                                     |

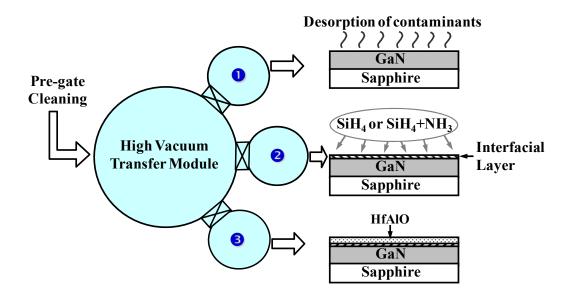

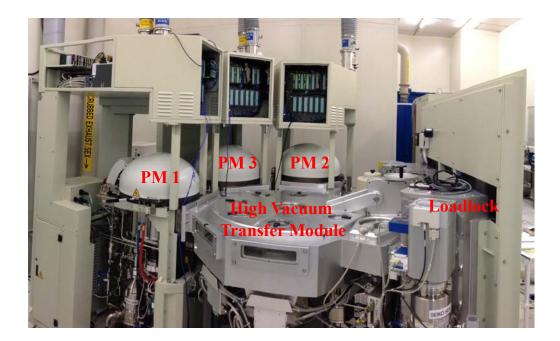

| Fig. 2.2. | Schematic diagram illustrating the <i>in situ</i> passivation and HfAlO deposition processes in a multi-chamber metal-organic chemical vapor deposition (MOCVD) gate cluster system. A high vacuum transfer module is connected to the three process chambers, including the first chamber for VA, the second chamber for surface treatment with SiH <sub>4</sub> +NH <sub>3</sub> or SiH <sub>4</sub> only, and the third chamber for HfAlO deposition |

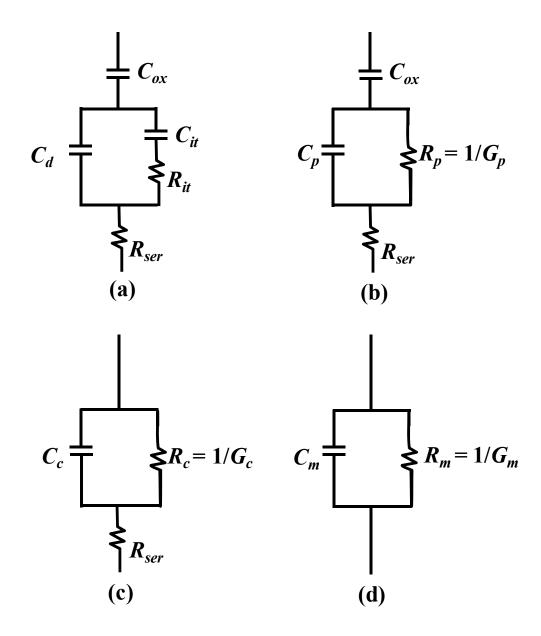

- Fig. 2.9. (a) Equivalent circuit of the metal-oxide-semiconductor structure, showing the oxide capacitance  $C_{ox}$ , the capacitance of the depletion region  $C_d$ , the capacitance  $C_{it}$  and resistance  $R_{it}$  of the interface states, and the series resistance  $R_{ser}$ . (b) A simplified circuit of (a) with  $C_d$ ,  $C_{it}$ , and  $R_{it}$  replaced by  $C_p$  and  $R_p$ . (c) A

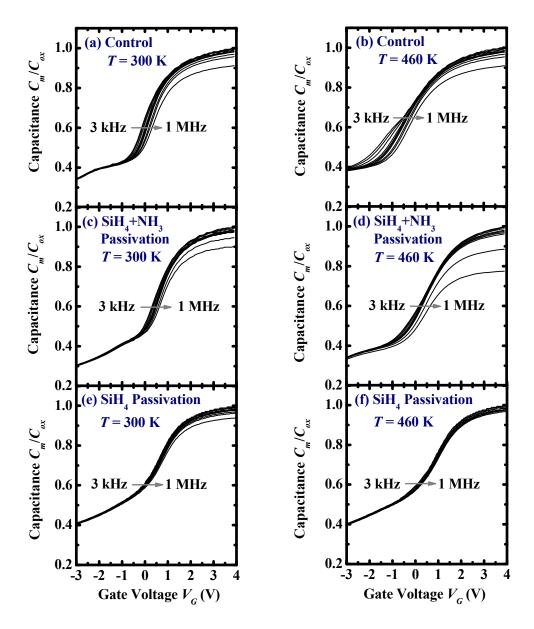

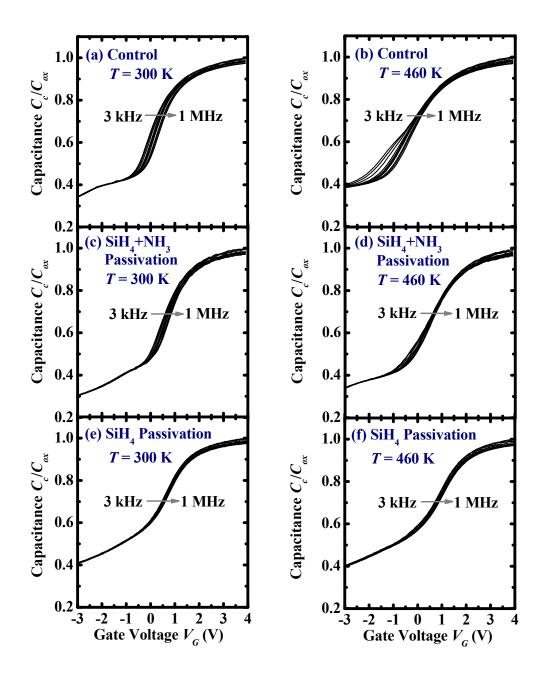

- Fig. 2.10. Measured normalized capacitance-gate voltage curves  $(C_m/C_{ox}$  versus  $V_G$ ) of the control sample obtained at characterization temperatures of (a) 300 K and (b) 460 K. The control did not undergo any vacuum anneal or surface treatment.  $C_m/C_{ox}$  versus  $V_G$  curves of samples which received *in situ* 300 °C vacuum anneal and 400 °C SiH<sub>4</sub>+NH<sub>3</sub> treatment, and characterized at (c) 300 K and (d) 460 K. Similar measurements at (e) 300 K and (f) 460 K were performed for samples which received *in situ* 300 °C vacuum anneal and 400 °C SiH<sub>4</sub> treatment. For each plot, ten characterization frequencies (3, 5, 10, 30, 50, 70, 100, 300, 500, and 1000 kHz) were used.

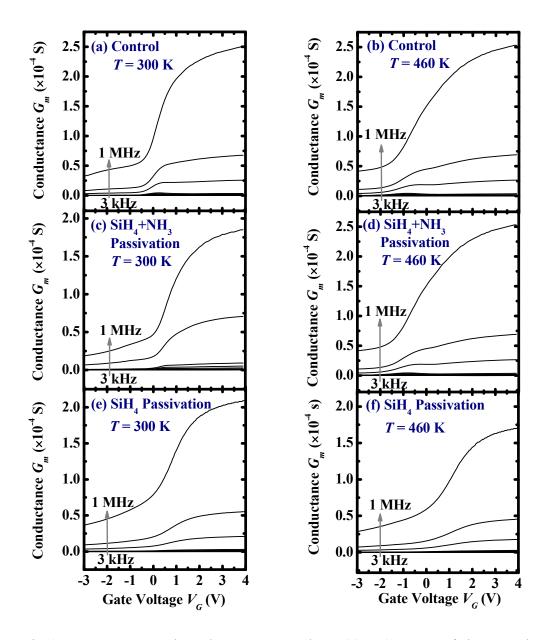

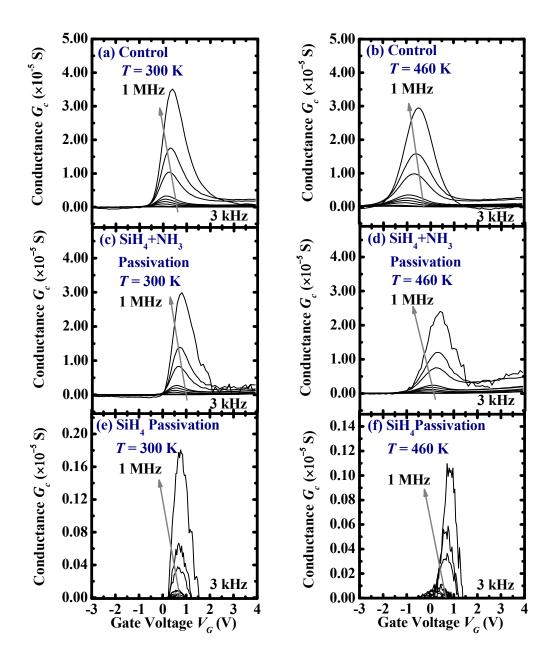

- Fig. 2.11. Measured conductance-gate voltage  $(G_m V_G)$  curves of the control sample at characterization temperatures of (a) 300 K and (b) 460 K.  $G_m V_G$  curves of samples which received *in situ* 300 °C vacuum anneal and 400 °C SiH<sub>4</sub>+NH<sub>3</sub> treatment, characterized at (c) 300 K and (d) 460 K. Similar measurements at (e) 300 K and (f) 400 K were performed for samples which received *in situ* 300 °C vacuum anneal and 400 °C SiH<sub>4</sub> treatment. For each plot, ten characterization frequencies (3, 5, 10, 30, 50, 70, 100, 300, 500, and 1000 kHz) were used. .......40

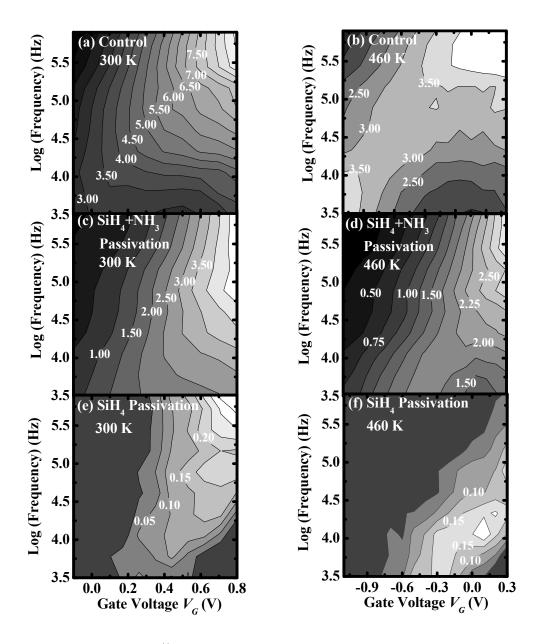

- Fig. 2.14.  $G_p(\times 10^{-11})/\omega$  contours as a function of frequency (log scale) and gate voltage  $V_G$  for the control sample at characterization temperatures of (a) 300 K and (b) 460 K.  $G_p(\times 10^{-11})/\omega$  contours as a function of frequency (log scale) and gate voltage  $V_G$  for samples which received *in situ* 300 °C vacuum anneal and 400 °C SiH<sub>4</sub>+NH<sub>3</sub> treatment at characterization temperatures of (c)

300 K and (d) 460 K. Similarly,  $G_p(\times 10^{-11})/\omega$  contours as a function of frequency (log scale) and gate voltage  $V_G$  for samples which received *in situ* 300 °C vacuum anneal and 400 °C SiH<sub>4</sub> treatment at characterization temperatures of (e) 300 K and (f) 460 K. .....44

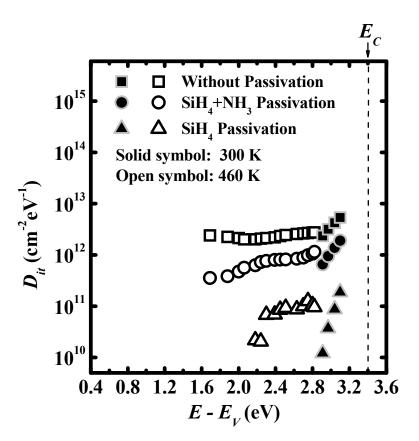

- Fig. 2.15. Interface state density  $D_{it}$  from near  $E_C$  to mid-gap for the control sample, sample with *in situ* 300 °C vacuum anneal and 400 °C SiH<sub>4</sub>+NH<sub>3</sub> treatment, and sample with *in situ* 300 °C vacuum anneal and 400 °C SiH<sub>4</sub> treatment, extracted using the conductance method at 300 K and 460 K with series resistance correction. 46

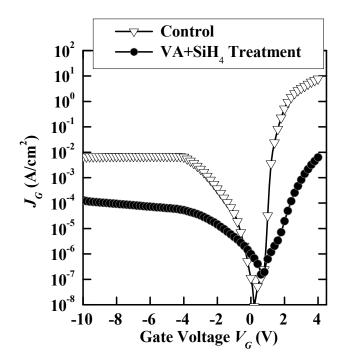

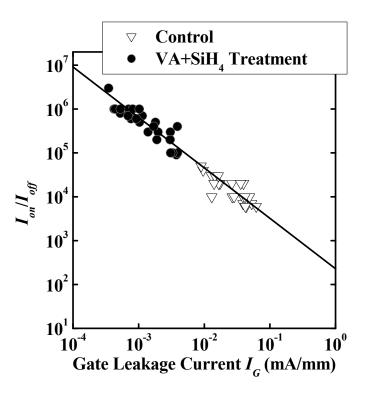

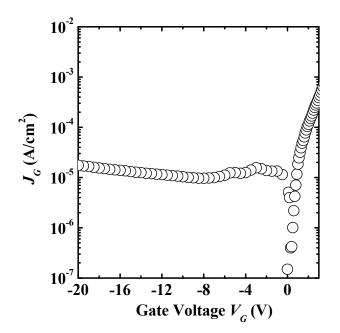

- Fig. 3.7. Gate leakage current density  $J_G$  as a function of gate voltage  $V_G$  of the AlGaN/GaN MOS-HEMTs with and without *in situ* VA and SiH<sub>4</sub> treatment.  $J_G$  of the device with *in situ* VA and SiH<sub>4</sub> treatment is suppressed by ~ 3 orders of magnitude at  $V_G = 4$  V.

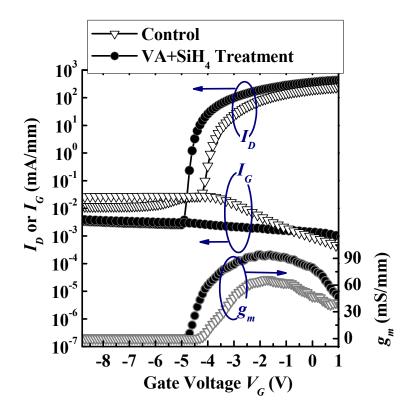

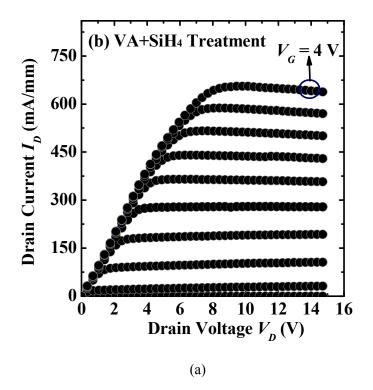

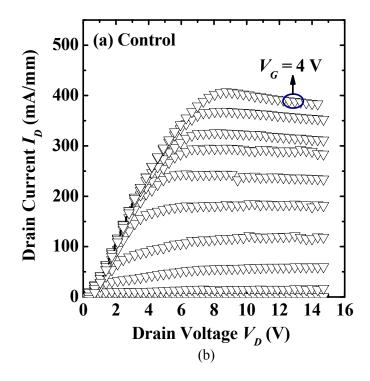

- Fig. 3.9. Drain current  $(I_D-V_G)$ , gate leakage current  $(I_G-V_G)$ , and extrinsic transconductance  $(g_m-V_G)$  as a function of gate voltage  $V_G$  of the AlGaN/GaN MOS-HEMTs with and without *in situ* VA and SiH<sub>4</sub> treatment at  $V_D = 5$  V.....60

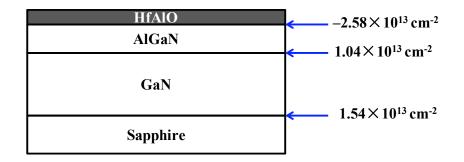

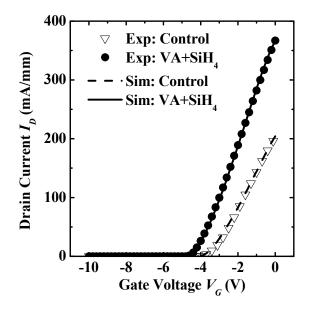

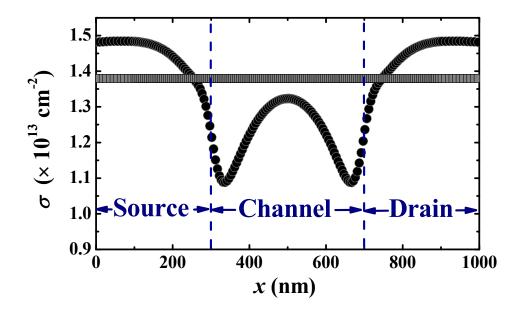

- Fig. 3.10: Polarization charge used in the simulation at HfAlO/AlGaN, AlGaN/GaN, and GaN/Sapphire interfaces are  $-2.58 \times 10^{13}$ ,  $1.04 \times 10^{13}$ , and  $1.54 \times 10^{13}$  cm<sup>-2</sup>, respectively.......62

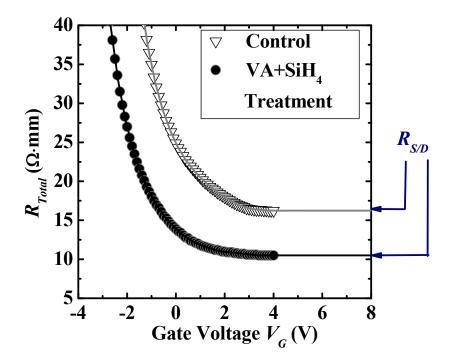

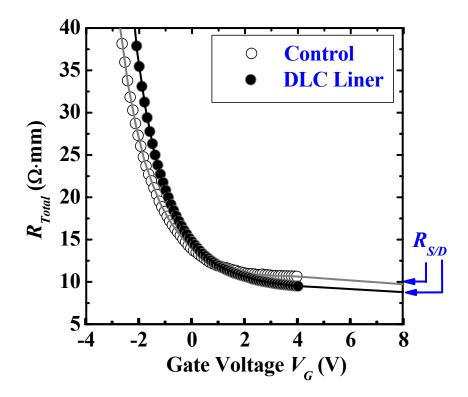

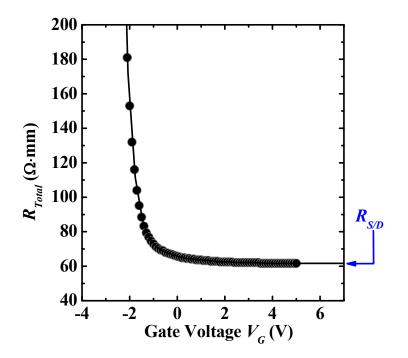

- Fig. 3.12. Total resistance  $R_{Total}$  as a function of gate voltage  $V_G$  when the drain voltage was fixed at 1 V. Parasitic S/D series resistance  $R_{S/D}$  for the devices with and without *in situ* VA and SiH<sub>4</sub> treatment shown in Fig. 3.9 is 10.4 and 16.2  $\Omega$ ·mm, respectively.

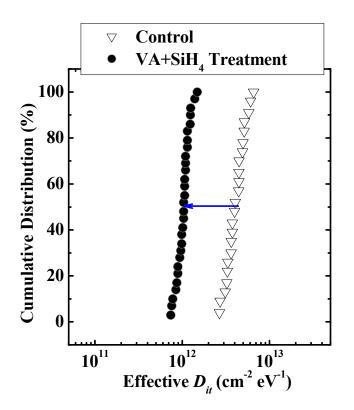

- Fig. 3.16. Cumulative distribution plot of effective  $D_{it}$  for the AlGaN/GaN MOS-HEMTs with and without *in situ* VA and SiH<sub>4</sub> treatment. The number of the measured devices with and without *in situ* VA and SiH<sub>4</sub> treatment are 29 and 23, respectively. With *in situ* VA

and SiH<sub>4</sub> treatment, the median value of effective  $D_{it}$  was reduced from  $4.2 \times 10^{12}$  to  $1.1 \times 10^{12}$  cm<sup>-2</sup> eV<sup>-1</sup>.....69

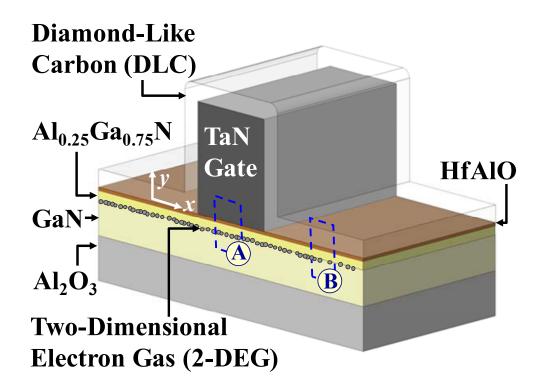

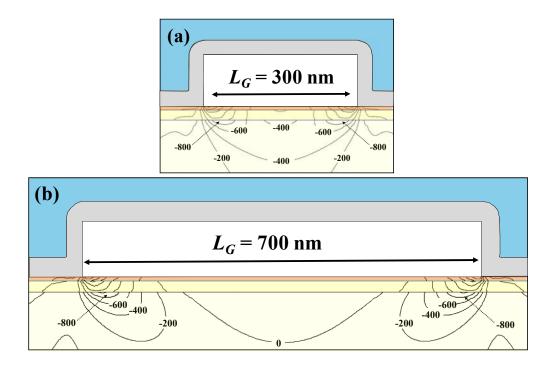

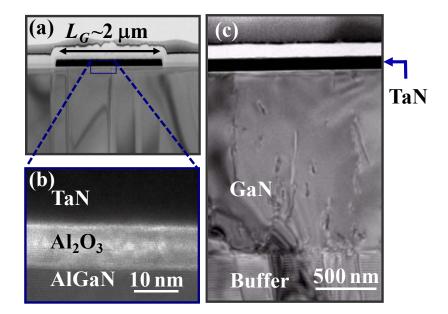

- Fig. 4.1. Schematic diagram of the AlGaN/GaN MOS-HEMT encapsulated by a diamond-like carbon (DLC) liner with highly compressive stress. The thicknesses of the DLC Layer, HfAlO layer, and AlGaN barrier layer are 40 nm, 7 nm, and 20 nm, respectively. TEM image were taken in regions of A and B, and shown in Fig. 4.7.

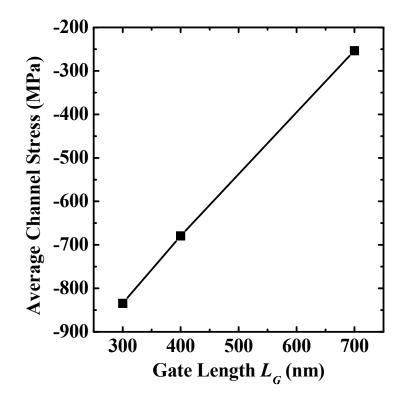

- Fig. 4.5. Average channel stress in the 2-DEG due to a 40 nm thick DLC liner was simulated for various gate lengths (300, 400, and 700 nm). Stress magnitude increases with decreasing gate length..80

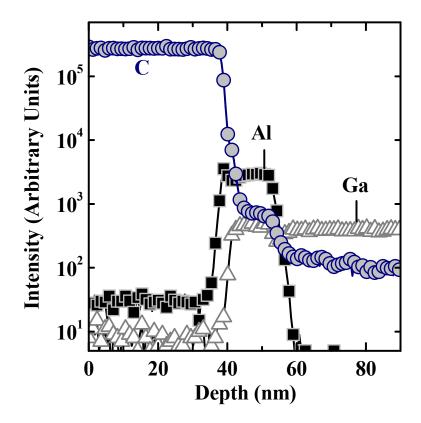

- Fig. 4.8. Elemental profiles of C, Al, and Ga in the DLC/AlGaN/GaN stack was obtained using secondary ion mass spectrometry (SIMS). The region with a high C concentration is the DLC liner.

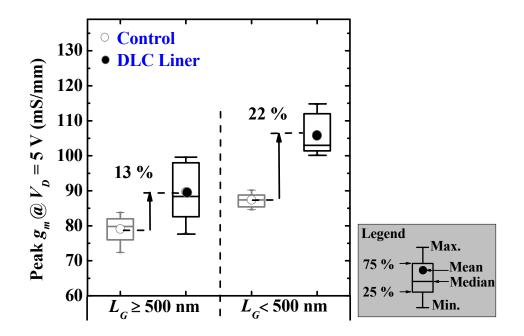

- Fig. 4.15. The extrinsic peak transconductance  $g_{m,max}$  of the AlGaN/GaN MOS-HEMTs with the DLC liner shows enhancement over the control devices at  $V_D = 5$  V. The extrinsic peak transconductance enhancement is larger for the devices with  $L_G$  less than 500 nm than that of the devices with  $L_G$  more than 500 nm. The device length here varies from 300 to 1000 nm. .......94

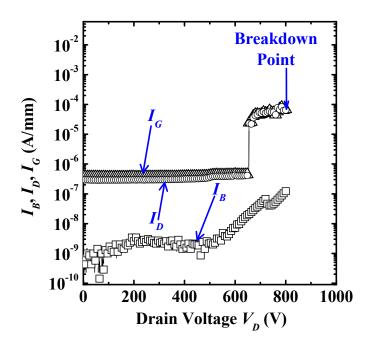

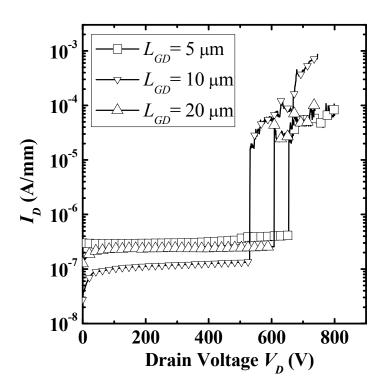

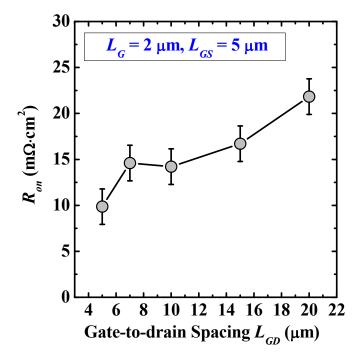

- Fig. 5.7 Drain current  $I_D$  was plotted as a function of drain voltage  $V_D$  during the four-terminal off-state measurement in the Fluorinert ambient, where  $V_S = V_B = 0$  V and  $V_G = -12$  V. Devices have a gate length  $L_G$  of 2 µm,  $L_{GS}$  of 5 µm, and various  $L_{GD}$ ......107

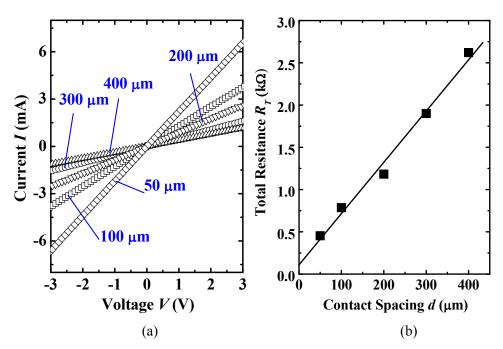

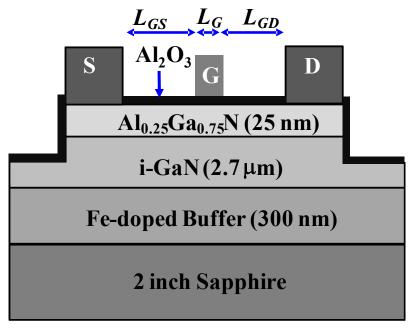

- Fig. 5.9. (a) Current-voltage (*I-V*) characteristics and (b) total resistance  $R_T$  as a function of contact spacing *d* for the TLM test structure, fabricated on the same die as the AlGaN/GaN-on-sapphire MOS-HEMTs, after an annealing step at 650 °C for 30 s in N<sub>2</sub> ambient.

- Fig. 5.10. Gate leakage current density  $J_G$  as a function of gate voltage  $V_G$  of the fabricated AlGaN/GaN MOS-HEMTs, when both source and drain were grounded. In the negative gate voltage regime,  $J_G$  is below ~ 2 × 10<sup>-5</sup> A/cm<sup>2</sup> for  $V_G$  as negative as -20 V.......112

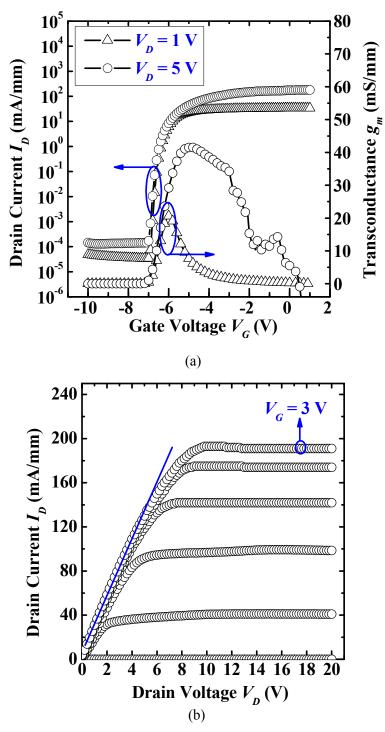

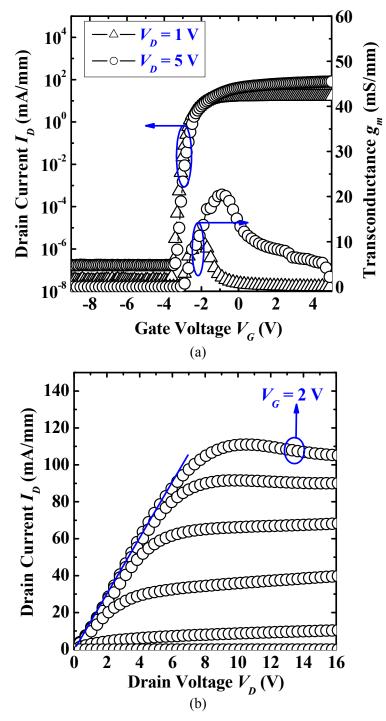

- Fig. 5.11. (a)  $I_D$ - $V_G$  and  $g_m$ - $V_G$  characteristics of the AlGaN/GaN-onsapphire MOS-HEMT ( $L_G = 2 \ \mu m$  and  $L_{GS} = L_{GD} = 5 \ \mu m$ ). (b)

Output  $(I_D - V_D)$  characteristics of the AlGaN/GaN-on-sapphire MOS-HEMT, where  $V_G$  is varied in steps of 1 V from -3 to 2 V.

| l | 13 | 3 |

|---|----|---|

|   |    |   |

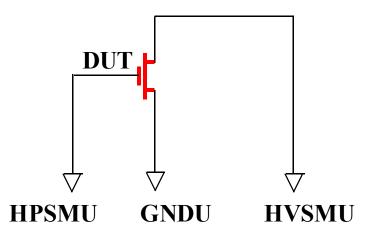

- Fig. 5.15 During the high voltage measurement by Agilent B1505A, the gate of DUT is biased below threshold voltage using high power (HP) SMU, source is connected to the ground unit (GNDU), and drain is connect to the high voltage (HV) SMU. The device is kept in the Fluorinert ambient. (DUT: device under test.) .....118

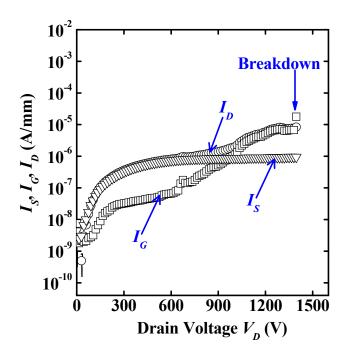

- Fig. 5.16. Source current  $I_S$ , gate current  $I_G$ , and drain current  $I_D$  as a function of drain voltage  $V_D$  for the high voltage off-state measurement in a Fluorinert ambient of the AlGaN/GaN MOS-HEMT ( $L_G = 2 \ \mu m$ ,  $L_{GS} = 5 \ \mu m$ , and  $L_{GD} = 20 \ \mu m$ ), where  $V_S = 0$  V and  $V_G = -10$  V. The drain current  $I_D$  is below 1 mA/mm when  $V_D = 1400$  V.

| Symbol                            | Description                           | Unit                               |

|-----------------------------------|---------------------------------------|------------------------------------|

| $E_G$                             | Bandgap                               | eV                                 |

| E <sub>r</sub>                    | Dielectric constant                   |                                    |

| ξbr                               | Breakdown field                       | MV/cm                              |

| $v_p$                             | High-field peak electron velocity     | cm/s                               |

| $\mu_n$                           | Electron mobility                     | $cm^2/V \cdot s$                   |

| K                                 | Thermal conductivity                  | WK <sup>-1</sup> cm <sup>-1</sup>  |

| $P_{PE}$                          | Piezoelectric polarization charge     | $C/m^2$                            |

| $P_{SP}$                          | Spontaneous polarization charge       | $C/m^2$                            |

| $\sigma$                          | Polarization charge density           | C/m <sup>2</sup>                   |

| $e_{31,}e_{33}$                   | Piezoelectric constant                | $C/m^2$                            |

| C <sub>13</sub> , C <sub>33</sub> | Elastic constant                      | GPa                                |

| а                                 | Lattice constant                      | Å                                  |

| $n_s$                             | Density of 2-dimensional electron gas | cm <sup>-2</sup>                   |

| d                                 | Thickness of the AlGaN barrier layer  | nm                                 |

| q                                 | Electronic charge                     | С                                  |

| $\phi_b$                          | Schottky barrier height               | V                                  |

| $E_F$                             | Fermi level                           | eV                                 |

| $\Delta Ec$                       | Conduction band offset                | eV                                 |

| $V_{BR}$                          | Breakdown voltage                     | V                                  |

| Ron                               | On-state resistance                   | $\Omega \cdot cm^2$                |

| ζρ                                | Vertical polarization field           | V/cm                               |

| Sbr,AlGaN                         | Breakdown field of the AlGaN layer    | MV/cm                              |

| $L_{GD}$                          | Gate-to-drain spacing                 | μm                                 |

| $J_G$                             | Gate leakage current density          | A/cm <sup>2</sup>                  |

| $D_{it}$                          | Interface state density               | $\mathrm{cm}^{-2}\mathrm{eV}^{-1}$ |

| $V_{th}$                          | Threshold voltage                     | V                                  |

| S                                 | Sub-threshold swing                   | mV/decade                          |

| $I_G$                             | Gate leakage current                  | A/mm                               |

| $\Delta V_{FB}$                   | Flatband voltage shift                | V                                  |

| С                                 | Capacitance                           | F                                  |

| $E_C$                             | Conduction band edge                  | eV                                 |

| $E_V$                             | Valence band edge                     | eV                                 |

| G                                 | Conductance                           | S                                  |

# List of Symbols

| $	au_e$            | Characteristic emission time                   | S                 |

|--------------------|------------------------------------------------|-------------------|

| $E_t$              | Trap energy                                    | eV                |

| k                  | Boltzmann constant                             | eVK <sup>-1</sup> |

| Т                  | Temperature                                    | K                 |

| $v_{th}$           | Thermal velocity                               | cm/s              |

| N                  | Density of states in the majority carrier band | cm <sup>-2</sup>  |

| $\sigma_{cro}$     | Capture cross section of the trap state        | $cm^2$            |

| fres               | Characteristic response frequency              | Hz                |

| $C_{ox}$           | Gate oxide capacitance                         | F                 |

| $C_d$              | Depletion capacitance                          | F                 |

| $C_{it}$           | Capacitance of interface states                | F                 |

| $R_{it}$           | Resistance of interface states                 | Ω                 |

| $G_m$              | Measured conductance                           | S                 |

| $C_m$              | Measured capacitance                           | F                 |

| R <sub>ser</sub>   | Series resistance                              | Ω                 |

| $C_{ma}$           | Measured accumulation capacitance              | F                 |

| $G_{ma}$           | Measured accumulation conductance              | S                 |

| $G_c$              | Corrected conductance                          | S                 |

| $C_c$              | Corrected capacitance                          | F                 |

| f                  | Measurement frequency                          | Hz                |

| $C_p$              | Parallel capacitance                           | F                 |

| $R_p$              | Parallel resistance                            | Ω                 |

| $G_p$              | Parallel conductance                           | S                 |

| $L_{GS}$           | Gate-to-drain spacing                          | μm                |

| $L_G$              | Gate length                                    | μm                |

| $I_{off}$          | Off-state current (per unit width)             | A/mm              |

| Ion                | On-state current (per unit width)              | A/mm              |

| $g_m$              | transconductance                               | S                 |

| $V_D$              | Drain voltage                                  | V                 |

| $g_m$              | Measured extrinsic transconductance            | S                 |

| $g_{m,i}$          | Intrinsic transconductance                     | S                 |

| g <sub>m,max</sub> | Measured extrinsic peak transconductance       | S                 |

| $g_{m,i,max}$      | Intrinsic peak transconductance                | S                 |

| Rs                 | Parasitic source resistance                    | Ω·mm              |

| $R_{S/D}$          | Parasitic source/drain series resistance       | Ω·mm              |

| $R_{Channel}$      | Channel resistance                             | Ω·mm              |

| $\sigma_{xx}$      | Lateral stress                                 | GPa               |

| $t_1$    | AlGaN barrier layer thickness | nm                  |

|----------|-------------------------------|---------------------|

| $t_2$    | Gate oxide thickness          | nm                  |

| d        | Contact spacing               | μm                  |

| $R_{sh}$ | Sheet resistance              | $\Omega$ /square    |

| $ ho_c$  | Specific contact resistivity  | $\Omega \cdot cm^2$ |

## List of Abbreviations

| Abbreviation     | Description                                       |  |  |  |

|------------------|---------------------------------------------------|--|--|--|

| BFOM             | Baliga's figure of merit                          |  |  |  |

| 2-DEG            | Two-dimensional electron gas                      |  |  |  |

| HEMTs            | High-electron-mobility tansistors                 |  |  |  |

| IT               | Information technology                            |  |  |  |

| PV               | Photovoltaic                                      |  |  |  |

| EV               | Electric Vehicles                                 |  |  |  |

| HEV              | Hybrid electric vehicles                          |  |  |  |

| MOS              | Metal-oxide-semiconductor                         |  |  |  |

| MOSFET           | Metal-oxide-semiconductor field-effect transistor |  |  |  |

| CMOS             | Complementary metal-oxide-semiconductor           |  |  |  |

| MOCVD            | Metal-organic chemical vapor deposition           |  |  |  |

| $I_{on}/I_{off}$ | Current on/off ratio                              |  |  |  |

| JVD              | Jet vapor deposition                              |  |  |  |

| BCB              | Benzocyclobutene                                  |  |  |  |

| PDA              | Post-deposition anneal                            |  |  |  |

| XPS              | X-ray photoelectron spectroscopy                  |  |  |  |

| TEM              | Transmission electron microscopy                  |  |  |  |

| C-V              | Capacitance-voltage                               |  |  |  |

| PM 1             | Process module 1                                  |  |  |  |

| PM 2             | Process module 2                                  |  |  |  |

| PM 3             | Process module 3                                  |  |  |  |

## **Chapter 1**

### Introduction

### 1.1 Overview of Gallium Nitride

#### **1.1.1 Gallium Nitride Material and Potential Applications**

Over the past three decades, enormous progress has been made on the development of gallium nitride (GaN) and its family of alloys (InAlGaN) for both electronic and optoelectronic applications [1]-[3]. GaN possesses a large bandgap of 3.4 eV, a very high breakdown field of  $3.3 \times 10^6$  V/cm, an extremely high-field peak electron velocity ( $3 \times 10^7$  cm/s) and saturation electron velocity ( $1.5 \times 10^7$  cm/s) [4]. These GaN properties together with the combination of a large conduction band offset and a high electron mobility of the AlGaN/GaN heterostructure, make the GaN-based transistor an excellent candidate for the application in electronic devices operating at high temperature, high power, and high frequency [5]-[6], even in a harsh environment, due to the chemical inertness of GaN [7].

Silicon has long been the dominant semiconductor for power devices. However, the electrical performance of silicon-based devices is approaching the theoretical limit. As a result, wide bandgap materials, such as GaN, have attracted significant attention, because they offer numerous advantages over other materials. To further describe the advantages of GaN in high temperature and high power electronic devices, the material properties of GaN and its competing materials are presented in Table 1.1 [5]. As shown in

| Material                                                            | Si   | GaAs | 4H-SiC | GaN  |

|---------------------------------------------------------------------|------|------|--------|------|

| Bandgap $E_G$ (eV)                                                  | 1.12 | 1.42 | 3.2    | 3.4  |

| Dielectric Constant $\varepsilon_r$                                 | 11.9 | 12.5 | 10     | 9.5  |

| Breakdown Field $\xi_{br}$ (MV/cm)                                  | 0.3  | 0.4  | 3.0    | 3.3  |

| High-field Peak Electron<br>Velocity $v_p$ (× 10 <sup>7</sup> cm/s) | 1.0  | 2.0  | 2.0    | 3.0  |

| Electron Moblity $\mu_n$<br>(cm <sup>2</sup> /V·s)                  | 1300 | 5000 | 260    | 1500 |

| Thermal Conductivity $K$ (WK <sup>-1</sup> cm <sup>-1</sup> )       | 1.5  | 0.5  | 4.9    | 1.3  |

| BFOM Ratio                                                          | 1.0  | 9.6  | 3.1    | 24.6 |

Table 1.1. Comparison of material properties of Si, GaAs, 4H-SiC, and GaN at 300 K. BFOM is Baliga's figure of merit for power transistor performance  $(\mu_n.\varepsilon_r.E_G^3)$ , and the benchmark is Si [5].

Table 1.1, the value of the Baliga's figure of merit (BFOM) for GaN normalized to that of Si is higher than those of all the other materials. For the high power and high voltage power devices, large bandgap  $E_G$ , high breakdown field  $\zeta_{br}$ , high thermal conductivity K, and high electron mobility  $\mu_n$  are essential requirements. As compared with other materials, GaN has a larger  $E_G$  and a higher  $\zeta_{br}$ , which means that GaN-based transistors can achieve a higher breakdown voltage for high-voltage switching devices. The highfield peak electron velocity  $v_p$  and high electron mobility  $\mu_n$  of the twodimensional electron gas (2-DEG) in AlGaN/GaN heterostructures allow the AlGaN/GaN high-electron-mobility transistors (HEMTs) to have a low onstate resistance and to operate at high switching frequencies. The large polarization charge in the GaN-based materials can lead to a high output current for AlGaN/GaN or InAlN/GaN HEMTs, thus making GaN-based HEMTs very promising candidates for high power devices. The large  $E_G$  and thus low intrinsic carrier concentration, together with the intermediate thermal conductivity, all benefit to the high temperature operation of GaN transistors.

Fig. 1.1 illustrates the potential applications of GaN-based power devices. There are three major categories, in which GaN-based devices can compete with the existing or new technologies [6], [8]. In the lower supply voltage range, such as information technology (IT) and consumer electronics, traditional silicon devices currently take almost all the markets due to their low cost and good reliability. GaN market players in the low voltage range, such as International Rectifier and Efficient Power Conversion, are bringing their GaN products into this market (source: http://www.irf.com/ and http://www.epc-co.com/). In the high supply voltage range, such as motor drives and the power inverters for photovoltaic (PV) cell or uninterruptible power supplies (UPS), GaN-based devices can compete with both Si and SiC

**Supply Voltage Range**

Potential applications for GaN-based power devices. Based on the Fig. 1.1. supply voltage range, the applications are divided into three categories: IT and consumer electronics, automotive, and industry [8].

devices, which have already been commercially adopted. Recently (July 2012), a 600 V GaN power diode was announced by Transphorm Inc. for application in PV panels and electric vehicles (EV) or hybrid electric vehicles (HEV) (source: http://www.transphormusa.com/).

As shown in Fig. 1.2, GaN belongs to a group of nitride materials, such as indium gallium nitride (InGaN) and aluminum gallium nitride (AlGaN), which covers a broad range of the direct bandgap energy from 1.9 to 6.2 eV [2]-[3]. With the development of GaN-based heterostructure growth, the advantages of GaN-based devices are being further exploited. A brief review of the polarization charge in AlGaN/GaN heterostructure is given in Section 1.1.2.

Fig. 1.2. Bandgap  $E_G$  of hexagonal ( $\alpha$ -phase) and cubic ( $\beta$ -phase) InN, GaN, AlN, and their alloys versus lattice constant a [3].

#### 1.1.2 AlGaN/GaN Heterostructure: Polarization Charge

The AlGaN/GaN heterostructure offers a high density of 2-DEG (~ 1 ×  $10^{13}$  cm<sup>-2</sup>), due to its large spontaneous and piezoelectric polarization [9]-[10]. In addition, electron mobility of more than 2000 cm<sup>2</sup>/V·s in the 2-DEG has been achieved [9]. Typically AlGaN/GaN HEMTs use the Ga-polarity face. Fig. 1.3 (a) shows the crystal structure of wurtzite GaN with the Ga-polarity face. Due to the smaller lattice constant as compared to GaN, the AlGaN barrier layer is under tensile strain if there is no strain relaxation. Usually, the GaN layer under the AlGaN barrier layer is assumed to be relaxed, since the thickness of the GaN layer is usually several micrometers, whereas the thickness of the AlGaN barrier layer is in the order of tens of nanometers. Directions of the spontaneous (*P*<sub>SP</sub>) and piezoelectric (*P*<sub>PE</sub>) polarization for wurtzite AlGaN/GaN heterostructure with the Ga-polarity face are labeled in Fig. 1.3 (b). Polarization charge density  $\sigma$  for an abrupt pseudomorphic

Fig. 1.3. (a) Schematic drawing of the crystal structure of wurtzite GaN with the Ga-polarity face. (b) Directions of the spontaneous  $(P_{SP})$  and piezoelectric  $(P_{PE})$  polarization for wurtzite AlGaN/GaN heterostructure with the Ga-polarity face are labeled [9].

AlGaN/GaN heterostructure can be expressed as [10]:

$$\sigma = P(AlGaN) - P(GaN)$$

$$= \{P_{SP}(AlGaN) + P_{PE}(AlGaN)\} - \{P_{SP}(GaN)\}.$$

(1.1)

To calculate the dependence of polarization charge density  $\sigma$  on the Al content x of the Al<sub>x</sub>Ga<sub>1-x</sub>N barrier layer, the equations for  $P_{SP}$  and  $P_{PE}$  of the Al<sub>x</sub>Ga<sub>1-</sub> <sub>x</sub>N barrier layer are given by [10]:

$$P_{SP}(Al_xGa_{1-x}N) = (-0.052x - 0.029) \text{ C/m}^2,$$

(1.2)

$$P_{PE}(Al_xGa_{1-x}N) = 2\frac{a-a_0}{a_0}(e_{31}-e_{33}\frac{C_{13}}{C_{33}}) C/m^2, \qquad (1.3)$$

where *a* is the lattice constant of the  $Al_xGa_{1-x}N$  barrier layer,  $a_0$  is the equilibrium value of the lattice constant of GaN,  $C_{13}$  and  $C_{33}$  are the elastic constants, and  $e_{31}$  and  $e_{33}$  are piezoelectric constants. With a linear interpolation between the physical properties of GaN and AlN, the lattice constant of the  $Al_xGa_{1-x}N$  barrier layer is given by [10]:

$$a(x) = (-0.077x + 3.189)10^{-10} \,\mathrm{m},$$

(1.4)

the elastic constants of the  $Al_xGa_{1-x}N$  barrier layer are:

$$C_{13}(x) = (5x + 103) \text{ GPa}, \tag{1.5}$$

$$C_{33}(x) = (-32x + 405) \text{ GPa},$$

(1.6)

the piezoelectric constants of the  $Al_xGa_{1-x}N$  barrier layer are:

$$e_{31}(x) = (-0.11x - 0.49) \text{ C/cm}^2,$$

(1.7)

$$e_{33}(x) = (0.73x + 0.73) \text{ C/cm}^2.$$

(1.8)

Based on Equations (1.1)-(1.3), the amount of polarization charge density  $\sigma$  for the Al<sub>x</sub>Ga<sub>1-x</sub>N/GaN heterostructure can be expressed as [10]:

$$|\sigma(x)| = |P_{SP}(Al_xGa_{1-x}N) + P_{PE}(Al_xGa_{1-x}N) - P_{SP}(GaN)|$$

$$= \left| 2 \frac{a(0) - a(x)}{a(x)} (e_{31} - e_{33} \frac{C_{13}}{C_{33}}) + P_{SP}(x) - P_{SP}(x) \right|. (1.9)$$

Due to the positive polarization charges at the Al<sub>x</sub>Ga<sub>1-x</sub>N/GaN interface, the free electrons tend to compensate at the AlGaN/GaN interface, and form 2-DEG. The density of 2-DEG  $n_s$  can be estimated using [10]

$$n_s(x) = \frac{+\sigma(x)}{q} - \left(\frac{\varepsilon_0 \varepsilon_r(x)}{t_1 q^2}\right) [q \phi_b(x) + E_F(x) - \Delta E_C(x)], \quad (1.10)$$

where  $t_1$  is thickness of the Al<sub>x</sub>Ga<sub>1-x</sub>N barrier layer,  $\varepsilon_r$  is the dielectric constant of the Al<sub>x</sub>Ga<sub>1-x</sub>N barrier layer, q is the electronic charge,  $\phi_b$  is the Schottky-barrier height,  $E_F$  is the Fermi level with respect to the GaN

Fig. 1.4. The calculated density of 2-DEG  $n_s$  of pseudomorphic AlGaN/GaN heterosture as a function of Al content *x* of the Al<sub>x</sub>Ga<sub>1-x</sub>N barrier layer [10].

conduction band edge energy, and  $\Delta E_c$  is the conduction band offset at the Al<sub>x</sub>Ga<sub>1-x</sub>N/GaN interface. Fig. 1.4 plots the calculated  $n_s$  of pseudomorphic AlGaN/GaN heterostructure as a function of Al content x of the Al<sub>x</sub>Ga<sub>1-x</sub>N barrier layer [10].

#### 1.2 Literature Review of High Voltage AlGaN/GaN HEMTs

For the AlGaN/GaN HEMTs in high voltage applications, high breakdown voltage  $V_{BR}$  and low on-state resistance  $R_{on}$  are two of the most important requirements. For a vertical device with a uniform doping profile, if low on-state resistance  $R_{on}$  is desired, the device doping level should be increased. However, breakdown voltage  $V_{BR}$  decreases with increasing doping level. For the lateral AlGaN/GaN HEMTs during the off-state, it is assumed that the electric field in the depletion region under the gate is a combination of a vertical polarization field  $\xi_P$  and a constant lateral electric field due to the drain bias (assuming the gate-to-drain is fully depleted), the relationship between on-state resistance  $R_{on}$  and breakdown voltage  $V_{BR}$  can be expressed as [11]:

$$R_{on} = \frac{V_{BR}^2}{q\mu_n n_s \xi_C^{,2}}, \text{ and } \xi_C^{,2} = \xi_{br,AlGaN}^2 - \xi_P^2, \qquad (1.11)$$

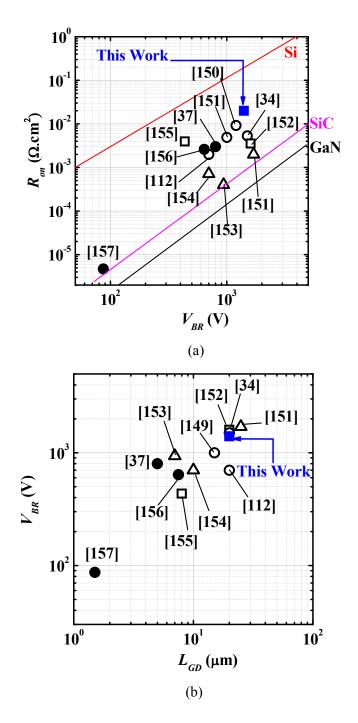

where *q* is the electronic charge and  $\xi_{br,AlGaN}$  is the breakdown field of the AlGaN barrier layer. Fig. 1.5 shows the theoretical limit of on-state resistance  $R_{on}$  as a function of breakdown voltage  $V_{BR}$  for GaN, SiC, and Si. With a given breakdown voltage, for example, 1000 V, GaN-based devices can offer an on-state resistance  $R_{on}$  of 2 ~ 3 orders of magnitude lower than that of Si.

Fig. 1.5. Theoretical limit of the on-state resistance  $R_{on}$  as a function of breakdown voltage  $V_{BR}$  for GaN, SiC, and Si devices [11].

Since the first demonstration of AlGaN/GaN HEMTs on sapphire substrate by Khan *et al.* [12] in 1993, tremendous progress has been made for AlGaN/GaN HEMTs on sapphire, SiC, or silicon substrates [13]-[14]. Preliminary work on high voltage AlGaN/GaN HEMTs was done by Zhang *et al.* [15]. The breakdown mechanism of AlGaN/GaN HEMTs is due to an avalanche process that usually occurs near the gate edge of the drain side. It is generally accepted that the essence of achieving a high breakdown voltage  $V_{BR}$ in AlGaN/GaN HEMTs is to have an increased depletion width from the drain to the gate or to decrease the peak electrical field near the gate edge of the drain side. It is worth noting that a highly resistive buffer is essential to achieve AlGaN/GaN HEMTs with a high breakdown voltage  $V_{BR}$ . Technologies of increasing the breakdown voltage  $V_{BR}$  of AlGaN/GaN HEMTs can be divided into two categories: (1) GaN buffer growth technology and (2) device design technology. The purpose of GaN buffer growth technology is to reduce the buffer leakage current and avoid the vertical breakdown by using various methods, such as C-doped [16] or Fe-doped buffer [17], thick GaN buffer [18]-[19], AlN buffer [20], AlGaN-based buffer [21], multi-pairs of alternate AlN/GaN layer buffer [22], etc. Buffer layer growth technologies are mainly developed by the GaN epitaxial growth groups. On the other side, there are many innovative designs from device groups to reduce the peak electrical field near the gate edge of the drain side, such as field plate structure [15], trench gate structure [23], etc.

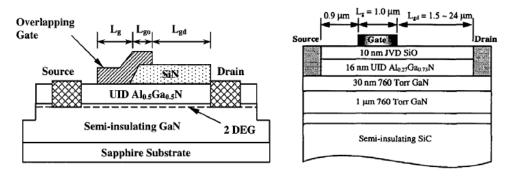

For the conventional AlGaN/GaN HEMTs with a Schottky gate structure, breakdown voltage  $V_{BR}$  of 460 V was achieved by Zhang *et al.* [15] for devices with a gate-to-drain spacing  $L_{GD}$  of 20 µm. With an integration of an overlapping gate structure on the AlGaN/GaN HEMTs, the breakdown voltage V<sub>BR</sub> of devices was increased to 570 V by Zhang et al. [15] [Fig. 1.6 (a)]. Enhancement of breakdown voltage  $V_{BR}$  was due to the reduction of the peak electrical field near the gate edge of the drain side, since it can locally cause the impact ionization near the drain side of the gate structure and increase the gate leakage current. To further reduce the gate leakage current, AlGaN/GaN HEMTs with an insulated gate structure were demonstrated by Zhang *et al.* [24] using jet vapor deposition (JVD) SiO<sub>2</sub> as the gate dielectric, and achieved a breakdown voltage  $V_{BR}$  of 1300 V and an on-state resistance  $R_{on}$  of 1.7 m $\Omega$ ·cm<sup>2</sup> for the devices with a gate-to-drain spacing  $L_{GD}$  of 20  $\mu$ m [Fig. 1.6 (b)]. Later, Xing et al. [25] demonstrated the conventional AlGaN/GaN HEMTs with a breakdown voltage  $V_{BR}$  up to 900 V using multiple field plates over insulators [Fig. 1.6 (c)]. With a modification of the

(a)

(b)

Fig. 1.6. Schematic diagrams of epitaxial layers and cross sections of (a) AlGaN/GaN HEMT with an overlapping gate [15], (b) insulated gate AlGaN/GaN HEMT with JVD deposited SiO<sub>2</sub> gate dielectric [24], (c) AlGaN/GaN HEMT with discrete multiple field plates [25], and (d) AlGaN/GaN HEMT with a trench gate [23].

gate shape for conventional AlGaN/GaN HEMTs, Dora *et al.* [23] achieved a breakdown voltage  $V_{BR}$  of 1900 V and an on-state resistance  $R_{on}$  of 2 m $\Omega$ ·cm<sup>2</sup> for the devices with a gate-to-drain spacing  $L_{GD}$  of 20 µm by introducing a trench gate structure [Fig. 1.6 (d)].

Most of the early work done on high voltage AlGaN/GaN HEMTs employed sapphire or SiC substrates. Single crystalline GaN was first realized on sapphire using vapor phase deposition by Marusha *et al.* [26] in 1969. Since then, GaN-on-sapphire growth technique has become more mature, due to the demand of GaN-based optical devices [27]. As for the GaN-on-SiC wafers, there are two main advantages. The first is that it is much easier to grow semi-insulating GaN layers on SiC (3.3 % lattice mismatch) than on sapphire substrate (14 % lattice mismatch), and the other reason is that SiC has a high thermal conductivity K (4.9 WK<sup>-1</sup>cm<sup>-1</sup>), which is highly desired for high power AlGaN/GaN HEMTs [28]. However, the high cost of SiC substrates makes it difficult for commercial application in the cost sensitive consumer electronics sector. Although there is a large lattice mismatch of 17 % between silicon and GaN, huge progress has been made for GaN grown on silicon substrate in recent years. For example, growth of GaN-on-silicon wafers with diameters of 6 inches [29]-[31] or 8 inches [32] was demonstrated. In addition, device results of AlGaN/GaN HEMTs on 8-inch GaN-on-silicon wafers were

Fig. 1.7. Process flow of the substrate transfer technology [34]. (a) Standard AlGaN/GaN HEMT on Si substrate. (b) Bonding to a Si carrier wafer and Si (111) substrate removal, and BCB stands for benzocyclobutene. (c) GaN/AlGaN buffer bonded to a glass wafer. (d) Final device structure after releasing the carrier wafer. G, S and D stand for gate, source and drain, respectively.

reported by Arulkumaran *et* al. [33]. Due to the low cost of silicon wafers, GaN-on-silicon technology on large diameter wafers (6-inch or 8-inch) is a promising approach for the next-generation power electronic devices.

For GaN-on-silicon power devices, it was suggested that the  $V_{BR}$  of the AlGaN/GaN-on-silicon HEMTs is limited by the silicon substrate [34]. By removing the silicon substrate and transferring the AlGaN/GaN HEMTs to a glass substrate, the devices with a gate-to-drain spacing  $L_{GD}$  of 20 µm achieved a breakdown voltage  $V_{BR}$  of 1900 V and an on-state resistance  $R_{on}$  of 2 m $\Omega \cdot \text{cm}^2$  (Lu *et al.* [34]). The process flow of silicon substrate transfer technology is shown in Fig. 1.7. Instead of removing the whole silicon wafer,

Fig. 1.8. Schematic cross section after the local silicon removal process [35]. G, S and D stand for gate, source and drain, respectively.

Fig. 1.9. Cross-sectional SEM images of (a) ohmic contact on AlGaN/GaN and (b) Schottky contact on AlGaN/GaN structure grown on Si substrate [36].

a local silicon removal technology for AlGaN/GaN/AlGaN doubleheterostructure HEMTs was demonstrated by Srivastava *et al.* [35]. The devices with a gate-to-drain spacing  $L_{GD}$  of 20 µm achieved a breakdown voltage  $V_{BR}$  of 2200 V. The schematic cross section after the local silicon removal process is shown in Fig. 1.8 [35]. In addition, Schottky drain technology for AlGaN/GaN HEMTs was proposed by Lu *et al.* [36] to improve the device breakdown voltage  $V_{BR}$ . A cross-sectional scanning electron microscope (SEM) image of the ohmic contact (Au/Ni/Al/Ti) on AlGaN/GaN is shown in Fig. 1.9 (a). It can be seen that there are "metal spikes" in the GaN underneath the ohmic contacts. However, the surface of AlGaN/GaN with a Schottky contact (Au/Ti) is smooth [Fig. 1.9 (b)]. It was suggested by Lu *et al.* [36] that the "metal spikes" in the GaN created during the ohmic alloying process are responsible for the higher leakage current and lower breakdown voltage  $V_{BR}$  of the devices with ohmic source/drain contacts.

Some of major device design technologies to enhance the breakdown voltage  $V_{BR}$  of AlGaN/GaN HEMTs were discussed above. Most of the efforts are to reduce the peak electric field near the gate edge of the drain side, or to eliminate the vertical breakdown through the silicon substrate.

## 1.3 Challenges of AlGaN/GaN High Electron Mobility Transistors1.3.1 Formation of High Quality Gate Stack

Conventional AlGaN/GaN HEMTs employ a Schottky gate, which typically have the shortcoming of a large gate leakage current density  $J_G$ . High  $J_G$  not only results in a lower breakdown voltage, but also leads to issues related to noise, power loss, and reliability. High  $J_G$  could be reduced by integrating a metal-oxide-semiconductor (MOS) structure into the AlGaN/GaN HEMTs to form AlGaN/GaN MOS-HEMTs. There has been many work using a MOS gate structure by using various dielectrics, such as HfO<sub>2</sub>[37], Al<sub>2</sub>O<sub>3</sub>[38], MgO [39], Sc<sub>2</sub>O<sub>3</sub>[40], ZrO<sub>2</sub> [41], Gd<sub>2</sub>O<sub>3</sub>[42], SiO<sub>2</sub> [43], SiN<sub>x</sub> [43], and TiO<sub>2</sub> [44], to reduce the gate leakage current density  $J_G$  of the AlGaN/GaN HEMTs. In addition, treatment on the AlGaN/GaN surface has also been intensively explored in many ways, such as treatment using (NH<sub>4</sub>)<sub>2</sub>S<sub>x</sub> [45], H<sub>2</sub>O<sub>2</sub> [46], ultraviolet (UV) illumination [47], and gas plasma (O<sub>2</sub> [48], [49], NH<sub>3</sub> [50], BCl<sub>3</sub> [51], CHF<sub>3</sub> [52], CF<sub>4</sub> [52]-[53], SF<sub>6</sub> [54], or N<sub>2</sub> [55]). Nevertheless, further improvement on the quality of the interface between the dielectric and GaN or AlGaN is still highly desired.

#### 1.3.2 Strain Engineering

Strain engineering for silicon metal-oxide-semiconductor field-effect transistor (MOSFET) has been intensively studied, such as SiGe source/drain stressor for silicon p-MOSFET [56]-[60], silicon-carbon source/drain stressor for silicon n-MOSFET [61]-[65], gate-induced channel stress [66], diamond-like carbon (DLC) stress liner for silicon p-silicon MOSFET [68]-[71], and silicon nitride stress liner for silicon n-MOSFET [67]. Polarization charge density for AlGaN/GaN heterostructure could be locally modulated through piezoelectric polarization of AlGaN/GaN heterostructure, thus further enhancing the carrier mobility by reducing the Coulomb carrier scattering." In the literature, AlGaN/GaN HEMTs with a tensile silicon nitride liner has been studied [72]. In order to further enhance the performance of AlGaN/GaN

HEMTs, strain engineering by a higher stress liner for AlGaN/GaN HEMTs is worthy to be further explored.

#### **1.3.3 Gold-Free CMOS Compatible Process**

GaN power devices have been considered as one of the candidates for the next-generation power devices. If GaN devices can be fabricated using the current mature silicon complementary metal-oxide-semiconductor (CMOS) technologies, the fabrication cost can be lowered down. The use of gold is typically avoided in the silicon CMOS fabrication process, because gold will introduce deep-level traps in silicon transistors. However, in the reported literatures, most of the GaN-based HEMTs were fabricated using a goldcontained process, where gold was used either in the gate or the source/drain contacts [73]-[74]. Therefore, the development of gold-free fabrication process is essential to fabricate the GaN-based HEMTs in silicon CMOS foundries.

#### 1.4 Objective of Research

The objective of the research work in this thesis is to address some of the most challenging issues faced by AlGaN/GaN HEMTs. In order to form a high quality MOS gate stack on GaN or AlGaN, novel *in situ* surface passivation technique, such as *in situ* vacuum anneal and SiH<sub>4</sub> treatment, was proposed. The quality of the interface between the dielectric and GaN was evaluated using a GaN MOS capacitor structure. Effectiveness of this *in situ* surface passivation technique on AlGaN/GaN MOS-HEMTs was also demonstrated. In order to further boost the device performance of AlGaN/GaN MOS-HEMTs, strain engineering using a DLC stress liner was explored. In order to enable GaN power devices to be fabricated in the silicon foundries, high voltage AlGaN/GaN MOS-HEMTs using a CMOS compatible gold-free process were demonstrated on both AlGaN/GaN-on-silicon and AlGaN/GaN-on-sapphire substrates.

#### 1.5 Thesis Organization

The main work in this thesis is documented in 4 Chapters.

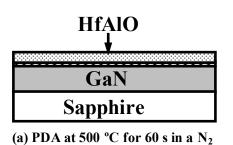

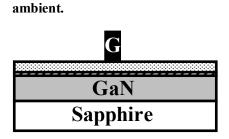

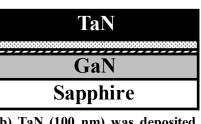

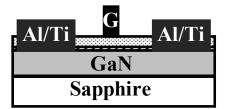

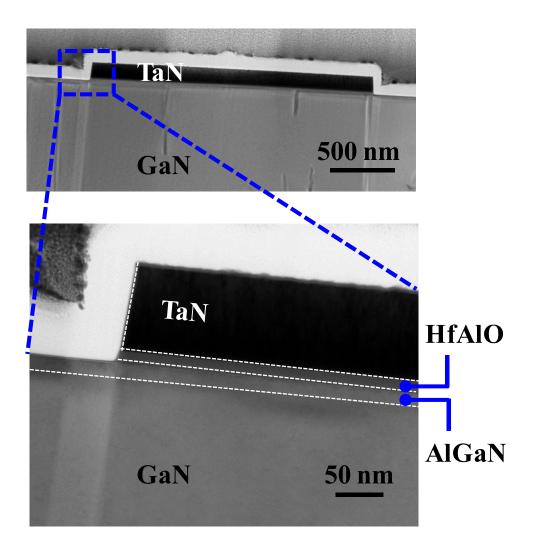

Chapter 2 describes the novel surface passivation technique to realize high quality metal gate/high-permittivity dielectric stacks on GaN surface. This novel *in situ* surface passivation technique comprises vacuum anneal for desorption of contaminants on the GaN surface, followed by a surface treatment in a multi-chamber metal-organic chemical vapor deposition (MOCVD) gate cluster system. A capacitor test structure consisting of a tantalum nitride (TaN)-hafnium aluminum oxide (HfAlO) gate stack on GaN was used. Interface state density  $D_{it}$  was measured from midgap to near conduction band edge using the conductance method at a high temperature, and the lowest  $D_{it}$  of ~ 1 × 10<sup>11</sup> cm<sup>-2</sup> eV<sup>-1</sup> between GaN and HfAlO was achieved using *in situ* vacuum anneal and SiH<sub>4</sub> treatment [75]-[77].

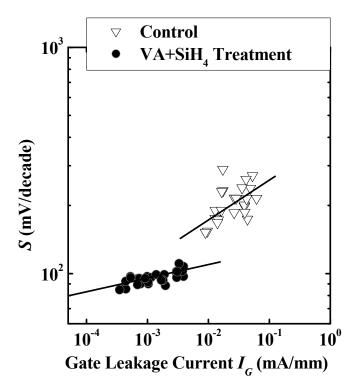

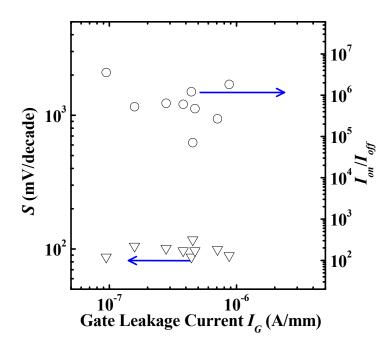

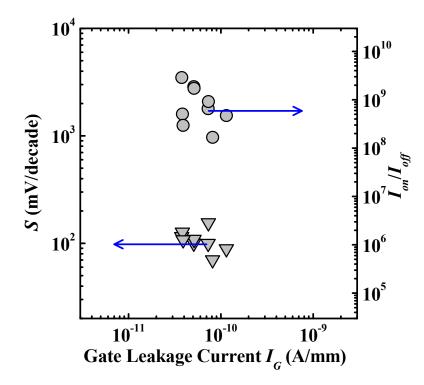

Chapter 3 reports the effect of *in situ* vacuum anneal and SiH<sub>4</sub> treatment on the electrical characteristics of AlGaN/GaN MOS-HEMTs. Devices with *in situ* vacuum anneal and SiH<sub>4</sub> treatment show reduced gate leakage current  $I_G$  and improved saturation drain current. In addition, devices with *in situ* vacuum anneal and SiH<sub>4</sub> treatment achieved current on/off,  $I_{on}/I_{off}$ , ratio of ~ 10<sup>6</sup> and sub-threshold swing *S* of less than 100 mV/decade [78].

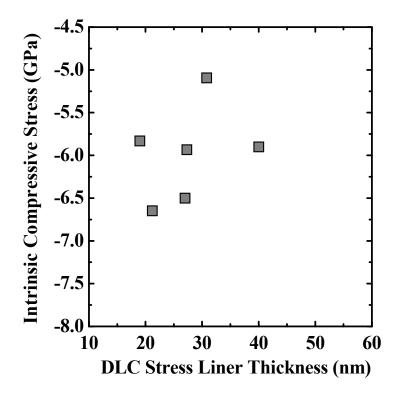

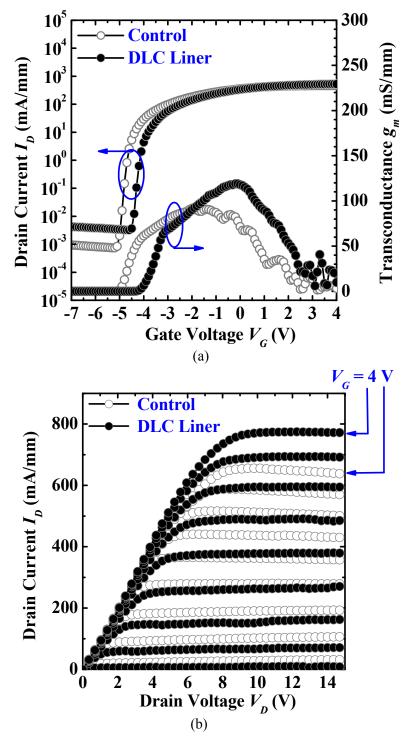

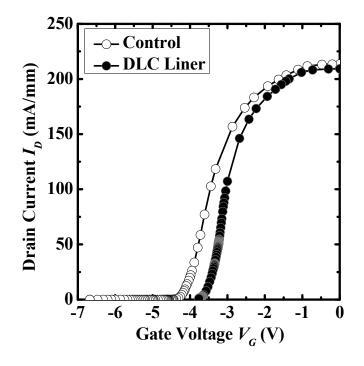

Chapter 4 demonstrates the integration of a highly compressive DLC stress liner on AlGaN/GaN MOS-HEMTs. In this work, a 40 nm thick DLC film with a highly intrinsic compressive stress of up to 6 GPa was integrated on AlGaN/GaN MOS-HEMTs. Up to 32 % enhancement of saturation drain current and 10 % reduction of the source/drain series resistance were observed for the DLC-strained AlGaN/GaN MOS-HEMTs over the control. Also, a positive threshold voltage ( $V_{th}$ ) shift was observed for the DLC-strained AlGaN/GaN MOS-HEMTs, which thus shows the potential of realizing enhancement mode AlGaN/GaN MOS-HEMTs by strain engineering [79]-[80].

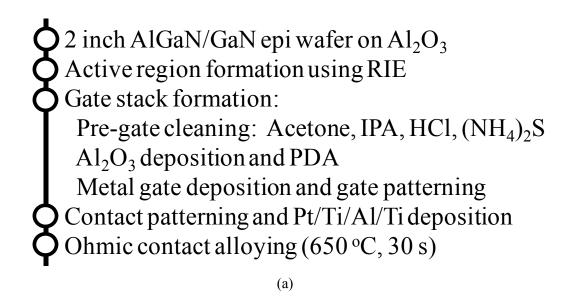

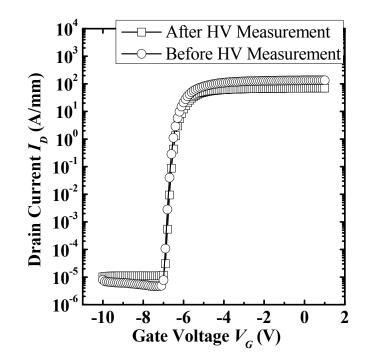

Chapter 5 reports the realization of high voltage AlGaN/GaN MOS-HEMTs using a CMOS compatible gold-free process. AlGaN/GaN-on-silicon MOS-HEMTs with a gate-to-drain spacing  $L_{GD}$  of 5 µm achieved a breakdown voltage  $V_{BR}$  of 800 V and an on-state resistance  $R_{on}$  of 3 m $\Omega$ ·cm<sup>2</sup>. In addition, sub-threshold swing *S* of ~ 97 mV/decade and current on/off,  $I_{on}/I_{off}$ , ratio of ~ 10<sup>6</sup> were obtained. Compared with those of gold-free AlGaN/GaN-on-silicon MOS-HEMTs having a gate-to-drain spacing  $L_{GD}$  of less than 10 µm reported in the literature, the breakdown voltage  $V_{BR}$  achieved in this work is the highest to date. Also, AlGaN/GaN-on-sapphire MOS-HEMTs with a gate-todrain spacing  $L_{GD}$  of 20 µm achieved a breakdown voltage  $V_{BR}$  of 1400 V and an on-state resistance  $R_{on}$  of 22 m $\Omega$ ·cm<sup>2</sup>. This is the highest breakdown voltage  $V_{BR}$  achieved for gold-free AlGaN/GaN MOS-HEMTs to date. In addition, high  $I_{on}/I_{off}$  ratio of ~ 10<sup>9</sup> and low  $I_G$  of ~ 10<sup>-11</sup> A/mm were also obtained [81]-[83].

Finally, the main contributions of this thesis and suggestions for future work are summarized in Chapter 6.

## **Chapter 2**

# *In Situ* Surface Passivation of Gallium Nitride in Advanced Gate Stack Process

#### **2.1 Introduction**

Gallium nitride (GaN)-based materials are attractive for high power, high temperature, and high frequency applications [84]-[87], primarily due to their superior properties, such as large breakdown electric field, wide energy bandgap, and high electron mobility. High electron mobility transistors (HEMTs) employing the AlGaN/GaN heterostructure further exploit the high electron mobility in the two-dimensional electron gas (2-DEG) at the AlGaN/GaN interface. However, many GaN-based HEMTs employ a Schottky gate structure, which has the shortcoming of a high gate leakage current density  $J_G$ . High  $J_G$  could be reduced by using a metal-oxidesemiconductor (MOS) structure [88] and through optimal selection of gate dielectric materials [89]. In addition, AlGaN/GaN HEMTs suffer from current collapse during large signal operation at high frequency, usually referred as "dc-to-radio frequency (RF) dispersion". Slow response of surface traps is believed to be one of the major contributing factors [90].

Employing a MOS gate structure using various dielectrics, such as HfO<sub>2</sub> [37], Al<sub>2</sub>O<sub>3</sub> [38], MgO [39], Sc<sub>2</sub>O<sub>3</sub> [40], ZrO<sub>2</sub> [41], Gd<sub>2</sub>O<sub>3</sub> [42], SiO<sub>2</sub> [43], SiN<sub>x</sub> [43], and TiO<sub>2</sub> [44], can significantly reduce  $J_G$  for the AlGaN/GaN HEMTs with a Schottky gate structure. As shown in Table 2.1, various

| Dielectric                     | Deposition Method                                                   | Interface State<br>Density <i>D<sub>it</sub></i><br>(cm <sup>-2</sup> eV <sup>-1</sup> ) | Characterization<br>Method                             | Ref. |

|--------------------------------|---------------------------------------------------------------------|------------------------------------------------------------------------------------------|--------------------------------------------------------|------|

| HfO <sub>2</sub>               | Atomic Layer Deposition (ALD)                                       | $\sim 2 \times 10^{11}$ at midgap                                                        | Terman method                                          | [37] |

| Al <sub>2</sub> O <sub>3</sub> | ALD                                                                 | $\sim$ (4-9) $\times$ 10 <sup>11</sup> near the midgap                                   | -                                                      | [38] |

| MgO                            | Electron-Cyclotron-Resonance<br>Molecular Beam Epitaxy<br>(ECR-MBE) | ~ $6 \times 10^{11}$ at 0.3 eV<br>below $E_C$                                            | Both Terman and<br>conductance<br>methods at 300<br>°C | [39] |

| Sc <sub>2</sub> O <sub>3</sub> | MBE                                                                 | -                                                                                        | _                                                      | [40] |

| ZrO <sub>2</sub>               | Electron Beam Evaporation                                           | _                                                                                        | _                                                      | [41] |

| Gd <sub>2</sub> O <sub>3</sub> | MBE                                                                 | $\sim 4.2 \times 10^{11}$                                                                | _                                                      | [42] |

| SiO <sub>2</sub>               | Plasma Enhanced Chemical<br>Vapor Deposition (PECVD)                | $\sim 2.5 \times 10^{11}$                                                                | Terman method                                          | [43] |

| SiN <sub>x</sub>               | PECVD                                                               | $\sim 6.5 \times 10^{11}$                                                                | Terman method                                          | [43] |

| TiO <sub>2</sub>               | Liquid Phase Deposition                                             | $\sim 7.48 \times 10^{11}$                                                               | Terman method                                          | [44] |

Table 2.1.Various deposition methods to achieve a high quality dielectric/GaNinterface [37]-[44]. "-" means "not reported".

deposition methods were intensively investigated to achieve a high quality dielectric/GaN interface in terms of interface state density  $(D_{it})$ .

As illustrated in Fig. 2.1, there are two commonly employed techniques for passivating AlGaN/GaN HEMTs: (1)surface passivation/treatment is to reduce surface traps on the GaN or AlGaN surface by using various treatment methods (e.g. in situ VA and SiH<sub>4</sub> passivation), and (2) device passivation is to encapsulate the device by using various insulators or dielectrics (e.g. oxide/nitride passivation). Surface passivation on the GaN or AlGaN surface before the dielectric layer deposition has been intensively explored to further improve the interface quality between dielectric and GaN or AlGaN layer, such as  $(NH_4)_2S_x$  treatment [45],  $H_2O_2$  treatment [46], ultraviolet (UV) illumination[47], and various gas plasma treatments,

Fig. 2.1. Schematic diagram illustrating two approaches for passivating AlGaN/GaN HEMTs: surface passivation/treatment and device passivation.

including the use of O<sub>2</sub> [48]-[49], NH<sub>3</sub> [50], BCl<sub>3</sub> [51], CHF<sub>3</sub> [52], CF<sub>4</sub> [52]-[53], SF<sub>6</sub> [54], and N<sub>2</sub> [55] plasma. Although plasma-enhanced chemical vapor deposition (PECVD) SiN<sub>x</sub> film is the most widely used as the device passivation layer for AlGaN/GaN HEMTs [91], some reports show that it increases the device gate leakage, which is dominated by surface leakage current due to the electron hopping through the gap-states in the SiN<sub>x</sub> layer [92]-[93]. Besides, an even more effective device passivation technique was demonstrated by performing *in situ* Si<sub>3</sub>N<sub>4</sub> [94] or SiCN cap layer [95] growth, immediately after the AlGaN/GaN layers were grown without breaking the chamber vacuum.

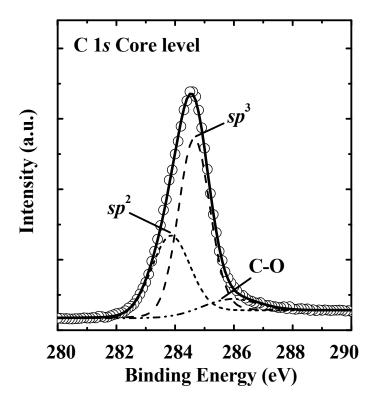

In this Chapter, a novel and effective surface passivation technique for GaN is demonstrated, and it comprises the steps of *in situ* vacuum anneal (VA) and treatment in either silane-ammonia (SiH<sub>4</sub>+NH<sub>3</sub>) or silane (SiH<sub>4</sub>) only, prior to the deposition of hafnium-based high-permittivity dielectric using a metal-organic chemical vapor deposition (MOCVD) system [75]-[77]. The effect of VA temperature and the SiH<sub>4</sub>+NH<sub>3</sub> or SiH<sub>4</sub> treatment temperature on

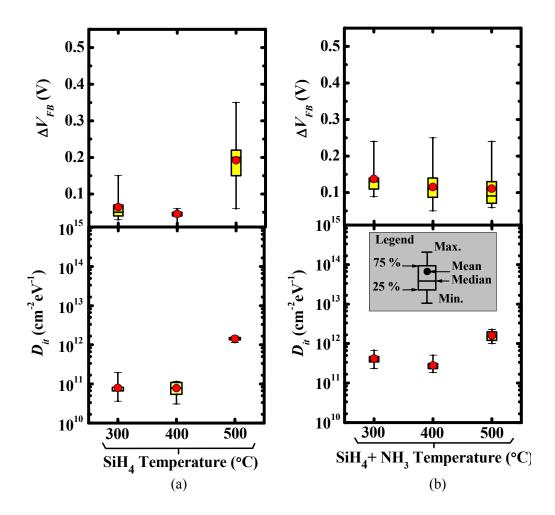

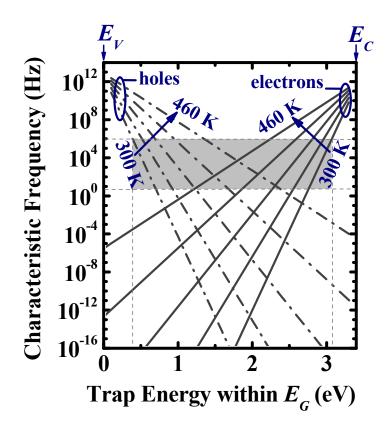

$D_{it}$  and flatband voltage shift  $\Delta V_{FB}$  was investigated. A capacitor test structure consisting of a tantalum nitride (TaN)-hafnium aluminum oxide (HfAlO) gate stack on GaN was used.  $D_{it}$  from near the conduction band edge  $E_C$  to the mid-gap of GaN was measured at temperatures of 300 and 460 K using the conductance method with series resistance correction. HfAlO with 10 % Al was chosen as the dielectric for this study due to its higher crystallization temperature (~ 800 °C) than that of pure HfO<sub>2</sub> (~ 400 °C) and its higher dielectric constant ( $\varepsilon_r \sim 20$ ) than that of pure Al<sub>2</sub>O<sub>3</sub> ( $\varepsilon_r \sim 9$ ) [96]-[97].

#### 2.2 Development of In Situ Surface Passivation for Gallium Nitride

#### 2.2.1 Experiment

Si-doped  $(2 \times 10^{18} \text{ cm}^{-3})$  GaN (0001) epitaxial layer on sapphire substrates were used as the starting materials. The GaN epitaxial layer has a thickness of 2 µm and a root-mean-square surface roughness of less than 0.5 nm. Pre-gate cleaning for all samples comprised a 2-minute acetone and a 3minute isopropanol degreasing step, a 10-minute dilute HCl (H<sub>2</sub>O:HCl=1:1) native oxide removal step, and an *ex situ* surface passivation step in an undiluted (NH<sub>4</sub>)<sub>2</sub>S solution for 30 minutes.

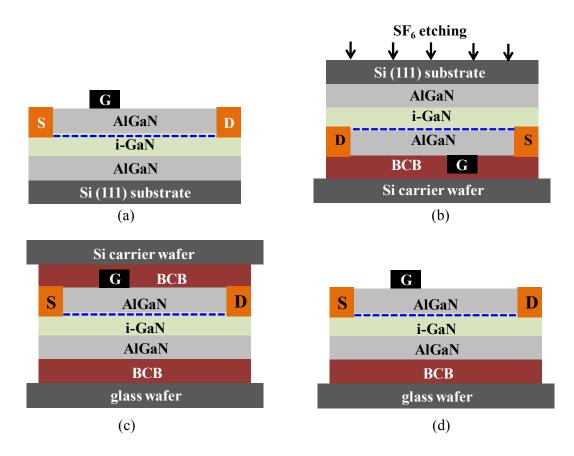

After pre-gate cleaning, the wafers were quickly loaded into a multichamber MOCVD gate cluster system, where VA, SiH<sub>4</sub>+NH<sub>3</sub> or SiH<sub>4</sub> treatment, and deposition of HfAlO were performed (Fig. 2.2). In the first chamber of the MOCVD system, the wafers were annealed at various temperatures ranging from 200 to 600 °C for 1 minute under a pressure of ~ 1×  $10^{-6}$  Torr. After VA, the wafers were transferred to the second chamber

Fig. 2.2. Schematic diagram illustrating the *in situ* passivation and HfAlO deposition processes in a multi-chamber metal-organic chemical vapor deposition (MOCVD) gate cluster system. A high vacuum transfer module is connected to the three process chambers, including the first chamber for VA, the second chamber for surface treatment with  $SiH_4$ +NH<sub>3</sub> or  $SiH_4$  only, and the third chamber for HfAlO deposition.

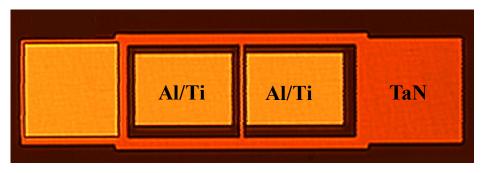

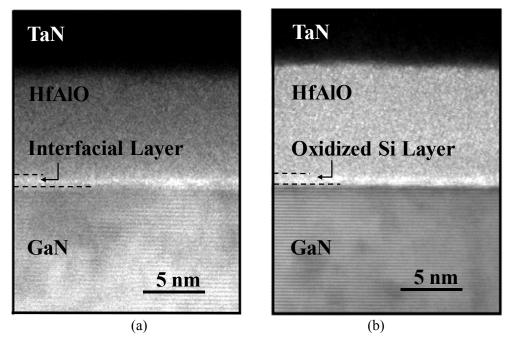

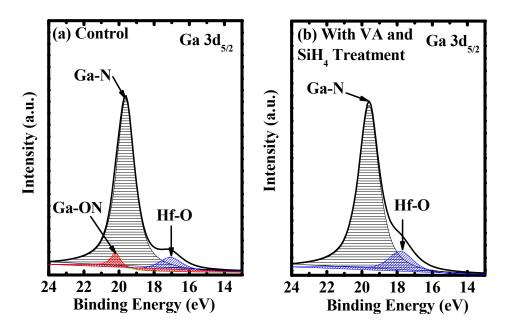

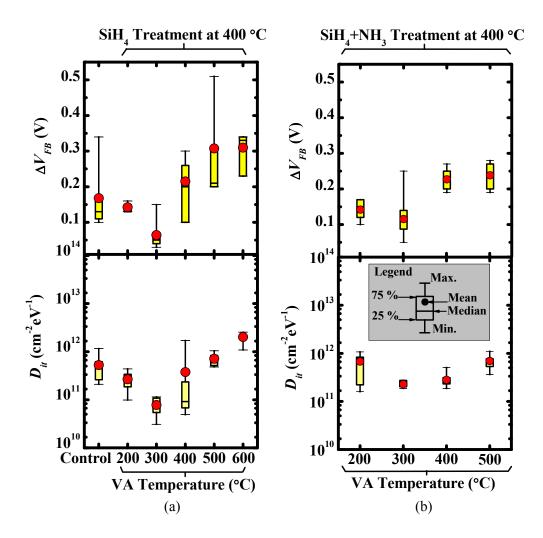

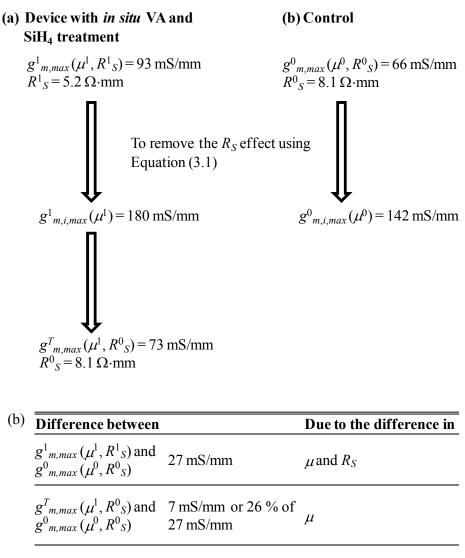

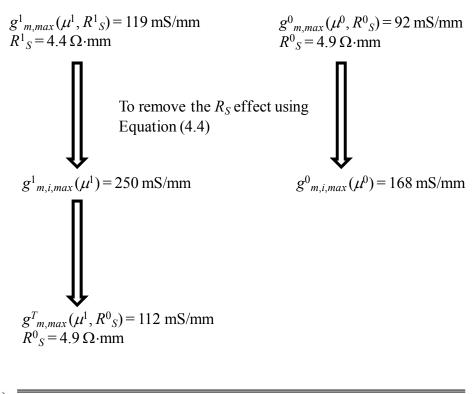

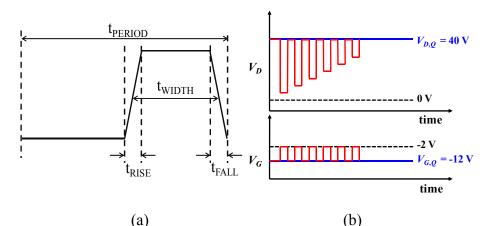

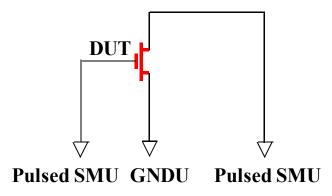

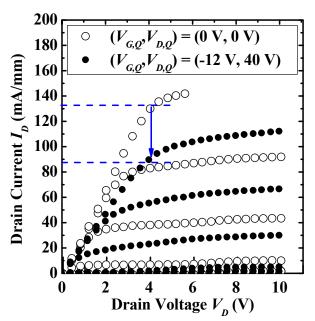

for either SiH<sub>4</sub>+NH<sub>3</sub> or SiH<sub>4</sub> treatment at various temperatures ranging from 300 to 500 °C for 1 minute at a pressure of 5 Torr. For SiH<sub>4</sub>+NH<sub>3</sub> treatment, the flow rates of SiH<sub>4</sub> (mole fraction of 49.3 % and partial pressure of 2.46 Torr), NH<sub>3</sub> (mole fraction of 50.5 % and partial pressure of 2.53 Torr), and N<sub>2</sub> were 60, 60, and 250 standard cubic centimeter per minute (sccm), respectively. For the SiH<sub>4</sub> treatment, the flow rates of SiH<sub>4</sub> (mole fraction of 99.6 % and partial pressure of 4.98 Torr ) and N<sub>2</sub> were 60 and 250 sccm, respectively. The detailed recipes for the VA, SiH<sub>4</sub>+NH<sub>3</sub> or SiH<sub>4</sub> treatment, and HfAlO deposition are documented in Appendix A. Without breaking vacuum, the wafers were transferred to the third chamber for the deposition of HfAlO thickness was ~ 20 nm. For the control sample, the VA and SiH<sub>4</sub>+NH<sub>3</sub> or SiH<sub>4</sub> treatment steps were skipped [98]-[100].