# SEMICONDUCTOR NANOWIRES FOR THERMOELECTRIC APPLICATIONS

## LI YIDA

(B. Eng. (Hons.), NUS)

## A THESIS SUBMITTED

## FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

## NUS GRADUATE SCHOOL FOR INTEGRATIVE SCIENCES

## AND ENGINEERING

## NATIONAL UNIVERSITY OF SINGAPORE

## Declaration

I hereby declare that this thesis is my original work and it has been written by me in its entirety. I have duly acknowledged all the sources of information which have been used in the thesis.

This thesis has also not been submitted for any degree in any university previously.

layde:

Li Yida

21 October 2013

### Acknowledgements

Firstly, I would like to express my gratitude to my supervisor, Associate Professor John Thong Thiam Leong, and my co-supervisors, Associate Professor Lee Sung Joo (SKKU), and Dr Wang Xinpeng (IME). They have given me this invaluable opportunity to work with them, as well as inspiring and encouraging me on during the course of my research work. Their kind guidance and encouragement has greatly increased my passion in working on the project and to attain the next level of academic excellence. Not forgetting my TAC committee comprising of Professor Wu Yihong and Associate Professor Thomas Liew Yun Fook who provided me with their valuable advice for my work during our meetings.

Secondly, I would like to extend my gratitude to my supervisors over at Institute of Microelectronics, Agency for Science, Technology and Research, Singapore – Dr Patrick Lo Guo Qiang, Dr Navab Singh, and Ms Kavitha Buddharaju for their kind guidance and instructions during my research attachment.

Thirdly, I would like to thank my research buddies in IME and staff members of CICFAR Lab for their kind assistance and discussions whenever I met with any problems in my research work. Last but not least, I would like to embrace my wife, my parents, and my family for providing me with emotional support, concern and care relentlessly. This gives me the strength to persevere till the end. Without them, this work in this thesis would not have been possible.

## **Table of Contents**

| Declaration                                                                                                                                                                                                                                                                                           | i                                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| Acknowledgements                                                                                                                                                                                                                                                                                      | ii                                    |

| Table of Contents                                                                                                                                                                                                                                                                                     | iii                                   |

| Summary                                                                                                                                                                                                                                                                                               | viii                                  |

| List of Tables                                                                                                                                                                                                                                                                                        | xi                                    |

| List of Figures                                                                                                                                                                                                                                                                                       | xii                                   |

| List of Symbols                                                                                                                                                                                                                                                                                       | . xviii                               |

| Chapter 1: Introduction                                                                                                                                                                                                                                                                               | 1                                     |

| References                                                                                                                                                                                                                                                                                            | 7                                     |

| Chapter 2: Concepts and Development of Thermoelectricity in                                                                                                                                                                                                                                           | 0                                     |

| Chapter 2. Concepts and Development of Thermoelectricity in                                                                                                                                                                                                                                           | One-                                  |

| Dimensional Nanowire                                                                                                                                                                                                                                                                                  |                                       |

|                                                                                                                                                                                                                                                                                                       | 8                                     |

| Dimensional Nanowire                                                                                                                                                                                                                                                                                  | 8<br>8                                |

| Dimensional Nanowire<br>2.1 Thermoelectric efficiency                                                                                                                                                                                                                                                 | 8<br>8<br>10                          |

| Dimensional Nanowire<br>2.1 Thermoelectric efficiency<br>2.1.1 Coefficient of Performance (COP)                                                                                                                                                                                                       | <b>8</b><br>10<br>11                  |

| <ul> <li>Dimensional Nanowire</li> <li>2.1 Thermoelectric efficiency</li> <li>2.1.1 Coefficient of Performance (COP)</li> <li>2.1.2 Thermoelectric conversion efficiency (η)</li> </ul>                                                                                                               | 8<br>10<br>11<br>13                   |

| <ul> <li>Dimensional Nanowire</li> <li>2.1 Thermoelectric efficiency</li> <li>2.1.1 Coefficient of Performance (COP)</li> <li>2.1.2 Thermoelectric conversion efficiency (η)</li> <li>2.2 Thermoelectric transport in one-dimensional nanostructures</li> </ul>                                       | 8<br>10<br>11<br>13<br>14             |

| <ul> <li>Dimensional Nanowire</li> <li>2.1 Thermoelectric efficiency</li> <li>2.1.1 Coefficient of Performance (COP)</li> <li>2.1.2 Thermoelectric conversion efficiency (η)</li> <li>2.2 Thermoelectric transport in one-dimensional nanostructures</li> <li>2.2.1 Electronics properties</li> </ul> | 8<br>10<br>11<br>13<br>14<br>17       |

| <ul> <li>Dimensional Nanowire</li> <li>2.1 Thermoelectric efficiency</li></ul>                                                                                                                                                                                                                        | 8<br>10<br>11<br>13<br>14<br>17<br>22 |

| 2.3.2 Development of silicon/silicon-germanium/germanium nanowire for       |

|-----------------------------------------------------------------------------|

| thermoelectrics                                                             |

| 2.3.3 Development of micro thermoelectric device for power                  |

| generation/cooling applications                                             |

| 2.4 Chapter summary                                                         |

| References                                                                  |

| Chapter 3: Design of a Silicon Nanowire based Thermoelectric Cooler using   |

| Numerical Simulations44                                                     |

| 3.1 Modeling of a single nanowire thermoelectric cooler                     |

| 3.1.1 Thermoelectric field equations45                                      |

| 3.1.2 Silicon nanowire model47                                              |

| 3.2 Effect of thermal conductivity, length and filler material on a silicon |

| nanowire-based thermoelectric cooler48                                      |

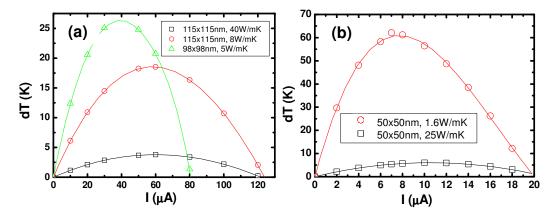

| 3.2.1 Effect of thermal conductivity48                                      |

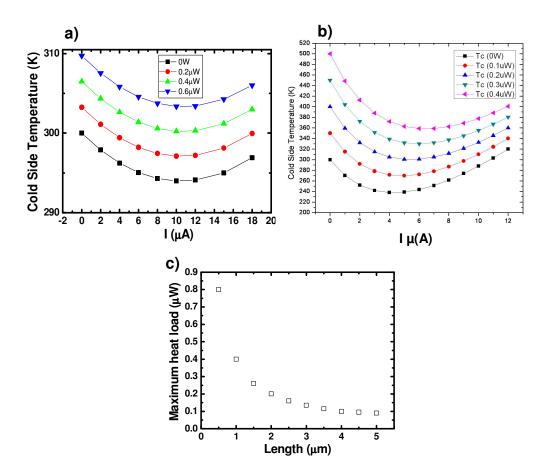

| 3.2.2 Effect of silicon nanowire length                                     |

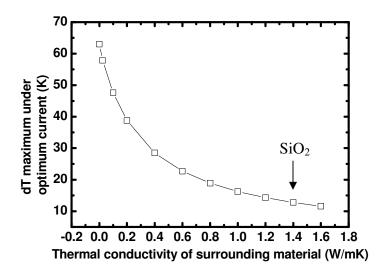

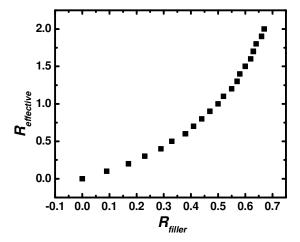

| 3.2.3 Effect of filler material                                             |

| 3.3 Effects of electrical contact resistance on a silicon nanowire-based    |

| thermoelectric cooler                                                       |

| 3.3.1 Experimental details55                                                |

| 3.3.2 Electrical contact resistance of a silicon nanowire-aluminum system58 |

| 3.3.3 Modeling of a silicon nanowire-based thermoelectric cooler with       |

| electrical contact resistance60                                             |

| 3.4 Proposal of a SiNW-based TEC design guideline for on-chip cooling          |

|--------------------------------------------------------------------------------|

| application63                                                                  |

| 3.5 Chapter summary66                                                          |

| References67                                                                   |

| Chapter 4: Development and Fabrication of a Silicon Nanowire Based             |

| Thermoelectric Device using CMOS Process70                                     |

| 4.1 Design considerations of a silicon nanowire based thermoelectric device    |

|                                                                                |

| 4.2 Fabrication process of a complete silicon nanowire based                   |

| thermoelectric device72                                                        |

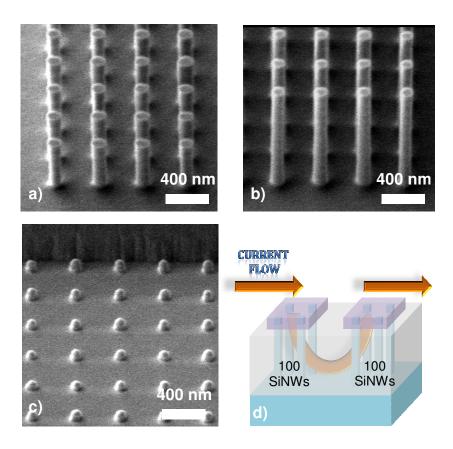

| 4.2.1 Formation of silicon nanowire array74                                    |

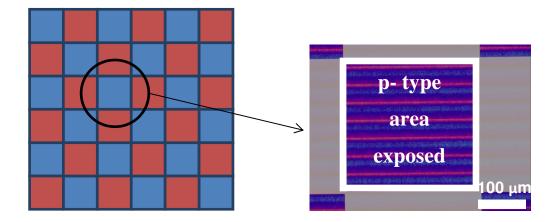

| 4.2.2 Defining n- and p- type thermoelectric legs of a thermoelectric device79 |

| 4.2.3 Nickel Silicidation                                                      |

| 4.2.4 Filler material application87                                            |

| Oxide as filler material87                                                     |

| Polyimide as filler material                                                   |

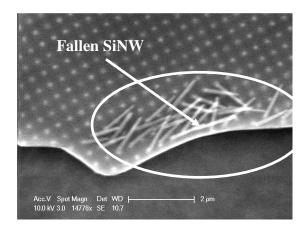

| 4.3 Problems encountered in the fabrication process                            |

| 4.4 Chapter summary93                                                          |

| References95                                                                   |

| Chapter 5: Characterization of a Silicon Nanowire Based Thermoelectric         |

| Device                                                                         |

| 5.1 Micro-level characterization (Individual silicon nanowire)97               |

| 5.1.1 Experimental setup97                                                     |

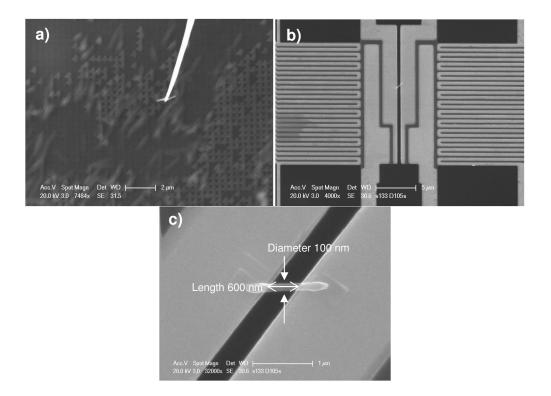

| 5.1.2 Individual silicon nanowire sample preparation100                                                                                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.1.3 Concepts of thermal conductivity measurements102                                                                                                                                                                     |

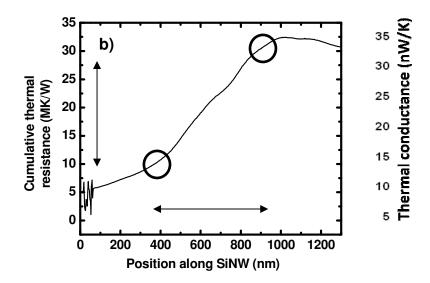

| 5.1.4 Thermal conductance measurements of silicon nanowire105                                                                                                                                                              |

| 5.2 Device level characterization107                                                                                                                                                                                       |

| 5.2.1 Experimental setup107                                                                                                                                                                                                |

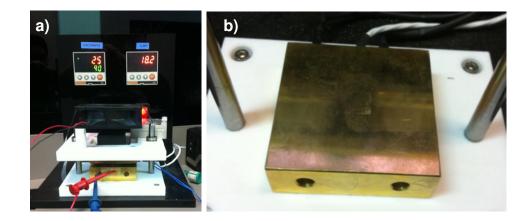

| Setup 1 – Macro heating setup107                                                                                                                                                                                           |

| Setup 2 – Thermal Test Chip108                                                                                                                                                                                             |

| 5.2.2 Thermoelectric power characterization110                                                                                                                                                                             |

| Electrical characterization110                                                                                                                                                                                             |

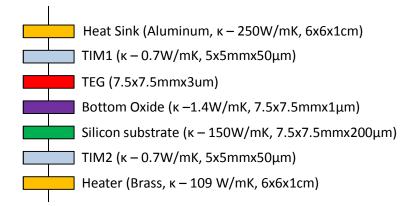

| Thermal stacks in experimental setup111                                                                                                                                                                                    |

| Thermoelectric power generation114                                                                                                                                                                                         |

| Improving electrical contact resistance via nickel silicidation optimization120                                                                                                                                            |

| 5.2.3 Thermoelectric cooling124                                                                                                                                                                                            |

| 5.3 Chapter summary128                                                                                                                                                                                                     |

|                                                                                                                                                                                                                            |

| References129                                                                                                                                                                                                              |

| References                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                            |

| Chapter 6: Characterization of a Silicon-Germanium Nanowire Based                                                                                                                                                          |

| Chapter 6: Characterization of a Silicon-Germanium Nanowire Based<br>Thermoelectric Device131                                                                                                                              |

| Chapter 6: Characterization of a Silicon-Germanium Nanowire Based<br>Thermoelectric Device                                                                                                                                 |

| Chapter 6: Characterization of a Silicon-Germanium Nanowire Based         Thermoelectric Device         131         6.1 Fabrication process         131         6.2 Characterization of a silicon-germanium nanowire-based |

| 6.2.3 Origin of the large electrical resistance of the silicon-germanium |

|--------------------------------------------------------------------------|

| nanowire-based thermoelectric device137                                  |

| 6.3 Growth mechanism of nickel-germanosilicide in silicon-germanium      |

| nanowire143                                                              |

| 6.3.2 Real-time transmission electron microscope imaging with in situ    |

| annealing145                                                             |

| 6.3.3 Results and discussion151                                          |

| 6.4 Chapter summary156                                                   |

| References158                                                            |

| Chapter 7: Summary and Future Works160                                   |

| List of Publications/Conferences165                                      |

| Publications165                                                          |

| Conferences                                                              |

### Summary

This thesis aims to develop a complete semiconductor nanowire (NW) based thermoelectric device (TED), and to benchmark it with current bulk materials-based TEDs. First of all, by using finite element analysis (FEA) simulation, the effects of key material parameters – NW's length, thermal conductivity, electrical contact resistance, and filler material, on the thermoelectric cooling (TEC) performance were elucidated. Accordingly, a design guideline was proposed for the implementation of a complete silicon (Si) NW-based TEC.

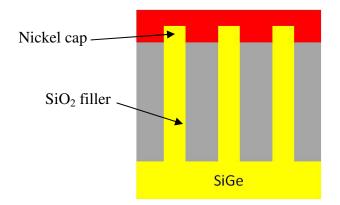

Following, by using complementary-metal-oxide-semiconductor (CMOS) process which is prevalent in the semiconductor industry, SiNW and silicongermanium (SiGe) NW were successfully integrated into a complete TED. Two filler materials – Si dioxide (SiO<sub>2</sub>) and polyimide for the NW array were explored during the TED's fabrication. The SiO<sub>2</sub> filled TED generated a maximum thermoelectric power of 1.5nW with open circuit voltage ( $V_{oc}$ ) of 1.5V under 70K across experimental setup. This represented the first complete SiNW-based TED to be demonstrated, from fabrication to characterization. Characterizing the polyimide filled TED, it was found that its incorporation enhanced the maximum thermoelectric power output > 2 orders to 1.3µW with  $V_{oc}$  of 17.9mV at the same testing condition as the SiO<sub>2</sub> filled TED. With various process optimizations, our polyimide filled TED achieved a power output density (17kW/m<sup>3</sup>) compared to a bismuth-based TED (18.1kW/m<sup>3</sup>). As a TEC, the maximum temperature depression was measured to be 0.1K due to the existence of large electrical contact resistance between the SiNW and aluminum metallization. Concurrently, individual SiNW was extracted from the fabricated TED, and characterized for its thermal conductivity using a micro-electrothermal system (METS) device. The results exhibited a commendable SiNW thermal conductivity value (4.1W/mK) comparable to that reported in notable literature.

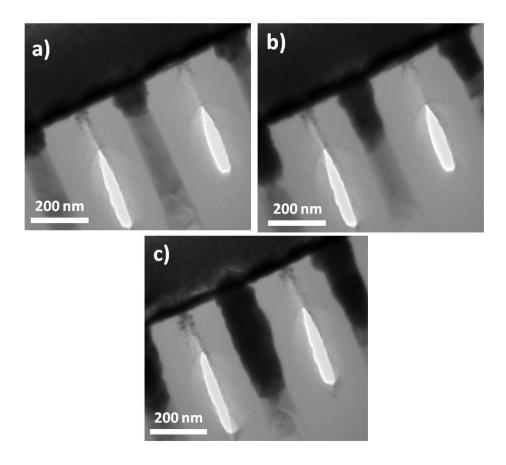

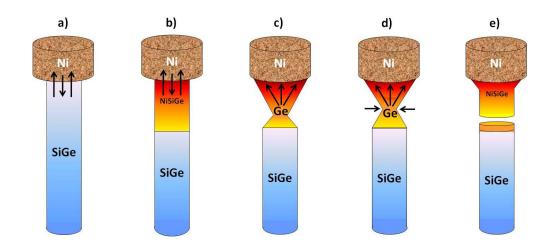

In a NW-based TED, the formation of good ohmic contacts from the top metal traces to the NW array is a key to device performance. For free standing-SiGe NWs, it was found that attempts at silicidation with nickel (Ni) metallization gave rise to voids. Hence, the growth mechanism of Ni-germanosilicide in SiGe NW was thoroughly investigated using real time transmission electron microscope with *in-situ* annealing. Annealing at temperatures 200°C and 400°C, the growth of Ni-germanosilicide was minimal. On the other hand, during annealing at 600°C, loss of material with time in the SiGe NW was observed. However, it was found that by incorporating a compressive stress (constraining the boundary of the SiGe NW with a SiO<sub>2</sub> shell), the loss of material and void can be effectively suppressed.

Hence, in this thesis, we successfully demonstrated the integration of Si/SiGe NW in a complete TED using CMOS process, and characterized its thermoelectric performance. With proper filler material and contact process optimizations, the thermoelectric performance of the SiNW-based TED improved significantly. In SiGe NW, we discovered a way to suppress the void formation which is critical to improve the electrical performance of the TED. Our fabrication and characterization methodologies provide a platform in which future works of a NW-based TED can be built on.

## List of Tables

| Table 3.1: Material parameters used in the simulation. The different kinds of SiNW used (electroless etch <i>versus</i> VLS) are indicated in the parentheses where r – rough, s – smooth. [3.1]                                   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 3.2: Performance of simulated SiNW cooling performance with literatures52                                                                                                                                                    |

| Table 3.3: Parameters calculation using design methodology described. A chip $V_{operating}$ of 5 V and hot spot size of 400 x 400µm were considered. In all cases, number of thermoelectric leg is fixed at 72 and thus not shown |

| Table 5.1: Comparison between the polyimide filled SiNW TED and the SiO <sub>2</sub> filled SiNW TED under a temperature difference $dT$ of 70K across the experimental setup                                                      |

| Table 5.2: Comparison of the thermoelectric properties of the fabricated SiNW-based TEDs                                                                                                                                           |

| Table 5.3: Parameters of the optimized TED and the earlier fabricated TED with       SiO2 and polyimide filler material as indicated.         123                                                                                  |

| Table 5.4: comparison of SiNW and BiTe based superlattice thermoelectric power generation parameters.    123                                                                                                                       |

| Table 6.1: Comparison of the SiGe NW and SiNW based TED136                                                                                                                                                                         |

## List of Figures

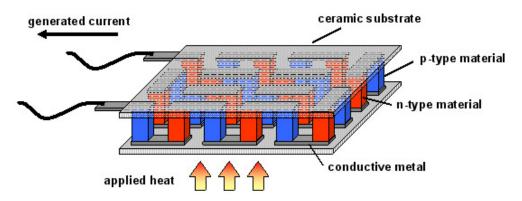

| Figure 1.1: Alternating n- and p- type thermoelectric legs in a device (HIS GlobalSpec CR4, 2013)2                                                                                                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

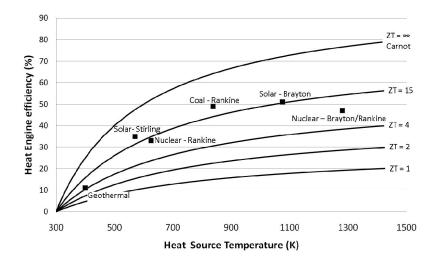

| Figure 1.2: Relation of <i>ZT</i> with the efficiency of heat engine [1.3]                                                                                                                                                                                 |

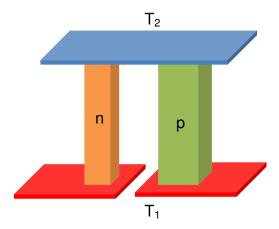

| Figure 2.1: A thermocouple with n- and p- type thermoelectric legs connected in series                                                                                                                                                                     |

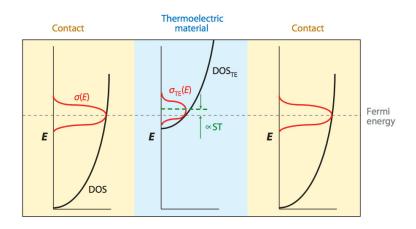

| Figure 2.2: Density of states (DOS) and differential conductivity $\sigma(E)$ versus electron energy ( <i>E</i> ) for a thermoelectric material and the contact layers. [2.10]15                                                                           |

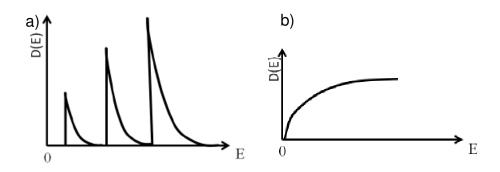

| Figure 2.3: DOS of a) 1-D system, and b) 3-D system17                                                                                                                                                                                                      |

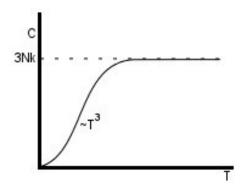

| Figure 2.4: Debye's model of heat capacity $C_D$ plotted with respect to temperature [2.11]                                                                                                                                                                |

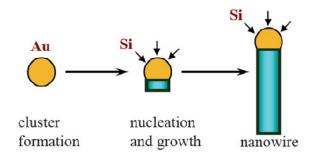

| Figure 2.5: Schematic illustration of Si NW growth using VLS method. This reaction is catalyzed by gold-silicon droplet deposited on the wafer surface prior to whisker growth                                                                             |

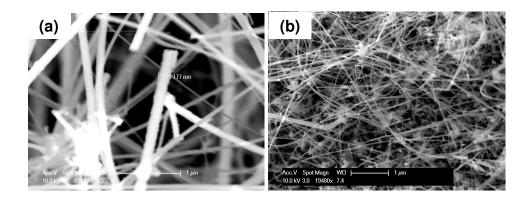

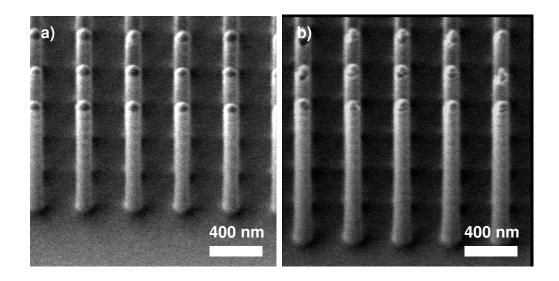

| Figure 2.6: SiNW grown from VLS method. (a) The non-uniformity in size of the SiNW and (b) random orientation of the growth SiNW are clearly seen                                                                                                          |

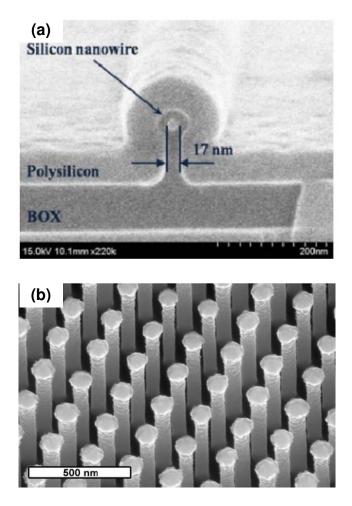

| Figure 2.7: SEM images of (a) lateral SiNW [2.30], and (b) vertical SiNW array synthesized using the top down approach [2.31]                                                                                                                              |

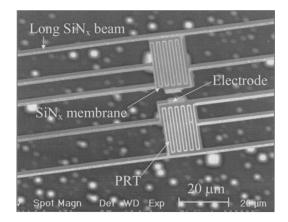

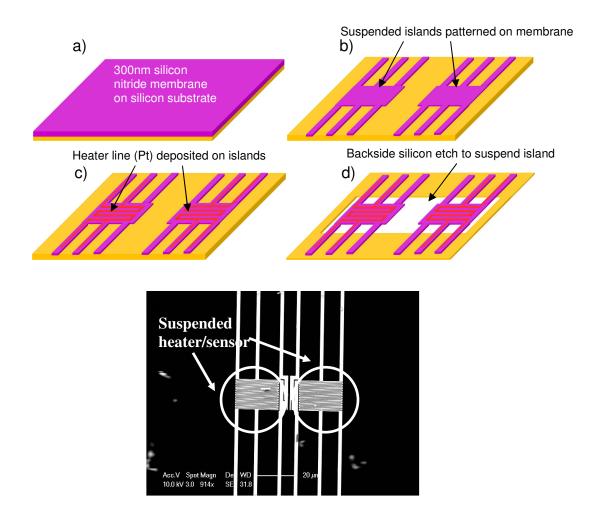

| Figure 2.8: SEM image of a microfabricated device used to measure nanostructures thermal properties [2.39]                                                                                                                                                 |

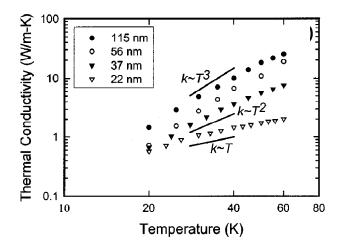

| Figure 2.9: Thermal conductivity results extracted from 20 K to 60 K and plot in logarithmic scale [2.26]                                                                                                                                                  |

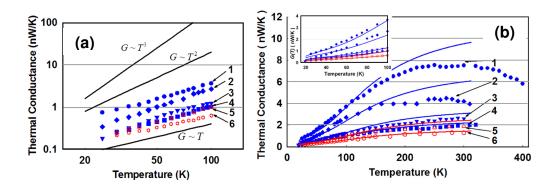

| Figure 2.10: (a) Thermal conductance of thin SiNW measured from 20 K to 100 K and (b) thermal conductance of thin SiNW over a temperature range of 20 K to 400 K. The theoretical model (solid line) is fit to the experimental model (dotted line) [2.25] |

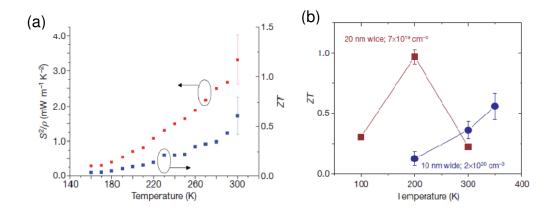

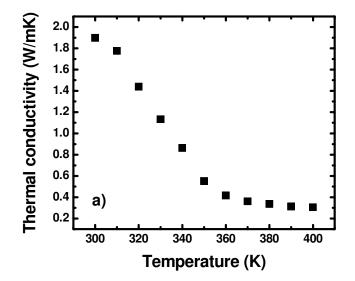

| Figure 2.11: Thermoelectric properties measurements of a) rough SiNW by Berkeley group [2.22], (b) Ultra thin SiNW by Caltech group [2.23]                                                                                                                 |

| Figure 2.12: Schematic of a polysilicon thin film TEG fabricated using CMOS process [2.46]                                                                                                                                                                 |

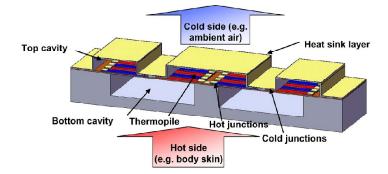

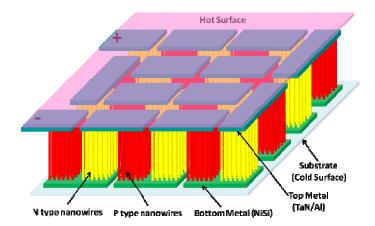

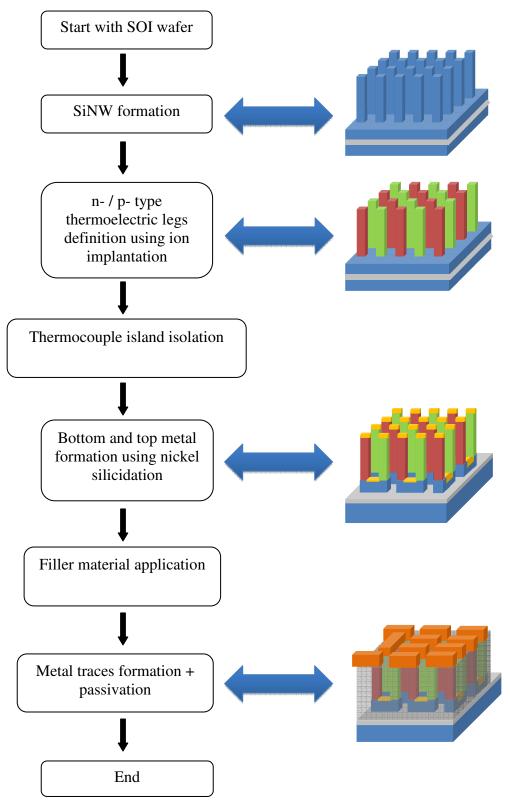

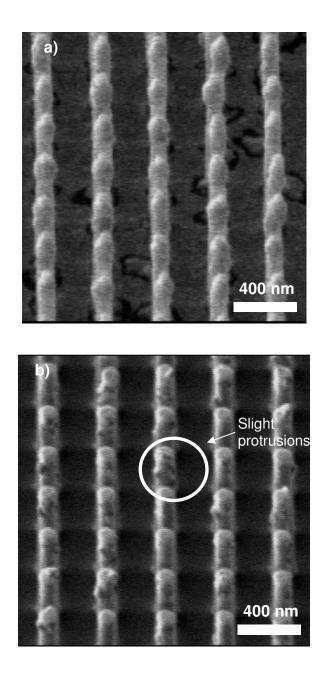

Figure 4.1: Schematic of a SiNW-based TED. The layer responsible for power generation is a composite layer consisting of alternating doped n- and p- type

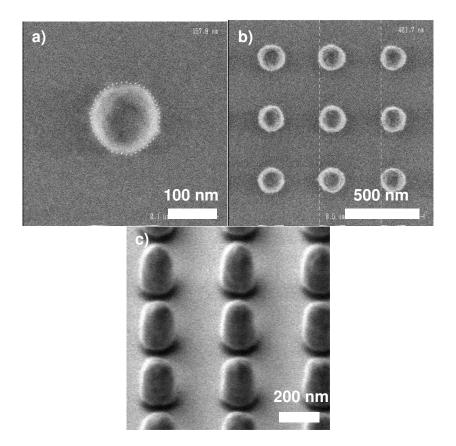

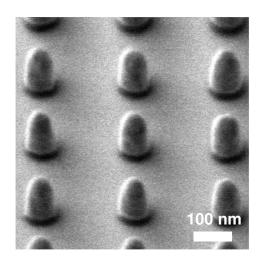

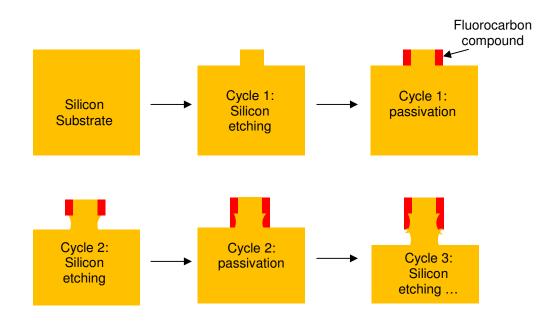

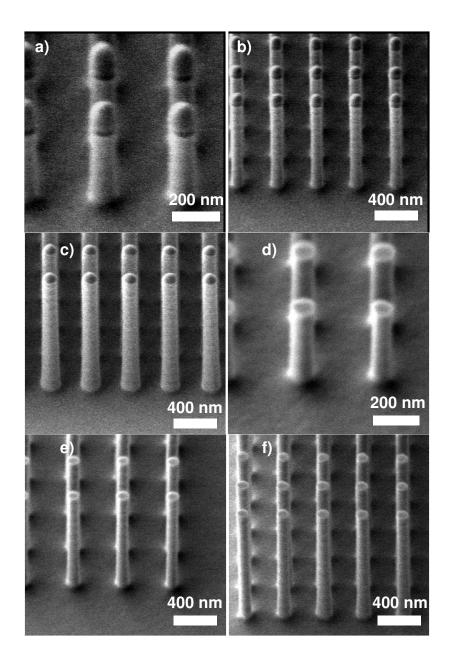

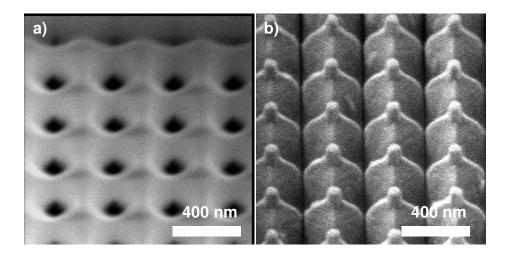

Figure 4.5: Schematic illustrating the etching process used to form the SiNW array. The etching process of the different cycles are indicated......77

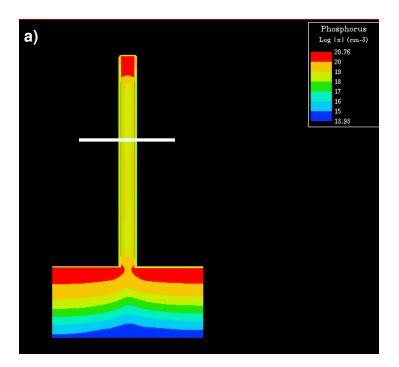

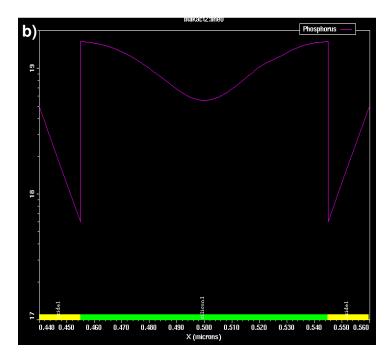

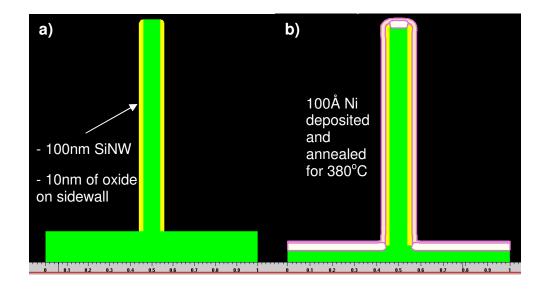

Figure 4.10: TSUPREM4 model of SiNW after a) spacer formation, Ni silicide profile after annealing for b) 380°C, c) 400°C, and d) 420°C for 30 s......85

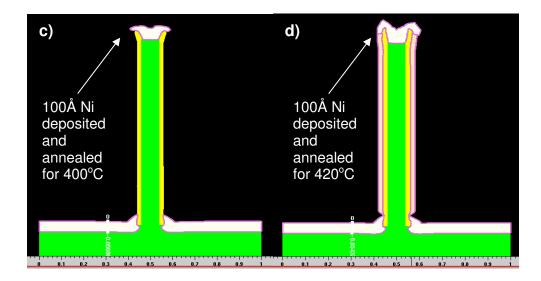

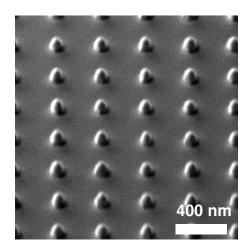

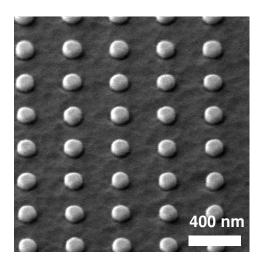

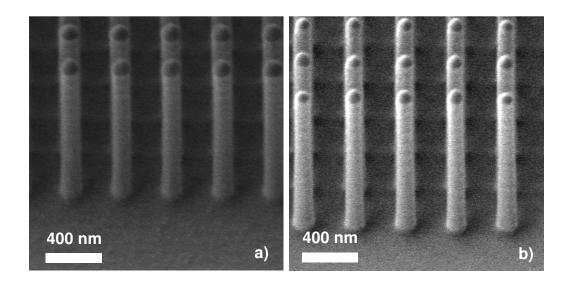

Figure 4.14: SEM images of the SiNW after polyimide etchback using O<sub>2</sub> plasma.90

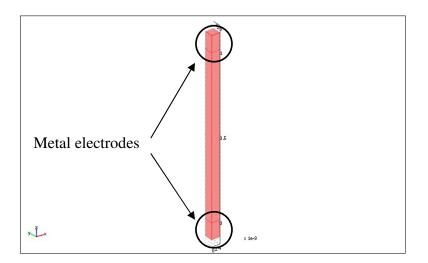

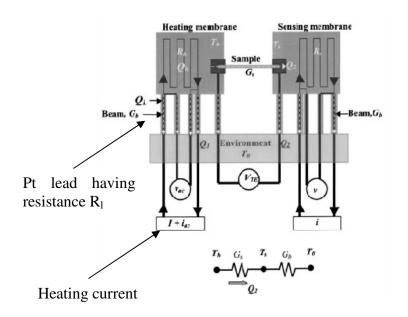

Figure 5.4: Schematic for measurement of thermal conductivity [5.4] ......103

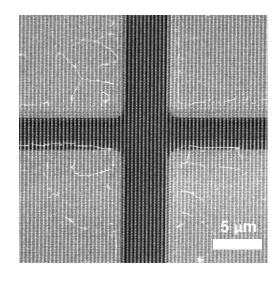

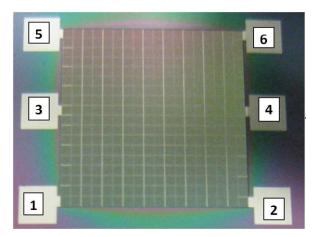

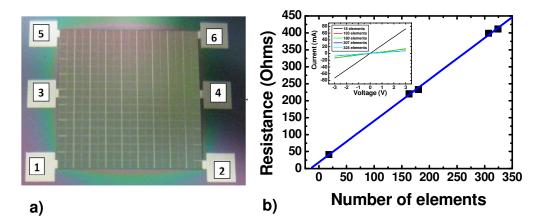

Figure 5.8: a) Photograph taken of the fabricated SiNW-based TED, and b) measured plot of resistance as function of the number of elements connected in series. The inset shows the I-V characteristics between the six measurement pads

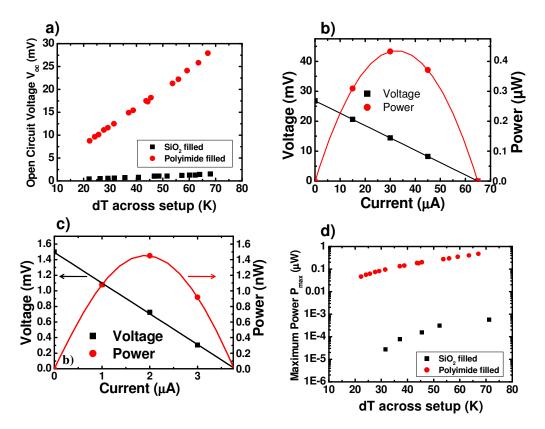

Figure 5.11: Relationship between a)  $V_{oc}$  and varying dT across the experimental setup, a voltage/power *versus* current curve for the b) SiO<sub>2</sub> filled TED, c) polyimide filled TED, at 70K across the experimental setup and d) a comparison between the maximum power output between the SiO<sub>2</sub> and polyimide filled TED

| under varying <i>dT</i> . The length of the SiNW with SiO <sub>2</sub> filler was 0.85µm as compared to 1.1µm with polyimide filler (shown in Figure 5.12)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

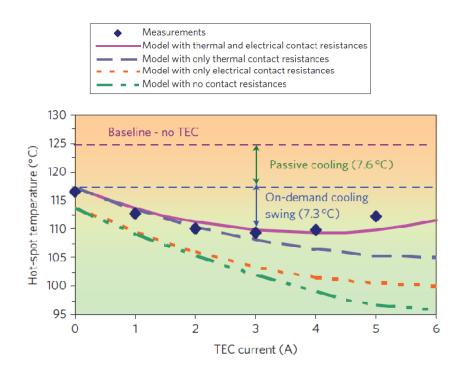

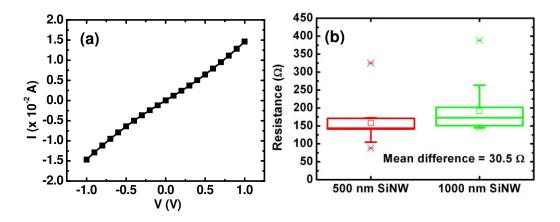

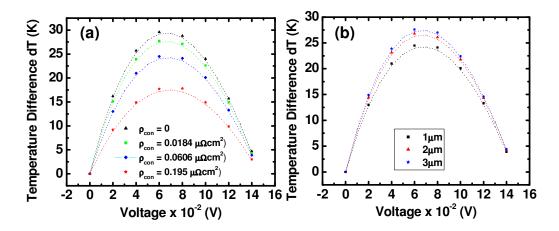

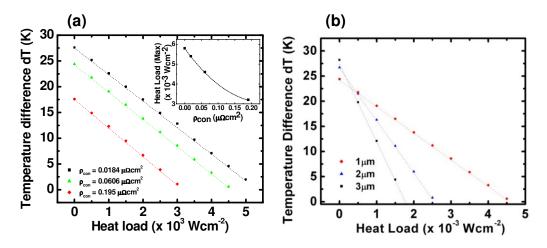

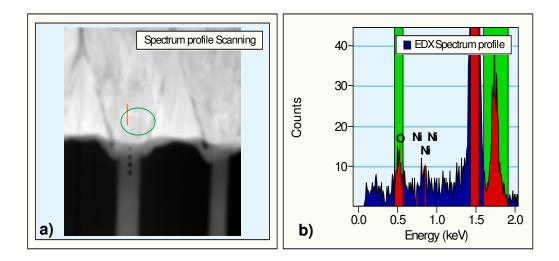

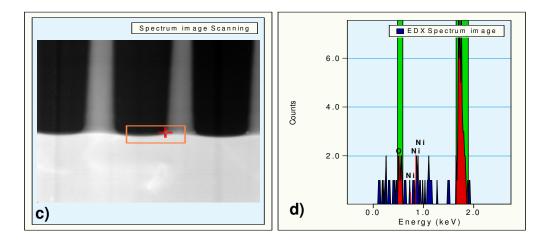

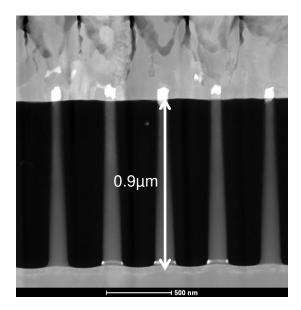

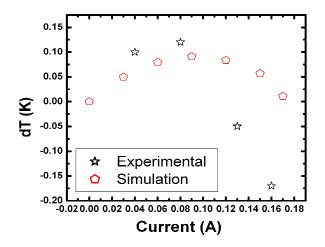

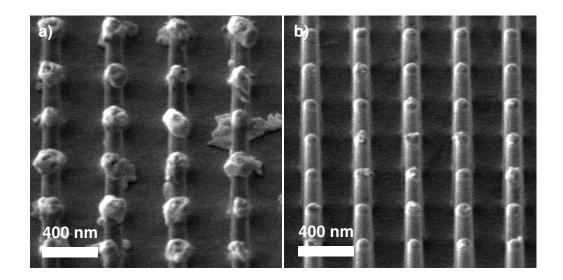

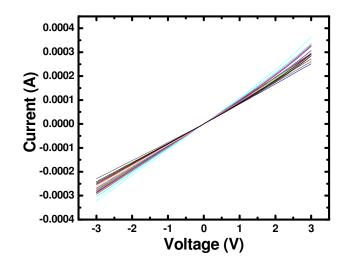

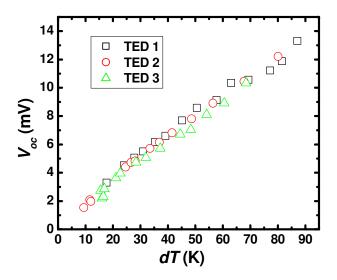

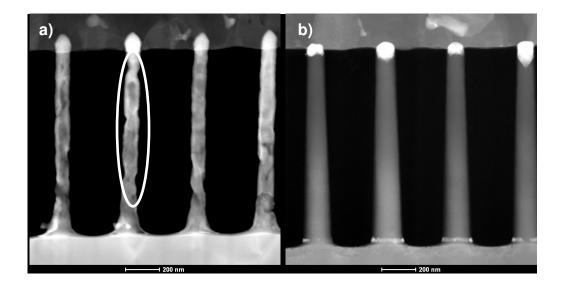

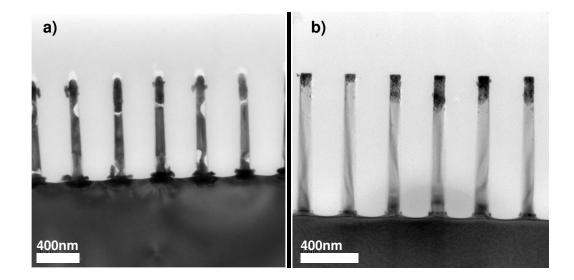

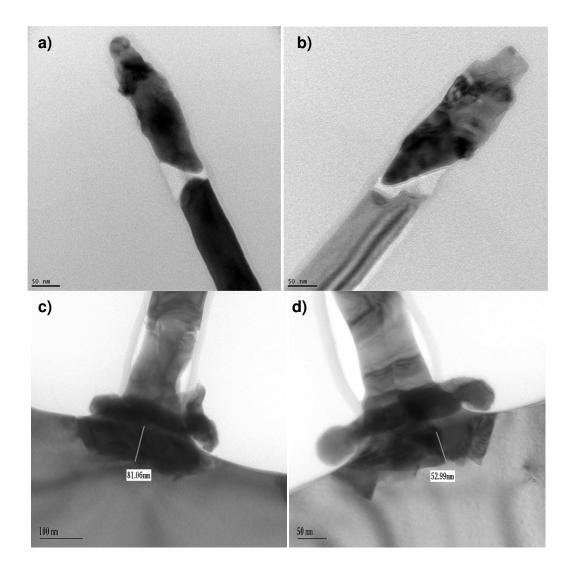

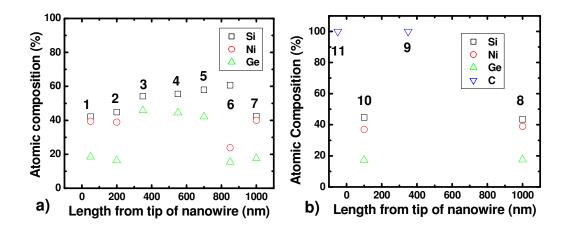

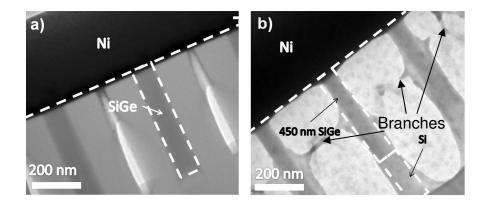

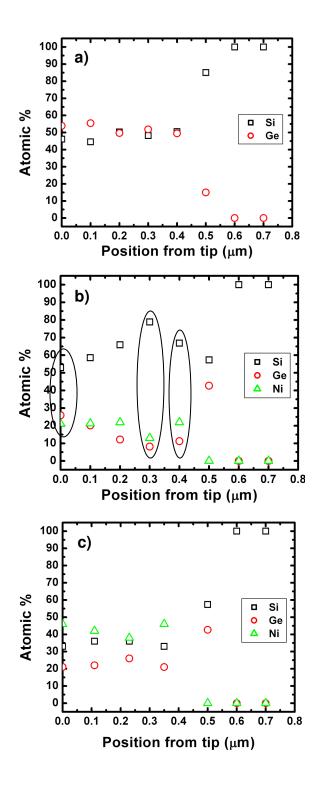

| polyimide filled SiNW-based TEDs respectively.118Figure 5.13: a) and b) show the TEM image zoom in at the tip and the EDX resultrespectively; c) and d) show the same analysis at the SiNW bottom.121Figure 5.14: TEM image of the optimized TED's cross section showing desiredNi silicide thickness of ~100nm.122Figure 5.15: Simulated cooling performance curve of the SiNW-based TED withthe optimized contact. The curve is a polynomial fit of all the data points.125Figure 5.16: IR images of the TED as the current through it was varied. The "star"on the image represented the spot where the surface temperature was monitored126Figure 5.17: Graph comparing the measured result with that of simulation ascurrent varies127Figure 6.1: SEM images of (a) SiGe NW, and (b) SiNW for comparison purpose132Figure 6.2: a) SEM image of the SiGe NW, and b) SiNW after annealing under400°C for 30s and having excessive nickel removed using SPM.133Figure 6.3: I-V measurements were shown because of the much largerelectrical resistance measured as compared to the SiNW-based TED.135Figure 6.4: Open circuit voltage ( $V_{oc}$ ) with varying temperature across theexperimental setup138Figure 6.5: Dark-field TEM images of the (a) SiGe NW and (b) SiNW.139Figure 6.7: TEM image showing the zoom in view of the SiGe NW array, andb) SiNW array139Figure 6.7: TEM images of the SiGe NW array. The labels indicated in the imageshows the area where EDX analysis was carried                                                                                                                                                                          |

| respectively; c) and d) show the same analysis at the SiNW bottom                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

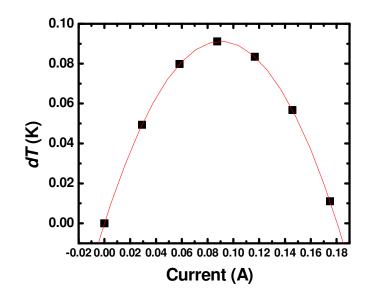

| Ni silicide thickness of ~100nm.       122         Figure 5.15: Simulated cooling performance curve of the SiNW-based TED with the optimized contact. The curve is a polynomial fit of all the data points.       125         Figure 5.16: IR images of the TED as the current through it was varied. The "star" on the image represented the spot where the surface temperature was monitored       126         Figure 5.17: Graph comparing the measured result with that of simulation as current varies.       127         Figure 6.1: SEM images of (a) SiGe NW, and (b) SiNW for comparison purpose       132         Figure 6.2: a) SEM image of the SiGe NW, and b) SiNW after annealing under 400°C for 30s and having excessive nickel removed using SPM.       133         Figure 6.3: I-V measurements of the SiGe NW-based TEDs across the whole wafer. A series of measurements were shown because of the much larger electrical resistance measured as compared to the SiNW-based TED.       135         Figure 6.4: Open circuit voltage (Voc) with varying temperature across the experimental setup       136         Figure 6.5: Dark-field TEM images of the (a) SiGe NW and (b) SiNW.       138         Figure 6.7: TEM images showing a zoom out view of the a) SiGe NW near the a) tip area 1, b) tip area 2, c) bottom area 1, and d) bottom area 2.       140         Figure 6.8: TEM images of the SiGe NW array. The labels indicated in the image shows the area where EDX analysis was carried out to find out the material composition of the structure.       141         Figure 6.9: TEM images of the SiGe NW array. The numbered red circles |

| the optimized contact. The curve is a polynomial fit of all the data points125<br>Figure 5.16: IR images of the TED as the current through it was varied. The "star"<br>on the image represented the spot where the surface temperature was monitored<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| on the image represented the spot where the surface temperature was monitored                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| current varies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Figure 6.2: a) SEM image of the SiGe NW, and b) SiNW after annealing under $400^{\circ}$ C for 30s and having excessive nickel removed using SPM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 400°C for 30s and having excessive nickel removed using SPM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| wafer. A series of measurements were shown because of the much larger electrical resistance measured as compared to the SiNW-based TED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| experimental setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Figure 6.6: TEM image showing a zoom out view of the a) SiGe NW array, and<br>b) SiNW array                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| <ul> <li>b) SiNW array</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| tip area 1, b) tip area 2, c) bottom area 1, and d) bottom area 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| shows the area where EDX analysis was carried out to find out the material composition of the structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| out the material composition of the structure. a) spot $1 - 7$ , and b) spot $8 - 11$ (indicated)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

Figure 6.11: TEM image of the prepared samples (a) with the SiO<sub>2</sub> filler intact, and (b) with the SiO<sub>2</sub> filler removed. In figure 6.11 (a), the bright spots are the air gaps which cannot be filled completely by the SiO<sub>2</sub> while in figure 6.11 (b), the observed "branches" are residues of the SiO<sub>2</sub> after the etching process. The darker and lighter contrast along the SiGe NW indicated the SiGe and Si portion respectively.

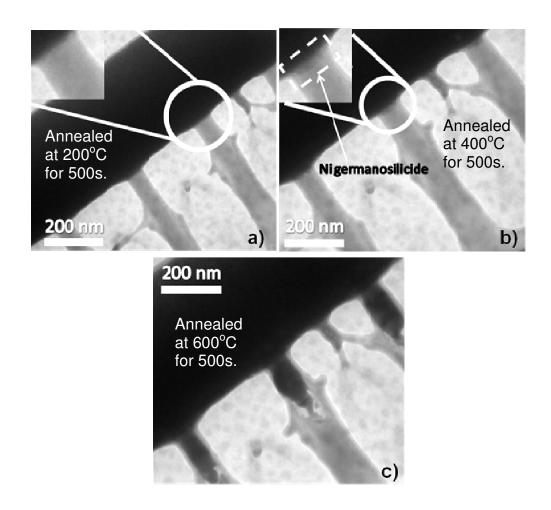

Figure 6.12: TEM images of the SiGe NW sample (without compressive stress) annealed at (a) 200°C, (b) 400°C, and (c) 600°C for 500s. The insets of figure 6.12 (a) and (b) are the magnified view of the SiGe NW near the tip area, which indicated minimal growth of the Ni-germanosilicide at 200°C and 400°C. ......146

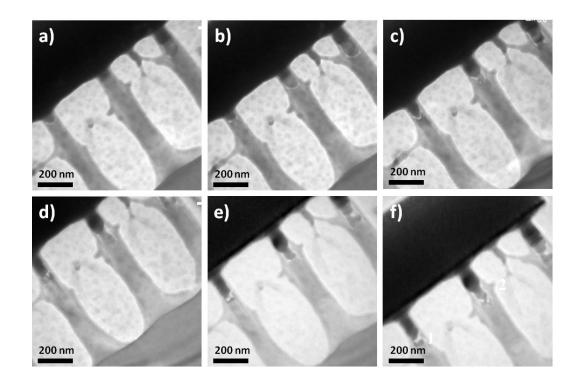

Figure 6.13: TEM images of the SiGe NW at times (a) 10 s, (b) 50 s, (c) 100 s, (d) 150 s, (e) 200 s, and (f) 250 s in the course of annealing ( $600^{\circ}$ C).....147

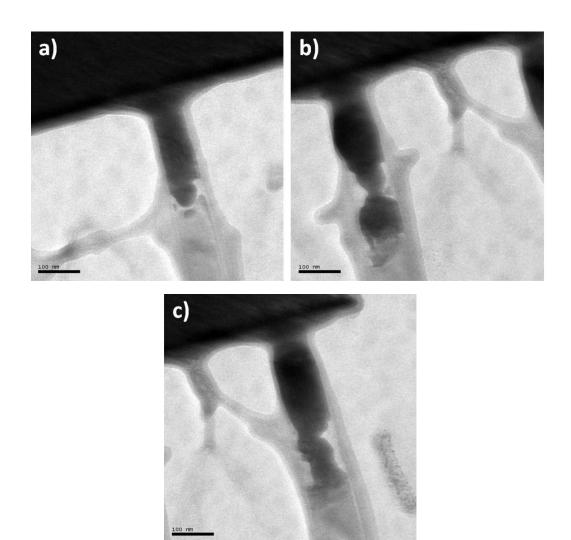

Figure 6.14: TEM images showing the magnified view of the three SiGe NW labeled (a) 1, (b) 2 and (c) 3 in Figure 6.13 (f) after the annealing process. ......148

Figure 6.17: Schematic illustrating the formation of Ni-germanosilicide in SiGe NW without  $SiO_2$  shell encapsulation. a) During annealing, Ni and SiGe interdiffuse to form b) Ni-germanosilicide. c) Considering Ge atoms being the dominant diffusion species, a neck in the Ni-germanosilicide starts to form with bulging near the tips. d) Due to the lack of restriction to the out-diffusion of the Ge atoms, the neck formed constricted further while the Ni-germanosilicide further expands into the surrounding, and e) upon prolonged annealing, a break occurs in the SiGe NW.

## List of Symbols

| 1-D   | One-dimensional                         |

|-------|-----------------------------------------|

| BARC  | Bottom anti reflection coating          |

| BOX   | Bottom oxide                            |

| CLT   | Central limit theorem                   |

| CMOS  | Complementary metal oxide semiconductor |

| СОР   | Coefficient of performance              |

| CVD   | Chemical vapor deposition               |

| DOS   | Density of states                       |

| DRIE  | Dry reactive ion etching                |

| DUV   | Deep ultraviolet                        |

| EBL   | Electron beam lithography               |

| EDX   | Energy dispersive x-ray spectroscopy    |

| FEA   | Finite element analysis                 |

| IMD   | Implantable medical device              |

| IR    | Infra-red                               |

| LPCVD | Low pressure chemical vapor deposition  |

| MC      | Monte carlo                           |

|---------|---------------------------------------|

| MD      | Molecular dynamics                    |

| METS    | Micro-electrothermal system           |

| PCB     | Printed circuit board                 |

| PID     | Proportional-integral-derivative      |

| RTD     | Resistance temperature detector       |

| SiNW    | Silicon nanowire                      |

| SiGe NW | Silicon-germanium nanowire            |

| SEM     | Scanning electron microscope          |

| SOI     | Silicon-on-insulator                  |

| TCR     | Temperature coefficient of resistance |

| TED     | Thermoelectric device                 |

| TEC     | Thermoelectric cooler                 |

| TEG     | Thermoelectric power generator        |

| TEM     | Transmission electron microscope      |

| TIM     | Thermal interface material            |

| VLS     | Vapor liquid solid                    |

### **Chapter 1: Introduction**

The thermoelectric phenomenon has been an active area of research since the discovery of the Seebeck and Peltier effects in the 1800s. This phenomenon was first explained by Seebeck where an electrical voltage is generated in a conducting material that is subjected to a temperature gradient. 12 years later, Peltier discovered that a temperature change occurs at the vicinity of a junction between dissimilar conductors when a current is passed. Subsequently, from the development of thermodynamics, Lord Kelvin established a relationship between both effects and predicted a third thermoelectric effect known as the Thomson effect [1.1]. This effect relates to the heating/cooling in a homogeneous conductor when a current is passed in the presence of a temperature gradient.

A thermoelectric material is characterized by a figure of merit  $ZT = \frac{S^2 \sigma}{\kappa}T$ , where *S*,  $\sigma$ , and  $\kappa$  represent the Seebeck coefficient, electrical conductivity, and thermal conductivity respectively. A good thermoelectric material should possess a high Seebeck coefficient and electrical conductivity to reduce ohmic losses while having a low thermal conductivity to prevent unwanted heat flow between the two junctions. In the early days, researchers focused on metal/metal alloys and found that most of them possess a Seebeck coefficient less than  $10\mu$ V/K. This resulted in an efficiency of a fraction of 1%. It was only in the 1930s when semiconductors were found to be much better thermoelectric materials with Seebeck coefficients > $100\mu$ V/K. In addition, the electrical conductivity can be controlled with doping which results in a much larger ZT value, and hence the focus shifted to semiconductors thereafter.

A modern TED design is made up of alternating n- and p- type semiconductors which are connected electrically in series and thermally in parallel as shown in Figure 1.1. Such a design improves the thermoelectric effect greatly as opposed to using solely n- or p- type thermoelectric legs [1.2].

Figure 1.1: Alternating n- and p- type thermoelectric legs in a device (HIS GlobalSpec CR4, 2013)

Established thermoelectric materials used in a TED are generally grouped into three categories depending upon their operating range of temperature. They are namely Bismuth telluride and its alloys, lead telluride and its alloy, and silicon germanium alloy. Bismuth telluride alloys are extensively used in refrigeration with a maximum operating temperature of ~450K while Lead telluride and silicon germanium are commonly used for power generation with an operating temperature >1000K. A comparison of the thermoelectric efficiencies as a function of *ZT* and operating temperature are compared to several heat engines in Figure 1.2.

Figure 1.2: Relation of *ZT* with the efficiency of heat engine [1.3]

It can be seen that in order for TED to contend with large scale power production technology, a ZT in excess of 4 is needed. However, commercial bismuth telluride and its alloys based TED have a ZT of ~1. Hence, more efficient materials are needed before a TED it can compete at the same level [1.3].

In the early 1990s, low dimensional (D) materials – 2-D quantum well, 1-D quantum wire/nanowire (NW), and 0-D quantum dot were theoretically predicted to have enhanced *ZT* as compared to their bulk counterpart due to the quantum confinement effect [1.4-1.5]. However, experimental work on such systems was limited by technology at that time. The availability of new methods for nanostructure synthesis, complemented with the use of powerful analysis tools such as scanning electron microscope (SEM) and transmission electron microscope, resulted in a spate of studies involving such class of nanostructures [1.6-1.8].

1-D nanoscale NW with its unusual mechanical, optical, electrical, and thermal properties holds potential in the area of thermoelectrics. Depending on its size at the nanoscale, the thermal conductivity of NW is modified greatly from its bulk counterpart [1.8]. The thermal conductance suppression is primarily due to two reasons. Firstly, there is increased phonon boundary scattering as the diameter reduces to the order of the phonon mean free path in the bulk material (tens to hundreds of nm) [1.7]. Secondly, the size confinement of a NW modifies the phonon frequency *versus* wave-vector dispersion relation from that of the bulk material [1.9]. This will lead to the discovery of much more efficient thermoelectric materials. Complementary-metal-oxide-semiconductor (CMOS) compatible semiconductor NW such as silicon (Si), silicon-germanium (SiGe) alloy, germanium (Ge) etc., are particularly attractive due to the availability of established processing technology for large scale fabrication. This is supplemented by two highly interesting works on SiNW which reported tremendous improvement in the ZT value of two orders of magnitude as compared to bulk Si [1.10-1.11].

The promise of NW as an efficient thermoelectric material makes it a potential replacement for commercially used bismuth telluride and its alloys. Two interesting areas of implementations are on-chip cooling or miniaturize power source. Due to aggressive transistor scaling, the emergence of hot spots (typical size –  $400\mu$ m x  $400\mu$ m) on a microprocessor chip becomes prevalent, and brings about the need to dissipate it so as to retain performance [1.2]. SiNW being able

to scale to appropriate size and target hot spots directly is much more efficient compared to conventional fan cooling [1.12].

Furthermore, a NW-based TED can be possibly used to provide a continuous and uninterrupted source of power for miniaturized devices, for example, as a wearable electronics such as watches, and implantable medical devices (IMDs). Low powered wearable watch and IMD such as a cardiac pacemaker typically requires a power supply in the region of tens to hundreds of  $\mu$ W [1.13-1.14]. It was experimentally measured that power harvested from body heat can exceed 80 $\mu$ W/cm<sup>2</sup> [1.13]. Hence, a SiNW-based TED which is efficient enough to harvest sufficient power (tens of  $\mu$ W) from body heat could be a potential candidate for low powered devices.

The potentials of Si/SiGe NW as a thermoelectric material, and how it can be applied in real applications deserve further investigation. Hence, this thesis aims to develop a fabrication method to assemble Si/SiGe NW into a complete TED, as well as to evaluate the suitability of the Si/SiGe NW-based TED in practical power generation and cooling applications. This thesis is organized as follows. In Chapter 2, the concepts of thermoelectricity are introduced, focusing on the underlying physics of 1-D NW. In addition, the development of micro scale TEDs is presented. In Chapter 3, we present the potential of SiNW as a TEC through finite element analysis (FEA) simulation. The impact of key material parameters in the performance was investigated, followed by a design guideline for a complete SiNW-based TEC. In Chapter 4, we fully describe the fabrication steps of a Si/SiGe NW-based TED using CMOS process; this includes the

5

problems encountered and the mitigating solutions. Following, Chapter 5 discusses the characterization methodology of the fabricated SiNW-based TED. This includes the thermal measurement of individual SiNW using a home-made micro-electrothermal system (METS) device, as well as power generation/cooling measurements at the device level. Chapter 6 on the other hand, focuses on the characterization of a SiGe NW-based TED, and the investigation of the growth mechanism of nickel-germanosilicide in SiGe NW. Finally in Chapter 7, the thesis will be concluded with proposed future works that can be carried out to further understand and optimize the Si/SiGe NW-based TED's performance for future implementation.

### References

[1.1] H. J. Goldsmid, CRC Handbook of Thermoelectrics, D. M. Rowe, Ed. Boca Raton, FL: CRC Press, 1995

[1.2] G. J. Snyder, M. Soto, R. Alley, D. Koester, and B. Conner, "Hot Spot Cooling using Embedded Thermoelectric Coolers", Nextreme Thermal Solutions, RTI, IEEE Semi-Therm Symposium, 2006

[1.3] Thermoelectric generators, J. M. Weisse, Stanford University, 2010, retrieved from http://large.stanford.edu/courses/2010/ph240/weisse1/ on 5<sup>th</sup> April 2013

[1.4] L. D. Hicks, and M. S. Dresselhaus, "Thermoelectric figure of merit of a onedimensional conductor", Physical Review B, v. 47, n. 24, pp. 16631 – 16634, June 1993

[1.5] L. D. Hicks, and M. S. Dresselhaus, "Effect of quantum-well structures on the thermoelectric figure of merit", Physical Review B, v. 47, n. 19, pp. 12727 – 12731, May 1993

[1.6] Y. Xia, P. Yang, Y. Sun, Y. Wu, B. Mayers, B. Gates, Y. Yin, F. Kim, H. Yan, "One-Dimensional Nanostructures: Synthesis, Characterization, and Applications", Adv. Mater., v. 15, n. 5, pp. 353 – 389, March 2003

[1.7] S. G. Volz, and G. Chen "Molecular dynamics simulation of thermal conductivity of silicon nanowires", Appl. Phys. Lett., v. 75, n. 14, 2056, October 1999

[1.8] D. Li, Y. Wu, P. Kim, L. Shi, P. Yang, and A. Majumdar, "Thermal conductivity of individual silicon nanowires", Appl. Phys. Lett., v. 83, n. 14, pp. 2934–2936, October 2003

[1.9] A. Khitun, A. Balandin, and K. L. Wang, "Modification of the Lattice Thermal Conductivity in Silicon Quantum Wires due to Spatial Confinement of Acoustic Phonons", Superlatt. Microstruct., v. 26, n. 3, pp. 181 – 193, September 1999

[1.10] A. I. Hochbaum, R.Chen, R. D. Delgado, W. Liang, E. C. Garnett, M. Najarian, A. Majumdar, and P. Yang, "Enhanced thermoelectric performance of rough silicon nanowires", Nature, v. 451, n. 7175, pp. 163–167, January 2008

[1.11] A. I. Boukai, Y. Bunimovich, J. T. Kheli, J. K. Yu, W. A. Goddard, and J. R. Heath, "Silicon nanowires as efficient thermoelectric materials, Nature", vol. 451, no. 7175, pp. 168–171, January 2008

[1.12] I. Chowdhury, R. Prasher, K. Lofgreen, G. Chrysler, S. Narasimhan, R. Mahajan, D. Koester, R. Alley, and R. Venkatasubramanian, "On-chip cooling by superlatticebased thin-film thermoelectric", Nature Nanotechnology, v 4, p 235, January 2009

[1.13] V. Leonov, and R. J. M. Vullers, "Wearable thermoelectric generators for body powered devices", J. of Electronics Mat., v. 38, n. 7, pp. 1491 – 1498, Jan. 2009

[1.14] Y Yang, X. J. Wei, and J. Liu, "Suitability of a thermoelectric power generator for implantable medical electronic devices", J. Phys. D, v. 40., n. 18, July 2007

## **Chapter 2: Concepts and Development of Thermoelectricity in One-Dimensional Nanowire**

In this chapter, the concepts of thermoelectricity and its relevance in onedimensional (1-D) nanostructures, in particular, silicon (Si), silicon-germanium (Ge), and germanium (Ge) nanowire (NW) will be presented. The thermoelectric parameters that characterize a thermoelectric device (TED) will first be discussed, followed by the thermoelectric transport (electronic and thermal), and engineering efforts of a thermoelectric material. In addition, the developments of Si/SiGe/Ge NW in reported theoretical and experimental works will be reviewed. The discussion on theoretical efforts includes the prediction and optimization of the thermoelectric properties via modeling and simulations. On the other hand, the discussion on experimental works will focus on the methods of synthesizing Si/SiGe/Ge NW, the measurement technique, and the results. Lastly, the development of micro/nano scale TED will be touched on.

### 2.1 Thermoelectric efficiency

The performance of a thermoelectric material is universally recognized to be dependent on a special parameter known as the figure of merit Z given in Equation 2.1 [2.1].

$$Z = \frac{S^2 \sigma}{\kappa} - (2.1)$$

where *S*,  $\sigma$ , and  $\kappa$  refer to the Seebeck coefficient, electrical conductivity, and thermal conductivity, respectively. A thermoelectric material has the ability to transport heat (refrigeration), or to generate a potential difference across its two ends (power generation), depending on the type of input energy supplied (thermal or electrical). In refrigeration mode, the coefficient of performance (COP) is the characterizing parameter while in power generation mode, the conversion efficiency ( $\eta$ ) is of interest; both the COP and  $\eta$  and are related to *Z*. The following discussion on the COP and  $\eta$  will be made on a thermocouple – two alternately doped n- and p- type thermoelectric legs connected electrically in series and thermally in parallel (Figure 2.1). It is worth pointing out that the number of thermoelectric legs will not affect the overall efficiency of the device; it only affects the amount of useful work output. In the following analysis, temperature independent thermoelectric parameters are used.

Figure 2.1: A thermocouple with n- and p- type thermoelectric legs connected in series

#### **2.1.1** Coefficient of Performance (COP)

COP determines the cooling efficiency of conventional refrigeration as well as a thermoelectric cooler (TEC) [2.2-2.6]. The COP of a refrigerator is defined as the ratio of the maximum heat (Q) that can be removed and the input power (W) supplied to the device as:

$$COP = \frac{Q}{W} - (2.2)$$

A simple illustration of the COP: if 1 W of power is required to be removed by a TEC with a COP of 0.5, 2 W of input power is needed; this translates to a total of 3 W of heat to be removed. From a mathematical perspective, considering the thermocouple illustrated in Figure 2.1, the total amount of power W supplied to the n- and p- type thermoelectric legs with input current I is given by:

$$W_{total} = W_n + W_p = (S_p - S_n)I(T_2 - T_1) + I^2 R^{--} (2.3)$$

where the subscript refers to the doping type and R refers to the total electrical resistance of the thermocouple. Given the amount of heat that can be removed from the cold side:

$$Q = \left(S_p - S_n\right)IT_1 - \frac{1}{2}I^2R - K(T_2 - T_1) - (2.4)$$

the *COP* as a function of *Z* is derived as:

$$COP = \frac{Q}{W} = \frac{(S_p - S_n)IT_1 - \frac{1}{2}I^2R - K(T_2 - T_1)}{(S_p - S_n)I(T_2 - T_1) + I^2R} \dots (2.5)$$

by taking the derivative of COP with respect to I and setting it to zero, the maximum COP can be expressed as a function of Z:

$$COP_{max} = \frac{T_1 \left[ (1 + ZT_m)^{1/2} - T_2 / T_1 \right]}{(T_2 - T_1) \left[ (1 + ZT_m)^{1/2} + 1 \right]} \dots (2.6)$$

where  $T_m = (T_1 + T_2)/2$  is the mean temperature of the two ends. It can be seen that apart from the temperature difference at the two ends, the *Z* value is a main determinant of the COP.

### **2.1.2** Thermoelectric conversion efficiency $(\eta)$

The thermoelectric conversion efficiency  $\eta$  of a material is related to the product of the Carnot efficiency and Z [2.7]. Mathematically,  $\eta$  is defined as:

$$\eta = \frac{\text{Useful work done}}{\text{Total input energy}} -- (2.7)$$

To further illustrate, let us consider a load of resistance  $R_L$  connected across the thermocouple in Figure 2.1. In the presence of a temperature gradient ( $\Delta T = T_2 - T_I$ ), a potential difference is generated by the thermocouple and results in a total useful work *W* generated across  $R_L$ :

$$W = \left[\frac{(S_p - S_n)(T_2 - T_1)}{(R_L + R)}\right]^2 R_L - (2.8)$$

In supplying heat by the source, most of the heat is conducted to the sink through the thermocouple and some is used to balance the Peltier effect associated with the flow of current. According to Peltier's equation, half of the Joule heat from the thermoelectric legs will travel all the way to the source. With the inclusion of all the mentioned terms, q is expressed as:

$$q = K(T_2 - T_1) + (S_p - S_n)IT_2 - \frac{I^2 R}{2} - (2.9)$$